#### (19) World Intellectual Property Organization

International Bureau

###

## (43) International Publication Date 11 June 2009 (11.06.2009)

# (10) International Publication Number WO 2009/072104 A2

(51) International Patent Classification: *G06F 12/02* (2006.01)

(21) International Application Number:

PCT/IL2008/001239

(22) International Filing Date:

17 September 2008 (17.09.2008)

(25) Filing Language: English

(26) Publication Language: English

(30) Priority Data:

| 60/996,782 | 5 December 2007 (05.12.2007) | US |

|------------|------------------------------|----|

| 61/006,805 | 31 January 2008 (31.01.2008) | US |

| 61/064,853 | 31 March 2008 (31.03.2008)   | US |

| 61/071,465 | 30 April 2008 (30.04.2008)   | US |

| 61/129,608 | 8 July 2008 (08.07.2008)     | US |

|            |                              |    |

(71) Applicant (for all designated States except US): DENS-BITS TECHNOLOGIES LTD. [IL/IL]; Building 30, Flr 3, Matam Industrial Park, P.O.Box 15111, 31015 Haifa (IL).

- (72) Inventors; and

- (75) Inventors/Applicants (for US only): WEINGARTEN, Hanan [IL/IL]; Hayarden 2, 46377 Herzliya (IL). LEVY,

Shmuel [IL/IL]; 9 Fish Street, 36025 Tivon (IL). KATZ, Michael [IL/IL]; 75 Moriah Ave., 34616 Haifa (IL).

- (74) Agent: PEARL COHEN ZEDEK LATZER; 5 Shenkar Street, P.O. Box 12704, Herzlia 46733 (IL).

- (81) Designated States (unless otherwise indicated, for every kind of national protection available): AE, AG, AL, AM, AO, AT, AU, AZ, BA, BB, BG, BH, BR, BW, BY, BZ, CA, CH, CN, CO, CR, CU, CZ, DE, DK, DM, DO, DZ, EC, EE, EG, ES, FI, GB, GD, GE, GH, GM, GT, HN, HR, HU, ID, IL, IN, IS, JP, KE, KG, KM, KN, KP, KR, KZ, LA, LC, LK, LR, LS, LT, LU, LY, MA, MD, ME, MG, MK, MN, MW, MX, MY, MZ, NA, NG, NI, NO, NZ, OM, PG, PH, PL, PT, RO, RS, RU, SC, SD, SE, SG, SK, SL, SM, ST, SV, SY, TJ, TM, TN, TR, TT, TZ, UA, UG, US, UZ, VC, VN, ZA, ZM, ZW.

- (84) Designated States (unless otherwise indicated, for every kind of regional protection available): ARIPO (BW, GH, GM, KE, LS, MW, MZ, NA, SD, SL, SZ, TZ, UG, ZM, ZW), Eurasian (AM, AZ, BY, KG, KZ, MD, RU, TJ, TM), European (AT, BE, BG, CH, CY, CZ, DE, DK, EE, ES, FI, FR, GB, GR, HR, HU, IE, IS, IT, LT, LU, LV, MC, MT, NL, NO, PL, PT, RO, SE, SI, SK, TR), OAPI (BF, BJ, CF, CG, CI, CM, GA, GN, GQ, GW, ML, MR, NE, SN, TD, TG).

#### Published:

without international search report and to be republished upon receipt of that report

(54) Title: SYSTEMS AND METHODS FOR ERROR CORRECTION AND DECODING ON MULTI-LEVEL PHYSICAL MEDIA

(57) Abstract: A method for determining thresholds useful for converting cell physical levels into cell logical values in an array of digital memory cells storing physical levels which diminish over time, the method comprising determining extent of deterioration of the physical levels and determining thresholds accordingly for at least an individual cell in said array; and reading the individual cell including reading a physical level in the cell and converting the physical level into a logical value using the thresholds, wherein the determining comprises storing predefined physical levels rather than data-determined physical levels in each of a plurality of cells and computing extent of deterioration by determining deterioration of the predefined physical levels.

# FLASH MEMORY DEVICE WITH PHYSICAL CELL VALUE DETERIORATION ACCOMMODATION AND METHODS USEFUL IN CONJUNCTION THEREWITH

#### 5 REFERENCE TO CO-PENDING APPLICATIONS

10

15

20

25

30

Priority is claimed from the following co-pending applications: US Provisional Application No. 60/996,782, filed December 5, 2007 and entitled "Systems and Methods for Using a Training Sequence in Flash Memory", US Provisional Application No. 61/064,853, filed March 31, 2008 and entitled "Flash Memory Device with Physical Cell Value Deterioration Accommodation and Methods Useful in Conjunction Therewith", US Provisional Application No. 61/006,805, filed January 31, 2008 and entitled "A Method for Extending the Life of Flash Devices", US Provisional Application No. 61/071,465, filed April 30, 2008 and entitled "Systems and Methods for Temporarily Retiring Memory Portions" and US Provisional Application No. 61/129,608, filed July 8, 2008 and entitled "A Method for Acquiring and Tracking Detection Thresholds in Flash Devices".

Other co-pending applications include: US Provisional Application No. 60/960,207, filed September 20, 2007 and entitled "Systems and Methods for Coupling Detection in Flash Memory", US Provisional Application No. 61/071,467, filed April 30, 2008 and entitled "Improved Systems and Methods for Determining Logical Values of Coupled Flash Memory Cells", US Provisional Application No. 60/960,943, filed October 22, 2007 and entitled "Systems and methods to reduce errors in Solid State Disks and Large Flash Devices" and US Provisional Application No. 61/071,469, filed April 30, 2008 and entitled "Systems and Methods for Averaging Error Rates in Non-Volatile Devices and Storage Systems", US Provisional Application No. 60/996,027, filed October 25, 2007 and entitled "Systems and Methods for Coping with Variable Bit Error Rates in Flash Devices", US Provisional Application No. 61/071,466, filed April 30, 2008 and entitled "Systems and Methods for Multiple Coding Rates in Flash Devices", US Provisional Application No. 61/006,120, filed December 19, 2007 and entitled "Systems and Methods for Coping with Multi Stage Decoding in Flash Devices", US Provisional

5

10

15

20

25

30

Application No. 61/071,464, filed April 30, 2008 and entitled "A Decoder Operative to Effect A Plurality of Decoding Stages Upon Flash Memory Data and Methods Useful in Conjunction Therewith", US Provisional Application No. 61/006,385, filed January 10, 2008 and entitled "A System for Error Correction Encoder and Decoder Using the Lee Metric and Adapted to Work on Multi-Level Physical Media", US Provisional Application No. 61/064,995, filed April 8, 2008 and entitled "Systems and Methods for Error Correction and Decoding on Multi-Level Physical Media", US Provisional Application No. 60/996,948, filed December 12, 2007 and entitled "Low Power BCH/RS Decoding: a Low Power Chien-Search Implementation", US Provisional Application No. 61/071,487, filed May 1, 2008 and entitled "Chien-Search System Employing a Clock-Gating Scheme to Save Power for Error Correction Decoder and other Applications", US Provisional Application No. 61/071,468, filed April 30, 2008 and entitled "A Low Power Chien-Search Based BCH/RS Recoding System for Flash Memory, Mobile Communications Devices and Other Applications", US Provisional Application No. 61/006,806, filed January 31, 2008 and entitled "Systems and Methods for using a Erasure Coding in Flash memory", US Provisional Application No. 61/071,486, filed May 1, 2008 and entitled "Systems and Methods for Handling Immediate Data Errors in Flash Memory", US Provisional Application No. 61/006,078, filed December 18, 2007 and entitled "Systems and Methods for Multi Rate Coding in Multi Level Flash Devices", US Provisional Application No. 61/064,923, filed April 30, 2008 and entitled "Apparatus For Coding At A Plurality Of Rates In Multi-Level Flash Memory Systems, And Methods Useful In Conjunction Therewith", US Provisional Application No. 61/064,760, filed March 25, 2008 and entitled "Hardware efficient implementation of rounding in fixed-point arithmetic", US Provisional Application No. 61/071,404, filed April 28, 2008 and entitled "Apparatus and Methods for Hardware-Efficient Unbiased Rounding", US Provisional Application No. 61/136,234, filed August 20, 2008 and entitled "A Method Of Reprogramming A Non-Volatile Memory Device Without Performing An Erase Operation", US Provisional Application No. 61/129,414, filed June 25, 2008 and entitled "Improved Programming Speed in Flash Devices Using Adaptive Programming", and several other co-pending patent applications being filed concurrently (same day).

#### FIELD OF THE INVENTION

The present invention relates generally to flash memory devices and more particularly to generating threshold values for use when reading flash memory devices.

5

10

15

20

#### BACKGROUND OF THE INVENTION

A variety of conventional flash memory devices are described in the following US Patents and patent documents: USP 6,751,766; USP 7,196,946; USP 7,203,874; US 2006/0101193 A1; US 2007/0180346 A1.

The state of the art is believed to be described by the following publications inter alia:

- [1] "Interleaving policies for flash memory", United States Patent 20070168625

- [2] "Minimization of FG-FG coupling in flash memory", United States Patent 6996004

- [3] Construction of Rate (n-1)/n Punctured Convolution Code with Minimum Required SNR Criterion, Pil J. Lee, IEEE Trans. On Comm. Vol. 36, NO. 10, Oct. 1988

- [4] "Introduction to Coding Theory", Ron M. Roth, Cambridge University Press, 2006, particularly chapters 5 and 8 re BCH.

The disclosures of all publications and patent documents mentioned in the specification, and of the publications and patent documents cited therein directly or indirectly, are hereby incorporated by reference.

#### SUMMARY OF THE INVENTION

5

10

15

20

25

30

Nowadays, flash memory devices store information with high density on Flash cells with ever-decreasing dimensions. In addition, Multi-Level Cells (MLC) store several bits per cell by setting the amount of charge in the cell. The amount of charge is then measured by a detector, calculated by a threshold voltage of the transistor gate. Due to inaccuracies during the programming procedure and charge loss due to time and temperature (also known as retention), the measured levels during a Read operation suffer from detection errors. The small dimensions of the Flash cells result in cells that can store very small amounts of charge, enhancing the effects of inaccuracies due to programming and retention. Thus, new single level cells (SLC) and Multi-Level Cell (MLC) devices have significantly increased bit error rate (BER), decreasing the reliability of the device.

Flash devices are organized into (physical) pages. Each page contains a section allocated for data (512 bytes-4K bytes) and a small number of bytes (16-32 bytes for every 512 data bytes) dedicated to redundancy and management information. The redundancy bytes are used to store error correcting information, for correcting errors which may have occurred up to and during the page Read. Each Read operation and each Write operation is performed on an entire page. A number of pages are grouped together to form an Erase Block (EB). A page cannot be erased unless the entire erase block which contains it is erased.

An important measure of a Flash device quality is the number of times (Np) it may be reprogrammed and the period (usually 10 years) that it can store data before irrecoverable errors occur. The higher the number of program-erase cycles, the higher the bit error rate. Thus, today's Multi-Level Cell(MLC) devices can perform around Np=1000 cycles for 10 year retention before the allocation of 16-32 bytes of redundancy per 512 bytes of data bytes becomes insufficient to correct errors. Single level cell (SLC) devices usually perform better but obtain a much lower density and hence their prices are much higher. Following Np program-erase cycles the device is still operational but the bit error rate is higher. Furthermore, in many devices (e.g.

NROM Flash devices), this behavior is predictable and it can be shown that the number of redundancy bytes required to correct these errors does not jump rapidly.

The reliability of a specific page or erase block is not known because, among others, the retention time is not known prior to reading, hence the decoding parameters are not known. Using a single decoding scheme may result in poor read performance (read time and power consumption). The ECC complexity may be designed for the end of life conditions and may force higher complexity decoding for pages that are more reliable or at the beginning of life.

5

10

15

20

25

Certain embodiments of the present invention seek to provide an improved flash memory device and improved methods for determining thresholds for use in reading from cells of the device. In some embodiments of the present invention, a set of representative cells is designated for monitoring deterioration, relative to highly reliable cells which store statistics (e.g. mean and/or standard deviation or even raw values) of the set of representative cells as originally programmed i.e. before deterioration. Cells may be adapted to be reliable e.g. by using them as single level cells and/or by using high-level error correction code. The set of representative cells may be set aside and not used for data ("controlled' embodiments) or the set of representative cells is not set aside; instead, the representative cells are pre-designated ("earmarked") ones from among the normal data cells and are used throughout to store normal, uncontrolled data ("blind" embodiments).

In some embodiments, only one set of representative cells is designated for each erase sector, as opposed to embodiments in which each and every page in the erase sector has its own set of representative cells. In the former, per-erase sector embodiments, typically, a reliably stored indicator ("offset cell") in each page indicates the interval of time which elapsed between the programming of the per-erase sector representative cells and the programming of the page in question, thereby allowing retention time between the programming of a certain page and its reading to be obtained. Alternatively, in certain applications, all pages in each erase sector may be programmed at approximately the same time.

It is appreciated that optionally, typically to save memory which may be required for storing representative cell location information, representative cells may be provided at a uniform, predetermined location within each page or each erase sector, such as at the beginning of each page, or at the beginning of each first page in each erase sector.

In controlled embodiments, the representative cells may be programmed with only a few levels, perhaps even only one. They are then read with high accuracy, which is generally time-consuming, in order to compute and store a deterioration-affected statistic thereof such as but not limited to a mean. Alternatively, to save reading time, the representative cells may be programmed with a more complex "ramp" or range of almost continuous values corresponding in size to the maximum extent of deterioration. For example, if the flash memory device is intended for use over a 10 year period over which the deterioration that may be expected to occur is 0.5 V at most, a range of values from 0 V to 0.5 V may be programmed into the representative cells. When reading takes place, it is then only necessary to determine how many of the cells lie below a certain value as opposed to above, however, the "ramp" embodiment may require more representative cells than its alternative.

Representative cells may be used to determine reading thresholds for each reading operation, so as to take into account the deterioration which may have taken place up until the time at which an individual reading operation happens to be taking place. For example, current values in the representative cells may be compared to the mean or other deterioration affected statistic of the representative cells which has been stored in reliable cells since the time of writing. The ratio between current and reliably stored statistics may be multiplied by an original reading threshold to obtain a new reading threshold which adapts to the deterioration that has occurred since the original threshold was determined. Alternatively, the representative cells may be used to compute a deterioration affected statistic such as a mean and a look up table may be used that associates this statistic with a retention time. Another look up table is used to return a set of new threshold values, for each retention time value obtained from the first table and each number of program/erase cycles.

Flash memory device cells are conventionally divided into 3 types:

5

10

15

20

25

1. Data cells: store the information for which the flash memory is being employed in the first place.

2. Management cells: store control information conventionally used by the micro-controller, such as Back pointers, ECC redundancy, back pointers, set of representative cells, training statistics, and training offset.

3. On-Time-Programming (OTP) cells: A set of constants determined in the course of production of the flash memory and conventionally used by the microcontroller 110, such as page size, representative base statistics, look-up tables.

There is thus provided, in accordance with at least one embodiment of the present invention, a method for converting a measured physical level of a cell into a logical value, in an array of memory cells storing physical levels which diminish over time, the method comprising determining extent of deterioration of the physical levels and determining thresholds accordingly for at least an individual cell in the array; and reading the individual cell including reading a physical level in said cell and converting said physical level into a logical value using at least some of said thresholds, wherein said determining extent of deterioration comprises storing predefined physical levels rather than data-determined physical levels in each of a plurality of cells and determining extent of deterioration by computing deterioration of said predefined physical levels.

It is appreciated that reading need not take place immediately after threshold determination. In general the order of operations and duration of time elapsing between operations shown and described herein is not intended to be limiting and can be determined at will in accordance with the particular demands of each application.

Further in accordance with at least one embodiment of the present invention, the predefined physical levels are maximum physical levels.

Still further in accordance with at least one embodiment of the present invention, determining extent of deterioration comprises determining deterioration of said

predefined physical levels and assuming that said deterioration is a known function of said physical levels.

Additionally in accordance with at least one embodiment of the present invention, the known function comprises a linear function.

Still further in accordance with at least one embodiment of the present invention, storing comprises storing said predefined physical levels in cells whose reliability is no different than the reliability of those cells in the array which are not used for storing said predefined physical levels.

5

10

15

20

25

Further in accordance with at least one embodiment of the present invention, said array comprises more than one erase sector, each of which includes a subset of cells which together undergo cycles affecting said extent of deterioration; and wherein said determining of said extent of deterioration is performed no more than once per erase sector.

Still further in accordance with at least one embodiment of the present invention, the array of digital memory cells comprises a plurality of pages characterized in that the cells within each page are written onto as a single operation and wherein said determining is performed no more than once per page.

Also provided, in accordance with at least one embodiment of the present invention, is a method for determining thresholds useful for converting cell physical levels into cell logical values in an array of digital memory cells storing physical levels which diminish over time, the method comprising determining extent of deterioration of the physical levels and determining thresholds accordingly for at least an individual cell in said array; and reading said individual cell including using reading a physical level in said cell and converting said physical level into a logical value using said thresholds.

Further in accordance with at least one embodiment of the present invention, determining comprises computing extent of deterioration by determining deterioration of said predefined physical levels in each of a plurality of cells.

Still further in accordance with at least one embodiment of the present invention, reading comprises binary reading and wherein said predefined physical levels comprise an ascending sequence of physical levels.

Further in accordance with at least one embodiment of the present invention, the ascending sequence is evenly spaced.

5

10

15

20

25

30

Still further in accordance with at least one embodiment of the present invention, the array comprises more than one erase sector, each of which includes a subset of cells which together undergo cycles affecting said extent of deterioration; wherein said determination of extent of deterioration comprises storing predefined physical levels rather than data physical levels in each of a plurality of cells and wherein said storing is performed no more than once per erase sector.

Further in accordance with at least one embodiment of the present invention, the physical levels comprise charge levels.

Also provided, in accordance with at least one embodiment of the present invention, is a computer program product comprising a computer useable medium having computer readable program code having embodied therein a method for determining thresholds useful for converting cell physical levels into cell logical values in an array of memory cells storing physical levels which diminish over time, said computer program product comprising computer readable program code for determining extent of deterioration of the physical levels and determining thresholds accordingly for at least an individual cell in said array; and reading said individual cell including using reading a physical level in said cell and converting said physical level into a logical value using said thresholds, wherein said determining comprises storing predefined physical levels rather than data-determined physical levels in each of a plurality of cells and computing extent of deterioration by determining deterioration of said predefined physical levels.

Also provided, in accordance with still another embodiment of the present invention, is a system for determining thresholds useful for converting cell physical levels into cell logical values in an array of memory cells storing physical levels which diminish over time, the system comprising deterioration determining apparatus

determining extent of deterioration of the physical levels and determining thresholds accordingly for at least an individual cell in said array; and reading circuitry operative to read said individual cell including reading a physical level in said cell and converting said physical level into a logical value using said thresholds, wherein said deterioration determining apparatus is operative to store predefined physical levels rather than data-determined physical levels in each of a plurality of cells and to compute extent of deterioration by determining deterioration of said predefined physical levels.

5

10

15

20

25

Still further provided, in accordance with yet another embodiment of the present invention, is a method for determining thresholds useful for converting cell physical levels into cell logical values in an array of memory cells storing physical levels which diminish over time, the method comprising determining extent of deterioration of the physical levels by comparing at least a central tendency of previous physical levels with at least a central tendency of current physical levels and determining thresholds accordingly for at least an individual cell in said array; and reading said individual cell including reading a physical level in said cell and converting said physical level into a logical value using said thresholds.

Also provided, in accordance with another embodiment of the present invention, is a method for determining thresholds useful for converting cell physical levels into cell logical values in an array of memory cells storing physical levels which diminish over time, the method comprising determining extent of deterioration of the physical levels and systematically determining thresholds accordingly for at least an individual cell in said array; and reading said individual cell including reading a physical level in said cell and converting said physical level into a logical value using said thresholds.

Further in accordance with at least one embodiment of the present invention, the systematic determination of thresholds comprises computation of thresholds.

Still further in accordance with at least one embodiment of the present invention, said computation assumes linearity of deterioration throughout the range of physical levels stored in individual cells in said array.

Additionally in accordance with at least one embodiment of the present invention, said computation does not assume linearity of deterioration throughout the range of physical levels stored in individual cells in said array.

Further in accordance with at least one embodiment of the present invention, said systematic determination of thresholds comprises use of a look-up table.

5

10

15

20

25

30

Also provided, in accordance with yet another embodiment of the present invention, is a method for determining thresholds useful for converting cell physical levels into cell logical values in an array of memory cells storing physical levels which diminish over time, the method comprising determining extent of deterioration of the physical levels and determining thresholds accordingly for at least an individual cell in said array; and reading said individual cell including reading a physical level in said cell and converting said physical level into a logical value using said thresholds, wherein said determining comprises reliably storing at least a central tendency of only a subset of original physical values of said array of memory cells and computing extent of deterioration by comparing, generally at the same time as reading, at least said central tendency of said subset of original physical values to at least a central tendency of corresponding current physical values.

Further in accordance with at least one embodiment of the present invention, determining extent of deterioration comprises determining deterioration of said predefined physical levels and assuming a known function of deterioration as a function of program/erase cycle number.

Still further in accordance with at least one embodiment of the present invention, determining extent of deterioration comprises determining deterioration of said predefined physical levels and assuming a known function of deterioration as a function of address of said predefined physical levels.

Also provided, in accordance with at least one embodiment of the present invention, is a computer program product comprising a computer useable medium having computer readable program code having embodied therein a method for determining thresholds useful for converting cell physical levels into cell logical values in an array of memory cells storing physical levels which diminish over time, said

computer program product comprising computer readable program code for determining extent of deterioration of the physical levels and determining thresholds accordingly for at least an individual cell in said array; and reading said individual cell including using reading a physical level in said cell and converting said physical level into a logical value using said thresholds.

5

10

15

20

25

30

Further provided, in accordance with at least one embodiment of the present invention, is a computer program product comprising a computer useable medium having computer readable program code having embodied therein a method for determining thresholds useful for converting cell physical levels into cell logical values in an array of memory cells storing physical levels which diminish over time, said computer program product comprising computer readable program code for determining extent of deterioration of the physical levels by comparing at least a central tendency of previous physical levels with at least a central tendency of current physical levels and determining thresholds accordingly for at least an individual cell in said array; and reading said individual cell including reading a physical level in said cell and converting said physical level into a logical value using said thresholds.

Also provided, in accordance with at least one embodiment of the present invention, is a computer program product comprising a computer useable medium having computer readable program code having embodied therein a method for determining thresholds useful for converting cell physical levels into cell logical values in an array of memory cells storing physical levels which diminish over time, said computer program product comprising computer readable program code for determining extent of deterioration of the physical levels and systematically determining thresholds accordingly for at least an individual cell in said array; and reading said individual cell including reading a physical level in said cell and converting said physical level into a logical value using said thresholds.

Additionally provided, in accordance with at least one embodiment of the present invention, is a computer program product comprising a computer useable medium having computer readable program code having embodied therein a method for determining thresholds useful for converting cell physical levels into cell logical values in an array of memory cells storing physical levels which diminish over time, said

computer program product comprising computer readable program code for determining extent of deterioration of the physical levels and determining thresholds accordingly for at least an individual cell in said array; and reading said individual cell including reading a physical level in said cell and converting said physical level into a logical value using said thresholds, wherein said determining comprises reliably storing at least a central tendency of only a subset of original physical values of said array of memory cells and computing extent of deterioration by comparing, generally at the same time as reading, at least said central tendency of said subset of original physical values to at least a central tendency of corresponding current physical values.

Further provided, in accordance with still another embodiment of the present invention, is a system for determining thresholds useful for converting cell physical levels into cell logical values in an array of memory cells storing physical levels which diminish over time, the system comprising deterioration determining apparatus determining extent of deterioration of the physical levels and determining thresholds accordingly for at least an individual cell in said array; and reading circuitry operative to read said individual cell including reading a physical level in said cell and converting said physical level into a logical value using said thresholds, wherein said array comprises more than one erase sectors, each of which including a subset of cells which together undergo cycles affecting said extent of deterioration; wherein said deterioration determining apparatus comprises apparatus for storing predefined physical levels rather than data physical levels in each of a plurality of cells, the apparatus for storing being characterized in that said storing is performed no more than once per erase sector.

Further provided, in accordance with at least one embodiment of the present invention, is a system for determining thresholds useful for converting cell physical levels into cell logical values in an array of memory cells storing physical levels which diminish over time, the system comprising deterioration determining apparatus determining extent of deterioration of the physical levels by comparing at least a central tendency of previous physical levels with at least a central tendency of current physical levels and determining thresholds accordingly for at least an individual cell in said array; and reading circuitry operative to read said individual cell including reading a

physical level in said cell and converting said physical level into a logical value using said thresholds.

Also provided, in accordance with at least one embodiment of the present invention, is a system for determining thresholds useful for converting cell physical levels into cell logical values in an array of memory cells storing physical levels which diminish over time, the system comprising deterioration determining apparatus determining extent of deterioration of the physical levels and systematically determining thresholds accordingly for at least an individual cell in said array; and reading circuitry operative to read said individual cell including reading a physical level in said cell and converting said physical level into a logical value using said thresholds.

5

10

15

20

25

30

Further provided, in accordance with at least one embodiment of the present invention, is a system for determining thresholds useful for converting cell physical levels into cell logical values in an array of memory cells storing physical levels which diminish over time, the system comprising deterioration determining apparatus determining extent of deterioration of the physical levels and determining thresholds accordingly for at least an individual cell in said array; and reading circuitry operative to read said individual cell including reading a physical level in said cell and converting said physical level into a logical value using said thresholds, wherein said deterioration determining apparatus is operative to reliably store at least a central tendency of only a subset of original physical values of said array of memory cells and compute extent of deterioration by comparing, generally at the same time as reading circuitry read, at least said central tendency of said subset of original physical values to at least a central tendency of corresponding current physical values.

Further in accordance with at least one embodiment of the present invention, said plurality of cells comprises a number of cells selected to as to achieve a level of reading errors which does not exceed a predetermined acceptable level.

Still further in accordance with at least one embodiment of the present invention, reading comprises using error correction code to eliminate errors and wherein said predetermined acceptable level comprises a predetermined maximum proportion of pages containing so many errors as to be uncorrectable by said error correction code.

Additionally in accordance with at least one embodiment of the present invention, determining extent of deterioration is performed no more than once per erase sector and said threshold determining is performed once for each of a plurality of pages included in each erase sector.

Further in accordance with at least one embodiment of the present invention, said array comprises more than one erase sector, each of which includes a subset of cells which together undergo cycles affecting said extent of deterioration; wherein said determining extent of deterioration comprises storing predefined physical levels rather than data physical levels in each of a plurality of cells and wherein said storing is performed no more than once per erase sector.

5

10

15

25

30

Also provided, in accordance with at least one embodiment of the present invention, is a method for using an array of memory cells storing physical levels which diminish over time, the method comprising determining extent of deterioration of the physical levels; and using said array of memory cells so as to take into account said extent of deterioration.

The following terms may be construed either in accordance with any definition thereof appearing in the prior art literature or in accordance with the specification, or as follows:

Block: a set of flash memory device cells which must, due to physical limitations of the flash memory device, be erased together. Also termed erase sector, erase block.

Cell: A component of flash memory that stores one bit of information (in single-level cell devices) or n bits of information (in a multi-level device having 2 exp n levels). Typically, each cell comprises a floating-gate transistor. n may or may not be an integer. "Multi-level" means that the physical levels in the cell are, to an acceptable level of certainty, statistically partionable into multiple distinguishable regions, plus a region corresponding to zero, such that digital values each comprising multiple bits can be represented by the cell. In contrast, in single-level cells, the physical levels in the cell are assumed to be statistically partitionable into only two regions, one corresponding to

zero and one other, non-zero region, such that only one bit can be represented by a single-level cell.

Charge level: the measured voltage of a cell which reflects its electric charge.

Cycling: Repeatedly writing new data into flash memory cells and repeatedly erasing the cells between each two writing operations.

Decision regions: Regions extending between adjacent decision levels, e.g. if decision levels are 0, 2 and 4 volts respectively, the decision regions are under 0 V, 0 V - 2 V, 2V - 4V, and over 4 V.

Demapping: basic cell-level reading function in which a digital n-tuple originally received from an outside application is derived from a physical value representing a physical state in the cell having a predetermined correspondence to the digital n-tuple.

Digital value or "logical value": n-tuple of bits represented by a cell in flash memory capable of generating 2 exp n distinguishable levels of a typically continuous physical value such as charge, where n may or may not be an integer.

20

25

30

5

10

15

Erase cycle: The relatively slow process of erasing a block of cells (erase sector), each block typically comprising more than one page, or, in certain non-flash memory devices, of erasing a single cell or the duration of so doing. An advantage of erasing cells collectively in blocks as in flash memory, rather than individually, is enhanced programming speed: Many cells and typically even many pages of cells are erased in a single erase cycle.

Erase-write cycle: The process of erasing a block of cells (erase sector), each block typically comprising a plurality of pages, and subsequently writing new data into at least some of them. The terms "program" and "write" are used herein generally interchangeably.

Flash memory: Non-volatile computer memory including cells that are erased block by block, each block typically comprising more than one page, but are written into and read from, page by page. Includes NOR-type flash memory, NAND-type flash memory, and PRAM, e.g. Samsung PRAM, inter alia, and flash memory devices with any suitable number of levels per cell, such as but not limited to 2, 4, or (as in the

embodiment illustrated herein) 8.

5

10

15

20

25

Mapping: basic cell-level writing function in which incoming digital n-tuple is mapped to a program level by inducing a program level in the cell, having a predetermined

correspondence to the incoming logical value.

Page = A portion, typically 512 or 2048 or 4096 bytes in size, of a flash memory e.g. a NAND or NOR flash memory device. Writing can be performed page by page, as opposed to erasing which can be performed only erase sector by erase sector. A few bytes, typically 16 - 32 for every 512 data bytes are associated with each page

(typically 16, 64 or 128 per page), for storage of error correction information. A typical

block may include 32 512-byte pages or 64 2048-byte pages.

Precise read, soft read: Cell threshold voltages are read at a precision (number of bits)

greater than the number of Mapping levels (2<sup>n</sup>). The terms precise read or soft read are

interchangeable. In contrast, in "hard read", cell threshold voltages are read at a

precision (number of bits) smaller than the number of Mapping levels (2<sup>n</sup> where n =

number of bits per cell).

Present level, Charge level: The amount of charge in the cell. The amount of charge

currently existing in a cell, at the present time, as opposed to "program level", the

amount of charge originally induced in the cell (i.e. at the end of programming).

Program: same as "write".

30

Program level (programmed level, programming level): amount of charge originally

induced in a cell to represent a given logical value, as opposed to "present level".

17

Reprogrammability (Np): An aspect of flash memory quality. This is typically operationalized by a reprogrammability parameter, also termed herein "Np", denoting the number of times that a flash memory can be re-programmed (number of erase-write cycles that the device can withstand) before the level of errors is so high as to make an unacceptably high proportion of those errors irrecoverable given a predetermined amount of memory devoted to redundancy. Typically recoverability is investigated following a conventional aging simulation process which simulates or approximates the data degradation effect that a predetermined time period e.g. a 10 year period has on the flash memory device, in an attempt to accommodate for a period of up to 10 years between writing of data in flash memory and reading of the data therefrom.

Resolution: Number of levels in each cell, which in turn determines the number of bits the cell can store; typically a cell with 2<sup>n</sup> levels stores n bits. Low resolution (partitioning the window, W, of physical values a cell can assume into a small rather than large number of levels per cell) provides high reliability.

Retention: of original physical levels induced in the cells; retention is typically below 100% resulting in deterioration of original physical levels into present levels.

20

5

10

15

Retention time: The amount of time that data has been stored in a flash device, typically without, or substantially without, voltage having been supplied to the flash device i.e. the time which elapses between programming of a page and reading of the same page.

25 Symbol: Logical value

Threshold level: the voltage (e.g.) against which the charge level of a cell is measured. For example, a cell may be said to store a particular digital n-tuple D if the charge level or other physical level of the cell falls between two threshold values T.

30

Unless specifically stated otherwise, as apparent from the following discussions, it is appreciated that throughout the specification discussions, utilizing terms such as,

"processing", "computing", "selecting", "ranking", "grading", "calculating", "determining", "generating", "reassessing", "classifying", "generating", "producing", "stereo-matching", "registering", "detecting", "associating", "superimposing", "obtaining" or the like, refer to the action and/or processes of a computer or computing system, or processor or similar electronic computing device, that manipulate and/or transform data represented as physical, such as electronic, quantities within the computing system's registers and/or memories into other data similarly represented as physical quantities within the computing system's memories, registers or other such information storage, transmission or display devices.

5

10

15

20

25

30

In this specification, the terms "decision levels" and "threshold levels" are used interchangeably. "Reliably storing" and "reliable" are used to indicate that certain information is stored with high reliability in the sense that it can be expected to be read without error throughout the guaranteed lifetime of the flash memory device.

Any suitable processor, display and input means may be used to process, display, store and accept information, including computer programs, in accordance with some or all of the teachings of the present invention, such as but not limited to a conventional personal computer processor, workstation or other programmable device or computer or electronic computing device, either general-purpose or specifically constructed, for processing; a display screen and/or printer and/or speaker for displaying; machine-readable memory such as optical disks, CDROMs, magnetic-optical discs or other discs; RAMs, ROMs, EPROMs, EEPROMs, magnetic or optical or other cards, for storing, and keyboard or mouse for accepting. The term "process" as used above is intended to include any type of computation or manipulation or transformation of data represented as physical, e.g. electronic, phenomena which may occur or reside e.g. within registers and /or memories of a computer.

The above devices may communicate via any conventional wired or wireless digital communication means, e.g. via a wired or cellular telephone network or a computer network such as the Internet.

The apparatus of the present invention may include, according to certain embodiments of the invention, machine readable memory containing or otherwise

storing a program of instructions which, when executed by the machine, implements some or all of the apparatus, methods, features and functionalities of the invention shown and described herein. Alternatively or in addition, the apparatus of the present invention may include, according to certain embodiments of the invention, a program as above which may be written in any conventional programming language, and optionally a machine for executing the program such as but not limited to a general purpose computer which may optionally be configured or activated in accordance with the teachings of the present invention.

5

Any trademark occurring in the text or drawings is the property of its owner and occurs herein merely to explain or illustrate one example of how an embodiment of the invention may be implemented.

#### BRIEF DESCRIPTION OF THE DRAWINGS

Certain embodiments of the present invention are illustrated in the following drawings:

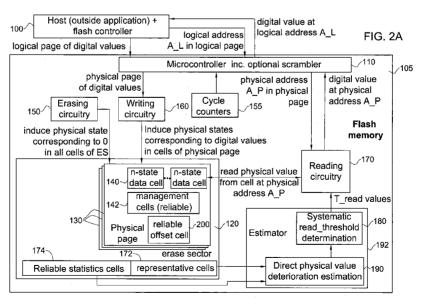

- Fig. 1 is a graph (top) of manufacturer-defined initial cell voltage distributions, which apply to a flash memory device which has yet to undergo cycling and retention vs. a graph (bottom) of cell voltage distributions which apply to a flash memory device which has undergone cycling and retention;

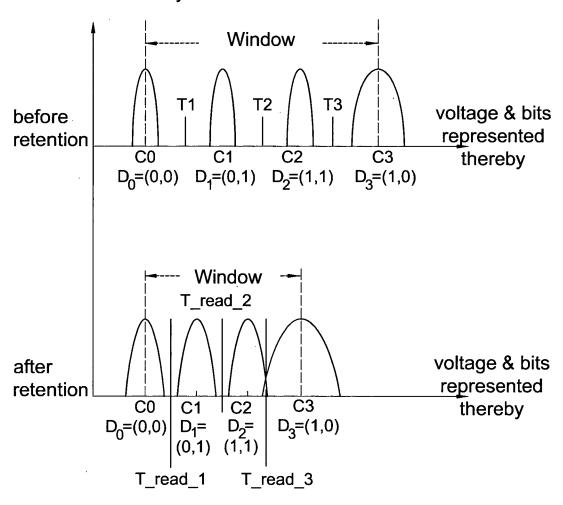

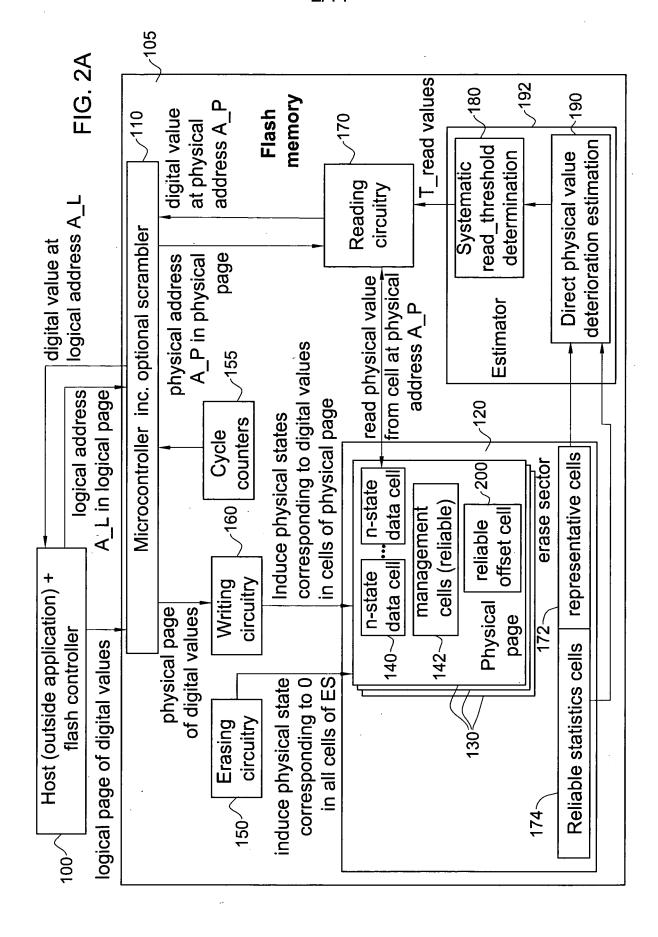

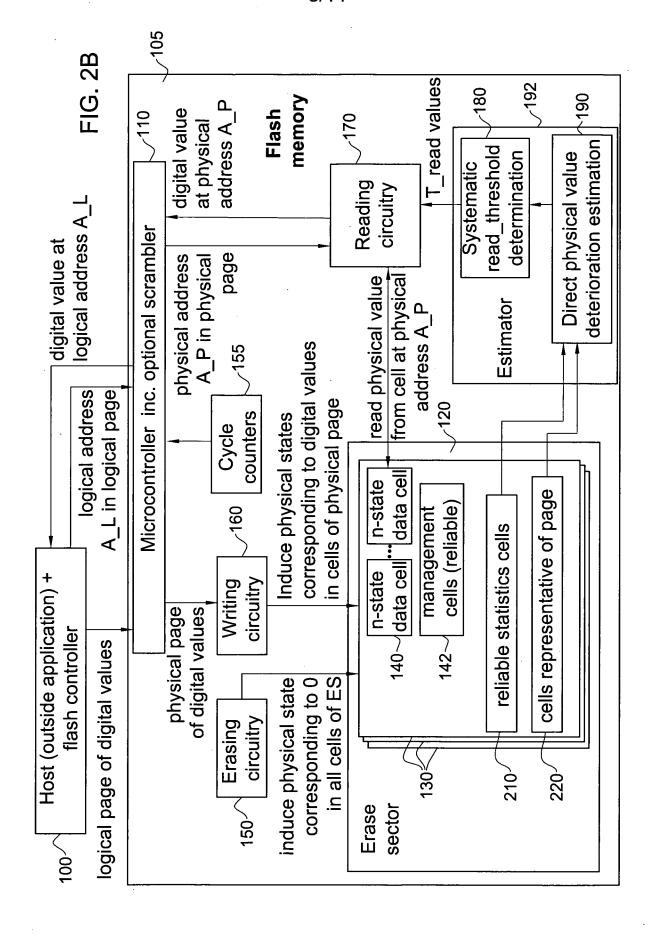

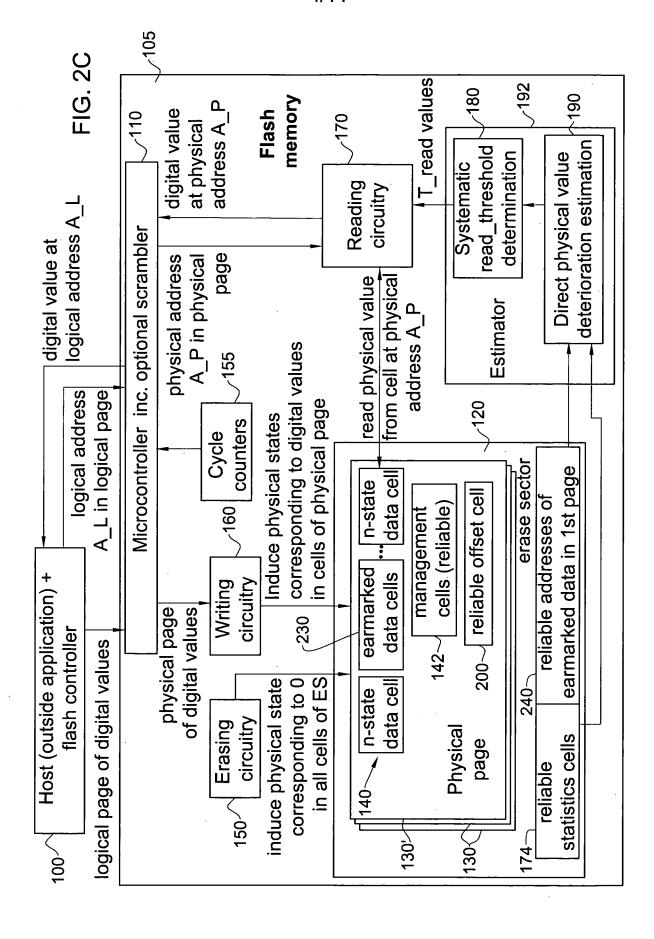

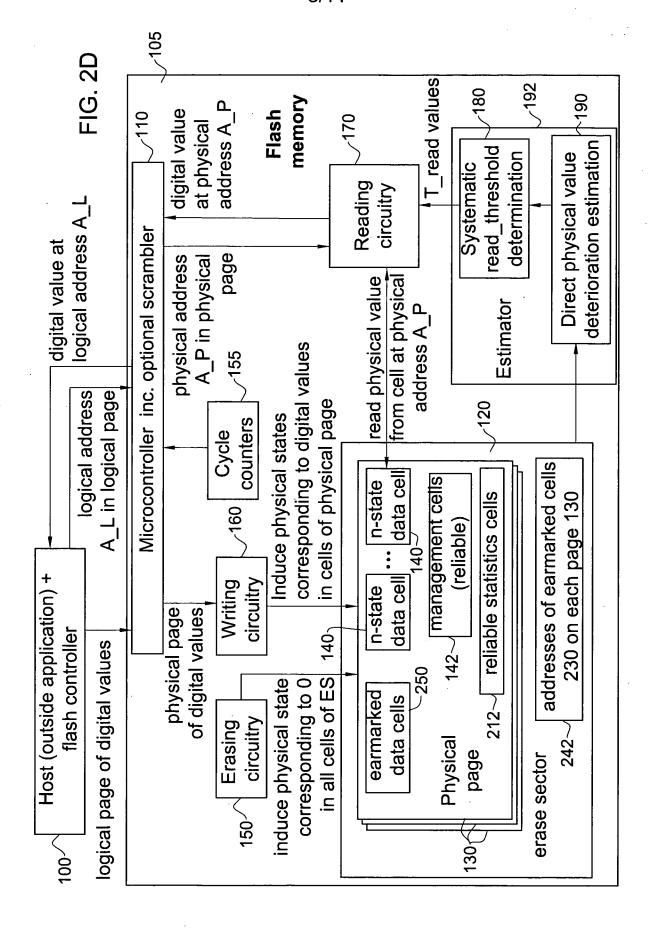

- Figs. 2A 2D are simplified functional block diagrams of an improved flash memory system with adjustable read thresholds, constructed and operative in accordance with certain embodiments of the present invention; specifically Fig. 2A illustrates a controlled, per-erase sector embodiment, Fig. 2B illustrates a controlled, per-page embodiment, Fig. 2C illustrates a blind, per-erase sector embodiment and Fig. 2D illustrates a blind, per-page embodiment;

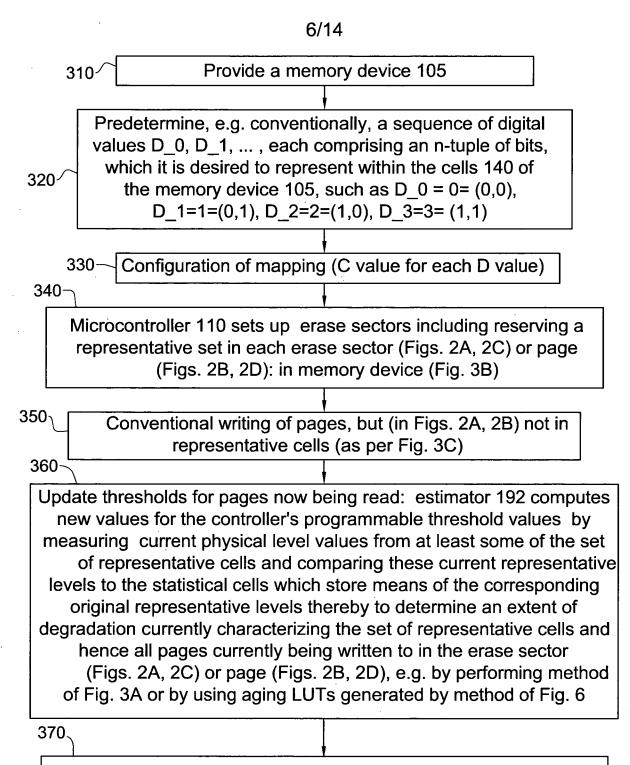

- Fig. 3A is a simplified flowchart illustration of a method of operation for the systems of any of Figs. 2A 2D, in accordance with certain embodiments of the present invention;

- Fig. 3B is a simplified flowchart illustration of a method for performing step 340 of Fig. 3A, in accordance with certain embodiments of the present invention;

- Fig. 3C is a simplified flowchart illustration of a method for performing step 350 of Fig. 3A, in accordance with certain embodiments of the present invention;

- Fig. 3D is a simplified flowchart illustration of a method for performing step 360 of Fig. 3A, in accordance with certain embodiments of the present invention;

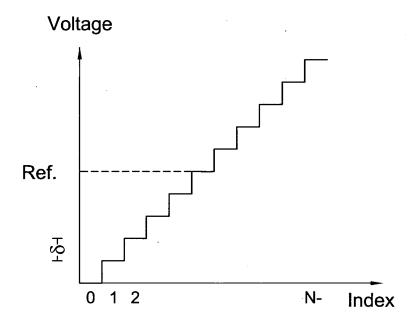

- Fig. 4 is a voltage vs. cell index graph showing reference voltages for each of a plurality of representative cells provided in accordance with a "soft" embodiment of the present invention suitable for "hard read" applications;

25

Fig. 5 is a prior art, simplified data structure illustration of a data structure for an erase sector;

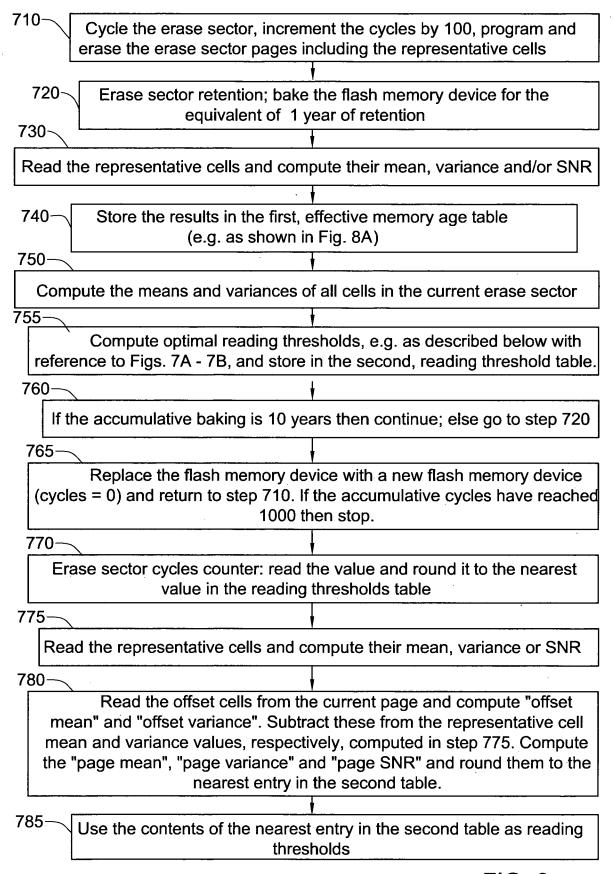

Fig. 6 is a simplified flowchart illustration of a method for constructing look-up tables useful in generating read thresholds adapted to the effective age of a flash memory device as affected by the retention and cycling undergone by the device, according to certain embodiments of the present invention;

Figs. 7A – 7B, taken together, form a simplified flowchart illustration of a method for constructing a look-up table which can be used to update thresholds each time a flash memory device is read e.g. as described in the threshold updating step 360 of Fig. 3A; and

Figs. 8A – 8B are examples of look-up tables useful in generating read thresholds adapted to the effective age of a flash memory device as affected by the retention and cycling undergone by the device, according to certain embodiments of the present invention.

15

20

10

#### DETAILED DESCRIPTION OF CERTAIN EMBODIMENTS

Reference is now made to Fig. 1 which is a graph (top) of manufacturer-defined initial cell voltage distributions, which apply to a flash memory device which has yet to undergo cycling and retention vs. a graph (bottom) of cell voltage distributions which apply to a flash memory device which has undergone cycling and retention.

A read threshold, T\* (also termed herein T\_read) is used to distinguish between each two adjacent programming charge levels. Generally these two charge levels comprise physical values clustering normally around a first charge C\_1, and physical values clustering normally around a second charge level C\_2.

25

As described in detail below, T\_read may be computed by dedicating a first subset of the representative cells, comprising at least one and typically several representative cells, to storing C\_1. A second subset of the representative cells, comprising at least one and typically several representative cells is dedicated to storing

C\_2. These two subsets can be used to compute the read threshold level when it is desired to read, e.g. using the following formula also termed herein the "read-threshold computation formula", where the means and standard deviations of the first and second subsets are represented by m and sigma respectively, and suitable subscripts 1 or 2:

$$T_i^* = \frac{\sigma_{i-1}m_i + \sigma_i m_{i-1}}{\left(\sigma_{i-1} + \sigma_i\right)}$$

m - mean

5

10

15

20

25

$\sigma$  - standard deviation

The above formula computes the reading threshold as a weighted average of the mean present values in the two subsets, weighted by the standard deviations of the two subsets. Optionally, the reading threshold as computed above may be further adjusted to take into account coupling between adjacent cells. It is appreciated that the mean and standard deviation of adjacent levels may be estimated using the representative cells. If the standard deviation is equal for all levels, the optimal decision level may be computed as a simple average between two adjacent means.

Various embodiments for computing read thresholds are described hereinbelow in detail.

Reference is now made to Figs. 2A – 2D which are simplified functional block diagrams of an improved flash memory system with adjustable read thresholds, constructed and operative in accordance with certain embodiments of the present invention. The systems of Figs. 2A – 2D typically comprise a host (outside application) 100 and associated interface and interface controller, interacting with a flash memory device 105. The flash memory device 105 includes a micro-controller 110 and an array of cells including at least one erase sector 120, each erase sector including at least one physical page 130, each page including a plurality of cells 140. For example, if the page size is 2-4 KB and 2 to 4 bits are used per cell the number of cells is 4000 to 16000.

The flash memory device also includes circuitry for erasing data from cells 140, erase sector by erase sector rather than cell by cell, writing data into cells typically page by page, and reading data from cells, page by page (e.g. in NAND type

flash memory) or cell by cell (e.g. in NOR type flash memory). The circuitry performing these functions is referenced herein as erasing circuitry 150, writing circuitry 160 and reading circuitry 170 respectively. An array of cycle counters 155 count, for each erase sector respectively, all erase-write cycles performed on that sector.

5

10

15

20

25

30

According to certain embodiments of the present invention, each erase sector includes at least one and optionally exactly one set of representative cells 172 whose cells are typically programmed during the manufacturing stage, and at least one high-reliability "statistic cell" 174 storing, e.g. previous mean information and/or previous standard deviation information regarding the representative cells 172 as described in detail herein. A direct physical value deterioration estimation unit 190 and a systematic read-threshold determination unit 180, which together are termed herein a read threshold estimator or "estimator" 192, interact with the representative cells 172 and high-reliability statistic cell/s 174 to generate read-thresholds and/or to estimate the extent of data deterioration, as described in detail herein with reference to Figs. 3A – 5.

It is appreciated that certain embodiments of the systems and methods shown and described herein typically include at least one of the following features:

a. Estimation of the deterioration of the physical values residing in the n-level cells is direct because current physical values, or a central tendency e.g. mean thereof, are compared to previous, high-reliability stored physical values or a central tendency e.g. mean thereof. In contrast, prior art systems may not directly estimate deterioration; instead they may indirect estimate deterioration e.g. by computing and comparing frequency of occurrence of current logical values thresholded from current physical values to a previously computed and high-reliability stored histogram of previous logical values thresholded from previous physical values or other stored indication of frequency of occurrence of certain categories of previous logical values.

High reliability cells are typically designed to store data so that the data can be retrieved without error even after cycling and retention. For example, high reliability cells may comprise single-level cells and/or may store BCH-encoded data with a large proportion of redundant bits such as 50% redundant bits. Or, to give a particularly

simple example, high reliability cells may store each bit of information repeated many times such as 8 times.

5

10

15

20

25

30

b. Systematic determination of read thresholds (e.g. by computation or by use of look up tables) as a function of estimated deterioration of the physical values residing in the n-level cells. In contrast, prior art systems may employ a trial and error-based method for determination of read thresholds to fit estimated deterioration of the physical values residing in the n-level cells. For example, in the prior art, a first histogram of logical values may be generated initially by thresholding logical values from the initial physical values (programmed values) using original, typically manufacturer determined thresholds. This histogram is high-reliability stored. A second histogram of current logical values may be thresholded from current physical values (present values) using the same original threshold values and may be compared to the first histogram, so as to generate a first putative set of read thresholds which, if used on the current physical values, is hoped to result in a third histogram which is the same as the stored histogram. If the putative set of read thresholds does not succeed in doing this, the disappointing third histogram is compared to the first and second histograms so as to generate a second putative set of read thresholds. This process is repeated, typically on a trial and error basis, until eventually, a putative set of read thresholds is found which, if used on the current physical values, results in a current histogram which is the same as the stored histogram.

c. Only a small amount of previous information needs be high-reliability stored, as opposed to larger amounts of previous information which may require high-reliability storage in prior art systems. The representative cells, whose deterioration is representative of other cells in the erase sector or in the page, are stored at an ordinary level of reliability, like any other data cell. Typically, the only information pertaining to previous states of the flash memory cells is central tendency and/or variance information of these states. This central tendency (previous mean) information may be stored at a relatively low resolution typically comprising only a few bits (e.g. 4-5 bits), since this is the level of noise characterizing the physical charge induction distributions shown in Fig. 1. These few bits may be stored once per physical page or even only once per erase sector.

In contrast, in prior art flash memory systems with n-level cells, n-1 histogram values may be stored for each page, representing the original (before cycling and retention) distribution of physical values over the page. Each such histogram value typically must be stored at a resolution of a few dozen bits, since there are typically at least 1000 cells per page. Therefore, certain embodiments of the present invention may require as little as 4-5 bits of high-reliability storage per erase sector, as opposed to certain prior art systems which may require several thousand bits of high-reliability storage for each of the dozens or even hundreds of physical pages in the erase sector.

5

10

15

20

25

30

The embodiments of Figs. 2A – 2D are now compared. As described above, Figs. 2A – 2D are all simplified functional block diagrams of an improved flash memory system with adjustable read thresholds, constructed and operative in accordance with different embodiments of the present invention. Specifically, however, Fig. 2A illustrates a controlled, per-erase sector embodiment, Fig. 2B illustrates a controlled, per-page embodiment, Fig. 2C illustrates a blind, per-erase sector embodiment and Fig. 2D illustrates a blind, per-page embodiment.

In all of Figs. 2A – 2D, a set of representative cells is designated for monitoring deterioration, relative to highly reliable statistics cells which store at least statistics (e.g. mean and/or standard deviation or even raw values) of the set of representative cells as originally programmed i.e. before deterioration. The terms "controlled" and "blind" are used herein to differentiate embodiments in which the set of representative cells is set aside ("controlled" embodiments) from "blind" embodiments in which the set of representative cells is not set aside; instead, the representative cells are pre-designated ones from among the normal data cells and are used throughout to store normal, uncontrolled data. In the "controlled" embodiments of Figs. 2A and 2B, the representative cells store controlled, special data such as several repetitions of each possible program level or only the highest program level. The terms "per erase sector" and "per page" are used to denote embodiments in which only one set of representative cells is designated for each erase sector, as opposed to embodiments in which each and every page in the erase sector has its own set of representative cells.

In the per-erase sector embodiments of Figs. 2A - 2C, a high reliability offset cell is typically provided on each page, whereas representative cells are stored only

once per erase sector (as opposed to once per page in the per-page embodiments of Figs. 2B and 2D). Before writing on a particular page in the erase sector, the representative cells are read, and their mean, variance and/or SNR at time of writing, are computed. At least one of these is stored in the particular page's offset cell or cells and is used, at the time of reading, as an indication of the time which elapsed between erasure of the erase sector to which the particular page belongs, and programming of the particular page. Typically, before reading the page, perhaps some years after it was programmed, the page's offset cells 200 and the erase sector's representative cells 172 are read. The mean and/or variance of the representative cells 172 at approximate time of reading is computed and the value of the corresponding offset cell is subtracted. The resulting delta-mean and/or delta-variance values are indicative of the time that has elapsed between the programming of the page and the reading thereof.

5

10

15

20

25

More generally, the time that has elapsed between programming and reading of a particular page is used as an indicator of deterioration. In per-page embodiments, this time can be directly estimated by comparing, e.g. subtracting, current (reading time) values of representative cells on a particular page, with highly reliably stored statistics of their values at time of programming. In per-erase sector embodiments, however, this time interval is estimated by subtracting an indicator of the time interval between writing and erasing, from an indicator of the time interval between reading and erasing. The representative cells' mean, variance or SNR serve as an indicator of the time interval between reading and erasing, whereas the corresponding statistic stored in the offset cell serves as an indicator of the time interval between writing and erasing.

It is appreciated that change in various statistics of the representative cells may be used to quantify the extent of deterioration, and, accordingly, to adjust reading thresholds, such as but not limited to any of the following:

$$\begin{split} V_{mean\_new} &= \frac{1}{N} \sum_{i=1}^{N} V_{training\_cell\_i} \\ \sigma_{Variance\_new} &= \frac{1}{N} \sum_{i=1}^{N} (V_{training\_cell\_i} - V_{mean\_new})^2 \\ \alpha &= \frac{V_{mean\_new}}{V_{W\_mean}} \\ SNR_{new} &= \frac{V_{mean\_new}^2}{\sigma^2_{Variance\_new}} \\ diff\_SNR &= SNR_W - SNR_{new} \end{split}$$

The above formulae represent, respectively, current mean; current variance; proportion between current mean and stored original mean; current SNR i.e. proportion between current mean and current variance; and difference between current SNR and original SNR, where "current" refers to values existing during reading and "original" refers to values existing during erasing or during writing.

Generally, SNR is defined as follows, where V\_training\_cell\_i refers to the physical value stored in an individual one of the representative cells, N is the number of representative cells, and W is the window defined in Fig. 1.

$$V_{W\_mean} = \frac{1}{N} \sum_{i=1}^{N} V_{training\_cell\_i}$$

$$\sigma_{W\_Variance} = \frac{1}{N} \sum_{i=1}^{N} (V_{training\_cell\_i} - V_{W\_mean})^{2}$$

$$SNR_{W} = \frac{V^{2}_{W\_mean}}{\sigma^{2}_{W\_Variance}}$$

5

15

Fig. 3A is a simplified flowchart illustration of a method of operation for any of the systems of Figs. 2A - 2D, in accordance with certain embodiments of the present invention. The method of Fig. 3A typically comprises some or all of the following steps, suitably ordered e.g. as shown:

In step 310, conventionally provide a memory device 105 having erasing circuitry 150, writing circuitry 160, and reading circuitry 170; a micro-controller 110 controlling these; and erase sectors 120 (typically from a few to a few dozen), each erase sector including physical pages 130 (typically a few hundred), each physical page

including cells 140, each erase sector being erased as a unit by the erasing circuitry, each page being written into e.g. as a unit by the writing circuitry 160.

In step 320, a sequence of logical values  $D_0$ ,  $D_1$ , ..., each comprising an n-tuple of bits, which it is desired to represent within the cells 140 of the memory device 105, is predetermined, such as  $D_0 = 0 = (0,0)$ ,  $D_1 = 1 = (0,1)$ ,  $D_2 = 2 = (1,0)$ ,  $D_3 = 3 = (1,1)$

5

10

15

20

25

30

In step 330, configuration of mapping is performed: typically at the manufacturing stage, configure at least one of the micro-controller 110, reading circuitry 170 and writing circuitry 160 to cause individual cells 140 in the memory device 105 to return a predetermined one of the predetermined sequence of logical values D\_0, D\_1, ..., if the memory cell 140 is found to be loaded with a corresponding one of a corresponding sequence of central physical values C\_0, C\_1, ... e.g. charge levels. Each charge level (except the lowest and highest) falls within a pair of programmable threshold physical values disposed on either side of the central physical value. In the above example, the sequence of charge levels corresponding to the sequence D\_0, D\_1, D\_2, D\_3 of logical values is C\_0, C\_1, C\_2, and C\_3. There may be 3 original threshold values T\_0, T\_1, T\_2, and T\_3 where central value C\_0 is located below T\_0, C\_1 is located between T\_0 and T\_1, C\_2 is located between T\_1 and T\_2, and C\_3 is located above T\_2. If the micro-controller finds a charge between T\_i and T\_(i+1) in an individual cell, the micro-controller associates the cell with the logical value i (i = 0, 1, 2, 3).

For example, C\_0, C\_1, C\_2, and C\_3 may be -1 V, 1 V, 3 V and 5 V respectively, and T\_1, T\_2, and T\_3 may be 0 V, 2 V and 4 V respectively i.e. each threshold value may be halfway between the C values on either side of it.

In step 340, microcontroller 110 sets up erase sectors including reserving a representative set in each erase sector (Figs. 2A, 2C) or page (Figs. 2B, 2D): e.g. for each erase sector (Figs. 2A, 2C) or page (Figs. 2B, 2D) in memory device, perform method of Fig. 3B.

In step 350 perform conventional writing of pages, but (in Figs. 2A, 2B) not in representative cells: writing circuitry 160 writes data from an outside application 100

e.g. a Windows-generated document, e.g. page by page, in cells 140, within a given erase sector 120, however (in Figs. 2A, 2B) not in the set of representative cells. Specifically, for each page j, perform the method of Fig. 3C.

In step 360, thresholds for pages now being read are updated: estimator 192 computes new values for the controller's programmable threshold values by measuring current physical level values from at least some of the set of representative cells and comparing these current representative levels to the statistical cells which store means of the corresponding original representative levels thereby to determine an extent of degradation currently characterizing the set of representative cells and hence all pages currently being written to in the erase sector (Figs. 2A, 2C) or page (Figs. 2B, 2D), e.g. by performing method of Fig. 3D.

5

10

15

20

25

In step 370, de-mapping is performed: reading circuitry 170 reads pages using updated read thresholds received from estimator 192: micro-controller 110 causes individual cells 140 in the current page in the current erase sector to return a predetermined one of the predetermined sequence of logical values, by comparing the charge level found in each cell, with the up-to-date read thresholds computed in step 630 of Fig. 3D.

Fig. 3B is a simplified flowchart illustration of a method for performing step 340 of Fig. 3A, in accordance with certain embodiments of the present invention. The method of Fig. 3B typically comprises some or all of the following steps, suitably ordered e.g. as shown:

In step 410, micro-controller 110 instructs erasing circuitry 150 to erase a sector.

In step 420, at about the same time, micro-controller 110 designates at least one set (e.g. 172) of representative cells e.g. 20 representative cells, per erase sector, e.g. 1 representative set per erase sector (per-erase sector embodiments of Figs. 2A and 2C) or 1 representative set for each page in the erase sector (per-page embodiments of Figs. 2B and 2D). Designation may comprise reserving the set/s of representative cells in the sense that no data is written in them (in controlled embodiments of Figs. 2A, 2B) or earmarking certain data cells (in "blind" embodiments of Figs. 2C, 2D) in the sense of

making note of their addresses, typically by reliably storing these e.g. at memory locations 240 or 242.

In step 430 performed in controlled embodiments e.g. as per Figs. 2A and 2B, micro-controller 110 loads the reserved representative cells 172 or 220 by instructing writing circuitry 160 to write, in each of the set of representative cells, predetermined physical levels such as all (typically manufacturer-determined) central values e.g. C0, ... C3 or such as only the maximum central value such as C3 in the example of Fig. 1 which may be 5V or any other manufacturer-determined value, or such as stepwise values as described below with reference to Fig. 4. Each value written into a set of representative cells may be written more than once so as to allow more than one independent evaluation of the degradation undergone by the value in question.

5

10

15

20

25

30

In step 435, micro-controller 110 stores, in a high-reliability location e.g. statistics cells 174, 210 or 212, at least one statistic of the charge levels stored in each set of representative cells e.g. central tendency (mean (M\_erase), median, or mode) and/or standard deviation And/or even at least some of the charge levels themselves.

Fig. 3C is a simplified flowchart illustration of a method for performing step 350 of Fig. 3A, in accordance with certain embodiments of the present invention. The method of Fig. 3C typically comprises some or all of the following steps, suitably ordered e.g. as shown:

In step 510, for each cell 140, writing circuitry 160 receives, ultimately from the outside agent 100, a specific logical value D\_i.

In step 520, writing circuitry 160 maps value D\_i into a current cell 140 in current page 130 in a current erase sector 120 by generating, in the cell, an initial physical value e.g. charge level (or electrical current level or voltage level) P\_Ii belonging to a known random distribution, due to physical effects e.g. tunnel effect, of physical values centered about the central physical level C\_i corresponding to the specific logical value D\_i, wherein each initial physical level P\_Ii tends to diminish over time. Charge or current or voltage levels in a cell may be generated in any suitable application-specific manner e.g. by changing resistance, changing capacitor voltage, or changing current, in the cell.

Fig. 3D is a simplified flowchart illustration of a method for performing step 360 of Fig. 3A, in accordance with certain embodiments of the present invention. The method of Fig. 3D typically comprises some or all of the following steps, suitably ordered e.g. as shown:

5

10

15

20

25

30

In step 610, direct physical value deterioration estimation unit 190 computes at least one current central characteristic, e.g. mean (or median or mode) of current charge levels in the erase sector's representative set, M\_read (Figs. 2A, 2C) or M\_read\_j (Figs. 2B, 2D); this can be stored in temporary memory of the micro-controller 110. M\_read is page-specific (has subscript j) in per-page embodiments (Figs. 2B, 2D) in which each page has a representative set, and is global (has no subscript j) over all pages in erase sector, in per-erase sector embodiments (Figs. 2A, 2C) in which the erase sector has but a single representative set.

In step 620, direct physical value deterioration estimation unit 190 computes a proportion (threshold attenuation factor) alpha = M\_read/M\_write for the entire erase sector (per-erase sector embodiments of Figs. 2A, 2C)) or M\_read\_j/M\_write\_j for each page therewithin (per-page embodiments of Figs. 2B, 2D).

In step 630, for the entire erase sector (per-erase sector embodiments of Figs. 2A, 3C) or for each page therewithin (per page embodiments of Figs. 2B, 2D), systematic read-threshold determination unit 180 defines a current sequence of read thresholds T\_READ\_0, T\_READ\_1, T\_ READ\_2,T\_ READ\_3, T\_ READ\_4 e.g. by multiplying the appropriate proportion computed in step 620 by the initial sequence of read thresholds T\_0, T\_1, T\_2,T\_3,T\_4 respectively or by using a LUT as described herein with reference to Figs. 7A – 7B.

In the blind, per ES embodiment of Fig. 2C, the high-reliability management cells 142 store, inter alia, an indicator of a page e.g. pointer or stored page number, to be used as a reference for mean computations. It is appreciated that in the embodiment of Fig. 2C, only some of the pages in the erase sector, as indicated by reference numeral 130', have earmarked data cells 230 among the array 140 of data cells. No data cells are earmarked in the remaining pages which are indicated in Fig. 2C by reference numeral 130. In the illustrated embodiment, by way of example, it is assumed that only

one of the pages in the erase sector 120 – the first page – has earmarked data cells, however this is not intended to be limiting.

Referring again to Fig. 3A, generally, in blind embodiments, inter alia, of this invention, a representative set is designated, e.g. for each erase sector, or for each page in each erase sector. However, in blind embodiments as opposed to controlled embodiments, instead of reserving, including subsequently not storing data in, a representative set for each page, in step 340, a subset of the data cells in each page or erase sector is designated. This subset is typically larger than the representative set of the controlled embodiment (e.g. 100 cells instead of 20 cells per representative set). Typically, the designation of the subset may be preprogrammed into the microcontroller 110 and may comprise (for per-ES embodiments) an indication of a page within each erase sector, and cell addresses within that page, which constitute the representative cells, or (for per-page embodiments) an indication of the cell addresses within each page which constitute the representative cells. Typically, in per-ES embodiments, the same page is used in all erase sectors to store the representative cells. Also, typically, the same cell addresses within each relevant page, are assigned to the representative cells.

Any suitable number of representative cells may be provided. It may be desired to select a number of cells so as to achieve a level of reading errors which does not exceed a predetermined acceptable level. The predetermined level may for example comprise P\_target, a predetermined maximum proportion of pages containing so many errors as to be uncorrectable by said error correction code. To achieve this, for applications in which gray coding is used as is conventional, the number of representative cells, N, may be selected on the basis of the following inequality:

$$\max_{x} \frac{(2L-2)}{L \log_{2} L} \cdot Q\left(\frac{W-2(L-1)|x|}{2(L-1)\sigma}\right) \cdot f_{Shift}(|x|) < P_{T \operatorname{arget}}$$

N is selected as the x which maximizes the expression appearing on the left of the above inequality, from among all x's for which the above inequality holds. The parameters in the above inequality are described below:

L = number of program levels per cell

10

15

20

25

$$Q(X) = \int_{x=X}^{\infty} \frac{1}{\sqrt{2\pi}} e^{-x^2/2}$$

5

10

15

20

25

W = the window of logical values each cell may store after retention (during reading) e.g. the "window" in the bottom graph of Fig. 1 extending between D\_0 and D\_3.

$\sigma$  = Standard variation of the random free coefficient n after retention (i.e. during reading), using the following model for the current physical value V\_read from a cell, after retention, as a function of the physical value V\_program originally programmed into the cell: V read = alpha(retention, cycling) x V program + n.

$$f_{Shift}(|x|) = 2\sqrt{\frac{N}{2\pi(\sigma^2 + \sigma_{measure}^2)}} \exp\left(-\frac{x^2}{(\sigma^2 + \sigma_{measure}^2)} \cdot \frac{N}{2}\right)$$

$\sigma$  measure = Standard variation of the soft measurements

Fig. 4 is a voltage vs. representative cell index graph showing one alternative for performing step 430 of Fig. 3B, termed herein the "ramp" or "soft" embodiment. Specifically, Fig. 4 illustrates a method for loading representative cells provided in accordance with any of the controlled embodiments of the present invention (e.g. the embodiments of Figs. 2A and 2B), in accordance with a "soft" variation of the present invention suitable for "hard read" applications.

In these applications, "hard values", e.g. as defined below, are written into cells, and a precise read (also termed herein "soft read") is used to estimate the statistics of the representative cells. As described above, the terms "Precise read" and " soft read" refer to reading cell threshold voltages at a precision (number of bits) greater than the number of Mapping levels (2^n) of the cell. In contrast, in "hard read", cell threshold voltages are read at a precision (number of bits) smaller than the number of Mapping levels (2^n).

If it is desired to estimate the degradation proportion (threshold attenuation factor) in resolution of less than  $\delta$  volts, the method of Figs. 3A – 3D may be varied as follows:

1. In step 430 of Fig. 3B, write  $N = W/\delta$  staircase values in the N representative cells 172 or 220 (W is the window shown in the top, before-retention graph of Fig. 1). Each staircase value is  $\delta$  volts greater than the previous one as illustrated in Fig. 5.

- 2. In step 435, a reference level, indicated by "Ref" in Fig. 4, and the original decision levels (original, typically manufacturer-determined, thresholds) are stored e.g. as OTPs (one-time programmed values) in a high reliability section of the flash memory device e.g. in management cells 142 of Figs. 2A 2B.