(19) 대한민국특허청(KR)

(12) 등록특허공보(B1)

(45) 공고일자 2009년01월30일

(11) 등록번호 10-0880631

(24) 등록일자 2009년01월20일

(51) Int. Cl.<sup>9</sup>

H01L 33/00 (2008.05)

(21) 출원번호 10-2004-7016180

(22) 출원일자 2004년10월09일

심사청구일자 2006년10월23일

번역문제출일자 2004년10월09일

(65) 공개번호 10-2005-0013989

(43) 공개일자 2005년02월05일

(86) 국제출원번호 PCT/US2003/009504

국제출원일자 2003년03월31일

(87) 국제공개번호 WO 2003/088320

국제공개일자 2003년10월23일

(30) 우선권주장

10/118,317 2002년04월09일 미국(US)

(56) 선행기술조사문헌

JP13339100 A\*

KR1020020000141 A\*

US0686982 B2

US5804834 A

\*는 심사관에 의하여 인용된 문헌

전체 청구항 수 : 총 35 항

심사관 : 조근상

(54) 금속 지지막을 사용한 수직 디바이스 및 그 제조방법

### (57) 요 약

본 발명은 사파이어 기판과 같은 절연 기판 상에 GaN LED와 같은 반도체 디바이스를 제조하는 방법에 관한 것이다. 반도체 층들은 통상적인 기술을 이용하여 절연 기판 상에 형성된다. 개별 디바이스들의 경계를 구획하는 트렌치들이 반도체 층들을 관통하여 절연 기판 안으로 형성되며, 이는 유도결합 플라스마 반응성 이온 에칭에 의해 수행되는 것이 바람직하다. 제1 지지구조물이 반도체 층들에 부착된다. 다음으로, 단단한 기판이 제거되며, 이는 레이저 리프트오프에 의해 수행되는 것이 바람직하다. 바람직하게는 전도성인 제2 지지구조물로 단단한 기판을 대체하고 제1 지지구조물은 제거된다. 이어서, 개별 디바이스들이 다이싱되며, 이는 제2 지지구조물을 통한 에칭에 의하는 것이 바람직하다. 보호 포토레지스트 층이 반도체 층들을 제1 지지구조물의 부착으로부터 보호할 수 있다. (가능하면 반사성인) 전도성 저면 접촉부가 제2 지지구조물과 반도체 층들 사이에 삽입될 수 있다.

**대 표 도** - 도10

## 특허청구의 범위

### 청구항 1

제 1 표면과, 상기 제 1 표면과 반대면인 제 2 표면을 갖는 도전성 부착 구조물;

상기 제 1 표면 상에 위치하는 도전성 후막 지지부;

상기 제 2 표면 상에 위치하며, 상부 전기 접촉부를 가지는 반도체 디바이스; 및

상기 제 2 표면 및 상기 반도체 디바이스 사이에 배치되며, 상기 도전성 부착 구조물과 반도체 디바이스 사이에

서 전기 접촉부로 작용하는 반사성 접촉 구조물을 포함하고,

상기 도전성 후막 지지부 및 상기 상부 전기 접촉부 사이에 전류가 흐르는 것을 특징으로 하는 수직 토플로지

(topology) 디바이스.

### 청구항 2

삭제

### 청구항 3

제 1 항에 있어서,

상기 반사성 접촉 구조물은 알루미늄 층 및/또는 티타늄 층을 포함하는 것을 특징으로 하는 수직 토플로지 디바이스.

### 청구항 4

삭제

### 청구항 5

제 1 항에 있어서,

상기 반도체 디바이스는 상기 제 2 표면에 인접한 버퍼층을 포함하는 것을 특징으로 하는 수직 토플로지 디바이스.

### 청구항 6

제 1 항에 있어서,

상기 도전성 부착 구조물은 Cr 부착층을 포함하는 것을 특징으로 하는 수직 토플로지 디바이스.

### 청구항 7

제 1 항에 있어서,

상기 도전성 부착 구조물은 Au 부착층을 포함하는 것을 특징으로 하는 수직 토플로지 디바이스.

### 청구항 8

제 1 항에 있어서,

상기 후막 지지부는 1 내지 100 마이크론 두께인 것을 특징으로 하는 수직 토플로지 디바이스.

### 청구항 9

제 1 항에 있어서,

상기 후막 지지부는 Cu 또는 Al을 포함하는 것을 특징으로 하는 수직 토플로지 디바이스.

### 청구항 10

제 1 항에 있어서, 상기 반도체 디바이스는,

GaN 계열 디바이스인 것을 특징으로 하는 수직 토플로지 디바이스.

#### 청구항 11

제 1 항에 있어서, 상기 반도체 디바이스는,

발광 소자 구조인 것을 특징으로 하는 수직 토플로지 디바이스.

#### 청구항 12

제 1 항에 있어서, 상기 반도체 디바이스는,

p-형 반도체층과;

상기 p-형 반도체층 상에 위치하는 활성층과;

상기 활성층 상에 위치하는 n-형 반도체층을 포함하는 것을 특징으로 하는 수직 토플로지 디바이스.

#### 청구항 13

제 12 항에 있어서,

상기 활성층은 AlInGaN을 포함하는 것을 특징으로 하는 수직 토플로지 발광 디바이스.

#### 청구항 14

제 1 항에 있어서, 상기 반도체 디바이스는,

n-형 반도체층과;

상기 n-형 반도체층 상에 위치하는 활성층과;

상기 활성층 상에 위치하는 p-형 반도체층을 포함하는 것을 특징으로 하는 수직 토플로지 디바이스.

#### 청구항 15

제 14 항에 있어서,

상기 p-형 반도체층과 상기 상부 전기 접촉부 사이에는 p 투명 접촉부를 더욱 포함하는 것을 특징으로 하는 수직 토플로지 디바이스.

#### 청구항 16

도전성 후막 지지부;

상기 도전성 후막 지지부 상에 위치하며, 반사성의 제 1 접촉부;

상기 제 1 접촉부 상에 위치하는 다층 구조의 반도체층; 및

상기 반도체층 상에 위치하는 제 2 접촉부를 포함하고,

상기 도전성 후막 지지부 및 상기 제 2 접촉부 사이에 전류가 흐를 수 있고, 상기 제 1 접촉부는 상기 다층 구조의 반도체층에서 발생된 빛을 반사시키는 것을 특징으로 하는 수직 토플로지(topology) 발광 다이오드.

#### 청구항 17

제 16 항에 있어서,

상기 도전성 후막 지지부와 상기 제 1 접촉부 사이에는 도전성 부착층을 더 포함하는 것을 특징으로 하는 수직 토플로지 발광 다이오드.

#### 청구항 18

삭제

#### 청구항 19

제 16 항에 있어서,

상기 제 1 접촉부는 Al을 포함하는 것을 특징으로 하는 수직 토플로지 발광 다이오드.

#### 청구항 20

제 17 항에 있어서,

상기 도전성 부착층은 Au 및/또는 Cr을 포함하는 것을 특징으로 하는 수직 토플로지 발광 다이오드.

#### 청구항 21

제 16 항에 있어서, 상기 다층구조의 반도체층은,

제 1 도전형 GaN 반도체층;

상기 제 1 도전형 GaN 반도체층 상에 위치하는 활성층; 및

상기 활성층 상에 위치하는 제 2 도전형 GaN 반도체층을 포함하는 것을 특징으로 하는 수직 토플로지 발광 다이오드.

#### 청구항 22

제 16 항에 있어서,

상기 후막 지지부는 Cu 또는 Al을 포함하는 것을 특징으로 하는 수직 토플로지 발광 다이오드.

#### 청구항 23

절연 기판 상에 복수의 반도체층을 에피택셜 성장시키는 단계;

상기 반도체층 상에 제 1 접촉부를 형성하는 단계;

제 1 접촉부가 형성된 반도체층 상에 제 1지지 구조물을 부착하는 단계;

상기 반도체층으로부터 상기 절연 기판을 제거하는 단계;

상기 절연 기판이 제거된 반도체층에 도전성 제 2지지 구조물을 부착하는 단계; 및

상기 제 1지지 구조물을 제거하는 단계를 포함하는 반도체 디바이스 생산 방법.

#### 청구항 24

제 23 항에 있어서, 상기 반도체층을 에피택셜 성장시키는 단계 이후에는,

상기 반도체층 또는 절연 기판을 식각하여 복수의 개별 반도체 디바이스들을 구획하는 트렌치(trench)를 형성하는 단계를 더 포함하는 반도체 디바이스 생산 방법.

#### 청구항 25

제 24 항에 있어서,

상기 트렌치들에 맞추어서 상기 도전성 제 2지지 구조물을 예칭하는 단계를 더욱 포함하는 것을 특징으로 하는 반도체 디바이스 생산 방법.

#### 청구항 26

제 25 항에 있어서,

상기 개별 반도체 디바이스들을 분리하는 단계를 더욱 포함하는 것을 특징으로 하는 반도체 디바이스 생산 방법.

#### 청구항 27

제 26 항에 있어서,

상기 개별 반도체 디바이스들을 분리하는 단계는 상기 트렌치들에 스트레스를 가함으로써 달성되는 것을 특징으로 하는 반도체 디바이스 생산 방법.

#### 청구항 28

제 26 항에 있어서,

상기 개별 반도체 디바이스들을 분리하는 단계는 톱질을 함으로써 달성되는 것을 특징으로 하는 반도체 디바이스 생산 방법.

#### 청구항 29

제 23 항에 있어서,

상기 절연 기판 상에 복수의 반도체 층들을 에피택셜 성장시키는 단계는 사파이어 기판 상에 GaN 반도체층을 형성하는 단계를 포함하는 것을 특징으로 하는 반도체 디바이스 생산 방법.

#### 청구항 30

제 24 항에 있어서,

상기 트렌치들은 유도 결합 플라스마 반응성 이온 에칭(ICP RIE)을 사용하여 형성되는 것을 특징으로 하는 반도체 디바이스 생산 방법.

#### 청구항 31

제 23 항에 있어서,

상기 제 1 접촉부가 형성된 반도체층 상에 제 1지지 구조물을 부착하는 단계는, 포토 레지스트 층을 이용하여 부착하는 것을 특징으로 하는 반도체 디바이스 생산 방법.

#### 청구항 32

제 23 항에 있어서,

상기 에피택셜 반도체 층들로부터 절연 기판을 제거하는 단계는 레이저 리프트 오프(laser lift off)를 사용하여 행해지는 것을 특징으로 하는 반도체 디바이스 생산 방법.

#### 청구항 33

제 32 항에 있어서, 레이저 리프트 오프는,

상기 절연 기판에 진공 척(vacuum chuck)을 부착하는 단계;

적어도 하나의 에피택셜 반도체 층을 가열하기 위해 상기 진공 척 및 절연 기판을 통해 레이저 광을 조사하는 단계; 및

상기 절연 기판이 상기 에피택셜 반도체 층들로부터 분리될 때까지 레이저 조사 동안에 상기 에피택셜 반도체 층들로부터 상기 절연기판을 분리하려는 바이어스 힘을 가하는 단계를 포함하는 것을 특징으로 하는 반도체 디바이스 생산 방법.

#### 청구항 34

제 23 항에 있어서,

상기 제 2지지 구조물을 부착하는 단계는, 상기 에피택셜 반도체 층들 상에 상기 제 2지지 구조물을 부착하기 위한 부착 구조물을 형성하는 단계를 포함하는 것을 특징으로 하는 반도체 디바이스 생산 방법.

#### 청구항 35

제 34 항에 있어서,

상기 제 2지지 구조물을 부착하는 단계는 상기 부착 구조물 상에 도전성 제 2지지 구조물을 형성하는 단계를 포

함하는 것을 특징으로 하는 반도체 디바이스 생산 방법.

#### 청구항 36

삭제

#### 청구항 37

삭제

#### 청구항 38

제 34 항에 있어서,

상기 도전성 제 2지지 구조물을 형성하는 단계는 1 내지 100 마이크론 두께인 도전성 제 2지지 구조물을 형성하는 것을 특징으로 하는 반도체 디바이스 생산 방법.

#### 청구항 39

제 38 항에 있어서,

도전성 제 2 지지구조물을 형성하는 단계는 Cu 도전성 제 2지지 구조물을 형성하는 것을 특징으로 하는 반도체 디바이스 생산 방법.

#### 청구항 40

삭제

#### 청구항 41

제 23 항에 있어서,

상기 도전성 제 2지지 구조물을 형성하는 단계는, 상기 제 2지지 구조물 및 상기 에피택셜 반도체 층들 사이에 배치되는 반사성 층을 형성하는 단계를 포함하는 것을 특징으로 하는 반도체 디바이스 생산 방법.

#### 청구항 42

삭제

#### 청구항 43

삭제

#### 청구항 44

삭제

#### 청구항 45

삭제

#### 청구항 46

삭제

#### 청구항 47

삭제

#### 청구항 48

삭제

#### 청구항 49

삭제

청구항 50

삭제

청구항 51

삭제

청구항 52

삭제

청구항 53

삭제

청구항 54

삭제

청구항 55

삭제

청구항 56

삭제

청구항 57

삭제

청구항 58

삭제

청구항 59

삭제

청구항 60

삭제

청구항 61

삭제

## 명세서

### 기술분야

<1> 본 발명은 반도체 디바이스 제조에 관한 것이다. 보다 구체적으로, 본 발명은 금속 지지막을 사용한 수직 디바이스 및 그 제조방법에 관한 것이다.

### 배경기술

<2> 발광 다이오드(LED)는 전류를 빛으로 변환하는 잘 알려진 반도체 디바이스이다. LED에 의해 방출되는 빛의 색깔(파장)은 LED를 제조하는데 사용되는 반도체 재료에 따라 달라진다. 이는 방출되는 빛의 파장이 반도체 재료의 밴드갭(band-gap) 에너지에 따라 달라지기 때문이며, 상기 밴드갭 에너지는 가전자대(valence band)와 전도대(conduction band) 전자들 사이의 에너지 차이를 나타낸다.

- <3> 질화갈륨(GaN)은 LED 연구자들로부터 많은 주목을 받아왔다. 그 한 가지 이유는 GaN이 인듐과 결합되어, 녹색, 청색 및 백색의 가시광을 방출하는 InGaN/GaN 반도체 층들을 생성할 수 있기 때문이다. 이 과정 제어 능력은 LED 반도체 설계자들로 하여금 유익한 디바이스 특성을 이루어내기 위해 재료의 특성을 필요에 따라 변화시킬 수 있게 한다. 예를 들어, GaN은 LED 반도체 설계자들이, 천연색 디스플레이(display)와 광 기록(optical recording)에 있어 유익한 청색 LED 및 청색 레이저 다이오드와, 백열전구를 대체할 수 있는 백색 LED를 생산할 수 있게 한다.

- <4> 상기 이점들 및 기타 이점들 때문에, GaN 기반 LED 시장은 급속히 성장하고 있다. 따라서, GaN 기반의 광전자 디바이스 기술은 1994년의 상업적 도입 이후 급속히 발전하였다. GaN 발광 다이오드의 효율이 백열 조명을 능가하였고, 현재는 형광 조명에 필적하므로, GaN 기반 LED 시장은 급속 성장을 계속할 것으로 기대된다.

- <5> GaN 디바이스 기술의 급속한 발전에도 불구하고, GaN 디바이스들은 많은 응용분야에 있어서 너무 비싸다. 그 한 가지 이유는 GaN 기반 디바이스들의 높은 제조비용이며, 이는 다시 GaN 에피층(epitaxial layers)의 성장 및 이에 뒤따르는 완성된 GaN 기반 디바이스들의 다이싱이 어렵다는 점에 관련된다.

- <6> GaN 기반 디바이스들은 일반적으로 사파이어 기판 상에서 제조된다. 이는 사파이어 웨이퍼들이 GaN 기반 디바이스들의 대량생산에 적합한 크기로 시장에서 입수 가능하기 때문이고, 사파이어가 고품질의 GaN 에피층 성장을 지원하기 때문이며, 또한 사파이어의 광범위한 온도처리능력 때문이다. 전형적으로, GaN 기반 디바이스들은 두께가 330 또는 430 마이크론인 2" 직경의 사파이어 웨이퍼 상에서 제조된다. 상기 직경은 수천 개의 개별 디바이스들을 제조할 수 있게 하는 한편, 상기 두께는 웨이퍼의 과도한 뒤틀림(warping) 없이 디바이스 제조를 지원하기에 충분하다. 더욱이, 사파이어 결정은 화학적 및 열적으로 안정하며, 융점이 높아 고온 제조공정을 가능하게 하고, 높은 결합 에너지(122.4 kcal/mol) 및 높은 유전상수(dielectric constant)를 가진다. 화학적으로, 사파이어는 결정질 산화 알루미늄( $\text{Al}_2\text{O}_3$ )이다.

- <7> 사파이어 상에서의 반도체 디바이스 제조는 일반적으로 산화금속 화학기상증착(MOCVD) 또는 분자 범 성장법(MBE)을 사용하여 사파이어 기판 상에서 n-GaN 에피층을 성장시킴으로써 수행된다. 그 후에, GaN LED와 같은 다수의 개별 디바이스들이 통상의 반도체 공정기술을 이용하여 에피층 상에 제조된다. 개별 디바이스들이 제조된 후 이들은 사파이어 기판에서 다이싱되어야 한다. 그러나, 사파이어는 지극히 단단하고, 화학적으로 내성이 있으며, 또한 고유의 조개침 각(natural cleave angle)을 갖지 않으므로, 사파이어 기판들은 다이싱하기 어렵다. 사실, 다이싱은 일반적으로 사파이어 기판이 기계적인 그라인딩(grinding), 랩핑(lapping), 및/또는 폴리싱(polishing)에 의해 약 100 마이크론까지 얇게 만들어질 것을 요구한다. 이러한 기계적 과정들은 시간이 걸리고 비싸며, 또한 이러한 과정들은 디바이스 수율을 감소시킨다는 점에 유의해야 한다. 얇게 만든 후에도 사파이어는 여전히 다이싱하기가 어렵다. 따라서, 얇게 만들고 폴리싱한 후에, 사파이어 기판은 통상적으로 지지 테이프에 부착된다. 그 후, 다이아몬드 톱 또는 스타일러스 형(stylus forms)이 개별 디바이스들 사이에 선들을 긋는다. 이러한 선긋기는 하나의 기판을 처리하는데 적어도 30분이 걸리므로, 제조비용을 더욱 증가시킨다. 선긋기 후에, 사파이어 기판들은 고무 롤러를 사용하여 압연됨으로써 그은 선들로부터 전파되며 곧이어 개별 반도체 디바이스들을 다이싱하게 되는 용력 크랙을 발생시킨다. 이러한 기계적인 처리는 수율을 더욱더 감소시킨다.

- <8> 사파이어 기판 또는 일반적으로 기타 절연 기판으로부터 개별 디바이스들을 다이싱하는 것에 대한 전술한 문제점들에 더하여, 사파이어 기판이나 기타 절연 기판은 다른 결점들을 갖고 있다. 유의할 것은, 사파이어가 절연체이기 때문에, 사파이어 기판(또는 기타 절연 기판)을 사용할 때 이용 가능한 디바이스 토폴로지(topology)가 제한된다는 점이다. 실무상으로 단지 두 개의 디바이스 토폴로지만이 존재한다. 즉, 측방향 및 수직의 두 가지이다. 측방향 토폴로지에서는 전류를 주입하는데 사용되는 금속제 전기 접촉부들이 둘 다 상부면 상에 위치된다. 수직 토폴로지에서는 기판이 제거되고, 하나의 금속제 접촉부는 상부면 상에, 다른 하나의 접촉부는 하부면상에 있다.

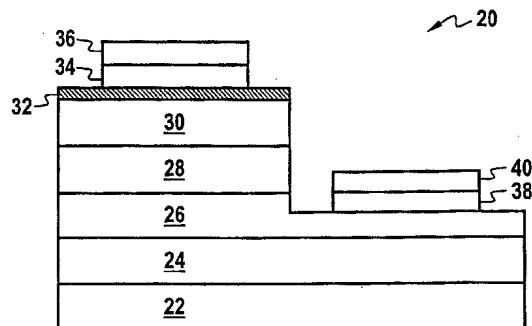

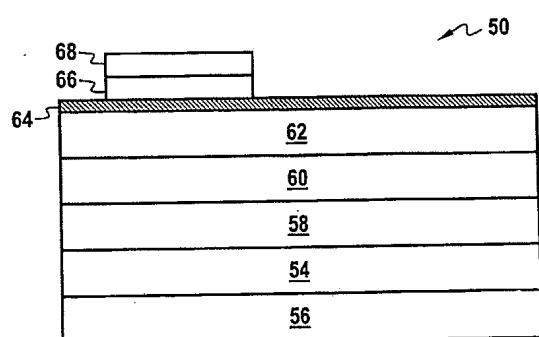

- <9> 도 1a 및 도 1b는 사파이어 기판(22) 상에 제조된 전형적인 측방향 GaN 기반 LED(20)를 도시한다. 특히 도 1a를 참조하면, n-GaN 버퍼층(buffer layer)(24)이 기판(22) 상에 형성된다. 비교적 두꺼운 n-GaN 층(26)이 버퍼층(24) 위에 형성된다. 질화-알루미늄-인듐-갈륨 또는 InGaN/GaN의 다중 양자 우물(multiple quantum wells)을 갖는 활성층(28)이 그 후 n형 GaN 층(26) 위에 형성된다. p-GaN 층(30)이 다음으로 활성층(26) 위에 형성된다. 이어서 투명 전도성 층(32)이 p-GaN 층(30) 위에 형성된다. 투명 전도성 층(32)은 Ru/Au, Ni/Au 또는 산화-인듐-주석(ITO)과 같은 임의의 적합한 물질로 만들어질 수 있다. 다음으로 p형 전극(34)이 투명 전도성 층(32)의 일측에 형성된다. 적합한 p형 전극 재료에는 Ni/Au, Pd/Au, Pd/Ni 및 Pt가 포함된다. 다음으로

패드(36)가 p형 전극(34) 위에 형성된다. 패드(36)는 Au로 하는 것이 유익하다. 투명 전도성 층(32), p-GaN 층(30), 활성층(28) 및 일부 n-GaN 층(26)은 에칭되어 단차부를 형성한다. GaN을 습식 에칭하는 것의 어려움 때문에, 건식 에칭이 단차부를 형성하는데 보통 사용된다. 이러한 에칭은 추가적인 리소그라피(lithography) 및 스트립핑(stripping) 공정을 필요로 한다. 더욱이, 건식 에칭 공정 중에 GaN 단차부 면에 대한 플라스마 손상을 종종 입게 된다. LED(20)는 n-전극 패드(38)(보통 Au) 및 패드(40)를 단차부 상에 형성함으로써 완료된다.

<10> 도 1b는 LED(20)의 평면도를 도시한다. 보는 바와 같이, 측방향 GaN 기반 LED는 두 금속 접촉부(36,40) 모두를 LED의 동일한 쪽에 가짐으로써 광 방출에 이용가능한 표면적을 크게 감소시킨다는 점에서 중대한 결점을 갖는다. 도 1b에 도시된 바와 같이, 금속 접촉부(36,40)는 물리적으로 서로 가깝다. 게다가, 전술한 바와 같이 패드(36)는 종종 Au이다. 외부 와이어본드(wire bond)가 패드(36,40)에 부착될 때 상기 Au는 종종 확산된다. Au 확산은 전기 접촉부들을 더욱 가깝게 할 수 있다. 이렇게 가깝게 배치된 전극들(34)은 ESD 문제의 영향을 받기가 매우 쉽다.

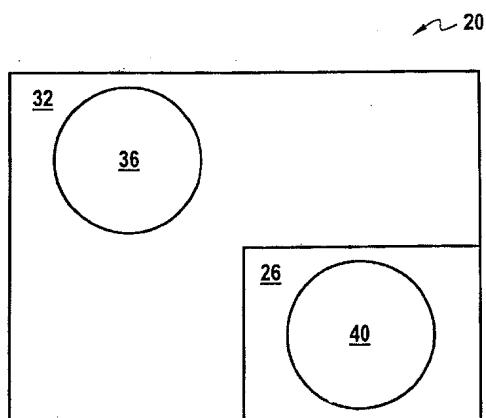

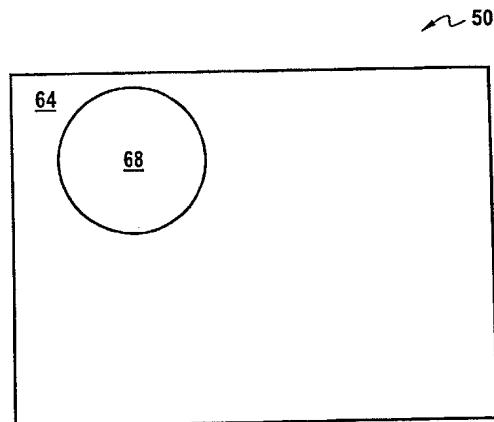

<11> 도 2a 및 도 2b는 추후 제거된 사파이어 기판 상에 형성된 수직 GaN 기반 LED(50)를 도시한다. 특히 도 2a를 참조하면, LED(50)는 저면 측에 n-금속 접촉부(56)를 그리고 반대측에 비교적 두꺼운 n-GaN 층(58)을 가지는 GaN 베퍼층(54)을 포함한다. n-금속 접촉부(56)는 고전도율 금속(바람직하게는 Au)에 의해 덮어씌워지는 고반사율 층으로부터 형성되는 것이 유익하다. 다중 양자 우물을 가지는 활성층(60)이 n형 GaN 층(58) 위에 형성되고, p-GaN 층(62)이 활성층(60) 위에 형성된다. 다음으로 투명 전도성 층(64)이 p-GaN 층(62) 위에 형성되고, p-형 전극(66)이 투명 전도성 층(64) 위에 형성된다. 패드(68)가 p형 전극(66) 위에 형성된다. 상기 여러 층들의 재료는 측방향 LED(20)에서 사용된 것들과 유사하다. 수직 GaN 기반 LED(50)는 단차부 에칭이 필요하지 않다는 이점을 갖는다. 그러나, n-금속 접촉부(56)를 GaN 베퍼층(54) 아래에 위치시키기 위해서는 사파이어 기판(도시되지 않음)을 제거해야만 한다. 이러한 제거는 곤란할 수 있으며, 특히 디바이스 수율이 문제가 된다면 더욱 그러하다. 하지만, 이어서 논의되는 바와 같이, 레이저 리프트오프(laser lift off)를 이용한 사파이어 기판 제거가 알려져 있다(2000년 6월 6일자로 발행된 "선택적 광학 공정에 의한 투명 기판으로부터의 박막 분리(Separation of Thin Films From Transparent Substrates By Selective Processing)"라는 명칭의 청(Cheung) 등의 미국특허 6,071,795와, 켈리(Kelly) 등의 "그룹 III-질화물 막의 리프트오프를 위한 광학 공정(Optical process for liftoff of group III-nitride films)", Physica Status Solidi (a) vol. 159, 1997, pp.R3-R4를 참조할 것).

<12> 도 2b를 참조하면, 수직 GaN 기반 LED는 하나의 금속 접촉부(68)만이 광 방출을 차단한다는 이점을 갖는다. 따라서, 동일한 광 방출 면적을 제공하기 위해서는, 측방향 GaN 기반 LED는 더 큰 표면적을 가져야 하며, 이는 디바이스 수율을 낮추게 된다. 더욱이, 수직 GaN 기반 LED에 사용되는 n형 접촉부(56)의 반사층은 측방향 GaN 기반 LED에서는 흡수되었을 빛을 반사한다. 따라서, 수직 GaN 기반 LED와 동일한 양의 빛을 방출하기 위해서는, 측방향 GaN 기반 LED는 훨씬 더 큰 표면적을 가져야만 한다. 이러한 문제들 때문에, 2" 직경의 사파이어 웨이퍼는 수직 GaN 기반 LED는 약 35,000개를 생산할 수 있는 반면에, 측방향 GaN 기반 LED는 약 12,000개밖에 생산하지 못한다. 더욱이, 측방향 토폴로지는 정전기에 더 취약한데, 이는 주로 두 개의 전극들(36,40)이 서로 매우 가깝기 때문이다. 게다가, 측방향 토폴로지는 절연 기판 상에 제조되기 때문에, 그리고 수직 토폴로지는 히트 싱크(heat sink)에 부착될 수 있기 때문에, 측방향 토폴로지는 열 발산이 비교적 취약하다. 따라서, 여러 관점에서, 수직 토폴로지가 측방향 토폴로지에 비해 사용상 우월하다.

<13> 그러나, 절연 기판 상에 제조된 대부분의 GaN 기반 LED는 측방향 토폴로지를 갖는다. 이는 주로 절연 기판 제거의 어려움과 지지 기판 없이 GaN 웨이퍼 구조물을 취급하는 어려움 때문이다. 이러한 문제점들에도 불구하고, 절연(성장) 기판의 제거와, 이에 뒤따르는, 위와 같이 만들어진 GaN 기반 웨이퍼를 Pd/In 금속층들을 이용하여 Si 기판 상에 웨이퍼 본딩하는 것이 매우 작은 면적의 웨이퍼, 대략 1cm × 1cm 면적의 웨이퍼에 대해 실증되었다(버클리 소재 캘리포니아 대학 및 제록스 사에 의해 보고됨). 하지만, 기판 제거 및 뒤따르는 대면적 웨이퍼의 웨이퍼 본딩은, GaN 웨이퍼와 제2(대체용) 기판 사이의 불균질한 본딩 때문에, 여전히 매우 어렵다. 이는 주로 레이저 리프트오프 중 및 그 후의 웨이퍼 휨(bowing) 때문이다.

<14> 따라서, 원래의(성장) 절연 기판을 제2의(대체용) 기판으로 대신하는 보다 우수한 방법이 유익할 것임은 명백하다. 특히, 웨이퍼의 기계적 안정성을 제공하고, 우수한 전기적 접촉을 지원하며, 열 발산에 도움을 주는 방법이 매우 유용할 것이며, 이는 특히 레이저 다이오드나 고출력 LED와 같이 높은 전류 주입을 받는 디바이스들에 있어서 그러하다. 이는 반도체 층들을 절연 기판 위에 형성하고, 이어서 절연 기판을 제거하여 형성된 반도체 층들을 가지는 웨이퍼를 격리시키며, 다음으로 웨이퍼를 금속 대용 기판에 부착하는 것을 가능하게 할 것이

다. 사파이어 기판을 부분적으로 제조된 반도체 디바이스들로부터 제거하기에 적합한 새로운 방법이 특히 유익할 것이며, 이 디바이스들이 GaN 기반 디바이스들이라면 특히 그러하다. 예를 들어, 반도체 층들을 사파이어 기판으로부터 제거하고, 부분적으로 제조된 반도체 디바이스들을 가지는 웨이퍼를 격리시켜 웨이퍼의 휨(warping)이 감소되거나 방지되며, 다음으로 금속 지지층으로 대체하는 방법이 유용할 것이다. 보다 구체적으로, 사파이어 기판(또는 기타 다른 절연 기판) 상에 GaN 기반 디바이스들을 부분적으로 제조하고, 이어서 전도성 지지층으로 대체하며, 다음으로 대체한 층을 다이싱하여 수직 토폴로지 GaN 기반 LED를 생산하는 방법이 유익할 것이다.

### 발명의 상세한 설명

- <15> 아래 본 발명의 개요는 본 발명 특유의 혁신적인 특징들 일부를 보다 쉽게 이해할 수 있도록 하기 위하여 제공되며, 본 발명을 완전하게 설명하려는 것은 아니다. 본 발명의 여러 측면의 완전한 이해는 명세서 전체와, 청구범위, 도면 및 요약서를 전체로서 파악할 때 얻을 수 있다.

- <16> 본 발명의 원리는 절연 기판 상에 반도체 디바이스들을 제조하는 방법으로서, 우선 절연 기판 상에 반도체 층들을 형성하고, 이어서 절연 기판을 제거하여 형성된 반도체 층들을 가지는 웨이퍼를 격리시키며, 다음으로 웨이퍼를 지지할 금속 지지층을 (반도체 층 위 또는 아래에) 추가하고, 이 모든 과정에 있어 휨 및/또는 다른 손상을 방지하도록 웨이퍼가 지지되는 반도체 디바이스 제조방법을 제공한다.

- <17> 본 발명의 원리는 금속 지지막을 이용하여 절연 기판 상에 GaN 기반 수직 디바이스들을 제조하는 방법을 또한 제공한다. 상기 방법에 따르면, GaN 기반 디바이스들을 위한 반도체 층들이 통상적인 반도체 제조 기술을 이용하여 절연(사파이어) 기판 상에 형성된다. 다음으로, 트렌치들(trenches)이 반도체 층들을 통과하여 절연 기판 안으로 형성된다. 상기 트렌치들은 유도결합 플라스마 반응성 이온 에칭(ICP RIE)을 이용하여 제조되는 것이 바람직하다. 이어서, 제1 지지구조물이 반도체 층들에 부착된다. 제1 지지구조물은 실리콘으로 이루어지는 것이 바람직하지만, 거의 모든 단단하고 평평한 면이 사용가능하다. 상기 제1 지지구조물은 에폭시 접착제를 사용하여, 가능한 한 반도체 층 위에 보호용 포토레지스트(photo-resist) 층을 구비하여, 반도체 층들에 부착되는 것이 바람직하다. 다음으로, 절연 기판이 제거되며, 이때 레이저 리프트오프 공정을 사용하는 것이 바람직하다. 다음으로, 제2 지지구조물로 절연 기판을 대체한다. 제2 지지구조물은 Cu, Au, 또는 Al의 금속막으로 이루어지는 것이 바람직하지만, 거의 모든 전도성 막이 사용가능하다. 필요하다면, 전도성 접촉부가 반도체 층과 제2 지지구조물 사이에 삽입될 수 있다. LED의 경우, 전도성 접촉부를 반사성으로 하여 광자들을 위쪽으로 되튀게 함으로써 저면 리드 프레임(lead frame)에서의 흡수를 방지하는 것이 바람직하다. 그 다음에 제1 지지구조물이 제거된다. 이어서 개별 디바이스들이 다이싱되며, 이는 기계적 다이싱 또는 제2 지지구조물을 통한 습/건식 에칭에 의해 수행되는 것이 바람직하다.

- <18> 아래의 설명은 반도체 층들 위에 금속 지지막을 형성하는 다른 방법을 설명한다. 반도체 층들을 관통하여 절연 기판 안으로 트렌치를 형성하는 것은 상술한 과정과 동일하다. 그 다음으로, 반도체 층들을 지지구조물(Si 또는 단단하고 평평한 면) 위로 부착하는 대신에, 화학적 및/또는 물리적 증착(deposition) 기술(전기도금 또는 비전기도금 등과 같은)을 이용하여, 두꺼운 금속 지지막이 GaN 기반 디바이스들 위에 증착된다. 이어서, 절연 기판이 제거되며, 이는 레이저 리프트오프 공정을 이용하는 것이 바람직하다. 두꺼운 금속 지지막은 Cu, Au 또는 Al로 이루어지는 것이 바람직하지만, 거의 모든 전도성 막이 사용가능하다. 필요하다면, 전도성 접촉부를 반도체 층과 제2 지지구조물 사이에 삽입할 수 있다. LED의 경우에는, LED의 경우, 전도성 접촉부를 반사성으로 하여 광자들을 위쪽으로 되튀게 함으로써 저면 리드 프레임에서의 흡수를 방지하는 것이 바람직하다. 그 후에, 전기 접촉부들이 반도체 층들의 노출된 표면 위에 형성될 수 있다. 이어서 개별 디바이스들이 다이싱되며, 이는 기계적 다이싱 또는 두꺼운 금속 지지막을 통한 습/건식 에칭에 의해 수행되는 것이 바람직하다.

- <19> 본 발명의 원리는 사파이어 기판 상에 수직 토폴로지 GaN 기반 LED를 제조하는 방법을 특히 제공한다. 상기 방법에 따르면, 수직 토폴로지 GaN 기반 LED를 위한 반도체 층들이 통상적인 반도체 제조 기술을 이용하여 사파이어 기판 상에 형성된다. 다음으로, 트렌치들이 반도체 층들을 관통하여 사파이어 기판 안으로 형성된다. 상기 트렌치들은 개별 수직 토폴로지 GaN 기반 LED의 경계를 구획한다. 트렌치들은 ICP RIE를 이용하여 제조되는 것이 바람직하다. 이어서, 보호 포토레지스트 층이 반도체 층들 위로 위치된다. 그 다음에, 제1 지지구조물이 반도체 층들에 부착된다. 제1 지지구조물은 실리콘 판으로 하는 것이 바람직하나, 거의 모든 단단하고 평평한 재료가 사용가능하다. 제1 지지구조물은 에폭시 접착제를 사용하여 반도체 층들(또는 포토레지스트 층)에 부착되는 것이 바람직하다. 다음으로, 사파이어 기판이 제거되며, 이는 레이저 리프트오프 공정을 이용하는 것이 바람직하다. 이어서, 전도성 저면 접촉부가 노출된 반도체 층 위에 위치된다. 상기 전도성 저면 접촉부는 반

사층을 포함하는 것이 바람직하다. Cr 및/또는 Au층과 같은 하나 이상의 접착지지층이 반사층 위로 형성된다. 다음으로, 제2 지지구조물로 사파이어 기판을 대체한다. 제2 지지구조물은 Cu, Au 또는 Al의 전도성 막으로 이루어지는 것이 바람직하나, 거의 모든 전도성 막이 사용가능하다. 그 후, 제1 지지구조물이 제거된다. 마지막으로, 개별 디바이스 다이들이 다이싱되며, 이는 기계적 다이싱 또는 제2 지지구조물을 통한 습/건식 에칭에 의해 수행되는 것이 바람직하다. 기계적 압연 또는 전단 커팅(shear cutting)을 사용하여 다이(die)들을 분리할 수 있다.

<20> 본 발명의 원리는 사파이어 기판 상에 수직 토폴로지 GaN 기반 LED를 제조하는 다른 방법을 또한 제공한다. 상기 방법에 따르면, 수직 토폴로지 GaN 기반 LED를 위한 반도체 층들이 통상적인 반도체 제조 기술을 이용하여 사파이어 기판 상에 형성된다. 다음으로, 트렌치들이 반도체 층들을 관통하여 사파이어 기판 안으로 형성된다. 상기 트렌치들은 개별 수직 토폴로지 GaN 기반 LED의 경계를 구획한다. 트렌치들은 ICP RIE를 이용하여 제조되는 것이 바람직하다. 이어서, 예를 들어 Cr 및 Au의 층들로 이루어진 접촉층이 반도체 층들 위로 위치된다. 그 다음에, 금속 지지구조물이 접촉층/반도체 층들 위로 형성된다. 다음으로, 사파이어 기판이 제거되며, 이는 레이저 리프트오프 공정을 이용하는 것이 바람직하다. 이어서, 전도성 저면 접촉부가 나중에 노출된 반도체 층 위에 위치된다. 마지막으로, 개별 디바이스 다이들이 다이싱되며, 이는 기계적 다이싱 또는 금속 지지구조물을 통한 습/건식 에칭에 의해 수행되는 것이 바람직하다.

<21> 본 발명의 신규한 특징들은 당업자라면 아래 본 발명의 상세한 설명을 검토하거나 또는 본 발명을 실시함으로써 알 수 있다. 그러나, 본 발명의 상세한 설명 및 제시된 구체적인 예들은, 본 발명의 특정 실시예들을 나타내는 것이긴 하지만, 예시를 위한 목적으로만 제공된 것들이며, 이는 당업자라면 본 발명의 상세한 설명 및 그 다음의 청구범위로부터 본 발명의 사상과 범위 내에서 다양한 변경과 수정이 가능함을 알 수 있기 때문에 유의해야 한다.

### 실시예

<28> 본 발명의 원리들은 금속지지 후막(厚膜)들을 사용하여 절연 기판들 상에 GaN 기반 수직 디바이스들을 제조하는 방법을 제공한다. 상기 원리들은 사파이어 기판 상에 수직 토폴로지 GaN 기반 LED를 제조하는 방법의 자세한 설명에서 상술되어 있지만, 상기 원리들은 상기 방법보다 더 넓다. 따라서, 본 발명의 원리를 미국 특허법 하에서 이해되는 바와 같이 첨부된 청구의 범위에 의해서만 제한되어야 한다.

<29> 도 3 내지 25는 사파이어 기판을 사용하여 수직 토폴로지 GaN 기반 발광 다이오드(LED)를 제조하는 방법을 도시한다. 사파이어 기판들은 적당한 사이즈로 쉽게 사용될 수 있고, 열적 화학적 그리고 기계적으로 안정하고, 상대적으로 저렴하고, 양질의 GaN 에피택셜 층의 성장을 지원한다.

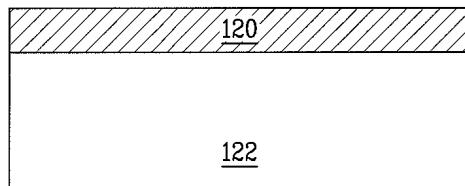

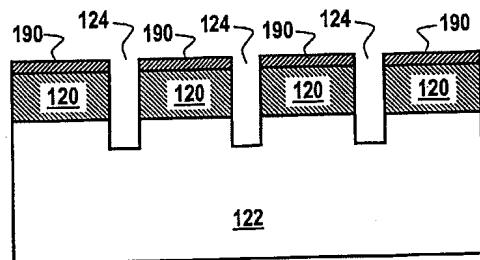

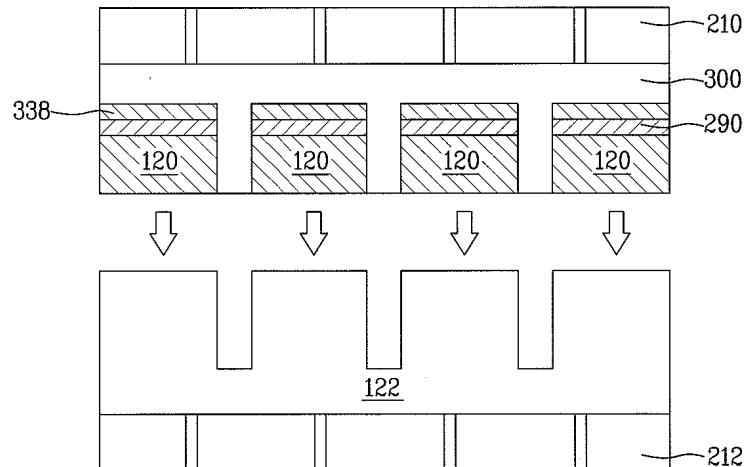

<30> 이제 도 3을 참조하면, 도 2A 내지 도 2B에서 도시된 수직 GaN 기반 LED(50)의 반도체 층과 유사하거나 동일한 수직 토폴로지 GaN 기반 LED 층 구조물(120)이 330 ~ 430 마이크론 두께의 2인치 직경의 사파이어 기판(122) 위에 형성된다. 예를 들면, 수직 토폴로지 GaN 기반 LED 층 구조물(120)은 청색광을 발광하기 위해 적절한 조성물을 갖는 InGaN/GaN 활성층(60)을 가질 수 있다. 수직 토폴로지 GaN 기반 LED 층 구조물(120)은 유익하게는 5마이크론 두께 미만이다. 적절한 도편트 및 다른 재료들과 함께, 기상 에피택셜, MOCVD, 및 MBE와 같은 다양한 표준 에피택셜 성장 기술들이 사용되어 수직 토폴로지 GaN 기반 LED 층 구조(120)를 생산할 수 있다.

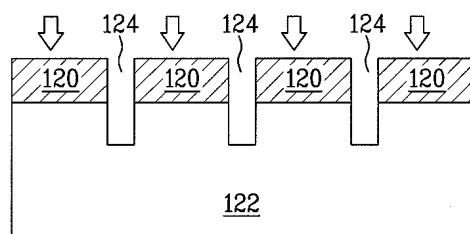

<31> 이제 도 4를 참조하면, 트렌치(trench)들(124)이 수직 토폴로지 GaN 기반 LED 층 구조(120)를 통과하여 사파이어 기판(122) 내부까지 형성된다. 트렌치는 생산되어 분리될 개별 LED 반도체 구조물들을 구획한다. 각 개별 LED 반도체 구조물은 유익하게는 약 200 마이크론 넓이의 정사각형이다. 트렌치들은 유익하게는 10 마이크론 넓이보다 좁고, 약 5마이크론 보다 깊게 사파이어 기판(122)으로 연장된다.

<32> 사파이어 및 GaN의 경도 때문에, 트렌치들(124)은 유익하게는 반응성 이온 에칭, 바람직하게는 유도 결합 플라스마 반응성 이온 에칭(ICP RIE)을 사용하여 도3의 구조물에 형성된다. ICP RIE를 사용하여 트렌치를 형성하는 것을 2개의 주요 공정을 거친다: 표시 라인의 형성 공정 및 에칭 공정. 표시 라인들은, 트렌치들(124)이 형성되어야 할 곳의 사파이어 기판(122)의 영역이 노출되는 포토 레지스트 패턴을 사용하여 도 3의 구조물 상에 형성된다. 노출되는 영역들은 표시 라인들이고 다른 모든 영역들은 포토레지스트에 의해 도포된다. 포토 레지스트 패턴은 유익하게는, 강력한 플라즈마를 견디는 상대적으로 단단한 포토 레지스트 물질로부터 제조된다. 예를 들어, 포토 레지스트는 AZ9269일 수 있는 한편, 표시 라인들을 형성하기 위해 포토 레지스트를 현상하기 위해 사용되는 현상물질은 AZ MIF 500일 수 있다.

<33> 설명되는 예에서, 포토 레지스트는 바람직하게는 약 10마이크론의 두께로 스펀 코팅된다. 그러나, 일반적으로,

포토 레지스트 두께는 수직 토플로지 GaN 기반 LED 층 구조(120)의 두께와 사파이어 기판(122) 내부로의 에칭 깊이의 합과 대략 동일해야 한다. 이는, 포토 레지스트 마스크가 에칭동안에 온전하도록 한다. 한 번의 공정으로 두꺼운 포토 레지스트 코팅을 형성하는 것은 어려우므로, 포토 레지스트는 한 번에 약 5 마이크론의 두께로 두 번 스핀 코팅된다. 제 1 포토 레지스트 코팅은 스핀 코팅된 다음, 약 90°F에서 약 15분 동안 소프트 베이킹(soft baking)된다. 그 다음, 제 2 포토 레지스트 코팅은 유사한 방법으로 도포되나, 약 110°F에서 약 8분 동안 소프트 베이킹된다. 그 다음, 포토 레지스트 코팅이 패터닝되어 표시 라인들을 형성한다. 이는 유익하게는 리소그래피 기술 및 현상을 사용하여 행해진다. 현상은 포토 레지스트 코팅의 두께 때문에 상대적으로 장시간 걸린다. 현상 이후에, 포토 레지스트 패턴은 약 80°F에서 약 30분 동안 하드 베이킹(hard baking)된다. 그 다음, 하드 베이킹된 포토 레지스트는 유익하게는 MCB(Metal Chlorobenzene) 트리트먼트에 약 3.5분 동안 담가 둔다. 이렇게 담가 두는 것은 포토 레지스트를 단단하게 한다.

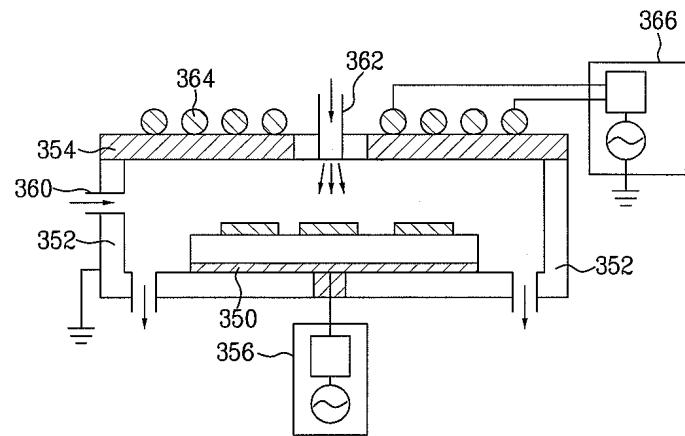

<34> 표시 라인들이 정의된 후에, 도 3의 구조물이 에칭된다. 도 5를 참조하면, ICP RIE 에칭 프로세스는 절연 창(354)(유익하게는 1cm 두께의 수정 창)을 갖는 RIE 챔버(352) 내에서 도 3의 구조물을 바닥 전극(350) 위에 둘으로써 행해진다. 바닥 전극(350)은, 에칭이 가능하도록 하기 위해 도 3의 구조물을 바이어스하는 바이어스 전압원(356)에 연결된다. 바이어스 전압원(356)은 유익하게는 13.56 MHz RF 전력 및 DC 바이어스 전압을 공급한다. 절연 창(354)으로부터 바닥 전극(350)까지의 거리는 유익하게는 약 6.5cm이다. Cl<sub>2</sub> 및 BCl<sub>3</sub>의 기체 혼합물(Ar 포함 가능)이 반응성 기체 포트(360)를 통해 RIE 챔버(352)로 주입된다. 더욱이, 포트(362)를 통해 챔버 내부로 전자들이 주입된다. 2.5-턴 정도의 나선형 Cu 코일(364)이 절연 창(365) 위에 위치한다. 13.56MHz의 무선 주파수(RF) 전력이 RF 소스(366)에서부터 코일(364)로 가해진다. 자기장이 RF 전력에 의해 절연 창(354)에 대해 직각으로 생성됨을 주목해야 한다.

<35> 도 5를 계속 참조하면, 코일(364)에 의해 생성된 전자기장 내에 있는 전자들이 주입된 기체의 중성 입자들과 충돌하여, 이온 및 중성자들을 생성하고, 이는 플라즈마를 생성한다. 플라즈마 내의 이온들은 바이어스 전압원(356)에 의해 바닥 전극(350)으로 가해지는 바이어스 전압에 의해 도 3의 구조물로 가속된다. 가속된 이온들이 표시 라인들을 통과하여, 에칭 채널(124)을 형성한다(도 4 참조).

<36> 도 4의 구조물과 함께, 2개의 일반적 절차 중에 하나를 사용하여 제조가 계속된다. 제 1 절차는 도 4의 구조물의 상부에 임시 기판을 형성하는 것이다. 제 2 절차는 도 4의 구조물 상부에 영구 금속층을 형성하는 것이다. 임시 기판의 형성에 대해 먼저 설명한 다음에(도 6 내지 15 참조), 영구 금속층의 사용에 대해 설명하겠다(도 16 내지 도 20 참조).

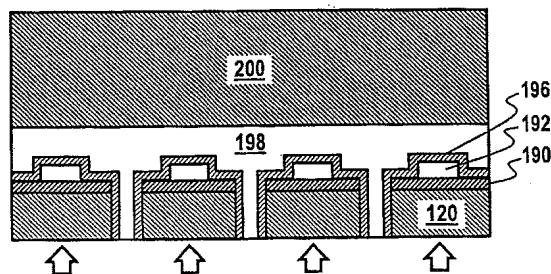

<37> 도 6을 참조하여, 트렌치들(124)이 형성된 후에, 얇은 투명 접촉부(190)가 수직 토플로지 GaN 기반 LED 층 구조물(120)의 개별 LED 반도체 구조물 위에 형성된다. 이들 투명 접촉부들(190)은 바람직하게는 Ru/Au, Ni/Au로 구성되거나 인듐 주석 산화물(ITO)/Au로 구성되고, 10nm 미만이다. 도 7에 도시된 바와 같이, 투명 접촉부들(190)이 형성된 다음, 금속 접촉 패드(192)가 각 투명 접촉부(190) 위에 위치한다. 금속 접촉 패드들(192)은 유익하게는 Pd, Pt, Au 또는 Al로 구성된다. 각 금속 접촉 패드(192)는 약 100마이크론의 직경을 갖고, 약 1마이크론의 두께를 갖는다. 얇은 Cr/Au 내부 층이 사용되어 투명 접촉부(190) 및 금속 접촉 패드(192) 사이의 부착을 향상시킬 수 있다.

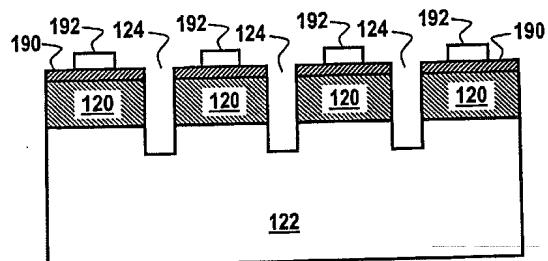

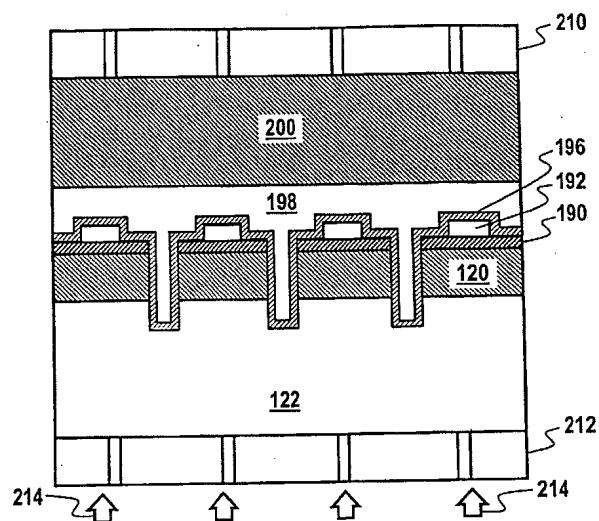

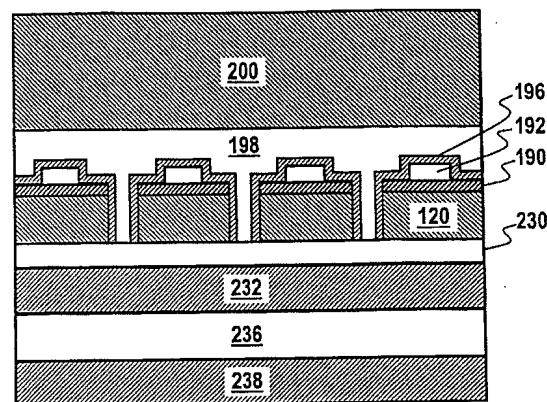

<38> 이제 도 8을 참조하면, 보호 포토 레지스트 막(196)이 도 7의 구조물 위에 형성된다. 상기 포토 레지스트 막은 GaN 기반 LED 층 구조물(120)을 보호하고, 이후 접합을 돋기 위한 것이다. 그 다음, 에폭시 접착제(198)가 사용되어 임시지지 웨이퍼(200) 형태를 가지는 제 1지지 구조물을 부착한다. 임시지지 웨이퍼(200)는 유익하게는 사파이어 웨이퍼보다 큰 실리콘 플레이트이다. 그러나, 기판 스와핑(이후 설명됨) 동안에 개별 LED 반도체 디바이스들을 포함하는 웨이퍼를 지지하는 충분한 두께를 갖는 거의 모든 임의의 딱딱하고 평편한 표면이라면 사용 가능하다. 계속 도 8을 참조하면, 제 1 기판 스와핑 프로세스는 사파이어 기판(122)의 후면(도 8의 바닥면)을 표면 연마하고 샌드블라스트(sand blast)(또는 건식 에칭 프로세서를 이용한 표면 거친 마무리(surface roughening))를 한다. 이 공정은 이후 행해지는 레이저 리프트 오프(laser lift off) 공정 동안에 일정한 레이저 빔 가열을 보장하도록 돋는다.

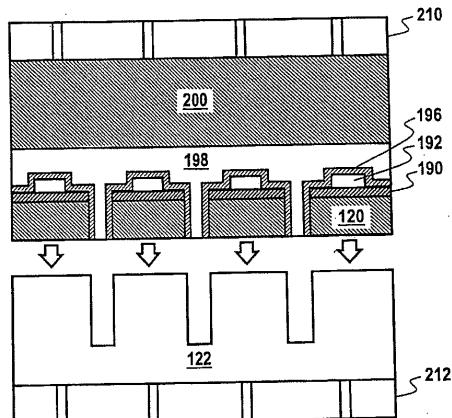

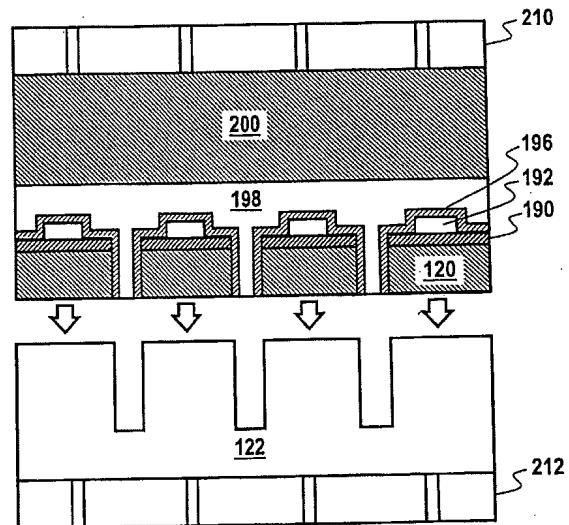

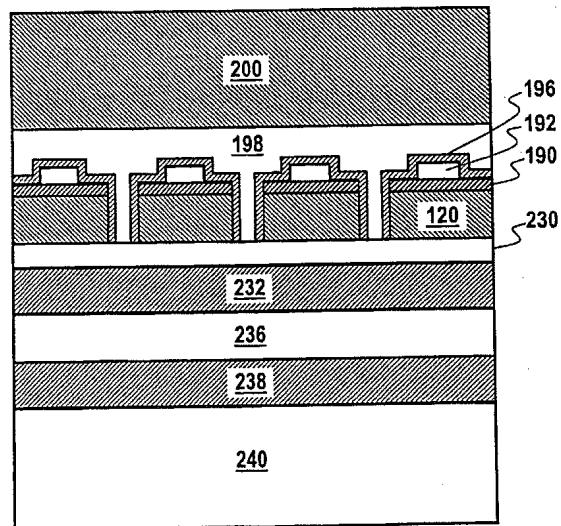

<39> 이제 도 9를 참조하면, 도 8에 도시된 구조물은 2개의 진공 척(chuck)에 부착된다. 제 1 진공 척(210)은 지지 웨이퍼(200)에 부착되고, 제 2 진공 척(212)은 사파이어 기판(122)에 부착된다. 그 후, 계속 도 9를 참조하면, 레이저 빔(214)이 사파이어 기판(122)을 통해 조사된다. 레이저 빔(214)은 유익하게는 3mm x 50mm 직사각형 빔과 200~600mJ/cm<sup>2</sup>의 빔 에너지를 갖는 248nm의 KrF 레이저이다. 248nm KrF 레이저 빔에 대해 투명한 물질, 바람직하게는 사파이어로 만들어진 진공 척들(210, 212)은 사파이어 기판(122)이 지지 웨이퍼(200)로부터 떨어지도록

록 바이어스 힘을 가한다. 레이저 조사 및 바이어스의 조합으로 인해, 도 10에 도시된 바와 같이 사파이어 기판(122)이 분리된다.

<40> 유사한 레이저 리프트 오프 프로세스가, 2000년 6월 6일에 등록되어 정 등(Cheung et al.)에게 허여되고 발명이 명칭이 "선택적 광학 프로세싱에 의한 투명 기판으로부터의 박막의 분리"인 미국특허 제6,071,795호와, 1997년의 Physica status Solidi(a) 159권의 R3 내지 R4 페이지의 켈리 등(Kelly et al.)에 의한 "그룹 III 질화물 막을 리프트 오프하기 위한 광학 프로세스"에 서술되어 있다. 유익하게는, 임시지지 웨이퍼(200)는 휘는 것을 막는 방식으로 수직 토플로지 GaN 기반 LED 층 구조(120) 내에서 개별 LED 반도체 구조물들을 충분히 지지한다.

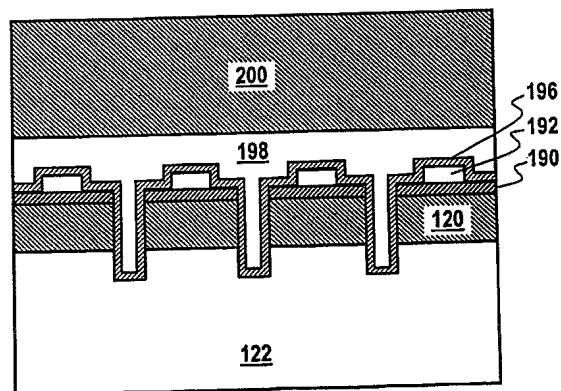

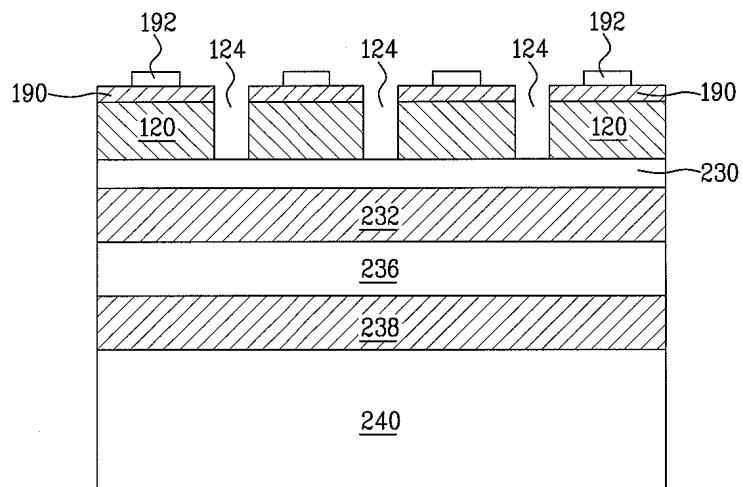

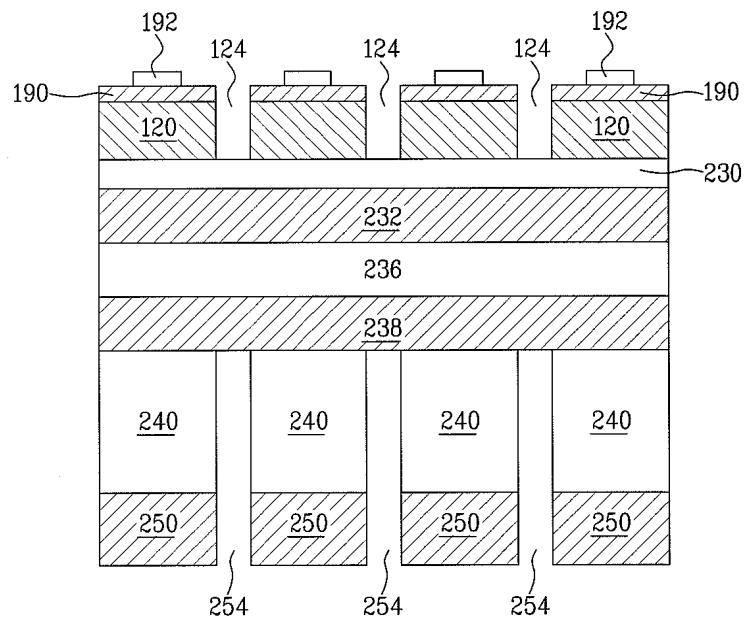

<41> 도 11을 참조하면, 사파이어 기판(122)이 제거된 후, 그 결과로 생기는 구조물의 바닥(임시지지 웨이퍼(200)에 대향하는 면)이 먼저 HCl로 청소되어, Ga 물방울을 제거한다(레이저 빔(214)은 GaN을 Ga + N으로 분리시키는 가열이 일어나도록 한다). 청소 후에, ICP RIE 에칭(전술 내용 참조) 및 연마가 행해진다. 상기 에칭 및 연마는 순수 n-GaN의 원자 수준의 평편한 표면을 노출시키고 생성한다. 이러한 평편한 표면은 이후 도포되는 반사성 구조물로부터 높은 반사도를 생성하는데 특히 유익하다. 반사성 층 도포에 앞서, 에칭된 n-GaN 표면은 더욱 청소되고, 왕수(aqua regia) 용액( $H_2SO_4$  및 HCl의 혼합물)으로 에칭되어 n-GaN 및 Ti/Al 금속 층들 간의 부착을 향상시킨다.

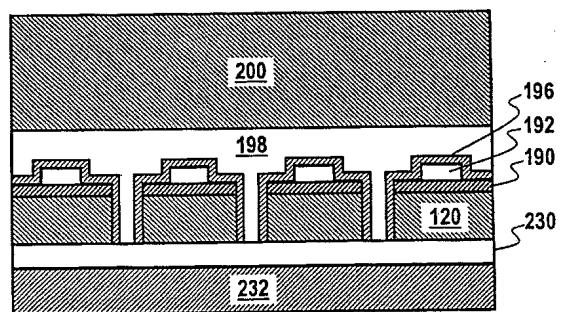

<42> 이제 도 12를 참조하면, 티타늄층(230) 및 알루미늄 층(232)으로 구성되는 도전성 반사성 구조물이 도 11의 구조물 바닥 위에 형성된다. 상기 반사성 구조물은, LED의 상부에서 나와서 LED 뒤의 바닥으로 향하여 조사되는 완전한 LED로부터의 광을 반사시킬 것이다. 이들 바닥 금속층들은 또한 LED 디바이스에 대해 n 타입 접촉층 역할을 한다.

<43> 이제 도 13을 참조하면, 연속적으로 생성되는 제 2지지 구조물의 형성을 돋기 위해, 약 30nm 두께 미만인 Cr 부착층(236)이 Al 층(232) 위에 형성되고, 약 100nm 두께 미만인 Au 부착층이 Cr 부착층(236) 위에 형성된다.

<44> 도 14를 이제 참조하면, Au 부착층(238)이 제 위치에 배치된 다음, Cu, Au 또는 Al 후막 지지부(240) 형태의 제 2지지 구조물이 Au 부착층(238) 위에 형성된다. 후막 지지부(240)는 물리 기상 증착법, 전기도금법, 무전해 도금법, 또는 다른 적절한 수단에 의해 형성될 수 있다. 상기 후막 지지부(240)는 바람직하게는 100마이크론 두께 미만이다. Cu, Au, 또는 Al 후막 지지부가 유익하지만, 거의 모든 임의의 전기 도전성, 및 유익하게는 열전도성 물질이면 사용가능하다.

<45> 도 15를 참조하면, 후막 지지부(240)가 제 위치로 배치된 다음, 에폭시 접착제(198) 및 임시지지 웨이퍼(200)가 제거된다. 상기 제거는 유익하게는, 임시지지 웨이퍼(200)를 제거할 수 있도록 에폭시 접착제를 약하게 하기 위해 도 14의 구조물을 가열함으로써 달성된다. 임시지지 웨이퍼(200)가 제거된 다음, 그 결과로 생기는 구조물은 아세톤에 담겨져서 포토 레지스트 및 잔류 에폭시 접착제(198)를 제거한다.

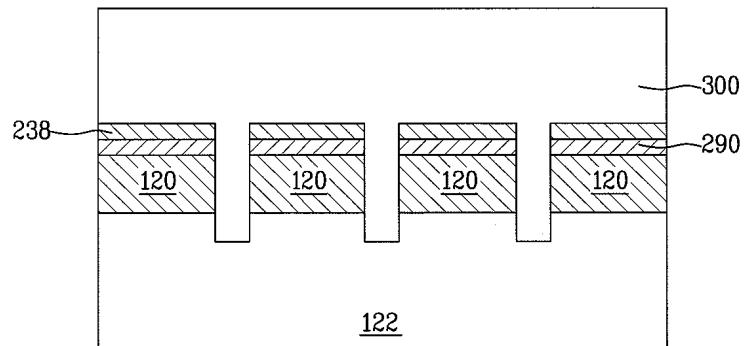

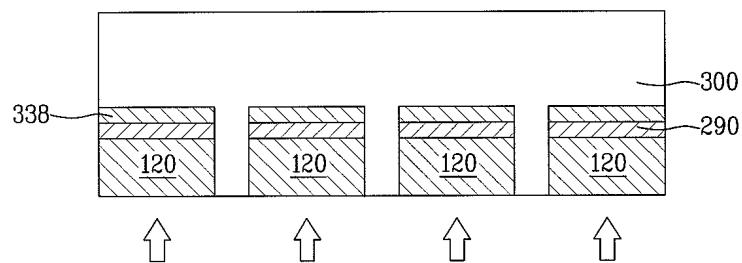

<46> 도 6 내지 15에서 설명된 프로세스 공정들은 임시지지 구조물(200)을 사용하는 일반적 제조 프로세스를 제공한다. 이제 도 16을 참조하면, 또다른 방법은 도 4의 구조물의 상부에 형성되는 금속 지지 후막(300)을 사용한다.

<47> 먼저, 투명 금속층(290)이 수직 토플로지 GaN 기반 LED 층 구조물(120) 상에 형성된다. 그 다음, Cr 및 Au 층으로 구성되는 부착층(338)이 투명 금속층(290) 위에 위치된다. 그 다음, 유익하게는 Cu, Au 또는 Al로 구성되는 금속지지 후막(300)이 부착층(338) 위에 형성된다. 금속지지 후막(300)은 물리 기상 증착법, 전기도금법, 전해/무전해 도금법, 또는 다른 적절한 수단에 의해 형성될 수 있다. 상기 금속지지 후막(300)은 바람직하게는 100마이크론 두께 미만이다. Cu, Au, 또는 Al 금속지지 후막(300)이 유익하지만, 거의 모든 임의의 전기 도전성, 및 유익하게는 열전도성 물질이면 사용가능하다.

<48> 이제 도 17을 참조하면, 도 16에 도시된 구조물은 2개의 진공 척(chuck)에 부착된다. 제 1 진공 척(210)은 금속 지지 후막(300)에 부착되고, 제 2 진공 척(212)은 사파이어 기판(122)에 부착된다. 그 후, 계속 도 17을 참조하면, 레이저 빔(214)이 사파이어 기판(122)을 통해 조사된다. 레이저 빔(214)은 유익하게는 3mm x 50mm 직사각형 빔과 200~600mJ/cm<sup>2</sup>의 빔 에너지를 갖는 248nm의 KrF 레이저이다. 248nm KrF 레이저 빔에 대해 투명한 물질, 바람직하게는 사파이어로 만들어진 진공 척들(210, 212)은 금속지지 후막(300)으로 지지되는 GaN-LED 디바이스들로부터 사파이어 기판(122)이 떨어지도록 바이어스 힘을 가한다. 레이저 조사 및 바이어스의 조합으로 인해, 도 18에 도시된 바와 같이 사파이어 기판(122)이 분리된다.

<49> 유사한 레이저 리프트 오프 프로세스가, 2000년 6월 6일에 등록되어 정 등(Cheung et al.)에게 허여되고 발명이 명칭이 "선택적 광학 프로세싱에 의한 투명 기판으로부터의 박막의 분리"인 미국특허 제6,071,795호와, 1997년

의 *Physica status Solidi(a)* 159권의 R3 내지 R4 페이지의 켈리 등(Kelly et al.)에 의한 "그룹 III 질화물 막을 리프트 오프하기 위한 광학 프로세스"에 서술되어 있다. 유익하게는, 임시지지 웨이퍼(200)는 수직 토플로지 GaN 기반 LED 층 구조(120) 내에서 개별 LED 반도체 구조물을 충분히 지지한다.

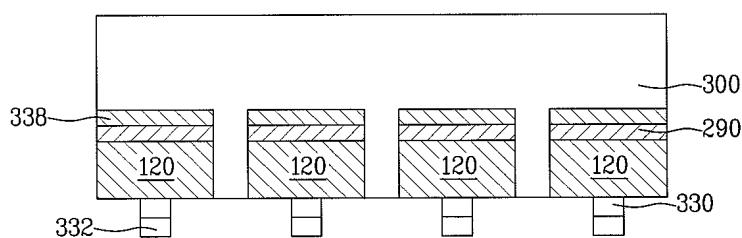

<50> 이제 도 19를 참조하면, 사파이어 기판(122)이 제거된 후, 그 결과로 생기는 구조물의 바닥(금속 후막(240)에 대향하는 면)이 먼저 HCl로 청소되어, Ga 물방울을 제거한다(레이저 빔(214)은 GaN을 Ga + N으로 분리시키는 가열이 일어나도록 한다). 청소 후에, ICP RIE 예칭(전술 내용 참조) 및 연마가 행해진다. 상기 예칭 및 연마는 순수 n-GaN의 원자 수준의 평편한 표면을 노출시키고 생성한다. n 타입 접촉부의 형성에 앞서, 예칭된 n-GaN 표면은 더욱 청소되고, 왕수(aqua regia) 용액( $H_2SO_4$  및 HCl의 혼합물)으로 예칭되어 n-GaN 및 Ti/Al 금속 층들 간의 부착을 향상시킨다.

<51> 도 20을 참조하면, 예칭 및 연마가 원자 수준으로 평편한 표면을 생성한 다음에(도 19 참조), 전기 접촉부는 개별 수직 토플로지 GaN 기반 LED 층 구조물(120) 상에 형성된다. 상기 전기 접촉부들은 수직 토플로지 GaN 기반 LED 층 구조물들(120)에 대한 Ti/Al 인터페이스 층(330), 및 상기 Ti/Al 인터페이스 층(330) 상의 Cr/Au 접촉 패드(332)를 포함한다.

<52> 임시지지 웨이퍼(200)를 제거하여 도 15에 도시된 구조물을 남긴 다음에, 또는 Cr/Au 접촉층(332)을 형성하여 도 20에 도시된 구조물을 남긴 다음에, 개별 LED 디바이스들은 분리될 준비가 된다. 분리하는 것은 예컨대, 화학/전기화학 예칭에 의해 또는 기계적 작업에 의해 여러 방식으로 달성될 수 있다. 기본적 분리 작업들은 동일 하므로, 도 20의 구조물을 분리하는 것은 유사하다는 것을 고려하여, 도 15에 도시된 구조물을 특히 참조하여 분리하는 것을 설명하겠다. 이제 도 21을 참조하면, 분리하는 것은 유익하게는 후막 지지부(240) 상에 포토 레지스트 패턴(250)을 도포함으로써 달성된다. 그 다음, 상기 포토-레지스트 패턴(250)은 현상되어 트렌치(124)와 일렬로 되는 후막 지지부(240)의 영역을 노출시킨다. 그 다음, 개구(254)는 후막 지지부(240)를 통해 예칭된다. 그 다음, 포토 레지스트 패턴(250)은 제거된다.

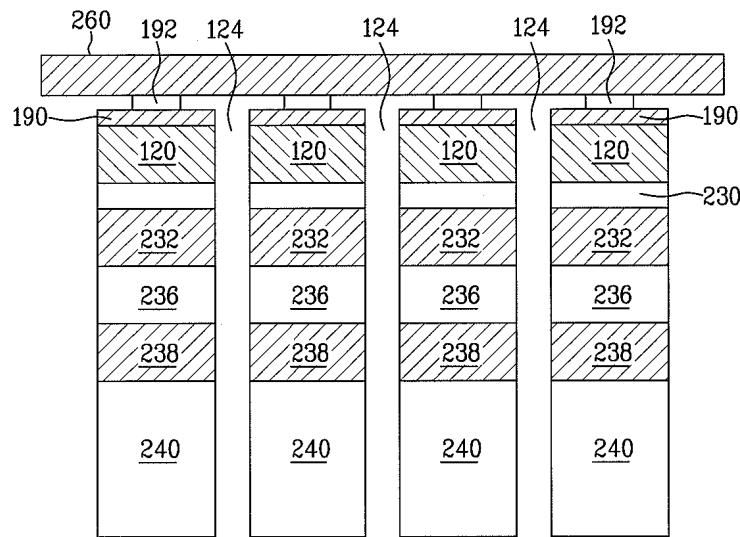

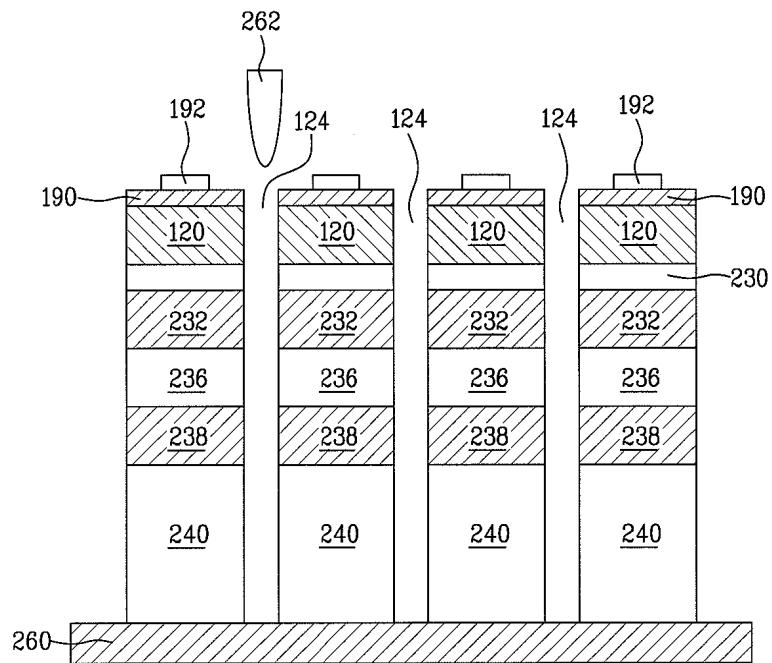

<53> 개별 디바이스들의 실제 분리는 여러 방식으로 달성될 수 있다. 예컨대, 도 22에서 도시된 바와 같이, 마운팅 테이프(260)가 도 21의 구조물 상부에 위치될 수 있다. 그 다음, 롤러가 마운팅 테이프 위에서 롤링을 하여 남아있는 온전한 층들에 스트레스를 가하여, 개별 디바이스들이 분리되도록 할 수 있다. 선택적으로, 도 23에 도시된 바와 같이, 마운팅 테이프(260)가 도 21의 구조물의 바닥에 위치될 수 있다. 그 다음, 다이아몬드-컷팅 휠(262)로 개별 디바이스들을 분리시킬 수 있다.

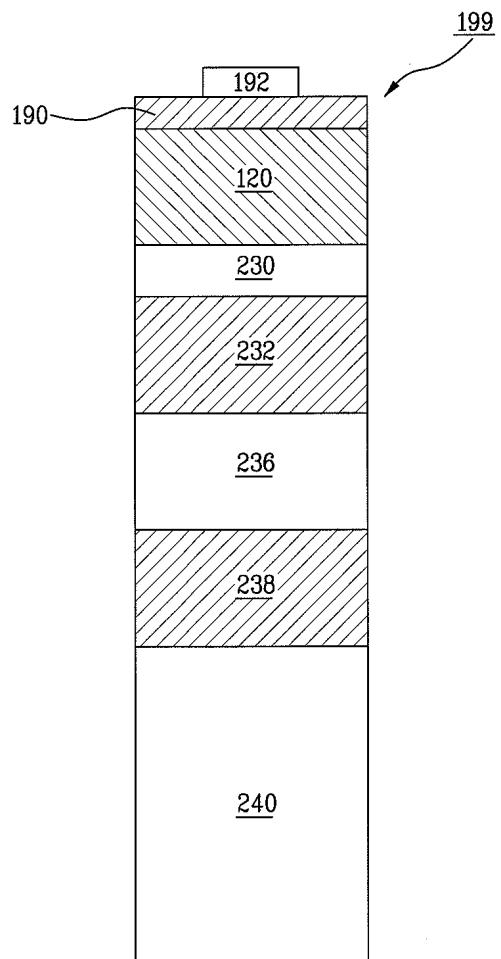

<54> 그 결과로, 도전성 기판 상에 복수의 수직 토플로지 GaN LED가 생긴다. 도 24에 도시된 바와 같이, 각 LED는 후막 지지부(240), 부착 지지부(Cr 부착층(236) 및 Au 부착층(238)), 반사성 구조물(티타늄 층(230) 및 알루미늄 층(232)), 반도체 층들(120), 및 상부 접촉부들(투명 접촉부(190) 및 금속 접촉 패드(192))을 포함한다. 이들 반도체 층은 도 2A에 도시된 바와 같은 반도체 층들을 포함한다.

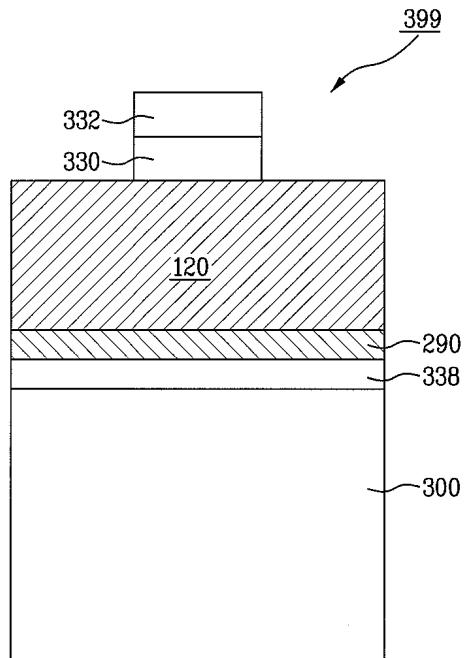

<55> 선택적으로, 금속 지지 후막(300)이 사용되면, 그 결과로 도 25에 도시된 LED(399)가 생긴다. 상기 LED는 금속 지지 후막(300), 부착층(338), 반사성 및 p 타입 투명 접촉부(290), 반도체 층들(120), n 타입 상부 인터페이스 층(330), 및 접촉 패드(332)를 포함한다. 이들 반도체 층은 도 2A에 도시된 바와 같은 반도체 층들을 포함한다.

<56> 본 명세서에서 설명된 실시예들 및 예시들은 본 발명과 그 실제 응용을 가장 잘 설명하여 본 기술분야의 당업자가 본 발명을 이용할 수 있도록 제공된 것이다. 그러나, 본 기술분야의 당업자는 전술한 설명 및 실시예들이 단지 설명 및 예시의 목적으로 주어졌음을 알 것이다. 본 발명의 다른 변형 및 수정이 본 기술분야의 당업자에게 분명할 것이며, 상기 변형 및 수정은 첨부된 청구의 범위에 속하는 것으로 의도된다. 전술한 설명은 본 발명의 범위를 제한하는 것으로 의도되지 않는다. 많은 변형 및 수정이 다음의 청구의 범위의 사상 및 범주를 벗어남 없이 전술한 설명으로부터 가능할 것이다. 본 발명을 이용할 때 다른 특성을 갖는 구성요소들도 포함될 수 있는 것으로 고려된다. 본 발명의 범위는 첨부된 청구의 범위에 의해 정의되며, 모든 면에서의 균등률도 포함하는 것으로 의도된다.

### 도면의 간단한 설명

<22> 도면들에 걸쳐 동일하거나 기능적으로 유사한 요소들을 동일유사한 도면부호로 인용하고 있고, 명세서에 포함되어 그 일부를 형성하는 첨부도면들은, 본 발명의 상세한 설명과 함께 본 발명을 또한 예시하며, 본 발명의 원리를 설명하는 역할을 한다.

<23> 도 1a는 일반적인 측방향 토플로지 GaN 기반 LED의 단면을 도시한다.

- <24> 도 1b는 도 1a에서 도시된 GaN 기반 LED의 평면도를 도시한다.

- <25> 도 2a는 일반적인 수직 토플로지 GaN 기반 LED의 단면을 도시한다.

- <26> 도 2b는 도 2a에서 도시된 GaN 기반 LED의 평면도를 도시한다.

- <27> 도 3 내지 도 25는 본 발명의 원리에 따른 발광 다이오드들을 형성하는 공정들을 도시한다.

## 도면

### 도면1a

### 도면1b

### 도면2a

도면2b

도면3

도면4

도면5

도면6

도면7

도면8

도면9

도면10

도면11

도면12

도면13

도면14

도면15

도면16

도면17

도면18

도면19

도면20

도면21

도면22

도면23

도면24

도면25