(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第6315892号

(P6315892)

(45) 発行日 平成30年4月25日(2018.4.25)

(24) 登録日 平成30年4月6日(2018.4.6)

(51) Int.Cl.

F 1

G02F 1/1368 (2006.01)

G02F 1/1368

G02F 1/1335 (2006.01)

G02F 1/1335

請求項の数 9 (全 15 頁)

(21) 出願番号

特願2013-102687 (P2013-102687)

(22) 出願日

平成25年5月15日 (2013.5.15)

(65) 公開番号

特開2014-224840 (P2014-224840A)

(43) 公開日

平成26年12月4日 (2014.12.4)

審査請求日

平成28年5月11日 (2016.5.11)

(73) 特許権者 000006013

三菱電機株式会社

東京都千代田区丸の内二丁目7番3号

(74) 代理人 100088672

弁理士 吉竹 英俊

(74) 代理人 100088845

弁理士 有田 貴弘

(72) 発明者 武田 和浩

東京都千代田区丸の内二丁目7番3号 三菱電機株式会社内

(72) 発明者 三宅 史郎

東京都千代田区丸の内二丁目7番3号 三菱電機株式会社内

最終頁に続く

(54) 【発明の名称】 液晶表示パネル

## (57) 【特許請求の範囲】

## 【請求項 1】

各画素の TFT (Thin Film Transistor) が配設された TFT アレイ基板と、前記 TFT アレイ基板に対向配置され、外側の面にシールド導電層を有する対向基板と、

前記 TFT アレイ基板と前記対向基板との間に挟持された液晶層と、を備える横電界方式の液晶表示パネルであつて、

前記 TFT アレイ基板は、

前記 TFT のゲート電極に接続したゲート配線と、

前記ゲート配線を表示領域より外側の額縁領域へ引き出すゲート引き出し配線と、

前記ゲート引き出し配線が配置されない辺を含む全ての辺の前記額縁領域において、前記 TFT アレイ基板における前記ゲート引き出し配線を覆うように形成された絶縁膜の表面を覆って配置されるとともに、前記液晶層と前記絶縁膜の表面との境界面に配置された導電層と、を備え、

前記液晶表示パネルは、

前記額縁領域において前記 TFT アレイ基板と前記対向基板の間に形成され、前記液晶層を封止するシール材をさらに備え、

前記導電層は、前記シール材と表示領域との間に形成されており、

前記シールド導電層は、特定の電位に固定されないフローティング状態であることを特徴とする液晶表示パネル。

10

20

**【請求項 2】**

前記導電層には、各画素の共通電極の電位である共通電位が供給される

請求項 1記載の液晶表示パネル。

**【請求項 3】**

前記導電層は、各画素の画素電極または共通電極と同じ透明導電膜により形成されている

請求項 1または請求項 2記載の液晶表示パネル。

**【請求項 4】**

前記導電層は、金属膜により形成されている

請求項 1または請求項 2記載の液晶表示パネル。

10

**【請求項 5】**

前記対向基板は、前記液晶層側の面に、黒色粒子を分散させた樹脂により形成されたブラックマトリクスをさらに備える

請求項 1から請求項 4のいずれか一項記載の液晶表示パネル。

**【請求項 6】**

前記シールド導電層は、視差バリアを構成する遮光性導電膜である

請求項 1記載の液晶表示パネル。

**【請求項 7】**

前記シールド導電層は、前記対向基板の前面側に配置されるタッチパネルと前記対向基板との間にノイズシールドとして設けられた透明導電膜である

20

請求項 1記載の液晶表示パネル。

**【請求項 8】**

前記導電層の外側端部は、前記シール材に接触するように前記シール材と重複しており

、前記シール材の表面の抵抗値は、前記液晶層の抵抗値よりも小さい

請求項 1から請求項 7のいずれか一項記載の液晶表示パネル。

**【請求項 9】**

前記導電層の外側端部は、前記シール材に接触するように前記シール材と重複しており

、前記シール材は、導電性材料により構成されている

30

請求項 1から請求項 7のいずれか一項記載の液晶表示パネル。

**【発明の詳細な説明】****【技術分野】****【0001】**

本発明は、液晶表示装置、特に、横電界方式の液晶表示装置の表示品位と信頼性の向上に関するものである。

**【背景技術】****【0002】**

従来、液晶表示装置における液晶の駆動方式としては、TN (Twisted Nematic) モードが広く用いられてきた。しかし近年では、TNモードの液晶表示装置に代わり、画素電極と共に共通電極(対向電極)との間に電圧を印加すると表示パネルの表面に対してほぼ水平方向(横方向)の電界が発生し、その横方向の電界で液晶分子を駆動する横電界方式の液晶表示装置が普及してきている。横電界方式の液晶表示装置は、視野角が広く、何れの視野範囲でも高い表示品位を得ることができる。

40

**【0003】**

横電界方式としては、In-Plane SwitchingモードとFFS(Fringe Field Switching)モードがよく知られている。特にFFSモードは、液晶を駆動する画素電極および共通電極が透明導電膜で形成され、画素電極と共に共通電極の上のほぼ全ての領域の液晶を駆動して表示に寄与させることができることから、In-Plane Switchingモードよりも光の利用効率が高い。よって、FFSモードでは、TNモードと同等以上の高輝度化あるいは低消費電

50

力化を、広視野角や高精細化と両立できる。さらに、FFSモードは、In-Plane Switchingモードよりも電極構造が単純であり、構造的にも高精細化に有利である。

#### 【0004】

今後有望な製品分野であるスマートフォンやタブレット端末などに使用される中小型パネルは、高精細化と高輝度化あるいは低消費電力化の要求が高い。よって、それらを実現できるFFSモードの液晶表示装置は、当該製品分野の主流になりつつある。

#### 【0005】

一般に、液晶表示装置を構成する液晶表示パネル（以下「液晶パネル」）は、TFT（Thin Film Transistor）や画素電極などが形成されたTFTアレイ基板と、カラーフィルタやブラックマトリクス（BM）などが形成された対向基板との間に液晶層が挟持された構造となる。横電界方式の液晶パネルでは、画素電極と対向電極が共にTFTアレイ基板側に配設されるため、基本的に対向基板側には電極を設ける必要がない。そのため、横電界方式の液晶パネルでは、対向基板の内側（液晶層側）には導電膜が形成されない。従って、対向基板の電位が不安定になりやすく、また、外部からの電磁ノイズが液晶層に侵入して画質に影響を与えることが懸念される。

10

#### 【0006】

この問題を解決するために、横電界方式の液晶表示装置では、対向基板の外側にITO（Indium Tin Oxide）などの透明導電膜よりなるシールド導電層が設けられていた。通常、対向電極に設けられるシールド導電層は、電位を安定させるために接地（アース接続）される。シールド導電層の接地の方法としては、接地された導電性の金属筐体や端子電極を銀ペーストや金属テープを介してシールド導電層に接続させる方法や、接地された金属筐体の一部をシールド導電層に接するバネ構造とする方法などがある。

20

#### 【0007】

対向基板の外側にシールド導電層を設けることで液晶パネルの外部からの電磁ノイズ等をシールドでき、さらに、シールド導電層を接地することで対向基板の外側表面を接地電位に安定させることができる。しかし、液晶パネル内部で発生する帯電への対策は困難である。特に、比較的高い電位のゲート信号が印加されるゲート引き出し配線が配設された画面周辺の部分では、ゲート信号の影響を受けやすく、液晶パネルの内部に帯電を生ずる。その結果、画面周辺にコントラストが劣化する「白抜け」が生じる。この白抜けは、液晶パネルの内側表面の各箇所における導電性の大小に応じて、場所ごとに発生の程度が異なり、例えば、対向基板が備えるカラーフィルタの色材間に導電性の差がある場合には、特定色の光漏れとして現れる場合もある。

30

#### 【0008】

特許文献1では、横電界方式の液晶表示装置において、TFTアレイ基板のゲート引き出し配線上に、絶縁膜を介してシールド導電層を配設することで、ゲート引き出し配線に印加されたゲート信号の影響による白抜けの改善を図る技術が提案されている。特許文献1のシールド導電層は、液晶パネルの外周部で液晶を封止しているシール材の下にまで延在して、ゲート引き出し配線の上を覆う構造となっている。

#### 【先行技術文献】

#### 【特許文献】

40

#### 【0009】

#### 【特許文献1】特開2010-049185号公報

#### 【発明の概要】

#### 【発明が解決しようとする課題】

#### 【0010】

先に述べたように、横電界方式の液晶表示装置の対向基板には、その外側に接地されたシールド導電層が設けられ、外部からの電磁ノイズ等による帯電を防止している。しかし、シールド導電層の接地構造が何らかの理由（例えば断線など）により機能しなくなった場合には、シールド導電層に電荷が蓄積される。その場合、電荷が蓄積されたシールド導電層と液晶パネル内部の各導電体とで形成される容量の大小に応じた不均一な電界が液晶

50

層に印加されて、白抜けなどに起因する表示ムラが現れる。

【0011】

特に対向基板においては、抵抗値の低いブラックマトリクスの部分に多くの電荷が誘起される。ブラックマトリクスは、表示領域では部分的に形成されるが、表示領域外側の額縁領域では全体的に形成されるので、表示領域における額縁領域に近接する部分、すなわち表示領域の外周部で、局所的に異なる電界が液晶に印加されることになり、表示ムラを引き起こす。

【0012】

一方、特許文献1のTFTアレイ基板上に設けられるシールド導電層は、ゲート引き出し配線からの電界をシールドすることのみが意図されており、矩形の液晶パネルの4辺のうちゲート引き出し配線が配設された辺にのみ設けられている。そのため、シールド導電層が設けられている辺と設けられていない辺とで、ブラックマトリクスに誘起された電荷が生じさせる電界が異なることになる。その結果、表示領域外周部の特にシールド導電層が設けられていない辺において、局所的に異なる電界が液晶に印加され、その部分に表示ムラが生じる。

【0013】

つまり、特許文献1の液晶表示装置であっても、シールド導電層の接地構造が機能しなくなった状況では、液晶パネルの内部で発生する帯電に起因する表示ムラを充分に抑えることはできない。

【0014】

また、白抜けは、液晶パネルの内側表面の各箇所における導電性の大小に応じて発生の程度が異なるため、TFTアレイ基板側に設けるシールド導電層は、TFTアレイ基板の最表面に配設すると効果的である。その点、特許文献1のシールド導電層は、絶縁膜の下に設けられる共通電極と同じ層で形成されるため、TFTアレイ基板の最表面ではなく絶縁膜の下に設けられている。

【0015】

さらに、対向基板外側に設けられるシールド導電層の接地構造は、銀ペーストや金属テープの形成プロセスが必要になることによる製造プロセスの複雑化およびそれに伴うコスト増加、部品点数増加による信頼性の低下、あるいは、金属筐体の一部をバネ構造とすることによる金属筐体の設計自由度の低下を招く。

【0016】

このように、横電界方式の液晶表示装置では、信頼性、コスト面などの課題も含めて、液晶パネル内部で発生する帯電を起因とする表示ムラに対する十分な解決手段は提案されてなかった。

【0017】

本発明は以上のような課題を解決するためになされたものであり、表示領域の外周部の表示ムラを効果的に抑制できる横電界方式の液晶表示装置を提供することを目的とする。

【課題を解決するための手段】

【0018】

本発明に係る液晶表示パネルは、各画素のTFT (Thin Film Transistor) が配設されたTFTアレイ基板と、前記TFTアレイ基板に対向配置され、外側の面にシールド導電層を有する対向基板と、前記TFTアレイ基板と前記対向基板との間に挟持された液晶層と、を備える横電界方式の液晶表示パネルであって、前記TFTアレイ基板は、前記TFTのゲート電極に接続したゲート配線と、前記ゲート配線を表示領域より外側の額縁領域へ引き出すゲート引き出し配線と、前記ゲート引き出し配線が配置されない辺を含む全ての辺の前記額縁領域において、前記TFTアレイ基板における前記ゲート引き出し配線を覆うように形成された絶縁膜の表面を覆って配置されるとともに、前記液晶層と前記絶縁膜の表面との境界面に配置された導電層と、を備え、前記液晶表示パネルは、前記額縁領域において前記TFTアレイ基板と前記対向基板の間に形成され、前記液晶層を封止するシール材をさらに備え、前記導電層は、前記シール材と表示領域との間に形成されており

10

20

30

40

50

、前記シールド導電層は、特定の電位に固定されないフローティング状態であることを特徴とする。

### 【発明の効果】

#### 【0019】

本発明に係る液晶表示装置によれば、ゲート引き出し配線が配設されていない辺も含めて全ての辺の額縁領域の最表面に導電層を備えるため、表示ムラが生じ易い表示領域端部で局所的に異なる電界が発生することが抑制され、表示ムラを効果的に抑制できる。よって、例えばシールド導電層の接地構造が機能しなくなつた場合や、その接地構造を省略した場合にも、表示ムラの発生を抑えることができる。また、接地構造の不具合による表示不良が防止されることによる信頼性向上、あるいは、接地構造を省略することによる製造プロセス簡略化および低コスト化を図ることができる。

#### 【0020】

さらに、液晶層を封止するシール材表面の抵抗値が液晶の抵抗値よりも小さい場合、対向基板表面の電荷が、シール材の近傍で基板表面およびシール材表面を通して導電層へ流れる。それにより、対向基板表面と TFT アレイ基板表面の電位差、つまり液晶に印加される縦方向（表示パネルの表面に対して垂直方向）の電界が緩和され、このことも表示ムラの抑制に寄与する。

#### 【図面の簡単な説明】

#### 【0021】

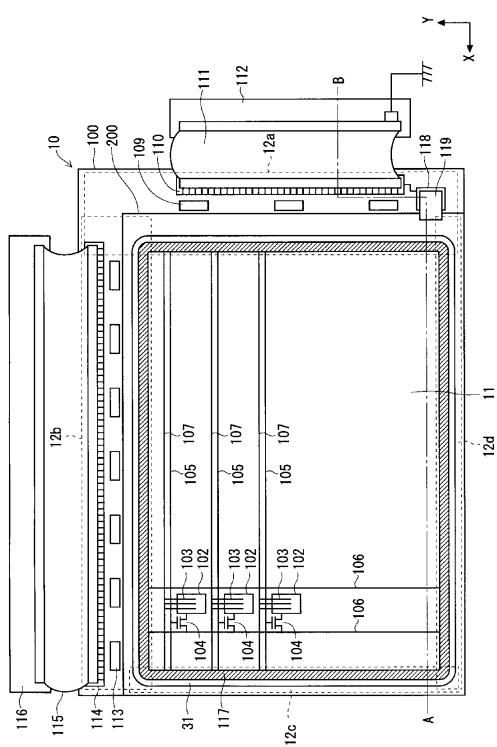

【図1】実施の形態1に係る液晶パネルの構成を示す平面図である。

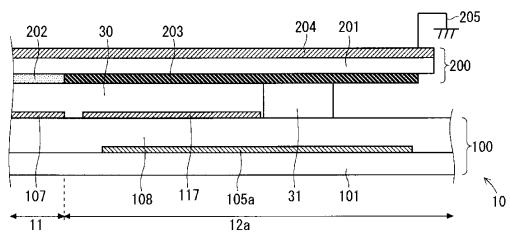

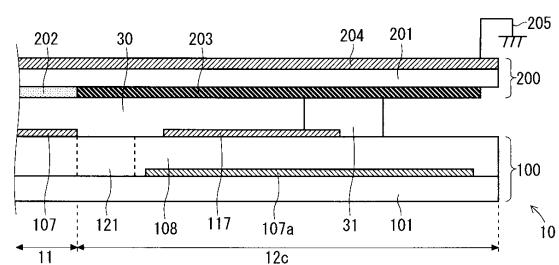

【図2】実施の形態1に係る液晶パネルの構成を示す断面図である。

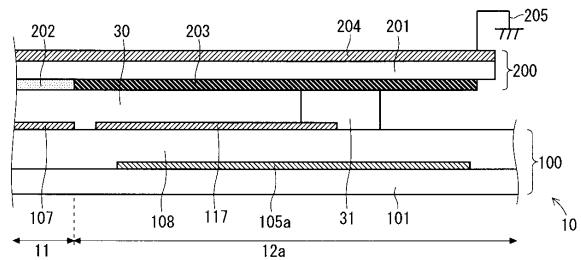

【図3】実施の形態1に係る液晶パネルにおける額縁領域近傍の断面図である。

【図4】実施の形態1に係る液晶パネルにおける額縁領域近傍の断面図である。

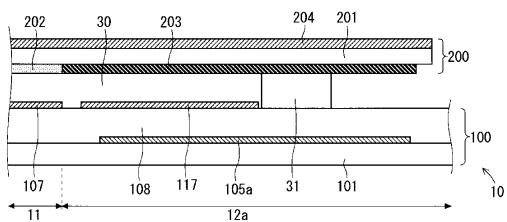

【図5】実施の形態2に係る液晶パネルにおける額縁領域近傍の断面図である。

【図6】実施の形態2に係る液晶パネルにおける額縁領域近傍の断面図である。

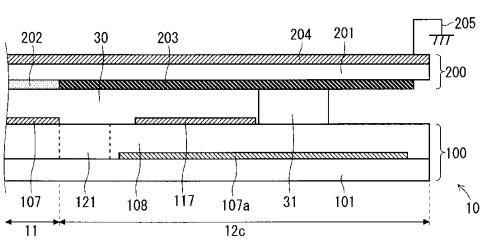

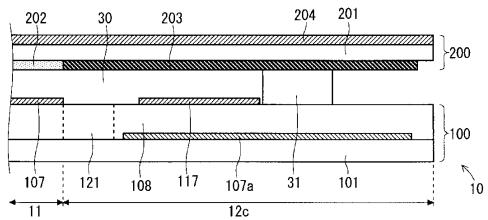

【図7】実施の形態4に係る液晶パネルにおける額縁領域近傍の断面図である。

【図8】実施の形態4に係る液晶パネルにおける額縁領域近傍の断面図である。

#### 【発明を実施するための形態】

#### 【0022】

##### <実施の形態1>

図1および図2は、本発明の実施の形態1に係る液晶表示装置を構成する液晶パネルの概略図である。図1は、液晶パネルの全体構成を示した平面図であり、図2は、図1におけるA-B線に沿った断面図である。本実施の形態では、各画素のスイッチング素子としてTFTを用いた横電界方式の液晶パネル、特にFFS方式の液晶パネルに本発明を適用した例を説明する。

#### 【0023】

液晶パネル10は、各画素のTFT104が配設されたTFTアレイ基板100と、TFTアレイ基板100に対向配置されたカラーフィルタ基板である対向基板200との間に液晶層30が挟持されて成る構造を有している。TFTアレイ基板100と対向基板200は、複数の画素が配置される表示領域11を囲うように設けられたシール材31を介して接着され、液晶層30はシール材31によって封止されている。すなわち、シール材31は、表示領域11よりも外側の額縁領域12（12a～12d）に設けられる。また、図示は省略するが、TFTアレイ基板100と対向基板200との間には、その間隔を一定に保持するための柱状スペーサが、表示領域11に多数配置される。

#### 【0024】

ここで、額縁領域12は、矩形の表示領域11を取り囲むフレーム状の領域であるが、以下の説明では、図1に示すように、液晶パネル10の右側の辺の部分を「額縁領域12a」、上側の辺の部分を「額縁領域12b」、左側の辺の部分を「額縁領域12c」、下

10

20

30

40

50

側の辺の部分を「額縁領域 12d」と称する。また、表示領域 11 および額縁領域 12 は、液晶パネル 10 上だけでなく、TFT アレイ基板 100 上、対向基板 200 上、あるいは TFT アレイ基板 100 と対向基板 200 との間の空間（液晶層 30 を含む）においても規定されるものとする。

【0025】

図 2 に示すように、対向基板 200 は、第 1 の透明基板であるガラス基板 201 を用いて形成されている。ガラス基板 201 の内側の面（液晶層 30 側の面）には、表示領域 11 に各色のカラーフィルタ 202 が配設され、カラーフィルタ 202 間および額縁領域 12 には、遮光層であるブラックマトリクス（BM）203 が配設される。

【0026】

図示は省略するが、対向基板 200 の液晶層 30 側の面には、表示領域 11 に、カラーフィルタ 202 およびブラックマトリクス 203 を覆うように、液晶層 30 の液晶を配向させるための配向膜が設けられる。また、横電界方式の液晶表示装置で必要な基板間隔（TFT アレイ基板 100 と対向基板 200 との間隔）の均一性を確保するために、カラーフィルタ 202 およびブラックマトリクス 203 と配向膜の間に、対向基板 200 の表面を平坦化する透明樹脂膜（オーバーコート層）を設けてもよい。

【0027】

カラーフィルタ 202 としては、例えば樹脂中に顔料などを分散させた色材層を用いることができる。カラーフィルタ 202 は、赤、緑、青などの特定の波長範囲の光を選択的に透過するフィルタとして機能し、各色の色材層が規則的に配列される。

【0028】

ブラックマトリクス 203 としては、例えば、酸化クロムなどを用いた金属系の材料や、樹脂中に黒色粒子を分散させた樹脂系の材料を用いることができる。実施の形態 1 では、横電界方式の液晶表示装置で焼き付き特性において優れることから汎用される後者の樹脂系の材料で構成した、いわゆる樹脂 BM を採用した。樹脂 BM は、樹脂中に分散される黒色粒子が、炭素やチタンなどの導電性材料であることから、金属系の材料ほど低抵抗ではないが、ある程度の導電性を有している。

【0029】

また、対向基板 200 は、ガラス基板 201 の外側の面（液晶層 30 とは反対側の面）に、透明導電膜からなるシールド導電層 204 を備えている。シールド導電層 204 は、ガラス基板 201 の少なくとも表示領域 11 を覆うように設けられ、所定の接地構造を通して接地される（シールド導電層 204 の接地構造については後述する）。シールド導電層 204 は、横電界方式の液晶パネル 10 において静電気による帯電や外部電界の影響による表示不良を防止するのに有効な手段である。

【0030】

一方、TFT アレイ基板 100 は、第 2 の透明基板であるガラス基板 101 を用いて形成されている。ガラス基板 101 の内側の面（液晶層 30 側の面）の表示領域 11 には、画素電極 102、共通電極 103、TFT 104、ゲート配線 105、ソース配線 106、共通配線 107 および絶縁膜 108 などが形成される。

【0031】

画素電極 102 および共通電極 103 は、透明導電膜で形成されており、画像信号に応じた電圧が印加されると、液晶層 30 の液晶を駆動するための横方向（TFT アレイ基板 100 の表面に平行な方向）の電界を発生する。TFT 104 は、画像信号に応じた電圧を、そのソース電極に接続された画素電極 102 に印加するスイッチング素子である。ゲート配線 105 は、TFT 104 のゲート電極に駆動信号（ゲート信号）を供給するためのものであり、ソース配線 106 は TFT 104 のソース電極に画像信号を供給するためのものである。共通配線 107 は、共通電極 103 に所定の共通電位を供給するためのものである。画素電極 102、TFT 104、ゲート配線 105 およびソース配線 106 は絶縁膜 108 に覆われる（図示の便宜上、画素電極 102 と共通電極 103 の間の層間絶縁膜も絶縁膜 108 に含めている）。共通電極 103 は、絶縁膜 108 の上すなわち TFT

10

20

30

40

50

Tアレイ基板100の最表面に形成される。

【0032】

本実施の形態では、共通配線107は、表示領域11内では共通電極103と接続するよう共通電極103と同層(TFTアレイ基板100の最上層)に形成され、額縁領域12ではゲート配線105と同層(絶縁膜108の下)に形成されるものとする。ただし、表示領域11内でも共通配線107を絶縁膜108の下に形成し、絶縁膜108上の共通電極103がコンタクトホールを通して共通配線107に接続するように構成してもよい。

【0033】

絶縁膜108は、単層の透明絶縁膜、あるいは複数の透明絶縁膜からなる積層膜により構成される。また、図示は省略するが、TFTアレイ基板100の液晶層30側の面には、表示領域11に、液晶層30の液晶を配向させるための配向膜が設けられる。

【0034】

画素電極102および共通電極103の構成に関して、実施の形態1では、平板状の画素電極102の上方に、スリットを有する櫛歯状あるいは格子状の共通電極103を対向配置させている。ただし、それらの形状と上下関係を逆にして、平板状の共通電極103の上方に、櫛歯状あるいは格子状の画素電極102を対向配置させてもよい。画素電極102および共通電極103の具体的なパターン形状は、公知のFFS方式の液晶パネルに用いられるものと同様でよい。

【0035】

TFTアレイ基板100の表示領域11には、図1に示すように、複数のゲート配線105がそれぞれ平行に延在し、複数のソース配線106もそれぞれ平行に延在する。複数のゲート配線105と複数のソース配線106とは互いに交差するように配設されている。また、共通配線107は、ゲート配線105と平行にゲート配線105と同数配置されている。

【0036】

ゲート配線105とソース配線106とで囲まれる領域のそれが画素の領域となるため、複数の画素はアレイ状(マトリクス状)に配列されることになる。画素電極102、共通電極103およびTFT104は、各画素ごとに形成される。各画素の共通電極103は、共通配線107に接続しており、全て同じ電位(共通電位)に設定される。

【0037】

TFTアレイ基板100および対向基板200はそれぞれ矩形であり、TFTアレイ基板100の方が対向基板200よりも大きくなっている。そのため、TFTアレイ基板100と対向基板200を重ね合わせると、TFTアレイ基板100の額縁領域12の一部が対向基板200の端部から突出することになる。図1においては、右側の額縁領域12aの一部と、上側の額縁領域12bの一部が、対向基板200の端部から突出している。

【0038】

対向基板200の端部よりも突出した部分の額縁領域12aには、対向基板200に対向する側の面に、ゲート配線105を駆動する駆動IC(Integrated Circuit)チップ109(ゲート側駆動ICチップ)およびゲート側駆動ICチップ109に信号を入力するための信号端子110(ゲート側信号端子)が実装されている。ゲート側信号端子110は、複数の矩形のパッドが図1の上下方向(Y方向)に多数配列した構成となっている。ゲート側信号端子110には、接続配線であるFFC(Flexible Flat Cable)111(ゲート側FFC)を通して、ソース側駆動ICチップ113の動作を制御する制御基板112(ゲート側制御基板)が接続されている。

【0039】

ゲート側制御基板112は、ゲート側駆動ICチップ109を制御する制御信号を生成する制御ICチップなどを装備しており、当該制御信号をゲート側信号端子110に入力する。ゲート側信号端子110に入力された制御信号は、ゲート側駆動ICチップ109に入力される。ゲート側駆動ICチップ109は、その制御信号に基づいて、ゲート配線

10

20

30

40

50

105に接続されたTFT104の駆動信号(ゲート信号)を生成する。ゲート側駆動ICチップ109が生成したゲート信号は、表示領域11内のゲート配線105から額縁領域12aのゲート側駆動ICチップ109まで引き出された不図示の配線(ゲート引き出し配線)を通してゲート配線105に供給され、それに接続したTFT104のゲート電極に入力される。本実施の形態では、ゲート引き出し配線は、額縁領域12aに形成されているものとする。

【0040】

一方、対向基板200の端部よりも突出した部分の額縁領域12bには、対向基板200に対向する側の面に、ソース配線106に画像信号を供給する駆動ICチップ113(ソース側駆動ICチップ)およびソース側駆動ICチップ113に信号を入力するための信号端子114(ソース側信号端子)が実装されている。ソース側信号端子114は、複数の矩形のパッドが図1の左右方向(X方向)に多数配列した構成となっている。ソース側信号端子114には、FFC115(ソース側FFC)を通して、ソース側駆動ICチップ113の動作を制御する制御基板116(ソース側制御基板)が接続されている。

10

【0041】

ソース側制御基板116は、ソース側駆動ICチップ113を制御する制御信号および画像信号を生成する制御ICチップなどを装備しており、それらの信号をソース側信号端子114に入力する。ソース側信号端子114に入力された制御信号および画像信号は、ソース側駆動ICチップ113に入力される。ソース側駆動ICチップ113は、その制御信号に基づいたタイミングで、ソース配線106に画像信号を出力する。ソース側駆動ICチップ113が出力した画像信号は、表示領域11内のソース配線106から額縁領域12bのソース側駆動ICチップ113まで引き出された不図示の配線(ソース引き出し配線)を通してソース配線106に供給され、TFT104を通して各画素の画素電極102に供給される。本実施の形態では、ソース引き出し配線は、額縁領域12cに形成されているものとする。

20

【0042】

図1のように、実施の形態1の液晶パネル10の額縁領域12には、シール材31と表示領域11の間を埋めるように、表示領域11を囲む導電層117が配設されている。すなわち、導電層117は、ゲート引き出し配線が設けられた額縁領域12a、ソース引き出し配線が設けられた額縁領域12bだけでなく、ゲート引き出し配線やソース引き出し配線が設けられていない額縁領域12c, 12dも含めた全ての辺の額縁領域12に形成されている。

30

【0043】

導電層117は、図2のようにTFTアレイ基板100の最表面を覆うように形成される。実施の形態1では、導電層117を、表示領域11に設けられる共通電極103と同じ透明導電膜の層で形成している。それにより、導電層117のパターン形成を共通電極103のパターン形成と同時に行うことができ、導電層117を設けることによる製造工程の増加は生じない。

【0044】

なお、図2の画素電極102および共通電極103の形状と上下関係を逆にして、平板状の共通電極103の上方に、櫛歯状あるいは格子状の画素電極102を対向配置させる場合には、導電層117がTFTアレイ基板100の最上層となるように、導電層117を画素電極102と同じ透明導電膜の層で形成するとよい。

40

【0045】

導電層117には、特定の固定電位が供給されることが望ましい。実施の形態1では、共通配線107および共通電極103と同じ共通電位を導電層117に供給した。導電層117を共通電位に固定した場合、導電層117を表示領域11の周辺に配置しても、表示領域11に表示される画像に導電層117が悪影響を与えることが抑えられる。

【0046】

なお、このように導電層117に共通電位を供給する場合には、導電層117の一部を

50

、表示領域11内の共通配線107に共通電位を供給する経路（額縁領域12に形成される共通配線107）として利用してもよい。また、共通電位が供給される導電層117は、額縁領域12に形成される共通配線107がゲート配線105と交差して配置される場合における、共通配線107の迂回経路としても活用できる。さらに、共通電位が供給される導電層117を、額縁領域12に形成される共通配線107と併設し、導電層117を共通配線107のバイパスとして利用してもよく、それによって共通電位の供給経路を低抵抗化でき、液晶パネル10内の共通電位が安定化する作用が得られる。

#### 【0047】

また、本実施の形態1のように表示領域11に設けられる共通電極103がTFTアレイ基板100の最上層に形成される場合には、導電層117と同じ透明導電膜の層で形成し、さらに、この同じ透明導電膜によって両者が接続する構成、つまり、導電層117と共通電極103とが、少なくとも一部で繋がって一体化したパターンに形成される構成としてもよい。そのように構成すると、導電層117に共通電極103と同じ共通電位を比較的容易に供給することができる。

#### 【0048】

TFTアレイ基板100の外側の面には偏光板120が設けられる。また、対向基板200の外側の面には、シールド導電層204の上に、偏光板220が設けられる。偏光板220および偏光板120は、液晶パネル10の少なくとも表示領域11を覆っている。

#### 【0049】

対向基板200のシールド導電層204は接地される。シールド導電層204の接地構造は任意の構造でよいが、本実施の形態では、対向基板200の端部よりも突出した部分の額縁領域12aに接地電位が供給されるアースパッド118を設け、アースパッド118とシールド導電層204とを導電テープ119を用いて電気的に接続させている。シールド導電層204は、その大部分が偏光板220で覆われるが、一部を対向基板200から露出させている。導電テープ119の一端はシールド導電層204の露出部分に貼り付けられ、他端はアースパッド118に貼り付けられる。

#### 【0050】

アースパッド118は、ゲート側信号端子110およびゲート側FFC111を通して接地される。導電テープ119としては、Al箔やCu箔などの金属箔よりなる母材に導電粘着剤を塗布したものを使用することができ、一般的な市販品を利用できる。

#### 【0051】

実施の形態1に係る液晶パネル10の構成は以上のとおりである。図示は省略するが、液晶パネル10の背面側に、バックライトユニットおよびバックライトユニットが発した光を調整する光学シートが配置され、それらを表示領域11の前面側（視認側）が開口された筐体に収納することによって、液晶表示装置が構成される。

#### 【0052】

次に、実施の形態1に係る液晶パネル10およびそれを用いた液晶表示装置で得られる効果について説明する。図3および図4は、実施の形態1の液晶パネル10の額縁領域12近傍の断面図であり、図3は額縁領域12aの近傍、図4は額縁領域12cの近傍をそれぞれ示している。これらの図では、図1～図4に示したものと同様の要素には、同一符号を付してある。

#### 【0053】

図3のように、TFTアレイ基板100の額縁領域12aには、絶縁膜108下にゲート引き出し配線105aが配設されている。一方、図4のように、TFTアレイ基板100の額縁領域12cには、TFTアレイ基板100の製造途中で各配線の導通検査やTFT104の動作検査などを行うための検査回路部121が配設されており、その表面の一部には検査針を当てるための検査パッド（不図示）が設けられる。また、表示領域11内の共通配線107はTFTアレイ基板100の最上層に配設されるが、額縁領域12c内の共通配線107aは絶縁膜108の下に配設されている。

#### 【0054】

10

20

30

40

50

対向基板 200 上に形成されたシールド導電層 204 は、接地構造 205 ( 図 2 のアースパッド 118 および導電テープ 119 など ) を通して接地されている。

【 0055 】

額縁領域 12b, 12d の断面の図示は省略するが、実施の形態 1 の液晶パネル 10 では、額縁領域 12a ~ 12d の全てにおいて、表示領域 11 とシール材 31 の間に、 TFT アレイ基板 100 の最表面を覆う導電層 117 が形成されている。すなわち、導電層 117 は、ゲート引き出し配線 105a が設けられる額縁領域 12a のみならず、共通配線 107a が設けられる額縁領域 12c、さらには、ソース引き出し配線が設けられる額縁領域 12b、額縁領域 12c と同様に共通配線 107a が設けられる額縁領域 12d においても、TFT アレイ基板 100 の最表面を覆うように形成される。

10

【 0056 】

なお、額縁領域 12c の検査回路部 121 は、比較的狭い領域であるため表示ムラへの影響が小さく、また、検査回路部 121 上に設けられる検査パッドと干渉することから、図 3 の例では検査回路部 121 上に導電層 117 を形成していない。しかし、検査パッドを除く範囲であれば、検査回路部 121 上にも導電層 117 を配設してもよい。

【 0057 】

実施の形態 1 によれば、FFS 方式などの横電界方式の液晶表示装置において、ゲート引き出し配線 105a が配置されない辺も含む全ての辺の額縁領域 12 ( 12a ~ 12d ) に、TFT アレイ基板 100 の最表面を覆う導電層 117 を配設している。従って、仮に対向基板 200 上に形成されたシールド導電層 204 の接地構造 205 が機能しなくなったとしても、表示ムラが生じ易い表示領域 11 の端部に局所的に異なる電界が生じることが抑えられ、表示ムラの発生を抑制できる。

20

【 0058 】

表示ムラの問題に関して、対向基板 200 におけるブラックマトリクス 203 の抵抗値が低いと、ブラックマトリクス 203 が全体的に形成される額縁領域 12 に多くの電荷が誘起され易く、さらに、金属系の材料に比べて抵抗値の高い樹脂系の材料でブラックマトリクス 203 を形成した場合には、その誘起された電荷の分布が均一化され難いので、表示領域 11 の外周部に局所的な表示ムラが発生しやすい。従って、導電層 117 により得られる表示ムラの抑制効果は、特に比較的抵抗値の高い樹脂系の材料からなるブラックマトリクス 203 を有する液晶パネル 10 において、より顕著に得られることになる。

30

【 0059 】

また、シール材 31 表面の抵抗値が、液晶層 30 の液晶の抵抗値よりも小さい場合、シール材 31 の近傍で、対向基板 200 の表面に帯電した電荷がシール材 31 の表面を通して導電層 117 へ流れる。よって、対向基板 200 の表面と TFT アレイ基板 100 の表面との電位差、つまり液晶層 30 に縦方向に印加される電界が緩和され、それによっても表示領域 11 の端部に表示ムラが発生することを抑制できる。

【 0060 】

このように、実施の形態 1 の液晶パネル 10 によれば、シールド導電層 204 の接地構造 205 が機能しなくなった場合でも、表示ムラによる表示不良の発生が抑えられるので、液晶表示装置の信頼性の向上に寄与できる。

40

【 0061 】

実施の形態 1 では、液晶パネル 10 の 4 辺のうち、ゲート側駆動機構 ( ゲート側駆動 IC チップ 109 、ゲート側制御基板 112 など ) が実装される額縁領域 12a にゲート引き出し配線が配設され、ソース側駆動機構 ( ソース側駆動 IC チップ 113 、ソース側制御基板 116 など ) が実装される額縁領域 12b にソース引き出し配線が配設されるように構成したが、本発明の適用はこの構成の液晶パネルに限られない。

【 0062 】

例えば、小型の液晶表示装置では、液晶パネルの 4 辺のうち 1 辺の額縁領域にゲート側駆動機構とソース側駆動機構の両方が実装されることも多い。その場合、ゲート引き出し配線は、液晶パネルの 4 辺のうち駆動機構の実装される 1 辺とその両側の 2 辺、すなわち

50

計 3 辺の額縁領域に配設されることが多い。本発明は、そのような構成の液晶パネルにも適用可能であり、ゲート引き出し配線が配置されない辺も含めて、全ての辺の額縁領域に、TFTアレイ基板 100 の最表面を覆う導電層を設けることで、上記と同様の効果を得ることができる。

#### 【0063】

すなわち、本発明は、4 辺のうち 1 辺ないし 3 辺の額縁領域にゲート引き出し配線が配置される構造の液晶パネルに対して適用可能であり、ゲート引き出し配線の配置されない辺も含めて全ての辺に、TFTアレイ基板の最表面を覆う導電層が設ければよい。

#### 【0064】

＜実施の形態 2＞

実施の形態 1 では、TFTアレイ基板 100 の最表面を覆う導電層 117 を、液晶層 30 内（シール材 31 よりも内側）のみに配置したが、その配置場所はこの限りではない。

#### 【0065】

図 5 および図 6 は、実施の形態 2 に係る液晶パネル 10 の額縁領域 12 近傍の断面図であり、図 5 は額縁領域 12a の近傍、図 6 は額縁領域 12c の近傍をそれぞれ示している。実施の形態 2 では、導電層 117 がシール材 31 にかかるように、つまり、導電層 117 の外側端部がシール材 31 と重複するように、導電層 117 を配置する。額縁領域 12b, 12d の図示は省略するが、額縁領域 12a ~ 12d の全てにおいて、導電層 117 の外側端部がシール材 31 と重複するように、導電層 117 を配置するとよい。

#### 【0066】

シール材 31 表面の抵抗値が液晶層 30 の液晶の抵抗値よりも小さい場合には、実施の形態 2 のように、導電層 117 をシール材 31 に接触させることで、対向基板 200 の表面に蓄積された電荷がより効率的に導電層 117 に流れるようになる。それにより、対向基板 200 表面と TFTアレイ基板 100 の表面の電位差、つまり液晶層 30 に縦方向に印加される電界を緩和する作用が向上し、表示ムラの発生を防止する効果が高くなる。

#### 【0067】

さらに、シール材 31 自体を導電性材料より構成してもよい。具体的には、例えば表面に金メッキがされた球形の樹脂等の導電性粒子を混入した樹脂材料などを、シール材 31 として用いてもよい。そうすることにより、対向基板 200 の表面に蓄積された電荷を、シール材 31 の内部とシール材 31 と導電層 117 の重なり部分を介して、導電層 117 に流すことができ、上記の効果がより顕著に得られる。なお、シール材 31 を導電性材料で構成とする際の抵抗値の目安としては、上記の具体例のように、金属などのいわゆる導体を介した程度の抵抗値が望ましいが、少なくとも液晶層 30 の液晶の抵抗値よりも小さければ、シール材 31 表面の抵抗値が液晶層 30 の液晶の抵抗値よりも小さい場合と同等の効果は得られる。また、実施の形態 1 においても、シール材 31 を導電性材料で形成してもよい。

#### 【0068】

また、導電層 117 の端部がシール材 31 に達することで、シール材 31 近傍の領域の全てが導電層 117 で覆われることとなり、導電層 117 の下に配設されるゲート引き出し配線 105a、共通配線 107a、ソース引き出し配線（不図示）などからの電界をシールドする作用が最大限に発揮されるようになる。

#### 【0069】

＜実施の形態 3＞

実施の形態 1 では、TFTアレイ基板 100 の最表面を覆う導電層 117 を、表示領域 11 に設けられる共通電極 103 または画素電極 102 と同じ透明導電膜を用いて形成したが、導電層 117 の材料はこれに限られない。

#### 【0070】

実施の形態 3 では、導電層 117 を、例えば Al 膜などの低抵抗な金属膜により形成する。それにより、対向基板 200 に蓄積された電荷がより効率的に導電層 117 へ流れるようになり、表示ムラを抑制する作用がさらに向上する。実施の形態 3 は、実施の形態 2

10

20

30

40

50

の液晶パネル 10 に対しても適用可能である。

【0071】

<実施の形態4>

図7および図8は、実施の形態4に係る液晶パネル10の額縁領域12近傍の断面図であり、図7は額縁領域12aの近傍、図8は額縁領域12cの近傍をそれぞれ示している。実施の形態4の液晶パネル10の構成は、実施の形態1とほぼ同様であるが、対向基板200のシールド導電層204の接地構造(図3および図4の接地構造205)を省略している。

【0072】

実施の形態1で説明したように、本発明に係る液晶パネル10では、シールド導電層204の接地構造が機能しなくなった場合でも、表示領域11端部に局所的に異なる電界を生じることを防止でき、表示ムラの発生を抑制できる。従って、シールド導電層204の接地構造を省略することも可能になる。

【0073】

そこで実施の形態4では、シールド導電層204の接地構造を省略することにより、液晶パネル10の製造プロセスの簡略化を図っている。また、TFTアレイ基板100および対向基板200の構造も簡単になるため、歩留まりの向上も期待できる。

【0074】

また、実施の形態4では、シールド導電層204は特定の電位に固定される必要はなく、例えは電位的にフローティング状態であってもよい。そのため、他の目的で対向基板200の外側表面に形成される導電膜を、シールド導電層204として兼用してもよい。

【0075】

例えは、異なる方向に異なる画像を表示する2画面液晶表示装置や3D液晶表示装置などでは、対向基板200の前面側に「視差バリア」と呼ばれる遮光膜が設けられるが、視差バリアとして導電性の遮光膜を用いることで、それをシールド導電層204として機能させることができる。また、例えは、相互容量方式のタッチパネルを対向基板200の前面側に配置した液晶表示装置では、タッチパネルと対向基板200との間にノイズシールド用の透明導電膜が設けられるが、それをシールド導電層204として機能させることもできる。

【0076】

さらに、図2に示した対向基板200の前面側に配置される偏光板220を導電性の材料で形成し、それをシールド導電層204として機能させてもよい。あるいは、偏光板220を対向基板200に貼り付けるための粘着剤を導電性にし、接着剤の層をシールド導電層204として機能させてもよい。いずれにしても、本実施の形態ではシールド導電層204を接地しないため、シールド導電層204は、対向基板200の外側に露出していないてもよい。

【0077】

なお、本発明は、その発明の範囲内において、各実施の形態を自由に組み合わせたり、各実施の形態を適宜、変形、省略することが可能である。

【符号の説明】

【0078】

10 液晶パネル、11 表示領域、12, 12a~12d 額縁領域、30 液晶層

、31 シール材、100 TFTアレイ基板、101 ガラス基板、102 画素電極

、103 共通電極、104 TFT、105 ゲート配線、105a ゲート引き出し配線、106 ソース配線、107, 107a 共通配線、108 絶縁膜、109 ゲート側駆動ICチップ、110 ゲート側信号端子、111 ゲート側FFC、112 ゲート側制御基板、113 ソース側駆動ICチップ、114 ソース側信号端子、115 ソース側FFC、116 ソース側制御基板、117 導電層、118 アースパッド、119 導電テープ、120 偏光板、121 検査回路部、200 対向基板、201 ガラス基板、202 カラーフィルタ、203 ブラックマトリクス、204 シ

10

20

30

40

50

— ルド導電層、205 接地構造、220 偏光板。

【図1】

【図3】

【図5】

【図4】

【図6】

【図7】

【図8】

---

フロントページの続き

(72)発明者 永野 慎吾

東京都千代田区丸の内二丁目7番3号 三菱電機株式会社内

(72)発明者 外 徳仁

東京都千代田区丸の内二丁目7番3号 三菱電機株式会社内

審査官 廣田 かおり

(56)参考文献 特開2013-064800(JP, A)

特開2006-323097(JP, A)

特開2010-122704(JP, A)

国際公開第2013/021929(WO, A1)

特開2010-224406(JP, A)

特開2011-191639(JP, A)

特開昭63-055524(JP, A)

(58)調査した分野(Int.Cl., DB名)

G 02 F 1 / 1368

G 02 F 1 / 1335