(19) 日本国特許庁(JP)

## (12) 公開特許公報(A)

(11) 特許出願公開番号

特開2004-103081

(P2004-103081A)

(43) 公開日 平成16年4月2日(2004.4.2)

(51) Int.CI.<sup>7</sup>

F 1

テーマコード(参考)

**G 11 C 11/403**

G 11 C 11/34

3 6 3 M

5 L 1 O 6

**G 11 C 11/401**

G 11 C 29/00

6 0 3 P

5 M 0 2 4

**G 11 C 29/00**

G 11 C 29/00

6 0 3 Z

G 11 C 11/34

3 7 1 D

G 11 C 11/34

3 7 1 A

審査請求 未請求 請求項の数 13 O L (全 42 頁)

(21) 出願番号

特願2002-261343(P2002-261343)

(22) 出願日

平成14年9月6日(2002.9.6)

(71) 出願人

503121103

株式会社ルネサステクノロジ

東京都千代田区丸の内二丁目4番1号

(74) 代理人

100064746

弁理士 深見 久郎

(74) 代理人

100085132

弁理士 森田 俊雄

(74) 代理人

100083703

弁理士 仲村 義平

(74) 代理人

100096781

弁理士 堀井 豊

(74) 代理人

100098316

弁理士 野田 久登

(74) 代理人

100109162

弁理士 酒井 将行

最終頁に続く

(54) 【発明の名称】半導体記憶装置

## (57) 【要約】

【課題】低コストで高速動作を可能とし、かつ、エリアペナルティを小さく抑える半導体記憶装置を提供する。

【解決手段】2つのメモリセルアレイMA # 0 0 , MA # 0 1 の間に配置されるセンスアンプS A B # 0 は、センスアンプ6 2 , 6 3 と、メモリセルアレイMA # 0 0 , MA # 0 1 に含まれるメモリセルの予備メモリセルとして利用可能なスペアメモリセルS C e l l 0 0 ~ S C e l l 1 5 1 を含む。このスペアメモリセルを用いて、リフレッシュ動作が2段階に分けて実行される。すなわち、センスアンプ6 2 , 6 3 に読み出されたリフレッシュ対象のデータは、いずれかのスペアメモリセルに一旦記憶され、その後再び読み出されて元のメモリセルに書き込まれる。

【選択図】

図3

**【特許請求の範囲】****【請求項 1】**

リフレッシュ動作が必要な半導体記憶装置であって、

メモリブロックと、

当該半導体記憶装置の動作を制御する制御回路とを備え、

前記メモリブロックは、

複数のメモリセルを含むメモリセルアレイと、

複数のワード線および複数のビット線対と、

前記複数のビット線対を介して前記メモリセルアレイに接続されるセンスアンプ帯とを含み、

前記センスアンプ帯は、

前記複数のビット線対に対応して設けられる複数のセンスアンプと、

前記センスアンプによって読出されたデータを保持するデータ保持回路とからなり、

前記制御回路は、リフレッシュ動作において、リフレッシュ対象のメモリセルから前記複数のセンスアンプに読出されたデータを前記データ保持回路に保持する第1の動作と、前記データ保持回路に保持された前記データを前記複数のセンスアンプに読み出し、その読み出されたデータを前記リフレッシュ対象のメモリセルへ書込む第2の動作とにわけて、前記リフレッシュ動作を実行する、半導体記憶装置。

**【請求項 2】**

前記制御回路は、前記リフレッシュ動作時、前記複数のセンスアンプに既にデータが読み出されているとき、その読み出されているデータを前記データ保持回路に保持する動作をさらに実行する、請求項1に記載の半導体記憶装置。

**【請求項 3】**

前記センスアンプ帯は、前記制御回路からの指令に基づいて前記メモリセルアレイを当該センスアンプ帯と分離する分離回路をさらに含み、前記データ保持回路は、前記複数のセンスアンプと前記分離回路との間に設けられ、

前記制御回路は、前記データ保持回路に対するデータの読み書き動作を実行するとき、前記分離回路を活性化する動作を実行する、請求項1に記載の半導体記憶装置。

**【請求項 4】**

前記データ保持回路は、

前記複数のメモリセルの予備メモリセルとして動作可能な複数のスペアメモリセルと、

前記複数のスペアメモリセルに対応して設けられる複数のスペアワード線とによって構成される、請求項2に記載の半導体記憶装置。

**【請求項 5】**

前記複数のスペアメモリセルは、対を構成する複数の第1および第2のスペアメモリセルからなり、

前記複数の第1のスペアメモリセルの各々は、前記複数のビット線対に含まれるいずれかのビット線対を構成する一方のビット線に接続され、

前記複数の第2のスペアメモリセルの各々は、前記いずれかのビット線対を構成するもう一方のビット線に接続され、対となる前記第1のスペアメモリセルが記憶するデータの反転データを記憶する、請求項4に記載の半導体記憶装置。

**【請求項 6】**

外部から入力された行アドレスを保持し、前記複数のメモリセルおよび前記複数のスペアメモリセルに対するデータの入出力をそれぞれ前記ワード線単位および前記スペアワード線単位で管理する行アドレス管理回路と、前記外部から入力された行アドレスに応じて異なるデータ入出力タイミングを外部へ通知する制御信号出力端子とをさらに備える、請求項4に記載の半導体記憶装置。

**【請求項 7】**

前記行アドレス管理回路は、

前記複数のワード線に含まれるいずれかのワード線を活性化するコマンドとともに外部か

ら与えられる第1の行アドレスを保持し、後に入力される第2の行アドレスを前記第1の行アドレスと比較する行アドレス比較回路と、

前記複数のスペアワード線に対応して設けられ、対応するスペアワード線に対して予め設定された動作モードに基づいて、前記対応するスペアワード線を活性化する複数のデコーダとを含む、請求項6に記載の半導体記憶装置。

#### 【請求項8】

前記動作モードは、

前記複数のワード線の予備線として前記スペアワード線を使用する第1の動作モードと、前記リフレッシュ動作時のリフレッシュ対象のデータを一時的に記憶するメモリセルとして、前記スペアワード線に接続される前記スペアメモリセルを使用する第2の動作モードと、

前記リフレッシュ動作時に前記複数のセンスアンプに既に読出されているデータを一時的に記憶するメモリセルとして、前記スペアワード線に接続される前記スペアメモリセルを使用する第3の動作モードとを備える、請求項7に記載の半導体記憶装置。

#### 【請求項9】

リフレッシュ動作時、

前記制御回路は、前記複数のスペアワード線に含まれるいずれかのスペアワード線の活性化を指示する信号を前記行アドレス管理回路へ出力し、

前記第2の動作モードに設定されているスペアワード線に対応する前記デコーダは、前記信号に応じて、対応する前記スペアワード線を活性化する、請求項8に記載の半導体記憶装置。

#### 【請求項10】

データ読出時、

前記行アドレス比較回路は、外部から読出コマンドとともに与えられる前記第2の行アドレスを前記第1の行アドレスと比較し、その比較結果を前記制御回路へ出力し、

前記制御回路は、前記第2の行アドレスが前記第1の行アドレスと一致するとの比較結果を前記行アドレス比較回路から受け、かつ、前記第1の行アドレスの入力以降に前記リフレッシュ動作を実行しているとき、前記第1の行アドレスに接続されるメモリセルのデータを一時的に記憶しているスペアメモリセルが接続されるスペアワード線の活性化を指示する信号を前記行アドレス管理回路へ出力し、前記信号に応じて前記スペアメモリセルから前記センスアンプ帯に読出された前記データを外部へ出力する動作を実行し、

前記第3の動作モードに設定されているスペアワード線に対応する前記デコーダは、前記信号に応じて、対応する前記スペアワード線を活性化する、請求項8に記載の半導体記憶装置。

#### 【請求項11】

データ読出時、

前記行アドレス比較回路は、外部から読出コマンドとともに与えられる前記第2の行アドレスを前記第1の行アドレスと比較し、その比較結果を前記制御回路へ出力し、

前記制御回路は、前記第2の行アドレスが前記第1の行アドレスと一致するとの比較結果を前記行アドレス比較回路から受け、かつ、前記第1の行アドレスの入力以降に前記リフレッシュ動作を実行していないとき、前記センスアンプ帯に保持されているデータを外部へ出力する動作を実行する、請求項7に記載の半導体記憶装置。

#### 【請求項12】

データ読出時、

前記行アドレス比較回路は、外部から読出コマンドとともに与えられる前記第2の行アドレスを前記第1の行アドレスと比較し、その比較結果を前記制御回路へ出力し、

前記制御回路は、前記第2の行アドレスが前記第1の行アドレスと一致しないとの比較結果を前記行アドレス比較回路から受けたとき、前記メモリセルアレイに含まれる、前記第2の行アドレスに対応するワード線に接続されるメモリセルからデータを読出して外部へ出力する動作を実行する、請求項7に記載の半導体記憶装置。

10

20

30

40

50

**【請求項 13】**

もう1つのメモリブロックと、

前記制御回路からの指令に基づいて前記メモリブロックを前記もう1つのメモリブロックと接続する接続回路とをさらに備え、

前記制御回路は、前記メモリブロックに含まれるメモリセルアレイからデータを読出すとき、前記接続回路を活性化する動作を実行し、前記メモリブロックに含まれる前記センスアンプ帯から前記もう1つのメモリブロックに含まれるセンスアンプ帯へ前記データを転送する動作を実行し、前記もう1つのメモリブロックに含まれるセンスアンプ帯から前記データを外部へ出力する動作を実行する、請求項1に記載の半導体記憶装置。

**【発明の詳細な説明】**

10

**【0001】****【発明の属する技術分野】**

この発明は、半導体記憶装置に関し、特に、リフレッシュ動作が必要な半導体記憶装置に関する。

**【0002】****【従来の技術】**

半導体記憶装置の代表格の1つであるDRAM(Dynamic Random Access Memory)は、メモリセルが1つのトランジスタおよび1つのキャパシタで構成され、メモリセル自体の構造が単純であることから、半導体デバイスの高集積化および大容量化に最適なものとして、様々なシステムにおいて使用されている。そして、DRAMが利用されるシステムの性能、用途、規模などによって、様々なタイプのDRAMがこれまで開発されている。

20

**【0003】**

近年、コンピュータにおける半導体記憶装置としては、シンクロナスダイナミックランダムアクセスメモリ(SDRAM)が主に利用されている。SDRAMは、ワード線を活性化するアクティベートコマンド(ACTコマンド)とセンスアンプに蓄えられた値を読出すリードコマンド(RDコマンド)との組合せによってデータの読出動作を行なう。SDRAMは、複数のコラムアドレスのデータを連續して出力するバースト動作を行なうため、同一のワード線に対してRDコマンドが連續して入力される場合には、高速に動作することができる。

30

**【0004】**

また、小規模なシステムにおいては、擬似SRAM(Static Random Access Memory)が利用されることがある。擬似SRAMは、基本的にはDRAMであるが、アドレスのマルチプレクス入力が不要であり、また、リフレッシュ動作も不要であるため、利用するシステム側からはSRAMとして制御することができる。

**【0005】**

一方、DRAMとともに代表的な半導体記憶装置の1つであるSRAMは、DRAMにおいて不可欠なリフレッシュ動作が不要なRAMである。SRAMは、リフレッシュ動作が不要であるため消費電力が少なく、また、リフレッシュ動作が不要であるという点からみれば高速化も期待できるが、一般的なSRAMにおいては、アドレスを指定してからデータが外部へ出力されるまでのデータ読出にかかる時間はそれほど短くない。

40

**【0006】**

そこで、高速動作を可能としたSRAMとして、パイプラインバーストSRAM(PBSRAM)が知られている。PBSRAMは、従来の一般的なSRAMでは不可能であったパイプライン動作を可能したものであり、これによって、従来のSRAMに比べて高速に動作することができる。

**【0007】****【発明が解決しようとする課題】**

上述したSDRAMを含むDRAMは、メモリセルが1つのトランジスタおよび1つのキャパシタで構成され、その構造が単純であることから、半導体デバイスの高集積化および

50

大容量化に対しては最適なものといえる。しかしながら、そのような利点を有する一方で、D R A Mは、高速化には不向きであると一般にいわれている。

#### 【 0 0 0 8 】

すなわち、D R A Mのメモリセルにおいては、記憶データに相当するキャパシタの電荷が種々の要因によってリークし、徐々に失われていく。すなわち、時間とともに記憶データが失われる。このため、D R A Mにおいては、記憶データが失われる前に記憶データを一旦読出して書込むというリフレッシュ動作が必要不可欠となる。

#### 【 0 0 0 9 】

このリフレッシュ動作中、D R A Mは、外部からの制御コマンドを受付けることができず、制御コマンドの受け付けに対する待ち時間が発生する。すべてのメモリセルに対して同時に一括してリフレッシュ動作を実行すると、外部からの制御コマンドを受け付けなくなる時間が長期になるため、リフレッシュ動作は、一般に、ワード線単位で実行される。

10

#### 【 0 0 1 0 】

しかしながら、リフレッシュ動作は、ピット線対のプリチャージ、ピット線対へのデータの読み出し、センスアンプによる増幅、およびデータの書き込みという一連の動作からなり、従来のリフレッシュ動作は、これら一連の動作が連続して行なわれるため、リフレッシュ動作がワード線単位で実行されても、その間、外部からの制御コマンドは受け付けられず、さらなる高速化を実現するためには無視できない待ち時間が発生していた。

#### 【 0 0 1 1 】

また、上述したように、従来のS D R A Mは、前述のリフレッシュ動作の問題はあるものの、バースト動作によって動作速度の高速化が図られているが、このバースト動作を可能とするためには、該当するワード線が既に活性化していること、あるいは、他のワード線が活性化されていないかなどについて、S D R A Mを利用するシステム側で認識している必要がある。すなわち、従来のS D R A Mにおいては、外部のシステム側でS D R A Mのロウアドレスを管理することが必要となる。このロウアドレスの管理は一般に難しく、従来のS D R A Mにおいては、システム側の制御負荷が大きくなってしまうという問題があった。

20

#### 【 0 0 1 2 】

一方、上述した擬似S R A Mは、リフレッシュ動作が不要であるが、バースト動作を行なうことができず、したがって、高速に動作することができない。

30

#### 【 0 0 1 3 】

一方、P B S R A Mは、リフレッシュ動作が不要というS R A Mの利点を活かしつつ、高速動作を実現したものであるが、S R A Mのメモリセルは複数個のバルクトランジスタを含むため、メモリセルが大型化する。一般に、S R A Mのメモリセルは、4個あるいは6個のバルクトランジスタを含み、1つのトランジスタおよび1つのキャパシタでメモリセルが構成されるD R A Mと比べて、メモリセルの面積はかなり大型化する。したがって、P B S R A Mも、従来のS R A Mと同様に、十分な記憶容量が得られないという問題が残る。また、コスト面でも、S R A Mは、D R A Mに比べて1ピット当たりのコストが高いえ、P B S R A Mは、一般的なS R A Mでは不可能なパイプライン機能をさらに備えるため、コストが高い。

40

#### 【 0 0 1 4 】

そこで、この発明は、かかる課題を解決するためになされたものであり、その目的は、低コストで高速動作を可能とし、かつ、エリアペナルティを小さく抑える半導体記憶装置を提供することである。

#### 【 0 0 1 5 】

また、この発明の別の目的は、ロウアドレスの管理を不要とし、システムからの利用を簡便にする半導体記憶装置を提供することである。

#### 【 0 0 1 6 】

#### 【 課題を解決するための手段 】

この発明によれば、半導体記憶装置は、リフレッシュ動作が必要な半導体記憶装置であつ

50

て、メモリブロックと、当該半導体記憶装置の動作を制御する制御回路とを備え、メモリブロックは、複数のメモリセルを含むメモリセルアレイと、複数のワード線および複数のビット線対と、複数のビット線対を介してメモリセルアレイに接続されるセンスアンプ帯とを含み、センスアンプ帯は、複数のビット線対に対応して設けられる複数のセンスアンプと、センスアンプによって読出されたデータを保持するデータ保持回路とからなり、制御回路は、リフレッシュ動作において、リフレッシュ対象のメモリセルから複数のセンスアンプに読出されたデータをデータ保持回路に保持する第1の動作と、データ保持回路に保持されたデータを複数のセンスアンプに読み出し、その読み出されたデータをリフレッシュ対象のメモリセルへ書込む第2の動作とにわけて、リフレッシュ動作を実行する。

## 【0017】

10

好ましくは、制御回路は、リフレッシュ動作時、複数のセンスアンプに既にデータが読み出されているとき、その読み出されているデータをデータ保持回路に保持する動作をさらに実行する。

## 【0018】

好ましくは、センスアンプ帯は、制御回路からの指令に基づいてメモリセルアレイを当該センスアンプ帯と分離する分離回路をさらに含み、データ保持回路は、複数のセンスアンプと分離回路との間に設けられ、制御回路は、データ保持回路に対するデータの読み書き動作を実行するとき、分離回路を活性化する動作を実行する。

## 【0019】

20

好ましくは、データ保持回路は、複数のメモリセルの予備メモリセルとして動作可能な複数のスペアメモリセルと、複数のスペアメモリセルに対応して設けられる複数のスペアワード線とによって構成される。

## 【0020】

好ましくは、複数のスペアメモリセルは、対を構成する複数の第1および第2のスペアメモリセルからなり、複数の第1のスペアメモリセルの各々は、複数のビット線対に含まれるいずれかのビット線対を構成する一方のビット線に接続され、複数の第2のスペアメモリセルの各々は、いずれかのビット線対を構成するもう一方のビット線に接続され、対となる第1のスペアメモリセルが記憶するデータの反転データを記憶する。

## 【0021】

30

好ましくは、半導体記憶装置は、外部から入力された行アドレスを保持し、複数のメモリセルおよび複数のスペアメモリセルに対するデータの入出力をそれぞれワード線単位およびスペアワード線単位で管理する行アドレス管理回路と、外部から入力された行アドレスに応じて異なるデータ入出力タイミングを外部へ通知する制御信号出力端子とをさらに備える。

## 【0022】

40

好ましくは、行アドレス管理回路は、複数のワード線に含まれるいずれかのワード線を活性化するコマンドとともに外部から与えられる第1の行アドレスを保持し、後に入力される第2の行アドレスを第1の行アドレスと比較する行アドレス比較回路と、複数のスペアワード線に対応して設けられ、対応するスペアワード線に対して予め設定された動作モードに基づいて、対応するスペアワード線を活性化する複数のデコーダとを含む。

## 【0023】

好ましくは、動作モードは、複数のワード線の予備線としてスペアワード線を使用する第1の動作モードと、リフレッシュ動作時のリフレッシュ対象のデータを一時的に記憶するメモリセルとして、スペアワード線に接続されるスペアメモリセルを使用する第2の動作モードと、リフレッシュ動作時に複数のセンスアンプに既に読み出されているデータを一時的に記憶するメモリセルとして、スペアワード線に接続されるスペアメモリセルを使用する第3の動作モードとを備える。

## 【0024】

好ましくは、リフレッシュ動作時、制御回路は、複数のスペアワード線に含まれるいずれかのスペアワード線の活性化を指示する信号を行アドレス管理回路へ出力し、第2の動作

50

モードに設定されているスペアワード線に対応するデコーダは、信号に応じて、対応するスペアワード線を活性化する。

【0025】

好ましくは、データ読出時、行アドレス比較回路は、外部から読出コマンドとともに与えられる第2の行アドレスを第1の行アドレスと比較し、その比較結果を制御回路へ出力し、制御回路は、第2の行アドレスが第1の行アドレスと一致するとの比較結果を行アドレス比較回路から受け、かつ、第1の行アドレスの入力以降にリフレッシュ動作を実行しているとき、第1の行アドレスに接続されるメモリセルのデータを一時的に記憶しているスペアメモリセルが接続されるスペアワード線の活性化を指示する信号を行アドレス管理回路へ出力し、信号に応じてスペアメモリセルからセンスアンプ帯に読出されたデータを外部へ出力する動作を実行し、第3の動作モードに設定されているスペアワード線に対応するデコーダは、信号に応じて、対応するスペアワード線を活性化する。10

【0026】

好ましくは、データ読出時、行アドレス比較回路は、外部から読出コマンドとともに与えられる第2の行アドレスを第1の行アドレスと比較し、その比較結果を制御回路へ出力し、制御回路は、第2の行アドレスが第1の行アドレスと一致するとの比較結果を行アドレス比較回路から受け、かつ、第1の行アドレスの入力以降にリフレッシュ動作を実行していないとき、センスアンプ帯に保持されているデータを外部へ出力する動作を実行する。

【0027】

好ましくは、データ読出時、行アドレス比較回路は、外部から読出コマンドとともに与えられる第2の行アドレスを第1の行アドレスと比較し、その比較結果を制御回路へ出力し、制御回路は、第2の行アドレスが第1の行アドレスと一致しないとの比較結果を行アドレス比較回路から受けたとき、メモリセルアレイに含まれる、第2の行アドレスに対応するワード線に接続されるメモリセルからデータを読出して外部へ出力する動作を実行する。20

【0028】

好ましくは、半導体記憶装置は、もう1つのメモリブロックと、制御回路からの指令に基づいてメモリブロックをもう1つのメモリブロックと接続する接続回路とをさらに備え、制御回路は、メモリブロックに含まれるメモリセルアレイからデータを読出すとき、接続回路を活性化する動作を実行し、メモリブロックに含まれるセンスアンプ帯からもう1つのメモリブロックに含まれるセンスアンプ帯へデータを転送する動作を実行し、もう1つのメモリブロックに含まれるセンスアンプ帯からデータを外部へ出力する動作を実行する。30

【0029】

このように、この発明による半導体記憶装置においては、センスアンプに読出されたデータを保持するデータ保持回路を備え、このデータ保持回路を用いてリフレッシュ動作が2段階にわけられて実行される。

【0030】

したがって、この発明によれば、リフレッシュ動作時に外部からコマンドを受付けなくなる期間が短縮され、リフレッシュ動作による動作遅延が小さくなり、その結果、半導体記憶装置の高速動作化が達成される。また、メモリセルの構成は、従来のDRAMと同じであるため、低成本であり、かつ大容量化も実現できる。さらに、データ保持回路としてスペアメモリセルを利用できるため、新たな回路を設ける必要がなく、エリアペナルティを抑えることができる。40

【0031】

また、この発明による半導体記憶装置は、行アドレス管理機能を内蔵し、ワード線の活性化状態によって異なるデータ入出力タイミングが制御信号出力端子を介して外部のシステムへ通知される。

【0032】

したがって、この発明によれば、この半導体記憶装置を利用するシステム側でロウアドレ50

スの管理を行なう必要がなく、システム側の制御負荷が削減される。

【0033】

さらに、この発明による半導体記憶装置においては、センスアンプに読出されたデータは、隣接するメモリブロックのセンスアンプ帯に転送することができ、転送先のセンスアンプ帯において外部とデータのインターフェースを行なうことができる。

【0034】

したがって、データ読出中においても並行してリフレッシュ動作が可能となり、リフレッシュ動作によってバースト動作が中断されることなく、さらなる高速化が達成される。

【0035】

【発明の実施の形態】

以下、本発明の実施の形態について、図面を参照しながら詳細に説明する。なお、図中同一または相当部分には同一符号を付してその説明は繰返さない。

【0036】

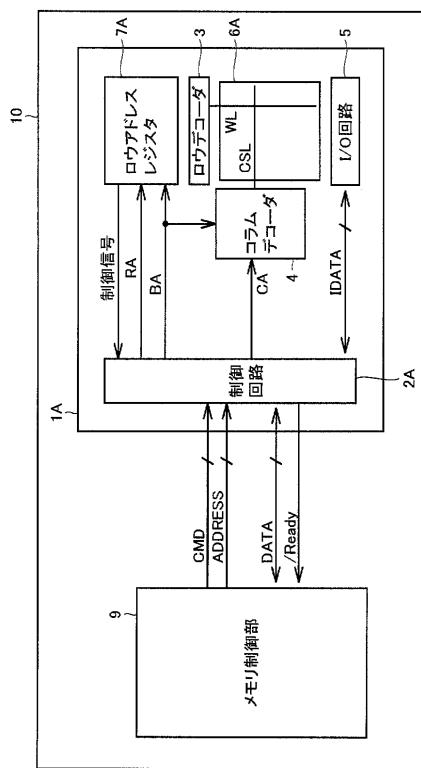

【実施の形態1】

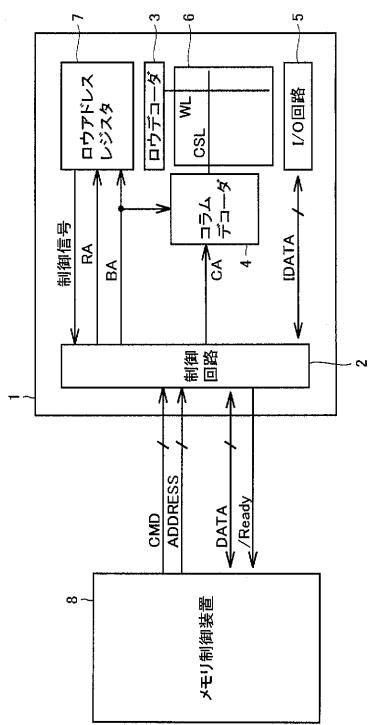

図1は、この発明の実施の形態1による半導体記憶装置の全体構成を示す概略ブロック図である。

【0037】

図1を参照して、半導体記憶装置1は、制御回路2と、ロウデコーダ3と、コラムデコーダ4と、入出力回路5と、メモリセルアレイ6と、ロウアドレスレジスタ7とを備える。

【0038】

制御回路2は、外部のメモリ制御装置8からコマンドCMDおよびアドレス信号ADDRESSを受ける。制御回路2は、アドレス信号ADDRESSに基づいて、ロウアドレス信号RAおよびコラムアドレス信号CAをそれぞれロウアドレスレジスタ7およびコラムデコーダ4へ出力し、バンクアドレス信号BAをロウアドレスレジスタ7およびコラムデコーダ4へ出力する。

【0039】

また、制御回路2は、メモリ制御装置8からコマンドCMDおよびアドレス信号ADDRESSを受けると、それに応じてデータDATAの授受をメモリ制御装置8との間で行なう。また、制御回路2は、データDATAに対応する内部データIDATAを入出力回路5と授受し、メモリセルアレイ6に対してデータの読み書きが行なわれる。

【0040】

さらに、制御回路2は、ロウアドレスレジスタ7からロウアドレスに関する制御信号を受け、その制御信号に基づいて各回路の動作を制御する。この制御信号および制御回路2の詳細な動作については、後ほど詳細に説明する。そして、制御回路2は、メモリ制御装置8から指定されたロウアドレスの状態に応じて異なる、データDATAの入出力タイミングを示す信号/Readyをメモリ制御装置8へ出力する。

【0041】

ロウデコーダ3およびコラムデコーダ4は、制御回路2からロウアドレス信号RAおよびコラムアドレス信号CAをそれぞれ受けてデコードし、ロウアドレス信号RAおよびコラムアドレス信号CAに対応するワード線WLおよびコラム選択線CSLをそれぞれ選択する。

【0042】

入出力回路5は、制御回路2と内部データIDATAの授受を行ない、メモリセルアレイ6に対してデータの入出力を行なう。

【0043】

メモリセルアレイ6は、メモリセルが行列状に配列された記憶素子群である。メモリセルアレイ6は、独立して動作可能な複数のバンクに分割され、アドレス信号ADDRESSに含まれるバンクアドレス信号BAによってバンクが選択される。なお、説明の便宜上、以降の説明においてはバンクアドレスは適宜省略され、特に説明がないかぎり、バンク0に対してのみコマンドが与えられる場合について説明する。

10

20

30

40

50

**【 0 0 4 4 】**

ロウアドレスレジスタ7は、メモリ制御装置8から指定されたロウアドレス信号RAを一時的に記憶し、その後、ロウアドレス信号RAを受けると、記憶しているロウアドレス信号RAと比較してその比較結果を制御回路2へ出力する。また、ロウアドレスレジスタ7は、メモリセルアレイ6においてデータの一時的な記憶回路として用いられるスペアメモリセルが接続されるスペアワード線SWLの動作管理を行なう。ロウアドレスレジスタ7の構成および動作については、後ほど詳細に説明する。

**【 0 0 4 5 】**

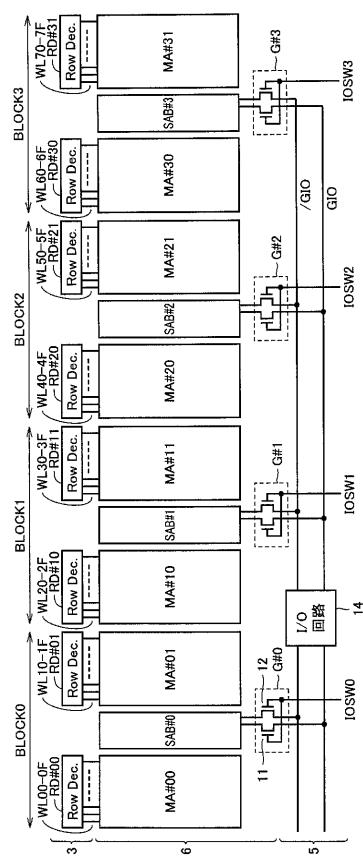

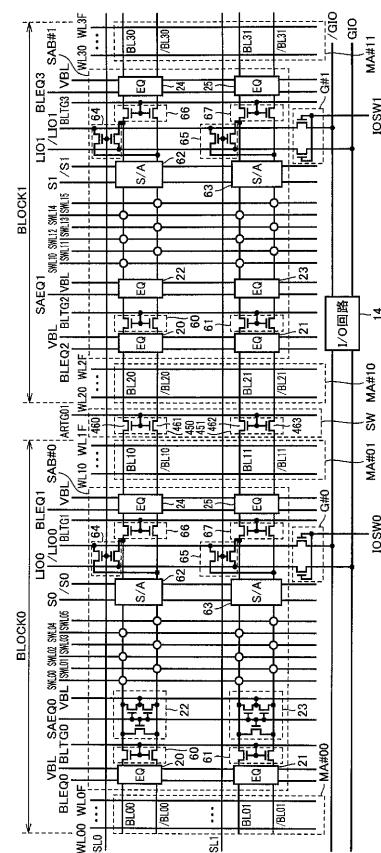

図2は、図1に示すメモリセルアレイ6のアレイ配置を模式的に示す図である。なお、上述したように、メモリセルアレイ6は、複数のバンクに分割されているが、図2においては、1つのバンク0についてのアレイ構成が示されている。

**【 0 0 4 6 】**

図2を参照して、メモリセルアレイ6は、メモリブロックBLOCK0～BLOCK3を含む。メモリブロックBLOCK0は、センスアンプ帯SAB#0と、センスアンプ帯SAB#0の両側に配置されてこのセンスアンプ帯SAB#0を共有するメモリセルアレイMA#00, MA#01とを含む。メモリブロックBLOCK1は、センスアンプ帯SAB#1と、センスアンプ帯SAB#1の両側に配置されてこのセンスアンプ帯SAB#1を共有するメモリセルアレイMA#10, MA#11とを含む。

**【 0 0 4 7 】**

メモリブロックBLOCK2は、センスアンプ帯SAB#2と、センスアンプ帯SAB#2の両側に配置されてこのセンスアンプ帯SAB#2を共有するメモリセルアレイMA#20, MA#21とを含む。メモリブロックBLOCK3は、センスアンプ帯SAB#3と、センスアンプ帯SAB#3の両側に配置されてこのセンスアンプ帯SAB#3を共有するメモリセルアレイMA#30, MA#31とを含む。

**【 0 0 4 8 】**

ロウデコーダ3は、メモリセルアレイMA#00～MA#31に対応してそれぞれ設けられるロウデコーダRD#00～RD#31を含む。ロウデコーダRD#00は、ワード線WL00～WL0Fの制御を行ない、ロウデコーダRD#01は、ワード線WL10～WL1Fの制御を行なう。ロウデコーダRD#10は、ワード線WL20～WL2Fの制御を行ない、ロウデコーダRD#11は、ワード線WL30～WL3Fの制御を行なう。ロウデコーダRD#20は、ワード線WL40～WL4Fの制御を行ない、ロウデコーダRD#21は、ワード線WL50～WL5Fの制御を行なう。ロウデコーダRD#30は、ワード線WL60～WL6Fの制御を行ない、ロウデコーダRD#31は、ワード線WL70～WL7Fの制御を行なう。

**【 0 0 4 9 】**

すなわち、各メモリセルアレイには、ロウアドレス信号RA0～RA3によって区別されるワード線が16本ずつある。1つのメモリブロックにおいては、メモリセルアレイは、センスアンプ帯を中心にして左右に分割されており、ロウアドレス信号RA4によってそのいずれかが指定される。そして、ロウアドレス信号RA5, 6によって4つのメモリブロックBLOCK0～BLOCK3のいずれかが指定される。また、各メモリブロックごとに、ローカルIO線LIO, /LIOをグローバルIO線GIO, /GIOにそれぞれ接続する接続ゲート回路G#0～G#3が設けられている。

**【 0 0 5 0 】**

なお、図2には図示されていないが、コラムアドレスは、コラムアドレス信号CA0～CA3によって指定される16アドレスとする。そして、ワード線と直行するコラム選択線CSL0～CSLF(図示せず)が、図示されたメモリセルアレイに共通して設けられている。

**【 0 0 5 1 】**

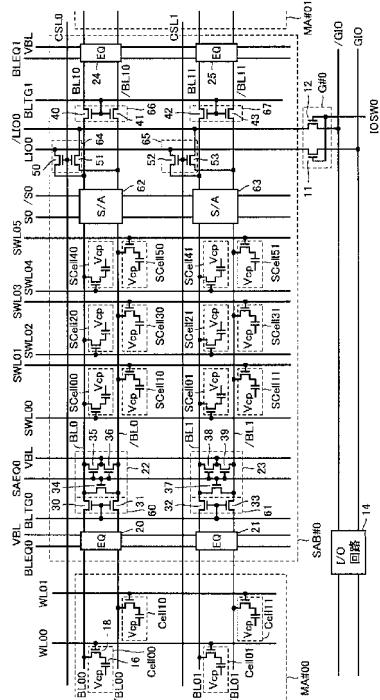

図3は、実施の形態1による半導体記憶装置1のセンスアンプ帯周辺の構成を示す回路図である。

10

20

30

40

50

**【 0 0 5 2 】**

図3を参照して、メモリセルアレイMA#00は、ワード線WL00とビット線BL00との交点に対応して設けられるメモリセルCe1100と、ワード線WL01とビット線/BL00との交点に対応して設けられるメモリセルCe1110と、ワード線WL00とビット線BL01との交点に対応して設けられるメモリセルCe1101と、ワード線WL01とビット線/BL01との交点に対応して設けられるメモリセルCe1111とを含む。

**【 0 0 5 3 】**

なお、図3においては、図示の関係上、メモリセルアレイMA#00に含まれる4つのメモリセルのみ示されているが、実際には、ワード線WL00～WL0Fおよびビット線対BL00, /BL00～BL0F, /BL0Fに対応して256個のメモリセルがメモリセルアレイMA#00に含まれる。以下では、図3に示された範囲で説明を行なう。

10

**【 0 0 5 4 】**

メモリセルCe1100は、セルプレート電位Vcpに一端が接続されるキャパシタ16と、キャパシタ16のもう一端とビット線BL00との間に接続され、ワード線WL00にゲートが接続されるNチャネルMOSトランジスタ18とを含む。メモリセルCe1101, Ce1110, Ce1111も、メモリセルCe1100と同様の構成を有しており、各メモリセルの構成の説明は繰返さない。

**【 0 0 5 5 】**

また、メモリセルアレイMA#01についても、メモリセルアレイMA#00と同様の構成を有しており、その説明は繰返さない。

20

**【 0 0 5 6 】**

センスアンプ帯SAB#0は、センスアンプ62と、センスアンプ62に対応して設けられる、イコライズ回路20, 22, 24、分離ゲート回路60, 66、接続回路64およびスペアメモリセルSCe1100, SCe1110, SCe1120, SCe1130, SCe1140, SCe1150とを含む。

30

**【 0 0 5 7 】**

センスアンプ62は、ビット線対BL0, /BL0に対応して設けられ、メモリセルアレイMA#00に接続されるビット線対BL00, /BL00およびメモリセルアレイMA#01に接続されるビット線対BL10, /BL10に共有される。このように、センスアンプ帯SAB#0においては、センスアンプのレイアウト面積を削減するため、センスアンプの両側にビット線対を2組設けたシェアードセンスアンプ構成となっている。

**【 0 0 5 8 】**

センスアンプ62は、駆動信号S0, /S0によって制御される。なお、センスアンプは、メモリブロックごとに独立して制御されるため、メモリブロックBLOCK0のセンスアンプ帯SAB#0に含まれるセンスアンプの駆動信号はS0と表わされ、たとえば、メモリブロックBLOCK1のセンスアンプ帯SAB#1に含まれるセンスアンプの駆動信号はS1と表わされる。

40

**【 0 0 5 9 】**

イコライズ回路22は、NチャネルMOSトランジスタ34～36を含む。NチャネルMOSトランジスタ34は、ビット線BL0とビット線/BL0との間に接続され、信号SAEQ0をゲートに受ける。NチャネルMOSトランジスタ35は、電位VBLが与えられるノードとビット線BL0との間に接続され、信号SAEQ0をゲートに受ける。NチャネルMOSトランジスタ36は、電位VBLが与えられるノードとビット線/BL0との間に接続され、信号SAEQ0をゲートに受ける。

**【 0 0 6 0 】**

イコライズ回路22は、信号SAEQ0が活性化されると、センスアンプ62と直接接続されるビット線対BL0, /BL0を電位VBLにイコライズしてセンスアンプ62を初期化する。

**【 0 0 6 1 】**

50

分離ゲート回路 60 は、N チャネルMOS トランジスタ 30, 31 を含む。N チャネルMOS トランジスタ 30 は、ビット線 BL0 とビット線 BL00との間に接続され、信号 BLTG0 をゲートに受ける。N チャネルMOS トランジスタ 31 は、ビット線 / BL0 とビット線 / BL00との間に接続され、信号 BLTG0 をゲートに受ける。

#### 【 0 0 6 2 】

分離ゲート回路 60 は、信号 BLTG0 が非活性化されると、ビット線 BL0 をビット線 BL00 と電気的に分離し、ビット線 BL / 0 をビット線 / BL00 と電気的に分離する。

#### 【 0 0 6 3 】

分離ゲート回路 66 は、N チャネルMOS トランジスタ 40, 41 を含む。N チャネルMOS トランジスタ 40 は、ビット線 BL0 とビット線 BL10との間に接続され、信号 BLTG1 をゲートに受ける。N チャネルMOS トランジスタ 41 は、ビット線 / BL0 とビット線 / BL10との間に接続され、信号 BLTG1 をゲートに受ける。

#### 【 0 0 6 4 】

分離ゲート回路 66 は、信号 BLTG1 が非活性化されると、ビット線 BL0 をビット線 BL10 と電気的に分離し、ビット線 BL / 0 をビット線 / BL10 と電気的に分離する。

#### 【 0 0 6 5 】

接続回路 64 は、N チャネルMOS トランジスタ 50, 51 を含む。N チャネルMOS トランジスタ 50 は、ローカルIO 線 LIO0 とビット線 BL0 との間に接続され、コラム選択線 CSL0 にゲートが接続される。N チャネルMOS トランジスタ 51 は、ローカルIO 線 / LIO0 とビット線 / BL0 との間に接続され、コラム選択線 CSL0 にゲートが接続される。

#### 【 0 0 6 6 】

接続回路 64 は、コラム選択線 CSL0 が活性化されると、ビット線 BL0 をローカルIO 線 LIO0 と電気的に接続し、ビット線 / BL0 をローカルIO 線 / LIO0 と電気的に接続する。

#### 【 0 0 6 7 】

イコライズ回路 20, 24 は、信号 SAEQ0 に代えてそれぞれ信号 BЛЕQ0, BЛЕQ1 を受ける点でイコライズ回路 22 と異なるが、その回路構成は、イコライズ回路 22 と同じであるので、説明は繰返さない。ただし、イコライズ回路 22 がイコライズするビット線対 BL0, / BL0 は、メモリセルアレイが接続されるビット線 BL00, / BL00, BL10, / BL10 に比べて容量が小さいので、イコライズ回路 22 に含まれる 3 つのトランジスタのサイズは、イコライズ回路 20, 24 に含まれるトランジスタのサイズに比べて小さい。

#### 【 0 0 6 8 】

スペアメモリセル SCe1100 は、スペアワード線 SWL00 とビット線 BL0 との交点に対応して設けられ、スペアメモリセル SCe1110 は、スペアワード線 SWL01 とビット線 / BL0 との交点に対応して設けられる。スペアメモリセル SCe1120 は、スペアワード線 SWL02 とビット線 BL0 との交点に対応して設けられ、スペアメモリセル SCe1130 は、スペアワード線 SWL03 とビット線 / BL0 との交点に対応して設けられる。スペアメモリセル SCe1140 は、スペアワード線 SWL04 とビット線 BL0 との交点に対応して設けられ、スペアメモリセル SCe1150 は、スペアワード線 SWL05 とビット線 / BL0 との交点に対応して設けられる。

#### 【 0 0 6 9 】

なお、各スペアメモリセル SCe1100 ~ SCe1150 の構成は、メモリセル Ce1100 の構成と同じであるので、その説明は繰返さない。

#### 【 0 0 7 0 】

スペアメモリセル SCe1100 ~ SCe1150 は、メモリセルアレイ MA#00, MA#01 に含まれるメモリセルの予備用セルとして用いられるほか、センスアンプ 62 に

読み出されたデータを一時的に保持するデータ保持回路として用いられる。スペアメモリセル S C e l l 0 0 ~ S C e l l 5 0 は、メモリセル C e l l 0 0 , C e l l 1 0 に比べてセンスアンプ 6 2 に近接して配置されているので、センスアンプ 6 2 からのデータの書き込みおよびセンスアンプ 6 2 へのデータの読み出しが高速に行なわれる。

#### 【 0 0 7 1 】

センスアンプ帯 S A B # 0 は、さらに、センスアンプ 6 3 と、センスアンプ 6 3 に対応して設けられる、イコライズ回路 2 1 , 2 3 , 2 5 、分離ゲート回路 6 1 , 6 7 、接続回路 6 5 およびスペアメモリセル S C e l l 0 1 , S C e l l 1 1 1 , S C e l l 1 2 1 , S C e l l 3 1 , S C e l l 4 1 , S C e l l 5 1 とを含む。

#### 【 0 0 7 2 】

センスアンプ 6 3 は、ビット線対 B L 1 , / B L 1 に対応して設けられ、メモリセルアレイ M A # 0 0 に接続されるビット線対 B L 0 1 , / B L 0 1 およびメモリセルアレイ M A # 0 1 に接続されるビット線対 B L 1 1 , / B L 1 1 に共有される。センスアンプ 6 3 も、センスアンプ 6 2 と同様に、駆動信号 S 0 , / S 0 によって制御される。

#### 【 0 0 7 3 】

イコライズ回路 2 3 は、N チャネル M O S トランジスタ 3 7 ~ 3 9 を含む。N チャネル M O S トランジスタ 3 7 は、ビット線 B L 1 とビット線 / B L 1 との間に接続され、信号 S A E Q 0 をゲートに受ける。N チャネル M O S トランジスタ 3 8 は、電位 V B L が与えられるノードとビット線 B L 1 との間に接続され、信号 S A E Q 0 をゲートに受ける。N チャネル M O S トランジスタ 3 9 は、電位 V B L が与えられるノードとビット線 / B L 1 との間に接続され、信号 S A E Q 0 をゲートに受ける。

#### 【 0 0 7 4 】

イコライズ回路 2 3 は、信号 S A E Q 0 が活性化されると、センスアンプ 6 3 と直接接続されるビット線対 B L 1 , / B L 1 を電位 V B L にイコライズしてセンスアンプ 6 3 を初期化する。

#### 【 0 0 7 5 】

分離ゲート回路 6 1 は、N チャネル M O S トランジスタ 3 2 , 3 3 を含む。N チャネル M O S トランジスタ 3 2 は、ビット線 B L 1 とビット線 B L 0 1 との間に接続され、信号 B L T G 0 をゲートに受ける。N チャネル M O S トランジスタ 3 3 は、ビット線 / B L 1 とビット線 / B L 0 1 との間に接続され、信号 B L T G 0 をゲートに受ける。

#### 【 0 0 7 6 】

分離ゲート回路 6 1 は、信号 B L T G 0 が非活性化されると、ビット線 B L 1 をビット線 B L 0 1 と電気的に分離し、ビット線 B L / 1 をビット線 / B L 0 1 と電気的に分離する。

#### 【 0 0 7 7 】

分離ゲート回路 6 7 は、N チャネル M O S トランジスタ 4 2 , 4 3 を含む。N チャネル M O S トランジスタ 4 2 は、ビット線 B L 1 とビット線 B L 1 1 との間に接続され、信号 B L T G 1 をゲートに受ける。N チャネル M O S トランジスタ 4 3 は、ビット線 / B L 1 とビット線 / B L 1 1 との間に接続され、信号 B L T G 1 をゲートに受ける。

#### 【 0 0 7 8 】

分離ゲート回路 6 7 は、信号 B L T G 1 が非活性化されると、ビット線 B L 1 をビット線 B L 1 1 と電気的に分離し、ビット線 B L / 1 をビット線 / B L 1 1 と電気的に分離する。

#### 【 0 0 7 9 】

接続回路 6 5 は、N チャネル M O S トランジスタ 5 2 , 5 3 を含む。N チャネル M O S トランジスタ 5 2 は、ローカル I O 線 L I O 0 とビット線 B L 1 との間に接続され、コラム選択線 C S L 1 にゲートが接続される。N チャネル M O S トランジスタ 5 3 は、ローカル I O 線 / L I O 0 とビット線 / B L 1 との間に接続され、コラム選択線 C S L 1 にゲートが接続される。

#### 【 0 0 8 0 】

10

20

30

40

50

接続回路 65 は、コラム選択線 C S L 1 が活性化されると、ビット線 B L 1 をローカル I O 線 L I O 0 と電気的に接続し、ビット線 / B L 1 をローカル I O 線 / L I O 0 と電気的に接続する。

#### 【 0 0 8 1 】

イコライズ回路 21, 25 は、信号 S A E Q 0 に代えてそれぞれ信号 B L E Q 0 , B L E Q 1 を受ける点でイコライズ回路 23 と異なるが、その回路構成は、イコライズ回路 23 と同じであるので、説明は繰返さない。ただし、イコライズ回路 23 がイコライズするビット線対 B L 1 , / B L 1 は、メモリセルアレイが接続されるビット線 B L 0 1 , / B L 0 1 , B L 1 1 , / B L 1 1 に比べて容量が小さいので、イコライズ回路 23 に含まれる 3 つのトランジスタのサイズは、イコライズ回路 21, 25 に含まれるトランジスタのサイズに比べて小さい。10

#### 【 0 0 8 2 】

スペアメモリセル S C e 1 1 0 1 は、スペアワード線 S W L 0 0 とビット線 B L 1 との交点に対応して設けられ、スペアメモリセル S C e 1 1 1 1 は、スペアワード線 S W L 0 1 とビット線 / B L 1 との交点に対応して設けられる。スペアメモリセル S C e 1 1 2 1 は、スペアワード線 S W L 0 2 とビット線 B L 1 との交点に対応して設けられ、スペアメモリセル S C e 1 1 3 1 は、スペアワード線 S W L 0 3 とビット線 / B L 1 との交点に対応して設けられる。スペアメモリセル S C e 1 1 4 1 は、スペアワード線 S W L 0 4 とビット線 B L 1 との交点に対応して設けられ、スペアメモリセル S C e 1 1 5 1 は、スペアワード線 S W L 0 5 とビット線 / B L 1 との交点に対応して設けられる。20

#### 【 0 0 8 3 】

なお、各スペアメモリセル S C e 1 1 0 1 ~ S C e 1 1 5 1 の構成は、メモリセル C e 1 1 0 0 の構成と同じであるので、その説明は繰返さない。20

#### 【 0 0 8 4 】

スペアメモリセル S C e 1 1 0 1 ~ S C e 1 1 5 1 は、メモリセルアレイ M A # 0 0 , M A # 0 1 に含まれるメモリセルの予備用セルとして用いられるほか、センスアンプ 63 に読み出されたデータを一時的に保持するデータ保持回路として用いられる。スペアメモリセル S C e 1 1 0 1 ~ S C e 1 1 5 1 は、メモリセル C e 1 1 0 1 , C e 1 1 1 1 に比べてセンスアンプ 63 に近接して配置されているので、センスアンプ 63 からのデータの書き込みおよびセンスアンプ 63 へのデータの読み出しが高速に行なわれる。30

#### 【 0 0 8 5 】

センスアンプによってローカル I O 線 L I O 0 , / L I O 0 に読み出されたデータは、ゲート回路 G # 0 を介してグローバル I O 線 G I O , / G I O に読み出され、入出力回路 14 に伝達される。ゲート回路 G # 0 は、N チャネル M O S トランジスタ 11 , 12 を含む。N チャネル M O S トランジスタ 11 は、ローカル I O 線 L I O 0 とグローバル I O 線 G I O との間に接続され、信号 I O S W 0 をゲートに受ける。N チャネル M O S トランジスタ 12 は、ローカル I O 線 / L I O 0 とグローバル I O 線 / G I O との間に接続され、信号 I O S W 0 をゲートに受ける。30

#### 【 0 0 8 6 】

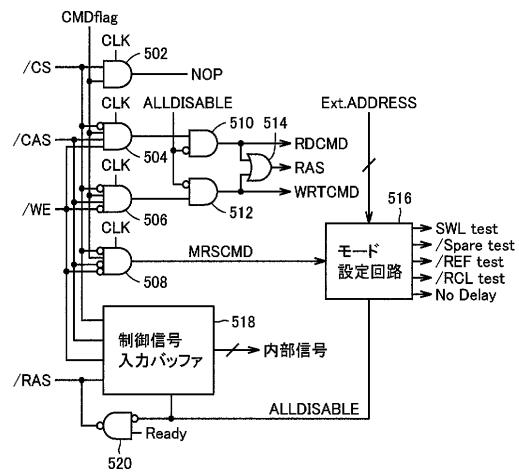

図 4 ~ 図 8 は、図 1 に示す制御回路 2 の構成を示す回路図である。説明の便宜上、図 4 ~ 図 8 においては、バンク 0 のメモリブロック B L O C K 0 に対応する部分のみが示され、以下では、特に必要がないかぎり、バンクおよびメモリブロックに対応する符号は付せず説明を行なう。40

#### 【 0 0 8 7 】

図 4 を参照して、制御回路 2 は、A N D ゲート 5 0 2 ~ 5 1 2 と、O R ゲート 5 1 4 と、モード設定回路 5 1 6 と、制御信号入力バッファ 5 1 8 と、N A N D ゲート 5 2 0 とを含む。

#### 【 0 0 8 8 】

A N D ゲート 5 0 2 は、クロック信号 C L K に同期して動作し、内部フラグ C M D f 1 a g およびメモリ制御装置 8 からコマンド C M D として受けるチップセレクト信号 / C S の50

論理積を演算し、その演算結果を信号 N O P として出力する。ここで、内部フラグ C M D f l a g は、メモリ制御装置 8 からコマンド C M D を受付ける状態にあるときに H (論理ハイ) レベルとなる信号である。A N D ゲート 5 0 4 は、クロック信号 C L K に同期して動作し、チップセレクト信号 / C S の反転信号、内部フラグ C M D f l a g 、およびメモリ制御装置 8 からコマンド C M D として受けるコラムアドレスストローブ信号 / C A S 、ライトイネーブル信号 / W E の論理積を演算し、その演算結果を A N D ゲート 5 1 0 へ出力する。

#### 【 0 0 8 9 】

A N D ゲート 5 0 6 は、クロック信号 C L K に同期して動作し、チップセレクト信号 / C S の反転信号、内部フラグ C M D f l a g 、コラムアドレスストローブ信号 / C A S 、およびライトイネーブル信号 / W E の反転信号の論理積を演算し、その演算結果を A N D ゲート 5 1 2 へ出力する。A N D ゲート 5 0 8 は、クロック信号 C L K に同期して動作し、チップセレクト信号 / C S の反転信号、内部フラグ C M D f l a g 、コラムアドレスストローブ信号 / C A S の反転信号およびライトイネーブル信号 / W E の反転信号の論理積を演算し、その演算結果をモードセレクトコマンド M R S C M D としてモード設定回路 5 1 6 へ出力する。

#### 【 0 0 9 0 】

A N D ゲート 5 1 0 は、モード設定回路 5 1 6 から出力される信号 A L L D I S A B L E の反転信号および A N D ゲート 5 0 4 からの出力信号の論理積を演算し、その演算結果をリードコマンド R D C M D として出力する。A N D ゲート 5 1 2 は、信号 A L L D I S A B L E の反転信号および A N D ゲート 5 0 6 からの出力信号の論理積を演算し、その演算結果をライトコマンド W R T C M D として出力する。O R ゲート 5 1 4 は、A N D ゲート 5 1 0 , 5 1 2 の出力信号の論理和を演算し、その演算結果を内部信号 R A S として出力する。

#### 【 0 0 9 1 】

制御信号入力バッファ 5 1 8 は、信号 A L L D I S A B L E が H レベルのとき活性化し、チップセレクト信号 / C S 、コラムアドレスストローブ信号 / C A S 、ライトイネーブル信号 / W E およびロウアドレスストローブ信号 / R A S を受け、半導体記憶装置 1 を従来の S D R A M として機能させるための各種内部信号を出力する。すなわち、信号 A L L D I S A B L E が H レベルのときは、リードコマンド R D C M D 、ライトコマンド W R T C M D および内部信号 R A S は発生せず、一方、制御信号入力バッファ 5 1 8 が活性化されて、半導体記憶装置 1 は従来の S D R A M として動作する。

#### 【 0 0 9 2 】

モード設定回路 5 1 6 は、モードセレクトコマンド M R S C M D が H レベルのとき、メモリ制御装置 8 からモード設定信号として受けるアドレス信号 A D D R E S S に応じて半導体記憶装置 1 のモードを設定する。そして、モード設定回路 5 1 6 は、その設定したモードに応じて、信号 S W L \_ t e s t , / S p a r e \_ t e s t , / R E F \_ t e s t , / R C L \_ t e s t 、信号 N o \_ D e l a y および信号 A L L D I S A B L E を出力する。

#### 【 0 0 9 3 】

信号 S W L \_ t e s t , / S p a r e \_ t e s t , / R E F \_ t e s t , / R C L \_ t e s t は、テスト用の信号であって、後ほど説明する。信号 N o \_ D e l a y は、後述するリード信号 R D の発生を 1 クロック早めるための信号である。信号 A L L D I S A B L E は、この半導体記憶装置 1 を従来の半導体記憶装置として動作させるための信号である。

#### 【 0 0 9 4 】

N A N D ゲート 5 2 0 は、信号 A L L D I S A B L E の反転信号および内部信号 R e a d y の論理積を演算し、その演算結果を反転して信号 / R e a d y を出力する。そして、信号 A L L D I S A B L E が L レベルのとき、N A N D ゲート 5 2 0 の出力信号は、半導体記憶装置 1 が従来機能として動作するときにロウアドレスストローブ信号 / R A S が入力される端子を介して、外部のメモリ制御装置 8 へ出力される。すなわち、半導体記憶装置 1 においては、信号 / R e a d y 用の出力端子と、半導体記憶装置 1 が従来機能として動

10

20

30

40

50

作するときのロウアドレスストローブ信号 / R A S の入力端子とが共用される。

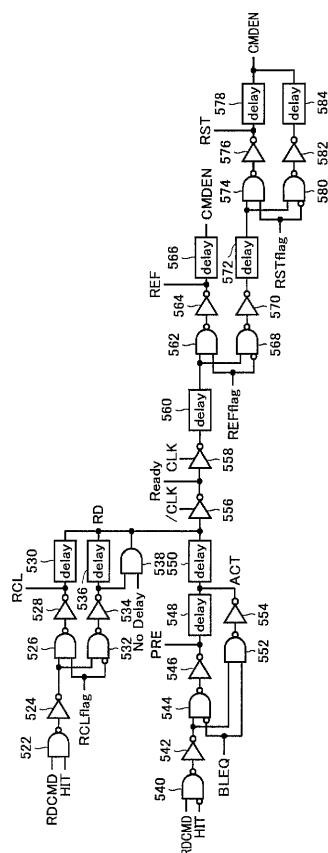

【 0 0 9 5 】

図 5 を参照して、制御回路 2 は、リードコマンド R D C M D および内部信号 H I T の論理積を演算し、その演算結果を反転した信号を出力する N A N D ゲート 5 2 2 と、 N A N D ゲート 5 2 2 からの出力信号を反転した信号を出力するインバータ 5 2 4 とをさらに含む。

【 0 0 9 6 】

また、制御回路 2 は、インバータ 5 2 4 からの出力信号および内部フラグ R C L f 1 a g の論理積を演算し、その演算結果を反転した信号を出力する N A N D ゲート 5 2 6 と、 N A N D ゲート 5 2 6 からの出力信号を反転してリコール信号 R C L を出力するインバータ 5 2 8 と、インバータ 5 2 8 からの出力信号を 1 クロック遅延してリード信号 R D を出力する遅延回路 5 3 0 とを含む。 10

【 0 0 9 7 】

また、さらに、制御回路 2 は、インバータ 5 2 4 からの出力信号および内部フラグ R C L f 1 a g の反転信号の論理積を演算し、その演算結果を反転した信号を出力する N A N D ゲート 5 3 2 と、 N A N D ゲート 5 3 2 からの出力信号を反転した信号を出力するインバータ 5 3 4 と、インバータ 5 3 4 からの出力信号を 1 クロック遅延してリード信号 R D を出力する遅延回路 5 3 6 と、インバータ 5 3 4 からの出力信号および信号 N o \_ D e l a y の論理積を演算し、その演算結果をリード信号 R D として出力する A N D ゲート 5 3 8 とを含む。 20

【 0 0 9 8 】

また、さらに、制御回路 2 は、内部信号 H I T の反転信号およびリードコマンド R D C M D の論理積を演算し、その演算結果を反転した信号を出力する N A N D ゲート 5 4 0 と、 N A N D ゲート 5 4 0 からの出力信号を反転した信号を出力するインバータ 5 4 2 とを含む。 30

【 0 0 9 9 】

また、さらに、制御回路 2 は、信号 B L E Q の反転信号およびインバータ 5 4 2 からの出力信号の論理積を演算し、その演算結果を反転した信号を出力する N A N D ゲート 5 4 4 と、 N A N D ゲート 5 4 4 からの出力信号を反転してプリチャージ信号 P R E を出力するインバータ 5 4 6 と、インバータ 5 4 6 からの出力信号を 2 クロック遅延してアクト信号 A C T を出力する遅延回路 5 4 8 と、インバータ 5 4 2 からの出力信号および信号 B L E Q の論理積を演算し、その演算結果を反転した信号を出力する N A N D ゲート 5 5 2 と、 N A N D ゲート 5 5 2 からの出力信号を反転してアクト信号 A C T を出力するインバータ 5 5 4 と、アクト信号 A C T を 2 クロック遅延してリード信号 R D を出力する遅延回路 5 5 0 とを含む。 40

【 0 1 0 0 】

また、さらに、制御回路 2 は、クロック信号 C L K に相補なクロック信号 / C L K に同期して動作し、リード信号 R D を反転して信号 R e a d y を出力するインバータ 5 5 6 と、クロック信号 C L K に同期して動作し、インバータ 5 5 6 からの出力信号を反転した信号を出力するインバータ 5 5 8 と、インバータ 5 5 8 からの出力信号を 1 クロック遅延した信号を出力する遅延回路 5 6 0 とを含む。 40

【 0 1 0 1 】

また、さらに、制御回路 2 は、遅延回路 5 6 0 からの出力信号および内部フラグ R E F f 1 a g の論理積を演算し、その演算結果を反転した信号を出力する N A N D ゲート 5 6 2 と、 N A N D ゲート 5 6 2 からの出力信号を反転してリフレッシュ信号 R E F を出力するインバータ 5 6 4 と、インバータ 5 6 4 からの出力信号を 3 クロック遅延して内部信号 C M D E N を出力する遅延回路 5 6 6 とを含む。 50

【 0 1 0 2 】

また、さらに、制御回路 2 は、遅延回路 5 6 0 からの出力信号および内部フラグ R E F f 1 a g の反転信号の論理積を演算し、その演算結果を反転した信号を出力する N A N D ゲ

ート 568 と、NAND ゲート 568 からの出力信号を反転した信号を出力するインバータ 570 と、インバータ 570 からの出力信号を 1 クロック遅延した信号を出力する遅延回路 572 とを含む。

#### 【0103】

また、さらに、制御回路 2 は、遅延回路 572 からの出力信号および内部フラグ RST flag の論理積を演算し、その演算結果を反転した信号を出力する NAND ゲート 574 と、NAND ゲート 574 からの出力信号を反転してリストア信号 RST を出力するインバータ 576 と、インバータ 576 からの出力信号を 2 クロック遅延して内部信号 CMDEN を出力する遅延回路 578 とを含む。

#### 【0104】

また、さらに、制御回路 2 は、遅延回路 572 からの出力信号および内部フラグ RST flag の反転信号の論理積を演算し、その演算結果を反転した信号を出力する NAND ゲート 580 と、NAND ゲート 580 からの出力信号を反転した信号を出力するインバータ 582 と、インバータ 582 からの出力信号を 2 クロック遅延して内部信号 CMDEN を出力する遅延回路 584 とを含む。

#### 【0105】

内部信号 HIT は、図 1 に示したロウアドレスレジスタ 7 から出力される信号であって、メモリ制御装置 8 からアドレス信号 ADDRESS によって指定されたロウアドレスに対応するワード線が既に選択されているときに H レベルとなる信号である。なお、ロウアドレスレジスタ 7 の構成については、後ほど詳しく説明する。

#### 【0106】

リコール信号 RCL は、リコール動作を指示する信号である。リコール動作とは、データ保持回路として用いられるスペアメモリセルに一時的に保持されているデータをセンスアンプに再度読出す動作をいう。

#### 【0107】

リード信号 RD は、センスアンプに読出されたデータの外部への出力を指示する信号である。リード信号 RD が H レベルになると、その半クロック後に信号 Ready が L (論理 0) レベルとなり、H レベルの信号 /Ready がメモリ制御装置 8 へ出力される。これによって、メモリ制御装置 8 は、データ出力タイミングを認識することができ、信号 /Ready が H レベルになった後、データ DATA がメモリ制御装置 8 へ出力される。

#### 【0108】

プリチャージ信号 PRE は、ビット線対のプリチャージ動作を指示する信号である。アクト信号 ACT は、指定されたロウアドレスに対するワード線を活性化する信号である。

#### 【0109】

リフレッシュ信号 REF は、リフレッシュ動作を指示する信号である。実施の形態 1 による半導体記憶装置 1 においては、リフレッシュ動作は、2 段階で実行される。すなわち、リフレッシュ動作の実行が指示されると、リフレッシュ対象のメモリセルからセンスアンプにデータが読出されて増幅された後、予め指定されるスペアワード線に接続されるスペアメモリセルに一時的にそのデータが格納され、一旦リフレッシュ動作は終了する。そして、第 2 段階として、後述するリストア動作が実行され、スペアメモリセルに一時的に格納していたデータがセンスアンプに読出されて元のメモリセルに書き込まれる。

#### 【0110】

このようにリフレッシュ動作を 2 段階にわけたのは、以下の理由による。半導体記憶装置 1 は、ビット線のプリチャージ、データの読み出し、センスアンプによる増幅および元のメモリセルへの書き込みからなる一連のリフレッシュ動作中にコマンド CMD を受付けることはできない。これは、半導体記憶装置 1 の外部からみれば、コマンドが受けられない待ち時間となる。そこで、リフレッシュ動作を 2 段階にわけ、リフレッシュ動作により発生する待ち時間が短縮されている。

#### 【0111】

また、一時的なデータ保持回路として、センスアンプに近接して配置されるスペアメモリ

10

20

30

40

50

セルが用いられるため、スペアメモリセルに対するデータの読書きは高速である。さらに、新たなデータ保持回路をセンスアンプ近傍に備える必要がないので、エリアペナルティが抑えられる。

【0112】

リストア信号RSTは、リストア動作を指示する信号である。リストア動作とは、リフレッシュ信号REFによってスペアメモリセルに一時的に保持されたデータを元のメモリセルへ書戻す動作をいう。

【0113】

なお、NANDゲート544, 552に入力される信号BLEQは、メモリセルアレイに接続されるビット線対をイコライズする信号であって、該当するメモリブロックのプリチャージ信号PREによってHレベルとなり、アクト信号ACTによってLレベルとなる。10

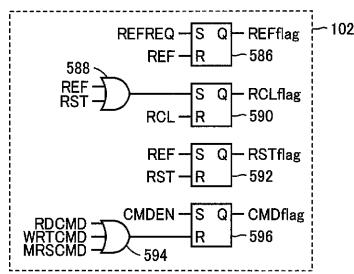

【0114】

図6を参照して、制御回路2は、内部フラグセット回路102をさらに含む。内部フラグセット回路102は、SRフリップフロップ回路586, 590, 592, 596と、ORゲート588, 594とからなる。

【0115】

SRフリップフロップ回路586は、後述するリフレッシュ要求信号REFREQおよびリフレッシュ信号REFをそれぞれセット入力およびリセット入力に受け、内部フラグREFflagを出力する。

【0116】

ORゲート588は、リフレッシュ信号REFおよびリストア信号RSTの論理和を演算し、その演算結果をSRフリップフロップ回路590へ出力する。SRフリップフロップ回路590は、ORゲート588からの出力信号およびリコール信号RCLをそれぞれセット入力およびリセット入力に受け、内部フラグRCLflagを出力する。20

【0117】

SRフリップフロップ回路592は、リフレッシュ信号REFおよびリストア信号RSTをそれぞれセット入力およびリセット入力に受け、内部フラグRSTflagを出力する。。

【0118】

ORゲート594は、リードコマンドRDCMD、ライトコマンドWRTCMDおよびモードセレクトコマンドMRSCMDの論理和を演算し、その演算結果をSRフリップフロップ回路596へ出力する。SRフリップフロップ回路596は、内部信号CMDENおよびORゲート588からの出力信号をそれぞれセット入力およびリセット入力に受け、内部フラグCMDflagを出力する。30

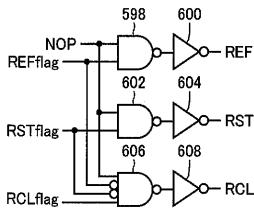

【0119】

図7を参照して、制御回路2は、信号NOPおよび内部フラグREFflagの論理積を演算し、その演算結果を反転した信号を出力するNANDゲート598と、NANDゲート598からの出力信号を反転してリフレッシュ信号REFを出力するインバータ600とをさらに含む。

【0120】

また、制御回路2は、信号NOPおよび内部フラグRSTflagの論理積を演算し、その演算結果を反転した信号を出力するNANDゲート602と、NANDゲート602からの出力信号を反転してリストア信号RSTを出力するインバータ604とを含む。40

【0121】

さらに、制御回路2は、信号NOP、内部フラグREFflagの反転信号、内部フラグRSTflagの反転信号および内部フラグRCLflagの論理積を演算し、その演算結果を反転した信号を出力するNANDゲート606と、NANDゲート606からの出力信号を反転してリコール信号RCLを出力するインバータ608とを含む。

【0122】

この回路は、メモリ制御装置8からコマンドCMDによる動作指令を受けておらず、かつ50

、内部フラグ C M D f l a g が H レベルにあるとき、すなわち信号 N O P が H レベルとなるノーオペレーション状態のときに活性化される。

【 0 1 2 3 】

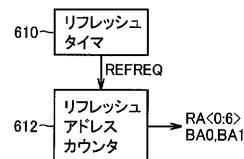

図 8 を参照して、制御回路 2 は、リフレッシュタイム 6 1 0 と、リフレッシュアドレスカウンタ 6 1 2 とをさらに含む。

【 0 1 2 4 】

リフレッシュタイム 6 1 0 は、所定のリフレッシュ周期でリフレッシュ動作を要求するリフレッシュ要求信号 R E F R E Q を発生し、リフレッシュアドレスカウンタ 6 1 2 へ出力する。リフレッシュアドレスカウンタ 6 1 2 は、リフレッシュ要求信号 R E F R E Q に応じてリフレッシュカウンタをカウントアップし、リフレッシュ対象のメモリセル行を選択するためのロウアドレス信号 R A < 0 : 6 > およびバンクアドレス信号 B A 0 , B A 1 を発生する。

10

【 0 1 2 5 】

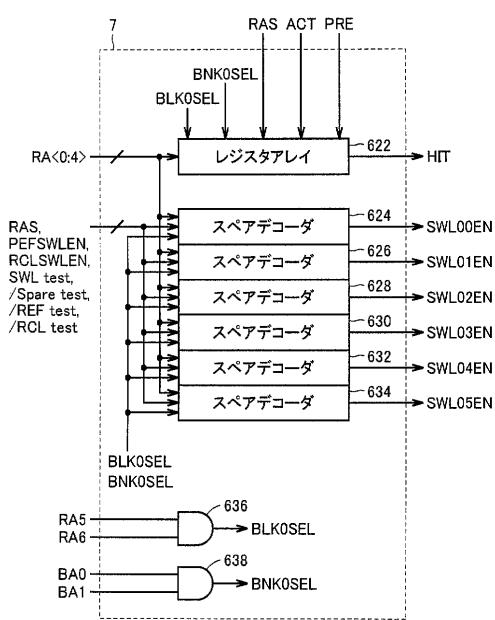

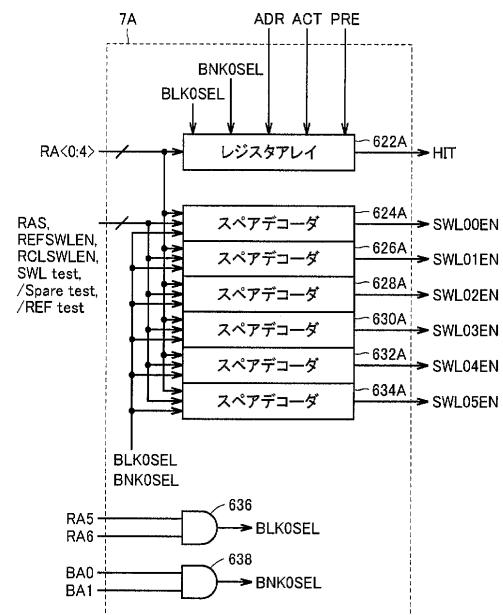

図 9 は、図 1 に示すロウアドレスレジスタ 7 の機能ブロック図である。ここで、ロウアドレスレジスタ 7 は、メモリセルアレイ 6 の各バンクのメモリブロック毎に設けられ、図 9 においては、バンク 0 のメモリブロック B L O C K 0 に対応するロウアドレスレジスタについて示されている。

【 0 1 2 6 】

図 9 を参照して、ロウアドレスレジスタ 7 は、レジスタアレイ 6 2 2 と、スペアワード線 S W L 0 0 ~ S W L 0 5 にそれぞれ対応して設けられるスペアデコーダ 6 2 4 ~ 6 3 4 と、A N D ゲート 6 3 6 , 6 3 8 とを含む。

20

【 0 1 2 7 】

レジスタアレイ 6 2 2 は、A C T 信号により活性化されたワード線に対応するロウアドレスを内部に保持する。レジスタアレイ 6 2 2 は、アクト信号 A C T を受けると、そのアクト信号 A C T に応じて活性化されるワード線に対応するロウアドレス信号 R A < 0 : 4 > を制御回路 2 から受け、次にプリチャージ信号 P R E を受けるまで内部に保持する。そして、リードコマンド R D C M D およびライトコマンド W R T C M D の論理和である内部信号 R A S を受けると、その内部信号 R A S とともに受ける読出または書込対象のロウアドレス信号 R A < 0 : 4 > を、保持しているロウアドレスと比較し、一致すると、内部信号 H I T を H レベルで出力する。

30

【 0 1 2 8 】

スペアデコーダ 6 2 4 ~ 6 3 4 は、それぞれに対応するスペアワード線 S W L 0 0 ~ S W L 0 5 の動作モードを設定し、スペアワード線 S W L 0 0 ~ S W L 0 5 それぞれに対応する活性化信号 S W L 0 0 E N ~ S W L 0 5 E N を出力する。各スペアワード線に対して、スペアワード線をワード線の予備線として使用する第 1 の動作モード、リフレッシュ動作に伴って読出されたデータの一時記憶メモリセルとして使用する第 2 の動作モード、およびリコール動作用のデータの一時記憶メモリセルとして使用する第 3 の動作モードのいずれかのモードが設定される。

【 0 1 2 9 】

スペアデコーダ 6 2 4 ~ 6 3 4 は、対応するスペアワード線が第 1 の動作モードとして使用されるとき、対象のワード線に対応するロウアドレスが内部設定され、内部信号 R A S とともに受ける読出または書込対象のロウアドレス信号 R A < 0 : 4 > を、内部設定されたロウアドレスと比較し、一致していれば、対応する活性化信号 S W L 0 E N ~ S W L 5 E N を H レベルで出力する。

40

【 0 1 3 0 】

また、スペアデコーダ 6 2 4 ~ 6 3 4 は、対応するスペアワード線が第 2 の動作モードとして使用されるとき、信号 R E F S W L E N が活性化されると、対応する活性化信号 S W L 0 E N ~ S W L 5 E N を H レベルで出力する。ここで、信号 R E F S W L E N は、リフレッシュ動作に伴ってセンスアンプに読出されたデータをスペアワード線に接続されるスペアメモリセルに書込むとき、およびスペアメモリセルに書込まれたデータを元のメモリ

50

セルに復帰するために再びセンスアンプに読出すときに活性化される信号であって、制御回路2においてリフレッシュ信号REFまたはリストア信号RSTを遅延して生成される。

### 【0131】

さらに、スペアデコーダ624～634は、対応するスペアワード線が第3の動作モードとして使用されるとき、信号RCLSWLENが活性化されると、対応する活性化信号SWL0EN～SWL5ENをHレベルで出力する。ここで、信号RCLSWLENは、リコール動作において、センスアンプに読出されたデータをスペアワード線に接続されるスペアメモリセルに書込むとき、およびスペアメモリセルに書込まれたデータを再びセンスアンプに読出すときに活性化される信号であって、制御回路2において信号SAEQが活性化される直前に活性化される。10

### 【0132】

各スペアデコーダ624～634においては、その動作モードを設定する前に各動作モードをテストすることができる。信号SWL<sub>test</sub>, /Spare<sub>test</sub>, /REF<sub>test</sub>, /RCL<sub>test</sub>は、各動作モードをテストするための信号であって、信号SWL<sub>test</sub>が活性化されているとき、信号/Spare<sub>test</sub>, /REF<sub>test</sub>, /RCL<sub>test</sub>が活性化されると、それぞれ第1, 第2および第3の動作モードの動作テストを行うことができる。

### 【0133】

ANDゲート636は、ロウアドレス信号RA5, RA6の論理積を演算し、その演算結果をブロック選択信号BLK0SELとして出力する。また、ANDゲート638は、バンクアドレス信号BA0, BA1の論理積を演算し、その演算結果をバンク選択信号BNK0SELとして出力する。20

### 【0134】

なお、図9においては、バンク0のメモリブロックBLOCK0に対応するロウアドレスレジスタについて図示されているが、たとえば、バンク1のメモリブロックBLOCK1に対応するロウアドレスレジスタにおいては、ANDゲート636は、ロウアドレス信号RA5の反転信号およびロウアドレス信号RA6の論理積を演算し、その演算結果をブロック選択信号BLK1SELとして出力し、ANDゲート638は、バンクアドレス信号BA0の反転信号およびバンクアドレス信号BA1の論理積を演算し、その演算結果をバンク選択信号BNK1SELとして出力する。30

### 【0135】

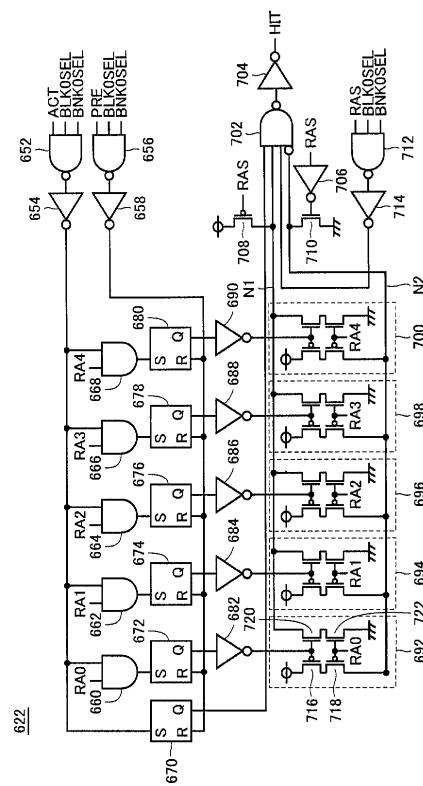

図10は、図9に示すレジスタアレイ622の構成を示す回路図である。

図10を参照して、レジスタアレイ622は、NANDゲート652, 656と、インバータ654, 658と、ANDゲート660～668と、SRフリップフロップ回路670～680と、インバータ682～690とを含む。

### 【0136】

NANDゲート652は、アクト信号ACT、ブロック選択信号BLK0SELおよびバンク選択信号BNK0SELの論理積を演算し、その演算結果を反転した信号を出力する。インバータ654は、NANDゲート652からの出力信号を反転した信号を出力する。ANDゲート660～668は、それぞれロウアドレス信号RA0～RA4およびインバータ654からの出力信号の論理積を演算し、その演算結果をそれぞれSRフリップフロップ回路672～680へ出力する。40

### 【0137】

NANDゲート656は、プリチャージ信号PRE、ブロック選択信号BLK0SELおよびバンク選択信号BNK0SELの論理積を演算し、その演算結果を反転した信号を出力する。インバータ658は、NANDゲート656からの出力信号を反転した信号を出力する。

### 【0138】

SRフリップフロップ回路670は、インバータ654からの出力信号をセット入力に受50

ける。SRフリップフロップ回路672～680は、ANDゲート660～668からの出力信号をそれぞれセット入力に受ける。SRフリップフロップ回路670～680は、いずれもインバータ658からの出力信号をリセット入力に受け、その信号に応じて内部状態がリセットされる。インバータ682～690は、それぞれSRフリップフロップ回路672～680からの出力信号を反転した信号を出力する。

## 【0139】

また、レジスタアレイ622は、PチャネルMOSトランジスタ708と、インバータ706と、NチャネルMOSトランジスタ710と、ノードN1，N0の間に並列に接続されるアドレスビット比較回路692～700とをさらに含む。

## 【0140】

PチャネルMOSトランジスタ708は、電源ノードおよびノードN1に接続され、内部信号RASをゲートに受ける。インバータ706は、内部信号RASを反転した信号を出力する。NチャネルMOSトランジスタ710は、ノードN0および接地ノードに接続され、インバータ706からの出力信号をゲートに受ける。

## 【0141】

アドレスビット比較回路692は、PチャネルMOSトランジスタ716，718と、NチャネルMOSトランジスタ720，722とを含む。PチャネルMOSトランジスタ716，718は、電源ノードとノードN0との間に直列に接続され、インバータ682からの出力信号およびロウアドレス信号RA0をそれぞれゲートに受ける。NチャネルMOSトランジスタ720，722は、ノードN1と接地ノードとの間に直列に接続され、インバータ682からの出力信号およびロウアドレス信号RA0をそれぞれゲートに受ける。

## 【0142】

アドレスビット比較部694～700は、入力されるロウアドレス信号RA0に代えてロウアドレス信号RA1～RA4がそれぞれ与えられ、インバータ682からの出力信号に代えてインバータ684～690からの出力信号がそれぞれ与えられる点においてアドレスビット比較部692と異なるが、内部の構成は、アドレスビット比較部692と同じであるので、説明は繰返さない。

## 【0143】

さらに、レジスタアレイ622は、NANDゲート702，712と、インバータ704，714とを含む。

## 【0144】

NANDゲート712は、内部信号RAS、ブロック選択信号BLK0SELおよびバンク選択信号BNK0SELの論理積を演算し、その演算結果を反転した信号を出力する。インバータ714は、NANDゲート712からの出力信号を反転してNANDゲート702へ出力する。

## 【0145】

NANDゲート702は、SRフリップフロップ回路670からの出力信号、ノードN1上の信号、インバータ714からの出力信号およびノードN0上の信号を反転した信号の論理積を演算し、その演算結果を反転した信号を出力する。インバータ704は、NANDゲート702からの出力信号を反転して内部信号HITを出力する。

## 【0146】

以下、このレジスタアレイ622の動作について簡単に説明する。メモリ制御装置8から入力されたアドレス信号ADDRESSおよびコマンドCMDに基づいて、バンク0のメモリブロック0が選択され、アクト信号ACTが活性化されると、SRフリップフロップ回路672～680は、そのアドレス信号ADDRESSによって指定されたロウアドレス信号RA<0：4>を保持する。これによって、活性化されたワード線のロウアドレスがレジスタアレイ622に記憶される。

## 【0147】

そして、その後、メモリ制御装置8から入力されたアドレス信号ADDRESSおよびコ

10

20

30

40

50

マンドCMDに基づいて、リードコマンドRDCMDまたはライトコマンドWRTCMDが活性化されると、アドレスビット比較部692～700は、アドレス信号ADDRESSESによって指定されたロウアドレス信号RA<0：4>をSRフリップフロップ回路672～680が保持するロウアドレスと比較する。

#### 【0148】

ロウアドレスが一致するときは、対象のワード線は既に選択されているので、レジスタアレイ622は、内部信号HITをHレベルで出力する。なお、SRフリップフロップ回路672～680は、選択されているワード線が非活性化され、対応するビット線対がプリチャージされるプリチャージ信号PREが活性化されると、内部に保持しているロウアドレスをリセットする。

10

#### 【0149】

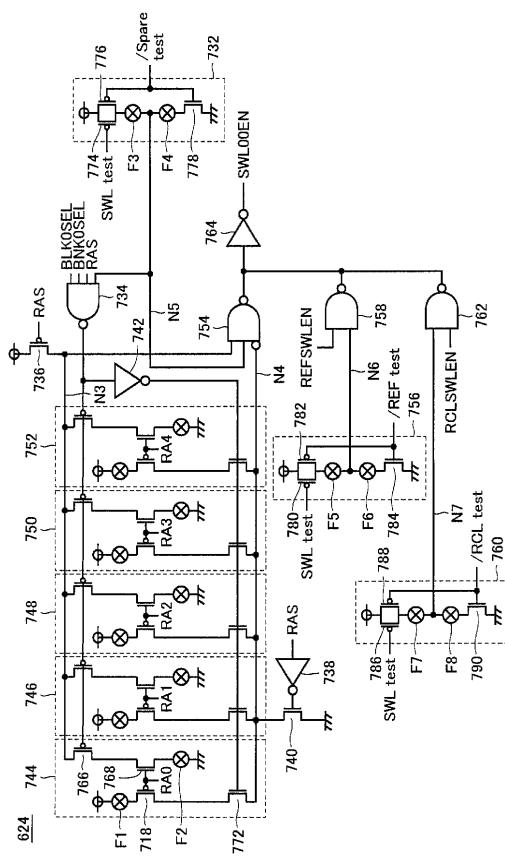

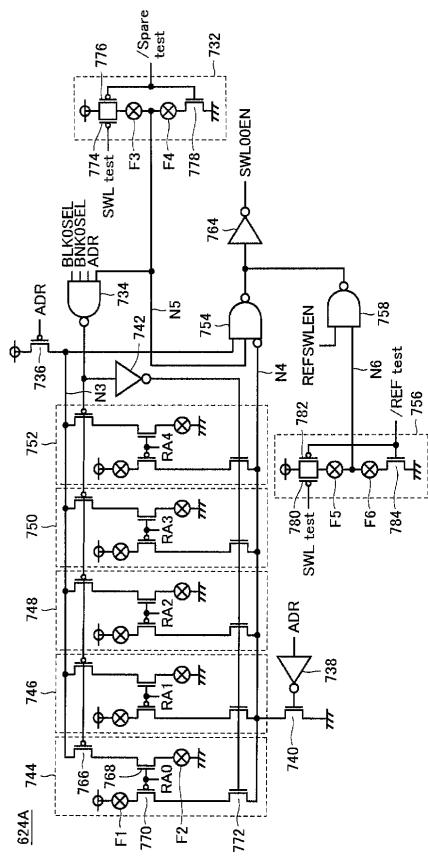

図11は、図9に示すスペアデコーダ624の構成を示す回路図である。

図11を参照して、スペアデコーダ624は、第1動作モード設定部732と、第2動作モード設定部756と、第3動作モード設定部760とを含む。

#### 【0150】

第1動作モード設定部732は、PチャネルMOSトランジスタ774, 776と、NチャネルMOSトランジスタ778と、ヒューズF3, F4とを含む。PチャネルMOSトランジスタ774, 776は、電源ノードおよびヒューズF3に接続され、信号SWL<sub>test</sub>, /Spare<sub>test</sub>をそれぞれゲートに受ける。NチャネルMOSトランジスタ778は、ヒューズF4および接地ノードに接続され、信号/Spare<sub>test</sub>をゲートに受ける。ヒューズF3は、PチャネルMOSトランジスタ774, 776とノードN5との間に接続され、ヒューズF4は、NチャネルMOSトランジスタ778とノードN5との間に接続される。

20

#### 【0151】

第2動作モード設定部756は、PチャネルMOSトランジスタ780, 782と、NチャネルMOSトランジスタ784と、ヒューズF5, F6とを含む。PチャネルMOSトランジスタ780, 782は、電源ノードおよびヒューズF5に接続され、信号SWL<sub>test</sub>, /REF<sub>test</sub>をそれぞれゲートに受ける。NチャネルMOSトランジスタ784は、ヒューズF6および接地ノードに接続され、信号/REF<sub>test</sub>をゲートに受ける。ヒューズF5は、PチャネルMOSトランジスタ780, 782とノードN6との間に接続され、ヒューズF6は、NチャネルMOSトランジスタ784とノードN6との間に接続される。

30

#### 【0152】

第3動作モード設定部760は、PチャネルMOSトランジスタ786, 788と、NチャネルMOSトランジスタ790と、ヒューズF7, F8とを含む。PチャネルMOSトランジスタ786, 788は、電源ノードおよびヒューズF7に接続され、信号SWL<sub>test</sub>, /RCL<sub>test</sub>をそれぞれゲートに受ける。NチャネルMOSトランジスタ790は、ヒューズF8および接地ノードに接続され、信号/RCL<sub>test</sub>をゲートに受ける。ヒューズF7は、PチャネルMOSトランジスタ786, 788とノードN7との間に接続され、ヒューズF8は、NチャネルMOSトランジスタ790とノードN7との間に接続される。

40

#### 【0153】

第1モード設定部732は、スペアワード線SWL00を一般のワード線の予備線として使用する第1の動作モードを設定する。第2モード設定部756は、スペアワード線SWL00をリフレッシュ動作に伴って読出されたデータの一時記憶メモリセルとして使用する第2の動作モードを設定する。第3モード設定部760は、スペアワード線SWL00をリコール動作用のデータの一時記憶メモリセルとして使用する第3の動作モードを設定する。

#### 【0154】

すなわち、スペアワード線SWL00を第1の動作モードとして使用するときは、ヒュー

50

ズ F 3 を除くヒューズ F 4 ~ F 8 が切断され、スペアワード線 SWL 0 0 は、一般的のワード線の予備線として使用される。また、スペアワード線 SWL 0 0 を第 2 の動作モードとして使用するときは、ヒューズ F 5 を除く各ヒューズが切断され、スペアワード線 SWL 0 0 は、リフレッシュ動作時の一時記憶メモリセルとして使用される。さらに、スペアワード線 SWL 0 0 を第 3 の動作モードとして使用するときは、ヒューズ F 7 を除く各ヒューズが切断され、スペアワード線 SWL 0 0 は、リコール動作時の一時記憶メモリセルとして使用される。

#### 【 0 1 5 5 】

なお、第 1 ~ 第 3 モード設定部 732, 756, 760 の各々においては、上述したように、ヒューズを切断する前に、信号 SWL\_test, /Spare\_test, /REF\_test, /RCL\_test を入力することによって、事前に動作テストが可能となっている。10

#### 【 0 1 5 6 】

また、スペアデコーダ 624 は、NAND ゲート 734, 754, 758, 762 と、P チャネル MOS トランジスタ 736 と、N チャネル MOS トランジスタ 740 と、インバータ 738, 742, 764 と、置換ワード線設定部 744 ~ 752 とを含む。

#### 【 0 1 5 7 】

NAND ゲート 734 は、ブロック選択信号 BLK0SEL、バンク選択信号 BNK0SEL、内部信号 RAS およびノード N5 上の信号の論理積を演算し、その演算結果を反転した信号を出力する。インバータ 742 は、NAND ゲート 734 からの出力信号を反転した信号を出力する。P チャネル MOS トランジスタ 736 は、電源ノードおよびノード N3 に接続され、内部信号 RAS をゲートに受ける。インバータ 738 は、内部信号 RAS を反転した信号を出力する。N チャネル MOS トランジスタ 740 は、ノード N4 および接地ノードに接続され、インバータ 738 からの出力信号をゲートに受ける。20

#### 【 0 1 5 8 】

NAND ゲート 754 は、ノード N3 ~ N5 上の信号の論理積を演算し、その演算結果を反転した信号を出力する。すなわち、NAND ゲート 754 は、スペアワード線 SWL 0 0 が第 1 の動作モードとして使用されるとき、入力されたロウアドレスが置換対象のワード線に対応するロウアドレスと一致すると、内部信号 RAS が入力されたタイミングで L レベルの信号を出力する。30

#### 【 0 1 5 9 】

NAND ゲート 758 は、ノード N6 上の信号および信号 REFSWLEN の論理積を演算し、その演算結果を反転した信号を出力する。すなわち、NAND ゲート 758 は、スペアワード線 SWL 0 0 が第 2 の動作モードとして使用されるとき、信号 REFSWLEN を受けたタイミングで L レベルの信号を出力する。NAND ゲート 762 は、ノード N7 上の信号および信号 RCLSWLEN の論理積を演算し、その演算結果を反転した信号を出力する。すなわち、NAND ゲート 762 は、スペアワード線 SWL 0 0 が第 3 の動作モードとして使用されるとき、信号 RCLSWLEN を受けたタイミングで L レベルの信号を出力する。インバータ 764 は、NAND ゲート 754, 758, 762 出力信号のいずれかが L レベルであるとき、活性化信号 SWLOEN を H レベルで出力する。40

#### 【 0 1 6 0 】

置換ワード線設定部 744 は、P チャネル MOS トランジスタ 766, 770 と、N チャネル MOS トランジスタ 768, 772 と、ヒューズ F1, F2 とを含む。

#### 【 0 1 6 1 】

P チャネル MOS トランジスタ 766 および N チャネル MOS トランジスタ 768 は、ノード N3 とヒューズ F2 との間に直列に接続され、NAND ゲート 734 からの出力信号およびロウアドレス信号 RAO をそれぞれゲートに受ける。P チャネル MOS トランジスタ 770 および N チャネル MOS トランジスタ 772 は、ヒューズ F1 とノード N4 との間に直列に接続され、ロウアドレス信号 RAO およびインバータ 742 からの出力信号をそれぞれゲートに受ける。ヒューズ F1 は、電源ノードと P チャネル MOS トランジスタ50

770との間に接続され、ヒューズF2は、NチャネルMOSトランジスタ768と接地ノードとの間に接続される。

#### 【0162】

置換ワード線設定部746～752は、入力されるロウアドレス信号RA0に代えてロウアドレス信号RA1～RA4がそれぞれ与えられる点において置換ワード線設定部744と異なるが、内部の構成は、置換ワード線設定部744と同じであるので、説明は繰返さない。

#### 【0163】

置換ワード線設定部744～752は、スペアワード線SWL00を第1の動作モードとして使用するとき、外部から入力されたロウアドレスを、事前に設定された置換されるワード線に対応するロウアドレスと比較し、その比較結果を出力する。10

#### 【0164】

なお、図9に示すその他のスペアデコーダ626～634の構成は、スペアデコーダ624の構成と同じであるので、説明は繰返さない。

#### 【0165】

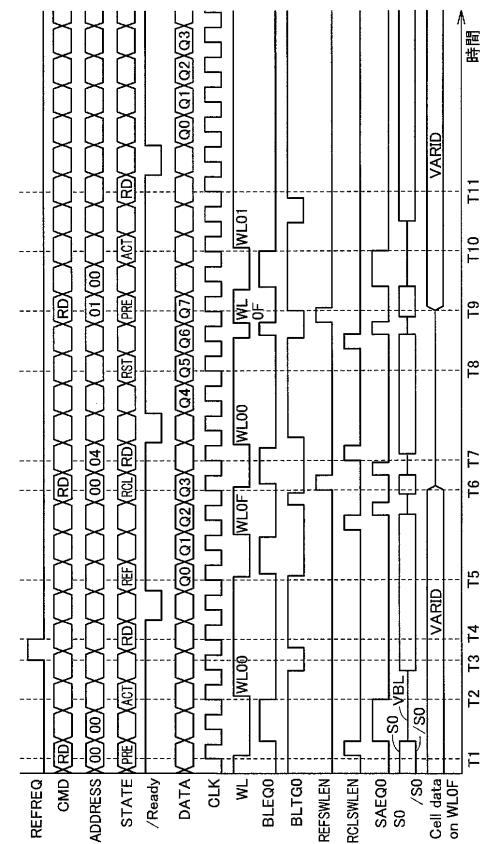

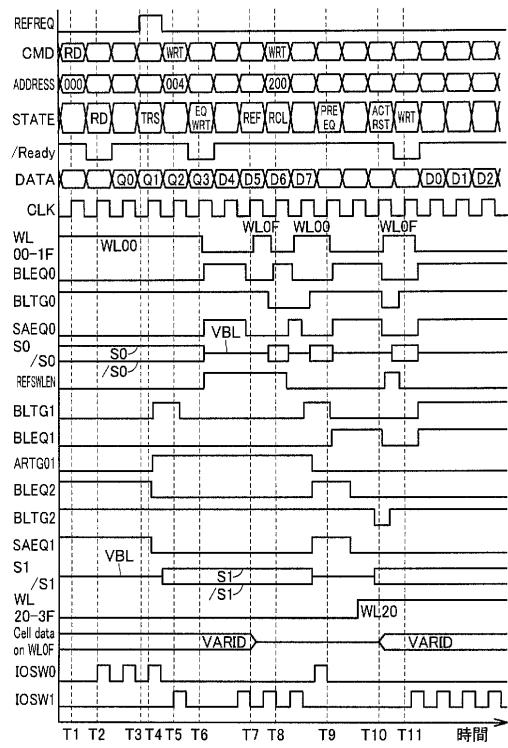

図12は、実施の形態1による半導体記憶装置1の動作を説明するための動作波形図である。なお、説明の便宜上、図12においては、1つのバンクアドレスに対して動作が行なわれるものとする。また、バースト長は4としている。

#### 【0166】

図12を参照して、時刻T1前においては、ワード線WL01～WL0Fのいずれかが既に活性化されており、信号BLTG0は、Hレベルであるとする。したがって、NチャネルMOSトランジスタ30～33は導通しており、ビット線対BL00, /BL00は、ビット線対BL0, /BL0とそれぞれ電気的に接続され、ビット線対BL01, /BL01は、ビット線対BL1, /BL1とそれぞれ電気的に接続されている。そして、駆動信号S0, /S0は、それぞれHレベル, Lレベルに活性化されており、センスアンプ62, 63は、ビット線対BL0, /BL0およびビット線対BL1, /BL1の電位をそれぞれ増幅している。20

#### 【0167】

時刻T1において、コマンドCMDとしてリードコマンドRDが入力され、アドレス信号ADDRESSとしてロウアドレス00が入力されると、ロウアドレスレジスタ7は、入力されたロウアドレスを内部に記憶しているロウアドレスと比較する。そして、これらのアドレスは異なるため、ロウアドレスレジスタ7は、内部信号HITをLレベルで出力する。30

#### 【0168】

そうすると、制御回路2は、プリチャージ信号PREを活性化し、これに応じて、活性化されているワード線が非活性化され、信号BLEQ0および信号SAEQ0が活性化され、さらに、駆動信号S0, /S0がともに電位VBLに設定される。そして、ビット線対BL00, /BL00およびビット線対BL0, /BL0ならびにビット線対BL01, /BL01およびビット線対BL1, /BL1は、所定の電位にプリチャージされる。40

#### 【0169】

そして、時刻T1から2クロック後の時刻T2において、制御回路2は、アクト信号ACTを活性化し、これに応じて、信号BLEQ0, SAEQ0が非活性化され、ワード線WL00が活性化されて、アクティベート動作が実行される。また、信号ACTの活性化に応じて、ロウアドレスレジスタ7は、ロウアドレス信号RA<0:4>を内部に記憶する。

#### 【0170】

アクト信号ACTに応じてビット線対BL0, /BL0およびビット線対BL1, /BL1にデータが読出されると、一旦信号BLTG0が非活性化され、ビット線対BL0, /BL0がビット線対BL00, /BL00と電気的に分離され、ビット線対BL1, /BL1がビット線対BL01, /BL01と電気的に分離される。その後、駆動信号S0, /S0が活性化され、センスアンプ62, 63は、ビット線対BL0, /BL0およびビット線対BL1, /BL1の電位をそれぞれ増幅する。50

/ S 0 がそれぞれ H レベル , L レベルに活性化され、センスアンプ 6 2 , 6 3 は、それぞれビット線対 B L 0 , / B L 0 およびビット線対 B L 1 , / B L 1 の電位を増幅する。

#### 【 0 1 7 1 】

そして、アクト信号 A C T が活性化された時刻 T 2 から 2 クロック後の時刻 T 4 において、制御回路 2 は、リード信号 R D を活性化し、これに応じて、時刻 T 1 の 1 クロック後にロウアドレス 0 0 に続いて入力されたコラムアドレス 0 0 に対応するコラム選択線 C S L 0 が選択され、センスアンプ 6 2 に読出されたデータがローカル I O 線 L I O 0 , / L I O 0 、接続ゲート回路 G # 0 およびグローバル I O 線 G I O , / G I O を介して入出力回路 1 4 に伝達される。

#### 【 0 1 7 2 】

リード信号 R D が活性化された半クロック後には、制御回路 2 は、信号 R e a d y を H レベルとし、L レベルの信号 / R e a d y をメモリ制御装置 8 へ出力する。これによって、次のクロック C L K からデータ出力されることがメモリ制御回路 8 に通知される。そして、信号 / R e a d y がメモリ制御回路 8 に通知された 1 クロック後から、コラムアドレス 0 0 ~ 0 3 に対応するデータ Q 0 ~ Q 3 が順次出力される。

#### 【 0 1 7 3 】

時刻 T 3 においては、時刻 T 1 において外部から与えられたリードコマンド R D に関連する動作とは独立して、制御回路 2 が、リフレッシュ要求信号 R E F R E Q を発生する。

#### 【 0 1 7 4 】

そうすると、リード信号 R D を活性化した 2 クロック後の時刻 T 5 において、制御回路 2 は、リフレッシュ信号 R E F を活性化し、リフレッシュ動作が開始される。リフレッシュ信号 R E F が活性化されると、リードコマンド R D に応じて活性化されていたワード線 W L 0 0 が非活性化され、信号 B L T G 0 が非活性化されて、ビット線対 B L 0 0 , / B L 0 0 がそれぞれビット線対 B L 0 , / B L 0 と分離され、ビット線対 B L 0 1 , / B L 0 1 がそれぞれビット線対 B L 1 , / B L 1 と分離される。そして、信号 B L E Q 0 が活性化され、センスアンプ 6 2 , 6 3 にワード線 W L 0 0 に対応するデータを残したままビット線対 B L 0 0 , / B L 0 0 およびビット線対 B L 0 1 , / B L 0 1 が初期化される。

#### 【 0 1 7 5 】

センスアンプ 6 2 , 6 3 に読出されている、ワード線 W L 0 0 に対応するデータは、外部からいつ再度読出されるかわからないため、高速に復帰できるように、スペアワード線に接続されるスペアメモリセルに一時的に保持される。すなわち、制御回路 2 は、信号 R C L S W L E N を活性化し、センスアンプ 6 2 , 6 3 のデータは、予めモード設定されたりコール動作用のスペアワード線に接続されるスペアメモリセルに書き込まれる。

#### 【 0 1 7 6 】

一方、信号 B L E Q 0 に応じてビット線対 B L 0 0 , / B L 0 0 およびビット線対 B L 0 1 , / B L 0 1 が初期化されると、リフレッシュ対象のメモリセル行に対応するワード線 W L 0 F が活性化され、ビット線対 B L 0 0 , / B L 0 0 およびビット線対 B L 0 1 , / B L 0 1 にデータが読出される。そして、センスアンプ 6 2 , 6 3 に読出されていた、ワード線 W L 0 0 に対応するデータのスペアメモリセルへの書き込みが終了すると、駆動信号 S 0 , / S 0 がともに電位 V B L に設定され、信号 S A E Q 0 が活性化されて、ビット線対 B L 0 , / B L 0 およびビット線対 B L 1 , / B L 1 が初期化される。

#### 【 0 1 7 7 】

その後、信号 B L T G 0 が活性化し、ビット線対 B L 0 0 , / B L 0 0 は、ビット線対 B L 0 , / B L 0 と電気的に接続され、ビット線対 B L 0 1 , / B L 0 1 は、ビット線対 B L 1 , / B L 1 とそれぞれ電気的に接続される。これによって、ビット線対 B L 0 0 , / B L 0 0 およびビット線対 B L 0 1 , / B L 0 1 の電位がそれぞれセンスアンプ 6 2 , 6 3 によって増幅される。そして、センスアンプ 6 2 , 6 3 によって電位増幅されたデータは、予め設定されたスペアワード線に接続されるスペアメモリセルに書き込まれ、この段階で一旦リフレッシュ動作は終了する。

#### 【 0 1 7 8 】

10

20

30

40

50

時刻 T 6において、リフレッシュ動作とは独立して、コマンド C M D としてリードコマンド R D が入力され、アドレス信号 A D D R E S S としてロウアドレス 0 0 が入力されると、ロウアドレスレジスタ 7 は、入力されたロウアドレスを内部に記憶するロウアドレスと比較する。そして、これらのアドレスはともに 0 0 で一致するため、ロウアドレスレジスタ 7 は、内部信号 H I T を H レベルで出力する。

#### 【 0 1 7 9 】

そうすると、制御回路 2 は、リコール信号 R C L を活性化し、これに応じて、リフレッシュ動作で活性化されていたワード線 W L 0 F が非活性化され、信号 B L E Q 0 および信号 S A E Q 0 が活性化され、さらに、駆動信号 S 0 , / S 0 がともに電位 V B L に設定されて、ビット線対 BL 0 0 , / BL 0 0 およびビット線対 BL 0 , / BL 0 ならびにビット線対 BL 0 1 , / BL 0 1 およびビット線対 BL 1 , / BL 1 は、所定の電位にプリチャージされる。10

#### 【 0 1 8 0 】

そして、時刻 T 6 から 1 クロック後の時刻 T 7 において、制御回路 2 は、信号 R C L S W L E N を再び活性化し、スペアメモリセルに一時的に保持されていたワード線 W L 0 0 に対応するデータがセンスアンプ 6 2 , 6 3 に読出される。

#### 【 0 1 8 1 】

一方、時刻 T 7 においては、ロウアドレス 0 0 に続いてコラムアドレス 0 4 が入力され、また、制御回路 2 は、リード信号 R D を活性化する。これに応じて、コラムアドレス 0 4 に対応するコラム選択線 C S L 4 (図 3 などにおいて図示せず) が選択され、対応するセンスアンプに読出されたデータがローカル I O 線 L I O 0 , / L I O 0 、接続ゲート回路 G # 0 およびグローバル I O 線 G I O , / G I O を介して入出力回路 1 4 に伝達される。20

#### 【 0 1 8 2 】

そして、リード信号 R D が活性化された半クロック後には、制御回路 2 は、信号 R e a d y を H レベルとし、L レベルの信号 / R e a d y をメモリ制御装置 8 へ出力する。これによって、次のクロック信号 C L K からデータ出力されることがメモリ制御回路 8 に通知される。そして、信号 / R e a d y がメモリ制御回路 8 に通知された 1 クロック後から、コラムアドレス 0 4 ~ 0 7 に対応するデータ Q 4 ~ Q 7 が順次出力される。

#### 【 0 1 8 3 】

リード信号 R D を活性化した 3 クロック後の時刻 T 8 において、制御回路 2 は、リストア信号 R S T を活性化し、スペアメモリセルに一時的に記憶されているワード線 W L 0 F に対応するデータのリストア動作が開始される。活性化しているワード線 W L 0 0 が非活性化され、信号 B L T G 0 が非活性化されて、ビット線対 BL 0 0 , / BL 0 0 がビット線対 BL 0 , / BL 0 とそれぞれ電気的に分離され、ビット線対 BL 0 1 , / BL 0 1 がビット線対 BL 1 , / BL 1 とそれぞれ電気的に分離される。30

#### 【 0 1 8 4 】

その後、信号 B L E Q 0 および信号 S A E Q 0 が活性化され、さらに、駆動信号 S 0 , / S 0 がともに電位 V B L に設定されて、ビット線対 BL 0 0 , / BL 0 0 およびビット線対 BL 0 , / BL 0 ならびにビット線対 BL 0 1 , / BL 0 1 およびビット線対 BL 1 , / BL 1 は、所定の電位にプリチャージされる。そして、制御回路 2 は、信号 R E F S W L E N を再び活性化し、スペアメモリセルに一時的に保持されていたワード線 W L 0 F に対応するデータがセンスアンプ 6 2 , 6 3 に読出される。40

#### 【 0 1 8 5 】

さらに、制御回路 2 は、センスアンプ 6 2 , 6 3 に読出されたデータを元のメモリセルに書きむため、ワード線 W L 0 F を活性化する。その後、信号 B L T G 0 が再び活性化され、センスアンプ 6 2 , 6 3 に読出されていたデータが元のメモリセルに書き込まれ、リフレッシュ動作に伴うデータの復帰が完了する。

#### 【 0 1 8 6 】

時刻 T 9 においては、リフレッシュ動作とは独立して、コマンド C M D としてリードコマンド R D が入力され、アドレス信号 A D D R E S S としてロウアドレス 0 1 が入力される50

。そうすると、ロウアドレスレジスタ7は、入力されたロウアドレスを内部に保持しているロウアドレスと比較する。ロウアドレスレジスタ7は、時刻T2における信号ACTに応じてロウアドレス00を保持しているため、アドレスは一致せず、ロウアドレスレジスタ7は、内部信号HITをLレベルで出力する。

#### 【0187】

したがって、この場合は、時刻T1以降の動作と同じ動作が行なわれる。すなわち、制御回路2は、時刻T9から2クロック後の時刻T10において、アクト信号ACTを活性化し、これに応じて、ロウアドレスレジスタ7は、時刻T9において入力されたロウアドレス01を内部に保持する。そして、制御回路2は、時刻T10から2クロック後の時刻T11において、リード信号RDを活性化し、その後、信号/R e a d yをメモリ制御装置8へ出力した後、信号データQ0～Q3を順次メモリ制御装置8へ出力する。

10

#### 【0188】

なお、リコール動作時およびリフレッシュ動作時にスペアメモリセルにデータを一時的に記憶する際、隣接するスペアワード線、たとえば、スペアワード線SWL00, SWL01を同時に活性化し、センスアンプ62のデータを互いに相補なデータとして2つのスペアメモリセルSce1100, Sce1110に記憶してもよい。このように、スペアメモリセルをいわゆるツインメモリセルとして使用することによって、リコール動作時およびリフレッシュ動作時のセンスアンプによる増幅動作を高速化でき、さらに半導体記憶装置1の高速化を図ることができる。

#### 【0189】

以上のように、この実施の形態1による半導体記憶装置1によれば、センスアンプ近傍に備えられるスペアワード線に接続されるスペアメモリセルを一時的なデータ保持回路として用い、これを用いてリフレッシュ動作を2段階にわけて実行するようにしたので、リフレッシュ動作時に外部からコマンドを受けなくなる期間が短縮され、リフレッシュ動作による遅延が小さくなり、その結果、半導体記憶装置1の高速動作化が達成される。

20

#### 【0190】

また、リフレッシュ動作の際、リフレッシュ動作前にセンスアンプに読出されていたデータも、スペアメモリセルに保持されるので、その後のそのデータに対するアクセスが高速化される。

#### 【0191】

さらに、メモリセルアレイMAをセンスアンプ帯SABと分離する分離回路60, 61, 66, 67が設けられ、スペアメモリセルに対するデータ入出力の際、センスアンプ帯SABからメモリセルアレイMAを分離するようにしたので、スペアメモリセルに対するデータ入出力の際のセンスアンプの動作が高速化される。

30

#### 【0192】

また、さらに、スペアメモリセルにデータを一時的に記憶する際、スペアメモリセルをツインメモリセルとして動作させることができるので、これによって、さらに動作を高速化することが可能である。

#### 【0193】

また、この半導体記憶装置1によれば、ロウアドレスを管理するロウアドレスレジスタ7を備え、さらに、ロウアドレスの活性化／非活性化状態に応じて異なるデータ入出力タイミングを外部に通知するようにしたので、内部のロウアドレスの状態を考慮することなく外部からロウアドレスおよびコラムアドレスを入力することができる。そして、当該半導体記憶装置1を制御するメモリ制御装置8は、ロウアドレスを管理する必要がないので、外部の制御装置にとって簡便に利用できる半導体記憶装置が実現される。

40

#### 【0194】

さらに、この半導体記憶装置1によれば、スペアワード線を事前にテストする機能をスペアデコーダ624～634に備えたので、正常動作が確認されたスペアワード線のみを使用することができる。

#### 【0195】

10

20

30

40

50

また、さらに、この半導体記憶装置1によれば、外部コマンドに応じて従来機能のSDRAMとして機能することができるので、従来のSDRAMの互換品として使用することもできる。

### 【0196】

#### [実施の形態2]

実施の形態1では、バースト動作中にリフレッシュ動作が実行されると、バースト動作を中止してリフレッシュ動作を実行するか、あるいは、バースト動作が終了するまでリフレッシュ動作を待つ必要がある。実施の形態2においては、この対策がなされ、外部からみると半導体記憶装置内部のリフレッシュ動作は、完全に隠される。

### 【0197】

また、この発明による半導体記憶装置は、アドレス管理回路を内蔵するため、半導体記憶装置を制御する制御装置の負荷が軽くなる。この実施の形態2では、半導体記憶装置と制御装置とが小型ユニット内に内蔵されたSIP(システム・イン・パッケージ)の構成がとられている。

### 【0198】

図13は、この発明の実施の形態2による半導体記憶装置の全体構成を示す概略ブロック図である。

### 【0199】

図13を参照して、半導体記憶装置1Aは、半導体記憶装置1Aを制御するメモリ制御部9とともに、ユニット10に含まれる。半導体記憶装置1Aは、実施の形態1による半導体記憶装置1の構成において、制御回路2、メモリセルアレイ6およびロウアドレスレジスタ7に代えて、制御回路2A、メモリセルアレイ6Aおよびロウアドレスレジスタ7Aをそれぞれ備える。その他の回路の構成については、実施の形態1による半導体記憶装置1と同じであるので、説明は繰返さない。

### 【0200】

通常のSDRAMでは、ロウアドレスとコラムアドレスとが共通の端子から時間差を置いて入力されるマルチプレクス方式が一般的であるが、この実施の形態2による半導体記憶装置1Aにおいては、ロウアドレスRA、コラムアドレスCAおよびバンクアドレスBAは、メモリ制御部9から制御回路2Aに同時に入力される。また、メモリ制御部9から与えられるコマンドCMDについても、実施の形態1による半導体記憶装置1のように複数の信号の組合せで与えられるのではなく、1つの信号で1つのコマンドが与えられる。

### 【0201】

なお、この実施の形態2による半導体記憶装置1Aにおいても、SIP構成や上述のインターフェース構成をとらず、実施の形態1と同様のシステム構成およびインターフェース構成にすることも可能である。

### 【0202】

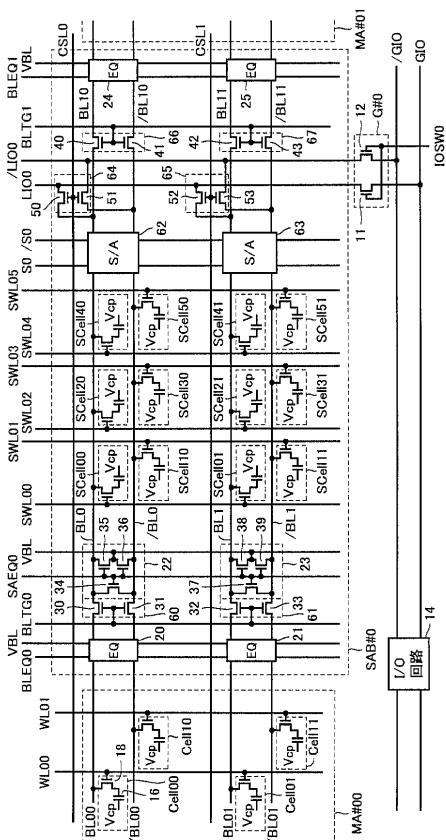

図14は、図13に示すメモリセルアレイ6Aに含まれるセンスアンプ帯周辺の構成を示す回路図である。

### 【0203】

図14を参照して、メモリブロックBLOCK0,BLOCK1の間にスイッチアレイSWが設けられる。メモリブロックBLOCK0,BLOCK1の構成は、実施の形態1による半導体記憶装置1におけるメモリブロックBLOCK0,BLOCK1の構成と同じであるので、説明は繰返さない。

### 【0204】

スイッチアレイSWは、メモリブロックBLOCK0に含まれるメモリセルアレイMA#01とメモリブロックBLOCK1に含まれるメモリセルアレイMA#10との間に配置される。スイッチアレイSWは、ビット線対BL10,/BL10をビット線対BL20,/BL20と接続する接続回路450と、ビット線対BL11,/BL11をビット線対BL21,/BL21と接続する接続回路451とを含む。

### 【0205】

10

20

30

40

50

接続回路 450 は、N チャネル MOS トランジスタ 460, 461 からなる。N チャネル MOS トランジスタ 460 は、ビット線 BL10 とビット線 BL20との間に接続され、信号 ARTG01 をゲートに受ける。N チャネル MOS トランジスタ 461 は、ビット線 /BL10 とビット線 /BL20との間に接続され、信号 ARTG01 をゲートに受ける。接続回路 451 は、N チャネル MOS トランジスタ 462, 463 からなる。N チャネル MOS トランジスタ 462 は、ビット線 BL11 とビット線 BL21との間に接続され、信号 ARTG01 をゲートに受ける。N チャネル MOS トランジスタ 463 は、ビット線 /BL11 とビット線 /BL21との間に接続され、信号 ARTG01 をゲートに受ける。

## 【0206】

10

信号 ARTG01 が活性化されると、接続回路 450 は、ビット線 BL10, /BL10 をビット線 BL20, /BL20 とそれぞれ電気的に接続し、接続回路 451 は、ビット線 BL11, /BL11 をビット線 BL21, /BL21 とそれぞれ電気的に接続する。

## 【0207】

半導体記憶装置 1A では、メモリブロック BLOCK0 においてメモリセルからセンスアンプに読出されたデータは、メモリセルアレイ MA#01、スイッチアレイ SW およびメモリブロック BLOCK1 のメモリセルアレイ MA#10 を介してメモリブロック BLOCK1 のセンスアンプに転送される。そして、メモリブロック BLOCK1 のセンスアンプからローカル IO 線 LIO1, /LIO1 にデータが読出され、ゲート回路 G#1 を介してグローバル IO 線 GIO, /GIO に読出されて、入出力回路 14 にデータが伝達される。

20

## 【0208】

このようにすることで、メモリブロック BLOCK0 からデータをバースト動作で読出している最中にメモリブロック BLOCK0 においてリフレッシュ動作が発生しても、読出データは、メモリブロック BLOCK1 のセンスアンプに転送されて外部とインターフェースされるので、メモリブロック BLOCK0 のセンスアンプは、リフレッシュ動作に用いることができ、バースト動作が中断されたり、リフレッシュ動作が待たされることなくなる。

## 【0209】

30

なお、メモリブロック BLOCK1 においてメモリセルからセンスアンプに読出されたデータが、メモリセルアレイ MA#10、スイッチアレイ SW およびメモリブロック BLOCK0 のメモリセルアレイ MA#01 を介してメモリブロック BLOCK0 のセンスアンプに転送されるケースもあるが、これら 2 つのケースの動作は、本質的に同じであるので、以下の説明では、メモリブロック BLOCK0 においてメモリセルからセンスアンプにデータが読出されるケースについて説明する。

## 【0210】

40

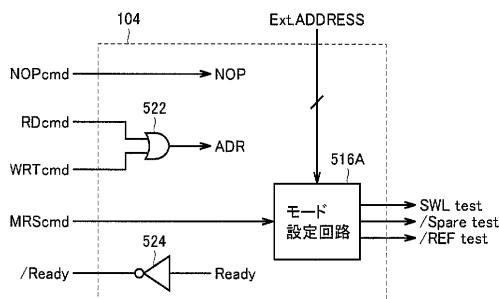

図 15 ~ 図 18 は、図 13 に示す制御回路 2A の構成を示す回路図である。説明の便宜上、図 15 ~ 図 18 においても、実施の形態 1 において行なった説明と同様に、バンク 0 のメモリブロック BLOCK0 に対応する部分のみが示され、以下では、特に、バンクおよびメモリブロックに対応する符号は付せずに説明を行なう。

## 【0211】

図 15 を参照して、制御回路 2A は、信号入出力回路 104 を含む。信号入出力回路 104 は、OR ゲート 522 と、モード設定回路 516A と、インバータ 524 とを含む。

## 【0212】

OR ゲート 522 は、メモリ制御部 9 からコマンド CMD として受けるリードコマンド RD およびライトコマンド WRT の論理和を演算し、その演算結果を内部信号 ADR として出力する。モード設定回路 516A は、モードセレクトコマンド MRS が H レベルのとき、メモリ制御部 9 からモード設定信号として受けるアドレス信号 ADDRESS に応じて半導体記憶装置 1A のモードを設定する。そして、モード設定回路 516A は、設定したモードに応じて、信号 SWL\_test, /Spare\_test, /REF\_test

50

を出力する。インバータ 524 は、内部信号 Ready を反転して信号 /Ready をメモリ制御部 9 へ出力する。

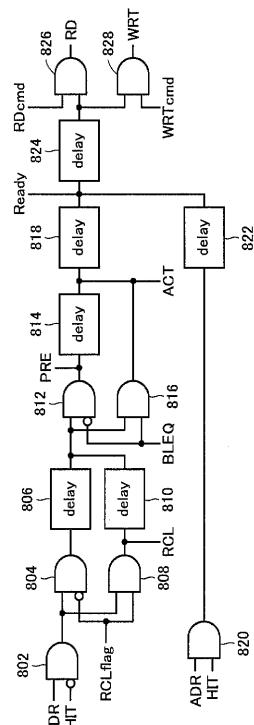

【0213】

図 16 を参照して、制御回路 2A は、内部信号 HIT の反転信号および内部信号 ADR の論理積を演算し、その演算結果を出力する AND ゲート 802 と、AND ゲート 802 からの出力信号および内部フラグ RCL\_f1ag の反転信号の論理積を演算し、その演算結果を出力する AND ゲート 804 と、AND ゲート 804 からの出力信号を 2クロック遅延した信号を出力する遅延回路 806 とをさらに含む。

【0214】

また、制御回路 2A は、AND ゲート 802 からの出力信号および内部フラグ RCL\_f1ag の論理積を演算し、その演算結果をリコール信号 RCL として出力する AND ゲート 808 と、AND ゲート 808 からの出力信号を 2クロック遅延した信号を出力する遅延回路 810 とをさらに含む。

【0215】

さらに、制御回路 2A は、遅延回路 806 または 810 からの出力信号および信号 BQE の反転信号の論理積を演算し、その演算結果をプリチャージ信号 PRE として出力する AND ゲート 812 と、AND ゲート 812 からの出力信号を 2クロック遅延してアクト信号 ACT を出力する遅延回路 814 と、遅延回路 806 または 810 からの出力信号および信号 BQE の論理積を演算し、その演算結果をアクト信号 ACT として出力する AND ゲート 816 と、アクト信号 ACT を半クロック遅延して内部信号 Ready を出力する遅延回路 818 とを含む。

【0216】

また、さらに、制御回路 2A は、内部信号 ADR および内部信号 HIT の論理積を演算し、その演算結果を出力する AND ゲート 820 と、AND ゲート 820 からの出力信号を半クロック遅延して内部信号 Ready を出力する遅延回路 822 とを含む。

【0217】

また、さらに、制御回路 2A は、内部信号 Ready を半クロック遅延した信号を出力する遅延回路 824 と、リードコマンド RD および遅延回路 824 からの出力信号の論理積を演算し、その演算結果をリード信号 RD として出力する AND ゲート 826 と、ライトコマンド WRT および遅延回路 824 からの出力信号の論理積を演算し、その演算結果をライト信号 WRT として出力する AND ゲート 828 とを含む。

【0218】

リコール信号 RCL、プリチャージ信号 PRE、アクト信号 ACT、内部信号 Ready 、リード信号 RD および信号 BQE については、実施の形態 1 において既に説明しているので、説明は繰返さない。ライト信号 WRT は、外部からの信号の書き込みを指示する信号である。

【0219】

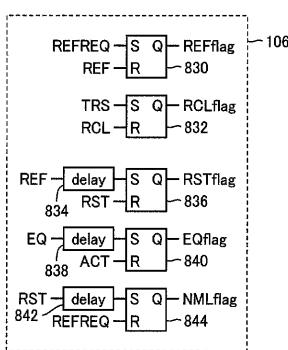

図 17 を参照して、制御回路 2A は、内部フラグセット回路 106 をさらに含む。内部フラグセット回路 106 は、SR フリップフロップ回路 830, 832, 836, 840, 844 と、遅延回路 834, 838, 842 とからなる。

【0220】

SR フリップフロップ回路 830 は、リフレッシュ要求信号 REFREQ およびリフレッシュ信号 REF をそれぞれセット入力およびリセット入力に受け、内部フラグ REFF1ag を出力する。SR フリップフロップ回路 832 は、後述するトランスマスク信号 TRS およびリコール信号 RCL をそれぞれセット入力およびリセット入力に受け、内部フラグ RCL\_f1ag を出力する。

【0221】

遅延回路 834 は、リフレッシュ信号 REF を 1クロック遅延した信号を出力する。SR フリップフロップ回路 836 は、遅延回路 834 からの出力信号およびリストア信号 RST をそれぞれセット入力およびリセット入力に受け、内部フラグ RST\_f1ag を出力す

10

20

30

40

50

る。

【0222】

遅延回路838は、後述するイコライズ信号EQを1クロック遅延した信号を出力する。SRフリップフロップ回路840は、遅延回路838からの出力信号およびアクト信号ACTをそれぞれセット入力およびリセット入力に受け、内部フラグEQflagを出力する。

【0223】

遅延回路842は、リストア信号RSTを1クロック遅延した信号を出力する。SRフリップフロップ回路844は、遅延回路842からの出力信号およびリフレッシュ要求信号REFREQをそれぞれセット入力およびリセット入力に受け、内部フラグNMLflagを出力する。

【0224】

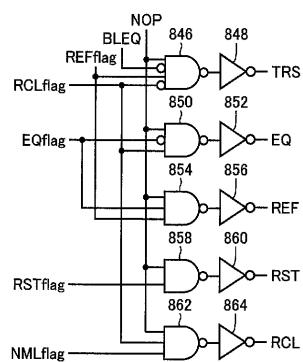

図18を参照して、制御回路2Aは、信号NOP、信号BLEQの反転信号、内部フラグREFflagおよび内部フラグRCLflagの反転信号の論理積を演算し、その演算結果を反転した信号を出力するNANDゲート846と、NANDゲート846からの出力信号を反転してトランスマスク信号TRSを出力するインバータ848とを含む。トランスマスク信号TRSは、活性化されているセンスアンプのデータを隣接するメモリブロックのセンスアンプへ転送する動作を指示する信号である。

【0225】

また、制御回路2Aは、信号NOP、内部フラグEQflagの反転信号および内部フラグRCLflagの論理積を演算し、その演算結果を反転した信号を出力するNANDゲート850と、NANDゲート850からの出力信号を反転してイコライズ信号EQを出力するインバータ852とを含む。イコライズ信号EQは、該当するメモリブロックのビット線対の初期化を指示する信号である。

【0226】

さらに、制御回路2Aは、信号NOP、内部フラグEQflagおよび内部フラグREFflagの論理積を演算し、その演算結果を反転した信号を出力するNANDゲート854と、NANDゲート854からの出力信号を反転してリフレッシュ信号REFを出力するインバータ856とを含む。

【0227】

また、さらに、制御回路2Aは、信号NOPおよび内部フラグRSTflagの論理積を演算し、その演算結果を反転した信号を出力するNANDゲート858と、NANDゲート858からの出力信号を反転してリストア信号RSTを出力するインバータ860とを含む。

【0228】

また、さらに、制御回路2Aは、信号NOP、内部フラグRCLflagおよび内部フラグNMLflagの論理積を演算し、その演算結果を反転した信号を出力するNANDゲート862と、NANDゲート862からの出力信号を反転してリコール信号RCLを出力するインバータ864とを含む。

【0229】

この回路は、メモリ制御部9からコマンドCMDによる動作指令を受けていないとき、すなわち信号NOPがHレベルとなるノーオペレーション状態のときに活性化される。

【0230】

また、さらに、制御回路2Aは、図示されないリフレッシュタイム610と、リフレッシュアドレスカウンタ612とを含む。リフレッシュタイム610およびリフレッシュアドレスカウンタ612の構成については、実施の形態1において既に説明したので、その説明は繰返さない。

【0231】

図19は、図13に示すロウアドレスレジスタ7Aの機能ブロック図である。ここで、実施の形態1と同様に、ロウアドレスレジスタ7Aは、メモリセルアレイ6Aの各バンクの

10

20

30

40

50

メモリブロック毎に設けられ、図19においては、バンク0のメモリブロックBLOCK0に対応するロウアドレスレジスタについて示されている。

#### 【0232】

図19を参照して、ロウアドレスレジスタ7Aは、図9に示した実施の形態1による半導体記憶装置1におけるロウアドレスレジスタ7の構成において、レジスタアレイ622に代えてレジスタアレイ622Aを備え、スペアデコーダ624～634に代えてスペアデコーダ624A～634Aを備える。

#### 【0233】

レジスタアレイ622Aは、レジスタアレイ622と同様に、ACT信号により活性化されたワード線に対応するロウアドレスを内部に保持するが、内部信号RASに代えて内部信号ADRを受けている点がレジスタアレイ622と異なる。

#### 【0234】

レジスタアレイ622Aは、アクト信号ACTを受けると、そのアクト信号ACTに応じて活性化されるワード線に対応するロウアドレス信号RA<0：4>を制御回路2Aから受け、次にプリチャージ信号PREを受けるまで内部に保持する。そして、内部信号ADRを受けると、その内部信号ADRとともに受ける読出または書込対象のロウアドレス信号RA<0：4>を、保持しているロウアドレスと比較し、一致すると、内部信号HITをHレベルで出力する。

#### 【0235】

スペアデコーダ624A～634Aは、スペアデコーダ624～634と同様に、対応するスペアワード線SWL00～SWL05の動作モードを設定し、スペアワード線SWL00～SWL05それぞれに対応する活性化信号SWL0EN～SWL5ENを出力するが、内部信号RASに代えて内部信号ADRを受け、信号/RCL\_testを受けない点でスペアデコーダ624～634と異なる。

#### 【0236】

スペアデコーダ624A～634Aは、対応するスペアワード線に対して、スペアワード線をワード線の予備線として使用する第1の動作モード、およびリフレッシュ動作に伴って読出されたデータの一時記憶メモリセルとして使用する第2の動作モードのいずれかのモードを設定する。

#### 【0237】

なお、実施の形態2による半導体記憶装置1Aは、スペアワード線をリコール動作用のデータの一時記憶メモリセルとして使用する動作モードを備えていない。半導体記憶装置1Aにおいては、読出データは、センスアンプに読出された後、隣接するセンスアンプに転送されるため、読出データをスペアワード線に記憶する必要がないからである。そのため、スペアデコーダ624A～634Aは、スペアワード線をリコール動作用のデータの一時記憶メモリセルとして使用する動作モードの設定回路を備えていない。

#### 【0238】

レジスタアレイ622Aは、内部信号RASに代えて内部信号ADRを受ける点がレジスタアレイ622と異なり、その回路構成は同じであるので、構成についての説明は繰返さない。

#### 【0239】

図20は、図19に示すスペアデコーダ624Aの構成を示す回路図である。図20を参照して、スペアデコーダ624Aは、図11に示した実施の形態1による半導体記憶装置1におけるスペアデコーダ624の構成において、内部信号RASに代えて内部信号ADRを受け、第3モード設定部760およびNANDゲート762を備えない構成となっている。その他の構成については、スペアデコーダ624の構成と同じであるので、説明は繰返さない。

#### 【0240】

なお、図19に示すその他のスペアデコーダ626A～634Aの構成は、スペアデコーダ624Aの構成と同じであるので、説明は繰返さない。

10

20

30

40

50

## 【0241】

図21は、実施の形態2による半導体記憶装置1Aの動作を説明するための動作波形図である。なお、説明の便宜上、図21においては、1つのバンクアドレスに対して動作が行なわれるものとする。また、バースト長は4としている。

## 【0242】

図21を参照して、時刻T1前においては、ワード線WL00が既に活性化されている。駆動信号S0, /S0は、それぞれHレベル, Lレベルに活性化されており、メモリブロックBLOCK0のセンスアンプ62, 63は、ビット線対BL0, /BL0およびビット線対BL1, /BL1の電位をそれぞれ増幅している。また、駆動信号S1, /S1は、いずれも電位VBLに初期設定されており、メモリブロックBLOCK1のセンスアンプ62, 63は、非活性状態にある。10

## 【0243】

時刻T1において、コマンドCMDとしてリードコマンドRDが入力され、アドレス信号ADDRESSとして000(左2桁がロウアドレスを表わし、右1桁がコラムアドレスを表わす。)が入力されると、ロウアドレスレジスタ7Aは、入力されたロウアドレスを内部に記憶しているロウアドレスと比較する。そして、これらのロウアドレスは一致するため、ロウアドレスレジスタ7は、内部信号HITをHレベルで出力する。

## 【0244】

そうすると、制御回路2Aは、半クロック後に内部信号ReadyをHレベルとし、Lレベルの信号/Readyをメモリ制御部9へ出力する。これによって、次のクロックCLKからデータ出力されることがメモリ制御部9に通知される。そして、制御回路2Aは、さらに半クロック後の時刻T2において、リード信号RDを活性化し、その1クロック後からコラムアドレス0~3に対応するデータQ0~Q3が順次出力される。20

## 【0245】

時刻T3においては、時刻T1において外部から与えられたリードコマンドRDに関連する動作とは独立して、制御回路2Aが、リフレッシュ要求信号REFREQを発生する。

## 【0246】

そうすると、次のクロック信号CLKの立上りエッジである時刻T4において、制御回路2Aは、トランスマスファ信号TRSを活性化し、メモリブロックBLOCK0のセンスアンプに読出されているデータの転送動作が開始される。すなわち、トランスマスファ信号TRSが活性化されると、信号BLEQ2, SAEQ1が非活性化され、信号BLTG1, ARTG1が活性化されて、メモリブロックBLOCK1のセンスアンプがメモリブロックBLOCK0のセンスアンプと電気的に接続される。30

## 【0247】

そして、メモリブロックBLOCK0のセンスアンプに読出されているデータが、メモリセルアレイMA#01、スイッチアレイSWおよびメモリセルアレイMA#10を介してメモリブロックBLOCK1のセンスアンプに伝達される。そして、駆動信号S1, /S1がそれぞれHレベル, Lレベルに活性化され、メモリブロックBLOCK1のセンスアンプは、メモリブロックBLOCK0のセンスアンプと同じデータを保持する。なお、データの転送が完了すると、信号BLTG1は非活性化される。40

## 【0248】

このとき、4番目の出力データQ3については、データ出力の際、既にメモリブロックBLOCK1のセンスアンプへの転送処理が完了しているので、信号IOSW1が活性化され、データQ3は、メモリブロックBLOCK1のセンスアンプから外部へ出力される。

## 【0249】

続いて、時刻T5において、リフレッシュ動作とは独立して、コマンドCMDとしてライトコマンドWRTが入力され、アドレス信号ADDRESSとして004が入力されると、ロウアドレスレジスタ7Aは、入力されたロウアドレスを内部に保持するロウアドレスと比較する。これらのロウアドレスは一致するため、ロウアドレスレジスタ7は、内部信号HITをHレベルで出力する。50

**【0250】**

そうすると、制御回路2Aは、半クロック後に内部信号ReadyをHレベルとし、Lレベルの信号/Readyをメモリ制御部9へ出力する。そして、信号/Readyを出力した1クロック後からデータD4～D7が入力される。ここで、ロウアドレス00のデータについては、メモリブロックBLOCK1のセンスアンプへの転送が行なわれているので、データD4～D7の書き込みは、メモリブロックBLOCK1のセンスアンプに対して行なわれる。

**【0251】**

一方、時刻T6において、制御回路2Aは、トランスマニフェスト信号TRSの活性化に応じて内部フラグRCLflagを活性化し、これに応じてイコライズ信号EQを活性化する。これに応じて、ワード線WL00が非活性化され、信号BLEQ0, SAEQ0が活性化され、駆動信号S0, /S0がともに電位VBLに設定される。そして、後に実行されるリフレッシュ動作に伴ってメモリブロックBLOCK0のセンスアンプに読み出されるデータをスペアメモリセルに記憶するため、制御回路2Aは、信号REFSWLENを活性化する。なお、制御回路2Aは、ビット線対の初期化が完了すると、信号BLEQ0, SAEQ0を非活性化する。

**【0252】**

続いて、イコライズ信号EQを活性化した2クロック後の時刻T7において、制御回路2Aは、リフレッシュ信号REFを活性化し、リフレッシュ動作が開始される。リフレッシュ信号REFが活性化されると、リフレッシュ対象のワード線WL0Fが活性化され、メモリブロックBLOCK0のセンスアンプにデータが読み出される。

**【0253】**

ここで、センスアンプによる増幅動作を高速化するため、データがビット線対に読み出された後、信号BLTG0が非活性化され、ビット線対BL00, /BL00がそれぞれビット線対BL0, /BL0と分離され、ビット線対BL01, /BL01がそれぞれビット線対BL1, /BL1と分離される。そして、データがセンスアンプに読み出されると、ワード線WL0Fが非活性化され、信号BLEQ0が活性化される。

**【0254】**

実施の形態2による半導体記憶装置1Aにおいても、実施の形態1による半導体記憶装置1と同様に、リフレッシュ動作は2段階で実施されるため、リフレッシュ動作に伴ってセンスアンプに読み出されたデータの元のメモリセルへの書き込みは直ちに行なわれず、データはスペアメモリセルに一旦書き込まれる。制御回路2Aは、データがスペアメモリセルに書き込まれると、信号REFSWLENを非活性化し、データがスペアメモリセルに保持される。

**【0255】**

続いて、時刻T8において、リフレッシュ動作とは独立して、コマンドCMDとしてライトコマンドWRTが入力され、アドレス信号ADDRESSとして200が入力されると、ロウアドレスレジスタ7Aは、入力されたロウアドレス20を内部に保持するロウアドレス00と比較する。これらのロウアドレスは異なるため、ロウアドレスレジスタ7Aは、内部信号HITをLレベルで出力する。

**【0256】**

一方、入力されたロウアドレス20は、メモリブロックBLOCK1に含まれるワード線に対応するが、メモリブロックBLOCK1のセンスアンプにはメモリブロックBLOCK0のワード線WL00に対応するデータが保持されている。そのため、制御回路2Aは、リコール信号RCLを活性化し、メモリブロックBLOCK1のセンスアンプのデータは、メモリブロックBLOCK0のセンスアンプへ再転送される。

**【0257】**

なお、時刻T5におけるライトコマンドWRTに応じた書き込み動作中であるため、再転送完了後に入力される4番目の入力データD7は、メモリブロックBLOCK0のセンスアンプに対して書き込まれる。その後、制御回路2Aは、ワード線WL00を活性化し、これら

10

20

30

40

50

の入力データは、ワード線WL00に接続されるメモリセルに書き込まれる。

【0258】

なお、データの再転送完了後、制御回路2Aは、信号ARTG01を非活性化し、メモリブロックBLOCK0およびメモリブロックBLOCK1は、スイッチアレイSWによって電気的に分離される。

【0259】

その後、時刻T9において、制御回路2Aは、プリチャージ信号PREおよびイコライズ信号EQを活性化し、メモリブロックBLOCK1におけるデータ書き込みの準備動作と、メモリブロックBLOCK0におけるリフレッシュデータに対するリストア動作のための初期化動作とが並行して実行される。 10

【0260】

続いて、時刻T10において、制御回路2Aは、アクト信号ACTおよびリストア信号RSTを活性化し、メモリブロックBLOCK1におけるワード線WL20の活性化と、メモリブロックBLOCK0におけるリフレッシュデータのリストア動作とが並行して実施される。

【0261】

そして、時刻T11において、制御回路2Aは、ライト信号WRTを活性化し、メモリブロックBLOCK1におけるワード線WL20に接続されるメモリセルへのデータの書き込みが行なわれる。

【0262】

なお、この半導体記憶装置1Aにおいても、実施の形態1で述べたように、リフレッシュ動作においてスペアメモリセルにデータを一時的に記憶する際、隣接するスペアワード線、たとえば、スペアワード線SWL00, SWL01を同時に活性化し、センスアンプ62のデータを互いに相補なデータとして2つのスペアメモリセルSCe1100, SCe1110に記憶してもよい。これによって、リフレッシュ動作時のセンスアンプによる増幅動作を高速化でき、半導体記憶装置1Aの動作の高速化を図ることができる。 20

【0263】

以上のように、この実施の形態2による半導体記憶装置1Aによれば、隣接するメモリブロックを接続するスイッチアレイSWを設け、一方のメモリブロックに含まれるセンスアンプに読み出されたデータを他方のメモリブロックに含まれるセンスアンプに転送できるようにしたので、バースト動作中にリフレッシュ動作が実行されても読み出データは途切れることなく出力され、その結果、半導体記憶装置1Aの高速動作化が達成される。 30

【0264】

今回開示された実施の形態は、すべての点で例示であって制限的なものではないと考えられるべきである。本発明の範囲は、上記した実施の形態の説明ではなくて特許請求の範囲によって示され、特許請求の範囲と均等の意味および範囲内のすべての変更が含まれることが意図される。

【0265】

【発明の効果】

この発明による半導体記憶装置によれば、センスアンプ近傍にデータ保持回路を備え、このデータ保持回路を用いてリフレッシュ動作を2段階にわけて実行するようにしたので、リフレッシュ動作時に外部からコマンドを受けなくなる期間が短縮され、リフレッシュ動作による遅延が小さくなり、その結果、半導体記憶装置の高速動作化が達成される。 40

【0266】

また、リフレッシュ動作の際、リフレッシュ動作前にセンスアンプに読み出されていたデータも、データ保持回路に保持されるので、その後のそのデータに対するアクセスが高速化される。

【0267】

さらに、この発明による半導体記憶装置によれば、メモリセルアレイをセンスアンプ帯と分離する分離回路が設けられ、データ保持回路に対するデータ入出力の際、データ保持回 50

路を含むセンスアンプ帯からメモリセルアレイを分離するようにしたので、データ保持回路に対するデータ入出力の際のセンスアンプの動作が高速化される。

【0268】

また、さらに、この発明による半導体記憶装置によれば、データ保持回路としてスペアワード線に接続されるスペアメモリセルを使用するようにしたので、エリアペナルティが小さく、装置面積の増大を抑えることができる。

【0269】

また、さらに、この発明による半導体記憶装置によれば、スペアメモリセルにデータを一時的に記憶する際、スペアメモリセルをツインメモリセルとして動作させることができるので、これによって半導体記憶装置の動作は、さらに高速化される。

10

【0270】

また、さらに、この発明による半導体記憶装置によれば、ロウアドレスを管理するロウアドレス管理回路を備え、ロウアドレスの活性化／非活性化状態に応じて異なるデータ入出力タイミングを外部に通知するための制御信号出力端子を備えたので、内部のロウアドレスの状態を考慮することなく外部からロウアドレスおよびコラムアドレスを入力することができる。そして、当該半導体記憶装置を制御するメモリ制御装置は、ロウアドレスを管理する必要がないので、外部の制御装置にとって簡便に利用できる半導体記憶装置が実現される。

【0271】

さらに、この発明による半導体記憶装置によれば、スペアワード線を事前にテストする機能を備えたので、正常動作が確認されたスペアワード線のみを使用することができる。

20

【0272】

また、さらに、この発明による半導体記憶装置によれば、外部コマンドに応じて従来機能のSDRAMとして機能することができるので、従来のSDRAMの互換品として使用することもできる。

【0273】

また、さらに、この発明による半導体記憶装置によれば、隣接するメモリブロックを接続する接続ゲート回路を設け、一方のメモリブロックに含まれるセンスアンプに読み出されたデータを他方のメモリブロックに含まれるセンスアンプに転送できるようにしたので、バースト動作中にリフレッシュ動作が実行されても読み出データは途切れることなく出力され、その結果、半導体記憶装置の高速動作化が達成される。

30

【図面の簡単な説明】

【図1】この発明の実施の形態1による半導体記憶装置の全体構成を示す概略ブロック図である。

【図2】図1に示すメモリセルアレイのアレイ配置を模式的に示す図である。

【図3】実施の形態1による半導体記憶装置のセンスアンプ帯周辺の構成を示す回路図である。

【図4】図1に示す制御回路の構成を示す第1の回路図である。

【図5】図1に示す制御回路の構成を示す第2の回路図である。

【図6】図1に示す制御回路の構成を示す第3の回路図である。

【図7】図1に示す制御回路の構成を示す第4の回路図である。

【図8】図1に示す制御回路の構成を示す第5の回路図である。

40

【図9】図1に示すロウアドレスレジスタの機能ブロック図である。

【図10】図9に示すレジスタアレイの構成を示す回路図である。

【図11】図9に示すスペアデコーダの構成を示す回路図である。

【図12】実施の形態1による半導体記憶装置の動作を説明するための動作波形図である。

【図13】この発明の実施の形態2による半導体記憶装置の全体構成を示す概略ブロック図である。

【図14】図13に示すメモリセルアレイに含まれるセンスアンプ帯周辺の構成を示す回

50

路図である。

- 【図15】図13に示す制御回路の構成を示す第1の回路図である。

- 【図16】図13に示す制御回路の構成を示す第2の回路図である。

- 【図17】図13に示す制御回路の構成を示す第3の回路図である。

- 【図18】図13に示す制御回路の構成を示す第4の回路図である。

- 【図19】図13に示すロウアドレスレジスタの機能ブロック図である。

- 【図20】図19に示すスペアデコーダの構成を示す回路図である。

- 【図21】実施の形態2による半導体記憶装置の動作を説明するための動作波形図である。

【符号の説明】

10

1 , 1 A 半導体記憶装置、 2 , 2 A 制御回路、 3 ロウデコーダ、 4 コラムデコーダ、 5 入出力回路、 6 , 6 A メモリセルアレイ、 7 , 7 A ロウアドレスレジスタ、 8 メモリ制御装置、 9 メモリ制御部、 10 ユニット、 11 , 12 NチャネルMOSトランジスタ、 14 入出力回路、 20 ~ 25 イコライズ回路、 60 , 61 , 66 , 67 分離ゲート回路、 62 , 63 センスアンプ、 64 , 65 接続回路、 516 , 516 A モード設定回路、 518 制御信号入力バッファ、 530 , 536 , 548 , 550 , 560 , 566 , 572 , 578 , 584 , 806 , 810 , 814 , 818 , 822 , 824 , 834 , 838 , 842 遅延回路、 586 , 590 , 592 , 596 , 670 ~ 680 , 830 , 832 , 836 , 840 , 844 SRフリップフロップ回路、 610 リフレッシュタイム、 612 リフレッシュアドレスカウンタ、 622 , 622 A レジスタアレイ、 624 ~ 634 , 624 A ~ 634 A スペアデコーダ、 BL00 ~ BL31 , / BL00 ~ / BL31 , BL0 ~ BL3 , / BL0 ~ / BL3 ピット線、 B LOCK0 ~ B LOCK3 メモリブロック、 C e l l 0 0 ~ C e l l 1 1 メモリセル、 C S L 0 , C S L 1 コラム選択線、 F1 ~ F8 ヒューズ、 G I O , / G I O グローバルI O線、 G # 0 ~ G # 3 ゲート回路、 L I O 0 , / L I O 0 , L I O 1 , / L I O 1 ローカルI O線、 M A # 0 0 ~ M A # 3 1 メモリセルアレイ、 R D # 0 0 ~ R D # 3 1 ロウデコーダ、 S A B # 0 ~ S A B # 3 センスアンプ帯、 S C e l l 0 0 ~ S C e l l 1 5 1 スペアメモリセル、 S W スイッチアレイ、 S W L 0 0 ~ S W L 1 5 スペアワード線、 W L 0 0 ~ W L 7 F ワード線。

20

【 図 1 】

【 四 2 】

【 図 3 】

【 四 4 】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図 1 1】

【図 1 2】

【図 1 3】

【図 1 4】

【図15】

【図16】

【図17】

【図18】

【図19】

【図20】

【図21】

---

フロントページの続き

(72)発明者 田中 信二

東京都千代田区丸の内二丁目2番3号 三菱電機株式会社内

F ターム(参考) 5L106 AA01 CC04 CC17 DD00 EE07

5M024 AA50 AA52 AA87 AA90 AA91 BB02 BB22 BB30 BB39 CC20

CC50 CC90 DD06 DD20 DD62 DD73 DD77 DD80 DD85 EE05

EE10 EE30 MM04 MM10 MM12 MM15 PP01 PP02 PP03 PP07