(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第6178836号

(P6178836)

(45) 発行日 平成29年8月9日(2017.8.9)

(24) 登録日 平成29年7月21日(2017.7.21)

(51) Int.Cl.

F 1

|              |           |             |      |

|--------------|-----------|-------------|------|

| HO1L 29/786  | (2006.01) | HO1L 29/78  | 617K |

| HO1L 21/336  | (2006.01) | HO1L 29/78  | 618B |

| HO1L 21/8234 | (2006.01) | HO1L 29/78  | 617S |

| HO1L 27/088  | (2006.01) | HO1L 27/088 | E    |

| HO1L 29/49   | (2006.01) | HO1L 29/58  | G    |

請求項の数 2 (全 34 頁) 最終頁に続く

(21) 出願番号 特願2015-250736 (P2015-250736)

(22) 出願日 平成27年12月23日 (2015.12.23)

(62) 分割の表示 特願2011-157783 (P2011-157783)

の分割

原出願日 平成23年7月19日 (2011.7.19)

(65) 公開番号 特開2016-76725 (P2016-76725A)

(43) 公開日 平成28年5月12日 (2016.5.12)

審査請求日 平成27年12月28日 (2015.12.28)

(31) 優先権主張番号 特願2010-171597 (P2010-171597)

(32) 優先日 平成22年7月30日 (2010.7.30)

(33) 優先権主張国 日本国 (JP)

(73) 特許権者 000153878

株式会社半導体エネルギー研究所

神奈川県厚木市長谷398番地

(72) 発明者 山崎 舜平

神奈川県厚木市長谷398番地 株式会社

半導体エネルギー研究所内

審査官 竹口 泰裕

最終頁に続く

(54) 【発明の名称】半導体装置

## (57) 【特許請求の範囲】

## 【請求項 1】

基板上の酸化物半導体層と、

前記酸化物半導体層上のソース電極と、

前記酸化物半導体層上のドレイン電極と、

前記ソース電極上及び前記ドレイン電極上の絶縁層と、

前記絶縁層上のゲート電極と、を有し、

前記酸化物半導体層は、前記ソース電極及び前記ドレイン電極と重ならない第1の領域を有し、

前記絶縁層は、前記第1の領域と接する第2の領域を有し、

前記ゲート電極は、前記絶縁層を介して前記第1の領域と対向する第3の領域と、前記絶縁層を介して前記ソース電極の側面と対向する第4の領域と、前記絶縁層を介して前記ドレイン電極の側面と対向する第5の領域と、を有し、

前記ゲート電極は、前記絶縁層を介して前記ソース電極の上面と重なる領域を有さず、

前記ゲート電極は、前記絶縁層を介して前記ドレイン電極の上面と重なる領域を有さず

前記ゲート電極の上面は、前記絶縁層の最上面より低い領域を有することを特徴とする半導体装置。

## 【請求項 2】

基板上の酸化物半導体層と、

10

20

前記酸化物半導体層上のソース電極と、

前記酸化物半導体層上のドレイン電極と、

前記ソース電極上の第1の絶縁層と、

前記ドレイン電極上の第2の絶縁層と、

前記第1の絶縁層上、前記第2の絶縁層上、前記酸化物半導体層上の第3の絶縁層と、

前記第3の絶縁層上のゲート電極と、を有し、

前記酸化物半導体層は、前記ソース電極及び前記ドレイン電極と重ならない第1の領域を有し、

前記第3の絶縁層は、前記第1の領域と接する第2の領域を有し、

前記ゲート電極は、前記第3の絶縁層を介して前記第1の領域と対向する第3の領域と

前記第3の絶縁層を介して前記ソース電極の側面と対向する第4の領域と、前記第3の絶縁層を介して前記ドレイン電極の側面と対向する第5の領域と、を有し、

前記ゲート電極は、前記第3の絶縁層を介して前記ソース電極の上面と重なる領域を有さず、

前記ゲート電極は、前記第3の絶縁層を介して前記ドレイン電極の上面と重なる領域を有さず、

前記ゲート電極の上面は、前記第3の絶縁層の最上面より低い領域を有することを特徴とする半導体装置。

【発明の詳細な説明】

【技術分野】

20

【0001】

発明の技術分野は、半導体装置に関する。ここで、半導体装置とは、半導体特性を利用することで機能する素子および装置全般を指すものである。

【背景技術】

【0002】

金属酸化物は多様に存在し、さまざまな用途に用いられている。酸化インジウムはよく知られた材料であり、液晶表示装置などに必要とされる透明電極の材料として用いられている。

【0003】

金属酸化物の中には半導体特性を示すものがある。半導体特性を示す金属酸化物としては、例えば、酸化タンゲステン、酸化錫、酸化インジウム、酸化亜鉛などがあり、このような金属酸化物をチャネル形成領域に用いた薄膜トランジスタが既に知られている（例えば、特許文献1乃至特許文献4、非特許文献1等参照）。

【0004】

ところで、金属酸化物には、一元系酸化物のみでなく多元系酸化物も知られている。例えば、ホモロガス相を有する $InGaO_3$  ( $ZnO$ )<sub>m</sub> ( $m$  : 自然数) は、In、GaおよびZnを有する多元系酸化物半導体として知られている（例えば、非特許文献2乃至非特許文献4等参照）。

【0005】

そして、上記のようなIn-Ga-Zn系酸化物で構成される酸化物半導体も、薄膜トランジスタのチャネル形成領域に適用可能であることが確認されている（例えば、特許文献5、非特許文献5および非特許文献6等参照）。

【先行技術文献】

【特許文献】

【0006】

【特許文献1】特開昭60-198861号公報

【特許文献2】特開平8-264794号公報

【特許文献3】特表平11-505377号公報

【特許文献4】特開2000-150900号公報

【特許文献5】特開2004-103957号公報

10

20

30

40

50

## 【非特許文献】

## 【0007】

【非特許文献1】M. W. Prins, K. O. Grosse-Holz, G. Muller, J. F. M. Cilleissen, J. B. Giesbers, R. P. Weening, and R. M. Wolf、「A ferroelectric transparent thin-film transistor」、*Appl. Phys. Lett.*、17 June 1996, Vol. 68 p. 3650 - 3652

【非特許文献2】M. Nakamura, N. Kimizuka, and T. Mohri、「The Phase Relations in the  $In_2O_3$  -  $Ga_2ZnO_4$  -  $ZnO$  System at 1350」、*J. Solid State Chem.*、1991, Vol. 93, p. 298 - 315 10

【非特許文献3】N. Kimizuka, M. Isobe, and M. Nakamura、「Syntheses and Single-Crystal Data of Homologous Compounds,  $In_2O_3(ZnO)_m$  ( $m = 3, 4$ , and  $5$ ),  $InGaO_3(ZnO)_3$ , and  $Ga_2O_3(ZnO)_m$  ( $m = 7, 8, 9$ , and  $16$ ) in the  $In_2O_3$  -  $ZnGa_2O_4$  -  $ZnO$  System」、*J. Solid State Chem.*、1995, Vol. 116, p. 170 - 178

【非特許文献4】中村真佐樹、君塚昇、毛利尚彦、磯部光正、「ホモロガス相、 $InFeO_3(ZnO)_m$  ( $m$  : 自然数) とその同型化合物の合成および結晶構造」、固体物理、1993年、Vol. 28、No. 5、p. 317 - 327 20

【非特許文献5】K. Nomura, H. Ohta, K. Ueda, T. Kamiya, M. Hirano, and H. Hosono、「Thin-film transistor fabricated in single-crystalline transparent oxide semiconductor」、*SCIENCE*、2003, Vol. 300, p. 1269 - 1272

【非特許文献6】K. Nomura, H. Ohta, A. Takagi, T. Kamiya, M. Hirano, and H. Hosono、「Room-temperature fabrication of transparent flexible thin-film transistors using amorphous oxide semiconductors」、*NATURE*、2004, Vol. 432 p. 488 - 492 30

## 【発明の概要】

## 【発明が解決しようとする課題】

## 【0008】

ところで、酸化物半導体を用いたトランジスタにおいても、トランジスタの動作の高速化、トランジスタの低消費電力化、低価格化、などを達成するためには、トランジスタの微細化を図ることが重要である。

## 【0009】

しかし、その一方でトランジスタの微細化を図ることにより発生する不良が大きな問題となる。例えば、トランジスタの微細化を図ることにより生じる問題として、導電層を配線や電極に加工する際に用いるマスクの位置がずれ、設計寸法通りにトランジスタを形成できなくなることが挙げられる。特にトップゲート型のトランジスタの作製においてゲート電極を形成する際、酸化物半導体層上のソース電極とドレイン電極に挟まれた領域内にゲート電極を形成することが好ましいが、トランジスタの微細化を図ることによって当該領域は非常に狭くなるため、当該領域上にゲート電極を精確に形成することは困難になる。

## 【0010】

また、ゲート電極と、酸化物半導体層上のソース電極とドレイン電極に挟まれた領域と、が十分重畳するようにゲート電極を大きく形成すると、ゲート電極と当該トランジスタの 40

ソース電極またはドレイン電極とが余分に重畳し、寄生容量の増大を招く恐れがある。

【0011】

酸化物半導体を用いたトランジスタは、室温においてシリコンを用いたトランジスタと比較してオフ電流が小さいことが知られている。しかし、上述のようにゲート電極の位置がずれたり、トランジスタの寄生容量が増大すると、このようなオフ電流に代表される、酸化物半導体を用いたトランジスタのトランジスタ特性が生かされず、一方で当該トランジスタを用いた半導体装置の性能や歩留まりを低下させることになる。

【0012】

そこで、開示する発明の一態様は、不良を抑制しつつ微細化を達成する半導体装置の作製方法を提供することを目的の一とする。

10

【課題を解決するための手段】

【0013】

開示する発明の一態様は、絶縁表面上に、酸化物半導体層と、酸化物半導体層と接するソース電極およびドレイン電極と、ソース電極上の絶縁層と、ドレイン電極上の絶縁層と、を形成し、酸化物半導体層、ソース電極、ドレイン電極および絶縁層上にゲート絶縁層を形成し、ソース電極とドレイン電極に挟まれた領域の少なくとも一部と重畳するように、ゲート絶縁層上に導電層を形成し、導電層を覆うように絶縁膜を形成し、導電層におけるソース電極またはドレイン電極と重畳する領域の少なくとも一部が露出するように絶縁膜を加工し、導電層の露出した領域をエッチングして、ソース電極とドレイン電極に挟まれた領域の少なくとも一部と重畳するゲート電極を自己整合的に形成する半導体装置の作製方法である。

20

【0014】

上記において、ゲート電極のゲート絶縁層の最上面より上部は、ソース電極およびドレイン電極とは重畳しないようにすることが好ましい。

【0015】

開示する発明の他の一態様は、絶縁表面上に、酸化物半導体層と、酸化物半導体層と接するソース電極およびドレイン電極と、ソース電極上の絶縁層と、ドレイン電極上の絶縁層と、を形成し、酸化物半導体層、ソース電極、ドレイン電極および絶縁層上にゲート絶縁層を形成し、ソース電極とドレイン電極に挟まれた領域の少なくとも一部と重畳するように、ゲート絶縁層上に導電層を形成し、ゲート絶縁層におけるソース電極またはドレイン電極と重畳する領域の少なくとも一部が露出するように導電層を加工して、ソース電極とドレイン電極に挟まれた領域の少なくとも一部と重畳するゲート電極を自己整合的に形成する半導体装置の作製方法である。

30

【0016】

上記において、ゲート電極の上面がゲート絶縁層の最上面より低いことが好ましい。

【0017】

また、ソース電極およびドレイン電極は、少なくとも酸化物半導体層の上面の一部と接するようにしても良いし、酸化物半導体層が、少なくともソース電極およびドレイン電極の上面の一部と接するようにしてもよい。また、ゲート電極を形成する際に残存した導電層の一部を加工して、配線を形成するようにしてもよい。また、ソース電極の端部とドレイン電極の端部との間隔が10nm以上200nm以下であることが好ましい。

40

【0018】

ここで半導体装置とは、半導体特性を利用することで機能しうる装置全般を指す。例えば、表示装置や記憶装置、集積回路などは半導体装置に含まれうる。

【0019】

また、上記半導体装置において、半導体は酸化物半導体に限定されず、例えば、シリコン、ゲルマニウム、シリコンゲルマニウム、炭化シリコン、またはガリウムヒ素等の非晶質半導体、微結晶半導体、多結晶半導体または単結晶半導体などを用いる構成としても良い。

【0020】

50

また、本明細書等において「上」や「下」の用語は、構成要素の位置関係が「直上」または「直下」であることを限定するものではない。例えば、「ゲート絶縁層上のゲート電極」の表現であれば、ゲート絶縁層とゲート電極との間に他の構成要素を含むものを除外しない。

【0021】

また、本明細書等において「電極」や「配線」の用語は、これらの構成要素を機能的に限定するものではない。例えば、「電極」は「配線」の一部として用いられることがあり、その逆もまた同様である。さらに、「電極」や「配線」の用語は、複数の「電極」や「配線」が一体となって形成されている場合などをも含む。

【0022】

また、「ソース」や「ドレイン」の機能は、異なる極性のトランジスタを採用する場合や、回路動作において電流の方向が変化する場合などには入れ替わることがある。このため、本明細書においては、「ソース」や「ドレイン」の用語は、入れ替えて用いることができるものとする。

【0023】

また、本明細書等において、「電気的に接続」には、「何らかの電気的作用を有するもの」を介して接続されている場合が含まれる。ここで、「何らかの電気的作用を有するもの」は、接続対象間での電気信号の授受を可能とするものであれば、特に制限を受けない。例えば、「何らかの電気的作用を有するもの」には、電極や配線をはじめ、トランジスタなどのスイッチング素子、抵抗素子、インダクタ、キャパシタ、その他の各種機能を有する素子などが含まれる。

【発明の効果】

【0024】

開示する発明の一態様によって、微細化を図ったトランジスタにおいて、酸化物半導体層上のソース電極とドレイン電極に挟まれた領域内にゲート電極を精確且つ容易に形成し、且つゲート電極が、ソース電極およびドレイン電極と重畳することを防ぎ、寄生容量の増大を抑制することができる。

【0025】

このような効果により、微細化に伴う問題点が解消されることになるため、結果として、トランジスタサイズを十分に小さくすることが可能になる。トランジスタサイズを十分に小さくすることで、半導体装置の占める面積が小さくなり、半導体装置の取り数が増大する。これにより、半導体装置あたりの製造コストは抑制される。また、半導体装置が小型化されるため、従来の半導体装置と同程度の大きさでさらに機能が高められた半導体装置を実現することができる。また、チャネル長の縮小による、動作の高速化、低消費電力化などの効果を得ることもできる。つまり、開示する発明の一態様により酸化物半導体を用いたトランジスタの微細化が達成されることで、これに付随する様々な効果を得ることが可能である。

【0026】

このように、開示する発明の一態様によって、不良を抑制しつつ、微細化を達成する半導体装置の作製方法を提供することができる。

【図面の簡単な説明】

【0027】

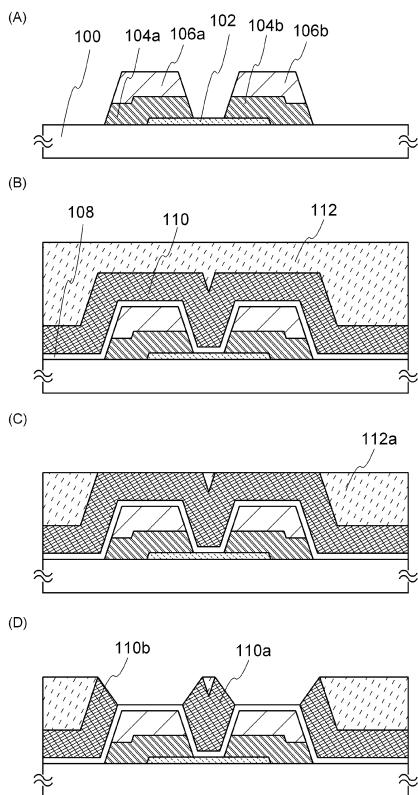

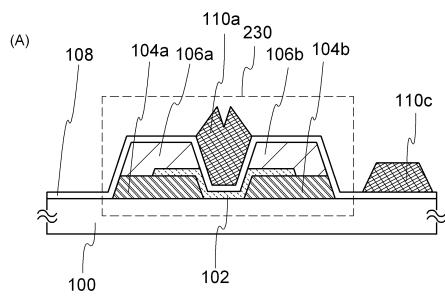

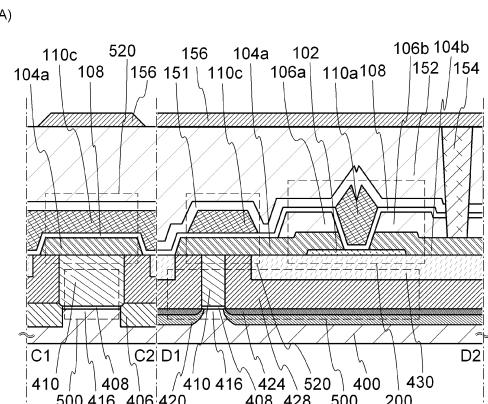

【図1】半導体装置の作製工程に係る断面図。

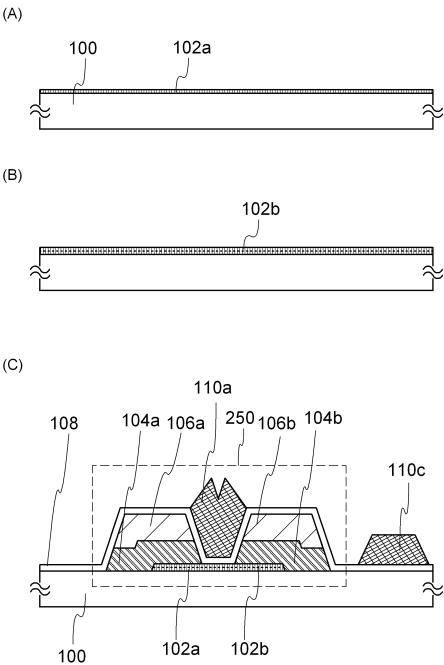

【図2】半導体装置の作製工程に係る断面図。

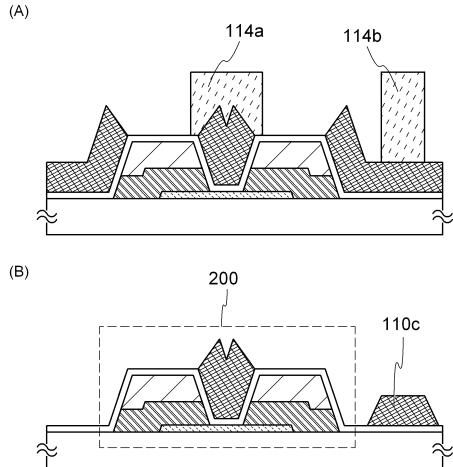

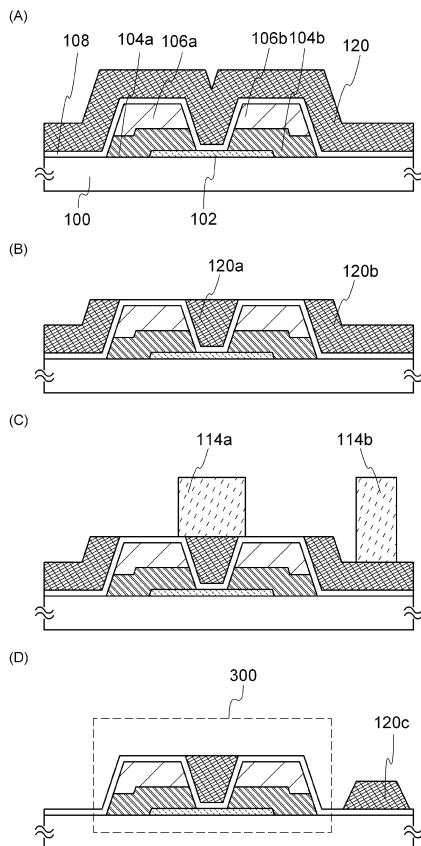

【図3】半導体装置の作製工程に係る断面図。

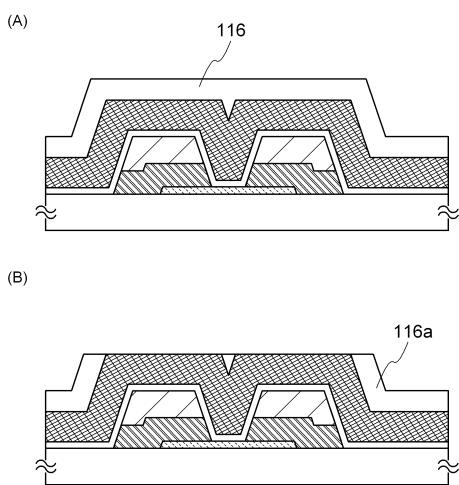

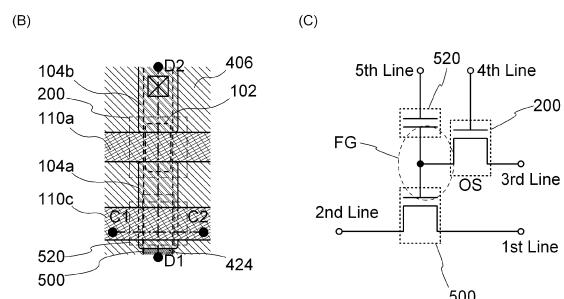

【図4】半導体装置の断面図。

【図5】半導体装置の断面図。

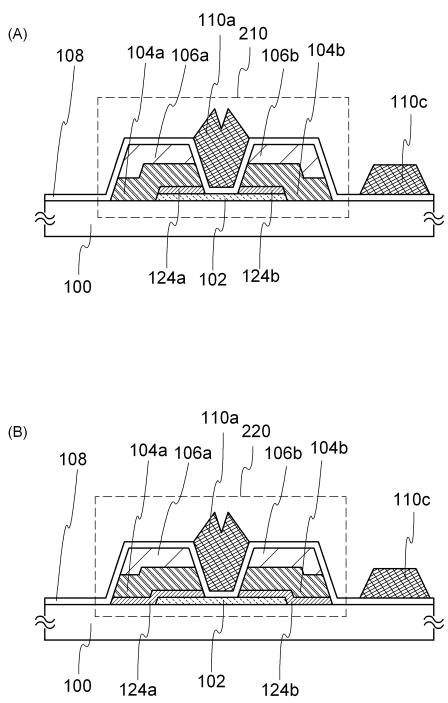

【図6】半導体装置の作製工程に係る断面図。

【図7】半導体装置の作製工程に係る断面図。

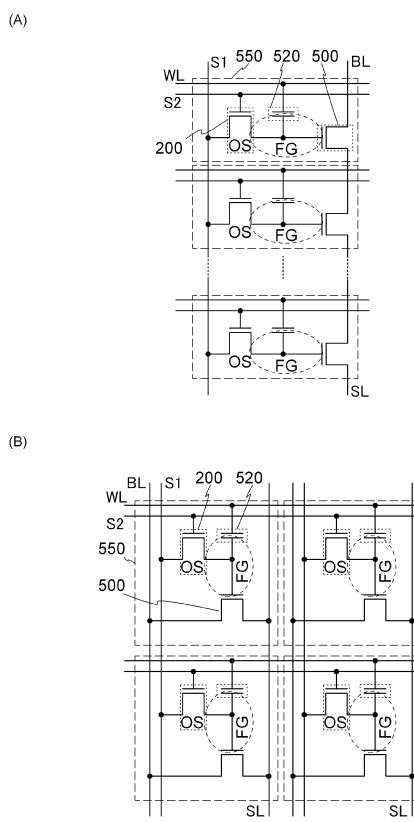

【図8】半導体装置の断面図、平面図および回路図。

10

20

30

40

50

【図9】半導体装置の回路図。

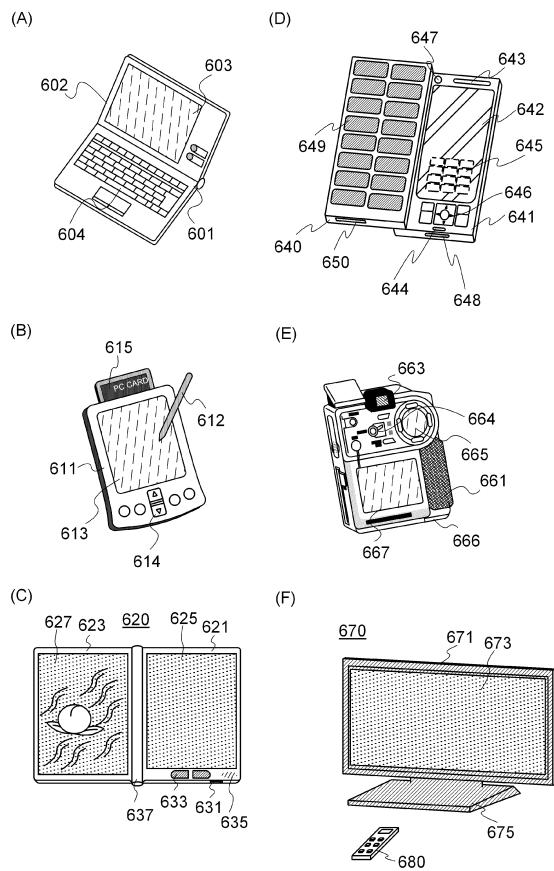

【図10】電子機器の例。

【発明を実施するための形態】

【0028】

本発明の実施の形態の一例について、図面を用いて以下に説明する。但し、本発明は以下の説明に限定されず、本発明の趣旨およびその範囲から逸脱することなくその形態および詳細を様々に変更し得ることは当業者であれば容易に理解される。従って、本発明は以下に示す実施の形態の記載内容に限定して解釈されるものではない。

【0029】

なお、図面等において示す各構成の、位置、大きさ、範囲などは、理解の簡単のため、実際の位置、大きさ、範囲などを表していない場合がある。このため、開示する発明は、必ずしも、図面等に開示された位置、大きさ、範囲などに限定されない。

10

【0030】

なお、本明細書等における「第1」、「第2」、「第3」などの序数は、構成要素の混同を避けるために付すものであり、数的に限定するものではないことを付記する。

【0031】

(実施の形態1)

本実施の形態では、半導体装置および半導体装置の作製方法の一形態を、図1乃至図6を用いて説明する。

【0032】

20

図1乃至図3に、開示する発明の一態様に係る半導体装置の作製方法の例として、トランジスタ200の作製工程の断面図を示す。ここで、図2(B)に示すトランジスタ200は、基板100上の、酸化物半導体層102、ソース電極104a、ドレイン電極104b、絶縁層106a、絶縁層106b、ゲート絶縁層108およびゲート電極110aを含む。またゲート絶縁層108上に、ゲート電極110aと同様の材料からなる配線110cが形成されている。

【0033】

ここで、トランジスタ200のチャネル長(L)は10nm以上200nm以下とするのが好ましく、より好ましくは20nm以上100nm以下とする。このようにトランジスタの微細化を図り、チャネル長(L)を縮小することによりトランジスタの動作高速化および低消費電力化を図ることができる。なお、本明細書中において、チャネル長(L)は、ソース電極104aの端部とドレイン電極104bの端部との間隔によって決定されるものとする。

30

【0034】

また、ゲート絶縁層108上に設けられたゲート電極110aは、酸化物半導体層102上のソース電極104aとドレイン電極104bに挟まれた領域の少なくとも一部と重畳する。さらに、ゲート電極110aにおいてゲート絶縁層108の最上面より上部がソース電極104aおよびドレイン電極104bと重畳しないようにすることができる。このような構成とすることにより、ゲート電極110aを酸化物半導体層102上のソース電極104aとドレイン電極104bに挟まれた領域に精確に形成し、且つ寄生容量の増大を抑制できるので、トランジスタ200に設計通りのトランジスタ特性を有せしめることができる。なお、本明細書中において、ゲート絶縁層の最上面とは、ゲート絶縁層の上面においてソース電極またはドレイン電極と重畳し、且つ基板に対して平行な面を指す。また、ソース電極104a、ドレイン電極104b、をテープ形状とし、ゲート電極110aにおけるゲート絶縁層108の最上面より下部を逆テープ形状とする場合、ゲート絶縁層108の最上面より下部において、ゲート電極110aの逆テープ形状部分はソース電極104aおよびドレイン電極104bと重畳してもよい。その場合、当該箇所で、ゲート電極110aにおいてゲート絶縁層108の最上面より上部がソース電極104aおよびドレイン電極104bと重畳してもよい。

40

【0035】

50

以下、図1(A)乃至図1(D)、図2(A)および図2(B)、図3(A)および図3(B)を用いて、図2(B)に示すトランジスタ200の作製工程の一例について説明する。

#### 【0036】

まず、絶縁表面を有する基板100上に、酸化物半導体層102と、酸化物半導体層102と接するソース電極104aおよびドレイン電極104bと、を形成する(図1(A)参照)。図1(A)に示す構成においては、基板100上に酸化物半導体層102を形成した後に導電層を成膜し、当該導電層をエッチングして、酸化物半導体層102の上面の一部と接するようにソース電極104aおよびドレイン電極104bを形成する。

#### 【0037】

基板100の材質等に大きな制限はないが、少なくとも、後の熱処理に耐えうる程度の耐熱性を有していることが必要となる。例えば、ガラス基板、セラミック基板、石英基板、サファイア基板などを、基板100として用いることができる。また、シリコンや炭化シリコンなどの単結晶半導体基板、多結晶半導体基板、シリコンゲルマニウムなどの化合物半導体基板、SOI基板などを適用することも可能であり、これらの基板上に半導体素子が設けられたものを、基板100として用いてもよい。

#### 【0038】

また、基板100として、可撓性基板を用いてもよい。可撓性基板上にトランジスタを設ける場合、例えば、可撓性基板上に直接的にトランジスタを作り込むことができる。

#### 【0039】

ここで、酸化物半導体層102を形成する前に基板100上に下地絶縁層を形成しておくのが好ましい。当該下地絶縁層は、後述するゲート絶縁層108と同様の材料および方法で形成することができる。

#### 【0040】

酸化物半導体層102に用いる材料としては、四元系金属酸化物であるIn-Sn-Ga-Zn-O系の材料や、三元系金属酸化物であるIn-Ga-Zn-O系の材料、In-Sn-Zn-O系の材料、In-Al-Zn-O系の材料、Sn-Ga-Zn-O系の材料、Al-Ga-Zn-O系の材料、Sn-Al-Zn-O系の材料や、二元系金属酸化物であるIn-Zn-O系の材料、Sn-Zn-O系の材料、Al-Zn-O系の材料、Zn-Mg-O系の材料、Sn-Mg-O系の材料、In-Mg-O系の材料、In-Ga-O系の材料や、一元系金属の酸化物であるIn-O系の材料、Sn-O系の材料、Zn-O系の材料などを用いることができる。また、上記の材料にSiO<sub>2</sub>を含ませてもよい。ここで、例えば、In-Ga-Zn-O系の材料とは、インジウム(In)、ガリウム(Ga)、亜鉛(Zn)を有する酸化物膜、という意味であり、その組成比は特に問わない。また、InとGaとZn以外の元素を含んでいてもよい。

#### 【0041】

また、酸化物半導体層102は、化学式InMO<sub>3</sub>(ZnO)<sub>m</sub>(m>0)で表記される材料を用いた薄膜とすることができます。ここで、Mは、Ga、Al、MnおよびCoから選ばれた一または複数の金属元素を示す。例えば、Mとして、Ga、GaおよびAl、GaおよびMn、またはGaおよびCoなどを用いることができる。

#### 【0042】

また、酸化物半導体層102の厚さは、3nm以上30nm以下とするのが望ましい。酸化物半導体層102を厚くしすぎると(例えば、膜厚を50nm以上)、トランジスタがノーマリーオンとなってしまうおそれがあるためである。

#### 【0043】

酸化物半導体層は、水素、水、水酸基又は水素化物などの不純物が混入しにくい方法で作製するのが望ましい。例えば、スパッタリング法などを用いて作製することができる。

#### 【0044】

本実施の形態では、酸化物半導体層を、In-Ga-Zn-O系の酸化物半導体成膜用ターゲットを用いたスパッタリング法により形成する。

10

20

30

40

50

## 【0045】

In - Ga - Zn - O 系の酸化物半導体成膜用ターゲットとしては、例えば、組成比として、In<sub>2</sub>O<sub>3</sub> : Ga<sub>2</sub>O<sub>3</sub> : ZnO = 1 : 1 : 1 [mol 数比] の酸化物半導体成膜用ターゲットを用いることができる。なお、酸化物半導体成膜用ターゲットの材料および組成を上述に限定する必要はない。例えば、In<sub>2</sub>O<sub>3</sub> : Ga<sub>2</sub>O<sub>3</sub> : ZnO = 1 : 1 : 2 [mol 数比] の組成比の酸化物半導体成膜用ターゲットを用いることもできる。

## 【0046】

また、酸化物半導体としてIn - Zn - O 系の材料を用いる場合、用いるターゲットの組成比は、原子数比で、In : Zn = 50 : 1 ~ 1 : 2 (モル数比に換算するとIn<sub>2</sub>O<sub>3</sub> : ZnO = 25 : 1 ~ 1 : 4)、好ましくはIn : Zn = 20 : 1 ~ 1 : 1 (モル数比に換算するとIn<sub>2</sub>O<sub>3</sub> : ZnO = 10 : 1 ~ 1 : 2)、さらに好ましくはIn : Zn = 15 : 1 ~ 1.5 : 1 (モル数比に換算するとIn<sub>2</sub>O<sub>3</sub> : ZnO = 15 : 2 ~ 3 : 4)とする。例えば、In - Zn - O 系酸化物半導体の形成に用いるターゲットは、原子数比がIn : Zn : O = X : Y : Zのとき、Z > 1.5X + Yとする。

10

## 【0047】

酸化物半導体成膜用ターゲットの充填率は、90%以上100%以下、好ましくは95%以上99.9%以下とする。充填率の高い酸化物半導体成膜用ターゲットを用いることにより、成膜した酸化物半導体層を緻密な膜とすることができます。

## 【0048】

成膜の雰囲気は、希ガス(代表的にはアルゴン)雰囲気下、酸素雰囲気下、または、希ガスと酸素の混合雰囲気下などとすればよい。また、酸化物半導体層への水素、水などの不純物の混入を防ぐために、水素、水などの不純物が十分に除去された高純度ガスを用いた雰囲気とすることが望ましい。

20

## 【0049】

例えば、酸化物半導体層は、次のように形成することができる。

## 【0050】

まず、減圧状態に保持された成膜室内に基板100を保持し、基板温度が、200を超えて500以下、好ましくは300を超えて500以下、より好ましくは350以上450以下となるように加熱する。

## 【0051】

30

次に、成膜室内の残留水分を除去しつつ、水素、水などの不純物が十分に除去された高純度ガスを導入し、上記酸化物半導体成膜用ターゲットを用いて基板100上に酸化物半導体層を成膜する。成膜室内の残留水分を除去するためには、排気手段として、クライオポンプ、イオンポンプ、チタンサブリメーションポンプなどの吸着型の真空ポンプを用いることが望ましい。また、排気手段は、ターボポンプにコールドトラップを加えたものであってもよい。クライオポンプを用いて排気した成膜室は、例えば、水素、水などの不純物(より好ましくは炭素原子を含む化合物も)などが除去されているため、当該成膜室で成膜した酸化物半導体層に含まれる水素、水などの不純物の濃度を低減することができる。

## 【0052】

成膜中の基板温度が低温(例えば、100以下)の場合、酸化物半導体層に水素、水などの不純物が混入するおそれがあるため、基板100を上述の温度で加熱することが好ましい。基板100を上述の温度で加熱して、酸化物半導体層の成膜を行うことにより、基板は高温となるため、水素結合は熱により切断され、酸化物半導体層に取り込まれにくい。したがって、基板100が上述の温度で加熱された状態で、酸化物半導体層の成膜を行うことにより、酸化物半導体層に含まれる水素、水などの不純物の濃度を十分に低減することができる。また、スパッタリングによる損傷を軽減することができる。

40

## 【0053】

なお、酸化物半導体層に含まれる水の含有量の測定法としては、昇温脱離分析法(TDS : Thermal Desorption Spectroscopy)が挙げられる。

例えば、室温から400程度に温度を上げていくことにより、200から300程

50

度にかけて酸化物半導体層に含まれる水、水素、水酸基などの脱離を観測することができる。

【0054】

成膜条件の一例として、基板とターゲットの間との距離を60mm、圧力を0.4Pa、直流(DC)電源を0.5kW、基板温度を400、成膜雰囲気を酸素(酸素流量比率100%)雰囲気とする。なお、パルス直流電源を用いると、成膜時に発生する粉状物質(パーティクル、ごみともいう)が軽減でき、膜厚分布も均一となるため好ましい。

【0055】

なお、酸化物半導体層をスパッタリング法により形成する前に、アルゴンガスを導入してプラズマを発生させる逆スパッタを行い、基板100の表面に付着している粉状物質(パーティクル、ごみともいう)を除去することが好ましい。逆スパッタとは、基板に電圧を印加し、基板近傍にプラズマを形成して、基板側の表面を改質する方法である。なお、アルゴンに代えて、窒素、ヘリウム、酸素などのガスを用いてもよい。

【0056】

酸化物半導体層の加工は、所望の形状のマスクを酸化物半導体層上に形成した後、当該酸化物半導体層をエッチングすることによって行うことができる。上述のマスクは、フォトリソグラフィなどの方法を用いて形成することができる。または、インクジェット法などの方法を用いてマスクを形成しても良い。なお、酸化物半導体層のエッチングは、ドライエッチングでもウェットエッチングでもよい。もちろん、これらを組み合わせて用いてもよい。

10

【0057】

このようにして形成された酸化物半導体層102に対して、熱処理を行ってもよい。熱処理を行うことによって、酸化物半導体層102中に含まれる水素、水などの不純物をさらに除去し、酸化物半導体層102の構造を整え、エネルギーギャップ中の欠陥準位を低減することができる。

20

【0058】

熱処理の温度は、不活性ガス雰囲気下、250以上700以下、好ましくは450以上600以下、または基板の歪み点未満とする。不活性ガス雰囲気としては、窒素、または希ガス(ヘリウム、ネオン、アルゴン等)を主成分とする雰囲気であって、水素、水などの不純物が含まれない雰囲気を適用するのが望ましい。例えば、熱処理装置に導入する窒素や、ヘリウム、ネオン、アルゴン等の希ガスの純度を、6N(99.9999%)以上、好ましくは7N(99.99999%)以上(すなわち、不純物濃度が1ppm以下、好ましくは0.1ppm以下)とする。

30

【0059】

熱処理は、例えば、抵抗発熱体などを用いた電気炉に被処理物を導入し、窒素雰囲気下、450、1時間の条件で行うことができる。この間、酸化物半導体層102は大気に触れさせず、水素、水などの不純物の混入が生じないようにする。

【0060】

ところで、上述の熱処理には水素、水などの不純物を除去する効果があるから、当該熱処理を、脱水化処理や脱水素化処理などと呼ぶこともできる。当該熱処理は、例えば、酸化物半導体層を成膜した後などのタイミングにおいて行うことも可能である。また、このような脱水化処理、脱水素化処理は、一回に限らず複数回行っても良い。

40

【0061】

次に、酸化物半導体層102に対して、酸素を供給する処理(酸素ドープ処理などとも呼ぶ)を行うことが望ましい。酸素を供給する処理としては、酸素雰囲気における熱処理や、酸素プラズマによる処理などがある。また、電界で加速した酸素イオンを照射して、酸素を添加してもよい。

【0062】

なお、酸素の添加をより好適に行うために、基板には電気的なバイアスを加えておいても良い。

50

## 【0063】

酸化物半導体層102に酸素ドープ処理を行うことにより、酸化物半導体層102中、酸化物半導体層102界面近傍、または、酸化物半導体層102中および該界面近傍に酸素を含有させることができる。この場合、酸素の含有量は、酸化物半導体層の化学量論比を超える程度とするのが望ましい。

## 【0064】

なお、酸素ドープ処理を行った酸化物半導体層102に熱処理を行っても良い。当該熱処理の温度は、250以上700以下、好ましくは400以上600以下、または基板の歪み点未満とする。

## 【0065】

当該熱処理により、酸素と酸化物半導体層中に含まれる水素との反応によって生成された水、水酸化物(OH)などを酸化物半導体層から除去することができる。また、当該熱処理によって、上述の酸素ドープ処理において酸化物半導体層102などに混入した水素なども除去することができる。熱処理は、水、水素などが十分に低減された窒素、酸素、超乾燥空気(CRDS(キャビティリングダウンレーザー分光法)方式の露点計を用いて測定した場合の水分量が20ppm(露点換算で-55)以下、好ましくは1ppm以下、好ましくは10ppb以下の空気)、希ガス(アルゴン、ヘリウムなど)などの雰囲気下で行えばよく、特に酸素を含む雰囲気で行うことが好ましい。また、熱処理装置に導入する窒素、酸素、または希ガスの純度は、6N(99.9999%)以上(即ち不純物濃度を1ppm以下)とするのが好ましく、7N(99.99999%)以上(即ち不純物濃度を0.1ppm以下)とすると、より好ましい。

10

## 【0066】

なお、酸素ドープ処理のタイミングは、上記に限定されない。ただし、脱水化等を目的とする熱処理以降に行うことが望ましい。

## 【0067】

ソース電極104aおよびドレイン電極104bは、酸化物半導体層102上にスパッタリング法や真空蒸着法などを用いて導電層を形成し、当該導電層を加工して形成する。このようにソース電極104aおよびドレイン電極104bを形成することにより、ソース電極104aおよびドレイン電極104bは、酸化物半導体層102の上面の一部と接することになる。ソース電極104aおよびドレイン電極104bの膜厚を厚くすると、それぞれの電極およびその配線の抵抗を下げる効果があるのみならず、後述するように、ゲート電極110aを厚く形成することができるため、ゲート電極110aの抵抗を下げる事にも効果がある。一方で、ゲート電極110aとソース電極104aおよびドレイン電極104bとの間の寄生容量が大きくなる。したがって、ここで、ソース電極104aおよびドレイン電極104bの膜厚は、例えば、50nm以上500nm以下とする。

20

## 【0068】

ここで形成されるソース電極104aの端部とドレイン電極104bの端部との間隔によって、トランジスタのチャネル長(L)が決定されることになる。トランジスタのチャネル長(L)は10nm以上200nm以下とするのが好ましく、より好ましくは20nm以上100nm以下とする。

30

## 【0069】

ソース電極104aおよびドレイン電極104bに用いる導電層としては、例えば、アルミニウム、クロム、銅、タンタル、チタン、モリブデン、タンクスチタンから選ばれた元素を含む金属膜、または上述した元素を成分とする金属窒化物膜(窒化チタン膜、窒化モリブデン膜、窒化タンクスチタン膜)等を用いることができる。ソース電極104aおよびドレイン電極104bは、単層構造としても良いし、積層構造としてもよい。また、アルミニウム、銅などの金属膜の下側または上側の一方または双方にチタン、モリブデン、タンクスチタンなどの高融点金属膜またはそれらの金属窒化物膜(窒化チタン膜、窒化モリブデン膜、窒化タンクスチタン膜)を積層させた構成を用いても良い。

## 【0070】

40

50

また、ソース電極 104a およびドレイン電極 104b に用いる導電層は、導電性の金属酸化物で形成しても良い。導電性の金属酸化物としては酸化インジウム ( $In_2O_3$ )、酸化スズ ( $SnO_2$ )、酸化亜鉛 ( $ZnO$ )、酸化インジウム酸化スズ合金 ( $In_2O_3 - SnO_2$ 、ITOと略記する)、酸化インジウム酸化亜鉛合金 ( $In_2O_3 - ZnO$ ) またはこれらの金属酸化物材料に酸化シリコンを含ませたものを用いることができる。

#### 【0071】

導電層の加工は、所望の形状のマスクを導電層上に形成した後、当該導電層をエッチングすることによって行うことができる。上述のマスクは、レジストマスクなどを用いることができる。当該レジストマスク形成時の露光には、紫外線や KrF レーザ光や ArF レーザ光などを用いるとよい。

10

#### 【0072】

なお、チャネル長  $L = 25\text{ nm}$  未満の露光を行う場合には、例えば、数 nm ~ 数 10 nm と極めて波長が短い超紫外線 (Extreme Ultraviolet) を用いて、レジストマスク形成時の露光を行うとよい。超紫外線による露光は、解像度が高く焦点深度も大きい。したがって、トランジスタのチャネル長 ( $L$ ) を微細化することが可能であり、回路の動作速度を高めることができる。

#### 【0073】

また、いわゆる多階調マスクによって形成されたレジストマスクを用いてエッチング工程を行ってもよい。多階調マスクを用いて形成されたレジストマスクは、複数の膜厚を有する形状となり、アッシングによってさらに形状を変形させることができるために、異なるパターンに加工する複数のエッチング工程に用いることが可能である。このため、一枚の多階調マスクによって、少なくとも二種類以上の異なるパターンに対応するレジストマスクを形成することができる。つまり、工程の簡略化が可能となる。

20

#### 【0074】

ソース電極 104a およびドレイン電極 104b となる導電層のエッチングには、ウェットエッチングまたはドライエッチングのいずれを用いても良いが、微細加工の観点からドライエッチングを用いることが好適である。所望の形状にエッチングできるよう、材料に合わせてエッチング条件 (エッチングガスやエッチング液、エッチング時間、温度等) を適宜設定するものとする。ソース電極 104a およびドレイン電極 104b となる導電層のエッチングにドライエッチングを用いる場合、エッチングガスとしては、例えば、塩素 ( $Cl_2$ )、三塩化ホウ素 ( $BCl_3$ )、四塩化ケイ素 ( $SiCl_4$ )、四フッ化メタン ( $CF_4$ )、六フッ化硫黄 ( $SF_6$ )、三フッ化窒素 ( $NF_3$ ) 等を用いることができ、これらのうちから複数を選択した混合ガスを用いることもできる。また、これらに、希ガス (ヘリウム ( $He$ )、アルゴン ( $Ar$ ))、酸素等を添加しても良い。

30

#### 【0075】

また、図 1 (A) に示すようにソース電極 104a およびドレイン電極 104b をテーパ形状としても良い。テーパ角は  $45^\circ$  以上  $90^\circ$  未満とし、好ましくは  $60^\circ$  以上  $80^\circ$  以下とすることができる。このようにソース電極 104a およびドレイン電極 104b をテーパ形状とすることにより、後に形成されるゲート絶縁層 108 の被覆性を向上し、段切れを防止することができる。なお、テーパ角とは、テーパ形状を有する層 (例えば、ソース電極 104a またはドレイン電極 104b) を、その断面に垂直な方向から観察した際に、当該層の側面と底面がなす傾斜角を示す。

40

#### 【0076】

なお、導電層のエッチングの際に、酸化物半導体層 102 の一部がエッチングされ、溝部 (凹部) を有する酸化物半導体層 102 となることもある。

#### 【0077】

その後、 $N_2O$ 、 $N_2$ 、または  $Ar$  などのガスを用いたプラズマ処理を行い、露出している酸化物半導体層 102 の表面に付着した水素、水などの不純物を除去してもよい。

#### 【0078】

次に、酸化物半導体層 102、ソース電極 104a およびドレイン電極 104b を覆うよ

50

うに絶縁層を形成し、フォトマスクを用いて当該絶縁層を加工して、ソース電極 104a 上に絶縁層 106a を、ドレイン電極 104b 上に絶縁層 106b を形成する（図1（A）参照）。

#### 【0079】

ここで、絶縁層 106a および絶縁層 106b は、例えば、酸化シリコン、窒化シリコン、酸化窒化シリコン、窒化酸化シリコンなどの材料を用いて形成することができる。また、絶縁層 106a および絶縁層 106b は、CVD法やスパッタ法等を用いて形成することができる。また絶縁層 106a および絶縁層 106b の膜厚は 10nm 以上 500nm 以下とするのが好ましい。

#### 【0080】

絶縁層 106a、絶縁層 106b の形成は、絶縁層上にレジストマスクを形成し、該レジストマスクを用いたエッティングにより行う。レジストマスクの形成はソース電極 104a およびドレイン電極 104b と同様の方法で行うことができ、同じフォトマスクを用いることが好ましい。絶縁層のエッティングには、ウェットエッティングまたはドライエッティングのいずれを用いても良いが、微細加工の観点からドライエッティングを用いることが好適である。絶縁層を所望の形状にエッティングできるよう、材料に合わせてエッティング条件（エッティングガスやエッティング液、エッティング時間、温度等）を適宜設定するものとする。ただし、トランジスタのチャネル長（L）を微細に加工するためには、ドライエッティングを用いるのが好ましい。ドライエッティングに用いるエッティングガスとしては、例えば、六フッ化硫黄（SF<sub>6</sub>）、三フッ化窒素（NF<sub>3</sub>）、トリフルオロメタン（CHF<sub>3</sub>）、オクタフルオロシクロブタン（C<sub>4</sub>F<sub>8</sub>）などのフッ素を含むガス、又は、四フッ化メタン（CF<sub>4</sub>）と水素の混合ガス等を用いることができ、希ガス（ヘリウム（He）、アルゴン（Ar）、キセノン（Xe））、一酸化炭素、又は二酸化炭素等を添加しても良い。

#### 【0081】

このように、絶縁層 106a および絶縁層 106b を設けることにより、ソース電極 104a とドレイン電極 104b に挟まれた領域の凹部を深くすることができるので、後に形成するゲート電極 110a の膜厚を十分に厚くすることができる。よって後に形成するゲート電極 110a が消失する、またはゲート電極 110a の膜厚が極端に薄くなることを防ぐことができる。これにより、ゲート電極 110a の導電性を十分に保持することができる。

#### 【0082】

また、絶縁層 106a および絶縁層 106b は必ずしも形成しなくても良い。例えば、ソース電極 104a およびドレイン電極 104b の膜厚を十分に厚くする場合、絶縁層 106a および絶縁層 106b を形成しなくても、後に形成するゲート電極 110a の膜厚を十分厚くすることができるので、絶縁層 106a および絶縁層 106b を形成しなくてもよい。

#### 【0083】

なお、ここでは、ソース電極 104a およびドレイン電極 104b を形成した後で絶縁層 106a および絶縁層 106b を形成する方法について説明したが、本実施の形態はこれに限られるものではない。例えば、酸化物半導体層 102 の上面の一部と接するようにソース電極 104a およびドレイン電極 104b を形成する場合、酸化物半導体層 102 上に導電層を成膜し、当該導電層上に絶縁層を成膜した後、当該絶縁層および当該導電層を同じレジストマスクを用いて加工して絶縁層 106a および絶縁層 106b、並びにソース電極 104a およびドレイン電極 104b を形成することができる。このようにして絶縁層 106a および絶縁層 106b、並びにソース電極 104a およびドレイン電極 104b を形成することにより、絶縁層 106a の端部がソース電極 104a の端部に、絶縁層 106b の端部がドレイン電極 104b の端部にそれぞれ概略一致するように形成することができるので、絶縁層 106a および絶縁層 106b がソース電極 104a およびドレイン電極 104b に対して位置ずれを起こすのを防ぐことができる。また、フォトマスクの枚数を低減することができるので、半導体装置のコスト削減を図ることができる。な

10

20

30

40

50

お、「概略一致」は、厳密な一致を要しない意味で用いる。例えば、「概略一致」の表現は、複数の層を同一のマスクを用いてエッチングして得られた形状における一致の程度を包含する。

【0084】

次に、酸化物半導体層102、ソース電極104a、ドレイン電極104b、絶縁層106aおよび絶縁層106b上にゲート絶縁層108を形成する(図1(B)参照)。

【0085】

ゲート絶縁層108は、例えば、酸化シリコン、窒化シリコン、酸化窒化シリコン、窒化酸化シリコンなどの材料を用いて形成する。また、ゲート絶縁層108は、酸化ガリウムを含む材料を用いて形成することもできる。また、酸化ガリウムを含む材料として、さらに酸化アルミニウムを加えた、酸化アルミニウムガリウムまたは酸化ガリウムアルミニウムを含む材料などを用いててもよい。ここで、酸化アルミニウムガリウムとは、ガリウムの含有量(原子%)よりアルミニウムの含有量(原子%)が多いものを示し、酸化ガリウムアルミニウムとは、ガリウムの含有量(原子%)がアルミニウムの含有量(原子%)以上のものを示す。また、酸化ハフニウム、酸化タンタル、酸化イットリウム、ハフニウムシリケート( $HfSi_xO_y$  ( $x > 0$ ,  $y > 0$ ))、窒素が添加されたハフニウムシリケート( $HfSi_xO_y$  ( $x > 0$ ,  $y > 0$ ))、窒素が添加されたハフニウムアルミネート( $HfAl_xO_y$  ( $x > 0$ ,  $y > 0$ ))、などの比誘電率が高い材料を採用しても良い。ゲート絶縁層108は、上述の材料を用いて単層構造または積層構造で形成することができる。

10

20

【0086】

ゲート絶縁層108として酸化ガリウム膜を用いた場合、 $Ga_2O_{3+x}$  ( $x > 0$ )とすることが好ましい。は、3.04以上3.09以下とすることが好ましい。または、ゲート絶縁層108として酸化アルミニウムガリウム膜を用いた場合、 $Al_xGa_{2-x}O_3$  ( $1 < x < 2$ ,  $x > 0$ )とすることが好ましい。または、ゲート絶縁層108として酸化ガリウムアルミニウム膜を用いた場合、酸素ドープを行うことにより、 $Al_xGa_{2-x}O_{3+x}$  ( $0 < x < 1$ ,  $x > 0$ )とすることが好ましい。

【0087】

なお、酸化物半導体層に用いられる酸化物半導体材料には、ガリウムを含むものが多い。このため、酸化ガリウムを含む材料を用いて、酸化物半導体層と接するゲート絶縁層108を形成する場合には、酸化物半導体層との界面の状態を良好に保つことができる。例えば、酸化物半導体層と酸化ガリウムを含む絶縁層とを接して設けることにより、酸化物半導体層と絶縁層の界面における水素のパイルアップを低減することができる。これは、酸化ガリウムを含む材料と、酸化物半導体材料との相性が良いことによる。

30

【0088】

なお、ゲート絶縁層108に酸化物半導体の成分元素と同じ族の元素を用いる場合には、同様の効果を得ることが可能である。つまり、酸化アルミニウムなどを含む材料を加えてゲート絶縁層108を形成することも有効である。なお、酸化アルミニウムは、水を透過させにくいという特性を有しているため、当該材料を用いることは、酸化物半導体層への水の侵入防止という点においても好ましい。例えば、上述のガリウムとアルミニウムを含有する酸化アルミニウムガリウム(または酸化ガリウムアルミニウム)などの材料を、ゲート絶縁層108に用いても良い。この場合、ガリウムを含有することに起因する効果と、アルミニウムを含有することに起因する効果を合わせて得ることができるために、好適である。例えば、酸化物半導体層と酸化アルミニウムガリウムを含む絶縁層とを接して設けることにより、酸化物半導体層への水の侵入を防ぎ、酸化物半導体層と絶縁層の界面における水素のパイルアップを十分に低減することができる。

40

【0089】

ゲート絶縁層108は、水素、水などの不純物を混入させない方法を用いて成膜することが好ましい。ゲート絶縁層108に水素、水などの不純物が含まれると、酸化物半導体層への水素、水などの不純物の侵入や、水素、水などの不純物による酸化物半導体層中の酸

50

素の引き抜き、などによって酸化物半導体層が低抵抗化（n型化）するおそれがあるためである。よって、ゲート絶縁層108はできるだけ水素、水などの不純物が含まれないよう作製することが好ましい。例えば、スパッタリング法によって成膜するのが好ましく、成膜する際に用いるスパッタガスとしては、水素、水などの不純物が除去された高純度ガスを用いることが好ましい。

【0090】

スパッタリング法としては、直流電源を用いるDCスパッタリング法、パルス的に直流バイアスを加えるパルスDCスパッタリング法、又はACスパッタリング法などを用いることができる。

【0091】

またゲート絶縁層108の形成後に、不活性ガス雰囲気下、または酸素雰囲気下で熱処理を行うのが望ましい。熱処理の温度は、200以上450以下、望ましくは250以上350以下である。例えば、窒素雰囲気下で250、1時間の熱処理を行えばよい。当該熱処理を行うことによって、トランジスタの電気的特性のばらつきを軽減することができる。また、ゲート絶縁層108が酸素を含む場合、酸化物半導体層102に酸素を供給し、酸化物半導体層102の酸素欠損を補填することができる。この意味において、当該熱処理を、加酸化（加酸素化）の熱処理と呼ぶこともできる。

【0092】

なお、本実施の形態では、ゲート絶縁層108の形成後に加酸化の熱処理を行っているが、加酸化の熱処理のタイミングはこれに限定されない。例えば、ゲート電極110aの形成後に加酸化の熱処理を行っても良い。また、脱水化または脱水素化の熱処理に続けて加酸化の熱処理を行っても良い。

【0093】

上述のように、脱水化または脱水素化の熱処理と、酸素ドープ処理または加酸化の熱処理とを適用し、酸化物半導体層102中の不純物を低減し、酸素欠損を補填することで、酸化物半導体層102を、その主成分以外の元素（不純物元素）が極力含まれないように高純度化することができる。高純度化された酸化物半導体層102中にはドナーに由来するキャリアが極めて少ない。

【0094】

次に、少なくともソース電極104aとドレイン電極104bに挟まれた領域の一部と重畳するように、ゲート絶縁層108上に導電層110を成膜する（図1（B）参照）。

【0095】

導電層110は、後の工程において、ゲート電極110aおよび配線110cを形成するために用いられる。導電層110は、ソース電極104aおよびドレイン電極104bを形成するために用いた導電層と同様の材料を用いて成膜することができる。また、導電層110はPVD法やCVD法を用いて成膜することができ、絶縁層106aと絶縁層106b並びにソース電極104aとドレイン電極104bに挟まれた凹部に導電層110の一部が埋め込まれるように導電層110を成膜する。

【0096】

次に、導電層110を覆うように絶縁膜112を形成する（図1（B）参照）。絶縁膜112は、導電層110をエッチングする際のマスクとして機能する。後の工程において、絶縁膜112は、導電層110の最上面を露出するように加工されるので、上面が基板100に対して平行な平坦化絶縁膜とするのが好ましい。なお、本明細書において、導電層110の最上面とは、導電層110の上面においてソース電極104aまたはドレイン電極104bと重畳し、且つ基板100に対して平行な面を指す。

【0097】

絶縁膜112として用いる平坦化絶縁膜としては、例えば、ポリイミド、アクリル樹脂、ベンゾシクロブテン系樹脂、ポリアミド、エポキシ樹脂等の有機材料を用いることができる。また上記有機材料の他に、低誘電率材料（low-k材料）、シロキサン系樹脂、PSG（リンガラス）、BPSG（リンボロンガラス）等を用いることができる。絶縁膜1

10

20

30

40

50

12の形成法は、特に限定されず、その材料に応じて、スパッタ法、SOG法、スピニコート、ディップ、スプレー塗布、液滴吐出法（インクジェット法、スクリーン印刷、オフセット印刷等）、ドクターナイフ、ロールコーティング、カーテンコーティング、ナイフコーティング等を用いることができる。なお、シロキサン系樹脂とは、シロキサン系材料を出発材料として形成されたSi-O-Si結合を含む樹脂に相当する。シロキサン系樹脂は置換基としては有機基（例えばアルキル基やアリール基）やフルオロ基を用いてもよい。また、有機基はフルオロ基を有していてもよい。

#### 【0098】

ただし、導電層110をエッティングする際のマスクとして機能する絶縁膜は、必ずしも平坦化絶縁膜を用いる必要はない。例えば、後の工程において、CMP処理などを用いて当該絶縁膜の加工を行う場合は、図3(A)に示すように、導電層110上に平坦化されていない絶縁膜116を形成しても良い。絶縁膜116は酸化シリコン、酸化窒化シリコン等の無機絶縁材料を含む材料を用いて形成することができる。

10

#### 【0099】

次に、導電層110におけるソース電極104aまたはドレイン電極104bと重畳する領域の少なくとも一部が露出するように絶縁膜112を加工し、絶縁膜112aを形成する（図1(C)参照）。

#### 【0100】

ここで、絶縁膜112の全面において当該絶縁膜112の上面から均等な速度で絶縁膜112を除去し、導電層110の最上面を露出させた段階（あるいは、導電層110の最上面を露出させた後、導電層110を少し除去した段階）でこの操作を停止して、絶縁膜112aを形成することができる。このような絶縁膜112の加工は、アッシング処理、エッティング処理または研磨処理を用いて行うことができ、加工方法は絶縁膜112の材料に合わせて適宜決定すればよい。

20

#### 【0101】

絶縁膜112のアッシング処理としては、例えば、酸素プラズマアッシングを用いることができる。酸素プラズマによるアッシング処理は、酸素雰囲気下において、高周波電力などにより酸素をプラズマ化し、当該プラズマ化した酸素により絶縁膜112の分解除去を行う。このようにして、絶縁膜112の全面において当該絶縁膜112の上面から均等な速度で絶縁膜112を除去していくことができる。また、このように絶縁膜112を除去することにより、絶縁膜112の残渣や当該残渣の反応物を発生させることなく絶縁膜112を除去することができる。

30

#### 【0102】

また、絶縁膜112のエッティング処理としては、ウェットエッティングまたはドライエッティングのいずれを用いても良い。絶縁膜112を所望の形状にエッティングできるよう、材料に合わせてエッティング条件（エッティングガスやエッティング液、エッティング時間、温度等）を適宜設定するものとする。特に、導電層110に対して十分にエッティング選択比をとるように、エッティング条件を設定するようにする。

#### 【0103】

また、絶縁膜112の研磨処理としては、例えば、化学的機械的研磨（Chemical Mechanical Polishing: CMP）処理を用いることができる。CMP処理とは、被加工物の表面を基準にし、それにならって表面を化学的・機械的な複合作用により、平坦化する手法である。一般的に研磨ステージの上に研磨布を貼り付け、被加工物と研磨布との間にスラリー（研磨剤）を供給しながら研磨ステージと被加工物とを各々回転または揺動させて、スラリーと被加工物表面との間での化学反応と、研磨布と被加工物との機械的研磨の作用により、被加工物の表面を研磨する方法である。

40

#### 【0104】

また、図3(A)に示すように、導電層110上に平坦化されていない絶縁膜116を形成した場合、CMP処理を用いて絶縁膜116を加工すればよい。CMP処理を用いて絶縁膜116を加工することにより、図3(B)に示すように、導電層110の最上面を露

50

出するように絶縁膜 116 aを形成することができる。なお、図3(B)に示す工程以降の工程も絶縁膜 112を形成した場合と同様の方法で行うことができる。

【0105】

次に、導電層 110の露出した領域をエッティングして、ソース電極 104 aおよびドレイン電極 104 bに挟まれた領域の少なくとも一部と重畳するゲート電極 110 aを自己整合的に形成する(図1(D)参照)。ここで、ゲート電極 110 aを除いて、絶縁膜 112 aに覆われた部分に導電層 110 bが残存する。

【0106】

導電層 110のエッティングは、ソース電極 104 aおよびドレイン電極 104 bと同様の方法で行うことができ、ウェットエッティングまたはドライエッティングのいずれを用いても良いが、微細加工の観点からドライエッティングを用いることが好適である。また、このとき、エッティング条件を適宜設定し、ゲート絶縁層 108に対して十分にエッティング選択比をとるようにエッティングを行う。このようにして、ゲート絶縁層 108の最上面が露出するまで導電層 110のエッティングを行う。

10

【0107】

通常、フォトマスクを用いてこのようにトランジスタのゲート電極を形成する場合、数  $n$   $m$  ~ 数百  $n$   $m$  程度ゲート電極の位置がずれることがある。トランジスタのチャネル長が  $1 \mu m$  以上ならば大きな問題とはならないが、本実施の形態に示すようにトランジスタの微細化を図る場合、トランジスタ特性に大きな影響を与える不良となり得る。しかし、上述のように、ゲート電極 110 aを自己整合的に形成することにより、酸化物半導体層 102上のソース電極 104 aとドレイン電極 104 bに挟まれた領域内にゲート電極 110 aを精確且つ容易に形成することができる。

20

【0108】

さらに、ゲート電極 110 aのゲート絶縁層 108の最上面より上部において、ゲート電極 110 aはソース電極 104 aおよびドレイン電極 104 bと重畳しないので、ゲート電極 110 aとソース電極 104 aおよびドレイン電極 104 bとの寄生容量の増大を抑制することができる。以上より、設計通りのトランジスタ特性を有するトランジスタを作製することができる。なお、ソース電極 104 a、ドレイン電極 104 b、をテーパ形状とし、ゲート電極 110 aにおけるゲート絶縁層 108の最上面より下部を逆テーパ形状とする場合、ゲート絶縁層 108の最上面より下部において、ゲート電極 110 aの逆テーパ形状部分はソース電極 104 aおよびドレイン電極 104 bと重畳してもよい。その場合、当該箇所で、ゲート電極 110 aにおいてゲート絶縁層 108の最上面より上部がソース電極 104 aおよびドレイン電極 104 bと重畳してもよい。

30

【0109】

また、ゲート電極 110 aはフォトマスクを用いずに形成することができ、作製工程全体におけるフォトマスクの枚数を低減することができるので、半導体装置のコスト削減を図ることができる。

【0110】

次に、ゲート電極 110 aを覆うようにレジストマスク 114 aを形成し、導電層 110 bの一部の上にレジストマスク 114 bを形成する(図2(A)参照)。それから、レジストマスク 114 aおよびレジストマスク 114 bを用いて導電層 110 bを加工して配線 110 cを形成する(図2(B)参照)。

40

【0111】

レジストマスク 114 aおよびレジストマスク 114 bは感光性樹脂などを材料としてスピニコート法などを用いて成膜した後、フォトマスクを用いてフォトリソグラフィにより形成することができる。

【0112】

それから、ゲート電極 110 aと同様の方法でエッティングを行うことで、配線 110 cを形成することができる。このようにしてゲート電極 110 aを形成する際に残存した導電層 110 bの一部を利用して配線 110 cを形成することができるので、半導体装置のコ

50

スト削減を図ることができる。

【0113】

以上の工程で、微細化を図り、且つゲート電極110aが酸化物半導体層102上のソース電極104aとドレイン電極104bに挟まれた領域に重畳するトランジスタ200を形成することができる(図2(B)参照)。

【0114】

以上のように、トランジスタ200に用いられる酸化物半導体層102は水素や水などの不純物が十分に除去され、十分な酸素が供給されることにより、高純度化されたものであることが望ましい。具体的には、例えば、酸化物半導体層102の水素濃度は $5 \times 10^{-9}$  atoms/cm<sup>3</sup>以下、望ましくは $5 \times 10^{-8}$  atoms/cm<sup>3</sup>以下、より望ましくは $5 \times 10^{-7}$  atoms/cm<sup>3</sup>以下とする。なお、上述の酸化物半導体層102中の水素濃度は、二次イオン質量分析法(SIMS: Secondary Ion Mass Spectroscopy)で測定されるものである。このように、水素濃度が十分に低減されて高純度化され、十分な酸素の供給により酸素欠乏に起因するエネルギーギヤップ中の欠陥準位が低減された酸化物半導体層102では、キャリア濃度が $1 \times 10^{12}$ /cm<sup>3</sup>未満、望ましくは、 $1 \times 10^{11}$ /cm<sup>3</sup>未満、より望ましくは $1.45 \times 10^{10}$ /cm<sup>3</sup>未満となる。例えば、室温(25)でのオフ電流(ここでは、単位チャネル幅(1 μm)あたりの値)は100 zA(1 zA(ゼプトアンペア)は $1 \times 10^{-2}$  A)以下、望ましくは10 zA以下となる。このように、i型(真性半導体)またはi型に限りなく近い酸化物半導体を用いることで、良好な電気特性のトランジスタを得ることができる。

【0115】

以下、図1乃至図3に示す半導体装置の作製方法とは異なる半導体装置の作製方法について、図4乃至図6を参照して説明する。なお、図4乃至図6において、図1乃至図3と対応する箇所については同じ符号を用い、同じ箇所の詳細な説明については省略する。

【0116】

図1乃至図3に示す半導体装置の作製方法においては、酸化物半導体層102上に直接接するようにソース電極104aおよびドレイン電極104bを形成したが、開示する発明の一態様はこれに限られるものではない。

【0117】

例えば、図4(A)に示すように、酸化物半導体層102の上面にn+層124aおよびn+層124bが形成され、ソース電極104aがn+層124a上に形成され、ドレイン電極104bがn+層124b上に形成されるようなトランジスタ210を形成しても良い。ここでn+層124aおよびn+層124bは、ソース電極104aおよびドレイン電極104bと酸化物半導体層102の接触抵抗を低減する機能を有する層であり、In-Zn-O系の材料、In-Sn-O系の材料、In-O系の材料、Sn-O系の材料を用いることができる。また、上記の材料にSiO<sub>2</sub>を含ませてもよい。また、n+層124aおよびn+層124bの膜厚は1 nm以上10 nm以下とするのが好ましく、本実施の形態においては、膜厚5 nmのn+層124aおよびn+層124bを用いるものとする。

【0118】

このようなトランジスタ210は、上述のトランジスタ200の作製工程において、酸化物半導体層として機能する膜とn+層として機能する膜とを連続して成膜した後で、これらの膜を同時に加工して酸化物半導体層102と島状のn+層として機能する膜を形成する。さらに、ソース電極104aおよびドレイン電極104bを形成する際に島状のn+層として機能する膜を加工してn+層124aおよびn+層124bを形成する。なお、ソース電極104aおよびドレイン電極104bを形成した後の工程については、上述の図1乃至図3に示す方法と同様の方法でトランジスタ210を形成することができる。

【0119】

なお、図4(A)に示すトランジスタ210においては、酸化物半導体層102の上面の

みに  $n+$  層 124a および  $n+$  層 124b を形成したが、開示する発明の一態様はこれに限られるものではなく、図 4 (B) に示すように、 $n+$  層 124a および  $n+$  層 124b がさらに酸化物半導体層 102 の側面も覆うようなトランジスタ 220 を形成しても良い。この場合、トランジスタ 210 の作製方法とは異なり、島状の酸化物半導体層 102 を形成した後に、 $n+$  層として機能する膜とソース電極 104a およびドレイン電極 104b として機能する導電膜とを連続成膜する。それから、これらの膜を同時に島状に加工してソース電極 104a およびドレイン電極 104b と、 $n+$  層 124a および  $n+$  層 124b を同時に形成する。なお、ソース電極 104a およびドレイン電極 104b を形成した後の工程については、上述の図 1 乃至図 3 に示す方法と同様の方法でトランジスタ 220 を形成することができる。

10

#### 【0120】

このように酸化物半導体層 102 とソース電極 104a およびドレイン電極 104b との間に  $n+$  層 124a および  $n+$  層 124b を形成することにより、酸化物半導体層 102 とソース電極 104a との接触抵抗および酸化物半導体層 102 とドレイン電極 104b との接触抵抗よりも低減された接触抵抗を実現することができる。また、 $n+$  層 124a および  $n+$  層 124b を形成することによって、寄生抵抗の低減、さらにはバイアス - 熱ストレス試験 (BT 試験) においてマイナスゲート・ストレスを印加する前後のオン電流の変化量 ( $I_{on}$  劣化) を抑えることができる。

#### 【0121】

また、図 1 乃至図 3 に示す半導体装置の作製方法においては、ソース電極 104a およびドレイン電極 104b が酸化物半導体層 102 の上面の一部と接するようにトランジスタ 200 を形成したが、開示する発明の一態様はこれに限られるものではない。

20

#### 【0122】

例えば、図 5 (A) に示すように、酸化物半導体層 102 がソース電極 104a およびドレイン電極 104b の上面の一部と接するようなトランジスタ 230 を形成しても良い。この場合、トランジスタ 200 の作製方法とは異なり、絶縁表面を有する基板 100 上にソース電極 104a およびドレイン電極 104b を形成してから、ソース電極 104a およびドレイン電極 104b の上面の一部と接するように酸化物半導体層 102 を形成する。それから、ソース電極 104a およびドレイン電極 104b 上にそれぞれ絶縁層 106a および絶縁層 106b を形成する。ここで、酸化物半導体層 102、ソース電極 104a、ドレイン電極 104b、絶縁層 106a および絶縁層 106b は、上述の図 1 乃至図 3 に示す方法と同様の方法で形成することができる。なお、絶縁層 106a および絶縁層 106b を形成した後の工程については、上述の図 1 乃至図 3 に示す方法と同様の方法でトランジスタ 230 を形成することができる。

30

#### 【0123】

また、図 5 (B) に示すように、トランジスタ 230 において、さらにソース電極 104a の下に  $n+$  層 124a を形成し、ドレイン電極 104b の下に  $n+$  層 124b を形成するようなトランジスタ 240 を形成しても良い。トランジスタ 240 は  $n+$  層 124a および  $n+$  層 124b は側面において、酸化物半導体層 102 と接するので、上述のように酸化物半導体層 102 とソース電極 104a との接触抵抗および酸化物半導体層 102 とドレイン電極 104b との接触抵抗よりも低減された接触抵抗を実現することができる。

40

#### 【0124】

また、酸化物半導体層 102 について、図 1 乃至図 3 に示す構成および作製方法とは異なる一例について、図 6 を参照して説明する。

#### 【0125】

まず、絶縁表面を有する基板 100 上に、膜厚 1 nm 以上 10 nm 以下の第 1 の酸化物半導体層を形成する。なお、第 1 の酸化物半導体層を形成する前に基板 100 上に下地絶縁層を形成しておくのが好ましい。当該下地絶縁層は、上述のゲート絶縁層 108 と同様の材料および方法で形成することができる。

#### 【0126】

50

図6に示す半導体装置の作製方法においては、酸化物半導体用ターゲット(  $In - Ga - Zn - O$  系酸化物半導体用ターゲット(  $In_2O_3 : Ga_2O_3 : ZnO = 1 : 1 : 2$  [mol数比] )を用いて、基板とターゲットの間との距離を170mm、基板温度400、圧力0.4Pa、直流(DC)電源0.5kW、酸素のみ、アルゴンのみ、又はアルゴン及び酸素雰囲気下で膜厚5nmの第1の酸化物半導体層を成膜する。

【0127】

次いで、基板の雰囲気を窒素、または乾燥空気とし、第1の加熱処理を行う。第1の加熱処理の温度は、450以上基板の歪み点未満、好ましくは400以上650以下とする。第1の加熱処理によって第1の結晶性酸化物半導体層102aを形成する(図6(A)参照)。

10

【0128】

次いで、第1の結晶性酸化物半導体層102a上に10nmよりも厚い第2の酸化物半導体層を形成する。

【0129】

本実施の形態では、酸化物半導体用ターゲット(  $In - Ga - Zn - O$  系酸化物半導体用ターゲット(  $In_2O_3 : Ga_2O_3 : ZnO = 1 : 1 : 2$  [mol数比] )を用いて、基板とターゲットの間との距離を170mm、基板温度400、圧力0.4Pa、直流(DC)電源0.5kW、酸素のみ、アルゴンのみ、又はアルゴン及び酸素雰囲気下で膜厚25nmの第2の酸化物半導体層を成膜する。

【0130】

20

次いで、基板の雰囲気を窒素、または乾燥空気とし、第2の加熱処理を行う。第2の加熱処理の温度は、450以上基板の歪み点未満、好ましくは400以上650以下とする。第2の加熱処理によって第2の結晶性酸化物半導体層102bを形成する(図6(B)参照)。

【0131】

1回目及び2回目の加熱処理温度を650よりも高い温度で加熱処理を行うと、ガラス基板の収縮により酸化物半導体層にクラック(厚さ方向に伸びるクラック)が形成されやすい。従って、1回目及び2回目の加熱処理温度や、スパッタ成膜時の基板温度を650以下のプロセスとすることで、大面積のガラス基板上に信頼性の高いトランジスタを作製することができる。

30

【0132】

このようにして形成された第1の結晶性酸化物半導体層102a上に第2の結晶性酸化物半導体層102bが積層された酸化物半導体層を用いて、上述の図1乃至図3に示す方法と同様の方法でトランジスタを作製することによりトランジスタ250を形成することができる(図6(C)参照)。

【0133】

図6(C)に示すトランジスタ250において、第1の結晶性酸化物半導体層102a、及び第2の結晶性酸化物半導体層102bは、少なくとも一部が結晶化して得られた結晶層の表面に対して垂直方向にc軸配向をしており、信頼性が高められたトランジスタ250が実現する。

40

【0134】

また、図6(C)の構造において、トランジスタ250の酸化物半導体積層は、ゲート絶縁層との界面に沿った方向において、秩序化がきれいにできている。その界面に沿ってキャリアが流れる場合、酸化物半導体積層には直接バイアスがかからない、あたかもフローティング状態のようになるため、光照射が行われ、またはBTストレスが与えられても、トランジスタ特性の劣化は抑制され、または低減される。

【0135】

以上に示す構成、方法などは、お互いに適宜組み合わせて用いることができる。

【0136】

以上のように、微細化を図ったトランジスタにおいても、ゲート電極110aを自己整合

50

的に形成することにより、酸化物半導体層 102 上のソース電極 104a とドレイン電極 104b に挟まれた領域内にゲート電極 110a を精確且つ容易に形成することができる。さらに、ゲート電極 110a がソース電極 104a およびドレイン電極 104b と重畳することを防ぎ、ゲート電極 110a とソース電極 104a およびドレイン電極 104b との寄生容量の増大を抑制することができる。以上より、微細化に伴う不良を抑制し、設計通りのトランジスタ特性を有するトランジスタを作製することができる。

#### 【0137】

このように、開示する発明の一態様では、微細化に伴う問題点を解消することができるため、結果として、トランジスタサイズを十分に小さくすることが可能になる。トランジスタサイズを十分に小さくすることで、半導体装置の占める面積が小さくなるため、半導体装置の取り数が増大する。これにより、半導体装置あたりの製造コストは抑制される。また、半導体装置が小型化されるため、従来の半導体装置と同程度の大きさでさらに機能が高められた半導体装置を実現することができる。また、チャネル長の縮小による、動作の高速化、低消費電力化などの効果を得ることもできる。つまり、開示する発明の一態様により酸化物半導体を用いたトランジスタの微細化が達成されることで、これに付随する様々な効果を得ることが可能である。

#### 【0138】

以上、本実施の形態に示す構成、方法などは、他の実施の形態に示す構成、方法などと適宜組み合わせて用いることができる。

#### 【0139】

##### (実施の形態 2)

本実施の形態では、実施の形態 1 とは異なる、開示する発明の一態様に係る半導体装置の作製方法の一形態を、図 7 を参照して説明する。なお、図 7 において、図 1 乃至図 3 と対応する箇所については同じ符号を用い、同じ箇所の詳細な説明については省略する。

#### 【0140】

図 7 に、開示する発明の一態様に係る半導体装置の作製方法の例として、トランジスタ 300 の作製工程の断面図を示す。ここで、図 7 (D) に示すトランジスタ 300 は、基板 100 上の、酸化物半導体層 102、ソース電極 104a、ドレイン電極 104b、絶縁層 106a、絶縁層 106b、ゲート絶縁層 108 およびゲート電極 120a を含む。またゲート絶縁層 108 上に、ゲート電極 120a と同様の材料からなる配線 120c が形成されている。

#### 【0141】

ここで、トランジスタ 300 のチャネル長 (L) は 10 nm 以上 200 nm 以下とするのが好ましく、より好ましくは 20 nm 以上 100 nm 以下とする。このようにトランジスタの微細化を図り、チャネル長 (L) を縮小することによりトランジスタの動作高速化および低消費電力化を図ることができる。

#### 【0142】

また、ゲート絶縁層 108 上に設けられたゲート電極 120a は、酸化物半導体層 102 上のソース電極 104a とドレイン電極 104b に挟まれた領域の少なくとも一部と重畳する。さらに、ゲート電極 120a の上面がゲート絶縁層 108 の最上面より低くなるようにする。このような構成とすることにより、ゲート電極 120a を酸化物半導体層 102 上のソース電極 104a とドレイン電極 104b に挟まれた領域に精確に形成し、且つ寄生容量の増大を抑制できるので、トランジスタ 300 に設計通りのトランジスタ特性を有せしめることができる。

#### 【0143】

以下、図 7 (A) 乃至図 7 (D) を用いて、図 7 (D) に示すトランジスタ 300 の作製工程の一例について説明する。

#### 【0144】

まず、図 1 (A) に示す半導体装置の作製方法と同様の方法を用いて酸化物半導体層 102、ソース電極 104a およびドレイン電極 104b、絶縁層 106a および絶縁層 10

10

20

30

40

50

6 b を作製する。酸化物半導体層 102、ソース電極 104 a およびドレイン電極 104 b、絶縁層 106 a および絶縁層 106 b の詳細については、先の実施の形態の記載を参酌することができる。

#### 【 0145 】

次に、図 1 (B) に示す半導体装置の作製方法と同様の方法を用いてゲート絶縁層 108 を形成し、ゲート絶縁層 108 上に導電層 120 を形成する (図 7 (A) 参照)。ゲート絶縁層 108 および導電層 120 の詳細については、先の実施の形態のゲート絶縁層 108 および導電層 110 の記載を参酌することができる。

#### 【 0146 】

次に、ゲート絶縁層 108 におけるソース電極 104 a またはドレイン電極 104 b と重畠する領域の少なくとも一部が露出するように導電層 120 を加工し、ソース電極 104 a およびドレイン電極 104 b に挟まれた領域の少なくとも一部と重畠するゲート電極 120 a を自己整合的に形成する (図 7 (B) 参照)。ここで、ゲート電極 120 a を形成する際に導電層 120 b が残存する。

#### 【 0147 】

導電層 120 の加工は CMP 处理などの研磨処理を用いることにより、導電層 120 のソース電極 104 a およびドレイン電極 104 b と重畠する領域において、当該導電層 120 の上面から均等な速度で導電層 120 を除去していくことができる。除去し、ゲート絶縁層 108 の最上面を露出させた段階 (あるいは、ゲート絶縁層 108 の最上面を露出させた後、ゲート絶縁層 108 を少し除去した段階) でこの操作を停止する。これにより、ゲート絶縁層 108 の最上面を露出させるようにゲート電極 120 a、導電層 120 b を形成することができる。CMP 处理は導電層 120 の材料に合わせて条件を適宜設定して行えばよい。

#### 【 0148 】

また、導電層 120 のソース電極 104 a およびドレイン電極 104 b に挟まれた領域における膜厚が十分厚い場合には、ゲート絶縁層 108 の最上面が露出するまで導電層 120 をエッティングしてゲート電極 120 a を形成しても良い。この場合、ゲート電極 120 a の上面がエッティングされ、ゲート電極 120 a の上面が凹状の形状になる場合がある。また、図 7 (B) において、導電層 120 b にあたる部分も同時にエッティングされるため、導電層 120 b が形成されない場合がある。なお、導電層 120 のエッティングは、ウェットエッティングまたはドライエッティングのいずれを用いても良い。導電層 120 を所望の形状にエッティングできるよう、材料に合わせてエッティング条件 (エッティングガスやエッティング液、エッティング時間、温度等) を適宜設定するものとする。特に、ゲート絶縁層 108 に対して十分にエッティング選択比をとるように、エッティング条件を設定するようにする。

#### 【 0149 】

次に、ゲート電極 120 a を覆うようにレジストマスク 114 a を形成し、導電層 120 b の一部の上にレジストマスク 114 b を形成する (図 7 (C) 参照)。それから、レジストマスク 114 a およびレジストマスク 114 b を用いて導電層 120 b を加工して配線 120 c を形成する (図 7 (D) 参照)。

#### 【 0150 】

レジストマスク 114 a およびレジストマスク 114 b の詳細については、先の実施の形態の記載を参酌することができる。

#### 【 0151 】

また、配線 120 c は、先の実施の形態に示す配線 110 c と同様の方法でエッティングを行って形成することができる。このようにしてゲート電極 120 a を形成する際に残存した導電層 120 b の一部を利用して配線 120 c を形成することができるので、半導体装置のコスト削減を図ることができる。

#### 【 0152 】

以上の工程で、微細化を図り、且つゲート電極 120 a が酸化物半導体層 102 上のソ-

10

20

30

40

50

ス電極 104a とドレイン電極 104b に挟まれた領域に重畠するトランジスタ 300 を形成することができる（図 7（D）参照）。

#### 【0153】

なお、本実施の形態に示す半導体装置の作製方法においても、先の実施の形態と同様に、図 4 乃至図 6 に示す半導体装置の作製方法を適宜組み合わせて用いることができる。

#### 【0154】

以上のように、微細化を図ったトランジスタにおいても、ゲート電極 120a を自己整合的に形成することにより、酸化物半導体層 102 上のソース電極 104a とドレイン電極 104b に挟まれた領域内にゲート電極 120a を精確且つ容易に形成することができる。さらに、ゲート電極 120a がソース電極 104a およびドレイン電極 104b と重畠することを防ぎ、ゲート電極 120a とソース電極 104a およびドレイン電極 104b との寄生容量の増大を抑制することができる。以上より、微細化に伴う不良を抑制し、設計通りのトランジスタ特性を有するトランジスタを作製することができる。

#### 【0155】

このように、開示する発明の一態様では、微細化に伴う問題点を解消することができるため、結果として、トランジスタサイズを十分に小さくすることが可能になる。トランジスタサイズを十分に小さくすることで、半導体装置の占める面積が小さくなるため、半導体装置の取り数が増大する。これにより、半導体装置あたりの製造コストは抑制される。また、半導体装置が小型化されるため、同程度の大きさでさらに機能が高められた半導体装置を実現することができる。また、チャネル長の縮小による、動作の高速化、低消費電力化などの効果を得ることもできる。つまり、開示する発明の一態様により酸化物半導体を用いたトランジスタの微細化が達成されることで、これに付随する様々な効果を得ることが可能である。

#### 【0156】

以上、本実施の形態に示す構成、方法などは、他の実施の形態に示す構成、方法などと適宜組み合わせて用いることができる。

#### 【0157】

##### （実施の形態 3）

本実施の形態では、先の実施の形態に示す半導体装置の作製方法を用いて形成する半導体装置の一例として、記憶媒体（メモリ素子）を示す。本実施の形態では、先の実施の形態において示す半導体装置の作製方法で形成した、酸化物半導体を用いたトランジスタと、酸化物半導体以外の材料を用いたトランジスタとを同一基板上に形成する。

#### 【0158】

図 8 は、半導体装置の構成の一例である。図 8（A）には、半導体装置の断面を、図 8（B）には、半導体装置の平面を、それぞれ示す。ここで、図 8（A）は、図 8（B）の C1 - C2 および D1 - D2 における断面に相当する。また、図 8（C）には、上記半導体装置をメモリ素子として用いる場合の回路図の一例を示す。図 8（A）および図 8（B）に示される半導体装置は、下部に第 1 の半導体材料を用いたトランジスタ 500 を有し、上部に先の実施の形態で示したトランジスタ 200 を有する。なお、トランジスタ 200 は、第 2 の半導体材料として酸化物半導体を用いている。本実施の形態では、第 1 の半導体材料を酸化物半導体以外の半導体材料とする。酸化物半導体以外の半導体材料としては、例えば、シリコン、ゲルマニウム、シリコンゲルマニウム、炭化シリコン、またはガリウムヒ素等を用いることができ、単結晶半導体を用いるのが好ましい。他に、有機半導体材料などを用いてもよい。このような半導体材料を用いたトランジスタは、高速動作が容易である。一方で、酸化物半導体を用いたトランジスタは、その特性により長時間の電荷保持を可能とする。

#### 【0159】

なお、本実施の形態においては、トランジスタ 200 を用いて記憶媒体を構成する例を示すが、トランジスタ 200 に代えて、先の実施の形態で示したトランジスタ 210、トランジスタ 220、トランジスタ 230、トランジスタ 240、トランジスタ 250 または

トランジスタ 300 等を適用可能であることは、いうまでもない。

【0160】

図8におけるトランジスタ500は、半導体材料（例えば、シリコンなど）を含む基板400に設けられたチャネル形成領域416と、チャネル形成領域416を挟むように設けられた不純物領域420と、不純物領域420に接する金属化合物領域424と、チャネル形成領域416上に設けられたゲート絶縁層408と、ゲート絶縁層408上に設けられたゲート電極410と、を有する。

【0161】

半導体材料を含む基板400は、シリコンや炭化シリコンなどの単結晶半導体基板、多結晶半導体基板、シリコンゲルマニウムなどの化合物半導体基板、SOI基板などを適用することができる。なお、一般に「SOI基板」は、絶縁表面上にシリコン半導体膜が設けられた構成の基板をいうが、本明細書等においては、絶縁表面上にシリコン以外の材料からなる半導体膜が設けられた構成の基板も含む。つまり、「SOI基板」が有する半導体膜は、シリコン半導体膜に限定されない。また、SOI基板には、ガラス基板などの絶縁基板上に絶縁層を介して半導体膜が設けられた構成のものが含まれるものとする。

10

【0162】

基板400上にはトランジスタ500を囲むように素子分離絶縁層406が設けられており、トランジスタ500を覆うように絶縁層428および絶縁層430が設けられている。なお、高集積化を実現するためには、図8に示すようにトランジスタ500がサイドウォール絶縁層を有しない構成とすることが望ましい。一方で、トランジスタ500の特性を重視する場合には、ゲート電極410の側面にサイドウォール絶縁層を設け、不純物濃度が異なる領域を含む不純物領域420を設けても良い。

20

【0163】

トランジスタ500はシリコン、ゲルマニウム、シリコンゲルマニウム、炭化シリコン、またはガリウムヒ素等を用いて作製することができる。このようなトランジスタ500は、高速動作が可能であるという特徴を有する。このため、当該トランジスタを読み出し用のトランジスタとして用いることで、情報の読み出しを高速に行うことができる。

【0164】

なお、トランジスタ500を形成した後、トランジスタ200および容量素子520の形成前の処理として、絶縁層428や絶縁層430にCMP処理を施して、ゲート電極410の上面を露出させる。ゲート電極410の上面を露出させる処理としては、CMP処理の他にエッチング処理などを適用することも可能であるが、トランジスタ200の特性を向上させるために、絶縁層428や絶縁層430の表面は可能な限り平坦にしておくことが望ましい。

30

【0165】

また、トランジスタ200は先の実施の形態で示したように、酸化物半導体層102、ソース電極104a、ドレイン電極104b、絶縁層106a、絶縁層106b、ゲート絶縁層108およびゲート電極110aを含み、詳細については、実施の形態1の記載を参考することができる。また、トランジスタ200に代表される上部のトランジスタは、実施の形態1または実施の形態2に記載の方法で作製することができる。

40

【0166】

ここで、ソース電極104aはゲート電極410と接するように設けられるので、トランジスタ500のゲート電極410とトランジスタ200のソース電極104aとが接続される。

【0167】

また、先の実施の形態で示した配線110cを、ゲート絶縁層108を介してソース電極104a上に設けることにより、容量素子520を形成することができる。なお、容量が不要の場合は、容量素子520を設けない構成とすることも可能である。

【0168】

また、ゲート絶縁層108、ゲート電極110aおよび配線110c上に、絶縁層151

50

および絶縁層 152 が形成される。絶縁層 151 および絶縁層 152 は、スパッタ法や CVD 法などを用いて形成することができる。また、酸化シリコン、酸窒化シリコン、窒化シリコン、酸化ハフニウム、酸化アルミニウム、酸化ガリウム等の無機絶縁材料を含む材料を用いて形成することができる。

【 0169 】

また、絶縁層 152 上に配線 156 が形成されている。配線 156 は、絶縁層 106b、ゲート絶縁層 108、絶縁層 151 および絶縁層 152 に設けられた開口に形成された電極 154 を介してドレイン電極 104b と電気的に接続されている。

【 0170 】

電極 154 は、例えば、開口を含む領域に PVD 法や CVD 法などを用いて導電膜を形成した後、エッチング処理や CMP といった方法を用いて、上記導電膜の一部を除去することにより形成することができる。

【 0171 】

配線 156 は、スパッタ法をはじめとする PVD 法や、プラズマ CVD 法などの CVD 法を用いて導電層を形成した後、当該導電層をパターニングすることによって形成される。また、配線 156 は、ソース電極 104a およびドレイン電極 104b と同様の材料で形成することができる。

【 0172 】

図 8 (C) には、上記半導体装置をメモリ素子として用いる場合の回路図の一例を示す。図 8 (C) において、トランジスタ 200 のソース電極またはドレイン電極の一方と、容量素子 520 の電極の一方と、トランジスタ 500 のゲート電極と、は電気的に接続されている。また、第 1 の配線 (1st Line : ソース線とも呼ぶ) とトランジスタ 500 のソース電極とは、電気的に接続され、第 2 の配線 (2nd Line : ビット線とも呼ぶ) とトランジスタ 500 のドレイン電極とは、電気的に接続されている。また、第 3 の配線 (3rd Line : 第 1 の信号線とも呼ぶ) とトランジスタ 200 のソース電極またはドレイン電極の他方とは、電気的に接続され、第 4 の配線 (4th Line : 第 2 の信号線とも呼ぶ) と、トランジスタ 200 のゲート電極とは、電気的に接続されている。そして、第 5 の配線 (5th Line : ワード線とも呼ぶ) と、容量素子 520 の電極の他方は電気的に接続されている。

【 0173 】

酸化物半導体を用いたトランジスタ 200 は、オフ電流が極めて小さいという特徴を有しているため、トランジスタ 200 をオフ状態とすることで、トランジスタ 200 のソース電極またはドレイン電極の一方と、容量素子 520 の電極の一方と、トランジスタ 500 のゲート電極とが電気的に接続されたノード (以下、ノード FG) の電位を極めて長時間にわたって保持することが可能である。そして、容量素子 520 を有することにより、ノード FG に与えられた電荷の保持が容易になり、また、保持された情報の読み出しが容易になる。

【 0174 】

半導体装置に情報を記憶させる場合 (書き込み) は、まず、第 4 の配線の電位を、トランジスタ 200 がオン状態となる電位にして、トランジスタ 200 をオン状態とする。これにより、第 3 の配線の電位が、ノード FG に供給され、ノード FG に所定量の電荷が蓄積される。ここでは、異なる二つの電位レベルを与える電荷 (以下、ロー (Low) レベル電荷、ハイ (High) レベル電荷という) のいずれかが与えられるものとする。その後、第 4 の配線の電位を、トランジスタ 200 がオフ状態となる電位にして、トランジスタ 200 をオフ状態とすることにより、ノード FG が浮遊状態となるため、ノード FG には所定の電荷が保持されたままの状態となる。以上のように、ノード FG に所定量の電荷を蓄積及び保持させることで、メモリセルに情報を記憶させることができる。

【 0175 】

トランジスタ 200 のオフ電流は極めて小さいため、ノード FG に供給された電荷は長時間にわたって保持される。したがって、リフレッシュ動作が不要となるか、または、リフ

10

20

30

40

50

レッシュ動作の頻度を極めて低くすることが可能となり、消費電力を十分に低減することができる。また、電力の供給がない場合であっても、長期にわたって記憶内容を保持することが可能である。

【0176】

記憶された情報を読み出す場合（読み出し）は、第1の配線に所定の電位（定電位）を与えた状態で、第5の配線に適切な電位（読み出し電位）を与えると、ノードFGに保持された電荷量に応じて、トランジスタ500は異なる状態をとる。一般に、トランジスタ500をnチャネル型とすると、ノードFGにHighレベル電荷が保持されている場合のトランジスタ500の見かけのしきい値電圧 $V_{th\_H}$ は、ノードFGにLowレベル電荷が保持されている場合のトランジスタ500の見かけのしきい値電圧 $V_{th\_L}$ より低くなるためである。ここで、見かけのしきい値電圧とは、トランジスタ500を「オン状態」とするために必要な第5の配線の電位をいうものとする。したがって、第5の配線の電位を $V_{th\_H}$ と $V_{th\_L}$ の中間の電位 $V_0$ とすることにより、ノードFGに保持された電荷を判別できる。例えば、書き込みにおいて、Highレベル電荷が与えられていた場合には、第5の配線の電位が $V_0$ （ $> V_{th\_H}$ ）となれば、トランジスタ500は「オン状態」となる。Lowレベル電荷が与えられていた場合には、第5の配線の電位が $V_0$ （ $< V_{th\_L}$ ）となっても、トランジスタ500は「オフ状態」のままである。このため、第5の配線の電位を制御して、トランジスタ500のオン状態またはオフ状態を読み出す（第2の配線の電位を読み出す）ことで、記憶された情報を読み出すことができる。

10

20

【0177】

また、記憶させた情報を書き換える場合においては、上記の書き込みによって所定量の電荷を保持したノードFGに、新たな電位を供給することで、ノードFGに新たな情報に係る電荷を保持させる。具体的には、第4の配線の電位を、トランジスタ200がオン状態となる電位にして、トランジスタ200をオン状態とする。これにより、第3の配線の電位（新たな情報に係る電位）が、ノードFGに供給され、ノードFGに所定量の電荷が蓄積される。その後、第4の配線の電位をトランジスタ200がオフ状態となる電位にして、トランジスタ200をオフ状態とすることにより、ノードFGには、新たな情報に係る電荷が保持された状態となる。すなわち、ノードFGに第1の書き込みによって所定量の電荷が保持された状態で、第1の書き込みと同様の動作（第2の書き込み）を行うことで、記憶させた情報を上書きすることができる。

30

【0178】

本実施の形態で示すトランジスタ200は、高純度化され、真性化された酸化物半導体層102を用いることで、トランジスタ200のオフ電流を十分に低減することができる。また、酸化物半導体層102を酸素過剰な層とすることで、トランジスタ200の電気的特性変動が抑制されており、電気的に安定なトランジスタとすることができます。そして、このようなトランジスタを用いることで、極めて長期にわたり記憶内容を保持することができる、信頼性の高い半導体装置が得られる。

【0179】

さらに、ゲート電極110aを自己整合的に形成することにより、酸化物半導体層102上のソース電極104aとドレイン電極104bに挟まれた領域内にゲート電極110aを精確且つ容易に形成することができる。さらに、ゲート電極110aがソース電極104aおよびドレイン電極104bと重畳することを防ぎ、ゲート電極110aとソース電極104aおよびドレイン電極104bとの寄生容量の増大を抑制することができる。以上より、微細化に伴う不良を抑制し、設計通りのトランジスタ特性を有するトランジスタを作製することができる。

40

【0180】

このように、本実施の形態において示す半導体装置では、微細化に伴う問題点を解消することができるため、結果として、トランジスタサイズを十分に小さくすることが可能になるので、集積度が十分に高められた半導体装置が実現される。

50

**【0181】**

また、本実施の形態において示す半導体装置では、トランジスタ500とトランジスタ200を重畳させることで、集積度が十分に高められた半導体装置が実現される。

**【0182】**

以上、本実施の形態に示す構成、方法などは、他の実施の形態に示す構成、方法などと適宜組み合わせて用いることができる。

**【0183】****(実施の形態4)**

本実施の形態では、開示する発明の一態様に係る半導体装置の応用例について、図9を用いて説明する。

10

**【0184】**

図9(A)および図9(B)は、図8(A)乃至図8(C)に示す半導体装置(以下、メモリセル550とも記載する。)を複数用いて形成される半導体装置の回路図である。図9(A)は、メモリセル550が直列に接続された、いわゆるNAND型の半導体装置の回路図であり、図9(B)は、メモリセル550が並列に接続された、いわゆるNOR型の半導体装置の回路図である。

**【0185】**

図9(A)に示す半導体装置は、ソース線SL、ピット線BL、第1信号線S1、複数本の第2信号線S2、複数本のワード線WL、複数のメモリセル550を有する。図9(A)では、ソース線SLおよびピット線BLを1本ずつ有する構成となっているが、これに限られることなく、ソース線SLおよびピット線BLを複数本有する構成としてもよい。

20

**【0186】**

各メモリセル550において、トランジスタ500のゲート電極と、トランジスタ200のソース電極またはドレイン電極の一方と、容量素子520の電極の一方とは、電気的に接続されている。また、第1信号線S1とトランジスタ200のソース電極またはドレイン電極の他方とは、電気的に接続され、第2信号線S2と、トランジスタ200のゲート電極とは、電気的に接続されている。そして、ワード線WLと、容量素子520の電極の他方は電気的に接続されている。

**【0187】**

また、メモリセル550が有するトランジスタ500のソース電極は、隣接するメモリセル550のトランジスタ500のドレイン電極と電気的に接続され、メモリセル550が有するトランジスタ500のドレイン電極は、隣接するメモリセル550のトランジスタ500のソース電極と電気的に接続される。ただし、直列に接続された複数のメモリセルのうち、一方の端に設けられたメモリセル550が有するトランジスタ500のドレイン電極は、ピット線BLと電気的に接続される。また、直列に接続された複数のメモリセルのうち、他方の端に設けられたメモリセル550が有するトランジスタ500のソース電極は、ソース線SLと電気的に接続される。

30

**【0188】**

図9(A)に示す半導体装置では、行ごとの書き込み動作および読み出し動作を行う。書き込み動作は次のように行われる。書き込みを行う行の第2の信号線S2にトランジスタ200がオン状態となる電位を与え、書き込みを行う行のトランジスタ200をオン状態にする。これにより、指定した行のトランジスタ500のゲート電極に第1の信号線S1の電位が与えられ、該ゲート電極に所定の電荷が与えられる。このようにして、指定した行のメモリセルにデータを書き込むことができる。

40

**【0189】**

また、読み出し動作は次のように行われる。まず、読み出しを行う行以外のワード線WLに、トランジスタ500のゲート電極に与えられた電荷によらず、トランジスタ500がオン状態となるような電位を与え、読み出しを行う行以外のトランジスタ500をオン状態とする。それから、読み出しを行う行のワード線WLに、トランジスタ500のゲート電極が有する電荷によって、トランジスタ500のオン状態またはオフ状態が選択される

50

のような電位（読み出し電位）を与える。そして、ソース線 S L に定電位を与え、ビット線 B L に接続されている読み出し回路（図示しない）を動作状態とする。ここで、ソース線 S L - ビット線 B L 間の複数のトランジスタ 500 は、読み出しを行う行を除いてオン状態となっているため、ソース線 S L - ビット線 B L 間のコンダクタンスは、読み出しを行う行のトランジスタ 500 の状態（オン状態またはオフ状態）によって決定される。読み出しを行う行のトランジスタ 500 のゲート電極が有する電荷によって、トランジスタのコンダクタンスは異なるから、それに応じて、ビット線 B L の電位は異なる値をとることになる。ビット線 B L の電位を読み出し回路によって読み出すことで、指定した行のメモリセルから情報を読み出すことができる。

【0190】

10

図 9 (B) に示す半導体装置は、ソース線 S L 、ビット線 B L 、第 1 信号線 S 1 、第 2 信号線 S 2 、およびワード線 W L をそれぞれ複数本有し、複数のメモリセル 550 を有する。各トランジスタ 500 のゲート電極と、トランジスタ 200 のソース電極またはドレイン電極の一方と、容量素子 520 の電極の一方とは、電気的に接続されている。また、ソース線 S L とトランジスタ 500 のソース電極とは、電気的に接続され、ビット線 B L とトランジスタ 500 のドレイン電極とは、電気的に接続されている。また、第 1 信号線 S 1 とトランジスタ 200 のソース電極またはドレイン電極の他方とは、電気的に接続され、第 2 信号線 S 2 と、トランジスタ 200 のゲート電極とは、電気的に接続されている。そして、ワード線 W L と、容量素子 520 の電極の他方は電気的に接続されている。

【0191】

20

図 9 (B) に示す半導体装置では、行ごとの書き込み動作および読み出し動作を行う。書き込み動作は、上述の図 9 (A) に示す半導体装置と同様の方法で行われる。読み出し動作は次のように行われる。まず、読み出しを行う行以外のワード線 W L に、トランジスタ 500 のゲート電極に与えられた電荷によらず、トランジスタ 500 がオフ状態となるような電位を与え、読み出しを行う行以外のトランジスタ 500 をオフ状態とする。それから、読み出しを行う行のワード線 W L に、トランジスタ 500 のゲート電極が有する電荷によって、トランジスタ 500 のオン状態またはオフ状態が選択されるような電位（読み出し電位）を与える。そして、ソース線 S L に定電位を与え、ビット線 B L に接続されている読み出し回路（図示しない）を動作状態とする。ここで、ソース線 S L - ビット線 B L 間のコンダクタンスは、読み出しを行う行のトランジスタ 500 の状態（オン状態またはオフ状態）によって決定される。つまり、読み出しを行う行のトランジスタ 500 のゲート電極が有する電荷によって、ビット線 B L の電位は異なる値をとることになる。ビット線 B L の電位を読み出し回路によって読み出すことで、指定した行のメモリセルから情報を読み出すことができる。

【0192】

30

なお、上記においては、各メモリセル 550 に保持させる情報量を 1 ビットとしたが、本実施の形態に示す記憶装置の構成はこれに限られない。トランジスタ 500 のゲート電極に与える電位を 3 以上用意して、各メモリセル 550 が保持する情報量を増加させても良い。例えば、トランジスタ 500 のゲート電極にあたえる電位を 4 種類とする場合には、各メモリセルに 2 ビットの情報を保持させることができる。

【0193】

40

本実施の形態に示す構成、方法などは、他の実施の形態に示す構成、方法などと適宜組み合わせて用いることができる。

【0194】

(実施の形態 5)

本実施の形態では、上述の実施の形態で説明した半導体装置を電子機器に適用する場合について、図 10 を用いて説明する。本実施の形態では、コンピュータ、携帯電話機（携帯電話、携帯電話装置ともいう）、携帯情報端末（携帯型ゲーム機、音響再生装置なども含む）、デジタルカメラ、デジタルビデオカメラ、電子ペーパー、テレビジョン装置（テレビ、またはテレビジョン受信機ともいう）などの電子機器に、上述の半導体装置を適用す

50

る場合について説明する。

【0195】

図10(A)は、ノート型のパーソナルコンピュータであり、筐体601、筐体602、表示部603、キーボード604などによって構成されている。筐体601と筐体602内には、先の実施の形態に示す微細化された半導体装置が設けられている。そのため、小型、高速動作、低消費電力、といった特徴を備えたノート型のパーソナルコンピュータが実現される。

【0196】

図10(B)は、携帯情報端末(PDA)であり、本体611には、表示部613と、外部インターフェイス615と、操作ボタン614等が設けられている。また、携帯情報端末を操作するスタイルス612などを備えている。本体611内には、先の実施の形態に示す微細化された半導体装置が設けられている。そのため、小型、高速動作、低消費電力、といった特徴を備えた携帯情報端末が実現される。

10

【0197】

図10(C)は、電子ペーパーを実装した電子書籍であり、電子書籍620は、筐体621と筐体623の2つの筐体で構成されている。筐体621及び筐体623には、それぞれ表示部625及び表示部627が設けられている。筐体621と筐体623は、軸部637により接続されており、該軸部637を軸として開閉動作を行うことができる。また、筐体621は、電源631、操作キー633、スピーカー635などを備えている。筐体621、筐体623の少なくとも一には、先の実施の形態に示す微細化された半導体装置が設けられている。そのため、小型、高速動作、低消費電力、といった特徴を備えた電子書籍が実現される。

20

【0198】

図10(D)は、携帯電話機であり、筐体640と筐体641の2つの筐体で構成されている。さらに、筐体640と筐体641は、スライドし、図10(D)のように展開している状態から重なり合った状態とすることができる、携帯に適した小型化が可能である。また、筐体641は、表示パネル642、スピーカー643、マイクロフォン644、ポイントティングデバイス646、カメラ用レンズ647、外部接続端子648などを備えている。また、筐体640は、携帯電話機の充電を行う太陽電池セル649、外部メモリスロット650などを備えている。また、表示パネル642はタッチパネル機能を備えており、図10(D)には映像表示されている複数の操作キー645を点線で示している。また、アンテナは、筐体641に内蔵されている。筐体640と筐体641の少なくとも一には、先の実施の形態に示す微細化された半導体装置が設けられている。そのため、小型、高速動作、低消費電力、といった特徴を備えた携帯電話機が実現される。

30

【0199】

図10(E)は、デジタルカメラであり、本体661、表示部667、接眼部663、操作スイッチ664、表示部665、バッテリー666などによって構成されている。本体661内には、先の実施の形態に示す微細化された半導体装置が設けられている。そのため、小型、高速動作、低消費電力、といった特徴を備えたデジタルカメラが実現される。

40

【0200】

図10(F)は、テレビジョン装置であり、テレビジョン装置670は、筐体671、表示部673、スタンド675などで構成されている。テレビジョン装置670の操作は、筐体671が備えるスイッチや、リモコン操作機680により行うことができる。筐体671及びリモコン操作機680には、先の実施の形態に示す微細化された半導体装置が搭載されている。そのため、高速動作、低消費電力、といった特徴を備えたテレビジョン装置が実現される。

【0201】

以上のように、本実施の形態に示す電子機器には、先の実施の形態に係る半導体装置が搭載されている。このため、小型、高速動作、低消費電力、といった特徴を備えた電子機器が実現される。

50

## 【符号の説明】

## 【0202】

|       |               |    |

|-------|---------------|----|

| 100   | 基板            |    |

| 102   | 酸化物半導体層       |    |

| 102 a | 第1の結晶性酸化物半導体層 |    |

| 102 b | 第2の結晶性酸化物半導体層 |    |

| 104 a | ソース電極         |    |

| 104 b | ドレイン電極        |    |

| 106 a | 絶縁層           | 10 |

| 106 b | 絶縁層           |    |

| 108   | ゲート絶縁層        |    |

| 110   | 導電層           |    |

| 110 a | ゲート電極         |    |

| 110 b | 導電層           |    |

| 110 c | 配線            |    |

| 112   | 絶縁膜           |    |

| 112 a | 絶縁膜           |    |

| 114 a | レジストマスク       |    |

| 114 b | レジストマスク       |    |

| 116   | 絶縁膜           | 20 |

| 116 a | 絶縁膜           |    |

| 120   | 導電層           |    |

| 120 a | ゲート電極         |    |

| 120 b | 導電層           |    |

| 120 c | 配線            |    |

| 151   | 絶縁層           |    |

| 152   | 絶縁層           |    |

| 154   | 電極            |    |

| 156   | 配線            |    |

| 200   | トランジスタ        | 30 |

| 210   | トランジスタ        |    |

| 220   | トランジスタ        |    |

| 230   | トランジスタ        |    |

| 240   | トランジスタ        |    |

| 250   | トランジスタ        |    |

| 300   | トランジスタ        |    |

| 400   | 基板            |    |

| 406   | 素子分離絶縁層       |    |

| 408   | ゲート絶縁層        |    |

| 410   | ゲート電極         | 40 |

| 416   | チャネル形成領域      |    |

| 420   | 不純物領域         |    |

| 424   | 金属化合物領域       |    |

| 428   | 絶縁層           |    |

| 430   | 絶縁層           |    |

| 500   | トランジスタ        |    |

| 510   | トランジスタ        |    |

| 520   | 容量素子          |    |

| 550   | メモリセル         |    |

| 601   | 筐体            | 50 |

|       |             |    |

|-------|-------------|----|

| 6 0 2 | 筐体          |    |

| 6 0 3 | 表示部         |    |

| 6 0 4 | キー ボード      |    |

| 6 1 1 | 本体          |    |

| 6 1 2 | スタイラス       |    |

| 6 1 3 | 表示部         |    |

| 6 1 4 | 操作ボタン       |    |

| 6 1 5 | 外部インターフェイス  |    |

| 6 2 0 | 電子書籍        |    |

| 6 2 1 | 筐体          | 10 |

| 6 2 3 | 筐体          |    |

| 6 2 5 | 表示部         |    |

| 6 2 7 | 表示部         |    |

| 6 3 1 | 電源          |    |

| 6 3 3 | 操作キー        |    |

| 6 3 5 | スピーカー       |    |

| 6 3 7 | 軸部          |    |

| 6 4 0 | 筐体          |    |

| 6 4 1 | 筐体          |    |

| 6 4 2 | 表示パネル       | 20 |

| 6 4 3 | スピーカー       |    |

| 6 4 4 | マイクロフォン     |    |

| 6 4 5 | 操作キー        |    |

| 6 4 6 | ポインティングデバイス |    |

| 6 4 7 | カメラ用レンズ     |    |

| 6 4 8 | 外部接続端子      |    |

| 6 4 9 | 太陽電池セル      |    |

| 6 5 0 | 外部メモリスロット   |    |

| 6 6 1 | 本体          |    |

| 6 6 3 | 接眼部         | 30 |

| 6 6 4 | 操作スイッチ      |    |

| 6 6 5 | 表示部         |    |

| 6 6 6 | バッテリー       |    |

| 6 6 7 | 表示部         |    |

| 6 7 0 | テレビジョン装置    |    |

| 6 7 1 | 筐体          |    |

| 6 7 3 | 表示部         |    |

| 6 7 5 | スタンド        |    |

| 6 8 0 | リモコン操作機     |    |

【図1】

【図2】

【図3】

【図4】

【 5 】

【図6】

【図7】

【図8】

【図9】

【図10】

---

フロントページの続き

(51)Int.Cl. F I

H 01 L 29/423 (2006.01) H 01 L 27/108 321

H 01 L 21/8242 (2006.01)

H 01 L 27/108 (2006.01)

(56)参考文献 米国特許出願公開第2010/0163865(US, A1)

特開昭60-177676(JP, A)

特開2008-211144(JP, A)

特開平03-233938(JP, A)

特開2010-170110(JP, A)

(58)調査した分野(Int.Cl., DB名)

H 01 L 21/336、29/786