## (12) 发明专利

(10) 授权公告号 CN 107689783 B

(45) 授权公告日 2020.12.15

(21) 申请号 201710604182.7

H03H 11/28 (2006.01)

(22) 申请日 2017.07.21

H03G 3/30 (2006.01)

(65) 同一申请的已公布的文献号

H03F 1/26 (2006.01)

申请公布号 CN 107689783 A

H03F 3/19 (2006.01)

(43) 申请公布日 2018.02.13

## (56) 对比文件

CN 101128977 A, 2008.02.20

(30) 优先权数据

JP H077451 A, 1995.01.10

2016-155024 2016.08.05 JP

CN 1445926 A, 2003.10.01

(73) 专利权人 株式会社村田制作所

CN 1394391 A, 2003.01.29

地址 日本京都府

CN 103001687 A, 2013.03.27

(72) 发明人 照田千寻

CN 1708899 A, 2005.12.14

(74) 专利代理机构 中科专利商标代理有限责任公司 11021

EP 1246358 A2, 2002.10.02

代理人 赵琳琳

周卫. “低损耗、高Q值声表面波谐振器和低相位噪声SAW振荡器”.《中国优秀硕士学位论文全文数据库(电子期刊)》.2006, I135-344.

(51) Int.Cl.

审查员 曹坤

H03H 9/52 (2006.01)

权利要求书2页 说明书15页 附图11页

H03H 3/02 (2006.01)

## (54) 发明名称

高频模块以及弹性波滤波器的制造方法

## (57) 摘要

本发明提供一种通过减少通频带端的噪声指数的劣化,能够提高传输特性的高频模块等。高频模块(1)具备:弹性波滤波器(10);和低噪声放大器(40),对从弹性波滤波器(10)输出的高频信号进行放大,弹性波滤波器(10)的输出阻抗( $Z(Fout)$ )在该弹性波滤波器(10)的通频带的低频端( $fL$ )以及高频端( $fH$ )的至少一方的频率下,在史密斯圆图上位置靠近表示低噪声放大器(40)的噪声指数最小的输出阻抗( $Z(Fout)$ )的噪声匹配阻抗( $NF_{min}$ )、以及表示低噪声放大器(40)的增益最大的输出阻抗( $Z(Fout)$ )的增益匹配阻抗( $Gain_{max}$ )之中的噪声匹配阻抗( $NF_{min}$ )。

1.一种高频模块,具备:

弹性波滤波器;和

低噪声放大器,对从所述弹性波滤波器输出的高频信号进行放大,

所述弹性波滤波器的输出阻抗在该弹性波滤波器的通频带的低频端以及高频端的至少一方的频率下,在史密斯圆图上位置靠近表示所述低噪声放大器的噪声指数最小的所述输出阻抗的噪声匹配阻抗、以及表示所述低噪声放大器的增益最大的所述输出阻抗的增益匹配阻抗之中的所述噪声匹配阻抗,

所述弹性波滤波器具有在连结输入端与输出端的路径上串联连接的纵耦合型的滤波器构造,

所述噪声匹配阻抗相对于所述增益匹配阻抗在所述史密斯圆图上位于左侧并且上侧的区域,

所述纵耦合型的滤波器构造被配置得最接近于所述输出端。

2.一种高频模块,具备:

弹性波滤波器;和

低噪声放大器,对从所述弹性波滤波器输出的高频信号进行放大,

所述弹性波滤波器的输出阻抗在该弹性波滤波器的通频带的低频端以及高频端的至少一方的频率下,在史密斯圆图上位置靠近表示所述低噪声放大器的噪声指数最小的所述输出阻抗的噪声匹配阻抗、以及表示所述低噪声放大器的增益最大的所述输出阻抗的增益匹配阻抗之中的所述噪声匹配阻抗,

所述弹性波滤波器具有在连结输入端与输出端的路径上串联连接的纵耦合型的滤波器构造,

所述噪声匹配阻抗相对于所述增益匹配阻抗在所述史密斯圆图上位于右侧的区域,

所述弹性波滤波器具有被配置得最接近于所述输出端并且在连结所述路径与接地的路径上串联连接的并联陷波器。

3.根据权利要求2所述的高频模块,其中,

所述并联陷波器具有频率比所述通频带的低频端低的谐振点。

4.一种高频模块,具备:

弹性波滤波器;和

低噪声放大器,对从所述弹性波滤波器输出的高频信号进行放大,

所述弹性波滤波器的输出阻抗在该弹性波滤波器的通频带的低频端以及高频端的至少一方的频率下,在史密斯圆图上位置靠近表示所述低噪声放大器的噪声指数最小的所述输出阻抗的噪声匹配阻抗、以及表示所述低噪声放大器的增益最大的所述输出阻抗的增益匹配阻抗之中的所述噪声匹配阻抗,

所述弹性波滤波器具有在连结输入端与输出端的路径上串联连接的纵耦合型的滤波器构造,

所述噪声匹配阻抗相对于所述增益匹配阻抗在所述史密斯圆图上位于左侧并且下侧的区域,

所述弹性波滤波器具有被配置得最接近于所述输出端并且在所述路径上串联连接的串联陷波器。

5. 根据权利要求4所述的高频模块,其中,

所述串联陷波器具有频率比所述通频带的高频端高的反谐振点。

6. 根据权利要求1~5中任一项所述的高频模块,其中,

所述输出阻抗在所述通频带的低频端以及高频端的任意频率下,在所述史密斯圆图上位置靠近所述噪声匹配阻抗。

7. 根据权利要求1~5中任一项所述的高频模块,其中,

在所述史密斯圆图上,所述通频带中的所述输出阻抗的轨迹与连结所述噪声匹配阻抗和所述增益匹配阻抗的线交叉。

8. 一种弹性波滤波器的制造方法,所述弹性波滤波器在输出端侧连接低噪声放大器,所述弹性波滤波器的制造方法包含:

获取表示所述低噪声放大器的噪声指数最小的所述弹性波滤波器的输出阻抗的噪声匹配阻抗、以及表示所述低噪声放大器的增益最大的所述输出阻抗的增益匹配阻抗的工序;和

依存于获取到的所述增益匹配阻抗与所述噪声匹配阻抗的史密斯圆图上的位置关系,制造所述弹性波滤波器的工序,

所述弹性波滤波器具有在连结输入端与所述输出端的路径上串联连接的纵耦合型的滤波器构造,

在制造所述弹性波滤波器的工序中,

(i) 在所述噪声匹配阻抗相对于所述增益匹配阻抗在所述史密斯圆图上位于左侧并且上侧的区域的情况下,制造所述弹性波滤波器以使得所述纵耦合型的滤波器构造被配置得最接近于所述输出端,

(ii) 在所述噪声匹配阻抗相对于所述增益匹配阻抗在所述史密斯圆图上位于右侧的区域的情况下,制造所述弹性波滤波器以使得在连结所述路径与接地的路径上串联连接的并联陷波器被配置得最接近于所述输出端,

(iii) 在所述噪声匹配阻抗相对于所述增益匹配阻抗在所述史密斯圆图上位于左侧并且下侧的区域的情况下,制造所述弹性波滤波器以使得在连结所述输入端与所述输出端的所述路径上串联连接的串联陷波器被配置得最接近于所述输出端。

## 高频模块以及弹性波滤波器的制造方法

### 技术领域

[0001] 本发明涉及具备低噪声放大器的高频模块、以及在后级连接低噪声放大器的弹性波滤波器的制造方法。

### 背景技术

[0002] 近年来,由于电子设备的高速化以及高速无线通信的普及,包含低噪声放大器(LNA:Low Noise Amplifier)的高频电路的需要提高。在接收电路中具备这种低噪声放大器的通信装置中,在低噪声放大器与其前级的滤波器电路之间设置匹配电路(例如,参照专利文献1)。

[0003] 这种匹配电路的输入阻抗以及输出阻抗相对于接收信号为标准化阻抗。换句话说,匹配电路构成为在滤波器电路的通频带具有成为标准化阻抗的输入阻抗以及输出阻抗。

[0004] 在先技术文献

[0005] 专利文献

[0006] 专利文献1:JP特开2009-60511号公报

[0007] 但是,在具备低噪声放大器以及这种匹配电路及滤波器电路的构成中,会产生以下问题。也就是说,低噪声放大器对具备其的高频模块或者通信装置等系统整体的低噪声性造成较大影响。因此,一般地关于低噪声放大器,最好构成为兼顾最大增益和最小噪声指数。但是,另一方面,一般地,在低噪声放大器的增益最大的阻抗和噪声指数最小的阻抗之间存在偏差。因此,在通过匹配电路对滤波器电路和低噪声放大器进行阻抗匹配以使得增益相对于滤波器电路的通频带最大的情况下,存在低噪声放大器的噪声指数特别是在通频带端容易劣化的问题。因此,在该情况下,难以实现高频模块等的传输特性的提高。

### 发明内容

[0008] 鉴于上述课题,本发明的目的在于,提供一种通过减少通频带端的噪声指数的劣化,能够提高传输特性的高频模块以及弹性波滤波器的制造方法。

[0009] 为了实现上述目的,本发明的一方式所涉及的高频模块具备:弹性波滤波器;和低噪声放大器,对从所述弹性波滤波器输出的高频信号进行放大,所述弹性波滤波器的输出阻抗在该弹性波滤波器的通频带的低频端以及高频端的至少一方的频率下,在史密斯圆图上位置靠近表示所述低噪声放大器的噪声指数最小的所述输出阻抗的噪声匹配阻抗、以及表示所述低噪声放大器的增益最大的所述输出阻抗的增益匹配阻抗之中的所述噪声匹配阻抗。

[0010] 通过这样弹性波滤波器的输出阻抗在通频带的低频端以及高频端的至少一方的频率靠近噪声匹配阻抗,从而在该至少一方的频率,能够减少低噪声放大器的噪声指数。由此,高频模块整体能够减少噪声指数的劣化容易产生的通频带端的噪声指数的劣化,因此能够提高传输特性。也就是说,能够提供传输特性优良的高频模块。

[0011] 此外,也可以所述输出阻抗在所述通频带的低频端以及高频端的任意频率下,在所述史密斯圆图上位置靠近所述噪声匹配阻抗。

[0012] 通过这样在弹性波滤波器的输出阻抗在通频带的低频端以及高频端的任意的频率都靠近噪声匹配阻抗,从而在该低频端以及高频端的双方的频率,能够减少低噪声放大器的噪声指数。由此,高频模块整体能够减少噪声指数的劣化容易产生的通频带端的双方的噪声指数的劣化,因此能够进一步提高传输特性。

[0013] 此外,也可以所述弹性波滤波器具有在连结输入端与输出端的路径上串联连接的纵耦合型的滤波器构造。

[0014] 通过这样弹性波滤波器具有纵耦合型的滤波器构造,从而通过调整电极参数等,能够容易地变更弹性波滤波器的输出阻抗。因此,相应于根据低噪声放大器的设计等而规定的噪声匹配阻抗以及增益匹配阻抗,能够构成具有适当的输出阻抗的弹性波滤波器。因此,例如,针对弹性波滤波器的输出阻抗,在通频带中央部能够使其与增益匹配阻抗一致,并且在通频带的低频端以及高频端的至少一方的频率能够使其与噪声匹配阻抗一致。因此,能够兼顾增益特性以及噪声特性。

[0015] 此外,也可以所述噪声匹配阻抗相对于所述增益匹配阻抗在所述史密斯圆图上位于左侧并且上侧的区域,所述纵耦合型的滤波器构造被配置得最接近于所述输出端。

[0016] 由此,与在纵耦合型的滤波器构造与输出端之间连接其他谐振器的情况相比,变得容易使弹性波滤波器的输出阻抗在通频带的低频端以及高频端的双方,在史密斯圆图上位于增益匹配阻抗的左侧并且上侧的区域。因此,在低频端以及高频端双方的频率,能够减少低噪声放大器的噪声指数。

[0017] 此外,也可以所述噪声匹配阻抗相对于所述增益匹配阻抗在所述史密斯圆图上位于右侧的区域,所述弹性波滤波器具有被配置得最接近于所述输出端并且在连结所述路径与接地的路径上串联连接的并联陷波器。

[0018] 由此,与不具有并联陷波器的情况相比,容易使弹性波滤波器的输出阻抗在通频带的低频端以及高频端的双方,在史密斯圆图上位于增益匹配阻抗的右侧的区域。因此,在低频端以及高频端的双方的频率,能够减少低噪声放大器的噪声指数。

[0019] 另外,也可以所述并联陷波器具有频率比所述通频带的低频端低的谐振点。

[0020] 通过具有这种谐振点的并联陷波器,针对弹性波滤波器的输出阻抗,在通频带中央部能够使其与增益匹配阻抗一致,在通频带的低频端以及高频端的至少一方的频率能够使其与噪声匹配阻抗一致。因此,能够兼顾增益特性以及噪声特性。

[0021] 此外,也可以所述噪声匹配阻抗相对于所述增益匹配阻抗在所述史密斯圆图上位于左侧并且下侧的区域,所述弹性波滤波器具有被配置得最接近于所述输出端并且在所述路径上串联连接的串联陷波器。

[0022] 由此,与不具有串联陷波器的情况相比,容易使弹性波滤波器的输出阻抗在通频带的低频端以及高频端的双方,在史密斯圆图上位于增益匹配阻抗的左侧并且下侧的区域。因此,在低频端以及高频端的双方的频率,能够减少低噪声放大器的噪声指数。

[0023] 此外,也可以所述串联陷波器具有频率比所述通频带的高频端高的反谐振点。

[0024] 通过具有这种反谐振点的串联陷波器,针对弹性波滤波器的输出阻抗,在通频带中央部能够使其与增益匹配阻抗一致,并且在通频带的低频端以及高频端的至少一方的频

率能够使其与噪声匹配阻抗一致。因此,能够兼顾增益特性以及噪声特性。

[0025] 此外,也可以在所述史密斯圆图上,所述通频带中的所述输出阻抗的轨迹与连结所述噪声匹配阻抗与所述增益匹配阻抗的线交叉。

[0026] 通过具备具有这种输出阻抗的弹性波滤波器,能够减少通频带端的噪声指数的劣化,并且兼顾增益特性以及噪声特性。

[0027] 此外,本发明也能够作为在输出端侧连接低噪声放大器的弹性波滤波器的制造方法来实现。也就是说,该弹性波滤波器的制造方法是一种在输出端侧连接低噪声放大器的弹性波滤波器的制造方法,包含:获取表示所述低噪声放大器的噪声指数最小的所述弹性波滤波器的输出阻抗的噪声匹配阻抗、以及表示所述低噪声放大器的增益最大的所述输出阻抗的增益匹配阻抗的工序;和依存于获取到的所述增益匹配阻抗与所述噪声匹配阻抗的史密斯圆图上的位置关系,制造所述弹性波滤波器的工序。

[0028] 通过这样依存于2个匹配阻抗(增益匹配阻抗以及噪声匹配阻抗)的史密斯圆图上的位置关系来制造弹性波滤波器,能够制造在通频带的低频端以及高频端的至少一方的频率,能够减少低噪声放大器的噪声指数的弹性波滤波器。因此,在将这样制造的弹性波滤波器应用于具备对从该弹性波滤波器输出的高频信号进行放大的低噪声放大器的例如高频模块的情况下,能够实现该高频模块的传输特性的提高。

[0029] 此外,也可以所述弹性波滤波器具有在连结输入端与所述输出端的路径上串联连接的纵耦合型的滤波器构造,在制造所述弹性波滤波器的工序中,(i)在所述噪声匹配阻抗相对于所述增益匹配阻抗在所述史密斯圆图上位于左侧并且上侧的区域的情况下,制造所述弹性波滤波器以使得所述纵耦合型的滤波器构造被配置得最接近于所述输出端,(ii)在所述噪声匹配阻抗相对于所述增益匹配阻抗在所述史密斯圆图上位于右侧的区域的情况下,制造所述弹性波滤波器以使得在连结所述路径与接地的路径上串联连接的并联陷波器被配置得最接近于所述输出端,(iii)在所述噪声匹配阻抗相对于所述增益匹配阻抗在所述史密斯圆图上位于左侧并且下侧的区域的情况下,制造所述弹性波滤波器以使得在连结所述输入端与所述输出端的所述路径上串联连接的串联陷波器被配置得最接近于所述输出端。

[0030] 由此,无论增益匹配阻抗与噪声匹配阻抗的史密斯圆图上的位置关系如何的情况下,都容易使弹性波滤波器的输出阻抗在通频带的低频端以及高频端双方,在史密斯圆图上位置靠近增益匹配阻抗。因此,能够制造在低频端以及高频端双方的频率,能够减少低噪声放大器的噪声指数的弹性波滤波器。

[0031] 根据本发明所涉及的高频模块等,能够减少通频带端的噪声指数的劣化,因此能够提高传输特性。

## 附图说明

[0032] 图1是表示实施方式所涉及的高频模块的构成的概念图。

[0033] 图2是表示实施方式中的谐振器的构成的示意图,(a)是俯视图,(b)是(a)所示的点划线中的向视剖视图。

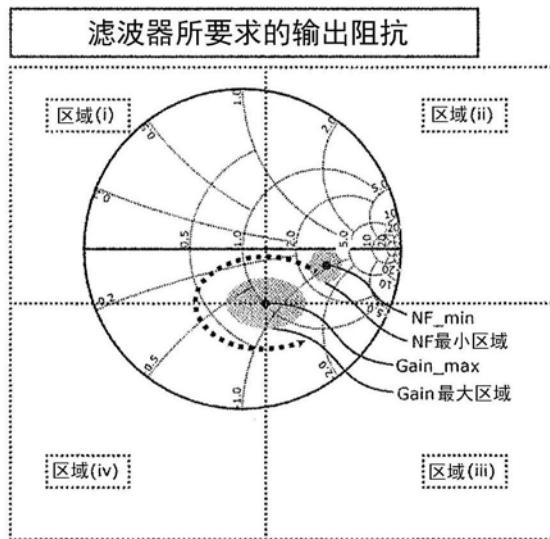

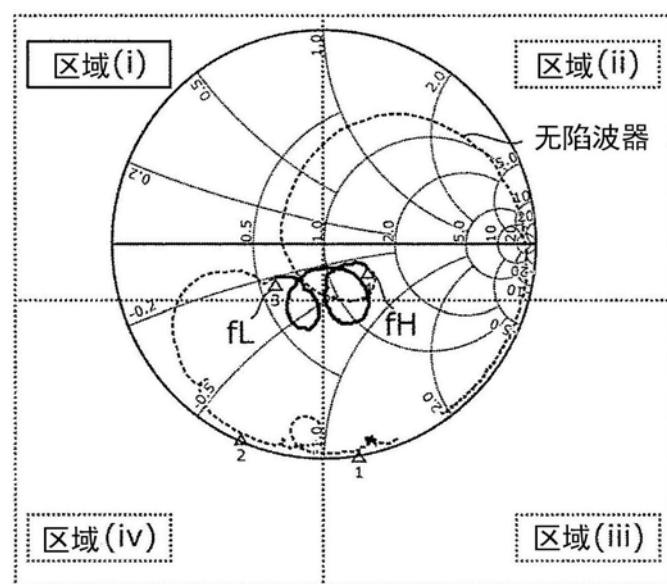

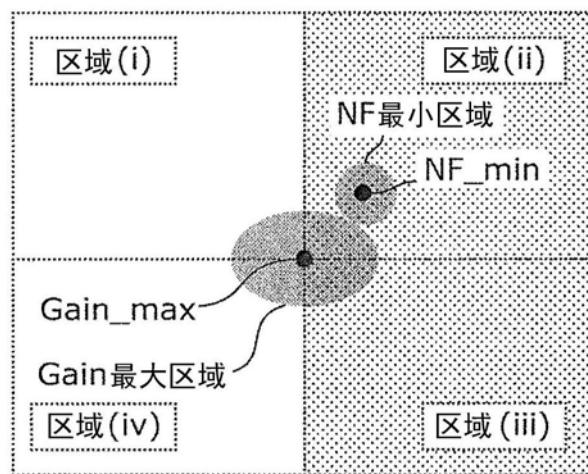

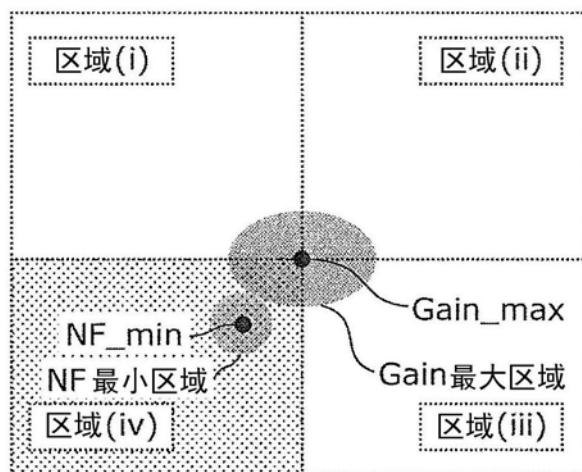

[0034] 图3A是对噪声匹配阻抗与增益匹配阻抗的位置关系改变进行说明的史密斯圆图。

[0035] 图3B是表示实施方式所涉及的弹性波滤波器的通频带内的输出阻抗的史密斯圆

图。

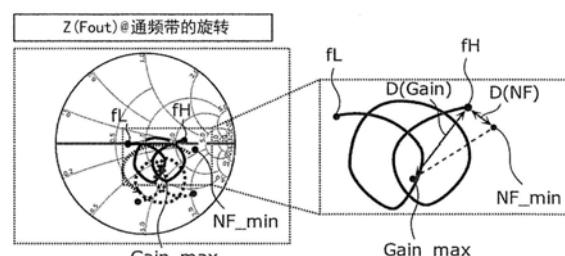

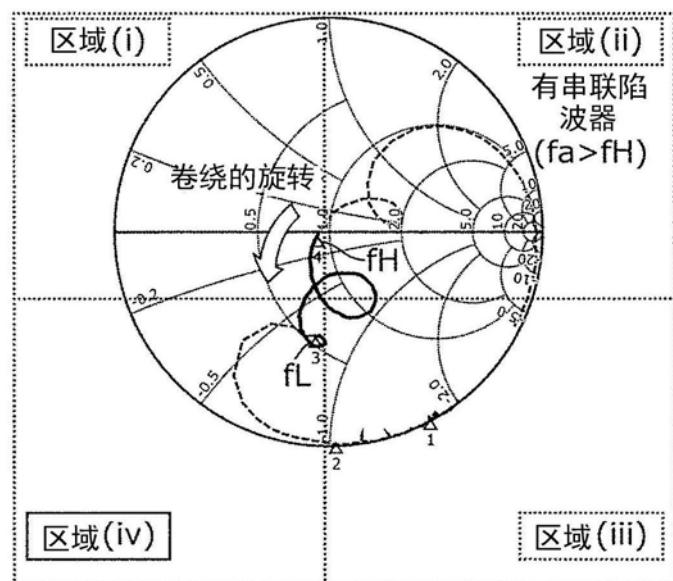

[0036] 图3C是对实施方式中,依赖于噪声匹配阻抗以及增益匹配阻抗的史密斯圆图上的位置关系,输出阻抗的卷绕进行旋转进行说明的图及其局部放大图。

[0037] 图4A是对实施例1中噪声匹配阻抗相对于增益匹配阻抗的位置进行说明的图。

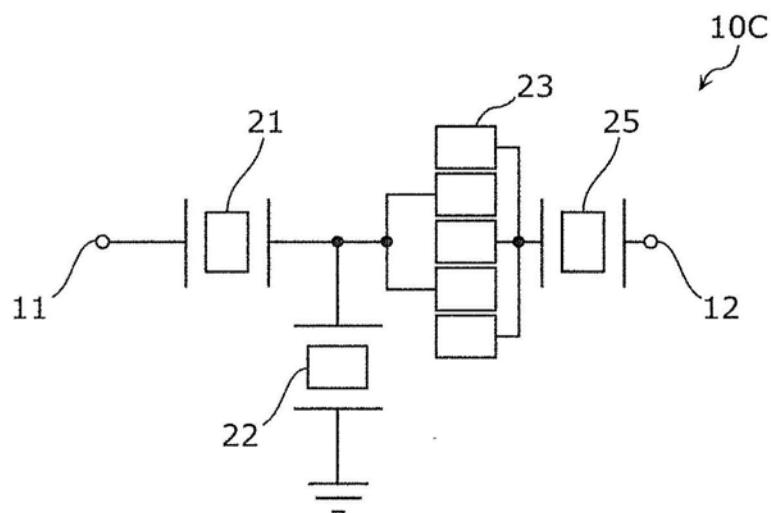

[0038] 图4B是实施例1中的弹性波滤波器的电路构成图。

[0039] 图4C是表示实施例1中的弹性波滤波器的输出阻抗的史密斯圆图。

[0040] 图5A是对实施例2中噪声匹配阻抗相对于增益匹配阻抗的位置进行说明的图。

[0041] 图5B是实施例2中的弹性波滤波器的电路构成图。

[0042] 图5C是表示实施例2中的弹性波滤波器的输出阻抗的史密斯圆图。

[0043] 图6A是对实施例3中噪声匹配阻抗相对于增益匹配阻抗的位置进行说明的图。

[0044] 图6B是实施例3中的弹性波滤波器的电路构成图。

[0045] 图6C是表示实施例3中的弹性波滤波器的输出阻抗的史密斯圆图。

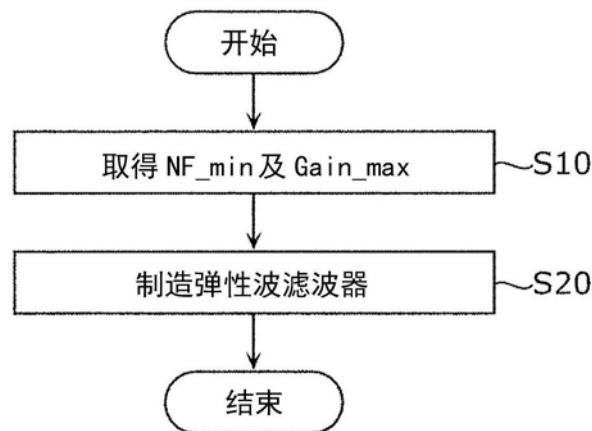

[0046] 图7是表示实施方式所涉及的弹性波滤波器的制造工序的流程图。

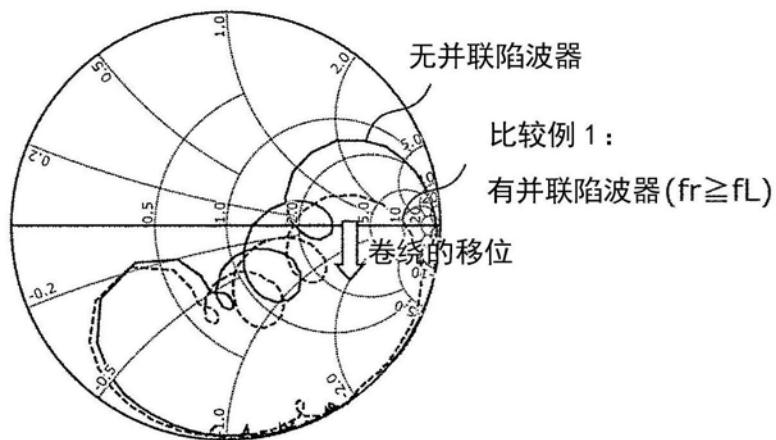

[0047] 图8A是表示不具有并联陷波器的弹性波滤波器以及比较例1中的弹性波滤波器的输出阻抗的史密斯圆图。

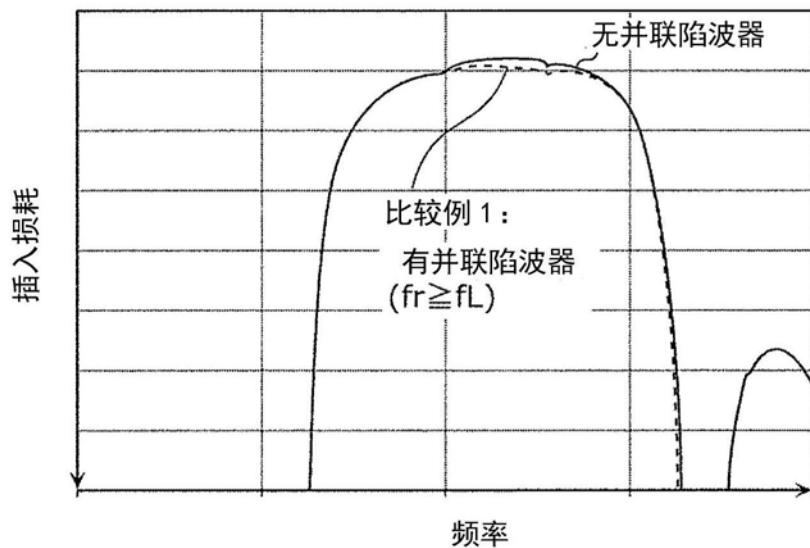

[0048] 图8B是表示不具有并联陷波器的弹性波滤波器以及比较例1中的弹性波滤波器的通过特性的图。

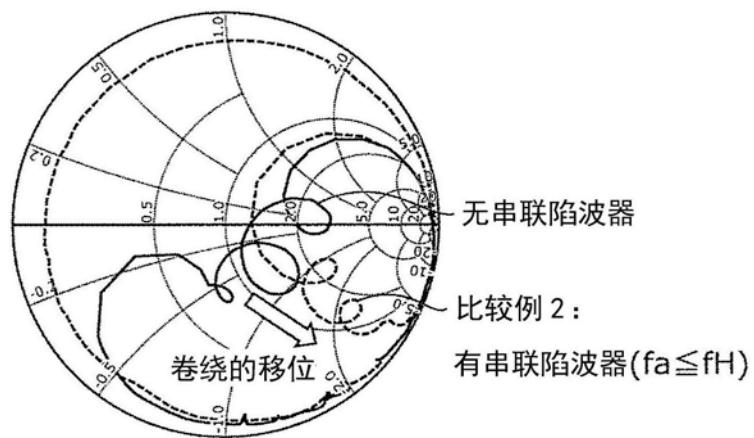

[0049] 图9A是表示不具有串联陷波器的弹性波滤波器以及比较例2中的弹性波滤波器的输出阻抗的史密斯圆图。

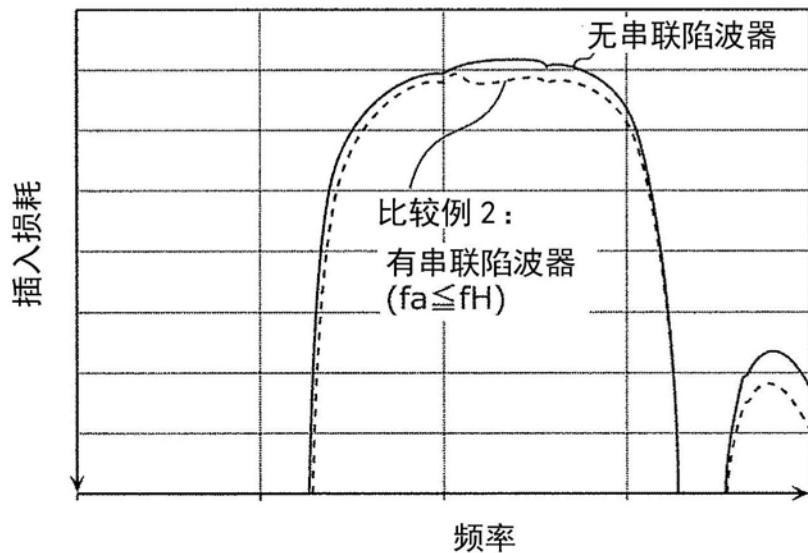

[0050] 图9B是表示不具有串联陷波器的弹性波滤波器以及比较例2中的弹性波滤波器的通过特性的图。

[0051] -符号说明-

[0052] 1 高频模块

[0053] 3 RFIC (RF信号处理电路)

[0054] 4 通信装置

[0055] 10、10A、10B、10C 弹性波滤波器

[0056] 11 输入端

[0057] 12 输出端

[0058] 21 串联谐振器

[0059] 22 并联谐振器

[0060] 23 纵耦合谐振器(纵耦合型的滤波器构造)

[0061] 24 并联谐振器(并联陷波器)

[0062] 25 串联谐振器(串联陷波器)

[0063] 30 匹配电路

[0064] 40 低噪声放大器

[0065] 100 谐振器

[0066] 101a、101b IDT电极

[0067] 110a、110b 电极指

[0068] 111a、111b 汇流条电极

- [0069] 123 压电基板

- [0070] 124a 密接层

- [0071] 124b 主电极层

- [0072] 125 保护层

## 具体实施方式

[0073] 以下,对本发明的实施方式进行说明。另外,以下说明的实施方式均表示本发明的优选的一具体例。因此,以下的实施方式中所示的数值、形状、材料、构成要素、构成要素的配置位置以及连接方式等是一个例子,并不是限定本发明的主旨。因此,以下的实施方式中的构成要素之中,针对表示本发明的最上位概念的独立权利要求中未记载的构成要素,被说明为任意的构成要素。

[0074] 此外,各图是示意图,不必严格地进行图示。各图中,对实质相同的构成赋予相同的符号,省略或者简化重复的说明。此外,在图示的电极构造中,为了使本发明的理解容易,比实际的电极指的根数更少地图示谐振器以及反射器中的电极指的根数。

- [0075] (实施方式)

- [0076] 以下,对实施方式进行说明。

- [0077] [1.整体构成]

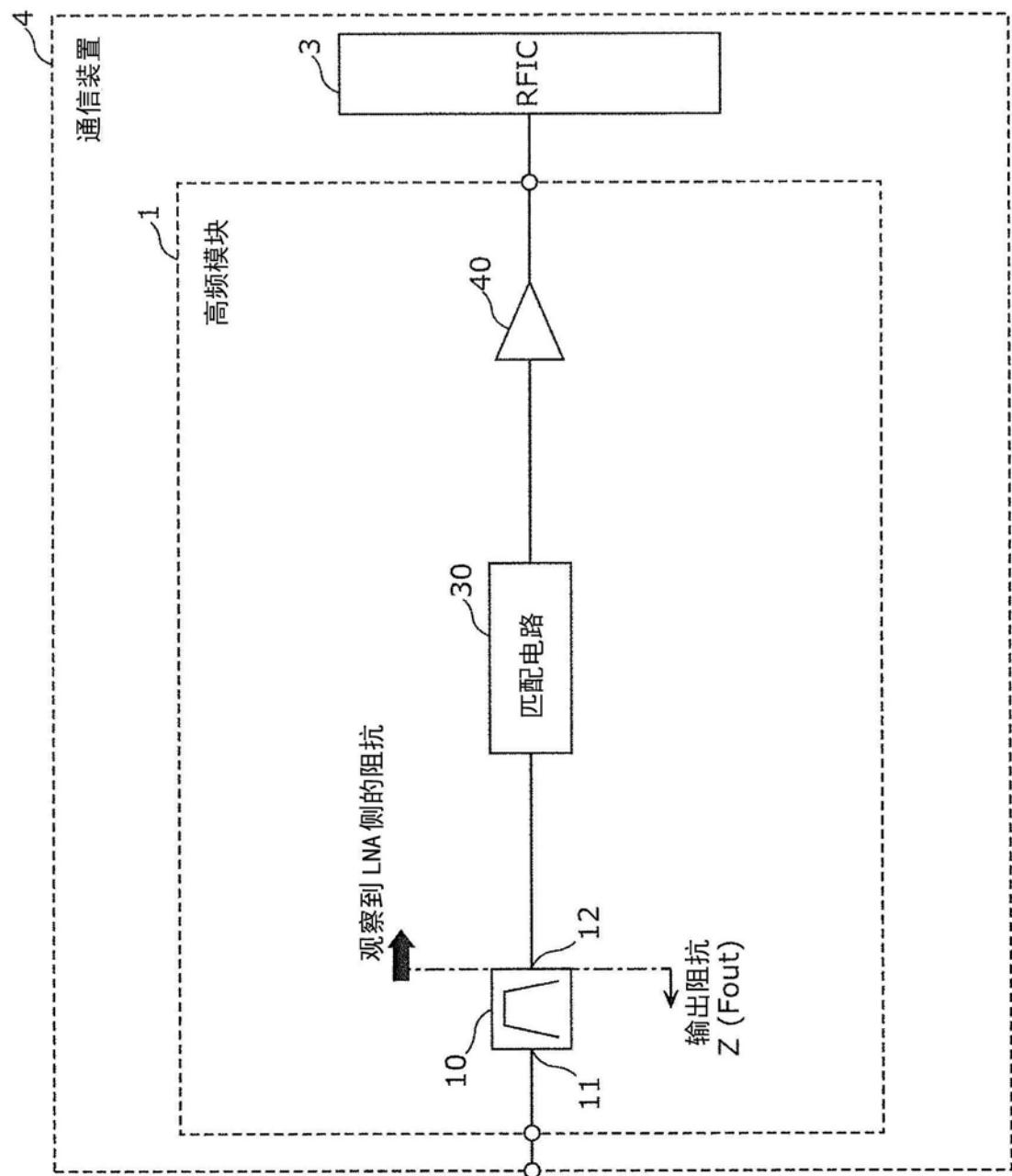

[0078] 首先,对本实施方式所涉及的高频模块1的构成进行说明。图1是表示本实施方式所涉及的高频模块1的概念图。另外,该图中,与高频模块1一并图示构成通信装置4的RF信号处理电路(RFIC:Radio Frequency Integrated Circuit,射频集成电路)3。

[0079] RFIC3是对由天线元件(未图示)收发的高频信号进行处理的RF信号处理电路。具体而言,RFIC3通过向下变换等对从天线元件经由高频模块1而输入的高频信号(这里为高频接收信号)进行信号处理,将该进行信号处理而生成的接收信号输出到基带信号处理电路(未图示)。

- [0080] 接下来,对高频模块1的详细构成进行说明。

[0081] 如图1所示,本实施方式所涉及的高频模块1具备:弹性波滤波器10、匹配电路30和低噪声放大器40。

[0082] 弹性波滤波器10是以规定的通频带对从天线元件输入到输入端11(输入端子)的高频信号进行滤波并从输出端12(输出端子)输出的例如带通滤波器。弹性波滤波器10为了提高高频模块1整体的传输特性,具有依存于从输出端12观察低噪声放大器40侧的阻抗的输出阻抗Z(Fout)。关于此,与根据低噪声放大器40的设计等而对弹性波滤波器10的输出端12要求的阻抗一并后面进行叙述。

[0083] 另外,所谓弹性波滤波器10的输出阻抗Z(Fout),是指从该弹性波滤波器10的输出端12观察弹性波滤波器10内部时的阻抗。

[0084] 在本实施方式中,弹性波滤波器10由使用了声表面波(SAW:Surface Acoustic Wave)的弹性波谐振器构成。另外,弹性波滤波器10并不局限于带通滤波器,例如也可以是高通滤波器或者低通滤波器。此外,弹性波滤波器10的构成并不局限于上述,例如也可以由使用了体波(BAW:Bulk Acoustic Wave)或者弹性边界波的弹性波谐振器构成。

- [0085] 匹配电路30是对从弹性波滤波器10的输出端12观察在低噪声放大器40连接有该

匹配电路30的电路部分时的阻抗进行调整的电路。在本实施方式中,匹配电路30由串联连接于将该匹配电路30的输入端子与输出端子连结的路径的电感器构成。

[0086] 一般地,设置于前级的电路与后级的电路之间的连接电路被设计为从前级的电路的输出端观察后级的电路侧时的阻抗成为特性阻抗(例如50Ω)。

[0087] 与此相对地,在本实施方式中,通过匹配电路30由电感器构成,从弹性波滤波器10的输出端12观察低噪声放大器40侧的阻抗不必为特性阻抗。由于这种匹配电路30与一般的T型或π型的匹配电路相比,能够减少元件数,因此能够小型化。

[0088] 另外,匹配电路30的构成并不局限于此,由连接于该路径的阻抗元件构成即可。具体而言,匹配电路30能够由串联连接于将输入端子与输出端子连结的路径的电感器或者电容器、或串联连接于将该路径与接地连结的路径的电感器或者电容器等构成。此外,在本实施方式所涉及的高频模块1中,匹配电路30不是必须的构成要素,也可以不被设置。

[0089] 低噪声放大器40是尽量在不增加噪声的情况下对接收后的微弱的电波进行放大的放大器。换句话说,低噪声放大器40是对从弹性波滤波器10输出的高频信号进行放大的低噪声放大电路,由晶体管等构成。

[0090] [2. 弹性波滤波器]

[0091] 接下来,对弹性波滤波器10的详细构成进行说明。本实施方式所涉及的弹性波滤波器10由以下说明的谐振器构成,具体而言,具有纵耦合型的滤波器构造。

[0092] [2-1. 谐振器构造]

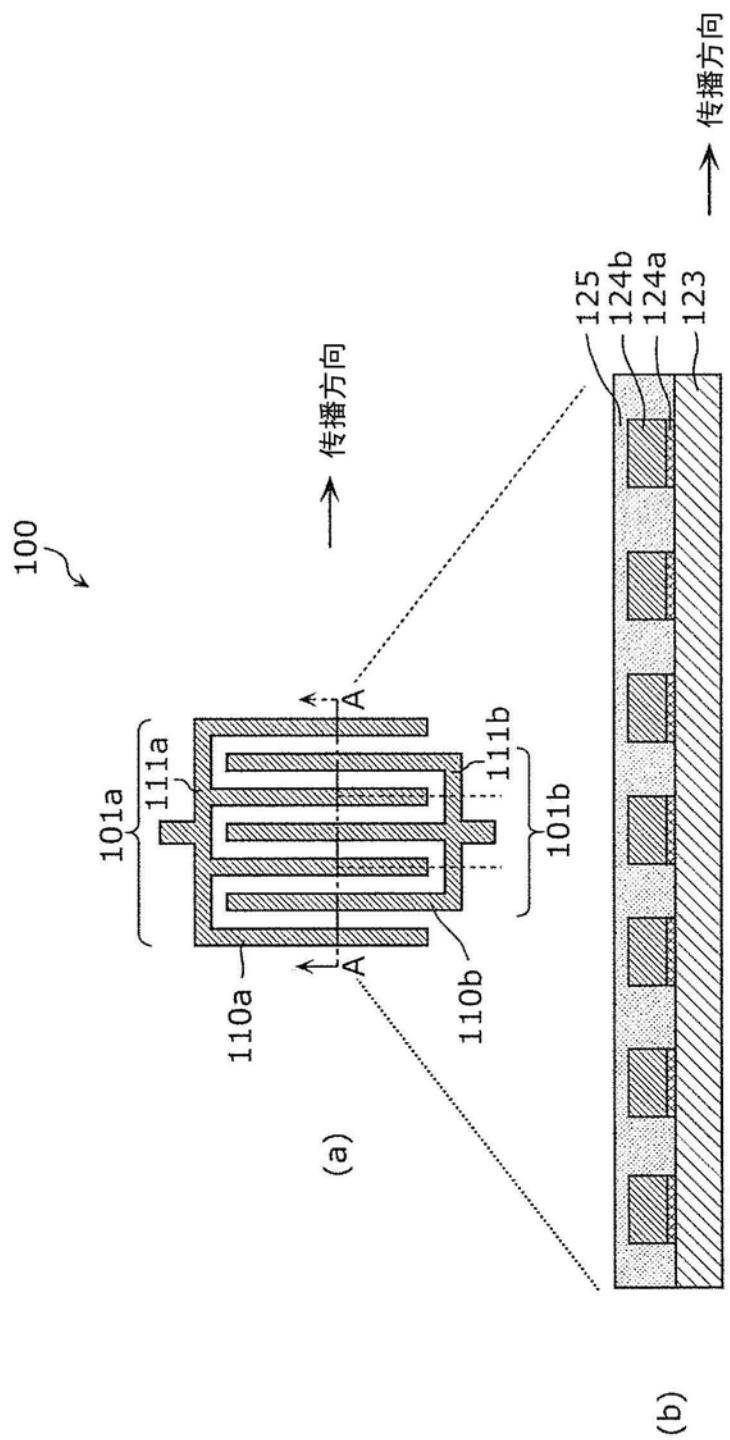

[0093] 图2是表示本实施方式中的谐振器100的构成的示意图,(a)是俯视图,(b)是(a)所示的点划线中的向视剖视图。另外,该图所示的谐振器100用于对构成弹性波滤波器10的多个谐振器的典型构造进行说明,构成电极的电极指的根数、长度并不限定于此。

[0094] 如图2(a)以及(b)所示,谐振器100由压电基板123、具有梳形形状的IDT电极101a以及IDT电极101b构成。

[0095] 压电基板123例如由以规定的切割角被切断的LiNbO<sub>3</sub>的单晶构成。在压电基板123中,在规定的方向传播声表面波。

[0096] 如图2(a)所示,在压电基板123上,形成对置的一对IDT电极101a以及IDT电极101b。IDT电极101a由相互平行的多个电极指110a和将多个电极指110a连接的汇流条电极111a构成。此外, IDT电极101b由相互平行的多个电极指110b和将多个电极指110b连接的汇流条电极111b构成。IDT电极101a和IDT电极101b为在IDT电极101a与IDT电极101b之中的一个IDT电极的多个电极指110b的每一个之间,分别配置另一个IDT电极的多个电极指110a的构成。

[0097] 此外,如图2(b)所示, IDT电极101a以及IDT电极101b为密接层124a与主电极层124b层叠而成的构造。

[0098] 密接层124a是用于提高压电基板123与主电极层124b的密接性的层,作为材料,例如使用NiCr。

[0099] 主电极层124b例如使用Pt来作为材料。主电极层124b可以是一种膜厚,也可以是多种膜厚。

[0100] 保护层125形成为覆盖IDT电极101a以及IDT电极101b。保护层125是以保护主电极层124b不受外部环境影响、调整频率温度特性以及提高耐湿性等为目的的层。保护层125例

如是以二氧化硅为主成分的膜。保护层125可以是一种膜厚,也可以是多种膜厚。

[0101] 另外,构成密接层124a、主电极层124b以及保护层125的材料并不限定于上述的材料。进一步地, IDT电极101a以及IDT电极101b也可以不是上述层叠构造。IDT电极101a以及IDT电极101b例如也可以由Ti、Al、Cu、Pt、Au、Ag、Pd等金属或者合金构成,此外,也可以由上述的金属或者合金所构成的多个层叠体构成。此外,保护层125也可以不形成。

[0102] 通过以上那样的谐振器100,本实施方式所涉及的弹性波滤波器10形成上述的带通滤波器。

[0103] [2-2.输出阻抗调整的概要]

[0104] 这里,由于高频模块1整体的噪声指数受到弹性波滤波器10的传输特性的影响,因此在弹性波滤波器10的通频带的特别是低频端fL(通频带的下限频率)以及高频端fH(通频带的上限频率)容易劣化。因此,为了在该通频带整体抑制高频模块1的噪声指数的劣化,需要改善通频带的低频端fL以及高频端fH处的噪声指数。

[0105] 关于此,本申请发明人进行仔细研究的结果,着眼于以下内容并实现了上述噪声指数的改善。也就是说,一般地,在弹性波滤波器和低噪声放大器中,被进行阻抗匹配以使得在弹性波滤波器的通频带中央部,低噪声放大器的增益最大。但是,另一方面,一般地,在低噪声放大器中,增益最大的阻抗与噪声指数最小的阻抗不同。

[0106] 因此,认为通过在弹性波滤波器的通频带的低频端fL以及高频端fH,使弹性波滤波器与低噪声放大器进行阻抗匹配以使得低噪声放大器的噪声指数变小,从而能够在该通频带整体抑制高频模块的噪声指数的劣化。

[0107] 但是,在低噪声放大器中,增益最大的阻抗与噪声指数最小的阻抗的相对关系依存于该低噪声放大器的设计等。因此,为了如上述那样使其进行阻抗匹配,需要依存于与弹性波滤波器的后级连接的低噪声放大器的增益最大的阻抗与噪声指数最小的阻抗的相对关系,设计该弹性波滤波器。

[0108] 因此,本实施方式所涉及的弹性波滤波器10具有依存于从输出端12观察低噪声放大器40侧的阻抗而被调整的输出阻抗Z(Fout)。具体而言,该输出阻抗Z(Fout)在弹性波滤波器10的通频带的低频端fL以及高频端fH的至少一方的频率下,在史密斯圆图上位置更靠近噪声匹配阻抗以及增益匹配阻抗之中的噪声匹配阻抗。

[0109] 这里,噪声匹配阻抗表示低噪声放大器40的噪声指数最小的弹性波滤波器10的输出阻抗。换句话说,噪声匹配阻抗是在低噪声放大器40的噪声指数最小时,从弹性波滤波器10的输出端12观察低噪声放大器40侧的阻抗的复共轭阻抗。换言之,噪声匹配阻抗是为了低噪声放大器40的噪声指数最小而对弹性波滤波器10的输出端12要求的阻抗。

[0110] 此外,增益匹配阻抗表示低噪声放大器40的增益最大的弹性波滤波器10的输出阻抗。换句话说,增益匹配阻抗是在低噪声放大器40的增益最大时,从弹性波滤波器10的输出端12观察低噪声放大器40侧的阻抗的复共轭阻抗。换言之,增益匹配阻抗是为了低噪声放大器40的增益最大而对弹性波滤波器10的输出端12要求的阻抗。

[0111] 这些噪声匹配阻抗与增益匹配阻抗的史密斯圆图上的位置关系通过低噪声放大器40单体的阻抗、以及基于弹性波滤波器10与低噪声放大器40之间的匹配电路30等的阻抗调整而被规定。因此,噪声匹配阻抗与增益匹配阻抗的史密斯圆图上的位置关系根据构成高频模块1的低噪声放大器40等电路元件、以及匹配电路30等电路构成而变化。

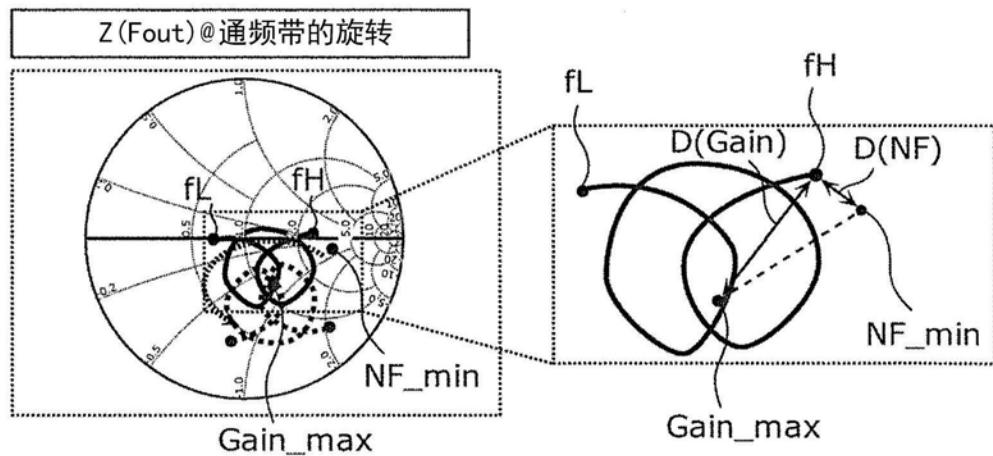

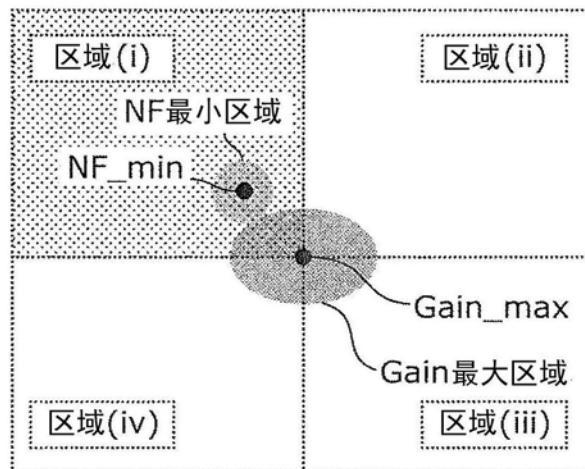

[0112] 图3A是对噪声匹配阻抗与增益匹配阻抗的位置关系变化进行说明的史密斯圆图。

[0113] 另外,在该图中,以通过匹配电路30等来将增益匹配阻抗Gain\_max调整为规定的阻抗(例如50以上且小于70Ω)附近的情况为例进行图示,以下,以此为前提来进行说明。但是,增益匹配阻抗Gain\_max的值并不局限于上述的规定的阻抗,能够根据对高频模块1要求的特性等,适当地进行调整。

[0114] 此外,该图所示的NF最小区域例如表示由噪声指数从噪声匹配阻抗NF\_min劣化(增大)了规定量(例如0.1dB)的NF圆形包围的区域。此外,该图所示的Gain最大区域例如表示增益从增益匹配阻抗Gain\_max劣化(降低)了规定量(例如,0.5dB)的增益圆形。这在以下的图中也是同样的。

[0115] 如该图所示,在增益匹配阻抗Gain\_max被调整为规定的阻抗的情况下,在史密斯圆图上,噪声匹配阻抗NF\_min能够位于增益匹配阻抗Gain\_max的周围的任意方向。

[0116] 换句话说,若在史密斯圆图上以增益匹配阻抗Gain\_max为基准规定上下左右的4个区域(象限),则噪声匹配阻抗NF\_min在史密斯圆图上能够位于以下4个区域(i)~(iv)的任意区域。所谓4个区域(i)~(iv),是指在史密斯圆图上相对于增益匹配阻抗Gain\_max为左侧并且上侧的区域的区域(i)、在史密斯圆图上相对于增益匹配阻抗Gain\_max为右侧并且上侧的区域的区域(ii)、在史密斯圆图上相对于增益匹配阻抗Gain\_max为右侧并且下侧的区域的区域(iii)、以及在史密斯圆图上相对于增益匹配阻抗Gain\_max为左侧并且下侧的区域的区域(iv)。

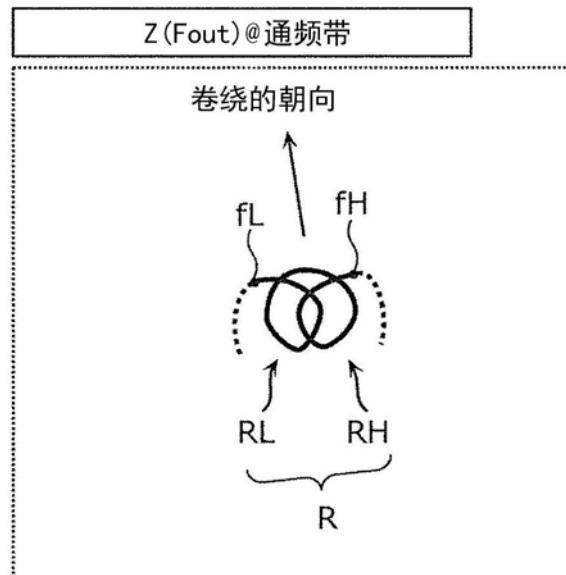

[0117] 图3B是表示本实施方式所涉及的弹性波滤波器10的通频带内的输出阻抗Z(Fout)的史密斯圆图。另外,在该图中,通频带外的一部分的输出阻抗也由虚线表示。此外,该图所示的输出阻抗Z(Fout)的轨迹是一个例子,本实施方式所涉及的弹性波滤波器10的输出阻抗Z(Fout)的轨迹并不限定于此。

[0118] 如该图所示,弹性波滤波器10的输出阻抗Z(Fout)在史密斯圆图上,从通频带的低频端fL到高频端fH形成卷绕R。该卷绕R包含低频端fL侧的卷绕RL以及高频端fH侧的卷绕RH,低频端fL以及高频端fH位于卷绕RL以及RH的一侧。因此,以下,在史密斯圆图上,将相对于卷绕RL以及RH的排列方向垂直并且朝向低频端fL以及高频端fH的方向设为“卷绕的朝向”来进行说明。

[0119] 这种输出阻抗Z(Fout)的卷绕R在被调整为通频带中央部的输出阻抗Z(Fout)为增益匹配阻抗Gain\_max的情况下,依存于噪声匹配阻抗NF\_min与增益匹配阻抗Gain\_max的史密斯圆图上的位置关系来进行旋转。

[0120] 图3C是对本实施方式中,依存于噪声匹配阻抗NF\_min以及增益匹配阻抗Gain\_max的史密斯圆图上的位置关系,输出阻抗Z(Fout)的卷绕R进行旋转进行说明的图及其局部放大图。

[0121] 如该图所示,弹性波滤波器10为了兼顾增益特性以及噪声特性,被调整为通频带中央部的输出阻抗Z(Fout)为增益匹配阻抗Gain\_max并且被调整为通频带的低频端fL以及高频端fH的至少一方的输出阻抗靠近于噪声匹配阻抗NF\_min。

[0122] 因此,如该图所示,在史密斯圆图上噪声匹配阻抗NF\_min相对于增益匹配阻抗Gain\_max位于上侧的情况下,弹性波滤波器10在通频带的低频端fL以及高频端fH的至少一方(该图中为高频端fH)的频率具有在史密斯圆图上位置靠近噪声匹配阻抗NF\_min的输出

阻抗Z(Fout)。因此,在史密斯圆图上,上述卷绕大体向上。

[0123] 另一方面,在史密斯圆图上噪声匹配阻抗NF\_min相对于增益匹配阻抗Gain\_max位于下侧的情况下,弹性波滤波器10在通频带的低频端fL以及高频端fH的至少一方(在该图中为高频端fH)的频率具有在史密斯圆图上位置靠近噪声匹配阻抗NF\_min的输出阻抗Z(Fout)。因此,在史密斯圆图上,上述卷绕大体向下。

[0124] 这里,在史密斯圆图上,所谓输出阻抗Z(Fout)位置靠近噪声匹配阻抗NF\_min,如局部放大图所示,是指到噪声匹配阻抗NF\_min的距离D(NF)以及到增益匹配阻抗Gain\_max的距离D(Gain)满足D(NF) < D(Gain)。换句话说,输出阻抗Z(Fout)在通频带的低频端fL以及高频端fH的至少一方的频率,在史密斯圆图上位置比将噪声匹配阻抗NF\_min与增益匹配阻抗Gain\_max连结的线段的垂直二等分线更靠噪声匹配阻抗NF\_min一侧。

[0125] 此外,如局部放大图所示,在史密斯圆图上,通频带中的输出阻抗Z(Fout)的轨迹与将噪声匹配阻抗NF\_min与增益匹配阻抗Gain\_max连结的线(图中的点线)交叉。

[0126] 通过使用具有以上那样的输出阻抗Z(Fout)的弹性波滤波器10,根据本实施方式,能够改善弹性波滤波器10的通频带的特别是在低频端以及高频端容易劣化的噪声指数。因此,能够减少高频模块1整体的噪声指数的劣化并提高传输特性。

[0127] [3.实施例]

[0128] 因此,以下,使用实施例来对增益匹配阻抗Gain\_max与噪声匹配阻抗NF\_min的史密斯圆图上的位置关系所对应的弹性波滤波器10的构成以及阻抗特性详细进行说明。

[0129] [3-1.实施例1]

[0130] 首先,作为实施例1,对噪声匹配阻抗NF\_min相对于增益匹配阻抗Gain\_max在史密斯圆图上位于左侧并且上侧的区域(i)的情况进行说明。

[0131] 图4A是对实施例1中噪声匹配阻抗NF\_min相对于增益匹配阻抗Gain\_max的位置进行说明的图。

[0132] 如该图所示,在本实施例中,噪声匹配阻抗NF\_min位于区域(i)。例如,噪声匹配阻抗NF\_min位于区域(i)之中比较接近于增益匹配阻抗Gain\_max的区域。

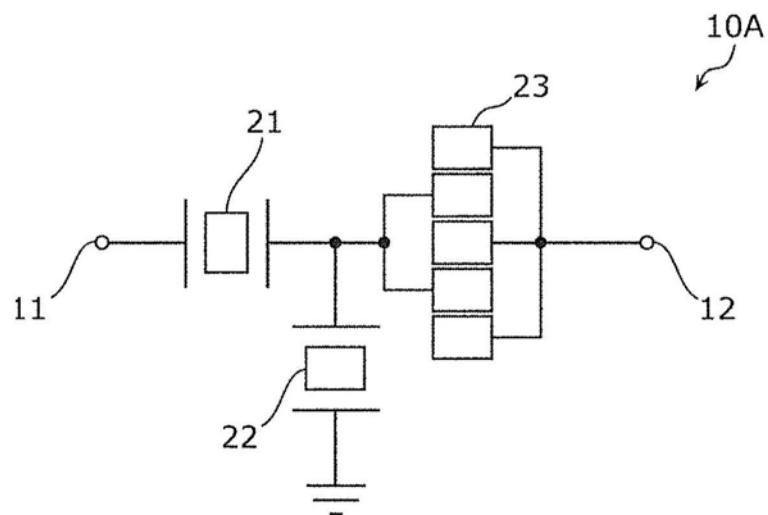

[0133] 图4B是实施例1中的弹性波滤波器10A的电路构成图。

[0134] 如该图所示,弹性波滤波器10A从输入端11侧起依次具备:串联谐振器21、并联谐振器22以及纵耦合谐振器23。

[0135] 串联谐振器21是在连结输入端11与输出端12的路径上串联连接的谐振器。并联谐振器22是在连结该路径与接地的路径上串联连接的谐振器。这些串联谐振器21以及并联谐振器22形成梯子型的滤波器构造。

[0136] 纵耦合谐振器23是在连结输入端11与输出端12的路径上串联连接的纵耦合型的滤波器构造。在本实施例中,纵耦合谐振器23最接近于输出端12而被配置。换句话说,纵耦合谐振器23与输出端12在不连接其他谐振器的情况下进行连接。

[0137] 这样,实施例1所涉及的弹性波滤波器10A是梯子型的滤波器构造与纵耦合型的滤波器构造组合的。另外,弹性波滤波器10A的构成并不局限于此,例如也可以仅由纵耦合型的滤波器构造(即纵耦合谐振器23)构成。

[0138] 图4C是表示实施例1中的弹性波滤波器10A的输出阻抗的史密斯圆图。另外,在该图中,弹性波滤波器10A的通频带中的该输出阻抗由实线表示,通频带外的该输出阻抗由虚

线表示。这在以下的实施例中表示输出阻抗的史密斯圆图中也是同样的。

[0139] 此时,虽省略图示,但通频带的低频端fL以及高频端fH的至少一方(在本实施例中为低频端fL)中的输出阻抗在噪声匹配阻抗NF\_min以及增益匹配阻抗Gain\_max之中位置靠近噪声匹配阻抗NF\_min。

[0140] 此外,由该图可知,在本实施例1中,从通频带的低频端fL到高频端fH形成的卷绕的朝向为区域(i)侧。具体而言,通频带的低频端fL中的输出阻抗位于区域(i),通频带的高频端fH中的输出阻抗位于区域(ii)。

[0141] [3-2. 实施例2]

[0142] 接下来,作为实施例2,对噪声匹配阻抗NF\_min相对于增益匹配阻抗Gain\_max在史密斯圆图上位于右侧的区域(ii)或者(iii)的情况进行说明。

[0143] 图5A是对实施例2中噪声匹配阻抗NF\_min相对于增益匹配阻抗Gain\_max的位置进行说明的图。

[0144] 如该图所示,在本实施例中,噪声匹配阻抗NF\_min位于区域(ii)或者(iii)。例如,噪声匹配阻抗NF\_min在区域(ii)之中位于比较接近于增益匹配阻抗Gain\_max的区域。

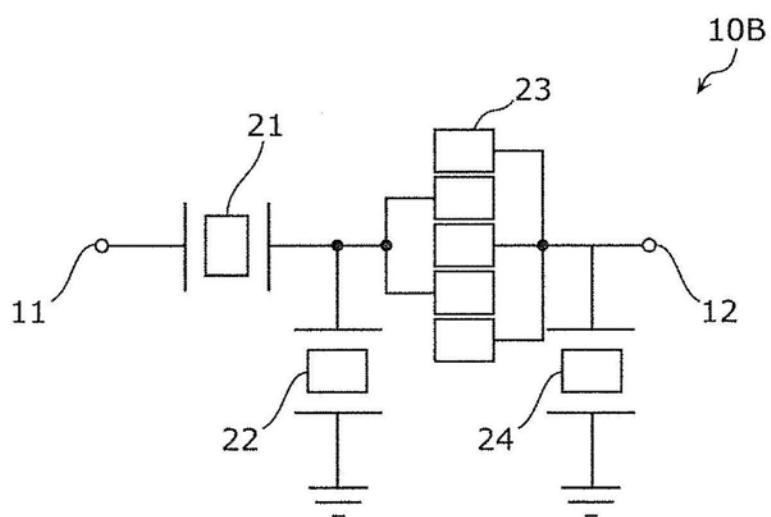

[0145] 图5B是实施例2中的弹性波滤波器10B的电路构成图。

[0146] 如该图所示,弹性波滤波器10B与实施例1所涉及的弹性波滤波器10A相比,还具备并联谐振器24。

[0147] 并联谐振器24被配置为最接近于输出端12,并且是在将连结输入端11与输出端12的路径和接地连结的路径串联连接的并联陷波器。换句话说,并联谐振器24与输出端12在不连接其他谐振器的情况下进行连接。

[0148] 这样,实施例2所涉及的弹性波滤波器10B在梯子型的滤波器构造与纵耦合型的滤波器构造的组合上附加了并联陷波器。另外,弹性波滤波器10B的构成并不局限于此,例如也可以仅由纵耦合型的滤波器构造(即纵耦合谐振器23)和并联陷波器(即并联谐振器24)构成。

[0149] 这里,并联谐振器24(并联陷波器)具有频率比弹性波滤波器10B的通频带的低频端fL低的谐振点。换句话说,若将该谐振点的频率(谐振频率)设为fr,则满足fr<fL。

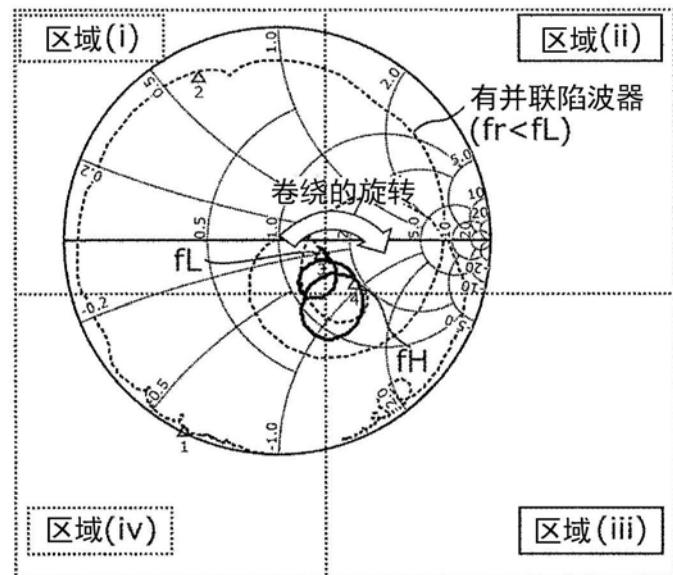

[0150] 图5C是表示实施例2中的弹性波滤波器10B的输出阻抗的史密斯圆图。

[0151] 此时,虽省略图示,但通频带的低频端fL以及高频端fH的至少一方(在本实施例中为高频端fH)的输出阻抗在噪声匹配阻抗NF\_min以及增益匹配阻抗Gain\_max之中位置靠近噪声匹配阻抗NF\_min。

[0152] 此外,由该图所示,在本实施例2中,从通频带的低频端fL到高频端fH形成的卷绕的朝向为区域(ii)侧。换句话说,实施例2所涉及的弹性波滤波器10B与实施例1所涉及的弹性波滤波器10A相比,通过具备并联谐振器24(并联陷波器),从而上述卷绕的朝向右旋地旋转。具体而言,通频带的低频端fL中的输出阻抗位于区域(i),通频带的高频端fH中的输出阻抗位于区域(ii)。

[0153] [3-3. 实施例3]

[0154] 接下来,作为实施例3,对噪声匹配阻抗NF\_min相对于增益匹配阻抗Gain\_max在史密斯圆图上位于左侧并且下侧的区域(iv)的情况进行说明。

[0155] 图6A是对实施例3中噪声匹配阻抗NF\_min相对于增益匹配阻抗Gain\_max的位置进

行说明的图。

[0156] 如该图所示,在本实施例中,噪声匹配阻抗NF\_min位于区域(iv)。例如,噪声匹配阻抗NF\_min位于区域(iv)中比较接近于增益匹配阻抗Gain\_max的区域。

[0157] 图6B是实施例3中的弹性波滤波器10C的电路构成图。

[0158] 如该图所示,弹性波滤波器10C与实施例1所涉及的弹性波滤波器10A相比,还具备串联谐振器25。

[0159] 串联谐振器25是最接近于输出端12而被配置、并且在将输入端11与输出端12连结的路径上串联连接的串联陷波器。换句话说,串联谐振器25与输出端12在不与其他谐振器连接的情况下进行连接。

[0160] 这样,实施例3所涉及的弹性波滤波器10C在梯子型的滤波器构造与纵耦合型的滤波器构造的组合上附加了串联陷波器。另外,弹性波滤波器10C的构成并不局限于此,例如也可以仅由纵耦合型的滤波器构造(即纵耦合谐振器23)和串联陷波器(即串联谐振器25)构成。

[0161] 这里,串联谐振器25(串联陷波器)具有频率比弹性波滤波器10C的通频带的高频端fH高的反谐振点。换句话说,若将该反谐振点的频率(反谐振频率)设为fa,则满足fa>fH。

[0162] 图6C是表示实施例3中的弹性波滤波器10C的输出阻抗的史密斯圆图。

[0163] 此时,虽省略图示,但通频带的低频端fL以及高频端fH的至少一方(在本实施例中为低频端fL以及高频端fH的双方)的输出阻抗位置靠近噪声匹配阻抗NF\_min以及增益匹配阻抗Gain\_max之中的噪声匹配阻抗NF\_min。

[0164] 此外,由该图所示,在本实施例3中,从通频带的低频端fL到高频端fH形成的卷绕的朝向为区域(i)与(ii)的边界部。换句话说,实施例3所涉及的弹性波滤波器10C与实施例1所涉及的弹性波滤波器10A相比,通过具备串联谐振器25(串联陷波器),上述卷绕的朝向左旋地进行旋转。具体而言,通频带的低频端fL中的输出阻抗位于区域(iv),通频带的高频端fH中的输出阻抗位于区域(i)。

[0165] [4. 制造方法]

[0166] 使用以上的实施例1~3来说明的本实施方式所涉及的弹性波滤波器10例如通过如下制造工序(制造方法)而被制造。

[0167] 图7是表示本实施方式所涉及的弹性波滤波器10的制造工序的流程图。换句话说,在该图中,表示在输出端12侧连接低噪声放大器40的弹性波滤波器10的制造工序。

[0168] 如该图所示,弹性波滤波器10的制造方法包含:获取噪声匹配阻抗NF\_min以及增益匹配阻抗Gain\_max的第1工序(S10)、和制造弹性波滤波器10的第2工序(S20)。

[0169] 在第1工序(S10)中,例如,在制造弹性波滤波器10之前的高频模块1中,通过从应成为弹性波滤波器10的输出端12的点测量低噪声放大器40侧的阻抗,从而获取2个匹配阻抗(噪声匹配阻抗NF\_min以及增益匹配阻抗Gain\_max)。

[0170] 另外,获取这2个匹配阻抗的手法并不局限于此,例如,也可以使用低噪声放大器40的构成等规格、以及从弹性波滤波器10到低噪声放大器40的电路构成等,通过EDA(Electronic Design Automation,电子设计自动化)等自动工具来获取。换句话说,第1工序(S10)也可以在具有该自动工具的计算机中被执行。

[0171] 在第2工序(S20)中,根据第1工序(S10)中获取的2个匹配阻抗的史密斯圆图上的位置关系,制造弹性波滤波器10。在本工序中,例如计算机判定2个匹配阻抗的位置关系,使用判定结果,CAD(Computer-Aided Design)装置等决定弹性波滤波器10的构成以及设计参数。并且,通过根据决定的构成以及设计参数来制作谐振器等,由此制造弹性波滤波器10。

[0172] 另外,也可以第1工序以及第2工序的至少一部分通过基于设计者的与计算机的对话操作,在该计算机中被执行。

[0173] 此外,在上述第2工序(S20)中,(i)制造弹性波滤波器10以使得在噪声匹配阻抗NF\_min相对于增益匹配阻抗Gain\_max在史密斯圆图上位于左侧并且上侧的区域(上述说明的区域(i))的情况下,纵耦合型的滤波器构造最接近于输出端12而被配置。换句话说,在该情况下,在第2工序中,作为弹性波滤波器10,制造实施例1所涉及的弹性波滤波器10A。

[0174] 此外,在上述第2工序(S20)中,(ii)制造弹性波滤波器10以使得在噪声匹配阻抗NF\_min相对于增益匹配阻抗Gain\_max在史密斯圆图上位于右侧的区域的情况下(上述说明的区域(ii)或者(iii))情况下,在将连结输入端11与输出端12的路径与接地连结的路径上串联连接的并联陷波器(即并联谐振器24)最接近于输出端12而被配置。换句话说,在该情况下,在第2工序中,作为弹性波滤波器10,制造实施例2所涉及的弹性波滤波器10B。

[0175] 此外,在上述第2工序(S20)中,(iii)制造弹性波滤波器10以使得在噪声匹配阻抗NF\_min相对于增益匹配阻抗Gain\_max在史密斯圆图上位于左侧并且下侧的区域的情况下(上述说明的区域(iv))情况下,在连结输入端11与输出端12的路径上串联连接的串联陷波器(即串联谐振器25)最接近于输出端12而被配置。换句话说,在该情况下,在第2工序中,作为弹性波滤波器10,制造实施例3所涉及的弹性波滤波器10C。

[0176] 通过这样的制造工序,制造本实施方式所涉及的弹性波滤波器10。

[0177] [5.效果等]

[0178] 以上,针对本实施方式所涉及的高频模块1,使用实施例1~3所涉及的弹性波滤波器10A~10C来作为弹性波滤波器10进行了说明。以下,对通过这样的高频模块1而起到的效果进行说明。

[0179] 如上述那样,根据本实施方式所涉及的高频模块1,通过弹性波滤波器10的输出阻抗Z(Fout)在通频带的低频端fL以及高频端fH的至少一方的频率靠近噪声匹配阻抗NF\_min,从而在该至少一方的频率,能够减少低噪声放大器40的噪声指数。由此,针对高频模块1整体,由于能够减少噪声指数的劣化容易产生的通频带端的噪声指数的劣化,因此能够提高传输特性。也就是说,能够提供一种传输特性优良的高频模块1。

[0180] 特别地,根据本实施方式所涉及的高频模块1,例如在实施例2中,通过弹性波滤波器10的输出阻抗Z(Fout)在通频带的低频端fL以及高频端fH的任意频率都靠近噪声匹配阻抗NF\_min,从而在该低频端fL以及高频端fH的双方的频率,能够减少低噪声放大器40的噪声指数。由此,针对高频模块1整体,由于能够减少噪声指数的劣化容易产生的通频带端的双方的噪声指数的劣化,因此能够进一步提高传输特性。

[0181] 此外,根据本实施方式所涉及的高频模块1,通过弹性波滤波器10具有纵耦合型的滤波器构造(即纵耦合谐振器23),从而通过调整电极参数等,能够容易地变更弹性波滤波器10的输出阻抗Z(Fout)。因此,相应于根据低噪声放大器40的设计等而规定的噪声匹配阻抗NF\_min以及增益匹配阻抗Gain\_max,能够构成具有适当的输出阻抗Z(Fout)的弹性波滤

波器10。因此,例如,针对弹性波滤波器10的输出阻抗Z (Fout),在通频带中央部能够与增益匹配阻抗Gain\_max一致,并且在通频带的低频端fL以及高频端fH的至少一方的频率能够与噪声匹配阻抗NF\_min一致。因此,能够兼顾增益特性以及噪声特性。

[0182] 此外,根据本实施方式所涉及的高频模块1,例如在实施例1中,与在纵耦合型的滤波器构造与输出端之间连接其他谐振器的情况相比,变得容易使弹性波滤波器10的输出阻抗Z (Fout) 在通频带的低频端fL以及高频端fH的双方在史密斯圆图上位于增益匹配阻抗Gain\_max的左侧并且上侧的区域。因此,在低频端fL以及高频端fH的双方的频率,能够减少低噪声放大器40的噪声指数。

[0183] 此外,根据本实施方式所涉及的高频模块1,例如在实施例2中,通过具有最接近于输出端而被配置的并联陷波器(即并联谐振器24),与不具有该并联陷波器的情况相比,变得容易使弹性波滤波器10的输出阻抗Z (Fout) 在通频带的低频端fL以及高频端fH的双方在史密斯圆图上位于增益匹配阻抗Gain\_max的右侧的区域。因此,在低频端fL以及高频端fH的双方的频率,能够减少低噪声放大器40的噪声指数。

[0184] 具体而言,例如在实施例2中,并联陷波器具有频率比通频带的低频端fL低的谐振点。通过具有这样的谐振点的并联陷波器,针对弹性波滤波器10的输出阻抗Z (Fout),在通频带中央部能够使其与增益匹配阻抗Gain\_max一致,在通频带的低频端fL以及高频端fH的至少一方的频率能够使其与噪声匹配阻抗NF\_min一致。

[0185] 使用实施例2的比较例(比较例1)来对此进行说明。

[0186] 图8A以及图8B是为了对实施例2的效果进行说明,将不具有并联陷波器的弹性波滤波器(图中的“无并联陷波器”)、以及具有其中存在频率比通频带的低频端fL高或者相等的谐振点的并联陷波器的弹性波滤波器(图中的“比较例1”)进行比较来表示的图。具体而言,图8A是表示这2个弹性波滤波器各自的输出阻抗的史密斯圆图,图8B是表示这2个弹性波滤波器各自的通过特性的图。

[0187] 如图8A所示,比较例1所涉及的弹性波滤波器的输出阻抗与不具有并联陷波器的弹性波滤波器的输出阻抗相比,形成于通频带的卷绕不旋转,卷绕的位置移动。换句话说,比较例1所涉及的弹性波滤波器的输出阻抗不仅通频带端与噪声匹配阻抗NF\_min不一致,而且通频带中央部从增益匹配阻抗Gain\_max偏离。

[0188] 因此,如图8B所示,比较例1所涉及的弹性波滤波器与不具有并联陷波器的弹性波滤波器相比,通频带内的损耗劣化(增大)。

[0189] 与此相对地,在实施例2中,并联陷波器具有频率比通频带的低频端fL低的谐振点。因此,能够兼顾增益特性以及噪声特性。

[0190] 另外,在上述实施例2中,以从通频带的低频端fL到高频端fH形成的卷绕的朝向为区域(ii)侧的情况为例进行了说明。但是,该卷绕通过调整并联陷波器的容量成分,也能够朝向区域(ii)以及区域(iii)的任意区域。并联陷波器的容量成分例如能够根据构成并联陷波器的IDT电极101a以及101b的设计参数(交叉宽度、对数、间距、膜厚等)来调整。

[0191] 此外,根据本实施方式所涉及的高频模块1,例如在实施例3中,通过具有最接近于输出端而被配置的串联陷波器(即串联谐振器25),与不具有该串联陷波器的情况相比,变得容易使弹性波滤波器10的输出阻抗Z (Fout) 在通频带的低频端fL以及高频端fH的双方在史密斯圆图上位于增益匹配阻抗Gain\_max的左侧并且下侧的区域。因此,在低频端fL以及

高频端fH的双方的频率,能够减少低噪声放大器40的噪声指数。

[0192] 具体而言,例如在实施例3中,具有频率比通频带的高频端fH高的反谐振点。通过具有这样的反谐振点的串联陷波器,针对弹性波滤波器10的输出阻抗Z(Fout),在通频带中央部能够使其与增益匹配阻抗Gain\_max一致,在通频带的低频端fL以及高频端fH的至少一方的频率能够使其与噪声匹配阻抗NF\_min一致。

[0193] 使用实施例3的比较例(比较例2)来对此进行说明。

[0194] 图9A以及图9B是为了对实施例3的效果进行说明,将不具有串联陷波器的弹性波滤波器(图中的“无串联陷波器”)、以及具有其中存在频率比通频带的高频端fH低或者相等的反谐振点的串联陷波器的弹性波滤波器(图中的“比较例2”)进行比较来表示的图。具体而言,图9A是表示这2个弹性波滤波器各自的输出阻抗的史密斯圆图,图9B是表示这2个弹性波滤波器各自的通过特性的图。

[0195] 如图9A所示,比较例2所涉及的弹性波滤波器的输出阻抗与不具有串联陷波器的弹性波滤波器的输出阻抗相比,虽然形成于通频带的卷绕旋转,但卷绕的位置移动。换句话说,比较例2所涉及的弹性波滤波器的输出阻抗的通频带中央部从增益匹配阻抗Gain\_max偏离。

[0196] 因此,如图9B所示,比较例2所涉及的弹性波滤波器与不具有串联陷波器的弹性波滤波器相比,通频带内的损耗劣化(增大)。

[0197] 与此相对地,在实施例3中,串联陷波器具有频率比通频带的高频端fH高的反谐振点。因此,能够兼顾增益特性以及噪声特性。

[0198] 另外,在上述实施例3中,以从通频带的低频端fL到高频端fH形成的卷绕的朝向为区域(iv)侧的情况为例进行了说明。但是,该卷绕也能够通过调整串联陷波器的容量成分,朝向区域(i)。因此,在噪声匹配阻抗NF\_min相对于增益匹配阻抗Gain\_max位于区域(i)的情况下,也可以设置串联陷波器。串联陷波器的容量成分例如能够根据构成串联陷波器的IDT电极101a以及101b的设计参数(交叉宽度、对数、间距、膜厚等)来进行调整。

[0199] 此外,根据本实施方式所涉及的高频模块1,在史密斯圆图上,通频带的输出阻抗Z(Fout)的轨迹与连结噪声匹配阻抗NF\_min与增益匹配阻抗Gain\_max的线交叉。因此,能够减少通频带端的噪声指数的劣化,并且兼顾增益特性以及噪声特性。

[0200] 此外,本实施方式所涉及的弹性波滤波器10的制造方法包含:获取2个匹配阻抗(增益匹配阻抗Gain\_max以及噪声匹配阻抗NF\_min)的工序(S10);和依存于获取到的2个匹配阻抗的史密斯圆图上的位置关系来制造弹性波滤波器10的工序(S20)。由此,能够制造在通频带的低频端fL以及高频端fH的至少一方的频率,能够减少低噪声放大器40的噪声指数的弹性波滤波器10。因此,在将这样制造的弹性波滤波器10应用于具备对从该弹性波滤波器10输出的高频信号进行放大的低噪声放大器40的例如高频模块1的情况下,能够实现该高频模块1的传输特性的提高。

[0201] 此外,根据本实施方式所涉及的弹性波滤波器10的制造方法,分别在以下3个情况下,容易使弹性波滤波器10的输出阻抗Z(Fout)在通频带的低频端fL以及高频端fH的双方在史密斯圆图上位置靠近增益匹配阻抗Gain\_max。换句话说,无论在2个匹配阻抗(增益匹配阻抗Gain\_max以及噪声匹配阻抗NF\_min)的史密斯圆图上的位置关系如何的情况下,都能够起到这样的效果。因此,能够制造在低频端fL以及高频端fH的双方的频率,能够减少低

噪声放大器40的噪声指数的弹性波滤波器10。所谓3个情况,是指以下3种情况:噪声匹配阻抗NF\_min相对于增益匹配阻抗Gain\_max在史密斯圆图上位于左侧并且上侧的区域(本实施方式的区域(i))的情况、噪声匹配阻抗NF\_min相对于增益匹配阻抗Gain\_max在史密斯圆图上位于右侧的区域的情况(本实施方式的区域(ii)或者(iii))、以及噪声匹配阻抗NF\_min相对于增益匹配阻抗Gain\_max在史密斯圆图上位于左侧并且下侧的区域(本实施方式的区域(iv))的情况。

[0202] (变形例)

[0203] 以上,使用实施例1~3,基于实施方式来对本发明所涉及的高频模块以及弹性波滤波器的制造方法进行了说明,本发明并不限于上述实施方式。针对上述实施方式,在不脱离本发明的主旨的范围内实施本领域技术人员想到的各种变形而得到的变形例、内置有本发明所涉及的高频模块的通信装置等各种设备也包含于本发明。

[0204] 例如,在上述说明中,弹性波滤波器10具有纵耦合型的滤波器构造(即,实施例1~3中的纵耦合谐振器23)。但是,弹性波滤波器10的构成并不局限于此,例如也可以仅具有梯子型的滤波器构造。

[0205] 此外,在上述说明中,并联陷波器(即,实施例2中的并联谐振器24)具有频率比通频带的低频端fL低的谐振点。但是,该谐振点的频率也可以为通频带的低频端fL以上。但是,在具有这种构成的弹性波滤波器10中,在史密斯圆图上,通过通频带的输出阻抗Z(Fout)来形成的卷绕难以旋转,并且通频带中央部的输出阻抗Z(Fout)容易从增益匹配阻抗Gain\_max偏离。因此,由于存在增益特性以及噪声特性的均劣化的情况,因此,例如,优选适当地调整弹性波滤波器10的设计参数(电极指膜厚或者占空比等)以使得满足对高频模块1要求的特性等的规格。

[0206] 此外,在上述说明中,串联陷波器(即,实施例3中的串联谐振器25)具有频率比通频带的高频端fH高的反谐振点。但是,该反谐振点的频率也可以为通频带的高频端fH以下。但是,在具有这样的构成的弹性波滤波器10中,在史密斯圆图上,通过通频带的输出阻抗Z(Fout)来形成的卷绕进行旋转,但通频带中央部的输出阻抗Z(Fout)容易从增益匹配阻抗Gain\_max偏离。因此,由于存在增益特性及劣化的情况,因此,例如,优选适当地调整弹性波滤波器10的设计参数,以使得满足对高频模块1要求的特性等规格。

[0207] 此外,在上述说明中,在史密斯圆图上,通频带的输出阻抗Z(Fout)的轨迹与连结2个匹配阻抗(噪声匹配阻抗NF\_min以及增益匹配阻抗Gain\_max)的线交叉。但是,该轨迹也可以不与连结2个匹配阻抗的线交叉。但是,为了减少增益特性的劣化,优选在史密斯圆图上,通频带中央部的输出阻抗Z(Fout)位于Gain最大区域。

[0208] -产业上的可利用性-

[0209] 本发明能够利用于使用了与低噪声放大器连接的弹性波滤波器的高频模块、双工器、多工器、接收装置等。

图1

图2

图3A

图3B

图3C

图4A

图4B

图4C

图5A

图5B

图5C

图6A

图6B

图6C

图7

图8A

图8B

图9A

图9B