#### (12) INTERNATIONAL APPLICATION PUBLISHED UNDER THE PATENT COOPERATION TREATY (PCT)

## (19) World Intellectual Property Organization

International Bureau

#### (43) International Publication Date 15 December 2011 (15.12.2011)

# (10) International Publication Number WO 2011/156404 A2

- (21) International Application Number:

PCT/US2011/039491

(22) International Filing Date:

7 June 2011 (07.06.2011)

(25) Filing Language:

English

(26) Publication Language:

English

(30) Priority Data:

| 61/352,379 | 7 June 2010 (07.06.2010) | US |

|------------|--------------------------|----|

| 61/352,381 | 7 June 2010 (07.06.2010) | US |

| 61/352,357 | 7 June 2010 (07.06.2010) | US |

| 61/352,362 | 7 June 2010 (07.06.2010) | US |

| 13/154,436 | 6 June 2011 (06.06.2011) | US |

|            |                          |    |

- (72) Inventors; and

- (71) Applicants: SULLIVAN, Jason, A. [US/US]; 299

South Main Street, Suite 1300, Salt Lake City, Utah

84111 (US). ABDOUCH, Charles [US/US]; 299 South

Main Street, Suite 1300, Salt Lake City, Utah 84111 (US).

- (74) Agent: TINGEY, David, B.; Kirton & McConkie, 60 East South Temple, Suite 1800, Salt Lake City, UT 84111 (US).

- (81) Designated States (unless otherwise indicated, for every kind of national protection available): AE, AG, AL, AM, AO, AT, AU, AZ, BA, BB, BG, BH, BR, BW, BY, BZ, CA, CH, CL, CN, CO, CR, CU, CZ, DE, DK, DM, DO, DZ, EC, EE, EG, ES, FI, GB, GD, GE, GH, GM, GT, HN, HR, HU, ID, IL, IN, IS, JP, KE, KG, KM, KN, KP, KR, KZ, LA, LC, LK, LR, LS, LT, LU, LY, MA, MD, ME, MG, MK, MN, MW, MX, MY, MZ, NA, NG, NI, NO, NZ, OM, PE, PG, PH, PL, PT, RO, RS, RU, SC, SD, SE, SG, SK, SL, SM, ST, SV, SY, TH, TJ, TM, TN, TR, TT, TZ, UA, UG, US, UZ, VC, VN, ZA, ZM, ZW.

- (84) Designated States (unless otherwise indicated, for every kind of regional protection available): ARIPO (BW, GH, GM, KE, LR, LS, MW, MZ, NA, SD, SL, SZ, TZ, UG, ZM, ZW), Eurasian (AM, AZ, BY, KG, KZ, MD, RU, TJ, TM), European (AL, AT, BE, BG, CH, CY, CZ, DE, DK, EE, ES, FI, FR, GB, GR, HR, HU, IE, IS, IT, LT, LU,

[Continued on next page]

# (54) Title: SYSTEMS AND METHODS FOR INTELLIGENT AND FLEXIBLE MANAGEMENT AND MONITORING OF COMPUTER SYSTEMS

(57) Abstract: Systems and methods for intelligent and flexible management and monitoring of computer systems are provided using platform management controllers (PMCs) located on circuit boards of a computer system. The PMCs provide for enhanced circuit board certification and security, enhanced systems monitoring and reporting, and enhanced systems control. The PMCs also allow for emulation of processor-based devices and are lowpower, low-cost and very fast when compared to the devices replaced and functionality provided. A power supply tracking apparatus helps to ensure that a first power input to an operational circuit maintains a predefined relationship to a second power input to the operational circuit. Systems and methods for receiving computer systems diagnostics information and for customizably displaying such information from a diagnostics monitoring device are incorporated into a computer system. The monitored computer system information is transmitted to a diagnostics device, such as by infrared or by a novel temporary wired connection.

LV, MC, MK, MT, NL, NO, PL, PT, RO, RS, SE, SI, SK, SM, TR), OAPI (BF, BJ, CF, CG, CI, CM, GA, GN, GQ, GW, ML, MR, NE, SN, TD, TG).

Published:

- without upon a

without international search report and to be republished upon receipt of that report (Rule 48.2(g))

WO 2011/156404 PCT/US2011/039491

### SYSTEMS AND METHODS FOR INTELLIGENT AND FLEXIBLE MANAGEMENT AND MONITORING OF COMPUTER SYSTEMS

1

#### CROSS-REFERENCE TO RELATED APPLICATIONS

This application claims the benefit of U.S. Patent Application No. 13/154,436, filed June 6, 2011 and titled "SYSTEMS AND METHODS FOR INTELLIGENT AND FLEXIBLE MANAGEMENT OF AND MONITORING OF COMPUTER SYSTEMS", and claims the benefit of U.S. Provisional Application No. 61/352,362, filed June 7, 2010 and titled "Systems and Methods for Intelligent and Flexible Management and Monitoring of Computer Systems," U.S. Provisional Application No. 61/352,357, filed June 7, 2010 and titled "Tracking Apparatus," U.S. Provisional Application No. 61/352,381, filed June 7, 2010 and titled "Systems and Methods for Wirelessly Receiving Computer System Diagnostics Information," and U.S. Provisional Application No. 61/352,379, filed June 7, 2010 and titled "Systems and Methods for Providing Connectivity," and hereby incorporates by reference each of the foregoing provisional applications by reference in their entireties for all they disclose. Additionally, this application incorporates by reference in their entireties for all they disclose each of the further applications and patents incorporated by reference in the referenced provisional applications.

#### **BACKGROUND OF THE INVENTION**

#### 1. **Field of the Invention**

5

10

15

20

25

30

The present invention relates to systems and methods for intelligent and flexible management and monitoring of computer systems, and more particularly to systems and methods that flexibly monitor and manage computer system operation and transmit and receive information regarding computer system operation for external use.

#### 2. **Background and Related Art**

Computer systems have grown increasingly complex with a variety of results of this increasing complexity. One result of the increasing complexity is that it has become more difficult to diagnose problems in the computer systems as they arise. It has also become more difficult to correctly manage the computer systems in ways that prevent problems with one portion of the computer system from leading to damage or problems with other portions of the computer system.

Problems with computer systems, including problems that may require diagnosis, may arise at any time during their lifetime, and the likelihood of problems has only increased with the

10

15

20

25

30

complexity of the computer systems. A variety of problems may initially arise at the time of manufacture. Such problems should be properly detected at the time of manufacture, or the manufacturer may risk customer unhappiness and even customer loss. Other problems arise later, during use of the computer systems, and may reduce or completely impair functionality of the computer systems. Current methods for detecting and addressing problems with computer systems both at the time of manufacture and during use of the computer systems are inadequate.

Another difficulty caused by the evolution and complexity of computer systems is a result of obsolescence of certain aspects of computer technology. As certain aspects of the computer technology become obsolete, it becomes difficult to determine how best to deal with older aspects of the computer technology. Because of the complexity of the computer systems, it can be difficult to even remove obsolete technology from the computer systems without causing significant unintended problems to the computer system. Therefore, obsolete and unused technologies remain in computer systems and the operating systems thereof simply because the work involved in safely removing the technologies is not deemed justified. Sadly, results of the failure to adequately address obsolete technology include slower-operating computer systems and systems that are unnecessarily more costly.

The difficulties discussed above may be further exacerbated in embedded systems that may be located in locations distant from traditional resources for diagnosing and addressing computer problems. As the need for embedded systems increases, the need for mechanisms to address such problems will only increase. Accordingly, it would be an improvement in the art to augment or even replace current techniques with other techniques.

Electronics systems, and in particular computer systems, have become ubiquitous. In order to function, electronics systems require input power. Electronic systems often include a power supply, which converts raw input power (e.g., alternating current supplied from commercial mains) into necessary internal supply voltages (e.g., direct current voltages such as 5 volts, 3.3. volts, etc.) within the system.

Power consumption within electronic systems has become a consideration, as increased power consumption leads to increased heat and operating expense. Accordingly, there have been efforts to reduce power consumption in many electronics systems. One technique for reducing power consumption is to use lower voltages. For example, the use of 5 volt supplies for digital logic systems was the standard for many years. Trends have been to use lower voltages, such as

10

15

20

25

30

3.3 volts, 2.5, volts, and even 1.8 volts. The use of lower voltages, in addition to reducing power consumption, has also provided additional benefits.

In some cases, electronic circuitry (e.g., in an integrated circuit) requires multiple voltages to operate properly. For example, some integrated circuits use relatively low voltages (e.g., 1.8 volts) to power internal circuitry, while input/output circuitry operates at a higher voltage (e.g., 3.3 volts). Some integrated circuits can use a combination of two or more different voltages.

Unfortunately, integrated circuits which require multiple voltages often place a number of rules or constraints on the relative values of the voltages. Such constraints can apply during the power up or power down sequencing. Unfortunately, power supplies tend to ramp up over a finite period of time, and thus it can be difficult to ensure that such constraints are maintained during power up or power down. Violation of power constraints can result in incorrect operation (e.g., due to latch-up) or even failure of integrated circuits (e.g., due to over current through improperly forward-biased junctions).

As a specific example, consider a device which operates using both 3.3 volts and 1.8 volts and requires (1) that the 3.3 volt power input must always be higher than the 1.8 volt power input, and (2) that the 3.3 volt power input can never be more than 2.1 volts higher than the 1.8 volt power input. If the 3.3 volt power input ramps up too slowly, it can lag behind the 1.8 volt power input and violate the first requirement. Conversely, if the 3.3 volt power input ramps up too quickly, it can get too far ahead of the 1.8 volt power input and violate the second requirement.

Maintaining required constraints can be even more difficult when a failure occurs. For example, in a system which has multiple power supplies generating multiple voltages, failure of one supply can result in simultaneous or serial violation of several constraints.

Some integrated circuit manufacturers have provided so-called "reference" designs that control sequencing of power supplies to ensure some of the constraints are met. Some reference designs, however, fail to ensure that the constraints are met in all possible operating scenarios. Moreover, most reference designs are not optimized for manufacturing environments. Typically, the reference designs include a large number of components, require a large amount of board area, and are relatively complex to debug. Moreover, in some instances, the reference designs

WO 2011/156404 PCT/US2011/039491

5

10

15

20

25

30

4

require that additional integrated circuits be purchased from the same integrated circuit manufacturer.

It has been the inventors' experience that the most common type of failure in electronic computer systems is failure in the power supplies. In an electronics system (e.g., a computer system) which requires multiple power supplies, failure of one supply can result in violation of power constraints for some integrated circuits within the system. This can cause failures of integrated circuits, and even cause a cascade of failures. Accordingly, it would be an improvement in the art to augment or even replace current techniques with other techniques.

Printed circuit boards (PCB) are a key component of the foundation upon which many computer logic systems, as well as other electrical devices, are built. During the manufacturing process, PCBs may be programmed, debugged or otherwise communicated with to transmit or receive data. To facilitate a constant connection between the PCB and associated devices during this process, PCBs often have a tab which can later be snapped off or otherwise removed such that the PCB can be conveniently installed in a larger computer or electrical system. Prior to removal, however, the tab is used to facilitate a semi-permanent connection between the PCB and associated external manufacturing devices to facilitate programming and debugging. Alternatively, the PCB may be programmed, debugged or otherwise communicated with via complex automated devices, which electrically contact numerous locations on the PCB simultaneously. In production, programming connectors are typically not included on the PCB to reduce the cost of the PCB and since many end-users do not program the PCB further in the field.

Following the initial manufacturing process, however, it is sometimes desirable to temporarily connect to a PCB in order to communicate with the PCB for any number of purposes or reasons. For example, it may be desirable to communicate with the PCB to upload additional or alternative programming, to further debug the PCB, to diagnose and/or repair the PCB or to otherwise communicate with the PCB to transmit or receive data associated with the PCB. However, following removal of the tab as discussed above and in the absence of sophisticated automation it is difficult to temporarily connect with and thereby communicate with the PCB directly. As result, various ports or other electronic connectors are often soldered onto the PCB such that external devices can conveniently connect to the PCB via appropriate wires and corresponding connectors at the PCB's ports or electrical connectors. For example, a PCB port

10

15

20

25

30

or connector may be a standard electrical "male" component and a device intended to connect to the PCB may be outfitted with a wire having a corresponding standard "female" component or collar thereon (or vice-versa). As the "female" collar mates with the "male" component the PCB may be effectively contacted and communicated with.

While outfitting a PCB with various ports and connectors works to facilitate temporary communication between the PCB and other external devices, the ports or connectors, which are soldered to the PCB, are generally left behind after the desired connection is completed. This results in increased costs. This cost is exacerbated by the fact that multiple ports or connectors are often required to facilitate connections for variable purposes – often resulting in multiple ports/connectors being left behind. Further, in the increasingly small computing and electrical devices common to modern technology, it is often undesirable to have bulky or space-consuming ports/connectors retained on a given PCB once installed in an associated device. However, removal of the ports/connectors can result in damage to the PCB and likewise diminishes the convenience with which the PCB can subsequently be connected to in the field for further programming, debugging and the like if necessary or desirable at a later time.

Assuming the PCB's ports/connectors are left intact, there are additional drawbacks. In complex or sophisticated PCBs it can often be onerous and difficult to locate and/or mate with the appropriate port or connector to accomplish a particular purpose. Further, if an end user desires to connect to the PCB, the associated wiring and corresponding connector necessarily result in additional costs to the user. Such costs can be substantial. Further, if the user damages either the PCB port/connector or the corresponding wiring or connector in attempting to mate them, this can result in additional costs. Ultimately, under current techniques the costs associated with connecting to a PCB after the manufacturing process is complete include, at a minimum, two connectors: one on the PCB and the other on the wiring. If the user makes any mistakes, the costs simply escalate.

### **SUMMARY OF THE INVENTION**

Implementation of the invention provides systems and methods for intelligent and flexible management and monitoring of a variety of aspects of computer systems and computer system operation. Implementations of the invention are applicable to a wide variety of existing and future computer systems, including a wide variety of general-purpose computer systems and a wide variety of special-purpose computer systems. One class or configuration of computer

10

15

20

25

30

system in which the invention may be implemented in a variety of ways is disclosed in U.S. Patent No. 7,256,991 titled Non-Peripherals Processing Control Module Having Improved Heat Dissipating Properties, U.S. Patent No. 7,242,574 titled Robust Customizable Computer Processing System, and U.S. Patent No. 7,075,784 titled Systems and Methods for Providing a Dynamically Modular Processing Unit, and all U.S. applications related thereto, which are expressly incorporated herein by reference for all they disclose.

In a computer system configured to have and use a plurality of interconnected circuit boards, certain implementations of the invention provide a system for ensuring that only certified circuit boards are used in the computer system. The system includes a certification chip located on each of the circuit boards. Each certification chip includes 1) key functionality necessary for the computer to function and for the circuit board on which the certification chip is located to function and 2) certification functionality communicating that the circuit board has been tested and certified to function properly in the computer system. The system also includes a certification communications bus allowing each of the certification chips to communicate with each other to verify a certified status of each circuit board incorporated into the system. In at least some such systems, each certification chip is configured to prevent the computer system from functioning if a circuit board lacking the certification chip is attached to the computer system.

In certain implementations, each certification chip is configured to monitor conditions on its respective circuit board. The certification chips may keep a record of monitored conditions on the circuit boards, and each certification chip may be configured to transmit reports of conditions on its respective circuit board.

In some implementations, wherein each certification chip is configured to intelligently participate in power control for the computer system, the certification chips collaboratively participate in timing of turning on and off a plurality of power supplies for the computer system. In some such implementations, the certification chips jointly prevent the existence of power conditions in the computer system that are known to risk destruction of chips of the computer system by sequentially turning power supplies of the computer on in a chip-safe order and only after verifying that all power supplies previous in a sequential order have properly turned on. Additionally or alternatively, the certification chips jointly prevent the existence of power conditions in the computer system that are known to risk destruction of chips of the computer

10

15

20

25

30

system by quickly turning off power supplies that may cause damage to chips if left on upon detection of a power supply failure in the computer system.

In at least some implementations, the certification chips comprise logic gates configured to monitor power control and control activation and deactivation of the power supplies, whereby upon failure of a power supply deactivation of other power supplies is sufficiently fast to prevent damage to the computer system. In at least some implementations, deactivation of other power supplies occurs within several to a few clock cycles.

As implemented, the certification chips may operate at any time the computer system is connected to power, even if the computer system is turned off. The certification chips perform sideband management of the computer systems, and may do so using only logic gates.

In certain implementations, failure events are detected and recorded by logic gates within the certification chips, whereupon the certification chips are configured to cooperatively log the failure events and shut down the computer system. The certification chips may be configured to transmit a record of the failure events on one or more of a next power-on attempt, and at the time of failure.

In some implementations, the certification chips are configured to snoop on communications occurring on one or more busses of the computer system when the computer system is running, such as an inter-integrated circuit (I<sup>2</sup>C) bus, and a low pin count (LPC) bus. The certification chips may be configured to respond to snooped communications, such as input/output (I/O) communications and post codes.

In implementations of the invention, one or more of the certification chips is configured to provide real-time processor emulation using logic gates. The one or more certification chips providing real-time processor emulation may automatically and rapidly provide specific selected outputs for selected inputs. In certain instances, the one or more certification chips provide emulation of one of a keyboard controller and a video controller.

In certain implementations, the certification chips are configured so that when power is initially connected to the computer system, the certification chips provide communications to each other to ensure each is active and ready to function before allowing the computer system to be turned on and used.

Certain implementations occur in a computer system, wherein a system for providing integrated sideband management of the computer system is provided using a sideband

10

15

20

25

30

management device that is integrated into the computer system and that provides sideband management of the computer system using only logic gates. The sideband management device may provide power-on management that ensures proper sequencing of activation of power supplies of the computer system on power-up. The sideband management device may ensure that activation of power supplies only occurs in a way that prevents improper, potentially-damaging, voltage combinations from occurring in the computer system. The sideband management device may be configured to interrupt power supply sequencing, turn off the computer system, and log details of a fault condition when one or more power supplies fails to activate.

A sideband management device of certain implementations may include a plurality of devices distributed across multiple circuit boards of the computer system. Regardless, the sideband management device may remain powered when the computer system is turned off. In certain implementations, the computer system is a single computer device and the sideband management device is integrated into at least one circuit board of the computer device, whereby the sideband management device does not include a separate processor or computer device.

Implementation of the invention provides a method for controlling activation of power supplies in a computer system comprising a plurality of power supplies of different voltages necessary for functioning of the computer system. The method includes selectively instructing activation of one or more of the plurality of power supplies and monitoring whether the power supply or supplies instructed to be activated properly turned on. When one or more of the power supplies that was instructed to be activated fails to properly turn on within a set time, the method includes logging a failure event and turning the computer system off.

In some implementations of the method, power supplies are activated in a sequence designed to prevent damage to components of the computer system caused by improper voltage sequences and activation of each power supply is monitored for proper activation before the sequence of activation is continued. In at least some implementations, turning the computer system off includes deactivating any power supplies that are on in an order that prevents damage to components of the computer system caused by improper voltage sequences.

Implementation of the invention provides a power management system for a computer system having a plurality of circuit boards. The power management system includes a power management bus that extends across the circuit boards of the computer system and a plurality of platform management controllers communicatively coupled to the power management bus,

10

15

20

25

30

wherein each platform management controller is located on a different circuit board and is configured to control power supplies on its respective circuit board.

In at least some implementations, each platform management controller is implemented entirely in logic gates. The platform management controllers may be configured to operate at any time the computer system is connected to an input power source, regardless of whether the computer is turned on. The platform management controllers may also be configured to ensure that the other platform management controllers are active before allowing any power supplies of the computer system to be activated. The platform management controllers may determine that the other platform management controllers are active by generating controller-specific keys that are passed to the other controllers and passed on by the other controllers as received when the other controllers are active using the power management bus, whereby when each controller receives its own key back it knows that all controllers are active.

Implementation of the invention provides a system for emulating a processor-based computer component in a computer system while improving speed of the computer system. The system for emulating a processor-based computer component includes a logic-gate-based device configured to emulate a processor-based computer component using only logic gates, wherein the logic gates are configured to receive a set of commands normally handled by the processor-based computer component and to provide output that would normally be output by the processor-based computer component but at a much faster speed. In some implementations, the logic gates are configured to recognize and respond to only a subset of all possible commands that would normally be handled by the processor-based computer component. The logic-gate-based device may provide emulation of a legacy computer device not actively used by the computer system but the presence of which is required for proper operation of one of 1) a basic input/output system (BIOS) of the computer system and 2) an operating system (OS) of the computer system.

Certain implementations of the invention provide a method for encoding, transmitting, and decoding digital communications wherein data portions of a communication inherently include checksum information concerning the validity of received data portions without requiring extra data bits. The method includes encoding information into a digital stream using a scheme wherein certain patterns of digital data are invalid and transmitting the digital stream repeatedly using a transmitter. A receiver receives received information, and the received

10

15

20

25

30

information is evaluated for valid and invalid patterns. The received information is only kept and decoded when a valid start pattern is followed by one or more valid data patterns.

The start pattern may include information regarding the type of data included in the data stream. The start pattern may also include information regarding the number of times the digital stream has been repeated.

Implementation of the invention provides a method for monitoring startup and function of a computer system using a platform management controller integrated into the computer system. The method includes providing a platform management controller in a computer system, wherein the platform management controller is connected to the computer system so as to be able to manage power of the computer system and obtain information from the computer system regarding function of the computer system, and wherein the platform management controller is operatively connected to a transmitter. The method also includes using the platform management controller to monitor startup and operation of the computer system, using the platform management controller to log events related to at least one of the startup and operation of the computer system, and using the platform management controller to transmit logged events using the transmitter.

The logged events may include post codes generated by the computer system on startup. When the logged events include post codes, the platform management controller may transmit the post codes at the time of startup. The logged events may additionally or alternatively include a temperature reading obtained from the computer system at one of a shutdown time and a time of a detected abnormal temperature. In some implementations, an operating system of the computer system is configured to direct messages to the platform management controller for external transmission.

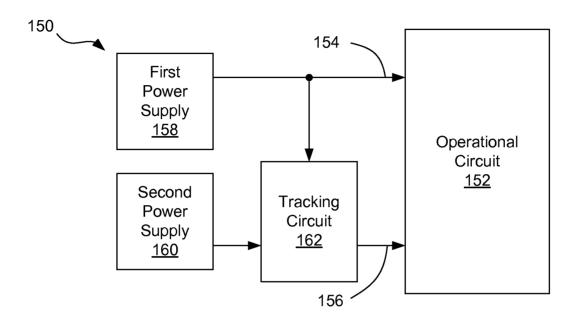

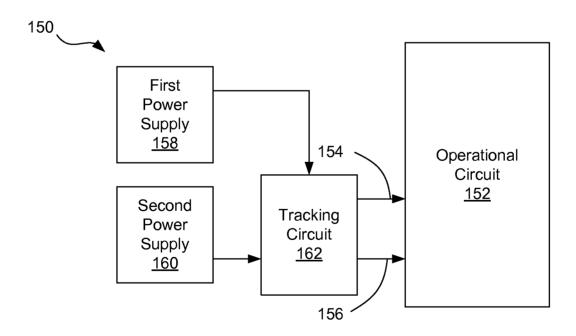

Implementation of the present invention relates to techniques for providing a power supply tracking apparatus. In particular, at least some implementations of the present invention relate to a power supply tracking apparatus for ensuring that a first power input to an operational circuit maintains a predefined relationship to a second power input to the operational circuit.

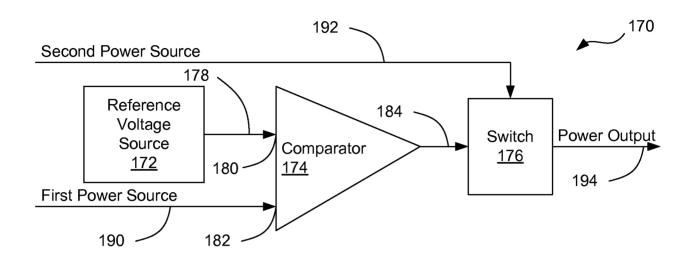

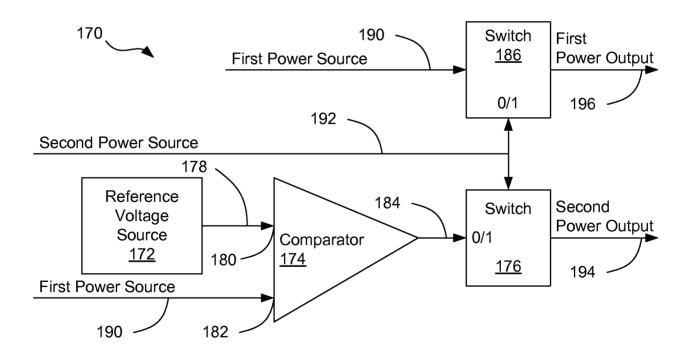

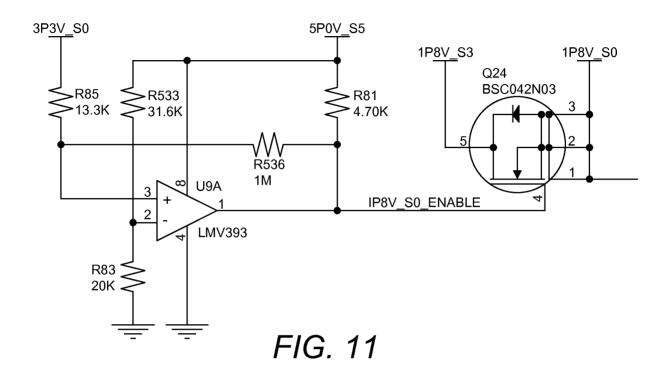

Implementation of the present invention includes a power supply tracking apparatus having a reference voltage source, a comparator, and a switch. The reference voltage source provides a reference voltage to a first input of the comparator. A second input of the comparator is coupled to a first power input. An output of the comparator switches state as a function of the

10

15

20

25

30

relative voltage of the reference voltage and the first power input. The output of the comparator controls a switch, and thus opens and closes the switch according to the relative voltage of the reference voltage and the first power input. The switch is disposed between a power supply and the second power input. Accordingly, the second power input can be maintained in a predefined relationship to the first power input.

While the methods and processes of implementations of the present invention have proven to be particularly useful in the area of personal computing enterprises, those skilled in the art will appreciate that the methods and processes of the present invention can be used in a variety of different applications and in a variety of different areas of manufacture to yield customizable enterprises, including enterprises for any industry utilizing control systems or smart-interface systems and/or enterprises that benefit from the implementation of such devices. Examples of such industries include, but are not limited to, automotive industries, avionic industries, hydraulic control industries, auto/video control industries, telecommunications industries, medical industries, special application industries, and electronic consumer device industries. Accordingly, the systems and methods of the present invention can provide benefits to many different markets, including markets that have traditionally been untapped by current computer techniques.

Implementation of the invention provides systems and methods for wirelessly receiving computer systems diagnostics information and for customizably displaying such information. The information may be received from a wide variety of existing and future computer systems, including a wide variety of general-purpose computer systems and a wide variety of special-purpose computer systems. As disclosed herein, a platform management controller (PMC) or similar device incorporated into a computer system monitors computer system information and transmits or otherwise conveys the monitored information, such as by infrared. Embodiments of the invention receive the transmitted information so it can be used for a variety of purposes such as disclosed herein.

In implementations of the invention, a plurality of logged events transmitted by the PMC or other similar device may be received and monitored by a diagnostics device such as a wireless diagnostics device. In at least some implementations of the invention, the processing features of the diagnostics device are implemented primarily or entirely in logic gates. Such implementation provides certain advantages as will be discussed in detail herein.

10

15

20

25

30

Implementation of the present invention relates to temporary electrical connections. In particular, the present invention relates to systems and methods for temporarily connecting an external device to a printed circuit board (PCB) in order to receive or transmit information from or to the PCB.

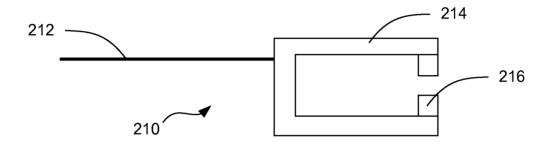

Implementation of the present invention takes place in association with temporary electrical connections between an external source and a PCB to facilitate the transfer of data across the connection. In at least one implementation, a temporary electrical system includes a PCB having electrical contact pads disposed adjacent one or more edges of the PCB. The electrical contact pads in turn are electrically connected to particular locations on the PCB. The systems further includes a temporary electrical connector apparatus which in turn includes an electrical wire ribbon and a head at the distal end of the electrical wire ribbon having one or more electrical contact pads disposed thereon that correspond to the electrical pads disposed on the edge(s) of the PCB.

In a further implementation, an apparatus adapted to temporarily electrically connect with a PCB includes an electrical wire ribbon. The apparatus further includes a head at the distal end of the electrical wire ribbon having one or more electrical contact pads disposed thereon. In some implementations, the head also has an adhesive disposed on it, which substantially surrounds the electrical contact pads. Prior to use, the adhesive is protected by a non-stick paper backing or the like, which can be removed upon use. In another implementation, the head includes a compression fitting that can be manipulated to tension the head such that it temporarily remains fixed to a corresponding surface, such as a PCB. In yet another implementation, the head includes pins or other locators that that can be used to facilitate a temporary connection between the head and a corresponding surface, such as a PCB. In still another implementation, the head is comprised of two opposing jaws connected by an operable spring which biases the jaws in a closed position such that the jaws can be selectively opened by a user and the head temporary "clipped" to a corresponding surface, such as a PCB. In yet another implementation, the head is comprised of two opposing stationary surfaces connectably separated the width of a PCB such that the head can be temporarily slipped over the edge of the PCB to remain temporarily affixed thereto.

While the methods and processes of implementation of the present invention have proven to be particularly useful in the area of temporary PCB connections, those skilled in the art can

10

15

20

25

30

appreciate that the methods and processes can be used in a variety of different applications and in a variety of different areas of manufacture to yield temporary, convenient and inexpensive electrical connections.

#### **BRIEF DESCRIPTION OF THE DRAWINGS**

The objects and features of the present invention will become more fully apparent from the following description and appended claims, taken in conjunction with the accompanying drawings. Understanding that these drawings depict only typical embodiments of the invention and are, therefore, not to be considered limiting of its scope, the invention will be described and explained with additional specificity and detail through the use of the accompanying drawings in which:

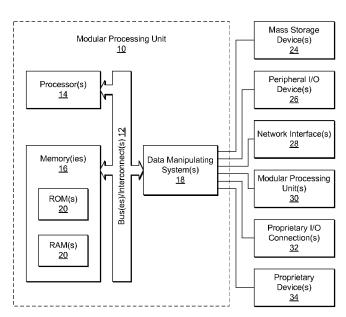

Figure 1 shows a copy of Figure 1 of U.S. Patent No. 7,075,784, in which the original reference numbering has been preserved, by way of illustration of another representative computer system for use with embodiments of the invention;

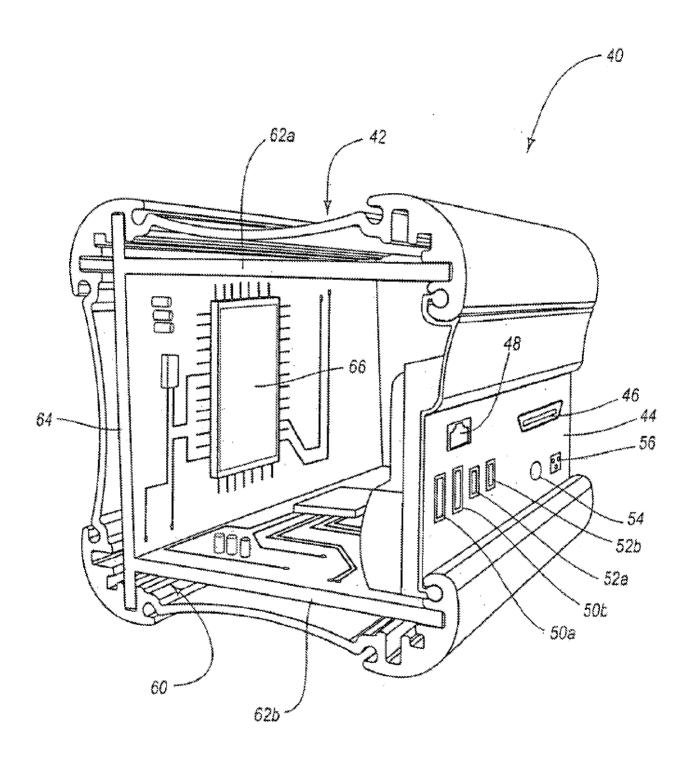

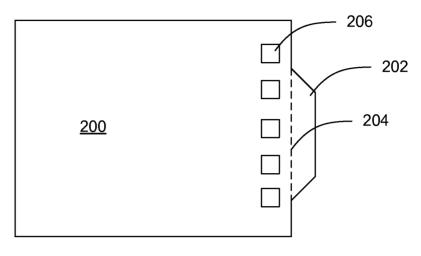

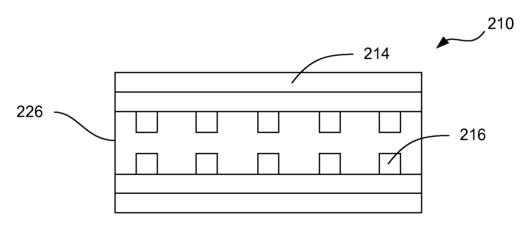

Figure 2 shows a copy of Figure 3 of U.S. Patent No. 7,075,784, in which the original reference number has been preserved, showing a representative circuit board configuration of a representative computer system for use with embodiments of the invention;

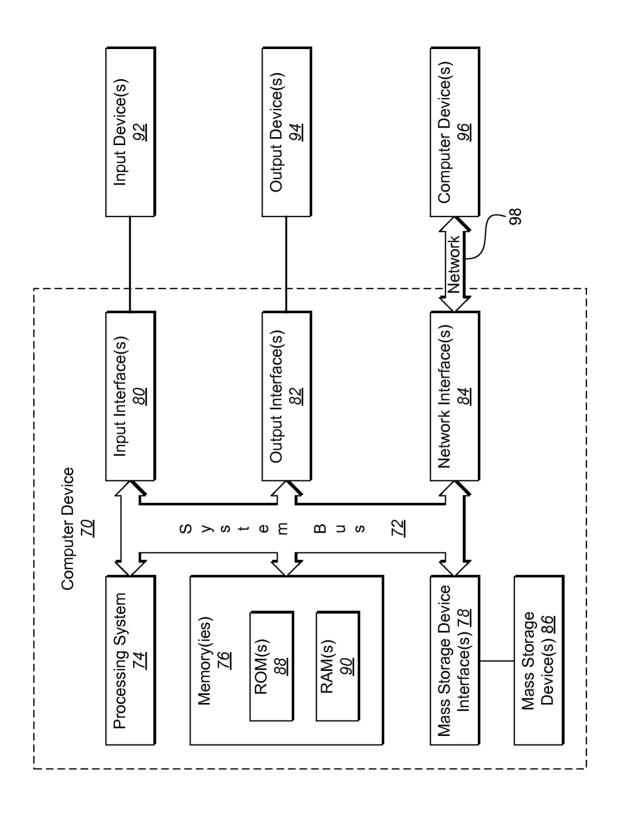

Figure 3 shows a representative computer system for use with embodiments of the invention;

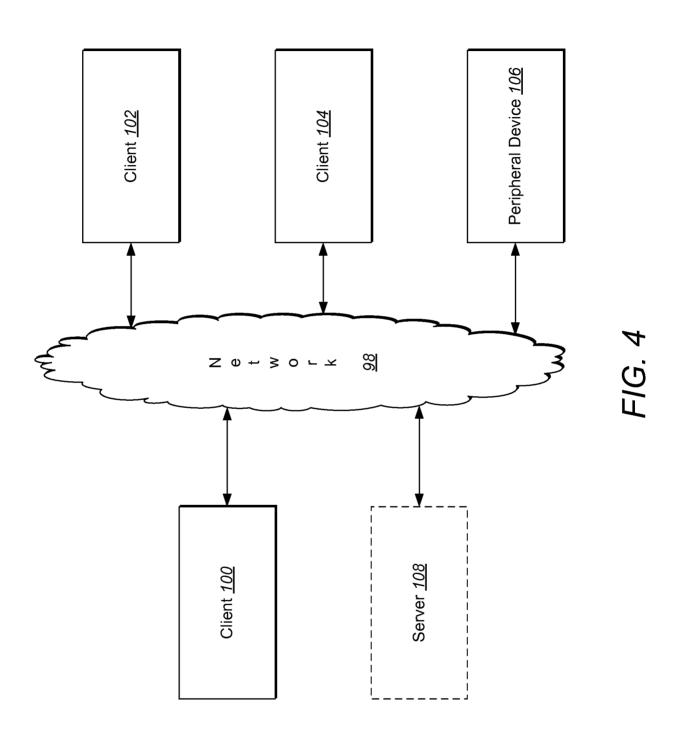

Figure 4 shows a representative networked computer system for use with embodiments of the invention;

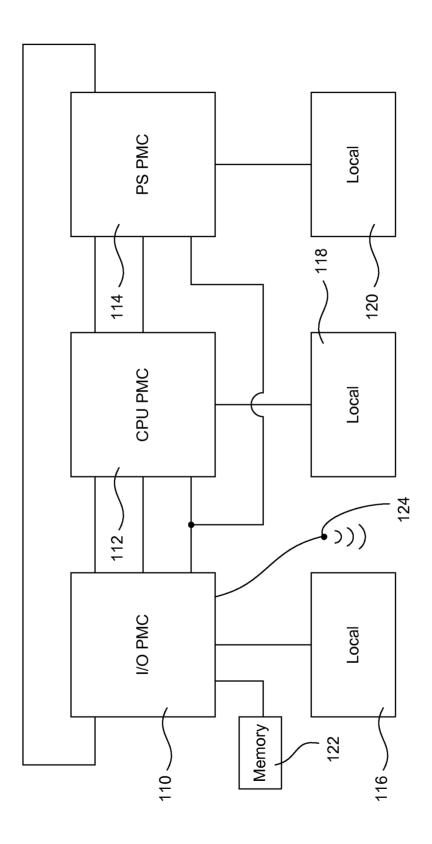

Figure 5 shows a schematic diagram of representative connections between multiple platform management controllers;

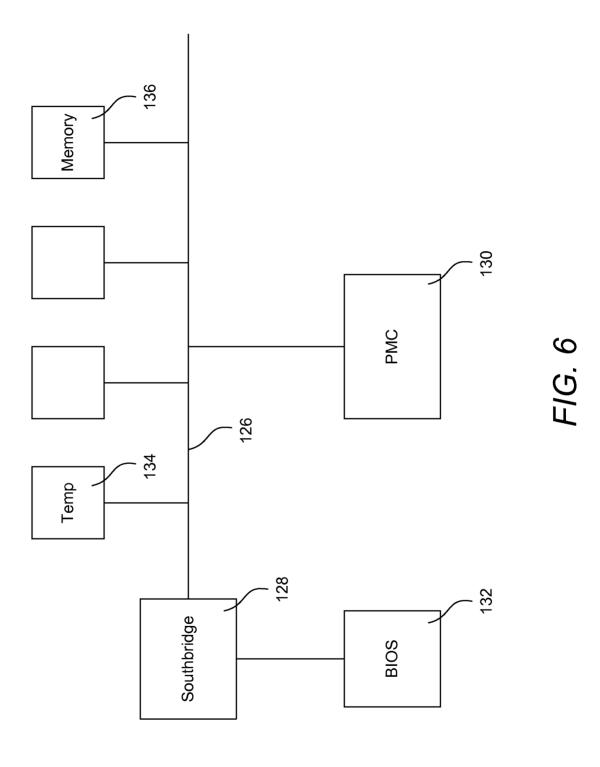

Figure 6 shows a schematic diagram of connections between a representative platform management controller and other devices in a computer system.

Figure 7 illustrates a representative block diagram of an electronic system with a tracking circuit according to some embodiments of the present invention;

Figure 8 illustrates a representative block diagram of an electronic system with a tracking circuit according to some embodiments of the present invention;

Figure 9 illustrates a representative block diagram of a tracking circuit according to some embodiments of the present invention;

10

15

20

25

Figure 10 illustrates a representative block diagram of a tracking circuit according to some embodiments of the present invention;

Figure 11 illustrates a representative schematic diagram of a tracking circuit according to some embodiments of the present invention;

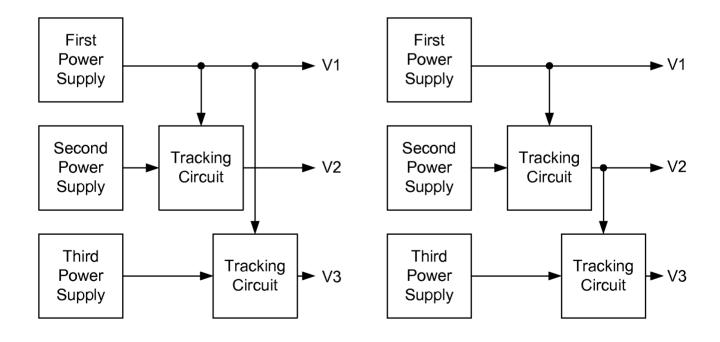

Figure 12 illustrates a representative parallel arrangement of tracking circuits according to some embodiments of the present invention;

Figure 13 illustrates a representative series arrangement of tracking circuits according to some embodiments of the present invention;

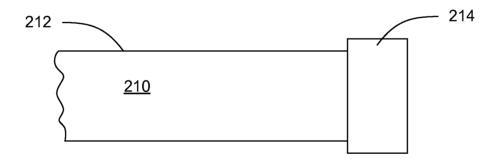

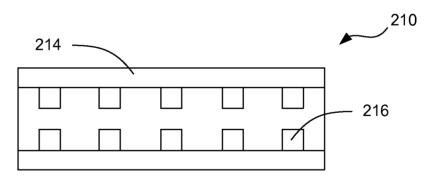

Figure 14 illustrates a plan view of a representative PCB during the production process;

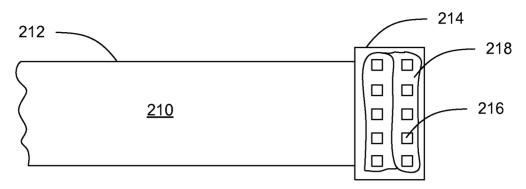

Figure 15 illustrates a plan view of a representative PCB after production;

Figure 16 illustrates a plan view of the top of a representative temporary electrical connection apparatus as contemplated by embodiments of the present invention;

Figure 17 illustrates a plan view of the underside of another representative embodiment of a temporary electrical connection apparatus having adhesive thereon;

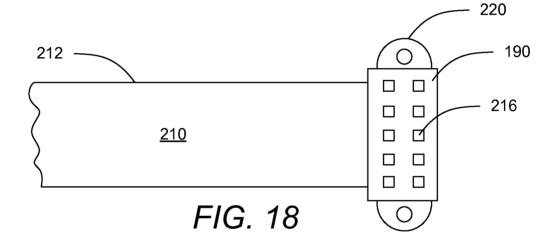

Figure 18 illustrates a plan view of the underside of another representative embodiment of a temporary electrical connection apparatus having locators on both sides of the head;

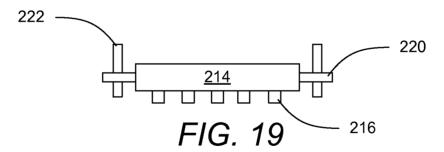

Figure 19 illustrates a front view of a representative embodiment similar to that of Figure 18 having pins in the locators;

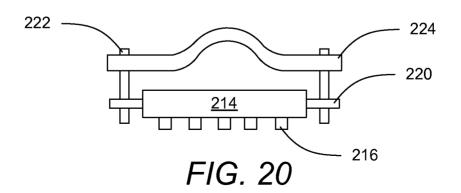

Figure 20 illustrates a front view of a representative embodiment similar to that of Figure 18 having pins in the locators and a compression fitting attached thereto;

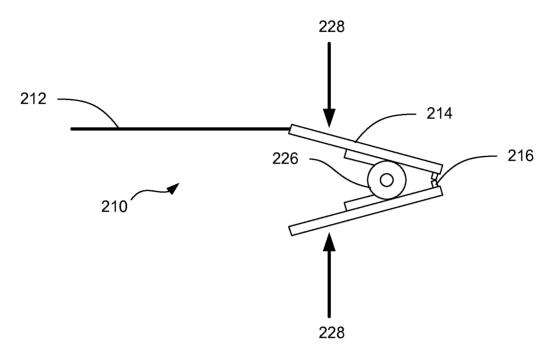

Figure 21 illustrates a side view of a representative embodiment of a temporary electrical connection apparatus having opposing biased jaws;

Figure 22 illustrates a front view of the representative embodiment of Figure 21;

Figure 23 illustrates a side view of another representative embodiment of a temporary electrical connection apparatus head having two opposing stationary surfaces connectively separated the width of a PCB; and

Figure 24 illustrates a front view of the representative embodiment of Figure 23.

### **DETAILED DESCRIPTION OF THE INVENTION**

A description of embodiments of the present invention will now be given with reference to the Figures. It is expected that the present invention may take many other forms and shapes, hence the following disclosure is intended to be illustrative and not limiting, and the scope of the invention should be determined by reference to the appended claims.

5

10

15

20

25

30

Embodiments of the invention provide systems and methods for intelligent and flexible management and monitoring of a variety of aspects of computer systems and computer system operation. Embodiments of the invention are applicable to a wide variety of existing and future computer systems, including a wide variety of general-purpose computer systems and a wide variety of special-purpose computer systems. One class or configuration of computer system in which the invention may be implemented in a variety of ways is disclosed in U.S. Patent Nos. 7,256,991 titled Non-Peripherals Processing Control Module Having Improved Heat Dissipating Properties, 7,242,574 titled Robust Customizable Computer Processing System, and 7,075,784 titled Systems and Methods for Providing a Dynamically Modular Processing Unit, which are expressly incorporated herein by reference for all they disclose.

In a computer system configured to have and use a plurality of interconnected circuit boards such as that disclosed in the above-referenced patents, certain embodiments of the invention provide a system for ensuring that only certified circuit boards are used in the computer system. The system includes a certification chip located on each of the circuit boards. Each certification chip includes 1) key functionality necessary for one of the computer to function and for the circuit board on which the certification chip is located to function and 2) certification functionality communicating that the circuit board has been tested and certified to function properly in the computer system. The system also includes a certification communications bus allowing each of the certification chips to communicate with each other to verify a certified status of each circuit board incorporated into the system. In at least some such systems, each certification chip is configured to prevent the computer system from functioning if a circuit board lacking the certification chip is attached to the computer system.

In certain embodiments, each certification chip is configured to monitor conditions on its respective circuit board. The certification chips may keep a record of monitored conditions on the circuit boards, and each certification chip may be configured to transmit reports of conditions on its respective circuit board.

10

15

20

25

30

In some embodiments, wherein each certification chip is configured to intelligently participate in power control for the computer system, the certification chips collaboratively participate in timing of turning on and off a plurality of power supplies for the computer system. In some such embodiments, the certification chips jointly prevent the existence of power conditions in the computer system that are known to risk destruction of chips of the computer system by sequentially turning power supplies of the computer on in a chip-safe order and only after verifying that all power supplies previous in a sequential order have properly turned on. Additionally or alternatively, the certification chips jointly prevent the existence of power conditions in the computer system that are known to risk destruction of chips of the computer system by quickly turning off power supplies that may cause damage to chips if left on upon detection of a power supply failure in the computer system.

In at least some embodiments, the certification chips comprise logic gates configured to monitor power control and control activation and deactivation of the power supplies, whereby upon failure of a power supply deactivation of other power supplies is sufficiently fast to prevent damage to the computer system. In at least some embodiments, deactivation of other power supplies occurs within several to a few clock cycles.

As implemented, the certification chips may operate at any time the computer system is connected to power, even if the computer system is turned off. The certification chips perform sideband management of the computer systems, and may do so using only logic gates.

In certain embodiments, failure events are detected and recorded by logic gates within the certification chips, whereupon the certification chips are configured to cooperatively log the failure events and shut down the computer system. The certification chips may be configured to transmit a record of the failure events on one or more of a next power-on attempt, and at the time of failure.

In some embodiments, the certification chips are configured to snoop on communications occurring on one or more busses of the computer system when the computer system is running, such as an inter-integrated circuit (I<sup>2</sup>C) bus, and a low pin count (LPC) bus. The certification chips may be configured to respond to snooped communications, such as input/output (I/O) communications and post codes.

In embodiments of the invention, one or more of the certification chips is configured to provide real-time processor emulation using logic gates. The one or more certification chips WO 2011/156404 PCT/US2011/039491

5

10

15

20

25

30

17

providing real-time processor emulation may automatically and rapidly provide specific selected outputs for selected inputs. In certain instances, the one or more certification chips provides emulation of one of a PS/2 keyboard controller and a video controller.

In certain embodiments, the certification chips are configured so that when power is initially connected to the computer system, the certification chips provide communications to each other to ensure each is active and ready to function before allowing the computer system to be turned on and used.

Certain embodiments occur in a computer system, wherein a system for providing integrated sideband management of the computer system is provided using a sideband management device that is integrated into the computer system and that provides sideband management of the computer system using only logic gates. The sideband management device may provide power-on management that ensures proper sequencing of activation of power supplies of the computer system on power-up. The sideband management device may ensure that activation of power supplies only occurs in a way that prevents improper, potentially-damaging, voltage combinations from occurring in the computer system. The sideband management device may be configured to interrupt power supply sequencing, turn off the computer system, and log details of a fault condition when one or more power supplies fails to activate.

A sideband management device of certain embodiments may include a plurality of devices distributed across multiple circuit boards of the computer system. Regardless, the sideband management device may remain powered when the computer system is turned off. In certain embodiments, the computer system is a single computer device and the sideband management device is integrated into at least one circuit board of the computer device, whereby the sideband management device does not include a separate processor or computer device.

Embodiments of the invention provides a method for controlling activation of power supplies in a computer system comprising a plurality of power supplies of different voltages necessary for functioning of the computer system. The method includes selectively instructing activation of one or more of the plurality of power supplies and monitoring whether the power supplies instructed to be activated properly turned on. When one or more of the power supplies that was instructed to be activated fails to properly turn on within a set time, the method includes logging a failure event and turning the computer system off.

4833-9392-0777, v. 1

10

15

20

25

30

In some embodiments of the method, power supplies are activated in a sequence designed to prevent damage to components of the computer system caused by improper voltage sequences and activation of each power supply is monitored for proper activation before the sequence of activation is continued. In at least some embodiments, turning the computer system off includes deactivating any power supplies that are on in an order that prevents damage to components of the computer system caused by improper voltage sequences.

Embodiments of the invention provide a power management system for a computer system having a plurality of circuit boards. The power management system includes a power management bus that extends across the circuit boards of the computer system and a plurality of platform management controllers (PMCs) communicatively coupled to the power management bus, wherein each PMC is located on a different circuit board and is configured to control power supplies on its respective circuit board.

In at least some embodiments, each PMC is implemented entirely in logic gates. The PMCs may be configured to operate at any time the computer system is connected to an input power source, regardless of whether the computer is turned on. The PMCs may also be configured to ensure that the other PMCs are active before allowing any power supplies of the computer system to be activated. The PMCs may determine that the other PMCs are active by generating controller-specific keys that are passed to the other controllers and passed on by the other controllers as received when the other controllers are active using the power management bus, whereby when each controller receives its own key back it knows that all controllers are active.

Embodiments of the invention provide a system for emulating a processor-based computer component in a computer system while improving speed of the computer system. The system for emulating a processor-based computer component includes a logic-gate-based device configured to emulate a processor-based computer component using only logic gates, wherein the logic gates are configured to receive a set of commands normally handled by the processor-based computer component and to provide output that would normally be output by the processor-based computer component but at a much faster speed. In some embodiments, the logic gates are configured to recognize and respond to only a subset of all possible commands that would normally be handled by the processor-based computer component. The logic-gate-based device may provide emulation of a legacy computer device not actively used by the

10

15

20

25

30

computer system but the presence of which is required for proper operation of one of 1) a basic input/output system (BIOS) of the computer system and 2) an operating system (OS) of the computer system.

Certain embodiments of the invention provide a method for encoding, transmitting, and decoding digital communications wherein data portions of a communication inherently include checksum information concerning the validity of received data portions without requiring extra data bits. The method includes encoding information into a digital stream using a scheme wherein certain patterns of digital data are invalid and transmitting the digital stream repeatedly using a transmitter. A receiver receives received information, and the received information is evaluated for valid and invalid patterns. The received information is only kept and decoded when a valid start pattern is followed by one or more valid data patterns.

The start pattern may include information regarding the type of data included in the data stream. The start pattern may also include information regarding the number of times the digital stream has been repeated.

Embodiments of the invention provide a method for monitoring startup and function of a computer system using a PMC integrated into the computer system. The method includes providing a PMC in a computer system, wherein the PMC is connected to the computer system so as to be able to manage power of the computer system and obtain information from the computer system regarding function of the computer system, and wherein the PMC is operatively connected to a transmitter. The method also includes using the PMC to monitor startup and operation of the computer system, using the PMC to log events related to at least one of the startup and operation of the computer system, and using the PMC to transmit logged events using the transmitter.

The logged events may include post codes generated by the computer system on startup. When the logged events include post codes, the PMC may transmit the post codes at the time of startup. The logged events may additionally or alternatively include a temperature reading obtained from the computer system at one of a shutdown time and a time of a detected abnormal temperature. In some embodiments, an operating system of the computer system is configured to direct messages to the PMC for external transmission.

Embodiments of the present invention relate to techniques for providing a power supply tracking apparatus. In particular, at least some embodiments of the present invention relate to a

10

15

20

25

30

power supply tracking apparatus for ensuring that a first power input to an operational circuit maintains a predefined relationship to a second power input to the operational circuit.

Embodiments of the present invention include a power supply tracking apparatus having a reference voltage source, a comparator, and a switch. The reference voltage source provides a reference voltage to a first input of the comparator. A second input of the comparator is coupled to a first power input. An output of the comparator switches state as a function of the relative voltage of the reference voltage and the first power input. The output of the comparator controls a switch, and thus opens and closes the switch according to the relative voltage of the reference voltage and the first power input. The switch is disposed between a power supply and the second power input. Accordingly, the second power input can be maintained in a predefined relationship to the first power input.

While the methods and processes of embodiments of the present invention have proven to be particularly useful in the area of personal computing enterprises, those skilled in the art will appreciate that the methods and processes of the present invention can be used in a variety of different applications and in a variety of different areas of manufacture to yield customizable enterprises, including enterprises for any industry utilizing control systems or smart-interface systems and/or enterprises that benefit from the embodiments of such devices. Examples of such industries include, but are not limited to, automotive industries, avionic industries, hydraulic control industries, auto/video control industries, telecommunications industries, medical industries, special application industries, and electronic consumer device industries. Accordingly, the systems and methods of the present invention can provide benefits to many different markets, including markets that have traditionally been untapped by current computer techniques.

Embodiments of the invention provide systems and methods for wirelessly receiving computer systems diagnostics information and for customizably displaying such information. The information may be received from a wide variety of existing and future computer systems, including a wide variety of general-purpose computer systems and a wide variety of special-purpose computer systems. As disclosed herein a platform management controller (PMC) or similar device incorporated into a computer system monitors computer system information and transmits or otherwise conveys the monitored information, such as by infrared. Embodiments of

10

15

20

25

30

21

the invention receive the transmitted information so it can be used for a variety of purposes such as disclosed herein.

In embodiments of the invention, a plurality of logged events transmitted by the PMC or other similar device may be received and monitored by a diagnostics device such as a wireless diagnostics device. In at least some embodiments of the invention, the processing features of the diagnostics device are implemented primarily or entirely in logic gates. Such embodiments provide certain advantages as will be discussed in detail herein. While certain embodiments of diagnostic devices as discussed herein are implemented using logic gate devices, it will be appreciated that the diagnostic devices may provide or pass on information to a variety of other computer systems of types currently known in the art or invented in the future. For example, in at least some embodiments, a diagnostic device may be connected to an external computer system using a wired or wireless connection such as a universal serial bus (USB) connection, an Ethernet connection, and the like. Such connection may be made at any time during use of the diagnostic device, including at the time that communications are received from the PMC or other similar device, or at some later time. Therefore, the following discussion is intended to describe computer systems that may be used with or connected to a diagnostic device for any reason.

Embodiments of the present invention relates to temporary electrical connections. In particular, the present invention relates to systems and methods for temporarily connecting an external device to a printed circuit board (PCB) in order to receive or transmit information from or to the PCB.

Embodiments of the present invention take place in association with temporary electrical connections between an external source and a PCB to facilitate the transfer of data across the connection. In at least one embodiments, a temporary electrical system includes a PCB having electrical contact pads disposed adjacent one or more edges of the PCB. The electrical contact pads in turn are electrically connected to particular locations on the PCB. The systems further includes a temporary electrical connector apparatus which in turn includes an electrical wire ribbon and a head at the distal end of the electrical wire ribbon having one or more electrical contact pads disposed thereon that correspond to the electrical pads disposed on the edge(s) of the PCB.

In further embodiments, an apparatus adapted to temporarily electrically connect with a PCB includes an electrical wire ribbon. The apparatus further includes a head at the distal end of

10

15

20

25

30

the electrical wire ribbon having one or more electrical contact pads disposed thereon. In some embodiments, the head also has an adhesive disposed on it, which substantially surrounds the electrical contact pads. Prior to use, the adhesive is protected by a non-stick paper backing or the like, which can be removed upon use. In other embodiments, the head includes a compression fitting that can be manipulated to tension the head such that it temporarily remains fixed to a corresponding surface, such as a PCB. In yet other embodiments, the head includes pins or other locators that that can be used to facilitate a temporary connection between the head and a corresponding surface, such as a PCB. In still another embodiments, the head is comprised of two opposing jaws connected by an operable spring which biases the jaws in a closed position such that the jaws can be selectively opened by a user and the head temporary "clipped" to a corresponding surface, such as a PCB. In yet other embodiments, the head is comprised of two opposing stationary surfaces connectably separated the width of a PCB such that the head can be temporarily slipped over the edge of the PCB to remain temporarily affixed thereto.

While the methods and processes of embodiments of the present invention have proven to be particularly useful in the area of temporary PCB connections, those skilled in the art can appreciate that the methods and processes can be used in a variety of different applications and in a variety of different areas of manufacture to yield temporary, convenient and inexpensive electrical connections.

Aspects of the embodiments of the invention will be discussed using various headings for purposes of discussion and clarity. The headings are provided only by way of facilitating aspects of the illustrated embodiments, and are not intended to be limiting in any way.

#### **Representative Computer Systems**

As mentioned above, embodiments of the invention may be implemented in a wide variety of computer systems and configurations, include systems and configurations similar to those disclosed in U.S. Patent Nos. 7,256,991 titled Non-Peripherals Processing Control Module Having Improved Heat Dissipating Properties, 7,242,574 titled Robust Customizable Computer Processing System, and 7,075,784 titled Systems and Methods for Providing a Dynamically Modular Processing Unit. By way of illustration only, Figures 1 and 2 are copies of Figures 1 and 3 of U.S. Patent No. 7,075,784 in which the original numbering has been maintained. These Figures and the corresponding discussion (which is essentially reproduced below) provide a first

10

15

20

25

30

23

PCT/US2011/039491

example of a representative computer system that may provide an operating embodiment in which at least certain embodiments of the invention may be implemented, as follows:

Figure 1 and the corresponding discussion are intended to provide a general description of a suitable operating environment in accordance with embodiments of the present invention. As will be further discussed below, embodiments of the present invention embrace the use of one or more dynamically modular processing units in a variety of customizable enterprise configurations, including in a networked or combination configuration, as will be discussed below.

Embodiments of the present invention embrace one or more computer-readable media, including non-transitory and/or tangible computer-readable media, wherein each medium may be configured to include or includes thereon data or computer executable instructions for manipulating data. The computer executable instructions include data structures, objects, programs, routines, or other program modules that may be accessed by one or more processors, such as one associated with a general-purpose modular processing unit capable of performing various different functions or one associated with a special-purpose modular processing unit capable of performing a limited number of functions.

Computer executable instructions cause the one or more processors of the enterprise to perform a particular function or group of functions and are examples of program code means for implementing steps for methods of processing. Furthermore, a particular sequence of the executable instructions provides an example of corresponding acts that may be used to implement such steps.

Examples of computer-readable media include random-access memory ("RAM"), read-only memory ("ROM"), programmable read-only memory ("PROM"), erasable programmable read-only memory ("EPROM"), electrically erasable programmable read-only memory ("EEPROM"), compact disk read-only memory ("CD-ROM"), any solid-state storage device (e.g., flash memory, smart media, etc.), or any other device or component that is capable of providing data or executable instructions that may be accessed by a processing unit.

With reference to Figure 1, a representative enterprise includes modular processing unit 10, which may be used as a general-purpose or special-purpose processing unit. For example, modular processing unit 10 may be employed alone or with one or more similar modular processing units as a personal computer, a notebook computer, a personal digital assistant

10

15

20

25

30

24

("PDA") or other hand-held device, a workstation, a minicomputer, a mainframe, a supercomputer, a multi-processor system, a network computer, a processor-based consumer device, a smart appliance or device, a control system, or the like. Using multiple processing units in the same enterprise provides increased processing capabilities. For example, each processing unit of an enterprise can be dedicated to a particular task or can jointly participate in distributed processing.

In Figure 1, modular processing unit 10 includes one or more buses and/or interconnect(s) 12, which may be configured to connect various components thereof and enables data to be exchanged between two or more components. Bus(es)/interconnect(s) 12 may include one of a variety of bus structures including a memory bus, a peripheral bus, or a local bus that uses any of a variety of bus architectures. Typical components connected bus(es)/interconnect(s) 12 include one or more processors 14 and one or more memories 16. Other components may be selectively connected to bus(es)/interconnect(s) 12 through the use of logic, one or more systems, one or more subsystems and/or one or more I/O interfaces, hereafter referred to as "data manipulating system(s) 18." Moreover, other components may be externally connected to bus(es)/interconnect(s) 12 through the use of logic, one or more systems, one or more subsystems and/or one or more I/O interfaces, and/or may function as logic, one or more systems, one or more subsystems and/or one or more I/O interfaces, such as modular processing unit(s) 30 and/or proprietary device(s) 34. Examples of I/O interfaces include one or more mass storage device interfaces, one or more input interfaces, one or more output interfaces, and the like. Accordingly, embodiments of the present invention embrace the ability to use one or more I/O interfaces and/or the ability to change the usability of a product based on the logic or other data manipulating system employed.

The logic may be tied to an interface, part of a system, subsystem and/or used to perform a specific task. Accordingly, the logic or other data manipulating system may allow, for example, for IEEE1394 (firewire), wherein the logic or other data manipulating system is an I/O interface. Alternatively or additionally, logic or another data manipulating system may be used that allows a modular processing unit to be tied into another external system or subsystem. For example, an external system or subsystem that may or may not include a special I/O connection. Alternatively or additionally, logic or other data manipulating system may be used wherein no external I/O is associated with the logic. Embodiments of the present invention also embrace the

10

15

20

25

30

use of specialty logic, such as for ECUs for vehicles, hydraulic control systems, etc. and/or logic that informs a processor how to control a specific piece of hardware. Moreover, those skilled in the art will appreciate that embodiments of the present invention embrace a plethora of different systems and/or configurations that utilize logic, systems, subsystems and/or I/O interfaces.

As provided above, embodiments of the present invention embrace the ability to use one or more I/O interfaces and/or the ability to change the usability of a product based on the logic or other data manipulating system employed. For example, where a modular processing unit 10 is part of a personal computing system that includes one or more I/O interfaces and logic designed for use as a desktop computer, the logic or other data manipulating system may be changed to include flash memory or logic to perform audio encoding for a music station that wants to take analog audio via two standard RCAs and broadcast them to an IP address. Accordingly, the modular processing unit 10 may be part of a system that is used as an appliance rather than a computer system due to a modification made to the data manipulating system(s) (e.g., logic, system, subsystem, I/O interface(s), etc.) on the back plane of the modular processing unit 10. Thus, a modification of the data manipulating system(s) on a back plane can change the application of the modular processing unit. Accordingly, embodiments of the present invention embrace very adaptable modular processing units 10.

As provided above, processing unit 10 includes one or more processors 14, such as a central processor and optionally one or more other processors designed to perform a particular function or task. It is typically processor 14 that executes the instructions provided on computer-readable media, such as on memory(ies) 16, a magnetic hard disk, a removable magnetic disk, a magnetic cassette, an optical disk, or from a communication connection, which may also be viewed as a computer-readable medium.

Memory(ies) 16 includes one or more computer-readable media that may be configured to include or includes thereon data or instructions for manipulating data, and may be accessed by processor(s) 14 through bus(es)/interconnect(s) 12. Memory(ies) 16 may include, for example, ROM(s) 20, used to permanently store information, and/or RAM(s) 22, used to temporarily store information. ROM(s) 20 may include a basic input/output system ("BIOS") having one or more routines that are used to establish communication, such as during start-up of modular processing unit 10. During operation, RAM(s) 22 may include one or more program modules, such as one or more operating systems, application programs, and/or program data.

10

15

20

25

30

As illustrated, at least some embodiments of the present invention embrace a non-peripheral encasement, which provides a more robust processing unit that enables use of the unit in a variety of different applications. In Figure 1, one or more mass storage device interfaces (illustrated as data manipulating system(s) 18) may be used to connect one or more mass storage devices 24 to bus(es)/interconnect(s) 12. The mass storage devices 24 are peripheral to modular processing unit 10 and allow modular processing unit 10 to retain large amounts of data. Examples of mass storage devices include hard disk drives, magnetic disk drives, tape drives, optical disk drives, and solid-state drives.

A mass storage device 24 may read from and/or write to a magnetic hard disk, a removable magnetic disk, a magnetic cassette, an optical disk, solid-state memory, or another computer-readable media media provide nonvolatile storage of data and/or executable instructions that may include one or more program modules, such as an operating system, one or more application programs, other program modules, or program data. Such executable instructions are examples of program code means for implementing steps for methods disclosed herein.

Data manipulating system(s) 18 may be employed to enable data and/or instructions to be exchanged with modular processing unit 10 through one or more corresponding peripheral I/O devices 26. Examples of peripheral I/O devices 26 include input devices such as a keyboard and/or alternate input devices, such as a mouse, trackball, light pen, stylus, or other pointing device, a microphone, a joystick, a game pad, a satellite dish, a scanner, a camcorder, a digital camera, a sensor, and the like, and/or output devices such as a monitor or display screen, a speaker, a printer, a control system, and the like. Similarly, examples of data manipulating system(s) 18 coupled with specialized logic that may be used to connect the peripheral I/O devices 26 to bus(es)/interconnect(s) 12 include a serial port, a parallel port, a game port, a universal serial bus ("USB"), a firewire (IEEE 1394), a wireless receiver, a video adapter, an audio adapter, a parallel port, a wireless transmitter, any parallel or serialized I/O peripherals or another interface.

Data manipulating system(s) 18 enable an exchange of information across one or more network interfaces 28. Examples of network interfaces 28 include a connection that enables information to be exchanged between processing units, a network adapter for connection to a local area network ("LAN") or a modem, a wireless link, or another adapter for connection to a

10

15

20

25

30

wide area network ("WAN"), such as the Internet. Network interface 28 may be incorporated with or peripheral to modular processing unit 10, and may be associated with a LAN, a wireless network, a WAN and/or any connection between processing units.

Data manipulating system(s) 18 enable modular processing unit 10 to exchange information with one or more other local or remote modular processing units 30 or computer devices. A connection between modular processing unit 10 and modular processing unit 30 may include hardwired and/or wireless links. Accordingly, embodiments of the present invention embrace direct bus-to-bus connections. This enables the creation of a large bus system. It also eliminates hacking as currently known due to direct bus-to-bus connections of an enterprise. Furthermore, data manipulating system(s) 18 enable modular processing unit 10 to exchange information with one or more proprietary I/O connections 32 and/or one or more proprietary devices 34.

Program modules or portions thereof that are accessible to the processing unit may be stored in a remote memory storage device. Furthermore, in a networked system or combined configuration, modular processing unit 10 may participate in a distributed computing environment where functions or tasks are performed by a plurality of processing units. Alternatively, each processing unit of a combined configuration/enterprise may be dedicated to a particular task. Thus, for example, one processing unit of an enterprise may be dedicated to video data, thereby replacing a traditional video card, and providing increased processing capabilities for performing such tasks over traditional techniques.

While those skilled in the art will appreciate that embodiments of the present invention may comprise a variety of configurations, reference is made to Figure 2, which illustrates a representative embodiment of a durable and dynamically modular processing unit. In the illustrated embodiment of Figure 2, processing unit 40 is durable and dynamically modular. In the illustrated embodiment, unit 40 is an approximately 3-1/2-inch (8.9 cm) cube platform that utilizes an advanced thermodynamic cooling model, eliminating any need for a cooling fan.

However, as provided herein, embodiments of the present invention embrace the use of other cooling processes in addition to or in place of a thermodynamic cooling process, such as a forced air cooling process and/or a liquid cooling process. Moreover, while the illustrated embodiment includes a 3-1/2-inch cube platform, those skilled in the art will appreciate that embodiments of the present invention embrace the use of a modular processing unit that is

10

15

20

25

30

greater than or less than a 3-1/2-inch cube platform. Similarly, other embodiments embrace the use of shapes other than a cube.

Processing unit 40 also includes a layered motherboard configuration, that optimizes processing and memory ratios, and a bus architecture that enhances performance and increases both hardware and software stability. Those skilled in the art will appreciate that other embodiments of the present invention also embrace non-layered motherboards. Moreover, other embodiments of the present invention embrace embedded motherboard configurations, wherein components of the motherboard are embedded into one or more materials that provide an insulation between components and embed the components into the one or more materials, and wherein one or more of the motherboard components are mechanical, optical, electrical or electro-mechanical. Furthermore, at least some of the embodiments of embedded motherboard configurations include mechanical, optical, electrical and/or electro-mechanical components that are fixed into a three-dimensional, sterile environment. Examples of such materials include polymers, rubbers, epoxies, and/or any non-conducting embedding compound(s).

Embodiments of the present invention embrace providing processing versatility. For example, in accordance with at least some embodiments of the present invention, processing burdens are identified and then solved by selectively dedicating and/or allocating processing power. For example, a particular system is defined according to specific needs, such that dedication or allocation of processing power is controlled. Thus, one or more modular processing units may be dedicated to provide processing power to such specific needs (e.g., video, audio, one or more systems, one or more subsystems, etc.). In some embodiments, being able to provide processing power decreases the load on a central unit. Accordingly, processing power is driven to the areas needed.

While the illustrated embodiment, processing unit 40 includes a 2 GHz processor and 1.5 GB of RAM, those skilled in the art will appreciate that other embodiments of the present invention embrace the use of a faster or slower processor and/or more or less RAM. In at least some embodiments of the present invention, the speed of the processor and the amount of RAM of a processing unit depends on the nature for which the processing unit is to be used.

A highly dynamic, customizable, and interchangeable back plane 44 provides support to peripherals and vertical applications. In the illustrated embodiment, back plane 44 is selectively coupled to encasement 42 and may include one or more features, interfaces, capabilities, logic

10

15

20

25

and/or components that allow unit 40 to be dynamically customizable. In the illustrated embodiment, back plane 44 includes DVI Video port 46, Ethernet port 48, USB ports 50 (50a and 50b), SATA bus ports 52 (52a and 52b), power button 54, and power port 56. Back plane 44 may also include a mechanism that electrically couples two or more modular processing units together to increase the processing capabilities of the entire system as indicated above, and to provide scaled processing as will be further disclosed below.