#### US006169432B1

# (12) United States Patent

Sharpe-Geisler

# (10) Patent No.: US 6,169,432 B1

(45) **Date of Patent: Jan. 2, 2001**

# (54) HIGH VOLTAGE SWITCH FOR PROVIDING VOLTAGES HIGHER THAN 2.5 VOLTS WITH TRANSISTORS MADE USING A 2.5 VOLT PROCESS

(75) Inventor: Bradley A. Sharpe-Geisler, San Jose,

CA (US)

(73) Assignee: Vantis Corporation, San Jose, CA

(US)

(\*) Notice: Under 35 U.S.C. 154(b), the term of this

patent shall be extended for 0 days.

(21) Appl. No.: 09/188,778

(22) Filed: Nov. 9, 1998

(51) **Int. Cl.**<sup>7</sup> ...... **H03B 1/00**; H03K 3/00

58) Field of Search ...... 327/108, 110,

327/111, 112, 415, 416, 436, 437, 544, 374; 326/81, 83, 77, 68, 70, 71, 80

#### (56) References Cited

#### U.S. PATENT DOCUMENTS

|             |         | Yero et al          |        |

|-------------|---------|---------------------|--------|

| 5,465,054 * | 11/1995 | Erhard              | 326/81 |

| 5,723,987 * | 3/1998  | Ronen               | 326/81 |

| 5,892,371 * | 4/1999  | Maley               | 326/81 |

|             |         | Rigazio             |        |

|             |         | Cranford, Jr. et al |        |

<sup>\*</sup> cited by examiner

Primary Examiner—Kenneth B. Wells Assistant Examiner—Long Nguyen (74) Attorney, Agent, or Firm—Fleisler, Dubb, Meyer & Lovejoy

# (57) ABSTRACT

A voltage switch is provided made up of 2.5 volt process transistors which tolerate a maximum gate to source, gate to drain, or drain to source voltage of 2.7 volts. The voltage switch transistors are arranged to switch between a voltage, such as 2.5 volts, and a much higher voltage, such as 4.5 volts. In one embodiment (350), the voltage switch includes an input provided to the source of an NMOS cascode connected transistor (360). An inverter (354) connects the source of the NMOS cascode (360) to the source of another NMOS cascode (361). A cascode transistor is defined as being connected so that it is turned on and off by varying source voltage with the gate voltage fixed, rather than varying gate voltage. Gates of the cascodes (360, 361) are connected to Vcc (2.5 volts). PMOS cascode transistors (362) and (363) connect the drains of respective cascode transistors (360) and (361) to PMOS transistors (364) and (365). The PMOS transistors (364) and (365) have sources connected to 4.5 volts. A PMOS transistor (366) has a gate tied to the drain of cascode (361) and provides Vcc to the switch output (n10). A PMOS transistor (368) has a gate tied to the gate of transistor 365 and supplies 4.5 volts to the switch output (n10). In operation, the switch (350) functions to selectively transition its output (n10) between Vcc and 4.5 volts without applying greater than 2.7 volts from the gate to source, gate to drain, or source to drain of any of its transistors.

# 8 Claims, 3 Drawing Sheets

FIG. 1

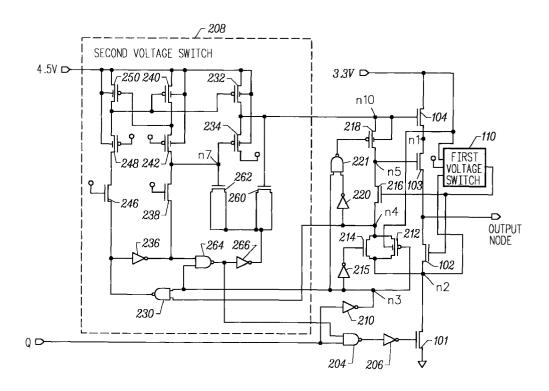

FIG. 2 OUTPUT NODE -902 -210 n 10 218-262 264 2667 234 SECOND VOLTAGE SWITCH  $^{-236}$ 230-

## HIGH VOLTAGE SWITCH FOR PROVIDING **VOLTAGES HIGHER THAN 2.5 VOLTS** WITH TRANSISTORS MADE USING A 2.5 **VOLT PROCESS**

#### BACKGROUND OF THE INVENTION

#### 1. Field of the Invention

The present invention relates to voltage switches for providing reference voltages in a circuit using 2.5 volt process transistors. More particularly, the present invention relates to an output buffer using such voltage switches.

#### 2. Description of the Related Art

With microprocessors manufactured using process technology enabling transistor size to be reduced well below 15 submicron level, the maximum source to drain, gate to drain, and gate to source voltage which such transistors can tolerate is likewise reduced. For instance, with one process referred to here as a 2.5 volt circuit process, transistor gate oxide thickness is reduced so that the maximum gate to 20 source, gate to drain, or drain to source voltage a microprocessor transistor can tolerate without failure is approximately 2.7 volts.

The reduced size of the transistors utilized in microprocessors enables an increase in operation speed as well as an 25 increase in density of transistors which can be integrated onto a single chip. Because of the increase in speed and density of transistors, the process technology utilized in manufacturing microprocessors is also desirable for use in other circuits.

For example programmable logic devices (PLDs), such as field programmable gate arrays (FPGAs), are some times utilized to perform the function similar to a microprocessors. The desirable operation speed and transistor density for PLDs is similar to microprocessors, so it would be desirable to use the same processing technology to manufacture such PLDs. However, unlike microprocessors, PLDs are utilized as glue logic to connect to devices with an operation voltage range which transistors made using the 2.5 volt circuit process will not tolerate.

For instance, PLDs typically connect to CMOS logic devices which operate over a 0–5 volt range, as well as TTL devices which operate over a 0-3.3 volt range. Although a transistor made using the 2.5 volt circuit process can produce a TTL output high of 2.4 volts, it is desirable for such a device to produce a voltage significantly higher than the 2.4 volt legal output high to assure errors do not occur.

## SUMMARY OF THE INVENTION

The present invention provides a high voltage switch for an output buffer made with 2.5 volt process transistors. The high voltage switch includes 2.5 volt process transistors configured to switch voltages significantly greater than 2.5

The high voltage switch of the present invention includes an input provided to the source of a first NMOS cascode transistor, and through an inverter to the source of a second NMOS cascode transistor. A cascode transistor is defined as being connected so that it is turned on and off by varying source voltage with gate voltage fixed, rather than varying gate voltage. The gates of the first and second cascodes are connected to Vcc, which in one embodiment is 2.5 volts. First and second PMOS cascode transistors connect the drains of the respective first and second NMOS cascode 65 drain of the PMOS transistor. transistors to first and second PMOS transistors. The first and second PMOS transistors have sources connected to a

high voltage potential, in one embodiment 4.5 volts. A third PMOS transistor has a gate tied to the drain of the second cascode and provides Vcc to the switch output. A fourth PMOS transistor has a gate tied to the second PMOS transistor gate and is connected to supply the high voltage potential to the switch output.

In operation, the high voltage switch functions to selectively transition its output between Vcc and the high voltage potential without applying greater than 2.7 volts from the gate to source, gate to drain, or source to drain of any of its transistors.

#### BRIEF DESCRIPTION OF THE DRAWINGS

Further details of the present invention are explained with the help of the attached drawings in which:

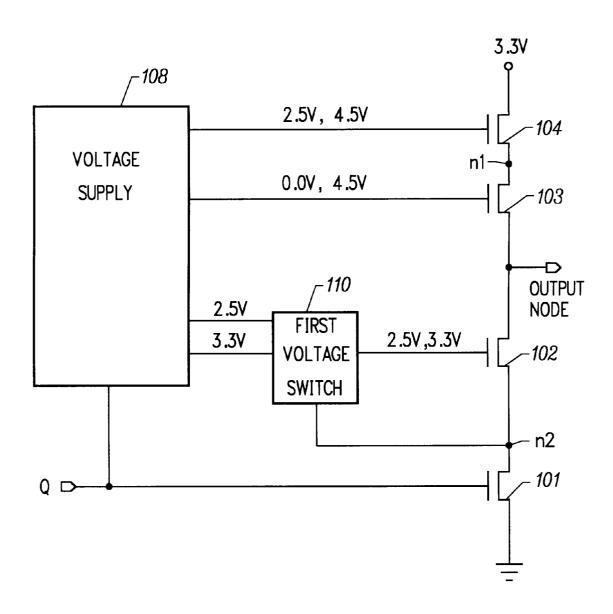

FIG. 1 illustrates components for an output buffer;

FIG. 2 shows one embodiment of circuitry including a high voltage switch of the present invention used to provide the output buffer of FIG. 1; and

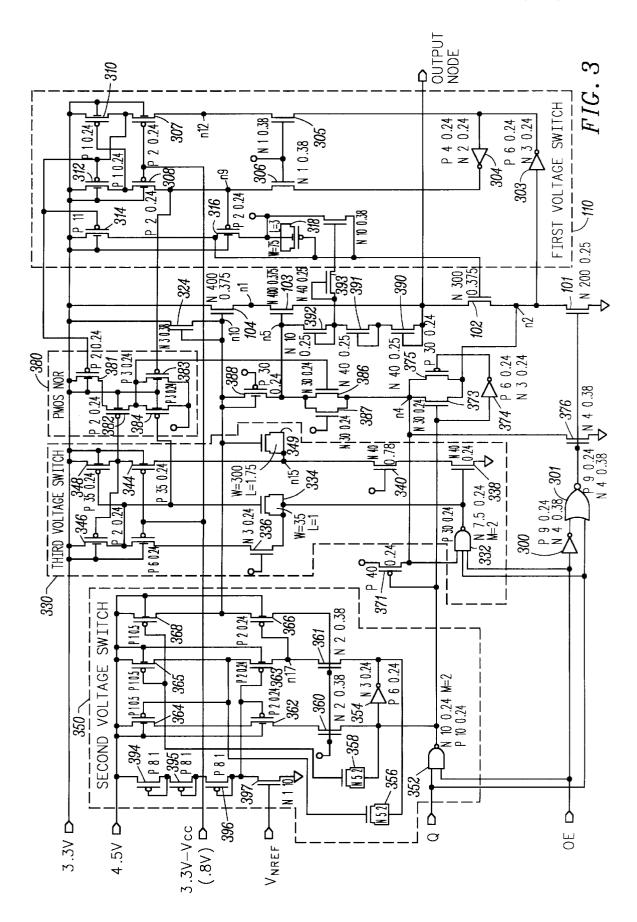

FIG. 3 shows another embodiment of circuitry for high voltage switches of the present invention used to provide the output buffer of FIG. 1.

#### DETAILED DESCRIPTION

A. Circuit of FIG. 1

FIG. 1 illustrates components for the output buffer using 2.5 volt process components. The output buffer includes a set of series connected pull down NMOS transistors 101 and 102 having source to drain paths connecting an output node to ground. The output buffer also includes a set of series connected NMOS transistors 103 and 104 having source to drain paths connecting a voltage supply, shown here as a 3.3 volt supply, to the output node. Transistors 101-104 have a 35 thin gate oxide region which will tolerate a maximum source to drain voltage of 2.7 volts. The transistors 101-104 will also only tolerate a maximum gate to drain and gate to source voltage of 2.7 volts.

An input Q to the output buffer is provided to the gate of 40 transistor 101. The gates of transistors 102-104 are driven by power supply circuitry including voltage supply 108 and a first voltage switch 110. The voltage supply 108 operates to provide 2.5 volts to the gate of transistor 104 when Q is high and 4.5 volts to the gate of transistor 104 when Q is low. 45 The voltage supply 108 also provides 0.0 volts to the gate of transistor 103 when Q is high and 4.5 volts when Q is low. The voltage supply 108 further provides 3.3 volts and  $V_{CC}$ , which here is 2.5 volts, to a first voltage switch 110. The first voltage switch 110 further receives feedback from node n2 and functions to apply 2.5 volts to the gate of transistor 102 when node n2 is low, and 3.3 volts when node n2 is high. The voltage supply 108 and first voltage switch 110 are controlled to apply voltages to the gates of transistors 101-104 so that the gate to drain, gate to source and drain to source voltages of the transistors 101-104 do not exceed a maximum of 2.7 volts.

NMOS transistors 103 and 104 are preferably utilized instead of PMOS transistors because if the voltage applied to the drain of one of the PMOS transistors exceeds its body voltage, it will forward bias its p+ to n-type well junction. To avoid forward biasing of the PMOS transistor, and enable PMOS transistors to be utilized for transistors 101 and 102, an n-type well in which the PMOS transistor is formed can be pumped to a higher voltage than a voltage applied to the

In operation, the input Q is first assumed to be high. With Q being high, transistor 101 will turn on, 2.5 volts will be

applied to the gate of transistor 104, and 0.0 volts will be applied to the gate of transistor 103. With transistor 101 on, node n2 will be pulled to ground and the first voltage switch 110 will apply 2.5 volts to the gate of transistor 102 to turn it on. Since the source and drain of transistor 102 are at ground, the 2.5 volts applied to its gate, as opposed to 3.3 volts, will not exceed the maximum gate to source, or gate drain voltage of 2.7 volts. The voltage at the source of transistor 104 will be its gate voltage minus an NMOS threshold, assumed here to be approximately 0.7 volts, 10 making the voltage at the source of transistor 104 (node n1) approximately 1.8 volts. Thus, the drain to source voltage drop across transistor 104 will be 1.5 volts which is less than the maximum tolerable 2.7 volts. With 0.0 volts applied to the gate of transistor 103, it will be turned off. With transistors 101 and 102 both being turned on by their gate voltage, the output node will be pulled to ground. The voltage drop across the source to drain of transistor 103 will then be 1.5 volts which is less than the maximum tolerable

With Q assumed to be low, transistor 101 will be off and 4.5 volts will be applied to the gates of transistors 103 and 104. With 4.5 volts applied to the gates of transistors 103 and 104, transistors 103 and 104 will both turn on to pass 3.3 volts to the output node. With transistor 101 turned off and 2.5 volts initially on the gate of transistor 102, node n2 will charge toward 2.5 volts so the first voltage switch 110 will transition the gate of transistor 102 from 2.5 to 3.3 volts. With 3.3 volts to the gate of transistor 102, its gate voltage minus an NMOS threshold, or 2.6 volts will be applied to the source of transistor 102 at node n2. None of the gate to source, gate to drain and source to drain voltage of transistor 102, thus, will exceed 2.7 volts. With transistor 101 turned off, the voltage drop across the source to drain of transistor 101 will then be 2.6 volts which is also less than the maximum tolerable 2.7 volts.

Although the voltage supply of 3.3 volts is used, and particular voltages are shown applied to the gates of transistors 101–104, other voltages can be used as long as the gate to drain, gate to source, and source to drain voltage for each of transistors 101–104 does not exceed the maximum 2.7 volts. Similarly, transistors having a different maximum gate to source, gate to drain, and source to drain voltage than 2.7 volts might be utilized, as long as the series connected pull down transistors, such as 101 and 102, are utilized in 45 conjunction with the series pull up transistors, such as 103 and 104, and appropriate gate voltages are applied. Further, although FIG. 1 shows only two pull down transistors 101-102 and two pull up transistors 103-104, additional series connected transistors might be utilized if the two pull up and pull down transistors are insufficient to provide the desired voltage drop from a reference to the output node, or from the output node to ground.

B. Circuit of FIG. 2

FIG. 2 shows one embodiment of circuitry used to provide 55 the output buffer of FIG. 1. Similar to FIG. 1, the circuit of FIG. 2 includes two series connected pull down transistors 101 and 102 connecting an output node to ground, and two series connected pull up transistors 103 and 104 connecting a 3.3 volt supply to the output node. Also as in FIG. 1, FIG. 60 2 further includes a first voltage switch 110 and circuitry to provide the voltage supply 108 of FIG. 1. Components carried over from FIG. 1 to FIG. 2 are similarly labeled, as will be components carried over in subsequent drawings. As in FIG. 1, the maximum tolerable gate to source, gate to 65 drain and source to drain voltage for transistors is assumed to be 2.7 volts.

4

The Q input of the buffer of FIG. 2 is coupled to the gate of transistor 101 through a NAND gate 204 and an inverter 206. The NAND gate 204 has one input receiving the signal Q. The output of the NAND gate 204 is connected to the input of inverter 206. The output of inverter 206 is connected to the gate of transistor 101. The second input of the NAND gate 204 is provided from a second voltage switch 208 to effectively disable the signal Q from turning on the gate of transistor 101 until the second voltage switch 208 can switch from providing 4.5 volts to providing 2.5 volts at its output node n10.

The Q input is further provided through an inverter 210 to a node n3. Node n3 provides one input to the second voltage switch 208. Node n3 is further connected to the gate of CMOS pass gates made up of a PMOS transistor 212 and an NMOS transistor 214. Node n3 is connected to the gate of transistor 214 through inverter 215. The source to drain paths of transistors 212 and 214 connect the source of transistor 102 at node n2 to the source of transistor 216 at node n4. Transistor 216 has a drain connected to the gate of transistor 103 at node n5. A PMOS transistor 103 at node n5 to the gate of transistor 104 at node n10. The gate of transistor 218 is driven by a NAND gate 221 having one input connected to node n3 and another input connected through an inverter 220 to node n4.

As in FIG. 1, the first voltage switch 110 receives inputs from the 3.3 volt supply,  $V_{CC}$  which here is 2.5 volts, and n2. The output of the first voltage switch is provided to the gate of transistor 102 as well as transistor 216. The first voltage switch 110 provides 3.3 volts at its output when node n2 is high and 2.5 volts at its output when node n2 is low.

102, thus, will exceed 2.7 volts. With transistor 101 turned off, the voltage drop across the source to drain of transistor 101 will then be 2.6 volts which is also less than the maximum tolerable 2.7 volts.

Although the voltage supply of 3.3 volts is used, and particular voltages are shown applied to the gates of transistors 101–104, other voltages can be used as long as the gate to drain, gate to source, and source to drain voltage for each of transistors 101–104 does not exceed the maximum 2.7 volts. Similarly, transistors having a different maximum gate to source, gate to drain, and source to drain voltage than 2.7 volts might be utilized, as long as the series connected of the voltage switch 208 includes a NAND gate 230 having one input provided from node n3, as indicated above. A second input of NAND gate 230 is provided from node n4. PMOS transistors 232 has a source to drain path connecting a 4.5 volt reference to node n10, while the PMOS transistor 234 has a source to drain path connecting V<sub>CC</sub>, V<sub>CC</sub> being assumed to be 2.5 volts here, to node n10 will be driven to 4.5 volts, and if PMOS transistor 234 is on, node n10 will be driven to 2.5 volts.

The gate of transistor 234 is coupled to the output of NAND gate 230 through an inverter 236 and source to drain path of an NMOS cascode transistor 238. The gate of transistor 234 is also coupled to the 4.5 volt reference through the source to drain path of PMOS transistor 240 and PMOS cascode transistor 242. The gate of transistor 232 is coupled to the output of NAND gate 230 through the source to drain paths of an NMOS cascode transistor 246 and a PMOS cascode transistor 248. The gate of transistor 232 is also coupled to the 4.5 volt reference through PMOS transistor 250. The gates of NMOS cascode transistors 238 and 246, as well as the gates of PMOS cascode transistors 242 and 248 are connected to  $V_{\it CC}$  or 2.5 volts. The gate of transistor 240 is further connected to the gate of transistor 232 and the drain of transistor 250, while the gate of transistor 250 is connected to the drain of transistor 240. Transistors 240 and 250, thus, form a cross coupled pair.

Note that a cascode transistor, such as transistors 246, 238, 242 and 248, are transistors defined by being turned on and off by varying voltage applied to the source with the gate voltage fixed, rather than varying the gate voltage. In a cascode transistor with  $(v_g-v_s)>v_p$ , wherein  $v_g$  is the gate voltage,  $v_s$  is the source voltage, and  $v_t$  is the threshold

voltage of the transistor, the cascode transistor will turn on. With  $(v_{\sigma}-v_{s}) < v_{r}$ , the cascode transistor will turn off.

Transistors 260 and 262 form capacitors utilized to pump nodes n10 and n7 so that the gate of transistor 104 quickly gets to a desired voltage level. Transistor 260 has a gate connected to node n10 and a source and drain connected to the output of inverter 236 through a series connected NAND gate 264 and inverter 266. Transistor 262 has a gate connected to node n7 and a source and drain connected to the output of inverter 266. A second input of NAND gate 264 is 10 connected to node n3, while the output of NAND gate 264 is further connected to an input of NAND gate 204 to assure NAND gate 204 does not turn on transistor 101 until the voltage switch 208 has had time to switch.

All of the PMOS transistors shown in FIG. 2, and in 15 subsequent drawings, are identified by a circle on their gate. An NMOS transistor has no circle on its gate.

In operation, the Q input is first assumed to be high. With O high, the output of inverter 210 at node n3 will be low. With n3 low, the output of NAND gate 264 will be high. 20 With NAND gate 264 and Q being high, the output of NAND gate 204 will be low and the output of inverter 206 will go high so transistor 101 will be turned on to pull node n2 to ground. With n3 low, transistors 212 and 214 will also turn on to pull node n4 to ground like node n2. With node n2 low, the output of the first voltage switch 110 will apply 2.5 volts to the gates of transistors 102 and 216. With transistor 216 being on, n5 will be pulled to ground like node n4. With n5 at ground, transistor 103 will be turned off. With transistor 102 being on and node n2 at ground, the output 30 node will be pulled to ground. With node n3 low, the output of NAND gate 221 will be at 2.5 volts to drive the gate of transistor 218 high to turn it off and isolate node n10 from node n5. With Q high, the output of the second voltage more detail below. With n10 at 2.5 volts, transistor 104 will partially turn on to drop node n1 to 2.5 volts minus an NMOS threshold of 0.7 volts, or to 1.8 volts. Thus, the drain to source voltage drop across transistor 104 will be 1.5 volts which is less than the maximum tolerable 2.7 volts. Further with 2.5 volts on the gates of transistors 102 and 216, as opposed to 3.3 volts, and zero volts on their source and drain, their gate to source and gate to drain voltage will be less than the maximum tolerable 2.7 volts.

The output of second voltage switch 208 with Q high will 45 function to maintain node n10 at approximately 2.5 volts, as described below. As indicated above, with Q high nodes n3 and n4 will be low so the output of NAND gate 230 will be high. With the output of NAND gate 230 high, the output of inverter 236 will be low so that NMOS cascode 238 turns on 50 to pull node n7 low, or to 0.0 volts. With the output of NAND gate 230 high, NMOS cascode 246 will turn off. With node n7 at 0.0 volts, PMOS transistor 234 will be on to provide  $V_{CC}$  to node n10. With node n7 at 0.0 volts,  $V_{CC}$ minus an PMOS threshold of typically -0.6 volts, or 3.1 volts will be placed on the gate of transistor 250. With the 4.5 volt reference applied to the source of transistor **250** and 3.1 volts on its gate, it will turn on to provide 4.5 volts to the gate of transistor 232 to assure transistor 232 is turned off. Note that 3.1 volts is applied to the gate of transistor 250 to assure its gate to source voltage is less than the maximum tolerable voltage of 2.7 volts. Similarly, the 3.1 volts is applied to the drain of transistor 240 to assure that its source to drain voltage does not exceed a maximum of 2.7 volts. With the gate of transistor 232 at 4.5 volts, the gate of 65 transistor 240 will also be at 4.5 volts to turn it off so that node n7 will remain low. With the output of inverter 236 low,

the output of NAND gate 264 will be high, and inverter 266 will provide a low output to the second end of capacitors 260 and **262**.

With Q assumed to transition from high to low, the output of NAND gate 204 will transition to high to turn off transistor 101. Further, the output of inverter 210 will pull node n3 high to turn off transistors 212 and 214. With node n3 high, the NAND gate 221 will be enabled so that the voltage at node n4 will drive the gate of transistor 218 to prevent its gate to source and gate to drain voltage from exceeding a maximum of 2.7 volts. With node n4 initially at 0.0 volts, transistor 218 will be on to connect nodes n5 and n10. With node n10 being initially at approximately 2.5 volts, node n5 will also charge up toward 2.5 volts.

With 2.5 volts initially on the gate of transistor 102, and nodes n5 and n10 being at 2.5 volts to turn on transistors 103 and 104 to a degree, and transistor 101 being off, node n2 will charge up to approximately 1.8 volts. With node n2 going to 1.8 volts, the first voltage switch 110 will transition from providing 2.5 volts at its output to providing 3.3 volts. The gates of transistors 216 and 102 will, thus transition to 3.3 volts. With 3.3 volts on the gate of transistor 216, node n5 being at 2.5 volts, and transistors 212 and 214 being off, node n4 will charge up to approximately 2.5 volts. Note that with 3.3 volts on the gates of transistors 102 and 216 and their source and drain charging up to at least 1.8 volts, the maximum gate to source and gate to drain voltage of 2.7 volts will not be exceeded.

With Q going low, the output of second voltage switch **208** will function to maintain node n**10** at approximately 4.5 volts, as described in detail below. With node n4 going to 2.5 volts, and node n3 being high, the output of NAND gate 230 will transition to low. With the output of NAND gate 230 low, the output of inverter 236 will go high to turn off switch 208 at node n10 will be at 2.5 volts as described in 35 cascode 238. With the output of NAND gate 230 low, cascode transistor 246 will turn on. With transistor 246 on, the source of PMOS cascode 248 will go to V<sub>CC</sub> minus a PMOS threshold of -0.6 volts, so a total of 3.1 volts will be applied to the gates of transistors 232 and 240 to turn them on. With transistor 232 being on, the 4.5 volt reference will be applied to node n10. Further, with transistor 240 being on, 4.5 volts will be applied through transistor 242 to transition node n7 to 4.5 volts and turn off transistor 234. 4.5 volts will also be applied to the gate of transistor 250 to turn it off.

> With the output of inverter 236 being high, and node n3 being high, the output of NAND gate 264 will be low. With the output of NAND gate 264 low, inverter 266 will provide a high of 2.5 volts to capacitors **262** and **260**. The capacitors 260 and 262 serve to assist transistor 232 in pulling node n10 to 4.5 volts.

> With node n4 charging to 2.5 volts, 2.5 volts will be applied to the gate of transistor 218 by NAND gate 221. With 4.5 volts on the gate of transistor 218 at node n10, transistor 218 will still be on to provide 4.5 volts to node n5. With 2.5 volts instead of 0.0 volts on its gate, the gate to source voltage and gate to drain voltage of transistor 218 will not exceed a maximum tolerable value of 2.7 volts.

> With the gates of transistors 103 and 104 both being at 4.5 volts, and transistor 101 being turned off, 3.3 volts will be applied to the output node. With 3.3 volts on the gate of transistor 102, a voltage drop of 2.6 volts will be provided across transistor **102** to charge node n**2** to approximately 1.9 volts. With such voltages applied to transistors 101-104, none of their gate to drain, gate to source, or source to drain voltages will exceed the maximum tolerable 2.7 volts.

> With Q transitioning back to high, node n3 will go low to turn on transistors 212 and 214. With node n3 going low, the

output of NAND gate 230 will transition to high so that the second voltage switch 208 transitions from providing 4.5 volts at node n10 to providing 2.5 volts to n10. Transistor 101 will remain off until NAND gate 264 transitions to high due to the NAND gate 264 providing an input to NAND gate **204**. Transistor **101** will remain off for a time necessary for the second voltage switch 208 to transition node n10 to 2.5 volts before transistor 101 connects node n2 to ground to prevent transistors 103 or 104 from exceeding the 2.7 volt maximum source to drain voltage drop. With node n3 low, 10 NAND gate 221 will turn off transistor 218 to isolate node n10 from node n5, enabling node n5 to be pulled to ground to turn off transistor 103, while 2.5 volts remains on the gate of transistor 104. The description of the function of the circuit of FIG. 2 with Q initially high as explained previously can be referenced above for the remaining description of function where Q has transitioned to high. C. Circuit of FIG. 3

7

FIG. 3 shows another embodiment of an output buffer using 2.5 volt process components which includes specific 20 circuitry for the first voltage switch 110 of FIGS. 1 and 2, and further includes additional circuitry to prevent the source to drain, gate to drain, or gate to source voltage of transistors in the output buffer from exceeding a maximum.

For transistor symbols in FIG. 3, a suggested channel type and transistor dimensions are indicated next to the transistor with a P or N indicating channel type followed by channel width and length in microns. For capacitors a length and width in microns is shown. An additional M=2 is included to indicate that two such transistors are included and connected identically. For inverters, NAND gates, and the NOR gate, channel type and dimensions are included with the inverter to show suggested sizes for the transistors making up those gates. Transistor sizes and types are only suggested and may be changed to meet particular design requirements.

Similar to FIGS. 1 and 2, the circuit of FIG. 3 includes two series connected pull down transistors 101 and 102 connecting an output node to ground, and two series connected pull up transistors 103 and 104 connecting a 3.3 volt supply to the output node. As before, the maximum tolerable gate to source, gate to drain, and drain to source voltage for each of the transistors in FIG. 3 is assumed to be 2.7 volts. 1. Transistor 101 and its Driving Circuitry

Transistor 101 has a gate coupled to receive an input signal Q through a NOR gate 301. The NOR gate 301 enables a tristate mode since its second input is provided from an output enable signal (OE). The source of transistor 101 is connected to  $V_{SS}$ , while its drain is connected to node n2. The output of the NOR gate 301, thus functions to transition the input of transistor 101 between 0.0 volts and 2.5 volts. With the OE signal high, transistor 101 will turn on when Q goes low and turn off when Q goes high. With OE low, the output of NOR gate 301 will remain at 0.0 volts to keep transistor 101 off in a tristate mode.

Note in FIG. 3 the output node will be pulled low when 55 Q goes low and OE is high to turn on transistor 101, while in FIGS. 1 and 2, the output node will go high when Q goes low. The reversed state of the output node in relation to the state of Q occurs due to the adding of the NOR gate 301 to accommodate the output enable (OE). If it is still desirable 60 to have the output node low when Q goes high, an inverter can be added between the Q input and NOR gate 301.

#### 2. Transistor 102 and its Driving Circuitry

Transistor 102 has a gate connected to a first voltage switch 110, similar to the transistor 102 of FIGS. 1 and 2. As before, the transistor 102 is not switched by its gate voltage, but remains always on. As in FIGS. 1 and 2, the first voltage

switch 110 functions to prevent the gate to source and gate to drain voltage on transistor 102 from exceeding a 2.7 volt maximum. Thus, when the source of transistor 102 at node n2 is connected to ground, the first voltage switch 110 functions to provide 2.5 volts to the gate of transistor 102. When the source of transistor 102 is connected to a voltage greater than 1.5 volts, the first voltage switch 110 will function to increase the voltage at the gate of transistor 102 to 3.3 volts to assure node n2 can charge up to 2.5 volts and the output node can sustain an applied voltage of at least 5.0

The first voltage switch 110 includes an inverter 303 having an input connected to the source of transistor 102 at node n2, and an output connected to the source of an NMOS cascode transistor 305, and through an inverter 304 to the source of an NMOS cascode 306. The drain of transistor 305 is connected to the drain of PMOS cascode 307 at a node n12, while the drain of transistor 306 is connected to the drain of a PMOS cascode 308 at a node n9. The gates of transistors 305 and 306 are connected to  $V_{CC}$ ,  $V_{CC}$  here being 2.5 volts. The source of transistor 307 is connected at node n13 to the drain of transistor 310, while the source of transistor 308 is connected to the drain of transistor 312. The gates of transistors 307 and 308 are connected to a supply having a voltage value of 3.3 volts minus  $V_{CC}$ , or 0.8 volts. Sources of transistors 310 and 312 are connected to the 3.3 volt supply. The gate of transistor 310 is connected to the drain of transistor 312, while the gate of transistor 312 is connected to node n13. Transistors 310 and 312, thus, form a cross-coupled pair. The source of a transistor 314 is connected to the 3.3 volt supply. The drain of transistor 316 is connected to  $V_{CC}$ . The drain of transistor 314 is connected to the source of transistor 316 and to the gate of transistor 102. The first end of a capacitor 318 and the drain of a clamp transistor 320 are connected to  $V_{CC}$ . The second end of capacitor 318 and the source and gate of clamp transistor 320 are connected to the gate of transistor 102. The gate of transistor 316 is connected to node n9. The gate of transistor 314 is connected to node n13.

In operation with the first voltage switch 110, Q is first assumed low with OE high to turn on transistor 101 to pull node n2 to ground. The output of inverter 303 will then be high to shut off NMOS cascode 305 and cause the output of inverter 304 to be low. With the output of inverter 304 low, NMOS cascode 306 will be on to pull node n9 low. With node n9 low, transistor 316 turns on to pull the gate of transistor 102 to  $V_{CC}$ . With n9 low, PMOS 308 pulls the gate of transistor 310 low to turn on transistor 310 to connect the 3.3 volt supply to node n13. With 3.3 volts on node n13, transistors 312 and 314 are turned off. With transistor 314 off, the 3.3 volt supply is not connected to the gate of transistor 102. The gate of transistor 102 is, thus, maintained at  $V_{CC}$ , or 2.5 volts.

It is next assumed that a low to high transition of the output node occurs. This can occur with Q going high and OE remaining high. This can also occur with OE going low to tristate the output and the output node being externally pulled high. With the output node high and transistor 102 being on as always, transistor 102 will pass the high from the output node to the input of inverter 303 so that the output of inverter 303 goes low. A low to high transition at the output node will, because of capacitive coupling, also push the gate of transistor 102 high. Capacitor 318 is appropriately sized so that the voltage swing at the gate of transistor 102 goes only up to 3.2 volts. With the output of inverter 303 low, NMOS cascode 305 turns on to pull node n12 to 0.0 volts. With n12

8

at 0.0 volts, PMOS transistor 307 pulls node n13 low and, thus, the gate of transistors 312 and 314 low to turn on transistors 312 and 314. With transistor 314 on, 3.3 volts will be passed to the gate of transistor 102. Clamp transistor 320 will limit the voltage at the gate of transistor 102 to 3.3 volts. With the output of inverter 303 low, the output of inverter 304 will go high to turn off transistor 306. With transistor 312 on, node n9 will be pulled high through cascade 308 to turn off transistor 316. With 3.3 volts on its gate, the NMOS approximately 2.5 volts when 3.3 volts is applied to the gate of transistor 102.

#### 3. Transistor 104 and its Driving Circuitry

The gate of pull-up transistor 104 is driven by a second voltage switch 350 which, similar to the second voltage switch 208 of FIG. 2, functions to transition the gate of transistor 104 at node n10 between 2.5 and 4.5 volts. The gate of transistor 104 is further driven by a third voltage switch 330 which functions to assist the second voltage switch 350 in transitioning node n10 between 2.5 and 4.5 volts. After a transition of node n10 to 4.5 volts, clamp transistor 324 controls the overdrive of transistor 104 to limit the voltage on node n10 to 4.5 volts.

#### i. Third Voltage Switch 330

The third voltage switch 330 includes a capacitor 349 connected on a first end to node n10. The third voltage switch functions to drive node n15 at the second end of capacitor 349 to pump node n10 to 4.5 volts, or pull node n10 back down to 2.5 volts.

The third voltage switch 330 also includes a three input 30 NAND gate 332 having a first input provided by the input signal Q, a second input provided from an output enable signal OE, and a third input provided from a transistor 371. The output of NAND gate 332 is connected to the second 336 and the gate of an NMOS pull down transistor 338. The source of transistor 338 is connected to the source of an NMOS cascode 340. Gates of cascodes 336 and 340 are connected to  $V_{CC}$ . The source of cascode 340 is connected to the drain of PMOS cascode 344 at a node n15, while the source of cascode 336 is connected to the drain of PMOS cascode 342. The gates of PMOS cascode transistors 342 and 344 are connected to the voltage supply providing 3.3 volts minus  $V_{CC}$ , or 0.8 volts. The source of cascode 342 is connected to the drain of a PMOS transistor 346 and the gate 45 of a PMOS transistor 348. The source of cascode 344 is connected to the drain of PMOS transistor 348 and the gate of PMOS transistor 346. Sources of transistors 346 and 348 are connected to the 3.3 volt supply. Transistors 346 and 348, thus, form a cross-coupled pair.

In operation with the third voltage switch 330, the output of NAND gate 332 is first assumed to be high. This will occur with Q high, OE high, and n5 being pulled sufficiently high to pull the drain of transistor 371 high. With the output of NAND gate 332 high, NMOS pull down transistor 338 turns on to pull the source of cascode 340 to 0.0 volts. Cascode 340 then conducts to pull node n15 to 0.0 volts and drain charge from capacitor 349 to pull node n10 down toward 2.5 volts. With node n15 at 0.0 volts, PMOS cascode 344 pulls the gate of transistor 346 low to turn it on. With transistor 346 on, the 3.3 volt supply is connected to the gate of transistor 348 to turn it off, and to a first terminal of capacitor 334. Transistor 346 being on in conjunction with transistor 342 pulls the drain of transistor 336 to 3.3 volts.

It is next assumed that the output of NAND gate 333 goes low. This can occur when any of Q, OE, or node n4 are pulled low. With the output of NAND gate 332 low, the

10

NMOS pull down transistor 338 is turned off. With the output of NAND gate 332 low, capacitor 334 will further pull charge from the gate of PMOS driver transistor 348 to turn it on. With transistor 348 on, the gate of transistor 346 will go to 3.3 volts to turn it off, and node n15 will be pulled up to 3.3 volts through transistor **344**. With node n**15** at 3.3 volts, capacitor 349 will pump node n10 toward 4.5 volts. Clamp transistor 324 will limit the voltage on node n10 to 4.5 volts. The output of NAND gate 332 being low also turns threshold of transistor 102 will make the voltage at node n2 10 on NMOS cascode 336 to provide 0.0 volts to the drain of transistor 342. With 0.8 volts on the gate of transistor 342, it will not pull the gate of transistor 348 below 0.8 volts. Transistor 348 will then have a minimal amount of voltage to enable it to remain on, while not having a gate to source voltage drop greater than the maximum tolerable 2.7 volts. ii. Second Voltage Switch 350

> Similar to the circuit 208 of FIG. 2, the circuit 350 includes PMOS transistors 368 and 366 to drive the output node n10 of the second voltage switch 208. The PMOS transistor 368 has a source to drain path connecting a 4.5 volt supply to node n10, while the PMOS transistor 366 has a source to drain path connecting  $V_{CC}$ ,  $V_{CC}$  being assumed to be 2.5 volts here, to node n10. Thus, if the PMOS transistor 368 is turned on, node n10 will be maintained at 4.5 volts, and if PMOS transistor 366 is on, node n10 will be maintained at 2.5 volts.

The second voltage switch 350 further includes a NAND gate 352 having a first input receiving the Q input, and a second input connected to receive the output enable (OE) signal. The output of NAND gate 352 is connected to the source of an NMOS cascode 360, a second terminal of a capacitor 356, and through an inverter 354 to the source of an NMOS cascode 361. The gates of the NMOS cascodes 360 and 361 are connected to  $V_{\it CC}$ . A PMOS cascode 362 input of a capacitor 334, the source of an NMOS cascode 35 has a drain connected to the drain of transistor 360, while an additional PMOS cascode 363 has a drain connected to the drain of transistor 361 at a node n17. Gates of transistors 362 and 363 are connected to the 4.5 volt supply through series connected PMOS transistor 394-396. The gates of transistors 394 are tied to their drains so that during power up, the PMOS threshold of transistors 394–396 will prevent the gate voltage on transistors 362-363 from exceeding a 2.7 volt maximum. An NMOS transistor 397 has a source to drain path tying the drain of transistor 396 to ground. A reference V<sub>NREF</sub> having a voltage just above an NMOS threshold is applied to the gate of transistor 397 so that transistor 397 forms a weak current sink. During normal operation, approximately 4.5 volts minus 3 PMOS thresholds (≈2.0 volts) will be applied to the gate of transistors 362 and 363.

> A PMOS transistor 364 has a source to drain path connecting a 4.5 volt supply to the source of transistor 362, while a PMOS transistor 365 connects the 4.5 volt supply to the source of transistor 363. A gate of transistor 364 is connected to the source of transistor 363, while the gate of transistor 365 is connected to the source of transistor 362. The gate of the 2.5 volt PMOS driver transistor 366 is connected to node n17. The gate of 4.5 volt PMOS driver transistor 368 is connected to the gate of transistor 365, to the drain of transistor 364, and to the first end of a capacitor 358. The gate of transistor 364 is also connected to the first end of a capacitor 356. A second end of capacitor 356 is connected to the output of inverter 354.

> In operation with the second voltage switch 350, either the Q input or OE is initially assumed to be low. With Q or OE low, the second voltage switch 350 will function to maintain node n10 at 2.5 volts, as described below. With Q low, the output of NAND gate 352 will be high. With the output of

NAND gate 352 high, the output of inverter 354 will go low to turn on NMOS cascode 361 to pull node n17 to 0.0 volts. With the output of NAND gate 352 high, cascode 360 will turn off. With node n17 now at 0.0 volts, transistor 366 will turn on to on connect the gate of transistor 104 at node n10 to  $V_{CC}$ , or 2.5 volts. With node n17 at 0.0 volts, transistor 363 will pass a low of 2.0 volts plus its threshold placing the source of transistor 363 at approximately 2.8 volts. With the source of transistor 363 at 2.8 volts or less, transistor 364 will turn on to connect the 4.5 volt supply to the gates of transistors 365 and 368 to turn them off. The 4.5 volt supply will also be connected by transistor 364 to a first terminal of capacitor 358. With 2.8 volts on the gate of transistor 364, it will remain on without its gate to source voltage exceeding a maximum of 2.7 volts. With 2.8 volts on the drain of transistor 365, its source to drain voltage will not exceed a maximum of 2.7 volts.

11

Capacitor 358 couples the 2.5 volt transition at the output of NAND gate 352 to the gates of transistors 365 and 368 to speed up switching action for those transistors. Capacitor 20 356 does the same for transistor 364.

With O going high and OE being high, the second voltage switch 350 will function to transition node n10 to 4.5 volts, as described below. With Q going high and OE being high, the output of NAND gate 352 will transition to low. With the output of NAND gate 352 low, the output of inverter 354 will then go high to turn off cascode 361. With the output of NAND gate 352 low, cascode transistor 360 will turn on. With transistor 360 on, the source of PMOS cascode 362 will go to 2.0 plus its threshold, placing a total of 2.8 volts on the gates of transistors 365 and 368 to turn them on, while preventing their gate to source voltage from exceeding a maximum of 2.7 volts. With transistor 368 being on, 4.5 volts will be applied to node n10. Further, with transistor 365 being on, 4.5 volts will be applied through transistor 363 to transition node n17 to 4.5 volts and turn off transistor 366. 4.5 volts will also be applied to the gate of transistor 364 to turn it off.

# 4. Transistor 103 and its Driving Circuitry

FIG. 3 includes additional circuitry to drive transistor 103, 40 and to assure that the gate to drain, gate to source and source to drain voltage of transistors in the output buffer do not exceed the maximum tolerable amount of 2.7 volts.

The additional circuitry of FIG. 3 includes a PMOS transistor 371 having a gate connected to the output of 45 373 and 375. Further, after nodes n4 and n5 are pulled high NAND gate 352 and a source to drain path connecting  $V_{CC}$ to a node n4. FIG. 3 further includes a CMOS pass gate made up of an NMOS transistor 373 and a PMOS transistor 375, each having a source to drain path connecting node n4 to the source of transistor 102 (node n2). The gate of transistor 373 is connected directly to the output of NAND gate 352, and the gate of transistor 375 is connected to the output of NAND gate 352 through an inverter 374. Transistor 376 has a gate connected to the output of NOR gate 301, a drain connected to node n4 and a source connected to 55

$V_{SS}$ . FIG. 3 further includes a PMOS NOR gate 380. The PMOS NOR gate includes transistors 381-384, and has inputs provided from the drains of transistors 346 and 348 of the third voltage switch 330, and from nodes n9 and n13 of the first voltage switch 110. The output of NOR gate 380 is connected to the gate of a transistor 386. Transistors 386 and 387 both have a source to drain path connecting node n4 to the gate of transistor 103 at node n5. The gate of transistor 387 is connected to  $V_{CC}$ .

A transistor 388 has a source to drain path connecting node n10 to node n5 and a gate connected to V<sub>CC</sub>. Transis12

tors 390-392 have source to drain paths connected in series to connect node n5 to the output node. Transistor 393 has a source to drain path connecting the source of transistor 392 to the gate of transistor 102 to provide over voltage protection. The gates of transistors 390-393 are connected to their respective drains.

Operation of the circuitry driving the gate of transistor 103 is dependent upon all of the first voltage switch 110, second voltage switch 350 and third voltage switch 330, so operation is explained in the context of the entire circuit of FIG. 3 provided below.

#### i. Input Q Low

In operation, the input signal O is first assumed to be low, while the output enable OE is high. With Q low and OE high, the output of NAND gate 352 goes high to shut off PMOS transistor 371 and turn on transistors 373 and 375. With OE high to drive the output of inverter 300 low, the output of NOR gate 301 goes high to turn on transistor 101 to pull node n2 to 0.0 volts. With transistor 102 always on, the output node will also be pulled low. With transistors 373 and 375 on, node n2 will also pull down node n4. With the output of NOR gate 301 being high, transistor 376 will also be turned on to speed up pull node n4 down to 0.0 volts. With node n2 at 0.0 volts, the first voltage switch 110 will drives the gate of transistor 102 to 2.5 volts, which places node n9 at 0.0 volts and node n13 at 3.3 volts. Transistor 383 in NOR gate 380 will then turn on to connect 2.5 volts to the gate of transistor 386. Node n4 being at 0.0 volts then pulls the gate of transistor 103 at node n5 to 0.0 volts through transistors 30 386 and 387.

With Q low, the output of NAND gate 332 will be high so the third voltage switch 330 will drive node n15 to 0.0 volts. With node n15 at 0.0 volts, capacitor 349 connecting node n15 to node n10 will pull down node n10 toward 2.5 volts. With the output of NAND 352 being high, the second voltage switch 350 will maintain node n10 at 2.5 volts. With node n10 at 2.5 volts, cascode 388 will turn off to isolate node n10 at the gate of transistor 104 from node n5 at the gate of transistor 103, node n5 being at 0.0 volts.

ii. Input Q Low to High Transition

On a low to high transition of the Q input with OE also high, the output of NOR gate 301 turns off transistors 376 and 101. The output of NAND gate 352 then also goes low which turns on PMOS transistor 371 and turns off pass gates by transistor 371, the output of NAND gate 332 will go low so that the third voltage switch 330 will transition node n15 to 3.3 volts which pushes node n10 from 2.5 volts to 4.5 volts. With the output of NAND gate 352 high, the second voltage switch 350 will then function to maintain node n10 at the gate of transistor 104 at 4.5 volts. As node n10 rises, PMOS cascode 388 then turns on raising node n5 at the gate of transistor 103 from 2.5 volts to 4.5 volts which allows transistor 103 to pass 3.3 volts.

As the output node goes high, the gate of transistor 102 will be increased to 3.3 volts by first voltage switch 110, and node n9 will go to 3.3 volts, while node n13 goes low, or to

With the third voltage switch 330 driving node n15 high, transistor 382 of NOR gate 380 is turned off and transistor **384** is turned on connecting the gate of transistor **386** to 2.5 volts. With transistor 383 being a weak transistor, it provides a high impedance, and thus capacitive coupling, to the gate of transistor 386. When node n4 transitions from low to high, the gate of transistor **386** is coupled toward 3.3 volts enabling 2.5 volts to pass to node n5 to speed up switching. Transistor 386, thus, remains on during a low to high

transition of Q, and is transitioned by NOR gate 380 from a gate voltage as high as 3.3 volts enabling it to provide 2.5 volts from node n4 to n5, to a gate voltage of 2.5 volts enabling it to provide 1.8 volts from node n4 to node n5. iii. Input Q High to Low Transition

The input Q transitioning back from high to low and OE being high causes the third voltage switch 330 to drive node n15 back to 0.0 volts. With node n15 going to 0.0 volts, capacitor 349 pulls charge from node n10 bringing it from 4.5 volts back toward 2.5 volts. With Q going low, the output of NAND gate 352 will go high and the second voltage switch 350 will maintain node n10 at 2.5 volts. With 2.5 volts on node n10, transistor 388 will turn off to isolate n10 and node n5.

With the output of NAND gate 352 high, PMOS transistor 371 will turn off and pass transistors 373 and 374 will turn on. NOR gate 301 turns on transistors 376 and 101 to pull down node n4 and to pull the output node low through transistor 102 which is on. The first voltage switch 110 then drives the gate of transistor 102 to 2.5 volts, and transitions node n9 to 0.0 volts and node n13 to 3.3 volts. With node n13 at 3.3 volts and node n9 at 0.0 volts, NOR gate 380 applies 2.5 volts through transistor 383 to the gate of transistor 386. With node n4 low, node n5 will also be pulled to 0.0 volts through transistor 386 and 387.

iv. Tristate Condition

The tristate condition varies from the conditions described above where Q is low except that OE goes low to transition the output of NOR gate 301 to 0.0 volts to turn off transistors 101 and 376. The circuitry controlling the gate of transistor 102 will still transition, but will only depend on voltage which appears on the output node rather than the state of transistor 101.

In particular, the second voltage switch 350 will help assure the gate of transistor 104 is held at 2.5 volts. With transistor 387 always on and the output of NOR gate 352 high, a link path exists connecting the gate of transistor 103 35 to the output node through transistors 102, 373, 375, 386 and **387**. With the link path, when the output node is at 0.0 volts, 0.0 volts appears at the gate of transistor 103. As the output node is pulled high, transistor 102 will pass a voltage less than or equal to 2.5 volts due to voltage provided its gate 40 from the first voltage switch 110, as described previously. When the drain of transistor 102 raises to a value exceeding the threshold of inverter 303 in the first voltage switch 110, node n13 will go low and the drain of transistor 348 in the third voltage switch 350 will go low to cause transistors 381 45 and 382 in NOR gate 380 to pull the gate of transistor 386 to 3.3 volts. This will allow a voltage up to 2.5 volts to be passed to the gate of transistor 103 at node n5. As the output node voltage continues to rise, the voltage at node n5 will not continue to increase significantly until the output node 50 voltage exceeds three times an NMOS threshold above 2.5 volts, at which time transistors 390-392 will push node n5 until a point where PMOS transistor 388 clamps the voltage at 3.3 volts.

When the output node voltage drops below 2.5 volts, the 55 transistors 390–392 in the link path must be sized appropriately to provide a low enough impedance to keep transistor 103 off. Should an over voltage condition occur to significantly raise the voltage on the output node, transistors 390–393 will serve to pull up the gate of transistor 102 to 60 prevent damage to transistors of the output buffer.

Although the present invention has been described above with particularity, this was merely to teach one of ordinary skill in the art how to make and use the invention. Many additional modifications will fall within the scope of the 65 invention, as that scope is defined by the claims which follow.

14

What is claimed is:

- 1. A voltage switch comprising:

- a first cascode connected transistor having a gate coupled to a first voltage potential, a source coupled to an input node for the voltage switch, and having a drain;

- a second cascode connected transistor having a gate coupled to the first voltage potential, a source coupled to receive a complement of a signal received at the input node for the voltage switch, and having a drain;

- a third cascode connected transistor having a drain coupled to the drain of the first cascode transistor, a gate coupled to a second voltage potential, and having a source;

- a fourth cascode connected transistor having a drain coupled to the drain of the second cascode transistor, a gate coupled to the second voltage potential, and having a source;

- a first transistor having a drain coupled to the source of the third cascode transistor, a source coupled to a third voltage potential which is greater than the first and second voltage potentials, and having a gate;

- a second transistor having a drain coupled to the source of the fourth cascode transistor and to the gate of the first transistor, a source coupled to the third voltage potential, and a gate coupled to the drain of the first transistor;

- a third transistor having a drain coupled to an output node for the voltage switch, a source coupled to the second voltage potential, and a gate coupled to the drain of the first transistor; and

- a fourth transistor having a source coupled to the output node for the voltage switch, a gate coupled to the drain of the second cascode, and a drain coupled to the first voltage potential.

- 2. The voltage switch of claim 1, wherein the first and second cascode transistors are NMOS transistors, the third and fourth cascode transistors are PMOS transistors, and the first, second, third, and fourth transistors are PMOS transistors.

- 3. The voltage switch of claim 1, further comprising:

- an inverter having an input coupled to the input node for the voltage switch and an output coupled to the source of the second cascode transistor.

- **4**. The voltage switch of claim **1**, wherein the first voltage potential and the second voltage potential are equal.

- 5. The voltage switch of claim 4, wherein the first voltage potential and the second voltage potential are approximately 2.5 volts and the third voltage potential is approximately 4.5 volts.

- 6. The voltage switch of claim 1, wherein the first voltage potential is approximately 2.5 volts, the second voltage potential is approximately 0.8 volts, and the third voltage potential is approximately 3.3 volts.

- 7. The voltage switch of claim 1, further comprising:

- a first capacitor coupling the gate of the second transistor to the input node for the voltage switch;

- a second capacitor coupling the gate of the first transistor to the source of the second cascode transistor;

- a fifth transistor having a source to drain path coupled from the gate of the first transistor to the first voltage potential, and having a gate coupled to the gate of the second transistor.

- 8. The voltage switch of claim 1, further comprising:

- a first capacitor coupling the gate of the second transistor to the input node for the voltage switch.

\* \* \* \* \*