(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第5222649号

(P5222649)

(45) 発行日 平成25年6月26日(2013.6.26)

(24) 登録日 平成25年3月15日(2013.3.15)

(51) Int.Cl.

F 1

G01J 1/44

(2006.01)

G01J 1/44

E

G01J 1/42

(2006.01)

G01J 1/42

J

H01L 31/10

(2006.01)

H01L 31/10

G

H03K 17/78

(2006.01)

H03K 17/78

F

H03K 17/78

Q

請求項の数 7 (全 38 頁) 最終頁に続く

(21) 出願番号

特願2008-190941 (P2008-190941)

(22) 出願日

平成20年7月24日 (2008.7.24)

(65) 公開番号

特開2009-47688 (P2009-47688A)

(43) 公開日

平成21年3月5日 (2009.3.5)

審査請求日

平成23年6月23日 (2011.6.23)

(31) 優先権主張番号

特願2007-193015 (P2007-193015)

(32) 優先日

平成19年7月25日 (2007.7.25)

(33) 優先権主張国

日本国 (JP)

(31) 優先権主張番号

特願2007-193151 (P2007-193151)

(32) 優先日

平成19年7月25日 (2007.7.25)

(33) 優先権主張国

日本国 (JP)

(73) 特許権者 000153878

株式会社半導体エネルギー研究所

神奈川県厚木市長谷398番地

(72) 発明者 宮戸 英明

神奈川県厚木市長谷398番地 株式会社

半導体エネルギー研究所内

(72) 発明者 広瀬 篤志

神奈川県厚木市長谷398番地 株式会社

半導体エネルギー研究所内

審査官 豊田 直樹

最終頁に続く

(54) 【発明の名称】光電変換装置及びその光電変換装置を具備する電子機器

## (57) 【特許請求の範囲】

## 【請求項 1】

光電変換素子と、pチャネル型の電界効果トランジスタである参照側トランジスタと、複数の出力生成回路と、負荷抵抗と、出力端子を有し、

前記複数の出力生成回路のそれぞれは、pチャネル型の電界効果トランジスタである出力側トランジスタと、前記出力側トランジスタのソース電極及びドレイン電極の一方に一端が接続されている内部抵抗を有し、

前記光電変換素子の陰極は、前記参照側トランジスタのソース電極及びドレイン電極の一方、前記参照側トランジスタのゲート電極、及び前記複数の出力生成回路のそれぞれの前記出力側トランジスタのゲート電極に接続され、

前記複数の出力生成回路のそれぞれの前記内部抵抗の他端は、前記負荷抵抗の一端及び前記出力端子に接続され、

前記参照側トランジスタのソース電極及びドレイン電極の他方、及び前記複数の出力生成回路のそれぞれの前記出力側トランジスタのソース電極及びドレイン電極の他方は、高電位側電源線に接続され、

前記光電変換素子の陽極及び前記負荷抵抗の他端は、低電位側電源線に接続され、

前記複数の出力生成回路のそれぞれの前記出力側トランジスタのチャネル長Lとチャネル幅Wとの比 = W / L の値が、互いに異なる値であることを特徴とする光電変換装置。

## 【請求項 2】

光電変換素子と、nチャネル型の電界効果トランジスタである参照側トランジスタと、

10

20

複数の出力生成回路と、負荷抵抗と、出力端子を有し、

前記複数の出力生成回路のそれぞれは、nチャネル型の電界効果トランジスタである出力側トランジスタと、前記出力側トランジスタのソース電極及びドレイン電極の一方で一端が接続されている内部抵抗を有し、

前記光電変換素子の陽極は、前記参照側トランジスタのソース電極及びドレイン電極の一方、前記参照側トランジスタのゲート電極及び前記複数の出力生成回路のそれぞれの前記出力側トランジスタのゲート電極に接続され、

前記複数の出力生成回路のそれぞれの前記内部抵抗の他端は、前記負荷抵抗の一端及び前記出力端子に接続され、

前記光電変換素子の陰極及び前記負荷抵抗の他端は、高電位側電源線に接続され、

10

前記参照側トランジスタのソース電極及びドレイン電極の他方及び前記複数の出力生成回路のそれぞれの前記出力側トランジスタのソース電極及びドレイン電極の他方は、低電位側電源線に接続され、

前記複数の出力生成回路のそれぞれの前記出力側トランジスタのチャネル長Lとチャネル幅Wとの比 = W / L の値が、互いに異なる値であることを特徴とする光電変換装置。

### 【請求項3】

光電変換素子と、pチャネル型の電界効果トランジスタである第1の参照側トランジスタと、nチャネル型の電界効果トランジスタである第2の参照側トランジスタと、nチャネル型の電界効果トランジスタである第2の出力側トランジスタと、複数の出力生成回路と、負荷抵抗と、出力端子を有し、

20

前記複数の出力生成回路のそれぞれは、pチャネル型の電界効果トランジスタである第1の出力側トランジスタと、前記第1の出力側トランジスタのソース電極及びドレイン電極の一方で一端が接続されている内部抵抗を有し、

前記光電変換素子の陽極は、前記第2の参照側トランジスタのソース電極及びドレイン電極の一方、前記第2の参照側トランジスタのゲート電極及び前記第2の出力側トランジスタのゲート電極に接続され、

前記第2の出力側トランジスタのソース電極及びドレイン電極の一方は、前記第1の参照側トランジスタのソース電極及びドレイン電極の一方、前記第1の参照側トランジスタのゲート電極及び前記複数の出力生成回路のそれぞれの前記第1の出力側トランジスタのゲート電極に接続され、

30

前記複数の出力生成回路のそれぞれの前記内部抵抗の他端は、前記負荷抵抗の一端及び前記出力端子に接続され、

前記光電変換素子の陰極、前記第1の参照側トランジスタのソース電極及びドレイン電極の他方及び前記複数の出力生成回路のそれぞれの前記第1の出力側トランジスタのソース電極及びドレイン電極の他方は、高電位側電源線に接続され、

前記第2の参照側トランジスタのソース電極及びドレイン電極の他方、前記第2の出力側トランジスタのソース電極及びドレイン電極の他方及び前記負荷抵抗の他端は、低電位側電源線に接続され、

複数の前記出力生成回路のそれぞれの前記第1の出力側トランジスタのチャネル長Lとチャネル幅Wとの比 = W / L の値が、互いに異なる値であることを特徴とする光電変換装置。

40

### 【請求項4】

光電変換素子と、nチャネル型の電界効果トランジスタである第1の参照側トランジスタと、pチャネル型の電界効果トランジスタである第2の参照側トランジスタと、pチャネル型の電界効果トランジスタである第2の出力側トランジスタと、複数の出力生成回路と、負荷抵抗と、出力端子を有し、

前記複数の出力生成回路のそれぞれは、nチャネル型の電界効果トランジスタである第1の出力側トランジスタと、前記第1の出力側トランジスタのソース電極及びドレイン電極の一方で一端が接続されている内部抵抗を有し、

前記光電変換素子の陰極は、前記第2の参照側トランジスタのソース電極及びドレイン

50

電極の一方、前記第2の参照側トランジスタのゲート電極及び前記第2の出力側トランジスタのゲート電極に接続され、

前記第2の出力側トランジスタのソース電極及びドレイン電極の一方は、前記第1の参照側トランジスタのソース電極及びドレイン電極の一方、前記第1の参照側トランジスタのゲート電極及び前記複数の出力生成回路のそれぞれの前記第1の出力側トランジスタのゲート電極に接続され、

前記複数の出力生成回路のそれぞれの前記内部抵抗の他端は、前記負荷抵抗の一端及び前記出力端子に接続され、

前記光電変換素子の陽極、前記第1の参照側トランジスタのソース電極及びドレイン電極の他方及び前記複数の出力生成回路のそれぞれの前記第1の出力側トランジスタのソース電極及びドレイン電極の他方は、低電位側電源線に接続され、 10

前記第2の参照側トランジスタのソース電極及びドレイン電極の他方、前記第2の出力側トランジスタのソース電極及びドレイン電極の他方及び前記負荷抵抗の他端は、高電位側電源線に接続され、

複数の前記出力生成回路のそれぞれの前記第1の出力側トランジスタのチャネル長Lとチャネル幅Wとの比 = W / L の値が、互いに異なる値であることを特徴とする光電変換装置。

#### 【請求項5】

前記電界効果トランジスタが、薄膜トランジスタである請求項1乃至請求項4のいずれか一項に記載の光電変換装置。 20

#### 【請求項6】

前記光電変換素子及び前記電界効果トランジスタが、透光性基板上に設けられている請求項1乃至請求項5のいずれか一項に記載の光電変換装置。

#### 【請求項7】

請求項1乃至請求項6のいずれか一項に記載の光電変換装置を表示部に具備する電子機器。

#### 【発明の詳細な説明】

#### 【技術分野】

#### 【0001】

本発明は、光電変換装置に関し、特に薄膜半導体素子で構成された光電変換装置及びその光電変換装置を用いた電子機器に関する。 30

#### 【背景技術】

#### 【0002】

一般的に電磁波の検知用途に用いられる光電変換装置は数多く知られており、例えば紫外線から赤外線にかけて感度を有するものは総括して光センサと呼ばれている。その中でも波長 400 nm ~ 700 nm の可視光線領域に感度を持つものは特に可視光センサと呼ばれ、人間の生活環境に応じて照度調整や、オンまたはオフの制御などが必要な機器類に数多く用いられている。

#### 【0003】

表示装置では、表示装置の周囲の明るさを検出し、その表示輝度を調整することが行なわれているものもある。光センサにより、周囲の明るさを検出して適度な表示輝度を得ることによって、表示装置の無駄な電力を減らすことができるものである。例えば、輝度調整用の光センサを具備する表示装置としては、携帯電話、コンピュータが挙げられる。 40

#### 【0004】

また表示部周囲の明るさだけではなく、表示装置、特に液晶表示装置のバックライトの輝度を光センサにより検出し、表示画面の輝度を調節することも行われている。

#### 【0005】

光センサは、光のセンシング部分にフォトダイオードなどの光電変換素子を用い、光電変換素子の出力電流を增幅回路にて増幅している。光センサの増幅回路としては、例えばカレントミラー回路が用いられている（例えば特許文献1参照）。 50

【特許文献 1】特許第 3 4 4 4 0 9 3 号公報

【発明の開示】

【発明が解決しようとする課題】

【0006】

特許文献 1 に示した光センサは、光電流を増幅する回路を設けることにより微弱光の検出は行うことができる。しかしながら、微弱光から強光までを検出しようとすると、出力電流の範囲が広くなり、外部の負荷抵抗などで出力電流を電圧に変換する場合に、照度に対して線形に出力電圧も増加する。そのため、広い照度に対して出力電圧を得ようすると、照度あたりの出力電圧は、微弱光では数 mV、強光では数 V となり、ダイナミックレンジを広くとれないという課題があった。

10

【課題を解決するための手段】

【0007】

上述の課題を解決するために本発明の光電変換装置は、光電流を増幅するカレントミラーレンジを並列に用いることにより、使用可能な照度範囲を広げることを可能にしたものである。

【発明の効果】

【0008】

本発明の光電変換装置は、光電流を増幅するカレントミラーレンジを並列に用いることにより、複数のトランジスタを並列に用いることにより、使用可能な照度範囲を広げることを可能にしたものである。

20

【発明を実施するための最良の形態】

【0009】

以下に、本発明の実施の形態を図面に基づいて説明する。但し、本発明は多くの異なる様で実施することが可能であり、本発明の趣旨及びその範囲から逸脱することなくその形態及び詳細を様々に変更し得ることは当業者であれば容易に理解される。従って、本実施の形態の記載内容に限定して解釈されるものではない。なお、実施の形態を説明するための全図において、同一部分又は同様な機能を有する部分には同一の符号を付し、その繰り返しの説明は省略する。

30

【0010】

なお、トランジスタはその構造上、ソース電極とドレイン電極の区別が困難である。さらに、回路の動作によっては、電位の高低を入れ替わる場合もある。したがって、本明細書中では、ソースとドレインは特に特定せず、第 1 の電極、第 2 の電極と記述する。例えば、第 1 の電極がソース電極である場合には、第 2 の電極とはドレイン電極を指し、逆に第 1 の電極がドレイン電極である場合には、第 2 の電極とはソース電極を指すものとする。

40

【0011】

また、本明細書において、接続されているとは、電気的に接続されていることと同義である。したがって、本発明が開示する構成において、所定の接続関係に加え、その間に電気的な接続を可能とする他の素子（例えば、別の素子やスイッチなど）が配置されていてよい。

【0012】

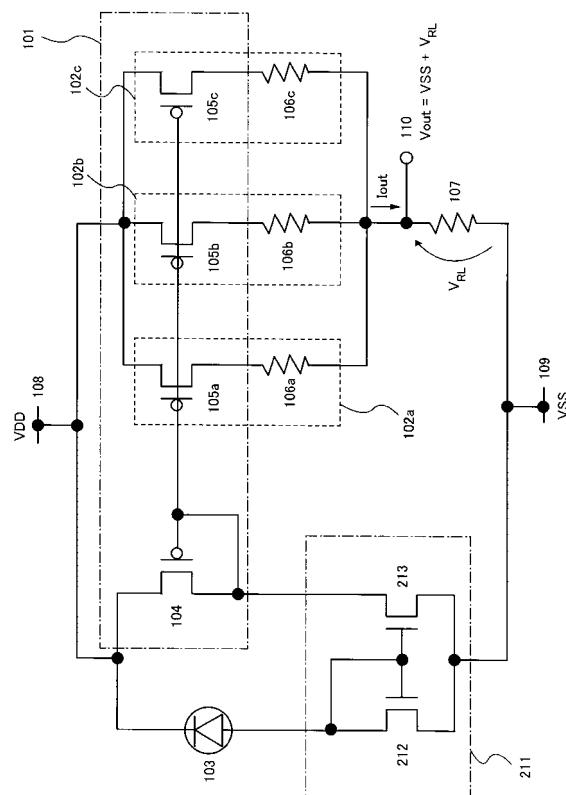

（実施の形態 1）

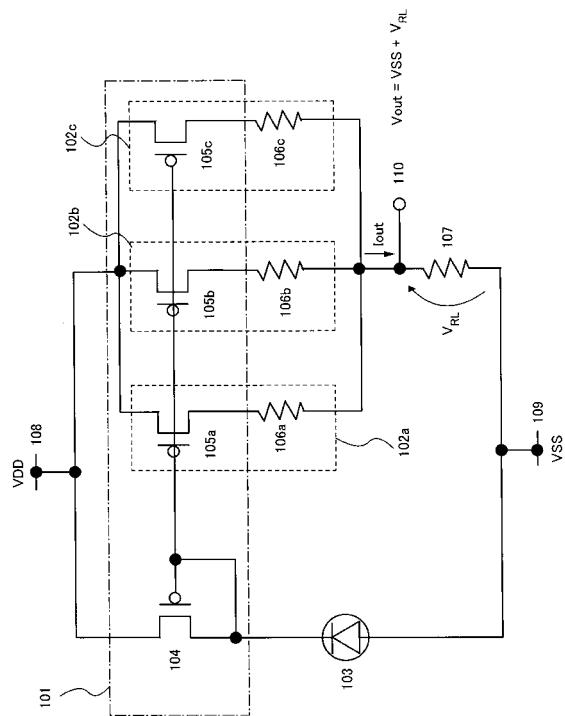

本実施の形態について図面を用いて説明する。図 1 は、本発明第 1 の実施の形態における光電変換装置の回路構成の一例を示す図である。

【0013】

本実施の形態の光電変換装置は、光電変換素子 103 と、光電変換素子 103 の出力電流

50

(光電流とも呼ぶ)を増幅する增幅回路であるカレントミラー回路101と、3個の内部抵抗106a～cと、負荷抵抗107と、高電位側電源線108と、低電位側電源線109と、出力端子110を有する。カレントミラー回路101は、参照側トランジスタ104及び3個の出力側トランジスタ105a～cを有している。

**【0014】**

なお、図1では、参照側トランジスタ104及び出力側トランジスタ105a～cは、ともにpチャネル型の電界効果型トランジスタである。

**【0015】**

なお、本明細書中では、高電位側の電源電位をVDD、低電位側の電源電位をVSSと記載する。

10

**【0016】**

図1において、参照側トランジスタ104は、第1の電極とゲート電極がダイオード接続されており、第1の電極は光電変換素子103の陰極に接続され、ゲート電極は3つの出力側トランジスタ105a～cそれぞれのゲート電極に接続され、第2の電極は高電位側電源線108に接続されている。

**【0017】**

出力側トランジスタ105aの第1の電極は内部抵抗106aの一端に接続され、第2の電極は高電位側電源線108に接続されている。内部抵抗106aの他端は負荷抵抗107の一端に接続されている。本明細書では、出力側トランジスタ105aと内部抵抗106aとが直列接続された構成の回路を、出力生成回路102aと呼ぶ。

20

**【0018】**

同様に、出力側トランジスタ105bの第1の電極は内部抵抗106bの一端に接続され、第2の電極は高電位側電源線108に接続されている。内部抵抗106bの他端は負荷抵抗107の一端に接続されている。本明細書では、出力側トランジスタ105bと内部抵抗106bとが直列接続された構成の回路を、出力生成回路102bと呼ぶ。

**【0019】**

同様に、出力側トランジスタ105cの第1の電極は内部抵抗106cの一端に接続され、第2の電極は高電位側電源線108に接続されている。内部抵抗106cの他端は負荷抵抗107の一端に接続されている。本明細書では、出力側トランジスタ105cと内部抵抗106cとが直列接続された構成の回路を、出力生成回路102cと呼ぶ。

30

**【0020】**

負荷抵抗107の一端は出力端子110と接続されており、光電変換素子103の陽極及び負荷抵抗107の他端は低電位側電源線109に接続されている。

**【0021】**

次に、本実施の形態の光電変換装置の動作について説明する。

**【0022】**

光電変換素子103では、光電変換素子103に入射される光の照度に応じた光電流が出力される。なお、照度が大きくなるにつれて、光電変換素子103から出力される光電流も大きくなる。光電変換素子103から出力された光電流が参照側トランジスタ104に流れることにより、参照側トランジスタ104のゲート・ソース間に電位差を生じさせる。その電位差が出力側トランジスタ105a～cのゲート・ソース間にも印加される。カレントミラー回路101においては、参照側トランジスタ104と出力側トランジスタ105a～cのゲート電極に同じ電圧を印加することで、参照側トランジスタ104に流れた光電流を基準として、出力側トランジスタ105a～cに流れる電流を制御する。

40

**【0023】**

出力側トランジスタ105a～cには、光電流に基づいた電流が流れる。これにより、出力生成回路102a～cで出力電流が生成される。出力生成回路102a～cの動作については後述する。複数の出力生成回路102a～cで生成された出力電流の総和が、負荷抵抗107に流れる。これにより、負荷抵抗107の端子間に電位差が発生する。当該電位差を $V_{RL}$ とし、出力電圧を $V_{out}$ と記述すると、出力端子110からは $V_{out} =$

50

$V_{RL} + VSS$  の電圧が出力される。

【0024】

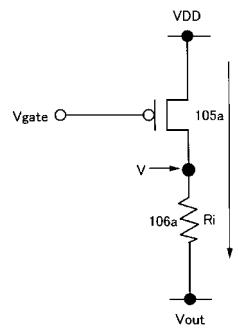

次に、出力生成回路 102a～c の動作について、図2、図3、図4を用いて説明する。

【0025】

図2は、出力生成回路102aの構成を示した図である。出力側トランジスタ105aと内部抵抗106aとが直列に接続されている。出力側トランジスタ105aのゲート電極には、光電流によって生じたゲート電圧が印加される。このゲート電圧を $V_{gate}$ と記述する。また、内部抵抗106aの第2の電極の電位は出力電位 $V_{out}$ となる。

【0026】

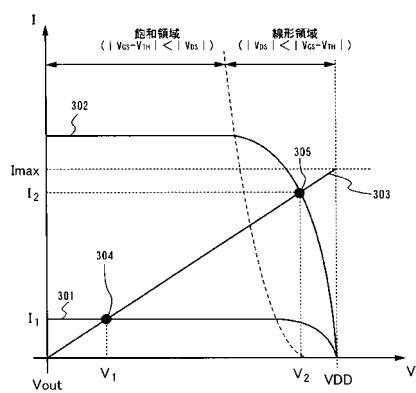

出力生成回路102aに流れる電流をI、出力側トランジスタ105aと内部抵抗106aとの接続部の電位をVとしたときの、出力側トランジスタ105a及び内部抵抗106aの電圧-電流特性を図3に示す。図3において縦軸が電流で横軸が電圧を表す。図3において、曲線301は光電変換素子に照度 $L_1$ （単位：ルクス）の光が照射された場合の出力側トランジスタ105aの電圧-電流特性を示し、曲線302は光電変換素子に照度 $L_2$ （ $L_1 < L_2$ ）の光が照射された場合の出力側トランジスタ105aの電圧-電流特性を示している。また、直線303は、内部抵抗106aの電圧-電流特性を示している。出力生成回路102aは、出力側トランジスタ105aの電圧-電流特性曲線と内部抵抗106aの電圧-電流特性直線の交点（これを動作点と呼ぶ）に対応した電圧V、電流Iで動作する。

【0027】

照度 $L_1$ の光が照射された場合、出力側トランジスタ105aは曲線301に示したような電圧-電流特性を有し、出力生成回路102aの動作点は曲線301と直線303の交点である点304となり、出力生成回路102aには電流 $I_1$ が流れる。

【0028】

このとき、出力側トランジスタ105aは飽和領域で駆動している。飽和領域とは、出力側トランジスタ105aのゲート・ソース間電圧を $V_{GS}$ 、ドレイン・ソース間電圧を $V_{DS}$ 、閾値電圧を $V_{TH}$ とすると、これらの電圧の大小関係が $|V_{GS} - V_{TH}| < |V_{DS}|$ を満たす領域である。この領域では、出力側トランジスタ105aには、出力側トランジスタ105aのゲート・ソース間電圧 $V_{GS}$ のみに依存した電流が流れる。そのため、出力生成回路102aには、照度に比例した電流が流れる。

【0029】

照度 $L_1$ よりも高い照度の光が照射された場合でも、出力側トランジスタ105aが飽和領域で駆動している照度範囲においては、出力生成回路102aには、照度に比例した電流が流れる。

【0030】

さらに照度が高くなり、照度 $L_2$ の光が照射された場合、出力側トランジスタ105aは、曲線302に示したような電圧-電流特性を有する。このとき、出力生成回路102aの動作点は点305となり、出力生成回路102aには電流 $I_2$ が流れる。

【0031】

このとき、出力側トランジスタ105aは線形領域で駆動している。線形領域とは、出力側トランジスタ105aのゲート・ソース間電圧 $V_{GS}$ 、ドレイン・ソース間電圧 $V_{DS}$ 、閾値電圧 $V_{TH}$ の大小関係が $|V_{GS} - V_{TH}| > |V_{DS}|$ を満たす領域である。この領域では、出力側トランジスタ105aには、出力側トランジスタ105aのゲート・ソース間電圧 $V_{GS}$ 及びドレイン・ソース間電圧 $V_{DS}$ に依存した電流が流れる。そのため、出力生成回路102aに流れる電流は照度に比例しなくなり、次第に $I_{max}$ に近づいていく。なお、 $I_{max}$ は、 $(VDD - V_{out}) / R_i$ で表される。ただし、 $R_i$ は内部抵抗106の抵抗値である。

【0032】

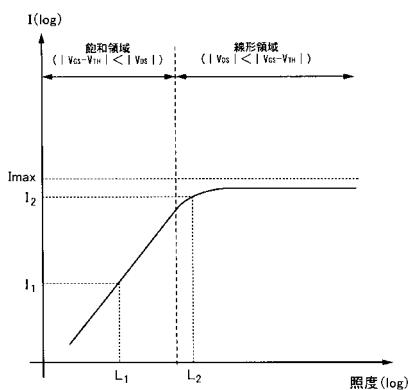

ここで、出力生成回路102aの照度-電流特性を図4に示す。図4において、横軸が照度、縦軸が出力生成回路102aに流れる電流であり、ともに対数目盛で表記している。

10

20

30

40

50

**【0033】**

上述の通り、出力側トランジスタ 105a が飽和領域で駆動している照度範囲（例えば、照度  $L_1$ ）においては、出力生成回路 102a には、照度に比例した電流が流れる。一方、出力側トランジスタ 105a が線形領域で駆動している照度範囲（例えば、照度  $L_2$ ）においては、出力生成回路 102a に流れる電流は照度に比例しなくなり、次第に  $I_{ma_x}$  に近づいていく。

**【0034】**

以上、出力生成回路 102a について説明したが、出力生成回路 102b 及び出力生成回路 102c についても同様に動作する。

**【0035】**

次に、再び本実施の形態の光電変換装置の動作について説明する。本実施の形態の光電変換装置は、上述したような動作を行う出力生成回路が複数個並列に接続されている。ここで、図 1 に示すような、3 個の出力生成回路 102a ~ 102c が並列に接続されている場合の回路動作について、説明する。

**【0036】**

3 個の出力生成回路 102a ~ 102c において、出力側トランジスタ 105a ~ 105c が有するチャネル長  $L$  とチャネル幅  $W$  との比  $= W / L$  の値を、それぞれ異なる値にする。例えば、第 1 の出力側トランジスタ 105a の  $= W / L$  を  $_1$ 、第 2 の出力側トランジスタ 105b の  $= W / L$  を  $_2$ 、第 3 の出力側トランジスタ 105c の  $= W / L$  を  $_3$  とし、の大小関係を  $_1 > _2 > _3$  とする。望ましくは、 $_1 / _2 = 10$  程度、 $_2 / _3 = 10$  程度となるように設定するとよい。

**【0037】**

なお、内部抵抗 106a ~ 106c の抵抗値は、説明の都合上、全て同じとする。なお、内部抵抗 106a ~ 106c の抵抗値はこれに限定されず、それぞれ異なる抵抗値を有してもよい。

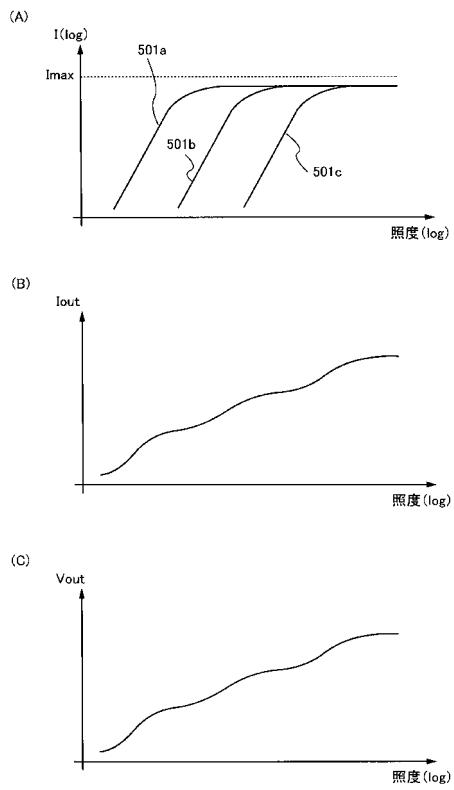

**【0038】**

このとき、図 1 に示した回路の回路動作について、図 5 に示す。図 5 (A) は、出力生成回路 102a ~ 102c の照度 - 電流特性を示している。図 5 (A) において、横軸が照度、縦軸が出力生成回路 102a ~ 102c のそれぞれに流れる電流であり、ともに対数目盛で表記している。

**【0039】**

なお、曲線 501a は第 1 の出力生成回路 102a の照度 - 電流特性、曲線 501b は第 2 の出力生成回路 102b の照度 - 電流特性、曲線 501c は第 3 の出力生成回路 102c の照度 - 電流特性をそれぞれ示している。

**【0040】**

出力生成回路 102a ~ c において、出力側トランジスタ 105a ~ c が内部抵抗 106a ~ c とそれぞれ直列に接続される構成となっているため、出力側トランジスタ 105a ~ c の  $= W / L$  が大きい程、より低い照度において出力側トランジスタ 105a ~ c を線形領域で駆動することができる。そのため、出力側トランジスタ 105a ~ c の  $= W / L$  が大きい程、より低い照度で出力生成回路 102a ~ c に流れる電流が頭打ちになる。

**【0041】**

出力生成回路 102a ~ 102c に流れる電流の総和が、本実施の形態の光電変換装置の出力電流となる（出力電流を  $I_{out}$  と記述する）。そして、この出力電流が負荷抵抗 107 に流れ、負荷抵抗 107 に生じた電位差と VSS の和を出力電圧  $V_{out}$  として出力する。

**【0042】**

ここで、出力生成回路 102a ~ 102c に流れる電流の総和（出力電流）を図 5 (B) に示す。また、出力電圧  $V_{out}$  を図 5 (C) に示す。なお、図 5 (B)、(C) において、横軸が照度であり、対数目盛で表記している。また、縦軸が出力電流もしくは出力電圧であり、線形目盛で表記している。

10

20

30

40

50

**【0043】**

出力電流  $I_{out}$  は、出力生成回路 602a ~ 602c に流れる電流の総和であるため、図 5 (B) に示したように、出力電流  $I_{out}$  は照度の対数に比例したような特性となる。また、出力電圧  $V_{out}$  も同様に照度の対数に比例したような特性となる。

**【0044】**

以上により、本実施の形態の光電変換装置では、照度の対数に比例したような出力を得ることが可能となり、光電変換装置として使用可能な照度範囲を広げることが可能となる。

**【0045】**

なお、図 1 に示した回路では、3 個の出力生成回路を並列に接続されていたが、出力生成回路の個数は、複数であればこれに限定されない。出力生成回路の個数を多くすることにより、光電変換装置として使用可能な照度範囲をより広げることができ、照度に対する出力の変化をより滑らかにすることが可能となる。10

**【0046】**

なお、負荷抵抗 607 は、光電変換装置に内製してもよいし、チップ抵抗などの外部抵抗を外付けしてもよい。負荷抵抗 607 を光電変換装置に内製することにより、外部抵抗が不要となるため、外部抵抗を接続する工程や部品点数を削減することができる。また、外部抵抗分の面積も不要となるため、電子機器などの光電変換部の面積を小さくすることができます。一方、負荷抵抗 607 を外付けにすることにより、負荷抵抗値のばらつき（特に温度に対する抵抗値のばらつき）の影響を低減することが可能となる。

**【0047】**

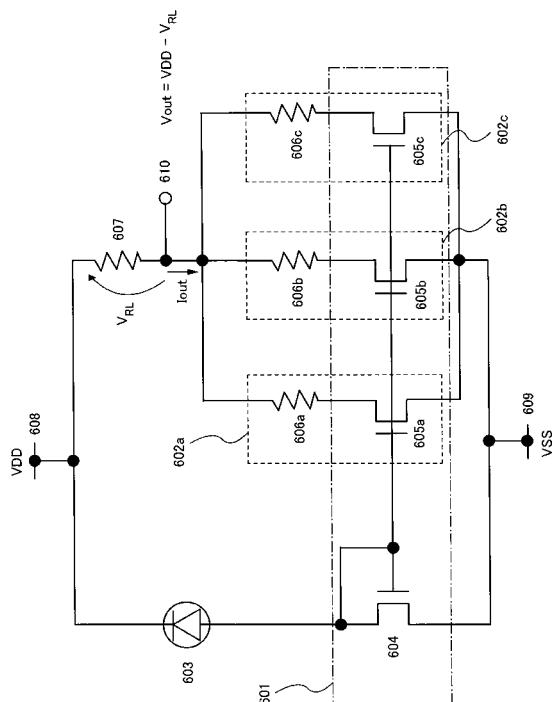

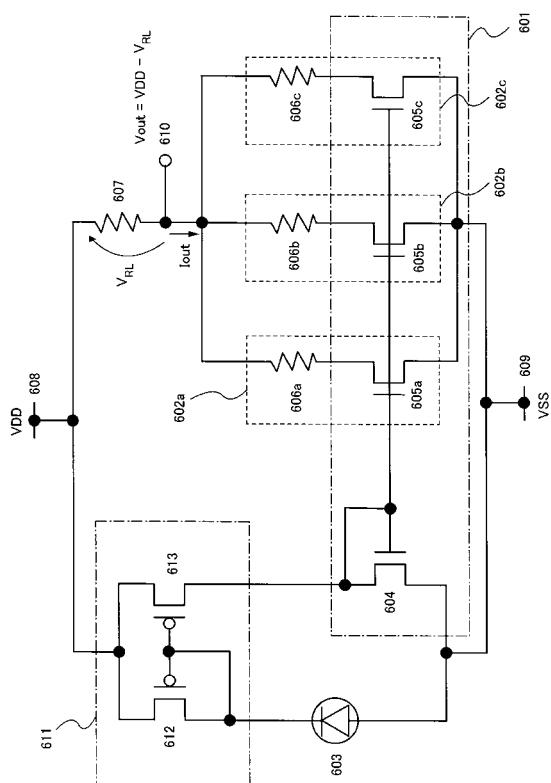

なお、図 1 に示した回路は、p チャネル型トランジスタで構成されていたが、n チャネル型トランジスタを用いて構成してもよい。n チャネル型トランジスタを用いた場合の回路構成を図 6 に示す。20

**【0048】**

図 6 に示す光電変換装置は、光電変換素子 603 と、光電変換素子 603 の出力電流（光電流とも呼ぶ）を增幅する增幅回路であるカレントミラー回路 601 と、3 個の内部抵抗 606a ~ c と、負荷抵抗 607 と、高電位側電源線 608 と、低電位側電源線 609 と、出力端子 610 を有する。カレントミラー回路 601 は、参照側トランジスタ 604 及び 3 個の出力側トランジスタ 605a ~ c を有している。

**【0049】**

なお、図 6 では、参照側トランジスタ 604 及び出力側トランジスタ 605a ~ c は、ともに n チャネル型の電界効果型トランジスタである。30

**【0050】**

なお、高電位側の電源電位を VDD、低電位側の電源電位を VSS と記載する。

**【0051】**

図 6 において、参照側トランジスタ 604 は、第 1 の電極とゲート電極がダイオード接続されており、第 1 の電極は光電変換素子 603 の陽極に接続され、ゲート電極は 3 つの出力側トランジスタ 605a ~ c それぞれのゲート電極に接続され、第 2 の電極は低電位側電源線 609 に接続されている。

**【0052】**

出力側トランジスタ 605a の第 1 の電極は内部抵抗 606a の一端に接続され、第 2 の電極は低電位側電源線 609 に接続されている。内部抵抗 606a の他端は負荷抵抗 607 の一端に接続されている。本明細書では、出力側トランジスタ 605a と内部抵抗 606a とが直列接続された構成の回路を、出力生成回路 602a と呼ぶ。40

**【0053】**

同様に、出力側トランジスタ 605b の第 1 の電極は内部抵抗 606b の一端に接続され、第 2 の電極は低電位側電源線 609 に接続されている。内部抵抗 606b の他端は負荷抵抗 607 の一端に接続されている。本明細書では、出力側トランジスタ 605b と内部抵抗 606b とが直列接続された構成の回路を、出力生成回路 602b と呼ぶ。

**【0054】**1020304050

同様に、出力側トランジスタ 605c の第 1 の電極は内部抵抗 606c の一端に接続され、第 2 の電極は低電位側電源線 609 に接続されている。内部抵抗 606c の他端は負荷抵抗 607 の一端に接続されている。本明細書では、出力側トランジスタ 605c と内部抵抗 606c とが直列接続された構成の回路を、出力生成回路 602c と呼ぶ。

#### 【0055】

負荷抵抗 607 の一端は出力端子 610 と接続されており、光電変換素子 603 の陰極及び負荷抵抗 607 の他端は高電位側電源線 608 に接続されている。

#### 【0056】

図 6 に示した回路は、基本的に図 1 に示した回路と同様の構成となっており、回路動作も基本的に図 1 にした回路と同様である。図 1 に示した回路と異なる点は、出力電圧  $V_{out}$  である。図 6 に示した回路の場合、負荷抵抗 607 の端子間に発生する電位差を  $V_{RL}$  とすると、出力端子 610 からは  $V_{out} = VDD - V_{RL}$  の電圧が出力される。

10

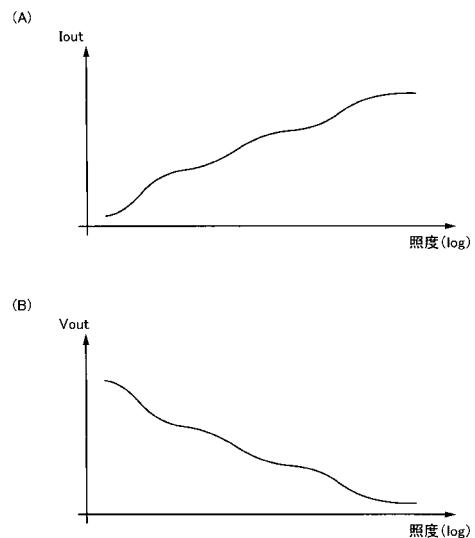

#### 【0057】

ここで、図 6 に示した回路の出力の照度特性を図 7 に示す。図 7 (A) は、出力電流  $I_{out}$  の照度特性を示し、縦軸が出力電流 (線形目盛) で横軸が照度 (対数目盛) である。図 7 (B) は、出力電圧  $V_{out}$  の照度特性を示し、縦軸が出力電圧 (線形目盛) で横軸が照度 (対数目盛) である。

#### 【0058】

図 1 に示した回路では、図 5 (C) に示したように、照度が高くなるにつれて出力電圧  $V_{out}$  も高くなる。一方、図 6 に示した回路では、照度が高くなるに連れて出力電圧  $V_{out}$  が低くなる。いずれにしても、出力電流  $I_{out}$  は照度の対数に比例したような特性となる。また、出力電圧  $V_{out}$  も同様に照度の対数に比例したような特性となる。

20

#### 【0059】

以上により、本実施の形態の光電変換装置では、照度の対数に比例したような出力を得ることが可能となり、光電変換装置として使用可能な照度範囲を広げることが可能となる。

#### 【0060】

なお、図 6 に示した回路では、3 個の出力生成回路を並列に接続されていたが、出力生成回路の個数は、複数であればこれに限定されない。出力生成回路の個数を多くすることにより、光電変換装置として使用可能な照度範囲をより広げることができ、照度に対する出力の変化をより滑らかにすることが可能となる。

30

#### 【0061】

なお、本実施の形態に示した光電変換装置は、n チャネル型もしくは p チャネル型の一方のトランジスタのみを用いて構成することが可能であるため、トランジスタの作製工程を削減することができ、コストを削減することができる。また、作製工程起因による回路特性のばらつきを低減させることができる。

#### 【0062】

なお、本実施の形態で説明した光電変換素子としては、通常のフォトダイオード等の光エネルギーを電気エネルギーに変換する素子を用いることができる。

#### 【0063】

なお、本実施の形態で説明した n チャネル型トランジスタ及び p チャネル型トランジスタとして、様々な形態の電界効果トランジスタを用いることが出来る。よって、用いるトランジスタの種類に限定はない。例えば、非晶質シリコン、多結晶シリコン、微結晶 (マイクロクリスタル、セミアモルファスとも言う) シリコンなどに代表される非単結晶半導体膜を有する薄膜トランジスタ (TFT) などを用いることが出来る。TFT を用いる場合、様々なメリットがある。例えば、単結晶シリコンの場合よりも低い温度で製造できるため、製造コストの削減、又は製造装置の大型化を図ることができる。製造装置を大きくできるため、大型基板上に製造できる。そのため、同時に多くの個数の光電変換装置を製造できるため、低コストで製造できる。さらに、製造温度が低いため、耐熱性の弱い基板を用いることができる。そのため、透光性基板上にトランジスタを製造できる。そして、透光性基板上のトランジスタを用いて光電変換素子での光の透過を制御することが出来る。

40

50

**【 0 0 6 4 】**

なお、多結晶シリコンを製造するときに、触媒（ニッケルなど）を用いることにより、結晶性をさらに向上させ、電気特性のよいトランジスタを製造することが可能となる。その結果、高速で動作させることが必要となる回路を基板上に一体に形成することが出来る。なお、微結晶シリコンを製造するときに、触媒（ニッケルなど）を用いることにより、結晶性をさらに向上させ、電気特性のよいトランジスタを製造することが可能となる。このとき、レーザを照射せずに、熱処理を加えるだけで、結晶性を向上させることができる。結晶化のためにレーザを用いない場合は、シリコンの結晶性のムラを抑えることができる。そのため、トランジスタ間の特性のばらつきを低減することができる。なお、触媒（ニッケルなど）を用いずに、多結晶シリコンや微結晶シリコンを製造することは可能である。

10

**【 0 0 6 5 】**

または、半導体基板やSOI基板などを用いてトランジスタを形成することが出来る。これらにより、特性やサイズや形状などのバラツキが少なく、電流供給能力が高く、サイズの小さいトランジスタを製造することができる。これらのトランジスタを用いると、回路の低消費電力化、又は回路の高集積化を図ることが出来る。

**【 0 0 6 6 】**

または、ZnO、a-InGaZnO、SiGe、GaAs、酸化インジウム酸化亜鉛（IZO）、インジウム錫酸化物（ITO）、SnOなどの化合物半導体または酸化物半導体を有するトランジスタや、さらに、これらの化合物半導体または酸化物半導体を薄膜化した薄膜トランジスタなどを用いることが出来る。これらにより、製造温度を低くでき、例えば、室温でトランジスタを製造することができる。その結果、耐熱性の低い基板、例えばプラスチック基板やフィルム基板に直接トランジスタを形成することが出来る。

20

**【 0 0 6 7 】**

または、インクジェットや印刷法を用いて形成したトランジスタなどを用いることが出来る。これらにより、室温で製造、低真密度で製造、又は大型基板上に製造することができる。また、マスク（レチクル）を用いなくても製造することができるため、トランジスタのレイアウトを容易に変更することができる。さらに、レジストを用いる必要がないので、材料費が安くなり、工程数を削減できる。さらに、必要な部分にのみ膜を付けるため、全面に成膜した後でエッチングする、という製法よりも、材料が無駄にならず、低コストにできる。

30

**【 0 0 6 8 】**

または、有機半導体やカーボンナノチューブを有するトランジスタ等を用いることができる。これらにより、曲げることが可能な基板上にトランジスタを形成することが出来る。そのため、衝撃に強くできる。

**【 0 0 6 9 】**

また、電界効果トランジスタは、様々なタイプを用いることができ、様々な基板上に形成させることができる。したがって、所定の機能を実現させるために必要な回路の全てが、同一の基板に形成されていてもよい。例えば、所定の機能を実現させるために必要な回路の全てが、ガラス基板、プラスチック基板、単結晶基板、またはSOI基板上に形成されていてもよく、さまざまな基板上に形成されていてもよい。なお本実施の形態の光電変換装置は、薄膜トランジスタを用いて電界効果トランジスタを構成することにより、ガラス基板等の透光性基板上に形成することが出来る。そのため、光電変換素子103又は603を基板上面に形成する場合に基板上面の片側からの光のみの受光に限らずに、基板の裏面から基板を透過した光を光電変換素子103又は603で受光することができるため、光の受光効率を高めることができるという効果がある。

40

**【 0 0 7 0 】**

なお本実施の形態は、本明細書の実施の形態の技術的要素と組み合わせて行うことができる。

**【 0 0 7 1 】**

50

(実施の形態 2 )

本実施の形態について図面を用いて説明する。図 2 1 は、本発明第 2 の実施の形態における光電変換装置の回路構成の一例を示す図である。

【 0 0 7 2 】

本実施の形態の光電変換装置は、光電変換素子 1 0 3 と、光電変換素子 1 0 3 の出力電流（光電流とも呼ぶ）を増幅する增幅回路である第 1 のカレントミラー回路 1 0 1 及び第 2 のカレントミラー回路 2 1 1 と、3 個の内部抵抗 1 0 6 a ~ c と、負荷抵抗 1 0 7 と、高電位側電源線 1 0 8 と、低電位側電源線 1 0 9 と、出力端子 1 1 0 を有する。第 1 のカレントミラー回路 1 0 1 は、第 1 の参照側トランジスタ 1 0 4 及び 3 個の第 1 の出力側トランジスタ 1 0 5 a ~ c を有している。第 2 のカレントミラー回路 2 1 1 は、第 2 の参照側トランジスタ 2 1 2 及び第 2 の出力側トランジスタ 2 1 3 を有している。

10

【 0 0 7 3 】

なお、図 2 1 において、第 1 の参照側トランジスタ 1 0 4 及び第 1 の出力側トランジスタ 1 0 5 a ~ c はすべて p チャネル型の電界効果型トランジスタであり、第 2 の参照側トランジスタ 2 1 2 及び第 2 の出力側トランジスタ 2 1 3 はともに n チャネル型の電界効果型トランジスタである。

【 0 0 7 4 】

なお、本明細書中では、高電位側の電源電位を V D D 、低電位側の電源電位を V S S と記載する。

【 0 0 7 5 】

図 2 1 において、第 2 の参照側トランジスタ 2 1 2 は、第 1 の電極とゲート電極がダイオード接続されており、第 1 の電極は光電変換素子 1 0 3 の陽極に接続され、ゲート電極は第 2 の出力側トランジスタ 2 1 3 のゲート電極に接続され、第 2 の電極は低電位側電源線 1 0 9 に接続されている。

20

【 0 0 7 6 】

第 2 の出力側トランジスタ 2 1 3 は、第 1 の電極が第 1 の参照側トランジスタ 1 0 4 の第 1 の電極に接続され、第 2 の電極が低電位側電源線 1 0 9 に接続されている。

【 0 0 7 7 】

第 1 の参照側トランジスタ 1 0 4 は、第 1 の電極とゲート電極がダイオード接続されており、ゲート電極は 3 つの第 1 の出力側トランジスタ 1 0 5 a ~ c それぞれのゲート電極に接続され、第 2 の電極は光電変換素子 1 0 3 の陰極及び高電位側電源線 1 0 8 に接続されている。

30

【 0 0 7 8 】

第 1 の出力側トランジスタ 1 0 5 a の第 1 の電極は内部抵抗 1 0 6 a の一端に接続され、第 2 の電極は高電位側電源線 1 0 8 に接続されている。内部抵抗 1 0 6 a の他端は負荷抵抗 1 0 7 の一端に接続されている。本明細書では、第 1 の出力側トランジスタ 1 0 5 a と内部抵抗 1 0 6 a とが直列接続された構成の回路を、出力生成回路 1 0 2 a と呼ぶ。

【 0 0 7 9 】

同様に、第 1 の出力側トランジスタ 1 0 5 b の第 1 の電極は内部抵抗 1 0 6 b の一端に接続され、第 2 の電極は高電位側電源線 1 0 8 に接続されている。内部抵抗 1 0 6 b の他端は負荷抵抗 1 0 7 の一端に接続されている。本明細書では、第 1 の出力側トランジスタ 1 0 5 b と内部抵抗 1 0 6 b とが直列接続された構成の回路を、出力生成回路 1 0 2 b と呼ぶ。

40

【 0 0 8 0 】

同様に、第 1 の出力側トランジスタ 1 0 5 c の第 1 の電極は内部抵抗 1 0 6 c の一端に接続され、第 2 の電極は高電位側電源線 1 0 8 に接続されている。内部抵抗 1 0 6 c の他端は負荷抵抗 1 0 7 の一端に接続されている。本明細書では、第 1 の出力側トランジスタ 1 0 5 c と内部抵抗 1 0 6 c とが直列接続された構成の回路を、出力生成回路 1 0 2 c と呼ぶ。

【 0 0 8 1 】

負荷抵抗 107 は、一端が出力端子 110 と接続されており、他端は低電位側電源線 109 に接続されている。

#### 【0082】

次に、本実施の形態の光電変換装置の動作について説明する。

#### 【0083】

光電変換素子 103 では、光電変換素子 103 に入射される光の照度に応じた光電流が10

出力される。なお、照度が大きくなるにつれて、光電変換素子 103 から出力される光電流も大きくなる。光電変換素子 103 から出力された光電流が第 2 の参照側トランジスタ 212 に流れることにより、第 2 の参照側トランジスタ 212 のゲート・ソース間に電位差を生じさせる。当該電位差が第 2 の出力側トランジスタ 213 のゲート・ソース間に印加される。第 2 のカレントミラー回路 211 において、第 2 の参照側トランジスタ 212 と第 2 の出力側トランジスタ 213 のゲート電極に同じ電圧を印加することで、第 2 の参照側トランジスタ 212 に流れた光電流を基準として、第 2 の出力側トランジスタ 213 に流れる電流を制御する。

#### 【0084】

上記のように第 2 の出力側トランジスタ 213 には、光電流に基づいた電流が流れる。この電流は、第 1 の参照側トランジスタ 104 にも流れる。このため、第 1 のカレントミラーリー回路 101 においても、第 2 のカレントミラー回路 211 と同様に、第 1 の参照側トランジスタ 104 と 3 つの第 1 の出力側トランジスタ 105a～c のゲート電極に同じ電圧が印加される。これにより、第 1 の参照側トランジスタ 104 に流れた光電流を基準として、第 1 の出力側トランジスタ 105a～c に流れる電流を制御する。

20

#### 【0085】

その結果、第 1 の出力側トランジスタ 105a～c にも光電流に基づいた電流が流れる。これにより、3 つの出力生成回路 102a～c で出力電流が生成される。出力生成回路 102a～c の動作については、後述する。3 つの出力生成回路 102a～c で生成された出力電流の総和が、負荷抵抗 107 に流れる。これにより、負荷抵抗 107 の端子間に電位差が発生する。当該電位差を  $V_{RL}$  とし、出力電圧を  $V_{out}$  と記述すると、出力端子 110 からは  $V_{out} = V_{RL} + VSS$  の電圧が出力される。

#### 【0086】

ここで、第 2 のカレントミラー回路 211 において、第 2 の参照側トランジスタ 212 と第 2 の出力側トランジスタ 213 の特性が同じであれば、光電流と同じ大きさの電流を第 1 のカレントミラー回路 101 の第 1 の参照側トランジスタ 104 に流すことができる。また、第 2 の参照側トランジスタ 212 及び第 2 の出力側トランジスタ 213 が有するチャネル長 L、チャネル幅 W の比  $= W / L$  の値を、それぞれ異なる値にすることにより、光電流を增幅することが可能である。例えば、第 2 の出力側トランジスタ 213 の  $W / L$  の値を変えるために、第 2 の出力側トランジスタ 213 のチャネル長 L 及びチャネル幅 W の大きさを変えてよいし、第 2 の出力側トランジスタ 213 の個数を増やして並列接続してもよい。

#### 【0087】

次に、出力生成回路 102a～c の動作について、図 2、図 3、図 4 を用いて説明する。

40

#### 【0088】

図 2 は、出力生成回路 102a の構成を示した図である。第 1 の出力側トランジスタ 105a と内部抵抗 106a とが直列に接続されている。第 1 の出力側トランジスタ 105a のゲート電極には、光電流によって生じたゲート電圧が印加される。このゲート電圧を  $V_{gate}$  と記述する。また、内部抵抗 106a の第 2 の電極の電位は出力電位  $V_{out}$  となる。

#### 【0089】

出力生成回路 102a に流れる電流を I、第 1 の出力側トランジスタ 105a と内部抵抗 106a との接続部の電位を V としたときの、第 1 の出力側トランジスタ 105a 及び内部抵抗 106a の電圧 - 電流特性を図 3 に示す。図 3 において縦軸が電流で横軸が電圧を

50

表す。図3において、曲線301は光電変換素子に照度 $L_1$ （単位：ルクス）の光が照射された場合の第1の出力側トランジスタ105aの電圧-電流特性を示し、曲線302は光電変換素子に照度 $L_2$ （ $L_1 < L_2$ ）の光が照射された場合の第1の出力側トランジスタ105aの電圧-電流特性を示している。また、直線303は、内部抵抗106aの電圧-電流特性を示している。出力生成回路102aは、第1の出力側トランジスタ105aの電圧-電流特性曲線と内部抵抗106aの電圧-電流特性直線の交点（これを動作点と呼ぶ）に対応した電圧V、電流Iで動作する。

#### 【0090】

照度 $L_1$ の光が照射された場合、第1の出力側トランジスタ105aは曲線301に示したような電圧-電流特性を有し、出力生成回路102aの動作点は曲線301と直線303の交点である点304となり、出力生成回路102aには電流 $I_1$ が流れる。

10

#### 【0091】

このとき、第1の出力側トランジスタ105aは飽和領域で駆動している。飽和領域とは、第1の出力側トランジスタ105aのゲート・ソース間電圧を $V_{GS}$ 、ドレイン・ソース間電圧を $V_{DS}$ 、閾値電圧を $V_{TH}$ とすると、これらの電圧の大小関係が $|V_{GS} - V_{TH}| < |V_{DS}|$ を満たす領域である。この領域では、第1の出力側トランジスタ105aには、第1の出力側トランジスタ105aのゲート・ソース間電圧 $V_{GS}$ のみに依存した電流が流れる。そのため、出力生成回路102aには、照度に比例した電流が流れる。

。

#### 【0092】

照度 $L_1$ よりも高い照度の光が照射された場合でも、第1の出力側トランジスタ105aが飽和領域で駆動している照度範囲においては、出力生成回路102aには、照度に比例した電流が流れる。

20

#### 【0093】

さらに照度が高くなり、照度 $L_2$ の光が照射された場合、第1の出力側トランジスタ105aは、曲線302に示したような電圧-電流特性を有する。このとき、出力生成回路102aの動作点は点305となり、出力生成回路102aには電流 $I_2$ が流れる。

#### 【0094】

このとき、第1の出力側トランジスタ105aは線形領域で駆動している。線形領域とは、第1の出力側トランジスタ105aのゲート・ソース間電圧 $V_{GS}$ 、ドレイン・ソース間電圧 $V_{DS}$ 、閾値電圧 $V_{TH}$ の大小関係が $|V_{GS} - V_{TH}| > |V_{DS}|$ を満たす領域である。この領域では、第1の出力側トランジスタ105aには、第1の出力側トランジスタ105aのゲート・ソース間電圧 $V_{GS}$ 及びドレイン・ソース間電圧 $V_{DS}$ に依存した電流が流れる。そのため、出力生成回路102aに流れる電流は照度に比例しなくなり、次第に $I_{max}$ に近づいていく。なお、 $I_{max}$ は、 $(VDD - Vout) / R_i$ で表される。ただし、 $R_i$ は内部抵抗106の抵抗値である。

30

#### 【0095】

ここで、出力生成回路102aの照度-電流特性を図4に示す。図4において、横軸が照度、縦軸が出力生成回路102aに流れる電流であり、ともに対数目盛で表記している。

#### 【0096】

上述の通り、第1の出力側トランジスタ105aが飽和領域で駆動している照度範囲（例えば、照度 $L_1$ ）においては、出力生成回路102aには、照度に比例した電流が流れる。一方、第1の出力側トランジスタ105aが線形領域で駆動している照度範囲（例えば、照度 $L_2$ ）においては、出力生成回路102aに流れる電流は照度に比例しなくなり、次第に $I_{max}$ に近づいていく。

40

#### 【0097】

以上、出力生成回路102aについて説明したが、出力生成回路102b及び出力生成回路102cについても同様に動作する。

#### 【0098】

次に、再び本実施の形態の光電変換装置の動作について説明する。本実施の形態の光電変

50

換装置は、上述で説明したような動作を行う出力生成回路が複数個並列に接続されている。ここで、図21に示すような、3個の出力生成回路102a～102cが並列に接続されている場合の回路動作について、説明する。

#### 【0099】

3個の出力生成回路102a～102cにおいて、第1の出力側トランジスタ105a～105cが有するチャネル長Lとチャネル幅Wとの比 $= W/L$ の値を、それぞれ異なる値にする。例えば、第1の出力側トランジスタ105aの $\square_1$ を $\square_1$ 、第1の出力側トランジスタ105bの $\square_2$ を $\square_2$ 、第1の出力側トランジスタ105cの $\square_3$ を $\square_3$ とし、 $\square$ の大小関係を $\square_1 > \square_2 > \square_3$ とする。望ましくは、 $\square_1 / \square_2 = 10$ 程度、 $\square_2 / \square_3 = 10$ 程度となるように設定するとよい。

10

#### 【0100】

なお、内部抵抗106a～106cの抵抗値は、説明の都合上、全て同じとする。なお、内部抵抗106a～106cの抵抗値はこれに限定されず、それぞれ異なる抵抗値を有してもよい。

#### 【0101】

このとき、図21に示した回路の回路動作について、図5に示す。図5(A)は、出力生成回路102a～102cの照度-電流特性を示している。図5(A)において、横軸が照度、縦軸が出力生成回路102a～102cのそれぞれに流れる電流であり、ともに対数目盛で表記している。

#### 【0102】

なお、曲線501aは第1の出力生成回路102aの照度-電流特性、曲線501bは第2の出力生成回路102bの照度-電流特性、曲線501cは第3の出力生成回路102cの照度-電流特性をそれぞれ示している。

20

#### 【0103】

出力生成回路102a～cにおいて、出力側トランジスタ105a～105cが内部抵抗106a～106cとそれぞれ直列に接続される構造となっているため、第1の出力側トランジスタ105a～cの $\square$ が大きい程、より低い照度において第1の出力側トランジスタ105a～cを線形領域で駆動することができる。そのため、第1の出力側トランジスタ105a～cの $\square$ が大きい程、より低い照度で出力生成回路102a～cに流れる電流が頭打ちになる。

30

#### 【0104】

出力生成回路102a～102cに流れる電流の総和が、本実施の形態の光電変換装置の出力電流となる(出力電流を $I_{out}$ と記述する)。そして、この出力電流が負荷抵抗107に流れ、負荷抵抗107に生じた電位差とVSSの和を出力電圧 $V_{out}$ として出力する。

#### 【0105】

出力生成回路102a～102cに流れる電流の総和(出力電流)を図5(B)に示す。また、出力電圧 $V_{out}$ を図5(C)に示す。なお、図5(B)、(C)において、横軸が照度であり、対数目盛で表記している。また、縦軸が出力電流もしくは出力電圧であり、線形目盛で表記している。

40

#### 【0106】

出力電流 $I_{out}$ は、出力生成回路102a～102cに流れる電流の総和であるため、図5(B)に示したように、出力電流 $I_{out}$ は照度の対数に比例したような特性となる。また、出力電圧 $V_{out}$ も同様に照度の対数に比例したような特性となる。

#### 【0107】

以上により、本実施の形態の光電変換装置では、照度の対数に比例したような出力を得ることが可能となり、光電変換装置として使用可能な照度範囲を広げることが可能となる。

#### 【0108】

また、第2のカレントミラー回路211を設けることにより、光電流を増幅した電流を第1のカレントミラー回路101に入力することができる。これにより、第1の参照側ト

50

ンジスタ 104 及び第 1 の出力側トランジスタ 105a ~ c のゲート電圧を所望の電圧にするまでに必要な時間を短くすることができる。したがって、照度が変化した場合に、出力が所望の値に到達するまでにかかる時間を短くすることができ、照度が変化した場合でも出力の応答速度が速い光電変換装置を実現することが可能となる。

#### 【0109】

なお、図 21 に示した回路では、3 個の出力生成回路を並列に接続されていたが、出力生成回路の個数は、複数であればこれに限定されない。出力生成回路の個数を多くすることにより、光電変換装置として使用可能な照度範囲をより広げることができ、照度に対する出力の変化をより滑らかにすることが可能となる。

#### 【0110】

なお、負荷抵抗 107 は、光電変換装置に内製してもよいし、チップ抵抗などの外部抵抗を外付けしてもよい。負荷抵抗 107 を光電変換装置に内製することにより、外部抵抗が不要となるため、外部抵抗を接続する工程や部品点数を削減することができる。また、外部抵抗分の面積も不要となるため、電子機器などの光電変換部の面積を小さくすることができます。一方、負荷抵抗 107 を外付けにすることにより、負荷抵抗値のばらつき（特に温度に対する抵抗値のばらつき）の影響を低減することが可能となる。

#### 【0111】

なお、図 21 に示した回路では、第 2 の参照側トランジスタ 212 及び第 2 の出力側トランジスタ 213 が n チャネル型トランジスタで構成され、第 1 の参照側トランジスタ 104 及び第 1 の出力側トランジスタ 105a ~ c が p チャネル型トランジスタで構成されて 10 いたが、逆の構成でも良い。逆の場合の回路構成を図 22 に示す。

#### 【0112】

図 22 に示す光電変換装置は、光電変換素子 603 と、光電変換素子 603 の出力電流（光電流とも呼ぶ）を增幅する增幅回路である第 1 のカレントミラー回路 601 及び第 2 のカレントミラー回路 611 と、3 個の内部抵抗 606a ~ c と、負荷抵抗 607 と、高電位側電源線 608 と、低電位側電源線 609 と、出力端子 610 を有する。第 1 のカレントミラー回路 601 は、第 1 の参照側トランジスタ 604 及び 3 個の第 1 の出力側トランジスタ 605a ~ c を有している。第 2 のカレントミラー回路 611 は、第 2 の参照側トランジスタ 612 及び第 2 の出力側トランジスタ 613 を有している。

#### 【0113】

なお、図 22 において、第 1 の参照側トランジスタ 604 及び第 1 の出力側トランジスタ 605a ~ c はすべて n チャネル型の電界効果型トランジスタであり、第 2 の参照側トランジスタ 612 及び第 2 の出力側トランジスタ 613 はともに p チャネル型の電界効果型トランジスタである。

#### 【0114】

なお、高電位側の電源電位を VDD、低電位側の電源電位を VSS と記載する。

#### 【0115】

図 22 において、第 2 の参照側トランジスタ 612 は、第 1 の電極とゲート電極がダイオード接続されており、第 1 の電極は光電変換素子 603 の陰極に接続され、ゲート電極は第 2 の出力側トランジスタ 613 のゲート電極に接続され、第 2 の電極は高電位側電源線 608 に接続されている。

#### 【0116】

第 2 の出力側トランジスタ 613 は、第 1 の電極が第 1 の参照側トランジスタ 604 の第 1 の電極に接続され、第 2 の電極が高電位側電源線 608 に接続されている。

#### 【0117】

第 1 の参照側トランジスタ 604 は、第 1 の電極とゲート電極がダイオード接続されており、ゲート電極は 3 つの第 1 の出力側トランジスタ 605a ~ c それぞれのゲート電極に接続され、第 2 の電極は光電変換素子 603 の陽極及び低電位側電源線 609 に接続されている。

#### 【0118】

10

20

30

40

50

第1の出力側トランジスタ605aの第1の電極は内部抵抗606aの一端に接続され、第2の電極は低電位側電源線609に接続されている。内部抵抗606aの他端は負荷抵抗607の一端に接続されている。本明細書では、第1の出力側トランジスタ605aと内部抵抗606aとが直列接続された構成の回路を、出力生成回路602aと呼ぶ。

#### 【0119】

同様に、第1の出力側トランジスタ605bの第1の電極は内部抵抗606bの一端に接続され、第2の電極は低電位側電源線609に接続されている。内部抵抗606bの他端は負荷抵抗607の一端に接続されている。本明細書では、第1の出力側トランジスタ605bと内部抵抗606bとが直列接続された構成の回路を、出力生成回路602bと呼ぶ。

10

#### 【0120】

同様に、第1の出力側トランジスタ605cの第1の電極は内部抵抗606cの一端に接続され、第2の電極は低電位側電源線609に接続されている。内部抵抗606cの他端は負荷抵抗607の一端に接続されている。本明細書では、第1の出力側トランジスタ605cと内部抵抗606cとが直列接続された構成の回路を、出力生成回路602cと呼ぶ。

#### 【0121】

負荷抵抗607は、一端が出力端子610と接続されており、他端は高電位側電源線608に接続されている。

#### 【0122】

図22に示した回路は、基本的に図21に示した回路と同様の構成となっており、回路動作も基本的に図21にした回路と同様である。図21に示した回路と異なる点は、出力電圧 $V_{out}$ である。図22に示した回路の場合、負荷抵抗607の端子間に発生する電位差を $V_{RL}$ とすると、出力端子610からは $V_{out} = VDD - V_{RL}$ の電圧が出力される。

20

#### 【0123】

ここで、図22に示した回路の出力の照度特性を図7に示す。図7(A)は、出力電流 $I_{out}$ の照度特性を示し、縦軸が出力電流(線形目盛)で横軸が照度(対数目盛)である。図7(B)は、出力電圧 $V_{out}$ の照度特性を示し、縦軸が出力電圧(線形目盛)で横軸が照度(対数目盛)である。

30

#### 【0124】

図21に示した回路では、図5(C)に示したように、照度が高くなるにつれて出力電圧 $V_{out}$ も高くなる。一方、図22に示した回路では、照度が高くなるに連れて出力電圧 $V_{out}$ が低くなる。いずれにしても、出力電流 $I_{out}$ は照度の対数に比例したような特性となる。また、出力電圧 $V_{out}$ も同様に照度の対数に比例したような特性となる。

#### 【0125】

以上により、本実施の形態の光電変換装置では、照度の対数に比例したような出力を得ることが可能となり、光電変換装置として使用可能な照度範囲を広げることが可能となる。

#### 【0126】

なお、図22に示した回路では、3個の出力生成回路を並列に接続されていたが、出力生成回路の個数は、複数であればこれに限定されない。出力生成回路の個数を多くすることにより、光電変換装置として使用可能な照度範囲をより広げることができ、照度に対する出力の変化をより滑らかにすることが可能となる。

40

#### 【0127】

なお、本実施形態に示した光電変換装置は、Nチャネル型及びPチャネル型の両方のトランジスタを用いて構成されているため、トランジスタの特性ばらつきに起因した回路特性のばらつきを低減させることができる。

#### 【0128】

なお、本実施の形態で説明した光電変換素子としては、通常のフォトダイオード等の光エネルギーを電気エネルギーに変換する素子を用いることができる。

50

## 【0129】

なお、本実施の形態で説明したnチャネル型トランジスタ及びpチャネル型トランジスタとして、様々な形態の電界効果トランジスタを用いることが出来る。よって、用いるトランジスタの種類に限定はない。例えば、非晶質シリコン、多結晶シリコン、微結晶（マイクロクリスタル、セミアモルファスとも言う）シリコンなどに代表される非単結晶半導体膜を有する薄膜トランジスタ（TFT）などを用いることが出来る。TFTを用いる場合、様々なメリットがある。例えば、単結晶シリコンの場合よりも低い温度で製造できるため、製造コストの削減、又は製造装置の大型化を図ることができる。製造装置を大きくできるため、大型基板上に製造できる。そのため、同時に多くの個数の光電変換装置を製造できるため、低コストで製造できる。さらに、製造温度が低いため、耐熱性の弱い基板を用いることができる。そのため、透光性基板上にトランジスタを製造できる。そして、透光性基板上のトランジスタを用いて光電変換素子での光の透過を制御することが出来る。

10

## 【0130】

なお、多結晶シリコンを製造するときに、触媒（ニッケルなど）を用いることにより、結晶性をさらに向上させ、電気特性のよいトランジスタを製造することが可能となる。その結果、高速で動作させることが必要となる回路を基板上に一体に形成することが出来る。なお、微結晶シリコンを製造するときに、触媒（ニッケルなど）を用いることにより、結晶性をさらに向上させ、電気特性のよいトランジスタを製造することが可能となる。このとき、レーザを照射せずに、熱処理を加えるだけで、結晶性を向上させることができる。結晶化のためにレーザを用いない場合は、シリコンの結晶性のムラを抑えることができる。そのため、トランジスタ間の特性のばらつきを低減することができる。なお、触媒（ニッケルなど）を用いずに、多結晶シリコンや微結晶シリコンを製造することは可能である。

20

## 【0131】

または、半導体基板やSOI基板などを用いてトランジスタを形成することが出来る。これらにより、特性やサイズや形状などのバラツキが少なく、電流供給能力が高く、サイズの小さいトランジスタを製造することができる。これらのトランジスタを用いると、回路の低消費電力化、又は回路の高集積化を図ることが出来る。

## 【0132】

または、ZnO、a-InGaZnO、SiGe、GaAs、酸化インジウム酸化亜鉛（IZO）、インジウム錫酸化物（ITO）、SnOなどの化合物半導体または酸化物半導体を有するトランジスタや、さらに、これらの化合物半導体または酸化物半導体を薄膜化した薄膜トランジスタなどを用いることが出来る。これらにより、製造温度を低くでき、例えば、室温でトランジスタを製造することが可能となる。その結果、耐熱性の低い基板、例えばプラスチック基板やフィルム基板に直接トランジスタを形成することが出来る。

30

## 【0133】

または、インクジェットや印刷法を用いて形成したトランジスタなどを用いることが出来る。これらにより、室温で製造、低真空間度で製造、又は大型基板上に製造することができる。また、マスク（レチクル）を用いなくても製造することが可能となるため、トランジスタのレイアウトを容易に変更することができる。さらに、レジストを用いる必要がないので、材料費が安くなり、工程数を削減できる。さらに、必要な部分にのみ膜を付けるため、全面に成膜した後でエッチングする、という製法よりも、材料が無駄にならず、低コストにできる。

40

## 【0134】

または、有機半導体やカーボンナノチューブを有するトランジスタ等を用いることができる。これらにより、曲げることが可能な基板上にトランジスタを形成することが出来る。そのため、衝撃に強くできる。

## 【0135】

また、電界効果トランジスタは、様々なタイプを用いることができ、様々な基板上に形成させることができる。したがって、所定の機能を実現させるために必要な回路の全てが、

50

同一の基板に形成されていてもよい。例えば、所定の機能を実現させるために必要な回路の全てが、ガラス基板、プラスチック基板、単結晶基板、またはS O I 基板上に形成されていてもよく、さまざまな基板上に形成されていてもよい。なお本実施の形態の光電変換装置は、薄膜トランジスタを用いて電界効果トランジスタを構成することにより、ガラス基板等の透光性基板上に形成することが出来る。そのため、光電変換素子103又は603を基板上面に形成する場合に基板上面の片側からの光のみの受光に限らずに、基板の裏面から基板を透過した光を光電変換素子103又は603で受光することが可能になるため、光の受光効率を高めることができるという効果がある。

#### 【0136】

なお本実施の形態は、本明細書の実施の形態の技術的要素と組み合わせて行うことができる。10

#### (実施の形態3)

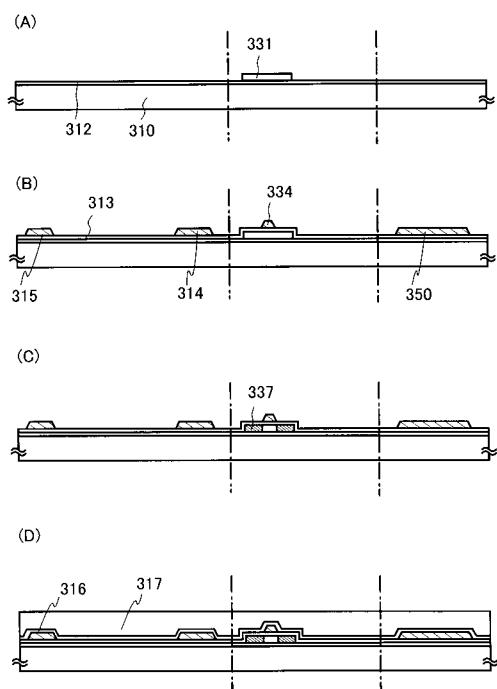

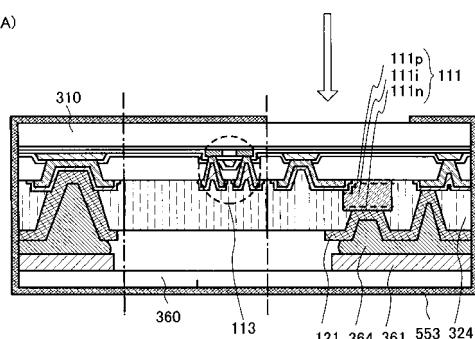

#### 【0137】

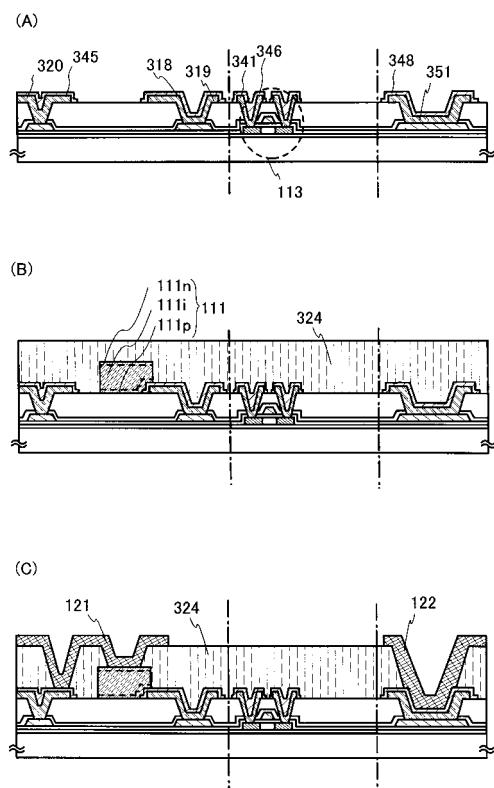

本実施の形態では、上記実施の形態で述べた光電変換回路の作製方法について、一例として、断面図を用いて述べる。図8(A)～図8(D)、及び図9(A)～図9(C)を用いて説明する。

#### 【0138】

まず、基板(第1の基板310)上に光電変換素子及び電界効果トランジスタを形成する。ここでは基板310として、ガラス基板の一つであるAN100を用いる。基板上に形成する電界効果トランジスタとしては、薄膜トランジスタを用いることにより、基板上に、光電変換素子と薄膜トランジスタを連続工程で作製することができるため、光電変換装置の量産化がしやすいといった利点がある。20

#### 【0139】

プラズマCVD法で下地絶縁膜312となる窒素を含む酸化珪素膜(膜厚100nm)を形成し、さらに大気にふれることなく、半導体膜例えば水素を含む非晶質珪素膜(膜厚54nm)を積層形成する。また、下地絶縁膜312は酸化珪素膜、窒化珪素膜、窒素を含む酸化珪素膜を用いて積層してもよい。例えば、下地絶縁膜312として、酸素を含む窒化珪素膜を50nm、さらに窒素を含む酸化珪素膜を100nm積層した膜を形成してもよい。なお、窒素を含む酸化珪素膜や窒化珪素膜は、ガラス基板からのアルカリ金属などの不純物拡散を防止するプロッキング層として機能する。30

#### 【0140】

次いで、上記非晶質珪素膜を公知の技術(固相成長法、レーザ結晶化方法、触媒金属を用いた結晶化方法など)により結晶化させて、結晶構造を有する半導体膜(結晶性半導体膜)、例えば多結晶珪素膜を形成する。ここでは、触媒元素を用いた結晶化方法を用いて多結晶珪素膜を得る。重量換算で10ppmのニッケルを含む酢酸ニッケル溶液をスピナーで添加する。なお、溶液を添加する方法に代えてスパッタ法でニッケル元素を全面に散布する方法を用いてもよい。次いで、加熱処理を行い結晶化させて結晶構造を有する半導体膜(ここでは多結晶珪素膜)を形成する。ここでは熱処理(500、1時間)の後、結晶化のための熱処理(550、4時間)を行って多結晶珪素膜を得る。

#### 【0141】

次いで、多結晶珪素膜表面の酸化膜を希フッ酸等で除去する。その後、結晶化率を高め、結晶粒内に残される欠陥を補修するためのレーザ光(XeCl:波長308nm)の照射を大気中、または酸素雰囲気中で行う。40

#### 【0142】

レーザ光には波長400nm以下のエキシマレーザ光や、YAGレーザの第2高調波又は第3高調波を用いる。ここでは、繰り返し周波数10～1000Hz程度のパルスレーザ光を用い、当該レーザ光を光学系にて100～500mJ/cm<sup>2</sup>に集光し、90～95%のオーバーラップ率をもって照射し、シリコン膜表面を走査させればよい。本実施の形態では、繰り返し周波数30Hz、エネルギー密度470mJ/cm<sup>2</sup>でレーザ光の照射を大気中で行なう。50

**【0143】**

なお、大気中、または酸素雰囲気中で行うため、レーザ光の照射により表面に酸化膜が形成される。なお、本実施の形態ではパルスレーザを用いた例を示したが、連続発振のレーザを用いてもよく、半導体膜の結晶化に際し、大粒径に結晶を得るためには、連続発振が可能な固体レーザを用い、基本波の第2高調波～第4高調波を適用するのが好ましい。代表的には、Nd:YVO<sub>4</sub>レーザ（基本波1064nm）の第2高調波（532nm）や第3高調波（355nm）を適用すればよい。

**【0144】**

連続発振のレーザを用いる場合には、出力10Wの連続発振のYVO<sub>4</sub>レーザから射出されたレーザ光を非線形光学素子により高調波に変換する。また、共振器の中にYVO<sub>4</sub>結晶と非線形光学素子を入れて、高調波を射出する方法もある。そして、好ましくは光学系により照射面にて矩形状または橜円形状のレーザ光に成形して、被処理体に照射する。このときのエネルギー密度は0.01～100MW/cm<sup>2</sup>程度（好ましくは0.1～10MW/cm<sup>2</sup>）が必要である。そして、10～2000cm/s程度の速度でレーザ光に対して相対的に半導体膜を移動させて照射すればよい。

10

**【0145】**

次いで、上記レーザ光の照射により形成された酸化膜に加え、オゾン水で表面を120秒処理して合計1～5nmの酸化膜からなるバリア層を形成する。このバリア層は、結晶化させるために添加した触媒元素、例えばニッケル（Ni）を膜中から除去するために形成する。ここではオゾン水を用いてバリア層を形成したが、酸素雰囲気下の紫外線の照射で結晶構造を有する半導体膜の表面を酸化する方法や酸素プラズマ処理により結晶構造を有する半導体膜の表面を酸化する方法やプラズマCVD法やスパッタ法や蒸着法などで1～10nm程度の酸化膜を堆積してバリア層を形成してもよい。また、バリア層を形成する前にレーザ光の照射により形成された酸化膜を除去してもよい。

20

**【0146】**

次いで、バリア層上にスパッタ法にてゲッタリングサイトとなるアルゴン元素を含む非晶質珪素膜を10nm～400nm、ここでは膜厚100nmで成膜する。ここでは、アルゴン元素を含む非晶質珪素膜は、シリコンターゲットを用いてアルゴンを含む雰囲気下で形成する。プラズマCVD法を用いてアルゴン元素を含む非晶質珪素膜を形成する場合、成膜条件は、モノシリコンとアルゴンの流量比（SiH<sub>4</sub>:Ar）を1:99とし、成膜圧力を6.665Paとし、RFパワー密度を0.087W/cm<sup>2</sup>とし、成膜温度を350とする。

30

**【0147】**

その後、650に加熱された炉に入れて3分の熱処理を行い触媒元素を除去（ゲッタリング）する。これにより結晶構造を有する半導体膜中の触媒元素濃度が低減される。炉に代えてランプアニール装置を用いてもよい。

**【0148】**

次いで、バリア層をエッチングストップとして、ゲッタリングサイトであるアルゴン元素を含む非晶質珪素膜を選択的に除去した後、バリア層を希フッ酸で選択的に除去する。なお、ゲッタリングの際、ニッケルは酸素濃度の高い領域に移動しやすい傾向があるため、酸化膜からなるバリア層をゲッタリング後に除去することが望ましい。

40

**【0149】**

なお、触媒元素を用いて半導体膜の結晶化を行わない場合には、上述したバリア層の形成、ゲッタリングサイトの形成、ゲッタリングのための熱処理、ゲッタリングサイトの除去、バリア層の除去などの工程は不要である。

**【0150】**

次いで、得られた結晶構造を有する半導体膜（例えば結晶性珪素膜）の表面にオゾン水で薄い酸化膜を形成した後、第1のフォトマスクを用いてレジストからなるマスクを形成し、所望の形状にエッチング処理して島状に分離された半導体膜（本明細書では「島状半導体領域331」という）を形成する（図8(A)参照）。島状半導体領域を形成した後、

50

レジストからなるマスクを除去する。

**【0151】**

次いで、必要があればTFTのしきい値を制御するために微量な不純物元素（ホウ素またはリン）のドーピングを行う。ここでは、ジボラン（B<sub>2</sub>H<sub>6</sub>）を質量分離しないでプラズマ励起したイオンドープ法を用いる。

**【0152】**

次いで、フッ酸を含むエッチャントで酸化膜を除去すると同時に島状半導体領域331の表面を洗浄した後、ゲート絶縁膜313となる珪素を主成分とする絶縁膜を形成する。ここでは、プラズマCVD法により115nmの厚さで窒素を含む酸化珪素膜（組成比Si = 32%、O = 59%、N = 7%、H = 2%）で形成する。

10

**【0153】**

次いで、ゲート絶縁膜313上に金属膜を形成した後、第2のフォトマスクを用いて、ゲート電極334、配線314、配線315、端子電極350を形成する（図8（B）参照）。この金属膜として、例えば窒化タンタル及びタングステン（W）をそれぞれ30nm、370nm積層した膜を用いる。

**【0154】**

また、ゲート電極334、配線314、配線315、端子電極350として、上記以外にもチタン（Ti）、タングステン（W）、タンタル（Ta）、モリブデン（Mo）、ネオジム（Nd）、コバルト（Co）、ジルコニウム（Zr）、亜鉛（Zn）、ルテニウム（Ru）、ロジウム（Rh）、パラジウム（Pd）、オスミウム（Os）、イリジウム（Ir）、白金（Pt）、アルミニウム（Al）、金（Au）、銀（Ag）、銅（Cu）から選ばれた元素、または前記元素を主成分とする合金材料若しくは化合物材料からなる単層膜、或いは、これらの窒化物、例えば、窒化チタン、窒化タングステン、窒化タンタル、窒化モリブデンからなる単層膜を用いることができる。

20

**【0155】**

次いで、島状半導体領域331への一導電型を付与する不純物の導入を行って、TFT113のソース領域又はドレイン領域337の形成を行う（図8（C）参照）。本実施の形態ではnチャネル型TFTを形成するので、n型の不純物、例えばリン（P）、砒素（As）を島状半導体領域331に導入する。

30

**【0156】**

次いで、CVD法により酸化珪素膜を含む第1の層間絶縁膜（図示しない）を50nm形成した後、それぞれの島状半導体領域に添加された不純物元素を活性化処理する工程を行う。この活性化工程は、ランプ光源を用いたラピッドサーマルアニール法（RTA法）、或いはYAGレーザまたはエキシマレーザを裏面から照射する方法、或いは炉を用いた熱処理、或いはこれらの方法のうち、いずれかと組み合わせた方法によって行う。

**【0157】**

次いで、水素及び酸素を含む窒化珪素膜を含む第2の層間絶縁膜316を、例えば10nmの膜厚で形成する。

**【0158】**

次いで、第2の層間絶縁膜316上に絶縁物材料から成る第3の層間絶縁膜317を形成する（図8（D）参照）。第3の層間絶縁膜317はCVD法で得られる絶縁膜を用いることができる。本実施の形態においては密着性を向上させるため、第3の層間絶縁膜317として、900nmの膜厚で形成した窒素を含む酸化珪素膜を形成する。

40

**【0159】**

次に、熱処理（300～550℃で1～12時間の熱処理、例えば窒素雰囲気中410℃で1時間）を行い、島状半導体領域331を水素化する。この工程は第2の層間絶縁膜316に含まれる水素により島状半導体領域331のダンギングボンドを終端させるために行うものである。ゲート絶縁膜313の存在に関係なく島状半導体領域331を水素化することができる。

**【0160】**

50

また第3の層間絶縁膜317として、シロキサンを用いた絶縁膜、及びそれらの積層構造を用いることも可能である。シロキサンは、シリコン(Si)と酸素(O)との結合で骨格構造で構成される。置換基として、少なくとも水素を含む有機基(例えばアルキル基、芳香族炭化水素)が用いられる。有機基として、フッ素を含む。

#### 【0161】

第3の層間絶縁膜317としてシロキサンを用いた絶縁膜、及びそれらの積層構造を用いた場合は、第2の層間絶縁膜316を形成後、島状半導体領域331を水素化するための熱処理を行い、次に第3の層間絶縁膜317を形成することもできる。

#### 【0162】

次いで、第3のフォトマスクを用いてレジストからなるマスクを形成し、第1の層間絶縁膜、第2の層間絶縁膜316及び第3の層間絶縁膜317およびゲート絶縁膜313を選択的にエッチングしてコンタクトホールを形成する。そして、レジストからなるマスクを除去する。

#### 【0163】

なお、第3の層間絶縁膜317は必要に応じて形成すればよく、第3の層間絶縁膜317を形成しない場合は、第2の層間絶縁膜316を形成後に第1の層間絶縁膜、第2の層間絶縁膜316及びゲート絶縁膜313を選択的にエッチングしてコンタクトホールを形成する。

#### 【0164】

次いで、スパッタ法で金属積層膜を成膜した後、第4のフォトマスクを用いてレジストからなるマスクを形成し、選択的に金属膜をエッチングして、配線319、接続電極320、端子電極351、TFT113のソース電極又はドレイン電極341を形成する。そして、レジストからなるマスクを除去する。なお、本実施の形態の金属膜は、膜厚100nmのTi膜と、膜厚350nmのSiを微量に含むAl膜と、膜厚100nmのTi膜との3層を積層したものとする。

#### 【0165】

また配線319、接続電極320、端子電極351、及びTFT113のソース電極又はドレイン電極341を単層の導電膜により形成する場合は、耐熱性及び導電率等の点からチタン膜(Ti膜)が好ましい。またチタン膜に変えて、タンゲステン(W)、タンタル(Ta)、モリブデン(Mo)、ネオジム(Nd)、コバルト(Co)、ジルコニウム(Zr)、亜鉛(Zn)、ルテニウム(Ru)、ロジウム(Rh)、パラジウム(Pd)、オスミウム(Os)、イリジウム(Ir)、白金(Pl)から選ばれた元素、または前記元素を主成分とする合金材料若しくは化合物材料からなる単層膜、或いは、これらの窒化物、例えば、窒化チタン、窒化タンゲステン、窒化タンタル、窒化モリブデンからなる単層膜を用いることができる。配線319、接続電極320、端子電極351、及びTFT113のソース電極又はドレイン電極341を単層膜にすることにより、作製工程において成膜回数を減少させることができる。

#### 【0166】

以上の工程で、多結晶硅素膜を用いたトップゲート型TFT113を作製することができる。

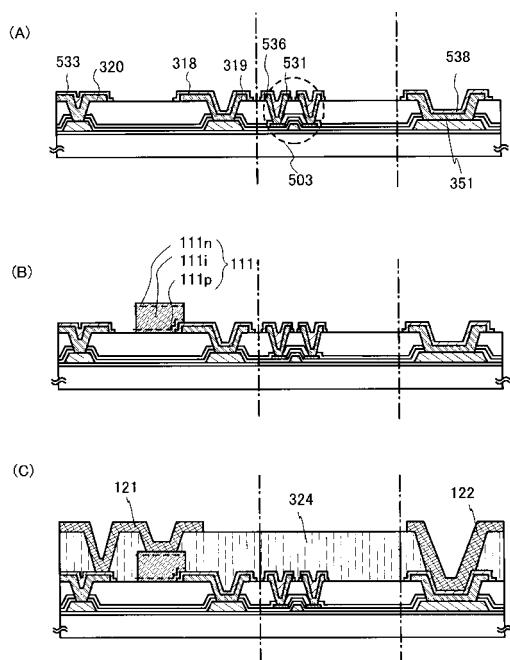

#### 【0167】

次いで、後に形成される光電変換層(代表的にはアモルファスシリコン)と反応して合金になりにくい導電性の金属膜(チタン(Ti)またはモリブデン(Mo)など)を成膜した後、第5のフォトマスクを用いてレジストからなるマスクを形成する。選択的に導電性の金属膜をエッチングして配線319を覆う保護電極318を形成する(図9(A))。ここではスパッタ法で得られる膜厚200nmのTi膜を用いる。なお、同様に接続電極320、端子電極351、TFT113のソース電極又はドレイン電極341も導電性の金属膜である保護電極345、346、348に覆われる。従って、導電性の金属膜は、これらの電極における2層目のAl膜が露呈されている側面も覆い、導電性の金属膜は光電変換層へのアルミニウム原子の拡散も防止できる。

10

20

30

40

50

## 【0168】

ただし、配線319、接続電極320、端子電極351、及びTFT113のソース電極又はドレイン電極341を、単層の導電膜で形成する場合、保護電極318、保護電極345、保護電極346、及び保護電極348は形成しなくてもよい。

## 【0169】

次に第3の層間絶縁膜317上に、p型半導体層111p、i型半導体層111i及びn型半導体層111nを含む光電変換層111を形成する。

## 【0170】

p型半導体層111pは、周期表第13属の不純物元素、例えばホウ素(B)を含んだセミアモルファスシリコン膜をプラズマCVD法にて成膜して形成すればよい。 10

## 【0171】

また配線319及び保護電極318は光電変換層111の最下層、本実施の形態ではp型半導体層111pと接している。

## 【0172】

p型半導体層111pを形成したら、さらにi型半導体層111i及びn型半導体層111nを順に形成する。これによりp型半導体層111p、i型半導体層111i及びn型半導体層111nを有する光電変換層111が形成される。

## 【0173】

i型半導体層111iとしては、例えばプラズマCVD法でセミアモルファスシリコン膜を形成すればよい。またn型半導体層111nとしては、周期表第15属の不純物元素、例えばリン(P)を含むセミアモルファスシリコン膜を形成してもよいし、セミアモルファスシリコン膜を形成後、周期表第15属の不純物元素を導入してもよい。 20

## 【0174】

またp型半導体層111p、i型半導体層111i、n型半導体層111nとして、セミアモルファス半導体膜だけではなく、アモルファス半導体膜を用いてもよい。

## 【0175】

次いで、全面に絶縁物材料(例えば珪素を含む無機絶縁膜)からなる封止層324を厚さ1μm~30μmで形成して図9(B)の状態を得る。ここでは絶縁物材料膜としてCVD法により、膜厚1μmの窒素を含む酸化珪素膜を形成する。CVD法による絶縁膜を用いることによって密着性の向上を図っている。 30

## 【0176】

次いで、封止層324をエッティングして開口部を設けた後、スパッタ法により端子電極121及び122を形成する。端子電極121及び122は、チタン膜(Ti膜)(100nm)と、ニッケル膜(Ni膜)(300nm)と、金膜(Au膜)(50nm)との積層膜とする。こうして得られる端子電極121及び端子電極122の固着強度は5Nを超える、端子電極として十分な固着強度を有している。

## 【0177】

以上の工程で、半田接続が可能な端子電極121及び端子電極122が形成され、図9(C)に示す構造が得られる。

## 【0178】

なお上記工程で得られる光電変換回路は、基板より個々に切断して複数の光電変換回路素子を切り出すことで大量生産が可能である。1枚の大面積基板(例えば600cm×720cm)からは大量の光電変換回路素子(例えば2mm×1.5mm)を製造することができる。

## 【0179】

なお、本実施の形態で示す島状半導体領域331の作製方法としては、上記作製方法に限らず他の作製方法を用いて形成することもできる。一例としては、SOI(シリコン・オン・インシュレータ)基板を用いて島状半導体領域331を形成してもよい。SOI基板としては、公知のSOI基板を用いればよく、その作製方法や構造は特に限定されない。SOI基板としては、代表的にはSIMOX基板や貼り合わせ基板が挙げられる。また、 50

貼り合わせ基板の例として、ELTRAN（登録商標）、UNIBOND（登録商標）、スマートカット（登録商標）等が挙げられる。

#### 【0180】

SIMOX基板は、単結晶シリコン基板に酸素イオンを注入し、1300以上で熱処理して埋め込み酸化膜層（BOX；Buried Oxide）を形成することにより、表面に薄膜シリコン層を形成し、SOI構造を得ることができる。薄膜シリコン層は、埋め込み酸化膜層により、単結晶シリコン基板と絶縁分離されている。また、埋め込み酸化膜層形成後に、さらに熱酸化するITOX（Internal Thermal Oxidation）と呼ばれる技術を用いることもできる。

#### 【0181】

貼り合わせ基板は、酸化膜層を介して2枚の単結晶シリコン基板（第1単結晶シリコン基板、第2単結晶シリコン基板）を貼り合わせ、一方の単結晶シリコン基板を貼り合わせた面ではない方の面から薄膜化することにより、表面に薄膜シリコン層を形成したSOI基板のことをいう。酸化膜層は、一方の基板（ここでは第1単結晶シリコン基板）を熱酸化して形成することができる。また、2枚の単結晶シリコン基板は、接着剤なしで直接貼り合わせることができる。

#### 【0182】

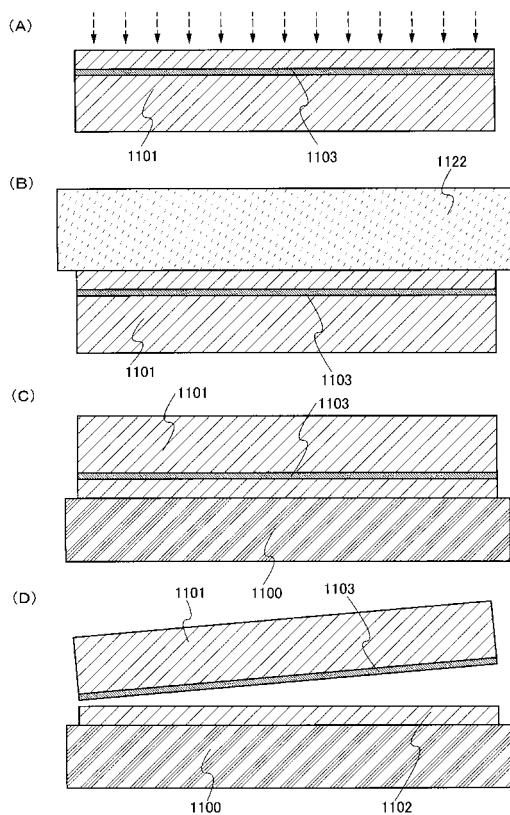

なお、貼り合わせ基板としては、2枚の単結晶半導体基板を貼り合わせることに限らず、ガラス基板や可撓性を有し且つ絶縁表面を有する基板等と、単結晶半導体基板とを貼り合わせてSOI基板を作製してもよい。ガラス基板と単結晶半導体基板との貼り合わせSOI基板について、図10(A)乃至図10(D)を説明する。

#### 【0183】

図10(A)に示す単結晶半導体基板1101は清浄化されており、その表面から電界で加速されたイオンを所定の深さに添加し、脆化層1103を形成する。イオンの添加はベース基板に転置する半導体膜の厚さを考慮して行われる。当該半導体膜の厚さは5nm乃至500nm、好ましくは10nm乃至200nm、更に好ましくは10nm乃至100nm、更に好ましくは10nm乃至50nmの厚さとする。イオンを添加する際の加速電圧はこのような厚さを考慮して、単結晶半導体基板1101に添加されるようとする。なお、分離後に半導体膜の表面を研磨または溶融して平坦化するため、分離直後の半導体膜の厚さは50nm乃至500nmとしておくことが好ましい。

#### 【0184】

脆化層1103は、水素、ヘリウム若しくはフッ素に代表されるハロゲンのイオンを添加することで形成される。この場合、一又は複数の同一の原子から成る質量数の異なるイオンを添加することが好ましい。水素イオンを添加する場合には、H<sup>+</sup>、H<sub>2</sub><sup>+</sup>、H<sub>3</sub><sup>+</sup>イオンを含ませると共に、H<sub>3</sub><sup>+</sup>イオンの割合を高めておくことが好ましい。水素イオンを添加する場合には、H<sup>+</sup>、H<sub>2</sub><sup>+</sup>、H<sub>3</sub><sup>+</sup>イオンを含ませると共に、H<sub>3</sub><sup>+</sup>イオンの割合を高めておくと添加効率を高めることができ、添加時間を短縮することができる。このような構成とすることで、後に行われる脆化層1103での分離を容易に行うことができる。

#### 【0185】

単結晶半導体基板1101にイオンを添加する場合、イオンを高ドーズ条件で添加する必要があり、このため単結晶半導体基板1101の表面が粗くなってしまう場合がある。そのためイオンが添加される表面に、酸化珪素層、窒化珪素層、若しくは窒化酸化珪素層などによりイオン添加に対する保護層を50nm乃至200nmの厚さで設けておいくことで、イオンドーピングによって表面がダメージを受け、平坦性が損なわれるのを防ぐことができるため好ましい。

#### 【0186】

次に、図10(B)に示すように、単結晶半導体基板1101の表面に圧着部材1122を設け、単結晶半導体基板1101及び圧着部材1122を密着させ加熱し、即ち加熱処理及び加圧処理を行うことで、後の工程で脆化層1103を劈開面として単結晶半導体基

10

20

30

40

50

板 1101 をガラス基板 1100 から分離することを容易とする。加熱処理の温度は、脆化層 1103 が劈開する温度未満であり、且つ脆化層 1103 が脆弱となる温度であることが好ましい。例えば、400 未満、好ましくは 350 未満、更に好ましくは 300

未満の熱処理を行うことにより、脆化層 1103 に形成された微小な空洞の体積変化が起こるが、単結晶半導体基板表面には圧着部材 1122 が設けられているため、単結晶半導体基板の表面は平坦性を保つことができる。この結果、脆化層 1103 の微小な空洞の体積変化により、脆化層 1103 に歪みが生じ、脆化層に沿って脆弱化することが可能となる。加圧処理においては、ガラス基板 1100 及び単結晶半導体基板 1101 の耐圧性を考慮して接合面に垂直な方向に圧力が加わるように行う。

#### 【0187】

10

図 10 (C) に示すように、ガラス基板 1100 と単結晶半導体基板 1101 とを密接させ、この両者を接合させる態様を示す。接合を行う面は、十分に清浄化しておく。そして、ガラス基板 1100 及び単結晶半導体基板 1101 を加圧しながら密着させることにより、ガラス基板 1100 及び単結晶半導体基板 1101 が接合する。この接合はファン・デル・ワールス力が作用しており、ガラス基板 1100 と単結晶半導体基板 1101 とを圧接することで水素結合により強固な接合を行うことが可能である。

#### 【0188】

20

良好な接合を行うために、表面を活性化することが好ましい。例えば、接合を行う面に原子ビーム若しくはイオンビームを照射する。原子ビーム若しくはイオンビームを利用する場合には、アルゴン等の不活性ガス中性原子ビーム若しくは不活性ガスイオンビームを用いることができる。その他に、プラズマ照射若しくはラジカル処理を行う。また、ガラス基板、または単結晶半導体層の少なくとも一方の接合面を、酸素プラズマによる処理や、オゾン水洗浄により、親水化してもよい。このような表面処理により 400 未満の温度であっても異種材料間の接合を行うことが容易となる。

#### 【0189】

30

なお、ガラス基板 1100 及び単結晶半導体基板 1101 の接合の前に行った加熱処理の代わりに、ガラス基板 1100 及び単結晶半導体基板 1101 を接合した後、ガラス基板 1100 側からレーザビームを単結晶半導体基板に照射し、脆化層 1103 を加熱してもよい。この結果、脆化層が脆弱化し、当該脆化層を劈開面として単結晶半導体基板 1101 をガラス基板 1100 から分離することができる。

#### 【0190】

図 10 (D) に示すように、ガラス基板 1100 と単結晶半導体基板 1101 を貼り合わせた後、脆化層 1103 を劈開面として単結晶半導体基板 1101 をガラス基板 1100 から分離することで、SOI 基板を得ることができる。単結晶半導体基板 1101 の表面はガラス基板 1100 と接合しているので、ガラス基板 1100 上には単結晶半導体基板 1101 と同じ結晶性の半導体膜 1102 が残存することとなる。

#### 【0191】

40

脆化層 1103 を劈開面として単結晶半導体基板 1101 をガラス基板 1100 から分離する前に、分離を容易に行うためにきっかけをつくることが好ましい。具体的には、脆化層 1103 及び半導体膜 1102 の密着性を選択的(部分的)に低下させる前処理を行うことで、分離不良が少くなり、さらに歩留まりも向上する。代表的には、ガラス基板 1100 または単結晶半導体基板 1101 から脆化層 1103 にレーザビームまたはダイサード溝を形成する例がある。

#### 【0192】

また、単結晶半導体基板 1101 をガラス基板 1100 から分離する際、ガラス基板 1100 または単結晶半導体基板 1101 の少なくとも一方の表面に光または熱により分離可能な粘着シートを設け、ガラス基板 1100 または単結晶半導体基板 1101 の一方を固定し、他方を引き剥がすことで、さらに分離が容易となる。このとき、ガラス基板 1100 または単結晶半導体基板 1101 の他方に支持部材を設けることで引き剥がし工程が容易となる。

50

## 【0193】

なお、分離により得られる半導体膜は、その表面を平坦化するため、化学的機械的研磨 (Chemical Mechanical Polishing : CMP) を行うことが好ましい。また、CMP等の物理的研磨手段を用いず、半導体膜の表面にレーザビームを照射して平坦化を行ってもよい。なお、レーザビームを照射する際は、酸素濃度が10 ppm以下の中性雰囲気下で行なうことが好ましい。これは、酸素雰囲気下でレーザビームの照射を行うと半導体膜表面が荒れる恐れがあるからである。また、得られた半導体膜の薄層化を目的として、CMP等を行ってもよい。

## 【0194】

以上が、ガラス基板等の絶縁表面を有する基板と、単結晶半導体基板とを貼り合わせてSOI基板を作製する方法に関する説明である。

10

## 【0195】

また、本実施の形態で示す島状半導体領域331としては、上記のような多結晶半導体膜又は単結晶半導体膜に限らず微結晶半導体膜を適用することもできる。

## 【0196】

微結晶半導体膜は、非晶質と結晶構造（単結晶、多結晶を含む）の中間的な構造の半導体を含む膜である。この半導体は、自由エネルギー的に安定な第3の状態を有する半導体であって、短距離秩序を持ち格子歪みを有する結晶質なものであり、その粒径を0.5~20 nmとして非晶質半導体中に分散させて存在せしめることが可能である。微結晶半導体の代表例である微結晶シリコンは、そのラマンスペクトルが単結晶シリコンを示す521 cm<sup>-1</sup>よりも低波数側に、シフトしている。即ち、481 cm<sup>-1</sup>以上520 cm<sup>-1</sup>以下の間に微結晶シリコンのラマンスペクトルのピークがある。また、未結合手（ダングリングボンド）を終端するため水素またはハロゲンを少なくとも1原子%またはそれ以上含ませている。さらに、ヘリウム、アルゴン、クリプトン、ネオンなどの希ガス元素を含ませて格子歪みをさらに助長させることで、安定性が増し良好な微結晶半導体膜が得られる。このような微結晶半導体膜に関する記述は、例えば、米国特許4,409,134号で開示されている。

20

## 【0197】

この微結晶半導体膜は、周波数が数十MHz~数百MHzの高周波プラズマCVD法、または周波数が1GHz以上のマイクロ波プラズマCVD装置により形成することができる。代表的には、SiH<sub>4</sub>、Si<sub>2</sub>H<sub>6</sub>、SiH<sub>2</sub>Cl<sub>2</sub>、SiHCl<sub>3</sub>、SiCl<sub>4</sub>、SiF<sub>4</sub>などの水素化珪素を水素で希釈して形成することができる。また、水素化珪素及び水素に加え、ヘリウム、アルゴン、クリプトン、ネオンから選ばれた一種または複数種の希ガス元素で希釈して微結晶半導体膜を形成することができる。これらのときの水素化珪素に対して水素の流量比を5倍以上200倍以下、好ましくは50倍以上150倍以下、更に好ましくは100倍とする。

30

## 【0198】

また、微結晶半導体膜は、価電子制御を目的とした不純物元素を意図的に添加しないときに弱いn型の電気伝導性を示すので、薄膜トランジスタのチャネル形成領域として機能する微結晶半導体膜に対しては、p型を付与する不純物元素を、成膜と同時に、或いは成膜後に添加することで、しきい値制御をすることが可能となる。p型を付与する不純物元素としては、代表的には硼素であり、B<sub>2</sub>H<sub>6</sub>、BF<sub>3</sub>などの不純物気体を1ppm~1000ppm、好ましくは1~100ppmの割合で水素化珪素に混入させると良い。そしてボロンの濃度を、例えば $1 \times 10^{-4}$ ~ $6 \times 10^{-6}$  atoms/cm<sup>3</sup>とすると良い。

40

## 【0199】

また、微結晶半導体膜の酸素濃度を、 $5 \times 10^{-8}$  cm<sup>-3</sup>以下、好ましくは $1 \times 10^{-8}$  cm<sup>-3</sup>以下とするとよい。また、窒素及び炭素の濃度それぞれを $1 \times 10^{-9}$  cm<sup>-3</sup>以下とすることが好ましい。酸素、窒素、及び炭素が微結晶半導体膜に混入する濃度を低減することで、微結晶半導体膜がn型化になることを防止することができる。

50

**【 0 2 0 0 】**

微結晶半導体膜による島状半導体領域331は、0 nmより厚く50 nm以下、好ましくは0 nmより厚く20 nm以下で形成する。微結晶半導体膜は後に形成される薄膜トランジスタのチャネル形成領域として機能する。微結晶半導体膜の厚さを上記の範囲内とすることで、後に形成される薄膜トランジスタは、完全空乏型となる。また、微結晶半導体膜は微結晶で構成されているため、非晶質半導体膜と比較して抵抗が低い。このため、微結晶半導体膜を用いた薄膜トランジスタは、電流電圧特性を示す曲線の立ち上がり部分の傾きが急峻となり、スイッチング素子としての応答性が優れ、高速動作が可能となる。また、薄膜トランジスタのチャネル形成領域に微結晶半導体膜を用いることで、薄膜トランジスタの閾値の変動を抑制することが可能である。このため、電気特性のばらつきの少ない液晶表示装置等を作製することができる。10

**【 0 2 0 1 】**

また、微結晶半導体膜は非晶質半導体膜と比較して移動度が高い。このため、表示素子のスイッチングとして、チャネル形成領域が微結晶半導体膜で形成される薄膜トランジスタを用いることで、チャネル形成領域の面積、即ち薄膜トランジスタの面積を縮小することが可能である。このため、一画素あたりに示す薄膜トランジスタの面積が小さくなり、画素の開口率を高めることができることである。この結果、解像度の高い装置を作製することができる。

**【 0 2 0 2 】**

なお本実施の形態は、本明細書の実施の形態の技術的要素と組み合わせて行うことができる。20

**( 実施の形態 4 )****【 0 2 0 3 】**

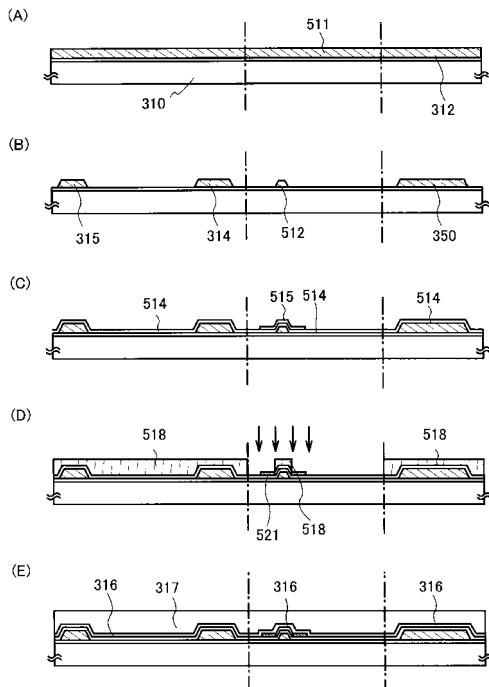

本実施の形態では、上記実施の形態で述べた光電変換回路の作製方法について、実施の形態2とは異なる例として、断面図を用いて述べる。本実施の形態では電界効果トランジスタをボトムゲート型TFTで形成した構成について、図11(A)～図11(D)、図12(A)～図12(C)及び図13を用いて説明する。

**【 0 2 0 4 】**

まず基板310上に、下地絶縁膜312及び金属膜511を形成する(図11(A)参照)。この金属膜511として、本実施の形態では例えば窒化タンタル及びタングステン(W)をそれぞれ30 nm、370 nm積層した膜を用いる。30

**【 0 2 0 5 】**

また、金属膜511として、上記以外にもチタン(Ti)、タングステン(W)、タンタル(Ta)、モリブデン(Mo)、ネオジム(Nd)、コバルト(Co)、ジルコニウム(Zr)、亜鉛(Zn)、ルテニウム(Ru)、ロジウム(Rh)、パラジウム(Pd)、オスミウム(Os)、イリジウム(Ir)、白金(Plt)、アルミニウム(Al)、金(Au)、銀(Ag)、銅(Cu)から選ばれた元素、または前記元素を主成分とする合金材料若しくは化合物材料からなる単層膜、或いは、これらの窒化物、例えば、窒化チタン、窒化タングステン、窒化タンタル、窒化モリブデンからなる単層膜を用いることができる。40

**【 0 2 0 6 】**

なお、下地絶縁膜312を基板310上に形成せず、金属膜511を直接基板310に形成してもよい。

**【 0 2 0 7 】**

次に金属膜511を用いて、ゲート電極512、配線314及び315、端子電極350を形成する(図11(B)参照)。

**【 0 2 0 8 】**

次いで、ゲート電極512、配線314及び315、端子電極350を覆うゲート絶縁膜514を形成する。本実施の形態では、珪素を主成分とする絶縁膜、例えばプラズマCVD法により115 nmの厚さで窒素を含む酸化珪素膜(組成比Si = 32%、O = 5950

%、N = 7 %、H = 2 %) を用いてゲート絶縁膜514を形成する。

**【0209】**

次にゲート絶縁膜514上に島状半導体領域515を形成する。島状半導体領域515は、実施の形態2で述べた島状半導体領域331と同様の材料及び作製工程により形成すればよい(図11(C)参照)。

**【0210】**

島状半導体領域515を形成したら、後にTFT503のソース領域又はドレイン領域521となる領域以外を覆ってマスク518を形成し、一導電型を付与する不純物の導入を行う(図11(D)参照)。一導電型の不純物としては、nチャネル型TFTを形成する場合には、n型不純物としてリン(P)、砒素(As)を用い、pチャネル型TFTを形成する場合には、p型不純物としてホウ素(B)を用いればよい。本実施の形態ではn型不純物であるリン(P)を島状半導体領域515に導入し、TFT503のソース領域又はドレイン領域521及びソース領域又はドレイン領域521の間にチャネル形成領域を形成する。

10

**【0211】**

次いでマスク518を除去し、図示しない第1の層間絶縁膜、第2の層間絶縁膜316、及び第3の層間絶縁膜317を形成する(図11(E)参照)。第1の層間絶縁膜、第2の層間絶縁膜316及び第3の層間絶縁膜317の材料及び作製工程は実施の形態2の記載に基づけばよい。

**【0212】**

次にゲート絶縁膜514、第1の層間絶縁膜、第2の層間絶縁膜316及び第3の層間絶縁膜317にコンタクトホールを形成し、金属膜を成膜、さらに選択的に金属膜をエッチングして、配線319、接続電極320、端子電極351、TFT503のソース電極又はドレイン電極531を形成する。そして、レジストからなるマスクを除去する。なお、本実施の形態の金属膜は、膜厚100nmのTi膜と、膜厚350nmのSiを微量に含むAl膜と、膜厚100nmのTi膜との3層を積層したものとする。次に保護電極318、533、536、538を形成する。

20

**【0213】**

また配線319及びその保護電極318、接続電極320及びその保護電極533、端子電極351及びその保護電極538、TFT503のソース電極又はドレイン電極531及びその保護電極536は、単層の導電膜を用いてそれぞれの配線や電極を形成してもよい。

**【0214】**

以上の工程で、ボトムゲート型TFT503を作製することができる(図12(A)参照)。

**【0215】**

次に第3の層間絶縁膜317上に、p型半導体層111p、i型半導体層111i及びn型半導体層111nを含む光電変換層111を形成する(図12(B))。光電変換層111の材料及び作製工程等は、実施の形態2を参照すればよい。

**【0216】**

次いで封止層324、端子電極121及び122を形成する(図12(C))。端子電極121はn型半導体層111nに接続されており、端子電極122は端子電極121と同一工程で形成される。

40

**【0217】**

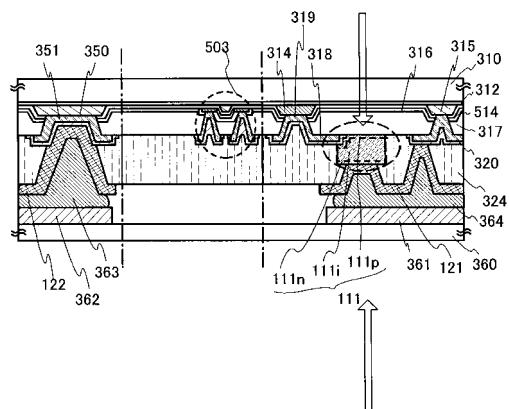

さらに電極361及び362を有する基板360を、半田364及び363で実装する。なお基板360上の電極361は、半田364で端子電極121に実装されている。また基板360の電極362は、半田363端子電極122に実装されている(図13参照)。

**【0218】**

図13に示す光電変換回路において、光電変換層111に入射する光は、透光性を有す

50

る基板310及び基板360を用いることにより、基板310側及び基板360側の両方から入ることができる。

【0219】

なお本実施の形態は、本明細書の実施の形態の技術的要素と組み合わせて行うことができる。

(実施の形態5)

【0220】

本実施の形態では、本発明の光電変換装置に筐体を形成して光の入射する方向を制御した例を、図14(A)～図14(B)及び図15(A)～図15(B)を用いて説明する。

【0221】

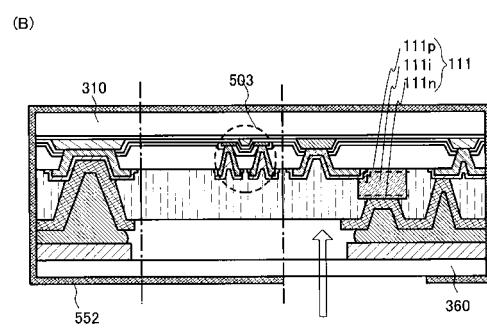

図14(A)は、図9(C)の光電変換装置に、基板360の電極361を半田364で端子電極121に実装した後に、筐体551を形成して、光電変換層111に入射する光を、基板310側からではなく、基板360側から入るようにしたものである。筐体551には、基板360側の光電変換層111が形成される領域に開口部が設けられている。

【0222】

図14(A)においては、端子電極121、電極361及び半田364が存在しているが、基板360側から入射した光は、封止層324を通して光電変換層111に斜めに入射するので光電流を発生させ、光を検知することが可能である。

【0223】

また筐体551、及び以下に述べる筐体552～554は、光を遮断する機能を有する材料なら何を用いてもよく、例えば金属材料や黒色顔料を有する樹脂材料等を用いて形成すればよい。

【0224】

図14(B)は、図13で示した光電変換回路に筐体552を形成して、光電変換層111に入射する光を、基板310側からではなく、基板360側から入るようにしたものである。筐体552には、基板360側の光電変換層111が形成される領域に開口部が設けられている。

【0225】

図14(B)においても、図14(A)同様、基板360側から入射した光は、封止層324を通して光電変換層111に斜めに入射するので光電流を発生させ、光を検知することが可能である。

【0226】

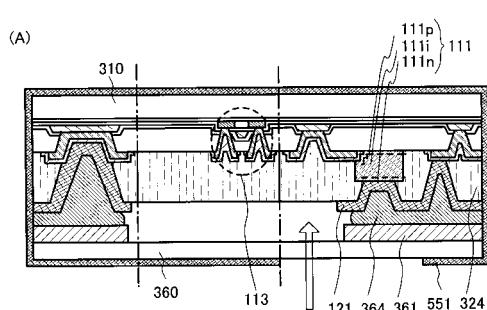

図15(A)では、図9(C)の光電変換装置に、基板360の電極361を半田364で端子電極121に実装した後に、筐体553を形成して、光電変換層111に入射する光を、基板360側からではなく、基板310側から入るようにしたものである。筐体553には、基板310側の光電変換層111が形成される領域に開口部が設けられている。

【0227】

図15(A)において、基板310側から入射した光は、第3の層間絶縁膜317を通して光電変換層111に直接入射するので光電流を発生させ、光を検知することが可能である。

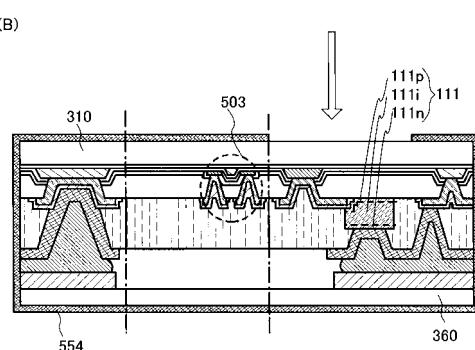

【0228】

図15(B)は、図13で示した光電変換回路に筐体554を形成し、光電変換層111に入射する光を基板360側からではなく、基板310側から入るようにしたものである。筐体554には、基板310側の光電変換層111が形成される領域に開口部が設けられている。

【0229】

図15(B)においては、基板310側から入射した光は、第3の層間絶縁膜317を通して光電変換層111に直接入射するので光電流を発生させ、光を検知することが可能である。

10

20

30

40

50

**【0230】**

なお本実施の形態は、本明細書の実施の形態の技術的要素と組み合わせて行うことができる。

**(実施の形態6)****【0231】**

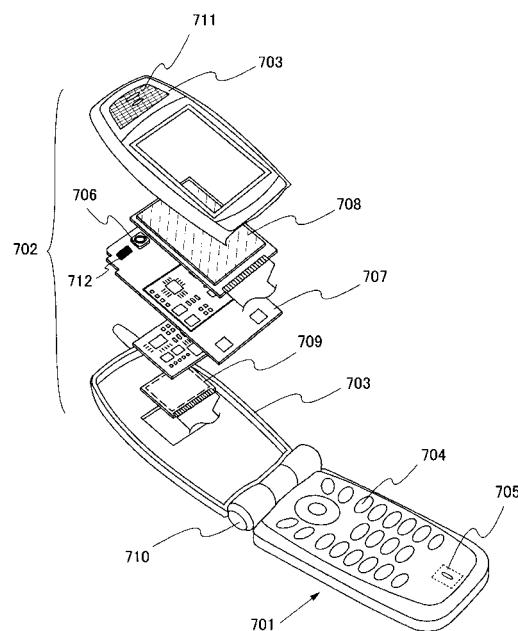

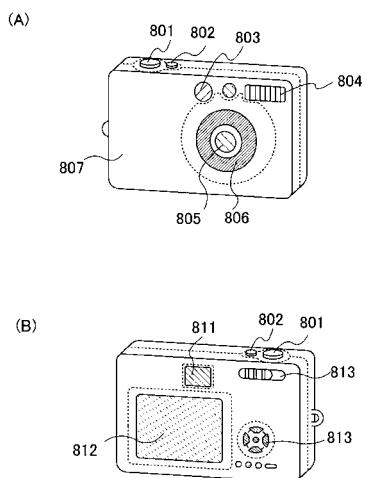

本実施例では、本発明により得られた光電変換装置を様々な電子機器に組み込んだ例について説明する。本発明が適用される電子機器として、コンピュータ、ディスプレイ、携帯電話、テレビなどが挙げられる。それらの電子機器の具体例を図16、図17(A)～図17(B)、図18(A)～図18(B)、図19、及び図20に示す。

**【0232】**

図16は携帯電話であり、本体(A)701、本体(B)702、筐体703、操作キー704、音声入力部705、音声出力部706、回路基板707、表示パネル(A)708、表示パネル(B)709、蝶番710、透光性材料部711、光電変換装置712を有している。本発明は光電変換装置712に適用することができる。

**【0233】**

光電変換装置712は透光性材料部711を透過した光を検知し、検知した外部光の照度に合わせて表示パネル(A)708及び表示パネル(B)709の輝度コントロールを行ったり、光電変換装置712で得られる照度に合わせて操作キー704の照明制御を行う。これにより携帯電話の消費電流を抑えることができる。

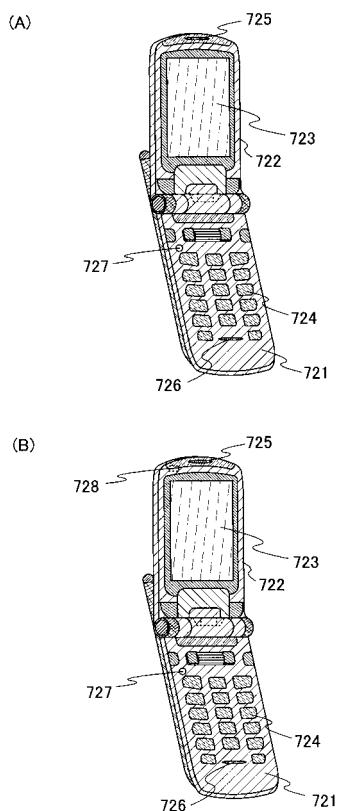

**【0234】**

図17(A)及び図17(B)に携帯電話の別の例を示す。図17(A)及び図17(B)において、本体721、筐体722、表示パネル723、操作キー724、音声出力部725、音声入力部726、光電変換装置727、光電変換装置728を示している。

**【0235】**

図17(A)に示す携帯電話では、本体721に設けられた光電変換装置727により外部の光を検知することにより表示パネル723及び操作キー724の輝度を制御することが可能である。

**【0236】**

また図17(B)に示す携帯電話では、図17(A)の構成に加えて、本体721の内部に光電変換装置728を設けている。光電変換装置728により、表示パネル723に設けられているバックライトの輝度を検出することも可能となる。

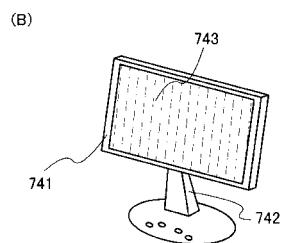

**【0237】**

図18(A)はコンピュータであり、本体731、筐体732、表示部733、キーボード734、外部接続ポート735、ポインティングデバイス736等を含む。

**【0238】**

また図18(B)は表示装置でありテレビ受像器などがこれに当たる。本表示装置は、筐体741、支持台742、表示部743などによって構成されている。

**【0239】**

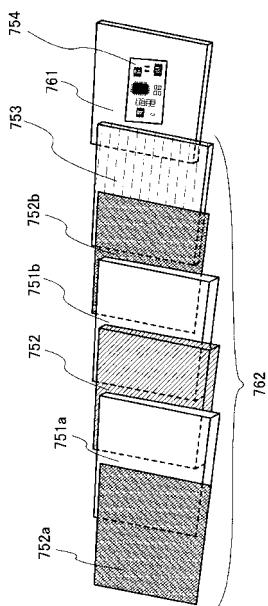

図18(A)のコンピュータに設けられる表示部733、及び図18(B)に示す表示装置の表示部743として、液晶パネルを用いた場合の詳しい構成を図19に示す。

**【0240】**

図19に示す液晶パネル762は、筐体761に内蔵されており、基板751a及び基板751b、基板751a及び基板751bに挟まれた液晶層752、偏光フィルタ752a及び偏光フィルタ752b、及びバックライト753等を有している。また筐体761には光電変換装置754が形成されている。

**【0241】**

本発明を用いて作製された光電変換装置754はバックライト753からの光量を感じし、その情報がフィードバックされて液晶パネル762の輝度が調節される。

**【0242】**

図20(A)及び図20(B)は、本発明の光電変換装置をカメラ、例えばデジタルカ

10

20

30

40

50

メラに組み込んだ例を示す図である。図20(A)は、デジタルカメラの前面方向から見た斜視図、図20(B)は、後面方向から見た斜視図である。図20(A)において、デジタルカメラには、リリースボタン801、メインスイッチ802、ファインダ窓803、フラッシュ804、レンズ805、鏡胴806、筐体807が備えられている。

#### 【0243】

また、図20(B)において、ファインダ接眼窓811、モニタ812、操作ボタン813が備えられている。

#### 【0244】

リリースボタン801は、半分の位置まで押下されると、焦点調整機構および露出調整機構が作動し、最下部まで押下されるとシャッターが開く。

10

#### 【0245】

メインスイッチ802は、押下又は回転によりデジタルカメラの電源のON/OFFを切り替える。

#### 【0246】

ファインダ窓803は、デジタルカメラの前面のレンズ805の上部に配置されており、図20(B)に示すファインダ接眼窓811から撮影する範囲やピントの位置を確認するための装置である。

#### 【0247】

フラッシュ804は、デジタルカメラの前面上部に配置され、被写体輝度が低いときに、リリースボタンが押下されてシャッターが開くと同時に補助光を照射する。

20

#### 【0248】

レンズ805は、デジタルカメラの正面に配置されている。レンズ805は、フォーカシングレンズ、ズームレンズ等により構成され、図示しないシャッター及び絞りと共に撮影光学系を構成する。また、レンズ805の後方には、CCD(Charge Coupled Device)等の撮像素子が設けられている。

#### 【0249】

鏡胴806は、フォーカシングレンズ、ズームレンズ等のピントを合わせるためにレンズ805の位置を移動するものであり、撮影時には、鏡胴806を繰り出すことにより、レンズ805を手前に移動させる。また、携帯時は、レンズ805を沈銅させてコンパクトにする。なお、本実施の形態においては、鏡胴を繰り出すことにより被写体をズーム撮影することができる構造としているが、この構造に限定されるものではなく、筐体807内での撮影光学系の構成により鏡胴を繰り出さずともズーム撮影が可能なデジタルカメラでもよい。

30

#### 【0250】

ファインダ接眼窓811は、デジタルカメラの後面上部に設けられており、撮影する範囲やピントの位置を確認する際に接眼するために設けられた窓である。

#### 【0251】

操作ボタン813は、デジタルカメラの後面に設けられた各種機能ボタンであり、セットアップボタン、メニューボタン、ディスプレイボタン、機能ボタン、選択ボタン等により構成されている。

40

#### 【0252】

本発明の光電変換装置を図20(A)及び図20(B)に示すカメラに組み込むと、光電変換装置が光の有無及び強さを感じることができ、これによりカメラの露出調整等を行うことができる。本発明の光電変換装置は、照度の対数に比例したような出力を得ることが可能なため、感知することができる光の有無及び強さの範囲を広げることができる。

#### 【0253】

また本発明の光電変換装置はその他の電子機器、例えばプロジェクションテレビ、ナビゲーションシステム等に応用することが可能である。すなわち光を検出する必要のあるものであればいかなるものにも用いることが可能である。

#### 【0254】

50

なお本実施の形態は、本明細書の実施の形態の技術的要素と組み合わせて行うことができる。

【図面の簡単な説明】

【0255】

【図1】本発明の光電変換装置の回路構成を示す図。

【図2】本発明の光電変換装置の出力生成回路の構成を示す図。

【図3】本発明の光電変換装置の出力生成回路の電圧・電流特性を示す図。

【図4】本発明の光電変換装置の出力生成回路の照度・電流特性を示す図。

【図5】本発明の光電変換装置の出力生成回路の照度・電流、電圧特性を示す図。

【図6】本発明の光電変換装置の回路構成を示す図。

10

【図7】本発明の光電変換装置の出力生成回路の照度・電流、電圧特性を示す図。

【図8】本発明の光電変換回路の作製工程を示す図。

【図9】本発明の光電変換回路の作製工程を示す図。

【図10】本発明の光電変換回路の作製工程を示す図。

【図11】本発明の光電変換回路の作製工程を示す図。

【図12】本発明の光電変換回路の作製工程を示す図。

【図13】本発明の光電変換回路の断面図。

【図14】本発明の光電変換回路の断面図。

【図15】本発明の光電変換回路の断面図。

【図16】本発明の光電変換装置を実装した装置を示す図。

20

【図17】本発明の光電変換装置を実装した装置を示す図。

【図18】本発明の光電変換装置を実装した装置を示す図。

【図19】本発明の光電変換装置を実装した装置を示す図。

【図20】本発明の光電変換装置を実装した装置を示す図。

【図21】本発明の光電変換装置の回路構成を示す図。

【図22】本発明の光電変換装置の回路構成を示す図。

【符号の説明】

【0256】

101 カレントミラー回路

102 a 出力生成回路

30

102 b 出力生成回路

102 c 出力生成回路

103 光電変換素子

104 参照側トランジスタ

105 a 出力側トランジスタ

105 b 出力側トランジスタ

105 c 出力側トランジスタ

106 内部抵抗

106 a 内部抵抗

106 b 内部抵抗

40

106 c 内部抵抗

107 負荷抵抗

108 高電位側電源線

109 低電位側電源線

110 出力端子

111 光電変換層

111 i i型半導体層

111 n n型半導体層

111 p p型半導体層

113 TFT

50

- 1 2 1 端子電極

1 2 2 端子電極

2 1 1 第2のカレントミラー回路

2 1 2 第2の参照側トランジスタ

2 1 3 第2の出力側トランジスタ

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【図16】

【図17】

【図18】

【図19】

【図20】

【図21】

---

フロントページの続き

(51)Int.Cl.

F I

H 03K 17/78

L

- (56)参考文献 特開2007-059889(JP,A)

特開2005-136394(JP,A)

特開2005-167157(JP,A)

特公平07-070064(JP,B2)

特開平08-129046(JP,A)

特開2007-294028(JP,A)

特開2005-129909(JP,A)

特開2007-318094(JP,A)

特開2008-109110(JP,A)

特開2007-318111(JP,A)

特開2007-119911(JP,A)

## (58)調査した分野(Int.Cl., DB名)

|        |           |   |           |

|--------|-----------|---|-----------|

| G 01 J | 1 / 0 0   | - | 1 / 6 0   |

| H 01 L | 3 1 / 1 0 |   |           |

| H 01 L | 2 7 / 1 4 |   |           |

| H 04 N | 5 / 3 0   | - | 5 / 3 3 5 |

| G 11 B | 7 / 0 9   | - | 7 / 1 0   |