**(19) 대한민국특허청(KR)**

**(12) 공개특허공보(A)**

(51) Int. Cl.<sup>7</sup>

G05F 1/565

(11) 공개번호 특2001-0014722

(43) 공개일자 2001년02월26일

---

|            |                                        |

|------------|----------------------------------------|

| (21) 출원번호  | 10-2000-0019207                        |

| (22) 출원일자  | 2000년04월12일                            |

| (30) 우선권주장 | 99-106253 1999년04월14일 일본(JP)           |

| (71) 출원인   | 마쓰시다덴기산교 가부시키가이샤 모리시타 요이찌              |

| (72) 발명자   | 일본국 오사카후 가도마시 오아자 가도마 1006반지<br>후루야시게키 |

|            | 일본오사카후오사카시니시쿠에도보리1-22-7-504            |

|            | 오카고지                                   |

|            | 일본오사카후미시마군시마모토쵸야마자키2-12-911            |

| (74) 대리인   | 이병호                                    |

---

**심사청구 : 있음**

**(54) 전압 검출 회로**

**요약**

제 1 전압의 상태를 검출하기 위한 전압 검출 회로는 제 1 전압에 의존하여 검출 전압을 발생하기 위한 검출 전압 발생 회로와, 기준 전압을 발생하기 위한 기준 전압 발생 회로와, 검출 전압을 기준 전압과 비교하고 그 비교 결과를 검출 신호로서 출력하기 위한 비교 회로 및 검출 전압 발생 회로, 기준 전압 발생 회로 및 비교 회로 중 적어도 하나를 제어하여 이를 회로 중 적어도 하나가 간헐적으로 동작하도록 하기 위한 제어 회로를 구비한다.

**대표도**

**도3**

**색인어**

검출 전압 발생 회로, 기준 전압 발생 회로, 비교 회로

**명세서**

**도면의 간단한 설명**

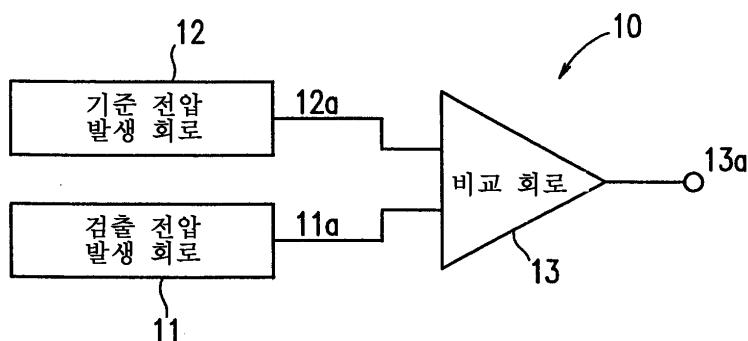

도 1은 종래의 전원 전압 검출 회로의 구성을 나타낸 도면.

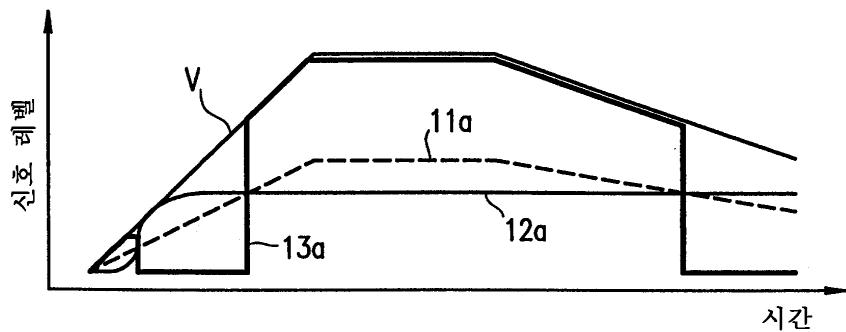

도 2는 검출 전압(11a), 기준 전압(12a), 비교 회로 출력 신호(13a) 및 전원 전압(V)의 시간에 대한 신호 레벨을 나타낸 도면.

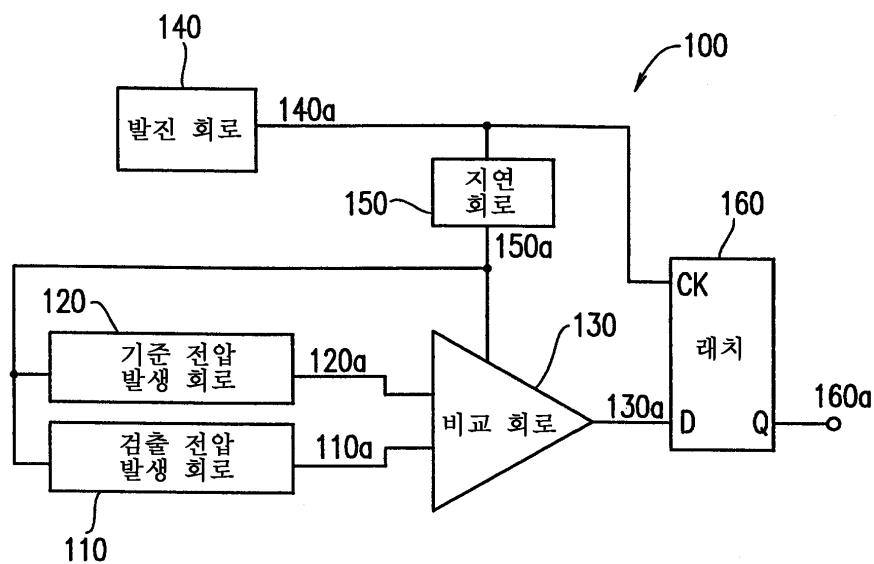

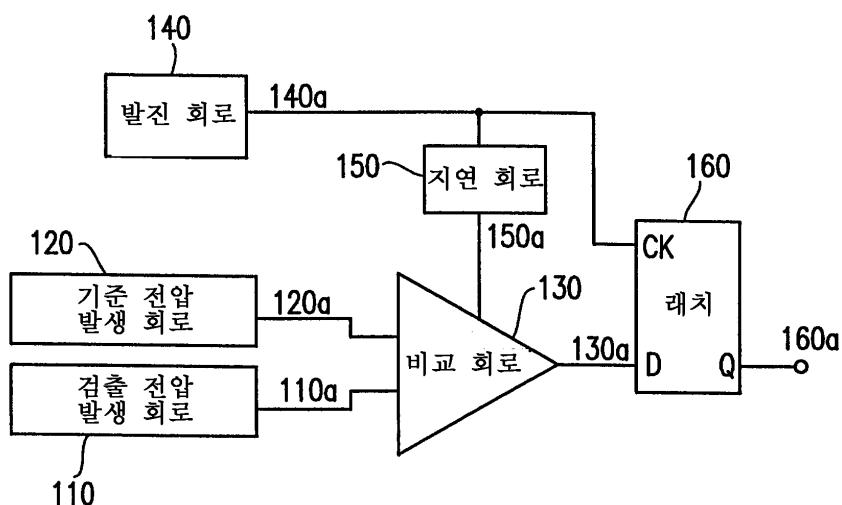

도 3은 본 발명의 실시예 1에 따른 전압 검출 회로(100)의 구성을 나타낸 도면.

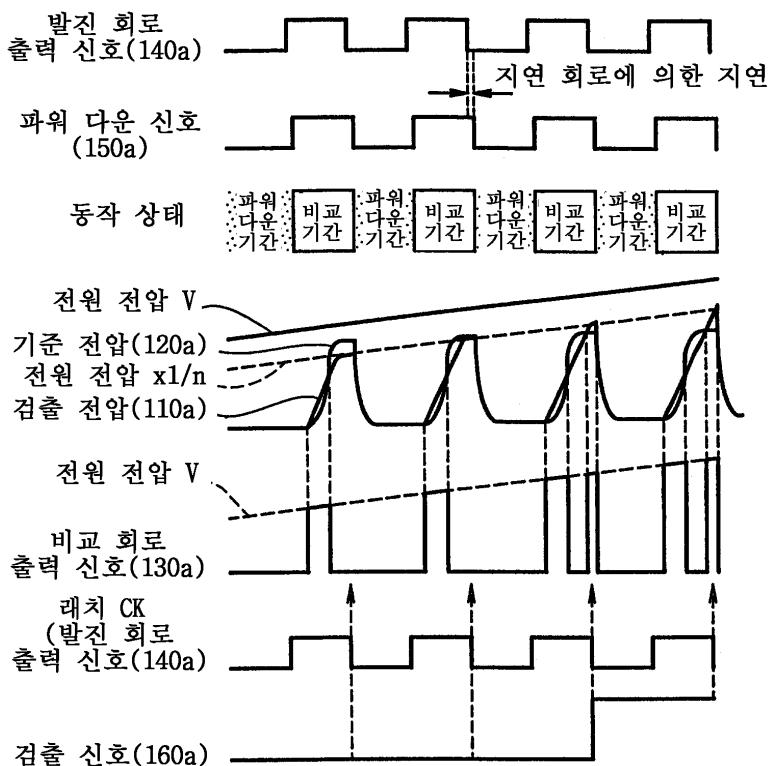

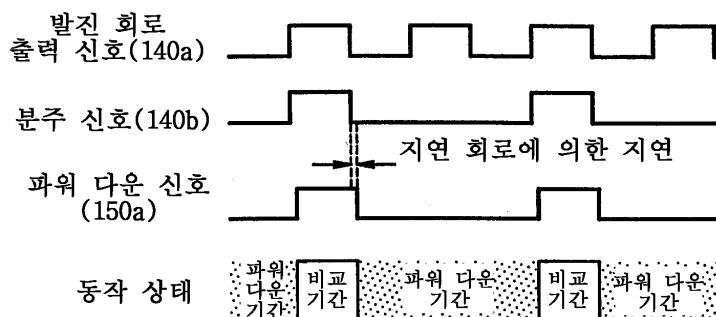

도 4는 전압 검출 회로(100) 각 부분의 출력을 나타낸 타이밍 채트.

도 5는 전압 검출 회로(100)의 부분 변형 형태의 구성을 나타낸 도면.

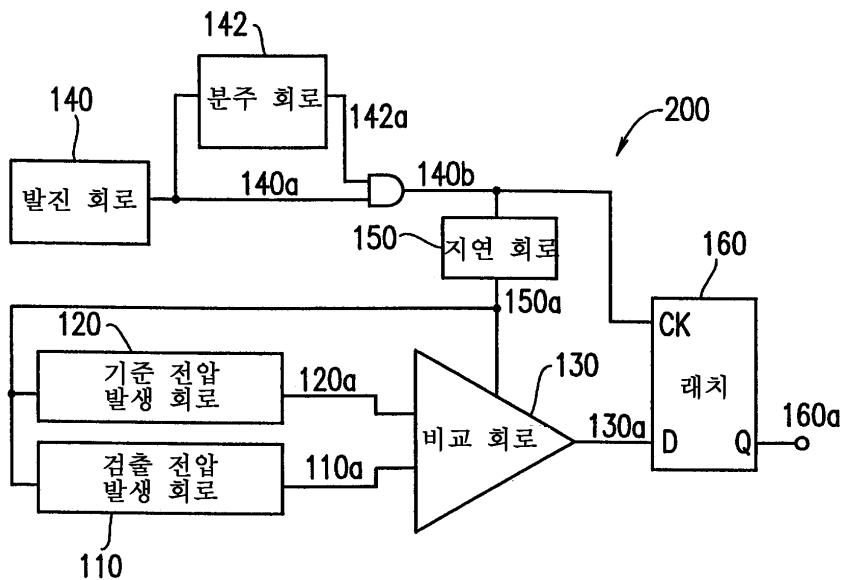

도 6은 본 발명의 실시예 2에 따른 전압 검출 회로(200)의 구성을 나타낸 도면.

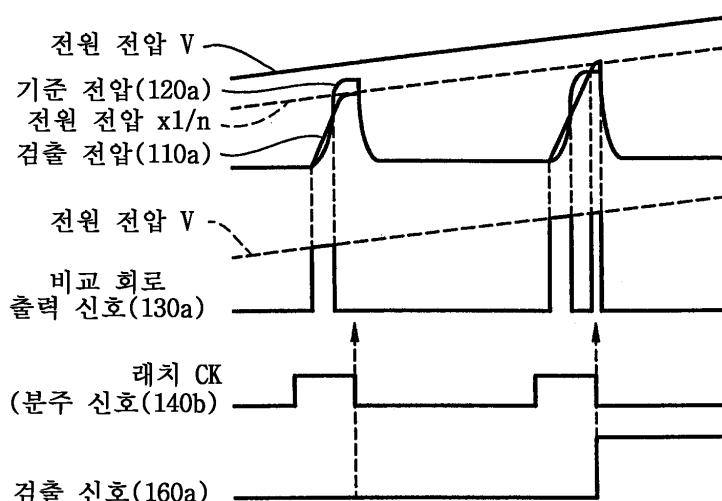

도 7은 전압 검출 회로(200) 각 부분의 출력을 나타낸 타이밍 채트.

도 8은 실시예 2의 전압 검출 회로(200)와 도 1에 나타낸 종래의 전압 검출 회로에 의해 소비되는 동작 전원 전류를 비교하기 위한 표.

\*도면의 주요 부분에 대한 부호의 설명

100 : 전압 검출 회로                    110 : 검출 전압 발생 회로

120 : 기준 전압 발생 회로            130 : 비교 회로

140 : 발진 회로

150 : 자연 회로

160 : 래치 회로

## 발명의 상세한 설명

### 발명의 목적

#### 발명이 속하는 기술분야 및 그 분야의 종래기술

본 발명은 전압 상태를 검출하기 위한 전압 검출 회로, 예를 들면 전원 전압 검출 회로에 관한 것이다.

전원 전압 검출 회로는 전지의 수명 검출 또는 백업(backups) 모드 상태에서의 커패시터 전원 전압 검출 등에 널리 사용되고 있다. 전원 전압 검출 회로는 주로 휴대 장치를 위한 마이크로 컴퓨터에 통상 내장된다. 더욱이, 전원 전압 검출 회로는 또한 파워-온(power-on)에서의 초기화를 위한 리셋 신호의 발생 또는 전원 전압이 변할 때의 시스템 폭주를 방지하기 위한 리셋 신호의 발생에 사용될 수 있다.

종래의 전원 전압 검출 회로(10)의 구성 및 동작은 도 1을 참조하여 설명한다. 전원 전압 검출 회로(10)는 검출 전압 발생 회로(11), 기준 전압 발생 회로(12) 및 비교 회로(13)를 구비한다. 검출 전압 발생 회로(11)는 전원 전압을 모니터하기 위한 검출 전압(11a)을 발생한다. 기준 전압 발생 회로(12)는 일정하고 전원 전압에 독립적인 기준 전압(12a)을 발생한다. 비교 회로(13)는 검출 전압(11a)과 기준 전압(12a)을 비교하여 그 비교 결과를 비교 회로 출력 신호(13a)로서 출력한다. 전원 전압 분압 회로는 예를 들면 검출 전압 발생 회로(11)로서 사용될 수 있다. 밴드갭(bandgap) 기준 회로는 예를 들면 기준 전압 발생 회로(12)로서 사용될 수 있다.

도 2는 전원 전압 V, 검출 전압(11a), 기준 전압(12a) 및 비교 회로 출력 신호(13a)를 시간에 대해 나타낸 도면이다. 도 2에 있어서, 검출 전압(11a)이 기준 전압(12a)보다 높을 때, 비교 회로(13)는 전원 레벨과 같은 레벨에서 비교 회로 출력 신호(13a)를 출력한다. 검출 전압(11a)은 전원 전압 V에 비례하도록 설계된다.

도 2로부터 알 수 있는 것과 같이, 검출 전압(11a)이 기준 전압(12a)보다 높은가의 여부는 전원 전압 V의 변동 절대치에 의존한다. 검출 전압(11a)이 기준 전압(12a)보다 높을 경우, 비교 회로(13)의 출력은 HIGH 레벨로 가고 전원 전압 V의 것과 같은 레벨을 갖는 비교 회로 출력 신호(13a)를 갖는다. 검출 전압(11a)이 기준 전압(12a)보다 낮을 경우, 비교 회로(13)는 LOW 레벨을 갖는 비교 회로 출력 신호(13a)를 출력한다. 이러한 동작은 전원 전압 V이 소정 레벨에 대해 HIGH 레벨 또는 LOW 레벨을 갖는지의 여부를 판정할 수 있게 한다.

전원 전압 검출 회로(10)는 검출 전압(11a)과 기준 전압(12a)을 연속적으로 비교한다. 비교 회로 출력 신호(13a)는 비교 회로(13)로부터 연속적으로 출력된다. 즉, 전원 전압 검출 회로(10)에 있어서, 검출 전압 발생 회로(11), 기준 전압 발생 회로(12) 및 비교 회로(13) 모두는 전원 전압을 검출할 수 있도록 연속적으로 동작한다. 이 때문에, 이를 회로를 동작시키는 데 필요한 전원 전류가 연속적으로 흐른다고 하는 문제가 있다.

#### 발명이 이루고자 하는 기술적 과제

이와 같은 문제를 해결하기 위한 좋은 방법은 비교 회로(13)가 비교 회로 출력 신호(13a)를 출력하면 회로를 동작시키기 위해 필요로 되는 전원 전류를 차단하는 것이다. 그러나, 이것은 비교 회로(13)의 출력이 또한 차단되기 때문에 실현 불가능하다. 다른 방법으로서는 회로를 동작시키는 데 필요한 전원 전류가 감소될 수 있다. 그러나, 이 경우 회로가 온도 변화 및 이를 소자의 변화에 의해 쉽게 영향을 받아 검출 정밀도를 감소시킨다는 다른 문제가 발생한다.

### 발명의 구성 및 작용

본 발명의 일 특징에 따르면, 제 1 전압의 상태를 검출하기 위한 전압 검출 회로는, 상기 제 1 전압에 의존하여 검출 전압을 발생하기 위한 검출 전압 발생 회로와, 기준 전압을 발생하기 위한 기준 전압 발생 회로와, 상기 검출 전압을 상기 기준 전압과 비교하고 상기 비교 결과를 검출 신호로서 출력하기 위한 비교 회로, 및 상기 검출 전압 발생 회로, 상기 기준 전압 발생 회로 및 상기 비교 회로 중 적어도 하나를 제어하여 이를 회로 중 적어도 하나가 간헐적으로 동작하도록 하기 위한 제어 회로를 포함한다.

본 발명의 일 실시예에 있어서, 상기 제어 회로는 클록 신호를 출력하기 위한 발진 회로를 구비한다.

본 발명의 일 실시예에 있어서, NOI 자연수일 때, 팩터 N에 의해 상기 발진 회로로부터 출력된 상기 클록 신호를 분할하는 분주 회로를 더 포함한다.

본 발명의 일 실시예에 있어서, 상기 간헐적으로 동작하는 회로는 상기 비교 회로이다.

본 발명의 다른 특징에 있어서, 제 1 전압의 상태를 검출하기 위한 전압 검출 방법은, 기준 전압과 상기 제 1 전압의 모니터(monitor)로서의 검출 전압을 비교하는 단계와, 상기 비교 결과를 검출 신호로서 출력하는 단계를 포함한다.

본 발명의 일 실시예에 있어서, 상기 간헐적인 비교 동작의 사이클은 미리 정해진 주파수를 갖는 클록 신

호에 의해 제어된다.

따라서, 본 명세서에 기재된 본 발명은 전압 검출 정밀도를 감소시키지 않고 저 전력 소비의 전압 검출 회로 및 방법을 제공하는 이점을 가질 수 있다.

이 기술분야에서 숙련된 사람은 첨부 도면을 참조한 이하의 상세한 설명을 읽고 이해할 때 본 발명의 상기 및 다른 목적을 명백하게 알 수 있을 것이다.

본 발명에 따른 전압 검출 회로는 검출 전압 발생 회로, 기준 전압 발생 회로 및 비교 회로를 구비한다. 전압 검출 회로는 또한 이들 회로 중 적어도 하나를 제어하여 이들 회로 중 적어도 하나가 간헐적으로 동작하도록 하기 위한 제어 회로를 구비한다. 이들 회로 중 적어도 하나의 간헐적인 동작은 전체 회로에 의한 전력 소비를 감소시킨다.

본 발명에 따른 전압 검출 회로는 우선적으로 전압(이하 제 1 전압이라 함)을 검출한다. 제 1 전압은 전압 검출 회로 또는 전압 검출 회로를 갖는 집적 회로를 위한 전원 전압 또는 상기 전원 전압 이외의 임의의 전원 전압(즉 다른 집적 회로의 전원 전압 또는 DRAM에 필요한 웰 바이어스(well bias))이어도 된다.

본 발명에 따른 전압 검출 회로는 히터(heater)의 돌입 전류(rush current) 및 래치-업(latch-up) 전류 등의 전류의 검출 또는 주파수의 검출을 위해 사용될 수 있다. 이를 위해, 전류 또는 주파수는 또한 검출을 위한 전압 검출 회로에 종속되는 전압으로 변환된다.

이하, 본 발명의 구체적인 실시예를 전원 전압 검출을 위한 전압 검출 회로를 사용하는 실시예로 설명한다.

#### (실시예 1)

도 3은 전원 전압을 검출하기 위한 실시예 1의 전압 검출 회로(100)의 구성을 나타낸다. 도 4는 전압 검출 회로(100) 각 부분의 출력을 나타내는 타이밍 채트이다.

전압 검출 회로(100)는 검출 전압 발생 회로(110), 기준 전압 발생 회로(120) 및 비교 회로(130)를 구비하고 있다. 검출 전압 발생 회로(110)는 전원 전압을 모니터하기 위한 검출 전압(110a)을 발생한다. 검출 전압(110a)은 전원 전압의 값에 비례하는 값(즉,  $n > 0$ 인 경우, 전원 전압의  $1/n$ )을 가진다. 기준 전압 발생 회로(120)는 일정하고 전원 전압에 독립적인 기준 전압(120a)을 발생한다. 비교 회로(130)는 검출 전압(110a)을 기준 전압(120a)과 비교하여 그 비교 결과를 비교 회로 출력 신호(130a)로서 출력한다. 전원 전압 분압 회로는 예를 들면 검출 전압 발생 회로(110)로서 사용되어도 된다. 밴드캡 기준 회로는 예를 들면 기준 전압 발생 회로(120)로서 사용되어도 된다.

실시예 1에 있어서, 전압 검출 회로(100)는 또한 발진 회로(140), 지연 회로(150) 및 래치 회로(160)를 구비한다. 발진 회로(140)는 예를 들면 링 발진 회로(ring oscillator circuit)를 구비해도 된다.

발진 회로(140)는 도 4에 나타낸 것과 같이 일정한 주파수를 갖는 클록 신호(발진 회로 출력 신호)(140a)를 출력한다. 도 4에 나타낸 것과 같이, 발진 회로 출력 신호(140a)의 위상은 지연 회로(150)에 의해 약  $5\text{ns} \pm 2$ 의 레벨로 지연되어 파워 다운(power down) 신호(150a)로서 출력된다. 파워 다운 신호(150a)는 지연 회로(150)로부터 출력된다. 도 4에 나타낸 것과 같이, 검출 전압 발생 회로(110), 기준 전압 발생 회로(120) 및 비교 회로(130)는 파워 다운 신호(150a)를 수신하고 파워 다운 신호(150a)에 따라 간헐적으로 동작하여 검출 전압(110a), 기준 전압(120a) 및 비교 회로 출력 신호(130a)를 출력한다.

도 4로부터 알 수 있는 것과 같이, 파워 다운 신호(150a)가 HIGH 레벨을 갖는 기간에, 비교 회로(130)와 검출 전압 발생 회로(110) 및 기준 전압 발생 회로(120)는 비교 동작을 행한다. 파워 다운 신호(150a)가 LOW 레벨을 갖는 기간에, 이들 회로는 파워 다운 상태에 있어 비교 동작은 행해지지 않는다. 상기한 바와 같이, 검출 전압 발생 회로(110), 기준 전압 발생 회로(120) 및 비교 회로(130)는 각각 파워 다운 기능을 갖는다. 간헐적인 비교 동작에 의해, 비교 회로(130)는 도 4에 나타낸 것과 같이 비교 회로 출력 신호(130a)를 출력한다. 전압 검출 회로(100)는 파워 다운 신호(150a)가 HIGH 레벨을 갖는 기간에는 종래 예와 동일한 비교 동작을 갖는다.

비교 회로(130)로부터 출력된 비교 회로 출력 신호(130a)는 상기한 간헐 동작이 행해지는 시간과 같은 시간에 래치 회로(160)에 의해 래치된다. 발진 회로(140)의 발진 회로 출력 신호는 래치 클록으로서 사용된다. 이러한 래칭은 도 4에 나타낸 것과 같이 래치 회로(160)로부터 출력된 연속 검출 신호(160a)를 발생한다. 실시예 1에 있어서, 래칭 데이터의 타이밍을 조정하는 지연 회로(150)가 제공되어 래치 회로(160)가 비교 회로 출력 신호(130a)를 확실하게 래치할 수 있게 한다.

이렇게 얻어진 검출 신호(160a)는 검출될 전원 전압에 대한 정보를 얻기 위해 사용될 수 있다. 이와 같은 정보의 예는 정보 휴대 장치의 주 전원으로서 사용되는 전지의 수명 또는 전압 강하 및 백업 모드 상태(즉 코드리스 다리미)의 커패시터 전원 전압의 전압 강하를 포함한다. 상기 정보에 기초하여, 정보 휴대 장치의 전지의 경우에 있어서, 예를 들면 전지의 전압이 기준 전압보다 낮을 경우, 정보 휴대 장치 내의 회로의 일부가 정지되어 전력을 소비할 수 있다. 검출 신호(160a)는 파워-온에서 초기화하기 위한 리셋 신호 또는 전원 전압이 변할 때 시스템 폭주(run away)를 방지하기 위한 리셋 신호로서 사용될 수 있다.

실시예 1에 있어서, 발진 회로(140)로부터 출력된 발진 회로 출력 신호(140a)가 뉴티 비 1을 갖는 펄스를 갖는 것으로 가정하면, 전체 회로에 의한 전력 소비는 회로 자체의 동작 전원 전류를 감소시키지 않고 절반으로 감소될 수 있다. 발진 회로 출력 신호(140a)의 뉴티 비를 조정하는 것에 의해 전력 소비의 감소율을 선택적으로 변경시킬 수 있다.

실시예 1에 있어서, 파워 다운 신호(150a)가 검출 전압 발생 회로(110), 기준 전압 발생 회로(120) 및 비교 회로(130)에 공급되어 모든 회로는 간헐적으로 동작한다. 본 발명은 이러한 것에 한정되는 것은 아니다. 본 발명의 효과, 즉 동작 전원 전류의 감소를 달성하기 위해, 단지 하나 이상의 이들 회로가 간헐적으로 동작해도 된다. 예를 들면, 도 5에 나타낸 것과 같이, 비교 회로(130)가 전압 검출 회로에서 간헐적으로 동작할 경우, 지연 회로(150)는 검출 전압 발생 회로(110) 또는 기준 전압 발생 회로(120)의 어느

것에도 접속되지 않지만 비교 회로(130)에는 접속된다. 마찬가지로, 지연 회로(150), 검출 전압 발생 회로(110) 및 기준 전압 발생 회로(120) 간의 접속이 선택적으로 제공되어 검출 전압 발생 회로(110) 및/ 또는 기준 전압 발생 회로(120)만을 간헐적으로 동작시켜도 된다. 이와 같은 변형은 이하에 기술되는 실시예 2에 적용될 수 있다.

실시예 1에 있어서, 발진 회로(140)와 지연 회로(150)는 상기한 간헐 동작을 얻기 위해 전압 검출 회로(100)를 제어하기 위한 제어 회로를 구성한다. 발진 회로(140) 및 지연 회로(150)는 간헐 동작을 얻기 위한 펄스 신호를 발생한다. 본 발명에 따르면, 검출 전압 발생 회로(110), 기준 전압 발생 회로(120) 및 비교 회로(130) 중 적어도 하나는 연속적으로 동작하지 않고 간헐적으로 동작한다. 이러한 관점에서, 상기한 파워 다운 신호와 래치 클록 신호를 공급할 수 있는 것이면, 발진 회로(140)와 지연 회로(150)의 조합 대신에 다른 수단이 제어 회로로서 사용되어도 된다.

(실시예 2)

본 발명의 실시예 2에 따른 전원 전압을 검출하기 위한 전압 검출 회로가 도 6 및 도 7을 참조하여 설명된다. 실시예 2의 전압 검출 장치는 실시예 2의 전압 검출 장치에 발진 회로로부터 출력된 펄스 신호의 주파수를 분할하기 위한 분주 회로가 설치되는 점에 있어서 실시예 1의 전압 검출 장치와 다르다. 이러한 점을 제외하고, 실시예 2의 전압 검출 장치는 실시예 1의 전압 검출 장치와 동일하다.

도 6은 실시예 2의 전압 검출 회로(200)의 구성을 나타낸다. 도 7은 전압 검출 회로(200) 각 부분의 출력을 나타낸 타이밍 채트이다. 전압 검출 회로(200)는 이하에 상세히 기술된다.

전압 검출 회로(200)는 검출 전압 발생 회로(110), 기준 전압 발생 회로(120) 및 비교 회로(130)를 구비한다. 검출 전압 발생 회로(110)는 전원 전압을 모니터하기 위한 검출 전압(110a)을 발생한다. 검출 전압(110a)은 전원 전압에 비례하는 값(즉  $n > 0$ 인 경우 전원 전압의  $1/n$ )을 가진다. 기준 전압 발생 회로(120)는 일정하고 전원 전압에 독립적인 기준 전압(120a)을 발생한다. 비교 회로(130)는 차동 비교기를 구비한다. 비교 회로(130)는 검출 전압(110a)을 기준 전압(120a)과 비교하여 그 비교 결과를 비교 회로 출력 신호(130a)로서 출력한다. 전원 전압 분압 회로는 예를 들면 검출 전압 발생 회로(110)로서 사용되어도 된다. 밴드캡 기준 회로는 예를 들면 기준 전압 발생 회로(120)로서 사용되어도 된다.

전압 검출 회로(200)는 또한 발진 회로(140), 분주 회로(142), 지연 회로(150) 및 래치 회로(160)를 구비한다. 발진 회로(140)는 예를 들면 링 발진 회로를 구비해도 된다. 발진 회로(140)는 실시예 1과 마찬가지로 도 7에 나타낸 것과 같은 일정 주파수를 갖는 클록 신호(발진 회로 출력 신호)(140a)를 출력한다.

분주 회로(142)는 발진 회로(140)로부터 출력된 발진 회로 출력 신호(140a)의 주파수를 분할하여 특정 주파수를 갖는 클록 신호인 분주 회로 출력 신호(142a)를 출력한다. 토글형 플립 플롭(T-FF) 회로가 분주 회로(142)로서 사용되어도 된다. 발진 회로 출력 신호(140a) 및 주파수 분할 회로 출력 신호(142a)는 AND 게이트에 의해 논리적으로 합성되고 발진 회로 출력 신호(140a)의 클록 주파수가 팩터 N(N은 자연수)에 의해 나누어져서 도 7에 나타낸 것과 같은 분주 신호(140b)가 얻어진다. 분주 신호(140b)는 지연 회로(150)와 래치 회로(160)에 공급된다.

분주 신호(140b)의 위상은 지연 회로(150)에 의해 약  $5\text{ns} \pm 2\text{ns}$ 의 레벨로 지연되고 도 7에 나타낸 것과 같이 파워 다운 신호(150a)로서 출력된다. 파워 다운 신호(150a)는 지연 회로(150)로부터 출력된다. 검출 전압 발생 회로(110), 기준 전압 발생 회로(120) 및 비교 회로(130)는 파워 다운 신호(150a)를 수신하고 파워 다운 신호(150a)에 따라 간헐적으로 동작하여 도 7에 나타낸 것과 같이 검출 전압(110a), 기준 전압(120a) 및 비교 회로 출력 신호(130a)를 출력한다.

도 7로부터 알 수 있는 것과 같이, 파워 다운 신호(150a)가 HIGH 레벨을 갖는 기간에, 비교 회로(130)와 검출 전압 발생 회로(110) 및 기준 전압 발생 회로(120)는 비교 동작을 행한다. 파워 다운 신호(150a)가 LOW 레벨을 갖는 기간에, 이들 회로는 파워 다운 상태에 있으므로 비교 동작은 행해지지 않는다. 상기한 바와 같이, 검출 전압 발생 회로(110), 기준 전압 발생 회로(120) 및 비교 회로(130)는 각각 파워 다운 기능을 가진다. 간헐 비교 동작에 의해, 비교 회로(130)는 도 7에 나타낸 것과 같이 비교 회로 출력 신호(130a)를 출력한다. 전압 검출 회로(200)는 파워 다운 신호(150a)가 HIGH 레벨을 갖는 기간에는 종래 예의 전압 검출 회로와 같이 동일한 비교 동작을 갖는다.

비교 회로(130)로부터 출력된 비교 회로 출력 신호(130a)는 상기한 간헐 동작과 동일한 시간에 래치 회로(160)에 의해 래치된다. 분주 신호는 래치 클록으로서 사용된다. 이러한 래칭은 도 7에 나타낸 것과 같이 래치 회로(160)로부터 출력된 연속 검출 신호(160a)를 발생한다. 실시예 2에 있어서, 래칭 데이터의 타이밍을 조정하는 지연 회로(150)는 래치 회로(160)가 비교 회로 출력 신호(130a)를 확실하게 래치할 수 있도록 하기 위해 제공된다.

실시예 2에 있어서, 분주 회로(142)는 입력 신호를 팩터 2로 나누어 전체 회로에 의한 전력 소비를 실시예 1에 비해 절반으로 더욱 많이 감소되게 한다. 분주비가 실시예 2에서는 20이지만, 분주비는 다른 값(또는 그 이상)이어도 된다. 전체 회로에 의한 전력 소비는 분주 회로의 분주비 N를 적당한 값(자연수)으로 설정함으로써 원하는 레벨로 감소될 수 있다.

도 8은 실시예 2의 전압 검출 회로(200)와 도 1에 나타낸 종래의 전압 검출 회로에 의해 소비되는 동작 전원 전류의 데이터를 나타낸 표이다. 도 8에 있어서, 전원 전압이 7V이고 분주 회로(142)의 분주비가 예를 들면 150(발진 회로(140)의 발진 회로 출력 신호(140a)의 클록 주파수가 팩터 150으로 나누어짐)이며, 즉 검출 동작이 약  $150\mu\text{s}$ 인 각 구간에서 약  $1\mu\text{s}$ 동안 행해질 경우 실시예 2의 전압 검출 회로(200)에 대한 결과가 얻어진다. 도 8로부터 알 수 있는 것과 같이, 전압 검출 회로(200)에 있어서, 기준 전압 발생 회로, 검출 전압 발생 회로 및 비교 회로의 동작 전원 전류의 전체 감소량은 발진 회로와 분주 회로의 동작 전원 전류의 전체 증가량보다 크다. 그 결과 150의 분주비를 갖는 분주 회로(142)는 도 1에 나타낸 종래 예에 비해 약 2.6%까지 전체 회로에 의해 소비되는 동작 전원 전류를 감소시킨다. 분주 회로(142)의 분주비는 검출될 전압을 갖는 대상에 따라 적당한 값으로 설정될 수 있다. 본 발명의 전압 검출 회로는 검출 전압 발생 회로, 기준 전압 발생 회로 및 비교 회로 중 적어도 하나가 간헐적으로 동작하도록 전압 검출

회로를 제어하기 위한 제어 회로를 구비한다. 회로의 간헐적인 동작에 의해 전체 회로에 의한 전력 소비를 감소시킬 수 있다.

### 발명의 효과

본 발명에 따르면, 저 전력 소비는 회로의 검출 정밀도를 감소시키지 않고 달성된다. 본 발명의 전압 검출 회로를 사용하는 것에 의해 주 전자로서의 전원 전지의 수명을 증가시킬 수 있다.

이 기술 분야에서 속련된 사람에게는 본 발명의 범위 및 사상을 이탈하지 않고 여러 가지 다른 변형에가 있을 수 있다는 것은 명백하고 또한 용이하게 만들어질 수 있을 것이다. 따라서, 다음의 특허청구의 범위는 상기 상세한 설명에 한정되어서는 안되며 그 특허청구범위는 상세한 설명에 기재된 것을 포함하여 그 보다 넓게 해석되어야 할 것이다.

### (57) 청구의 범위

#### 청구항 1

제 1 전압의 상태를 검출하기 위한 전압 검출 회로에 있어서,

상기 제 1 전압에 의존하여 검출 전압을 발생하기 위한 검출 전압 발생 회로와,

기준 전압을 발생하기 위한 기준 전압 발생 회로와,

상기 검출 전압을 상기 기준 전압과 비교하고 상기 비교 결과를 검출 신호로서 출력하기 위한 비교 회로,

및

상기 검출 전압 발생 회로, 상기 기준 전압 발생 회로 및 상기 비교 회로 중 적어도 하나를 제어하여 이들 회로 중 적어도 하나가 간헐적으로 동작하도록 하기 위한 제어 회로를 포함하는 전압 검출 회로.

#### 청구항 2

제 1 항에 있어서, 상기 제어 회로는 클록 신호를 출력하기 위한 발진 회로를 구비하는 전압 검출 회로.

#### 청구항 3

제 2 항에 있어서, N이 자연수일 때, 팩터 N에 의해 상기 발진 회로로부터 출력된 상기 클록 신호를 분할하는 분주 회로를 더 포함하는 전압 검출 회로.

#### 청구항 4

제 1 항에 있어서, 간헐적으로 동작하는 상기 회로는 상기 비교 회로인 전압 검출 회로.

#### 청구항 5

제 1 전압의 상태를 검출하기 위한 전압 검출 방법에 있어서,

기준 전압과 상기 제 1 전압의 모니터(monitor)로서의 검출 전압을 비교하는 단계와,

상기 비교 결과를 검출 신호로서 출력하는 단계를 포함하는 전압 검출 방법.

#### 청구항 6

제 5 항에 있어서, 상기 간헐적인 비교 동작의 사이클은 미리 정해진 주파수를 갖는 클록 신호에 의해 제어되는 전압 검출 방법.

### 도면

#### 도면1

도면2

도면3

## 도면4

## 도면5

## 도면6

## 도면7

## 도면8

|               | 기준 전압<br>발생 회로 | 검출 전압<br>발생 회로 | 비교 회로        | 발진 회로        | 분주 회로        | 회로 전체        |

|---------------|----------------|----------------|--------------|--------------|--------------|--------------|

| 종래 예<br>(도 1) | 25 $\mu$ A     | 40 $\mu$ A     | 90 $\mu$ A   | —            | —            | 155 $\mu$ A  |

| 본발명<br>(도 6)  | 0.35 $\mu$ A   | 0.3 $\mu$ A    | 0.76 $\mu$ A | 1.78 $\mu$ A | 0.86 $\mu$ A | 4.05 $\mu$ A |