(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第6059722号

(P6059722)

(45) 発行日 平成29年1月11日(2017.1.11)

(24) 登録日 平成28年12月16日(2016.12.16)

(51) Int.Cl.

F 1

|                       |            |     |

|-----------------------|------------|-----|

| HO4N 5/3745 (2011.01) | HO4N 5/335 | 745 |

| GO1T 1/17 (2006.01)   | GO1T 1/17  | G   |

| GO1T 1/24 (2006.01)   | GO1T 1/24  |     |

| GO1T 1/20 (2006.01)   | GO1T 1/20  | E   |

| GO1T 1/161 (2006.01)  | GO1T 1/20  | G   |

請求項の数 13 (全 15 頁) 最終頁に続く

(21) 出願番号 特願2014-523426 (P2014-523426)

(86) (22) 出願日 平成24年7月27日 (2012.7.27)

(65) 公表番号 特表2014-529923 (P2014-529923A)

(43) 公表日 平成26年11月13日 (2014.11.13)

(86) 國際出願番号 PCT/IB2012/053837

(87) 國際公開番号 WO2013/018006

(87) 國際公開日 平成25年2月7日 (2013.2.7)

審査請求日 平成27年6月30日 (2015.6.30)

(31) 優先権主張番号 61/514,504

(32) 優先日 平成23年8月3日 (2011.8.3)

(33) 優先権主張国 米国(US)

(73) 特許権者 590000248

コーニンクレッカ フィリップス エヌ

ヴェ

KONINKLIJKE PHILIPS

N. V.

オランダ国 5656 アーネー アイン

ドーフェン ハイテック キャンパス 5

High Tech Campus 5,

NL-5656 AE Eindhoven

(74) 代理人 100087789

弁理士 津軽 進

(74) 代理人 100122769

弁理士 笛田 秀仙

最終頁に続く

(54) 【発明の名称】デジタルシリコン光電子増倍管アレイに関する位置敏感な読み出しモード

## (57) 【特許請求の範囲】

## 【請求項 1】

光子検出器を有する装置であって、前記光子検出器が、

光子の衝突に基づき、ブレイクダウンするよう構成される単一光子アバランシェダイオード検出器を備える検出器アレイと、

前記検出器アレイの単一光子アバランシェダイオード検出器のブレイクダウンに基づき、

トリガー信号を生成するよう構成されるトリガー回路と、

ブレイクダウンにある前記検出器アレイの単一光子アバランシェダイオード検出器の位置座標を格納するよう構成され、前記トリガー回路により生成されるトリガー信号に基づき、ラッチするよう構成されるラッチと、

積分時間インターバル分、前記ラッチへの前記トリガー信号の伝搬を遅延させる少なくとも1つの遅延要素と、

を有し、ラッチした後、前記ラッチが、前記積分時間インターバルにわたりブレイクダウンする前記単一光子アバランシェダイオード検出器に関する位置座標を提供する、装置。

## 【請求項 2】

前記ラッチが、

行ラッチであって、各行ラッチが、前記検出器アレイの対応する行の単一光子アバランシェダイオード検出器の論理的「OR」組合せに接続される、行ラッチと、

列ラッチであって、各列ラッチが、前記検出器アレイの対応する列の単一光子アバランシェダイオード検出器の論理的「OR」組合せに接続される、列ラッチとを有する、請求

項1に記載の装置。

【請求項3】

前記検出器アレイ、前記トリガー回路及び前記ラッチを含む前記光子検出器が、シリコン基板にモノリシックに配置される、請求項1又は2に記載の装置。

【請求項4】

前記光子検出器が更に、前記トリガー回路により生成されるトリガー信号に関するデジタル時間スタンプを生成するよう構成される時間デジタル変換器回路を含む、請求項1乃至3の任意の一項に記載の装置。

【請求項5】

前記光子検出器が更に、前記トリガー回路により生成されるトリガー信号、及び前記ラッチのラッチングをもたらす前記トリガー信号に対して前記時間デジタル変換器回路により生成されるデジタル時間スタンプに基づき、ラッチング後のラッチに格納される値に基づき、ブレイクダウンにある単一光子アバランシェダイオード検出器の位置座標を有する光子検出位置を生成及び出力する処理及び出力回路を更に含む、請求項4に記載の装置。 10

【請求項6】

前記処理及び出力回路が、2つ又はこれ以上の単一光子アバランシェダイオード検出器がブレイクダウンにあることを示すラッチング後の前記ラッチに基づき、エラー信号を出力するよう更に構成される、請求項5に記載の装置。

【請求項7】

光子の衝突に基づきブレイクダウンするよう構成される単一光子アバランシェダイオード検出器を含む検出器アレイを提供するステップと、 20

ブレイクダウンにある前記検出器アレイの単一光子アバランシェダイオード検出器の位置座標を格納するよう構成されるラッチを提供するステップと、

前記検出器アレイの単一光子アバランシェダイオード検出器のブレイクダウンに基づき、トリガー信号を生成するステップと、

積分時間分前記ラッチへの前記トリガー信号の伝搬を遅延させるステップと、

前記トリガー信号に基づき、前記ラッチをラッチするステップと、

前記ラッチした後、前記積分インターバルにわたりブレイクダウンした前記検出器アレイの前記単一光子アバランシェダイオード検出器の画像を生成するため、前記ラッチを読み出すステップと 30

を有する、方法。

【請求項8】

前記トリガー信号の生成をもたらしたブレイクダウンのあった前記単一光子アバランシェダイオード検出器の前記ブレイクダウンに関する時間スタンプを生成するため、前記トリガー信号により起動される時間デジタル変換を実行するステップを更に有する、請求項7に記載の方法。

【請求項9】

光子検出器を有する装置であって、前記光子検出器が、

単一光子アバランシェダイオード検出器のアレイと、

ブレイクダウンにある前記アレイの単一光子アバランシェダイオード検出器の位置座標を格納するよう構成されるラッチと、 40

前記アレイの単一光子アバランシェダイオード検出器のブレイクダウンに基づき、トリガー信号を生成するよう構成されるトリガー回路であって、前記トリガー信号が、前記ラッチがラッチすることをもたらす、トリガー回路と、

前記ラッチされたラッチに格納される位置座標に基づき、光子検出位置を出力するよう構成される処理回路と、

を有し、前記光子検出器が更に、積分時間インターバル分、前記ラッチへの前記トリガー信号の伝搬を遅延させる少なくとも1つの遅延要素を有し、ラッチした後、前記ラッチが、前記積分時間インターバルにわたりブレイクダウンする前記単一光子アバランシェダイオード検出器に関する位置座標を提供する、装置。 50

## 【請求項 10】

前記光子検出器が更に、前記トリガー回路により生成されるトリガー信号に関するデジタル時間スタンプを生成するよう構成される時間デジタル変換器回路を有し、

前記処理回路が更に、前記ラッチのラッチングをもたらす前記トリガー信号に関する前記デジタル時間スタンプに基づき、光子検出時間を出力するよう構成される、請求項9に記載の装置。

## 【請求項 11】

光子検出器を有する装置であって、前記光子検出器が、

单一光子アバランシェダイオード検出器のアレイと、

ブレイクダウンにある前記アレイの单一光子アバランシェダイオード検出器の位置座標を格納するよう構成されるラッチと、

前記アレイの单一光子アバランシェダイオード検出器のブレイクダウンに基づきトリガー信号を生成するよう構成されるトリガー回路であって、前記トリガー信号が、前記ラッチのラッチングをもたらす、トリガー回路と、

積分時間分前記ラッチングを遅延させる少なくとも1つの遅延要素と、

前記ラッチされたラッチに格納される位置座標に基づき、前記積分時間にわたり検出される光子の検出位置を出力するよう構成される処理回路とを含む、装置。

## 【請求項 12】

光子検出器を有する装置であって、前記光子検出器が、

光子の衝突に基づき、ブレイクダウンするよう構成される单一光子アバランシェダイオード検出器を備える検出器アレイと、

前記検出器アレイの单一光子アバランシェダイオード検出器のブレイクダウンに基づき、トリガー信号を生成するよう構成されるトリガー回路と、

ブレイクダウンにある前記検出器アレイの单一光子アバランシェダイオード検出器の位置座標を格納するよう構成され、前記トリガー回路により生成されるトリガー信号に基づき、ラッチするよう構成されるラッチと、

を有し、

前記ラッチが、

行ラッチであって、各行ラッチが、前記検出器アレイの対応する行の单一光子アバランシェダイオード検出器の論理的「OR」組合せに接続される、行ラッチと、

列ラッチであって、各列ラッチが、前記検出器アレイの対応する列の单一光子アバランシェダイオード検出器の論理的「OR」組合せに接続される、列ラッチとを有する、装置。

## 【請求項 13】

光子の衝突に基づきブレイクダウンするよう構成される单一光子アバランシェダイオード検出器を含む検出器アレイを提供するステップと、

ブレイクダウンにある前記検出器アレイの单一光子アバランシェダイオード検出器の位置座標を格納するよう構成されるラッチを提供するステップと、

前記検出器アレイの单一光子アバランシェダイオード検出器のブレイクダウンに基づき、トリガー信号を生成するステップと、

前記トリガー信号の生成をもたらしたブレイクダウンのあった前記单一光子アバランシェダイオード検出器の位置座標を前記ラッチが格納することを確実にするのに有効な遅延インターバル分、前記ラッチへの前記トリガー信号の伝搬を遅延させるステップと、

前記トリガー信号に基づき、前記ラッチをラッチするステップと、

前記ラッチした後、前記トリガー信号の生成をもたらしたブレイクダウンのあった前記单一光子アバランシェダイオード検出器の位置を決定するため、前記ラッチを読み出すステップと、

を有する方法。

## 【発明の詳細な説明】

## 【技術分野】

10

20

30

40

50

## 【0001】

本願は、放射線検出技術に関する。本願はより詳細には、物理学、天文学、陽電子放出断層撮影（P E T）又は単一光子放出断層撮影（S P E C T）といった放射線撮像等の用途に関する高速の及び高い空間分解能の放射線検出器に関する。

## 【背景技術】

## 【0002】

光子計数光検出は、例えば物理学、天文学及び医療撮像といった多様な分野において用途を見い出す。いくつかの説明的な例を用いて、光子計数光検出は、チエレンコフ計数管といった物理学用途、例えば光検出及び測距（L I D A R）用途といった工学技術用途、例えば弱蛍光測定、弱光天体望遠鏡施設といった生物学用途等において有益である。（本書で使用される、用語「光子」は、電磁放射線の量子粒子を指す。用語「光子」は、可視光光子、例えば632.8 nmのHe Neレーザー光の1つの量子粒子に対応する1.96 eVの光子を含む。用語「光子」は、可視スペクトル外にある「光」又は電磁気エネルギーの量子粒子も含む。例えば、用語「光子」は、紫外線又は赤外線放射線の量子粒子も含む。）

10

## 【0003】

光子計数は従来は、光電子増倍管（P M T）検出器を用いて実現される。これは、光電性の光電陰極及び「増倍管」陽極端子のセットを有する。光電陰極は、光子の衝突に応じて少なくとも1つの電子を放出し、この電子は続いて、連続した陽極端子にぶつかる。斯かる各イベントは、カスケード状の電子放出をもたらし、測定可能な電気パルスを生じさせる増倍効果が生成される。P M Tは、高速光子計数が可能である。P M T検出器は、高い電圧で作動し、かつ真空管設計及び高い操作電圧による故障に影響されやすい大きな光学ウインドウを持つ比較的大きな別々のデバイスであるという不利な点を持つ。

20

## 【0004】

シリコン光電子増倍管（S i P M）デバイスは、これらの不利な点のいくつかを克服するため、及びシリコンベースの信号 / データ処理回路に容易に集積される光子計数検出器を提供するために開発された。いくつかの実施形態において、S i P Mデバイスは、光センサとしてアバランシェフォトダイオードを使用する。そのブレイクダウン電圧以上にバイアスされるとき、アバランシェダイオードは、単一光子の衝突に応じてブレイクダウンに入る。斯かるデバイスは、単一光子アバランシェダイオード（S P A D）検出器と呼ばれることがある。典型的なS P A D検出器において、アバランシェフォトダイオードは、そのブレイクダウン電圧以上に逆バイアスされ、クエンチングレジスタと直列にある。単一光子の衝突は、測定可能な電流としてS P A D検出器に流れる電子の倍数的な（即ち「アバランシェ」）カスケードにおいて、P N接合がブレイクダウンすることをもたらす。この電流は、比較的迅速にクエンチされる。なぜなら、電流が原因によるレジスタにわたる電圧が、そのブレイクダウン電圧を下回るレベルまで、アバランシェダイオードにわたる逆バイアスを低下させるからである。追加的に又は代替的に、（例えば）1つ又は複数のダイオード、レジスタ及び / 又はトランジスタを有するアクティブクエンチングサブ回路が、より急速なクエンチングを提供することができる。

30

## 【0005】

40

S P A D検出器は、比較的小さい。しかし、より大きな領域検出が、S P A D検出器の二次元アレイにより実現されることができる。読み出しは、アナログ又はデジタルとすることができる。アナログ設計において、任意の1つのS P A D検出器のブレイクダウンが論理的「O R」の組合せを作動させるよう、S P A D検出器は論理的「O R」回路において相互接続される。デジタル設計において、アレイは、積分期間後読み出されるデジタルカウンタを作動させる。いずれの場合でも、読み出し回路は、単一のチャネルを持つ。

## 【0006】

例えばタイムオブフライト陽電子放出断層撮影（P E T）撮像といったいくつかの用途では、検出の時間が重要である。有利には、時間デジタル変換（T D C）回路を含むシリコンベースの時間スタンプ機能が、この目的のためにシリコン・プラットフォーム上でS

50

P A D アレイにモノリシック的に一体化される。

【発明の概要】

【発明が解決しようとする課題】

【0007】

しかしながら、S P A D アレイを備えつつ高い空間分解能を実現することは、困難である。S P A D 検出器の論理的「O R」組合せを使用する既存のデザインは、組合せのどのS P A D 検出器が光子を検出したかを区別することができない。可能性のあるソリューションは、各S P A D 検出器に関して個別的読み出し回路を提供することである。しかしながら、これは、システム複雑さ及びコストを上昇させる。なぜなら、各S P A D 検出器が、それ自身の読み出しチャネルを持つからである。S P A D アレイを備えつつ高い空間分解能及び高い時間分解能を実現することは、さらに困難である。各S P A D 検出器に関して個別的読み出し及び個別的時間スタンピングを提供することは、通常は実際的でない。 10

【0008】

本願は、上述した限界及びその他を克服する改良された装置及び方法を想定する。

【課題を解決するための手段】

【0009】

1つの側面によれば、ある装置は、光子検出器を有し、この光子検出器は、光子の衝突に基づき、ブレイクダウンするよう構成される単一光子アバランシェダイオード(SPAD)検出器を備える検出器アレイと、上記検出器アレイのS P A D 検出器のブレイクダウンに基づき、トリガー信号を生成するよう構成されるトリガー回路と、ブレイクダウンにある上記検出器アレイのS P A D 検出器の位置座標を格納するよう構成され、上記トリガー回路により生成されるトリガー信号に基づき、ラッチするよう構成されるラッチとを含む。 20

【0010】

別の側面によれば、ある方法が、光子の衝突に基づきブレイクダウンするよう構成される単一光子アバランシェダイオード(SPAD)検出器を含む検出器アレイを提供するステップと、ブレイクダウンにある上記検出器アレイのS P A D 検出器の位置座標を格納するよう構成されるラッチを提供するステップと、上記検出器アレイのS P A D 検出器のブレイクダウンに基づき、トリガー信号を生成するステップと、上記トリガー信号に基づき、上記ラッチをラッチするステップとを有する。

【0011】

別の側面によれば、ある装置は、光子検出器を有し、この光子検出器は、単一光子アバランシェダイオード(SPAD)検出器のアレイと、ブレイクダウンにある上記アレイのS P A D 検出器の位置座標を格納するよう構成されるラッチと、上記アレイのS P A D 検出器のブレイクダウンに基づき、トリガー信号を生成するよう構成されるトリガー回路であって、上記トリガー信号が、上記ラッチがラッチすることをもたらす、トリガー回路と、上記ラッチされたラッチに格納される位置座標に基づき、光子検出位置を出力するよう構成される処理回路とを含む。 30

【0012】

別の側面によれば、ある装置は、光子検出器を有し、この光子検出器は、単一光子アバランシェダイオード(SPAD)検出器のアレイと、ブレイクダウンにある上記アレイのS P A D 検出器の位置座標を格納するよう構成されるラッチと、上記アレイのS P A D 検出器のブレイクダウンに基づきトリガー信号を生成するよう構成されるトリガー回路であって、上記トリガー信号が、上記ラッチのラッチングをもたらす、トリガー回路と、上記積分時間分上記ラッチングを遅延させる少なくとも1つの遅延要素と、上記ラッチされたラッチに格納される位置座標に基づき、上記積分時間にわたり検出される光子の検出位置を出力するよう構成される処理回路とを含む。 40

【0013】

1つの利点は、単一の(x, y)位置チャネルを持つ比較的簡単な読み出し回路を使用するS P A D アレイで、高い空間分解能を提供することにある。

【0014】

50

別の利点は、単一の(  $x$  ,  $y$  )位置チャネル及び単一の時間出力チャネルを持つ比較的簡単な読み出し回路を使用する S P A D アレイで、高い空間分解能及び高い時間分解能を提供することにある。

【 0 0 1 5 】

以下詳細な説明を読むとき、多数の追加的な利点及び利点が、当業者には明らかである。

【 図面の簡単な説明 】

【 0 0 1 6 】

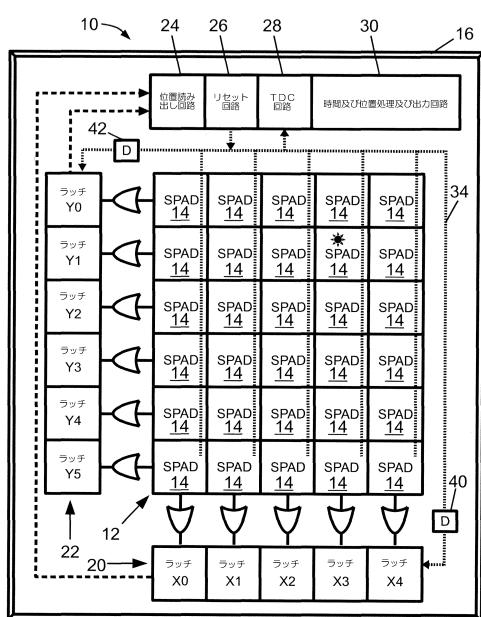

【 図 1 】 単一光子アバランシェダイオード ( S P A D ) 検出器のアレイ並びに関連付けられる空間位置読み出し及び時間スタンプ回路の俯瞰又は平面表示を図式的に示す図である。

10

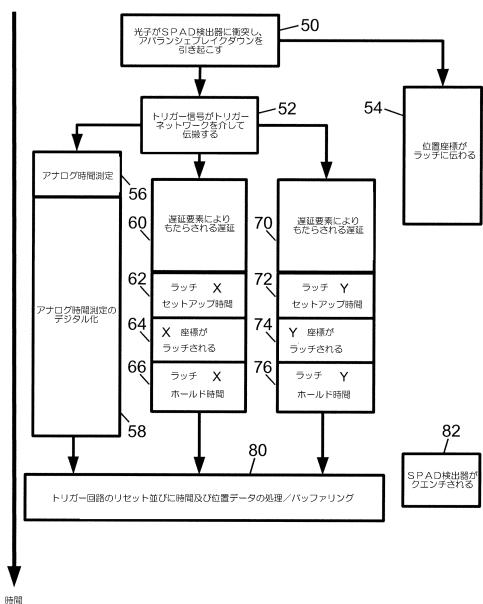

【 図 2 】 図 1 の S P A D アレイの 1 つの開示された動作モードのタイミング側面を図的に示す図である。

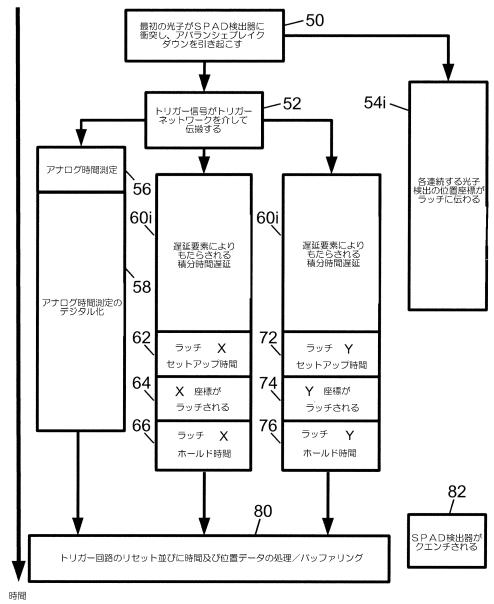

【 図 3 】 図 1 の S P A D アレイの別の開示された動作モードのタイミング側面を図的に示す図である。

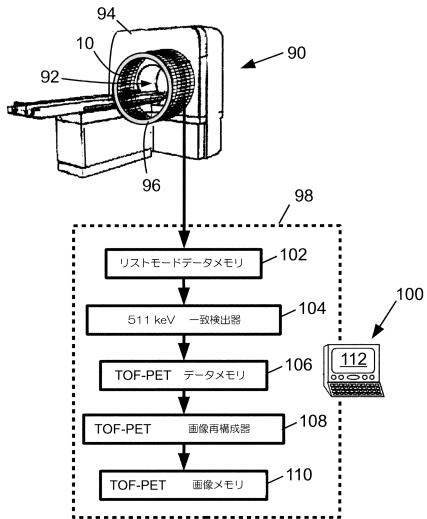

【 図 4 】 検出器として図 1 及び 2 を参照して説明される S P A D アレイを使用するタイムオブフライト ( T O F ) 陽電子放出断層撮影 ( P E T ) 撮像システムを図的に示す図である。

【 発明を実施するための形態 】

【 0 0 1 7 】

20

本発明は、様々な要素及び要素の配列の形式を取り、様々な処理動作及び処理動作の配列の形式を取ることができる。図面は、好ましい実施形態を説明するためだけにあり、本発明を限定するものとして解釈されるべきものではない。

【 0 0 1 8 】

図 1 を参照すると、光子検出器 1 0 は、単一光子アバランシェダイオード ( S P A D ) 検出器 1 4 のアレイを含む検出器アレイ 1 2 を有する。各 S P A D 検出器 1 4 は、そのブレイクダウン電圧以上に逆バイアスされ、クエンチング回路に接続されるアバランシェダイオードを適切に有する。クエンチング回路は例えば、いくつかの実施形態において、アバランシェダイオードと直列に電気的に配置される受動的なクエンチングレジスタ、又はアクティブトランジスタベースのクエンチング回路 ( 詳細は図示省略 ) である。 S P A D 検出器は、光子計数又はガイガーモードにおいて作動する。このモードでは、アバランシェダイオードでの単一光子の衝突が、ブレイクダウン、それに伴う電子増倍及び実質的な電流フローを生成する。これは、クエンチング回路によりクエンチされる。説明的な検出器アレイ 1 2 は、 $X_0 \sim X_4$  でインデックス化された 5 つの列及び  $Y_0 \sim Y_5$  でインデックス化された 6 つの行の矩形のアレイを有する。これは単に説明的なものであり、検出器アレイは、実質的に任意の数の行及び列を持つことができる。

30

【 0 0 1 9 】

説明的な光子検出器 1 0 は、シリコン基板 1 6 上に製造されるシリコンベースのデバイスである。これは、検出器アレイ 1 2 が、補助的なシリコンベースの要素を持つシリコン基板 1 6 上にモノリシック的に一体化されることを可能にする。補助的な要素は例えば、説明的なシリコンベースの列読み出しラッチ 2 0 ( 列座標が説明的な実施形態では  $X$  で表される ) 、説明的なシリコンベースの行読み出しラッチ 2 2 ( 行座標が説明的な実施形態では  $Y$  で表される ) 、説明的なシリコンベースの位置読み出し回路 2 4 、説明的なシリコンベースのリセット回路 2 6 、説明的なシリコンベースの時間デジタル変換 ( T D C ) 回路 2 8 、及び説明的なシリコンベースの時間及び位置の処理及び出力回路 3 0 である。これらの様々な要素 1 4 、 2 0 、 2 2 、 2 4 、 2 6 、 2 8 、 3 0 が、説明的な実施形態においてシリコンベースであるが、これらのシリコンベースの要素は、様々な酸化物、絶縁体又は誘電体 ( 例えば、シリコン酸化物、窒化物、酸化窒化物、又は非シリコン含有誘電体 ) といった非シリコン及び / 又はシリコン合金材料、様々なシリコン合金 ( 例えば、シリコンゲルマニウム又はシリコンゲルマニウム炭素合金 ) 、金属又は金属合金の層等を含む

40

50

ことができる点を理解されたい。更に、様々な回路が、別々の要素、集積回路（I C）又はこれらの様々な組み合わせにより、多様な態様で実現されることがある。

#### 【0020】

説明的な光子検出器10は、光子検出イベントに関する高い空間分解能（光子を検出した個別のS P A D 検出器14に対して通常は下がる）及び光子検出イベントに関する高い時間分解能（例えば、T D C 回路28の分解能又はこれに近い時間分解能）を可能にする読み出し回路を使用する。この目的のため、検出器アレイ12のS P A D 検出器14は、行及び列において電気的に相互接続される。ここで、各行ラッチ22（ラッチY0...Y5）は、検出器アレイ12の対応する行のS P A D の論理的「O R」組合せに接続され、各列ラッチ20（ラッチX0...X4）は、検出器アレイ12の対応する列のS P A D 検出器の論理的「O R」組合せに接続される。

10

#### 【0021】

説明的な図1において、（ラッチ20、22との論理的「O R」接続は、論理的「O R」ゲート要素シンボルを用いて、図式的に示される。しかしながら、本明細書で用いられる用語「論理的O R」が、検出器の論理的「O R」組合せのS P A D 検出器の1つがブレイクダウン状態にあるときいつでも、値としての「真」又は「オン」又は「アクティベーテッド」（その他）を出力する任意の包含的選言又は代替を含む点を理解されたい。論理的「O R」組合せの特有の実現は、論理的「O R」ゲート要素を使用しても、又は使用しなくてもよい。例えば、検出器の論理的「O R」組合せは、ド・モルガンの法則に基づき、論理的「N O T」及び論理的「N A N D」ゲート要素の組合せにより実現されることが可能。「ワイヤードO R」実施形態において、S P A D 検出器は、論理的「O R」を実現するため、一緒に物理的に有線接続される。

20

#### 【0022】

読み出し回路は、トリガー回路34も含む。これは、図1において鎖点入りのラインにより図式的に示される。トリガー回路は、検出器アレイ12のすべてのS P A D 検出器14に接続され、検出器アレイ12の任意のS P A D 検出器14のブレイクダウンは、トリガー回路34にトリガー信号を生成させる。言い換えると、トリガー回路34は、検出器アレイ12のS P A D 検出器14のブレイクダウンに基づき、トリガー信号を生成するよう構成される。トリガー信号は、トリガー回路34を介して、時間スタンプの生成が起動されるT D C 回路28へと、及びラッチ20、22へと伝搬する。ここで、この信号は、ラッチ20、22がラッチすることをもたらす。従って、検出器アレイ12の任意のS P A D 検出器14が光子及び従ってブレイクダウンを検出するとき、それは、トリガー回路34上でトリガー信号を生成し、平行して、ラッチは、ブレイクダウンを受けるS P A D 検出器14の位置を格納する。

30

#### 【0023】

図1を引き続き参照すると、図の例では、アスタリスク（\*）が、検出器アレイ12の行Y1及び列X3のS P A D 検出器14に示される。このブレイクダウンは、列ラッチ22のラッチY1及び行ラッチ20の行ラッチX3が、「真」又は「オン」又は「アクティベーテッド」を示す値を格納することをもたらす。同時に、行Y1及び列X3でのS P A D 検出器14のブレイクダウンは、トリガー回路34が、トリガー信号を生成することをもたらす。この信号は、時間スタンプを生成するため、T D C 回路28へと、及びラッチY1及びX3の「真」又は「オン」又は「アクティベーテッド」を示す値を保存するべく、ラッチ20、22のラッチをもたらすため、ラッチ20、22へと伝搬する。位置読み出し回路24は、適切な（及びオプションで比較的ゆっくりした）読み出し技術を用いて、ラッチ20、22から、これらの位置値を読み出すことができる。この技術は例えば、ラッチ20、22のビットパターンを、バイナリ数又は他の位置表現へと変換するルックアップテーブル又は経時的なカウンタである。

40

#### 【0024】

この読み出し手法は、ラッチ/位置読み出し動作の前にラッチ20、22に格納されるS P A D 検出器14のブレイクダウンに依存する。トリガー信号伝搬及びラッチ格納動作

50

の相対的な速度に基づき、動作のこの順序は、自然に発生することができる（例えば、論理的「OR」接続及びラッチ20、22が、トリガー回路34より実質的に速く作動する場合）。しかしながら、高い時間分解能に関して、高分解能時間スタンプを得るため、トリガー回路34が、実行可能な態様で速く作動することが望ましい。

【0025】

従って、説明的な実施形態において、ラッチするときラッチ20、22がSPAD検出器14の位置座標を格納することを確実にするのに実効的な量の分、ラッチ20、22へのトリガー信号の伝搬を遅延させるため、遅延要素40、42が提供される。この検出器のブレイクダウンが、トリガー回路34が、トリガー信号を生成することをもたらす。個別のラッチ20、22に関する遅延を提供するのに、説明的な図2では2つの遅延要素40、42が示されるが、トリガー回路の物理的な配置に基づき、単一の遅延要素を用いることが可能である（例えば、ある遅延要素があり、この後ろで、行及び列ラッチをファイドするため、送信ラインが中断する）。

10

【0026】

図1及び更に図2を参照すると、光子検出器10の動作が更に説明される。イベント50において、光子は、検出器アレイ12のSPAD検出器14に衝突する。これが、そのSPAD検出器14のアバランシェブレイクダウンをもたらす。このブレイクダウンは、2つの異なる結果を生じさせる。結果52において、ブレイクダウンは、トリガー回路34にトリガー信号を生成及び伝搬させる。結果54において、ブレイクダウンは、個別の列及び行ラッチ20、22に対して論理的「OR」接続を介して、ブレイクダウンを経験するSPAD検出器14の位置座標が伝搬することをもたらす。

20

【0027】

トリガー信号は続いて、3つの結果のイベントチェーンをもたらす。第1のイベントチェーンにおいて、トリガー信号は、TDC回路28に伝搬する。ここで、この信号は、TDC回路28が時間スタンプを生成することをもたらす。説明的な図2において、時間スタンプ動作は、2つのサブ動作を伴う。それは、アナログ時間測定56と、デジタル時間スタンプを生成するためアナログ時間測定がデジタル化されるデジタル化動作58とである。アナログ時間測定56は、遅延送信ライン、リング発振器等の任意のイベント時間測定技術を利用することができます。デジタル化動作58は、アナログ時間測定をデジタル化する。通常、アナログ時間測定は、高い時間分解能を提供する精細な時間測定を提供する。いくつかの実施形態においてデジタル化動作58は、デジタル時計の拡張された時間スケール上で高分解能時間スタンプを生成するため、デジタル時計（これは、送信遅回路、リング発振器又は他の精細なアナログ時間測定と比較して粗い時間測定を提供する）の値に、この精細な（デジタル化された）時間測定を加える。

30

【0028】

トリガー信号によりもたらされる第2のイベントチェーンにおいて、列（即ち、X）位置座標は、トリガー信号に基づき、列（X）ラッチ20によりラッチされる。このイベントチェーンは、オプションの遅延要素40により導入されるオプションの初期遅延60を含む。図2に示されるタイミングにおいて、遅延60は、ラッチ20、22への位置座標伝搬54が、ラッチ動作の前に完了されることを確実にする。この動作は、列（X）ラッチ20のラッチ64に先行するするセットアップ時間62と、その後のホールド時間66とを含む。セットアップ及びホールド時間62、66は、列ラッチ20の設計により決定され、ラッチ動作に先行する及び後続する時間インターバルである。この間、ラッチ20に格納される値は、ラッチ動作64の完全性を確実にするため、安定しているべきである。

40

【0029】

トリガー信号によりもたらされる第3のイベントチェーンにおいて、行（即ち、Y）位置座標は、トリガー信号に基づき、行（Y）ラッチ22によりラッチされる。このイベントチェーンは、オプションの遅延要素42により導入されるオプションの初期遅延70を含む。図2に示されるタイミングにおいて、遅延70は、ラッチ20、22への位置座標

50

伝搬 5 4 が、ラッチ動作の前に完了されることを確実にする。この動作は、行( Y )ラッチ 2 2 のラッチ 7 4 に先行するセットアップ時間 7 2 と、後続のホールド時間 7 6 を含む。セットアップ及びホールド時間 7 2 、 7 6 は、行ラッチ 2 2 の設計により決定され、ラッチ動作に先行する及び後続する時間インターバルである。この間、ラッチ 2 2 に格納される値は、ラッチ動作 7 4 の完全性を確実にするため、安定しているべきである。

#### 【 0 0 3 0 】

図 2 に示されるラッチ動作要素 6 2 、 6 4 、 6 6 、 7 2 、 7 4 、 7 6 は、単に説明的なものであり、詳細なラッチ動作は、ラッチ 2 0 、 2 2 の設計及び特性に基づき変化することができる。更に、図 2 は、持続時間に関して同一であるものとして、行及び列ラッチイベントチェーンを示すが、行及び列ラッチイベントチェーンがいくらか異なるタイミング特性を持つことも想定される。 10

#### 【 0 0 3 1 】

図 2 に示される図式的な動作 8 0 は、光子検出処理及び出力を完了するときに伴われる動作を集合的に示す。動作 8 0 は、トリガー回路 3 4 のリセット(図 1 において図式的に示されるリセット回路 2 6 により実行される)、並びに光子検出イベントに関する時間及び位置データの処理及びバッファリング(図 1 において図式的に示される時間及び位置処理及び出力回路 3 0 により実行される)を含む。

#### 【 0 0 3 2 】

S P A D 検出器がブレイクダウンした後いくらかの時間において、S P A D 検出器のクエンチングサブ回路が、それをクエンチ及びリセットすることをもたらす。クエンチ時間 8 2 が、図 2 に図式的に示される。このクエンチ時間は、S P A D 検出器のアバランシェダイオードが、非導電性逆バイアス状態に戻る時間を示す。クエンチ時間 8 2 で、S P A D 検出器は、再び別の光子を検出する用意が整う。しかしながら、クエンチ時間 8 2 では、S P A D 検出器はもはや、ブレイクダウンにはない。従って、ラッチ動作 6 2 、 6 4 、 6 6 、 7 2 、 7 4 、 7 6 は、クエンチ時間 8 2 の前に完了されなければならない。他方、時間スタンプデジタル化 5 8 及び完了動作 8 0 は、クエンチ時間 8 2 の前及び / 又は後に実行ができる。言い換えると、一旦アナログ時間測定 5 6 及びラッチ 6 2 、 6 4 、 6 6 、 7 2 、 7 4 、 7 6 が完了すると、時間的及び空間分解能は、実現され、残りのデータ処理は、S P A D 検出器クエンチングにより課される積極的な時間制約条件下にはない。他方、デジタル化 5 8 、処理 8 0 及びクエンチング(クエンチ時間 8 2 で終わる) 30 を出来るだけ早く完了することは、有利である。なぜなら、これらの動作が完了するまで、S P A D 検出器は、別の光子を検出するために用いられることがないからである。

#### 【 0 0 3 3 】

(完了動作 8 0 に含まれる)トリガー回路 3 4 をリセットするタイミングは、トリガー回路 3 4 の動作に依存する。トリガー回路 3 4 が、ブレイクダウンに移行する S P A D 検出器に応じて、トリガー信号を生成する場合、S P A D 検出器がクエンチされる前に、トリガー回路 3 4 をリセットすることが可能である。他方、トリガー回路 3 4 が、ブレイクダウンにある S P A D 検出器に応じて、トリガー信号を生成する場合、S P A D 検出器がクエンチされた後まで(即ち、図 2 に示されるクエンチ時間 8 2 の後まで)、トリガー回路 3 4 はリセットされることができない。 40

#### 【 0 0 3 4 】

完了動作 8 0 のリセット部分は、ラッチ 2 0 、 2 2 をアンラッチすることも含む。これは一般に、ラッチされた位置データが処理及びバッファリングされた後の任意の時間で実行ができる。いくつかの実施形態において、例えばホールド時間 6 6 、 7 6 が完了した後、ラッチ 2 0 、 2 2 は自動的にアンラッチすることができる。他の実施形態において、リセット回路 2 6 は、ラッチ 2 0 、 2 2 をアンラッチするため、信号を送信する。完了動作 8 0 のリセット部分はオプションで、例えばラッチ 2 0 、 2 2 に対して適切な制御信号を送信するリセット回路 2 6 により、ラッチ 2 0 、 2 2 に格納される値をリセットすることも含むことができる。代替的に、ラッチ 2 0 、 2 2 が、ラッチする前に 0 - > 1 及び 1 - > 0 への移行に従うタイプである場合、ラッチ 2 0 、 2 2 に格納される値は、 50

一旦ブレイクダウンにある S P A D 検出器がクエンチされると（即ちクエンチ時間 8 2 になれば）自動的にリセットすることができる。なぜなら、この時間で、ラッチに結びつけられる論理的「O R」が、論理的「O R」の組合せにおいて S P A D 検出器のいずれもが、ブレイクダウンないことを示す「偽」又は「オフ」又は「ディアクティベーテッド」（等）の値に戻るからである。

【0035】

図 2 を参照して説明される光子検出器 1 0 の動作は、高い空間及び時間分解能を持つ単一光子計数能力を提供する。衝突する光子流量が十分に低い用途に関して、連続した入力光子の間の平均時間が図 2 を参照して説明される処理の時間より長いことが、有効である。2 つの光子が一緒に到達することがたまに起きるが、これは、斯かるイベントの結果が、2 つの列ラッチ又は2 つの行ラッチをセットすることである限り収容されることができる。従って、これは、完了動作 8 0 により検出されることが可能、データは、放棄又は適切に調整されることができる。

10

【0036】

いくつかの用途において、少なくとも関心時間インターバルにわたり、衝突する光子流量はより高くなることができる。その結果、図 2 を参照して説明される処理が、連続した光子検出イベントの間のインターバルの間に完了されることはできない。例えば、シンチレータにより検出される放射線粒子に基づき、光子の短いバースト（即ち、シンチレーションイベント）を生成するシンチレータと連動して光子検出器 1 0 用いられるとき、斯かる状態は起こることができる。別の用途例は、低い強度であるが、図 2 の手法を使用するほど低くはない光状態の下での撮像である。

20

【0037】

図 1 及び更に図 3 参照すると、斯かるより高い光子流量用途に関して、別の動作モードが使用されることができる。このタイミングは、図 3 に図式的に示される。図 2 の操作モードにおいて、ラッチ 6 2、6 4、6 6、7 2、7 4、7 6 が実行される前に、位置データがラッチ 2 0、2 2 に格納されることを確実にするため、遅延 6 0、7 0 がオプションで含まれる。図 3 の実施形態において、これらの遅延 6 0、7 0 は、遅延要素 4 0、4 2 により再び適切に実現されるより長い積分時間遅延 6 0 i により置換される。言い換えると、遅延要素 4 0、4 2 により導入される遅延時間 6 0 i は、積分時間を提供するため、図 3 の実施形態においてより長い。図 3 の実施形態において、行及び列位置データが同じ時間 6 0 i に関して積分されるよう、両方の遅延要素 4 0、4 2 により同じ遅延時間 6 0 i が導入されることも有利である。（前述したように、いくつかの想定された実施形態において、これは、個別の列及び行ラッチ 2 0、2 2 に関する遅延要素 4 0、4 2 を单一の遅延要素として構築することにより実現される。ここで、ラッチ信号が、その单一の遅延要素からラッチ 2 0、2 2 の両方のセットへと枝分かれする。）

30

【0038】

遅延時間 6 0 i は、光子検出イベントに関する位置データが累算される積分時間を提供するよう選ばれる。図 3 の実施形態において、1 つ以上の光子が積分時間 6 0 i の間、検出器アレイ 1 2 に衝突するよう、光子の入力流量が十分高いと設定される。各光子検出イベントは、光子を検出する S P A D 検出器 1 4 が、ブレイクダウン状態に入り、その位置データをラッチ 2 0、2 2 にロードすることをもたらす。積分時間 6 0 i が終わった後、光子検出イベントに関する位置データをラッチするため、図 2 を参照してすでに説明されたように、ラッチ 6 2、6 4、6 6、7 2、7 4、7 6 が実行される。平行して、動作 5 6、5 8 は、図 2 を参照して説明されるよう作動するが、第 1 の光子検出イベントによってのみ起動される。その結果、結果として生じるデジタル時間スタンプは、第 1 の光子検出イベントに対するものである。

40

【0039】

積分時間 6 0 i にわたりすべての光子検出イベントに関する位置データを累算するため、ラッチが発生するまで、ラッチ 2 0、2 2 に格納される位置データは保持されるべきである。これは、クエンチ時間 8 2 が（説明的な図 3 の実施形態に示される）積分時間 6 0

50

$i$  の終了後に発生する場合、自然に発生する。なぜなら、その場合、ブレイクダウンにあるアバランシェダイオードは、ラッチする時にまだクエンチしていないことになるからである。他方、クエンチ時間が、積分時間 60i より短い場合、ラッチ 20、22 は、「真」又は「オン」又は「アクティベーテッド」(等) の値を保持するタイプであるべきで、S P A D 検出器のクエンチングの際リセットしない。(言い換えると、ラッチは、0 -> 1 移行に追従するべきだが、0 -> 1 移行に追従するべきではない)。この場合、アバランシェダイオードのクエンチングの際、ラッチは「偽」又は「オフ」又は「ディアクティベーテッド」に戻らない。(斯かるラッチは、図 2 の実施形態においても用いられることができるが、斯かるラッチが用いられるときはいつでも、完了動作 80 のリセット部分が、ラッチ 20、22 に格納される値をリセットすることを含むべきである点に留意されたい)。

10

#### 【 0 0 4 0 】

図 3 の実施形態において、完了回路 80 は、有益な位置情報を生成するため、データを処理する。いくつかの実施形態において、これは、各光子検出イベントに関する (X, Y) 座標を決定することを伴う。こうして、これらのイベントの「マップ」が生成される。他の実施形態において、完了回路 80 は、光子検出イベントのセットのセンター測定(例えば、中心軌跡又は重心)及び / 又は幅測定(例えば、空間半値全幅若しくは F W H M、又は最大拡散)といった、光子検出イベントのいくつかの統計的集合を生成するために、データを処理する。

#### 【 0 0 4 1 】

20

図 3 の実施形態において、完了回路 80 は、複数の光子検出イベントに関する位置データの曖昧さを完全になくすことができない場合がある。例えば、列ラッチ X1 及び X2 が「オン」で、行ラッチ Y1 及び Y2 が「オン」である場合、これは、以下の光子検出イベントセットのいずれかに対応することができる。[(X1, Y2) 及び (X2, Y1)]、又は [(X1, Y1) 及び (X2, Y2)]、又は、[(X1, Y2) 及び (X2, Y1)]、並びに (X1, Y1) 及び / 又は (X2, Y2) の一方又は両方]、又は [(X1, Y1) 及び (X2, Y2)]、並びに (X1, Y2) 及び / 又は (X2, Y1) の一方又は両方]。明確に結論付けられることは、この  $2 \times 2$  の S P A D 検出器方形において、2 ~ 4 の光子イベントが起こったということである。この曖昧な状態は、適切な近似の処理により完了回路 80 において処理可能 (addressable) である。この処理は例えば、光子検出イベントの位置として、曖昧な  $2 \times 2$  S P A D 検出器方形の 2 又は 3 つの S P A D 検出器をランダムに選択することである。一般に、積分時間 60i 及び入射する光子流量が、検出器アレイ 12 にわたる光子検出イベントの分布がまばらなであるようなものである場合、図 3 の手法は、(上述した曖昧性を回避する意味において) 最も有効であると予想される。これは、任意の単一の行又は列に沿った 2 つ又はこれ以上の光子検出イベントの発生が(あったとしても) ほとんどないことを意味する。

30

#### 【 0 0 4 2 】

位置データの曖昧さをより正確になくすための別の手法は、スイッチトキャパシタ又は送信ゲートといったストレージ要素(図示省略)にこれらのデータを高速でラッチすることにより、検出器アレイ 12 の行及び列をサンプリングすることである。ここで、ラッチングは、トリガー回路 34 により生成されるトリガー信号により開始される。サンプリングが、(光子検出イベントの平均レートと比較して) 十分高速である場合、ラインがその状態を変化させた時間が記録され、記録された時間は、トリガー信号に対する光子の到着の時間を決定するだけでなく、行及び列位置を相關させるために用いられることができる。

40

#### 【 0 0 4 3 】

複数の光子検出イベントによる曖昧性が、図 2 の操作モードにおいても可能であり、1 つ又は複数の追加的な光子がイベント 50、52 の時間及び遅延 60、70 の終了の間で検出される場合に発生することもできる点に留意されたい。しかしながら、これらの遅延 60、70 は短い。これは、複数の光子を検出する可能性を減らす。また、図 2 の操作モ

50

ードは通常、入射光子流量が低い用途において使用される。それにもかかわらず、図2の操作モードにおいて発生する場合、斯かる曖昧な状態は、容易に検出される。なぜなら、完了回路80が、対応するラッチが「真」又は「オン」又は「アクティベーテッド」（その他）の値を格納する2つ又はこれ以上の行及び/又は2つ又はこれ以上の列を検出するからである。斯かる場合、処理及び出力回路30は、（トリガー回路34により生成されるトリガー信号に基づくラッチングの後）2つ又はこれ以上のS P A D 検出器がブレイクダウンにあることを示すラッチに基づき、エラー信号を出力するよう適切に構成される。

#### 【0044】

開示された光子検出器10は、高い空間及び高い時間分解能を提供する。いくつかの実施形態において、高い時間分解能は、必要ではないか、又は、実際的に実現可能である。例えば、図3に適合する実施形態において、処理56、58により生成される時間スタンプは、積分時間60iの開始に対応する。時間分解能は、積分時間60iにより制限され、デジタル時間スタンプの時間分解能が、積分時間60iより実質的に精細であることは有益でない。斯かる場合、処理56、58はオプションで省略されることができ、T D C回路28は、（例えば）取得された光子検出イベントデータの現在のクロックサイクルを単に記録することにまで簡単化される。いくつかの斯かる実施形態において、T D C回路28は、完全に省略されることができ、時間スタンピングは、このデータに時間スタンプを割り当てるにより「オフチップ」で実行されることができる。なぜなら、これは、シリコンチップ又は基板16から離れて通信されるからである。

#### 【0045】

開示された光子検出器は、物理学、天文学、陽電子放出断層撮影（P E T）又は単一光子放出断層撮影（S P E C T）といった放射線撮像等において、多様な用途を見いだす。

#### 【0046】

図4を参照すると、陽電子放出断層撮影（P E T）撮像用途が、説明的な例として図式的に示される。この用途において、P E Tスキャナ90は、関心領域92を囲むリングとして配置される複数の開示された光子検出器10を含む。P E T検出器リングは、筐体又はガントリー94に適切に取り付けられ、シンチレータリング96が、光子検出器10のリングの内部に配置される。その結果、関心領域92に配置されるP E T撮像対象物から放射する511k e Vの粒子が、近接する光子検出器10により検出される光子のバースト（即ち、シンチレーション）を生成するため、シンチレータリング96により吸収される。この用途において、図3の積分操作モードは、最も有益になりそうである。しかし、低光子収率を持つ（例えば、各511k e Vのシンチレーションにおいて、わずか1又は2、3の光子を放出する）薄いシンチレータと連動して、図2の操作モードを使用することも想定される。

#### 【0047】

結果として生じるP E Tデータは、例えば、適切にプログラムされたコンピュータ100として実現される電子部品処理デバイス98により処理される。デジタル時間スタンプ及び（積分時間60iの間に検出される光子の数から推定される）粒子エネルギーと共に、光子検出イベント（又は、図3の操作モードにおいて決定される光子検出イベントのマップのセンター）は、リストモードデータメモリ102に格納されるリストモードP E Tデータを形成する。511k e Vの一一致検出器104は、適切な時間的及びエネルギーインドウ化を用いて、リストモードデータにおいて一致する511k e Vの検出イベントを特定する。一致する511k e Vの検出イベントの各ペアは、ラインオブレスポンス（L O R）を規定し、供給電子ホール消滅イベントは、タイムオブフライト（T O F）データとしての時間スタンプを用いて、L O Rに沿って局所化されることができる。T O F - P E Tデータは、メモリ106に格納され、再構成画像を形成する適切なP E T撮像データ再構成プロセッサ108により再構成される。この画像は、メモリ110に適切に格納され、コンピュータ100のディスプレイ112に表示され、又は、他の態様で利用される。

#### 【0048】

10

20

30

40

50

図4は、PET用途を示すが、より一般には、開示された光子検出器は、放射線撮像システムと共に用いられることができる。例えば、説明的なPETスキャナ90、又は関心領域の周りで放射線検出器ヘッドの周りを回るよう構成されるロボットアーム又はガントリーに取り付けられるガンマカメラの放射線検出器ヘッドの光子検出器と共に用いられることができる。

【 0 0 4 9 】

本発明が、好ましい実施形態を参照して説明されてきた。もちろん、上記の説明を読み、理解すれば、他者は修正及び変更を思いつくであろう。それらの修正及び変更が添付の特許請求の範囲又はその均等物の範囲内にある限り、本発明は、すべての斯かる修正及び変更を含むものとして構築されることが意図される。

10

( 1 )

( 2 )

【図3】

【図4】

---

フロントページの続き

(51)Int.Cl. F I

H 01 L 31/10 (2006.01) G 01 T 1/161 C

H 01 L 31/10 G

(74)代理人 100163809

弁理士 五十嵐 貴裕

(72)発明者 フラヒ トマス

オランダ国 5 6 5 6 アーエー アインドーフェン ハイ テック キャンパス ビルディング

4 4

審査官 松永 隆志

(56)参考文献 特表2009-544973 (JP, A)

特表2008-536600 (JP, A)

(58)調査した分野(Int.Cl., DB名)

H 04 N 5 / 3745

G 01 T 1 / 161

G 01 T 1 / 17

G 01 T 1 / 20

G 01 T 1 / 24

H 01 L 31 / 10