# WORLD INTELLECTUAL PROPERTY ORGANIZATION International Bureau

#### INTERNATIONAL APPLICATION PUBLISHED UNDER THE PATENT COOPERATION TREATY (PCT)

(51) International Patent Classification 6: G06F 9/02, 13/20, 13/10, 13/36, 13/40, 13/42, 15/16, 15/163, 15/173

(11) International Publication Number:

WO 96/35988

(43) International Publication Date: 14 November 1996 (14.11.96)

(21) International Application Number:

PCT/US96/06562

A1

(22) International Filing Date:

9 May 1996 (09.05.96)

(81) Designated States: AU, CA, GB, JP, KR, European patent (AT, BE, CH, DE, DK, ES, FI, FR, GB, GR, IE, IT, LU, MC, NL, PT, SE).

(30) Priority Data:

08/438,897 08/599,473

10 May 1995 (10.05.95) 23 January 1996 (23.01.96) US US **Published**

With international search report.

(71) Applicant: 3COM CORPORATION [US/US]; 5400 Bayfront Plaza, P.O. Box 58145, Santa Clara, CA 95052-8145 (US).

(72) Inventors: ISFELD, Mark, S.; 1125 Wunderlich Drive, San Jose, CA 95129 (US). MITCHELL, Bruce, W.; 5493 Tesoro Court, San Jose, CA 95124 (US). SEAMAN, Michael, J.; 632 Sylvan Avenue, Mountain View, CA 94041 (US). MALLORY, Tracy, D.; 4026 Ben Lomond Drive, Palo Alto, CA 94306 (US). ARUNKUMAR, Nagaraj; 3041 Cedar Ridge Court, San Jose, CA 95148 (US).

(74) Agents: HAYNES, Mark, A. et al.; Wilson, Sonsini, Goodrich & Rosati, 650 Page Mill Road, Palo Alto, CA 94304-1050 (US).

(54) Title: BRIDGE ROUTER FOR HIGH PERFORMANCE SCALABLE NETWORKING

#### (57) Abstract

A high peformance scalable networking bridge/router system (10-20) is based on a backbone communication medium and message passing process which interconnects a plurality of input/output modules (13-20). The input/output modules vary in complexity from a simple network interface device having no switching or routing resources on board, to a fully functional bridge/router system. A central internetworking engine (10) includes a physical layer communication system for transferring control messages and data packets across the backbone, a logical layer interprocessor messaging system which operates over the physical layer across the backbone for communication between intelligent input/output modules (13-20), and between such modules in the central internetworking engine, and distributed protocol modules which are supported on intelligent input/output modules, and communicate using the logical interprocessor messaging system with the central internetworking resources.

# FOR THE PURPOSES OF INFORMATION ONLY

Codes used to identify States party to the PCT on the front pages of pamphlets publishing international applications under the PCT.

| AM | Armenia                  | GB | United Kingdom               | MW | Malawi                   |

|----|--------------------------|----|------------------------------|----|--------------------------|

| AT | Austria                  | GE | Georgia                      | MX | Mexico                   |

| ΑU | Australia                | GN | Guinea                       | NE | Niger                    |

| BB | Barbados                 | GR | Greece                       | NL | Netherlands              |

| BE | Belgium                  | HU | Hungary                      | NO | Norway                   |

| BF | Burkina Faso             | IE | Ireland                      | NZ | New Zealand              |

| BG | Bulgaria                 | IT | Italy                        | PL | Poland                   |

| BJ | Benin                    | JP | Japan                        | PT | Portugal                 |

| BR | Brazil                   | KE | Kenya                        | RO | Romania                  |

| BY | Belarus                  | KG | Kyrgystan                    | RU | Russian Federation       |

| CA | Canada                   | KP | Democratic People's Republic | SD | Sudan                    |

| CF | Central African Republic |    | of Korea                     | SE | Sweden                   |

| CG | Congo                    | KR | Republic of Korea            | SG | Singapore                |

| CH | Switzerland              | KZ | Kazakhstan                   | SI | Slovenia                 |

| CI | Côte d'Ivoire            | LI | Liechtenstein                | SK | Slovakia                 |

| CM | Cameroon                 | LK | Sri Lanka                    | SN | Senegal                  |

| CN | China                    | LR | Liberia                      | SZ | Swaziland                |

| CS | Czechoslovakia           | LT | Lithuania                    | TD | Chad                     |

| CZ | Czech Republic           | LU | Luxembourg                   | TG | Togo                     |

| DE | Germany                  | LV | Latvia                       | TJ | Tajikistan               |

| DK | Denmark                  | MC | Monaco                       | TT | Trinidad and Tobago      |

| EE | Estonia                  | MD | Republic of Moldova          | UA | Ukraine                  |

| ES | Spain                    | MG | Madagascar                   | UG | Uganda                   |

| FI | Finland                  | ML | Mali                         | US | United States of America |

| FR | France                   | MN | Mongolia                     | UZ | Uzbekistan               |

| GA | Gabon                    | MR | Mauritania                   | VN | Viet Nam                 |

|    |                          |    |                              |    |                          |

# BRIDGE ROUTER FOR HIGH PERFORMANCE SCALABLE NETWORKING

5

10

# **BACKGROUND OF THE INVENTION**

## Field of the Invention

The present invention relates to high performance bridge/routers that supply transparent communication between a variety of types of network interfaces within a single chassis, integrating such local area network standards as Token Ring, Ethernet, FDDI, and ATM, and also supporting wide area links. More particularly, the present invention provides an internetworking device providing high performance, scalable internetworking.

# 15 <u>Description of Related Art</u>

A router is an internetworking device that chooses between multiple paths when sending data, particularly when the paths available span a multitude of types of local area and wide area interfaces. Routers are best used for (1) selecting the most efficient path between any two locations; (2) automatically re-routing around failures; (3) solving broadcast and security problems; and (4) establishing and administering organizational domains. One class of router, often called bridge/routers or Brouters, also implements switching functionality, such as transparent bridging and the like. One commercially available example of such system is known as NETBuilder II, provided by 3Com Corporation of Santa Clara, California.

25

20

Because bridge/routers are designed to interconnect a variety of networks, the volume of data flow through the router can be very high. The ability to move large amounts of data, according to a wide variety of networking protocols. makes the bridge/router a unique class of high performance data processing engines.

One problem with prior art bridge/router architectures is scalability, and another is backward compatibility. When a customer buys a prior art system, and fills up the available ports on the system, often the customer is required to buy another copy of the entire system, which may be much more than is necessary, or scrap the old

5

10

15

20

25

30

system and buying a new system with a larger number of ports. Thus, the prior art establishes plateaus in system hardware that are very expensive to cross.

The NETBuilder II architecture, which is described in the parent application from which this is a continuation in part, allows expansion on a port by port basis. However, there is a limit to the number of ports that can be mounted on the backplane bus of the NETBuilder II architecture, because this architecture requires that all of the data frames incoming through the ports get transferred across the backplane bus to a centrally shared memory and processed there.

An alternative prior art system allows for a number of sophisticated multi-port router engines to communicate with one another. Thus, the only packets that go across the link between the routers are those which must be transferred from a port on one router to a port on another. This architecture, however, requires that expansion of the system be done by adding an entire new router engine. Thus, the system does not allow incremental expansion on a port by port basis.

Accordingly, it is desirable to provide a high performance, scalable networking strategy which allows flexible growth of a switching, routing engine. Using such strategy, expertise can be brought together quickly to deliver projects or products efficiently and effectively, without requiring large scale hardware upgrades which are unsuited to the particular project or product needed. Custom applications can be developed faster and more cost effectively. The cost of incremental computing power will drop dramatically with a scalable platform. Further, the investment in current equipment and technologies is protected, while paving the way for future technologies.

# SUMMARY OF THE INVENTION

The present invention provides a high performance, scalable networking bridge/router system which overcomes many of the problems discussed above. The bridge/router architecture according to the present invention is based on a message passing system which interconnects a plurality of input/output modules. The input/output modules vary in complexity from a simple network interface device having no switching or routing resources on board, to a fully functional bridge/router

5

10

15

20

25

30

system. Also, in between these two extremes input/output modules which support distributed protocol processing with differing levels of intelligence are included.

The bridge/router architecture according to one aspect of the invention includes a central internetworking engine, including a shared memory resource coupled to the high speed backplane bus. Depending on the level of sophistication supported on the input/output module, the central internetworking engine may perform all routing decisions for packets received on a particular port, or may support distributed protocol processing at an input/output module in which certain classes of packets are routed locally on the input/output module while others are forwarded to the central engine. The architecture can be characterized as having a number of components, including a physical layer communication system for transferring control messages and data packets across the backplane bus; and a logical layer interprocessor messaging system which operates over the physical layer across the bus supporting communication between intelligent input/output modules, and between such modules in the central internetworking engine. Distributed protocol modules are supported on intelligent input/output modules, which communicate using the logical interprocessor messaging system with the central internetworking resources, and with other input/output modules on the system to make routing decisions for a majority of packets of a particular type received on such systems. As mentioned above, the central internetworking engine also supports input/output modules which only include the network interface chip and resources for communicating data across the backplane bus to the central engine, which acts as a data link layer agent for such systems. The logical layer can overlay a variety of physical layers, including in addition to a high speed bus, local area networks such as Ethernet, Token Ring, asynchronous transfer mode ATM, and others.

The centralized internetworking engine includes central distributed protocol module servers which manage the distributed protocol modules on the input/output modules, when the distributed protocol modules only partially support such protocols. Further, the centralized internetworking engine can support maintenance of synchronization between distributed protocol modules in the system. Thus, distributed protocol modules may include protocol address caches to support routing

5

10

15

20

25

30

decisions locally on the input/output module for addresses stored in the cache. The central internetworking engine according to this aspect stores the entire routing table for the particular protocol, and includes resources for responding to cache update requests from the input/output modules, and for managing routing data used in the operation of the distributed protocol modules on a plurality of input/output modules in the system. In a preferred system, the cache is loosely coupled with the central routing table, using a cache management protocol which is timer based and requests updates for stale entries in response to traffic using the stale entry.

Accordingly, the present invention can be characterized as an apparatus for interconnecting a plurality of networks. The apparatus comprises a communication medium having a physical layer protocol. A central routing processor is coupled to the physical layer. A plurality of input/output modules communicate with the central routing processor according to the physical layer protocol. The input/output modules have respective sets of physical network interfaces which support a variety of LAN and WAN network protocols. An interprocessor messaging system in a logical layer above the physical layer protocol is executed in the central routing processor and in a set of one or more intelligent input/output modules within the plurality of input/output modules. Distributed protocol services are executed over the interprocessor messaging system, and include a distributed protocol module in at least one of the plurality of input/output modules which makes routing decisions supported by the distributed protocol module, and a distributed protocol module server in the central routing processor which in response to queries from the distributed protocol module makes routing decisions on behalf of the distributed protocol module. Further, a particular input/output module in the plurality may include resources for signalling the central routing processor about events across the physical layer protocol. According to this aspect, there are centralized routing resources executed in the central routing processor over the physical layer protocol in response to such events for making routing decisions on behalf of such input/output modules.

The distributed protocol services according to the present invention may include resources for performing transparent bridging, internet protocol routing, or other routing or switching decisions based on other internetworking protocols. The

distributed protocol modules may include a protocol routing table cache and the distributed protocol module server includes resources for maintaining a central protocol routing table and supporting the protocol routing table caches.

5

10

15

20

25

30

The present invention provides for more general case data processing, a system that allows for transferring large amounts of input/output data among a plurality of processors, such as a network intermediate system or router. The apparatus includes a bus interconnecting the plurality of processors with a plurality of bus interface devices connected to the bus and to corresponding processors. The bus interface device which originates a transfer without obtaining permission from the destination device, includes a command list storing a list of commands which characterize transfers of data from local memory across the bus and a packing buffer which buffers the data subject of the command being executed between local memory and the bus. A bus interface device which receives a transfer includes a free buffer list storing pointers to free buffers in local memory into which the data may be loaded from the bus, a receive list storing pointers to buffers in local memory loaded with data from the bus, and an inbound data buffer which buffers data subject of a transfer addressed to the receiving processor between the bus and the free buffers in the local memory. By eliminating the requirement to obtain permission from the destination device, such as normally done by a handshake protocol or the like, bus performance is greatly improved. However, the system must be able to tolerate occasional lost messages on the bus.

According to one aspect of the invention, the command list includes at least a first high priority command list and a second lower priority command list so that the apparatus may manage latency of the higher priority commands according to a latency class for the command.

According to another aspect of the invention, the commands stored in the command list identify messages to be transferred across the bus. The bus interface device of the originating processor includes control logic which manages data transfer into and out of the packing buffer for messages identified by the commands in the command list to compose message transfer cells for the messages, and to drive the message transfer cells on the bus in a burst mode. The bus interface which receives

the transfer includes control logic which manages data transfer into and out of the inbound buffer, including receiving burst transfers of message transfer cells from the bus, loading free buffers in local memory from the inbound buffer with message transfer cells, and updating the receive list.

5

10

The present invention can also be characterized as providing a connectionless communication protocol, which enhances the reliability and control over latency of the processing of messages based on classifying messages according to latency and reliability classes. Thus, according to the present invention, the transmission of messages among processing nodes in an interprocessor system is managed to control transmit latency, that is the amount of time between the posting of a message to be transmitted at a source processor, and actual transmission of that message on the communication link; transmit reliability, that is the desired level of reliability required for a source processor that a command to transmit a message will actually be executed; receive reliability, that is the desired level of reliability required for a destination processor to actually receive a message transmitted from a source processor; and receive latency, that is the amount of time between actually receiving a message, and processing such message at the destination processor.

15

20

Thus, according to one aspect of the invention, it can be characterized as a method of transferring data on a communication medium from a source processor to a destination processor, wherein the data includes messages of a first transmit latency class and messages of a second transmit latency class. According to this aspect, messages of a first transmit latency class are queued at the source processor in a first transmit queue, and messages of the second transmit latency class are queued at the source processor in a second transmit queue. The first and second transmit queues operate to send messages on the communication link according to respective priority rules, such as a first-in first-out rules. According to this invention, a particular message selected from the first and second transmit queues in the source processor is sent on a communication link according to a queue priority rule to the destination processor without establishing connection with the destination processor for the particular message in advance. The queue priority rule provides, in one embodiment of the invention, for sending messages in the second transmit queue prior to sending

30

any message in the first transmit queue, so long as a message resides in the second transmit queue. Other queue priority rules may be implemented, to ensure fairness or other parameters of a particular system. Thus, a source processor is able to classify messages according to a transmit latency class, to ensure that certain classes of messages are transmitted quickly onto the communication link, while other classes of messages are handled in a best efforts type process.

According to another aspect of the invention, the step of queuing messages involves storing commands in either the first or second transmit queue. The commands identify the messages to be transferred across the communication medium. In order to send a message, the commands are created by the source processor. Further, the messages may include one or more fragments of data, such as an encapsulation header and an encapsulated frame. The commands are created by the source processor in a manner such that one command is stored for each fragment of the message to be transmitted. Furthermore, the commands will include pointers to, or otherwise be associated with, memory locations in the source processor where the messages or fragments to be transferred are stored. Optionally, the commands indicate the destination addresses for messages to be transferred. The fragments of a message are gathered for transmission in response to the commands, and may be segmented into cells for transmission, the cells having a data length which is specified according to characteristics of the communication medium in the preferred system.

An additional level of reliability queuing is provided according to another aspect of the invention by "quality of service" thresholds in the first or second transmit queues. According to the quality of service thresholds, the commands are classified according to command types. When storing commands into the first or second transmit queue, commands having a first type are dropped or returned to the sender, if a first threshold number of entries in the transmit queue data structure has been exceeded. Commands of a second type are written into the transmit queue if any entries are available. This way, software in the source processor is able to provide an additional level of reliability for certain classes of messages.

According to another aspect of the invention, a code in the messages (or cells making up the messages) being transmitted is provided at the source processor which

5

10

15

20

indicates one of a first and second reliability classes for the message. Preferably, a third reliability class is utilized as well. As the messages are received to destination processor, the reliability class of the message is determined. Messages are stored in the destination processor memory according to a received priority rule which provides for storing messages of the first reliability class if a first threshold amount of storage is available in the destination processor for such messages, and storing messages of the second reliability class if a second threshold amount of storage is available in the destination processor memory. The use of these receive priority rules act to preserve buffer space in destination processors for receiving high reliability messages.

10

15

5

According to yet another aspect of the invention, a code in messages being transmitted on the communication medium is provided to indicate one of first and second receive latency classes. As the messages are received at the destination processor, the receive latency class is determined, and the message is queued in one of the first and second receive queues according to the receive latency class. The messages are processed at the destination processor from the first and second receive queues according to a receive queue priority rule. For instance, all messages of a first receive latency class in the first receive queue will be processed prior to processing messages in the second receive queue which have the second receive latency class.

20

25

According to one approach to management of destination processor memory, a plurality of receive buffers is maintained in the destination processor memory. In addition, a list of free receive buffers is kept by the destination processor. The step of storing received messages involves loading the data of a received message into a free receive buffer which is identified by the list of free receive buffers. According to this aspect of the invention, the receive priority rule provides for dropping messages in the first reliability class if the list of free receive buffers indicates that less than the first threshold amount of storage is available in the receive buffers. Messages of the second reliability class are dropped if the list of free receive buffers indicates that less than the second threshold amount of storage is available. The receive priority rule preferably includes a rule for dropping messages of a third reliability class if no receive buffers are available in the destination processor memory.

Thus, a source processor is able to classify messages to be transmitted on the connectionless communication link according to transmit latency classifications, receive reliability classifications, and receive latency classifications. This greatly improves the control over message throughput in a communication backbone, along with reliability and latency of messages.

5

10

15

20

25

30

According to another aspect of the invention, the communication process based on latency and reliability classes discussed above is applied to a bridge/router system with multiple processors connected by a backbone communication link. As frames of data are received at the bridge/router from connected networks, they are processed in the receiving processor, and transmitted across the communication link based on classifications as discussed above. The communication link can be any type of connectionless protocol system, such as a high speed parallel or serial bus which executes a connectionless protocol, a local area network link, or even an internet protocol cloud. Also, the communication link may comprise a LAN or WAN protocol link used as a backplane bus within a single chassis, executing for example, asynchronous transfer mode ATM, high speed Ethernet, or fiber optic based protocols like FDDI.

The protocol of the present invention provides, for internetworking systems, an interprocessor messaging system including resources for transferring control messages and network packets in transit among a central routing processor and the input/output modules in the set of intelligent input/output modules. This allows the input/output modules to be developed with a logical layer communication system in mind for access to the centralized internetworking engine. This enables tremendous flexibility in the design and expansion of bridge/routers according to the present invention. Further, because the centralized internetworking engine supports communication across the backplane with input/output modules without higher layer protocol processing, backward compatibility is ensured, as well as the ability to incrementally expand an existing system with one network interface at a time growth.

The system further provides tremendous flexibility in utilization of the backplane. Thus, the interprocessing messaging system, as well as the physical layer protocol support communication among the central routing processor and the plurality

of input/output modules with messages in a plurality of latency classes, and in a plurality of reliability classes. Thus, certain control messages can be delivered across a system with very high reliability. Data packets in transit can be transferred across the system with lower reliability but higher throughput. A dropped data packet from time to time does not affect overall system performance significantly because network protocols are able to recover from such lost packets. The critical parameter for transferring data in transit is minimizing system overhead and maximizing throughput.

5

10

15

20

30

In sum, the present invention provides a high performance scalable internetworking platform based on an interprocessor messaging system which provides a logical layer for communicating among input/output modules, allowing diverse input/output modules. The diverse input/output modules may include distributed protocol modules which communicate with a distributed protocol module server on a centralized resource. This allows a large amount of routing decisions to be made in the distributed protocol modules without requiring transfer of data in transit from the port to the centralized processor. Rather, these packets are transferred directly from port to port in the system, maximizing efficiency of the data paths in the device. The centralized internetworking engine allows synchronization of internetworking functions, and provides for handling of exception packets in the host, which occur rarely and need not be supported in the distributed modules.

Other aspects and advantages of the present invention can be seen upon review of the figures, the detailed description, and the claims which follow.

## BRIEF DESCRIPTION OF THE FIGURES

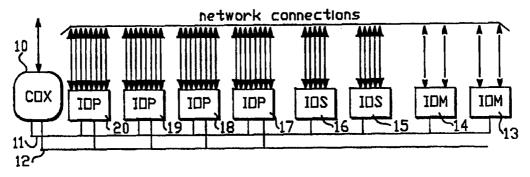

Fig. 1 provides a system block diagram for a scalable network intermediate system according to the present invention.

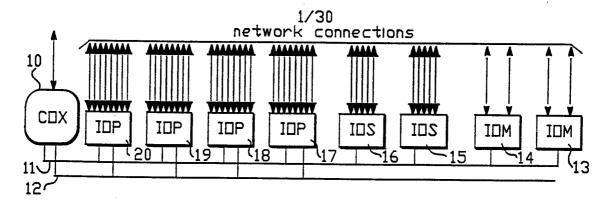

Fig. 2 provides a block diagram of a basic input/output module (IOM) which may be used in the system of Fig.1.

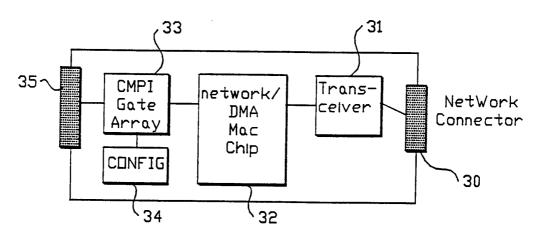

Fig. 3 provides a block diagram of a semi-intelligent I/O module (IOS) such as used in the system of Fig. 1.

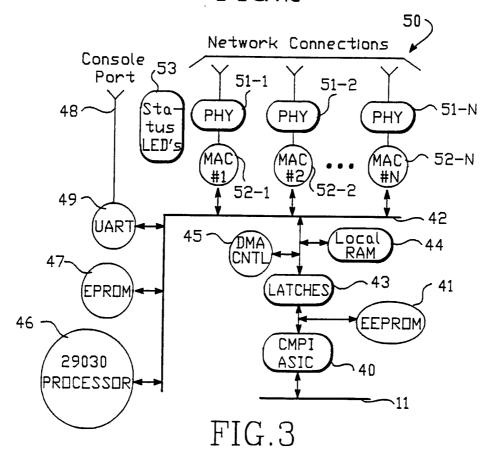

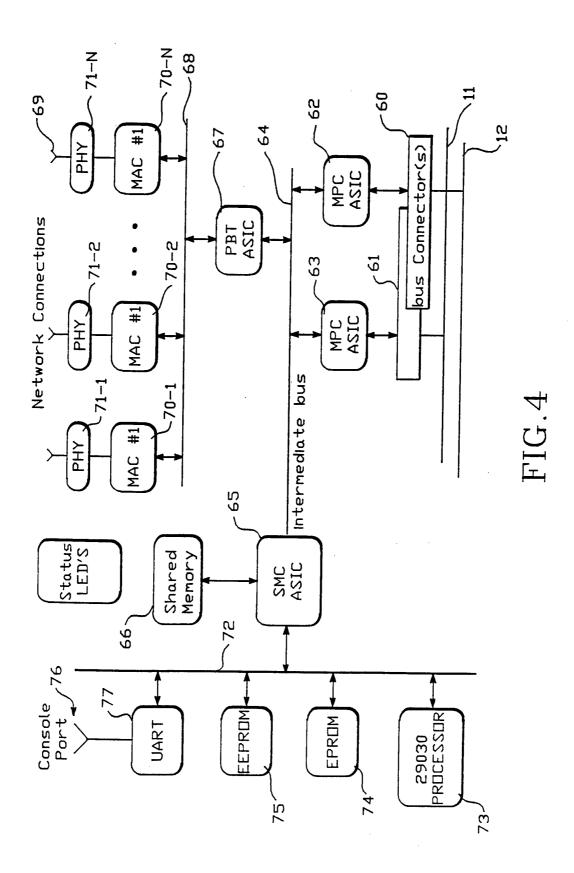

Fig. 4 provides a block diagram of an input/output module with an enhanced function processor (IOP) such as used in the system of Fig. 1.

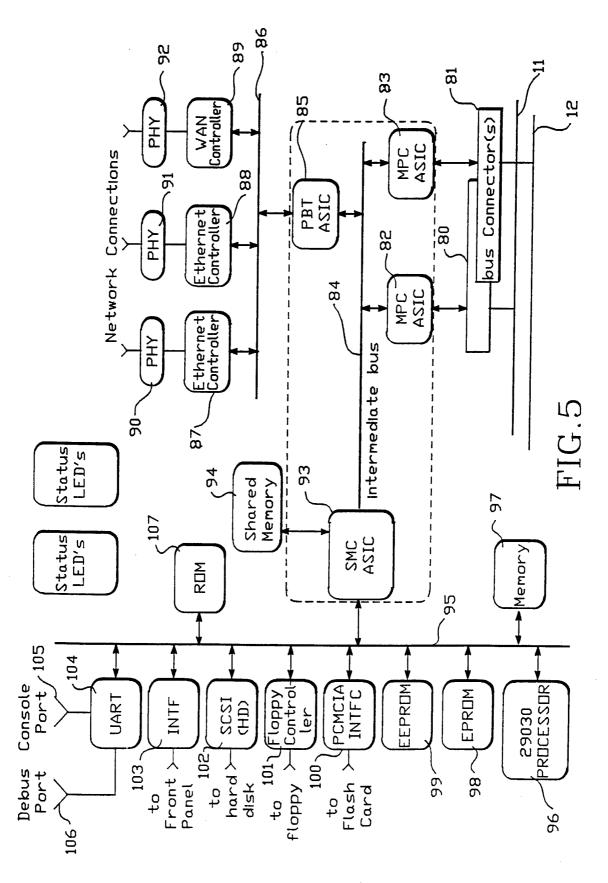

Fig. 5 provides a block diagram of the central internetworking processor (COX) used for providing a shared resource for the other processors coupled to the buses in the system of Fig. 1.

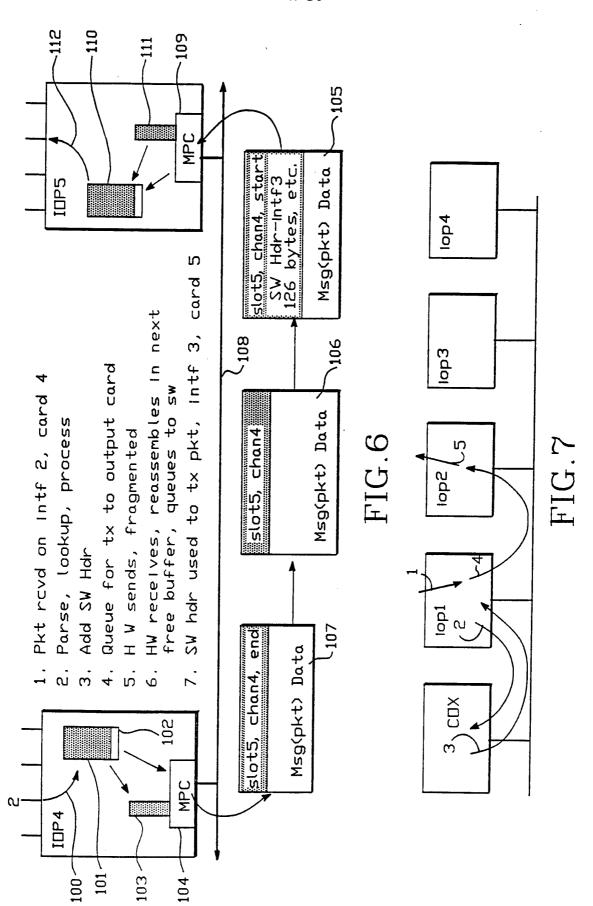

Fig. 6 is a heuristic diagram providing an example of message transmission for the system of Fig. 1.

Fig. 7 illustrates message flow scenarios for a system such as that shown in Fig.1.

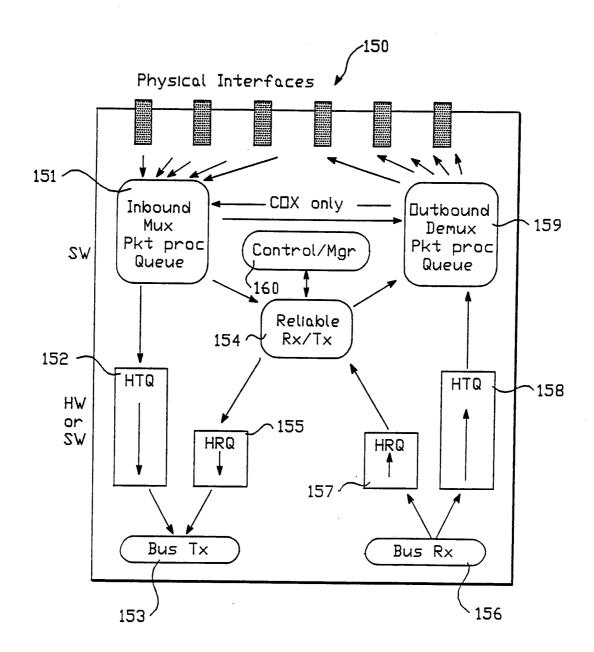

Fig. 8 provides a diagram of the dual queue structure and message paths for the bus interfaces in the system of Fig. 1.

5

15

20

25

Fig. 9 is a table setting forth the data transfer types in the system of Fig. 1.

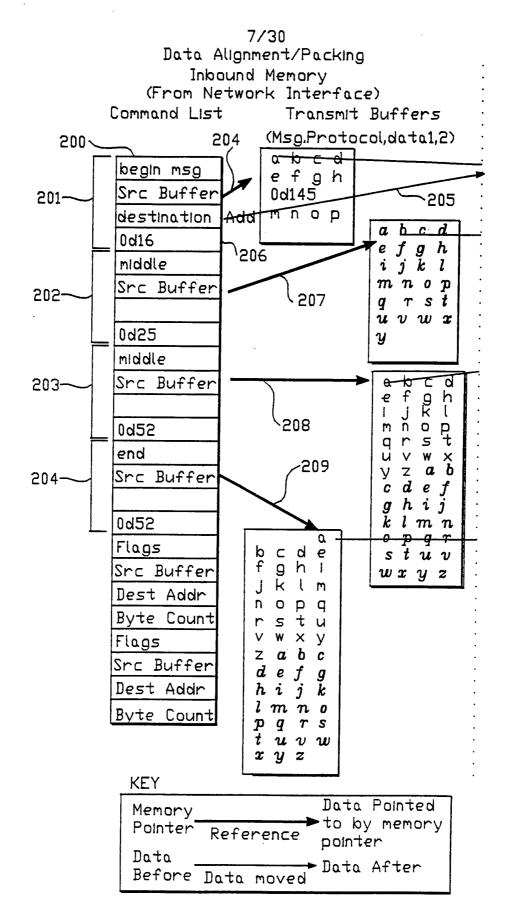

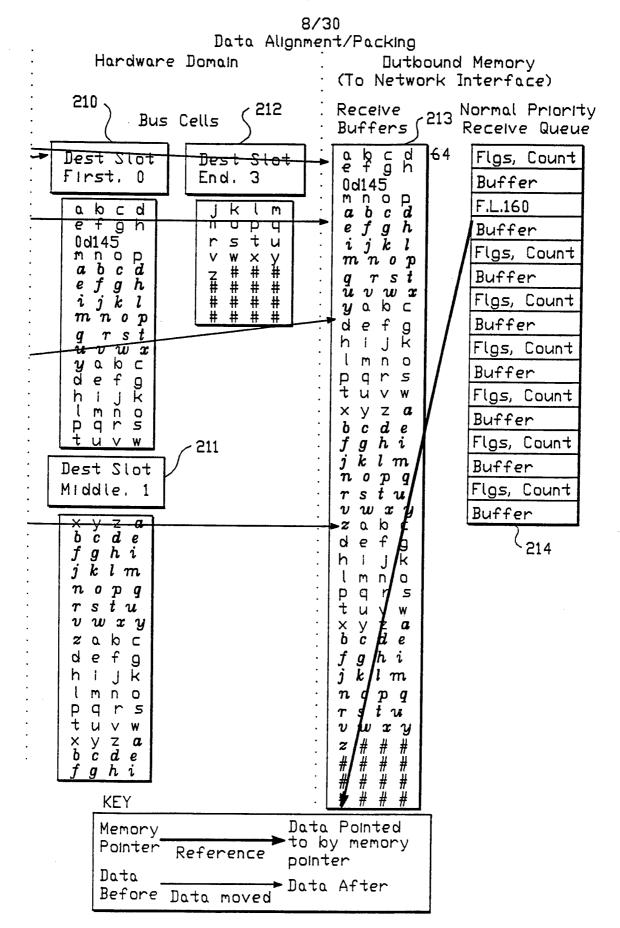

Figs. 10A and 10B illustrate the data alignment and packing for messages transferred on the bus.

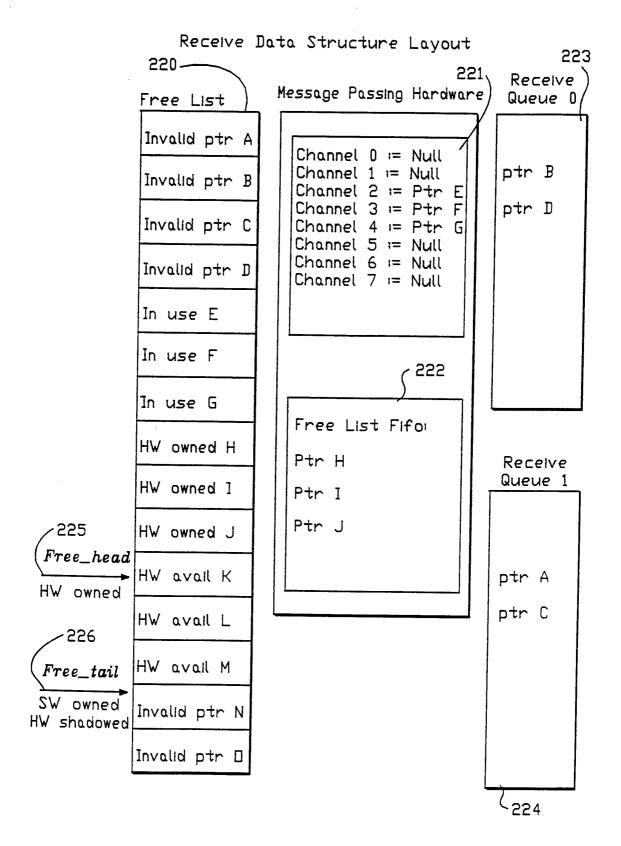

Fig. 11 illustrates the receive data structure layout for the bus interfaces.

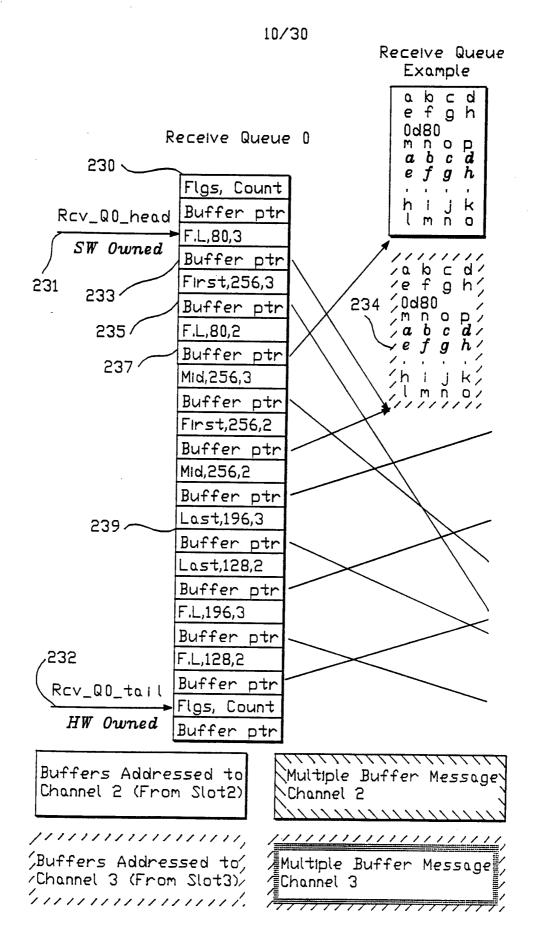

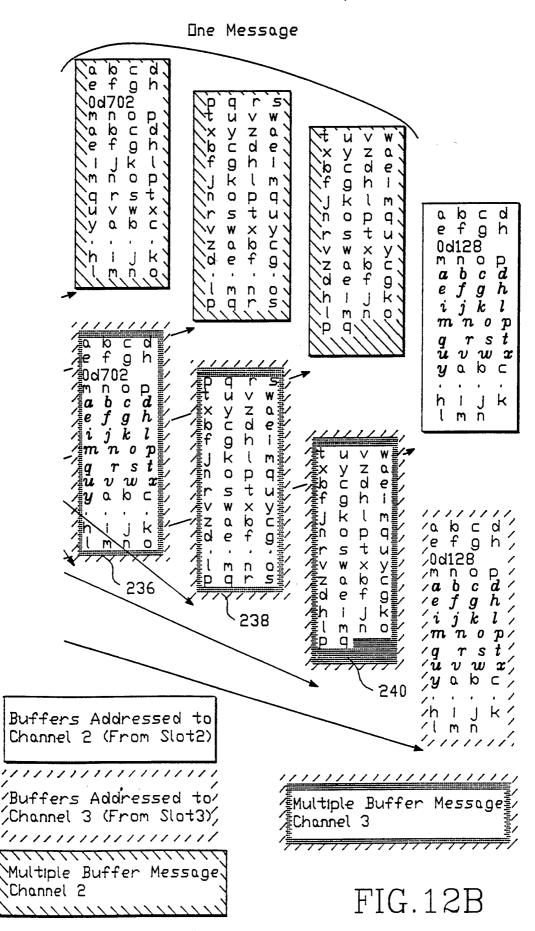

Figs. 12A and 12B provide a receive queue example for the bus interface according to the present invention.

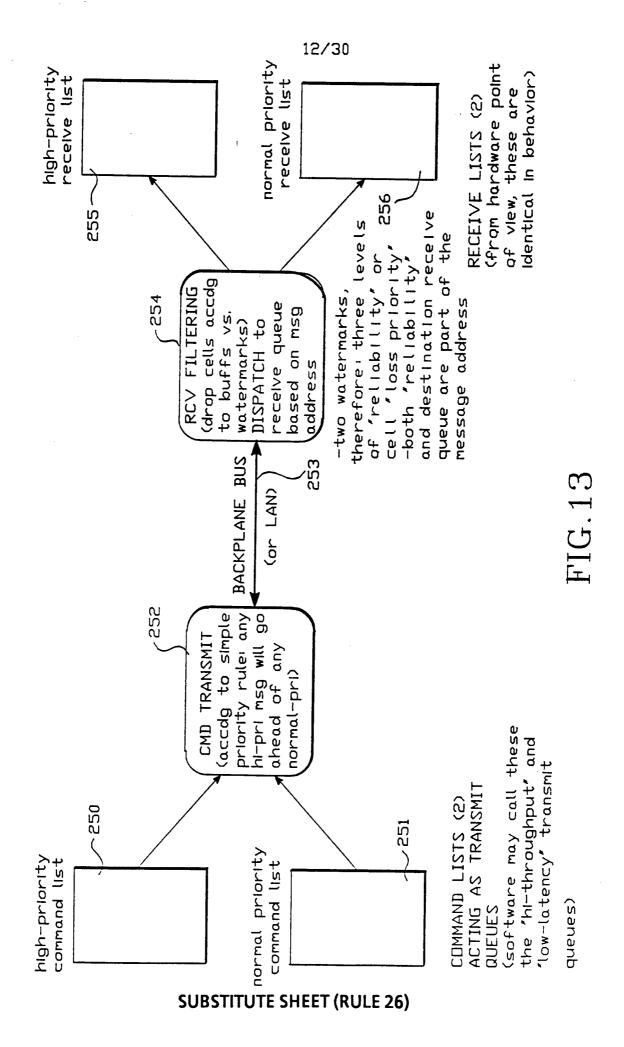

Fig. 13 illustrates the data flow from the high and normal priority command lists to the high and normal priority receive lists according to the present invention.

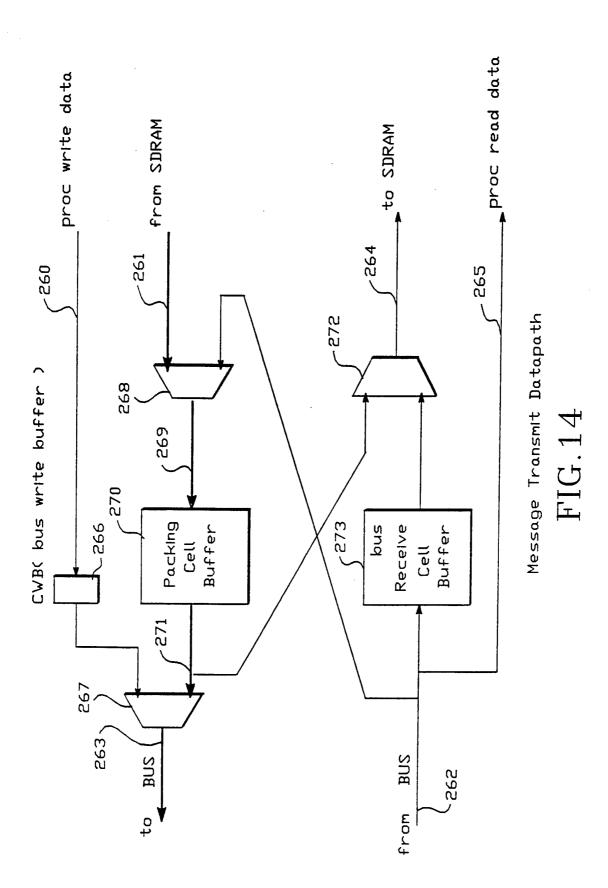

Fig. 14 illustrates the message transmit data path in the bus interface.

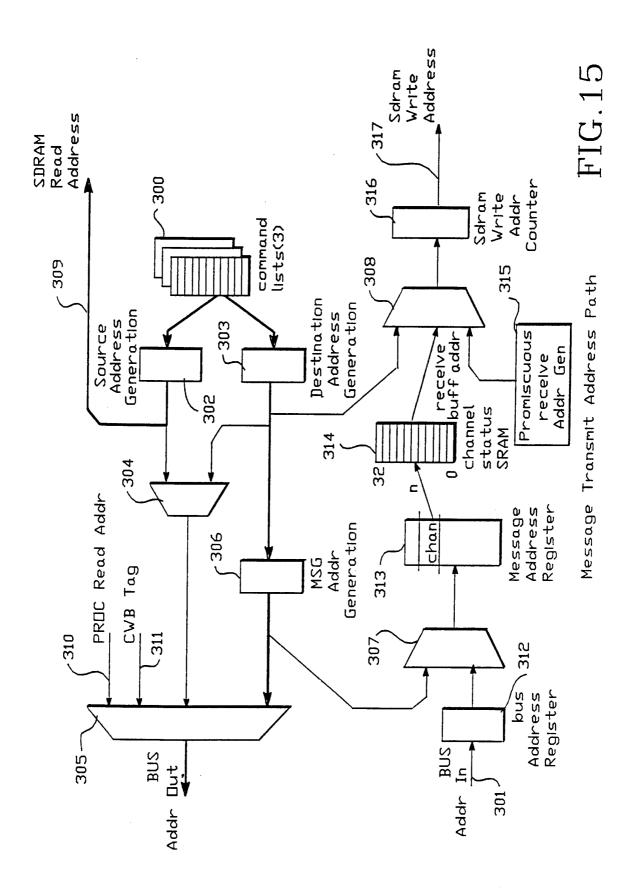

Fig. 15 illustrates the message transmit address path in the bus interface.

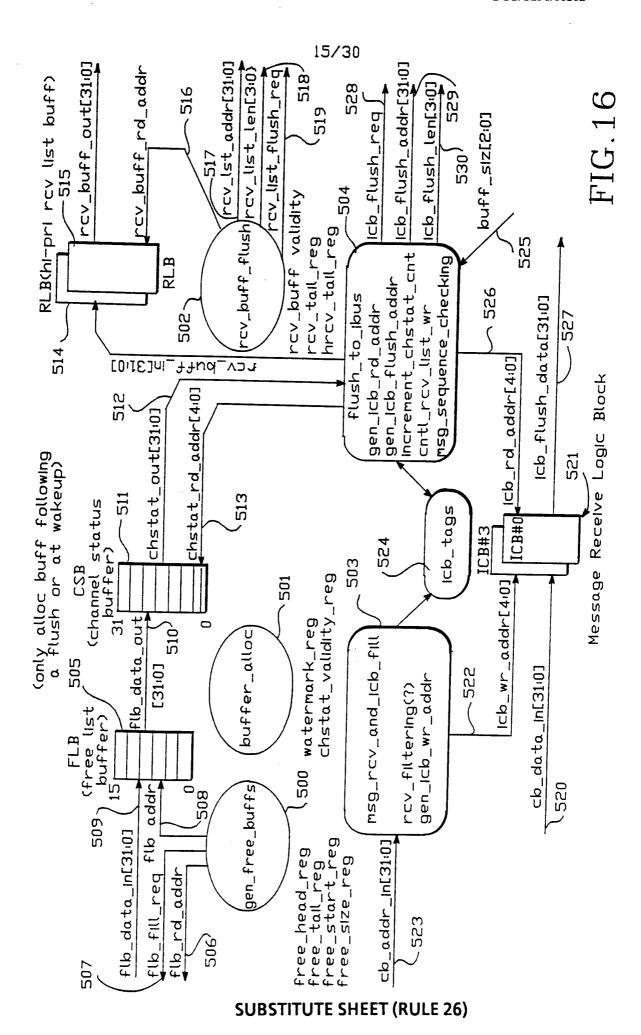

Fig. 16 illustrates the message receive logic in the message passing controller.

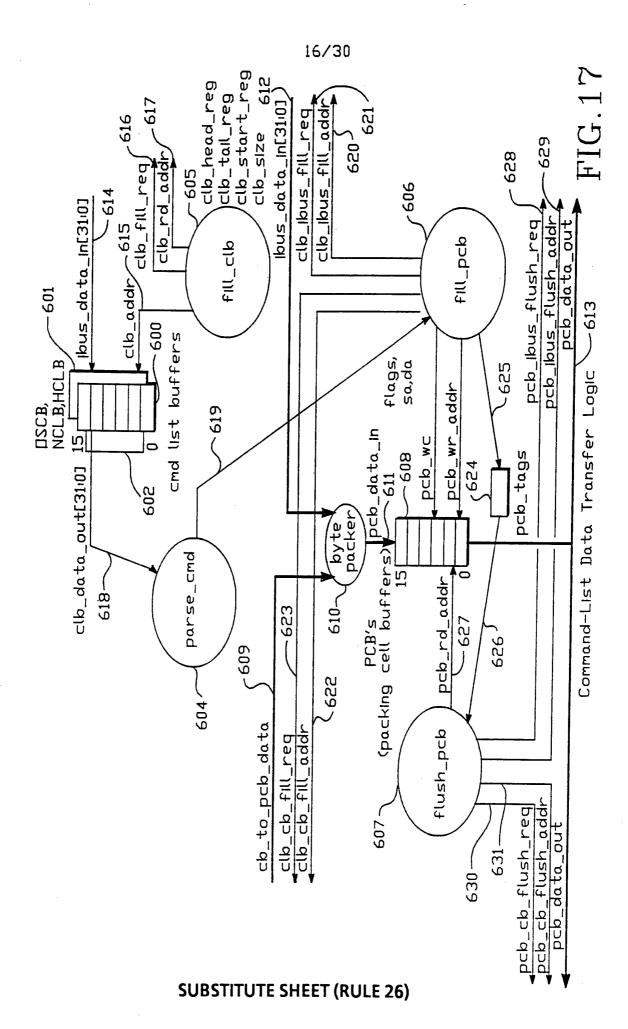

Fig. 17 illustrates the command list data transfer logic within the message passing controller.

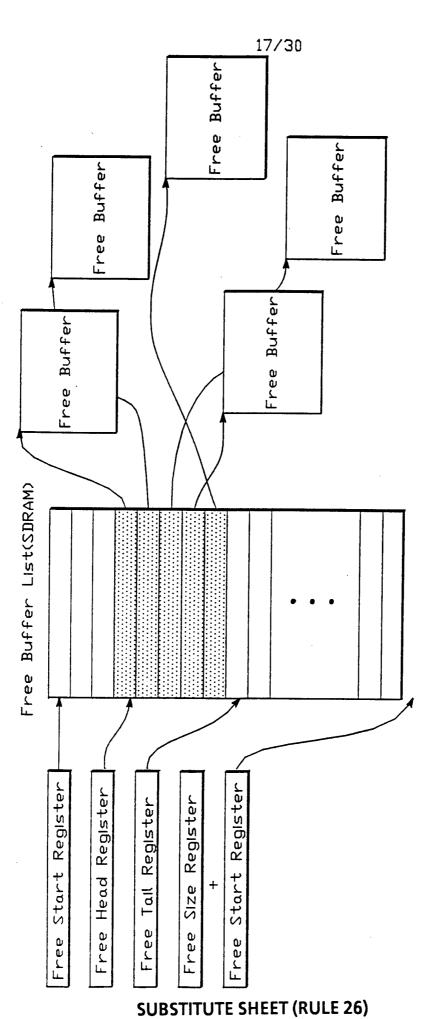

Fig. 18 illustrates the free list structure and its associated registers in the MPC and the free buffers in the SDRAM.

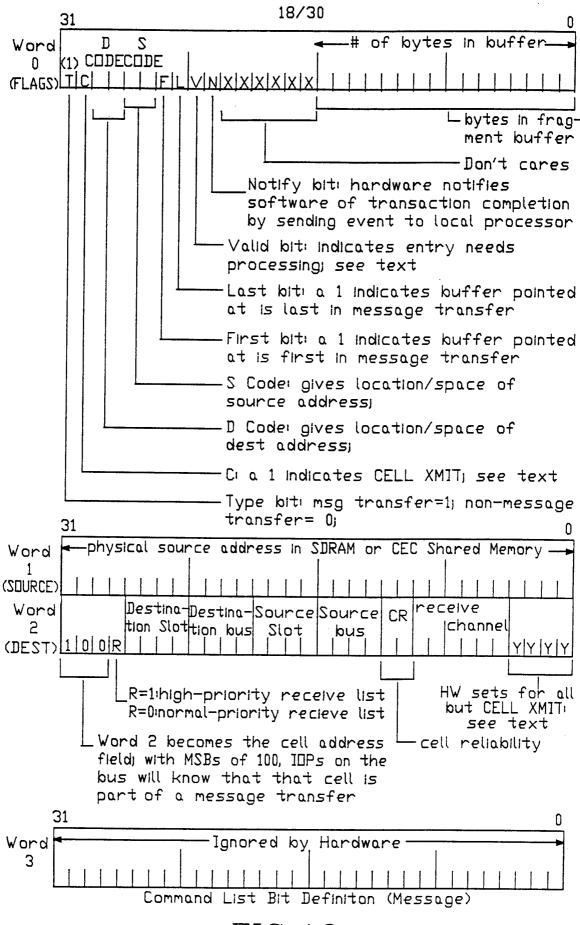

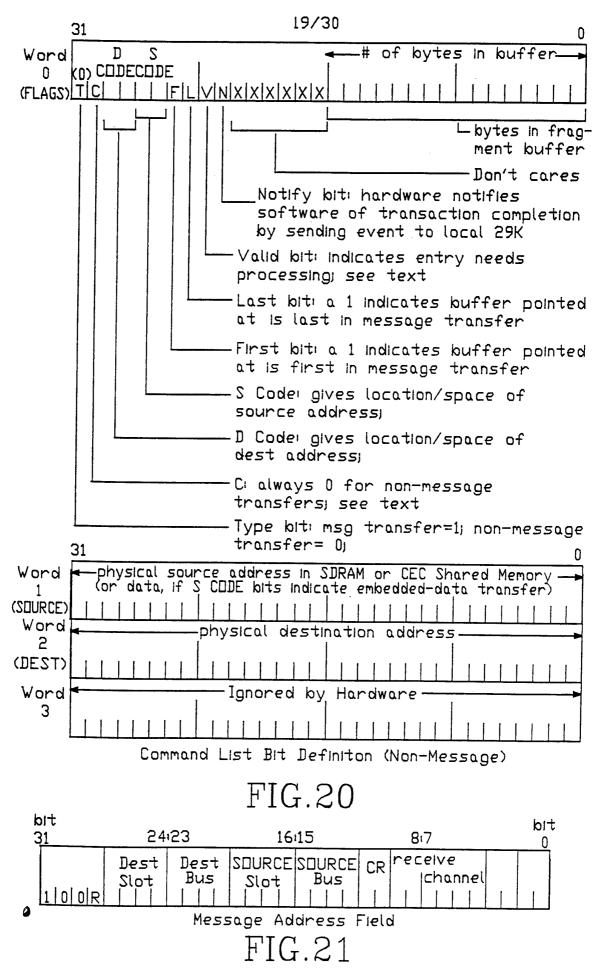

Fig. 19 illustrates the command list bit definition for a message type transfer.

Fig. 20 illustrates the command list bit definition for a non-message type transfer.

Fig. 21 illustrates the message address field for a message transferred on the bus.

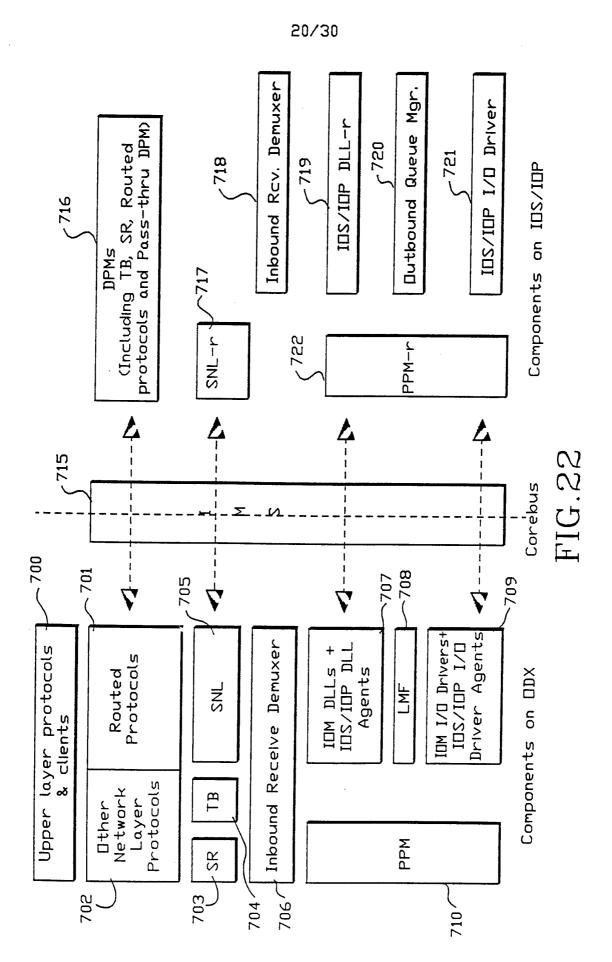

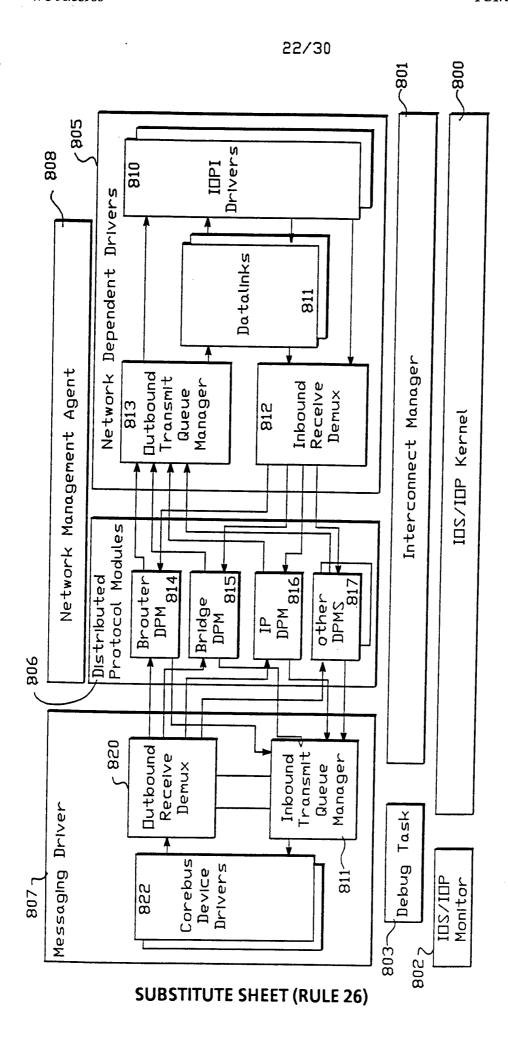

Fig. 22 is an overview of the major components in the centralized internetworking engine and the intelligent input/output modules according to the present invention.

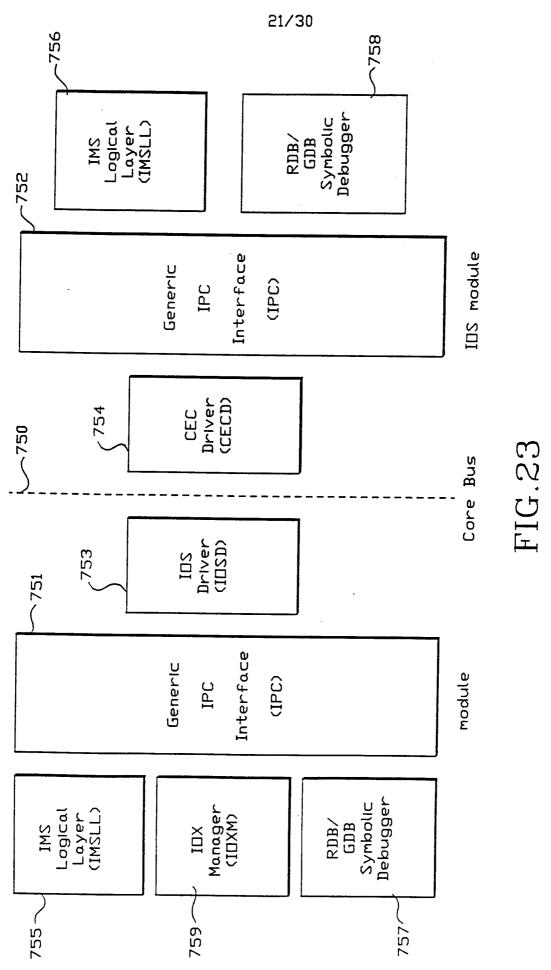

- Fig. 23 provides an overview of the interprocessor communication components for use in the system described in Fig. 22.

- Fig. 24 provides a perspective of the data paths in the intelligent input/output modules for the system of Fig. 22.

- Fig. 25 is a table showing the interprocessor messaging system message types and their priorities according to one implementation of the present invention.

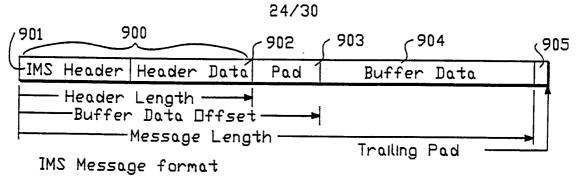

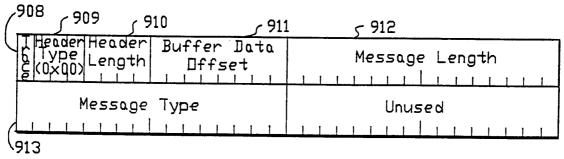

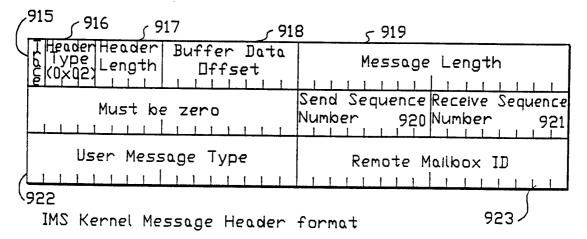

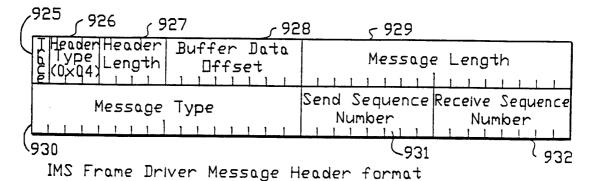

- Figs. 26 through 29 illustrate the message formats supported by the interprocessor messaging system according to one embodiment of the present invention.

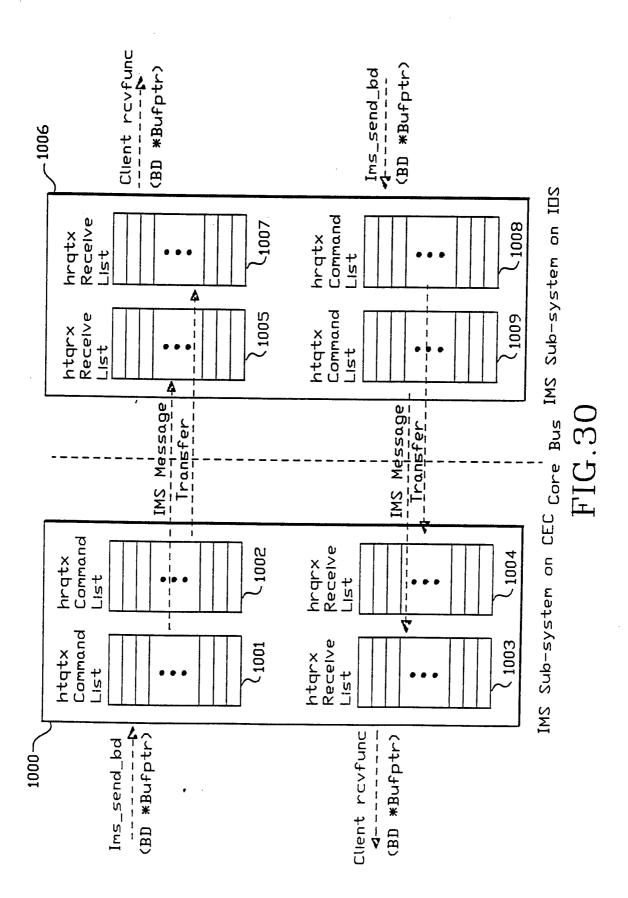

- Fig. 30 shows the functional operation for the interprocessor messaging system buffer data type message transfers.

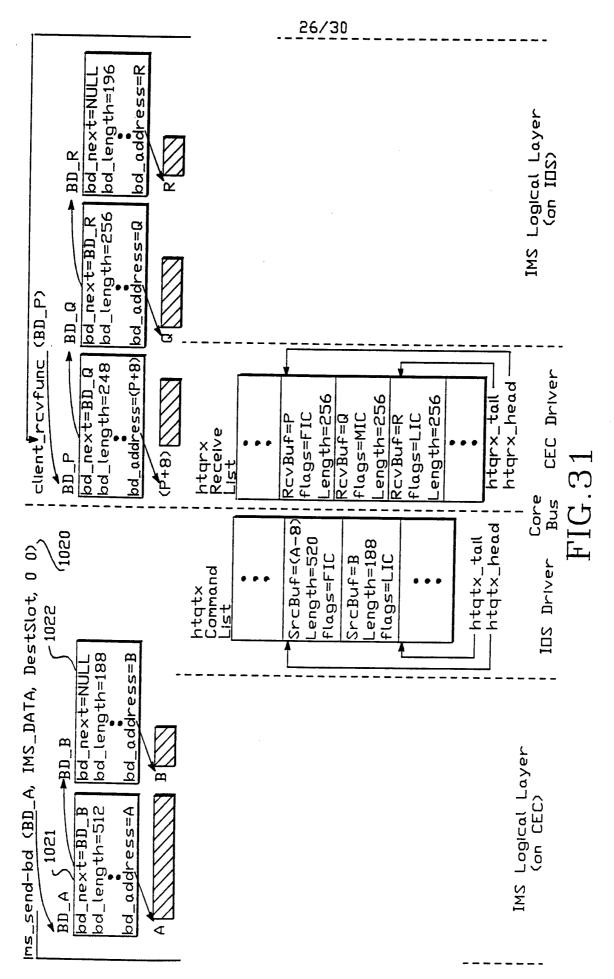

- Fig. 31 shows the interprocessor messaging system logical layer processing for data transfers from the central engine to the input/output modules.

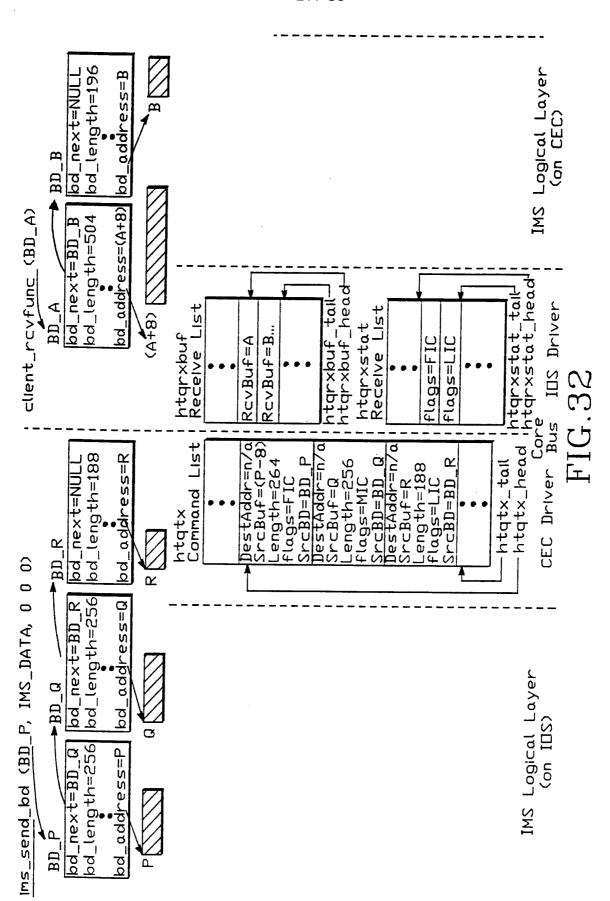

- Fig. 32 shows the interprocessor messaging system logical layer processing for data transfers from an input/output module to central internetworking engine.

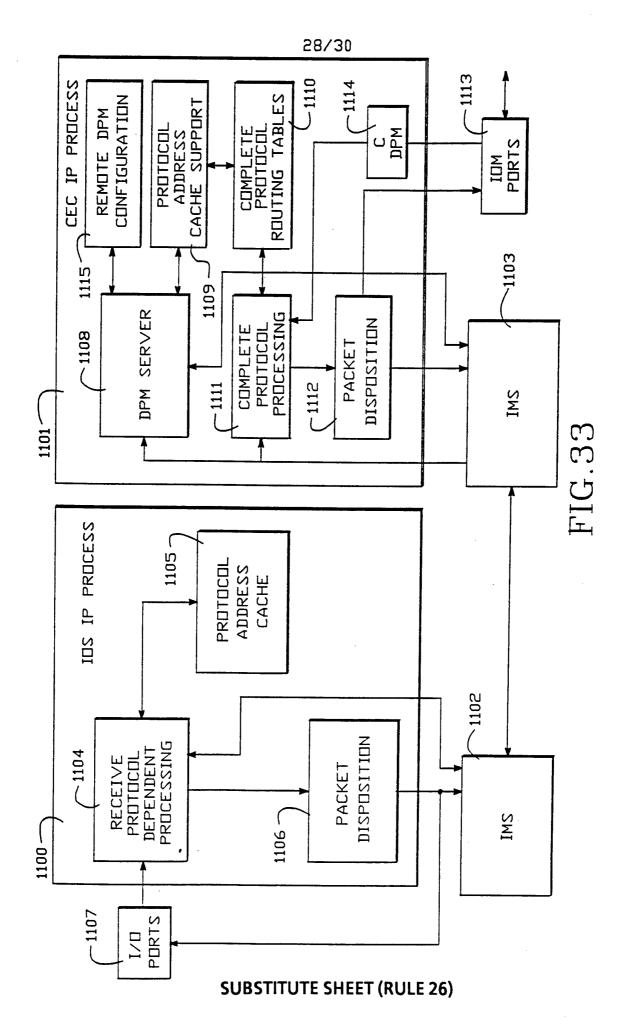

- Fig. 33 illustrates the components of distributed internet protocol (IP) processing according to the present invention.

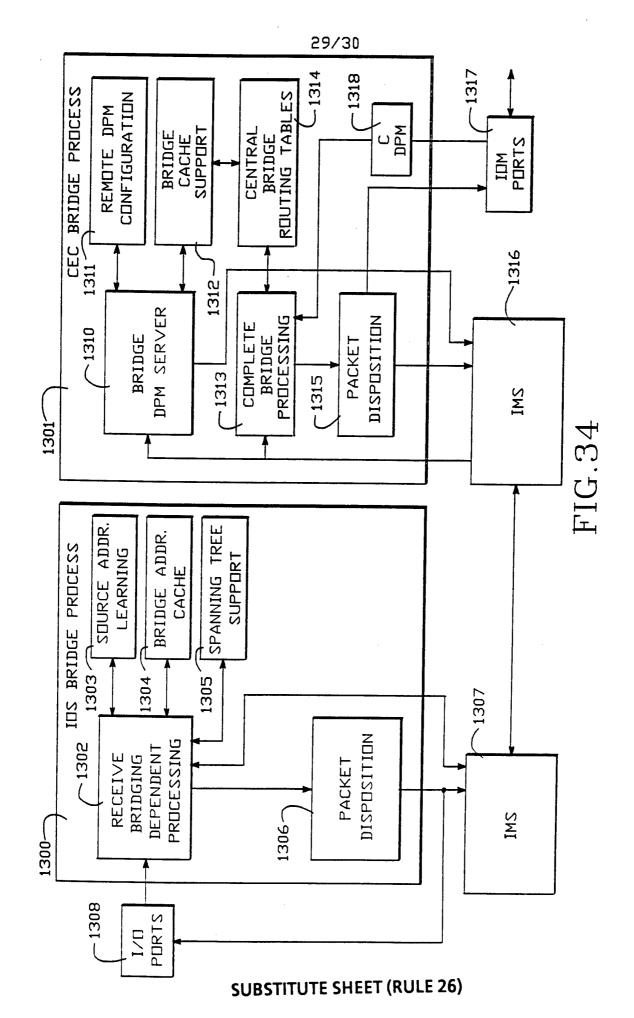

- Fig. 34 illustrates the components of distributed transparent bridging processing according to the present invention.

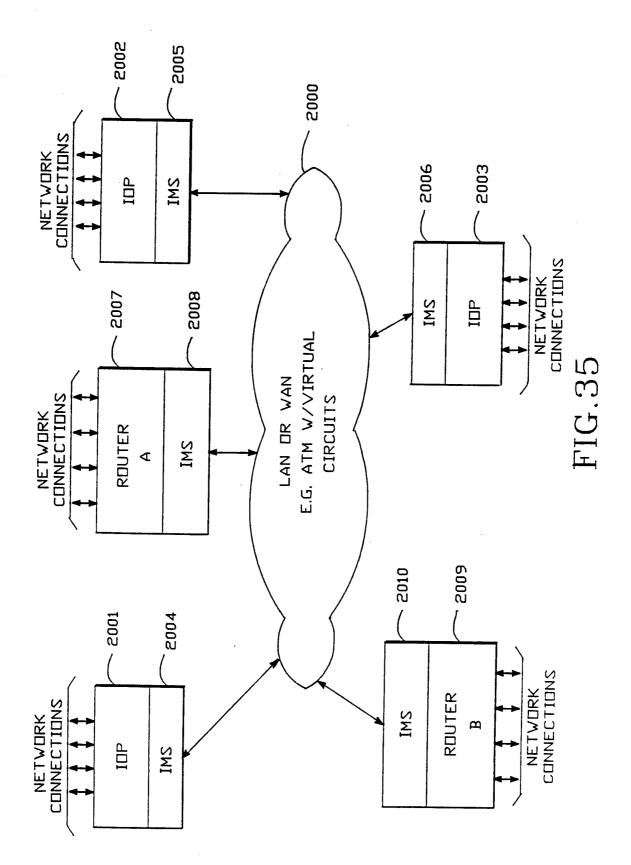

- Fig. 35 illustrates application of the scalable architecture across a LAN or WAN backbone.

25

30

20

5

10

#### **DETAILED DESCRIPTION**

A detailed description of an embodiment of the present invention is provided with reference to the figures. Figs. 1-5 illustrate a basic hardware environment for the system applied as a network intermediate system. Figs. 6-21 illustrate the message transfer hardware and techniques applied according to the present invention in the environment of Fig. 1.

Figs. 22 through 32 illustrate the processing resources and the logical layered interprocessor messaging system used over the physical layer.

Fig. 33 shows an internet protocol (IP) distributed protocol module and distributed protocol module server; and Fig. 34 shows distributed protocol resources for transparent bridging according to the present invention. Fig. 35 shows use of the scalable architecture with a LAN or WAN backbone.

# I. <u>SYSTEM DESCRIPTION</u>

5

10

15

20

25

30

Fig. 1 provides a board level block diagram of a scalable bridge/router illustrating the present invention. The bridge/router includes a central control card COX 10 coupled to a first high speed parallel bus 11 and a second high speed parallel bus 12. A plurality of input/output (I/O) modules are coupled to the bus 11 to provide input/output functions for connected networks. The plurality of I/O modules includes in the embodiment described a first relatively passive type interface device IOM 13 and 14, an intermediate level semi-intelligent processing device IOS 15 and 16, and a more powerful processing system IOP 17, 18, 19, and 20. The IOP boxes 17-20 include interfaces to both high speed buses 11 and 12.

Each of the plurality of processors has at least one associated network connection. Thus, the IOM boxes 13 and 14 include two network connections each, which might be coupled to, for instance, Ethernet or token ring local area networks. The IOS boxes 15 and 16 include five connections each, coupling to local area networks (LANs), such as Ethernet, FDDI, token ring, or the like and/or wide area networks (WAN) links. The IOP boxes 17-20 have eight network connections each and handle much higher throughputs.

The basic IOM box 13 is illustrated in Fig.2. It includes at least one network connector 30 which is coupled to a transceiver 31 and a network/DMA MAC chip 32, such as commercially available for a given type of network. This chip is coupled to a bus interface chip 33 with associated configuration data 34, and through the interface chip 33 to a backplane bus connection 35. The IOM box shown in Fig. 2 relies primarily on the central control box COX 10 for the management of data transfer and control functions.

The bus interface chip 33 is described in detail in our co-pending U.S. patent application entitled INPUT/OUTPUT BUS ARCHITECTURE WITH PARALLEL ARBITRATION, Application No. 08/033,008, filed February 26, 1993, invented by Mark Isfeld, et al. Such application is incorporated by reference as if fully set forth herein to fully provide a detailed description of the bus architecture in the preferred system. However, this particular bus architecture is not intended to be limiting. The preferred system uses a 32 bit (or greater) wide bus with a least a 25 MHz clock and preferably a 50 MHz clock, for a nominal data rate of 800 MBPS (megabits per second) or 1600

5

15

20

25

30

MBPS. Even higher data rates can be achieved with state of the art high speed parallel bus architecture, or other data transfer techniques. Also, the backplane may be implemented using a variety of local area network technologies as discussed below with reference to Fig. 35.

The semi-intelligent I/O processor IOS, 15 and 16, is illustrated in Fig. 3. As can be seen, this system is connected to the bus 11 through the bus interface chip 40. A non-volatile memory device 41, such as an EEPROM, stores configuration data and the like for the bus interface 40. A data interface to an intermediate bus 42 is provided through latches 43. Also, a local memory 44 and a DMA control module 45 are coupled to the intermediate bus 42 and the local memory 44. An intelligent microprocessor 46, such as the Am29030 manufactured by Advanced Micro Devices, Inc., is coupled to the intermediate bus 42. A flash programmable read only memory 47 provides storage for programs executed by the processor 46. A console port 48 is provided through a UART interface 49 to the bus 42. A plurality of network connections, generally 50, are coupled to the bus 42 through respective physical interfaces 51-1 through 51-N, and medium access control MAC devices 52-1 through 52-N. The box may include status light emitting diodes 53 connected and controlled as desired by the particular user.

Fig. 4 illustrates the block diagram of the higher performance input/output processor IOP of Fig. 1. This system is coupled to the first bus 11 and the second bus 12 through respective bus connectors 60 and 61. The bus connectors 60 and 61 are coupled to message passing controller ASICs 62 and 63, respectively, which are, in

turn, connected to an intermediate bus 64. The intermediate bus (also called internal bus herein) is coupled to a shared memory controller 65 which controls access to a shared memory resource 66. The intermediate bus 64 is coupled through a peripheral bus interface 67 to a network data bus 68. On the network data bus, there are a plurality of network connections, generally 69, made through respective MAC devices 70-1 through 70-N and physical interfaces 71-1 through 71-N. The shared memory controller 65 is also coupled to a control bus 72, which is connected to a high speed processor 73, flash programmable read only memory 74 storing programs, non-volatile EEPROM memory 75 storing parameters and static code, and a console port 76 through a UART interface 77.

5

10

15

20

25

30

The central control box is illustrated in Fig. 5. This box is basically similar to the box of Fig. 4. Thus, the box includes a first bus connector 80 and a second bus connector 81 for the first and second buses, respectively. Message passing controllers 82 and 83 are coupled to the bus connectors 80 and 81, and to an intermediate bus 84. A peripheral bus transfer ASIC 85 is connected between the intermediate bus and a peripheral bus 86. An Ethernet controller 87, an Ethernet controller 88, and a wide area network (WAN) controller 89 are coupled to the peripheral bus 86 and to the respective networks through physical connections 90, 91, and 92.

The intermediate bus 84 is also connected to a shared memory controller 93, and through the shared memory controller 93 to a shared memory resource 94. A second shared memory resource may also be connected directly to the MPC ASIC 82 or 83. The shared memory controller 93 is also connected to a processor bus 95 which interconnects a processor 96, working memory 97 for the processor, flash memory 98 for processor code, EEPROM memory 99 for static code and parameters, a PCMCIA interface 100 for accepting flash memory cards for upgrade purposes and the like, a floppy disk controller 101 for driving a floppy disk, an SCSI interface for connection to a hard disk 102, an interface 103 for connection to a front panel providing a user interface, and a dual UART device 104 which provides for connection to a console 105 and a debug port 106. In addition, read only memory 107 may be connected to the processor bus 95. The native PCMCIA interface is provided for enabling a redundant reliable boot mechanism.

5

10

15

20

25

30

The software processing for a high performance router breaks fairly cleanly into two major pieces: the data forwarding functions and the control/management functions. The data forwarding functions include device drivers and link-layer protocols such as HDLC-LAPD in addition to the per-packet processing involved with recognizing, validating, updating, and routing packets between physical interfaces. The control and management software functions include routing protocols and network control protocols in addition to all configuration and management functions.

In general, the data forwarding functions are optimized for maximum performance with near real-time constraints, whereas the control and management functions simply run to completion on a time available basis, with some exceptions. When system performance is measured, it is primarily the forwarding capacity of the router in terms of bandwidth, packets-per-second, and fan-out that is considered, with an implicit assumption that the control and management functions will be sufficient. The control and management software comprises the vast majority of the code and can use large amounts of data space, but most of the data space consumed by these functions need not be shared with the forwarding software.

In the system of Fig. 1, the forwarding function is replicated in distributed protocol modules in the semi-intelligent and full function processors IOS and IOP, with distributed protocol module servers along with the full function routing and other centralized functions running on the single central processor COX. Thus, the forwarding functions where possible run on processors near the physical interfaces, and mechanisms, including hardware supported message passing, tie the distributed processing modules to each other and to the central control functions. This architecture allows some forwarding functions to be distributed, while others are centralized on the central control box. The message passing architecture enables significant flexibility in the management of the location of software in the router architecture. Further, backward compatibility and system scalability are preserved.

# II. MESSAGE PASSING STRUCTURES AND PROCESSOR

The basic message passing technique is illustrated with respect to Fig. 6. In Fig. 6, the process of receiving a packet on interface 2 on card 4 is illustrated. Thus,

the packet is received and proceeds along arrow 100 into a buffer 101 in the card. While it is in the buffer, the processor parses the packet, looks up the destination for the packet, and processes it according to the routing code. Next, a software header 102 is added to the packet. Then, a command or set of commands to transmit a message which carries the packet is added to a queue 103 for message transmission. The hardware 104 in the card sends the message or messages in a segmented state, which includes a first message cell 105, which has a start identifier, a channel identifier, and a destination slot identifier (in this case, slot 5, channel 3). The first cell includes the software header which identifies the destination interface as interface 3 in processor 5, the length of the packet, etc. Cell 105 includes the first part of the packet data. The next cell 106 of the message includes a header indicating the destination slot and its channel as well as packet data. The final cell 107 includes the destination and its channel, and an indicator that it is the last cell or "end" in the message. Finally, this last cell 107 is filled with the balance of the message data. These three cells of the message are transferred across the high speed bus 108 to the destination slot 5. In slot 5, the hardware 109 receives the cells, reassembles then in the next free buffer 110, and queues the message to software in the queue 111. The software and hardware in the IOP at slot 5 transmit the packet carried by the message out interface 3 in card 5 across the arrow 112, in this example.

20

25

30

5

10

15

Thus, in this application, the term "packet" refers to a data structure which is received from a LAN or WAN link coupled to the router which executes the message passing process. A message is a data structure, which may comprise one or more fragments, specified by one or more commands in the transmit queue for transmission by the message passing system. A cell is a data structure which is created by segmenting a message for transmission across a particular backplane bus to the destination. The cells are then reassembled at the destination into messages. Packets for transmission out of the routing system can be recreated from messages or generated in response to messages. Thus, in this application, the use of the words "packet", "message", "fragment", and "cell", are intended to have the meanings implied by this paragraph, unless another meaning is clear from the context in which the term is used.

This message passing protocol is a "push" paradigm, which has the effect of using the bus more like a LAN than a normal memory bus. This has several important features:

Receiver allocates/manages buffering independent of transmitter.

Single "address" used for all data sent in one message.

Bus addressing is per-card, port-level addressing in software header.

Bus used in write-only mode.

No shared memory usage.

5

15

20

25

30

Reliability not guaranteed (must be supplied at a higher level, if needed).

Messages are sent as a stream of cells, interleaved with other message transmissions.

The paradigm provides the following benefits:

Improved protection/robustness.

Reduced driver overhead.

Reduced complexity, per-destination queues not required, etc.

Improved bus utilization (about 3x previous).

Bus is not monopolized by one device during a message transmission. Other slots can interleave cells on the bus, so they do not have to wait for a long message from another slot.

In Fig. 6, IOP4 receives a packet, and sends it to IOP5. Note that the input card simply sends the message to the output card. The sender does not need to allocate buffers or get permission from the receiver. A hardware address specifies the slot that should receive the message. A software message header specifies the message type (control, data, etc.), its actual length, output port number, etc. The output card is responsible for dropping messages if there is too much traffic.

Fig. 7 is an example of how messages will flow in the system of Fig. 1 in order to forward a network packet. In this example, the path that a packet follows to a destination unknown by the receiver card IOP1 is shown.

Packet enters from network attached to IOP1 (transition 1). The local processor looks up the destination (whether it be bridged, or routed by various protocols), and finds it does not know what to do with this packet. It generates a high

priority cache lookup request and sends it to the COX. The COX looks up the destination network in its database, and sends back the answer to IOP1(3). IOP1 adds the destination to its cache, and finds the held packet. It then directly forwards it to IOP2(4) as a message complete with instructions on what to do with the packet. IOP2 examines the message header and determines it should transmit the packet out port X(5). IOP2 DID NOT examine the actual packet in any way. It simply looked at a simple message header, and decoded the command to transmit the enclosed packet to port X.

5

10

15

20

25

30

If the packet originated from an IOM, then the IOM puts the packet in COX memory. The COX does the same functions as outlined above, for the IOM based packet. Packets destined for an IOM are sent to the COX which queues them for transmission. In other words, existing IOMs are just ports on the COX as far as the message passing paradigm goes.

Also notice that if IOP1 has the destination already stored in the local cache (normal case), then messages 2 and 3 are eliminated. In either case the packet data only travels across the bus once.

This system uses a layered architecture for communication between processors, with a common set of message passing services supporting both control and data paths. It utilizes the bus for the physical layer and either shared-memory DMA-based software or hardware-supported card-to-card transmissions to provide required services for various classes of messages. The three major classes of message are:

Internal control messages: low latency (<10ms), high reliability, low volume.

Network control messages: medium latency (<250ms), high reliability, low volume.

Normal data packets: best effort latency, average (best effort) reliability, high volume.

Note that the system is designed to require only loose synchronization between processors. There are no critical real-time constraints on any control messages between processors that would cause the system to break if they were not met. All inter-processor control functions must tolerate lost messages. Some data loss will be

acceptable. For instance, a route cache update or a port down message could be lost, as long as the system continues to run smoothly.

At the lowest layer above the actual data movement function is a dual-queue structure, as illustrated in Fig. 8, which supports these message classes according to their primary service requirements. These queues may be supported in software, in hardware, or in a combination of the two. One queue is designed to provide high reliability and low latency with relatively low throughput, and is used for the first two classes of messages -- internal and network control messages. The second queue is optimized for high throughput and supports the majority of the data traffic.

10

5

Both control messages and data packets are encapsulated with a standard header which conveys the message type, destination addressing (output port, control interface, etc.), and other control information associated with the message. For internal control messages this additional information might include sequence numbers, event handles, etc., while data packets might have MAC encapsulation type, transmission priority, etc.

15

20

Fig. 8 illustrates the basic dual queue structure used in the messaging paths. In this structure, the card will include a plurality of physical interfaces, generally 150. Inbound data from the physical interfaces is placed in an inbound multiplexing packet processing queue 151, generally implemented by software. This packet processing queue does the basic data transport processes as described above. From this queue 151, the messages which encapsulate the packets are transferred to a high throughput queue 152 implemented at either hardware or software. From the high throughput queue, messages are transferred out onto the bus transmission path 153.

25

Alternatively, communications which must be reliable are passed through a reliable receive and transmit block 154 where they are tagged for preferential handling at the receive end, and manually passed to a high priority, low latency queue (HRQ 155) and out through the bus transmit function 153. Similarly, cells of data received from a bus receive path 156 is passed either through a high reliability queue 157 or a high throughput queue 158. The high reliability queue is passed to the reliable receive and transmit block 154 into the outbound demultiplexing packet processing queue 159. Alternatively, control and management functions 160 receive data through the reliable

30

.

path. The outbound software queue 159 sends appropriate packets to the physical interfaces 150. There may also be a path between the inbound and outbound software queues 151 and 159.

As illustrated in the figure, preferably the lower level queues 152, 155, 157, and 158 are implemented in the hardware assisted environment while the higher level queues 151 and 159 are software executed by a local processor on the board. However, in the central processor unit, the lower level queues may be implemented in software which serves the IOM blocks described above with respect to Fig. 2, and interface processors may be implemented in the particular application with these queues in software.

Fig. 9 provides a table of the various data transfers supported by the system of the preferred embodiment. The table indicates the transfer type across the top row, including a message transmit, a shared memory write, a shared memory access read, a shared memory read, a memory move, a cell transmit, a message receive, a bus input/output and bus memory write, a bus read, and a promiscuous receive transfer. The table summarizes the source of the source address, the source of the destination address, the direction of the transfer, the origin of the cycle, the receive activity, the data buffering, and the alignment and packing functions for each of the different transfers.

Thus, the system includes a number of hardware and software system buffer structures and control and management modules. Generally, data fragments are gathered and byte-wise aligned to form cells which move across the bus. At the receiving end, cells may be placed into a receive buffer as allocated by the receiving processor.

The basic structures include a command list, a free list, and a receive list.

The command list is a managed string of four word entries through which software instructs hardware to perform certain data transfers, generally across the bus. The blocks of memory to be moved may be thought of as buffers, or as data fragments. There is no hardware requirement for these chunks of data to be aligned or sized in any specific way. Implicit in the source and destination address along with the command list entries control field is the type of data transfer. The command list is

30

25

5

10

15

built in synchronous dynamic RAM (SDRAM) and may be FIFOed (or cached) within the message passing controller hardware. Software writes entries into the command list, while hardware reads and executes those commands. The command list is managed via command head and command tail pointers.

5

The free list is a series of single word entries pointing to available or "free" receive buffers which may be allocated by hardware for buffering inbound bus data. The free list is maintained in SDRAM and may be FIFOed or cached within the message passing controller hardware. Software places free receive buffers into the free list so that hardware may then allocate a free buffer to a given receive channel, as required by incoming data. Once the buffer is actually filled, hardware places the buffer pointer into one of two receive lists. Only software writes entries to the free list, and those entries are known to be valid by the contents of the software based free tail pointer. Hardware may read entries from the list, and the only indication of what has been read is the value of the hardware-owned free head pointer.

15

10

The receive list is a series of two word entries pointing to full receive buffers which need the attention of software. The list itself is SDRAM resident and the list entries point to receive buffers which also reside in SDRAM. In addition to the physical address of the filled buffer, the receive list entry includes a flag and count field.

20

25

Figs. 10A and 10B show the data flow beginning with a command list and eventually showing up on a normal priority receive list.

As can be seen in Figs. 10A and 10B, a command list 200 includes a sequence

of four word entries. For example, the four entries 201, 202, 203, and 204 characterize a transfer from a network interface in one processor across the bus to a network interface in a different processor. The first entry is recognized as the beginning of a message, includes a pointer 204 to a source buffer, a destination address 205 indicating the destination slot (and bus if plural busses are used) of the message, and a data length field 206. The next entry 202 includes flag indicating that it is a middle fragment, a pointer 207 to a source buffer, and a data length field. The third entry in the list

203 includes a control parameter indicating that it is a middle fragment, a pointer

208 to a source buffer, and a data length field. The final entry 204 includes a

header indicating that it is the end of the message, a pointer 209 to the source buffer and a length field.

The transmit buffers pointed to by the pointers 204, 207, 208, and 209 contain the data of the message. They are concatenated according to the protocol and data length information in the first buffer pointed to by the pointer 204. The message packing buffers are used to generate a first bus cell generally 210 which includes a destination slot address, an indicator that it is the first cell in a message, and a count. The first cell in this example includes the contents of the buffer from pointer 204, the buffer from pointer 207, and a portion of the buffer at pointer 208.

10

5

The balance of the buffer at pointer 208 and the first portion of the buffer at pointer 209 are combined into the second cell 211. The balance of the buffer at pointer 109 is placed into the last cell 212.

The outbound path in the receiving processor loads the incoming data into the receive buffers 213 and creates an entry in the normal priority receive queue for the receive buffer.

The receive data structure is illustrated in Fig. 11. Basically, an incoming data stream is allocated to receive buffers using the free list 220, the channel status SRAM 221, the free list FIFO 222, and the high and low priority receive queues 223 and 224.

20

15

The hardware keeps state information for 32 receive channels. Each channel allows one message to be assembled into a cohesive message in memory. The channel keeps pointers to the next place to store the cell as well as a count and status information associated with the message. In one embodiment, receive channels are allocated to particular slots. Thus, slot zero on the bus will be given channel zero, for every processor on the bus; slot one will be given channel one; and so on.

25

The free list 220 is managed with a free head pointer 225 and a free tail pointer 226. Basically, buffers between the hardware owned free head pointer 225 and the software owned free tail pointer 226 are available for the hardware. Buffers pointed to by pointers above the free head pointer are either invalid because they contain data from previously received messages yet to be processed, are in use by a particular channel, or have been taken over by the hardware and loaded into the free list FIFO 222. In the example illustrated in Fig. 11, the invalid pointer N and invalid pointer O

5

10

15.

20

25

30

represent pointers to buffers which have been processed, and would be available for hardware when the free tail pointer is moved by the software.

Figs. 12A and 12B provide a receive queue example. The receive queue 230 is managed using a receive queue head pointer 231 and a receive queue tail pointer 232. Each entry in the receive queue includes flags, count, and a buffer pointer for a specific buffer. Thus, those entries between the head 231 and the tail 232 contain pointers to buffers in use. Thus, an entry 233 includes a flag indicating that it is both the first and the last cell in a particular message, a length value, and a channel identifier. Entry 233 also includes a buffer pointer to the end of buffer 234. In an alternative embodiment, the buffer pointer points to the beginning of the buffer, as can be seen, this is a pointer to a buffer in channel three of length 80.

The next entry 235 is the first buffer in a 256 byte transfer in channel three with a pointer to buffer 236. The next buffer in this message is characterized by entry 237. It includes a pointer to buffer 237 and a parameter indicating that it is the middle transfer in the message. The last cell in this message is characterized by entry 239, which includes a pointer to buffer 240. The other examples shown in Figs. 12A and 12B include transfers that are characterized through a second channel, channel two, as described in the figure.

Hardware calculates the difference between the free head and the free tail pointers and uses that value to decide when to drop buffers in the receive queue to free up space to accept additional messages. This mechanism provides higher reliability to high reliability queue, and a lower reliability to high throughput transfer queue which are found in the receive list. Hardware will provide a number of watermarks that can be used to determine whether to accept new high throughput queue messages, or whether to drop them. The high throughput messages will be dropped so that the free list will not become depleted and high reliability queue messages can always be received. The source of the high reliability queue messages either has to have exclusive permission to send X number of frames, or get new permission occasionally through a handshake protocol, or the sender can rate limit requests to some number/second that the receiver must be configured to handle.

This mechanism will also be used to provide several levels of priority to provide some level of fairness among the high throughput traffic. The concept is to mark a small number of packets per second as high priority, and the rest as normal priority. The receive hardware will start dropping normal priority messages first, and this should guarantee that each slot can get data through, even in the case of another sender trying to hog the bandwidth.

5

10

15

20

25

30

Fig. 13 illustrates transmit list and receive list processes according to one embodiment of the present invention. As can be seen in the figure, the transmit side includes a high priority command list 250 and a normal priority command list 251. In the message passing process, a command transmit function 252 is included which is coupled with both the high priority command list 250 and the normal priority command list 251. This transmit function 252 transmits commands across the backplane bus 253, or other communication media such as a LAN, to a receive filtering process 254 at the receiving end of the message transfer. Receive filtering process 254 also includes dispatch logic which dispatches the messages to either a high priority receive list 255 or a normal priority receive list 256.

In operation, these functions are managed by software according to latency, throughput, and reliability of the messages being transmitted. For example, software may write commands for messages that require low latency into the high priority command list 250, while writing the majority of commands which require high throughput into the normal priority command list. According to this approach, the command transmit function 252 can select commands for transmission according to a simple priority rule: any high priority message goes ahead of any normal priority message. More complex priority schemes, including fairness concepts and avoiding lockouts could be utilized as suits a certain implementation. Messages transmitted across the backplane 253 are accepted by the receive filtering function 254. The filtering function drops the cells in a message according to the available buffers as measured against watermarks based on reliability tags in the message header, and routes the received messages to either the high priority receive list 255 or the normal priority receive list 256, based on a control bit in the message header. For example, in a system with two receive buffer watermarks, there will be three levels of reliability

5

10

15

20

25

30

(or cell loss priority) established. All those cells making up a message in a first class will be dropped if the number of available receive buffers falls below a first watermark before all cells of a message are received. Cells of messages in a second class will be dropped when the number of available buffers falls below a second watermark. Cells of messages in the final class are dropped only if there are no receive buffers left to receive incoming cells of the message. Both the watermark class, which establishes the reliability of transfer, and the destination receive queue to which the message is dispatched, are specified in the message address, as control bits in a preferred embodiment. Thus, from the hardware point of view, the receive lists 255 and 256 are identical in behavior. Software manages the processing of messages listed in the high priority receive list and the normal priority receive list as desired in a particular implementation. For example, the software may process all high priority receive list messages first, so that so called low latency messages can achieve lowest latency available. High throughput messages will be routed into the normal priority receive list, and managed as quickly as possible by the receiving processor.

Figs. 14 and 15 illustrate the data paths and address paths for message passing controller hardware. The message transmit data path is illustrated in Fig. 14. The possible sources of the data include a processor write data on line 260, data from the local synchronous DRAM (SDRAM) on line 261, and data from the bus on line 262. The path on line 260 which provides processor write path is not used in one embodiment of the invention. Data is directed to the bus on line 263, to the local synchronous DRAM on line 264, or to the local processor directly during a processor read operation on line 265. The processor write data is supplied through a bus write buffer 266 to an output multiplexer 267. Data from the SDRAM on line 261 is supplied through multiplexer 268 across line 269 to a packing cell buffer 270. The output of the packing cell buffer 270 is supplied on line 271 to the output multiplexer 267. It is also supplied in feedback to the inbound multiplexer 272.

Data from the bus on line 262 is supplied to a receive cell buffer 273, the output of which is supplied as a second multiplexer 272. Also, data from the bus is supplied as a second input to the multiplexer 268 which supplies input to the packing

cell buffer 270. Further, data from the bus is supplied on line 265 directly to the processor read path.

As can be seen in the figure, the message transmit data path is sourced from the SDRAM on line 261, and selected through multiplexer 268 into the packing cell buffer 270. From the packing cell buffer 270, it is supplied through multiplexer 267 out onto the bus.

5

10

15

20

25

30

Fig. 15 illustrates the address path structures, and the message transmit address path. As can be seen, the addresses are generated in response to the command lists 300, and from the bus address in line 301. Addresses from the command list drive a source address generation block 302, and a destination address generation block 303. The output of the source address generation block is supplied through multiplexer 304 to the address out multiplexer 305. The output of the destination address generation block 303 is supplied through the message address generator 306 to the bus address output multiplexer 305, and to the multiplexer 307 in the inbound path. Also, the destination address generation output is supplied as a second input to multiplexer 304 in the output path, and as an input to multiplexer 308 in the input path. The source address generation block also sources the synchronous DRAM read address line 309.

Other inputs to the multiplexer 305 include a processor read address directly from the local processor on line 310, and a tag address on line 311.

The bus address register 312 is driven by the address in on line 301. The output of the register 312 is supplied through multiplexer 307 to the message address register 313. This address register identifies the channel for the message which is used to access the channel status RAM 314. The channel status RAM supplies a receive buffer address as an input to multiplexer 308. The mechanism also includes a promiscuous receive address generator 315 which supplies a third input to the multiplexer 308. The output of the multiplexer 308 is the synchronous DRAM write address counter 316, which drives the synchronous DRAM write address on line 317.

As can be seen, the message transmit address path originates with the command list 300. The command list drives the source address generation block 302 to supply a synchronous DRAM read address on line 309. Also, the command list drives the destination address generation block 303 to supply a message address

PCT/US96/06562 WO 96/35988

generator 306. This basically supplies the slot number and channel number for the message to be supplied on the output bus.

Hardware initiates message transmit from a command list maintained in SDRAM. The message may consist of multiple fragments stored in SDRAM memory which are then packed into double-buffered outbound cells. The bus transfer address is really a message control field containing such things as a field identifying the cell as part of a message, the destination slot and logic channel, first and last cell control bits, and the cell sequence number within the message.

To transmit a message fragment:

- read command list entry, decode as outbound msg fragment (for addr generation).

- recognize first, middle, last fragment of a message (for outbound buffer control purposes).

- request SDRAM read access (and check packing cell buffer availability).

- wait for granting of SDRAM resource.

- if buffer available, begin transferring data bytes/words from SDRAM to cell buffer.

- continue to move data to cell buffers (with data flow control).

- maintain cell buffer byte count and buffer status to implement flow control.

- pack and align data within cells.

- generate message address for bus (including first, last, sequence information).

- generate bus transfer byte count field (depends on size of buffer flush).

- queue cell for flush (i.e., bus transmit).

- arbitrate for bus interface resource (other functions may request bus transfer).

- wait until bus interface granted.

- arbitrate for ownership of bus.

- move data words from cell buffer to bus interface (with flow control).

- generate or check outbound data parity.

- complete burst write on bus.

5

15

25

20

- log cell transmit status (success/fail).

- free cell buffer for more outbound data.

- move more data from SDRAM into cell buffer.

- continue this process until fragment move is complete.

- update command list pointer (indicates transfer complete).

To transfer a complete message:

5

10

15

20

- process multiple fragments from command list as detailed above (a message may be a single fragment).

- pack fragments into continuous cells without gaps.

- flush partial cell buffer when message ends.

- notification of message sent.

Fig. 16 shows the structure of the Message Receive Logic Block 410 of Fig. 35. Any data transfer bound for SDRAM moves through this logic. Message and non-message transfers are treated differently: cells which are part of a message transfer are moved into the SDRAM receive buffer structure, while non-message cells do not move into receive buffers - they are written to a specific physical SDRAM address.

Quite a bit of the logic in this section is associated with management of the receive buffers and bus logical receive channels.

The major functional blocks are summarized as follows:

get free buffs 500

Maintain status of the double-buffered free list buffer FLB. Post ibus read requests and manage movement of data into the FLB from IBUS. Contains free head reg, free tail reg, free start reg, and free\_size\_reg registers.

buffer\_alloc 501

Allocate buffers from the FLB to logical receive channels. Read the next sequential FLB entry and write it into the channel status buffer CSB along with a zero count field. Maintain the Channel Status validity register. This module is necessarily

quite intimate with an icb\_flush module 504 which needs to mark CSB entries invalid as they are flushed to receive buffers and which needs to check for a valid channel status entry before flushing an ICB message cell to SDRAM.

5 rev buff flush 502

Manages the queuing and flushing of completed receive buffers onto the two receive lists maintained in SDRAM. Buffers and status are moved into the rcv and hrcv list buffers (RLB and HLB) by the flush\_to\_ibus function. Then, the rcv\_buff\_flush function manages posting requests to the ibus and the associated flushing of the RLB and HLB.

msg\_rcv\_and\_icb\_fill 503

Moves data from bus into the ICBs. Writes the ICB tags. Performs receive filtering (perhaps).

15

20

25

30

10

flush to ibus 504

Reads ICB tags and performs ICB flush to IBUS. Updates CSB cell count field and determines when an entry moves from the CSB to the RLB or HLB. Writes RLB entries based on CSB and ICB tags. Checks cell sequence and maintains channel status -may drop ICBs and report error conditions.

gen icb flush addr (within flush to ibus 504)

This function takes the bus channel status RAM contents and conditions them to create an ibus address for flushing one of the ICBs. At the same time, the cell count associated with the logical bus receive channel is incremented for write back into the channel status RAM or into the rcv\_list buffer RAM. Some registering logic may be required in this path, since the CSB is being modified as the flush occurs.

The get\_free\_bufs block 500 generates addresses and requests for management of the free list buffer 505. Thus, outputs of the block 500 include the free list buffer read address on line 506, the free list buffer fill request on line 507, and the free list buffer addresses on line 508. In response to requests from the get\_free\_bufs block

500, the free list buffer data is supplied from the intermediate bus on line 509 to the free list buffer 505. Data from the free list buffer is supplied on line 510 to the channel status buffer 511. This process is managed by the buffer allocation block 501, which maintains the watermark registers and the channel status validity registers. The channel status buffer outputs are supplied on line 512 to the flush\_to\_ibus block 504. Also, addresses from the flush\_to\_ibus block 504 are supplied on line 513 to the channel status buffer for accesses to it.

5

10

15

20

25

30

The rcv\_buff\_flush block 502 manages the high priority receive buffer 514 and the normal priority receive buffer 515. This block manages the receive buffer validity, and the tail registers for the receive buffers. Outputs of this block include receive buffer addresses on line 516, the receive list addresses on line 517, receive list length value on line 518, and a receive list flush request on line 519.

The incoming data path from the system bus is driven across line 520 to the incoming cell buffers generally 521. Write addresses for the incoming cell buses are supplied on line 522 from the msg\_rcv\_and\_icb\_fill block 503. Block 503 receives the addresses from the system bus on line 523 and generates the incoming cell buffer addresses on line 522. Also, the block 503 manages the incoming cell buffer tags 524.

Data from the incoming cell buffers are flushed to the internal bus under control of the flush\_to\_ibus block 504. This block receives the channel status on line 512 and buffer size information on line 525. It generates the read addresses for the incoming cell buffers on line 526 and causes a flush of data on line 527 to the local SDRAM. This block also generates the incoming cell buffer flush request on line 528, the flush address on line 529, an the flush length value on line using two control signals 530 for management of the flush to the local memory.

Fig. 17 shows the structure of the Command List Data Transfer Logic. The MPC transfers data according to commands placed by software onto one of two command lists (NCLB 600, HCLB 601) or onto a high priority one-shot command buffer (OSCB 602). All data transferred under command list flows through the packing cell buffers 608 PCBs, and both source and destination (fill and flush) may be either system bus or internal bus.

The major functions of this block are summarized as follows:

parse cmd 604

Read entries from the CLBs 600, 601 and OSCB 602. Determine which command to next process. Associate multiple CLB entries and handle as a single message (cause packing to occur). Move address entries to fill\_pcb module 606.

Write CLBs invalid once entries are processed. Flush entries for a message that hits an error condition.

fill clb 605

Generate ibus request to get next block of CLB entries. Mark CLBs valid as they are successfully filled.

fill pcb 606

Generate request to either ibus or bus to read data (through byte\_packer) into PCBs. Flow-control filling of PCBs. Write PCB tags.

15

20

25

30

5

flush\_pcb 607

Read PCB tags. Generate request to either ibus or system bus to flush PCBs. Write PCB tags empty once transfer completes.