(19)日本国特許庁(JP)

## (12)特許公報(B2)

(11)特許番号

特許第7445894号

(P7445894)

(45)発行日 令和6年3月8日(2024.3.8)

(24)登録日 令和6年2月29日(2024.2.29)

(51)国際特許分類

|        |                 |        |       |         |

|--------|-----------------|--------|-------|---------|

| H 02 H | 3/16 (2006.01)  | H 02 H | 3/16  | A       |

| G 01 R | 31/52 (2020.01) | G 01 R | 31/52 |         |

| H 02 J | 1/00 (2006.01)  | H 02 J | 1/00  | 3 0 9 S |

請求項の数 5 (全12頁)

|          |                             |          |                                   |

|----------|-----------------------------|----------|-----------------------------------|

| (21)出願番号 | 特願2020-219384(P2020-219384) | (73)特許権者 | 516131843                         |

| (22)出願日  | 令和2年12月28日(2020.12.28)      |          | A N P 株式会社                        |

| (65)公開番号 | 特開2022-104280(P2022-104280) |          | 滋賀県近江八幡市安土町常楽寺 975                |

|          | A)                          | (73)特許権者 | 516091112                         |

| (43)公開日  | 令和4年7月8日(2022.7.8)          |          | 神崎産業株式会社                          |

| 審査請求日    | 令和5年3月9日(2023.3.9)          |          | 三重県三重郡菰野町大字川北 2957 番地 2           |

|          |                             | (74)代理人  | 100095267                         |

|          |                             |          | 弁理士 小島 高城郎                        |

|          |                             | (74)代理人  | 100124176                         |

|          |                             |          | 弁理士 河合 典子                         |

|          |                             | (72)発明者  | 羽田 正二                             |

|          |                             |          | 滋賀県近江八幡市安土町常楽寺 975 番地 A N P 株式会社内 |

|          |                             | 審査官      | 下林 義明                             |

最終頁に続く

(54)【発明の名称】 漏電検出装置

## (57)【特許請求の範囲】

## 【請求項 1】

直流電源の正極に接続される第1のライン(L1)と前記直流電源の負極に接続される第2のライン(L2)との間に、第1の抵抗要素(R1)と第2の抵抗要素(R2)とが中点(N1)で直列接続された漏電検出装置において、

前記中点(N1)の中点電位(V1)が所定の正電位と所定の負電位との間で変動可能であるようにクランプする中点電位クランプ回路(30)と、

前記第1のライン(L1)に一端が接続された第1の電流路と、前記中点電位(V1)が印加されて前記第1の電流路の電流を制御する第1の制御端(Con1)とを具備する第1の地絡電流用回路(10)と、

前記第2のライン(L2)に一端が接続された第2の電流路と、前記中点電位(V1)が印加されて前記第2の電流路の電流を制御する第2の制御端(Con2)とを具備する第2の地絡電流用回路(20)と、を有し、

前記第1及び第2の地絡電流路用回路(10,20)の各々の他端同士が出力点(N2)にて接続され、かつ、前記出力点(N2)の電位(Vo)が前記第1及び第2の制御端(Con1,Con2)の電位に追随するように前記第1及び第2の地絡電流用回路(10,20)がそれぞれ構成されており、

前記第1のライン(L1)又は前記第2のライン(L2)の地絡時に流れる地絡電流を、前記出力点(N2)と接地点との間に接続された検出回路(40,50)により検出することを特徴とする漏電検出装置。

**【請求項 2】**

前記第1及び第2の地絡電流用回路(10,20)が、前記他端をエミッタ又はソースとするエミッタフォロワ回路又はソースフォロワ回路をそれぞれ有することを特徴とする請求項1に記載の漏電検出装置。

**【請求項 3】**

前記中点電位クランプ回路(30)が、逆向きに直列接続された2つのツェナーダイオード(ZD1,ZD2)を有することを特徴とする請求項1又は2に漏電検出装置。

**【請求項 4】**

前記検出回路(40)が、各々異なる抵抗値を有して切替可能に接続された複数の抵抗素子を有することを特徴とする請求項1～3のいずれかに記載の漏電検出装置。

10

**【請求項 5】**

前記検出回路(50)が、全波整流回路と、前記全波整流回路の出力側に接続された定電流ダイオードとを有することを特徴とする請求項1～3のいずれかに記載の漏電検出装置。

20

**【発明の詳細な説明】****【技術分野】****【0001】**

本発明は、中性点接地方式における直流電源の漏電検出装置に関する。

**【背景技術】****【0002】**

従来、直流電源の漏電検出装置として、ホール素子等を用いた零相電流検出方式や、直列接続された2つの抵抗の中点を接地する中性点接地方式などが知られている。零相電流検出方式はオフセット電圧変動の問題がある。中性点接地方式は、直流電源の正極側ラインと負極側ラインの間に中性点(以下「中点」と称する)を設定するために2つの抵抗素子を直列接続してその接続点を接地する構成を有する(例えば特許文献1～3)。中性点接地方式では、送電ラインの地絡が発生したとき、抵抗素子を流れる地絡電流による両端電圧又は分圧の変化、又は、抵抗素子と中点を通って流れる地絡電流を検出することによって地絡を検出している。

**【先行技術文献】****【特許文献】****【0003】**

30

【文献】特開2002-296316号公報

【文献】特開2009-261039号公報

【文献】特開2013-130536号公報

**【発明の概要】****【発明が解決しようとする課題】****【0004】**

従来の中性点接地方式における漏電検出装置においては、直列接続された2つの抵抗素子に地絡電流が流れることを利用して電圧変化又は電流変化により地絡を検出している。消費電力を抑制するためには、定常時に直列抵抗に流れる定常電流をできるだけ少量とすることが望ましい。そのため、中点を設定する抵抗素子の抵抗値を高く設定すると、地絡時の感度電流が例えば数mA程度の高感度領域での電流計測になるため、ノイズにも敏感となり誤動作が多くなる。

40

**【0005】**

そこで、抵抗素子の抵抗値を小さくして感度電流を大きくして低感度にしようとする、ノイズには強くなるが、定常時に抵抗素子に流れる定常電流も大きくなり消費電力が大きくなるという問題がある。また、地絡時に2つの抵抗素子が並列合成抵抗となりインピーダンスが低下することによって検出の感度が低下するという問題もある。また、地絡電流が流れる抵抗素子は、高電力用を用いる必要があった。

**【0006】**

以上の問題点に鑑み本発明の目的は、中性点接地方式における漏電検出装置において、

50

中点を設定するための抵抗素子における消費電力を抑制すると同時に、地絡時の地絡電流を低消費電力で精度よく検出することである。

【課題を解決するための手段】

【0007】

上記の目的を達成するべく、本発明は、以下の構成を提供する。なお、括弧内の符号は後述する図面中の符号であり、参考のために付するものである。

【0008】

本発明の態様は、直流電源の正極に接続される第1のライン（L1）と前記直流電源の負極に接続される第2のライン（L2）との間に、第1の抵抗要素（R1）と第2の抵抗要素（R2）とが中点（N1）で直列接続された漏電検出装置において、

10

前記中点（N1）の中点電位（V1）が所定の正電位と所定の負電位との間で変動可能であるようにクランプする中点電位クランプ回路（30）と、

前記第1のライン（L1）に一端が接続された第1の電流路と、前記中点電位（V1）が印加されて前記第1の電流路の電流を制御する第1の制御端（Con1）とを具備する第1の地絡電流用回路（10）と、

前記第2のライン（L2）に一端が接続された第2の電流路と、前記中点電位（V1）が印加されて前記第2の電流路の電流を制御する第2の制御端（Con2）とを具備する第2の地絡電流用回路（20）と、を有し、

前記第1及び第2の地絡電流用回路（10,20）の各々の他端同士が出力点（N2）にて接続され、かつ、前記出力点（N2）の電位（Vo）が前記第1及び第2の制御端（Con1,Con2）の電位に追随するように前記第1及び第2の地絡電流用回路（10,20）がそれぞれ構成されており、

20

前記第1のライン（L1）又は前記第2のライン（L2）の地絡時に流れる地絡電流を、前記出力点（N2）と接地点との間に接続された検出回路（40,50）により検出することを特徴とする。

上記態様において、前記第1及び第2の地絡電流用回路（10,20）が、前記他端をエミッタ又はソースとするエミッタフォロワ回路又はソースフォロワ回路をそれぞれ有することが、好適である。

上記態様において、前記中点電位クランプ回路（30）が、逆向きに直列接続された2つのツェナーダイオード（ZD1,ZD2）を有することが、好適である。

30

上記態様において、前記検出回路（40）が、各々異なる抵抗値を有して切替可能に接続された複数の抵抗素子を有することが、好適である。

上記態様において、前記検出回路（50）が、全波整流回路と、前記全波整流回路の出力側に接続された定電流ダイオードとを有することが、好適である。

【発明の効果】

【0009】

本発明によれば、中性点接地方式における漏電検出装置において、中点を設定するための抵抗素子における消費電力を抑制すると同時に、地絡時の地絡電流を低消費電力で精度よく検出することが可能となる。

【図面の簡単な説明】

40

【0010】

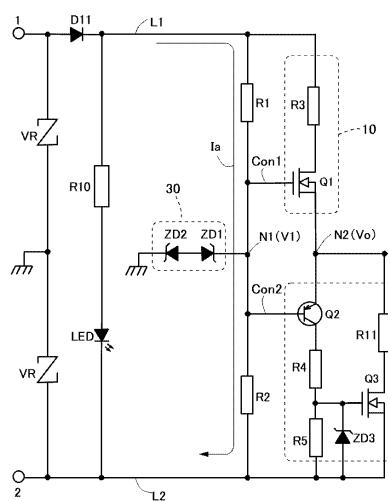

【図1】図1は、本発明による漏電検出装置の回路構成の一例を示した図である。

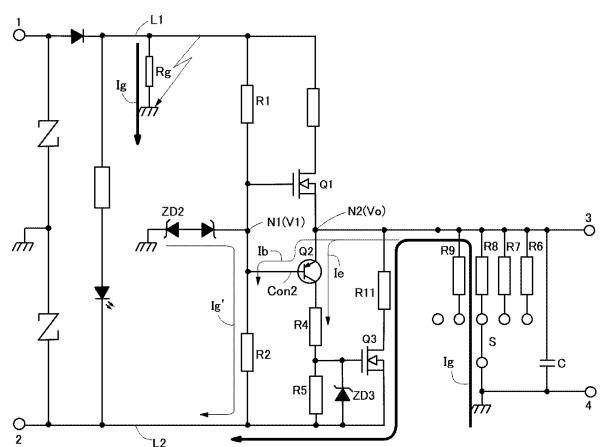

【図2】図2は、図1の漏電検出装置において正極側のライン上で地絡が発生したときの主要な電流の流れを示している。

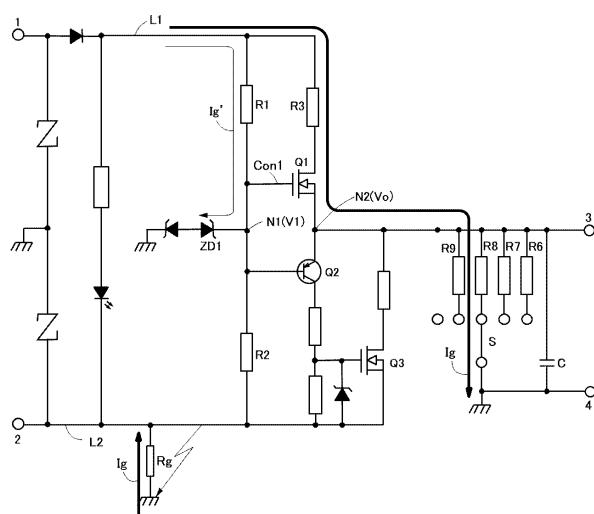

【図3】図3は、図1の漏電検出装置において負極側のライン上で地絡が発生したときの主要な電流の流れを示している。

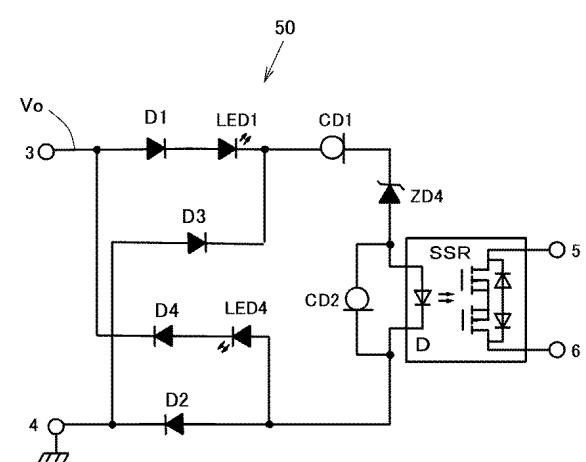

【図4】図4は、図1の漏電検出装置に任意に含まれる警報出力部の回路構成の一例を示した図である。

【発明を実施するための形態】

【0011】

50

以下、図面を参照しつつ、本発明による漏電検出装置の実施形態について詳細に説明する。本発明の漏電検出装置は、限定しないが好ましくは、直流電源の送電ラインから大地への漏電、すなわち地絡を検出するために用いられる装置である。地絡による漏電電流は、地絡電流と称されている。

【0012】

(1) 回路構成

図1は、本発明による漏電検出装置の主要部の回路構成の一例を示した図である。本発明の漏電検出装置は、直流電源(図示せず)の正極1に接続される第1のラインL1と、直流電源の負極2に接続される第2のラインL2との間に配置されている。

【0013】

本発明の漏電検出装置は、直流電源及びその負荷(図示せず)と並列に接続されている。直流電源は、例えば太陽光発電装置や蓄電池などであるが、これらに限られない。一例として、正極1の電位が+数百ボルト(例えば+190V)、負極2の電位が-数百ボルト(例えば-190V)である。

【0014】

<中点設定用の抵抗要素>

図1に示す漏電検出装置は、中性点接地方式であり、ラインL1とラインL2との間に、中点を設定するための第1の抵抗要素R1と第2の抵抗要素R2とが直列接続されている。抵抗要素R1と抵抗要素R2は、同じ抵抗値を有することが好ましいが、厳密に同じである必要はない。抵抗要素R1、R2はそれぞれ、1つの抵抗素子又は直列接続された複数の抵抗素子により構成することができる。抵抗要素R1と抵抗要素R2との接続点を「中点N1」と称し、中点N1の電位を「中点電位V1」と称することとする。なお、「抵抗素子」は、線形抵抗素子の意味で用いる。

【0015】

図1には、定常時(地絡が発生していないとき)に抵抗素子R1、R2に流れる定常電流Iaを示している。抵抗要素R1、R2は、定常時の消費電力を抑制するために十分に大きな抵抗値、例えば数百キロオーム~数メガオームの抵抗値とする。例えば電源電圧が+ - 190Vの場合、抵抗要素R1、R2をそれぞれ1Mとすると、定常時に流れる定常電流Iaは約0.2mAである。このような低レベルの定常電流Iaは、定常時の消費電力を抑制できるが、地絡時に抵抗要素R1、R2に流れる電流を用いて地絡検出を行うと、高感度領域での計測となるためノイズの影響を受けやすい。本発明の漏電検出装置では、これらの抵抗要素R1、R2に流れる電流を直接的に検出しないので、抵抗要素R1、R2を十分に高抵抗とすることができます。

【0016】

<中点電位クランプ回路>

さらに、接地電位である接地点と中点N1との間には、中点電位クランプ回路30が接続されている。図示の例では、中点電位クランプ回路30は、逆向きに直列接続された2つのツエナーダイオードZD1、ZD2により構成されている。ツエナーダイオードZD1とツエナーダイオードZD2は、同じツエナー電圧を有することが好ましいが、厳密に同じである必要はない。

【0017】

中点電位クランプ回路30は、中点電位V1が所定の正電位と所定の負電位との間でのみ変動可能であるようにクランプする役割を果たしている。ツエナー電圧をVzとすると、ツエナーダイオードZD1は、中点電位V1の上限を+Vzにクランプする。一方、ツエナーダイオードZD2は、中点電位V1の下限を-Vzにクランプする。したがって、中点電位V1は、接地電位を挟んで-Vz~+Vzの範囲内でのみ変動可能である。中点電位クランプ回路30の構成は、同等の機能をもつ回路であれば図示の構成に限定されない。

【0018】

また、限定しないが、ツエナー電圧Vzは15~25ボルト程度(例えば20V)とす

10

20

30

40

50

ることが好ましい。これは、中点電位  $V_1$  が、後述する第 1 及び第 2 の地絡電流用回路の制御端  $C_{on1}$ 、 $C_{on2}$  に印加される制御電圧として用いられるためである。

【0019】

<地絡電流用回路>

さらに、ライン  $L_1$  とライン  $L_2$  との間には、出力点  $N_2$  で接続された第 1 の地絡電流用回路  $1_0$  と、第 2 の地絡電流用回路  $2_0$  とが直列に配置されている。符号  $V_o$  は、出力点  $N_2$  の電位を示す。電位  $V_o$  は、漏電検出装置（その検出回路  $4_0$ ）の出力端子 3 の電位である。本発明の漏電検出装置は、地絡時の地絡電流の大部分が第 1 又は第 2 の地絡電流用回路  $1_0$ 、 $2_0$  に流れるように構成されている。

【0020】

第 1 の地絡電流用回路  $1_0$  は、一端が第 1 のライン  $L_1$  に接続された第 1 の電流路と、第 1 の電流路を流れる電流を制御する第 1 の制御端  $C_{on1}$  とを有する。第 2 の地絡電流用回路  $2_0$  は、一端が第 2 のライン  $L_2$  に接続された第 2 の電流路と、第 2 の電流路を流れる電流を制御する第 2 の制御端  $C_{on2}$  とを有する。第 1 及び第 2 の制御端  $C_{on1}$ 、 $C_{on2}$  はいずれも中点  $N_1$  の中点電位  $V_1$  が印加される。第 1 の地絡電流用回路  $1_0$  と第 2 の地絡電流用回路  $2_0$  の他端同士は、出力点  $N_2$  で接続されている。出力点  $N_2$  の電位  $V_o$  が第 1 及び第 2 の制御端  $C_{on1}$ 、 $C_{on2}$  の電位に追随するように第 1 及び第 2 の地絡電流用回路  $1_0$ 、 $2_0$  は、エミッタフォロワ回路又はソースフォロワ回路をそれぞれ有する。地絡電流用回路  $1_0$ 、 $2_0$  の具体的構成は、多様に設計可能である。

【0021】

図 1 に示す第 1 の地絡電流用回路  $1_0$  の一例では、第 1 の電流路が、抵抗素子  $R_3$  及び  $n$  チャネル  $FETQ_1$  により構成されている。抵抗素子  $R_3$  の一端が第 1 のライン  $L_1$  に接続されている。抵抗素子  $R_3$  の他端に  $FETQ_1$  のドレインが接続され、 $FETQ_1$  のソースが出力点  $N_2$  に接続されている。 $FETQ_1$  のゲートが第 1 の制御端  $C_{on1}$  である。 $FETQ_1$  は、ソースフォロワ回路を構成している。したがって、ソース電位すなわち出力点  $N_2$  の電位  $V_o$  は、制御端  $C_{on1}$  の電位に追随する。第 1 の制御端  $C_{on1}$  は中点  $N_1$  に接続されており、中点電位  $V_1$  が印加される。

【0022】

図 1 に示す第 2 の地絡電流用回路  $2_0$  の一例では、第 2 の電流路が、直列接続された抵抗素子  $R_4$ 、 $R_5$  及び  $pnp$  トランジスタ  $Q_2$  とからなる電流路と、抵抗素子  $1_1$  及び  $n$  チャネル  $FETQ_3$  とからなる電流路とを含み、2 つの電流路が並列に配置されている。ここでは、主として  $FETQ_3$  の電流路の方に電流が流れる。

【0023】

抵抗素子  $R_4$ 、 $R_5$  の一端が第 2 のライン  $L_2$  に接続されている。抵抗素子  $R_4$ 、 $R_5$  の他端がトランジスタ  $Q_2$  のコレクタに接続され、トランジスタ  $Q_2$  のエミッタが出力点  $N_2$  に接続されている。トランジスタ  $Q_2$  のベースが第 2 の制御端  $C_{on2}$  である。トランジスタ  $Q_2$  は、エミッタフォロワ回路を構成している。したがって、エミッタ電位すなわち出力点  $N_2$  の電位  $V_o$  は、制御端  $C_{on2}$  の電位に追随する。第 2 の制御端  $C_{on2}$  も中点  $N_1$  に接続されており、中点電位  $V_1$  が印加される。

【0024】

$FETQ_3$  のゲートには、抵抗素子  $R_4$  と抵抗素子  $R_5$  の接続点の電位が印加される。ツエナーダイオード  $ZD_3$  は過電圧保護用である。 $FETQ_3$  のソースはライン  $L_2$  に接続され、ドレインは抵抗素子  $R_11$  を介して出力点  $N_2$  に接続されている。

【0025】

第 2 の地絡電流用回路  $2_0$  の別の例として、 $FETQ_3$  を設けずにエミッタフォロワのトランジスタ  $Q_2$  のみで構成することもできる。第 1 及び第 2 の地絡電流用回路は、多様な構成が可能であるが、中点電位  $V_1$  により制御される制御端  $C_{on1}$ 、 $C_{on2}$  を有すること、及び、出力点  $N_2$  をエミッタ又はソースとするエミッタフォロワ回路又はソースフォロワ回路を有してあり出力点  $N_2$  の電位  $V_o$  が制御端  $C_{on1}$ 、 $C_{on2}$  の電位  $V_1$  に追随するように構成されることが重要である。

10

20

30

40

50

## 【0026】

定常時には、第1及び第2の地絡電流用回路10、20の電流路を構成するFETQ1、トランジスタQ2、FETQ3はいずれもオフ状態であり、ラインL1、L2が受ける外来ノイズ等による微小電流しか流れない。この定常時の微小電流は、ラインL1、L2の電位を維持することに寄与する。定常時の第1及び第2の地絡電流用回路10、20の消費電力はほぼ零である。

## 【0027】

## &lt;検出回路&gt;

さらに、出力点N2と接地点との間に検出回路40が接続されている。図1に示す検出回路40の一例では、各々異なる抵抗値を有する4つの抵抗素子R6、R7、R8、R9が配置されている。各抵抗素子は、例えば数百～数キロの抵抗値を有する。各抵抗素子が出力点N2と接地点との間に選択的に接続されるように、スイッチSにより切替可能である。感度調整のための感度電流を設定するために、予想される地絡抵抗や地絡電流の大きさなどに応じて、抵抗素子R6～R9のいずれかが予め選択され接続される。

10

## 【0028】

定常時には、出力点V0の電位は接地電位である。地絡時には、抵抗素子R6～R9のうち選択された抵抗素子に地絡電流が流れる。地絡電流の向きに応じて端子3と端子4(接地点)間に正又は負の電圧が出力される。コンデンサCは、ノイズ抑制用の平滑コンデンサである。図1では、スイッチSの選択位置の一つにオープン位置が示されているが、これについては、図4において説明する。

20

## 【0029】

本発明の漏電検出装置では、1つの検出回路40が正側及び負側のいずれの地絡時にも兼用される。従来方式で、抵抗要素R1と抵抗要素R2の各々の分圧を用いて地絡検出する場合、正側及び負側の地絡時の各々に対応するために正側と負側の検出回路を設ける必要があり、両方の検出回路の抵抗値を揃える必要もあった。検出回路が、選択可能な複数の抵抗素子からなる感度調整機能を有する場合、本発明では一組のみ設ければよいので、設計も製作も容易である。

## 【0030】

検出回路の別の例として、複数の抵抗素子に替えて、定電流値の異なる複数の定電流ダイオードを用いることもできる。その場合、各抵抗素子に替えて逆向きに直列接続された2つの定電流ダイオードを配置する。定電流ダイオードを流れる地絡電流が定電流値よりも増えようとすると定電流ダイオードの両端電圧が上昇することによって検出を行う。

30

## 【0031】

## &lt;その他の構成要素&gt;

任意要素として、漏電検出装置を過大な入力電圧から保護するための2つのバリスタVRが中点接地されて直列に接続されている。また任意要素として、漏電検出装置を直流電源に対して誤って逆極性に接続した場合の保護用のダイオードD11が順方向に接続されている。さらに任意要素として、ラインL1、L2間に、漏電検出装置の通電表示用の発光ダイオードLEDと抵抗素子R10が接続されている。

## 【0032】

## (2)動作説明

次に、図2、図3を参照して図1の漏電検出装置の地絡時の動作を説明する。漏電検出装置の端子1と端子2の間には、直流電源の両端電圧(以下「電源電圧」と称する)が印加されている。地絡の説明では、便宜上、第1及び第2のラインL1、L2を直流電源の正負の送電ラインとみなして説明する。

40

## 【0033】

地絡時における第1又は第2の地絡電流用回路10、20の両端の抵抗値は、中点設定用の抵抗要素R1、R2の抵抗値に比べて格段に小さくなる。したがって、地絡電流の大部分は第1又は第2の地絡電流用回路10、20に優先的に流れる。なお、第1の地絡電流用回路10は、負側のラインL2の地絡時に地絡電流が流れ、第2の地絡電流用回路2

50

0は、正側のラインL 1の地絡時に地絡電流が流れる。

【0034】

<正側の地絡時>

図2では、正側のラインL 1で地絡が発生した状況を概略的に示している。ラインL 1と接地点との間の地絡抵抗R gで地絡箇所を示している。地絡電流I gは、正側のライン1から地絡抵抗R gを介して接地点へ流れる。地絡抵抗R gの抵抗値は、抵抗要素R 1、R 2の抵抗値に比べて遙かに小さいか又はほぼ零である。

【0035】

正側のライン1の電位はほぼ接地電位となり、接地点と端子2の間に電源電圧が印加される。地絡電流I gの大部分は、図1に示した第2の地絡電流用回路20を流れるので、この部分を流れる電流を同じ符号I gで示している。また、地絡電流I gの一部は、第2の抵抗要素R 2を流れるので、この部分を流れる電流をI g'で示している。

10

【0036】

抵抗要素R 2にはほぼ電源電圧(ツェナーダイオードZD 2の電圧降下分を除く)が印加されており電流I g'が流れる。電流I g'は、図1に示した定常電流I aに比べて増えるが、地絡電流I g全体に比べると格段に(例えば一桁又は二桁)小さい。したがって、地絡時においても抵抗要素R 2の消費電力は抑制されている。これにより、抵抗要素R 2を高電力用とする必要がない。

【0037】

電流I g'が流れることにより、中点電位V 1は接地電位よりも降下する。地絡電流I gが大きくなると電流I g'も大きくなり、中点電位V 1の降下も大きくなる。但し、中点電位V 1の降下はツェナーダイオードZD 2によりクランプされるので、そのツェナー電圧V zを超えて降下することはない。正側の抵抗要素R 1には電流は流れない(無視できる)。

20

【0038】

降下した中点電位V 1が、負側のトランジスタQ 2のベース(制御端Con 2)に印加されることにより、ベース電流I bが流れてトランジスタQ 2のエミッタコレクタ間に電流I eが流れる。トランジスタQ 2に電流I eが流れ、抵抗素子R 4と抵抗素子R 5の接続点の電位がFETQ 3のゲート閾値電位を超えると、FETQ 3のドレインソース間に地絡電流I gが流れることが可能となる。一方、正側のFETQ 1はオフ状態のままである。

30

【0039】

地絡電流I gは、接続中の抵抗素子R 8を通り出力点N 2へと流れ、大部分はFETQ 3の電流路を通って負極側のラインL 2へと流れる。FETQ 3を流れる地絡電流I gは、中点電位V 1に相応して流れることができる。

【0040】

地絡が生じた後も、中点電位V 1は、地絡電流I gや地絡抵抗R gの変動があれば変動するが、その変動範囲は、接地電位と-V zとの間にクランプされる。エミッタフォロワ回路によって出力点N 2の電位V oは中点電位V 1の変動に追随するので、電位V oの変動範囲もほぼ同じである。電位V oは、選択された抵抗素子R 8の両端電圧になる(V o = I g × R 8)。正側の地絡では、地絡電流I gが接地点から出力点N 2へ流れるので、電位V oは負である。

40

【0041】

検出回路の感度調整において、大きい地絡電流I gには小さい抵抗値の抵抗素子を選択し、小さい地絡電流I gには大きい抵抗値の抵抗素子を選択する。いずれの抵抗素子が選択された場合も、電位V oの変動範囲は、中点電位V 1の変動範囲(例えば0~-20V程度)とほぼ同じである。また、地絡電流I gは、好ましくは数mA~数十mA程度を想定される。したがって、抵抗素子R 6~R 9は、この程度の電圧と電流に応じた数百~数キロの抵抗値となる。このような条件の場合、抵抗素子R 6~R 9には問題となるような発熱が生じないことに加え、精度のよい抵抗素子を用いることができる。

50

## 【0042】

地絡電流  $I_g$  により生じる発熱の大部分は FETQ3 のみで生じることになる。したがって、FETQ3 にヒートシンクなどを施すことで発熱対策ができる。また、発熱による FETQ3 の温度特性の変化は、検出精度に影響しない。

## 【0043】

<負側の地絡時>

図3では、負側のラインL2で地絡が発生した状況を概略的に示している。ラインL2と接地点との間の地絡抵抗  $R_g$  で地絡箇所を示している。地絡電流  $I_g$  は、接地点から地絡抵抗  $R_g$  を介して負側のライン2へ流れる。

## 【0044】

負側のライン2の電位はほぼ接地電位となり、接地点と端子1の間に電源電圧が印加される。地絡電流  $I_g$  の大部分は、図1に示した第1の地絡電流用回路10を流れるので、この部分を流れる電流を同じ符号  $I_g$  で示している。また、地絡電流  $I_g$  の一部は、第1の抵抗要素  $R_1$  を流れるので、この部分を流れる電流を  $I_g'$  で示している。

10

## 【0045】

抵抗要素  $R_1$  にはほぼ電源電圧（ツェナーダイオードZD1の電圧降下分を除く）が印加されており電流  $I_g'$  が流れる。電流  $I_g'$  は、図1に示した定常電流  $I_a$  に比べて増え、地絡電流  $I_g$  全体に比べると格段に（例えば一桁又は二桁）小さい。したがって、地絡時においても抵抗要素  $R_1$  の消費電力は抑制されている。これにより、抵抗要素  $R_1$  を高電力用とする必要がない。

20

## 【0046】

電流  $I_g'$  が流れることにより、中点電位  $V_1$  は接地電位よりも上昇する。地絡電流  $I_g$  が大きくなると電流  $I_g'$  も大きくなり、中点電位  $V_1$  の上昇も大きくなる。但し、中点電位  $V_1$  の上昇はツェナーダイオードZD1によりクランプされるので、そのツェナー電圧  $V_z$  を超えて上昇することはない。負側の抵抗要素  $R_2$  には電流は流れない（無視できる）。

## 【0047】

上昇した中点電位  $V_1$  が、正側のFETQ1のゲート（制御端  $Con1$ ）に印加されゲート閾値電位を超えると、FETQ3のドレインソース間に電流が流れることが可能となる。一方、負側のトランジスタQ2及びFETQ3はオフ状態のままである。

30

## 【0048】

地絡電流  $I_g$  は、ラインL1からFETQ1の電流路を通り、出力点N2へと流れ、接続中の抵抗素子  $R_8$  を通り接地点へと流れる。FETQ1を流れる地絡電流  $I_g$  は、中点電位  $V_1$  に相応して流れることができる。

## 【0049】

地絡が生じた後も、中点電位  $V_1$  は、地絡電流  $I_g$  や地絡抵抗  $R_g$  の変動があれば変動するが、その変動範囲は接地電位と  $+V_z$  との間にクランプされる。ソースフォロワ回路によって出力点N2の電位  $V_o$  は中点電位  $V_1$  の変動に追随するので、電位  $V_o$  の変動範囲もほぼ同じである。電位  $V_o$  は、選択された抵抗素子  $R_8$  の両端電圧になる（ $V_o = I_g \times R_8$ ）。負側の地絡では、地絡電流  $I_g$  が出力点N2から接地点へ流れるので、電位  $V_o$  は正である。

40

## 【0050】

検出回路の感度調整については、正側の地絡時について上述した通りである。本発明では、正側の地絡時には負側の地絡電流用回路にのみ地絡電流が流れ、負側の地絡時には正側の地絡電流用回路にのみ地絡電流が流れる。従って、地絡電流を検出するための検出回路は正負兼用の1つのみ設ければ足りる。

## 【0051】

地絡電流  $I_g$  により生じる発熱の大部分は FETQ1 のみで生じることになる。したがって、FETQ1 にヒートシンクなどを施すことで発熱対策ができる。また、発熱による FETQ1 の温度特性の変化は、検出精度に影響しない。

50

## 【0052】

## (3) 警報出力回路の構成

図4は、図1の漏電検出装置の一部を構成する警報出力回路50の一例を示している。警報出力回路50は、図1の検出回路40の後段に接続され、出力点N2の電位V0が端子3に印加され、端子4は接地点である。

## 【0053】

警報出力回路50は、入力段に全波整流回路を有する。入力される電位V0は、正側の地絡時には負電位となるので整流して正電位とするためである。全波整流回路は、正側のダイオードD1及びD2と負側のダイオードD3及びD4とを有し、ダイオードD1のアームに発光ダイオードLED1を直列接続し、ダイオードD4のアームに発光ダイオードLED4を直列接続することによって、正負いずれの側の地絡が生じたかを判別可能としている。

10

## 【0054】

全波整流回路の出力側の両端子間に、定電流ダイオードCD1と、ツェナーダイオードZD4と、定電流ダイオードCD2とが直列接続されている。さらに、フォトMOSリレーSSRの入力ダイオードDが、定電流ダイオードCD2と並列接続されている。定電流ダイオードCD1は、過大電流を制限する保護用でありその電圧降下は無視できる。

20

## 【0055】

一例として、電位V0が-20V～+20Vの範囲で変動可能に設定されている場合、警報出力回路50のツェナーダイオードZD4のツェナー電圧を10V程度に設定する。

## 【0056】

入力される電位V0の絶対値が、ツェナーダイオードZD4のツェナー電圧（例えば10V）に全波整流回路の電圧降下分を加えた電圧（例えば15V）を超えると、ツェナーダイオードZD4と定電流ダイオードCD2に電流が流れ始める。定電流ダイオードCD2に流れる電流が定電流値に達してさらに増えようすると、電流は一定に制限されかつ定電流ダイオードCD2の両端電圧が上昇する。定電流ダイオードCD2の両端電圧がSSRの入力ダイオードDの順方向電圧Vf（約2～3V）を超えると、入力ダイオードDに電流が流れ、SSRがオンする。この例では、電位V0が17～18VになったときにSSRがオンすることになる。

30

## 【0057】

SSRの出力端子5、6は、音響装置、表示装置、又は通信装置等の警報を発する装置や、地絡により損傷する箇所を遮断する装置を起動させるスイッチの役割を果たすことができる。

## 【0058】

ここで、図1に示した検出回路40におけるオープン位置について説明する。図1のスイッチSがオープン位置であるとき、地絡電流Igは、正の地絡時には出力端子4から、負の地絡時には出力端子3から、警報出力回路50の全波整流回路へと流れる。この場合、警報出力回路50は、検出回路40の役割を兼ねることになる。地絡電流Igが増加したときの動作は、オープン位置以外のときの警報出力回路50の動作と同じである。

40

## 【0059】

## (4) まとめ

本発明の漏電検出装置は、中点を設定する直列接続された2つの抵抗要素を有するが、地絡電流はこれらの抵抗要素にはほとんど流れない。その替わりに、第1及び第2の地絡電流用回路を設けて地絡電流の大部分が流れるように構成している。これにより抵抗要素を高抵抗とことができ、抵抗要素における定常時及び地絡時の消費電力を抑制できる。抵抗要素は、高耐圧高電力用を用いる必要がない。

## 【0060】

地絡時には、中点電位が地絡電流の大きさに応じて所定の変動範囲でのみ変動するようになり、検出回路の出力点の電位が中点電位に追随するように第1及び第2の地絡電流用回路をエミッタフォロワ回路又はソースフォロワ回路によって構成している。これにより地

50

絡電流の検出部に過電圧がかからない。また、地絡電流の検出部の回路構成を簡素化できる。

【0061】

負側のラインの地絡時には第1の地絡電流用回路にのみ地絡電流が流れ、正側のライン地絡時には第2の地絡電流用回路にのみ地絡電流が流れる。したがって、一方の地絡電流用回路に地絡電流が流れるとき、他方の地絡電流用回路の影響を受けない。従来は、地絡時に2つの抵抗要素が正極と負極間で並列接続状態となるため、一方の抵抗要素における検出感度が低下する問題があった。

【0062】

本発明の漏電検出装置では、1つの検出回路を正側及び負側のいずれの地絡時にも兼用することができる。

10

【0063】

本発明の実施形態を、例示としての構成を参照して説明したが、本発明の実施形態はこれらに限定されるものではない。本発明の原理に従う限り、多様な変形形態も本発明の範囲に含まれる。

【符号の説明】

【0064】

- 1 直流電源の正極

- 2 直流電源の負極

- 3 出力点

- 4 接地点

- 5、6 SSR出力端子

- L1、L2 ライン（送電ライン）

- ZD1、ZD2、ZD3、ZD4 ツエナーダイオード

- D1、D2、D3、D4 ダイオード

- LED、LED1、LED4 発光ダイオード

- R1、R2 抵抗要素

- R3、R4、R5、R6、R7、R8、R9、R10、R11 抵抗素子

- CD1、CD2 定電流ダイオード

- Q1、Q3 FET

- Q2 トランジスタ

- Rg 地絡抵抗

20

30

40

50

【図面】

【図 1】

【図 2】

【図 3】

【図 4】

10

20

30

40

50

---

フロントページの続き

- (56)参考文献

- 実開昭50-127630 (JP, U)

国際公開第2013/153596 (WO, A1)

特開2010-043916 (JP, A)

特開昭55-029211 (JP, A)

- (58)調査した分野 (Int.Cl., DB名)

- H02H 3/08 - 3/253

H02J 1/00 - 1/16

G01R 31/50 - 31/74