(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第5442951号

(P5442951)

(45) 発行日 平成26年3月19日(2014.3.19)

(24) 登録日 平成25年12月27日(2013.12.27)

(51) Int.Cl.

H01L 21/336 (2006.01)

H01L 29/78 (2006.01)

F 1

H01L 29/78 301V

請求項の数 2 (全 9 頁)

(21) 出願番号 特願2008-44393 (P2008-44393)

(22) 出願日 平成20年2月26日 (2008.2.26)

(65) 公開番号 特開2009-206145 (P2009-206145A)

(43) 公開日 平成21年9月10日 (2009.9.10)

審査請求日 平成22年12月8日 (2010.12.8)

(73) 特許権者 000002325

セイコーインスツル株式会社

千葉県千葉市美浜区中瀬1丁目8番地

(74) 代理人 100154863

弁理士 久原 健太郎

(74) 代理人 100142837

弁理士 内野 則彰

(74) 代理人 100123685

弁理士 木村 信行

(72) 発明者 理崎 智光

千葉県千葉市美浜区中瀬1丁目8番地 セイコーインスツル株式会社内

(72) 発明者 北島 裕一郎

千葉県千葉市美浜区中瀬1丁目8番地 セイコーインスツル株式会社内

最終頁に続く

(54) 【発明の名称】半導体装置の製造方法

## (57) 【特許請求の範囲】

## 【請求項 1】

半導体基板に第1導電型の下部ウェル領域を形成するステップと、

前記下部ウェル領域の一部に第2導電型の下部ソース領域及び下部ドレイン領域を形成するステップと、

前記下部ウェル領域、前記下部ソース領域、前記下部ドレイン領域の基板表面に半導体エピタキシャル層を形成するステップと、

前記半導体エピタキシャル層に上部ウェル領域を形成するステップと、

凹凸部を形成するためのトレンチを前記下部ソース領域及び前記下部ドレイン領域の深さ以上にエッティング形成するステップと、

前記凹凸部全面に絶縁膜を形成した後、当該絶縁膜を介してゲート電極を形成するステップと、

前記形成したゲート電極の両側にイオンを注入して、前記下部ソース領域および前記下部ドレイン領域に接するように上部ソース領域および上部ドレイン領域を形成するステップと、

を有する半導体装置の製造方法。

## 【請求項 2】

半導体基板に第1導電型の下部ウェル領域を形成するステップと、

前記下部ウェル領域の一部に第2導電型の下部低濃度領域を形成するステップと、

前記下部低濃度領域の一部に前記下部低濃度領域より不純物濃度の濃い第2導電型の下

部ソース領域及び下部ドレイン領域を形成するステップと、

前記下部ウェル領域、前記下部ソース領域、前記下部ドレイン領域の基板表面に半導体エピタキシャル層を形成するステップと、

前記半導体エピタキシャル層に上部ウェル領域を形成するステップと、

凹凸部を形成するためのトレンチを前記下部ソース領域及び前記下部ドレイン領域の深さ以上にエッチング形成するステップと、

前記凹凸部全面に絶縁膜を形成した後、当該絶縁膜を介してゲート電極を形成するステップと、

前記ゲート電極の両側にイオンを注入して、前記下部低濃度領域と接するように第2導電型の上部低濃度領域を形成するステップと、

前記ゲート電極のソース側と前記ゲート電極のドレイン側の一部に前記第2導電型の上部低濃度領域より不純物濃度の濃い第2導電型の上部ソース領域及び上部ドレイン領域を前記下部ソース領域および前記下部ドレイン領域に接するように形成するステップと、

を有する半導体装置の製造方法。

#### 【発明の詳細な説明】

##### 【技術分野】

##### 【0001】

本発明は、半導体装置及びその製造方法に関し、より詳細には、トレンチによりゲート幅を広くしたMOSトランジスタに関する。

##### 【背景技術】

##### 【0002】

MOSトランジスタは電子技術において中核を担う電子素子であって、MOSトランジスタの小型化と高駆動能力化は、重要な課題となっている。MOSトランジスタを高駆動能力化する方法の1つとして、ゲート幅を長くしてオン抵抗を低減させる方法があるが、ゲート幅を長くするとMOSトランジスタの占有面積が大きくなるという問題があった。

##### 【0003】

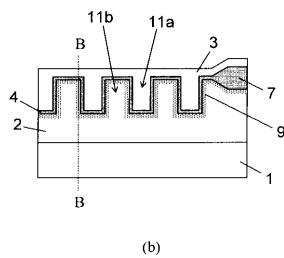

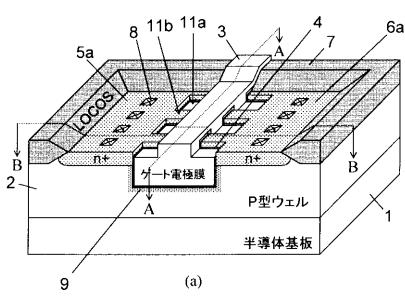

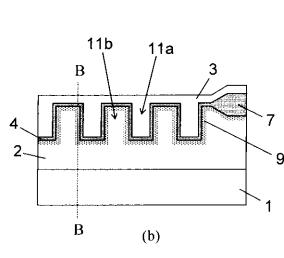

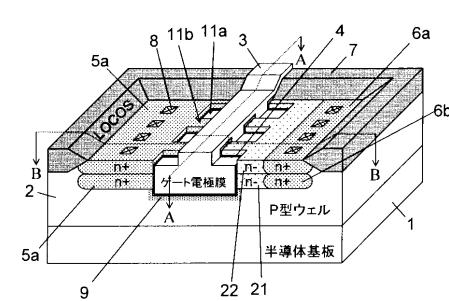

そこで、特許文献1には、横型MOS構造のMOSトランジスタの占有面積の増加を抑えながらゲート幅を長くする技術が提案されている。この技術は、図2(a)の斜視図に示したように、ウェル2に凹部(トレンチ)11aを設け、ゲート絶縁膜4を介して凸部11bと凹部11aの内部にゲート電極3を形成したものである。ウェル2の表面部分において、ゲート電極3の一方の側にはソース領域5が設けられており、他方の側にはドレイン領域6が設けられている。

##### 【0004】

図2(a)のA-A断面図、B-B断面図をそれぞれ図2(b)、図2(c)に示す。A-A断面図に示したように、凹部11a内にゲート電極3が形成されているため、絶縁膜4に接する輪郭の長さがゲート幅となる。このように、この技術では、ゲート部を凹部11aと凸部11bを有するトレンチ構造にすることによって、表面でのゲート電極3の長さに対して、実効的なゲート幅の長さを長くすることができ、これによって、MOSトランジスタの耐圧を低下させずに単位面積あたりのオン抵抗を低減することができる。

この技術は、図2(a)の斜視図に示したように、ウェル2にトレンチを形成し凹部11aと凸部11bを設け、絶縁膜4を介して凸部11bの上面と凹部11aの内部にゲート電極3を形成したものである。ウェル2の表面部分において、ゲート電極3の一方の側にはソース領域5aが設けられており、他方の側にはドレイン領域6aが設けられている。

##### 【0005】

図2(b)は、図2(a)のA-A断面図であるが、ゲート電極3に電圧を印加することにより凹部11aと凸部11bに沿ってチャネル領域9が形成され、一般的なトレンチを形成しないMOSに比べ凹部側面の長さだけゲート幅を長くすることができ、MOSトランジスタの耐圧を低下させずに単位面積あたりのオン抵抗を低減することができる。

#### 【特許文献1】特開2006-294645号公報

#### 【発明の開示】

10

20

30

40

50

**【発明が解決しようとする課題】**

**【0006】**

しかし、図2(a)の構造では、ゲート長Lが短くなるに従い、想定した駆動能力が得られないという問題があった。

**【0007】**

図2(c)は、図2(a)のB-B断面図である。図2(b)を見ると分かりやすいが、図2(c)は、チャネル領域9が形成されるトレンチ側壁のギリギリの部分を切り取った断面図である。図2(c)に示したソース・ドレイン間に生じたチャネル領域9内に電流が電流経路10を介して流れるが、チャネル領域9の上部の電流経路10のほうが下部の電流経路10より短く、この差はゲート長Lが短いほど顕著になる。つまり、ゲート長Lが短くなるほど、チャネル領域9の上部の電流経路10に集中的に電流が流れ、下部の電流経路10には殆ど電流が流れない現象が生じ、チャネル領域9を有効に利用することが出来ず、想定した駆動能力が得られない問題が生じる。そしてこの原因はソース領域5aおよびドレイン領域6aがトレンチ深さに比べ浅いからと考えられる。ソース領域5aおよびドレイン領域6aをトレンチ深さと同等まで深くすることが可能となればゲート長Lを短くしたとしても上記のような電流集中は生じず、チャネル全体に一様な電流が流れる。しかしながら、通常のインプラを利用してソース・ドレイン領域に関しては、深く形成したとしても、一般的に0.5μmより深くすることは難しい。

10

**【0008】**

インプラ後の熱拡散により深くまで拡散させることは可能であるが、拡散することによってソース・ドレインが低濃度化してしまうので、寄生抵抗が増加して駆動能力が悪くなってしまう。また、拡散により深さ方向だけでなく、横方向にも広がるため、実効L長が短くなり、狙いの実効L長を作成するためにはレイアウトのL長を横方向の広がり分だけ大きくしなくてはならず、結果的に素子サイズが大きくなり単位面積あたりの駆動能力は悪くなってしまう。

20

**【0009】**

もう一つの方法として、強引にインプラエネルギーを大きくして深くする方法があるが、この方法でも上記同様、不純物が横方向に広がってしまうため、単位面積あたりの駆動能力は悪くなってしまう。さらに、インプラエネルギーが高くするとゲート電極を突き抜けてチャネルにまでインプラされるリスクも生じる。

30

**【0010】**

そこで、本発明の目的は、トレンチ構造を有する半導体装置の単位面積あたりの駆動能力を向上させることである。

**【課題を解決するための手段】**

**【0011】**

(1) 本発明は、前記目的を達成するために、半導体基板と、前記半導体基板に形成され、ゲート幅方向に凹凸部が形成された第1導電型のウェル領域と、絶縁膜を介して前記凹凸部に形成されたゲート電極と、前記ゲート電極の凹凸長手方向の一方側に前記ウェル領域の上部近傍に掛けて形成された第2導電型の上部ソース領域と、前記上部ソース領域の下側に前記ウェル領域より浅く形成された第2導電型の下部ソース領域と、前記ゲート電極の凹凸長手方向の他方の側に前記ウェル領域の上部近傍に掛けて形成された第2導電型の上部ドレイン領域と、前記上部ドレイン領域の下側に前記ウェル領域より浅く形成された第2導電型の下部ドレイン領域を具備したことを特徴とする半導体装置とする。

40

(2) 前記ドレイン領域のうち、前記ゲート電極に隣接する領域では、不純物濃度が低く設定されていることを特徴とする半導体装置とする。

(3) 半導体基板に第1導電型の下部ウェル領域を形成するステップと、前記下部ウェル領域の一部に第2導電型の下部ソース領域及び下部ドレイン領域を形成するステップと、前記下部ウェル領域、前記下部ソース領域、前記下部ドレイン領域の基板表面に半導体エピタキシャル層を形成するステップと、前記半導体エピタキシャル層に上部ウェル領域を形成するステップと、凹凸部を形成するためのトレンチエッティングステップと、前記凹凸

50

部方面に絶縁膜を形成した後、当該絶縁膜を介してゲート電極を作成するステップと、前記形成したゲート電極の両側にイオンを注入して、前記下部ソース領域および前記下部ドレイン領域に接するように上部ソース領域および上部ドレイン領域を形成するステップを有する半導体装置の製造方法とする。

(4) 半導体基板に第1導電型の下部ウェル領域を形成するステップと、前記下部ウェル領域の一部に第2導電型の下部低濃度領域を形成するステップと、前記下部低濃度領域の一部に前記下部低濃度領域より不純物濃度の濃い第2導電型の下部ソース領域及び下部ドレイン領域を形成するステップと、前記下部ウェル領域、前記下部ソース領域、前記下部ドレイン領域の基板表面に半導体エピタキシャル層を形成するステップと、前記半導体エピタキシャル層に上部ウェル領域を形成するステップと、凹凸部を形成するためのトレンチエッティングステップと、前記凹凸部方面に絶縁膜を形成した後、当該絶縁膜を介してゲート電極を形成するステップと、前記ゲート電極の両側にイオンを注入して、第2導電型の上部低濃度領域を形成するステップと、前期ゲート電極のソース側と前記ゲート電極の一部のドレイン側に前記第2導電型の上部低濃度領域より不純物濃度の濃い第2導電型の上部ソース領域及び上部ドレイン領域を形成するステップを有する半導体装置の製造方法とする。10

#### 【発明の効果】

#### 【0012】

本発明によれば、ソース領域、ドレイン領域を従来技術より深く形成することにより、半導体装置の駆動能力を向上させることができる。20

#### 【発明を実施するための最良の形態】

#### 【0013】

##### (1) 実施の形態の概要

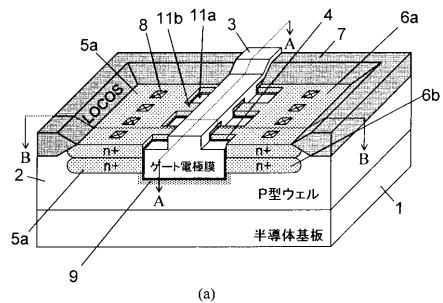

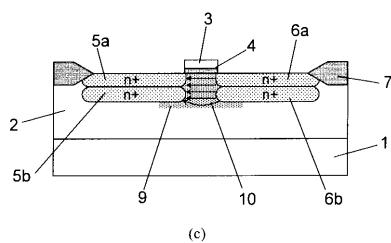

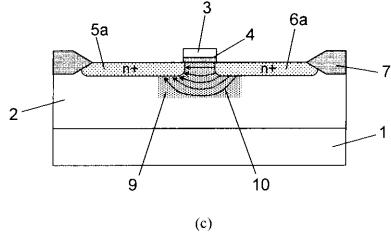

図1に、本発明の実施形態の半導体装置構成を示す。図1(a)が斜視図、図1(b)が図1(a)のA-A断面図、図11(c)が図1(a)のB-B断面図である。

#### 【0014】

ウェル領域2には、ゲート幅方向にウェル領域2に凹凸構造(11a、11b)が形成されており、絶縁膜4を介して、凹部11aの内部及び凸部11bの上面部にゲート電極3が形成されている。ゲート電極3のゲート長方向の一方の側には上部ソース領域5aと下部ソース領域5bが形成されており、他方の側には上部ドレイン領域6a、下部ドレイン領域6bが形成されている。このように、ソース領域、ドレイン領域に下部ソース領域5b、下部ドレイン領域6bを形成することにより、ゲート長Lが短くなるにつれて生じる図1(c)のチャネル領域9の上方の電流集中を抑えチャネル領域9全体に均一に電流を流すことができるようになり、駆動能力が高まる。30

##### (2) 実施の形態の詳細

図1は、本発明の実施形態の半導体装置の構成を説明するための図である。

#### 【0015】

本発明は、横型MOS構造のMOSトランジスタであり、半導体基板1にウェル領域2が形成され、更にウェル領域2に、ゲート電極3、上部ソース領域5a、下部ソース領域5b、上部ドレイン領域6a、下部ドレイン領域6bが形成されている。そして、これらの要素は、LOCOS(Local Oxidation of Silicon)7によって、半導体基板1の他の領域から電気的に分離されている。ウェル領域2は、第1導電型で形成され、上部ソース領域5a、下部ソース領域5b、上部ドレイン領域6a、下部ドレイン領域6bは、第2導電型で形成されている。第1導電型をP型半導体とする場合、第2導電型はN型半導体となり、第1導電型をN型半導体とする場合、第2導電型はP型半導体となる。40

#### 【0016】

図1では、第1導電型をP型、第2導電型をN型とし、ウェル領域2をP型半導体で形成し、ソース領域3とドレイン領域4をN型半導体で形成している。そして、図では、P型、N型の区別を明確化するため、P型のウェル領域を「P型ウェル領域」などと記している。また、図1において、第1導電型をN型、第2導電型をP型とし、ウェル領域2を50

N型半導体で形成し、上部ソース領域5a、下部ソース領域5b、上部ドレイン領域6a、下部ドレイン領域6bをP型半導体で形成する場合にも同様な説明が可能である。

#### 【0017】

ウェル領域2には、トレンチ、即ち、凹部11aがゲート幅方向に複数配列して形成されている。凹部11aの内面及び凸部11bの上面側、即ち、ゲート電極3がウェル領域2に対面する面には、例えばSiO<sub>2</sub>などによる絶縁膜4が形成されている。そして、凹部11aの内面及び凸部11bの上面には絶縁膜4を介してポリシリコンなどによるゲート電極3が形成されている。これら、凹部11a、凸部11b、絶縁膜4、ゲート電極3の構造は、図2(a)～(c)に示した従来例と同様である。

#### 【0018】

ゲート電極3のゲート長方向の側面領域には、一方にはN型半導体で構成された上部ソース領域5aおよび下部ソース領域5bが形成され、他方にはN型半導体で構成された上部ドレイン領域6aおよび下部ドレイン領域6bが形成されている。下部ソース領域5b、下部ドレイン領域6bを設けることにより、上部ソース領域5a、上部ドレイン領域6aのみの構成よりソース・ドレイン領域の深さが深くなる。そして、上部ソース領域5aおよび上部ドレイン領域6aにはコントラクト8が複数形成され、外部の回路との接合ができるようになっている。図中の「n+」の表記は、N型の濃度が高濃度(即ち、不純物が高濃度)であることを表す。低濃度である場合は「n-」と表記する。

#### 【0019】

このように、ソース領域、ドレイン領域に下部ソース領域5b、下部ドレイン領域6bを形成することにより、ゲート長Lが短くなるにつれて生じる図1(c)のチャネル領域9の上方の電流集中を抑えチャネル領域9全体に均一に電流を流すことができるようになり、駆動能力が高まる。これによって、本発明の半導体装置占有面積の増加を抑制しつつ駆動能力を向上させることができる。

#### 【0020】

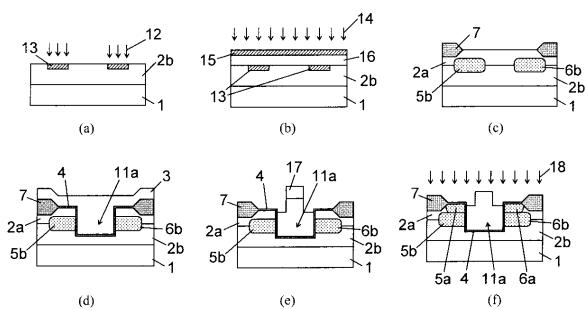

次に、図1の半導体装置の製造方法について説明する。

#### 【0021】

図1の半導体装置を製造するには、まず、図3(a)に示すように半導体基板1に第1導電型下部ウェル領域2bを形成した後、レジスト等でマスクを施し任意の部分に下部ソース・ドレイン用不純物インプラ12をし、下部ウェル領域2bに第2導電型の不純物領域13を形成する。次に、図3(b)に示すように基板表面に半導体エピタキシャル層16を成長させ、エピタキシャル層16表面に上部ウェル用不純物インプラ14をし、第1導電型の不純物領域15を形成する。

#### 【0022】

次に、図3(c)に示すようにLOCOS7を形成し、下部ソース・ドレイン用不純物領域13と上部ウェル用不純物領域15の不純物を拡散させ、下部ソース領域5b、下部ドレイン領域6b、上部ウェル領域2aを形成する。このとき、下部ソース領域5bと下部ドレイン領域6bが上部ウェル領域2aによって消されないように、下部ソース・ドレイン用不純物インプラのドーズ量を上部ウェル用不純物インプラ14のドーズ量より極めて大きくしておく。また、上部ウェル領域2aの濃度が下部ウェル領域2bの濃度と同程度になるように上部ウェル用不純物インプラ14のドーズ量を調整しておく。さらに、上部ウェル領域2aが下部ウェル領域2bと接触するようにエピタキシャル層の厚さも調整しておく。

#### 【0023】

次に、図3(d)に示すようにトレンチ11aを形成した後、ゲート絶縁膜4を形成し、ゲート絶縁膜の上にゲート電極3を形成する。このときトレンチ11a内部がゲート電極3で埋まるようにゲート電極3を形成する。次に、図3(e)に示すようにレジストで選択的にマスクを施し、ゲート電極3をエッチングする。最後に、図3(f)に示すように上部ソース・ドレイン用不純物インプラ18を施し、セルファーラインによって第2導電型の上部ソース領域5aおよび上部ドレイン領域6aを形成する。

10

20

30

40

50

**【0024】**

このとき、上部ソース領域5a、上部ドレイン領域6aがそれぞれ下部ソース領域5b、下部ドレイン領域6bに接触するように、エピタキシャル層の厚さ、上部ソース・ドレイン用不純物インプラ18のドーズ量やエネルギーを調整する。

**【0025】**

以上に説明した本実施の形態により次のような効果を得ることができる。

**【0026】**

(1) ゲート電極3を凹部11a及び凸部11bに形成して凹凸構造と接触させることにより、凹凸構造のチャネル9が形成され実効的なゲート幅を広げることができる。

**【0027】**

(2) ソース領域、ドレイン領域に下部ソース領域5b、下部ドレイン領域6bを形成することにより、ゲート長Lが短くなるにつれて生じる図1(c)のチャネル領域9の上方の電流集中を抑えチャネル領域9全体に均一に電流を流すことができ、チャネルを有効的に利用することができるようになる。

10

**【0028】**

(3) 実効的なゲート幅が広がるため、オン抵抗が低下し、半導体装置1の駆動能力を高めることができる。

**【0029】**

(4) 1チップで高駆動能力を有するCMOS(Complementary Metal Oxide Semiconductor)構造を形成できる。

20

**【0030】**

なお、図1において第1導電型をP型、第2導電型をN型とすることでNチャネルMOSとしたが、第1導電型をN型、第2導電型をP型とすればPチャネルMOSとして機能する。(変形例1)

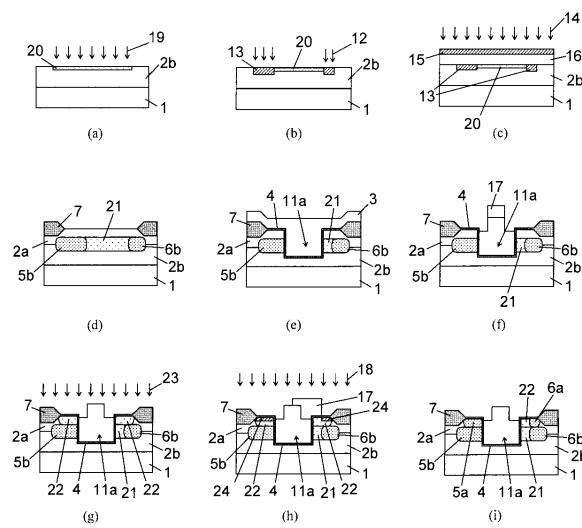

本変形例では、ドレイン領域に電界緩和領域を設けることにより半導体装置の耐圧を向上させる。

**【0031】**

図4は、本変形例に係る半導体装置の構造を説明するための図である。

**【0032】**

先に説明した図1の半導体装置のドレイン領域6a、6bのうち、ゲート電極3に対面する側の領域にN型の濃度が低いn-領域である上部低濃度ドレイン領域21、下部低濃度ドレイン領域22が設けてある。N型の濃度が高いn+ドレイン領域6a、6bは、図1のドレイン領域6a、6bと同程度の濃度であって、コンタクト8が形成されている。一方、ソース側の構成は、図1と同じである。このように、ゲート電極3とn+ドレイン領域6a、6bの間に、N型濃度が低い領域を形成すると、この領域で電界が緩和され、図4に示す半導体装置の耐圧が向上する。

30

**【0033】**

次に、図4の半導体装置の製造方法について説明する。図5が図4の半導体装置の製造方法であるが、基本的な製造方法は図1の半導体装置の製造方法である図3と同じである。図3と図5の違いは、図5(b)に下部低濃度ドレイン用インプラ、図5(g)に上部低濃度ドレイン用インプラが追加され、図5(h)に示すように上部低濃度ドレイン領域22が上部ドレイン領域6aで無くならない様にレジストマスクをしている点である。こうすることで、低濃度ドレイン領域が形成され図4の半導体装置の耐圧が向上する。

40

**【図面の簡単な説明】****【0034】**

【図1】本発明の実施形態の半導体装置の構成を説明するための図である。

【図2】従来の半導体装置を説明するための図である。

【図3】図1の半導体装置の製造法を説明するための図である。

【図4】変形例1に係る半導体装置の構造を説明するための図である。

【図5】図4の半導体装置の製造法を説明するための図である。

50

## 【符号の説明】

## 【0035】

- |                       |    |

|-----------------------|----|

| 1 半導体基板               |    |

| 2 ウエル領域               |    |

| 2 a 上部ウェル領域           | 10 |

| 2 b 下部ウェル領域           |    |

| 3 ゲート電極               |    |

| 4 ゲート絶縁膜              |    |

| 5 ソース領域               |    |

| 5 a 上部ソース領域           |    |

| 5 b 下部ソース領域           |    |

| 6 ドレイン領域              |    |

| 6 a 上部ドレイン領域          |    |

| 6 b 下部ドレイン領域          |    |

| 7 L O C O S           |    |

| 8 コンタクト               |    |

| 9 チャネル領域              |    |

| 10 電流経路               |    |

| 11 a 凹部(トレンチ)         | 20 |

| 11 b 凸部               |    |

| 12 下部ソース・ドレイン用不純物インプラ |    |

| 13 下部ソース・ドレインの不純物     |    |

| 14 上部ウェル用不純物インプラ      |    |

| 15 上部ウェルの不純物          |    |

| 16 半導体エピタキシャル層        |    |

| 17 レジスト               |    |

| 18 上部ソース・ドレイン用不純物インプラ |    |

| 19 下部低濃度領域用不純物インプラ    |    |

| 20 下部低濃度領域用不純物        | 30 |

| 21 下部低濃度領域            |    |

| 22 上部低濃度領域            |    |

【図1】

(a)

(b)

(c)

【図2】

(a)

(b)

(c)

【図3】

【図5】

【図4】

---

フロントページの続き

審査官 儀同 孝信

(56)参考文献 特開2006-019518(JP,A)

特表2007-520873(JP,A)

特開平11-103058(JP,A)

特開平09-008291(JP,A)

特開平03-209760(JP,A)

特開平11-168211(JP,A)

特開平05-168211(JP,A)

特開2003-303962(JP,A)

(58)調査した分野(Int.Cl., DB名)

H01L 21/336

H01L 29/78