(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第4629876号

(P4629876)

(45) 発行日 平成23年2月9日(2011.2.9)

(24) 登録日 平成22年11月19日(2010.11.19)

(51) Int.Cl.

G09C 1/00 (2006.01)

G06F 7/58 (2006.01)

F 1

G09C 1/00

G06F 7/58650B

A

請求項の数 3 (全 18 頁)

(21) 出願番号 特願2000-608542 (P2000-608542)

(86) (22) 出願日 平成12年3月16日 (2000.3.16)

(65) 公表番号 特表2002-540482 (P2002-540482A)

(43) 公表日 平成14年11月26日 (2002.11.26)

(86) 國際出願番号 PCT/US2000/006916

(87) 國際公開番号 WO2000/059153

(87) 國際公開日 平成12年10月5日 (2000.10.5)

審査請求日 平成19年2月15日 (2007.2.15)

(31) 優先権主張番号 09/283,096

(32) 優先日 平成11年3月31日 (1999.3.31)

(33) 優先権主張国 米国(US)

(73) 特許権者 591003943

インテル・コーポレーション

アメリカ合衆国 95052 カリフォルニア州・サンタクララ・ミッション・カレッジ ブーレバード・2200

(74) 代理人 100064621

弁理士 山川 政樹

(72) 発明者 ウエルズ・スティーブン・イー

アメリカ合衆国・95762・カリフォルニア州・エル・ドラド・ヒルズ・ウェザーベイン コート・4236

(72) 発明者 ワード、デイビッド・エイ

アメリカ合衆国・95826・カリフォルニア州・サクラメント・ハニーサックルウェイ・2808

最終頁に続く

(54) 【発明の名称】乱数発生器用デューティ・サイクル修正器

## (57) 【特許請求の範囲】

## 【請求項 1】

ランダム・ビット・ソースのランダム・ビット・ストリーム出力から修正されたビット・ストリームを生成する方法であつて、

前記ランダム・ビット・ストリーム内のペアとなるビットを比較回路で互いに比較するステップと、

前記ペアとなるビットが等しい場合には確認論理回路で前記ペアとなるビットを破棄するステップと、

前記ペアとなるビットが異なる場合には前記確認論理回路で前記ペアとなるビットを受け入れるステップと、

前記異なるビットの順序に基づいて前記確認論理回路で異なるビットの前記ペアのそれぞれ一方を、即ち、前記ペア内の最初のビットまたは2番目のビットの一方を破棄するステップと、

前記ペアとなるビットが異なる時は出力回路で前記ペアとなるビットの破棄されないビットを、即ち、前記ペア内の最初のビットまたは2番目のビットの他方を出力するステップと、

ビット間の自己相関を低減するためにモジュロ X カウンタにより決定された X ビットごとに破棄するステップとを含む方法。

## 【請求項 2】

ランダム・ビット・ソースのランダム・ビット・ストリーム出力から修正されたビット・

10

20

ストリームを生成するためのデューティ・サイクル修正回路であって、

前記ランダム・ビット・ストリームのペアとなるビットの第1のビットを受信及び記憶する第1のストレージ回路と、

前記ペアとなるビットの第2のビットを受信及び記憶する、前記第1のストレージ回路に直列に結合された第2のストレージ回路と、

前記ペアとなるビットを比較して前記ペアとなるビットが異なるかどうかを決定する前記第1のストレージ回路と前記第2のストレージ回路に結合された比較回路と、

前記第1と第2のストレージ回路と前記比較回路に結合された確認論理回路であって、前記ビットが同じ場合には前記ペアとなるビットを破棄し、前記ビットが異なる場合には前記ビットの順序に基づいて前記ペアとなるビットのそれぞれ一方を、即ち、前記ペア内の最初のビットまたは2番目のビットの一方を選択する確認論理回路と、

ビット間の自己相関を低減するためにモジュロXカウンタにより決定された前記ランダム・ビット・ストリームからXビットごとに破棄する、前記確認論理回路に結合されたタイミング回路とを備えるデューティ・サイクル修正回路。

### 【請求項3】

ネットワーク・メディアによりメッセージを送信及び受信を行うべく動作し得るネットワーク・インターフェース・デバイスと、

前記ネットワーク・メディアにより転送されたメッセージの符号化及び復号化を行うべく動作し得る暗号化／解読回路であって、ランダム・ビット・ストリームを生成するよう 20 動作し得る乱数発生器を有する暗号化／解読回路とを備えるコンピュータであって、前記乱数発生器が、

(a) 前記ランダム・ビット・ストリームのペアとなるビットの第1のビットを受信及び記憶する第1のストレージ回路と、

(b) 前記ペアとなるビットの第2のビットを受信及び記憶する、前記第1のストレージ回路に直列に結合された第2のストレージ回路と、

(c) 前記ペアとなるビットを比較して前記ペアとなるビットが異なるかどうかを決定する前記第1のストレージ回路と前記第2のストレージ回路に結合された比較回路と、

(d) 前記第1と第2のストレージ回路と前記比較回路に結合された確認論理回路であって、前記ビットが同じ場合には前記ペアとなるビットを破棄し、前記ビットが異なる場合には前記ビットの順序に基づいて前記ペアとなるビットのそれぞれ一方を、即ち、前記ペア内の最初のビットまたは2番目のビットの一方を選択する確認論理回路と、

(e) ビット間の自己相関を低減するためにモジュロXカウンタにより決定された前記ランダム・ビット・ストリームからXビットごとに破棄する、前記確認論理回路に結合されたタイミング回路とを備えることを特徴とするコンピュータ。

### 【発明の詳細な説明】

#### 【0001】

##### (技術分野)

本発明は、全体的にコンピュータ・セキュリティに関し、より詳細に述べれば、乱数発生器におけるほぼ一様なデューティ・サイクルの発生に関する。

#### 【0002】

##### (発明の背景)

乱数発生回路は、各種の電子応用において使用されている。乱数発生器に関する重要な応用の1つに、メッセージ・データの暗号化と解読が行なわれるコンピュータ・セキュリティの分野におけるものがある。暗号システムは、データを、符号化したメッセージに変える変換を含み、それが送信されたとき、意図された受取人だけがそれを復号することができる。もっとも一般的な暗号テクニックにおいては、暗号（キー）が使用され、送り側はそれを用いてメッセージを符号化し、受け側はそれを用いて当該符号化されたメッセージを復号する。広く知られた暗号システムには、メッセージの符号化および復号化に单一のキーを使用する方法と、メッセージの符号化とその復号化にそれぞれ別のキーを使用する方法がある。

10

20

30

40

50

**【0003】**

メッセージの符号化および復号化に使用されるキーは、基本的にバイナリ・データ・パターンであり、それに照らしてメッセージの処理、すなわちフィルタリングが行なわれる。効果的な暗号システムは、充分に大きなビット数を有し、再生がほとんど不可能なキーの使用を必要とする。さらに、キーを構成するデータ・パターンは、そのキーによって符号化が行なわれたメッセージ内において、それらのパターンないしはパターン群を予測不能にできる充分なランダム性を有していなければならない。したがって効果的な暗号システムには、メッセージ内のバイナリ・データが完全に予測不能な態様で変換されることを保証するように、質の高い乱数発生器を使用する必要がある。一般に、暗号スキームにおけるランダム性の欠如は、符号化済みデータと未符号化データの間に、ある種の相関をもたらす。その後、この相関を使用し、符号化済みメッセージに基づいて試行錯誤を繰り返し、可能性のある出力パターンの予測といったテクニックを通じて、コードの盗み出しが可能になる。

10

**【0004】**

バイナリ乱数に望ましい特徴は、純粹にランダムな順序において「0」と「1」のビットが出力されることである。すなわち、あらゆる時点において出力ビットの値が完全に予測不能となることである。乱数発生器の出力のデューティ・サイクルは、無限の標本サイズにわたって約50パーセントとなり、出力が論理ロー（「0」）になる確率と、出力が論理ハイ（「1」）になる確率が等しくなることが望ましい。また、乱数発生器によって示される任意ビットと他のビットの間の相関が低く（たとえば、約ゼロの相関）、出力ビットの間のフーリエ分布が平坦になることが望ましい。

20

**【0005】**

しかしながら、現在知られている乱数発生器は、統計的に有意な標本サイズにわたって「0」の数と「1」の数が等しくならない傾向にある。従来技術の乱数発生器が一様でないデューティ・サイクルとなる共通の理由としては、禁止されたセットアップ／ホールドタイムの間にデータがラッチされたとき、一般に、乱数発生器を構成するラッチが2つの状態のうちの一方に偏ることが挙げられる。乱数発生器におけるデューティ・サイクルの変動を抑える現在の一般的な方法は、ランダム・ビット・ソースの出力段におけるリニア・フィードバック・シフト・レジスタ（LFSR）の使用が関連する。

30

**【0006】**

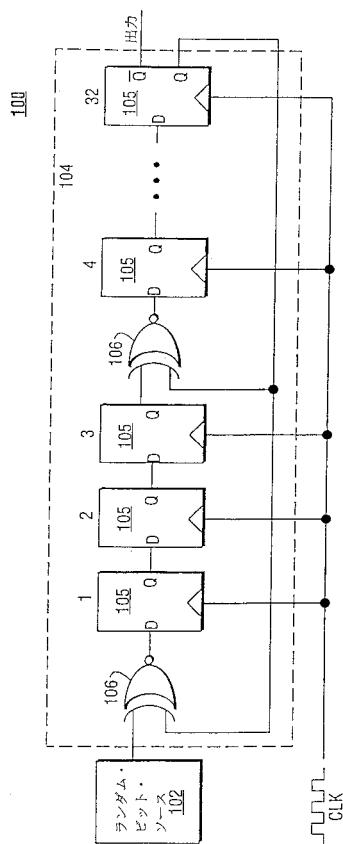

図1は、従来技術における乱数発生器の一例を示しており、ランダム・ビット・ソース102の出力と結合されるリニア・フィードバック・シフト・レジスタ104を使用する。LFSR 104は、多数のラッチ105とゲート106を含み、それを通じてランダム・ビット・ソース102からの出力ビットが伝播される。出力ビットの状態は、ゲート106によってランダムに反転され、ビットの順序がさらに、ラッチ105を通るビットのフィードバックを介して搅乱される。

**【0007】**

概して、図1に示したようなリニア・フィードバック・シフト・レジスタは、特定の不利益を有し、しかも典型的なランダム・ビット・ソースによってもたらされる一様でないデューティ・サイクル特性の完全な修正が得られない。LFSR 104によって示されるように、通常、LFSR自体が複数のラッチとゲートを包含している。これらのラッチとゲートは、ランダム・ビット・ソース102内のラッチの場合と同じく、特定の状況下において「0」または「1」のラッチへ偏る傾向にある。つまり、通常のLFSR自体が「1」と「0」の一様なデューティ・サイクルを生成せず、そのためランダム・ビット・ソースにおけるデューティ・サイクルの変動を完全には修正し得ない。

40

**【0008】**

それ以外にもリニア・フィードバック・シフト・レジスタは、多数のラッチとゲートを必要とするという不利益がある。たとえば、図1に示したような32ビットのLFSRであれば、32個のDタイプのラッチが必要になるだけでなく、多数の組み合わせゲートが必要になる。このことは、この種のLFSRを使用する乱数発生器のために必要となるシリ

50

コン面積を格段に増加させることになる。

**【0009】**

(発明の要約)

ここでは、ランダム・ビット・ソースによって出力されたランダム・ビット・ストリームから、修正後のビット・ストリームを生成する方法および装置を開示する。それにおいては、ランダム・ビット・ストリーム内のビットの連続するペアが比較される。ビットのペアを構成する2つのビットがまったく等しい場合には、出力されたビットが破棄される。ビットのペアを構成する2つのビットが互いに異なる場合には、そのビットのペアの一方のビットを出力ビットとして採用する。

**【0010】**

10

このほかの本発明の特徴ならびに利点は、添付の図面および以下の詳細な説明から逐次明らかなるものとなろう。

**【0011】**

なお、添付図面には、限定の意味ではなく、例示のための手段として本発明が示されており、それらにおいては、類似の要素に類似の参照番号が用いられている。

**【0012】**

(詳細な説明)

乱数発生器内で使用するデューティ・サイクル修正器を説明する。一実施形態においては、このデューティ・サイクル修正器によって、ランダム・ビット・ソースから出力されたビットの連続するペアが処理される。ビットのペアを構成する2つのビットがまったく等しい場合には、デューティ・サイクル修正器によってそのビットのペアが破棄されるか、あるいは出力されない。ビットのペアを構成する2つのビットが互いに異なる場合には、デューティ・サイクル修正器によってビット・ペア内のビットの一方が出力される。

20

**【0013】**

本発明の実施形態の利点として意図されていることは、ランダム・ビット・ソースの出力に関してほぼ一様なデューティ・サイクルを生成する回路を提供することである。さらに、集積回路デバイス内に実装された場合に、必要とするシリコン面積が小さい乱数発生器を提供することも本発明の実施形態の利点として意図されている。

**【0014】**

30

ここで、ランダム・ビット・ソースは、ランダムと推定される順序でバイナリ・ディジット系列を出力するデジタル回路であることを思い出されたい。理想的なランダム・ビット・ソースにおいては、所定の出力ビットが「0」となる確率が、それが「1」となる確率に等しい。つまり、ランダム・ビット・ソースの出力波形のデューティ・サイクルは、統計的に有意な標本サイズにわたって一様に50パーセントとなる。しかしながら、ほとんどのランダム・ビット・ソースは、禁止されたホールドタイムまたはセットアップタイムの間にデータがラッチされると、ランダム・ビット・ソース内のラッチならびにゲートが特定の論理・レベルをラッチするという傾向に起因したデューティ・サイクルの変動を呈する。

**【0015】**

ランダム・ビット・ソースによって特定時に所定のビットが出力される確率は、一定の数学的関係によって表すことができる。たとえば、出力が「0」になる確率( $P(0)$ )を $p$ とすれば、出力が「1」になる確率( $P(1)$ )は $1 - p$ で表される。すなわち、

「0」を生成する確率： $P(0) = p$

「1」を生成する確率： $P(1) = 1 - p$

40

である。理想的なランダム・ビット・ソースにおいては、 $p$ が50パーセントになる。逆に、理想的でないランダム・ビット・ソースの場合は、 $p$ が50パーセントより実質的に大きくなるか、あるいはそれより小さくなる。

**【0016】**

ランダム・ビット・ソースの連続する出力をペアとして考えると、この確率は次のようになる。

50

「0」「0」を生成する確率： $P(00) = P(0)P(0) = p^2$

「0」「1」を生成する確率： $P(01) = P(0)P(1) = p(1-p)$

「1」「0」を生成する確率： $P(10) = P(1)P(0) = (1-p)p$

「1」「1」を生成する確率： $P(11) = P(1)P(1) = (1-p)^2$

### 【0017】

数学的に、「0」「1」の出力ペアと「1」「0」の出力ペアが生成される確率は、上記の確率の式からもわかるように、互いに等しい。つまり、 $p(1-p) = (1-p)p$  であり、したがって  $P(01) = P(10)$  である。

### 【0018】

この性質は、ランダム・ビット・ソースが「1」を生成する確率、または「0」を生成する確率とは無関係に、与えられた任意の出力に関して真となる。したがって、特定のランダム・ビット・ソースについて、 $p$  が 50 パーセントとならない場合であっても、そのランダム・ビット・ソースが「0 - 1」の出力ペアを生成する確率は、それが「1 - 0」の出力ペアを生成する確率に等しい。本発明の一実施形態においては、この原理を用いて、一様でないデューティ・サイクルを呈し、かつ所定の出力ビット・ストリーム内の「0」と「1」の分布が一様でないランダム・ビット・ソースの出力を訂正する。

### 【0019】

本発明の 1 つの方法においては、デューティ・サイクル修正器がランダム・ビット・ソースから出力されたペアとなるビットを処理して、修正した、実質的にデューティ・サイクルが一様なビット・ストリームを決定する。一実施形態においては、ビットのペアを構成するビットがともに等しいときには、デューティ・サイクル修正器によってそのペアが破棄され、修正後のビット・ストリームの一部として出力されない。つまり、出力ビットのペアを構成するビットがともに「0」であれば、そのペアが破棄される。それと同様に、出力ビットのペアを構成するビットがともに「1」であれば、そのペアが破棄される。しかしながら、出力ビットのペアを構成するビットが互いに異なれば、デューティ・サイクル修正器により、そのペアの一方のビットが修正後のビット・ストリームの 1 つのビットとして出力される。一実施形態においては、デューティ・サイクル修正器が異なるビットからなるペア内の最初のビットを修正後のビットとして出力する。したがって、この実施形態においては、出力ペアが「0 - 1」であれば修正後のビットが「0」にセットされ；出力ペアが「1 - 0」であれば修正後のビットが「1」にセットされる。各種のペアの場合に対応する修正後のビット値は、次の関係を用いて表すことができる。

|                              |             |

|------------------------------|-------------|

| $P(00) = P(0)P(0) = p^2$     | 破棄される       |

| $P(01) = P(0)P(1) = p(1-p)$  | 論理「0」が出力される |

| $P(10) = P(1)P(0) = (1-p)p$  | 論理「1」が出力される |

| $P(11) = P(1)P(1) = (1-p)^2$ | 破棄される       |

### 【0020】

変形実施形態においては、デューティ・サイクル修正器が異なるビットからなるペア内の 2 番目のビットを修正後のビットとして出力する。つまり、この実施形態においては、出力ペアが「0 - 1」であれば修正後のビットが「1」にセットされ；出力ペアが「1 - 0」であれば修正後のビットが「0」にセットされる。したがって、この変形実施形態における各種のペアの場合に対応する修正後のビット値は、次の関係を用いて表すことができる。

|                              |             |

|------------------------------|-------------|

| $P(00) = P(0)P(0) = p^2$     | 破棄される       |

| $P(01) = P(0)P(1) = p(1-p)$  | 論理「1」が出力される |

| $P(10) = P(1)P(0) = (1-p)p$  | 論理「0」が出力される |

| $P(11) = P(1)P(1) = (1-p)^2$ | 破棄される       |

### 【0021】

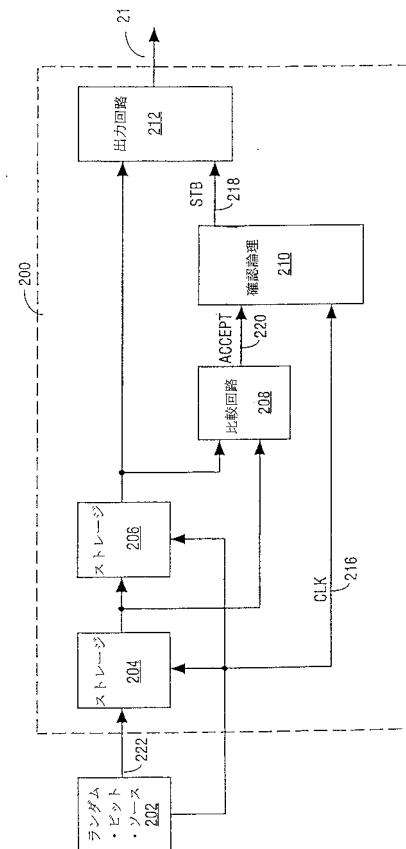

図 2 は、上記の実施形態を具体化したデューティ・サイクル修正器 200 の一実施形態を示しており、それにおいては、ランダム・ビット・ソース 202 の出力から実質的に一様なビット・ストリームが生成され、しかも従来の LFSR 回路より使用されているゲート

10

20

30

40

50

数が少ない。ランダム・ビット・ソース 202 は、信号ライン 222 上にランダムなビットのストリームを出力するものであれば、任意のランダム・ビット・ソースとすることができる。本発明の一実施形態においては、ランダム・ビット・ソース 202 が、高速発振信号を周期的にラッチするランダムに変化させた低速クロック信号を使用するラッチ回路として実装される。ランダム・ビット・ソースのラッチから出力されるビットの値は、低速信号によってラッチされたときの高速信号の電圧レベルに依存する。またランダム・ビット・ソース 202 は、この分野において一般に知られているように、クロック信号またはストローブ信号 CLK を生成して信号ライン 216 上に供給する。

#### 【0022】

デューティ・サイクル修正器 200 は、ストレージ・エレメント 204 と 206、比較回路 208、確認論理 210、および出力回路 212 を含んでいる。ストレージ回路 204 と 206 は、ランダム・ビット・ソース 202 から出力されたランダム・ビット・ストリーム内の連続するビットをペアとして、比較回路 208 による比較のためにストアする。CLK の第 1 のクロック・サイクルにおいて、ペアとなるビットの最初のビットがストレージ回路 204 にストアされる。この最初のビットは、続くクロック・サイクルにおいてストレージ回路 206 にストアされ、ストレージ回路 204 には、そのときランダム・ビット・ソース 202 から出力された次のビットがストアされる。ストレージ回路 204 と 206 は、ラッチ、レジスタ、揮発性もしくは不揮発性メモリ・セル、およびその他の等価物を含めた任意のタイプのストレージ・エレメントとすることができます。

#### 【0023】

ストレージ回路 204 と 206 にストアされたビットは、比較回路 208 によって比較される。この比較回路 208 は、エクスクルーシブ・オア・ゲートもしくはコンパレータといった任意のタイプの比較回路とすることができます。2つのビットが等しいときには、比較回路 208 が、信号ライン 220 上の信号を論理ハイの状態にセットして ACCEPT (アクセプト) をアサートする。2つのビットが等しくないときには、比較回路 208 が、その信号を論理ローの状態にセットして ACCEPT (アクセプト) のアサートを解く。つまり、ACCEPT (アクセプト) 信号は、ランダム・ビット・ソースから出力されるペアとなるビットが、デューティ・サイクル修正器 200 によって出力されるビット・ストリーム内の修正後のビットとなり得るか否かを示すことになる。

#### 【0024】

ACCEPT (アクセプト) 信号は、CLK とともに確認論理 210 に渡される。比較回路 208 は、ストレージ回路 204 と 206 内の連続する 2 つのビットが互いに異なるとき、ACCEPT (アクセプト) をアサートする。しかしながら、デューティ・サイクル修正器 200 が一様なデューティ・サイクルの出力ストリームを生成するためには、ランダム・ビット・ソース 202 から出力されるビットをオーバーラップさせることなく比較する方が好ましい。その機能を具体化している部分が確認論理 210 である。確認論理 210 は、ACCEPT (アクセプト) がアサートされ、かつ望ましいビットのペアがストレージ回路 204 と 206 にストアされているとき、信号ライン 218 上の信号を論理ハイの状態にセットしてストローブ信号 STB をアサートする。STB がアサートされると、出力回路 212 がストレージ回路 206 内のビットをストアする。出力回路 212 は、レジスタ、ラッチ、1 ないしは複数の揮発性もしくは不揮発性メモリ・エレメント、アンド・ゲート、あるいはその他の論理を含めて任意のストレージ・エレメントとすることができます。出力回路 212 によってストアされたビットは、ストレージ回路 204 と 206 内にストアされたビットに対応する修正後のビットとして信号ライン 214 に出力される。

#### 【0025】

変形実施形態に関しては、ストレージ回路 206 の出力を代えてストレージ回路 204 の出力を出力回路 212 に渡すことができる。その実施形態の場合、STB がアサートされると出力回路 212 がストレージ回路 204 内のビットをストアし、このビットをストレージ回路 204 と 206 内にストアされたビットに対応する修正後のビットとして出力す

10

20

30

40

50

る。

#### 【0026】

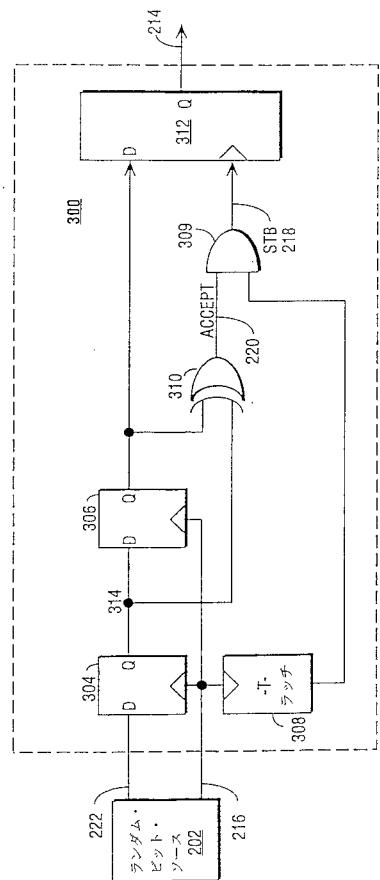

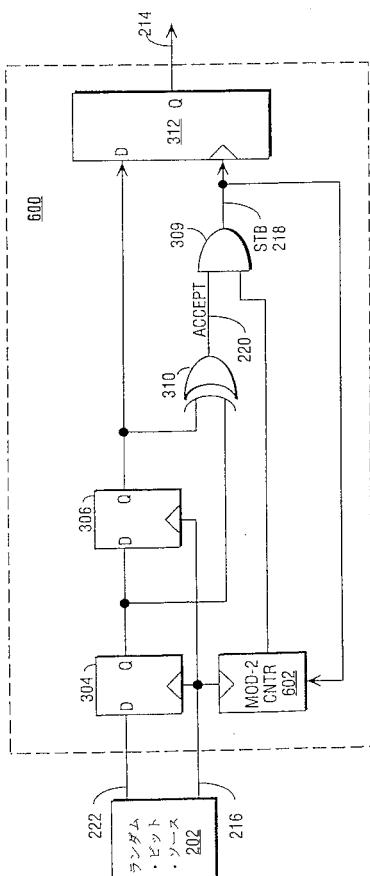

図3は、デューティ・サイクル修正器200の一実施形態であるデューティ・サイクル修正器300を示している。デューティ・サイクル修正器300は、ストレージ回路204と206のそれぞれ一実施形態であるラッチ304および306；比較回路210の一実施形態であるエクスクルーシブ-オア・ゲート310；確認論理210の一実施形態であるトランスペアレント・ラッチ308およびアンド・ゲート309の組み合わせ；および出力回路212の一実施形態であるラッチ312を含んでいる。

#### 【0027】

ラッチ304および306は、ランダム・ビット・ソース202から出力された連続するビットをペアとして、エクスクルーシブ-オア・ゲート310による比較のためにストアする。ペアとなるビットの最初のビットが、CLKによってラッチ304内にラッチされる。CLKの次のクロック・パルスでは、この最初のビットがラッチ306にラッチされ、ランダム・ビット・ソース202から出力された次のビットがラッチ304内にラッチされる。ビットのペアを構成する2つのビットが等しければ、エクスクルーシブ-オア・ゲート310がACCEPT(アクセプト)のアサートを行わずに「0」を出力し；ビットのペアを構成する2つのビットが互いに異なれば、エクスクルーシブ-オア・ゲート310が「1」を出力してACCEPT(アクセプト)をアサートする。

#### 【0028】

トランスペアレント・ラッチ308は、ランダム・ビット・ソース302からのCLKをラッチし、ACCEPT(アクセプト)がアサートされ、かつラッチ304および306にオーバーラップのないビットのペアがストアされているときにSTBがアサートされるようにアンド・ゲート309をクロックする。STBがアサートされると、ラッチ312がラッチ306から出力されたビットを、信号ライン214上に出力する修正後のビットとしてラッチする。別の実施形態においては、ラッチ304の出力をラッチ312に供給することができる。このビットを、ラッチ312によりSTBに応答してラッチすればよい。

#### 【0029】

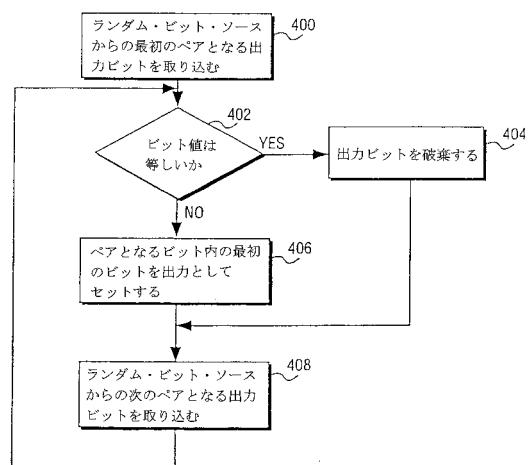

図4は、デューティ・サイクル修正器300の動作を示したフローチャートである。ステップ400において、ラッチ304および306がランダム・ビット・ソース202から最初のペアとなるビットをラッチするが、そのうちの最初のビットはラッチ306にストアされ、2番目のビットはラッチ304にストアされる。ステップ402においては、エクスクルーシブ-オア・ゲート310が、ペアを構成する2つのビットが等しいか否かを決定する。ペアを構成する2つのビットが等しいときには、ステップ204において、ACCEPT(アクセプト)のアサートおよびSTBのアサートが行なわれることなく、このビットのペアが拒絶または破棄される。ステップ204においては、いずれのビットもラッチ312によってラッチされることなく、また信号ライン214に出力されることもない。しかしながら、ステップ402において2つのビットが互いに異なると判断されると、ステップ406においてペア内の最初のビットが出力として獲得される。

#### 【0030】

ステップ408においては、続くオーバーラップするペアとなるビットがランダム・ビット・ソース202から取り込まれ、その後プロセスがステップ402から繰り返される。このプロセスは、ランダム・ビット・ソースからの出力ビットのペアがすべて処理されるまで繰り返される。ペアを構成しない乱数源からの出力ビットは、処理不可能であり、したがって破棄される。ここでは、ペアを構成する最初のビットがラッチ306から修正後のビットとして供給されているが、別の方においては、修正後のビットとして、ペアを構成する2番目のビットをラッチ304から供給できることに注意する必要がある。

#### 【0031】

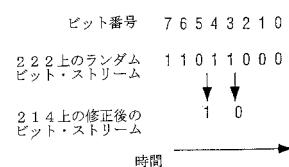

図5は、デューティ・サイクル修正器300の動作をさらに別の形で説明している。図5を参照すると、2番目のペアとなるビット(ビット2および3)および3番目のペアとな

10

20

30

40

50

るビット(ビット4および5)は修正後のビットを生成するが、最初のペアとなるビット(ビット0および1)および4番目のペアとなるビット(ビット6および7)からは生成されないことがわかる。

#### 【0032】

ランダム・ビット・ソース202は、ラッチ、論理ゲート、およびその他の回路エレメントの特性に起因して、連続的に生成されたビットの間に1次の自己相関を有するビットを出力することがある。つまり、図2および3に示したような上記のデューティ・サイクル修正器が実質的に一様なデューティ・サイクルを有するランダム・ビット・パターンを実質的に出力できる場合であっても、ランダム・ビット・ソースによって出力されるビット間の自己相関が低くないとデューティ・サイクル修正器の出力が一様なデューティ・サイクルに近づく可能性が高くならない。言い換えれば、ランダム・ビット・ストリーム内のビットが互いに相関を有していない場合においては、デューティ・サイクル修正器の出力が一様なデューティ・サイクルに近づく可能性が高くなる。10

#### 【0033】

図5に示されるように、図3に示したデューティ・サイクル修正器300は、ビットの連続するペアに対してデューティ・サイクル修正器300が作用することから、ランダム・ビット・ソース202によって出力されたランダム・ビット・ストリーム内のビット間における1次の自己相関による影響を受けることがあり得る。図6は、別の実施形態、すなわちランダム・ビット・ソース202によって出力されるビットのペアの間における1次の自己相関の影響を軽減するデューティ・サイクル修正器600を示している。このデューティ・サイクル修正器600は、修正後のビットを生成したビットのペアが検出されるごとに、ランダム・ビット・ソース202から出力されるビットを1つ破棄することによって1次の自己相関の影響を軽減する。20

#### 【0034】

デューティ・サイクル修正器600は、デューティ・サイクル修正器300に類似であるが、確認論理のトランスペアレント・ラッチ308がモジュロ2カウンタ602に置き換えられている点が異なる。デューティ・サイクル修正器600の動作を図7に示す。ステップ700においては、モジュロ2カウンタ602のカウント「0」と「1」に応答して、ラッチ304および306がランダム・ビット・ソース202からの最初のペアとなるビットをラッチする。ステップ702においては、エクスクルーシブ・オア・ゲート310が、ペアを構成する2つのビットが等しいか否かを決定する。ペアを構成する2つのビットが等しいときには、ステップ704において、ACCEPT(アクセプト)のアサートおよびSTBのアサートが行なわれることなく、このビットのペアが拒絶または破棄される。ステップ704においては、いずれのビットもラッチ312によってラッチされることなく、また信号ライン214に出力されることもない。しかし、ステップ702において2つのビットが互いに異なると判断されると、ステップ704において、カウント「1」に応答してACCEPT(アクセプト)がアサートされ、STBがアサートされて、ラッチ312により最初のビット(または、それに代えて2番目のビット)が出力される。このSTBは、モジュロ2カウンタ602にもフィードバックされ、その結果、STBがアサートされるとモジュロ2カウンタ602が1カウントをスキップし、次の2クロック・サイクルをローに(つまり両方をカウント「0」に)保持する。これによりステップ807において、デューティ・サイクル修正器600は、ランダム・ビット・ソース202からのランダム・ビット・ストリーム内の次のビットを破棄する。この「次のビット」はラッチ304内にロードされているが、モジュロ2カウンタ602が次にアンド・ゲート309に対してカウント「1」を出力する前に、クロックされてラッチ306を通り抜けることからこれが可能になる。ステップ708においては、続くオーバーラップするペアとなるビットがランダム・ビット・ソース202から取り込まれ、その後プロセスがステップ702から繰り返される。このプロセスは、ランダム・ビット・ソースからの出力ビットのペアがすべて処理されるまで繰り返される。30

#### 【0035】

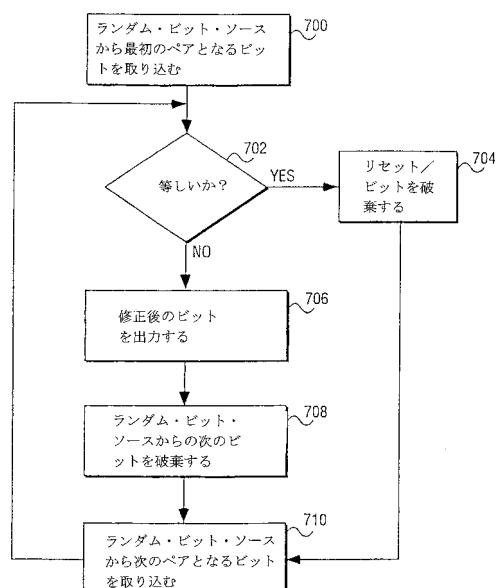

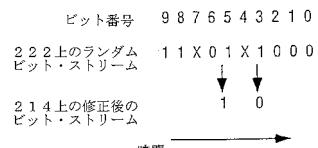

デューティ・サイクル修正器 600 の動作を別の形で図 8 に示す。最初のペアとなるビット（ビット 0 および 1）の処理時においては、ペア内のビットが等しいことから破棄され、このビットのペアに関しては修正後のビットが生成されない。それに加えて、STB のアサートがないことからモジュロ 2 カウンタ 602 によるカウントのスキップも行なわれない。2 番目のペアとなるビット（ビット 2 および 3）はビット値が異なることから、デューティ・サイクル修正器 600 が「0」を出力し、続いてモジュロ 2 カウンタ 602 がカウントをスキップすることから、その次のビット、つまりビット 4 が破棄される。3 番目のペアとなるビット（ビット 5 および 6）もビット値が等しくない。その結果、デューティ・サイクル修正器 600 が「1」を出力し、モジュロ 2 カウンタ 602 がカウントをスキップすることから、その次のビット、つまりビット 7 が破棄される。最後のペアとなるビット（ビット 8 および 9）は、ビット値が等しいことから破棄される。10

#### 【0036】

ビット 4 および 7 を破棄することによって 2 番目のビットのペア（ビット 2 および 3）と 3 番目のビットのペア（ビット 5 および 6）の間の 1 次の自己相関、および 3 番目のビットのペアと 4 番目のビットのペア（ビット 8 および 9）の間の 1 次の自己相関が低減される。修正後のビット・ストリームは、ランダム・ビット・ソース 202 によって出力された 2 番目のビットのペアと 3 番目のビットのペアの間、および 3 番目のビットのペアと 4 番目のビットのペアの間における 2 次の自己相関の影響を受けるが、その有意性はあまり高くない。

#### 【0037】

デューティ・サイクル修正器 600 は、ランダム・ビット・ソースによって生成されたビットの間における 1 次の自己相関を低減する。しかしながら、それぞれの破棄されるビット（たとえば図 8 のビット 4 および 7）がランダム・ビット・ストリーム内に一様に分布していないことから、修正後のビット・ストリームのデューティ・サイクルに非一様性が招かれる傾向を否定できない。20

#### 【0038】

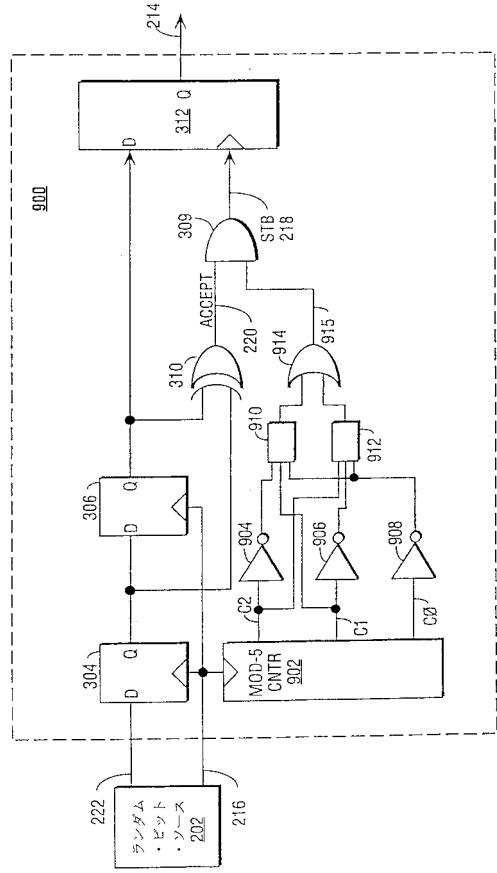

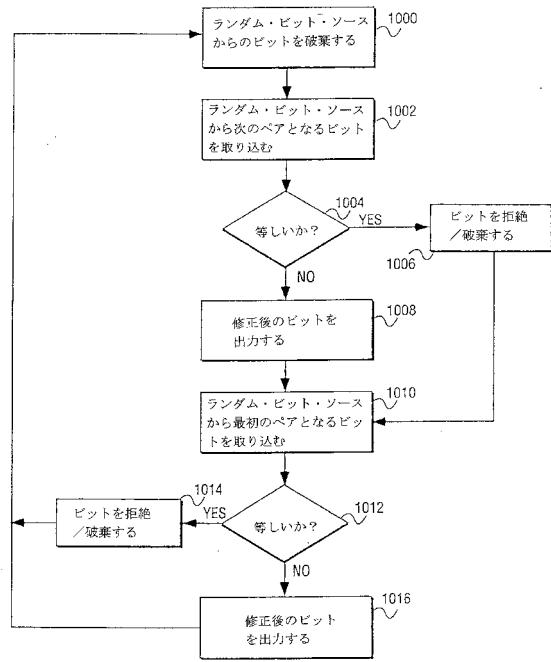

図 9 は、さらに別の実施形態、すなわちランダム・ビット・ソース 202 によって出力されるビットのペアの間における 1 次の自己相関の影響を軽減するデューティ・サイクル修正器 900 を示している。デューティ・サイクル修正器 900 は、ランダム・ビット・ソース 202 の、モジュロ 5 カウンタの特定のカウントに応じてシフト・インされたビットを破棄することによって、1 次の自己相関を低減する。30

#### 【0039】

デューティ・サイクル修正器 900 は、デューティ・サイクル修正器 300 に類似であるが、確認論理のトランスペアレント・ラッチ 308 が、モジュロ 5 カウンタ 902、インバータ 904、906、908、アンド・ゲート 910、912、およびノア・ゲート 914 に置き換えられている点が異なる。モジュロ 5 カウンタ 902 は、3 つのバイナリ出力ビット C0、C1、C2 を有している。アンド・ゲート 910 は、3 入力アンド・ゲートであり、第 1 の入力がインバータ 904 を介して C2 に結合され、第 2 の入力が C1 に結合され、第 3 の入力がインバータ 908 を介して C0 に結合されている。アンド・ゲート 912 は、3 入力アンド・ゲートであり、第 1 の入力が C2 に結合され、第 2 の入力がインバータ 906 を介して C1 に結合され、第 3 の入力がインバータ 908 を介して C0 に結合されている。ノア・ゲート 914 は、アンド・ゲート 910 および 912 の出力を受け取り、アンド・ゲート 309 の一方の入力をドライブする。40

#### 【0040】

デューティ・サイクル修正器 900 の動作を図 10 に示す。ステップ 1000 およびモジュロ 5 カウンタ 902 のカウント「0」において、最初のビットがラッチ 304 にロードされる。カウント「0」と「1」については、信号ライン 915 上に信号がアサートされないことから、このビットは破棄される。ステップ 1002 においては、カウント「1」と「2」に応答して、最初のペアとなるビットがランダム・ビット・ソース 202 からラッチ 304 および 306 にラッチされる。このラッチが、修正器 1000 に最初のビット

10

20

30

40

50

を破棄させる。ステップ1004およびカウント「2」においては、エクスクルーシブ・オア・ゲート310が、ペアを構成する2つのビットが等しいか否かを判断する。ペアとなるビットが等しいときには、ステップ1006において、ACCEPT(アクセプト)のアサートおよびSTBのアサートが行なわれることなく、このビットのペアが拒絶または破棄される。ステップ1006においては、いずれのビットもラッチ312によってラッチされることなく、また信号ライン214に出力されることもない。ステップ1004およびカウント「2」において、2つのビットが互いに異なると判断されると、ステップ1008においてACCEPT(アクセプト)がアサートされ、STBがアサートされて、ラッチ312によりペア内の最初のビット(または、それに代えて2番目のビット)が出力される。

10

#### 【0041】

ステップ1010においては、カウント「3」および「4」に応答して、2番目のペアとなるビットがランダム・ビット・ソース202からラッチ304および306にラッチされる。ステップ1012およびカウント「4」においては、エクスクルーシブ・オア・ゲート310が、ペアを構成する2つのビットが等しいか否かを判断する。ペアとなるビットが等しいときには、ステップ1014において、ACCEPT(アクセプト)のアサートおよびSTBのアサートが行なわれることなく、このビットのペアが拒絶または破棄される。ステップ1012およびカウント「4」において、2つのビットが互いに異なると判断されると、ステップ1016においてACCEPT(アクセプト)がアサートされ、STBがアサートされて、ラッチ312によりペア内の最初のビット(または、それに代えて2番目のビット)が出力される。このプロセスが、ランダム・ビット・ソースから出力されるすべてのビットのペアに対する処理を完了するまで繰り返される。

20

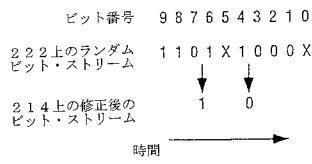

#### 【0042】

図11は、デューティ・サイクル修正器900の動作をさらに別の形で示している。最初のビット、すなわちビット0は、修正器900にロードされるが、最初のペアとなるビットがロードされるときに破棄される。最初のペアとなるビット(ビット1と2)は、ビット値が等しいことから破棄され、このビットのペアに関しては修正後のビットが生成されない。2番目のペアとなるビット(ビット3と4)はビット値が異なることから、デューティ・サイクル修正器900が「0」を出力する。その後、モジュロ5カウンタ902のカウントが「0」に戻り、その結果、ビット5が破棄される。3番目のペアとなるビット(ビット6と7)もビット値が異なり、デューティ・サイクル修正器900は「1」を出力する。最後のペアとなるビット(ビット8および9)はビット値が互いに等しく、したがって破棄される。

30

#### 【0043】

ビット0と5を破棄することによって2番目のビットのペア(ビット3と4)と3番目のビットのペア(ビット6と7)の間の1次の自己相関が低減される。修正後のビット・ストリームは、2番目のビットのペアと3番目のビットのペアの間ににおける2次の自己相関の影響を受けるが、その有意性はあまり高くない。カウント「0」(カウント「5」、カウント「10」等)で破棄されるビットは、ランダム・ビット・ストリーム内に一様に分布し、それらを除外しても、結果的に修正後のビット・ストリームに関するデューティ・サイクルは概略で一様になる。

40

#### 【0044】

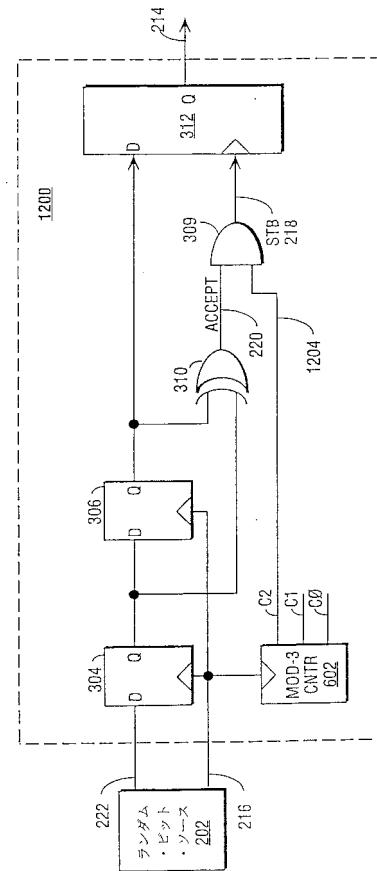

図12は、さらに別の実施形態、すなわちランダム・ビット・ソース202によって出力されるビットのペアの間における1次の自己相関の影響を軽減するデューティ・サイクル修正器1200を示している。デューティ・サイクル修正器1200は、ランダム・ビット・ソース202が出力したビットから、比較されるビットのペアの間に挟まれるビットを破棄することによって1次の自己相関を抑える。

#### 【0045】

デューティ・サイクル修正器1200は、デューティ・サイクル修正器300に類似であるが、確認論理のトランスペアレント・ラッチ308が、カウント「2」のときにのみ信

50

号ライン 1204 上に論理ハイの信号を出力するモジュロ 3 カウンタ 1202 に置き換えられている点が異なる。

#### 【0046】

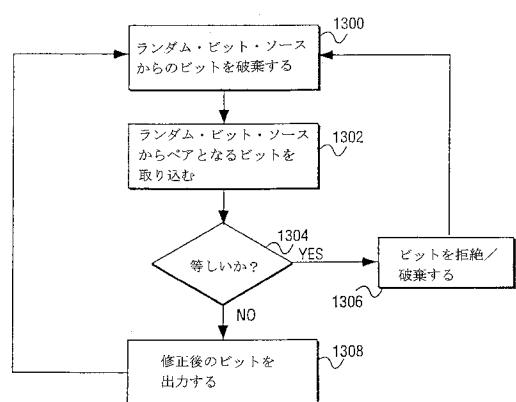

デューティ・サイクル修正器 1200 の動作を図 13 に示す。ステップ 1300 およびモジュロ 3 カウンタ 902 のカウント「0」において、最初のビットがラッチ 304 にロードされる。カウント「0」と「1」については、信号ライン 1204 上に信号がアサートされないことから、このビットは破棄されることになる。ステップ 1302 においては、カウント「1」と「2」に応答して、最初のペアとなるビットがランダム・ビット・ソース 202 からラッチ 304 および 306 にラッチされる。このラッチによって、修正器 1200 が最初のビットを破棄する。ステップ 1304 およびカウント「2」においては、エクスクルーシブ・オア・ゲート 310 が、ペアを構成する 2 つのビットが等しいか否かを判断する。ペアとなるビットが等しいときには、ステップ 1306 において、ACCEPT (アクセプト) のアサートおよび STB のアサートが行なわれることなく、このビットのペアが拒絶または破棄される。ステップ 1306 においては、いずれのビットもラッチ 312 によってラッチされることなく、また信号ライン 214 に出力されることもない。ステップ 1304 およびカウント「2」において、2 つのビットが互いに異なると判断されると、ステップ 1308 において ACCEPT (アクセプト) がアサートされ、STB がアサートされて、ラッチ 312 によりペア内の最初のビット（または、それに代えて 2 番目のビット）が出力される。このプロセスが、ランダム・ビット・ソースからの出力ビットのペアがすべて処理されるまで繰り返される。

10

20

#### 【0047】

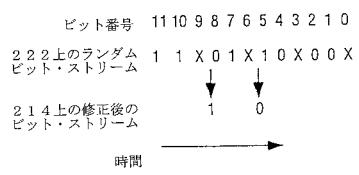

図 14 は、デューティ・サイクル修正器 1200 の動作をさらに別の形で示している。最初のビット、すなわちビット 0 は、修正器 1200 にロードされるが、最初のビットのペアがロードされるとき破棄される。最初のペアとなるビット（ビット 1 と 2）の処理においては、ペア内のビットが等しいことから破棄され、このビットのペアに関しては修正後のビットが生成されない。4 番目のビット、すなわちビット 3 は、修正器 1200 にロードされるが、2 番目のペアとなるビットがロードされるとき破棄される。2 番目のペアとなるビット（ビット 4 と 5）はビット値が異なることから、修正器 1200 が「0」を出力する。7 番目のビット、すなわちビット 6 は、修正器 1200 にロードされるが、3 番目のペアとなるビットがロードされるとき破棄される。3 番目のペアとなるビット（ビット 7 と 8）はビット値が異なり、デューティ・サイクル修正器 1200 は「1」を出力する。10 番目のビット、すなわちビット 9 は、修正器 1200 にロードされるが、4 番目のペアとなるビットがロードされるとき破棄される。4 番目のペアとなるビット（ビット 10 と 11）は、ビット値が等しいことから破棄される。

30

#### 【0048】

ビット 0、3、6、9 等を破棄することによって、比較を行うビットのペアの間における 1 次の自己相関が低減される。修正後のビット・ストリームは、比較を行うビットのペアの間における 2 次の自己相関の影響を受けるが、その有意性はあまり高くない。モジュロ 3 カウンタ 1202 のカウント 0、3、6、9 等において破棄されるビットは、ランダム・ビット・ストリーム内に一様に分布し、それらを除外しても、結果的に修正後のビット・ストリームに関するデューティ・サイクルは概略で一様になる。

40

#### 【0049】

以上、ランダム・ビット・ソースのランダム・ビット・ストリーム内の連続する 2 つのビットを比較するものとしてデューティ・サイクル修正器の説明を行ってきたが、変形実施形態として、連続しないビットを比較することもできる。たとえば、ストレージ回路 204 と 206 の間に追加のストレージ回路を挿入し、あるいはそれぞれのストレージ回路を異なるクロックもしくは異なるクロック・エッジを用いてクロックすることが考えられる。

#### 【0050】

また、ここで説明した出力回路 212 は、ストレージ回路 204 と 206 のうちのいずれ

50

か一方の出力を受け取る。変形実施形態においては、比較論理 208 に、ストレージ回路 204 と 206 にストアされているデータに応答して出力回路 212 に提供されるデータを決定する論理を含めることができる。

#### 【0051】

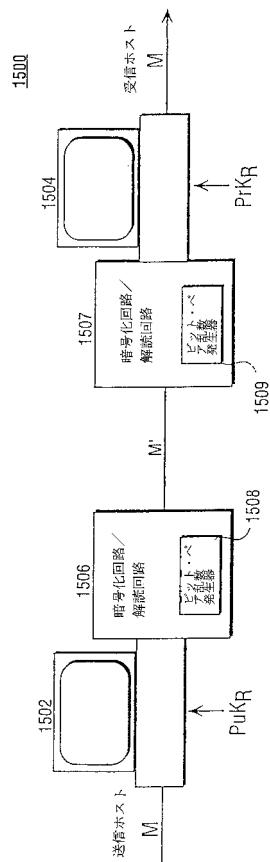

ランダム・ビット・ソースから実質的に一様な「1」と「0」の分布を生成するための、ここで説明したデューティ・サイクル修正器は、コンピュータ・ネットワークを介して送られるメッセージの符号化および復号化を行うための乱数発生器と組み合わせて使用することができる。図 15 は、上記のいずれかの実施形態を使用して暗号化されたメッセージを送信するためのコンピュータ・ネットワークを示したブロック図である。ネットワーク 1500 は、送信ホスト・コンピュータ 1502 およびネットワークを介してそれに結合された受信ホスト・コンピュータ 1504 を含んでいる。送信ホスト・コンピュータおよび受信ホスト・コンピュータは、ともにネットワーク・インターフェース・デバイスを備え、それによってホスト・コンピュータ・システムとネットワーク・メディアの間の物理的かつ論理的な接続が提供される。さらにいずれのホスト・コンピュータにも暗号化回路 / 解読回路が備わり、それが、データ通信のセキュリティに関する各種の暗号機能を実行する。送信ホスト 1502 は、暗号化回路 / 解読回路 1506 を備えており、受信ホスト 1504 は、暗号化回路 / 解読回路 1507 を備えている。暗号化回路 / 解読回路 1506 および 1507 には、それぞれ乱数発生器 1508 および 1509 が備わり、そこには、図 2、3、6、9、または 12 に示した実施形態のいずれかが採用されている。これらの乱数発生器は、公開キー / 秘密キーシステムにおける公開キー / 秘密キーの生成に使用される。

10

#### 【0052】

ネットワーク 1500 においては、送信ホスト 1502 と受信ホスト 1504 の間の安全な通信を保証するために、各種のデータ暗号化方法を使用することができる。一実施形態においては、ネットワーク 1500 が公開キー（非対称）暗号システムを使用する。公開キーシステムにおいては、2つの異なるキーが使用される。一方のキーは、送信側がメッセージの符号化のために使用し、他方のキーは、受信側が符号化されたメッセージの復号化のために使用する。このシステムにおいては、暗号化（公開）キーは広く公開してもよいが、復号（秘密）キーは、意図された受信側だけがメッセージの復号化を行えるよう 30 秘密にする必要がある。公開キーおよび秘密キーは、通常、非常に大きな素数および乱数からともに導かれる。したがって、真にランダムなキーのペアを生成するためには、効果的な乱数発生器が必要になる。

30

#### 【0053】

公開キーシステムを使用するデータ送信の例において、送信ホスト 1502 は、受信ホスト 1504 に送信するためのメッセージ M を作成する。この伝送のために使用される 2 つのキーは、受信側の公開キー（ $P_{u K_R}$ ）および受信側の秘密キー（ $P_{r K_R}$ ）からなる。通常、受信側は、公に入手可能な登録キーから公開キーを選択し、受信側のみが知っている変換プロセスを介して、当該公開キーから秘密キーを導く。つまり、一般に公開キーと秘密キーの間の相関は、秘密であり、かつ安全である。送信ホスト 1502 は、公開キーを使用し、暗号化回路 / 解読回路 1506 を介してメッセージを符号化し、符号化済みのメッセージ  $M'$  を生成する。符号化が行なわれた後は、適切な秘密キーを使用しない限りメッセージを復号化することができない。受信ホスト 1504 は、メッセージを受信すると、秘密キーを用いてメッセージ  $M'$  の復号化を行い、オリジナルのメッセージ M を取り出す。

40

#### 【0054】

一実施形態においては、受信ホスト 1504 内の暗号化回路 / 解読回路 1507 が、図 2、3、6、9、または 12 の実施形態のいずれかを採用した乱数発生器 1509 を備えている。このテクニックは、乱数発生器 1509 からのビットの分布が充分に一様かつランダムであり、そのため公開キーと、受信ホスト 1504 によって生成される秘密キーの間に一貫性のある相関が存在しない。ネットワーク 1500 内に示されるように、送信ホス

50

ト 1 5 0 2 内の暗号化回路 / 解読回路 1 5 0 6 もまた、図 2、3、6、9、または 1 2 の実施形態のいずれかを採用した乱数発生器 1 5 0 8 を備えている。これにより送信ホスト 1 5 0 2 は、公開キーによる送信を採用するときの、安全な秘密キーおよび公開キーの生成が可能になる。これらのキーのペアの生成には、秘密キーの網羅的でないサーチが極めて困難になるように高度のランダム性が要求される。

#### 【 0 0 5 5 】

別の実施形態においては、ネットワーク 1 5 0 0 が单一キー（対称）システムを使用して、暗号機能を実行する。单一キーシステムの場合には、送信側と受信側が 1 つのキーを共有し、それを使用して送信側はメッセージの暗号化を行い、受信側は、符号化されたメッセージの解読をおこなう。このシステムの信頼性は、キーのセキュリティに依存する。10 したがって、第三者に知られることのない、送信側と受信側の間のみにおけるキーの開示のために安全なプロセスが必要になる。この実施形態においては、通常、メッセージ・トランザクションが異なるごとに異なるキーが使用される。つまり、各種のキーが生成されることから、あるメッセージ・トランザクションに使用されるキーが、別のメッセージ・トランザクションに使用されたキーから決定不可能であることが保証される必要がある。このシステムの場合、ネットワーク 1 5 0 0 の各ホスト・コンピュータ内の暗号化回路 / 解読回路において、乱数発生器が使用されてホスト・コンピュータ間で送信されるメッセージ・データの符号化および復号化を行うためのランダムなキーパターンが生成される。

#### 【 0 0 5 6 】

なお、ここでは单一キーおよび公開キー / 秘密キー暗号システムとの関連から本発明の実施形態を説明したが、本発明の実施形態は、安全なコンピュータ・ネットワーキングのための、これ以外のタイプの暗号システムにも使用できることに注意する必要がある。さらに、図 15 に示した暗号化回路 / 解読回路は、安全なデータ送信システムにおけるメッセージの符号化および復号化、送信されたメッセージの認証、デジタル署名の検証、およびその他の機能を含めた各種の暗号機能の実行に使用することができる。20

#### 【 0 0 5 7 】

以上のとおり、一様なデューティ・サイクルの乱数発生器を作るための回路について説明した。ここでは、特定の具体例とする実施形態を参照して本発明についての説明を行ったが、特許請求の範囲に示される本発明の精神ならびに範囲はそれよりも広く、それから逸脱することなくこれらの実施形態に対して各種の修正ないしは変更を加え得ることは明らかである。したがって、明細書ならびに図面は、限定の意味ではなく例示と考える必要がある。30

#### 【 図面の簡単な説明 】

【 図 1 】 リニア・フィードバック・シフト・レジスタを使用する従来の乱数発生器を示した図である。

【 図 2 】 ランダム・ビット・ソースおよびデューティ・サイクル修正器の一実施形態を示したブロック図である。

【 図 3 】 図 2 に示したデューティ・サイクル修正器の一実施形態を示した論理図である。

【 図 4 】 図 2 に示したデューティ・サイクル修正器の動作を示したフローチャートである。40

【 図 5 】 図 3 に示したデューティ・サイクル修正器によって生成される修正後のビット・パターンの一例を示している。

【 図 6 】 図 2 に示したデューティ・サイクル修正器の別の実施形態を示した論理図である。

【 図 7 】 図 6 に示したデューティ・サイクル修正器の動作を示したフローチャートである。

【 図 8 】 図 6 に示したデューティ・サイクル修正器によって生成される修正後のビット・パターンの一例を示している。

【 図 9 】 図 2 に示したデューティ・サイクル修正器の一実施形態を示した論理図である50

。

【図10】 図10に示したデューティ・サイクル修正器の動作を示したフローチャートである。

【図11】 図9に示したデューティ・サイクル修正器によって生成される修正後のビット・パターンの一例を示している。

【図12】 図2に示したデューティ・サイクル修正器の一実施形態を示した論理図である。

【図13】 図12に示したデューティ・サイクル修正器の動作を示したフローチャートである。

【図14】 図12に示したデューティ・サイクル修正器によって生成される修正後のビット・パターンの一例を示している。 10

【図15】 本発明の一実施形態に従ったデータ暗号化／解読のためのビット・ペアリング・システムを使用するコンピュータ・ネットワークを示したブロック図である。

【図1】

【図2】

【図3】

【図4】

〔圖5〕

【 四 6 】

【 図 7 】

[ 8 ]

【図 9】

【図 10】

【図 11】

【図 12】

【図13】

【図15】

【図14】

---

フロントページの続き

審査官 中里 裕正

(56)参考文献 HANDBOOK of APPLIED CRYPTOGRAPHY , CRC PRESS , 1996年10月 , p.171-173

Martin Luescher , A Portable High-Quality Random Number Generator for Lattice Field Theory Simulations , The Internet , 1993年 9月28日 , URL , <http://arxiv.org/abs/hep-lat/93020>

(58)調査した分野(Int.Cl. , DB名)

G09C 1/00

G06F 7/58

JSTPlus/JMEDPlus/JST7580(JDreamII)