(19) 대한민국특허청(KR)

(12) 공개특허공보(A)

(11) 공개번호 10-2019-0099648

(43) 공개일자 2019년08월28일

(51) 국제특허분류(Int. Cl.)

*G06F 11/10* (2006.01) *G06F 12/02* (2018.01)

*G06F 7/58* (2006.01)

(52) CPC특허분류

*G06F 11/1008* (2013.01)

*G06F 12/0292* (2013.01)

(21) 출원번호 10-2018-0019326

(22) 출원일자 2018년02월19일

심사청구일자 없음

(71) 출원인

에스케이하이닉스 주식회사

경기도 이천시 부발읍 경충대로 2091

(72) 발명자

박창현

서울특별시 동작구 상도로30길 40, 두산트래지움

아파트 204-1903

(74) 대리인

특허법인태평양

전체 청구항 수 : 총 20 항

(54) 발명의 명칭 메모리 장치, 반도체 장치 및 반도체 시스템

### (57) 요 약

본 발명의 실시예에 의한 메모리 장치는, 복수의 페이지를 포함하여, 각 페이지는, 데이터가 저장되는 데이터 영역; 상기 데이터 영역에 저장된 데이터의 오류를 검출 및 정정하기 위한 ECC 데이터가 저장되는 ECC 영역; 및 당해 페이지의 라이트 카운트가 저장되는 메타데이터 영역을 포함한다.

대 표 도 - 도2

(52) CPC특허분류

**G06F 7/588** (2013.01)

---

## 명세서

### 청구범위

#### 청구항 1

복수의 페이지를 포함하며,

각 페이지는,

데이터가 저장되는 데이터 영역;

상기 데이터 영역에 저장된 데이터의 오류를 검출 및 정정하기 위한 ECC 데이터가 저장되는 ECC 영역; 및

당해 페이지의 라이트 카운트가 저장되는 메타데이터 영역

을 포함하는 메모리 장치.

#### 청구항 2

제1항에 있어서,

상기 데이터 영역은 복수의 제1 반도체 칩에 형성되고,

상기 ECC 영역 및 상기 메타데이터 영역은 제2 반도체 칩에 형성되고,

상기 복수의 제1 반도체 칩의 각각에 형성된 데이터 영역의 크기와, 상기 제2 반도체 칩에 형성된 상기 ECC 영역 및 상기 메타데이터 영역의 크기의 합은 동일한 메모리 장치.

#### 청구항 3

제2항에 있어서,

상기 제2 반도체 칩에 형성된, 상기 ECC 영역의 크기 및 상기 메타데이터 영역의 크기는 상기 복수의 제1 반도체 칩 각각에 형성된 데이터 영역의 크기의 절반인 메모리 장치.

#### 청구항 4

제2항에 있어서,

상기 제2 반도체 칩의 버스트 랭쓰는 상기 복수의 제1 반도체 칩 각각의 버스트 랭쓰의 절반인 메모리 장치.

#### 청구항 5

라이트 요청이 수신되면, 소정 확률로 어드레스 저장 신호를 생성하는 결정부;

상기 어드레스 저장 신호에 기초하여, 상기 라이트 요청에 대응하는 어드레스를 저장하는 어드레스 저장부; 및

상기 어드레스에 기초하여 메모리 장치에 저장된 페이지 라이트 카운트를 업데이트하는 업데이트부

를 포함하는 반도체 장치.

#### 청구항 6

제5항에 있어서,

상기 결정부는,

상기 소정 확률을 발생시키는 랜덤수 발생기(randomizer)를 포함하는 반도체 장치.

#### 청구항 7

제5항에 있어서,

상기 업데이트부는,

상기 메모리 장치의, 상기 어드레스에 해당하는 페이지에 저장된 페이지 라이트 카운트를 리드하고, 상기 리드된 페이지 라이트 카운트를 업데이트하고, 상기 업데이트된 페이지 라이트 카운트를 상기 어드레스에 라이트하는 반도체 장치.

### 청구항 8

제5항에 있어서,

상기 업데이트부는,

상기 어드레스 저장부에 저장된 하나 이상의 어드레스 중, 저장된 순서와 무관하게 하나의 어드레스를 선택하여 업데이트하는 반도체 장치.

### 청구항 9

제5항에 있어서,

상기 업데이트부는,

상기 메모리 장치에서 동시에 동작 가능한 최대 개수의 맹크가 동작 중일 때, 상기 페이지 라이트 카운트를 업데이트하는 반도체 장치.

### 청구항 10

제5항에 있어서,

상기 업데이트부는,

상기 메모리 장치에서 최대 소비 전력의 제한으로 인해 발생하는 대기 시간 중에 상기 페이지 라이트 카운트를 업데이트하는 반도체 장치.

### 청구항 11

블록 라이트 카운트에 기초하여 올 메타 리드 신호를 생성하는 블록 라이트 카운트 체크부;

상기 올 메타 리드 신호에 기초하여 어드레스에 해당하는 블록이 포함하는 페이지들의 페이지 라이트 카운트들을 획득하는 페이지 라이트 카운트 획득부; 및

상기 페이지 라이트 카운트들에 기초하여 어드레스 맵핑을 변경하는 어드레스 맵핑 변경부;

를 포함하는 웨어레밸링 장치.

### 청구항 12

제11항에 있어서,

상기 블록 라이트 카운트 체크부는,

라이트 요청에 기초하여 블록 라이트 카운트를 획득하는 블록 라이트 카운트 출력부 및

상기 블록 라이트 카운트를 기준치와 비교한 결과에 기초하여 상기 올 메타 리드 신호를 생성하는 비교부

를 포함하는 웨어레밸링 장치.

### 청구항 13

제12항에 있어서,

상기 블록 라이트 카운트 출력부는,

상기 블록 라이트 카운트를 저장하는 블록 라이트 카운트 저장부에 액세스하여 상기 블록 라이트 카운트를 획득

하는 웨어레밸링 장치.

## 청구항 14

제11항에 있어서,

상기 페이지 라이트 카운트 획득부는,

상기 어드레스에 기초하여, 상기 어드레스가 속하는 블록의 페이지들의 어드레스들을 생성하는 웨어레밸링 장치.

## 청구항 15

제11항에 있어서,

상기 어드레스 맵핑 변경부는 상기 페이지 라이트 카운트들의 최대값과 최소값의 차에 기초하여 상기 어드레스 맵핑을 변경하는 웨어레밸링 장치.

## 청구항 16

제11항에 있어서,

상기 블록 라이트 카운트 체크부는, 복수의 블록 라이트 카운트들이 미리 설정된 복수의 구간 중 어디에 속하는지를 나타내는 블록 구간 정보를 생성하는 웨어레밸링 장치.

## 청구항 17

복수의 페이지를 포함하며, 각 페이지에 페이지 라이트 카운트를 저장하는 메모리 장치; 및

입력 어드레스에 해당하는 블록의 블록 라이트 카운트와, 상기 블록이 포함하는 페이지들의 페이지 라이트 카운트들에 기초하여 어드레스 맵핑을 변경하는 반도체 장치;

를 포함하는 반도체 시스템.

## 청구항 18

제17항에 있어서,

상기 반도체 장치는,

복수의 블록의 블록 라이트 카운트들이 미리 설정된 복수의 구간 중 어디에 속하는지를 나타내는 블록 구간 정보 및, 입력 어드레스에 해당하는 블록의 블록 라이트 카운트에 기초하여 올 메타 리드 신호를 생성하는 블록 라이트 카운트 체크부;

상기 올 메타 리드 신호에 기초하여, 상기 입력 어드레스에 해당하는 블록이 포함하는 페이지들의 페이지 라이트 카운트들을 획득하는 페이지 라이트 카운트 획득부; 및

상기 페이지 라이트 카운트들에 기초하여 어드레스 맵핑 변경 신호를 생성하는 어드레스 맵핑 변경부;

를 포함하는 웨어레밸링 장치와,

상기 블록 구간 정보 및 상기 어드레스 맵핑 변경 신호에 기초하여 어드레스 맵핑을 변경하는 어드레스 맵핑 회로

를 포함하는 반도체 시스템.

## 청구항 19

제18항에 있어서,

상기 어드레스 맵핑 회로는, 복수의 어드레스 맵핑 테이블을 포함하고,

상기 블록 구간 정보에 기초하여 복수의 어드레스 맵핑 테이블 중 하나를 선택하고, 선택된 어드레스 맵핑 테이블을 이용하여 입력 어드레스를 변환하는 반도체 시스템.

## 청구항 20

제19항에 있어서,

상기 어드레스 맵핑부는, 상기 어드레스 맵핑 변경 신호로서 XOR 키를 생성하고,

상기 어드레스 맵핑 회로는, 상기 선택된 어드레스 맵핑 테이블을 이용하여 변환된 입력 어드레스에, 상기 XOR 키를 적용하는 반도체 시스템.

### 발명의 설명

#### 기술 분야

[0001]

본 발명은 메모리 장치, 반도체 장치 및 반도체 시스템에 관한 것으로, 보다 상세하게는 메타 데이터를 저장하는 메모리 장치, 메타 데이터를 이용하여 웨어레벨링을 수행하는 반도체 장치 및 반도체 시스템에 관한 것이다.

#### 배경 기술

[0002]

낸드 플래시 메모리 장치 또는 상변이 메모리 장치 등의 반도체 장치는 하나의 셀에 대하여 수행할 수 있는 라이트 동작의 횟수가 한정되어 있다. 따라서 특정 셀 영역에 대해서 라이트 동작이 집중되는 경우 반도체 장치 전체의 수명을 감소시킨다. 이를 방지하기 위하여 반도체 장치의 전체 셀 영역에 대해서 라이트 동작을 균등하게 분포시키기 위한 웨어 레벨링 동작이 수행된다.

[0003]

라이트 요청을 수행하는 단계에서 호스트로부터 제공되는 논리 주소를 물리 주소로 맵핑하고 맵핑된 물리 주소에 쓰기 요청을 수행한다. 웨어 레벨링 동작은 쓰기 요청의 횟수에 기초하여 논리 주소와 물리 주소의 맵핑을 변경함으로써 수행될 수 있다.

[0004]

종래에는 쓰기 요청의 횟수를 포함하는 메타 데이터를 블록 단위로 관리하고, 각 블록의 메타 데이터에 기초하여 웨어 레벨링 동작을 수행하였다. 여기서, 블록은 복수의 페이지를 그룹화한 것이고, 페이지는 반도체 장치에서 라이트 동작의 기본 단위가 되는 메모리 셀의 집합이다.

[0005]

그러나, 블록 단위로 메타 데이터를 관리하는 경우에는 페이지별 메타 데이터를 알기 어렵기 때문에 웨어 레벨링의 성능에 한계가 있다.

### 발명의 내용

#### 해결하려는 과제

[0006]

본 발명은 페이지별 메타 데이터를 저장하는 메모리 장치를 제공한다.

[0007]

본 발명은 페이지별 메타 데이터를 이용하여 웨어 레벨링을 수행하는 반도체 장치 및 반도체 시스템을 제공한다.

#### 과제의 해결 수단

[0008]

본 발명의 실시예에 따른 메모리 장치는, 복수의 페이지를 포함하며, 각 페이지는, 데이터가 저장되는 데이터 영역; 상기 데이터 영역에 저장된 데이터의 오류를 검출 및 정정하기 위한 ECC 데이터가 저장되는 ECC 영역; 및 당해 페이지의 라이트 카운트가 저장되는 메타데이터 영역을 포함한다.

[0009]

본 발명의 실시예에 따른 반도체 장치는, 라이트 요청이 수신되면, 소정 확률로 어드레스 저장 신호를 생성하는 결정부; 상기 어드레스 저장 신호에 기초하여, 상기 라이트 요청에 대응하는 어드레스를 저장하는 어드레스 저장부; 및 상기 어드레스에 기초하여 메모리 장치에 저장된 페이지 라이트 카운트를 업데이트하는 업데이트부를 포함한다.

[0010]

본 발명의 실시예에 따른 반도체 장치는, 블록 라이트 카운트에 기초하여 올 메타 리드 신호를 생성하는 블록 라이트 카운트 체크부; 상기 올 메타 리드 신호에 기초하여 어드레스에 해당하는 블록이 포함하는 페이지들의 페이지 라이트 카운트들을 획득하는 페이지 라이트 카운트 획득부; 및 상기 페이지 라이트 카운트들에 기초하여 어드레스 맵핑을 변경하는 어드레스 맵핑 변경부를 포함한다.

[0011]

본 발명의 실시예에 따른 반도체 시스템은, 복수의 페이지를 포함하며, 각 페이지에 페이지 라이트 카운트를 저

장하는 메모리 장치; 및 입력 어드레스에 해당하는 블록 라이트 카운트와, 상기 블록이 포함하는 페이지들의 폐이지 라이트 카운트들에 기초하여 어드레스 맵핑을 변경하는 반도체 장치를 포함한다.

### 발명의 효과

[0012] 본 발명의 실시예에 의하면, 페이지별 메타 데이터를 저장할 수 있다.

[0013] 본 발명의 실시예에 의하면, 웨어 레벨링의 성능을 향상시켜 반도체 장치의 수명을 증가시킬 수 있다.

### 도면의 간단한 설명

[0014] 도 1은 본 발명의 실시예에 따른 데이터 처리 시스템의 구성도.

도 2는 본 발명의 실시예에 따른 반도체 시스템의 구성도.

도 3은 본 발명의 실시예에 따른 반도체 장치의 구성도.

도 4는 본 발명의 실시예에 따른 반도체 장치의 페이지 라이트 카운트의 업데이트 방법을 설명하기 위한 타이밍도.

도 5는 본 발명의 실시예에 따른 메타데이터 업데이트 방법을 설명하기 위한 타이밍도.

도 6은 본 발명의 실시예에 따른 반도체 장치의 구성도.

도 7은 본 발명의 일 실시예에 따른 어드레스 맵핑 회로에 구비되는 어드레스 맵핑 테이블.

도 8은 본 발명의 실시예에 따른 웨어레벨링 장치의 구성도.

도 9는 본 발명의 실시예에 따른 블록 라이트 카운트 체크부의 구성도.

도 10은 본 발명의 실시예에 따른 반도체 장치의 구성도.

도 11은 본 발명의 실시예에 따른 웨어레벨링 장치의 구성도.

도 12는 본 발명의 실시예에 따른 어드레스 맵핑 회로의 동작을 설명하기 위한 도면.

### 발명을 실시하기 위한 구체적인 내용

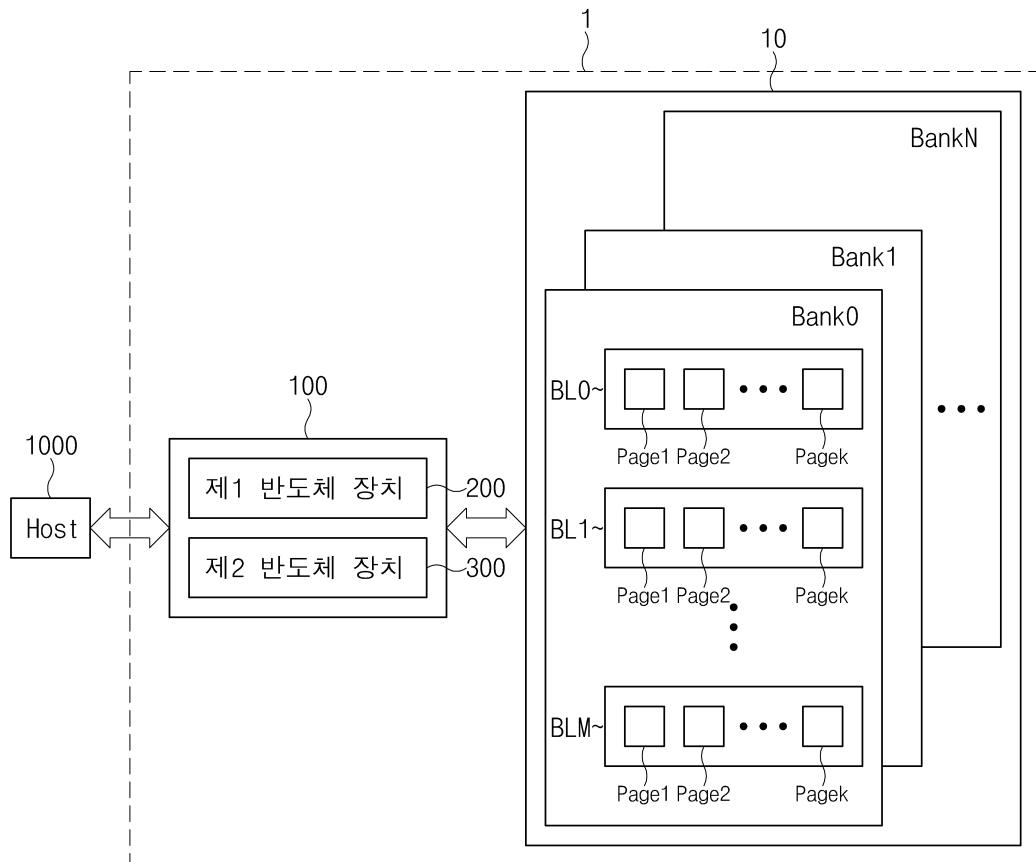

[0015] 도 1은 본 발명의 실시예에 따른 데이터 처리 시스템의 구성도이다.

[0016] 도 1을 참조하면, 데이터 처리 시스템은 호스트(1000) 및 반도체 시스템(1)을 포함한다.

[0017] 호스트(1000)는, 적어도 하나의 운영 시스템(OS: operating system)를 포함한다. 운영 시스템은 사용자의 사용 목적 및 용도에 상응한 기능 및 동작을 지원하며, 호스트(1000)의 기능 및 동작을 전반적으로 관리 및 제어한다. 또한, 운영 시스템은 메모리 장치(10)와 호스트(1000) 간에 상호 동작을 제공한다.

[0018] 반도체 시스템(1)은 데이터를 저장하는 메모리 장치(10)와, 메모리 장치(10)로의 데이터 저장을 제어하는 반도체 장치(100)를 포함한다. 도 1에서는 반도체 장치(100)와 메모리 장치(10)를 별개로 도시하였지만, 하나의 반도체 장치로 집적될 수 있다.

[0019] 반도체 장치(100)는 호스트(1000)로부터의 요청에 응답하여 메모리 장치(10)를 제어한다. 예를 들어, 반도체 장치(100)는, 메모리 장치(10)로부터 리드된 데이터를 호스트(1000)로 제공하고, 호스트(1000)로부터 제공된 데이터를 메모리 장치(10)에 저장한다. 본 실시예에 따른 반도체 장치(100)는 제1 반도체 장치(200)와 제2 반도체 장치(300) 중 적어도 하나를 포함한다.

[0020] 메모리 장치(10)는 리드 커맨드에 대응하여, 내부에 저장된 데이터를 출력하는 리드 동작을 수행하거나, 라이트 커맨드에 대응하여 제공되는 데이터를 내부에 저장하는 라이트 동작을 수행한다. 메모리 장치(10)는 전원이 공급되지 않아도 저장된 데이터를 유지할 수 있으며, 낸드 플래시 메모리나 상변화 메모리와 같은 비휘발성 메모리일 수 있으나, 본 발명의 범위는 이에 한하지 않는다.

[0021] 도 1을 참조하면, 메모리 장치(10)는 복수의 뱅크 Bank0~BankN를 포함한다. 각 뱅크 Bank0~BankN는 복수의 블록 BL0~BLM을 포함한다. 각 블록 BL0~BLM은 복수의 페이지 Page1~PageK를 포함한다. 복수의 뱅크 Bank0~BankN는 리드 동작이나 라이트 동작을 독립적으로 수행할 수 있다. 페이지 Page1~PageK는 복수의 메모리 셀의 집합이며, 라이트 동작의 기본 단위가 될 수 있다. 즉, 1회의 라이트 커맨드에 대해 1개의 페이지에 해당

하는 데이터 영역 또는 메타 데이터 영역에 데이터가 저장될 수 있다. 도 1에는 복수의 뱅크 Bank0~BankN의 각각이 동일한 개수의 블록 BL0~BLM을 포함하고, 블록 BL0~BLM의 각각이 동일한 개수의 페이지 Page1~PageK를 갖는 것으로 도시하였다. 그러나, 본 발명의 범위는 이에 한하지 않다. 각 뱅크에 포함되는 블록의 개수가 상이할 수 있고, 각 블록에 속하는 페이지의 개수가 상이할 수 있다. 또한, 도 1은 뱅크 Bank0~BankN, 블록 BL0~BLM, 페이지 Page1~PageK의 포함관계 또는 연결관계를 나타내기 위한 것이며, 물리적인 배치에 대응하지 않을 수 있다.

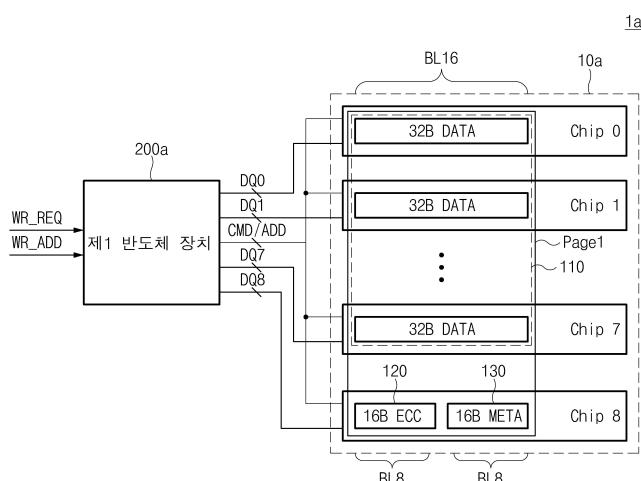

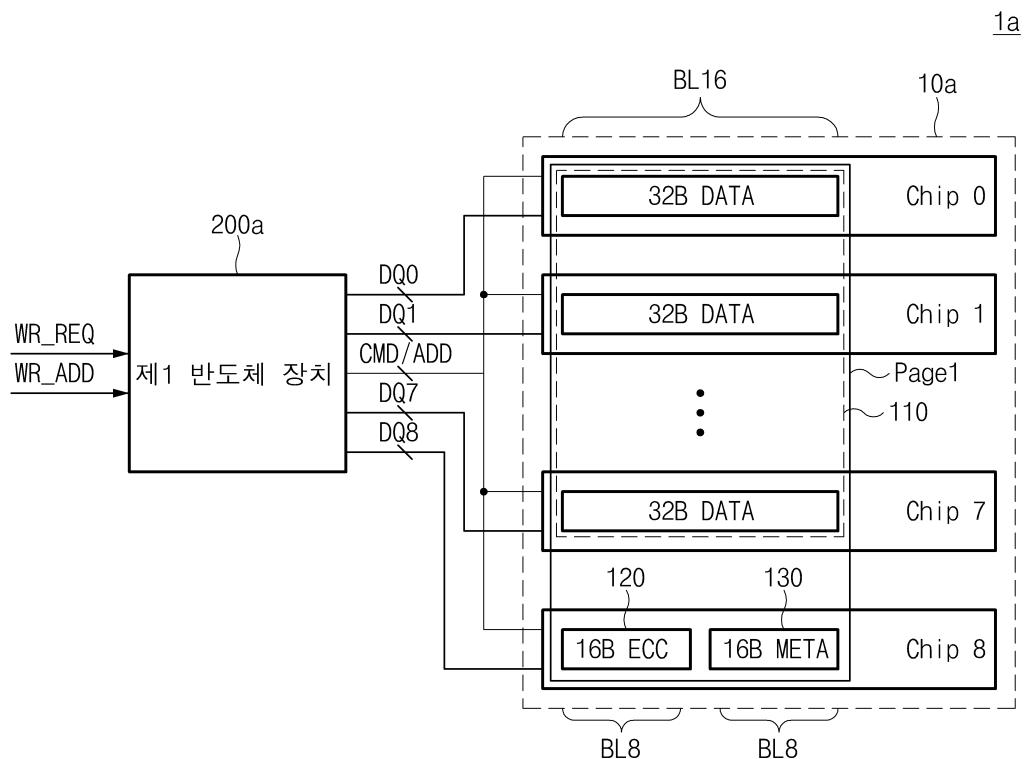

[0022] 도 2는 본 발명의 실시예에 따른 반도체 시스템(1a)의 구성도이다.

[0023] 도 2를 참조하면, 반도체 시스템(1a)은 메모리 장치(10a) 및 반도체 장치(200a)를 포함한다. 도 2의 메모리 장치(10a)는 도 1의 메모리 장치(10)에 대응하고, 반도체 장치(200a)는 도 1의 제1 반도체 장치(200)에 대응할 수 있다. 설명의 편의상 도 2의 메모리 장치(10a)에는 한개의 페이지(Page1)만을 도시하지만, 페이지(Page1)과 동일한 구조를 갖는 복수의 페이지가 포함될 수 있다.

[0024] 도 2를 참조하면, 페이지(Page1)는 데이터 영역(110), ECC 영역(120) 및 메타데이터 영역(130)을 포함한다. 데이터 영역(110), ECC 영역(120), 메타데이터 영역(130)은 저장되는 데이터의 종류를 기준으로 구분한 것이다. 데이터 영역(110)에는 라이트 커맨드에 따른 데이터가 저장되고, ECC 영역(120)에는 데이터 영역(110)에 저장되는 데이터의 에러를 검출 및 정정하기 위한 ECC 데이터가 저장되고, 메타데이터 영역(130)에는 당해 메타데이터 영역(130)이 속하는 페이지를 관리하기 위한 메타데이터가 저장된다. 예를 들어, 메타데이터 영역(130)에는, 당해 메타데이터 영역(130)이 속하는 페이지에 대한 라이트 요청의 횟수를 나타내는 페이지 라이트 카운트가 저장될 수 있다.

[0025] 메모리 장치(10a)는 복수의 반도체 칩(CHIP0~CHIP8)을 포함한다. 도 2에 도시된 바와 같이, 데이터 영역(110)은 제1~제8 반도체 칩(CHIP0~CHIP7)에 형성되고, ECC 영역(120) 및 메타데이터 영역(130)은 제9 반도체 칩(CHIP8)에 형성될 수 있다. 본 실시예에서는 데이터 영역(110)이 8개의 반도체 칩에 형성되는 것으로 설명하였지만, 본 발명의 범위는 이에 한하지 않으며 반도체 칩의 개수는 달라질 수 있다.

[0026] 제1~제8 반도체 칩 CHIP0~CHIP7의 각각은 복수의 입출력 라인 DQ0~DQ7을 가질 수 있으며, 복수의 입출력 라인 DQ0~DQ7의 각각은 복수 예를 들어 16개의 입출력 라인을 가질 수 있다. 또한, 제1~제8 반도체 칩(CHIP0~CHIP7)의 입출력 라인 DQ0~DQ7의 각각은 한번의 리드 커맨드 또는 라이트 커맨드에 대해 16bit의 데이터를 입력 또는 출력할 수 있다. 즉, 제1~제8 반도체 칩(CHIP0~CHIP7)의 각각은 버스트 랭쓰 16(BL16)의 방식으로 데이터를 입출력 할 수 있다. 이에 따라 한번의 리드 동작 또는 라이트 동작시 각 반도체 칩 CHIP0~CHIP7으로부터 16\*16bit, 즉 32Byte의 데이터가 입출력되며, 8개의 반도체 칩(CHIP0~CHIP7)으로부터는 8\*32Byte, 즉 256Byte의 데이터가 입출력될 수 있다. 다시 말해, 본 실시예에서 한 페이지의 데이터 영역(110)의 크기는 256Byte이고, 제1~제8 반도체 칩 CHIP0~CHIP7의 각각에는 32Byte의 데이터 영역(110)의 일부가 형성된다. 그러나, 페이지의 데이터 영역(110)의 크기 및 각 반도체 칩에 형성되는 데이터 영역(110)의 일부의 크기는 이에 한하지 않으며, 데이터가 저장되는 반도체 칩의 개수, 각 반도체 칩에 구비되는 입출력 라인의 수, 버스트 랭쓰 등에 따라 달라질 수 있다.

[0027] ECC 영역(120)과 메타데이터 영역(130)은 제9 반도체 칩(CHIP8)에 형성된다. 즉, ECC 영역(120)과 메타데이터 영역(130)은 동일한 칩에 형성될 수 있다. ECC 영역(120)은 각 페이지마다 구비될 수 있다. ECC 영역(120)에는 동일한 페이지에 속하는 데이터 영역(110)에 저장된 데이터에 대응하는 ECC 데이터가 저장될 수 있다. 라이트 동작시 데이터 영역(110)에 데이터가 저장될 때, 동일한 페이지에 속하는 ECC 영역(120)에는 ECC 데이터가 저장될 수 있다. 리드 동작시에는 데이터 영역(110)으로부터 데이터가 출력될 때, 동일한 페이지에 속하는 ECC 영역(120)에 저장된 ECC 데이터가 출력될 수 있다.

[0028] 메타데이터 영역(130)은 각 페이지마다 구비될 수 있다. 메타데이터 영역(130)에는 당해 메타데이터 영역(130)이 속하는 페이지의 라이트 카운트가 저장될 수 있다. 메타데이터 영역(130)은 데이터 영역(110) 및 ECC 영역(120)과는 독립적으로 액세스될 수 있다.

[0029] 본 실시예에서 제9 반도체 칩(CHIP8)의 입출력 라인 DQ8은 제1~제8 반도체 칩(CHIP0~CHIP7)과 동일한 개수의 입출력 라인, 즉 16개의 입출력 라인을 가질 수 있다. ECC 영역(120)과 메타데이터 영역(130)은 제1~제8 칩(CHIP0~CHIP8)의 버스트 랭쓰의 절반의 버스트 랭쓰로 동작할 수 있다. 본 실시예에서 ECC 영역(120)과 메타데이터 영역(130)의 각각은 버스트 랭쓰 8(BL8)로 동작할 수 있다. 따라서, ECC 영역(120) 및 메타데이터 영역(130)은 각 영역에 대한 한번의 리드 동작 또는 라이트 동작시 16\*8bit, 즉 16Byte의 ECC 데이터 또는 페이지

메타데이터가 입출력될 수 있다. 다시 말해, 본 실시예에서 한 페이지의 ECC 영역(120) 및 메타데이터 영역(130) 각각의 크기는 16Byte이다.

[0030] 라이트 동작시 제1~제8 반도체 칩(CHIP0~CHIP7)에 형성된 데이터 영역(110)에 데이터가 저장됨과 함께, 제9 칩(CHIP8)에 형성된 ECC 영역(120)에는 ECC 데이터가 저장된다. 전술한 바와 같이 데이터 영역(110)에는 256Byte의 데이터가 저장되고, ECC 영역에는 16Byte의 ECC 데이터가 저장된다. 리드 동작시에는 제1~제8 칩(CHIP0~CHIP7)에 형성된 데이터 영역(110)으로부터 데이터가 출력됨과 함께, 제9 칩(CHIP8)에 형성된 ECC 영역(120)으로부터 ECC 데이터가 출력된다. 라이트 동작과 마찬가지로, 데이터 영역(110)으로부터 256Byte의 데이터가 출력되고, 제9 칩(CHIP8)으로부터 16Byte의 ECC 데이터가 출력된다. 이와 같이 라이트 동작 및 리드 동작시 데이터 영역(110)과 ECC 영역(120)은 한꺼번에 액세스될 수 있다. 메타데이터 영역(130)은 데이터 영역(110) 및 ECC 영역(120)과는 별도로 독립적으로 액세스될 수 있다.

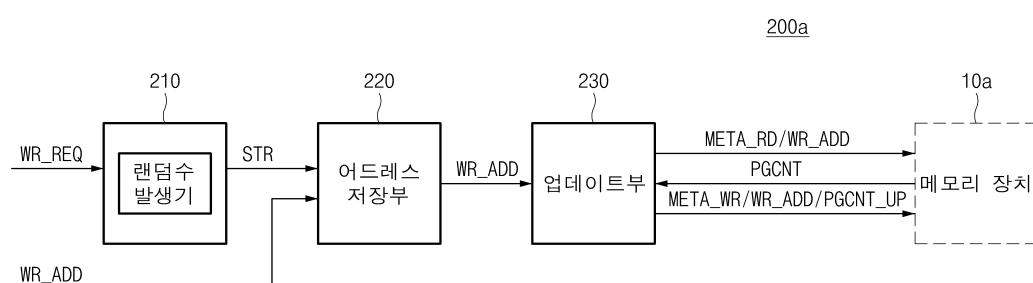

[0031] 도 3은 본 발명의 실시예에 따른 반도체 장치(200a)의 구성도이다.

[0032] 도 3을 참조하면, 반도체 장치(200a)는 결정부(210), 페이지 어드레스 저장부(220) 및 업데이트부(230)를 포함할 수 있다.

[0033] 결정부(210)는 라이트 요청 WR\_REQ이 수신되면, 라이트 요청 WR\_REQ에 대응하는 어드레스 WR\_ADD를 저장할지 여부를 결정한다. 본 실시예에서 반도체 시스템(1)의 라이트 동작은 페이지 단위로 수행되므로, 라이트 요청 WR\_REQ에 대응하는 어드레스 WR\_ADD는 메모리 장치(10a)의 특정 페이지를 가리키는 페이지 어드레스이다. 라이트 요청 WR\_REQ이 수신될 때마다, 수신된 라이트 요청 WR\_REQ에 대응하는 어드레스 WR\_ADD를 모두 저장할 수도 있지만, 이 경우 후술하는 어드레스 저장부(220)의 크기가 커지고, 반도체 장치(200a)가 메타데이터 영역(130)에 액세스해야 하는 횟수가 증가한다. 따라서, 본 실시예에서는 라이트 요청 WR\_REQ이 수신되면, 일정 확률로 어드레스 WR\_ADD를 저장한다. 이러한 결정부(210)는 랜덤수발생기(randomizer)를 포함할 수 있다. 예를 들어, 랜덤수 발생기는 1~16 중 임의의 수를 발생하고, 이 중 특정 수가 발생하는 경우 어드레스 저장 신호 STR를 활성화함으로써 1/16의 확률로 어드레스 WR\_ADD를 저장할 수 있다.

[0034] 어드레스 저장부(220)는 어드레스 저장 신호 STR에 기초하여 어드레스 WR\_ADD를 저장할 수 있다. 어드레스 저장부(220)는 FIFO(First In First Out) 또는 LIFO(Last In First Out)의 구조를 가지거나, 입력된 순서와 무관하게 어드레스 WR\_ADD를 출력할 수 있다.

[0035] 업데이트부(230)는 어드레스 WR\_ADD에 기초하여 메모리 장치(10a)의 각 페이지에 대한 라이트 요청의 횟수, 즉 페이지 라이트 카운트 PGCNT를 업데이트한다. 페이지 라이트 카운트 PGCNT는 어드레스 WR\_ADD에 해당하는 페이지에 속하는 메타데이터 영역(130)에 저장될 수 있다. 실시예에 따라, 업데이트부(230)는 어드레스 WR\_ADD에 대응하는 페이지에 속하는 메타데이터 영역(130)으로부터 페이지 라이트 카운트 PGCNT를 리드하고, 리드된 페이지 라이트 카운트 PGCNT를 업데이트한 값인 업데이트된 페이지 라이트 카운트 PGCNT\_UP를 메타데이터 영역(130)에 다시 라이트하는 방식으로, 페이지별 라이트 카운트를 저장할 수 있다.

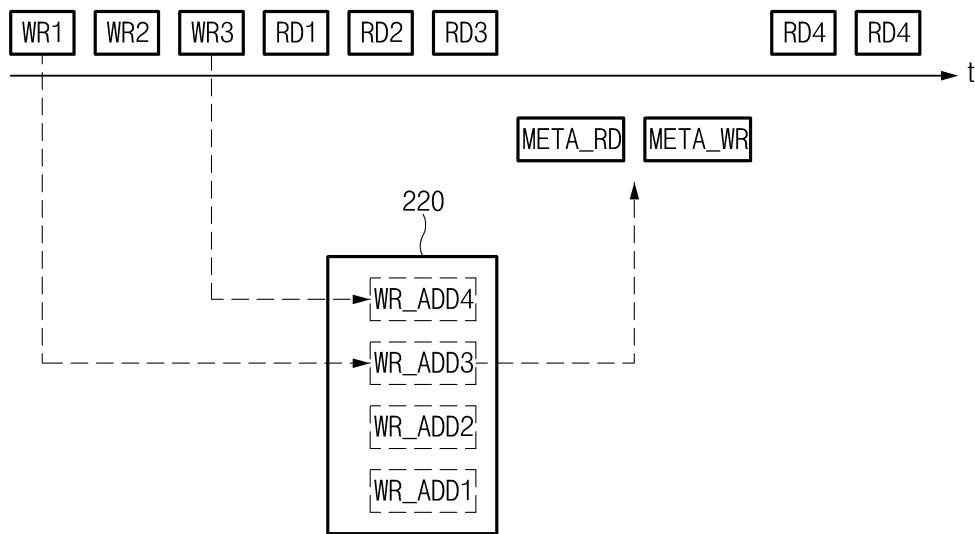

[0036] 도 4는 본 발명의 실시예에 따른 반도체 장치(200a)의 페이지 라이트 카운트의 업데이트 방법을 설명하기 위한 타이밍도이다. 도 4에서 라이트 커맨드 WR1~WR4 및 리드 커맨드 RD1~RD4는 데이터 영역(110) 및 ECC 영역(120)에 대한 라이트 동작 및 리드 동작을 지시하는 커맨드이고, 메타 라이트 커맨드 META\_WR 및 메타 리드 커맨드 META\_RD는 메타데이터 영역(130)에 대한 라이트 동작 및 리드 동작을 각각 지시하는 커맨드이다.

[0037] 도 4를 참조하면, 라이트 커맨드 WR1, WR2, WR3와, 리드 커맨드 RD1, RD2, RD3, 메타 리드 커맨드 META\_RD와 메타 라이트 커맨드 META\_WR, 리드 커맨드 RD4와 라이트 커맨드 WR4가 메모리 장치(10a)에 순차적으로 전송된다. 이와 같이, 메타데이터 영역(130)에 대한 메타 리드 커맨드 META\_RD와 메타 라이트 커맨드 META\_WR는 통상의 라이트 커맨드 또는 리드 커맨드가 입력되지 않는 동안에 전송될 수 있다.

[0038] 본 실시예에 따른 반도체 장치(200a)에서, 결정부(210)는 라이트 커맨드 WR1, WR2, WR3 각각에 대응하는 어드레스를 저장할지 여부를 결정한다. 본 실시예에서 결정부(210)는 1/16의 확률로 각 라이트 커맨드 WR1, WR2, WR3에 대응하는 어드레스를 저장하며, 이에 따라, 어드레스 저장부(220)는 라이트 커맨드 WR1, WR3에 해당하는 페이지 어드레스를 내부에 저장할 수 있다. 메모리 장치(10a)가 대기 중인 경우, 즉 메모리 장치(10a)가 리드 커맨드나 라이트 커맨드를 입력받고 있지 않는 동안, 업데이트부(230)는 어드레스 저장부(220)에 저장된 어드레스에 대해 메타 리드 커맨드 META\_RD를 전송한다. 메모리 장치(10a)는 메타 리드 커맨드 META\_RD에 대응하여, 메타데이터 영역(130)에 저장된 페이지 메타데이터, 즉 페이지 라이트 카운트를 전송한다. 업데이트부(230)는 수신된 페이지 라이트 카운트의 값을 1만큼 증가시키고, 증가된 페이지 라이트 카운트를 라이트하기 위해 메타 라

이트 커맨드 META\_WR를 전송한다. 메모리 장치(10a)는 메타 라이트 커맨드 META\_WR에 대응하여 메타데이터 영역(130)에 증가된 페이지 라이트 카운트를 라이트한다.

[0039] 업데이트부(230)는 어드레스 저장부(220)에 저장된 복수의 페이지 어드레스 중 임의의 어드레스의 페이지 라이트 카운트를 업데이트할 수 있다. 예를 들어, 도 4에 도시된 바와 같이, 어드레스 저장부(220)에 페이지 어드레스 WR\_ADD1, WR\_ADD2, WR\_ADD3, WR\_ADD4가 순차적으로 저장된 경우, 임의의 페이지 어드레스 WR\_ADD3에 해당하는 페이지 라이트 카운트가 먼저 업데이트될 수 있다. 다만, 본 발명의 범위는 이에 한하지 않으며, 가장 먼저 저장된 페이지 어드레스 WR\_ADD1의 페이지 라이트 카운트가 업데이트되거나, 가장 나중에 저장된 페이지 어드레스 WR\_ADD4의 페이지 라이트 카운트가 업데이트될 수도 있다.

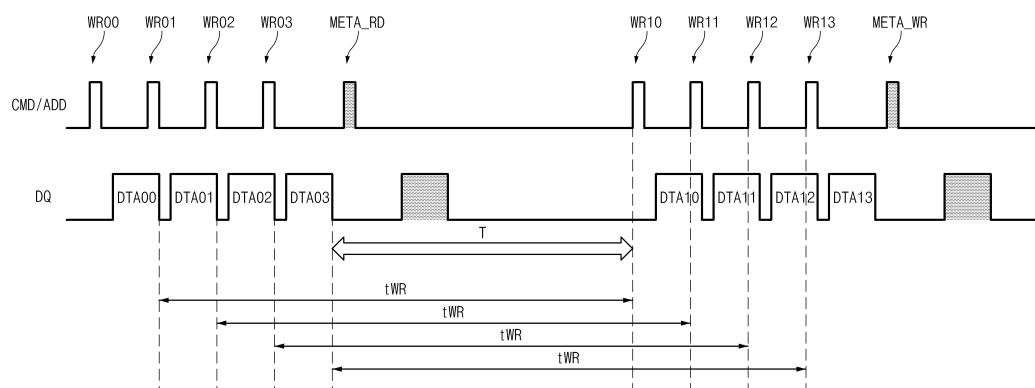

[0040] 도 5는 본 발명의 실시예에 따른 메타데이터 업데이트 방법을 설명하기 위한 타이밍도이다.

[0041] 최근 화상 처리나 빅데이터 처리 등 많은 양의 데이터를 사용하는 분야가 증가하고 있다. 많은 양의 데이터를 처리하기 위해서는 데이터의 처리 속도를 빠르게 하는 것도 중요하다. 반도체 메모리 장치에서 데이터 처리 속도를 증가시키기 위해 이용되는 방법으로서 뱅크 인터리빙이 있다. 뱅크 인터리빙이란, 복수의 뱅크를 동시에 이용하도록 데이터를 제어하는 기술이다. 그러나, 뱅크 인터리빙은 복수의 뱅크가 동시에 이용되므로, 소모 전력이 증가한다. 이에 따라, 동시에 실행 가능한 라이트 동작 또는 리드 동작의 개수를 제한할 수 있으며, 이에 따라 메모리 장치가 최대 개수의 라이트 동작 또는 리드 동작을 수행하는 중에는 커맨드를 입력받지 않고 대기하는 대기 시간이 발생할 수 있다.

[0042] 도 5에서는 메모리 장치(10a)가 4개의 뱅크 Bank0~Bank3를 포함하는 것으로 가정한다. 그러나, 이는 설명의 편의를 위한 것이고, 본 발명의 범위는 이에 한하지 않는다.

[0043] 도 5를 참조하면, 제1 뱅크 Bank0에 대한 라이트 커맨드 WR00 및 이에 대응하는 데이터 DTA00, 제2 뱅크 Bank1에 대한 라이트 커맨드 WR01 및 이에 대응하는 데이터 DTA01, 제3 뱅크 Bank2에 대한 라이트 커맨드 WR02 및 이에 대응하는 데이터 DTA02, 제4 뱅크 Bank3에 대한 라이트 커맨드 WR03 및 이에 대응하는 데이터 DTA03가 순차적으로 입력된다. 그리고 소정 시간 경과 후에 제1 뱅크 Bank0에 대한 라이트 커맨드 WR10 및 이에 대응하는 데이터 DTA10, 제2 뱅크 Bank1에 대한 라이트 커맨드 WR11 및 이에 대응하는 데이터 DTA11, 제3 뱅크 Bank2에 대한 라이트 커맨드 WR12 및 이에 대응하는 데이터 DTA12, 제4 뱅크 Bank3에 대한 라이트 커맨드 WR13 및 이에 대응하는 데이터 DTA13가 순차적으로 입력된다.

[0044] 제1 뱅크 Bank0에 대한 라이트 커맨드 WR00 및 이에 대응하는 데이터 DTA00의 입력이 완료되면, 제1 뱅크 Bank0에 대한 라이트 동작이 일정 시간 tWR 동안 수행된다. 제2~제4 뱅크 Bank1~3에 대해서도 마찬가지로 라이트 커맨드 WR01~WR03 및 이에 대응하는 데이터 DTA01~DTA03의 입력이 완료되면, 각 뱅크 Bank1~3에 대한 라이트 동작이 일정 시간 tWR 동안 수행된다.

[0045] 라이트 동작을 수행함에 따라 메모리 장치(10a)에서는 전력이 소모된다. 그러나, 메모리 장치(10a)에서 소비 가능한 전력에는 제한이 있기 때문에, 메모리 장치(10a)에서 동시에 처리할 수 있는 라이트 동작 또는 리드 동작의 개수에 제한이 있다. 본 실시예에서 동시에 처리할 수 있는 라이트 커맨드(라이트 동작)의 최대 개수는 4개이지만, 본 발명의 범위는 이에 한하지 않는다. 본 실시예에서는 뱅크 Bank0~Bank3의 개수와, 동시에 처리할 수 있는 라이트 커맨드의 최대 개수가 동일하지만, 서로 다를 수도 있다.

[0046] 소정 시간 T 동안, 동시에 처리할 수 있는 최대 개수인 4개의 뱅크 Bank0~Bank3에 대해 라이트 동작이 실행된다. 이에 따라, 메모리 장치(10a)에는 소정 시간 T 동안에는 추가적인 라이트 커맨드가 입력되지 않는다. 소정 시간 T 경과 후, 제1 뱅크 Bank0에 대한 라이트 동작이 완료되면, 제1 뱅크 Bank0에 대한 라이트 커맨드 WR10 및 이에 대응하는 데이터 DTA10가 추가적으로 입력된다. 이후, 제2 뱅크 Bank1에 대한 라이트 동작이 완료되면, 제2 뱅크 Bank1에 대한 라이트 커맨드 WR11 및 이에 대응하는 데이터 DTA11가 추가적으로 입력되고, 제3 뱅크 Bank2에 대한 라이트 동작이 완료되면, 제3 뱅크 Bank2에 대한 라이트 커맨드 WR12 및 이에 대응하는 데이터 DTA12가 추가적으로 입력되고, 제4 뱅크 Bank3에 대한 라이트 동작이 완료되면, 제4 뱅크 Bank3에 대한 라이트 커맨드 WR13 및 이에 대응하는 데이터 DTA13가 추가적으로 입력된다.

[0047] 본 실시예에 따른 반도체 장치(200a)는 뱅크 인터리빙 시 최대 개수의 뱅크가 동작하는 동안, 즉 대기 시간 T 동안 페이지 라이트 카운트를 저장할 수 있다. 페이지 라이트 카운트를 업데이트하기 위해서는, 메타데이터 영역(130)에 저장된 페이지 라이트 카운트를 리드한 후, 리드된 페이지 라이트 카운트를 증가시키고, 증가된 페이지 라이트 카운트를 다시 메타데이터 영역(130)에 라이트해야 한다. 일반적으로, 리드 동작시 소모되는 전력은 라이트 동작에 비해 훨씬 적다. 또한, 본 실시예에서 하나의 페이지에 대응하는 메타데이터 영역(130)의 크기는

16Byte이고, 한 페이지의 크기는 256Byte인 것과 같이, 메타데이터 영역(130)의 크기는 페이지의 크기보다 작다. 따라서, 최대 개수의 뱅크가 동작하는 동안 페이지 라이트 카운트를 업데이트하기 위한 메타 리드 동작 및 메타 라이트 동작을 수행하더라도, 메모리 장치(10a)에서 추가적으로 소비하는 전력이 크지 않다. 본 실시 예에 의하면, 뱅크 인터리빙시 최대 개수의 뱅크가 동작하는 동안 페이지 라이트 카운트를 업데이트할 수 있기 때문에, 페이지 라이트 카운트를 업데이트하기 위한 시간을 별도로 할당할 필요가 없어 반도체 시스템(1a)의 성능 저하를 막을 수 있다.

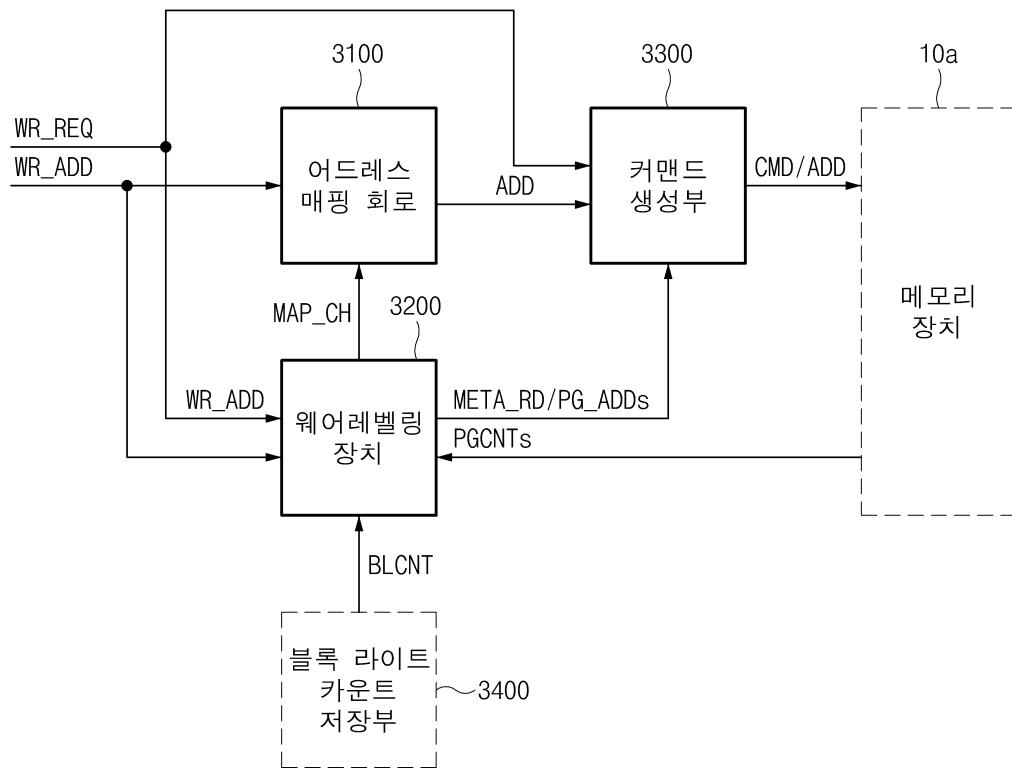

[0048] 다음으로, 전술한 페이지 메타데이터(페이지 라이트 카운트)를 이용하여 웨어레벨링을 수행하는 반도체 장치(300a)에 대해 설명한다.

[0049] 도 6은 본 발명의 실시예에 따른 반도체 장치(300a)의 구성도이다. 반도체 장치(300a)는 도 1의 제2 반도체 장치(300)에 대응한다. 반도체 장치(300a)는 호스트(미도시)로부터 수신된 라이트 요청 WR\_REQ과 어드레스 WR\_ADD에 기초하여 커맨드 CMD를 생성하거나, 메모리 장치(10a)로부터 페이지 라이트 카운트 PGCNTs를 리드하기 위한 커맨드 CMD를 생성하며, 웨어 레벨링 동작을 수행한다.

[0050] 반도체 장치(300a)는 어드레스 맵핑 회로(3100), 웨어레벨링 장치(3200) 및 커맨드 생성회로(3300)를 포함할 수 있다. 어드레스 맵핑 회로(3100)는 논리적 어드레스에 해당하는 어드레스 WR\_ADD를 물리적 어드레스 ADD로 변환하며, 어드레스 맵핑 변경 신호 MAP\_CH에 기초하여 논리적 어드레스 WR\_ADD와 물리적 어드레스 ADD의 대응관계를 변경한다. 웨어레벨링 장치(3200)는 라이트 요청 WR\_REQ에 기초하여 페이지 라이트 카운트들 PGCNTs를 획득하기 위한 메타 리드 신호 META\_RD 및 페이지 어드레스들 PG\_ADDs를 생성하고, 어드레스 맵핑 회로(3100)의 어드레스 맵핑을 변경하기 위한 어드레스 맵핑 변경 신호 MAP\_CH를 생성한다. 커맨드 생성부(3300)는 라이트 요청 WR\_REQ 및 물리적 어드레스 ADD에 기초하여 메모리 장치(100a)에 전송되는 라이트 커맨드 WR 및 어드레스 ADD를 생성한다. 실시예에 따라, 커맨드 생성부(3300)는 메타 리드 신호 META\_RD 및 PG\_ADDs에 기초하여 메모리 장치(100a)의 메타데이터 영역(130)으로부터 페이지 라이트 카운트들 PGCNTs를 리드하기 위한 메타 리드 커맨드 META\_RD를 생성할 수 있다.

[0051] 도 7은 본 발명의 일 실시예에 따른 어드레스 맵핑 회로(3100)에 구비되는 어드레스 맵핑 테이블이다.

[0052] 도 7을 참조하면, 페이지 어드레스 맵핑 테이블은 논리적 페이지 어드레스 들 LOG\_ADD1, LOG\_ADD2과, 이에 대응하는 물리적 페이지 어드레스들 PHY\_ADD1, PHY\_ADD2, PHY\_ADD3을 나타내는 테이블이다. 라이트 요청 WR\_REQ과 함께 입력되는 어드레스 WR\_ADD는 논리적 어드레스에 해당하고, 어드레스 맵핑 회로 3100에서 변환된 어드레스 ADD는 물리적 어드레스에 해당한다. 도 7에 도시된 바와 같이, 어드레스 맵핑 테이블 AMT1과 어드레스 맵핑 테이블 AMT2은 논리적 페이지 어드레스들과 물리적 페이지 어드레스들이 대응관계가 상이하다. 어드레스 맵핑 테이블(3200)은 논리적 페이지 어드레스와 물리적 페이지 어드레스의 대응관계가 상이한 복수의 페이지 어드레스 맵핑 테이블 AMT1, AMT2를 포함하고, 어드레스 맵핑 변경 신호 MAP\_CH에 기초하여 사용할 페이지 어드레스 맵핑 테이블을 변경할 수 있다.

[0053] 실시예에 따라 어드레스 맵핑 회로(3100)는 XOR 키(key)를 이용하여 논리적 페이지 어드레스 WR\_ADD를 물리적 페이지 어드레스 ADD로 변환할 수 있다. XOR 키의 값을 K라 하면, 하기의 식(1) 및 식(2)이 성립한다.

$$A \text{ XOR } K = B \quad \dots(1)$$

$$A = B \text{ XOR } K \quad \dots(2)$$

[0056] 예를 들어, A가 0이고, K가 1인 경우, A XOR K의 값, 즉 B는 1이 된다. 여기서, B가 1이고, K가 1인 경우, B XOR K의 값은 0, 즉 A와 동일한 값이 된다.

[0057] XOR 연산의 이러한 특성을 이용하여, 논리적 페이지 어드레스와 물리적 페이지 어드레스를 대응시킬 수 있다. 물리적 페이지 어드레스, 논리적 페이지 어드레스, XOR 키가 동일한 비트 수를 갖는 경우, 하기의 식(3) 및 식(4)가 성립한다. XOR 연산은 대응하는 각 비트에 대해 이루어진다.

$$\text{LOG\_ADD XOR K} = \text{PHY\_ADD} \quad \dots(3)$$

$$\text{LOG\_ADD} = \text{PHY\_ADD XOR K} \quad \dots(4)$$

[0060] 이러한 XOR 키를 이용하는 경우에는 물리적 페이지 어드레스와 논리적 페이지 어드레스의 쌍을 모두 저장할 필요 없이, XOR 키의 값만 저장하면 되므로, 페이지 어드레스 맵을 위한 저장 영역을 감소시킬 수 있다. 실시예에 따라, 어드레스 맵핑 변경 신호 MAP\_CH는 XOR 키 값일 수 있으며, 어드레스 맵핑 회로(3100)는 어드레스 맵

평 변경 신호 MAP\_CH로서 제공되는 XOR 키 값에 따라 물리적 페이지 어드레스를 논리적 페이지 어드레스로 변환 할 수 있다.

[0061] 실시예에 따라 어드레스 맵핑 회로(3100)는 전술한 어드레스 맵핑 테이블을 이용한 방식과 XOR 키를 이용한 방식을 모두 적용할 수도 있다. 어드레스 맵핑 변경 신호 MAP\_CH는 변경할 어드레스 맵핑 테이블 및 XOR 키를 모두 가리키는 신호일 수 있다.

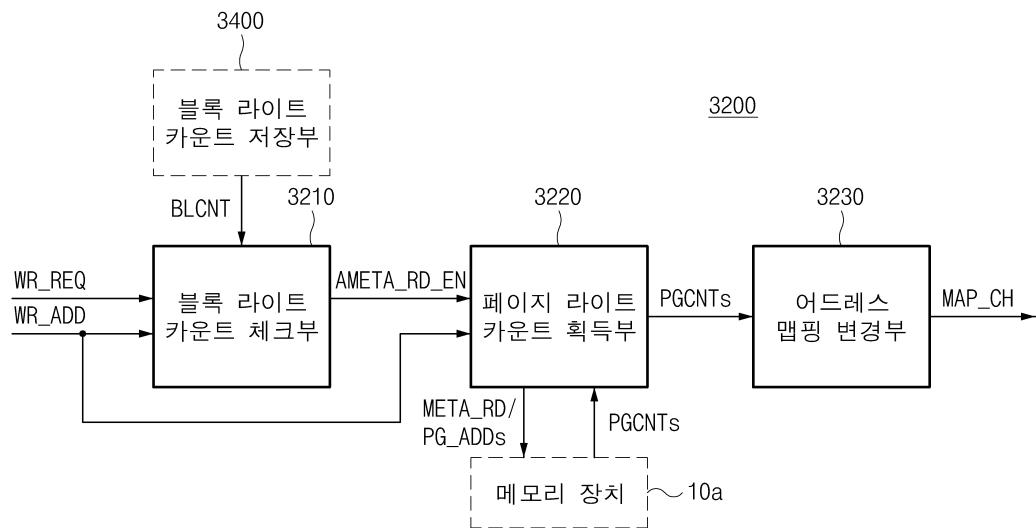

[0062] 도 8은 본 발명의 실시예에 따른 웨어레벨링 장치(3200)의 구성도이다.

[0063] 도 8을 참조하면, 웨어레벨링 장치(3200)는 블록 라이트 카운트 체크부(3210), 페이지 라이트 카운트 획득부(3220) 및 어드레스 맵핑 변경부(3230)를 포함한다.

[0064] 블록 라이트 카운트 체크부(3210)는 라이트 요청 WR\_REQ이 수신되면, 블록 라이트 카운트 저장부(3400)으로부터, 수신된 라이트 요청 WR\_REQ에 대응하는 블록의 블록 라이트 카운트 BLCNT를 획득하고, 획득한 블록 라이트 카운트 BLCNT에 기초하여 올 메타 리드 신호(AMETA\_RD\_EN)를 생성한다. 본 실시예에서 블록 라이트 카운트 BLCNT란 어떤 블록에 속하는 페이지들에 라이트 동작이 수행된 횟수를 나타낸다.

[0065] 페이지 라이트 카운트 획득부(3220)는 올 메타 리드 신호(AMETA\_RD\_EN)에 기초하여 라이트 요청 WR\_REQ에 대응하는 블록에 속하는 페이지들의 페이지 라이트 카운트들(PGCNTs)을 획득한다. 페이지 라이트 카운트 획득부(3220)는 메타 리드 커맨드 META\_RD와 함께, 라이트 요청 WR\_REQ에 대응하는 블록에 속하는 페이지들의 어드레스들 PG\_ADDs을 커맨드 생성부(3300)를 통해 메모리 장치(10a)에 전송할 수 있다. 메모리 장치(10a)는 메타 리드 커맨드 META\_RD 및 페이지 어드레스들 PG\_ADDs에 기초하여 메타데이터 영역(130)으로부터 페이지 라이트 카운트들 PGCNTs을 출력할 수 있다.

[0066] 어드레스 맵핑 변경부(3230)는 페이지 라이트 카운트들 PGCNTs에 기초하여 페이지 어드레스 맵핑을 변경하기 위한 어드레스 맵핑 변경 신호 MAP\_CH를 생성한다. 어드레스 맵핑 변경 신호 MAP\_CH는 어드레스 맵핑 테이블을 변경하는 신호이거나, XOR 키를 나타내는 신호이거나, 어드레스 맵핑 테이블을 변경하는 신호 및 XOR 키 모두를 나타내는 신호일 수 있다.

[0067] 실시예에 따라, 어드레스 맵핑 변경부(3230)는 페이지 라이트 카운트들 PGCNTs 중 최대값과 최소값의 차이에 기초하여 어드레스 맵핑 변경 신호 MAP\_CH를 생성할 수 있다. 예를 들어, 어드레스 맵핑 변경부(3230)는 페이지 라이트 카운트들 PGCNTs 중 최대값과 최소값의 차이가 미리 설정된 기준값보다 작으면 어드레스 맵핑 변경 신호 MAP\_CH를 비활성화하고, 페이지 라이트 카운트들 PGCNTs 중 최대값과 최소값의 차이가 미리 설정된 기준값 이상이면 어드레스 맵핑 변경 신호 MAP\_CH를 활성화할 수 있다. 페이지 라이트 카운트들 PGCNTs 중 최대값과 최소값의 차이가 미리 설정된 기준값보다 작으면 해당 블록에 속하는 페이지들이 고르게 라이트되고, 페이지 라이트 카운트들 PGCNTs 중 최대값과 최소값의 차이가 크면 해당 블록에 속하는 페이지들 고르게 라이트되지 않은 것으로 판단할 수 있기 때문이다. 페이지 라이트 카운트들 PGCNTs 중 최대값과 최소값의 차이가 큰지 작은지 여부를 결정하기 위한 기준값은 미리 설정될 수 있다.

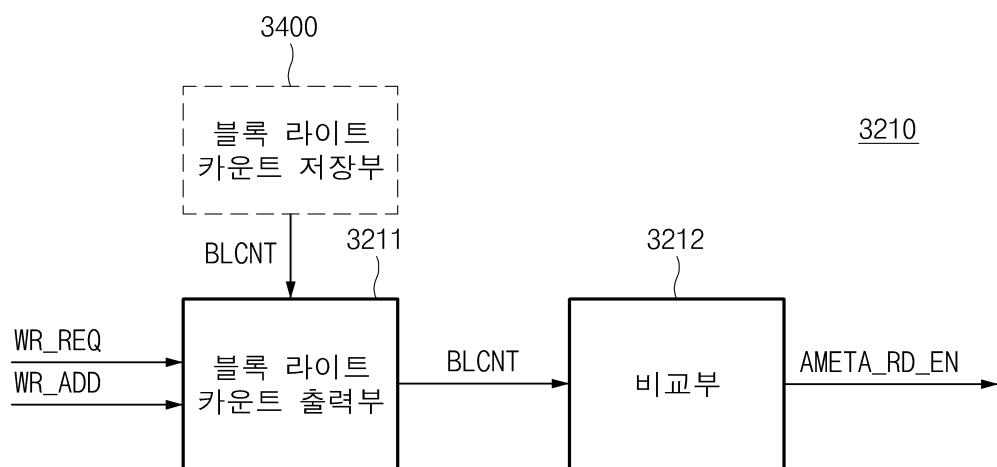

[0068] 도 9는 본 발명의 실시예에 따른 블록 라이트 카운트 체크부(3210)의 구성도이다. 도 9를 참조하면, 블록 라이트 카운트 체크부(3210)는 블록 라이트 카운트 출력부(3211) 및 비교부(3212)를 포함할 수 있다.

[0069] 블록 라이트 카운트 출력부(3211)는 블록 라이트 카운트 BLCNT를 저장하는 블록 라이트 카운트 저장부(3400)로부터 블록 라이트 카운트 BLCNT를 제공받는다. 블록 라이트 카운트 저장부(3400)는 블록에 관한 메타 데이터를 저장하는 메모리 장치이며, 예를 들면 DRAM일 수 있다. 실시예에 따라, 블록 라이트 카운트 저장부(3400)는 블록 라이트 카운트 출력부(3211) 내부에 포함될 수도 있다. 블록 라이트 카운트 출력부(3211)는 라이트 요청(WR\_REQ)이 수신되면 블록 라이트 카운트 BLCNT를 블록 라이트 카운트 저장부(3400)로부터 획득하여 출력한다. 실시예에 따라, 블록 라이트 카운트 출력부(3211)는 라이트 요청(WR\_REQ)에 대응하여, 블록 라이트 카운트 저장부(3400)에 블록 라이트 카운트 BLCNT를 출력시키기 위한 리드 신호를 생성함으로써, 블록 라이트 카운트 BLCNT를 획득할 수 있다.

[0070] 비교부(3212)는 블록 라이트 카운트 출력부(3211)로부터 제공된 블록 라이트 카운트 BLCNT와 미리 설정된 기준치를 비교한 결과에 기초하여 올 메타 리드 신호 AMETA\_RD\_EN를 생성할 수 있다. 예를 들어, 비교부(3212)는 블록 라이트 카운트 BLCNT가 미리 설정된 기준치와 동일하거나 미리 설정된 기준치보다 크면 페이지 라이트 올 메타 리드 신호 AMETA\_RD\_EN를 생성할 수 있다.

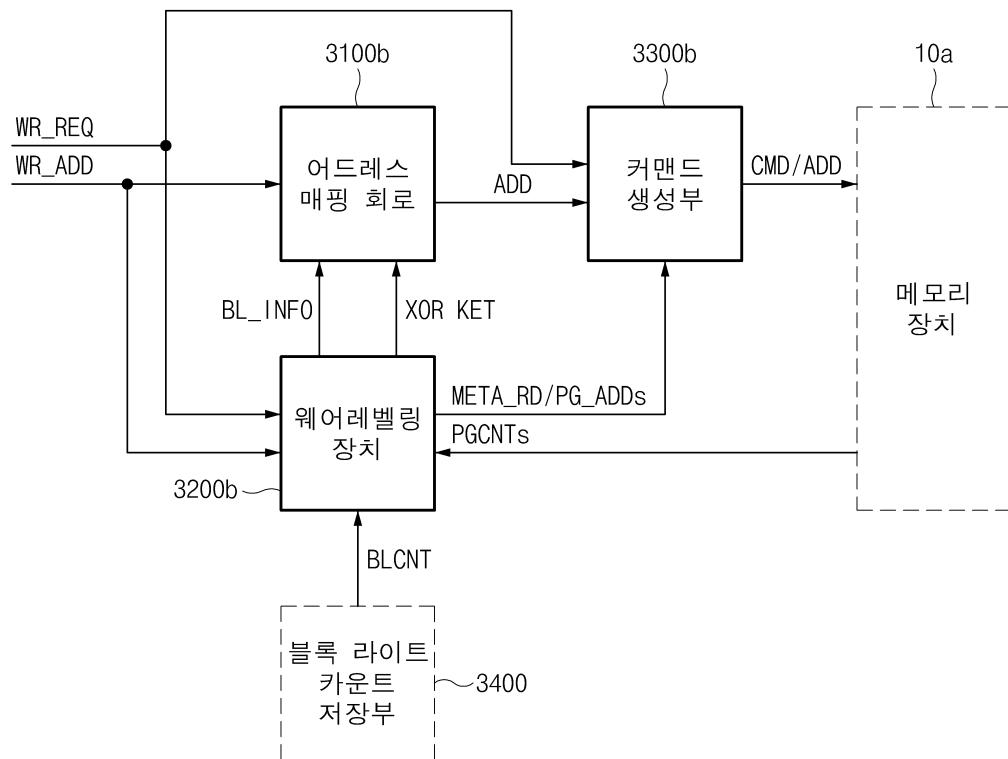

[0071] 도 10은 본 발명의 실시예에 따른 반도체 장치(300b)의 구성도이다. 반도체 장치(300b)는 도 1의 제2 반도체

장치(300)에 대응할 수 있다.

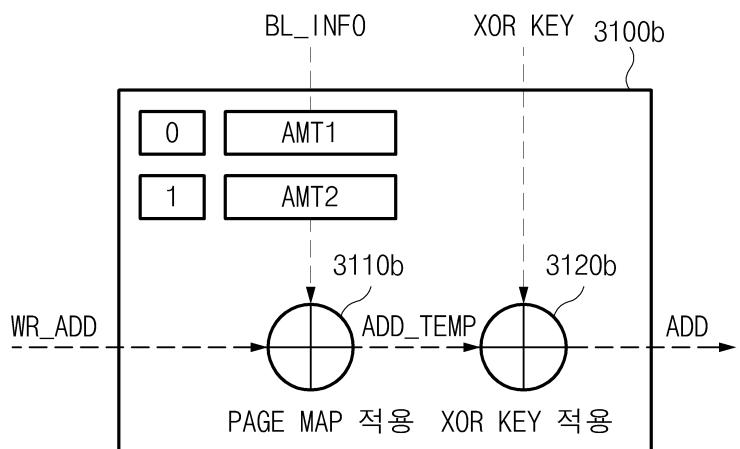

[0072] 도 10을 참조하면, 반도체 장치(300b)는 어드레스 맵핑 회로(3100b), 웨어레벨링 장치(3200b) 및 커맨드 생성회로(3300b)를 포함한다. 어드레스 맵핑 회로(3100b)는 블록 구간 정보 BL\_INFO에 기초하여 복수의 어드레스 맵핑 테이블 중 하나를 선택하여 어드레스를 변환한 후, 변환된 어드레스를 XOR 키를 이용하여 재변환한다. 웨어레벨링 장치(3200b)는 라이트 요청 WR\_REQ에 기초하여 블록 구간 정보 BL\_INFO 및 XOR 키를 제공한다. 커맨드 생성부(3300b)는 도 6의 커맨드 생성부(3300)와 그 기능이 동일하므로 설명을 생략한다.

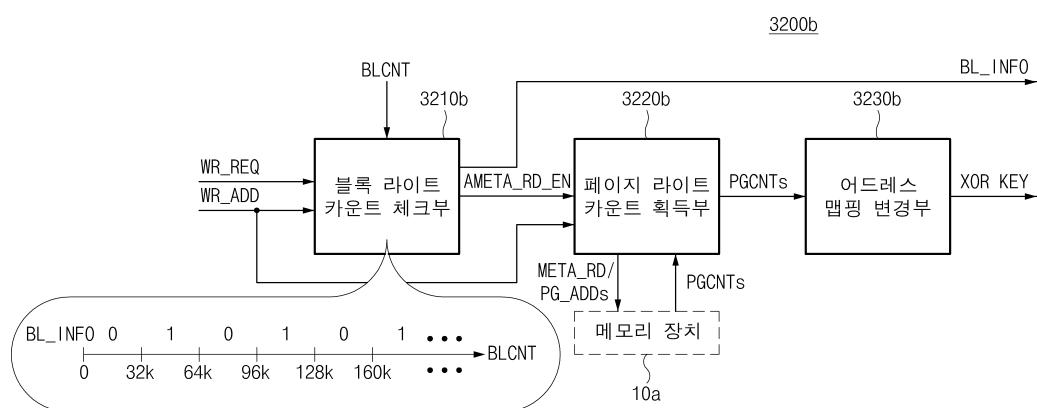

[0073] 도 11은 본 발명의 실시예에 따른 웨어레벨링 장치(3200b)의 구성도이다.

[0074] 도 11을 참조하면, 웨어레벨링 장치(3200b)는 블록 라이트 카운트 체크부(3210b), 페이지 라이트 카운트 획득부(3220b) 및 어드레스 맵핑 변경부(3230b)를 포함한다.

[0075] 블록 라이트 카운트 체크부(3210b)는 블록 라이트 카운트 체크부(3210)와 동일하게 라이트 요청 WR\_REQ이 수신되면 수신된 라이트 요청 WR\_REQ에 대응하는 블록의 블록 라이트 카운트에 기초하여 올 메타 리드 신호 AMETA\_RD\_EN를 생성한다. 본 실시예에서 추가적으로 블록 라이트 카운트 체크부(3210b)는 메모리 장치(10a)의 각 블록의 블록 라이트 카운트들이 미리 설정된 복수의 구간 중 어디에 속하는지를 판단한 결과에 기초하여 블록 구간 정보 BL\_INFO를 생성한다.

[0076] 도 11을 참조하면, 블록 라이트 카운트 체크부(3210b)는 블록 라이트 카운트 BLCNT를 예를 들면 32K마다 복수의 구간으로 설정할 수 있다. 그리고 블록 라이트 카운트 체크부(3210b)는 각 구간에 대응하여 블록 구간 정보 BL\_INFO를 생성할 수 있다. 예를 들어, 메모리 장치(10a)의 각 블록의 블록 라이트 카운트들이 0~32K의 구간에 위치하는 경우에는 블록 구간 정보 BL\_INFO로서 0을 출력하고, 메모리 장치(10a)의 각 블록의 블록 라이트 카운트들이 32K~64K의 구간에 위치하는 경우에는 블록 구간 정보 BL\_INFO로서 1을 출력하고, 메모리 장치(10a)의 각 블록의 블록 라이트 카운트들이 64K~96K의 구간에 위치하는 경우에는 블록 구간 정보 BL\_INFO로서 1을 출력하는 식으로 블록 구간 정보 BL\_INFO를 생성할 수 있다.

[0077] 페이지 라이트 카운트 획득부(3220b)는 페이지 라이트 카운트 획득부(3220)와 그 기능이 동일하므로 설명을 생략한다.

[0078] 어드레스 맵핑 변경부(3230b)는 페이지 라이트 카운트들 PGCNTs에 기초하여 어드레스 맵핑 변경을 위한 XOR 키를 생성한다. 어드레스 맵핑 변경부(3230b)는 페이지 라이트 카운트들 PGCNTs의 최소값과 최대값의 차이에 기초하여 XOR 키를 생성할 수 있다.

[0079] 도 12는 본 발명의 실시예에 따른 어드레스 맵핑 회로(3100b)의 동작을 설명하기 위한 도면이다. 어드레스 맵핑 회로(3100b)는 어드레스 맵핑 테이블 적용부(3110b) 및 XOR 키 적용부(3120b)를 포함할 수 있다.

[0080] 어드레스 맵핑 테이블 적용부(3110b)는 블록 구간 정보 BL\_INFO에 기초하여 복수의 어드레스 맵핑 테이블 중 한 개를 선택할 수 있다. 예를 들어, 블록 구간 정보가 0인 경우, 즉 블록 라이트 카운트들의 분포가 0~32K에 위치하는 경우, 어드레스 맵핑 테이블 적용부(3110b)는 어드레스 맵핑 테이블 AMT1을 이용하여 어드레스 WR\_ADD를 변환하여 임시 어드레스 ADD\_TEMP를 생성한다. XOR 키 적용부(3120b)는 임시 어드레스 ADD\_TEMP에 XOR 키를 적용하여 어드레스 ADD를 생성할 수 있다.

[0081] 실시예에 따라, 어드레스 맵핑 회로(3100b)는 블록 구간 정보 BL\_INFO에 기초하여 어드레스 맵핑 테이블 AMT1, AMT2를 재생성할 수 있다. 예를 들어, 어드레스 맵핑 회로(3100a)는 블록 구간 정보 BL\_INFO가 1에서 0으로 변경될 때마다, 어드레스 맵핑 테이블 AMT1, AMT2를 재생성할 수 있다.

[0082] 본 실시예에서 블록 라이트 카운트 구간들은 모두 32K의 동일한 크기를 갖는 것으로 가정하였지만, 본 발명의 범위는 이에 한하지 않으며, 블록 라이트 카운트 구간들의 크기는 서로 상이하게 설정될 수 있다.

[0083] 본 실시예에서 블록 구간 정보 BL\_INFO는 0과 1의 두 가지의 값을 갖고, 이에 대응하는 어드레스 맵핑 테이블 AMT1, AMT2도 2개인 것으로 가정하였지만, 본 발명의 범위는 이에 한하지 않는다. 예를 들어, 블록 구간 정보 BL\_INFO는 00, 01, 10, 11의 4가지의 값을 갖고, 어드레스 맵핑 테이블은 각 블록 구간 정보에 대응하여 4개일 수 있다. 또는 블록 구간 정보 BL\_INFO와 어드레스 맵핑 테이블 AMT1, AMT2이 일대일로 대응하는 대신, 블록 구간 정보 BL\_INFO가 00, 10인 경우에는 어드레스 맵핑 테이블 AMT1에 대응하고, 블록 구간 정보 BL\_INFO가 01, 11인 경우에는 어드레스 맵핑 테이블 AMT1에 대응하는 등 다수의 블록 구간 정보 BL\_INFO에 하나의 어드레스 맵핑 테이블이 대응하도록 구성할 수도 있다.

[0084] 본 실시예에서, 어드레스 맵핑 회로(3100a)는 어드레스 맵핑 테이블을 적용한 후 XOR 키를 적용하는 것으로 설명하였지만, 본 발명은 이에 한하지 않으며, XOR 키를 먼저 적용한 후에 어드레스 맵핑 테이블을 적용할 수도 있다.

[0085] 본 실시예에 의하면, 블록 전체에 대해서는 어드레스 맵핑 테이블을 적용하고, 각 블록에 대해서는 상이한 XOR 키를 적용하기 때문에 웨어레벨링의 효과를 향상시킬 수 있다. XOR 키만을 적용하는 경우 XOR 키의 값은 물리적 페이지 어드레스 또는 논리적 페이지 어드레스가 가질 수 있는 값으로 제한된다. 예를 들어, 물리적 페이지 어드레스와 논리적 페이지 어드레스가 4bit로 구성된 경우, XOR 키도 4bit를 갖는다. 이에 따라, XOR 키가 가질 수 있는 값은 16개로 제한된다. 어드레스 맵핑 테이블을 이용하는 경우, 모든 논리적 어드레스에 대한 물리적 어드레스를 대응시켜야 하기 때문에 저장 공간의 크기가 커진다. 본 실시예에 의하면, 블록 전체에 대해서는 동일한 어드레스 맵핑 테이블을 이용하고, 각 블록에 대해서는 상이한 XOR 키를 적용하기 때문에, 웨어레벨링시 필요한 저장 공간의 크기를 감소시키면서 웨어레벨링의 효과를 향상시킬 수 있다.

[0086] 이상, 본 발명의 상세한 설명에서는 구체적인 실시 예에 관해 설명하였으나, 본 발명의 범위에서 벗어나지 않는 한도 내에서 여러 가지 변형이 가능함은 물론이다. 그러므로, 본 발명의 범위는 설명된 실시 예에 국한되어 정해져서는 안되며 후술하는 특허청구의 범위뿐만 아니라 이 특허청구의 범위와 균등한 것들에 의해 정해져야 한다.

## 도면

### 도면1

## 도면2

## 도면3

## 도면4

## 도면5

## 도면6

300

## 도면7

| AMT1     |          | AMT2     |          |

|----------|----------|----------|----------|

| WR_ADD   | ADD      | WR_ADD   | ADD      |

| LOG_ADD1 | PHY_ADD1 | LOG_ADD1 | PHY_ADD3 |

| LOG_ADD2 | PHY_ADD2 | LOG_ADD2 | PHY_ADD1 |

| ⋮        | ⋮        | ⋮        | ⋮        |

## 도면8

## 도면9

## 도면10

300

## 도면11

## 도면12