(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第5820172号

(P5820172)

(45) 発行日 平成27年11月24日(2015.11.24)

(24) 登録日 平成27年10月9日(2015.10.9)

|                        |                |

|------------------------|----------------|

| (51) Int.Cl.           | F 1            |

| HO 1 L 23/28 (2006.01) | HO 1 L 23/28 F |

| HO 1 L 23/12 (2006.01) | HO 1 L 23/12 E |

| HO 1 L 23/00 (2006.01) | HO 1 L 23/00 A |

請求項の数 5 (全 14 頁)

|              |                              |           |                                       |

|--------------|------------------------------|-----------|---------------------------------------|

| (21) 出願番号    | 特願2011-155437 (P2011-155437) | (73) 特許権者 | 000003078<br>株式会社東芝<br>東京都港区芝浦一丁目1番1号 |

| (22) 出願日     | 平成23年7月14日(2011.7.14)        | (74) 代理人  | 110001092<br>特許業務法人サクラ国際特許事務所         |

| (65) 公開番号    | 特開2012-39104 (P2012-39104A)  | (72) 発明者  | 山田 啓壽<br>東京都港区芝浦一丁目1番1号 株式会社<br>東芝内   |

| (43) 公開日     | 平成24年2月23日(2012.2.23)        | (72) 発明者  | 山崎 尚<br>東京都港区芝浦一丁目1番1号 株式会社<br>東芝内    |

| 審査請求日        | 平成25年8月23日(2013.8.23)        | (72) 発明者  | 福田 昌利<br>東京都港区芝浦一丁目1番1号 株式会社<br>東芝内   |

| (31) 優先権主張番号 | 特願2010-160980 (P2010-160980) |           |                                       |

| (32) 優先日     | 平成22年7月15日(2010.7.15)        |           |                                       |

| (33) 優先権主張国  | 日本国(JP)                      |           |                                       |

最終頁に続く

(54) 【発明の名称】半導体装置とそれを用いた携帯通信機器

## (57) 【特許請求の範囲】

## 【請求項1】

第1の面と第2の面とを有する絶縁基材と、前記絶縁基材の前記第1の面に形成された第1の配線層と、前記絶縁基材の前記第2の面に形成された第2の配線層と、導体層とを備えるインターポーヴ基板と、

前記第1の面に設けられた外部接続端子と、

前記第2の面上に搭載された半導体チップと、

前記半導体チップを封止するように前記第2の面上に設けられた封止樹脂層と、

前記封止樹脂層と前記インターポーヴ基板の側面の少なくとも一部を覆う導電性シールド層とを備えし、

前記導電性シールド層は識別マークを有し、

前記識別マーク部分における前記導電性シールド層の厚さは2μm以上であり、

前記識別マーク部分における前記導電性シールド層の表面粗さは、前記識別マーク以外の部分における前記導電性シールド層の表面粗さよりも小さいことを特徴とする半導体装置。

## 【請求項2】

請求項1記載の半導体装置において、

前記導電性シールド層は前記インターポーヴ基板の切断面に露出した前記導体層を介して前記外部接続端子に含まれるグランドピンに電気的に接続されることを特徴とする半導体装置。

**【請求項 3】**

請求項 1 または請求項 2 記載の半導体装置において、

前記識別マークは前記導電性シールド層の厚さ方向の一部のみを削ることにより形成されていることを特徴とする半導体装置。

**【請求項 4】**

請求項 1 ないし請求項 3 のいずれか 1 項記載の半導体装置において、

前記導電性シールド層の表面に、さらに保護層を具備することを特徴とする半導体装置。

**【請求項 5】**

請求項 1 ないし請求項 4 のいずれか 1 項記載の半導体装置を具備することを特徴とする携帯通信機器。

10

**【発明の詳細な説明】****【技術分野】****【0001】**

本発明の実施形態は、半導体装置とそれを用いた携帯通信機器に関する。

**【背景技術】****【0002】**

携帯電話に代表される携帯通信機器に用いられる半導体装置には、通信特性への悪影響を防止するために、外部への不要電磁波の漏洩を抑制することが求められている。このため、シールド機能を有する半導体パッケージが適用されている。シールド機能を有する半導体パッケージとしては、インターポーラ基板上に搭載された半導体チップを封止する封止樹脂層の外面に沿ってシールド層を設けた構造を有するものが知られている。

20

**【0003】**

インターポーラ基板の側面からの不要電磁波の漏洩を抑制するために、グランド配線に接続されたピアを外周側に配置したインターポーラ基板を用いた半導体パッケージが知られている。このような半導体パッケージにおいては、シールド層とインターポーラ基板のグランド配線との電気的および機械的な接続信頼性を高めることが求められている。さらに、半導体パッケージを大型化することなく、インターポーラ基板の側面からの不要電磁波の漏洩を抑制することが求められている。

**【先行技術文献】**

30

**【特許文献】****【0004】**

【特許文献 1】特開 2009 - 218484 号公報

**【発明の概要】****【発明が解決しようとする課題】****【0005】**

本発明が解決しようとする課題は、インターポーラ基板を含む半導体パッケージからの不要電磁波の漏洩を抑制すると共に、シールド層とインターポーラ基板のグランド配線との密着性を向上させることを可能にした半導体パッケージとそれを用いた携帯通信機器を提供することにある。

40

**【課題を解決するための手段】****【0006】**

実施形態の半導体装置は、第 1 の面と第 2 の面とを有する絶縁基材と、絶縁基材の第 1 の面に形成された第 1 の配線層と、絶縁基材の第 2 の面に形成された第 2 の配線層と、導体層とを備えるインターポーラ基板と、第 1 の面に設けられた外部接続端子と、第 2 の面上に搭載された半導体チップと、半導体チップを封止するように第 2 の面上に設けられた封止樹脂層と、封止樹脂層とインターポーラ基板の側面の少なくとも一部を覆う導電性シールド層とを具備している。導電性シールド層は識別マークを有している。識別マーク部分における導電性シールド層の厚さは 2  $\mu$ m 以上である。識別マーク部分における導電性シールド層の表面粗さは、識別マーク以外の部分における導電性シールド層の表面粗さよ

50

りも小さい。

【図面の簡単な説明】

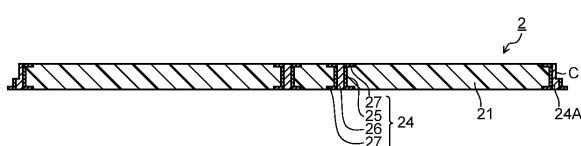

【0007】

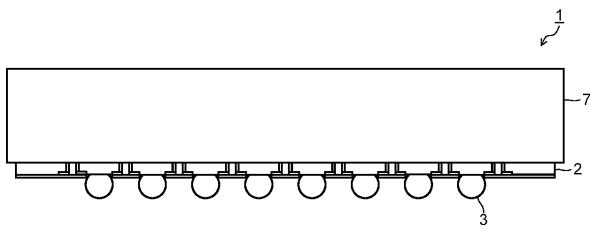

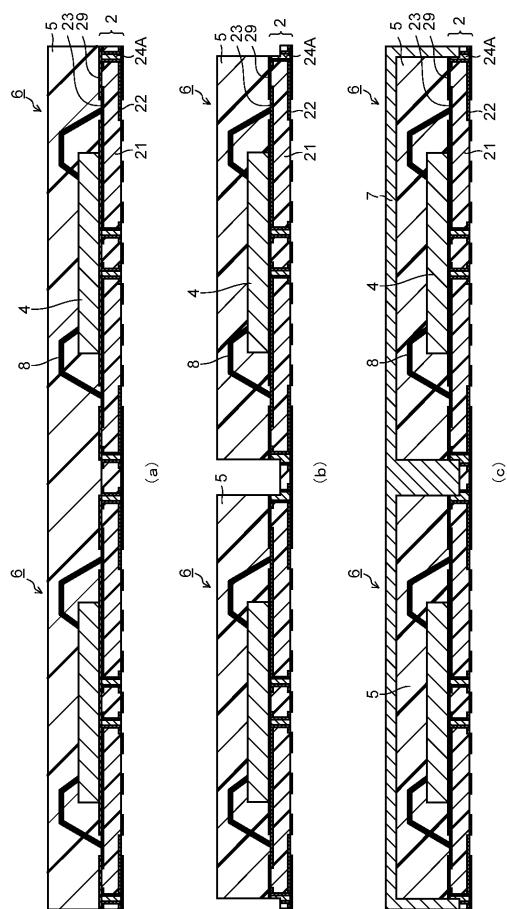

【図1】実施形態による半導体パッケージの構成を示す側面図である。

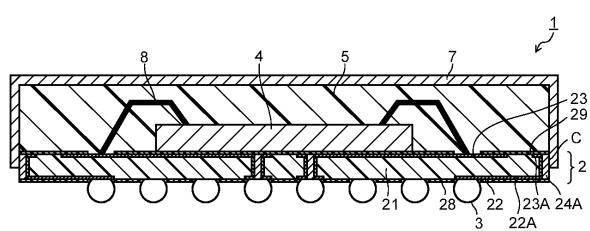

【図2】図1に示す半導体パッケージの断面図である。

【図3】図1に示す半導体パッケージにおける導電性シールド層の形成前の状態を示す側面図である。

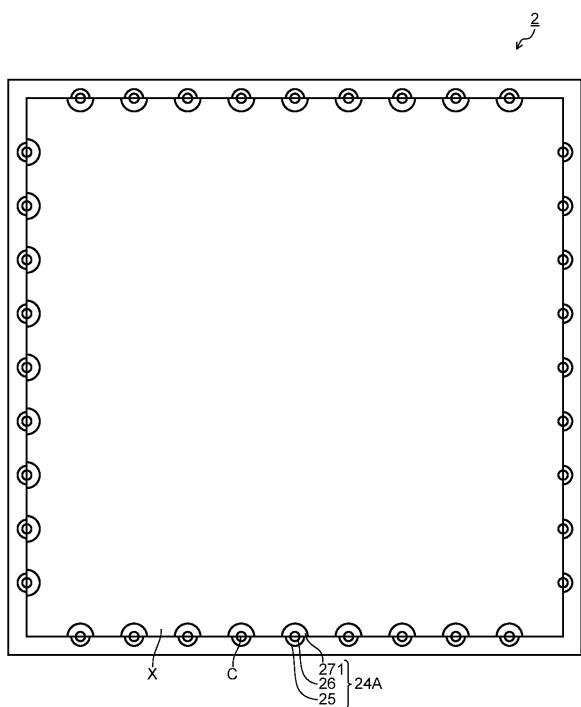

【図4】図1に示す半導体パッケージに使用するインターポーラ基板の一例を示す平面図である。

【図5】図4に示すインターポーラ基板の断面図である。

10

【図6】図1に示す半導体パッケージに使用するインターポーラ基板の他の例を示す平面図である。

【図7】実施形態による半導体パッケージの他の構成を示す側面図である。

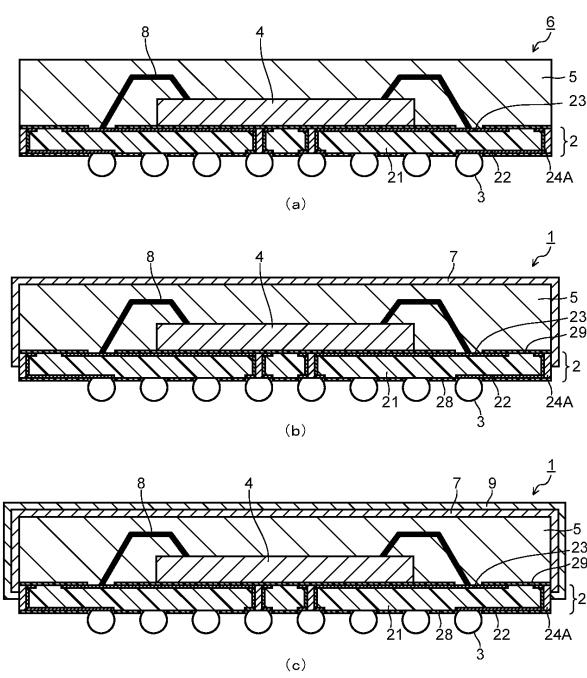

【図8】図7に示す半導体パッケージの断面図である。

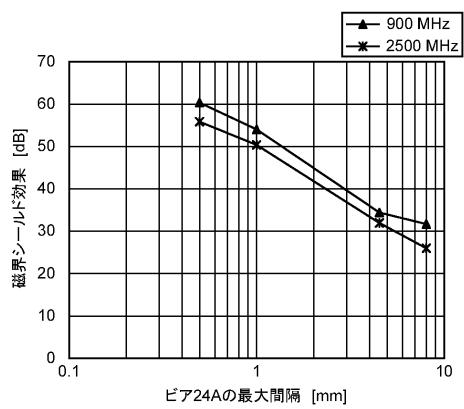

【図9】ビアの切断面の最大間隔と半導体パッケージの磁界シールド効果との関係を示す図である。

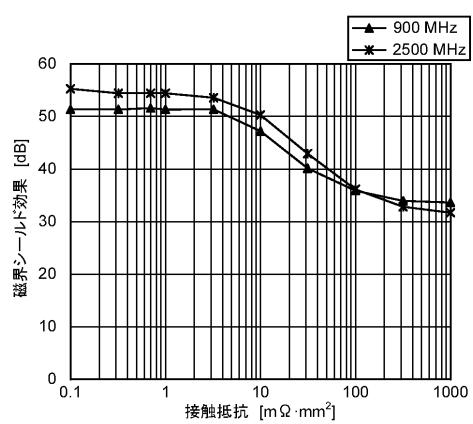

【図10】導電性シールド層とビアの切断面との接触抵抗と半導体パッケージの磁界シールド効果との関係を示す図である。

【図11】図7に示す半導体パッケージの製造工程を示す断面図である。

【図12】図1に示す半導体パッケージの製造工程における封止樹脂層の形成工程から導電性シールド層の形成工程までを示す断面図である。

20

【図13】図1に示す半導体パッケージの製造工程における外部接続端子の形成工程から切断工程までを示す断面図である。

【図14】図1に示す半導体パッケージを上面から見た図である。

【図15】図14に示す半導体パッケージの封止樹脂層および導電性シールド層の一部を拡大して示す断面図である。

【図16】導電性シールド層における識別マークの形成部分のシート抵抗率と半導体パッケージの磁界シールド効果との関係を示す図である。

【図17】実施形態による携帯電話の構成を示す斜視図である。

【発明を実施するための形態】

30

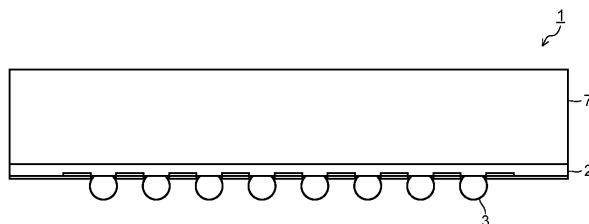

【0008】

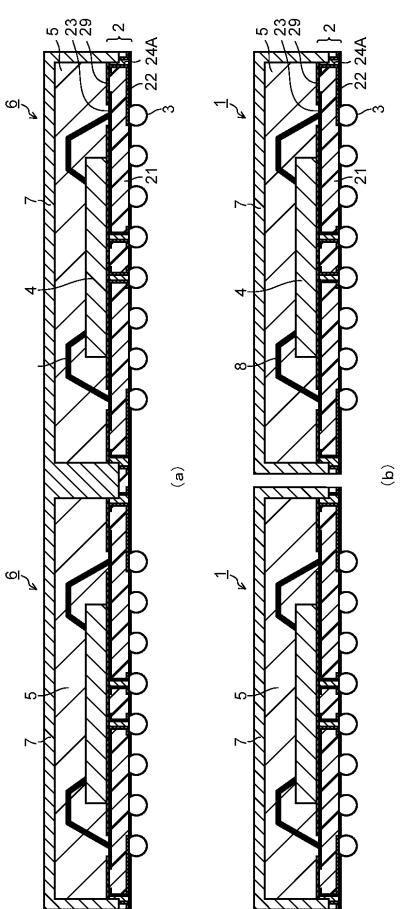

以下、実施形態の半導体パッケージについて、図面を参照して説明する。図1は第1の実施形態による半導体パッケージを示す側面図、図2は図1に示す半導体パッケージの断面図、図3は図1に示す半導体パッケージにおける導電性シールド層の形成前の状態を示す側面図、図4は図1に示す半導体パッケージに使用するインターポーラ基板の一例を示す平面図、図5は図4に示すインターポーラ基板の断面図である。

【0009】

これらの図に示す半導体パッケージ1は、インターポーラ基板2と、インターポーラ基板2の第1の面に外部接続端子として設けられた半田ボール3と、インターポーラ基板2の第2の面上に搭載された半導体チップ4と、半導体チップ4を封止する封止樹脂層5とを具備するFBGA(Fine pitch Ball Grid Array)6に、導電性シールド層7を形成したシールド機能付き半導体パッケージである。

40

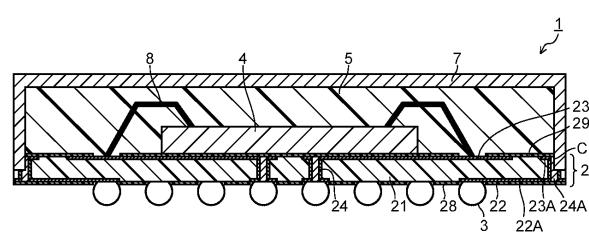

【0010】

インターポーラ基板2は、絶縁基材として絶縁基板21を有している。絶縁基板21の第1の面(下面)には第1の配線層22が設けられており、第2の面(上面)には第2の配線層23が設けられている。配線層22、23は単層構造の導体層に限らず、それぞれ2層以上の導体層からなるものであってもよい。インターポーラ基板2は、第1の配線層22と第2の配線層23とを電気的に接続するように、絶縁基板21を貫通して形成されたビア24を有している。配線層22、23やビア24は、銅箔や銀または銅を含む導電性ペーストからなり、必要に応じて表面にニッケルめっきや金めっき等が施されている。

50

## 【0011】

インターポーラ基板2のビア24は、図5に示すように、絶縁基板21を貫通する貫通孔の内面に形成された導体層25と、導体層25の内側の中空部に充填された穴埋め材26と、導体層25と配線層22、23とを電気的に接続するランド27、27とを有している。穴埋め材26は、例えば絶縁性樹脂や導電性樹脂からなる。穴埋め材26は、導電性シールド層7との密着性に優れる材料で形成することが好ましい。穴埋め材26を導電材料で形成した場合、導電性シールド層7との接触面積が増大するため、ビア24と導電性シールド層7との接触抵抗値の低下が見込める。ビア24は貫通孔内にめっき等により金属材料(銅等)を充填したものであってもよい。

## 【0012】

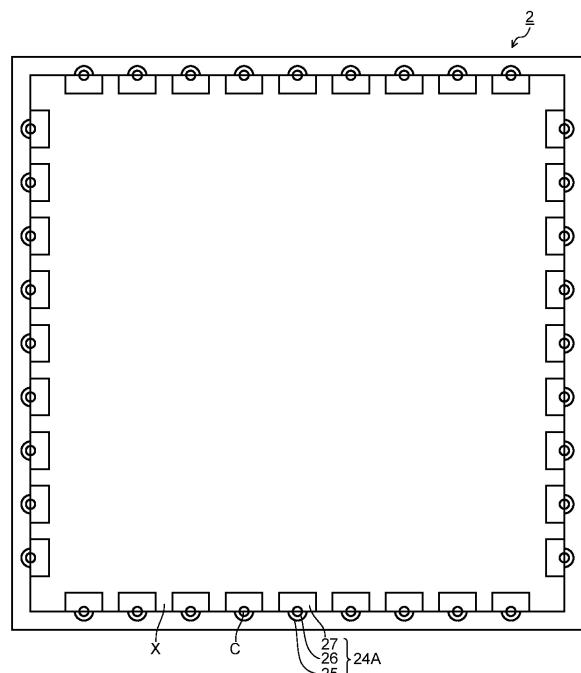

10

インターポーラ基板2の第1の面(第1の配線層22が設けられた面)には、半田ボール3が設けられている。半田ボール3は第1の配線層22と電気的に接続されている。インターポーラ基板2の第2の面(第2の配線層23が設けられた面)は、チップ搭載領域Xを有している。図4では図示を省略したが、チップ搭載領域Xにはチップ搭載部に加えて、第2の配線層23による信号配線やグランド配線等が設けられている。インターポーラ基板2は第1および第2の面に形成された半田レジスト層28、29を有している。

## 【0013】

20

インターポーラ基板2の第2の面上には、半導体チップ4が搭載されている。半導体チップ4の上面に設けられた電極パッド(図示せず)は、Auワイヤ等のポンディングワイヤ8を介してインターポーラ基板2の第2の配線層23と電気的に接続されている。さらに、インターポーラ基板2の第2の面には、半導体チップ4をポンディングワイヤ8等と共に封止する封止樹脂層5が形成されている。封止樹脂層5とインターポーラ基板2の側面の少なくとも一部は、導電性シールド層7で覆われている。

## 【0014】

導電性シールド層7は、封止樹脂層5内の半導体チップ4やインターポーラ基板2の配線層22、23から放射される不要電磁波の漏洩を防止する上で、抵抗率が低い金属層で形成することが好ましく、例えば銅、銀、ニッケル等からなる金属層が適用される。導電性シールド層7の厚さは、その抵抗率に基づいて設定することが好ましい。例えば、導電性シールド層7の抵抗率を厚さで割ったシート抵抗値が0.5以下となるように、導電性シールド層7の厚さを設定することが好ましい。導電性シールド層7のシート抵抗値を0.5以下とすることによって、封止樹脂層5からの不要電磁波の漏洩を再現性よく抑制することができる。

30

## 【0015】

半導体チップ4等から放射される不要電磁波は、封止樹脂層5を覆う導電性シールド層7により遮断されるため、外部への漏洩が防止される。不要電磁波はインターポーラ基板2の側面からも漏洩するおそれがある。そこで、この実施形態の半導体パッケージ1では、図2ないし図5に示すように、インターポーラ基板2の外周部にビア24の一部、すなわちグランド配線22A、23Aと接続されたビア24Aを配置している。ビア24Aはインターポーラ基板2の厚さ方向に切断された切断面Cを有し、この切断面Cがインターポーラ基板2の側面に露出するように配置されている。

40

## 【0016】

第1および第2の配線層22、23は、グランド配線22A、23Aを有している。グランド配線22A、23Aは、インターポーラ基板2の側面に露出するように外周部に配置されている。さらに、インターポーラ基板2の外周部には、グランド配線22A、23Aと接続されたビア24Aが配置されている。ビア24Aはインターポーラ基板2の厚さ方向に切断された切断面Cを有し、かつ切断面Cをインターポーラ基板2の側面に露出させるように配置されている。導電性シールド層7はインターポーラ基板2の側面の一部を覆うように形成されているため、導電性シールド層7はグランド配線23Aと電気的に接続されており、さらにビア24Aの切断面Cと電気的に接続されている。

## 【0017】

50

導電性シールド層 7 とビア 24 A とは、ビア 24 A の切断面 C を介して電気的に接続されているため、導電性シールド層 7 とビア 24 A との接続状態を高めることができる。具体的には、導電性シールド層 7 とビア 24 A との接触抵抗を低下させることができる。導電性シールド層 7 とビア 24 A の切断面 C との接続状態は、直接接続された状態（直流接続）に限らず、薄い絶縁体を介して高周波的に電気接続されていてもよい。

#### 【0018】

ビア 24 A の切断面 C は、導体層 25 の切断面と穴埋め材 26 の切断面を含んでいることが好ましい。図 4 および図 5 はビア 24 A の中心を通るように切断した状態を示している。これによって、導電性シールド層 7 とビア 24 A の切断面 C との接触面積が増大するため、導電性シールド層 7 とビア 24 A との接続状態をより一層向上させることができる。ただし、ビア 24 A の切断面 C は必ずしもビア 24 A の中心を通らなくてもよく、切断面 C にビア 24 A の一部が含まれていればよい。

10

#### 【0019】

ビア 24 A を切断するにあたって、ランド 27 の形状は図 4 に示すように矩形であることが好ましい。切断されたビア 24 A のランド 27 の形状は、図 4 に示すような長方形と図 6 に示すような半円形とが考えられる。図 4 に示す長方形のランド 27 は、例えば正方形のランドを切断したものである。図 6 に示す半円形のランド 27 は、例えば円形のランドを切断したものである。図 6 に示すように円形のランドを切断する場合、ダイシングラインの位置のばらつきの影響で、ランド 27 1 の断面露出面積がばらつきやすい。これに対して、図 4 に示す長方形のランド 27 は、ダイシングラインの位置がばらついた場合においても断面露出面積を一定にすることができる。

20

#### 【0020】

さらに、ビア 24 A を切断するにあたって、インターポーラ基板 2 の四隅にはビア 24 A を配置しないことが好ましい。四隅に配置されたビア 24 A は、ダイシング工程で 2 回切断されることになるため、銅箔のインターポーラ基板 2 からの分離等が生じやすい。このため、インターポーラ基板 2 の四隅にはビア 24 A を配置しないことが好ましい。ただし、ダイシング工程で銅箔の分離等によるビア 24 A の損傷や破壊が生じるおそれがない場合には、インターポーラ基板 2 の四隅にも切断されるビア 24 A を配置してもよい。

#### 【0021】

図 2 ないし図 5 に示すビア 24 A は、その厚さ方向（ビア 24 の貫通方向）の一部を、インターポーラ基板 2 の厚さ方向に切断した切断面 C を有している。ビア 24 A の切断面 C は、インターポーラ基板 2 の第 2 の面側からビア 24 A の厚さ方向の一部を切断した形状を有している。ビア 24 A のインターポーラ基板 2 の第 1 の面側の端部およびその近傍部分は、絶縁基板 21 によって覆われている。導電性シールド層 7 は、ビア 24 A の厚さ方向の一部を切断した切断面 C とビア 24 A の一部を切断することにより生じる段面とを覆うように形成されている。これによって、導電性シールド層 7 による F B G A 6 の被覆性や導電性シールド層 7 とビア 24 A の切断面 C との接続性を高めることができる。

30

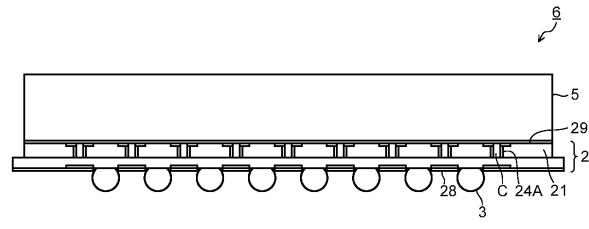

#### 【0022】

図 7 および図 8 に示すように、ビア 24 A はその厚さ方向（ビア 24 の貫通方向）の全体を、インターポーラ基板 2 の厚さ方向に切断した切断面 C を有してもよい。図 7 および図 8 に示すビア 24 A の切断面 C は、ビア 24 A の厚さ方向の全体を切断した形状を有している。導電性シールド層 7 は、ビア 24 A の切断面 C の厚さ方向の一部をインターポーラ基板 2 の第 2 の面側から覆うように形成されている。切断面 C の導電性シールド層 7 で覆われていない部分は、インターポーラ基板 2 の側面に露出している。導電性シールド層 7 は切断面 C 全体を覆うように形成されていてもよい。この場合、導電性シールド層 7 は第 1 の配線層 22 におけるグランド配線 22 A と電気的に接続されていてもよい。

40

#### 【0023】

図 7 および図 8 に示す半導体パッケージ 1 は、ビア 24 A 全体を切断しているため、半導体パッケージ 1 の面積の増大を抑制することができる。例えば、切断していないビアを外周部に配置したインターポーラ基板を用いた場合、ビアを外周部に配置していないイン

50

ターポーザ基板に比べて、半導体パッケージの一辺の長さがビアのランドの幅の2倍以上増加する。これに対して、中心で切断したビア24Aを外周に配置したインターポーザ基板2を用いた場合、半導体パッケージ1の一辺の長さの増加量はビア24のランドの幅程度に抑制される。ビア24のランドの幅が0.2mmの場合、切断しないビアを配置するとパッケージの一辺の長さが0.4mm以上増加するのに対し、切断したビアを配置すればパッケージの一辺の長さの増加量は0.2mm程度に抑制することができる。

#### 【0024】

導電性シールド層7と電気的に接続された切断面Cを有するビア24Aは、インターポーザ基板2の側面からの電磁波の漏洩を抑制する効果を有する。ビア24Aはインターポーザ基板2を貫通していると共に、切断面Cで導電性シールド層7と電気的に接続されているため、インターポーザ基板2の側面全体からの電磁波の漏洩を効果的に抑制することができる。例えば、インターポーザ基板2の外周部にグランド配線に接続されたビアが配置されていたとしても、そのビアがインターポーザ基板2の厚さ方向の一部のみに設けられていた場合、厚さ方向にビアが存在しない部分から電磁波が漏洩する。これに対して、インターポーザ基板2を貫通するビア24Aを配置することによって、ビア24Aがインターポーザ基板2の側面全体に対してシールド効果を発揮するため、インターポーザ基板2の側面からの電磁波の漏洩を効果的に抑制することができる。

10

#### 【0025】

インターポーザ基板2の側面からの電磁波の漏洩を抑制する上で、インターポーザ基板2の一辺当たりの側面に複数のビア24Aの切断面Cを露出させることが好ましい。さらに、インターポーザ基板2の側面に露出するビア24Aの切断面Cの間隔が狭いほど電磁波の漏洩抑制効果（磁界シールド効果）が向上する。ビア24Aの切断面Cの最大間隔は4mm以下とすることが好ましい。ビア24Aの配置間隔は等間隔に限定されるものではない。ビア24Aの配置間隔は一定でなくてもよい。そのような場合であっても、切断面Cの最大間隔が4mm以下となるように、ビア24Aを配置することが好ましい。

20

#### 【0026】

図9にインターポーザ基板2の側面におけるビア24Aの切断面Cの最大間隔と磁界シールド効果との関係を示す。図9は900MHz、2500MHzのそれぞれ周波数における磁界シールド効果を測定した結果である。測定サンプルは、一辺の長さが8.15mm、高さ（半田ボールを含む）が1.06mmの半導体パッケージとした。ノイズは外部から半田ボールに給電し、半田ボールからインターポーザ基板の信号配線とビアを伝わって基板に伝搬させて終端させた。導電性シールド層、露出したビア、グランド配線、半田ボールのグランドピンは電気的に接続させた。

30

#### 【0027】

磁界強度は、パッケージ中央部直上の封止樹脂層から1mmの距離（基準面）で走査して測定した。磁界シールド効果は、シールド層がある場合とない場合の基準面での磁界強度の差分から求めた。導電性シールド層の厚さは、パッケージ上面で50μm、側面で70μmとした。導電性シールド層の抵抗率は30μcm程度である。このようにして測定した磁界シールド効果を図9に示す。図9はビア24Aの切断面Cの最大間隔を変化させた場合の磁界シールド効果を示している。

40

#### 【0028】

図9に示すように、ビア24Aの切断面Cの最大間隔の対数と磁界シールド効果とは線形の関係を有している。ビア24Aの切断面Cの最大間隔が広い場合には、磁界シールド効果が低下することが分かる。磁界シールド効果を高める上で、ビア24Aの切断面Cの最大間隔は狭いことが好ましい。携帯機器で使用される半導体パッケージ1においては、900MHzでの磁界シールド効果を34dB以上とすることが求められる。このため、切断面Cの最大間隔は4mm以下とすることが好ましい。ビア24Aの切断面Cの間隔を狭くした方が効果が高いが、ビア24Aの間隔は構造上の制約を受けるため、その間隔は0.2mm以上となる。

#### 【0029】

50

さらに、導電性シールド層7による磁界シールド効果を高める上で、導電性シールド層7とインターポーラ基板2のグランド配線とを低抵抗に接触させることが好ましい。具体的には、導電性シールド層7とグランド配線23Aやビア24Aの切断面Cとの接触抵抗を低下させることが好ましい。図10に導電性シールド層7とビア24Aの切断面Cとの接触抵抗と導電性シールド層7による磁界シールド効果とを関係を電磁界シミュレーションにより求めた結果を示す。

#### 【0030】

電磁界シミュレーションによる解析は、一辺の長さが8.1mm、高さ（半田ボールを含む）が1.06mmの半導体パッケージについて行った。半導体パッケージの具体的な形状は、インターポーラ基板2の高さが0.1mm、ビア24Aの直径が0.08mm、ビア24Aのランド27の幅が0.2mm、第1および第2の配線層22、23の厚さが18μmとした。ビア24Aは貫通孔内に銅を充填したものとした。導電性シールド層7がビア24Aの切断面Cの上半分と接触しているとすると、ビア24Aの1個あたりの接触面積は0.0076mm<sup>2</sup>となる。ビアの24Aは1mmピッチで等間隔に配置し、インターポーラ基板2の四隅にも配置した。ビア24Aの個数は33個である。

10

#### 【0031】

ノイズは外部から半田ボールに給電し、半田ボールからインターポーラ基板の信号配線とビアを伝わって基板に伝搬させて終端させた。導電性シールド層、露出したビア、グランド配線、半田ボールのグランドピンは電気的に接続させた。磁界強度は、パッケージ中央部直上の封止樹脂層から1mmの位置（基準面）で算出した。磁界シールド効果は、シールド層がある場合とない場合の基準面での磁界強度の最大値の差分から求めた。導電性シールド層の厚さは、パッケージ上面および側面共に50μmとした。導電性シールド層の抵抗率は30μcmである。このようにして実施した電磁界シミュレーションの結果を図10に示す。

20

#### 【0032】

図10に示すように、導電性シールド層7とビア24Aの切断面Cとの接触抵抗が低いほうが磁界シールド効果は高くなる。携帯機器で使用される半導体パッケージ1においては、900MHzでの磁界シールド効果を34dB以上とすることが求められる。このため、導電性シールド層7とビア24Aの切断面Cとの接触面積抵抗率は300m<sup>2</sup>以下とすることが好ましい。ビア24A1個あたりの接触面積は0.0076mm<sup>2</sup>であるため、1個のビア24Aの切断面Cと導電性シールド層7との接触界面の抵抗値は39

30

以下とすることが好ましい。すなわち、導電性シールド層7はビア24Aの切断面Cとの接触抵抗が300m<sup>2</sup>以下となる導電材料、もしくは1個のビア24Aの切断面Cとの接触界面の抵抗値が39以下となる導電材料で形成することが好ましい。

#### 【0033】

この実施形態の半導体パッケージ1は、例えば以下のようにして作製される。まず、図11(a)に示すように、従来の製作工程を適用してFBGA6を作製する。FBGA6はダイシングにより個片化される。FBGA6を個片化するにあたって、インターポーラ基板2の側面にビア24Aの切断面Cが露出するようにダイシングする。次いで、封止樹脂層5をキュアした後、図11(b)に示すように導電性シールド層7を形成する。図11は図7および図8に示した半導体パッケージ1の製造工程を示している。

40

#### 【0034】

導電性シールド層7は、例えば転写法、スクリーン印刷法、スプレー塗布法、ジェットディスペンス法、インクジェット法、エアロゾル法等で導電性ペーストを塗布することにより形成される。導電性ペーストは、例えば銀や銅と樹脂とを主成分として含むものであり、抵抗率が低いものが望ましい。また、無電解めっき法や電解めっき法で銅やニッケル等を成膜する方法、スパッタ法により銅等を成膜する方法を適用して、導電性シールド層7を形成してもよい。導電性シールド層7は封止樹脂層5およびインターポーラ基板2の側面の少なくとも一部を覆うように形成される。

#### 【0035】

50

図11(c)に示すように、必要に応じて耐食性や耐マイグレーション性に優れる保護層9で導電性シールド層7を覆ってもよい。保護層9としては、ポリイミド樹脂等が用いられる。この後、導電性シールド層7や保護層9を焼成して硬化させることによって、半導体パッケージ1が作製される。半導体パッケージ1は必要に応じて印字される。印字はレーザによる印字や転写法等により実施される。

#### 【0036】

この実施形態の半導体パッケージ1は、図12および図13に示すように、個片化前にハーフダイシングし、次いで導電性シールド層7を形成した後に、個片化のためのダイシングを行って作製することも可能である。図12および図13は図1ないし図3に示した半導体パッケージ1の製造工程を示している。

10

#### 【0037】

まず、図12(a)に示すように、従来の製作工程を適用して複数のFBGA6を封止樹脂層5で一括封止したものを作製する。次いで、図12(b)に示すように、封止樹脂層5とインターポーラ基板2の一部を切断するようにハーフダイシングする。ハーフダイシングはインターポーラ基板2の外周部に配置されたビア24Aの厚さ方向の一部を切断するように実施される。ビア24Aの切断面Cはハーフダイシングにより形成される。

#### 【0038】

ハーフダイシングを実施するにあたって、インターポーラ基板2の四隅にビア24Aを配置すると、インターポーラ基板2からビア24Aが分離する場合がある。これを回避するためには、インターポーラ基板2の四隅にビア24Aを配置しないことが好ましい。インターポーラ基板2から分離した場合には、再度ダイシングブレードをハーフダイシングした部分と同一位置に通すことによって、分離したビア24Aを取り除くことができる。これによって、ビア24Aの分離による不良発生を抑制することができる。

20

#### 【0039】

次に、図12(c)に示すように、複数のFBGA6を覆うように導電性シールド層7を形成する。導電性シールド層7はハーフダイシングにより形成されたダンシング溝内に充填するように形成される。図13(a)に示すように、半田ボール3を一括して搭載した後、図13(b)に示すように個片化のためのダイシングを行って半導体パッケージ1を作製する。個片化のためのダイシングは、ダンシング溝内に充填された導電性シールド層7とインターポーラ基板2の残部を切断するように実施される。図11(c)に示したように、保護層9を適用する場合には、ダイシング工程前または工程後に導電性シールド層7上に保護層9を形成する。半導体パッケージ1は必要に応じて印字される。

30

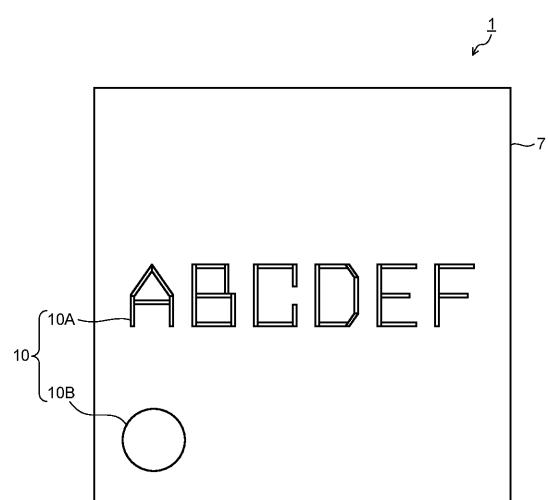

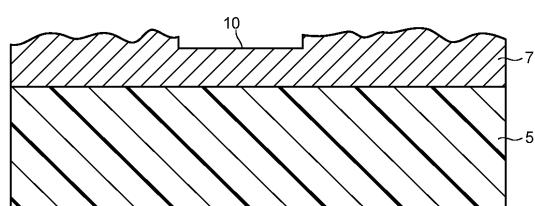

#### 【0040】

図14に示すように、半導体パッケージ1の導電性シールド層7の表面に文字10A、記号10B、図形等の識別マーク10を形成する場合、導電性シールド層7を厚さ方向に全て削り、封止樹脂層5が露出してしまうと、電磁ノイズが識別マーク10の形成部分から漏洩するおそれがある。このため、識別マーク10は導電性シールド層7を厚さ方向の一部のみを削ることにより形成することが好ましい。識別マーク10は、導電性シールド層7を削らないインクを転写する方法により形成してもよい。

40

#### 【0041】

識別マーク10の形成方法としては、導電性シールド層7をあまり削らないようにレーザ出力を調節したレーザマーキングが挙げられる。導電性シールド層7にレーザマーキングを行う場合、図15に示すように、レーザの出力を調節して識別マーク10の形成部分の表面粗さを、導電性シールド層7の他の部分のそれと変えることが好ましい。例えば、識別マーク10の形成部分の表面粗さを、導電性シールド層7の他の部分のそれより小さくする。これによって、導電性シールド層7を大きく削ることなく、識別マーク10を視認性よく形成することができる。

#### 【0042】

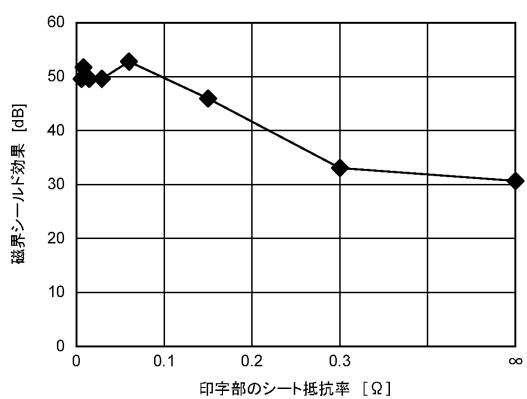

図16および表1に導電性シールド層7における識別マーク10の形成部分のシート抵

50

抗値と磁界シールド効果との関係を電磁界シミュレーションにより求めた結果を示す。電磁界シミュレーションによる解析は、一辺の長さが 8 . 1 mm、高さ（半田ボールを含む）が 1 . 0 6 mm の半導体パッケージについて行った。半導体パッケージの具体的な形状は、インターポーラ基板 2 の高さが 0 . 1 mm、ピア 2 4 A の直径が 0 . 0 8 mm、ピア 2 4 A のランド 2 7 の幅が 0 . 2 mm、第 1 および第 2 の配線層 2 2、2 3 の厚さが 1 8  $\mu$ m とした。ピア 2 4 A は貫通孔内に銅を充填したものとした。導電性シールド 7 がピア 2 4 A の切断面 C の上半分と接触しているとすると、ピア 2 4 A の 1 個あたりの接触面積は 0 . 0 0 7 6 mm<sup>2</sup> となる。ピアの 2 4 A は 1 mm ピッチで等間隔に配置し、インター ポーラ基板 2 の四隅にも配置した。ピア 2 4 A の個数は 3 3 個である。

## 【 0 0 4 3 】

10

ノイズは外部から半田ボールに給電し、半田ボールからインター ポーラ基板の信号配線とピアを伝わって基板に伝搬させて終端させた。導電性シールド層、露出したピア、グランド配線、半田ボールのグランドピンは電気的に接続させた。解析周波数は 9 0 0 M H z とした。磁界強度は、パッケージ中央部直上の封止樹脂層から 1 mm の位置（基準面）で算出した。磁界シールド効果は、シールド層がある場合とない場合の基準面での磁界強度の最大値の差分から求めた。導電性シールド層の厚さはパッケージ上面および側面共に 5 0  $\mu$ m とした。導電性シールド層の抵抗率は 3 0  $\mu$  c m であり、導電性シールド層のシート抵抗値は 0 . 0 0 6 である。

## 【 0 0 4 4 】

20

導電性シールド層 7 には、図 1 4 に示すような識別マーク 1 0 を形成した。文字 1 0 A の太さは 0 . 0 8 mm であり、文字 1 0 A の大きさは縦 1 mm、横 0 . 7 mm とした。パッケージの方向を示すマーク 1 0 B は、直径を 1 mm の円形とした。図 1 4 に示すような識別マーク 1 0 を、導電性シールド層 7 を切削することにより形成した。識別マーク 1 0 の形成部分における導電性シールド層 7 の厚さを 0  $\mu$ m から 5 0  $\mu$ m まで変化させ、磁界シールド効果との関係を解析した。導電性シールド層 7 の厚さが 0  $\mu$ m とき、マーク形成部分の導電性シールド層 7 は完全に削られて無くなっている状態であり、その場合のシート抵抗値は無限大である。導電性シールド層 7 の厚さが 5 0  $\mu$ m とき、マーク形成部分の導電性シールド層 7 は切削されておらず、その場合のシート抵抗値は 0 . 0 0 6 である。

## 【 0 0 4 5 】

## 【表 1】

30

|                               |       |        |       |      |      |      |     |          |

|-------------------------------|-------|--------|-------|------|------|------|-----|----------|

| 印字部のシールド層の厚さ [ $\mu$ m]       | 50    | 40     | 20    | 10   | 5    | 2    | 1   | 0        |

| 印字部のシールド層のシート抵抗率 [ $\Omega$ ] | 0.006 | 0.0075 | 0.015 | 0.03 | 0.06 | 0.15 | 0.3 | $\infty$ |

| 磁界シールド効果 [dB]                 | 50    | 52     | 50    | 50   | 53   | 46   | 33  | 31       |

## 【 0 0 4 6 】

40

図 1 6 および表 1 に示すように、導電性シールド層 7 における識別マーク 1 0 の形成部分のシート抵抗値が低いほうが、磁界シールド効果が高くなる。携帯機器で使用される半導体パッケージ 1 においては、9 0 0 M H z での磁界シールド効果を 3 4 d B 以上とすることが求められる。このため、導電性シールド層 7 における識別マーク 1 0 の形成部分のシート抵抗値は 0 . 2 8 以下とすることが好ましい。

## 【 0 0 4 7 】

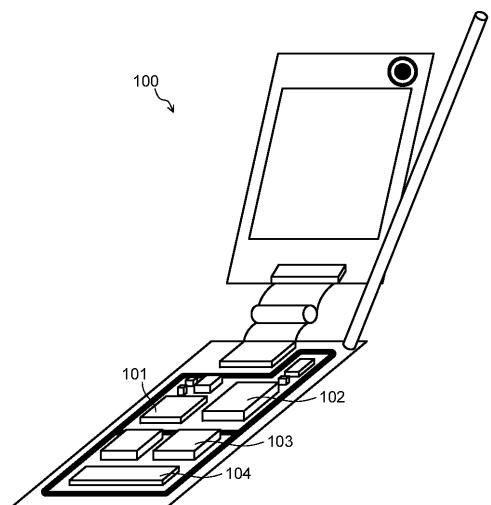

上述した実施形態の半導体パッケージ 1 は、携帯電話や携帯情報端末等の携帯通信機器に好適である。図 1 7 は実施形態による携帯電話を示している。図 1 7 に示す携帯電話 1 0 0 は、C P U パッケージ 1 0 1 、メモリチップパッケージ 1 0 2 、音源チップパッケージ 1 0 3 、電源チップパッケージ 1 0 4 等を有している。これら I C パッケージ 1 0 1 、1 0 2 、1 0 3 、1 0 4 はいずれもノイズ源となる。このような I C パッケージ 1 0 1 、

50

102、103、104に実施形態の半導体パッケージ1を適用することによって、携帯電話100の通信時におけるノイズを抑制することができる。

【0048】

なお、本発明のいくつかの実施形態を説明したが、これらの実施形態は例として提示したものであり、発明の範囲を限定することは意図していない。これら新規な実施形態は、その他の様々な形態で実施し得るものであり、発明の要旨を逸脱しない範囲で、種々の省略、置き換え、変更を行うことができる。これら実施形態やその変形は、発明の範囲や要旨に含まれると共に、特許請求の範囲に記載された発明とその均等の範囲に含まれる。

【符号の説明】

【0049】

1…半導体パッケージ、2…インターポーヴ基板、3…半田ボール、4…半導体チップ、5…封止樹脂層、6…F B G A、7…導電性シールド層、8…ボンディングワイヤ、21…絶縁基板、22…第1の配線層、22A…グランド配線、23…第2の配線層、23A…グランド配線、24…ビア、24A…切断面を有するビア、25…導体層、26…穴埋め材、27、271…ランド、28、29…半田レジスト層。

10

【図1】

【図4】

【図2】

【図3】

【図5】

【図6】

【図7】

【図8】

【図9】

【図11】

【図10】

【図12】

【図13】

【図14】

【図16】

【図15】

【図17】

---

フロントページの続き

(72)発明者 小塩 康弘

東京都港区芝浦一丁目1番1号 株式会社東芝内

審査官 太田 龍一

(56)参考文献 特開2009-218484 (JP, A)

特開平09-223761 (JP, A)

特開平10-284873 (JP, A)

特開2004-297554 (JP, A)

特開2002-353349 (JP, A)

特開2011-124413 (JP, A)

特開2010-114291 (JP, A)

(58)調査した分野(Int.Cl., DB名)

H01L 23/28

H01L 23/00

H01L 23/12