(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第6398776号

(P6398776)

(45) 発行日 平成30年10月3日(2018.10.3)

(24) 登録日 平成30年9月14日(2018.9.14)

(51) Int.Cl.

A 63 F 5/04 (2006.01)

F 1

A 63 F 5/04 512 Z

請求項の数 1 (全 108 頁)

(21) 出願番号 特願2015-29028 (P2015-29028)

(22) 出願日 平成27年2月17日 (2015.2.17)

(65) 公開番号 特開2016-150113 (P2016-150113A)

(43) 公開日 平成28年8月22日 (2016.8.22)

審査請求日 平成29年3月27日 (2017.3.27)

(73) 特許権者 390031783

サミー株式会社

東京都品川区西品川一丁目1番1号住友不動産大崎ガーデンタワー

(74) 代理人 100105315

弁理士 伊藤 温

(72) 発明者 坪田 亮一

東京都豊島区東池袋三丁目1番1号サンシャイン60 サミー株式会社内

(72) 発明者 松田 健二

東京都豊島区東池袋三丁目1番1号サンシャイン60 サミー株式会社内

(72) 発明者 小幡 直輝

東京都豊島区東池袋三丁目1番1号サンシャイン60 サミー株式会社内

最終頁に続く

(54) 【発明の名称】遊技機

## (57) 【特許請求の範囲】

## 【請求項 1】

複数のリールと、

スタートスイッチと、

複数のストップスイッチと、

遊技の進行を制御する主遊技制御手段と

を備えた遊技機であって、

主遊技制御手段は、

前記スタートスイッチが操作されたことに基づき役抽選を行う役抽選手段

を備え、

前記役抽選手段により決定された当選役に関する情報を、所定のRAM領域にて記憶するよう構成されており、

当選役に関する情報として、所定種類の当選役に関する第一の情報と、当該所定種類の当選役とは異なる特定種類の当選役に関する第二の情報を有し、前記所定のRAM領域における第一の記憶領域にて第一の情報を記憶可能とし、前記所定のRAM領域における第二の記憶領域にて第二の情報を記憶可能に構成されており、

前記所定のRAM領域における第三の記憶領域にて、所定の最小遊技時間を計時するための値を記憶可能に構成されており、

第三の記憶領域の値が0であって、規定数の遊技媒体が賭けられた状況下で前記スタートスイッチが操作された場合には、前記所定の最小遊技時間を計時するための値として特

定値を第三の記憶領域に記憶した後に、前記所定のRAM領域における第四の記憶領域に所定値を記憶可能とし、

第三の記憶領域の値が0より大きい値であって、規定数の遊技媒体が賭けられた状況下で前記スタートスイッチが操作された場合には、第三の記憶領域の値が0となった後、前記所定の最小遊技時間を計時するための値として前記特定値を第三の記憶領域に記憶した後に、前記所定のRAM領域における第四の記憶領域に前記所定値を記憶可能とし、

第四の記憶領域に記憶されている値は、更新条件を満たしたときに更新可能に構成され

、第一の記憶領域に第一の情報が記憶され、第二の記憶領域に第二の情報が記憶されている状況下において、

10

第四の記憶領域の値が0でなく且つ第四の記憶領域の値が所定範囲内である場合には、第一の情報に対して第一のビット位置に1をセットした情報を出力するための処理を実行可能とし、

第四の記憶領域の値が0でなく且つ第四の記憶領域の値が前記所定範囲とは異なる特定範囲内である場合には、第二の情報に対して第二のビット位置に1をセットした情報を出力するための処理を実行可能とし、

第四の記憶領域の値が0である場合には、当該値に基づく情報を出力するための処理を実行可能とするよう構成されている

ことを特徴とする遊技機。

**【発明の詳細な説明】**

20

**【技術分野】**

**【0001】**

遊技機に関する。

**【背景技術】**

**【0002】**

回胴式遊技機（スロットマシン）は、所定数の遊技メダルを投入後に遊技開始指示装置（スタートレバー）が操作されたことを契機として、複数の図柄が外周上に配置された複数列の回胴（リール）が回転動作し、当該回転動作を停止させるための回胴停止装置（ストップボタン）を駆使して回胴を停止させた結果、有効ライン上に所定の図柄の組合せ（例えば「777」）が並んだ場合には、通常遊技状態よりも遊技者にとって利益状態の高い特別遊技状態（通常時よりも当選役の抽選確率が上昇する遊技状態）に移行するタイプのものが一般的である。ここで、スロットマシンにおいては、遊技の興趣性を高めるための演出用の画像等が、リールの回転動作及び停止動作とシンクロした形で、液晶等のディスプレイ上にて表示される場合があり、ストップボタン等を操作した際に、リール上に表示された図柄とディスプレイ上に表示された演出用の画像等とを見比べながら、遊技の結果を予測して楽しむよう構成されているものが多い。

30

**【0003】**

また、ぱちんこ遊技機は、始動口（スタートチャッカー）に遊技球が入球したことを契機として、7セグ等の表示部上で「特別図柄」と称される図柄が変動表示され、当該特別図柄が特定態様（例えば「7」）となった場合、通常遊技状態よりも遊技者にとって利益状態の高い特別遊技状態（通常時は閉状態にある大入賞口（アタッカー）が所定条件で開放する内容の遊技）に移行するタイプの、いわゆる「デジパチ」と呼ばれている機種（従来の「第一種遊技機」）が一般的である。ここで、遊技者の利益に直結する特別図柄の表示制御の負担を軽減するために、前記の「特別図柄」とは別に、遊技の興趣性を高めるための演出用の「装飾図柄」と称される図柄が、前記特別図柄の変動とシンクロした形で、前記表示部よりもサイズが大きい液晶等のディスプレイ上で変動表示される場合がある。そして、特別図柄の変動が開始されると装飾図柄もこれに合わせて変動を開始し、特別図柄が特定態様（例えば「7」）で停止した場合、装飾図柄もこれに合わせて所定態様（例えば「777」）で停止することとなる。そして、装飾図柄が所定態様で停止したことにより、特別遊技へ移行が確定したことを遊技者が明確に認識できるよう構成されているも

40

50

のが多い。

**【0004】**

このような仕組みはこの種の多くの遊技機で共通するのであるが、遊技機の動作制御等を司るプログラム容量は、不正プログラムの混入防止（遊技機メーカーが提供するプログラムの正当性保障）の観点からその容量上限が厳しく規制されていると共に、遊技性仕様を実装するためのプログラムの他にも、出玉試験（遊技者の射幸心を著しく煽るような社会的不適合機でないことを認定するための試験）のみに供される出玉試験用プログラムも数多く実装されている。

**【先行技術文献】**

**【特許文献】**

10

**【0005】**

**【特許文献1】特開2014-100410**

**【発明の概要】**

**【発明が解決しようとする課題】**

**【0006】**

しかしながら、現状では、出玉試験用プログラムが煩雑となっていることに起因して、出玉試験用プログラムの正当性を検証することが困難となっているという課題が存在する。

**【課題を解決するための手段】**

**【0007】**

20

本態様に係る遊技機は、

複数のリールと、

スタートスイッチと、

複数のストップスイッチと、

遊技の進行を制御する主遊技制御手段と

を備えた遊技機であって、

主遊技制御手段は、

前記スタートスイッチが操作されたことに基づき役抽選を行う役抽選手段

を備え、

前記役抽選手段により決定された当選役に関する情報を、所定のRAM領域にて記憶するよう構成されており、

当選役に関する情報として、所定種類の当選役に関する第一の情報と、当該所定種類の当選役とは異なる特定種類の当選役に関する第二の情報を有し、前記所定のRAM領域における第一の記憶領域にて第一の情報を記憶可能とし、前記所定のRAM領域における第二の記憶領域にて第二の情報を記憶可能に構成されており、

前記所定のRAM領域における第三の記憶領域にて、所定の最小遊技時間を計時するための値を記憶可能に構成されており、

第三の記憶領域の値が0であって、規定数の遊技媒体が賭けられた状況下で前記スタートスイッチが操作された場合には、前記所定の最小遊技時間を計時するための値として特定値を第三の記憶領域に記憶した後に、前記所定のRAM領域における第四の記憶領域に所定値を記憶可能とし、

第三の記憶領域の値が0より大きい値であって、規定数の遊技媒体が賭けられた状況下で前記スタートスイッチが操作された場合には、第三の記憶領域の値が0となった後、前記所定の最小遊技時間を計時するための値として前記特定値を第三の記憶領域に記憶した後に、前記所定のRAM領域における第四の記憶領域に前記所定値を記憶可能とし、

第四の記憶領域に記憶されている値は、更新条件を満たしたときに更新可能に構成され、

第一の記憶領域に第一の情報が記憶され、第二の記憶領域に第二の情報が記憶されている状況下において、

第四の記憶領域の値が0でなく且つ第四の記憶領域の値が所定範囲内である場合には、

40

50

第一の情報に対して第一のビット位置に1をセットした情報を出力するための処理を実行可能とし、

第四の記憶領域の値が0でなく且つ第四の記憶領域の値が前記所定範囲とは異なる特定範囲内である場合には、第二の情報に対して第二のビット位置に1をセットした情報を出力するための処理を実行可能とし、

第四の記憶領域の値が0である場合には、当該値に基づく情報を出力するための処理を実行可能とするよう構成されている

ことを特徴とする遊技機である。

<付記>

尚、本態様とは異なる別態様について以下に列記しておくが、これらには何ら限定されることなく実施することが可能である。 10

本別態様に係る遊技機は、

複数種類の図柄を表示したリール（例えば、左リールM 5 1、中リールM 5 2、右リールM 5 3）を複数有する複数のリール（例えば、リールM 5 0）と、

前記複数のリール（例えば、リールM 5 0）を回転させるときに遊技者が操作するスタートスイッチ（例えば、スタートレバーD 5 0）と、

前記リール（例えば、左リールM 5 1、中リールM 5 2、右リールM 5 3）と対応して設けられ前記リール（例えば、左リールM 5 1、中リールM 5 2、右リールM 5 3）を停止させるときに遊技者が操作する複数のストップスイッチ（例えば、停止ボタンD 4 0）と、 20

遊技の進行を制御する主遊技制御部（例えば、主制御基板M）とを備えた遊技機であって、

主遊技制御部（例えば、主制御基板M）は、

前記スタートスイッチ（例えば、スタートレバーD 5 0）が操作されたことに基づき役抽選を行う役抽選手段（例えば、C P U C 1 0 0が実行するステップ1 2 5 7の処理）と、

所定の最小遊技時間が経過するまでは、前記スタートスイッチ（例えば、スタートレバーD 5 0）が操作されても前記複数のリール（例えば、リールM 5 0）の回転開始を待機させる遊技進行規制手段（例えば、C P U C 1 0 0が実行するステップ3 2 0 4の処理）と 30

を備え、

前記役抽選により決定された当選役に関する情報となる条件装置情報を、所定のRAM領域にて記憶するよう構成されており、

条件装置情報として、所定種類の当選役に関する第一の条件装置情報と、当該所定種類の当選役とは異なる特定種類の当選役に関する第二の条件装置情報を有し、前記所定のRAM領域における第一の記憶領域にて第一の条件装置情報を記憶し、前記所定のRAM領域における第二の記憶領域にて第二の条件装置情報を記憶するよう構成されており、

所定の遊技終了後において前記スタートスイッチ（例えば、スタートレバーD 5 0）が操作され前記役抽選が行われた場合、前記所定の最小遊技時間が経過した後に条件装置情報出力タイマ（例えば、出力時間タイマM 8 0）に所定値をセットし、 40

前記条件装置情報出力タイマ（例えば、出力時間タイマM 8 0）の値が0でなく且つ前記条件装置情報出力タイマ（例えば、出力時間タイマM 8 0）の値が所定範囲内である場合には、条件装置情報として第一の記憶領域にて記憶されている第一の条件装置情報を読み出し、当該読み出した第一の条件装置情報における第一のビット位置にて1をセットして遊技機外へ出力し、

前記条件装置情報出力タイマ（例えば、出力時間タイマM 8 0）の値が0でなく且つ前記条件装置情報出力タイマ（例えば、出力時間タイマM 8 0）の値が前記所定範囲とは異なる特定範囲内である場合には、条件装置情報として第二の記憶領域にて記憶されている第二の条件装置情報を読み出し、当該読み出した第二の条件装置情報における第二のビット位置にて1をセットして遊技機外へ出力し、 50

前記条件装置情報出力タイマ（例えば、出力時間タイマM 8 0）の値が0である場合には、当該値に基づく情報を遊技機外へ出力するよう構成されていることを特徴とする遊技機である。

【発明の効果】

【0 0 0 8】

本態様に係る遊技機によれば、出玉試験用プログラムの正当性を検証することが容易となるという効果を奏する。

【図面の簡単な説明】

【0 0 0 9】

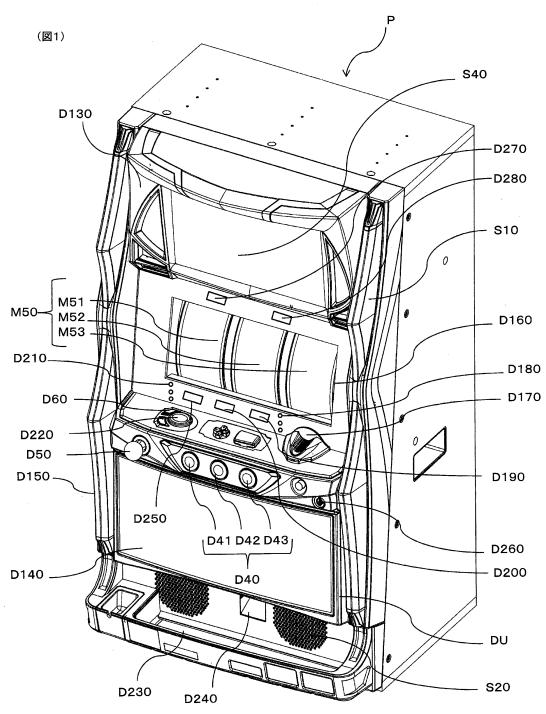

【図1】図1は、本実施形態に係る回胴式遊技機の斜視図である。

10

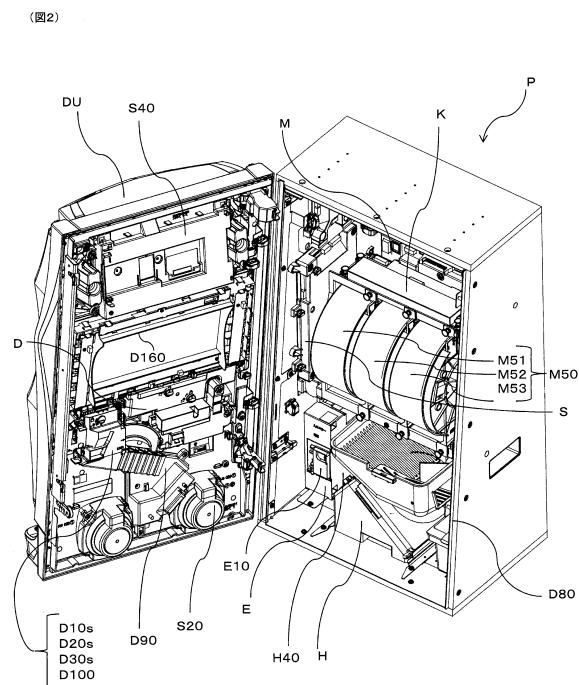

【図2】図2は、本実施形態に係る回胴式遊技機の扉を開いた状態の斜視図である。

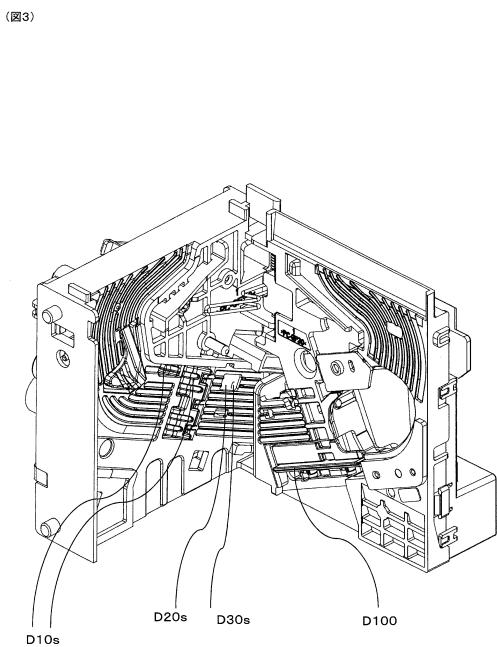

【図3】図3は、本実施形態に係る回胴式遊技機における、メダル投入口内部の斜視図である。

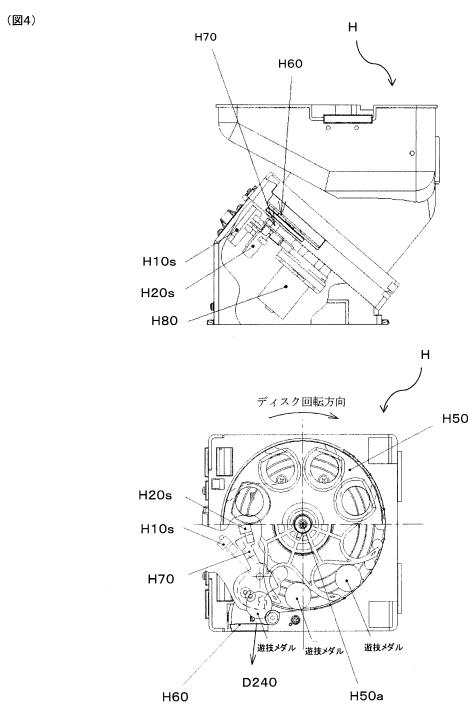

【図4】図4は、本実施形態に係る回胴式遊技機における、メダル払出手装置の正面図及び上面図である。

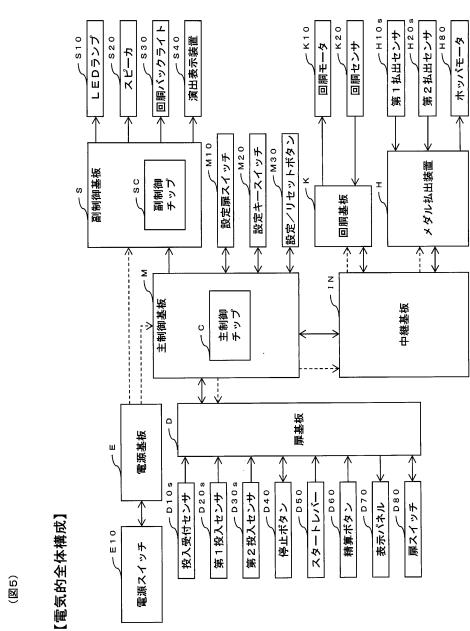

【図5】図5は、本実施形態に係る回胴式遊技機の電気的全体構成図である。

【図6】図6は、本実施形態に係る回胴式遊技機の主制御チップに係る電気的構成図である。

【図7】図7は、本実施形態に係る回胴式遊技機における、主制御チップのメモリマップ構成図である。

20

【図8】図8は、本実施形態に係る回胴式遊技機における、主制御基板側でのメインフローチャートである。

【図9】図9は、本実施形態に係る回胴式遊技機における、主制御基板側での設定変更装置制御処理のフローチャートである。

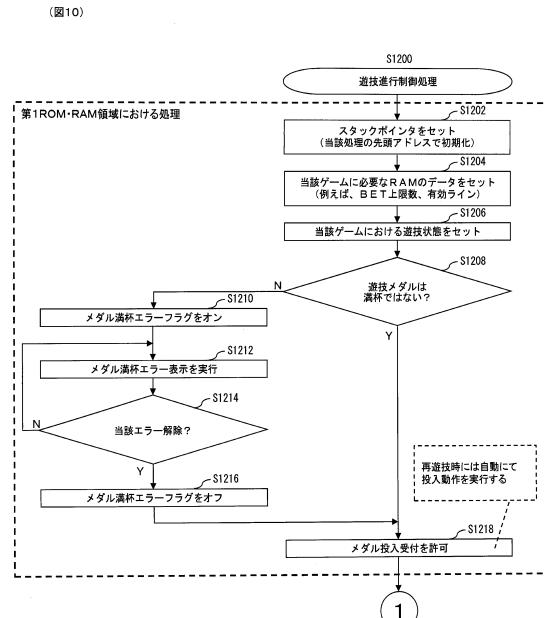

【図10】図10は、本実施形態に係る回胴式遊技機における、主制御基板側での遊技進行制御処理（1枚目）のフローチャートである。

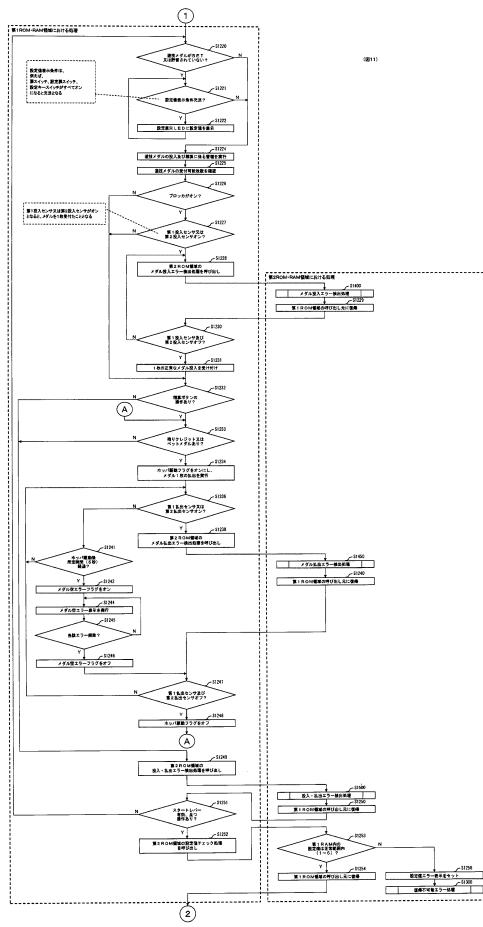

【図11】図11は、本実施形態に係る回胴式遊技機における、主制御基板側での遊技進行制御処理（2枚目）のフローチャートである。

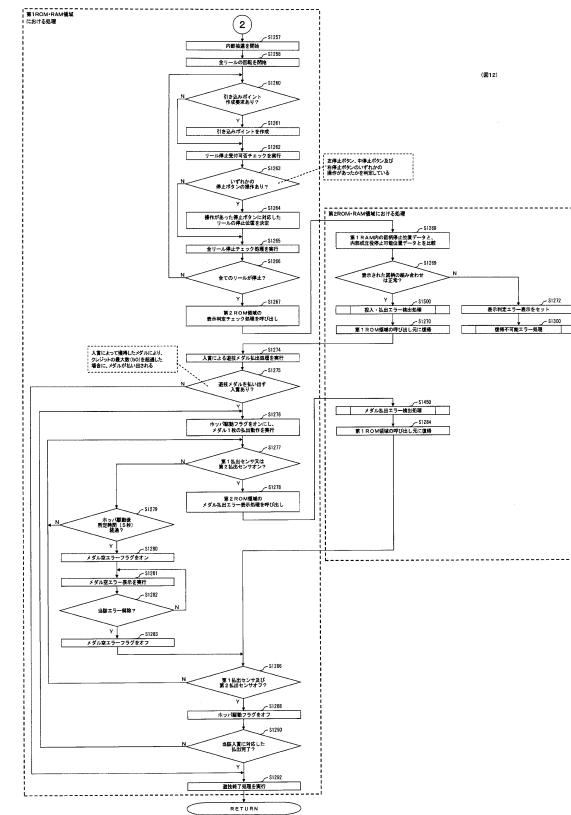

【図12】図12は、本実施形態に係る回胴式遊技機における、主制御基板側での遊技進行制御処理（3枚目）のフローチャートである。

30

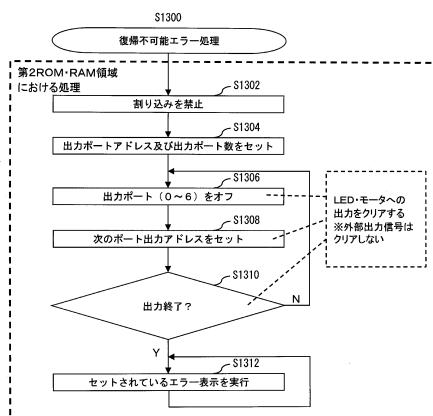

【図13】図13は、本実施形態に係る回胴式遊技機における、主制御基板側での復帰不可能エラー処理のフローチャートである。

【図14】図14は、本実施形態に係る回胴式遊技機における、主制御基板側でのメダル投入エラー検出処理のフローチャートである。

【図15】図15は、本実施形態に係る回胴式遊技機における、主制御基板側でのメダル払出手エラー検出処理のフローチャートである。

【図16】図16は、本実施形態に係る回胴式遊技機における、主制御基板側での投入・払出手エラー検出処理のフローチャートである。

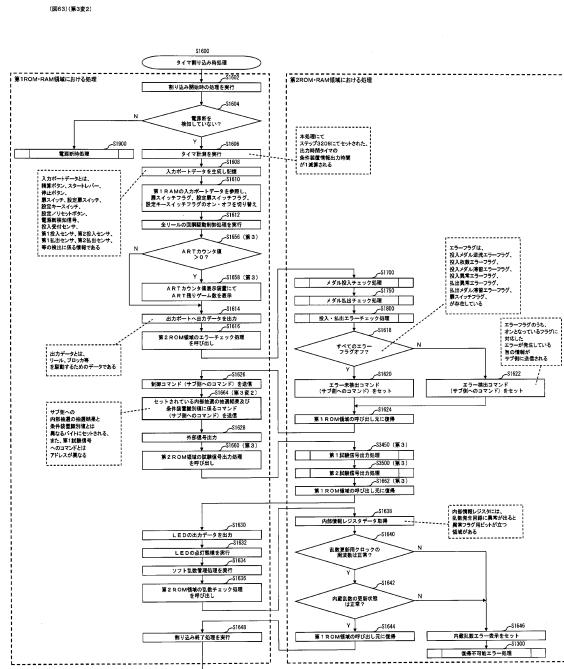

【図17】図17は、本実施形態に係る回胴式遊技機における、主制御基板側でのタイマ割り込み時処理のフローチャートである。

40

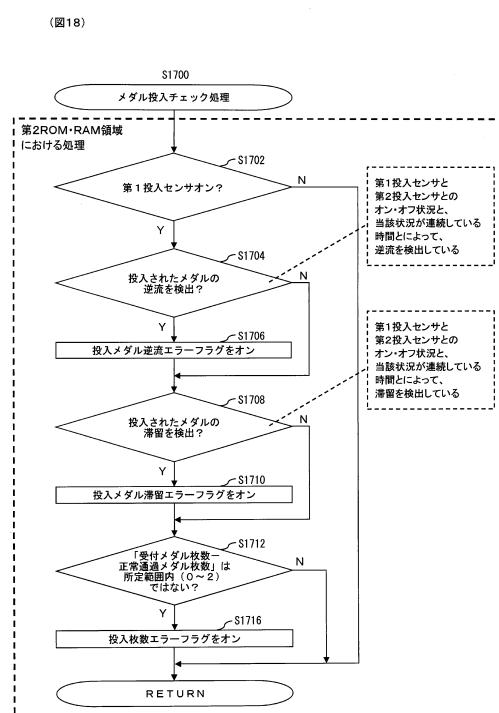

【図18】図18は、本実施形態に係る回胴式遊技機における、主制御基板側でのメダル投入チェック処理のフローチャートである。

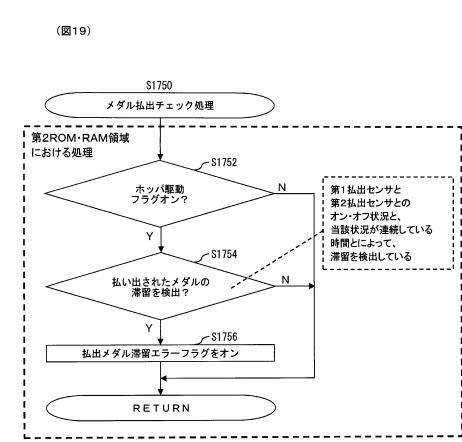

【図19】図19は、本実施形態に係る回胴式遊技機における、主制御基板側でのメダル払出手チェック処理のフローチャートである。

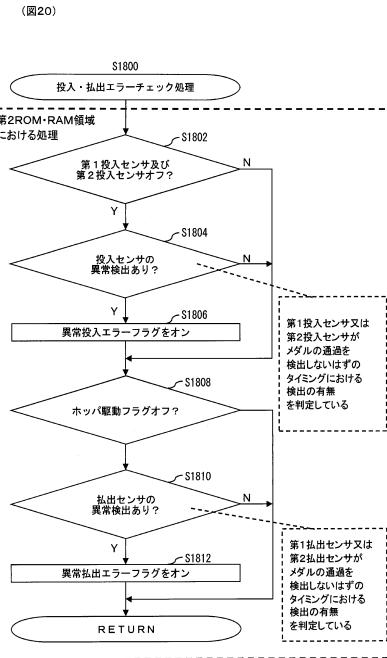

【図20】図20は、本実施形態に係る回胴式遊技機における、主制御基板側での投入・払出手エラーチェック処理のフローチャートである。

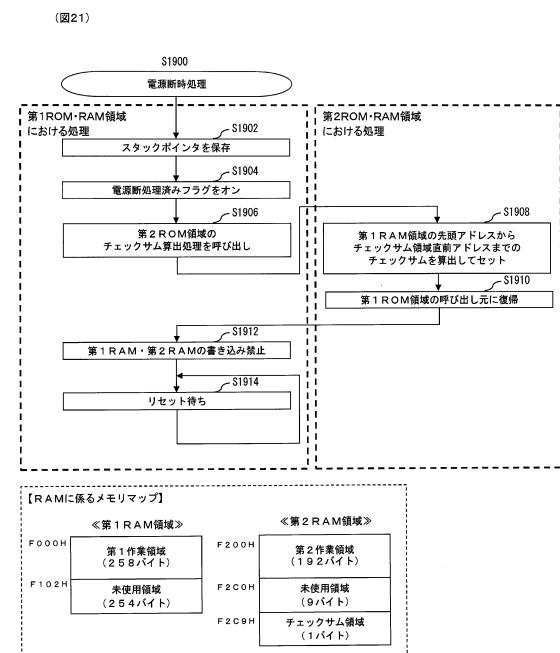

【図21】図21は、本実施形態に係る回胴式遊技機における、主制御基板側での電源断時処理のフローチャートである。

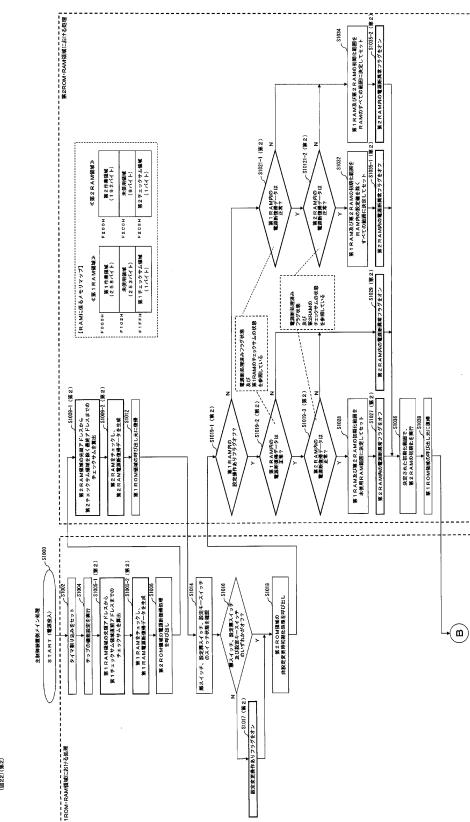

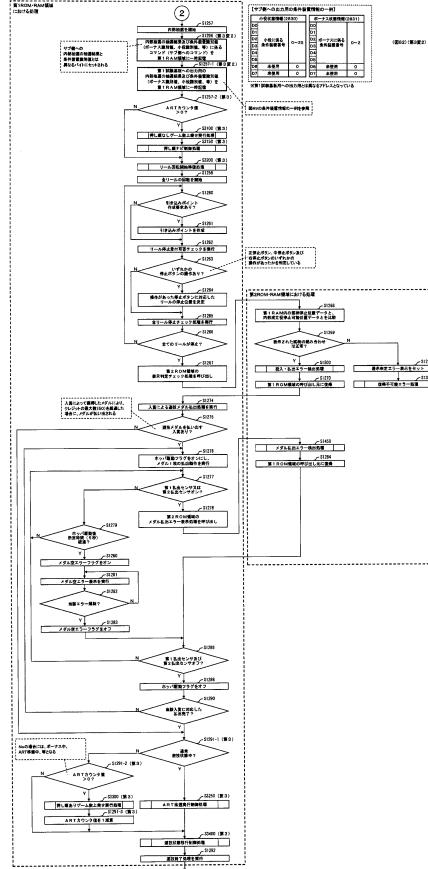

【図22】図22は、第2実施形態に係る回胴式遊技機における、主制御基板側でのメインフローチャート（1枚目）である。

50

【図23】図23は、第2実施形態に係る回胴式遊技機における、主制御基板側でのメインフローチャート(2枚目)である。

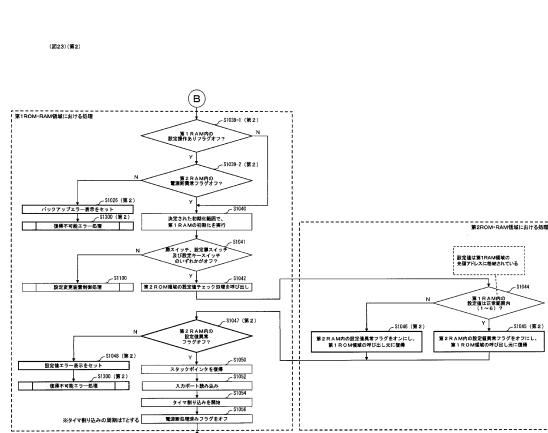

【図24】図24は、第2実施形態に係る回胴式遊技機における、主制御基板側での遊技進行制御処理(2枚目)のフローチャートである。

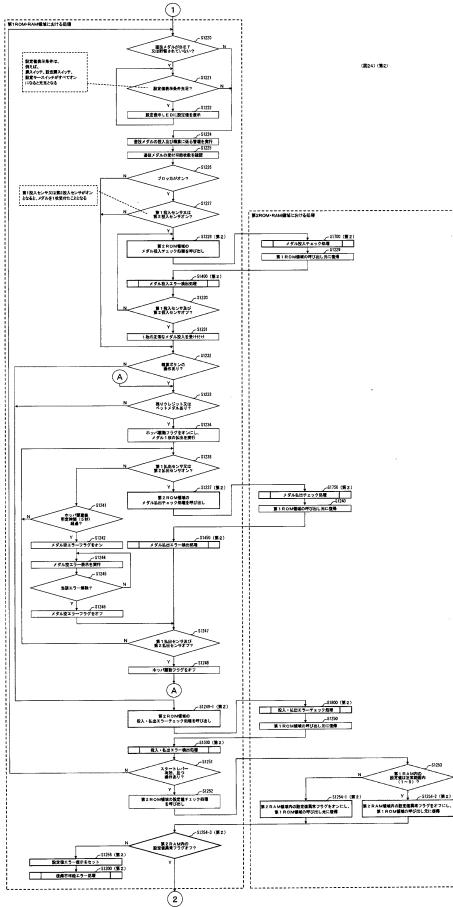

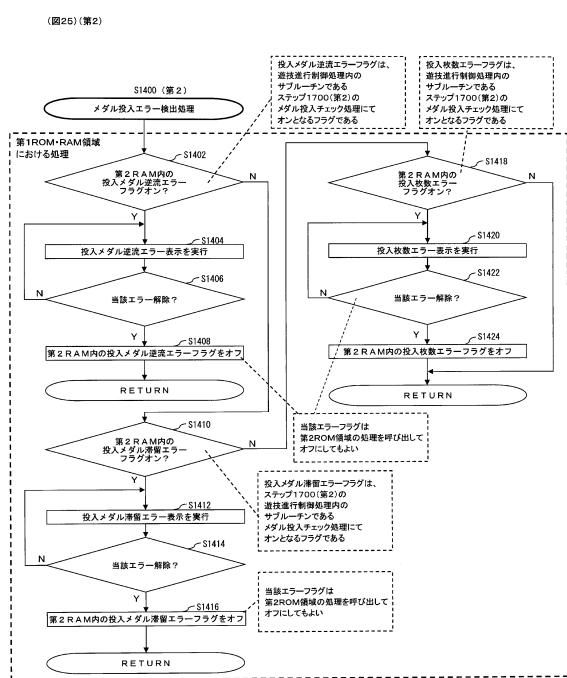

【図25】図25は、第2実施形態に係る回胴式遊技機における、主制御基板側でのメダル投入エラー検出処理のフローチャートである。

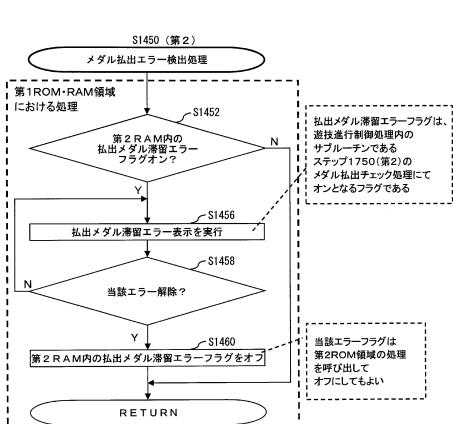

【図26】図26は、第2実施形態に係る回胴式遊技機における、主制御基板側でのメダル払出エラー検出処理のフローチャートである。

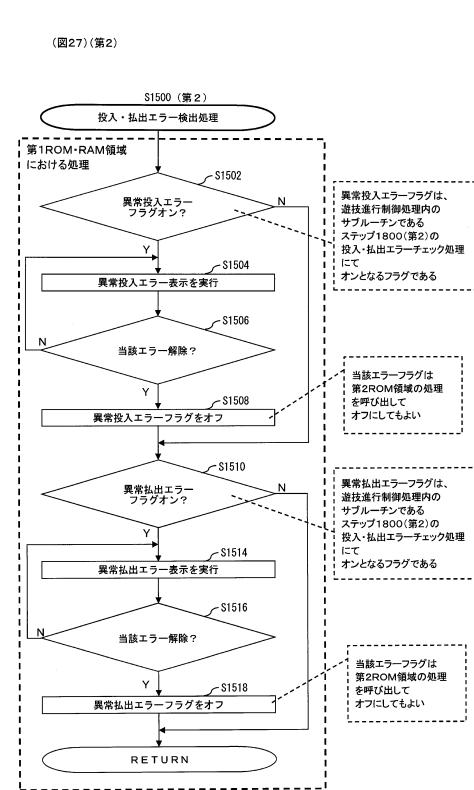

【図27】図27は、第2実施形態に係る回胴式遊技機における、主制御基板側での投入・払出エラー検出処理のフローチャートである。

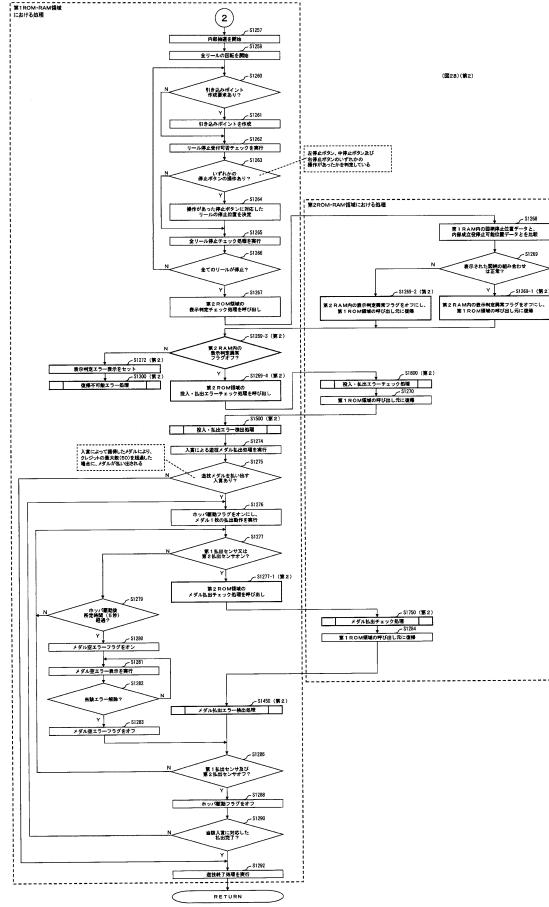

【図28】図28は、第2実施形態に係る回胴式遊技機における、主制御基板側での遊技進行制御処理(3枚目)のフローチャートである。

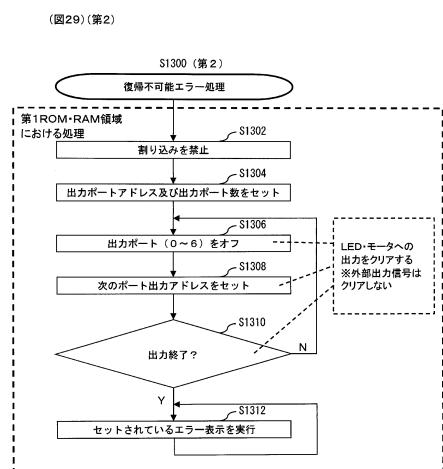

【図29】図29は、第2実施形態に係る回胴式遊技機における、主制御基板側での復帰不可能エラー処理のフローチャートである。

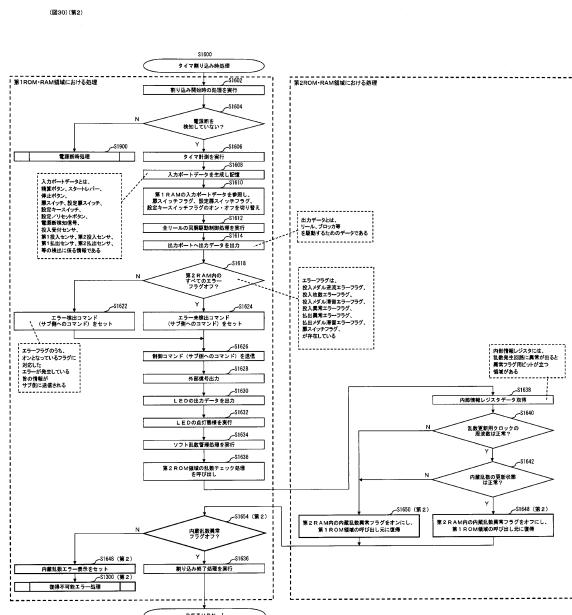

【図30】図30は、第2実施形態に係る回胴式遊技機における、主制御基板側でのタイマ割り込み時処理のフローチャートである。

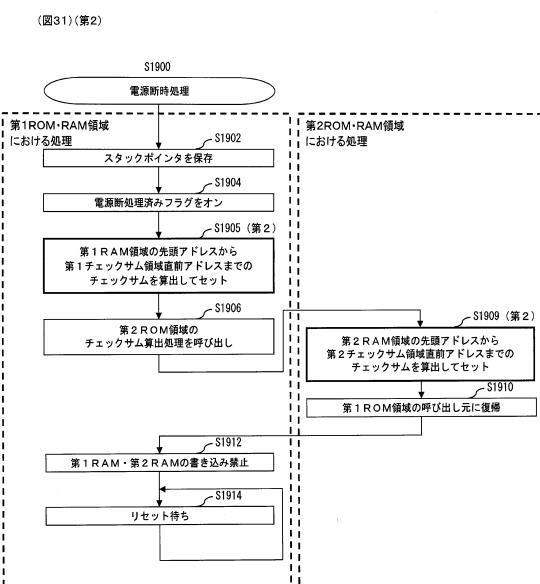

【図31】図31は、第2実施形態に係る回胴式遊技機における、主制御基板側での電源断時処理のフローチャートである。

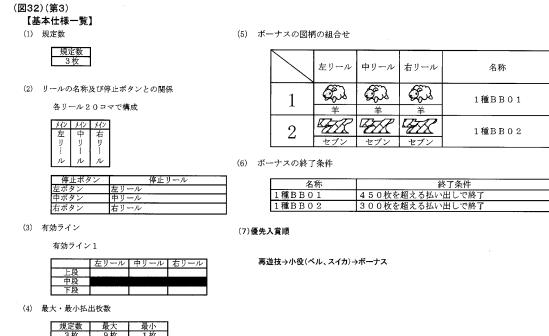

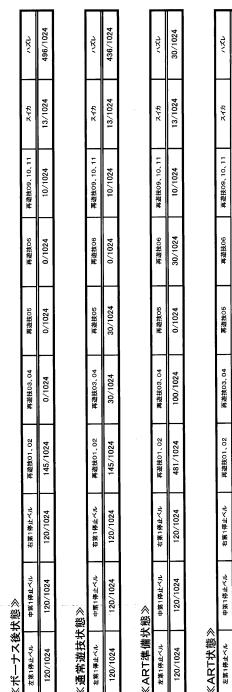

【図32】図32は、第3実施形態に係る回胴式遊技機における、基本仕様一覧である。

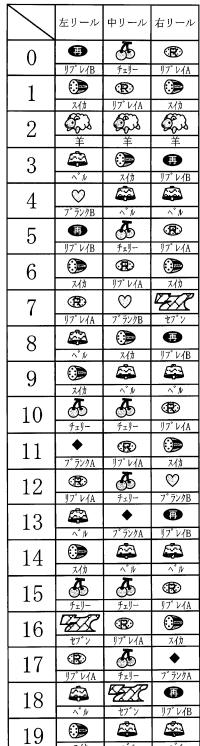

【図33】図33は、第3実施形態に係る回胴式遊技機における、リール配列一覧である。

【図34】図34は、第3実施形態に係る回胴式遊技機における、小役出現率一覧である。

【図35】図35は、第3実施形態に係る回胴式遊技機における、図柄組み合わせ一覧1である。

【図36】図36は、第3実施形態に係る回胴式遊技機における、図柄組み合わせ一覧2である。

【図37】図37は、第3実施形態に係る回胴式遊技機における、条件装置一覧1である。

【図38】図38は、第3実施形態に係る回胴式遊技機における、条件装置一覧2である。

【図39】図39は、第3実施形態に係る回胴式遊技機における、条件装置一覧3である。

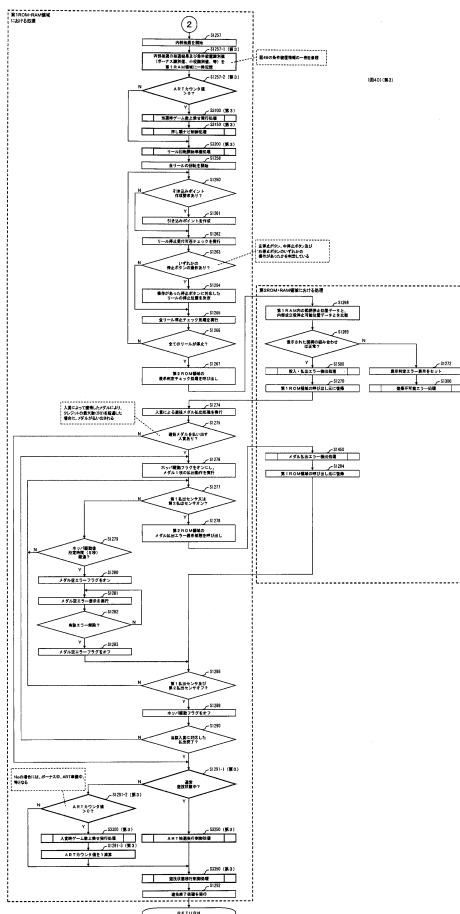

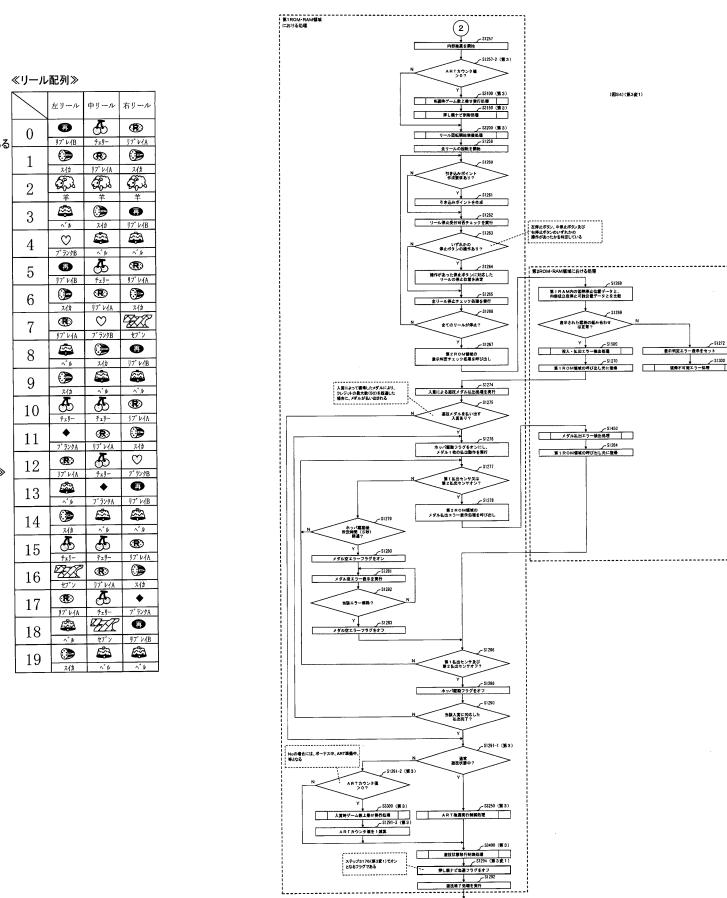

【図40】図40は、第3実施形態に係る回胴式遊技機における、主制御基板側での遊技進行制御処理(2枚目)のフローチャートである。

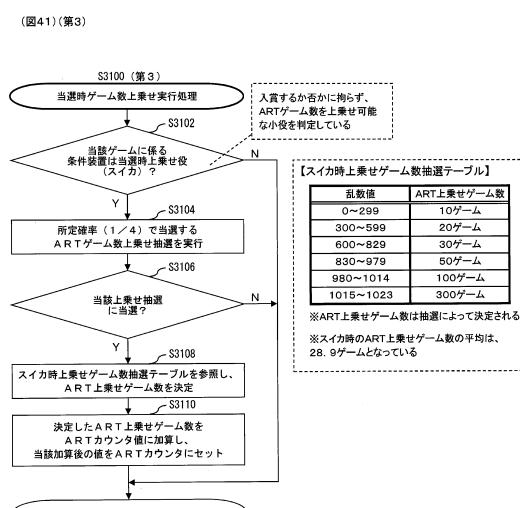

【図41】図41は、第3実施形態に係る回胴式遊技機における、主制御基板側での当選時ゲーム数上乗せ実行処理のフローチャートである。

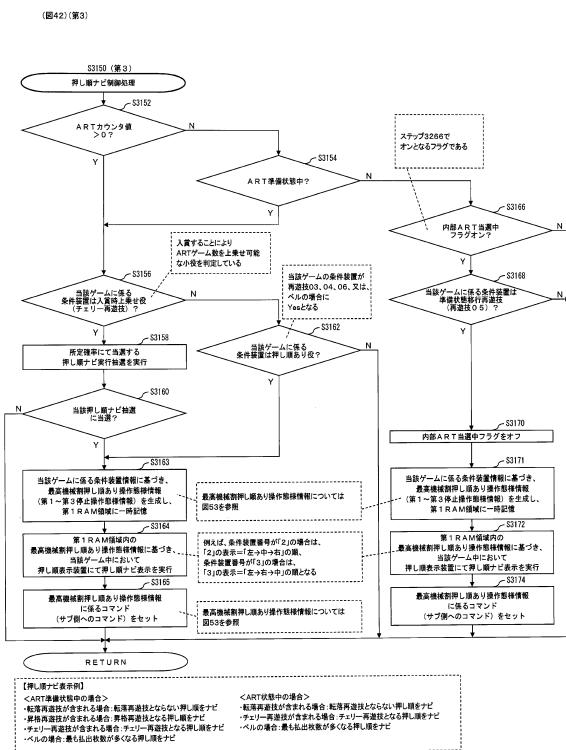

【図42】図42は、第3実施形態に係る回胴式遊技機における、主制御基板側での押し順ナビ制御処理のフローチャートである。

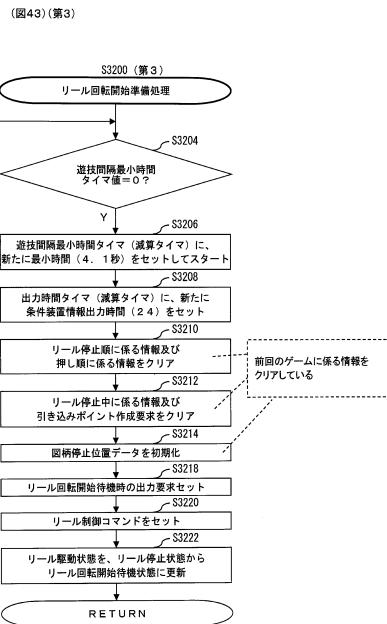

【図43】図43は、第3実施形態に係る回胴式遊技機における、主制御基板側でのリール回転開始準備処理のフローチャートである。

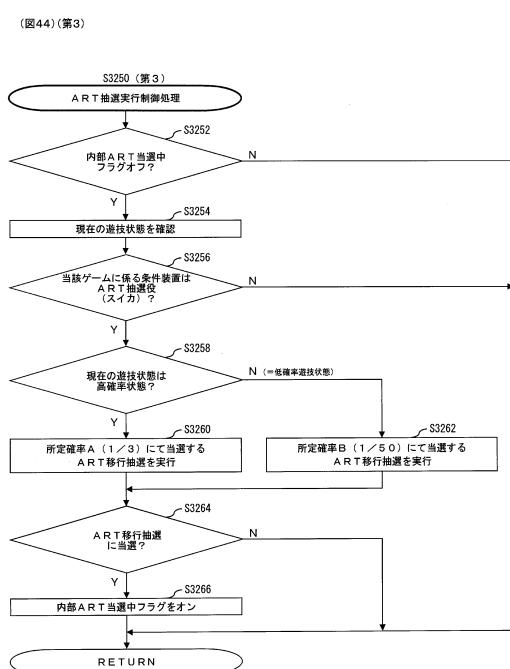

【図44】図44は、第3実施形態に係る回胴式遊技機における、主制御基板側でのA.R.T抽選実行処理のフローチャートである。

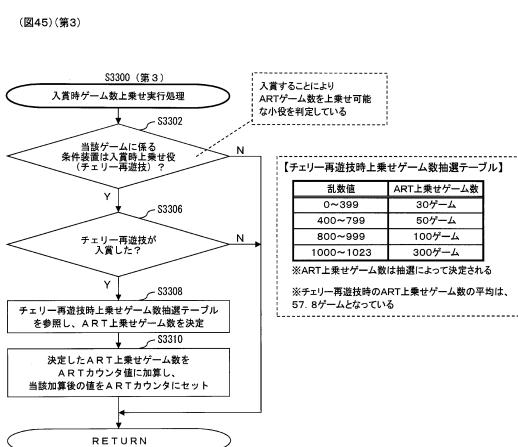

【図45】図45は、第3実施形態に係る回胴式遊技機における、主制御基板側での入賞時ゲーム数上乗せ実行処理のフローチャートである。

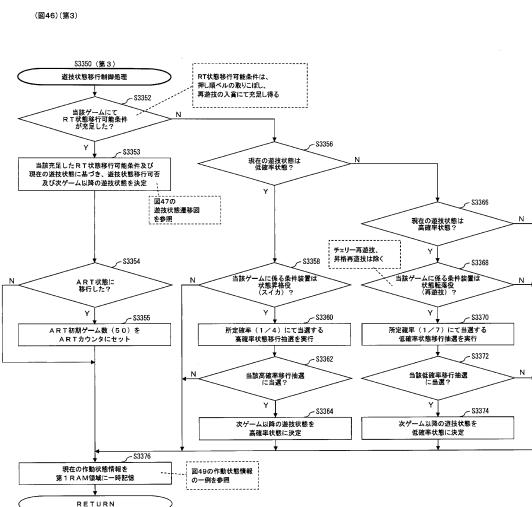

【図46】図46は、第3実施形態に係る回胴式遊技機における、主制御基板側での遊技状態移行制御処理のフローチャートである。

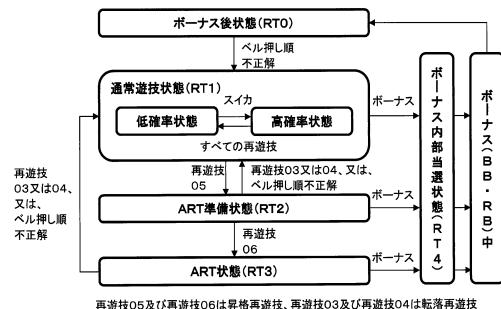

【図47】図47は、第3実施形態に係る回胴式遊技機における、主制御基板側での遊技状態遷移図である。

【図48】図48は、第3実施形態に係る回胴式遊技機における、主制御基板側でのタイ

10

20

30

40

50

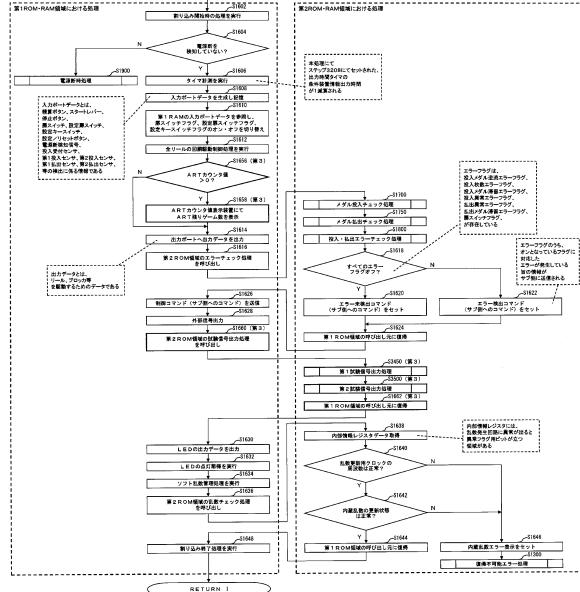

マ割り込み時処理のフローチャートである。

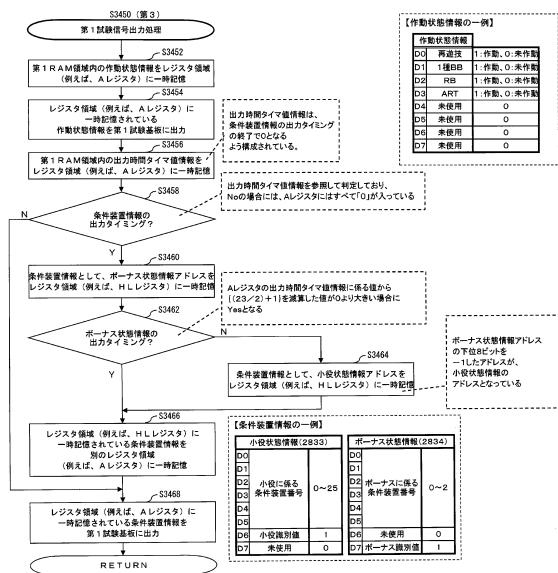

【図49】図49は、第3実施形態に係る回胴式遊技機における、主制御基板側での第1試験信号出力処理のフローチャートである。

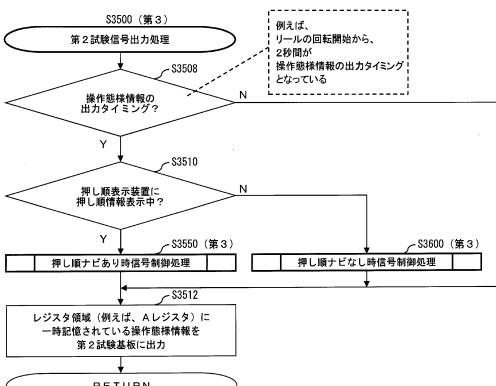

【図50】図50は、第3実施形態に係る回胴式遊技機における、主制御基板側での第2試験信号出力処理のフローチャートである。

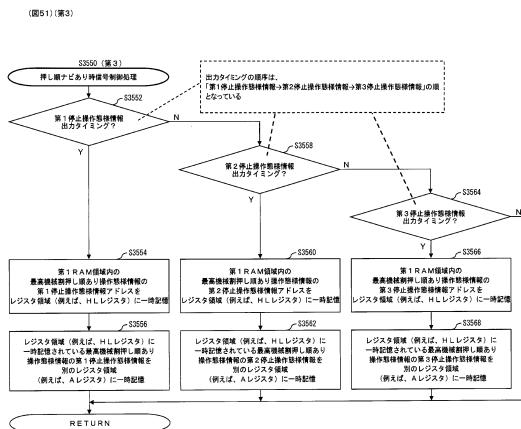

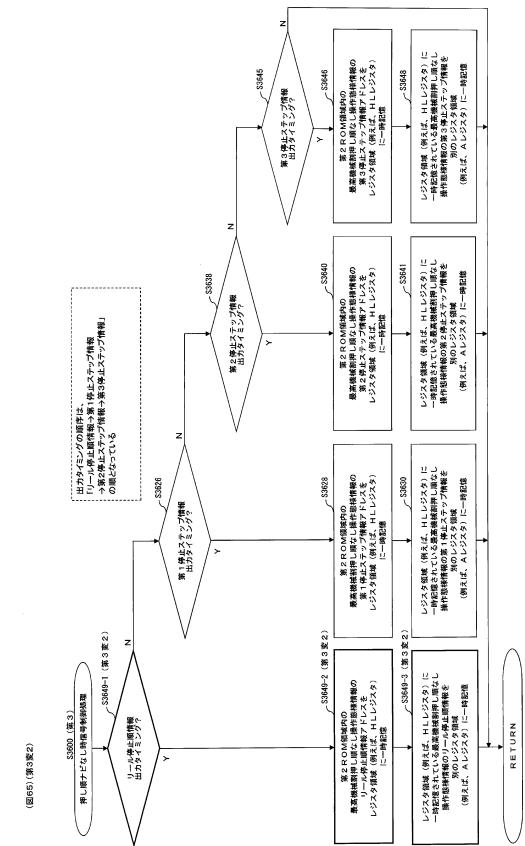

【図51】図51は、第3実施形態に係る回胴式遊技機における、主制御基板側での押し順ナビあり時信号制御処理のフローチャートである。

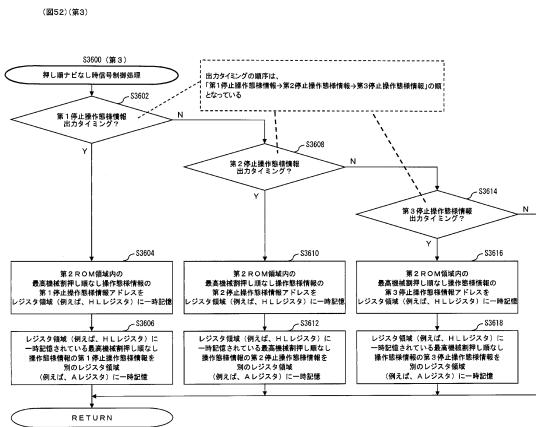

【図52】図52は、第3実施形態に係る回胴式遊技機における、主制御基板側での押し順ナビなし時信号制御処理のフローチャートである。

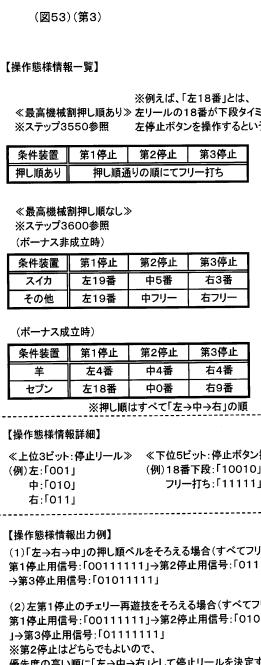

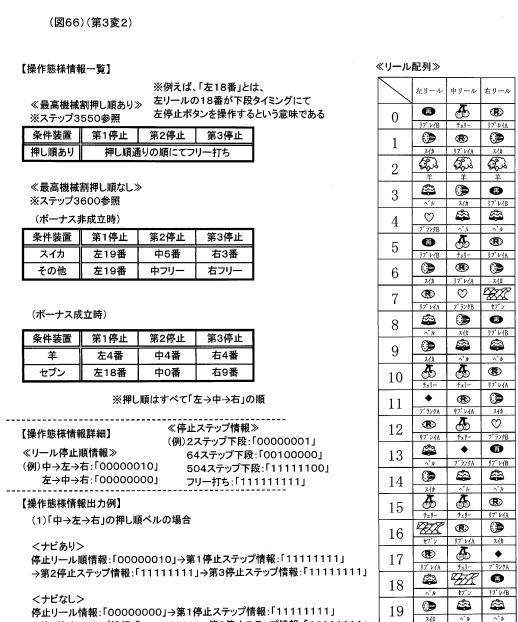

【図53】図53は、第3実施形態に係る回胴式遊技機における、操作態様情報一覧である。 10

【図54】図54は、第3実施形態からの変更例1に係る回胴式遊技機における、主制御基板側での遊技進行制御処理(2枚目)のフローチャートである。

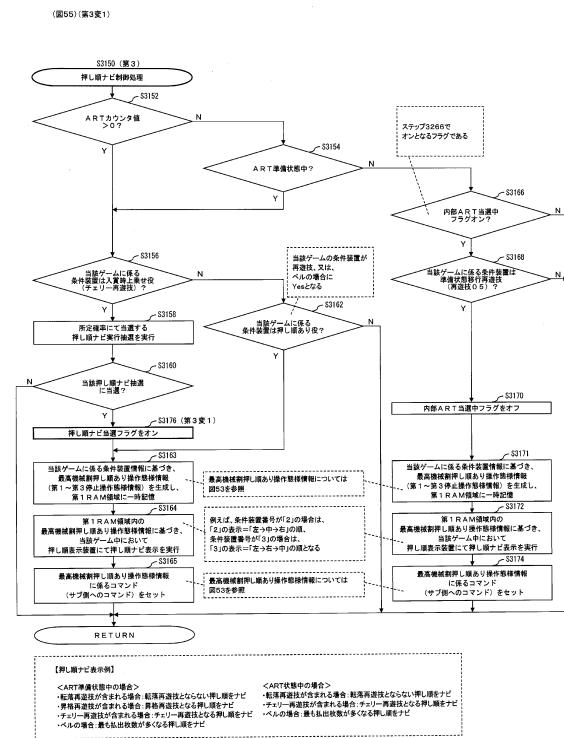

【図55】図55は、第3実施形態からの変更例1に係る回胴式遊技機における、主制御基板側での押し順ナビ制御処理のフローチャートである。

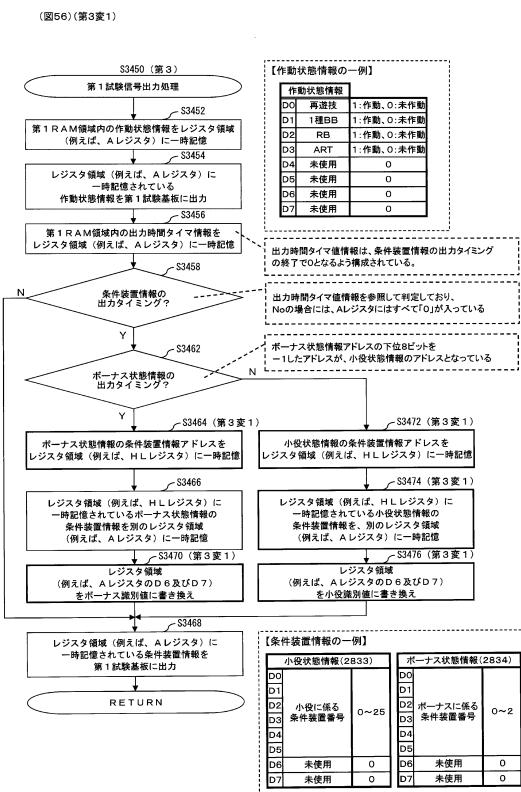

【図56】図56は、第3実施形態からの変更例1に係る回胴式遊技機における、主制御基板側での第1試験信号出力処理のフローチャートである。

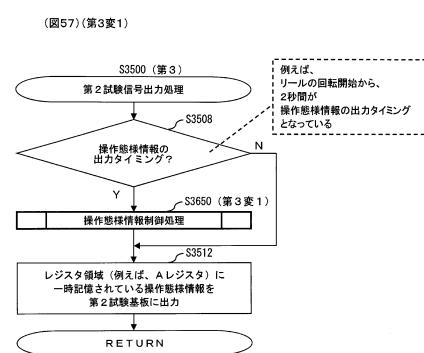

【図57】図57は、第3実施形態からの変更例1に係る回胴式遊技機における、主制御基板側での第2試験信号出力処理のフローチャートである。

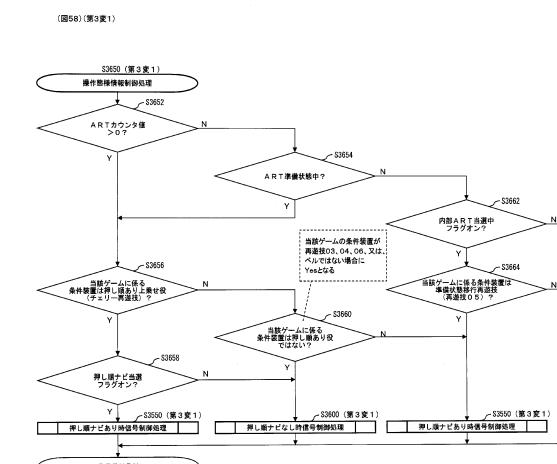

【図58】図58は、第3実施形態からの変更例1に係る回胴式遊技機における、主制御基板側での操作態様情報制御処理のフローチャートである。 20

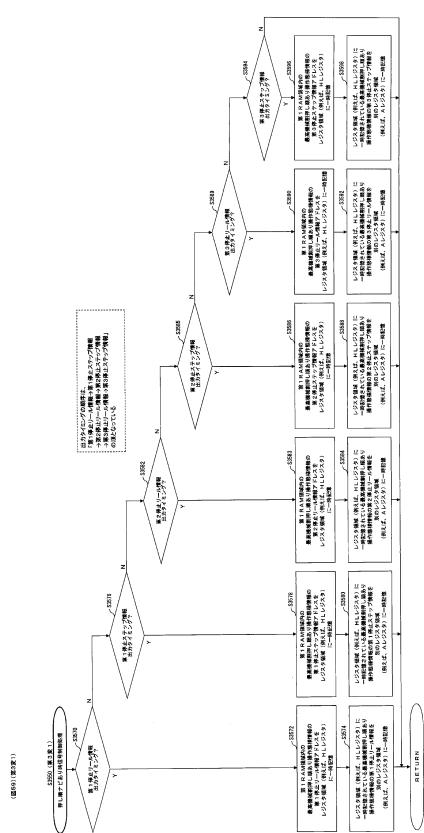

【図59】図59は、第3実施形態からの変更例1に係る回胴式遊技機における、主制御基板側での押し順ナビあり時信号制御処理のフローチャートである。

【図60】図60は、第3実施形態からの変更例1に係る回胴式遊技機における、主制御基板側での押し順ナビなし時信号制御処理のフローチャートである。

【図61】図61は、第3実施形態からの変更例1に係る回胴式遊技機における、操作態様情報一覧である。

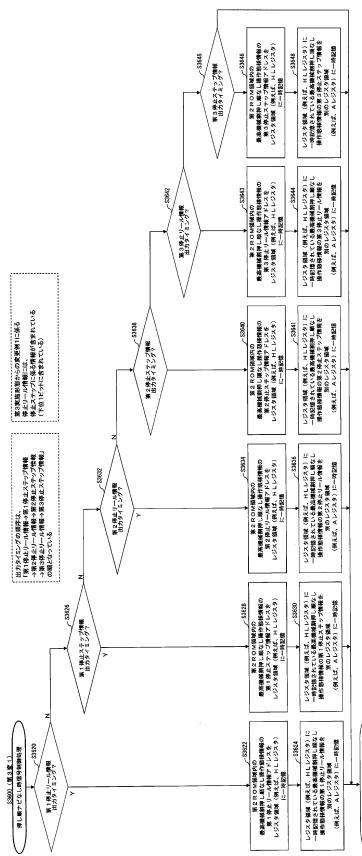

【図62】図62は、第3実施形態からの変更例2に係る回胴式遊技機における、主制御基板側での遊技進行制御処理(2枚目)のフローチャートである。

【図63】図63は、第3実施形態からの変更例2に係る回胴式遊技機における、主制御基板側でのタイマ割り込み時処理のフローチャートである。 30

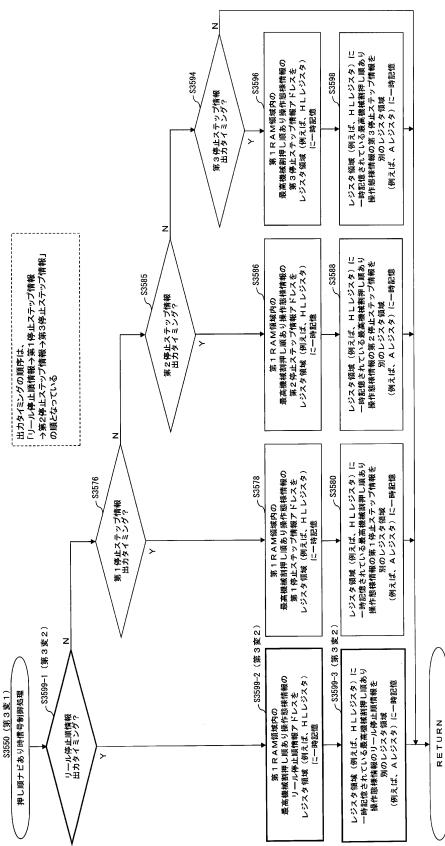

【図64】図64は、第3実施形態からの変更例2に係る回胴式遊技機における、主制御基板側での押し順ナビあり時信号制御処理のフローチャートである。

【図65】図65は、第3実施形態からの変更例2に係る回胴式遊技機における、主制御基板側での押し順ナビなし時信号制御処理のフローチャートである。

【図66】図66は、第3実施形態からの変更例2に係る回胴式遊技機における、操作態様情報一覧である。

#### 【0010】

はじめに、本明細書における各用語の意義について説明する。「乱数」とは、回胴式遊技機において何らかの遊技内容を決定するための抽選(電子計算機によるくじ)に使用される乱数であり、狭義の乱数の他に擬似乱数も含む(例えば、乱数としてはハード乱数、擬似乱数としてはソフト乱数)。例えば、遊技の結果に影響を与えるいわゆる「基本乱数」、具体的には、特別遊技の移行や入賞役と関連した「当選乱数」、等を挙げることができる。「C P U」とは、当業界において周知であるものと同義であり、使用されているアーキテクチャ(C I S C、R I S C、ビット数等)や処理性能等には何ら限定されない。

「電断(電源断)」とは、遊技機に設けられた電源スイッチの操作実行有無に係らず、遊技機に供給される電源電圧が一定レベル以下となつたことを指し、例えば、電源供給ユニットの破損や停電等による不測の事態による電源供給の遮断をも包含する。「R O M」とは、当業界において周知であるものと同義であり、情報を物理的に保持する(例えば、データ読み出し用の電流を与えた場合、導通する素子構成であれば「1」、導通しない素子

構成であれば「0」となる）。RAMとは、当業界において周知であるものと同義であり、情報を電気的に保持する（例えば、データ読み出し用の電流を与えた場合、蓄電されていれば「1」、蓄電されていなければ「0」となる。尚、RAM内で保持されているデータの一部又はすべてに対して、電断時にはバックアップ電源が供給されるよう構成されていることが一般的である）。「遊技状態」とは、例えば、遊技メダルが獲得容易であり遊技者にとって有利な特別遊技状態（いわゆる大当たり遊技であり、ボーナス遊技や第1種BB・第2種BB等と呼ばれるものが該当する）、再遊技の当選率があらかじめ定められた値である通常遊技状態よりも再遊技当選率が高い（又は低い）状態である再遊技確率変動遊技状態（RT状態）、当選した役を入賞させるためのリールの停止順を報知し得るAT（アシストタイム）状態、前記RT状態とAT状態とが複合したART（アシストリプレイタイム）状態、等が挙げられる。また、前記通常遊技状態においても、前記RT状態、AT状態、ART状態への移行抽選確率が異なる、高確率通常遊技状態、低確率通常遊技状態、等が挙げられる。また、前記遊技状態は複合しても問題ない（更に、これらの遊技状態や機能（例えば、AT状態への移行抽選や、リールの停止順に係る報知指示の出力等）は、遊技進行を制御する主制御基板側ですべて実装してしまっても問題ない）。

#### 【0011】

以下の実施形態は、回胴式遊技機（いわゆるスロットマシン）を前提としたものとなつてはいるが、これには何ら限定されず、他の遊技機（例えば、ぱちんこ遊技機、雀球、アレンジボール等）に応用された場合も範囲内であり、即ち、遊技進行を制御するマイコンチップ（CPU、ROM、RAMを搭載したチップ）を備え、当該マイコンチップにてプログラムを動作させるものに対して応用することができる技術である。尚、本実施形態は、あくまで一例であり、各手段が存在する場所や機能等、各種処理に関しての各ステップの順序、フラグのオン・オフのタイミング、各ステップの処理を担う手段名等に関し、以下の様に限定されるものではない。また、上記した実施形態や変更例は、特定のものに対して適用されると限定的に解すべきでなく、どのような組み合わせであってもよい。例えば、ある実施形態についての変更例は、別の実施形態の変更例であると理解すべきであり、また、ある変更例と別の変更例が独立して記載されていたとしても、当該ある変更例と当該別の変更例を組み合わせたものも記載されていると理解すべきである。

#### 【0012】

ここで本発明の詳細な説明に先立ち、本発明に係る簡潔な構成を説明する。

#### 【0013】

本発明に係る回胴式遊技機のうち、第2ROM領域にて配置されているプログラムコードに基づくCPU C100の処理にて、第1RAM領域（又は、レジスタ領域）を更新及び参照し得る構成を（本実施形態）にて詳細に説明する。

#### 【0014】

本発明に係る回胴式遊技機のうち、第1ROM領域にて配置されているプログラムコードに基づくCPU C100の処理にて、第2RAM領域を参照可能に構成し、且つ、第2ROM領域にて配置されているプログラムコードに基づくCPU C100の処理にて、第1RAM領域を参照し得る構成を（第2実施形態）にて詳細に説明する。

#### 【0015】

本発明に係る回胴式遊技機のうち、試験基板に出力する信号に係る処理を第2プログラム領域にて実行し、且つ、第1試験基板に出力する条件装置情報として、いずれの条件装置情報を出力するタイミングであるかに係る識別値（小役識別値、ボーナス識別値）を第1プログラム領域における処理によって第1RAM領域に一時記憶し、且つ、第1プログラム領域にて実行された押し順表示装置D270による押し順ナビに基づいて、第2試験基板への出力信号を制御するような構成を（第3実施形態）にて詳細に説明する。

#### 【0016】

本発明に係る回胴式遊技機のうち、第3実施形態をベースとして、且つ、第1試験基板に出力する条件装置情報として、いずれの条件装置情報を出力するタイミングであるかに係る識別値（小役識別値、ボーナス識別値）を第2プログラム領域における処理によって

10

20

30

40

50

レジスタ領域に一時記憶し、且つ、第1プログラム領域における押し順ナビに拘らず、第2プログラム領域にて第2試験基板への出力信号を制御するような構成を（第3実施形態からの変更例1）にて詳細に説明する。

#### 【0017】

本発明に係る回胴式遊技機のうち、第3実施形態からの変更例1をベースとして、且つ、第2試験基板に出力する操作様情報として、停止するリールに係る情報、即ちリール停止順に係る情報を一回の出力にて第2試験基板へ送信するような構成を（第3実施形態からの変更例1）にて詳細に説明する。

#### 【0018】

（本実施形態）

10

ここで、各構成要素について説明する前に、本実施形態に係る回胴式遊技機Pの特徴（概略）を説明する。以下、図面を参照しながら、各要素について詳述する。

#### 【0019】

まず、図1（一部の構成については図2）を参照しながら、本実施形態に係る回胴式遊技機の前面側の基本構造を説明する。まず、回胴式遊技機Pは、主に前扉（フロントドアとも称す）と、裏箱（キャビネット、基体とも称す）と裏箱内に設置されたリールユニット、ホッパ装置、電源ユニット、主制御基板M（主制御チップCが搭載されている基板）で構成される。以下、これらを順に説明する。

#### 【0020】

次に、回胴式遊技機Pの前扉DUは、装飾ランプユニットD150、メダル受け皿D230、を含む。まず、装飾ランプユニットD150は、回胴式遊技機Pの遊技の進行に応じて発光する発光源を有したものである。また、前扉DUの開閉状態を検出可能な扉スイッチD80が設けられている。また、前扉DUには鍵穴D260が設けられており、鍵穴D260の形状と整合するキー（ドアキー）を鍵穴D260に差し込む（加えて、所定の方向（例えば、時計回り）に捻る）ことで、前扉DUを開放し得るよう構成されている。更に、本実施形態においては、ドアキーを鍵穴D260に差し込む（加えて、所定の方向（例えば、反時計回り）に捻る）ことで、エラー状態（後述する、ドア開放エラー等）を解除し得るよう構成されている。次に、メダル受け皿D230は、放出口D240から放出された遊技メダル（或いは単にメダルと呼ぶことがある）の受け皿である。

20

#### 【0021】

30

次に、前扉DUは、遊技状態を視認可能にするための機構、遊技媒体の入力を可能にするための機構、リールユニットを操作するための機構、等を含む。具体的には、遊技状態を視認可能にするための機構として、リール窓D160、投入数表示灯D210、操作状態表示灯D180、特別遊技状態表示装置D250、払出数表示装置D190、クレジット数表示装置D200、押し順表示装置D270、ARTカウンタ値表示装置D280等が取り付けられている。また、遊技媒体の投入や賭け数（ベット数）の入力を可能にするための機構として、メダル投入口D170、ベットボタンD220、投入された遊技媒体の払い出しを可能にするための機構として、精算ボタンD60が取り付けられている。そして、リールユニットを操作するための機構として、スタートレバーD50、停止ボタンD40が取り付けられている。以下、各要素について詳述する。

40

#### 【0022】

<遊技状態を視認可能にするための機構>

次に、リール窓D160は、前扉DUの一部を構成する合成樹脂等によって形成された透明な部材であり、リール窓D160を通して遊技機枠内に設置されたリールユニットを視認可能に構成されている。また、投入数表示灯D210は、LEDによって構成されており、現在ベット（一の遊技を開始するために必要な遊技メダルを投入すること）されているメダル数と同数のLEDが点灯するよう構成されている。また、操作状態表示灯D180は、LEDによって構成されており、現在の操作状態（メダル受付可否状態、再遊技入賞状態、遊技開始ウェイト状態等）に応じて点灯・消灯するよう構成されている。また、特別遊技状態表示装置D250は、7セグメントディスプレイによって構成されており

50

、特別遊技中に払い出された払出数の総数が表示されるよう構成されている。尚、特別遊技状態表示装置D 250を設けない構成としてもよく、そのように構成した場合には、演出表示装置S 40にて当該払出数の総数を表示するよう構成することで遊技者は特別遊技中に払い出された払出数の総数を認識することができユーザーフレンドリーな遊技機とすることができる。また、払出数表示装置D 190は、7セグメントディスプレイによって構成されており、現在払出されている遊技メダル数が表示されるよう構成されている。また、クレジット数表示装置D 200は、7セグメントディスプレイによって構成されており、遊技者の持ちメダルとして遊技機内に貯留されているメダル数の総数（クレジット数）が表示されるよう構成されている。また、押し順表示装置D 270は、リール停止順（左停止ボタンD 41、中停止ボタンD 42、右停止ボタンD 43の停止順）によって入賞する役が相違し得る条件装置{いわゆる押し順小役であるが、入賞する役が相違した場合には、遊技者に付される利益率（払出枚数、その後のART状態等）が異なり得るよう構成されているものが一般的である}が成立したゲームにて、遊技者に最も有利となるリール停止順を報知し得るよう構成されている。また、ARTカウンタ値表示装置D 280は、押し順表示装置D 270に表示された押し順ナビ表示に従って遊技を進行した場合に保障されることとなるART状態（詳細は後述）に滞在し得るゲーム数を表示し得るよう構成されている。尚、押し順表示装置D 270は、払出数表示装置D 190と兼用してもよいし、兼用しない場合、払出数表示装置D 190には、後述するART状態中における入賞によって払出されたメダルの合計枚数（又は純増枚数）が表示されるよう構成されていてもよい。

10

20

#### 【0023】

<遊技媒体の入力を可能にするための機構>

次に、メダル投入口D 170は、遊技メダルの投入口であり、メダル受付可能状態である状況下において当該投入口に投入された遊技メダルは遊技機枠内部へと誘導される。また、遊技機枠内部にはメダルの投入を検出するセンサとして、投入受付センサD 10sと、第1投入センサD 20sと、第2投入センサD 30sと、が設けられており、当該遊技機枠内部へと誘導された遊技メダルが正常に投入されたと判断した場合に、当該投入されたメダルをベットされたメダルとして検出し得るよう構成されている。また、ベットボタンD 220は、遊技者によって操作可能に構成されており、当該操作によって、貯留されているメダル（クレジットのメダル）をベットすることができるよう構成されている。また、精算ボタンD 60は、遊技者によって操作可能に構成されており、当該操作によって、貯留されているメダル（クレジットのメダル）及び／又はベットされているメダルを遊技者に払い戻すことが可能となっている。尚、精算ボタンD 60の操作によって払い戻された遊技メダルは、放出口D 240に払い出されるよう構成されている。

30

#### 【0024】

<リールユニットを操作するための機構>

次に、スタートレバーD 50は、遊技者によって操作可能に構成されており、当該操作によってリールユニットの動作を開始可能に構成されている。また、停止ボタンD 40は、遊技者によって操作可能な左停止ボタンD 41、中停止ボタンD 42、右停止ボタンD 43を備えており、夫々の停止ボタンを操作することによってリールユニットの動作を順次停止可能に構成されている。

40

#### 【0025】

次に、回胴式遊技機Pのリールユニットは、リールM 50とリールM 50の駆動源（ステッピングモータ等）とを備えている。また、リールM 50は、左リールM 51、中リールM 52、右リールM 53を備えている。ここで、夫々のリール部は合成樹脂等により形成され、当該リール部の外周上（リール带上）には複数の図柄が描かれている。そして、スタートレバーD 50及び停止ボタンD 40における各停止ボタンの操作に基づき、夫々のリール部の回転動作及び停止動作を可能とするよう構成されている。また、図示しないが、左リールM 51、中リールM 52及び右リールM 53の内部にはLED（以下、リールバックライトと呼ぶことがある）が設けられており、当該LEDが点灯した際にはリー

50

ル部外周を透過した光によって、リール部外周が点灯したように視認できるよう構成されている。

### 【 0 0 2 6 】

#### < その他の機構 >

また、回胴式遊技機 P の遊技機枠の内外には、遊技の興趣性を高めるための機構として、予告演出や背景演出等の演出を表示するための演出表示装置 S 4 0 、様々な点灯態様にて点灯し得る L E D ランプ S 1 0 、サウンドを出力し得るスピーカ S 2 0 、合成樹脂等によって形成された部材である、上パネル D 1 3 0 及び下パネル D 1 4 0 、等が設けられている。

### 【 0 0 2 7 】

10

次に、図 2 は、前扉 D U を開いて回胴式遊技機 P の内部の構成を示した斜視図である。前扉 D U の裏面側上部には、演出表示装置 S 4 0 が取り付けられている。前扉 D U のほぼ中央にはリール窓 D 1 6 0 が設けられており、その下方には、後述する扉基板 D が設けられている。また、扉基板 D には、前述した停止ボタン D 4 0 や、スタートレバー D 5 0 、精算ボタン D 6 0 等の入力信号が入力される。また、扉基板 D の下方には、スピーカ S 2 0 が設けられている。

### 【 0 0 2 8 】

また、詳細は後述するが、扉基板 D の付近には、メダル投入口 D 1 7 0 から投入された遊技メダルの通路となる投入受付センサ D 1 0 s が設けられており、当該投入受付センサ D 1 0 s の下方には、遊技メダルを放出口 D 2 4 0 に導くためのコインシュータ D 9 0 などが設けられている。投入受付センサ D 1 0 s は、メダル投入口 D 1 7 0 から投入された遊技メダルを主に寸法に基づいて選別し、規格寸法に適合した遊技メダルだけを受け入れる機能を有しており、当該機能により適合しないと判断されたメダル（又は、他の異物）は、プロッカ D 1 0 0 により放出口 D 2 4 0 に払い戻されるよう構成されている。遊技者がスタートレバー D 5 0 を操作する前に（遊技メダルの投入が有効である状態にて）遊技メダルを投入すると、遊技メダルは投入受付センサ D 1 0 s によって選別され、規格を満足しているものだけがホッパ H 4 0 内に投入され、規格を満たしていないメダルは、コインシュータ D 9 0 を通って、放出口 D 2 4 0 に返却されるようになっている。これに対して、スタートレバー D 5 0 が操作された後に（遊技メダルの投入が有効でない状態にて）遊技メダルが投入された場合は、投入された遊技メダルはコインシュータ D 9 0 を通つて、放出口 D 2 4 0 に返却される。また、投入受付センサ D 1 0 s の内部（流路の奥）には、詳細後述するメダル投入に係るセンサが設けられており、寸法規格を満たして受け入れられた遊技メダルが通過すると、第 1 投入センサ D 2 0 s 及び第 2 投入センサ D 3 0 s によって検出されて、その信号が後述する主制御基板 M に供給されるようになっている。

### 【 0 0 2 9 】

リール M 5 0 の上方には、遊技全体の制御を司る後述する主制御基板 M が格納されており、リール M 5 0 の背後には、各リール（左リール M 5 1 、中リール M 5 2 、右リール M 5 3 ）を駆動するための後述する回胴基板 K が格納されている。また、リール M 5 0 の左方には、図 1 に示した演出表示装置 S 4 0 や、L E D ランプ S 1 0 、スピーカ S 2 0 等を用いて行われる各種演出の制御を司る後述する副制御基板 S が格納されている。また、主制御基板 M には、後述する設定変更装置制御処理を実行するため（設定変更を行うため）に使用する設定キースイッチ M 2 0 、設定値の変更やエラー解除等を実行し得る設定 / リセットボタン M 3 0 、設定キースイッチ M 2 0 や設定 / リセットボタン M 3 0 等を保護するための設定扉（不図示）の開閉を判定する設定扉スイッチ M 1 0 が接続されている。尚、設定キースイッチ M 2 0 、設定 / リセットボタン M 3 0 、設定扉スイッチ M 1 0 については何れも不図示としているが、主制御基板 M の基板上等の適宜位置に設けられていればよい（即ち、前扉 D U を開かなければ人為的なアクセスが困難な位置に設けられていればよい）。

### 【 0 0 3 0 】

20

30

40

50

リールM 5 0 の下方には、投入された遊技メダルが集められるホッパH 4 0 や、遊技メダルを払い出すメダル払出装置Hが設けられており、回胴式遊技機P全体に電源を供給するための電源基板Eが格納されている。メダル払出装置Hから払い出された遊技メダルは、コインシュータD 9 0 を通って、放出口D 2 4 0 から払い出されるようになっている。また、電源基板Eの前面には、回胴式遊技機Pの電源を投入するための電源スイッチE 1 0も設けられている。

#### 【0031】

次に、図3は、回胴式遊技機内部における、メダル投入口D 1 7 0 に投入された遊技メダルの経路（セレクタ）を示した斜視図である。メダル投入口D 1 7 0 に投入された遊技メダルは、まず投入受付センサD 1 0 sを通過する。当該投入受付センサD 1 0 sは機械式のダブルセンサになっており、遊技メダルが通過することによって、2つの突起した機構が押下されることによりオンとなり遊技メダルが正常に通路を通過することができることなる。また、このような構成により、遊技メダルではない異物（例えば、遊技メダルよりも径が小さいもの）が投入された場合には、前記2つの突起した機構が押下されない。このようなメダルは、起立した状態をメダルが維持できないため、通路を通過できず（メダルが倒れこむ）放出口D 2 4 0 に払い戻されることとなる。そのほかにも、投入受付センサD 1 0 sは、オンとなっている時間が所定時間以上連続した場合等にも、エラーであると判定し得る（その結果、ブロックD 1 0 0 がオフとなり得る）よう構成されている。

#### 【0032】

遊技メダルがブロックD 1 0 0 を正常に通過した場合に、当該通過直後に第1投入センサD 2 0 s及び第2投入センサD 3 0 sを通過することとなる。この投入センサ（第1投入センサD 2 0 s及び第2投入センサD 3 0 s）は2つのセンサで構成されており（遊技メダルの規格上の直径よりも小さい間隔で隣接配置されており）、夫々のセンサのオン・オフ状況（第1投入センサD 2 0 s及び第2投入センサD 3 0 sのオン・オフの組み合わせの遷移していく順序、等）及びオン・オフとなっている時間を監視することにより様々なエラー（後述する、投入メダル滞留エラー、投入メダル逆流エラー、等）を検出可能に構成されている。

#### 【0033】

次に、図4は、回胴式遊技機における、メダル払出装置Hの正面図及び斜視図である。メダル払出装置Hは、クレジット（遊技機内部に電子的に貯留されている遊技メダル）又はベットされているメダル（遊技を開始するために投入されたメダル）が存在する状態で、精算ボタンが操作された、又は、入賞により遊技メダルが払い出される場合に作動することとなる。作動する場合には、まず、ホッパモータH 8 0 が駆動することにより、ディスク回転軸H 5 0 aを中心にディスクH 5 0 が回転する。当該回転によりメダル払出装置H内の遊技メダルは放出付勢手段H 7 0 を変位させて遊技メダル出口H 6 0 から放出口D 2 4 0 に向かって流下していくこととなる。尚、払出センサ（第1払出センサH 1 0 s及び第2払出センサH 2 0 s）は2つのセンサで構成されており、夫々のセンサのオン・オフ状況（第1払出センサH 1 0 s及び第2払出センサH 2 0 sのオン・オフの組み合わせの遷移していく順序、等）及びオン・オフとなっている時間を監視することにより様々なエラー（後述する、払出メダル滞留エラー、等）を検出可能に構成されている。より具体的には、例えば、遊技メダル出口H 6 0 を正常に通過する際には、放出付勢手段H 7 0 の変位により、第1払出センサH 1 0 s = オフ・第2払出センサH 2 0 s = オフの状態から、第1払出センサH 1 0 s = オフ・第2払出センサH 2 0 s = オフ 第1払出センサH 1 0 s = オン・第2払出センサH 2 0 s = オフ 第1払出センサH 1 0 s = オン・第2払出センサH 2 0 s = オフ

第1払出センサH 1 0 s = オフ・第2払出センサH 2 0 s = オフ、というセンサ状態遷移となるため、このセンサ状態遷移と反する動きを検出した場合には、エラーとするよう構成することを例示することができる。

#### 【0034】

10

20

30

40

50

次に、図5のブロック図を参照しながら、本実施形態に係る回胴式遊技機Pの電気的な概略構成を説明する。はじめに、本実施形態に係る回胴式遊技機は、遊技の進行を制御する主制御基板Mを中心として、副制御基板S、扉基板D、回胴基板K、電源基板E、中継基板IN、設定扉スイッチM10、設定キースイッチM20、設定ノリセットボタンM30等がデータを取り可能に接続されて構成されている。尚、図中の実線部がデータのやり取りに関する動きを示したものであり、図中の破線部が電源供給ルートを示したものである。尚、電源供給ルートはこれに限られたものではなく、例えば電源基板Eから主制御基板を介さずに中継基板INや扉基板Dに電源を供給しても良い。

#### 【0035】

主制御基板Mは、回胴式遊技機Pで行われる遊技全体の進行を司る基板である。10 主制御基板Mには、主制御チップCが搭載されており、主制御チップCには、CPU C100、内蔵ROM C110、内蔵RAM C120等がバスによって互いにデータを取り可能に接続されて搭載されている(図示及び詳細については後述する)。そして、主制御基板Mは、前扉DUに搭載された扉基板Dから、スタートレバーD50等が操作されたことを示す信号等を受け取って、副制御基板Sや、扉基板D、回胴基板K等に向かって制御コマンド(あるいは制御信号)を出力することにより、これら各種基板の動作を制御している。

#### 【0036】

また、副制御基板Sにも、前述した主制御基板Mと同様に、副制御チップSCが搭載されており、副制御チップSCには、CPUや、ROM、RAM等が設けられていて、バスによって互いにデータを取り可能に接続されて構成されている。また、副制御基板Sには、各種LEDランプS10、スピーカS20、演出表示装置S40、回胴バックライトS30等が接続されている。ここで回胴バックライトS30とは、左リールM51、中リールM52、右リールM53夫々の内部に設けられ、当該リールの表面に描かれた図柄を裏側から照らすライトである。副制御基板Sは、主制御基板Mから受け取った制御コマンドを解析して、各種LEDランプS10、スピーカS20、演出表示装置S40、回胴バックライトS30等にそれぞれ駆動信号を出力することにより、各種の演出を行っている。

#### 【0037】

扉基板Dには、前述した投入受付センサD10s、第1投入センサD20s、第2投入センサD30s、回転しているリールM50を停止するための停止ボタンD40、リールM50の回転を開始するためのスタートレバーD50、貯留されている遊技メダル(クレジット)や投入された遊技メダルを払い出して遊技を終了するための精算ボタンD60、遊技の状態を表示する各種の表示パネルD70(前述した、投入数表示灯D210、操作状態表示灯D180、特別遊技状態表示装置D250、払出数表示装置D190は、クレジット数表示装置D200、等の表示装置の集合体)、前扉の開閉の判定やエラーの解除や設定値の変更を実行するための扉スイッチD80、投入された後に適合しないと判断された遊技メダル(又は、その他の異物)を放出口D240に払い戻すためのプロッカD100等が接続されている。また、この扉基板Dは、前述した主制御基板Mとデータを取り可能に接続されている。このため、前扉DUに設けられたスタートレバーD50や、停止ボタンD40、精算ボタンD60等を操作すると、扉基板Dを介して、当該操作に係る信号が主制御基板Mに供給されるようになっている。また、投入受付センサD10sが遊技メダルの通過を検出した信号も、扉基板Dを介して主制御基板Mに供給される。

#### 【0038】

また、回胴基板Kには、リールM50を回転させるための回胴モータK10と、リールM50の回転位置を検出するための回胴センサK20等が接続されている。回胴基板Kは、当該回胴センサK20によって、リールM50の回転位置を検出しながら回胴モータK10を駆動することにより、リールM50を、決定された停止位置で停止させることができとなっている。また、本実施形態の回胴式遊技機においては、回胴モータK10には、所謂ステップモータ(ステッピングモータ)が使用されている。尚、ステップモータは、50

リールM50が1回転するステップ数として、504ステップが設定されている。また、各リール(左リールM51、中リールM52、右リールM53)には略均一の大きさで所定数(例えば、21個)の図柄が設定されており、1図柄分に相当するステップ数としては、24ステップ(=21/504)が設定されている。尚、ステップ数、リール1周あたりの図柄の数は変更しても何ら問題ない。

#### 【0039】

また、メダル払出装置Hは、中継基板INを介して、主制御基板Mに接続されており、主制御基板Mからの制御信号に基づいて、所定枚数(例えば、10枚)の遊技メダルを払い出す動作を行う。尚、メダル払出装置Hにはメダルが正常に払い出されたか否かの判定や払い出された遊技メダルの数の計測を実行する第1払出センサH10s及び第2払出センサH20sと、ディスクH50を回転させるためのホッパモータH80と、が接続されている。10

#### 【0040】

これら各種制御基板、及び基板で消費される電力は、電源基板E(電源スイッチE10により電源供給の有無を制御する基板)から供給されている。図5では、電源基板Eから電力が供給される様子を破線の矢印で表している。図示されているように、主制御基板Mおよび副制御基板Sには、電源基板Eから電力が直接供給されており、各種基板(扉基板D、回胴基板K、中継基板IN)には、主制御基板Mを介して電力が供給されている。電源基板Eには所定量(例えば、100V)の交流電圧が供給されており、この電力を規定電圧の直流電圧に変換した後、夫々の制御基板及び基板に供給している。20

#### 【0041】

また、主制御基板Mには、後述する設定変更装置制御処理を実行するため(設定変更を行うため)に使用する設定キースイッチM20、設定値の変更やエラー解除等を実行し得る設定/リセットボタンM30、設定キースイッチM20や設定/リセットボタンM30等を保護するための設定扉(不図示)の開閉を判定する設定扉スイッチM10が接続されている。

#### 【0042】

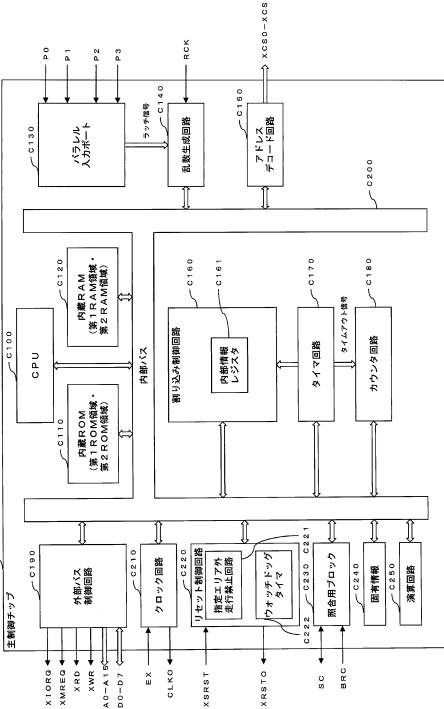

<主制御部の基本回路の構成例>

次に、図6を用いて、主制御基板Mの主制御チップCの構成例について説明する。

#### 【0043】

まず、図6に示す主制御チップCには、CPUC100、内蔵ROMC110(第1ROM領域C111、第2ROM領域C112)、内蔵RAMC120(第1RAM領域C121、第2RAM領域C122)、外部バス制御回路C190、パラレル入力ポートC130、アドレスデコード回路C150、タイマ回路C170、カウンタ回路C180、リセット制御回路C220に加え、割込み制御回路C160、クロック回路C210、乱数生成回路C140、照合用ブロックC230、固有情報C240、演算回路C250が備えられており、これら全てが内部バスC200を介して互いに接続されている。30

#### 【0044】

以下、上記説明した各部の詳細について説明する。

#### 【0045】

まず、CPUC100は、内蔵ROMC110や内蔵RAMC120のプログラムやデータによって様々な数値計算や情報処理、制御処理などを実行する。内蔵ROMC110は、制御プログラムや各種データを記憶する。内蔵RAMC120は、一時的にデータを記憶する。また、内蔵ROMC110及び内蔵RAMC120はアドレスとデータとをセットとして保持しており、アドレス範囲で用途が区切られている。尚、当該用途として主なものは、プログラム領域とデータ領域であるが、この点の詳細については、後述するメモリマップの説明に譲る。40

#### 【0046】

外部バス制御回路C190は、IORquest端子(XIORQ端子)、メモリリクエスト端子(XMRREQ端子)、リード信号端子(XRD端子)、ライト信号端子(XWR50

端子)、16ビット幅のアドレス出力端子(A0端子～A15端子)、および8ビット幅の入出力端子であるデータ入出力端子(D0端子～D7端子)を有する。本実施形態では、このうちデータ入出力端子(D0端子～D7端子)は、各駆動回路(例えば、中継基板INを介しての回胴基板K)へのデータ出力と、各周辺制御回路(例えば、扉基板Dを介しての各種センサや各種操作部材)からのデータ入力に用いられている。このデータ入出力端子(D0端子～D7端子)によるデータの入出力先は、アドレス出力端子(A0端子～A15端子)から出力されるアドレス信号、およびアドレスデコード回路C150から出力されるチップセレクト信号を用いて切り替えられる。

#### 【0047】

パラレル入力ポートC130は、4つの入力端子(P0端子～P3端子)を有する。これらの入力端子(P0端子～P3端子)は、例えば、その入力端子のいずれかがスタートレバーD50に接続されており、乱数生成回路C140が生成する乱数をCPUC100に取得させるためのラッチ信号として、乱数生成回路C140に出力する。10

#### 【0048】

アドレスデコード回路C150は、所定数(例えば、14)の出力端子(XCS0端子～XCS13端子)を有する。当該出力端子(XCS0端子～XCS13端子)は、主制御チップCの外部にある周辺制御回路に接続されており、外部バス制御回路C190のデータ入出力端子(D0端子～D7端子)から出力されるデータの送信先を切り替えるためのチップセレクト信号等の出力に用いられている。

#### 【0049】

タイマ回路C170は、時間の計測に用いられる。尚、タイマ回路C170は設定された計測時間を過ぎると、タイムアウト信号をカウンタ回路C180に出力する。一方、カウンタ回路C180は、各種信号の立ち上がり(あるいは立ち下がり)の回数の計測に用いられる。当該カウンタ回路で計測される信号には、主制御チップCのシステムクロックの他、前記タイマ回路からのタイムアウト信号、メモリの読み書き信号、メモリリクエスト信号、外部入出力の信号、割込みに対する応答信号等も計測することができる。20

#### 【0050】

リセット制御回路C220は、システムリセット入力端子(XSRT端子)と、リセット出力端子(XRSTO端子)の2つの端子を有する。このシステムリセット入力端子(XSRT端子)は電圧監視回路(電圧を監視するための回路であり、不図示となっている)に接続されている。当該システムリセット入力端子(XSRT端子)からシステムリセット信号(例えば一定時間Lレベルの信号)が入力されると、リセット制御回路C220は、主制御チップCの内部の回路に対してこのシステムリセット信号を出力するとともに、主制御チップCの外部にある周辺制御回路に対してリセット出力端子(XRSTO端子)からリセット信号(例えば、LレベルからHレベルへの立ち上がり信号)が出力される。この場合、主制御チップCでは、システムリセットと称する処理が実行され、各回路が初期化される。当該システムリセットが実行される一例として、電源投入時が挙げられる。30

#### 【0051】

また、リセット制御回路C220は、ウォッチドッグタイマC222と、指定エリア外走行禁止回路C221とを備えている。ウォッチドッグタイマC222がタイムアウトになった場合や、CPUC100が所定の範囲以外のアドレスを参照(指定エリア外走行)した場合には、リセット制御回路C220は、主制御チップCの内部の回路に対してシステムリセット信号およびユーザリセット信号のいずれかを出力する。尚、システムリセット信号およびユーザリセット信号のどちらを出力するかは、内蔵ROMC110内のプログラム領域(詳細は後述する)の設定に従う。また、主制御チップCの外部にある周辺制御回路に対しては、リセット出力端子(XRSTO端子)からリセット信号が出力される。

#### 【0052】

主制御チップCでは、設定によって上記のシステムリセットか、あるいはユーザリセット

50

50

50

50

50

と称する処理のいずれかを実行させることができる。

#### 【0053】

上記指定エリア外走行は、プログラムが想定外の動作をしていることを意味する。この場合、C P U C 1 0 0 が本来プログラムとして扱われるはずのないコードにより動作することになる。このような状況は、プログラムミスによる所謂暴走した状態の他に、何らかの不正によって生じている可能性がある。この場合、上記のシステムリセットおよびユーザリセットのいずれかの処理により、正常な動作に復帰させることができるようになっている。また、ウォッチドッグタイマC 2 2 2 がタイムアウトになった場合としては、プログラムミスによる暴走した状態や、電圧降下によりC P U C 1 0 0 が本来設計した動作を行うことができなくなった場合等がある。この場合にも、上記のシステムおよびユーザリセットのいずれかの処理により、正常な動作に復帰させることができるよう構成されている。10

#### 【0054】

割込み制御回路C 1 6 0 は、外部入力や内部状態の変化に応じて適宜処理を実行させるために割込みを発生させる。この割込み処理には、例えば外部からの入力（センサによる信号）を受け付けた場合に実行する処理がある。本実施形態では、タイマ回路からの割込み要求により実行されるタイマ割込み処理を実行するようにしている。尚、割込み制御回路C 1 6 0 は、内部情報レジスタC 1 6 1 を備えており、当該内部情報レジスタC 1 6 1 には、乱数生成回路C 1 4 0 で乱数更新周期を決める外部クロック（カウントクロック）の周期の異常、および乱数の更新に関する異常、さらに、直前に発生したユーザリセットのリセット要因の情報等が格納される。20

#### 【0055】

クロック回路C 2 1 0 は、水晶発振器（不図示）から外部クロック入力端子（E X 端子）を介して入力される外部クロック（この例では、2 4 M H z のクロック）を所定の分周比（例えば、1 / 2 ）で分周し、分周後のシステムクロック（この例では、1 2 M H z のクロック）をこの主制御チップC 内部の各回路に供給する。また、このシステムクロックをシステムクロック出力端子（C L K O 端子）を介して主制御チップC 外部の周辺制御回路に出力する。

#### 【0056】

乱数生成回路C 1 4 0 は、乱数を更新するためのクロック信号（カウントクロック）を用いて、乱数のラッチ信号を受信したときにこの更新された乱数を乱数レジスタ内に保持するものである。本実施形態では、水晶発振器から外部クロック入力端子（R C K 端子）を介して入力される外部クロック信号を所定の分周比（例えば、1 / 2 ）で分周してこのカウントクロックに用いているが、主制御チップC 内部のクロック信号を用いることもでき、この場合は水晶発振器は不要となる。乱数レジスタに保持された値は、乱数として読み出して使用することができる。尚、乱数レジスタから乱数を読み出すと、乱数レジスタが次の乱数をラッチすることを許容する許容状態とすることができます。30

#### 【0057】

照合用ブロックC 2 3 0 は、主制御チップC が型式認定で合格した正規のものかどうかの真贋検査であるセキュリティチェックを実行するものであり、S C 端子及びB R C 端子を介して当該セキュリティチェックに係る信号を外部端子板に送信又は外部端子板から受信し得るよう構成されている。40

#### 【0058】

固有情報C 2 4 0 には、主制御チップC の製造時に書き込まれた固有の識別番号が格納されており、当該識別番号は書き換えができないよう構成されている。また、演算回路C 2 5 0 は、四則演算や論理演算を実行する回路である。

#### 【0059】

<メモリマップ>

次に、図7を用いて、図6に示す主制御チップC のメモリマップの一例について説明する。当該メモリマップには、「0 0 0 0 H」から「F F F F H」までのアドレス空間が示50

されている。このうち、「0000H」から「27FFFH」までの空間には内蔵ROMC110が割り当てられ、「2800H」から「28FFFH」までの空間には主制御チップC内の各回路に内蔵されているレジスタ領域が割り当てられ、「F000H」から「F2FFFH」までの空間には内蔵RAMC120が割り当てられ、「FDD0H」から「FDFBHF」までの空間にはXCSデコードエリア（与えられた機械語を内部表現として解釈することであるデコードを実行する領域）が割り当てられている。CPUC100に、これらの番地に対してアクセスする命令を実行させることにより、対応するハードウェアに対するアクセスを実行させることができる。

#### 【0060】

尚、内蔵ROMC110は、主として遊技の進行を制御する領域である第1ROM領域と、主としてエラー関連等の遊技の正常な進行とは異なる処理を制御する領域である第2ROM領域と、を有しており、「0000H」から「1FFFH」までの空間には第1ROM領域が割り当てられ、「2000H」から「27FFFH」までの空間には第2ROM領域が割り当てられている。尚、第1ROM領域は、第2ROM領域よりも容量が大きくなるよう構成されている（換言すれば、第1ROM領域内に存在しCPUC100からアクセスされるデータ容量は、第2ROM領域内に存在しCPUC100からアクセスされるデータ容量よりも大きくなるよう構成されている）。

#### 【0061】

また、第1ROM領域は、プログラムコード（CPUC100に対する命令コードセット）が格納されている第1制御領域と、プログラムが使用する（このプログラムコードに基づくCPUC100の処理によって読みだされる）プログラムデータが格納されている第1データ領域と、各種識別情報（会社名、製造日、型式名等）が格納される領域と、主制御チップCを動作させる際に用いられる各種設定（乱数生成回路C140の動作設定、ウォッヂドッグタイマC222の動作設定等）が格納されているプログラム管理エリアとを有している。尚、同図にて、第1ROM領域におけるメモリマップイメージを図示しておくが、各領域のバイト数や未使用領域の有無はあくまでも一例である。

#### 【0062】

また、第2ROM領域は、プログラムコード（CPUC100に対する命令コードセット）が格納されている第2制御領域と、プログラムが使用する（このプログラムコードに基づくCPUC100の処理によって読みだされる）プログラムデータが格納されている第2データ領域と、を有しており、第2制御領域は、第1制御領域よりも容量が小さくなるよう構成されており（換言すれば、第2制御領域内に存在しCPUC100からアクセスされるプログラムコード容量は、第1制御領域内に存在しCPUC100からアクセスされるプログラムコード容量よりも小さくなり）、第2データ領域は、第1データ領域よりも容量が小さくなるよう構成されている（換言すれば、第2データ領域内に存在しCPUC100からアクセスされるプログラムデータ容量は、第1データ領域内に存在しCPUC100からアクセスされるプログラムデータ容量よりも小さくなる）。

#### 【0063】

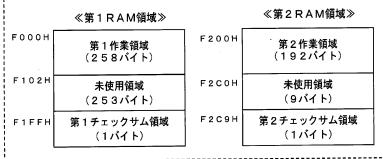

他方、内蔵RAMC120は、主として遊技の進行に基づく情報を格納する領域である第1RAM領域と、主としてエラー関連等の遊技の正常な進行とは異なる処理に基づく情報を格納する領域である第2RAM領域と、プログラムが内部的にデータを保存しておく必要がある場合使用されるスタッケリアと、を有しており、「F000H」から「F1FFFH」までの空間には第1RAM領域が割り当てられ、「F200H」から「F2C9H」までの空間には第2RAM領域が割り当てられ、「F2CAH」から「F2FFFH」までの空間にはスタッケリアが割り当てられている（但し、各領域のバイト数はあくまでも一例である）。

#### 【0064】

また、第1RAM領域は、主として遊技の進行に係る情報を一時記憶するための作業領域である第1作業領域を有しており、第2RAM領域は、主としてエラー関連等に係る情報を一時記憶するための作業領域である第2作業領域と、第1RAM領域及び第2RAM

10

20

30

40

50

領域に一時記憶された情報の誤り検出を行うための作業領域であるチェックサム領域を有している。尚、第1RAM領域は、第2RAM領域よりも容量が大きくなるよう構成されている。また、本実施形態においては、チェックサム領域は第2RAM領域のみが有しており（第1RAM領域は有しておらず）、当該チェックサム領域が第1RAM領域と第2RAM領域との双方の（双方に一時記憶された情報を通算した）チェックサムを管理するよう構成されている。また、本実施形態においては、後述するように、チェックサムを算出する際、未使用領域をも含めて算出しているが、これには限定されず、未使用領域を除いた領域（第1作業領域及び第2作業領域）についてチェックサムを算出するよう構成してもよい。また、誤り検出を行う手法は、チェックサムチェックを行う手法に限らず、その他の手法（例えば、パリティチェック等）を行う手法を用いてもよく、その場合には、当該チェックサム領域が、これら手法を用いる際に必要となる誤り検出用の情報（例えば、パリティビット等）を格納する領域となる。

#### 【0065】

尚、各種識別情報（会社名、製造日、型式名等）が格納される領域のアドレスは、内蔵RAMのアドレス以降としても何ら問題ない。また、未使用領域となっているアドレスも変更しても問題ないが、第1データ領域と第2制御領域との間（間のアドレス）には未使用領域を設けることが好適である。即ち、図7に示すようなメモリマップ構成である場合、第1制御領域内に存在しCPU C100からアクセスされるプログラムコードと、第2制御領域内に存在しCPU C100からアクセスされるプログラムコードとは、メモリマップ上において離隔して（アドレスが連続しない配置で）配置されており、未使用領域を間に挟んでいるため、プログラムソースコード上又はダンプリスト上において、双方のプログラムコードの配置位置を視覚上明確に切り分けることができる（その他、未使用領域を間に挟んでいる場合には、同様のことがいえる）。

#### 【0066】

ここで、主制御基板Mが搭載するROMに関しては、不正行為によって改造されたプログラム等を書き込まれることを防止するため、未使用的領域（充填されていない領域）を設けないよう構成することが好適である（例えば、未使用領域を全て0によって充填、使用している領域を若い番地に詰めて書き込む、等）。また、第1制御領域及び第1データ領域には、ノイズや不正行為によって、通常時には参照しないデータを参照してしまうことを防止するため、未使用的データ（例えば、スペック違いの遊技機において参照するデータや、開発段階でのテストにのみ使用するデータ等）を設けないよう構成することが好適である。また、第1制御領域、第1データ領域、第2制御領域、第2データ領域、第1作業領域及び第2作業領域は、若い番地に詰めて領域を使用し、当該領域内（当該領域内のアドレス）に未使用的領域を設けない（例えば、「0000H」～「0FA7H」の範囲となっている第1制御領域内の、「0010H」～「0050H」を未使用領域としない）よう構成することが好適である。尚、本例における、未使用領域は、すべてのビットが「0」となっており、当該未使用領域以外の領域は、いずれかのビットが「1」となっている（「0」ではなくなっている）。

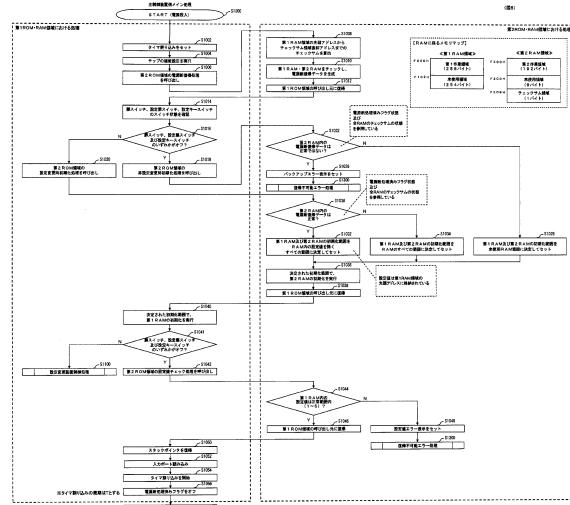

#### 【0067】

次に、図8～31は、本実施形態における、主制御基板Mが行う一般的な処理の流れを示したフローチャートである。はじめに、これら処理の流れを示したフローチャートにおいては、第1ROM領域にて配置されているプログラムコード及びプログラムデータに基づき、CPU C100が処理を実行する場合、もしくは、その処理結果をCPU C100内のレジスタ（レジスタ領域）や第1RAM領域へ格納（更新）したり、第1ROM領域にて配置されているプログラムコードに基づくCPU C100の処理にてその処理結果を参照する場合を、「第1ROM・RAM領域における処理」として点線で囲んで図示し、「第1ROM・RAM領域内のデータに基づき」CPU C100が処理を実行する旨を記載している。また、これら処理の流れを示したフローチャートにおいては、第2ROM領域にて配置されているプログラムコード及びプログラムデータに基づき、CPU C100が処理を実行する場合、もしくは、その処理結果をCPU C100内のレジスタ（レジス

10

20

30

40

50

タ領域)や第2RAM領域へ格納(更新)したり、第2ROM領域にて配置されているプログラムコードに基づくCPUC100の処理にてその処理結果を参照する場合を、「第2ROM・RAM領域における処理」として点線で囲んで図示し、「第2ROM・RAM領域内のデータに基づき」CPUC100が処理を実行する旨を記載している。

#### 【0068】

また、フローチャートは主に、処理ステップ(長方形にて図示)、判断(ひし形にて図示)、流れ線(矢印)、開始・終了・復帰等を示す端子(角丸長方形にて図示)によって構成されている。また、処理ステップの内、別のフローチャートにて詳細を図示している場合、当該別のフローチャートを参照するものをサブルーチン(左右の線が二重線である長方形にて図示)として図示している。ここで、遊技機の開発段階においては、スペック違いの遊技機を同時に開発することも行われているが、本例においては、メイン側の処理内に、スペック違いの遊技機で実行するサブルーチン(通常は使用しないサブルーチン)を残さないよう構成しており、ノイズや不正行為によって、通常時には実行されない未使用サブルーチンに係る処理が実行されることを防止している。10

#### 【0069】

そして、これらの動きに沿わない場合であり、例えば、第1ROM領域にて配置されているプログラムコードに基づくCPUC100の処理にて、第2RAM領域を更新又は参照する場合や、逆に、第2ROM領域にて配置されているプログラムコードに基づくCPUC100の処理にて、第1RAM領域を更新又は参照する場合には、その更新・参照先がいずれのものであるかを特記している(又は、これらの動きに沿う場合であっても、明確化のため必要に応じて特記している場合がある)。尚、以下に示す実施形態における処理の動きを概念的に纏めておくと、次のようなケースに分かれる。20

#### 【0070】

<動作1> 第1ROM領域(特に、第1制御領域)にて配置されているプログラムコードに基づくCPUC100の処理によって、第1ROM領域(特に、第1データ領域)にて配置されているプログラムデータが読みだされる、又は、第2ROM領域(特に、第2制御領域)にて配置されているプログラムコードに基づくCPUC100の処理によって、第2ROM領域(特に、第2データ領域)にて配置されているプログラムデータが読みだされる。但し、第1ROM領域(特に、第1制御領域)にて配置されているプログラムコードに基づくCPUC100の処理によっては、第2ROM領域(特に、第2データ領域)にて配置されているプログラムデータが読みだされない、及び、第2ROM領域(特に、第2制御領域)にて配置されているプログラムコードに基づくCPUC100の処理によっては、第1ROM領域(特に、第1データ領域)にて配置されているプログラムデータが読みだされない。30

#### 【0071】

<動作2> 第1ROM領域にて配置されているプログラムコード及びプログラムデータに基づくCPUC100の処理にて、第1RAM領域を更新及び参照する。また、第2ROM領域にて配置されているプログラムコード及びプログラムデータに基づくCPUC100の処理にて、第2RAM領域を更新及び参照する。40

#### 【0072】

<動作3> 第1ROM領域にて配置されているプログラムコードにおける呼び出し命令(例えば、ニーモニックでいうCALL命令)によって、第2ROM領域にて配置されているプログラムコードに基づくCPUC100の処理が実行され得るが、第2ROM領域にて配置されているプログラムコードにおける呼び出し命令(例えば、ニーモニックでいうCALL命令)によって、第1ROM領域にて配置されているプログラムコードに基づくCPUC100の処理が実行され得ない。即ち、第1ROM領域にて配置されているプログラムコードと第2ROM領域にて配置されているプログラムコードとは、主従関係にあり、主となる第1ROM領域にて配置されているプログラムコードにおける呼び出し命令があつてはじめて、従となる第2ROM領域にて配置されているプログラムコードに基づくCPUC100の処理が実行され得る状態となる。50

**【0073】**

<動作4>主となる第1ROM領域にて配置されているプログラムコードにおける呼び出し命令があって、従となる第2ROM領域にて配置されているプログラムコードに基づくCPUC100の処理が実行される場合、当該従となる第2ROM領域にて配置されているプログラムコードに基づくCPUC100の処理の実行時には、当該呼び出し命令があった時点で記憶されている情報（例えば、レジスタ領域内の情報）を参照する。或いは、当該従となる第2ROM領域にて配置されているプログラムコードに基づくCPUC100の処理が実行された後、当該主となる第1ROM領域にて配置されているプログラムコードに基づくCPUC100の処理に復帰する場合、当該主となる第1ROM領域にて配置されているプログラムコードに基づくCPUC100の処理の実行時には、当該復帰した時点で記憶されている情報（例えば、レジスタ領域内の情報）を参照する。

10

**【0074】**

<動作5>前述の<動作4>において、レジスタ領域内の情報を参照しない場合には、<動作5-1>主となる第1ROM領域にて配置されているプログラムコードに基づくCPUC100の処理結果を、第1RAM領域に格納しておき、従となる第2ROM領域にて配置されているプログラムコードに基づくCPUC100の処理の実行時には、当該第1RAM領域に格納された処理結果を参照及び更新可能としておく（当該主となる第1ROM領域にて配置されているプログラムコードに基づくCPUC100の処理の復帰時には、当該更新された第1RAM領域を参照する）、<動作5-2>主となる第1ROM領域にて配置されているプログラムコードに基づくCPUC100の処理結果を、第1RAM領域に格納しておき、従となる第2ROM領域にて配置されているプログラムコードに基づくCPUC100の処理の実行時には、当該第1RAM領域に格納された処理結果を参照可能としておく、且つ、従となる第2ROM領域にて配置されているプログラムコードに基づくCPUC100の処理結果を、第2RAM領域に格納しておき、当該主となる第1ROM領域にて配置されているプログラムコードに基づくCPUC100の処理の復帰時には、当該第2RAM領域に格納された処理結果を参照可能としておく、のいずれかで動作する。

20

**【0075】**

以上のような前提（説明を行うまでの前提）に基づき、主制御基板Mが行う一般的な処理の流れについて説明を行っていくこととするが、上記した<動作1>乃至<動作3>は必須となる前提となる一方で、<動作4>と<動作5>とは、CPUC100での処理結果を主従関係にあるプログラムコード間で、如何にして引き継いでいくかの実装方法によって取捨選択できる前提であるため、以下の処理の流れにおいて、<動作4>及び<動作5>のいずれか一方のみで例示されていた場合であっても、他方で代替することが可能であることを予め補足しておく。

30

**【0076】**

まず、図8は、回胴式遊技機Pの電源を投入した後（或いはシステムリセットやユーザリセット時において）、主制御基板MのCPUC100にて初めて実行される処理の流れを示したフローチャートである。この場合、一般的には、内蔵ROMC110の0000Hとなるアドレス（即ち、第1制御領域）に配置されているプログラムコードから順番に実行していくこととなる。尚、主制御基板Mにおける主制御チップCの構成によっては、回胴式遊技機Pの電源を投入した後（或いはシステムリセットやユーザリセット時において）、前述したセキュリティチェックを実行するよう構成される場合があり、当該セキュリティチェックを実行するためのプログラムコードが先に実行されるよう構成される場合も想定できるが、そのような構成であっても、本実施形態において示す第1制御領域に配置されているプログラムコードから順番に実行していくことには変わりない（加えて、内蔵ROMC110の初期アドレスが、0000Hではない場合であっても、前述したメモリマップの全体構成に変わりない=各アドレスが適宜ずれるのみ）。また、本実施形態においては、内蔵RAMC120に格納されているデータが電源断時においても保持されるよう、内蔵RAMC120に対してバックアップ電源が供給されるよう構成されてい

40

50

るものとしている。

#### 【0077】

##### <第1ROM・RAM領域における処理>

まず、ステップ1000で、回胴式遊技機Pの電源を投入した後、ステップ1002で、CPUC100は、第1ROM・RAM領域内のデータに基づき、タイマ割り込みをセットする(ここでは、タイマ割り込みの種類をセットするのみであり、以降の処理において、タイマ割り込みが開始されると定期的に後述するタイマ割り込み時処理に係るフローチャートが実行される)。次に、ステップ1004で、CPUC100は、第1ROM・RAM領域内のデータに基づき、主制御チップCの機能設定を実行する。次に、ステップ1006で、CPUC100は、第2ROM領域の電源断復帰処理を呼び出す。

10

#### 【0078】

##### <第2ROM・RAM領域における処理>

次に、ステップ1008で、CPUC100は、第1ROM・RAM領域内のデータに基づき、第1RAM領域の先頭アドレスからチェックサム領域直前のアドレスまでのチェックサムを算出する。次に、ステップ1010で、CPUC100は、第1ROM・RAM領域内のデータに基づき、第1RAM及び第2RAMをチェックし(例えば、当該算出したチェックサムとチェックサム領域に保持されているチェックサムデータに基づき、電源断・電源断復帰により内蔵RAMC120に格納されているデータが正しく保持されているか否かをチェックし)、電源断復帰データを生成する(当該チェック結果やステップ1800の電源断時処理にて実行した処理に基づいて生成し、第2RAM領域内で保持する)。次に、ステップ1012で、CPUC100は、第2ROM・RAM領域内のデータに基づき、第1ROM領域の呼び出し元に復帰し、ステップ1014に移行する。

20

#### 【0079】

##### <第1ROM・RAM領域における処理>

次に、ステップ1014で、CPUC100は、第1ROM・RAM領域内のデータに基づき、扉スイッチD80、設定扉スイッチM10及び設定キースイッチM20のスイッチ状態を確認する。次に、ステップ1016で、CPUC100は、第1ROM・RAM領域内のデータを参照し、扉スイッチD80、設定扉スイッチM10及び設定キースイッチM20のいずれかがオフであるか否かを判定する。ステップ1016でYesの場合、ステップ1018で、CPUC100は、第1ROM・RAM領域内のデータに基づき、第2ROM領域内の非設定変更時初期化処理を呼び出し、ステップ1022に移行する。他方、ステップ1016でNoの場合には、ステップ1020で、CPUC100は、第1ROM・RAM領域内のデータに基づき、第2ROM領域内の設定変更時初期化処理を呼び出し、ステップ1030に移行する。

30

#### 【0080】

##### <第2ROM・RAM領域における処理>

次に、ステップ1022で、CPUC100は、第2ROM・RAM領域内のデータに基づき、第1RAM内の電源断処理済みフラグのオン・オフ(ステップ1904でオンとなる)及び全RAMのチェックサム状態(ステップ1010でのチェック結果)を参照し、第2RAM内の電源断復帰データは正常ではないか否かを判定する。ステップ1022でYesの場合、ステップ1026で、CPUC100は、第2ROM・RAM領域内のデータに基づき、バックアップエラー表示をセットする(例えば、レジスタ領域内にエラー番号をセットする)。次に、ステップ1300で、CPUC100は、第2ROM・RAM領域内のデータに基づき、後述する、復帰不可能エラー処理を実行する。他方、ステップ1022でNoの場合、ステップ1028で、CPUC100は、第2ROM・RAM領域内のデータに基づき、第1RAM及び第2RAMの初期化範囲を未使用RAM範囲(図中欄外にて示す、第1RAM領域における未使用領域と第2RAM領域における未使用領域)に決定してセットし(例えば、レジスタ領域内にセットし)、ステップ1036に移行する。

40

#### 【0081】

50

他方、ステップ1020の処理の後、ステップ1030で、CPUC100は、第2ROM・RAM領域内のデータに基づき、第1RAM内の電源断処理済みフラグのオン・オフ（ステップ1904でオンとなる）及び全RAMのチェックサム状態（ステップ1010でのチェック結果）を参照し、第2RAM内の電源断復帰データは正常であるか否かを判定する。ステップ1030でYesの場合、ステップ1032で、CPUC100は、第2ROM・RAM領域内のデータに基づき、第1RAM及び第2RAMの初期化範囲をRAM内における設定値を除くすべての範囲に決定してセットし（例えば、レジスタ領域内にセットし）、ステップ1036に移行する。尚、設定値は第1RAM領域の先頭アドレスに格納されている。他方、ステップ1030でNoの場合、ステップ1034で、CPUC100は、第2ROM・RAM領域内のデータに基づき、第1RAM及び第2RAMの初期化範囲をRAMのすべての範囲に決定してセットし（例えば、レジスタ領域内にセットし）、ステップ1036に移行する。

10

#### 【0082】

次に、ステップ1036で、CPUC100は、第2ROM・RAM領域内のデータに基づき、決定された初期化範囲で第2RAM領域のみの初期化を実行する。次に、ステップ1038で、CPUC100は、第2ROM・RAM領域内のデータに基づき、第1ROM領域の呼び出し元に復帰し、ステップ1040に移行する。

#### 【0083】

<第1ROM・RAM領域における処理>

次に、ステップ1040で、CPUC100は、第1ROM・RAM領域内のデータに基づき、ステップ1028、ステップ1032又はステップ1034にて決定された初期化範囲で、第1RAM領域のみの初期化を実行する。次に、ステップ1041で、CPUC100は、第1ROM・RAM領域内のデータに基づき、扉スイッチD80、設定扉スイッチM10及び設定キースイッチM20のいずれかがオフであるか否かを判定する。ステップ1041でYesの場合、ステップ1042で、CPUC100は、第1ROM・RAM領域内のデータに基づき、第2ROM領域内の設定値チェック処理を呼び出し、ステップ1044に移行する。他方、ステップ1041でNoの場合には、ステップ1100で、CPUC100は、第1ROM・RAM領域内のデータに基づき、後述する、設定変更装置制御処理（設定変更処理とも称す）を実行する。

20

#### 【0084】

<第2ROM・RAM領域における処理>

次に、ステップ1044で、CPUC100は、第2ROM・RAM領域内のデータに基づき、第1RAM領域内を参照し、第1RAM領域内の設定値に係るデータは正常範囲内（本例では、1～6）であるか否かを判定する。ステップ1044でYesの場合、ステップ1046で、CPUC100は、第2ROM・RAM領域内のデータに基づき、第1ROM領域の呼び出し元に復帰し、ステップ1050に移行する。他方、ステップ1044でNoの場合、ステップ1048で、CPUC100は、第2ROM・RAM領域内のデータに基づき、設定値エラー表示（例えば、払出数表示装置D190に表示されることとなる）をセットする（例えば、レジスタ領域内にセットする）。次に、ステップ1300で、CPUC100は、第2ROM・RAM領域内のデータに基づき、後述する復帰不可能エラー処理を実行する。

40

#### 【0085】

<第1ROM・RAM領域における処理>

次に、ステップ1050で、CPUC100は、第1ROM・RAM領域内のデータに基づき、電源断時の処理（ステップ1902）にて保存したスタックポインタに係るデータに基づき、スタックポインタを復帰する。次に、ステップ1052で、CPUC100は、第1ROM・RAM領域内のデータに基づき、入力ポートの読み込みを実行する。次に、ステップ1054で、CPUC100は、第1ROM・RAM領域内のデータに基づき、ステップ1002にてセットしたタイマ割り込みを開始する。次に、ステップ1056で、CPUC100は、第1ROM・RAM領域内のフラグエリア内にある電源断処理

50

済みフラグをオフにし、復帰したスタックポインタに従い電源断時の処理に復帰する。

#### 【0086】

尚、不図示ではあるが、主制御基板Mが搭載する一時記憶領域（RAM領域等）の初期値（処理開始時の値）は、特別遊技が実行される値とならないよう構成することが好適である（プログラムの処理開始直後に、ノイズや不正行為により、特別遊技の実行判定を行う処理を実行してしまった場合に特別遊技が誤って実行されることを防止するため）。また、不図示ではあるが、主制御基板MのRAM領域内に当選乱数等の乱数を記憶する場合には、専用の記憶領域を確保し、乱数に係る情報を記憶しているバイト内には当該乱数に係る情報のみを記憶する（各種タイマ値等、その他の情報を記憶しない）よう構成することが好適である（同じ1バイト内に記憶した別のデータを操作する際に、ノイズ等によって乱数に係る情報が書き換わってしまうことを防止するため）。 10

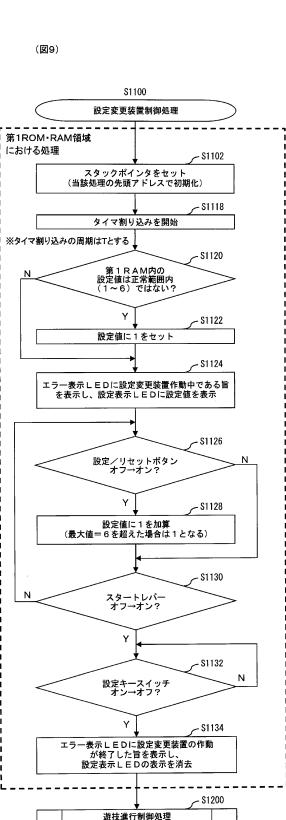

#### 【0087】

##### <第1ROM・RAM領域における処理>

次に、図9は、図8におけるステップ1100のサブルーチンに係る、設定変更装置制御処理のフローチャートである。まず、ステップ1102で、CPUC100は、第1ROM・RAM領域内のデータに基づき、スタックポインタをセットする（当該処理の先頭アドレスで初期化する）。次に、ステップ1118で、CPUC100は、第1ROM・RAM領域内のデータに基づき、タイマ割り込みを開始する。次に、ステップ1120で、CPUC100は、第1ROM・RAM領域内のデータを参照し、第1RAM領域内の設定値は正常範囲内（本例では、1～6）ではないか否かを判定する。ステップ1120でYesの場合、ステップ1122で、CPUC100は、第1ROM・RAM領域内のデータに基づき、設定値に所定値（例えば、1=遊技者にとって最も不利となる値）をセットし、ステップ1124に移行する。他方、ステップ1120でNoの場合にもステップ1124に移行する。次に、ステップ1124で、CPUC100は、第1ROM・RAM領域内のデータに基づき、エラー表示LED（不図示）に設定変更装置作動中である旨を表示し、設定表示LED（不図示）に設定値を表示し、ステップ1126に移行する。

20

#### 【0088】

次に、ステップ1126で、CPUC100は、第1ROM・RAM領域内のデータに基づき、設定リセットボタンM30がオフからオンに切り替わったか否かを判定する。ステップ1126でYesの場合、ステップ1128で、CPUC100は、第1ROM・RAM領域内のデータに基づき、現在の設定値に1を加算し（加算した結果設定値が6を超えた場合には、設定値は1となる）、ステップ1130に移行する。尚、ステップ1126でNoの場合にも、ステップ1130に移行する。次に、ステップ1130で、CPUC100は、第1ROM・RAM領域内のデータに基づき、スタートレバーD50がオフからオンに切り替わったか否かを判定する。ステップ1130でYesの場合、ステップ1132で、CPUC100は、第1ROM・RAM領域内のデータに基づき、設定キースイッチM20がオンからオフに切り替わったか否かを判定する。ステップ1132でNoの場合には、ステップ1132の処理をループする。他方、ステップ1132でYesの場合、ステップ1134で、CPUC100は、第1ROM・RAM領域内のデータに基づき、エラー表示LED（不図示）に設定変更装置の作動が終了した旨を表示し、設定表示LED（不図示）の設定値の表示を消去し、ステップ1200の遊技進行制御処理に移行する。尚、ステップ1130でNoの場合には、ステップ1126に移行する。

30

40

#### 【0089】

##### <第1ROM・RAM領域における処理>

次に、図10は、図9におけるステップ1200のサブルーチンに係る、遊技進行制御処理（1枚目）のフローチャートである。まず、ステップ1202で、CPUC100は、第1ROM・RAM領域内のデータに基づき、スタックポインタをセットする（当該処理の先頭アドレスで初期化する）。次に、ステップ1204で、CPUC100は、第1

50

R O M ・ R A M 領域内のデータに基づき、当該ゲームに必要な第1 R A M 領域内のデータ（例えば、ベット上限数、入賞の有効ライン、等）をセットする。次に、ステップ1206で、C P U C 1 0 0 は、第1 R O M ・ R A M 領域内のデータに基づき、当該ゲームにおける遊技状態（例えば、通常遊技中、大当たり遊技中、再遊技確率変動遊技中、A T 遊技中等）をセットする。次に、ステップ1208で、C P U C 1 0 0 は、第1 R O M ・ R A M 領域内のデータに基づき、メダル払出装置Hが遊技メダルで満杯ではないか否かを判定する。具体的には、メダル払出装置Hから溢れ出たメダルを格納するサブタンク（不図示）を備え、サブタンクに設けられた複数の満杯検知センサによる電流の導通／非導通にて判定する（メダルを介して電流が導通した場合には、満杯と判定する）。ステップ1208でY e s の場合、ステップ1218に移行する。

10

#### 【0090】

他方、ステップ1208でN o の場合、ステップ1210で、C P U C 1 0 0 は、第1 R O M ・ R A M 領域内のデータに基づき、メダル満杯エラーフラグをオンにする（例えば、第1 R A M 領域のメダル満杯エラーフラグ領域内をオンに相当する値で更新する）。次に、ステップ1212で、C P U C 1 0 0 は、第1 R O M ・ R A M 領域内のデータに基づき、メダル満杯エラーに対応したエラー番号の表示を7セグLED（例えば、貯留表示L E D又は獲得枚数L E D）で実行する。次に、ステップ1214で、C P U C 1 0 0 は、第1 R O M ・ R A M 領域内のデータを参照して、メダル満杯エラーが解除されたか否か（例えば、サブタンクによる電流が非導通、且つ、設定／リセットボタンM 3 0 が押下されたか否か）を判定する。ステップ1214でY e s の場合、ステップ1216で、C P U C 1 0 0 は、第1 R O M ・ R A M 領域内のデータに基づき、メダル満杯エラーフラグをオフにし（例えば、第1 R A M 領域のメダル満杯エラーフラグ領域内をオフに相当する値で更新し）、ステップ1218に移行する。他方、ステップ1214でN o の場合には、ステップ1212に移行する。次に、ステップ1218で、C P U C 1 0 0 は、第1 R O M ・ R A M 領域内のデータに基づき、メダル投入受付を許可し（再遊技の次ゲームにおいては自動にて投入動作が実行されることとなる）、次の処理（ステップ1220の処理）に移行する。ここで、ステップ1218では、プロッカD 1 0 0 のオン処理（メダル流路が形成する処理）を行う。具体的には、前回遊技で再遊技役が成立した場合には、現在の貯留数（クレジット）が所定値（本例では、50枚）未満であることを条件として、プロッカD 1 0 0 のオン処理を実行する。換言すると、現在の貯留数（クレジット）が所定値である場合には、プロッカD 1 0 0 のオン処理を実行しない。一方、前回遊技で再遊技役が成立しなかった場合には、一律にプロッカD 1 0 0 のオン処理を実行するようにしている。このように構成することにより、再遊技が成立した場合であっても貯留数（クレジット）が所定値に達していない場合には、遊技メダルが投入できるように構成され、通常遊技状態よりも再遊技確率の高いR T 状態に滞在しているときや、見た目では再遊技とは分かり辛い再遊技（小役に見せかけた再遊技：無効ライン上にベル・ベル・ベルや、左リールにチェリーが停止した図柄組合せ）が停止した場合であっても、遊技者はリズム良く（違和感なく）遊技を行うことができる。

20

#### 【0091】

<第1 R O M ・ R A M 領域における処理>

30

次に、図11は、図9におけるステップ1200のサブルーチンに係る、遊技進行制御処理（2枚目）のフローチャートである。まず、ステップ1220で、C P U C 1 0 0 は、第1 R O M ・ R A M 領域内のデータに基づき、遊技メダルがベットされていない、且つ、クレジットが存在していないか否かを判定する。ステップ1220でY e s の場合、ステップ1221で、C P U C 1 0 0 は、第1 R O M ・ R A M 領域内のデータに基づき、設定表示条件を充足している（例えば、扉スイッチD 8 0 、設定扉スイッチM 1 0 、設定キーイッチM 2 0 がすべてオンとなると当該条件を充足する）か否かを判定する。ステップ1221でY e s の場合、ステップ1222で、C P U C 1 0 0 は、第1 R O M ・ R A M 領域内のデータに基づき、設定表示L E D（不図示だが、払出数表示装置D 1 9 0 、クレジット数表示装置D 2 0 0 、投入数表示灯D 2 1 0 としてもよい）に設定値を表示し、

40

50

ステップ1221に移行する。ステップ1220又はステップ1221でNoの場合、ステップ1224で、CPUC100は、第1ROM・RAM領域内のデータに基づき、遊技メダルの投入及び精算に係る管理を実行する。次に、ステップ1225で、CPUC100は、第1ROM・RAM領域内のデータに基づき、遊技メダルの受付可能枚数を確認する。次に、ステップ1226で、CPUC100は、第1ROM・RAM領域内のデータに基づき、プロッカD100がオンか否かを判定する。ステップ1226でYesの場合、ステップ1227で、CPUC100は、第1ROM・RAM領域内のデータに基づき、第1投入センサD20s又は第2投入センサD30sがオンであるか否かを判定する（第1投入センサD20s又は第2投入センサD30sがオンとなると、遊技メダルを1枚受け付けたと判定する）。ステップ1227でYesの場合、ステップ1228で、CPUC100は、第1ROM・RAM領域内のデータに基づき、第2ROM領域のメダル投入エラー検出処理を呼び出し、ステップ1400に移行する。

#### 【0092】

<第2ROM・RAM領域における処理>

次に、ステップ1400で、CPUC100は、第2ROM・RAM領域内のデータに基づき、後述する、メダル投入エラー検出処理を実行する。次に、ステップ1229で、CPUC100は、第2ROM・RAM領域内のデータに基づき、第1ROM領域の呼び出し元に復帰し、ステップ1230に移行する。

#### 【0093】

<第1ROM・RAM領域における処理>

次に、ステップ1230で、CPUC100は、第1ROM・RAM領域内のデータに基づき、第1投入センサD20s及び第2投入センサD30sがオフであるか否かを判定する（第1投入センサD20s又は第2投入センサD30sがオンとなった後、第1投入センサD20s及び第2投入センサD30sがオフとなると、受け付けた1枚の遊技メダルが第1投入センサD20s及び第2投入センサD30sを通過したと判定する）。ステップ1230でYesの場合、ステップ1231で、CPUC100は、第1ROM・RAM領域内のデータに基づき、1枚の正常な遊技メダルの投入を受け付けたと判定する。不図示であるが、ステップ1231の後、CPUC100は、第1ROM・RAM領域内のデータに基づき、クレジットが上限数（本例では、50）、且つ、ベット数が最大数（本例では、3）ではないか否かを判定し、Yesと判定した場合にはプロッカD100をオフ（メダル流路を形成しない状態）に制御する。尚、ステップ1230でNoの場合には、ステップ1228に移行し、ステップ1226またはステップ1227でNoの場合には、ステップ1232に移行する。

#### 【0094】

次に、ステップ1232で、CPUC100は、第1ROM・RAM領域内のデータに基づき、精算ボタンD60の操作があったか否かを判定する。ステップ1232でYesの場合、ステップ1233で、CPUC100は、第1ROM・RAM領域内のデータに基づき、クレジットの残り枚数又はベットされている遊技メダルが存在するか否かを判定する。ステップ1233でYesの場合、ステップ1234で、CPUC100は、第1ROM・RAM領域内のデータに基づき、ホッパ駆動フラグ（第1RAM領域内のフラグであり、ホッパモータH80を駆動している際にオンとするフラグ）をオンにし、遊技メダル1枚の払出を実行する。次に、ステップ1236で、CPUC100は、第1ROM・RAM領域内のデータを参照し、第1払出センサH10s又は第2払出センサH20sがオンであるか否かを判定する（第1払出センサH10s又は第2払出センサH20sがオンとなると、遊技メダル1枚の払出動作が行われていると判定する）。ステップ1236でYesの場合、ステップ1238で、CPUC100は、第1ROM・RAM領域内のデータに基づき、第2ROM領域内のメダル払出エラー検出処理を呼び出し、ステップ1450に移行する。ここで、フローチャート上には明記してはいないが、前回遊技が再遊技役であった場合にはクレジットの残り枚数のみが精算の対象となる。

#### 【0095】

10

20

30

40

50

## &lt;第2ROM・RAM領域における処理&gt;

次に、ステップ1450で、CPUC100は、第2ROM・RAM領域内のデータに基づき、後述する、メダル払出エラー検出処理を実行する。次に、ステップ1240で、CPUC100は、第2ROM・RAM領域内のデータに基づき、第1ROM領域内の呼び出し元に復帰し、ステップ1247に移行する。

## 【0096】

## &lt;第1ROM・RAM領域における処理&gt;

他方、ステップ1236でNoの場合、ステップ1241で、CPUC100は、第1ROM・RAM領域内のデータに基づき、ホッパ駆動後（ステップ1234の処理のタイミング後）から所定時間（例えば、5秒）経過したか否かを判定する。具体的には、ホッパ駆動信号をホッパモータH80に送信している（ホッパモータH80が回転している）のにもかかわらず、メダルが払い出されていないと判定している状況が所定時間継続したか否かを判定する。ステップ1241でYesの場合、ステップ1242で、CPUC100は、第1ROM・RAM領域内のデータに基づき、メダル空エラーフラグをオンにする（例えば、第1RAM領域のメダル空エラーフラグ領域内をオンに相当する値で更新する）。次に、ステップ1244で、CPUC100は、第1ROM・RAM領域内のデータに基づき、メダル空エラー表示を実行する。次に、ステップ1245で、CPUC100は、第1ROM・RAM領域内のデータに基づき、メダル空エラーが解除されたか否か（例えば、設定／リセットボタンM30が押下されたか否か）を判定する。ステップ1245でYesの場合、ステップ1246で、CPUC100は、第1ROM・RAM領域内のフラグエリア内にある、メダル空エラーフラグをオフにし（例えば、第1RAM領域のメダル空エラーフラグ領域内をオフに相当する値で更新し）、ステップ1247に移行する。他方、ステップ1245でNoの場合、ステップ1244に移行する。

## 【0097】

## &lt;第1ROM・RAM領域における処理&gt;

次に、ステップ1247で、CPUC100は、第1ROM・RAM領域内のデータに基づき、第1払出センサH10s及び第2払出センサH20sがオフであるか否かを判定する（第1払出センサH10s又は第2払出センサH20sがオンとなった後、第1払出センサH10s及び第2払出センサH20sがオフとなると、払出動作が行われていた一枚の遊技メダルの払出動作が完了したと判定する）。ステップ1247でYesの場合、ステップ1248で、CPUC100は、第1ROM・RAM領域内のデータに基づき、ホッパ駆動フラグをオフにし、ステップ1233に移行する。尚、ステップ1241又はステップ1247でNoの場合には、ステップ1236に移行する。

## 【0098】

他方、ステップ1232又はステップ1233でNoの場合、ステップ1249で、CPUC100は、第1ROM・RAM領域内のデータに基づき、第2ROM領域の投入・払出エラー検出処理を呼び出し、ステップ1500に移行する。

## 【0099】

## &lt;第2ROM・RAM領域における処理&gt;

次に、ステップ1500で、CPUC100は、第2ROM・RAM領域内のデータに基づき、後述する、投入・払出エラー検出処理を実行する。次に、ステップ1250で、CPUC100は、第2ROM・RAM領域内のデータに基づき、第1ROM領域の呼び出し元に復帰し、ステップ1251に移行する。

## 【0100】

## &lt;第1ROM・RAM領域における処理&gt;

次に、ステップ1251で、CPUC100は、第1ROM・RAM領域内のデータに基づき、スタートレバーD50が有効であり（例えば、ゲームを開始するための規定枚数の遊技メダルが投入された等）、且つ、当該スタートレバーD50の操作があったか否かを判定する。ステップ1251でYesの場合、ステップ1252で、CPUC100は、第1ROM・RAM領域内のデータに基づき、乱数の取得、ブロックD100をオフに

10

20

30

40

50

する処理を実行した後に、第2ROM領域の設定値チェック処理を呼び出し、ステップ1253に移行する。

#### 【0101】

##### <第2ROM・RAM領域における処理>

次に、ステップ1253で、CPUC100は、第2ROM・RAM領域内のデータに基づき、第1RAM領域内の設定値は正常範囲内（本例では、1～6）であるか否かを判定する。ステップ1253でYesの場合、ステップ1254で、CPUC100は、第2ROM・RAM領域内のデータに基づき、第1ROM領域の呼び出し元に復帰し、次の処理（ステップ1257の処理）に移行する。他方、ステップ1253でNoの場合、ステップ1256で、CPUC100は、第2ROM・RAM領域内のデータに基づき、設定値エラー表示をセットする（例えば、レジスタ領域内にエラー番号をセットする）。次に、ステップ1300で、CPUC100は、第2ROM・RAM領域内のデータに基づき、後述する、復帰不可能エラー処理を実行する。10

#### 【0102】

##### <第1ROM・RAM領域における処理>

次に、図12は、図9におけるステップ1200のサブルーチンに係る、遊技進行制御処理（3枚目）のフローチャートである。まず、ステップ1257で、CPUC100は、第1ROM・RAM領域内のデータに基づき、内部抽選（当該ゲームにおいて入賞可能となる役を決定するための抽選）を開始する。次に、ステップ1258で、CPUC100は、第1ROM・RAM領域内のデータに基づき、全リール（リールM50）の回転を開始し、ステップ1260に移行する。次に、ステップ1260で、CPUC100は、第1ROM・RAM領域内のデータに基づき、引き込みポイント作成要求（回転している左リールM51、中リールM52、右リールM53の停止位置を決定するために要求され、停止順番や他のリールの停止位置に応じて適宜要求される）があったか否かを判定する。ステップ1260でYesの場合、ステップ1261で、CPUC100は、第1ROM・RAM領域内のデータに基づき、引き込みポイントを作成し、ステップ1262に移行する。他方、ステップ1260でNoの場合にも、ステップ1262に移行する。次に、ステップ1262で、CPUC100は、第1ROM・RAM領域内のデータに基づき、リール停止受付可否チェックを実行する。次に、ステップ1263で、CPUC100は、第1ROM・RAM領域内のデータに基づき、いずれかの停止ボタン（左停止ボタンD41、中停止ボタンD42、右停止ボタンD43）の操作があったか否かを判定する。ステップ1263でYesの場合、ステップ1264で、CPUC100は、第1ROM・RAM領域内のデータに基づき、操作があった停止ボタンに対応したリール（例えば、左停止ボタンD41には左リールM51が対応）の停止位置を決定し、ステップ1265に移行する。他方、ステップ1263でNoの場合にも、ステップ1265に移行する。次に、ステップ1265で、CPUC100は、第1ROM・RAM領域内のデータに基づき、全リール停止チェック処理を実行する。次に、ステップ1266で、CPUC100は、第1ROM・RAM領域内のデータに基づき、すべてのリール（左リールM51、中リールM52、右リールM53）が停止したか否かを判定する。ステップ1266でYesの場合、ステップ1267で、CPUC100は、第1ROM・RAM領域内のデータに基づき、第2ROM領域の表示判定チェック処理を呼び出し、ステップ1268に移行する。尚、ステップ1266でNoの場合、ステップ1260に移行する。203040

#### 【0103】

##### <第2ROM・RAM領域における処理>

次に、ステップ1268で、CPUC100は、第2ROM・RAM領域内のデータに基づき、第1RAM内の図柄停止位置データと、内部成立役停止可能位置データとを比較する。次に、ステップ1269で、CPUC100は、第2ROM・RAM領域内のデータを参照し、表示された図柄の組み合わせが正常であるか否かを判定する（内部抽選によって決定された入賞可能となる役と一致していなければ異常であると判定される）。ステップ1269でYesの場合、ステップ1500で、CPUC100は、第2ROM・R50

A M領域内のデータに基づき、後述する、投入・払出エラー検出処理を実行する。次に、ステップ1270で、CPUC100は、第2ROM・RAM領域内のデータに基づき、第1ROM領域の呼び出し元に復帰し、ステップ1274に移行する。他方、ステップ1269でNoの場合、ステップ1272で、CPUC100は、第2ROM・RAM領域内のデータに基づき、表示判定エラー表示をセットする（例えば、レジスタ領域内にセットする）。次に、ステップ1300で、CPUC100は、第2ROM・RAM領域内のデータに基づき、後述する、復帰不可能エラー処理を実行する。

#### 【0104】

##### <第1ROM・RAM領域における処理>

次に、ステップ1274で、CPUC100は、第1ROM・RAM領域内のデータに基づき、入賞による遊技メダルの払出処理を実行する。次に、ステップ1275で、CPUC100は、第1ROM・RAM領域内のデータに基づき、遊技メダルを払い出す入賞があったか否かを判定する（入賞によって獲得した遊技メダルが、クレジットの最大数（本例では、50）を超過した場合に、遊技メダルの払出が実行される）。ステップ1275でYesの場合、ステップ1276で、CPUC100は、第1ROM・RAM領域内のデータに基づき、ホッパ駆動フラグ（第1RAM領域内のフラグであり、ホッパモータH80を駆動している際にオンとするフラグ）をオンにし、遊技メダル1枚の払出を実行する。次に、ステップ1277で、CPUC100は、第1ROM・RAM領域内のデータに基づき、第1払出センサH10s又は第2払出センサH20sがオンであるか否かを判定する（第1払出センサH10s又は第2払出センサH20sがオンとなると、遊技メダル1枚の払出動作が行われていると判定する）。ステップ1277でYesの場合、ステップ1278で、CPUC100は、第1ROM・RAM領域内のデータに基づき、第2ROM領域内のメダル払出エラー検出処理を呼び出し、ステップ1450に移行する。

10

20

#### 【0105】

##### <第2ROM・RAM領域における処理>

次に、ステップ1450で、CPUC100は、第2ROM・RAM領域内のデータに基づき、後述する、メダル払出エラー検出処理を実行する。次に、ステップ1284で、CPUC100は、第2ROM・RAM領域内のデータに基づき、第1ROM領域内に呼び出し元に復帰し、ステップ1286に移行する。

30

#### 【0106】

##### <第1ROM・RAM領域における処理>

他方、ステップ1277でNoの場合、ステップ1279で、CPUC100は、第1ROM・RAM領域内のデータに基づき、ホッパ駆動後（ステップ1276の処理のタイミング後）から所定時間（例えば、5秒）経過したか否かを判定する。ステップ1279でYesの場合、ステップ1280で、CPUC100は、第1ROM・RAM領域内のデータに基づき、メダル空エラーフラグをオンにする（例えば、第1RAM領域のメダル空エラーフラグ領域内をオンに相当する値で更新する）。次に、ステップ1281で、CPUC100は、第1ROM・RAM領域内のデータに基づき、メダル空エラー表示を7セグLEDで実行する。次に、ステップ1282で、CPUC100は、第1ROM・RAM領域内のデータに基づき、メダル空エラーが解除されたか否か（例えば、設定／リセットボタンM30が押下されたか否か）を判定する。ステップ1282でYesの場合、ステップ1283で、CPUC100は、第1ROM・RAM領域内のデータに基づき、メダル空エラーフラグをオフにし（例えば、第1RAM領域のメダル空エラーフラグ領域内をオフに相当する値で更新し）、ステップ1286に移行する。他方、ステップ1282でNoの場合、ステップ1281に移行する。

40

#### 【0107】

##### <第1ROM・RAM領域における処理>

次に、ステップ1286で、CPUC100は、第1ROM・RAM領域内のデータに基づき、第1払出センサH10s及び第2払出センサH20sがオフであるか否かを判定する（第1払出センサH10s又は第2払出センサH20sがオンとなった後、第1払出

50

センサH10s及び第2揃出センサH20sがオフとなると、揃出動作が行われていた1枚の遊技メダルの揃出動作が完了したと判定する)。ステップ1286でYesの場合、ステップ1288で、CPUC100は、第1ROM・RAM領域内のデータに基づき、ホッパ駆動フラグをオフにし、ステップ1290に移行する。尚、ステップ1279又はステップ1286でNoの場合には、ステップ1277に移行する。次に、ステップ1290で、CPUC100は、第1ROM・RAM領域内のデータに基づき、当該入賞(ステップ1275でYesとなった入賞)に対応した揃出が完了したか否かを判定する。ステップ1290でYesの場合、ステップ1292で、CPUC100は、第1ROM・RAM領域内のデータに基づき、遊技終了処理(例えば、ベット数のクリア、遊技状態の移行処理等)を実行し、次の処理(ステップ1202の処理)に移行する。尚、ステップ1286でNoの場合には、ステップ1277に移行し、ステップ1275でNoの場合には、ステップ1292に移行する。

#### 【0108】

##### <第1ROM・RAM領域における処理>

次に、図13は、図8におけるステップ1300の(及び他のフローチャートにおいて呼び出された)サブルーチンに係る、復帰不可能エラー処理のフローチャートである。まず、ステップ1302で、CPUC100は、第1ROM・RAM領域内のデータに基づき、割り込みを禁止する(以降は、後述するタイマ割り込み時処理に係るフローチャートが実行されない)。次に、ステップ1304で、CPUC100は、第1ROM・RAM領域内のデータに基づき、出力ポートアドレス及び出力ポート数をセットする。次に、ステップ1306で、CPUC100は、第1ROM・RAM領域内のデータに基づき、出力ポート(本例では、0~6であり、各種LEDへの表示出力や各種モータへの駆動出力)をオフにする。次に、ステップ1308で、CPUC100は、第1ROM・RAM領域内のデータに基づき、次のポート出力アドレスをセットする(この繰り返しにより、各種LEDへの表示出力や各種モータへの駆動出力が順次停止される)。次に、ステップ1310で、CPUC100は、第1ROM・RAM領域内のデータに基づき、各出力ポートへの出力が終了したか否かを判定する。ステップ1310でYesの場合には、ステップ1312で、CPUC100は、第1ROM・RAM領域内のデータに基づき、セットされているエラー表示を実行し(本処理を実行する際には何らかのエラーが発生している)、当該処理の実行を繰り返し、電源電圧が低下することでリセット信号が入力されて終了する。(即ち、無限ループに突入するので、復帰を促す一切の操作を受け付けない)。尚、ステップ1310でNoの場合には、ステップ1306に移行する。尚、ステップ1306~ステップ1310の処理は、LED・モータへの出力をクリアする処理である(但し、外部出力信号はクリアしないので、エラーに関する情報やエラー発生時における遊技進行状況等をホールコンピュータ側へ出力することは可能である)。

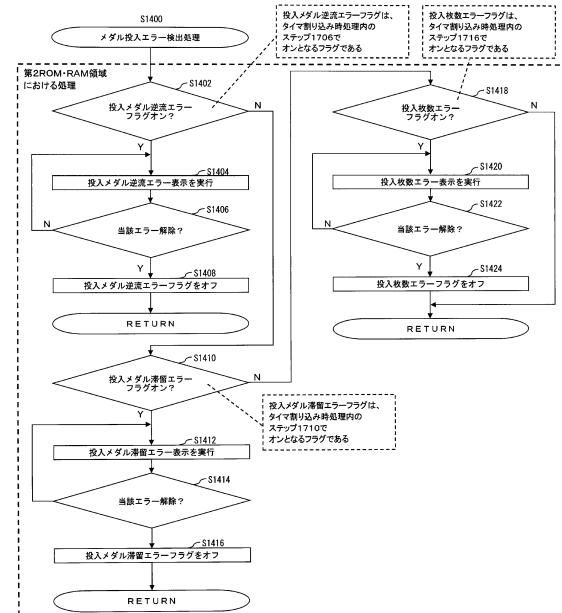

#### 【0109】

##### <第2ROM・RAM領域における処理>

次に、図14は、図11におけるステップ1400のサブルーチンに係る、メダル投入エラー検出処理のフローチャートである。まず、ステップ1402で、CPUC100は、第2ROM・RAM領域内のデータに基づき、投入メダル逆流エラーフラグ(ステップ1706でオンとなるフラグであり、本実施形態においては、第2RAM領域内のフラグ)がオンであるか否かを判定する。ステップ1402でYesの場合、ステップ1404で、CPUC100は、第2ROM・RAM領域内のデータに基づき、投入メダル逆流エラー(投入された遊技メダルが逆流したことによるエラーであり、例えば、第1投入センサD20sオフ且つ第2投入センサD30sオン 第1投入センサD20sオン且つ第2投入センサD30sオンとなつた場合にエラーとなる)表示を実行する。次に、CPUC100は、第2ROM・RAM領域内のデータに基づき、投入メダルエラー逆流エラーが解除されたか否か(例えば、設定/リセットボタンM30が押下されたか否か)を判定する。ステップ1406でYesの場合、ステップ1408で、CPUC100は、第2ROM・RAM領域内のデータに基づき、投入メダル逆流エラーフラグをオフにし、次の処

10

20

30

40

50

理（ステップ1229の処理）に移行する。

#### 【0110】

他方、ステップ1402でNoの場合、ステップ1410で、CPUC100は、第2ROM・RAM領域内のデータに基づき、投入メダル滞留エラーフラグ（ステップ1710でオンとなるフラグであり、本実施形態においては、第2RAM領域内のフラグ）がオンであるか否かを判定する。ステップ1410でYesの場合、ステップ1412で、CPUC100は、第2ROM・RAM領域内のデータに基づき、投入メダル滞留エラー（投入された遊技メダルが滞留したことによるエラーであり、例えば、第1投入センサD20sオン且つ第2投入センサD30sオンである状態が所定時間継続した場合にエラーとなる）表示を実行する。次に、ステップ1414で、CPUC100は、第2ROM・RAM領域内のデータに基づき、投入メダル滞留エラーが解除されたか否か（例えば、設定／リセットボタンM30が押下されたか否か）を判定する。ステップ1414でYesの場合、ステップ1416で、CPUC100は、第2ROM・RAM領域内のデータに基づき、投入メダル滞留エラーフラグをオフにし、次の処理（ステップ1229の処理）に移行する。

10

#### 【0111】

他方、ステップ1410でNoの場合、ステップ1418で、CPUC100は、第2ROM・RAM領域内のデータに基づき、投入枚数エラーフラグ（ステップ1716でオンとなるフラグであり、本実施形態においては、第2RAM領域内のフラグ）がオンであるか否かを判定する。ステップ1418でYesの場合、ステップ1420で、CPUC100は、第2ROM・RAM領域内のデータに基づき、投入枚数エラー（投入された遊技メダルの枚数と正常通過した遊技メダルの枚数とが一致しないことによるエラーであり、例えば、投入受付センサD10sが検知した遊技メダルの枚数と第2投入センサD30sが検知した遊技メダルの枚数とが一致しない場合又は所定の許容範囲外となった場合にエラーとなる）表示を実行する。次に、ステップ1422で、CPUC100は、第2ROM・RAM領域内のデータに基づき、投入枚数エラーフラグが解除されたか否か（例えば、設定／リセットボタンM30が押下されたか否か）を判定する。ステップ1422でYesの場合、ステップ1424で、CPUC100は、第2ROM・RAM領域内のデータに基づき、投入枚数エラーフラグをオフにし、次の処理（ステップ1229の処理）に移行する。

20

30

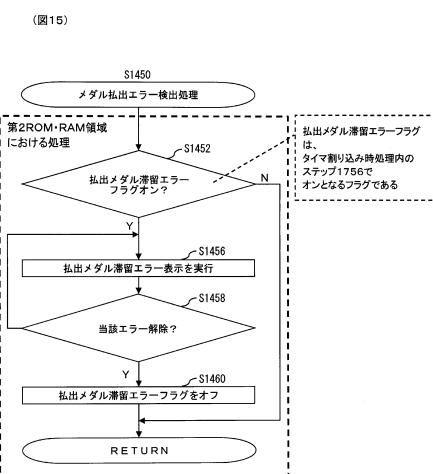

#### 【0112】

<第2ROM・RAM領域における処理>

次に、図15は、図11及び図12におけるステップ1450のサブルーチンに係る、メダル払出手エラー検出処理のフローチャートである。まず、ステップ1452で、CPUC100は、第2ROM・RAM領域内のデータに基づき、払出手メダル滞留エラーフラグ（ステップ1756でオンとなるフラグであり、本実施形態においては、第2RAM領域内のフラグ）がオンであるか否かを判定する。ステップ1452でYesの場合、ステップ1456で、CPUC100は、第2ROM・RAM領域内のデータに基づき、払出手メダル滞留エラー（払い出された遊技メダルが滞留したことによるエラーであり、例えば、第1払出手センサH10sオン且つ第2払出手センサH20sオンである状態が所定時間継続した場合にエラーとなる）表示を実行する。次に、ステップ1458で、CPUC100は、第2ROM・RAM領域内のデータに基づき、払出手メダル滞留エラーが解除されたか否か（例えば、設定／リセットボタンM30が押下されたか否か）を判定する。ステップ1458でYesの場合、ステップ1460で、CPUC100は、第2ROM・RAM領域内のデータに基づき、払出手メダル滞留エラーフラグをオフにし、次の処理（ステップ1240又はステップ1284の処理）に移行する。

40

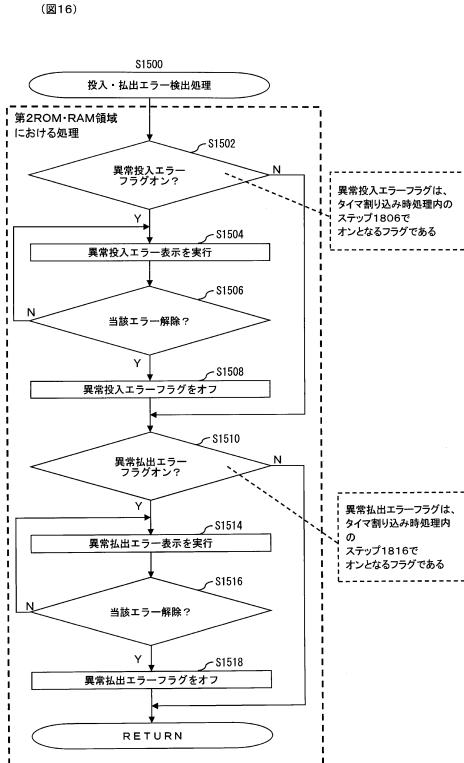

#### 【0113】

<第2ROM・RAM領域における処理>

次に、図16は、図11及び図12におけるステップ1500のサブルーチンに係る、投入・払出手エラー検出処理のフローチャートである。まず、ステップ1502で、CPU

50

C100は、第2ROM・RAM領域内のデータに基づき、異常投入エラーフラグ（ステップ1806でオンとなるフラグであり、本実施形態においては、第2RAM領域内のフラグ）がオンであるか否かを判定する。ステップ1502でYesの場合、ステップ1504で、CPUC100は、第2ROM・RAM領域内のデータに基づき、異常投入エラー（遊技メダルが投入されないはずのタイミングにて遊技メダルの投入を検出したことによるエラー）表示を実行する。次に、ステップ1506で、CPUC100は、第2ROM・RAM領域内のデータに基づき、異常投入エラーが解除されたか否か（例えば、設定／リセットボタンM30が押下されたか否か）を判定する。ステップ1506でYesの場合、ステップ1508で、CPUC100は、第2ROM・RAM領域内のデータに基づき、異常投入エラーフラグをオフにし、ステップ1510に移行する。尚、ステップ1502でNoの場合にも、ステップ1510に移行する。

10

#### 【0114】

次に、ステップ1510で、CPUC100は、第2ROM・RAM領域内のデータに基づき、異常払出エラーフラグ（ステップ1816でオンとなるフラグであり、本実施形態においては、第2RAM領域内のフラグ）がオンであるか否かを判定する。ステップ1510でYesの場合、ステップ1514で、CPUC100は、第2ROM・RAM領域内のデータに基づき、異常払出エラー（遊技メダルが払い出されないはずのタイミングにて遊技メダルの払出を検出したことによるエラー）表示を実行する。次に、ステップ1516で、CPUC100は、第2ROM・RAM領域内のデータに基づき、異常払出エラーが解除されたか否か（例えば、設定／リセットボタンM30が押下されたか否か）を判定する。ステップ1516でYesの場合、ステップ1518で、CPUC100は、第2ROM・RAM領域内のデータに基づき、異常払出エラーフラグをオフにし、次の処理（ステップ1250又はステップ1270の処理）に移行する。尚、ステップ1510でNoの場合にも、次の処理（ステップ1250又はステップ1270の処理）に移行する。

20

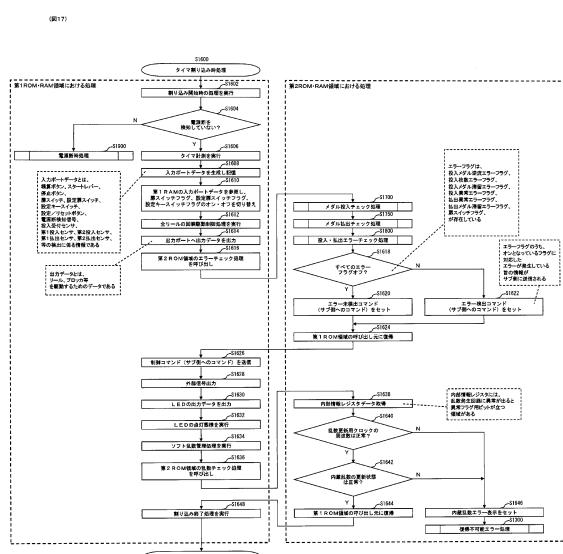

#### 【0115】

次に、図17は、本実施形態におけるステップ1600のサブルーチンに係る、タイマ割り込み時処理のフローチャートである。当該サブルーチンの処理は、ステップ1054又はステップ1118の処理にて、タイマ割り込みが開始された場合に実行開始され、以降、所定時間（本例では、Tとしているが、例えば、2ms程度の時間が設定される）を周期として定期的に実行されるよう構成されている。

30

#### 【0116】

##### <第1ROM・RAM領域における処理>

まず、ステップ1602で、CPUC100は、第1ROM・RAM領域内のデータに基づき、割り込み開始時の処理（例えば、CPUC100内のレジスタで保持されているデータの退避、電源断検知信号の入力ポートチェック等）を実行する。次に、ステップ1604で、CPUC100は、第1ROM・RAM領域内のデータに基づき、現在（今回の割り込み処理にて）電源断を検知していないか否かを判定する。ステップ1604でNoの場合、ステップ1900で、CPUC100は、第1ROM・RAM領域内のデータに基づき、後述する、電源断時処理を実行する。他方、ステップ1604でYesの場合、ステップ1606で、CPUC100は、第1ROM・RAM領域内のデータに基づき、タイマ計測（ソフトウェアで管理する各種タイマの更新処理）を開始する。次に、ステップ1608で、CPUC100は、第1ROM・RAM領域内のデータに基づき、入力ポートデータを生成して、当該データを記憶する（第1RAM領域内の各入力ポートデータの格納領域を更新する）。ここで、入力ポートデータとは、精算ボタンD60、スタートレバーD50、停止ボタンD40、扉スイッチD80、設定扉スイッチM10、設定キースイッチM20、設定／リセットボタンM30、電源断検知信号、投入受付センサD10s、第1投入センサD20s、第2投入センサD30s、第1払出センサH10s、第2払出センサH20s、等の検出に係る情報である（即ち、これらの操作部材での操作有無やセンサ検知状態が、割り込み間隔Tでサンプリングされる）。

40

50

## 【0117】

次に、ステップ1610で、CPUC100は、第1ROM・RAM領域内のデータに基づき、第1RAM領域内の入力ポートデータを参照し、各入力ポートデータのサンプリング結果に応じて、扉スイッチフラグ、設定扉スイッチフラグ、設定キースイッチフラグのオン・オフを切り替える（例えば、扉スイッチD80のスイッチ状態が複数回のサンプリングに亘って連続してオンである場合に、扉スイッチフラグをオンとすることで、ノイズの影響を受けることなく前扉DUが開状態であることを検出することもできる）。次に、ステップ1612で、CPUC100は、第1ROM・RAM領域内のデータに基づき、全リール（左リールM51、中リールM52、右リールM53）の回胴駆動制御処理（リールM50の駆動の制御に係る処理）を実行する。次に、ステップ1614で、CPUC100は、第1ROM・RAM領域内のデータに基づき、出力データを出力ポートに出力する。ここで、出力データとは、リールM50、ブロックD100、等を駆動するためのデータである。ステップ1616で、CPUC100は、第1ROM・RAM領域内のデータに基づき、第2ROM領域のエラーチェック処理を呼び出し、ステップ1700に移行する。10

## 【0118】

<第2ROM・RAM領域における処理>

次に、ステップ1700で、CPUC100は、第2ROM・RAM領域内のデータに基づき、後述する、メダル投入チェック処理を実行する。次に、ステップ1750で、CPUC100は、第2ROM・RAM領域内のデータに基づき、後述する、メダル払出手エックを実行する。次に、ステップ1800で、CPUC100は、第2ROM・RAM領域内のデータに基づき、後述する、投入・払出手エラーチェック処理を実行する。次に、ステップ1618で、CPUC100は、第2ROM・RAM領域内のデータに基づき、すべてのエラーフラグがオフ（投入メダル逆流フラグ、投入枚数エラーフラグ、メダル滞留エラーフラグ、投入異常エラーフラグ、払出手異常エラーフラグ、払出手メダル滞留エラーフラグ、扉スイッチフラグ、等のエラーに係るフラグが全てオフ）であるか否かを判定する（但し、本実施形態では、扉スイッチフラグに関しては、第1RAM領域内で格納されているため、第1RAM領域を参照して判定する）。ステップ1618でYesの場合、ステップ1620で、CPUC100は、第2ROM・RAM領域内のデータに基づき、エラー未検出コマンド（サブ側へのコマンドであり、エラーが検出されていない旨に係るコマンド）をセットし（例えば、レジスタ領域内にセットし）、ステップ1624に移行する。他方、ステップ1618でNoの場合、ステップ1622で、CPUC100は、第2ROM・RAM領域内のデータに基づき、エラー検出コマンド（サブ側へのコマンドであり、エラーが検出されている旨に係るコマンド）をセットし（例えば、レジスタ領域内にセットし）、ステップ1624に移行する。尚、ステップ1622においては、オンとなっているエラーフラグに対応したエラー（現在発生しているエラー）に係る情報がサブ側に送信されるよう構成されている。また、エラー未検出コマンドはエラーが発生していた状態からエラーが解除された場合にのみ（フラグがオフになったと判定された場合にのみ）セットしても良いし、エラー未検出のときには当該情報のセット処理を実行しなくても良い（S1620が無くても良い）。更に、エラー検出コマンドはエラーが発生していない状態からエラーが発生した場合にのみセット処理を実行しても良いし、第1のエラー（例えば、投入メダル滞留エラー）が発生している状態から第2のエラー（例えば、払出手メダル滞留エラー）のようにエラーの種類が変わった場合にセット処理を実行しても良い。次に、ステップ1624で、CPUC100は、第2ROM・RAM領域内のデータに基づき、第1ROM領域の呼び出し元に復帰し、ステップ1626に移行する。203040

## 【0119】

<第1ROM・RAM領域における処理>

次に、ステップ1626で、CPUC100は、第1ROM・RAM領域内のデータに基づき、制御コマンド（サブ側のコマンド）を送信する（例えば、ステップ1620やステップ1622でレジスタ領域内にセットされている場合には、そのセットされた制御コ50

マンドを引き継ぐこととなる)。次に、ステップ1628で、CPUC100は、第1ROM・RAM領域内のデータに基づき、外部信号(回胴式遊技機Pから外部のホールコンピュータ等へ情報伝達するための信号)を出力する。尚、当該外部信号にて出力されるエラーに係る情報としては、ドア開放エラー、投入異常エラー、払出異常エラー、設定扉開放エラー(不図示)、投入受付センサ滞留エラー(不図示)、等が出力される。尚、ドア開放エラーは、前扉DUが開放されドアスイッチフラグがオンとなった場合にエラーとなるよう構成されており、設定扉開放エラーは設定扉が開放され設定扉スイッチフラグがオンとなった場合にエラーとなるよう構成されており、投入受付センサ滞留エラーは投入受付センサが遊技メダルの滞留を検出した場合にエラーとなるよう構成されている。次に、ステップ1630で、CPUC100は、第1ROM・RAM領域内のデータに基づき、LED(7セグLEDランプ、等)の出力データ(例えば、複数の7セグLEDユニットのうち、所定の7セグLEDユニットを点灯させ、7セグの所定のセグメントを点灯させる)を出力する(所謂、ダイナミック点灯)。次に、ステップ1632で、CPUC100は、第1ROM・RAM領域内のデータに基づき、LEDの点灯態様(例えば、LEDの点灯色を変更)を実行する。尚、ステップ1632は実行されなくても良い。次に、ステップ1634で、CPUC100は、第1ROM・RAM領域内のデータに基づき、ソフト乱数管理処理(ソフトウェアで管理する乱数値の更新処理等)を実行する。次に、ステップ1636で、CPUC100は、第1ROM・RAM領域内のデータに基づき、第2ROM領域の乱数チェック処理を呼び出し、ステップ1638に移行する。

## 【0120】

10

## &lt;第2ROM・RAM領域における処理&gt;

次に、ステップ1638で、CPUC100は、第2ROM・RAM領域内のデータに基づき、内部情報レジスタデータを取得する(内部情報レジスタには、乱数発生回路に異常が出ると異常フラグ用ビットが立つ領域が存在している)。次に、ステップ1640で、CPUC100は、第2ROM・RAM領域内のデータに基づき、乱数更新用クロックの周波数は正常であるか否か(当該周波数異常を示す異常フラグ用ビットが立っていないか否か)を判定する。具体的には、乱数更新用クロックの周波数が所定値を下回った場合に異常用フラグビットが立つ。ステップ1640でYesの場合、ステップ1642で、CPUC100は、第2ROM・RAM領域内のデータに基づき、内蔵乱数の更新状態は正常であるか否か(当該更新状態異常を示す異常フラグ用ビットが立っていないか否か)を判定する。ステップ1642でYesの場合、ステップ1644で、CPUC100は、第2ROM・RAM領域内のデータに基づき、第1ROM領域の呼び出し元に復帰する。他方、ステップ1640又はステップ1642でNoの場合には、ステップ1646で、CPUC100は、第2ROM・RAM領域内のデータに基づき、内蔵乱数エラー表示をセットする(例えば、レジスタ領域内にエラー番号をセットする)。次に、ステップ1300で、CPUC100は、第2ROM・RAM領域内のデータに基づき、前述した、復帰不可能エラー処理を実行する。

20

## 【0121】

## &lt;第1ROM・RAM領域における処理&gt;

次に、ステップ1648で、CPUC100は、第1ROM・RAM領域内のデータに基づき、割り込み終了処理を実行し、次の処理(ステップ1602の処理)に移行する。

30

## 【0122】

## &lt;第2ROM・RAM領域における処理&gt;

次に、図18は、図17におけるステップ1700のサブルーチンに係る、メダル投入チェック処理のフローチャートである。まず、ステップ1702で、CPUC100は、第2ROM・RAM領域内のデータに基づき、第1投入センサD20sがオンであるか否か(検出しているか否か)を判定する(但し、第1投入センサD20sの入力ポートデータ自体が、第1RAM領域内で格納されている場合には、第1RAM領域を参照して判定する)。ステップ1702でYesの場合、ステップ1704で、CPUC100は、第2ROM・RAM領域内のデータに基づき、第1投入センサD20s及び第2投入センサ

40

50

D 3 0 s が、投入された遊技メダルの逆流を検知している（例えば、第1投入センサD 2 0 s オフ、且つ、第2投入センサD 3 0 s オン 第1投入センサD 2 0 s オン、且つ、第2投入センサD 3 0 s オンとなった場合に検知するものであり、この検知状態の時系列データ自体は第2RAM領域内で保持されている）か否かを判定する。ステップ1704でYesの場合、ステップ1706で、CPUC100は、第2ROM・RAM領域内のデータに基づき、投入メダル逆流エラーフラグをオンにし（例えば、第2RAM領域の投入メダル逆流エラーフラグ領域内をオンに相当する値で更新し）、ステップ1708に移行する。他方、ステップ1704でNoの場合にも、ステップ1708に移行する。

#### 【0123】

次に、ステップ1708で、CPUC100は、第2ROM・RAM領域内のデータに基づき、第1投入センサD 2 0 s 及び第2投入センサD 3 0 s が、投入されたメダルの滞留を検出している（例えば、第1投入センサD 2 0 s オンである状態が所定時間継続した場合、又は第2投入センサD 3 0 s オンである状態が所定時間継続した場合に検知するものであり、この検知状態のデータ自体は第2RAM領域内で保持されている）か否かを判定する。ステップ1708でYesの場合、ステップ1710で、CPUC100は、第2ROM・RAM領域内のデータに基づき、投入メダル滞留エラーフラグをオンにし（例えば、第2RAM領域の投入メダル滞留エラーフラグ領域内をオンに相当する値で更新し）、ステップ1712に移行する。他方、ステップ1708でNoの場合にも、ステップ1712に移行する。次に、ステップ1712で、CPUC100は、第2ROM・RAM領域内のデータに基づき、受付メダル枚数（遊技メダルの投入を受け付けた枚数）から正常通過枚数（正常に投入されたとみなされた遊技メダルの枚数）を減算した値が所定範囲内（例えば、0～2枚）でないか否かを判定する。ステップ1712でYesの場合、ステップ1716で、CPUC100は、第2ROM・RAM領域内のデータに基づき、投入枚数エラーフラグをオンにし（例えば、第2RAM領域の投入枚数エラーフラグ領域内をオンに相当する値で更新し）、次の処理（ステップ1750の処理）に移行する。尚、ステップ1712でNoの場合にも、次の処理（ステップ1750の処理）に移行する。尚、所定時間（例えば、5秒）の投入枚数エラー監視期間を設けて、当該監視期間中に、受付メダル枚数から正常通過枚数を減算した値が所定範囲内（例えば、0～2枚）ではなくなった場合に投入枚数エラーとなるよう構成してもよい。

#### 【0124】

<第2ROM・RAM領域における処理>

次に、図19は、図17におけるステップ1750のサブルーチンに係る、メダル払出手チェック処理のフローチャートである。まず、ステップ1752で、CPUC100は、第2ROM・RAM領域内のデータに基づき、ホッパ駆動フラグがオンであるか否か（検出しているか否か）を判定する（但し、ホッパ駆動フラグ自体が、第1RAM領域内で格納されている場合には、第1RAM領域を参照して判定する）。ステップ1752でYesの場合、ステップ1754で、CPUC100は、第2ROM・RAM領域内のデータに基づき、払い出されたメダルの滞留を検出（例えば、第1払出手センサH 1 0 s オンである状態が所定時間継続した場合、且つ、第2払出手センサH 2 0 s オンである状態が所定時間継続した場合に検知するものであり、この検知状態のデータ自体は第2RAM領域内で保持されている）しているか否かを判定する。ステップ1754でYesの場合、ステップ1756で、CPUC100は、第2ROM・RAM領域内のデータに基づき、払出手メダル滞留エラーフラグをオンにし（例えば、第2RAM領域の払出手メダル滞留エラーフラグ領域内をオンに相当する値で更新し）、次の処理（ステップ1800の処理）に移行する。尚、ステップ1752又はステップ1754でNoの場合も、次の処理（ステップ1800の処理）に移行する。

#### 【0125】

<第2ROM・RAM領域における処理>

次に、図20は、図17におけるステップ1800のサブルーチンに係る、投入・払出手エラーチェック処理のフローチャートである。まず、ステップ1802で、CPUC10

10

20

30

40

50

0は、第2ROM・RAM領域内のデータに基づき、プロッカD100がオフであるか否かを判定する（但し、プロッカD100の出力ポートデータ自体が、第1RAM領域内で格納されている場合には、第1RAM領域を参照して判定する）。ステップ1802でYesの場合、ステップ1804で、CPUC100は、第2ROM・RAM領域内のデータに基づき、投入センサの異常検出（第1投入センサD20s又は第2投入センサD30sが遊技メダルの検出をしないはずのタイミングにおける検出）があるか否かを判定する。ステップ1804でYesの場合、ステップ1806で、CPUC100は、第2ROM・RAM領域内のデータに基づき、異常投入エラーフラグをオンにし（例えば、第2RAM領域の異常投入エラーフラグ領域内をオンに相当する値で更新し）、ステップ1808に移行する。尚、ステップ1802又はステップ1804でNoの場合にも、ステップ1808に移行する。

10

#### 【0126】

次に、ステップ1808で、CPUC100は、第2ROM・RAM領域内のデータに基づき、ホッパ駆動フラグがオフであるか否かを判定する（但し、ホッパ駆動フラグ自体が、第1RAM領域内で格納されている場合には、第1RAM領域を参照して判定する）。ステップ1808でYesの場合、ステップ1810で、CPUC100は、第2ROM・RAM領域内のデータに基づき、払出センサの異常検出（第1払出センサH10s又は第2払出センサH20sが遊技メダルの検出をしないはずのタイミングにおける検出）があるか否かを判定する。ステップ1810でYesの場合、ステップ1812で、CPUC100は、第2ROM・RAM領域内のデータに基づき、異常払出エラーフラグをオンにし（例えば、第2RAM領域の異常払出エラーフラグ領域内をオンに相当する値で更新し）、次の処理（ステップ1618の処理）に移行する。尚、ステップ1808又はステップ1810でNoの場合にも、次の処理（ステップ1618の処理）に移行する。

20

#### 【0127】

<第1ROM・RAM領域における処理>

次に、図21は、図17におけるステップ1900のサブルーチンに係る、電源断時処理のフローチャートである。まず、ステップ1902で、CPUC100は、第1ROM・RAM領域内のデータに基づき、スタックポインタを保存する。次に、ステップ1904で、CPUC100は、第1ROM・RAM領域内のデータに基づき、電源断処理済みフラグをオンにする（例えば、第1RAM領域の電源断処理済みフラグ領域内をオンに相当する値で更新する）。次に、ステップ1906で、CPUC100は、第1ROM・RAM領域内のデータに基づき、第2ROM領域のチェックサム算出処理を呼び出し、ステップ1908に移行する。

30

#### 【0128】

<第2ROM・RAM領域における処理>

次に、ステップ1908で、CPUC100は、第2ROM・RAM領域内のデータに基づき、第1RAM領域の先頭アドレスからチェックサム領域直前アドレスまでのチェックサムを算出し、当該算出したチェックサムに基づく誤り検出用情報（例えば、当該算出したチェックサムにおける下位1バイト、或いは、その補数となるもの）をチェックサム領域にてセットする（チェックサム領域に係るアドレスは同図下段の「RAMに係るメモリマップ」を参照）。次に、ステップ1910で、CPUC100は、第2ROM・RAM領域内のデータに基づき、第1ROM領域の呼び出し元に復帰し、ステップ1912に移行する。

40

#### 【0129】

<第1ROM・RAM領域における処理>

次に、ステップ1912で、CPUC100は、第1ROM・RAM領域内のデータに基づき、第1RAM・第2RAMの書き込みを禁止し、ステップ1914に移行する。次に、ステップ1914で、CPUC100は、第1ROM・RAM領域内のデータに基づき、リセットを待機するための無限ループ処理を実行する。

#### 【0130】

以上のように構成することで、本実施形態に係る回胴式遊技機によれば、第2ROM領域にて配置されているプログラムコードに基づくCPU C100の処理にて、第1RAM領域（又は、レジスタ領域）を更新及び参照可能に構成し、エラー検出、エラー表示等の遊技機に対して不正行為がなされる（例えば、遊技媒体の投入口や払出口に対して不正にアクセスして遊技媒体を不正な手段で得る、等）ことを防御するための不正行為防止用のプログラムを第2ROM・RAM領域における処理にて実行し得るよう構成することで、遊技の進行に係る処理と領域を明確に分けることができ、当該不正行為防止用のプログラムの正当性を検証することが容易となる。

#### 【0131】

（第2実施形態）

10

尚、本実施形態においては、エラー表示処理等も不正行為防止用のプログラムとして見做し、第2ROM領域にて配置されているプログラムコードとして実装するための一例を示したが、エラー表示処理等は遊技進行を制御する上でも必要不可欠な処理であるため、不正行為防止用のプログラムではなく遊技性仕様を実装するためのプログラムとして見做した方が、人為的な検証が容易になる可能性がある。そこで、このような事情に鑑み、本実施形態で示した一例をベースとし、遊技性仕様を実装するためのプログラムとして見做した方が好適となり得る処理を、第1ROM領域にて配置されているプログラムコードとして実装するための一例を第2実施形態とし、以下、本実施形態からの変更点について詳述していく。

#### 【0132】

20

<第1ROM・RAM領域における処理>

はじめに、図22は、第2実施形態に係る回胴式遊技機Pの電源を投入した後（或いはシステムリセットやユーザリセット時において）、主制御基板MのCPU C100にて初めて実行される処理の流れを示したフローチャート（1枚目）である。本実施形態との相違点は、ステップ1005 1（第2）、ステップ1005 2（第2）、ステップ1009 1（第2）、ステップ1009 2（第2）、ステップ1017（第2）、ステップ1019 1（第2）～ステップ1019 3（第2）、ステップ1021 1（第2）、ステップ1021 2（第2）、ステップ1027（第2）、ステップ1029（第2）、ステップ1035 1（第2）及びステップ1035 2（第2）であり、即ち、ステップ1004で、チップの機能設定を実行した後、ステップ1005 1（第2）で、CPU C100は、第1ROM・RAM領域内のデータに基づき、第1RAM領域の先頭アドレスから第1チェックサム領域直前アドレスまでのチェックサムを算出する。ここで、同図右（RAMに係るメモリマップ）に示されるように、第2実施形態においては、第1RAM領域のチェックサム領域（第1チェックサム領域）と第2RAM領域のチェックサム領域（第2チェックサム領域）とが別々になっており、後述する第2実施形態における電源断時処理にて、第1RAM領域のチェックサム算出と第2RAM領域のチェックサム算出とが別々に行われ、夫々の算出結果に基づく誤り検出用情報が夫々の領域に格納される。次に、ステップ1005 2で、CPU C100は、第1ROM・RAM領域内のデータに基づき、第1RAMをチェックし、第1RAM電源断復帰データ（第1RAMに係る電源断復帰データ）を生成し、ステップ1006に移行する。よって、ここでの「第1RAMをチェック」とは、第1RAM領域を対象としたチェックサムと、第1チェックサム領域に保持されている誤り検出用情報に基づき、電源断・電源断復帰により内蔵RAM C120に格納されているデータが正しく保持されているか否かをチェックする処理となる。

30

#### 【0133】

<第2ROM・RAM領域における処理>

40

他方、ステップ1006で電源断復帰処理を呼び出した後、ステップ1009 1（第2）で、CPU C100は、第2ROM・RAM領域内のデータに基づき、第2RAM領域の先頭アドレスから、第2チェックサム領域を除く最終アドレスまでのチェックサムを算出する。次に、ステップ1009 2（第2）で、CPU C100は、第2ROM・R

50

A M領域内のデータに基づき、第2RAMをチェックし、第2RAM電源断復帰データ（第1RAMに係る電源断復帰データ）を生成し、ステップ1012に移行する。即ち、ここでの「第2RAMをチェック」とは、第2RAM領域を対象としたチェックサムと、第2チェックサム領域に保持されている誤り検出用情報に基づき、電源断・電源断復帰により内蔵RAMC120に格納されているデータが正しく保持されているか否かをチェックする処理となる。

#### 【0134】

<第1ROM・RAM領域における処理>

また、ステップ1016ですべてのスイッチがオンであった場合、ステップ1017（第2）で、CPUC100は、第1ROM・RAM領域内のデータに基づき、設定変更操作ありフラグをオンにし（例えば、第1RAM領域の設定変更操作ありフラグ領域内をオンに相当する値で更新し）、ステップ1018に移行する。

10

#### 【0135】

<第2ROM・RAM領域における処理>

また、ステップ1018で非設定変更時初期化処理を呼び出した後、ステップ1019

1（第2）で、CPUC100は、第2ROM・RAM領域内のデータに基づき、第1

RAM領域内の設定操作ありフラグがオフであるか否かを判定する。ステップ1019

1（第2）でYesの場合、ステップ1019\_2（第2）で、CPUC100は、第2

ROM・RAM領域内のデータに基づき、第1RAM領域内の電源断復帰データは正常で

あるか否か（特に、第1RAM領域を対象とした誤り検出結果が正常であるか否か）を判

定する。ステップ1019\_2（第2）でYesの場合、ステップ1019\_3（第2）

で、CPUC100は、第2ROM・RAM領域内のデータに基づき、第2RAM領域内

の電源断復帰データは正常であるか否か（特に、第2RAM領域を対象とした誤り検出

結果が正常であるか否か）を判定する。ステップ1019\_3（第2）でYesの場合、ス

テップ1028で、第1RAM領域及び第2RAM領域の初期化範囲を未使用RAM範

囲に決定してセットし、ステップ1027（第2）で、第2RAM領域内の電源断異常フラ

グをオフにし、ステップ1036に移行する。他方、ステップ1019\_2（第2）又は

ステップ1019\_3（第2）でNoの場合、ステップ1029（第2）で、CPUC1

00は、第2ROM・RAM領域内のデータに基づき、第2RAM領域内の電源断異常フ

ラグをオンにし、ステップ1036に移行する。

20

#### 【0136】

他方、ステップ1019\_1（第2）でNoの場合、ステップ1021\_1（第2）で

、CPUC100は、第2ROM・RAM領域内のデータに基づき、第1RAM領域内の

電源断復帰データは正常であるか否か（特に、第1RAM領域を対象とした誤り検出結果

が正常であるか否か）を判定する。ステップ1021\_1（第2）でYesの場合、ス

テップ1021\_2（第2）で、CPUC100は、第2ROM・RAM領域内のデータに基

づき、第2RAM領域内の電源断復帰データは正常であるか否か（特に、第2RAM領

域を対象とした誤り検出結果が正常であるか否か）を判定する。ステップ1021\_2（

第2）でYesの場合、ステップ1032で、CPUC100は、第2ROM・RAM領

域内のデータに基づき、第1RAM領域及び第2RAM領域の初期化範囲を第1RAM領

域内の設定値を除くすべての範囲に決定してセットし、ステップ1035\_1（第2）で

、CPUC100は、第2ROM・RAM領域内のデータに基づき、第2RAM領域内の

電源断異常フラグをオフにし、ステップ1036に移行する。他方、ステップ1021

\_1（第2）又はステップ1021\_2（第2）でNoの場合、ステップ1034で、CP

UC100は、第2ROM・RAM領域内のデータに基づき、第1RAM領域及び第2R

AM領域の初期化範囲をすべての範囲に決定してセットし、ステップ1035\_2（第2

）で、CPUC100は、第2ROM・RAM領域内のデータに基づき、第2RAM領域

内の電源断異常フラグをオンにし、ステップ1036に移行する。

40

#### 【0137】

<第1ROM・RAM領域における処理>

50

次に、図23は、第2実施形態に係る回胴式遊技機Pの電源を投入した後（或いはシステムリセットやユーザリセット時において）、主制御基板MのCPUC100にて初めて実行される処理の流れを示したフローチャート（2枚目）である。本実施形態との相違点は、ステップ1039 1（第2）、ステップ1039 2（第2）、ステップ1026（第2）、ステップ1300（第2）、ステップ1045（第2）、ステップ1046（第2）及びステップ1047（第2）であり、即ち、ステップ1039 1（第2）で、CPUC100は、第1ROM・RAM領域内のデータに基づき、第1RAM領域内の設定操作ありフラグがオフであるか否かを判定する。ステップ1039 1（第2）でYesの場合、ステップ1039 2（第2）で、CPUC100は、第1ROM・RAM領域内のデータに基づき、第2RAM領域内の電源断異常フラグがオフであるか否かを判定する。ステップ1039 2（第2）でYesの場合又はステップ1039 1（第2）でNoの場合には、ステップ1040に移行し（即ち、設定変更装置を作動させる場合か、設定変更装置を作動させない場合において第1RAM領域及び第2RAM領域を対象とした別個の誤り検出結果が正常であることを含め、正常に電断復帰している場合には以降の処理を続行し）、ステップ1039 2（第2）でNoの場合、ステップ1026（第2）で、CPUC100は、第1ROM・RAM領域内のデータに基づき、バックアップエラー表示をセットする（例えば、レジスタ領域内にエラー番号をセットする）。次に、ステップ1300（第2）で、CPUC100は、第1ROM・RAM領域内のデータに基づき、後述する、復帰不可能エラー処理をセットする（即ち、設定変更装置を作動させない場合において第1RAM領域及び第2RAM領域を対象とした別個の誤り検出結果が異常であることを含め、正常に電断復帰していない場合には復帰不可能な状態へと移行する）。ここで、本例においては、設定変更装置を作動させない場合において第1RAM領域及び第2RAM領域を対象とした別個の誤り検出結果がいずれも正常である場合において以降の処理を続行するよう構成されているが、これには限定されず、例えば、第1RAM領域を対象とした誤り検出結果が正常であれば、第2RAM領域を対象とした誤り検出結果が異常であっても（第2RAM領域の全領域を初期化した上で）以降の処理を続行するよう構成してもよい。

#### 【0138】

##### <第2ROM・RAM領域における処理>

また、ステップ1044で、第1RAM領域内の設定値が正常範囲内であった場合、ステップ1045（第2）で、CPUC100は、第2ROM・RAM領域内のデータに基づき、第2RAM領域内の設定値異常フラグをオフにし、第1ROM領域の呼び出し元に復帰し、ステップ1047（第2）に移行する。他方、ステップ1044でNoの場合、ステップ1046（第2）で、CPUC100は、第2ROM・RAM領域内のデータに基づき、第2RAM領域内の設定値異常フラグをオンにし、第1ROM領域の呼び出し元に復帰し、ステップ1047（第2）に移行する。

#### 【0139】

##### <第1ROM・RAM領域における処理>

次に、ステップ1047（第2）で、CPUC100は、第1ROM・RAM領域内のデータに基づき、第2RAM領域内の設定値異常フラグがオフであるか否かを判定する。ステップ1047（第2）でYesの場合には、ステップ1050に移行し、Noの場合には、ステップ1048（第2）で、CPUC100は、第1ROM・RAM領域内のデータに基づき、設定値エラー表示をセットする（例えば、レジスタ領域内にエラー番号をセットする）。次に、ステップ1300（第2）で、CPUC100は、第1ROM・RAM領域内のデータに基づき、後述する、復帰不可能エラー処理をセットする。このように、第2実施形態においては、復帰不可能エラー処理及び発生している復帰不可能エラー表示（バックアップエラー表示、設定値エラー表示）のセット処理を、第1ROM・RAM領域にて実行するよう構成している。

#### 【0140】

##### <第1ROM・RAM領域における処理>

次に、図24は、第2実施形態におけるステップ1200のサブルーチンに係る、遊技進行制御処理(2枚目)のフローチャートである。本実施形態との相違点は、ステップ1228(第2)、ステップ1700(第2)、ステップ1400(第2)、ステップ1237(第2)、ステップ1750(第2)、ステップ1450(第2)、ステップ1249(第2)、ステップ1800(第2)、ステップ1500(第2)、ステップ1254(第2)～ステップ1254(3)(第2)、ステップ1256(第2)及びステップ1300(第2)であり、即ち、ステップ1227で遊技メダルの投入を受け付けた後、又は、ステップ1230で第1投入センサD20s及び第2投入センサD30sがオフでなかった場合に、ステップ1228(第2)で、CPUC100は、第1ROM・RAM領域内のデータに基づき、第2ROM領域のメダル投入チェック処理を呼び出し、ステップ1700(第2)に移行する。

10

#### 【0141】

<第2ROM・RAM領域における処理>

次に、ステップ1700(第2)で、CPUC100は、第2ROM・RAM領域内のデータに基づき、メダル投入チェック処理を実行し、ステップ1229に移行する。尚、この第2ROM領域のメダル投入チェック処理の趣旨としては、本実施形態において、遊技進行制御処理(ループ処理)とタイマ割り込み時処理(非ループ処理)とで分けて実装されていたメダル投入チェック関連の処理を、遊技進行制御処理(ループ処理)にて纏めて実装する方法の一例を示すことがある。

#### 【0142】

<第1ROM・RAM領域における処理>

また、ステップ1229で第1ROM領域の呼び出し元に復帰した後、ステップ1400(第2)で、CPUC100は、第1ROM・RAM領域内のデータに基づき、後述する、メダル投入エラー検出処理を実行し、ステップ1230に移行する。尚、第2実施形態においては、メダル投入エラー検出処理を、第1ROM・RAM領域にて実行するよう構成している。

20

#### 【0143】

また、ステップ1236で第1払出センサH10s又は第2払出センサH20sがオンであった場合、ステップ1241でホッパ駆動後所定時間が経過していない場合、又は、ステップ1247で第1払出センサH10s及び第2払出センサH20sがオフでなかった場合に、ステップ1237(第2)で、CPUC100は、第1ROM・RAM領域内のデータに基づき、第2ROM領域のメダル払出チェック処理を呼び出し、ステップ1750(第2)に移行する。

30

#### 【0144】

<第2ROM・RAM領域における処理>

次に、ステップ1750(第2)で、CPUC100は、第2ROM・RAM領域内のデータに基づき、メダル払出チェック処理を実行し、ステップ1240に移行する。尚、この第2ROM領域のメダル払出チェック処理の趣旨としては、本実施形態において、遊技進行制御処理(ループ処理)とタイマ割り込み時処理(非ループ処理)とで分けて実装されていたメダル払出チェック関連の処理を、遊技進行制御処理(ループ処理)にて纏めて実装する方法の一例を示すことがある。

40

#### 【0145】

<第1ROM・RAM領域における処理>

また、ステップ1240で第1ROM領域の呼び出し元に復帰した後、ステップ1450(第2)で、CPUC100は、第1ROM・RAM領域内のデータに基づき、後述する、メダル払出エラー検出処理を実行し、ステップ1247に移行する。尚、第2実施形態においては、メダル払出エラー検出処理を、第1ROM・RAM領域にて実行するよう構成している。

45

#### 【0146】

また、ステップ1232で精算ボタンD60の操作がなかった場合、又は、ステップ1

50

233で残りクレジット及びベットメダルがなかった場合に、ステップ1249 1(第2)で、CPUC100は、第1ROM・RAM領域内のデータに基づき、第2ROM領域の投入・払出エラーチェック処理を呼び出し、ステップ1800(第2)に移行する。

#### 【0147】

<第2ROM・RAM領域における処理>

次に、ステップ1800(第2)で、CPUC100は、第2ROM・RAM領域内のデータに基づき、投入・払出エラーチェック処理を実行し、ステップ1250に移行する。尚、この第2ROM領域の投入・払出エラーチェック処理の趣旨としては、本実施形態において、遊技進行制御処理(ループ処理)とタイマ割り込み時処理(非ループ処理)とで分けて実装されていた投入・払出エラーチェック関連の処理を、遊技進行制御処理(ループ処理)にて纏めて実装する方法の一例を示すことがある。

10

#### 【0148】

<第1ROM・RAM領域における処理>

また、ステップ1250で第1ROM領域の呼び出し元に復帰した後、ステップ1500(第2)で、CPUC100は、第1ROM・RAM領域内のデータに基づき、後述する、投入・払出エラー検出処理を実行し、ステップ1251に移行する。尚、第2実施形態においては、投入・払出エラー検出処理を、第1ROM・RAM領域にて実行するよう構成している。

20

#### 【0149】

<第2ROM・RAM領域における処理>

また、ステップ1253で第1RAM領域内の設定値が正常範囲内であった場合、ステップ1254 2(第2)で、CPUC100は、第2ROM・RAM領域内のデータに基づき、第2RAM領域内の設定値異常フラグをオフにし、第1ROM領域の呼び出し元に復帰し、ステップ1254 3(第2)に移行する。他方、ステップ1253で第1RAM領域内の設定値が正常範囲内ではなかった場合、ステップ1254 1(第2)で、CPUC100は、第2ROM・RAM領域内のデータに基づき、第2RAM領域内の設定値異常フラグをオンにし、第1ROM領域の呼び出し元に復帰し、ステップ1254 3(第2)に移行する。

#### 【0150】

<第1ROM・RAM領域における処理>

30

次に、ステップ1254 3(第2)で、CPUC100は、第2ROM・RAM領域内のデータに基づき、第2RAM領域内の設定値異常フラグがオフであるか否かを判定する。ステップ1254 3(第2)でYesの場合、次の処理(ステップ1257の処理)に移行し、Noの場合には、ステップ1256(第2)で、CPUC100は、第1ROM・RAM領域内のデータに基づき、設定値エラー表示をセットする(例えば、レジスタ領域内にエラー番号をセットする)。次に、ステップ1300(第2)で、CPUC100は、第1ROM・RAM領域内のデータに基づき、後述する、復帰不可能エラー処理をセットする。このように、第2実施形態においては、復帰不可能エラー処理及び発生している復帰不可能エラー表示(設定値エラー表示)のセット処理を、第1ROM・RAM領域にて実行するよう構成している。

40

#### 【0151】

<第1ROM・RAM領域における処理>

次に、図25は、第2実施形態における、図24のステップ1400(第2)のサブルーチンに係る、メダル投入エラー検出処理のフローチャートである。本実施形態との相違点は、本サブルーチンの処理を、第1ROM・RAM領域における処理としていることである。即ち、本実施形態においては、メダル投入エラー関連のエラー表示処理を実行する場合、第2ROM領域において実装された当該処理を呼び出していたのであるが、第2実施形態においては、当該処理が第1ROM領域において実装されており、第2ROM・RAM領域における各種エラー検出処理にてエラーが検出された場合には、エラーが検出された旨の情報を第1ROM領域において実装された当該処理へ引き渡して実行しているの

50

である。このように構成した場合、遊技進行を制御する上でも必要不可欠な処理であるエラー表示処理を、遊技性仕様を実装するためのプログラム（遊技進行を制御するためのプログラム）として実装することができ、換言すれば、従来から実装されているエラー表示処理プログラムを流用することが可能となる。尚、エラーが検出された旨の情報を第1ROM領域において実装されたエラー表示処理へと引き渡すための第2RAM領域内のフラグである、投入メダル逆流エラーフラグ、投入メダル滞留エラーフラグ及び投入枚数エラーフラグは、エラーが解除された場合には、本例のように第1ROM領域において実装されたエラー表示処理から直接オフとしてもよいし、第2ROM領域の処理であり当該フラグをオフとするための処理を呼び出してオフにするよう構成してもよい。

## 【0152】

10

## &lt;第1ROM・RAM領域における処理&gt;

次に、図26は、第2実施形態における、図24のステップ1450（第2）のサブルーチンに係る、メダル払出手エラー検出処理のフローチャートである。本実施形態との相違点は、本サブルーチンの処理を、第1ROM・RAM領域における処理としていることである。即ち、本実施形態においては、メダル払出手エラー関連のエラー表示処理を実行する場合、第2ROM領域において実装された当該処理を呼び出していたのであるが、第2実施形態においては、当該処理が第1ROM領域において実装されており、第2ROM・RAM領域における各種エラー検出処理にてエラーが検出された場合には、エラーが検出された旨の情報を第1ROM領域において実装された当該処理へ引き渡して実行しているのである。このように構成した場合、遊技進行を制御する上でも必要不可欠な処理であるエラー表示処理を、遊技性仕様を実装するためのプログラム（遊技進行を制御するためのプログラム）として実装することができ、換言すれば、従来から実装されているエラー表示処理プログラムを流用することが可能となる。尚、エラーが検出された旨の情報を第1ROM領域において実装されたエラー表示処理へと引き渡すための第2RAM領域内のフラグである、払出手メダル滞留エラーフラグは、エラーが解除された場合には、本例のように第1ROM領域において実装されたエラー表示処理から直接オフとしてもよいし、第2ROM領域の処理であり当該フラグをオフとするための処理を呼び出してオフにするよう構成してもよい。

20

## 【0153】

30

## &lt;第1ROM・RAM領域における処理&gt;

次に、図27は、第2実施形態における、図24のステップ1500（第2）のサブルーチンに係る、投入・払出手エラー検出処理のフローチャートである。本実施形態との相違点は、本サブルーチンの処理を、第1ROM・RAM領域における処理としていることである。即ち、本実施形態においては、投入・払出手エラー関連のエラー表示処理を実行する場合、第2ROM領域において実装された当該処理を呼び出していたのであるが、第2実施形態においては、当該処理が第1ROM領域において実装されており、第2ROM・RAM領域における各種エラー検出処理にてエラーが検出された場合には、エラーが検出された旨の情報を第1ROM領域において実装された当該処理へ引き渡して実行しているのである。このように構成した場合、遊技進行を制御する上でも必要不可欠な処理であるエラー表示処理を、遊技性仕様を実装するためのプログラム（遊技進行を制御するためのプログラム）として実装することができ、換言すれば、従来から実装されているエラー表示処理プログラムを流用することが可能となる。尚、エラーが検出された旨の情報を第1ROM領域において実装されたエラー表示処理へと引き渡すための第2RAM内のフラグである、異常投入エラーフラグ及び異常払出手エラーフラグは、エラーが解除された場合には、本例のように第1ROM領域において実装されたエラー表示処理から直接オフとしてもよいし、第2ROM領域の処理であり当該フラグをオフとするための処理を呼び出してオフにするよう構成してもよい。

40

## 【0154】

## &lt;第2ROM・RAM領域における処理&gt;

次に、図28は、第2実施形態における、遊技進行制御処理（3枚目）のフローチャー

50

トである。本実施形態との相違点は、ステップ1269 1(第2)～ステップ1269 4(第2)、ステップ1272(第2)、ステップ1300(第2)、ステップ1800(第2)、ステップ1500(第2)、ステップ1277 1(第2)、ステップ1750(第2)及びステップ1450(第2)であり、即ち、ステップ1269で、表示された図柄の組み合わせが正常である場合、ステップ1269 1(第2)で、CPUC100は、第2ROM・RAM領域内のデータに基づき、第2RAM領域内の表示判定異常フラグをオフにし、第1ROM領域の呼び出し元に復帰し、ステップ1269 3(第2)に移行する。他方、ステップ1269で、表示された図柄の組み合わせが正常でない場合、ステップ1269 2(第2)で、CPUC100は、第2ROM・RAM領域内のデータに基づき、第2RAM領域内の表示判定異常フラグをオンにし、第1ROM領域の呼び出し元に復帰し、ステップ1269 3(第2)に移行する。

10

#### 【0155】

<第1ROM・RAM領域における処理>

次に、ステップ1269 3(第2)で、CPUC100は、第1ROM・RAM領域内のデータに基づき、第2RAM領域内の表示判定異常フラグがオフであるか否かを判定する。ステップ1269 3(第2)でYesの場合、ステップ1269 4(第2)で、CPUC100は、第1ROM・RAM領域内のデータに基づき、第2ROM領域の投入・払出エラーチェック処理を呼び出し、ステップ1500(第2)に移行する。他方、ステップ1269 3(第2)でNoの場合には、ステップ1272(第2)で、CPUC100は、第1ROM・RAM領域内のデータに基づき、表示判定エラー表示をセットする(例えば、レジスタ領域内にエラー番号をセットする)。次に、ステップ1300(第2)で、CPUC100は、第1ROM・RAM領域内のデータに基づき、前述した、復帰不可能エラー処理をセットする。このように、第2実施形態においては、復帰不可能エラー処理及び発生している復帰不可能エラー表示(表示判定エラー表示)のセット処理を、第1ROM・RAM領域にて実行するよう構成している。

20

#### 【0156】

<第2ROM・RAM領域における処理>

次に、ステップ1800(第2)で、CPUC100は、第2ROM・RAM領域内のデータに基づき、投入・払出エラーチェック処理を実行し、ステップ1270に移行する。尚、この第2ROM領域の投入・払出エラーチェック処理の趣旨としては、本実施形態において、遊技進行制御処理(ループ処理)とタイマ割り込み時処理(非ループ処理)とで分けて実装されていた投入・払出エラーチェック関連の処理を、遊技進行制御処理(ループ処理)にて纏めて実装する方法の一例を示すことがある。

30

#### 【0157】

<第1ROM・RAM領域における処理>

また、ステップ1270で第1ROM領域の呼び出し元に復帰した後、ステップ1500(第2)で、CPUC100は、第1ROM・RAM領域内のデータに基づき、前述した、投入・払出エラー検出処理を実行し、ステップ1274に移行する。尚、第2実施形態においては、投入・払出エラー検出処理を、第1ROM・RAM領域にて実行するよう構成している。

40

#### 【0158】

他方、ステップ1277で第1払出センサH10s又は第2払出センサH20sがオンであった場合、ステップ1277 1(第2)で、CPUC100は、第1ROM・RAM領域内のデータに基づき、第2ROM領域のメダル払出チェック処理を呼び出し、ステップ1750(第2)に移行する。

#### 【0159】

<第2ROM・RAM領域における処理>

次に、ステップ1750(第2)で、CPUC100は、第2ROM・RAM領域内のデータに基づき、メダル払出チェック処理を実行し、ステップ1284に移行する。尚、この第2ROM領域のメダル払出チェック処理の趣旨としては、本実施形態において、遊

50

技進行制御処理（ループ処理）とタイマ割り込み時処理（非ループ処理）とで分けて実装されていたメダル払出チェック関連の処理を、遊技進行制御処理（ループ処理）にて纏めて実装する方法の一例を示すことにある。

#### 【0160】

##### <第1ROM・RAM領域における処理>

また、ステップ1284で第1ROM領域の呼び出し元に復帰した後、ステップ1450（第2）で、CPUC100は、第1ROM・RAM領域内のデータに基づき、後述する、メダル払出エラー検出処理を実行し、ステップ1286に移行する。尚、第2実施形態においては、メダル払出エラー検出処理を、第1ROM・RAM領域にて実行するよう構成している。

10

#### 【0161】

##### <第1ROM・RAM領域における処理>

次に、図29は、第2実施形態における、図23、図24、図28及び図30のステップ1300（第2）のサブルーチンに係る、復帰不可能エラー処理のフローチャートである。本実施形態との相違点は、本サブルーチンの処理を、第1ROM・RAM領域における処理としていることである。即ち、本実施形態においては、復帰不可能エラー処理を実行する場合、第2ROM領域において実装された当該処理を呼び出していたのであるが、第2実施形態においては、当該処理が第1ROM領域において実装されており、第2ROM・RAM領域における各種エラー検出処理にてエラーが検出された場合には、エラーが検出された旨の情報を第1ROM領域において実装された当該処理へ引き渡して実行しているのである。このように構成した場合、復帰不可能な（即ち、回胴式遊技機Pを動作不能とする）状態へと移行させるという強制力をもった処理を、遊技性仕様を実装するためのプログラム（遊技進行を制御するためのプログラム）として実装することができる。

20

#### 【0162】

##### <第2ROM・RAM領域における処理>

次に、図30は、第2実施形態におけるステップ1600のサブルーチンに係る、タイマ割り込み時処理のフローチャートである。本実施形態との相違点は、ステップ1648（第2）、ステップ1650（第2）及びステップ1654（第2）であり、即ち、ステップ1642で、内蔵乱数の更新状態が正常であった場合、ステップ1648（第2）で、CPUC100は、第2ROM・RAM領域内のデータに基づき、第2RAM領域内の内蔵乱数異常フラグをオフにし、第1ROM領域の呼び出し元に復帰し、ステップ1654（第2）に移行する。他方、ステップ1640で、乱数更新用クロックの周波数が正常でなかった、又は、ステップ1642で、内蔵乱数の更新状態が正常でなかった場合に、ステップ1650（第2）で、CPUC100は、第2ROM・RAM領域内のデータに基づき、第2RAM領域内の内蔵乱数異常フラグをオンにし、第1ROM領域の呼び出し元に復帰し、ステップ1654（第2）に移行する。

30

#### 【0163】

##### <第1ROM・RAM領域における処理>

次に、ステップ1654（第2）で、CPUC100は、第1ROM・RAM領域内のデータに基づき、内蔵乱数異常フラグがオフであるか否かを判定する。ステップ1654（第2）でYesの場合には、ステップ1636に移行し、Noの場合には、ステップ1648（第2）で、CPUC100は、第1ROM・RAM領域内のデータに基づき、内蔵乱数エラー表示をセットする（例えば、レジスタ領域内にエラー番号をセットする）。次に、ステップ1300（第2）で、CPUC100は、第1ROM・RAM領域内のデータに基づき、前述した、復帰不可能エラー処理をセットする。このように、第2実施形態においては、復帰不可能エラー処理及び発生している復帰不可能エラー表示（内蔵乱数エラー表示）のセット処理を、第1ROM・RAM領域にて実行するよう構成している。

40

#### 【0164】

##### <第1ROM・RAM領域における処理>

次に、図31は、第2実施形態における、図30のステップ1900のサブルーチンに

50

係る、電源断時処理のフローチャートである。本実施形態との相違点は、ステップ1905（第2）及びステップ1909（第2）であり、即ち、ステップ1904で、電源断処理済みフラグをオンにした後、ステップ1905（第2）で、CPUC100は、第1ROM・RAM領域内のデータに基づき、第1RAM領域の先頭アドレスから第1チェックサム領域直前アドレスまでのチェックサムを算出し、当該算出したチェックサムに基づく誤り検出用情報（例えば、当該算出したチェックサムにおける下位1バイト、或いは、その補数となるもの）を第1チェックサム領域にてセットする。次に、ステップ1906で、第2ROM領域のチェックサム算出処理を呼び出し、ステップ1909（第2）に移行する。

#### 【0165】

10

##### <第2ROM・RAM領域における処理>