さらに、前記凹部を基準位置として、前記素子形成領域に回路素子を形成することを特徴とする半導体装置の製造方法。

【請求項 3】

前記第3工程が、

前記素子形成領域及び前記マーク形成領域の両領域の全面に第1サブシリコン窒化膜を形成する第1サブ工程と、

前記マーク形成領域以外に存在する前記第1サブシリコン窒化膜を除去する第2サブ工程と、

前記素子形成領域及び前記マーク形成領域の両領域の全面に第2サブシリコン窒化膜を形成することにより、前記マーク形成領域に、前記第1及び第2サブシリコン窒化膜の積層体としての前記第2の窒化膜を形成し、及び前記素子形成領域に、前記第2サブシリコン窒化膜からなる前記第1の窒化膜を形成する第3サブ工程と

を含むことを特徴とする請求項1又は2に記載の半導体装置の製造方法。

【請求項 4】

前記第6工程が、

前記素子形成領域の前記第1の窒化膜及び前記マーク形成領域に形成された前記凹部の底面を構成する前記第2の窒化膜を除去する第1サブ工程と、

前記素子形成領域の前記酸化膜及び前記凹部の底面を構成する前記第2の窒化膜の下に位置する前記酸化膜を除去する第2サブ工程と

を含むことを特徴とする請求項1～3の何れか一項に記載の半導体装置の製造方法。

【発明の詳細な説明】

【技術分野】

【0001】

この発明は、半導体装置の製造工程において位置合わせ用の基準位置として用いられるマークを具えた半導体装置及びその製造方法に関する。

【背景技術】

【0002】

通常、半導体集積回路装置の製造プロセスでは、ウェハ上の所定の膜を集積回路の形状にパターニングするフォトリソグラフィ工程を行っている。

【0003】

フォトリソグラフィ工程では、被エッチング膜上のフォトレジストにフォトマスクを通して回路パターンの露光及び現像を行い、所定の回路パターンを転写する。その後、このフォトレジストをマスクとして被エッチング膜をエッチングすることにより、所定の回路形状をパターニング形成する。

【0004】

フォトマスクとして、例えば、ガラス基板上に、露光光線に対して遮光性を有するクロム等によって所定の回路パターンが形成されたものがある。工業的には、このフォトマスクパターンを等倍あるいは縮小させた像を反射型や投影型方式等によってフォトレジストに結像させて露光・感光を行う、転写法が利用されている。

【0005】

露光を行うに当たり、フォトマスクとパターンが転写されるウェハとを設計値通りの位置に重ね合わせることが必要不可欠である。そのため、露光時における位置合わせを、例えば、フォトマスク及びウェハの双方に形成された位置合わせ用マークを重ね合わせることにより行っている。また、こうした重ね合わせを行うに当たり、ウェハ側に位置合わせ用マークとして凹部が形成されたものがある（例えば、特許文献1参照）。この場合、ウェハ側のマーク位置を、当該ウェハに照射した照射光の当該マークのエッジ部からの反射光や回折光によって検出して位置合わせを行っている。

【0006】

ところで、近年、集積回路の高性能化を目的として、SOI (Silicon on Insulator) デバイスが注目されている。SOIデバイスとは、半導体支持基板

10

20

30

40

50

上に、絶縁膜を介して素子形成用の半導体層（あるいは、SOI層とも言う。）を有するSOI基板を具えた構成である。半導体層に素子が形成されるSOIデバイスでは、これまでよりも素子の寄生容量を低減できるうえに接合リードを小さくでき、よって、高速動作及び低消費電力を実現することができる。

【特許文献1】特開2000-156506号公報

【発明の開示】

【発明が解決しようとする課題】

【0007】

しかしながら、近年の、SOIデバイスのさらなる高機能化及び高性能化に対する要求に伴い、トランジスタのゲート長の微細化がなされるとともに、ゲートのショートチャネル効果を抑制するために上述した半導体層のより一層の薄膜化が進んでいる。10

【0008】

そのため、ウェハの半導体層部分に形成されたマークのエッジ部の段差が不十分となつたり、あるいは半導体層自体がマーク形成時に除去される等の問題が発生している。

【0009】

その結果、露光時の位置合わせを行う際の、マークのエッジ部からの反射光や回折光の検出が困難となることによる、マーク位置の検出精度の低下が問題となっていた。

【0010】

そこで、この発明は、従来よりも検出精度を向上できるマークの形成方法を提供することにより、信頼性の高い半導体装置及びその製造方法を提供することを主たる目的とする。20

【課題を解決するための手段】

【0011】

この発明は、上記課題に鑑みてなされてものであり、この発明の半導体装置の製造方法によれば、下記のような構成上の特徴を有する。

【0016】

この発明の半導体装置の製造方法は、半導体支持基板、当該半導体支持基板上に形成された絶縁膜、及び当該絶縁膜上に形成された半導体層とを具え、素子形成領域と当該素子形成領域に隣接するマーク形成領域とを有する基板を用意する第1工程と、素子形成領域及びマーク形成領域の半導体層上に酸化膜を形成する第2工程と、素子形成領域の酸化膜上に第1の膜厚を有する第1の窒化膜を形成するとともに、マーク形成領域の酸化膜上に該第1の膜厚よりも厚い第2の膜厚を有する第2の窒化膜を形成する第3工程と、素子形成領域の第1の窒化膜に酸化膜を露出させる開口を形成するとともに、マーク形成領域の第2の窒化膜に酸化膜を露出させないように凹部を形成する第4工程と、素子形成領域の開口の下に位置する半導体層を酸化する第5工程と、素子形成領域の第1の窒化膜及び酸化膜を除去するとともに、マーク形成領域に形成された凹部の底面を構成する第2の窒化膜及びこの底面を構成する第2の窒化膜の下に位置する酸化膜を除去する第6工程とを含んでいる。30

上述の半導体装置の製造方法において、さらに、凹部を基準位置として、素子形成領域に回路素子を形成することが好ましい。

また、上述の半導体装置の製造方法において、第3工程が、素子形成領域及びマーク形成領域の両領域の全面に第1サブシリコン窒化膜を形成する第1サブ工程と、マーク形成領域以外に存在する第1サブシリコン窒化膜を除去する第2サブ工程と、素子形成領域及びマーク形成領域の両領域の全面に第2サブシリコン窒化膜を形成することにより、マーク形成領域に、第1及び第2サブシリコン窒化膜の積層体としての第2の窒化膜を形成し、及び素子形成領域に、第2サブシリコン窒化膜からなる第1の窒化膜を形成する第3サブ工程とを含むことが好ましい。

また、上述の半導体装置の製造方法において、第6工程が、素子形成領域の第1の窒化膜及びマーク形成領域に形成された凹部の底面を構成する第2の窒化膜を除去する第1サブ工程と、素子形成領域の酸化膜及び凹部の底面を構成する第2の窒化膜の下に位置する

50

20

30

40

50

酸化膜を除去する第2サブ工程とを含むことが好ましい。

【0017】

この発明によれば、基板上に、エッジ部に十分な段差が有するマークとしての凹部を形成することができる。

【0018】

したがって、基板表面に照射した照射光の反射光や回折光に基づいてマーク位置を検出して位置合わせを行う際に、マークのエッジ部からの反射光や回折光を確実に検出することができる。

【0019】

さらに、この発明のように基板自体にマークとしての凹部を形成しない構成の場合には 10 基板の半導体層のさらなる薄膜化を進めることができる。

【発明の効果】

【0020】

これらの発明によれば、基板側のマーク位置の検出精度が向上するため、当該マークを利用してフォトマスク等の位置合わせを行う際の合わせずれの発生を抑制することができる。

【0021】

よって、基板の位置合わせを設計値通りに行うことができるので、当該フォトマスクを用いて行う半導体製造プロセスを精度良く行うことができる。よって、従来よりも信頼性の高い半導体装置を実現することができる。 20

【0022】

さらに、この発明によれば、素子形成領域における工程を一部兼用して、マーク形成領域においてマーク形成を行うことができるので、マーク形成工程の簡便化に効果的である。

【発明を実施するための最良の形態】

【0023】

以下、図を参照して、この発明の実施の形態について説明する。尚、各図は、この発明が理解できる程度に各構成成分の形状、大きさ及び配置関係を概略的に示してあるに過ぎず、従って、この発明は図示例に限定されるものではない。また、図を分かり易くするために、断面を示すハッチングは、一部分を除き省略してある。また、以下の説明において、特定の材料及び条件等を用いることがあるが、これら材料及び条件は好適例の一つに過ぎず、従って、何らこれらに限定されない。また、各図において同様の構成成分については同一の番号を付して示し、その重複する説明を省略することもある。 30

【0024】

＜第1の実施の形態＞

図1から図4を参照して、この発明の第1の実施の形態について説明する。

【0025】

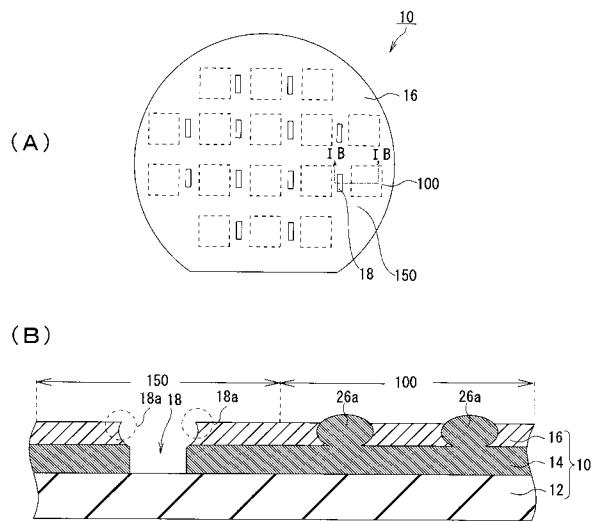

図1(A)は、この実施の形態の半導体装置の一構成例を概略的に示す平面図である。図1(B)は、図1(A)の鎖線部分IB-IB線に沿って切断して得られる切り口を示す概略図である。尚、図1(A)では、素子形成領域100の素子分離部26aの図示を省略してある。 40

【0026】

図1(A)及び(B)に示すように、この実施の形態の半導体装置を構成するウェハ状のSOI基板10には、素子形成領域100と、素子形成領域100同士を互いに隔てるマーク形成領域150とが指定されている。SOI基板10は、半導体支持基板としての第1のシリコン(Si)層12上に、絶縁膜としてのシリコン酸化膜(SiO<sub>2</sub>)14を介して半導体層としての第2の単結晶シリコン層(以下、単に、第2のシリコン層とも称する。)16を具えた構成である。

【0027】

ここでマーク形成領域150のSOI基板10には、第2のシリコン層16の表面か

50

ら第1のシリコン層12が露出される深さに、位置合わせ用マークとなる凹部18が形成されている。また、第2のシリコン層16のうち凹部18のエッジ部(すなわち、縁部)18aには十分な段差が形成されている。尚、ここでの凹部18の縁の形状は方形であるがこれに限定されるものではなく、目的や設計に応じてその形状、ならびに個数や配置を任意好適に設定することができる。

【0028】

続いて、この発明の半導体装置の製造方法について、以下に説明する。

【0029】

先ず、基板として、既に説明したように、第1のシリコン層12上にシリコン酸化膜14を介して第2のシリコン層16が形成されたSOI基板10を用意する。ここでは、ウエハ状の第1のシリコン層12であるシリコン基板上に、シリコン酸化膜14を100~200nm程度の膜厚で形成した後、当該シリコン酸化膜14上に第2のシリコン層16を30~100nmの膜厚で形成してSOI基板10とする。

10

【0030】

続いて、素子形成領域100及びマーク形成領域150の第2のシリコン層16上に、パッド酸化膜としてのシリコン酸化膜20を同時に形成する。シリコン酸化膜20を、例えば、SOI基板10を850程度で加熱して行う熱酸化により、例えば、10~30nm程度の膜厚で形成する。パッド酸化膜20は、SOI基板10への不純物の混入を抑制したり、後述するシリコン窒化膜14とSOI基板10との間の応力を緩和させるはたらきをする。

20

【0031】

続いて、素子形成領域100及びマーク形成領域150のシリコン酸化膜20上に窒化膜としてシリコン窒化膜22を同時に形成する。シリコン窒化膜22を、例えば、ジクロロシラン(SiH2Cl2)ガスを主成分とするLPCVD(Low Pressure Chemical Vapor Deposition)法を用いて、60~150nmの膜厚で形成する。ここでのシリコン窒化膜22の膜厚は、後工程で素子形成領域100及びマーク形成領域150の第2のシリコン層16に酸化部を選択酸化によって形成する際の酸化阻止用マスクとしてはもとより、凹部を形成する際の耐エッチングマスクとして機能する程度の膜厚とする(詳細後述)。

30

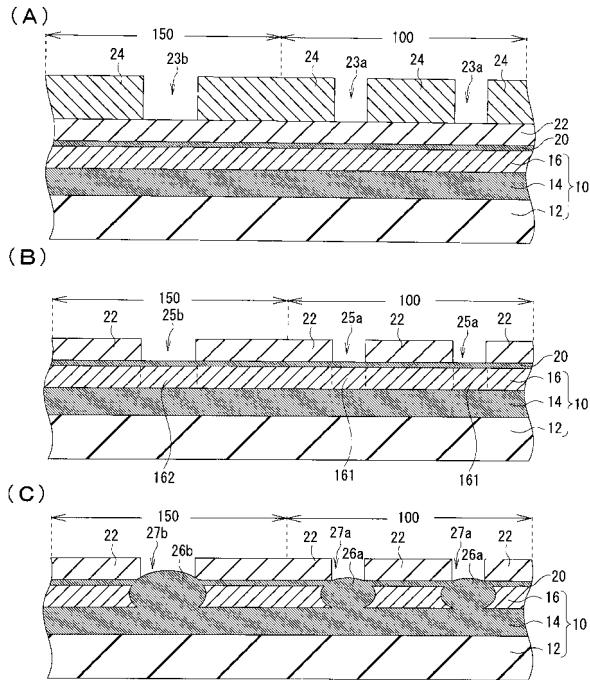

【0032】

続いて、素子形成領域100及びマーク形成領域150のシリコン窒化膜22上に、レジスト層を同時に形成する(不図示)。その後、素子形成領域100及びマーク形成領域150のレジスト層に対して露光・現像を行って、シリコン窒化膜22を露出させる開口(23a、23b)がそれぞれ設けられたマスクパターン24を形成する(図2(A))。このとき、素子形成領域100側の開口23aの位置は、SOI基板10において後述する素子分離部となる酸化部が形成されるべき位置とする。一方、マーク形成領域150側の開口23bの位置は、SOI基板10において後述するマーク形成用の酸化部が形成されるべき位置とする。

40

【0033】

その後、このマスクパターン24をマスクとして、素子形成領域100及びマーク形成領域150のシリコン窒化膜22をエッチング除去し、シリコン酸化膜20をそれぞれ露出させる開口(25a、25b)を形成する。エッチング終了後、マスクパターン24を除去する(図2(B))。

【0034】

その後、素子形成領域100及びマーク形成領域150の第2のシリコン層16のうちシリコン窒化膜22の開口(25a、25b)に対向する部分(161、162(図2(B)参照))をそれぞれ選択的に酸化する。こうして、素子形成領域100及びマーク形

50

成領域 150 に、シリコン酸化膜 14 に達する深さの酸化シリコンからなる酸化部 (26a、26b) をそれぞれ形成する。このとき素子形成領域 100 には、酸化部 26a によって素子分離部が形成される (図 2 (C))。

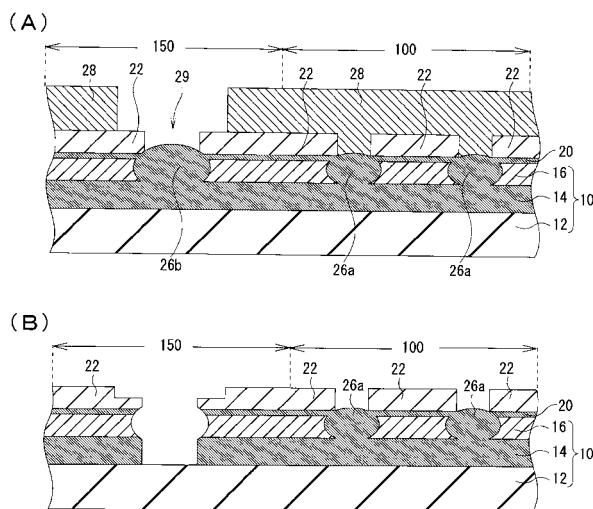

【0035】

その後、素子形成領域 100 及びマーク形成領域 150 の双方に形成された開口 (27a、27b) を埋め込むように、シリコン窒化膜 22 上にレジスト層を同時に形成する (不図示)。その後、マーク形成領域 150 のレジスト層に対してのみ露光・現像を行い、酸化部 26b を露出させる開口 29 が設けられたマスクパターン 28 を形成する (図 3 (A))。

【0036】

その後、残存しているシリコン窒化膜 22 を耐エッチングマスクとして、第 1 のシリコン層 12 が露出されるまで酸化部 26b 及びシリコン酸化膜 14 のエッチングを行う (図 3 (B))。ここでは、例えば、ブチレン ( $C_4H_8$ ) ガス、酸素 ( $O_2$ ) ガス及びアルゴン (Ar) ガスの混合ガスをエッチングガスとするドライエッチングを行い、シリコン酸化膜を選択的に除去する。また、ウェットエッチングを行う場合には、シリコン窒化膜 22 及び第 1 のシリコン層 12 よりもシリコン酸化膜に対するエッチングレートが大きいエッチング液 (例えば、フッ化水素 ( $HF$ ) 水溶液 (フッ化水素酸) を含有する液等) を用いて行うことができる。

【0037】

その後、素子形成領域 100 及びマーク形成領域 150 に残存するシリコン窒化膜 22 を、例えば、熱リン酸 ( $H_3PO_4$ ) を用いたウェットエッチングによって除去する。その後、第 2 のシリコン層 16 上のパッド酸化膜 20 を、例えば、フッ化水素水溶液を含有する液を用いたウェットエッチングによって除去する。

【0038】

こうして、マーク形成領域 150 の SOI 基板 10 に、第 2 のシリコン層 16 の表面から第 1 のシリコン層 12 が露出される深さに、位置合わせ用マークとなる凹部 18 を形成する (図 1 (B) 参照)。

【0039】

こうして、シリコン窒化膜 22 を耐エッチングマスクとしてマーク形成のためのエッチングを行うことにより、凹部 18 のエッジ部 18a には十分な段差が残存している。

【0040】

具体的に、耐エッチングマスクである窒化シリコンに対する酸化シリコンのエッチング選択比は 10 程度である。よって、例えば、酸化シリコンからなる酸化部 26b 及び絶縁膜 14 の膜厚がそれぞれ 200 nm、すなわち総厚が 400 nm の場合には、シリコン窒化膜 22 を最低でも 40 nm 程度 (膜厚のばらつきを見込んで 50 nm 程度) 以上の膜厚で形成すれば良い。

【0041】

さらに、この構成例では、シリコン窒化膜 22 の開口位置によって凹部 18 が位置決めされるため、当該凹部 18 を形成するための新たな位置合わせが不要である。よって、マークである凹部 18 を形成する際の位置ずれの発生を抑制することができる。

【0042】

続いて、以下に、マーク形成領域 150 に形成されたマークである凹部 18 を基準位置として、ゲート電極を形成する方法について説明する。

【0043】

そのために、先ず、凹部 18 を形成後、素子形成領域 100 及びマーク形成領域 150 で露出する第 1 及び第 2 のシリコン層 (12、16) の表面に、酸化膜 (すなわち、ゲート酸化膜) としてシリコン酸化膜 30 を形成する。その後、素子形成領域 100 及びマーク形成領域 150 の酸化膜 30 上に、例えば、ゲート電極材料としてのポリシリコン膜 32 及びタンゲステンシリサイド (WSi) 膜 34、ならびに絶縁膜としてのシリコン窒化膜 36 を順次形成する。その後、素子形成領域 100 及びマーク形成領域 150 のシリコ

10

20

30

40

50

ン窒化膜36上にレジスト層38を凹部18を埋め込むように形成して積層体40を得る(図4(A))。

【0044】

その後、この積層体40に対する露光を行い、凹部18の位置を基準位置として積層体40の位置を調整することにより、ウェハ状の積層体40とフォトマスクとの位置合わせを行う。

【0045】

具体的には、積層体40の上方から当該積層体40に対して、ハロゲン光やレーザー光等を照射して得られる反射光や回折光を検出することにより、マーク位置である凹部18の位置を検出する。このとき、この構成例では、凹部18のエッジ部からの回折光や反射光が他の領域での回折光や反射光に比べて著しく大きくなることから、凹部18の位置の検出を精度良く行うことができる。

【0046】

その結果、ウェハ状の積層体40とフォトマスク(不図示)との位置合わせを精度良く行うことができる。

【0047】

その後、レジスト層38に対して露光・現像を行い、素子形成領域100のゲート電極が形成されるべき位置にレジスト層が残存するように当該レジスト層38をパターニングして、マスクパターン39を形成する(図4(B))。このとき、ゲート電極形成後の、例えばコンタクトホール形成工程において再度凹部18をマークとして使用する場合には、マーク形成領域150にもマスクパターン39を形成するのが良い。すなわち、目的や設計に応じて、上述した凹部18を、ゲート電極形成時におけるマークのほかに、種々の半導体製造プロセスにおける位置合わせ用のマークとして用いることができる。

【0048】

その後、マスクパターン39をマスクとして、露出しているシリコン窒化膜36、タンゲステンシリサイド膜34、ポリシリコン膜32及びシリコン酸化膜30を順次エッチング除去し、素子形成領域100にゲート電極42を形成する。エッチング終了後、マスクパターン39を除去する(図4(C))。

【0049】

上述した説明から明らかなように、この実施の形態によれば、マーク位置の検出精度が向上するため、当該マーク位置を基準位置としてフォトマスクの位置合わせを行う際の合わせずれを抑制することができる。

【0050】

よって、フォトマスクの位置合わせを設計値通り行うことができるので、当該フォトマスクを用いて行う半導体製造プロセスを精度良く行うことができる。よって、従来よりも信頼性の高い半導体装置を実現することができる。

【0051】

さらに、この発明によれば、素子形成領域における工程を一部兼用して、マーク形成領域においてマーク形成を行うことができるので、マーク形成工程の簡便化に効果的である。

【0052】

<第2の実施の形態>

図5(A)から図9(C)を参照して、この発明の第2の実施の形態につき説明する。

【0053】

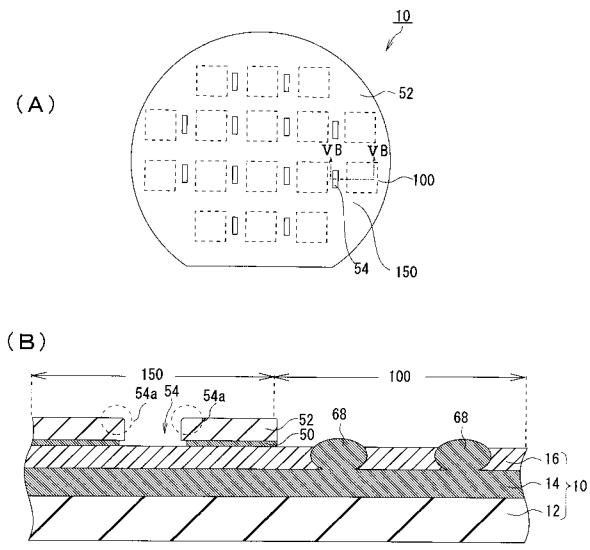

図5(A)はこの実施の形態の半導体装置の一構成例を概略的に示す平面図である。図5(B)は、図5(A)の鎖線部分VB-VB線に沿って切断して得られる切り口を示す概略図である。

【0054】

この実施の形態では、基板上に、エッジ部に十分な段差が形成されたマークとなる凹部を形成している点が第1の実施の形態との主な相違点である。尚、第1の実施の形態で既

10

20

30

40

50

に説明した構成要素と同一の構成要素には同一の番号を付して示し、その具体的な説明を省略する。

【0055】

図5(A)及び(B)に示すように、ここでマーク形成領域150には、SOI基板10上に順次形成されたシリコン酸化膜50及びシリコン窒化膜52によって、SOI基板10の第2のシリコン層16を露出させる深さの凹部54が形成されている。このとき、シリコン窒化膜52のうち凹部54のエッジ部(すなわち、縁部)を構成する部分54aには、十分な段差が形成されている。

【0056】

続いて、この発明の半導体装置の製造方法について、以下に説明する。

10

【0057】

先ず、第1の実施の形態と同様の構成を有するSOI基板10を用意する。

【0058】

その後、第1の実施の形態と同様の方法で、素子形成領域100及びマーク形成領域150の第2のシリコン層16上に、パッド酸化膜としてのシリコン酸化膜50を、10~30nm程度の膜厚で同時に形成する。ここでシリコン酸化膜50の膜厚は、後工程で素子形成領域100及びマーク形成領域150の第2のシリコン層16に素子分離部を選択酸化によって形成可能な程度とする。

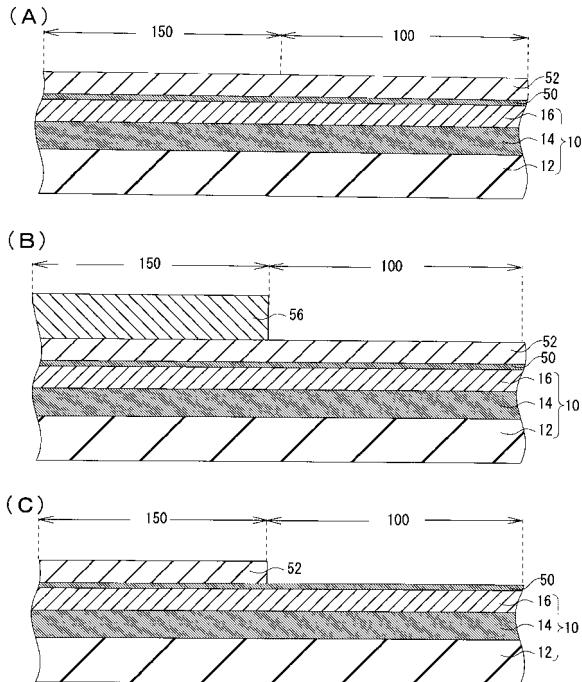

【0059】

その後、第1の実施の形態と同様の方法で、素子形成領域100及びマーク形成領域150のシリコン酸化膜50上に窒化膜としてシリコン窒化膜52を、LPCVDを用いて60~150nmの膜厚で同時に形成する(図6(A))。ここでシリコン窒化膜52の膜厚は、後工程で素子形成領域100に素子分離部を形成する際、マーク形成領域150の第2のシリコン層16が選択酸化されるのを阻止する第2のシリコン窒化膜(説明後述)の膜厚を考慮して決定する。

20

【0060】

その後、素子形成領域100及びマーク形成領域150のシリコン窒化膜52上に、レジスト層を同時に形成する(不図示)。その後、マーク形成領域150のレジスト層のみを残存させるように、レジスト層をパターニングしてマスクパターン56を形成する(図6(B))。

30

【0061】

その後、マスクパターン56をマスクとして、素子形成領域100のシリコン窒化膜52をエッティングによって除去する。エッティング終了後、マスクパターン56を除去する(図6(C))。

【0062】

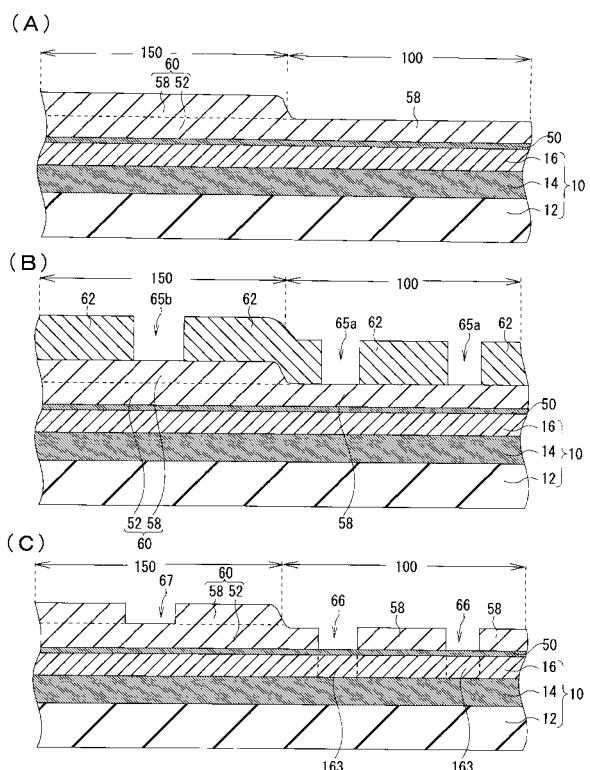

その後、素子形成領域100及びマーク形成領域150のシリコン酸化膜50上に、第1の窒化膜として第1のシリコン窒化膜58を、LPCVDを用いて第1の膜厚(60~150nm)で形成する(図7(A))。ここで第1のシリコン窒化膜58の第1の膜厚は、後工程において素子形成領域100に素子分離部を選択酸化によって形成するに当たり、第2のシリコン層16のうち素子分離部とする部分以外が選択酸化されるのを阻止するマスクとして機能する程度とする。

40

【0063】

こうして、素子形成領域100のシリコン酸化膜50上に、第1の膜厚を有する第1のシリコン窒化膜58が形成される。一方、マーク形成領域150のシリコン酸化膜50上に、既に形成済みのシリコン窒化膜52に加え第1のシリコン窒化膜58を形成することにより、第1の膜厚よりも厚い第2の膜厚を有する第2のシリコン窒化膜60が形成される。

【0064】

続いて、素子形成領域100の第1のシリコン窒化膜58上、及びマーク形成領域150の第2のシリコン窒化膜60上にレジスト層を同時に形成する(不図示)。その後、素

50

子形成領域 100 及びマーク形成領域 150 のレジスト層に対して露光・現像を行って、第 1 及び第 2 のシリコン窒化膜 (58、60) を露出させる開口 (65a、65b) がそれぞれ設けられたマスクパターン 62 を形成する (図 7 (B))。このとき、素子形成領域 100 側の開口 65a の位置は、SOI 基板 10 において後述する素子分離部となる酸化部が形成されるべき位置とする。一方、マーク形成領域 150 側の開口 65b の位置は、SOI 基板 10 上にマークとしての凹部が形成されるべき位置とする。

#### 【0065】

その後、マスクパターン 62 をマスクとして、素子形成領域 100 の第 1 のシリコン窒化膜 58 をエッティング除去してシリコン酸化膜 50 を露出させる開口 66 を形成する。ここでは、例えば、三フッ化メタン (CHF<sub>3</sub>) ガス、酸素 (O<sub>2</sub>) ガス及びアルゴン (Ar) ガスの混合ガスをエッティングガスとするドライエッティングを用いて行う。一方、マーク形成領域 150 の第 2 のシリコン窒化膜 60 には、第 1 の膜厚の深さ分だけオーバーエッティングされた凹部 67 が形成されている。エッティング終了後、マスクパターン 62 を除去する (図 7 (C))。

#### 【0066】

その後、マーク形成領域 150 には第 2 のシリコン窒化膜 60 を残存させた状態で、素子形成領域 100 の第 2 のシリコン層 16 のうち第 1 のシリコン窒化膜 58 の開口 66 に對向する部分 163 (図 7 (C) 参照) を選択的に酸化する (図 8 (A))。これにより、素子形成領域 100 に、シリコン酸化膜 14 に達する深さの酸化シリコンからなる素子分離部としての酸化部 68 を形成することができる。

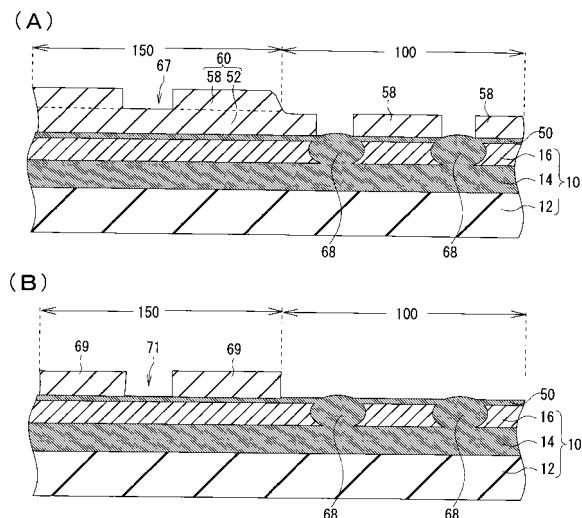

#### 【0067】

その後、素子形成領域 100 に残存する第 1 のシリコン窒化膜 58 を、例えば、熱リン酸を用いたウェットエッティングによって除去する。このとき、同時に、マーク形成領域 150 の第 2 のシリコン窒化膜 60 に対してもウェットエッティングを行う。こうして、マーク形成領域 150 に、凹部 67 に対応する位置のパッド酸化膜 50 を露出させる開口 71 を有するシリコン窒化膜 69 をパターニング形成する (図 8 (B))。

#### 【0068】

続いて、素子形成領域 100 及びマーク形成領域 150 の第 2 のシリコン層 16 上のパッド酸化膜 50 を、例えば、フッ化水素水溶液を用いたウェットエッティングによって除去する。このとき、マーク形成領域 150 では、シリコン窒化膜 69 がマスクとなり、パッド酸化膜 50 のうち当該シリコン窒化膜 69 に覆われていない部分が除去される。また、このとき、ウェットエッティングが等方性エッティングであることに起因して、パッド酸化膜 50 の側壁部がサイドエッティングされていても良い。

#### 【0069】

こうして、マーク形成領域 150 の SOI 基板 10 上に、シリコン酸化膜 50 及びシリコン窒化膜 69 によって、位置合わせ用マークとなる凹部 54 を形成する (図 5 (B) 参照)。こうして得られた凹部 54 のエッジ部 54a には、十分な段差が形成されている。尚、マークである凹部 54 の深さは、後工程における検出精度を考慮して最低でも 100 nm とするのがほしい。こうすることにより、凹部 54 のエッジ部からの反射光や回折光を確実に検出することができる。

#### 【0070】

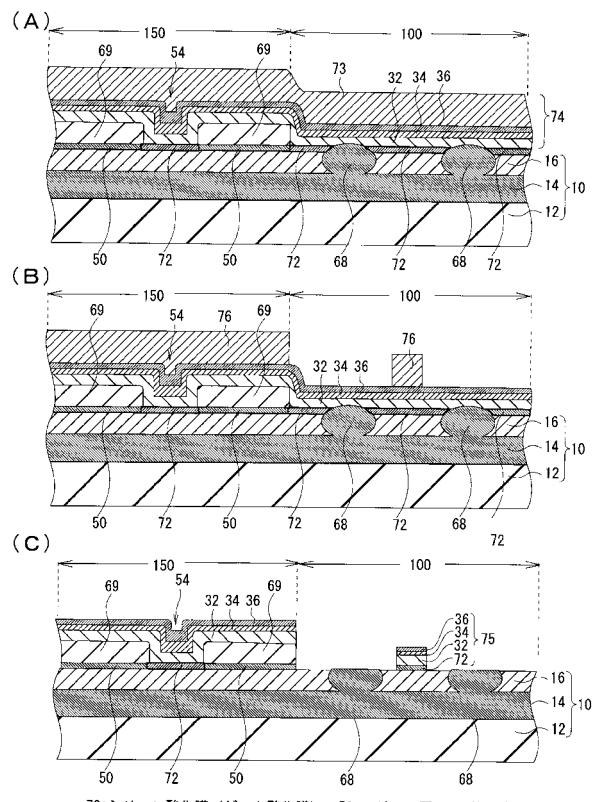

続いて、以下に、マーク形成領域 150 に形成されたマークである凹部 54 を基準位置として、ゲート電極を形成する方法について説明する。

#### 【0071】

そのために、先ず、凹部 54 形成後、素子形成領域 100 及びマーク形成領域 150 の露出する第 2 のシリコン層 16 の表面に、酸化膜 (すなわち、ゲート酸化膜) としてシリコン酸化膜 72 を形成する。その後、素子形成領域 100 及びマーク形成領域 150 において露出する、シリコン窒化膜 69、素子分離部 68 及びシリコン酸化膜 72 の表面に、第 1 の実施の形態と同様に、ゲート電極材料としてのポリシリコン膜 32 及びタンゲステンシリサイド (WSi) 膜 34、ならびに絶縁膜としてのシリコン窒化膜 36 を順次に形

10

20

30

40

50

成する。その後、素子形成領域 100 及びマーク形成領域 150 のシリコン窒化膜 36 上に、レジスト層 73 を凹部 54 を埋め込むように形成して積層体 74 を得る（図 9（A））。

【0072】

その後、この積層体 74 に対する露光を行い、凹部 54 の位置を基準位置として積層体 74 の位置を調整することにより、ウェハ状の積層体 74 とフォトマスクとの位置合わせを行う。

【0073】

具体的には、積層体 74 の上方から当該積層体 74 に対して、ハロゲン光やレーザー光等を照射して得られる反射光や回折光を検出することにより、マーク位置である凹部 54 の位置を検出する。このとき、この構成例では、凹部 54 のエッジ部からの回折光や反射光が、他の領域での回折光や反射光に比べて著しく大きくなることから、凹部 54 の位置の検出を精度良く行うことができる。

【0074】

その結果、ウェハ状の積層体 74 とフォトマスク（不図示）との位置合わせを精度良く行うことができる。

【0075】

その後、レジスト層 73 に対して露光・現像を行い、素子形成領域 100 のゲート電極が形成されるべき位置にレジスト層が残存するように当該レジスト層 73 をパターニング形成して、マスクパターン 76 を形成する（図 9（B））。このとき、ゲート電極形成工程後、例えばコンタクトホール形成工程において再度凹部 54 をマークとして使用する場合には、マーク形成領域 150 側にもマスクパターン 76 を形成するのが良い。すなわち、目的や設計に応じて、上述した凹部 54 を、ゲート電極形成時におけるマークのほかに、種々の半導体製造プロセスにおける位置合わせ用のマークとして用いることができる。

【0076】

その後、マスクパターン 76 をマスクとして、露出しているシリコン窒化膜 36、タンゲステンシリサイド膜 34、ポリシリコン膜 32 及びシリコン酸化膜 72 を順次エッティング除去し、素子形成領域 100 にゲート電極 75 を形成する。エッティング終了後、マスクパターン 76 を除去する（図 9（C））。

【0077】

上述した説明から明らかなように、この実施の形態によれば、第 1 の実施の形態と同様の効果を得ることができる。

【0078】

さらに、この実施の形態のように、基板自体にマークとしての凹部を形成しない構成の場合には、基板の半導体層のさらなる薄膜化を進めることができる。

【0079】

以上、この発明は、上述した実施の形態の組合せのみに限定されない。よって、任意好適な段階において好適な条件を組み合わせ、この発明を適用することができる。

【図面の簡単な説明】

【0080】

【図 1】第 1 の実施の形態の半導体装置の説明に供する図である。

【図 2】第 1 の実施の形態の半導体装置の製造工程を説明する工程図（その 1）である。

【図 3】第 1 の実施の形態の半導体装置の製造工程を説明する工程図（その 2）である。

【図 4】第 1 の実施の形態の半導体装置の製造工程を説明する工程図（その 3）である。

【図 5】第 2 の実施の形態の半導体装置の説明に供する図である。

【図 6】第 2 の実施の形態の半導体装置の製造工程を説明する工程図（その 1）である。

【図 7】第 2 の実施の形態の半導体装置の製造工程を説明する工程図（その 2）である。

【図 8】第 2 の実施の形態の半導体装置の製造工程を説明する工程図（その 3）である。

【図 9】第 2 の実施の形態の半導体装置の製造工程を説明する工程図（その 4）である。

【符号の説明】

10

20

30

40

50

## 【0081】

- 10 : S O I 基板 ( 基板 )

12 : 第 1 のシリコン層 ( 半導体支持基板 )

14 : シリコン酸化膜 ( 絶縁膜 )

16 : 第 2 のシリコン層 ( 半導体層 )

18 、 54 : 凹部 ( マーク )

18 a 、 54 a : 凹部のエッジ部

20 、 50 : シリコン酸化膜 ( パッド酸化膜 ( 酸化膜 ) )

22 、 52 、 69 : シリコン窒化膜 ( 窒化膜 )

24 、 28 、 39 、 56 、 62 、 76 : マスクパターン 10

23 a 、 23 b 、 25 a 、 25 b 、 27 a 、 27 b 、 29 、 65 a 、 65 b 、 66 、 7

1 : 開口

26 a 、 68 : 酸化部 ( 素子分離部 )

26 b : 酸化部

30 、 72 : シリコン酸化膜 ( ゲート酸化膜 )

32 : ポリシリコン膜

34 : タングステンシリサイド膜

36 、 69 : シリコン窒化膜

38 、 73 : レジスト層

40 、 74 : 積層体 20

42 、 75 : ゲート電極

58 : 第 1 のシリコン窒化膜 ( 窒化膜 )

60 : 第 2 のシリコン窒化膜 ( 窒化膜 )

67 : 凹部

100 : 素子形成領域

150 : マーク形成領域

161 : 第 2 のシリコン層のうち開口 25 a と対向する部分

162 : 第 2 のシリコン層のうち開口 25 b と対向する部分

163 : 第 2 のシリコン層のうち開口 66 と対向する部分

【図1】

10:SOI基板(基板) 12:第1のシリコン層(半導体支持基板)

14:シリコン酸化膜(絶縁膜) 16:第2のシリコン層(半導体層)

18:凹部(マーク) 18a:凹部のエッジ部 26a:酸化部(素子分離部)

100:素子形成領域 150:マーク形成領域

第1の実施の形態の半導体装置

【図2】

20:シリコン酸化膜(パッド酸化膜) 22:シリコン窒化膜

23a, 23b, 25a, 25b, 27a, 27b:開口 24:マスクパターン 26b:酸化部

161:第2のシリコン層のうち開口25aと対向する部分

162:第2のシリコン層のうち開口25bと対向する部分

第1の実施の形態の半導体装置の製作工程図(その1)

【図3】

28:マスクパターン 29:開口

第1の実施の形態の半導体装置の製作工程図(その2)

【図4】

30:シリコン酸化膜(ゲート酸化膜) 32:ポリシリコン膜

34:タンゲステンシリサイド膜 36:シリコン窒化膜 38:レジスト層

39:マスクパターン 40:積層体 42:ゲート電極

第1の実施の形態の半導体装置の製作工程図(その3)

【図5】

50:シリコン酸化膜(バッド酸化膜) 52:シリコン窒化膜

54:凹部 54a:凹部のエッジ部 68:酸化部(素子分離部)

第2の実施の形態の半導体装置の説明に供する図

【図6】

56:マスクパターン

第2の実施の形態の半導体装置の製造工程図(その1)

【図7】

58:第1のシリコン窒化膜 60:第2のシリコン窒化膜 62:マスクパターン

65a, 65b, 66:開口 67:凹部 163:第2のシリコン層のうち開口66と対向する部分

第2の実施の形態の半導体装置の製造工程図(その2)

【図8】

69:シリコン窒化膜 71:開口

第2の実施の形態の半導体装置の製造工程図(その3)

【図9】

72:シリコン酸化膜(ゲート酸化膜) 73:レジスト層 74:積層体

75:ゲート電極 76:マスクパターン

第2の実施の形態の半導体装置の製造工程図(その4)

---

フロントページの続き

(51)Int.CI. F I

H 0 1 L 27/08 (2006.01) H 0 1 L 27/08 3 3 1 E

(72)発明者 渡辺 実

東京都港区虎ノ門1丁目7番12号 沖電気工業株式会社内

審査官 秋田 将行

(56)参考文献 特開平02-262321 (JP, A)

特開平03-049212 (JP, A)

特開2000-156506 (JP, A)

特開2000-216400 (JP, A)

特開2002-353120 (JP, A)

特開2004-319637 (JP, A)

(58)調査した分野(Int.CI., DB名)

H 0 1 L 2 1 / 0 2 7

G 0 3 F 7 / 0 0 - 7 / 0 2

G 0 3 F 9 / 0 0 - 9 / 0 2