(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第6027059号

(P6027059)

(45) 発行日 平成28年11月16日(2016.11.16)

(24) 登録日 平成28年10月21日(2016.10.21)

(51) Int.Cl.

F 1

G 11 C 16/02 (2006.01)

G 11 C 16/04 (2006.01)G 11 C 17/00 6 14

G 11 C 17/00 6 22 E

G 11 C 17/00 6 41

請求項の数 19 外国語出願 (全 16 頁)

(21) 出願番号 特願2014-144986 (P2014-144986)

(22) 出願日 平成26年7月15日 (2014.7.15)

(65) 公開番号 特開2015-22788 (P2015-22788A)

(43) 公開日 平成27年2月2日 (2015.2.2)

審査請求日 平成27年1月20日 (2015.1.20)

(31) 優先権主張番号 13/943,441

(32) 優先日 平成25年7月16日 (2013.7.16)

(33) 優先権主張国 米国(US)

(73) 特許権者 500373758

シーゲイト テクノロジー エルエルシー

Seagate Technology

LLC

アメリカ合衆国、95014 カリフォルニア州、クパチーノ、サウス・ディ・アンザ・ブールバード、10200

10200 South De Anza Blvd Cupertino CA

95014 United States of America

(74) 代理人 110001195

特許業務法人深見特許事務所

最終頁に続く

(54) 【発明の名称】メモリ内のデータを管理するための方法および装置

## (57) 【特許請求の範囲】

## 【請求項 1】

一組のソリッドステート不揮発性メモリセルに、前記組の中の各メモリセルが書き込みにより関連する初期プログラム状態になるように、データを書き込むステップと、

前記組の中の選択されたメモリセルのプログラム状態のドリフトを検出するステップと、

前記選択されたメモリセルを部分的に再プログラムして前記選択されたメモリセルを前記関連する初期プログラム状態に戻すステップとを含み、前記組の中の少なくとも1つのその他のメモリセルは部分的に再プログラムされず、

電荷の複数の増分を与えて前記選択されたメモリセルを前記初期プログラム状態にプログラミし、その後、電荷の、より小さい複数の増分を与えて前記選択されたメモリセルを部分的に再プログラムして前記初期プログラム状態に戻す、方法。

## 【請求項 2】

前記一組のソリッドステート不揮発性メモリセルは、各フラッシュメモリセルのフローティングゲートに電荷を蓄積することにより1ページ分のデータを同時に格納することによってプログラムされる一行のフラッシュメモリセルを含む、請求項1に記載の方法。

## 【請求項 3】

前記フラッシュメモリセルは各々、2ページ分のデータが前記メモリセルによって格納されるように、マルチレベルセル(MLC)として構成される、請求項2に記載の方法。

## 【請求項 4】

10

20

第1の書込パルス幅を与えることによって、各メモリセルを前記関連する初期プログラム状態にプログラムし、その後第2の書込パルス幅を与えることによって、選択されたメモリセルをその関連するプログラム状態に再プログラムし、前記第2の書込パルス幅は前記第1の書込パルス幅よりも短い、請求項1から請求項3のいずれか1項に記載の方法。

**【請求項5】**

前記プログラム状態のドリフトは、電圧しきい値を選択されたメモリセルに与えることによって検出される、請求項1に記載の方法。

**【請求項6】**

前記プログラム状態のドリフトは、選択されたメモリセルに関連するピットエラーレート(BER)に応じて検出される、請求項1に記載の方法。

10

**【請求項7】**

前記プログラム状態のドリフトは、選択されたメモリセルが前記関連する初期プログラム状態にプログラムされてから経過した時間に応じて検出される、請求項1に記載の方法。

**【請求項8】**

前記プログラム状態のドリフトは、選択されたメモリセルに関連する温度測定値に応じて検出される、請求項1に記載の方法。

**【請求項9】**

前記メモリセルは、抵抗ランダムアクセスメモリ(ROM(登録商標))セル、相変化ランダムアクセスメモリ(PCRAM)セル、またはスピントルクトランスマーファーランダムアクセスメモリ(STRAM)セルのうちの選択されたいずれか1つである、請求項1に記載の方法。

20

**【請求項10】**

前記選択されたメモリセルを、再プログラムされたものとして、前記選択されたメモリセルに関連する制御データにマークするステップをさらに含む、請求項1から請求項9のいずれか1項に記載の方法。

**【請求項11】**

アドレス可能な単位になるように配列されたソリッドステート不揮発性メモリセルのアレイと、

メモリの選択されたアドレス可能単位に、前記選択されたアドレス可能単位の中の各メモリセルが関連する初期プログラム状態を有するように、データを書込むようにされた書回路と、

30

前記選択されたアドレス可能単位の中のメモリセルのうちの少なくとも1つのプログラム状態のドリフトを検出するように、かつ、前記選択されたアドレス可能単位の中の全メモリセルよりも少ないメモリセルを部分的に再プログラムして前記関連する初期プログラム状態にすることを前記書回路に指示するようにされた、部分再プログラミング回路とを備え、

前記部分再プログラミング回路は、前記選択されたメモリセルの消去を挿まずに、前記初期プログラム状態にプログラムした際の複数の電荷の増分よりも小さい、複数の電荷の増分を与えて前記選択されたメモリセルを部分的に再プログラムして前記初期プログラム状態に戻す、装置。

40

**【請求項12】**

前記選択されたアドレス可能単位は、1行のフラッシュメモリセルであり、前記書回路は、前記フラッシュメモリセルに電荷の第1の増分を蓄積し移動することによって1ページのデータを前記行に書き込み、前記書回路は、前記電荷の第1の増分よりも小さい電荷の第2の増分を蓄積し移動することによって前記行の前記フラッシュメモリセルを部分的に再プログラムする、請求項11に記載の装置。

**【請求項13】**

第1の書込パルス幅を与えることによって、各メモリセルを前記関連する初期プログラム状態にプログラムし、その後第2の書込パルス幅を与えることによって、選択されたメ

50

モリセルをその関連するプログラム状態に再プログラムし、前記第2の書込パルス幅は前記第1の書込パルス幅よりも短い、請求項11または請求項12に記載の装置。

**【請求項14】**

前記プログラム状態のドリフトは、電圧しきい値を選択されたメモリセルに与えることによって検出される、請求項11に記載の装置。

**【請求項15】**

前記プログラム状態のドリフトは、選択されたメモリセルに関連するビットエラーレート(BER)に応じて検出される、請求項11に記載の装置。

**【請求項16】**

前記プログラム状態のドリフトは、選択されたメモリセルが前記関連する初期プログラム状態にプログラムされてから経過した時間に応じて検出される、請求項11に記載の装置。 10

**【請求項17】**

前記プログラム状態のドリフトは、選択されたメモリセルに関連する温度測定値に応じて検出される、請求項11に記載の装置。

**【請求項18】**

一単位として消去され割当てられる複数のガーベジコレクション単位(GCU)になるように配列された不揮発性フラッシュメモリセルを含むフラッシュメモリアレイと、

選択されたGCUからデータを読み出し選択されたGCUにデータを書き込み選択されたGCUを消去するようにされた、読み出し/書き込み/消去(R/W/E)回路と。 20

前記選択されたGCUの中のプログラムされた一組のフラッシュメモリセルをプログラミングドリフトが生じたものであると識別し、かつ、前記プログラムされた一組のフラッシュメモリセルを部分的に再プログラムすることで電荷を前記メモリセルに移動させて前記メモリセルを前記選択されたGCUの消去を挟まずにその初期プログラム状態に戻すことを前記R/W/E回路に指示する、部分再プログラミング回路とを備え、

電荷の複数の増分を与えて、選択されたメモリセルを前記初期プログラム状態にプログラムし、その後、電荷の、より小さい複数の増分を与えて前記選択されたメモリセルを部分的に再プログラムして前記初期プログラム状態に戻す、装置。

**【請求項19】**

前記部分再プログラミング回路はさらに、前記部分的に再プログラムする動作の前に1つ以上の電圧しきい値を前記プログラムされた一組のフラッシュメモリセルに与えて各々のプログラム状態を評価することを前記R/W/E回路に指示する、請求項18に記載の装置。 30

**【発明の詳細な説明】**

**【発明の概要】**

**【課題を解決するための手段】**

**【0001】**

**概要**

本開示のさまざまな実施の形態は概してフラッシュメモリアレイ等のメモリ内のデータの管理に関する。 40

**【0002】**

いくつかの実施の形態に従うと、一組のソリッドステート不揮発性メモリセルに、この組の中の各メモリセルが書込により関連する初期プログラム状態になるように、データを書込む。この組の中の選択されたメモリセルのプログラム状態のドリフトを検出し、この選択されたメモリセルを部分的に再プログラムして上記関連する初期プログラム状態に戻す。

**【0003】**

さまざまな実施の形態を特徴付ける上記およびその他の特徴は、以下の詳細な説明および添付の図面に鑑みて理解することができる。

**【図面の簡単な説明】**

## 【0004】

【図1】さまざまな実施の形態に従う、ホスト装置と通信するように配置されたデータ記憶装置の機能ブロック図を示す。

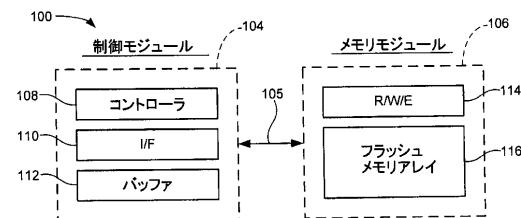

【図2】いくつかの実施の形態に従う、図1のデータ記憶装置のブロック図を示す。

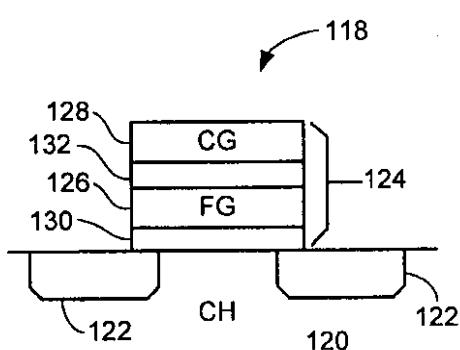

【図3】図1の装置で使用することができるフラッシュメモリセル構造を示す。

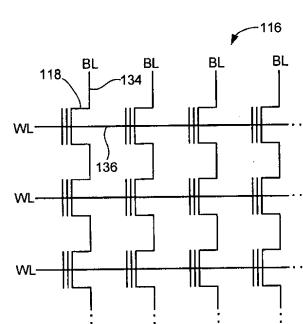

【図4】図3のセルを用いたフラッシュメモリアレイの一部の概略図である。

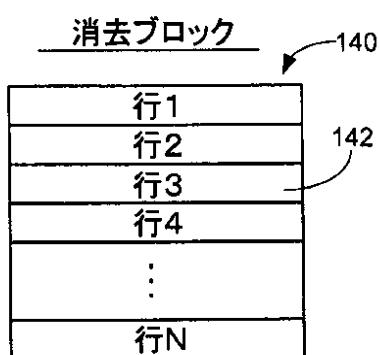

【図5】消去ブロックの代表的なフォーマットを示す。

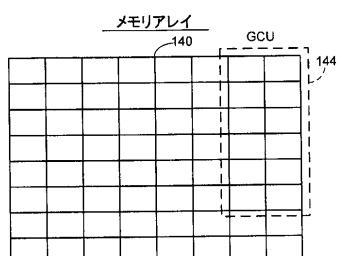

【図6】消去ブロックをガーベジコレクション単位(garbage collection unit)(GCU)になるように配列したものを示す。

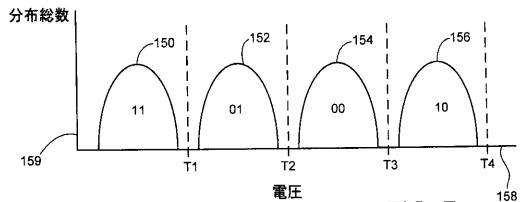

【図7】図6のメモリセルの電荷密度分布を示す。

10

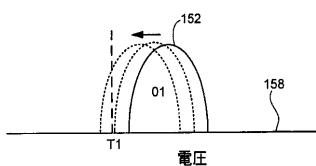

【図8】図7から選択された分布における電荷ドリフトを示す。

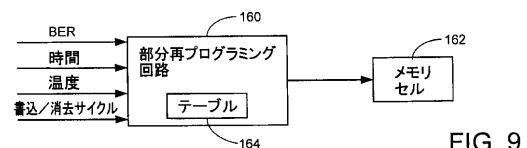

【図9】さまざまな実施の形態に従い動作することにより図8の電荷ドリフトを修正するデータ記憶装置の部分再プログラミング回路である。

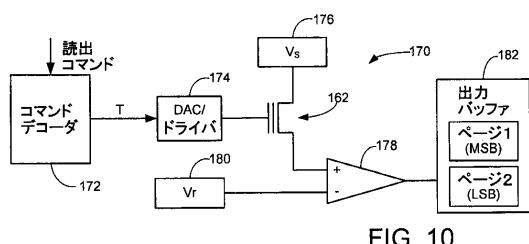

【図10】データ記憶装置の読み出し/書き込み/消去回路の読み出部である。

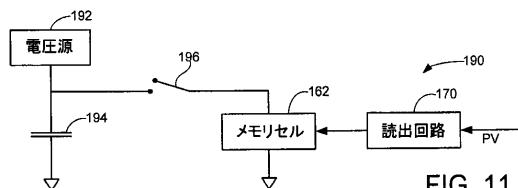

【図11】読み出し/書き込み/消去回路の書き込み部である。

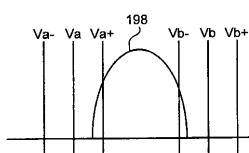

【図12】プログラミングドリフトの評価のために異なる電圧検知しきい値をメモリセルの分布に与える様子を示す。

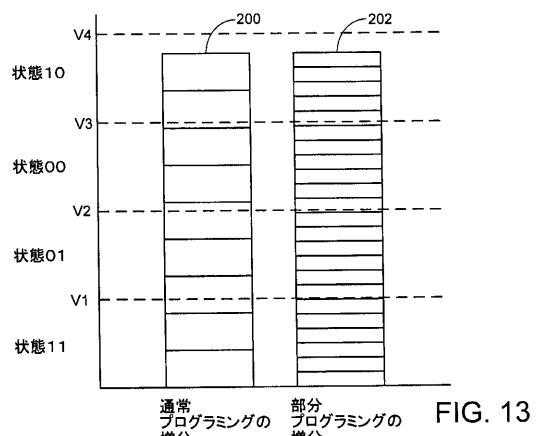

【図13】通常プログラミング動作および部分プログラミング動作それぞれの間に図11の書き込み部によって与えられる通常プログラミングの増分および部分プログラミングの増分を示す。

20

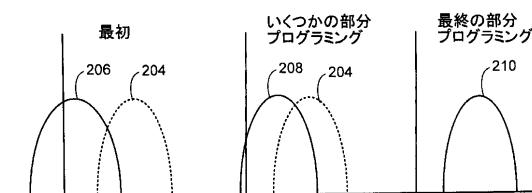

【図14】部分プログラミングシーケンスである。

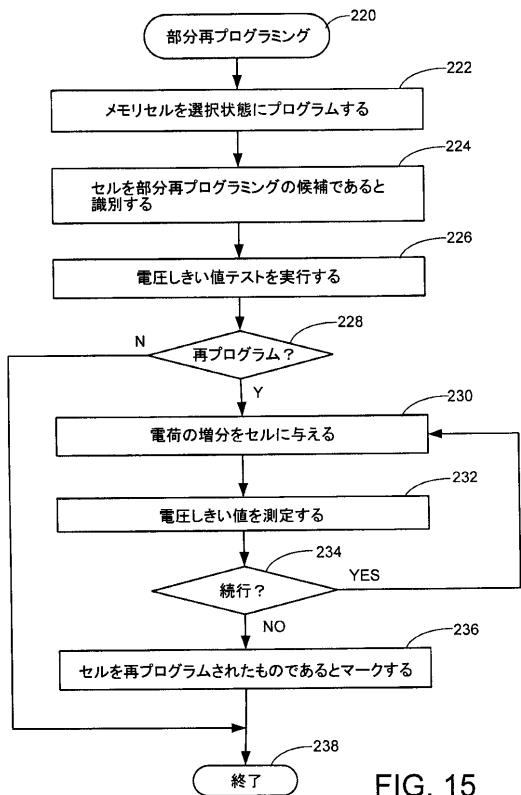

【図15】いくつかの実施の形態に従う部分プログラミングルーチンのフローチャートである。

## 【発明を実施するための形態】

## 【0005】

## 詳細な説明

本開示は概して、データ記憶装置のフラッシュメモリアレイ等であるがこれに限定されないメモリモジュールに格納されたデータの管理に関する。

## 【0006】

当該技術では多様な不揮発性データ記憶メモリが知られている。いくつかの不揮発性メモリは、フラッシュメモリ、抵抗ランダムアクセスメモリ(RRAM(登録商標))、スピントルクトランスマニアランダムアクセスメモリ(STRAM)、相変化ランダムアクセスメモリ(PCM)等の、ソリッドステートメモリセルの形態を取る。

30

## 【0007】

これらおよびその他の種類のメモリセルは、半導体構造であり、セルの、プログラムされた電気的、機械的、および/または構造的状態との関連でデータを格納する。プログラム状態が長期間維持されるという点では名目上不揮発性であるが、メモリセルはプログラムされた状態の変化(プログラミングドリフト)を引起すさまざまな影響を受ける可能性がある。こういった影響は、読み出しディスターブ(disturb)、書き込みディスターブ、電荷ドリフト、温度劣化、減磁、累積する書き込み/消去サイクル、消耗等を含み得るものであり、時間の経過に伴ってセルのプログラム完全性に影響する可能性がある。

40

## 【0008】

プログラミングドリフトが進行しプログラムされたデータの確実なりカバリを妨げるようになる前に、現在格納されているデータに対してリフレッシュ動作を実行して現在のセルを再プログラムするか、または、データを新たな一組のセルに書き込むことが一般的である。メモリセルの中には、データをセルに再び書き込む前に、消去動作を挟むことが必要なメモリセルがある。ガーベジコレクション動作は、現在のデータを新たな場所に再度書き込み続けて消去を行なうかそうでなければメモリの1ブロックをリセットすることによって、このメモリブロックを、利用できる割当プール(allocation pool)に戻すことのみ得る。

50

**【 0 0 0 9 】**

現在のリフレッシュ動作（ガーベジコレクション動作を含むがこれに限定される訳ではない）は、機能するものの、その問題は、データの再書き込みおよび必要に応じてメモリセルの消去が行なわれることによって、メモリセルの動作総寿命が短縮する可能性があることである。たとえば、いくつかの種類のフラッシュメモリセルは、わずか約 5000 書込み / 消去サイクル後に消耗して使えなくなる。それ以外の種類のメモリセルは、書き込みおよび / または消去の繰返しが原因で、同じように消耗し易くなる可能性がある。

**【 0 0 1 0 】**

ライトアンプリフィケーション (write amplification) は、フラッシュメモリセルを含むソリッドステート不揮発性メモリセルに付随する関連現象である。ライトアンプリフィケーションは一般的に、あるメモリ内に特定のデータセットが書き込まれる総回数に関係する。理想的なライトアンプリフィケーション値は 1 に等しいであろう。なぜなら、1 つのデータセットを一旦受けたらそのメモリへの書き込みは一度だけであることが最適であるからである。しかしながら実際は、ガーベジコレクションおよびその他のリフレッシュ動作の結果、1 つのアレイ内でのデータの移動、再書き込み、コピーまたは複製が複数回行なわれることが多い。現世代のソリッドステートドライブ (SSD) の中には、典型的なライトアンプリフィケーション値が 3 以上であるものがある。これは、ホストから受けた各データセットを、受けたときにメモリに最初に書き込んだ後、最終的にはさらに少なくとも二回書き込むことを意味する。

**【 0 0 1 1 】**

ライトアンプリフィケーションのレベルが高ければ、メモリの動作寿命が短くなる可能性があり、もしこのメモリ内において異なる場所に同一データの複数のセットが現在存在している場合は新たなデータを収容する能力が低下する可能性もあることが、理解できる。

**【 0 0 1 2 】**

したがって、本開示のさまざまな実施の形態は概して、ライトアンプリフィケーションを減じるようにソリッドステート不揮発性メモリ内のデータを管理するための装置および方法に関する。以下で説明するように、1 ブロックのメモリセルを、初期プログラミング状態にプログラムする。推定または検出されたプログラミングドリフトの結果、上記メモリセルのうちの 1 つ以上を部分再プログラミングの候補であると識別する。

**【 0 0 1 3 】**

部分再プログラミングはこの 1 つ以上のメモリセルに適用される。すなわち、メモリセルに、電荷の小さな増分等のプログラミング力 (programming effort) の相対的に小さい増分を与えることによって、このセルを、前に適用されたプログラミング状態に戻す。このセルは、再プログラムされたことを示すために、タイム / 日付スタンプまたは他の表示データでマークしてもよい。このようにして、オーバヘッド時間およびメモリアレイ内でデータを移動させるのに必要なリソースを減じることができ、不必要的消去および書き込み動作を原因とするメモリアレイの消耗を回避することができる。

**【 0 0 1 4 】**

いくつかの実施の形態では、部分再プログラミングを、フラッシュメモリ環境内で、フラッシュメモリセルに与えられた電圧しきい値またはフラッシュメモリセルのビットエラーレートを読み取ることによって測定された、時間の経過に伴いフラッシュメモリセルが失った電荷の量に基づいて、実行する。次に、このセルを優先的に部分的に再プログラムして元の状態に戻す。これにより、データを新しいフレッシュなブロックにコピーし古いブロックを再利用する必要はなくなる。

**【 0 0 1 5 】**

この部分再プログラミングは、小さくしたプログラミング電圧、パルス等を用いて実行することができる。フラッシュメモリセル、P C R A M セル、S T R A M セル、R R A M セル等を含む、種類が異なるメモリセルを、部分的に再プログラムすることができる。フラッシュメモリセルの場合は、実質上、セルの電圧しきい値をその元のプログラム状態に

10

20

30

40

50

戻すのに十分な電子だけをフローティングゲートの境界を越えて移動させる。

#### 【0016】

さらに他の実施の形態では、ルックアップテーブル、または、伝達関数等の他の手法を使用して、所与のメモリセルにとって適切な回復プログラミング力を決定することができる。フラッシュメモリセル内の電荷消失に影響し得る変数は、温度、時間、およびプログラム／消去サイクルを含む。この装置は、これらおよびその他の変数を追跡し、バックグラウンドにおいて部分再プログラミングの適用をスケジュールすることにより、特定の分布許容差の中でプログラミング状態を維持することができる。

#### 【0017】

さまざまな実施の形態の上記およびその他の特徴は、先ず図1を検討することによって理解できる。図1は、ホスト装置102に結合されたデータ記憶装置100を特徴とするデータ処理システムの簡略化されたブロック図を示している。記憶装置100およびホスト102は各々、任意の適切な形態を取ることができる。いくつかの実施の形態において、ホスト102は、デスクトップコンピュータ、サーバ、携帯型電子機器、スマートフォン、ラップトップコンピュータ、タブレット、ゲーム機等の、ネットワークアクセス可能な計算装置である。記憶装置100は、ホスト102に組込まれてもよく、または、ホストにローカル接続もしくはネットワークを介して接続されることによって、ホスト102に対し揮発性および／または不揮発性メモリデータ記憶機能を提供してもよい。

10

#### 【0018】

図2は、いくつかの実施の形態に従う図1の記憶装置102の代表的な構造を示す。この装置102は制御モジュール104とメモリモジュール106とを含む。制御モジュール104は、データ処理システムに対してトップレベルの制御を提供し、メモリモジュール106は、主データ記憶装置を提供する。メモリモジュール106は、制御／メモリモジュール通信インターフェイス105を通して制御モジュール104からメモリモジュール106に対して発せられたコマンドを受信し、処理し、実行するようにされている。

20

#### 【0019】

モジュール104、106はそれぞれいくつかの形態を取り得る。ソリッドステートドライブ(S SSD)に適用された場合、制御モジュール104およびメモリモジュール106双方を、一体化されたスタンドアローンアセンブリに組込んでもよい。ハイブリッドディスクドライブに適用された場合、メモリモジュール106はフラッシュおよびディスク双方に基づくメモリを含むものであってもよい。メモリカードに適用された場合、制御モジュール機能の一部またはすべてをホスト装置102(図1)に組込んでもよい。

30

#### 【0020】

図2に示される代表的な制御モジュール104は、コントローラ108と、インターフェイス(I/F)回路110と、メモリバッファ112とを含む。コントローラ108は、ホスト102とメモリモジュール106との間でのデータ転送を指示することを含めて、装置100に対する全体的な制御機能を提供する。I/F回路108は、ホストとの、およびメモリモジュール106との、インターフェイス通信を提供する。バッファ112は、コントローラ108が使用するプログラミングおよび制御データの記憶場所を提供することができ、かつ、データアクセス動作中のデータの一時記憶領域を提供することができる。図2には具体的に示されていないが、制御モジュール104は、暗号化、エラー検出および訂正、ならびにその他の信号処理機能を含むさらに他の機能を含み得る。

40

#### 【0021】

示されているメモリモジュール106は、読み出し／書き込み／消去(R/W/E)回路114と、1つ以上のフラッシュメモリアレイ116とを含む。R/W/E回路114は、制御モジュール104からの制御入力に応答してフラッシュメモリアレイ116に対して読み出し、書き込み、および消去機能を果たすように動作する。このメモリはフラッシュメモリを利用しているが、これは例示にすぎず限定ではない。なぜなら、複数種類のメモリ(たとえばフラッシュ、RRAM、STRAM、PCRAM等)を備えたハイブリッドシステムを含めて、任意の数の異種のソリッドステート不揮発性メモリを使用できるからである。

50

## 【0022】

フラッシュメモリアレイ 116 は、図 3 に概要が示されている個々のフラッシュメモリセル 118 からなるものであってもよい。フラッシュメモリセル 118 は、間隔をおいて設けられた  $n +$  ドープ領域 122 を有する半導体基板 120 上に形成される。ゲート構造 124 は、このフラッシュセルが一般的な nMOS トランジスタ構成となるように、一対の隣合うドープ領域にまたがっている。隣接するドープ領域 122 の対各々に、関連するゲート構造 124 が設けられるように、追加のフラッシュセルを基板上に形成することができる。

## 【0023】

ゲート構造 124 は、導電性ゲート 126、128 と絶縁性領域 130、132 を交互に積層したものを提供する。データは、各セル 118 に、フローティングゲート (FG) として特徴付けられている下部ゲート 126 上に蓄積された電荷の相対的な量との関連で格納される。

## 【0024】

フローティングゲートは、プログラミング動作中、隣接するドープ（ドレインおよびソース）領域 122 と制御ゲート (CG) として特徴付けられている上部ゲート 128 に対する適切な電圧の選択的な印加により、電荷を蓄積する。印加されたこれらの電圧により、半導体基板 120 のチャネル (CH) 部分から絶縁領域 130 を通してフローティングゲート 126 に、電荷の制御された移動が生じる。

## 【0025】

初期消去状態では、通常、電荷はフローティングゲート上に実質的に蓄積されていないであろう。この状態において、セルは一般的に、制御ゲートに電圧を印加しなくても、チャネルを通したドレイン - ソース間の導通を示す傾向がある。一旦フローティングゲート上に電荷が蓄積すると、十分に高いゲート制御電圧を制御ゲートに印加してその時点でセルが導通しない限り、ドレイン - ソース間の経路は非導通状態であろう。セルのプログラム状態は、一般的にフローティングゲート上に蓄積された電荷の量に対応する、ドレイン - ソース電流がセルを流れるのに必要な制御ゲート電圧のレベルを観察することにより、判別することができる。

## 【0026】

セル 118 は、シングルレベルセル (SLC) として構成してもマルチレベルセル (MLC) として構成してもよい。SLC は 1 ビットを格納し、通常は論理ビット値 1 を消去されたセルに割当て（実質的に蓄積電荷はない）論理ビット値 0 をプログラムされたセルに割当てる（蓄積電荷の選択されたしきい値が存在）。MLC は 2 ビット等のマルチビットを格納する。一般的に  $2^n$  の格納状態を用いて n ビットを格納することができる。通常は、マルチビット論理値 11 を電荷 C0（実質的に蓄積電荷はない）の消去されたセルに割当て、次に残りのマルチビット論理値 01、00 および 10 を、より高くなる電荷レベル C1、C2 および C3 に順次割当てる。

## 【0027】

蓄積電荷をフローティングゲート 126 から抜くためには、一般的に特別な消去動作が必要である。消去は、相対的に高い電圧を制御ゲートに印加して電荷をフローティングゲートからチャネルに戻るように移動させることによって、行なうことができる。その後データ書き動作中に異なる一組の電圧をセルに印加することによってフローティングゲートに電荷を加えてよい。

## 【0028】

図 3 の 118 のようなメモリセルを、メモリモジュール 106 において、概ね図 4 に示されるようにメモリセルの行と列からなるアレイとして配置することができる。隣接するセルの各列は、1 本以上のビット線 (BL) 134 を介して結合することができる。各行に沿うセル 118 の制御ゲート 128 は、個々のワード線 (WL) 136 を介して相互に接続することができる。

## 【0029】

10

20

30

40

50

図4に示されるメモリセルのアレイを、図5および図6に示されるように消去ブロック140にグループ分けしてもよい。各消去ブロック140は、メモリの個別にアドレス可能なブロックであってもよく、一回で同時に消去できるメモリの最小単位を表わしている。各消去ブロック140は、メモリセルの複数の行142として配置してもよく、各行は、共通のワード線(図4)を共有し、選択された量のユーザデータの記憶場所を提供する。希望に応じてその他の内部配列および相互接続を利用することができる。

#### 【0030】

ブロックレベルのウェアレベリング(wear leveling)を採用することにより、さまざまなブロック140の消去および書き込み状態を追跡してもよい。新たに受信したデータを収容するために、必要に応じて新たなブロック割当てを使用する。いくつかの実施の形態では、ブロック140のグループを集めて、一単位として割当てられ、使用され、消去されるより大きなガーベジコレクション単位(GCU)144にしてもよい。GCU144は任意の適切な大きさにすればよい。

10

#### 【0031】

少なくともいくつかの実施の形態では、ページと呼ばれることがある固定サイズのデータセットを、一回で各行142に書き込む。ページサイズは論理セクタに対応していてもよく、または、複数のユーザセクタを各ページ分のデータに組込んでもよい。セクタは各々、論理ブロックアドレス(LBA)等の、関連する論理アドレスを有してもよい。パリティビットまたはリードソロモン符号等のエラー訂正符号をページレベルで組込むことによって、1ページ分のデータを取出したときにエラーを訂正してもよい。メタデータおよびその他の制御情報は、各消去ブロック140に格納してもよく、または、この目的専用の特定のブロック等の他の場所に格納してもよい。

20

#### 【0032】

図7は、図6のアレイのさまざまなフラッシュメモリセル118上に蓄積される電荷のレベルの違いについて、代表的な正規化電荷分布150、152、154および156を示す。

#### 【0033】

これらの分布は、電圧の大きさを示す共通のx軸158およびセル分布総数を示す共通のy軸159に対してグラフ化されている。

30

#### 【0034】

分布150、152、154および156は、名目上の蓄積電荷状態C0 < C1 < C2 < C3の相違を表わしており、MLCのプログラム状態11、01、00および10に対応する。その他の符号化方式を用いてもよい。分布150は状態11にプログラムされたアレイのメモリセル上の電荷量の一例を表わし、分布152は状態01に対応し、分布154は状態00に対応し、分布156は状態10に対応する。分布156におけるセルの蓄積電荷が最も多く、分布150におけるセルの蓄積電荷が最も少ない。

#### 【0035】

プログラム状態11、01、00および10は、各セルにおけるデータの、異なる2つのページ(ブロック)のデータを表わすものであってもよい。この場合、プログラム状態の最下位ビット(LSB)は第1ページのビット値を与えてもよく、プログラム状態の最上位ビット(MSB)は第2ページのビット値を与えてもよい。

40

#### 【0036】

理想的なのは、電荷分布150～156が重なり合っていないことによって、適切な読み出しきい値電圧T1、T2、T3およびT4を印加すると、異なるプログラム状態が区別されることである。しきい値T1は名目上、分布150のメモリセルすべてをソース・ドレイン導通状態にするのに十分であるが分布152、154および156のセルを導通状態にするには不十分な電圧レベルを与える。しきい値T4は概ね、プログラム状態に関係なくすべてのセルを導通状態にするのに十分大きい。

#### 【0037】

選択されたフラッシュメモリセルのプログラム状態は、この選択セルのためのビット線

50

134(図4)を適切な順方向電圧(たとえば+3V等)にし、残りの非選択ビット線をそれ以外のより低い何らかの基準電圧(たとえば0V)にすることによって、読出しができる。上記選択セルを含まない行のための非選択ワード線136を最大のしきい値T4にすることによって、選択セル以外の、選択列のセルすべてを、ソース-ドレイン導通状態にすることができる。

#### 【0038】

その後、選択セルに関連するWL136に1つ以上の読出しきい値電圧を印加してもよく、選択セルのプログラム状態を、ビット線134および選択列のその他のセルに電流が流れかかる否かに基づいて、判別してもよい。読出動作はこのようにして、所与の読出しきい値電圧が選択されたセルを導通状態にするのに十分であるか否かを評価し、列に電流を流すのに必要な印加電圧が高いほど、フローティングゲート上の蓄積電荷量が多い。10

#### 【0039】

いくつかの実施の形態では、第1ページのデータを、SLCモードのセルの選択行に沿ってセルに書込む。第1ページのデータは、何らかの順序の論理0と1のビットシーケンスを構成するであろう(たとえば00101111010000100...)。各セルには1ビットが格納されるであろう。論理1を格納すべきセルは、プログラミング力を受けない(または最小プログラミング力を受ける)ことによって、「11」分布150の範囲内の電荷レベルを有することができる。論理0を格納すべきセルは、電荷レベルを「00」分布154の範囲内に引上げるのに十分なプログラミング力を受けるであろう。

#### 【0040】

格納されたビットシーケンスをSLCから読出す場合、今度は読出しきい値電圧T2を各セルに印加すればよく、格納状態(論理1または0)は、この読出しきい値電圧を印加した結果セルが導通状態になったか否かに基づいて判別すればよい。20

#### 【0041】

次に、第2ページのデータをSLCセルに実質的に上書きすることにより、セルをMLC形態に変換してもよい。先に述べたのと同じく、第2ページのデータは論理0と1のビットシーケンスを構成し、各セルには第2ページのデータのうちの1ビットが格納されるであろう。論理1を格納すべきセルは、それ以上プログラム力を受けないであろう。論理0を格納すべきセルは、次に高い分布に電荷レベルを増分するのに十分な追加の電荷を受けるであろう。30

#### 【0042】

論理1を「11」分布150内のプログラムされたメモリセルに書込む場合、電荷を追加することによってこのセルは「01」分布152に移行するであろう。同様に、論理1を「00」分布154内のプログラムされたメモリセルに書込む場合、電荷を追加することによってこのセルは「10」分布156に移行するであろう。いずれの場合も、プログラムされたセルのLSB(右端のビット)は第1ページのデータのビット値を示し、プログラムされたセルのMSB(左端のビット)は第2ページのデータのビット値を示す。

#### 【0043】

理想的なのは、分布150~156が十分な間隔を保っていることにより、異なるしきい値T1~T4によってセルのプログラム状態を正確に識別できることである。しかしながら、時間の経過に伴い、消耗、読出ディスターブ、書きディスターブ、温度、電荷ドリフト、製造許容差等のさまざまな影響が、図8において点線で示した分布152のシフトのように、所与の分布内のセルのドリフトを引起す可能性がある。シフトされた分布152のメモリセルのうちのいくつかは、実際のプログラム状態01ではなくプログラム状態11を格納しているものとして検出されるであろうことがわかる。電荷ドリフトの結果、総電荷蓄積量が増加または減少し、図8の分布の右方向のシフトが生じる可能性もある。40

#### 【0044】

図9は、さまざまな実施の形態に従う、メモリセル162内のプログラミングドリフトを修正するように動作可能な部分再プログラミング回路160を示す。フラッシュメモリセルの場合、プログラミングドリフトは、図8に示されるような電荷ドリフトの形態であ50

つてもよい。その他、メモリセルは、P C R A M セル、R R A M セル、S T R A M セル等の異なる形態を取ってもよく、プログラミングドリフトは、相変化ドリフト、抵抗ドリフト、減磁等の形態であってもよい。

#### 【 0 0 4 5 】

部分再プログラミング回路 1 6 0 は、再プログラミング力をメモリセル 1 6 2 に与えることにより、このセルを以前のプログラム状態に戻す。再プログラミング力は、時間、パルス幅、電荷移動量、印加電界強度等の点で、通常のプログラミング力よりも少ない。このようにして、回路 1 6 0 は、現在のプログラミング状態を「微調整」することによってプログラミング分布を引き締める。

#### 【 0 0 4 6 】

いくつかの実施の形態において、部分再プログラミング回路 1 6 0 は、コントローラ 1 0 8 もしくは読出 / 書込 / 消去 (R / W / E) 回路 1 1 4 の一部を形成するか、または、これらその他の回路とインターフェイスするスタンドアローン回路である。回路 1 6 0 は、検出または推定されたビットエラーレート (B E R) 、時間情報、温度測定値、累積書込 / 消去 (W / E) 回数等を含むいくつかの制御入力を用いることにより、再プログラミング力を与えるべきメモリセル候補を識別してもよい。ルックアップテーブル 1 6 4 は、さまざまな環境条件または状況の下で回路 1 6 0 が特定のセルを再プログラムできるようするために使用されるプロファイル情報を格納することができる。

#### 【 0 0 4 7 】

図 1 0 は、たとえば選択行に沿って 1 グループの M L C から 2 ページ ( ブロック ) のデータを読出すように動作可能な図 2 の読出 / 書込 / 消去回路 1 1 4 の読出部 1 7 0 を示す。コマンドデコーダブロック 1 7 2 は、読出コマンドを処理し、1 つ以上のデジタル読出しきい値 T を、デジタルアナログ (D A C) / ドライバ回路 1 7 4 に出力する。これに対し、D A C / ドライバ 1 7 4 は、対応するアナログゲート電圧を ( 図 9 のメモリセル 1 6 2 によって表される ) 各セルに出力する。電源電圧 V s が電源 1 7 6 によって印加される。セルの導通状態は、比較器 1 7 8 と、電源 1 8 0 からの適切な基準電圧 V r を用いることによって、検知される。検知されたデータは、出力バッファ 1 8 2 に与えられ、出力バッファは格納データを別々に格納する ( それぞれページ 1 およびページ 2 ) 。

#### 【 0 0 4 8 】

各セルの格納状態の検知には、複数のしきい値が必要であろう。電圧しきい値 T 2 を最初に印加することにより、M S B のページ 1 のデータの格納状態を検知することができる。次に、電圧しきい値 T 1 および T 3 を印加することにより、L S B のページ 2 のデータの格納状態を検知することができる。しきい値 T 2 がセルを導通状態にした場合は、次に T 1 を印加することにより、セルが分布 1 5 0 にあるのか 1 5 2 にあるのか判別すればよい。同様に、しきい値 T 2 がセルを導通状態にしなかった場合は、T 3 の印加によってセルが分布 1 5 4 にあるのか 1 5 6 にあるのか判別されるであろう。

#### 【 0 0 4 9 】

このように、格納状態 1 1 、 0 1 、 0 0 または 1 0 を容易に判別することができ、第 1 (M S B) ビットは第 1 ページにおけるビットを示し、第 2 (L S B) ビットは第 2 ページにおけるビットを示す。上記ステップを各 M L C について繰り返すことにより、第 1 および第 2 ページについて、回復されたビットシーケンスが生じるであろう。

#### 【 0 0 5 0 】

セルのプログラミングは、図 1 0 に示されるように読出 / 書込 / 消去回路 1 1 4 の書込回路部 1 9 0 によって実行することができる。チャージポンプ機構を用いることにより、離散的な量の蓄積電荷が順次選択されたセル 1 6 2 に移動し、それにより、電荷の総蓄積量が所望のプログラミング分布まで引上げられる。

#### 【 0 0 5 1 】

電圧源 1 9 2 は、プログラミング電圧を、キャパシタ 1 9 4 またはその他の電荷蓄積素子に供給する。パワー M O S F E T またはそれ以外の適切な装置の形態であってもよい、選択的に起動されたスイッチ 1 9 6 が周期的に閉じることにより、蓄積された電荷をキヤ

10

20

30

40

50

パシタ 194 から選択されたメモリセル 162 に移動させる。

#### 【0052】

図 10 の読出回路 170 を用いることにより、電荷の蓄積中に、いくつかのプログラムベリファイ (PV) 読出しきい値電圧のうちの 1 つを、セルに周期的に印加することができる。いくつかの実施の形態において、図 11 のプログラム処理は、セル 162 が特定の PV 読出しきい値に反応して導通状態になることがなくなるまで、続く。選択されたセルに対するプログラミング処理はその時点で終了する。

#### 【0053】

図 12 は、プログラムされたメモリセルの分布について、もう 1 つの分布曲線 198 を示す。一連の電圧しきい値の印加により、この分布の大きさおよび形状を判別することができる。図 12 に示されるように、低い方のベースラインしきい値  $V_a$  を、ベースラインしきい値よりもわずかに低いおよびわずかに高い（たとえば + / - 5 % 等）増分されたしきい値 ( $V_{a-}$ ,  $V_{a+}$ ) とともに印加することによって、分布曲線 198 の低い方の境界を特徴付けることができる。同様に、高い方のベースラインしきい値  $V_b$  とそれに関連する増分されたしきい値  $V_{b-}$ 、 $V_{b+}$  を印加することにより、分布曲線 198 の高い方の境界を特徴付けることができる。

#### 【0054】

図 13 は、通常プログラミングおよび部分プログラミング力の間に図 11 の書込回路 190 によって与え図 10 の読出回路 170 によって検知することができる、大きさが異なるプログラミング増分を示す。書込回路 190 によって、蓄積された電荷の相対的に大きいプログラミング増分 200 を与えることにより、メモリセルを初期状態にプログラムしてもよく、次に、書込回路 190 によって、蓄積された電荷の相対的に小さい再プログラミング増分 202 を与えることにより、このセルを初期プログラム状態に戻してもよい。

#### 【0055】

たとえば、再び図 7 を参照して、初期プログラム状態 11 の消去されたメモリセルは、蓄積電荷の総量を、電圧  $V_2$  より設定されたしきい値と電圧  $V_3$  によって設定されたしきい値の間のレベルになるまで増加させるための、5 または 6 (5 ~ 6) 個の増分 200 を与えることによって、00 状態にプログラムしてもよい。

#### 【0056】

その後、メモリセルのフローティングゲートから電荷が漏れて電荷の総量がしきい値  $V_2$  の方向にドリフトすると、蓄積電荷の相対的に小さい部分プログラミング増分 202 を 1 つ以上与えることによって、メモリセルを以前のプログラム状態（たとえば蓄積電荷の総量が名目上以前と同一）に戻すことができる。

#### 【0057】

この部分プログラミングシーケンスは図 14 に示されている。セルの最初の分布を、分布曲線 204 によって示される特定の状態にプログラムする。時間の経過に伴い、セルのうちの少なくともいくつかが電荷を失い、曲線 206 で示されるドリフトされた分布になる。

#### 【0058】

部分プログラミングの増分 202 を与えると、曲線 208 で示されるように分布全体が増す。増分 202 を引き継ぎ与えると、最終の部分プログラミング分布（曲線 210）は、名目上元の曲線 204 と一致するであろう。

#### 【0059】

図 14 のメモリセルの部分再プログラミングによって、完全な 1 サイクルの消去およびプログラミングを回避することにより、セルの消耗を減じメモリモジュール内におけるデータのコピーの総数を減じることができる。

#### 【0060】

図 15 は、さまざまな実施の形態に従い実行されるステップを説明する部分再プログラミングルーチン 220 のフローチャートである。説明のために、ルーチン 220 を、図 2 ~ 図 6 に示されるフラッシュメモリアレイとの関連で述べる。これは例示であって限定で

10

20

30

40

50

はない。

#### 【0061】

ステップ222で、メモリセルを選択状態にプログラムする。これは、希望に応じて、プログラム状態が1ページのデータに対応するかまたは複数ページのデータに対応する、SLC状態またはMLC状態であってもよい。プログラム状態は、図7の分布曲線で表される状態から選択された1つの状態（たとえば11、01、00または10）であってもよい。

#### 【0062】

選択されたある時間間隔の後、ステップ224で、このセルを部分再プログラミングの候補であると識別する。これはさまざまなやり方で実行できる。メモリセルの保持時間で、このセルが過度の劣化なしでプログラム状態を維持し得る経過時間として計算することができる。セルがそのプログラム状態を維持した実際の時間が計算された保持時間に等しくなるかそれ以上になった場合、このセルを部分再プログラミングの候補としてマークしてもよい。

10

#### 【0063】

その代わりに、セルに対して読み出動作を行なってもよく、このセルを含むメモリのブロックのビットエラーレート（BER）が予め定められたしきい値を超える場合がある。その他の実施の形態では、このブロックの書き込み／消去回数が、このセルを評価する必要があることを示す特定のしきい値に達する場合がある。さらに他の実施の形態では、セルおよび／または隣接するセルに対して、読み出ディスクアーブデータの可能性を示すのに十分多い回数の読み出動作が行なわれる。その他任意の適切な要因、パラメータ、測定値、またはそれ以外の徵候を用いて、スケジュールに基づく全セルの周期的な再プログラミングを含む、部分再プログラミングの候補として、セルを識別することができる。

20

#### 【0064】

次にステップ226で、選択されたメモリセルに対して電圧しきい値テストを実行する。これは、図12に示されるような1つ以上の電圧しきい値を印加してセルのプログラム状態を確認することを含み得る。

#### 【0065】

セルが十分なプログラミング劣化を示している場合、このルーチンは判定ステップ228からステップ230に進み電荷の1つ以上の増分をこのセルに与える。これは、図11の回路190を用いて図13の小さい増分202を与え、続いてステップ232に示されるように図12の回路180によって適切な読み出／プログラムベリファイ電圧しきい値を与えることを含み得る。このプロセスは、判定ステップ234で示されるように、セルが適切なレベルに回復するまで続行される。その後、ステップ236で、このセルは再プログラミされたものとしてマークされる。これは、上記メモリセルの関連メタデータにおける記録を含み得るものであり、セルがいつ再プログラミされたかを示すための日付／タイムスタンプを含んでもよい。その後ルーチンはステップ238で終了する。

30

#### 【0066】

本明細書で先に述べた部分再プログラミングを適用することによって、データの再書き込みおよび消去の発生頻度の低下が可能であることがわかる。それでもなお必要に応じてガベジコレクション動作を行なうことはできるが、所与のGCU内のデータは、データリフレッシュが必要な状態ではなく（すなわち十分に古いためにプログラミングドリフトが生じた）、概ね古い（すなわち修正の範囲を超えて）という前提がある。

40

#### 【0067】

必ずしもプログラムセルの最初の一組のすべてのセルを再プログラムする訳ではない。むしろ、ビットエラーを示しているセルを評価およびプログラミングの対象とすればよく、残りのセルはそのままにしておけばよい。同様に、プログラミングドリフトが生じる可能性がより高いプログラミング状態のセル（たとえば「10」にプログラミされたセル等）を部分的に再プログラムしてもよく、残りのセルはそのままにしておけばよい。その他の場合は、一行のメモリセルのうちのすべてのセルをプログラミングドリフトについて評

50

価し最悪 X パーセント (たとえば最悪 20 % 等) を部分的に再プログラミし残りのセルはそのままにしておく。

## 【 0068 】

フラッシュメモリセルに関連して本明細書に開示されているさまざまな実施の形態では、ドリフトメカニズムとして電荷レベルの低下を検討してきたが、状況によっては過剰な読み出の場合のように電荷の増加が発生することが考えられる。追加量の電荷をゲートに加えるのではなく、プログラミング電圧の他の組を与えて電荷のごく一部をフローティングゲートから抜くように、書き回路を構成することが可能である。同様に、その他の種類のメモリセルに対しては双方向プログラミング調整を適用することもできる。

## 【 0069 】

さまざまな実施の形態の構造および機能の詳細と併せて、本開示のさまざまな実施の形態の数多くの特徴および利点について上記説明の中で述べてきたが、この詳細な説明は例示にすぎず、以下の請求項を表現する用語の広い一般的な意味によって示される全範囲の本開示の原理の中で、詳細事項、特に構成要素の構造および配置を変更してもよいことが理解されるはずである。

10

【 図 1 】

FIG. 1

【 図 2 】

FIG. 2

【 図 3 】

FIG. 3

【 図 4 】

FIG. 4

【図5】

FIG. 5

【図7】

FIG. 7

【図8】

FIG. 8

【図6】

FIG. 6

【図9】

FIG. 9

【図10】

FIG. 10

【図11】

FIG. 11

【図12】

FIG. 12

【図13】

FIG. 13

【図14】

FIG. 14

【図15】

FIG. 15

---

フロントページの続き

(72)発明者 アントワーヌ・クエール

アメリカ合衆国、55124 ミネソタ州、アップル・バレー、ドウェラーズ・ウェイ、1557

8

(72)発明者 バルン・ボッティ

アメリカ合衆国、55379 ミネソタ州、シャコピー、ゴーマン・ストリート、560、アパー

トメント・312

(72)発明者 ロドニー・バージル・ボウマン

アメリカ合衆国、55431 ミネソタ州、ブルーミントン、シェファード・ヒルズ・ドライブ、

3325

審査官 後藤 彰

(56)参考文献 特開2008-181628(JP,A)

特開2010-039983(JP,A)

特開2009-151919(JP,A)

特開2007-058966(JP,A)

(58)調査した分野(Int.Cl., DB名)

G11C 16/02

G11C 16/04