(19) 日本国特許庁(JP)

## (12) 公開特許公報(A)

(11) 特許出願公開番号

特開2008-192938

(P2008-192938A)

(43) 公開日 平成20年8月21日(2008.8.21)

| (51) Int.Cl.               | F 1  |      | テーマコード (参考) |

|----------------------------|------|------|-------------|

| <b>H05K 1/09</b> (2006.01) | H05K | 1/09 | C 4 E 3 5 1 |

| <b>H05K 1/11</b> (2006.01) | H05K | 1/11 | H 5 E 3 1 7 |

| <b>H05K 3/38</b> (2006.01) | H05K | 3/38 | B 5 E 3 4 3 |

| <b>H05K 3/00</b> (2006.01) | H05K | 3/00 | N           |

審査請求 未請求 請求項の数 35 O L (全 26 頁)

|           |                            |          |                                                  |

|-----------|----------------------------|----------|--------------------------------------------------|

| (21) 出願番号 | 特願2007-27413 (P2007-27413) | (71) 出願人 | 000006633<br>京セラ株式会社<br>京都府京都市伏見区竹田鳥羽殿町 6 番地     |

| (22) 出願日  | 平成19年2月6日 (2007.2.6)       | (74) 代理人 | 100117167<br>弁理士 塩谷 隆嗣                           |

|           |                            | (72) 発明者 | 湯川 英敏<br>滋賀県野洲市市三宅 656 番地 京セラ S<br>LCテクノロジー株式会社内 |

|           |                            | (72) 発明者 | 山中 公博<br>滋賀県野洲市市三宅 656 番地 京セラ S<br>LCテクノロジー株式会社内 |

|           |                            | (72) 発明者 | 塙田 裕<br>滋賀県野洲市市三宅 656 番地 京セラ S<br>LCテクノロジー株式会社内  |

最終頁に続く

(54) 【発明の名称】配線基板、実装構造体および配線基板の製造方法

## (57) 【要約】

【課題】配線基板において、下地層とこの層に接する導体との間にクラックが発生することを抑制する。

【解決手段】本発明は、貫通孔 51A, 61A を有する絶縁層 51, 61 と、絶縁層 51, 61 に積層され、かつ少なくとも一部が貫通孔 51A, 61A を介して露出する導体層 50, 60 と、導体層 50, 60 に接続され、かつ貫通孔 51A, 61A の内面 51Aa, 61Aa を覆う下地層 52, 62 と、下地層 52, 62 を覆うように、少なくとも一部が貫通孔 51A, 61A に形成されたビア導体 53, 63 と、を備えた配線基板に関する。導体層 50, 60 と下地層 52, 62との間には、導体層 50, 60 の金属材料と下地層 52, 62 の金属材料との金属結晶が形成されている。

【選択図】図4

**【特許請求の範囲】****【請求項 1】**

貫通孔を有する絶縁層と、

前記絶縁層に積層され、かつ少なくとも一部が前記貫通孔を介して露出する導体層と、

前記導体層に接続され、かつ前記貫通孔の内面を覆う下地層と、

前記下地層を覆うように、少なくとも一部が前記貫通孔に形成されたビア導体と、

を備えた配線基板であって、

前記導体層と前記下地層との間には、前記導体層の金属材料と前記下地層の金属材料との金属結晶が形成されていることを特徴とする、配線基板。

**【請求項 2】**

前記導体層と前記下地層との間における酸化膜の厚みは、80 nm以下である、請求項1に記載の配線基板。

**【請求項 3】**

前記導体層は、銅、銀、金、アルミニウム、ニッケル、クロムのうちの少なくとも一つの金属材料を含んでおり、

前記下地層は、銅、ニッケル、クロム、チタン、タングステンおよびモリブデンのうちの少なくとも一つの金属材料を含んでいる、請求項1に記載の配線基板。

**【請求項 4】**

前記金属結晶は、前記導体層と前記下地層との仮想界面の55%以上の領域で形成されている、請求項1に記載の配線基板。

**【請求項 5】**

前記下地層と前記ビア導体との間には、前記下地層の金属材料と前記ビア導体の金属材料との金属結晶が形成されている、請求項1に記載の配線基板。

**【請求項 6】**

前記下地層は、銅、ニッケル、クロム、チタン、タングステンおよびモリブデンのうちの少なくとも一つの金属材料を含んでおり、

前記ビア導体は、銅、銀、金、アルミニウム、ニッケルおよびクロムのうちの少なくとも一つである、請求項5に記載の配線基板。

**【請求項 7】**

前記金属結晶は、前記下地層と前記ビア導体との仮想界面の55%以上の領域で形成されている、請求項5に記載の配線基板。

**【請求項 8】**

前記貫通孔の内面は、十点平均粗さRzが1 μm以下である、請求項1に記載の配線基板。

**【請求項 9】**

前記貫通孔の内面の十点平均粗さRzは、30 nm以上300 nm以下である、請求項8に記載の配線基板。

**【請求項 10】**

前記絶縁層は、ポリイミド樹脂、アクリル樹脂、エポキシ樹脂、シアネート樹脂、ウレタン樹脂、テフロン(登録商標)樹脂、シリコン樹脂、ポリフェニレンエーテル樹脂、ビスマレイミドトリアジン樹脂、およびポリパラフェニレンベンズオキサゾールのうち少なくとも一つの絶縁材料を含んでおり、

前記下地層は、銅、ニッケル、クロム、チタン、タングステンおよびモリブデンのうちの少なくとも1つの金属材料を含んでいる、請求項9に記載の配線基板。

**【請求項 11】**

前記請求項1ないし10のいずれかに記載の配線基板と、

前記配線基板に実装された半導体素子と、

を備えていることを特徴とする、実装構造体。

**【請求項 12】**

導体層が形成された絶縁層に対して、前記導体層の一部が露出するようにして貫通孔を

10

20

30

40

50

形成する第1工程と、

前記導体層における前記貫通孔から露出する露出面および前記貫通孔の内面を覆うように下地層を形成する第2工程と、

前記下地層を覆うようにピア導体を形成する第3工程と、

を含む配線基板の製造方法であって、

前記第2工程は、前記露出面における十点平均粗さRzを1μm以下に維持した状態で行なわれることを特徴とする、配線基板の製造方法。

【請求項13】

前記第2工程は、前記露出面における十点平均粗さRzを30nm以上300nm以下に維持した状態で行なわれる、請求項12に記載の配線基板の製造方法。 10

【請求項14】

前記第2工程は、前記貫通孔の内面の十点平均粗さRzを1μm以下に維持した状態で行なわれる、請求項12に記載の配線基板の製造方法。

【請求項15】

前記第2工程は、前記貫通孔の内面の十点平均粗さRzを30nm以上300nm以下に維持した状態で行なわれる、請求項14に記載の配線基板の製造方法。

【請求項16】

前記第2工程は、前記露出面における酸化膜の厚みが80nm以下に維持された状態で行なわれる、請求項12に記載の配線基板の製造方法。

【請求項17】

前記第1工程と前記第2工程との間において行われ、かつ前記導体層における露出面を粗面化する粗面化処理工程をさらに含んでいる、請求項12に記載の配線基板の製造方法。 20

【請求項18】

前記第1工程においては、前記貫通孔はレーザ加工により形成される、請求項12に記載の配線基板の製造方法。

【請求項19】

前記第2工程においては、前記下地層は、無電解めっき、スパッタリング、または蒸着により形成される、請求項12に記載の配線基板の製造方法。 30

【請求項20】

前記第3工程においては、前記ピア導体は、電解めっきにより形成される、請求項12に記載の配線基板の製造方法。

【請求項21】

前記第1ないし第3工程は、真空条件下あるいは不活性ガス雰囲気下において行なわれる、請求項12に記載の配線基板の製造方法。

【請求項22】

前記第2工程を行う前にあいて、前記導体層における前記貫通孔から露出した部分および前記貫通孔の内面を洗浄する洗浄工程をさらに含んでいる、請求項12に記載の配線基板の製造方法。 40

【請求項23】

前記洗浄工程は、洗浄液を用いたウェット洗浄であり、かつ20以上40以下の温風を吹きつけて前記洗浄液を乾燥させる処理を含んでいる、請求項22に記載の配線基板の製造方法。

【請求項24】

前記洗浄工程は、洗浄液を用いたウェット洗浄であり、かつ1.5気圧以上2.5気圧以下の高圧室温空気を吹き付けて前記洗浄液を乾燥させる処理を含んでいる、請求項22に記載の配線基板の製造方法。

【請求項25】

前記第3工程を行う前にあいて、前記下地層の表面を洗浄する洗浄工程をさらに含んでいる、請求項12に記載の配線基板の製造方法。 50

**【請求項 2 6】**

前記洗浄工程は、洗浄液を用いたウェット洗浄であり、かつ20以上40以下の温風を3秒以上10秒以下吹きつけて前記洗浄液を乾燥させる処理を含んでいる、請求項25に記載の配線基板の製造方法。

**【請求項 2 7】**

前記洗浄工程は、洗浄液を用いたウェット洗浄であり、かつ1.5気圧以上2.5気圧以下の高圧室温空気を吹き付けて前記洗浄液を乾燥させる処理を含んでいる、請求項25に記載の配線基板の製造方法。

**【請求項 2 8】**

導体層が形成された絶縁層に対して、前記導体層の一部が露出するようにして貫通孔を形成する第1工程と、

前記導体層における前記貫通孔から露出する露出面および前記貫通孔の内面を覆うように下地層を形成する第2工程と、

前記下地層を覆うようにピア導体を形成する第3工程と、

を含む配線基板の製造方法であって、

前記第2工程は、前記露出面における酸化膜の厚みが80nm以下に維持された状態で行なわれることを特徴とする、配線基板の製造方法。

**【請求項 2 9】**

前記第1ないし第3工程は、真空条件下あるいは不活性ガス雰囲気下において行なわれる、請求項28に記載の配線基板の製造方法。

**【請求項 3 0】**

前記第2工程を行う前において、前記導体層における前記貫通孔から露出した部分および前記貫通孔の内面を洗浄する洗浄工程をさらに含んでいる、請求項28に記載の配線基板の製造方法。

**【請求項 3 1】**

前記洗浄工程は、洗浄液を用いたウェット洗浄であり、かつ20以上40以下の温風を吹きつけて前記洗浄液を乾燥させる処理を含んでいる、請求項30に記載の配線基板の製造方法。

**【請求項 3 2】**

前記洗浄工程は、洗浄液を用いたウェット洗浄であり、かつ1.5気圧以上2.5気圧以下の高圧室温空気を吹き付けて前記洗浄液を乾燥させる処理を含んでいる、請求項30に記載の配線基板の製造方法。

**【請求項 3 3】**

前記第3工程を行う前において、前記下地層の表面を洗浄する洗浄工程をさらに含んでいる、請求項28に記載の配線基板の製造方法。

**【請求項 3 4】**

前記洗浄工程は、洗浄液を用いたウェット洗浄であり、かつ20以上40以下の温風を3秒以上10秒以下吹きつけて前記洗浄液を乾燥させる処理を含んでいる、請求項33に記載の配線基板の製造方法。

**【請求項 3 5】**

前記洗浄工程は、洗浄液を用いたウェット洗浄であり、かつ1.5気圧以上2.5気圧以下の高圧室温空気を吹き付けて前記洗浄液を乾燥させる処理を含んでいる、請求項33に記載の配線基板の製造方法。

**【発明の詳細な説明】****【技術分野】****【0 0 0 1】**

本発明は、各種オーディオビジュアル機器や家電機器、通信機器、コンピュータ装置およびその周辺機器などの電子機器に使用される配線基板およびその製造方法に関するものである。本発明はさらに、配線基板に半導体素子を実装した実装構造体、配線基板の製造

10

20

30

40

50

方法に関するものである。

【背景技術】

【0002】

従来より、I C (Integrated Circuit) や L S I (Large Scale Integration) といった半導体素子などを上面に搭載する配線基板として、樹脂製の配線基板が用いられている。配線基板としては、高密度化に有利なビルドアップ方式の配線基板が実用化されている(たとえば特許文献1参照)。

【0003】

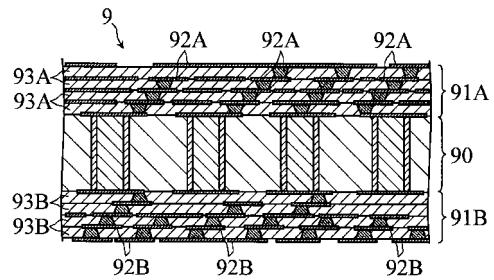

図13に示したように、ビルドアップ方式の配線基板9としては、平板状に形成されたコア基板90の両面に、ビルドアップ配線層91A, 91Bを積層形成したものがある。

10

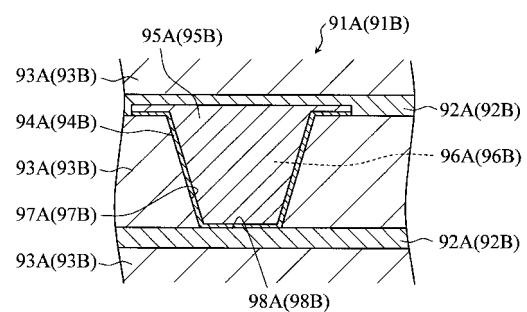

【0004】

ビルドアップ配線層91A, 91Bは、複数の導体層92A, 92Bおよび絶縁層93A, 93Bが交互に積層されたものである。図14に示したように、絶縁層93A, 93Bには下地層94A, 94Bおよびビア導体95A, 95Bが形成されている。

【0005】

下地層94A, 94Bは、導体層92A, 92Bとビア導体95A, 95Bとの間の密着性を高めるためのものであり、絶縁層93A, 93Bの貫通孔96A, 96Bの内面97A, 97Bおよび導体層92A, 92Bにおける貫通孔96A, 96Bから露出する部分98A, 98Bを覆うように形成されている。このような下地層94A, 94Bは、たとえばスパッタリングや無電解めっきにより銅を被着させることにより形成されている。

20

【0006】

ビア導体95A, 95Bは、上下の導体層92A, 92B同士を電気的に接続するためのものである。このビア導体95A, 95Bは、絶縁層93A, 93Bを厚み方向に貫通しているとともに、絶縁層93A, 93Bの上下に位置する導体層92A, 92Bの間に形成されている。このようなビア導体95A, 95Bは、たとえば電解めっきにより銅を被着させることにより形成されている。

【0007】

【特許文献1】特開平11-261228号公報

【発明の開示】

【発明が解決しようとする課題】

30

【0008】

しかしながら、導体層92A, 92B、下地層94A, 94Bおよびビア導体95A, 95Bが銅などの金属により形成されている一方で、絶縁層93A, 93Bはエポキシ樹脂などの熱硬化性樹脂により形成されており、絶縁層93A, 93Bと金属部分とでは熱膨張率が異なったものとなっている。そのため、配線基板9の絶縁層93A, 93Bや金属部分が、製造時や使用時に加熱された場合には、それらの熱膨張率の差に起因して、下地層94A, 94Bと導体層92A, 92Bとの間、あるいは下地層94A, 94Bとビア導体95A, 95Bとの間に応力が作用する。このような応力が作用した場合には、下地層94A, 94Bとこの層94A, 94Bに接する導体92A, 92B, 95A, 95Bとの間にクラックが発生することがある。

40

【0009】

このようなクラックの発生は、下地層94A, 94Bとこの層94A, 94Bに接する導体92A, 92B, 95A, 95Bとの間の界面状態に起因するものであると考えられる。すなわち、下地層94A, 94Bを形成するに当たっては、通常、貫通孔96A, 96Bの内面97A, 97Bや導体層92A, 92Bにおける貫通孔98A, 98Bから露出する部分98A, 98Bには、粗面化処理が施される。粗面化処理は、下地層94A, 94Bの密着性を高めるための処理であり、通常は、十点平均粗さRzが2μm~3μmとなるように行なわれる。そのため、下地層94A, 94Bは、比較的に粗い表面(たとえば十点平均粗さRzが2μm~3μm)に形成されることとなり、下地層94A, 94Bの表面も比較的に粗い面となる。その結果、下地層94A, 94Bとこの層94A, 94Bとの間にクラックが発生することがある。

50

4Bに接する導体92A, 92B, 95A, 95Bとの間には、結晶が不連続な界面が生じるため、その界面においてクラックが発生しやすくなる。

#### 【0010】

また、クラックは、製造時において、導体層92A, 92Bや下地層94A, 94Bの表面に酸化膜が形成された場合にも発生し得る。すなわち、酸化膜は金属原子と酸素原子が混在した結晶構造であるが、この酸化膜の結晶構造は、金属原子のみで形成された結晶構造とは構造が大きく異なる。そのため、導体層92A, 92Bや下地層94A, 94Bの表面と酸化膜との間では原子配列が不規則に乱れ、導体層92A, 92Bや下地層94A, 94Bと酸化膜との結合が弱くなる。その結果、下地層94A, 94Bと導体層92A, 92Bとの間には、その界面においてクラックが発生しやすくなる。

10

#### 【課題を解決するための手段】

#### 【0011】

本発明は、配線基板において、下地層とこの層に接する導体との間にクラックが発生することを抑制することを課題としている。

#### 【0012】

本発明では、貫通孔を有する絶縁層と、前記絶縁層に積層され、かつ少なくとも一部が前記貫通孔を介して露出する導体層と、前記導体層に接続され、かつ前記貫通孔の内面を覆う下地層と、前記下地層を覆うように、少なくとも一部が前記貫通孔に形成されたビア導体と、を備えた配線基板であって、前記導体層と前記下地層との間には、前記導体層の金属材料と前記下地層の金属材料との金属結晶が形成されていることを特徴とする、配線基板が提供される。

20

#### 【0013】

本発明ではさらに、前記配線基板と、前記配線基板に実装された半導体素子と、を備えていることを特徴とする、実装構造体が提供される。

#### 【0014】

前記導体層における前記貫通孔を介して露出する露出面における酸化膜の厚みは、80nm以下であるのが好ましい。

#### 【0015】

前記下地層と前記ビア導体との間には、前記下地層の金属材料と前記ビア導体の金属材料との金属結晶が形成されているのが好ましい。

30

#### 【0016】

前記導体層は、たとえば銅、銀、金、アルミニウム、ニッケルおよびクロムのうちの少なくとも一つの金属材料を含んでいる。

#### 【0017】

前記下地層は、たとえば銅、ニッケル、クロム、チタン、タングステンおよびモリブデンのうちの少なくとも一つの金属材料を含んでいる。

#### 【0018】

前記ビア導体は、たとえば銅、銀、金、アルミニウム、ニッケルおよびクロムのうちの少なくとも一つの金属材料を含んでいる。

#### 【0019】

前記金属結晶は、前記導体層と前記下地層との仮想界面の55%以上の領域、あるいは前記下地層と前記ビア導体との仮想界面の55%以上の領域で形成されているのが好ましい。ここで、仮想界面とは、前記導体層と前記下地層との間に金属結晶が形成されていない場合におけるそれらの層の間の界面、あるいは前記下地層と前記ビア導体との間に金属結晶が形成されていない場合におけるそれらの層の間の界面をいう。

40

#### 【0020】

前記絶縁層における貫通孔の内面は、十点平均粗さRzが1μm以下であるのが好ましい。

#### 【0021】

前記絶縁層は、たとえばポリイミド樹脂、アクリル樹脂、エポキシ樹脂、シアネット樹

50

脂、ウレタン樹脂、テフロン（登録商標）樹脂、シリコン樹脂、ポリフェニレンエーテル樹脂、ビスマレイミドトリアジン樹脂、およびポリパラフェニレンベンズオキサゾールのうち少なくとも一つの絶縁材料を含んでいる。

#### 【0022】

本発明ではまた、導体層が形成された絶縁層に対して、前記導体層の一部が露出するようにして貫通孔を形成する第1工程と、前記導体層における前記貫通孔から露出する露出面および前記貫通孔の内面を覆うように下地層を形成する第2工程と、前記下地層を覆うようにピア導体を形成する第3工程と、を含む配線基板の製造方法であって、前記第2工程は、前記露出面における十点平均粗さRzを1μm以下に維持した状態で行なわれることを特徴とする、配線基板の製造方法が提供される。

10

#### 【0023】

前記第2工程は、前記露出面における十点平均粗さRzを30nm以上300nm以下に維持した状態で行なうのが好ましい。

#### 【0024】

前記第2工程は、前記貫通孔の内面の十点平均粗さRzを1μm以下に維持した状態で行なうのが好ましく、30nm以上300nm以下に維持した状態で行なうのがさらに好ましい。

20

#### 【0025】

本発明の製造方法は、前記第1工程と前記第2工程との間において行われ、かつ前記導体層における露出面を粗面化する粗面化工程をさらに含んでいる。

#### 【0026】

前記第1工程においては、前記貫通孔は、たとえばレーザ加工により形成される。

#### 【0027】

前記第2工程においては、前記下地層は、たとえば無電解めっき、スパッタリング、または蒸着により形成される。

#### 【0028】

前記第3工程においては、前記ピア導体は、たとえば電解めっきにより形成される。

#### 【0029】

第2工程は、酸化膜の厚みを80nm以下に維持した状態で行なうのが好ましい。

#### 【0030】

本発明ではさらに、導体層が形成された絶縁層に対して、前記導体層の一部が露出するようにして貫通孔を形成する第1工程と、前記導体層における前記貫通孔から露出する露出面および前記貫通孔の内面を覆うように下地層を形成する第2工程と、前記下地層を覆うようにピア導体を形成する第3工程と、を含む配線基板の製造方法であって、前記第2工程は、前記露出面における酸化膜の厚みが80nm以下に維持された状態で行なわれることを特徴とする、配線基板の製造方法が提供される。

30

#### 【0031】

本発明の製造方法では、前記第1ないし第3工程は、真空条件下あるいは不活性ガス雰囲気下において行なってもよい。

#### 【0032】

前記第2工程を行う前、あるいは前記第3工程を行う前において、前記導体層における前記貫通孔から露出した部分および前記貫通孔の内面、あるいは下地層を洗浄する洗浄工程をさらに含んでいてもよい。

40

#### 【0033】

前記洗浄工程は、洗浄液を用いたウェット洗浄であり、かつ20以上40以下の温風を吹きつけて前記洗浄液を乾燥させる処理、あるいは1.5気圧以上2.5気圧以下の高圧室温空気を吹き付けて前記洗浄液を乾燥させる処理を含んでいるのが好ましい。

#### 【発明の効果】

#### 【0034】

本発明の配線基板によれば、下地層と導体層との間に金属結晶が形成されているため、

50

金属結晶の部分が原子配列に乱れのない連続的な結晶構造となる。そのため、配線基板の製造時や使用時において、絶縁層と熱膨張率の差に起因して、加熱により応力が作用したとしても、下地層と導体層との間に応力が集中しにくくなっている。その結果、下地層と導体層との間は剥離し難く、クラックの発生を抑制することができる。

#### 【0035】

本発明の配線基板において、導体層における露出面における酸化膜の厚みが80nm以下であれば、下地層と導体層との間の密着性を高く維持することができるため、下地層と導体層との間ににおけるクラックの発生を抑制することができる。

#### 【0036】

本発明の配線基板において、下地層とビア導体との間に金属結晶が形成されれば、金属結晶の部分が原子配列に乱れのない連続的な結晶構造となるため、絶縁層と熱膨張率の差に起因した加熱時の応力が、下地層とビア導体との間に応力が集中しにくくなる。その結果、下地層とビア導体との間は剥離し難く、クラックの発生を抑制することができる。

#### 【0037】

本発明の配線基板において、導体層と下地層との仮想界面の55%以上の領域で、あるいは下地層とビア導体との仮想界面の55%以上の領域で金属結晶を形成すれば、より適切に下地層とこれに接する導体部分との間に応力が集中することを抑制し、クラックの発生をより適切に抑制することができる。

#### 【0038】

本発明の配線基板において、絶縁層における貫通孔の内面を、十点平均粗さRzが1μm以下となるようにすれば、下地層と導体層との間、あるいはビア導体と下地層との間に、原子配列に乱れのない連続的な結晶構造の金属結晶を適切に形成するため、下地層と、これに接する導体部分との間のクラックの発生を適切に抑制することができる。

#### 【0039】

本発明の実装構造体によれば、先に説明した配線基板を備えていることから、半導体素子を駆動して配線基板が加熱されたとしても、配線基板における下地層と、これに接する導体部分との間への応力の集中ないしクラックの発生を抑制することができる。

#### 【0040】

本発明の配線基板の製造方法によれば、導体層における貫通孔から露出する部分の十点平均粗さRz( J I S B 0 6 0 1 - 1 9 9 4 )が1μm以下に形成されるため、下地層と導体層との間を、原子配列の乱れのない連続的な結晶構造(金属結晶)とすることができる。

#### 【0041】

本発明の製造方法によれば、導体層の露出面における酸化膜の厚みが80nm以下に維持された状態で下地層が形成されるため、導体層と下地層との間に酸化膜に起因した原子配列の乱れを抑制し、下地層と導体層との間の密着性を高く維持することができる。そのため、本発明の製造方法によれば、酸化膜に起因する下地層と導体層との間ににおけるクラックの発生を抑制することができる。

#### 【0042】

また、導体層における貫通孔から露出する部分および貫通孔の内面の十点平均粗さRzを1μm以下に形成すれば、下地層の表面粗さを小さくすることができるため、この下地層上にビア導体層を形成した場合には、下地層とビア導体層との間を、原子配列に乱れのない連続的な結晶構造(金属結晶)とすることができる。そのため、本発明の製造方法によれば、下地層と、これに接する導体部分との間に金属結晶を適切に形成するため、加熱によるクラックが発生しにくい配線基板を提供することができる。

#### 【0043】

本発明の製造方法において、第2工程あるいは第3工程を行う前に洗浄工程を行えば、導体層における貫通孔から露出した部分および貫通孔の内面、あるいは下地層の表面にお

10

20

30

40

50

ける油脂などの汚れを除去することができる。そのため、下地層と、これに接する導体部分との間に汚れなどの異物が存在することを抑制できるため、汚れ（異物）が存在することに起因するクラックの発生を抑制することができる。

#### 【0044】

また、洗浄工程をウェット洗浄として行なう場合に、20以上40以下の温風を3秒以上10秒以下吹きつけて洗浄液を乾燥させようすれば、酸化膜を80nm以下に抑制することができ、1.5気圧以上2.5気圧以下の高圧室温空気を吹きつけて洗浄液を乾燥させるようすれば、酸化膜を50nm以下に抑制することができる。このようにして洗浄工程を行なうことに起因する酸化膜の生成を抑制できれば、酸化膜に起因するクラックの発生を適切に抑制することができる。10

#### 【発明を実施するための最良の形態】

#### 【0045】

以下に、本発明について、図面を参照しつつ説明する。

#### 【0046】

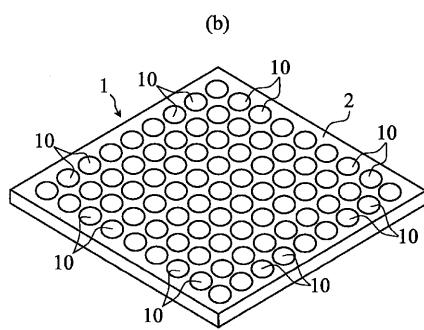

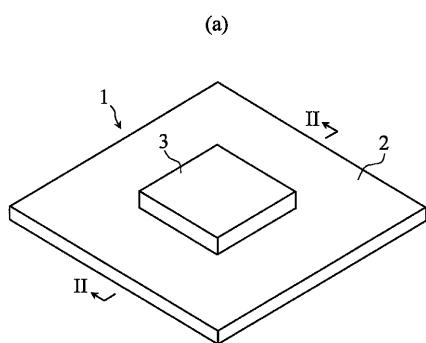

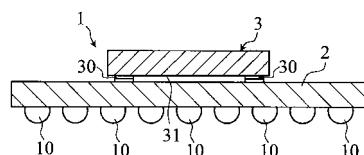

図1および図2に示した実装構造体1は、配線基板2に、半導体素子3を実装したものである。この実装構造体1は、配線基板2の裏面に複数のハンダボール10がマトリクス状に配置されたものであり、いわゆるBGA (Ball Grid Array) として構成されている。。

#### 【0047】

半導体素子3は、IC、LSI等のシリコンチップであり、複数のバンプ30を有している。複数のバンプ30は、配線基板2に導通接続されるものであり、たとえば半導体素子3の正面31における周縁部において、周縁に沿って並ぶように配置されている。各バンプ30は、たとえばハンダあるいは異方性導電接着剤により、配線基板2に導通接続されている。20

#### 【0048】

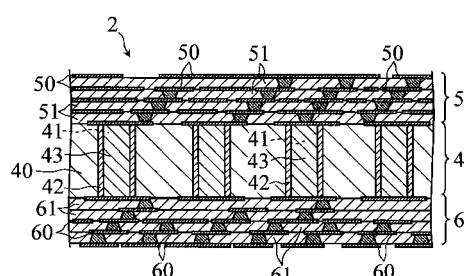

図3に示したように、配線基板2は、平板状に形成されたコア基板4と、コア基板4の上面および下面に積層されたビルドアップ配線層5, 6と、を含んでいる。

#### 【0049】

コア基板4は、絶縁体40、貫通孔41、ビア導体42および充填樹脂43を備えている。30

#### 【0050】

絶縁体40は、織布に熱硬化性樹脂を含浸させた絶縁シートを固化させたものである。好ましくは、絶縁体40は、複数の樹脂シートを積層・固化させて形成される。織布としては、たとえばポリパラフェニレンベンズビスオキサゾール樹脂などの纖維を縦横に織り込んだものを使用することができる。熱硬化性樹脂としては、エポキシ樹脂、ビスマレイミドトリアジン樹脂あるいはシアネット樹脂を使用することができる。この絶縁体40は、たとえば厚みが0.3mm以上1.5mm以下に形成されている。

#### 【0051】

貫通孔41は、ビア導体41が形成される部分であり、コア基板4の厚み方向に貫通している。貫通孔41の直径は、たとえば20μm以上100μm以下に設定されている。貫通孔41は、たとえばドリル加工やレーザ加工によって形成することができる。40

#### 【0052】

ビア導体42は、ビルドアップ配線層5とビルドアップ配線層6との間の導通を図るものである。このビア導体42は、貫通孔41の内面において、たとえば金、銀、銅、錫、ニッケルなどの金属材料により、たとえば厚みが3μm以上50μm以下に膜形成されている。

#### 【0053】

充填樹脂43は、貫通孔41の残存空間を埋めるためのものである。充填樹脂43は、たとえばポリイミド樹脂、アクリル樹脂、エポキシ樹脂、シアネット樹脂、テフロン（登録商標）樹脂、シリコン樹脂、ポリフェニレンエーテル樹脂あるいはビスマレイミドトリ

アジン樹脂により形成されている。

【0054】

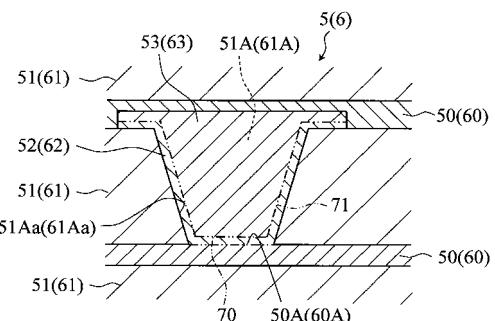

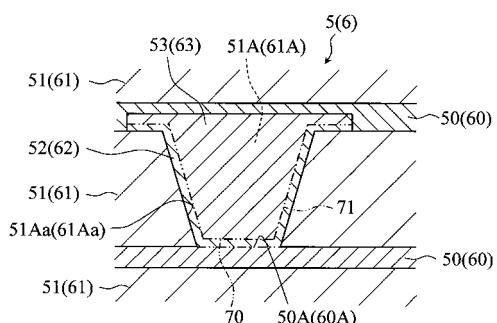

ビルドアップ配線層5，6は、複数の導体層50，60および絶縁層51，61を交互に積層したものであり、図4に示したように下地層52，62およびビア導体53，63をさらに含んでいる。

【0055】

導体層50，60は、導電性を有するものであり、電気信号を伝達するための伝達路としての機能を備えている。この導体層50，60は、たとえば銅、銀、金、アルミニウム、ニッケルあるいはクロムの金属材料により形成されている。

【0056】

絶縁層51，61は、貫通孔51A，61Aを有するものであり、たとえばポリイミド樹脂、アクリル樹脂、エポキシ樹脂、シアネット樹脂、ウレタン樹脂、シリコン樹脂あるいはビスマレイミドトリアジン樹脂などの樹脂材料により形成されている。貫通孔51A，61Aは、ビア導体53、63を形成するための部分である。この貫通孔51A，61Aの内面は、十点平均粗さRzが1μm以下とされている。

【0057】

貫通孔51A，61Aの内面51Aa，61Aaの十点平均粗さRzを1μm以下とすれば、下地層52，62と導体層50，60との間、あるいはビア導体53，63と下地層52，62との間に、連続的な結晶構造の金属結晶を適切に形成することができる。

【0058】

下地層52，62は、導体層50，60とビア導体53，63との間の密着性を高め、あるいは貫通孔51A，61Aの内面51Aa，61Aaとビア導体53，63との密着性を高めるためのものであり、銅、ニッケル、クロムあるいはチタン金属材料により形成されている。この下地層52，62は、導体層50，60との接触部分において、金属結晶を形成している。すなわち、下地層52，62と導体層50，60との間は、原子配列に乱れがなく、明確な界面が実質的に存在しないものとなっている。なお、図4においては、下地層52，62と導体層50，60との間に金属結晶が形成されなかった場合の仮想界面を二点鎖線70で示している。

【0059】

配線基板2においては、下地層52，62と導体層50，60との間に金属結晶が形成されているため、それらの層50，60(52，62)の間は、原子配列に乱れのない連続的な結晶構造となる。そのため、配線基板2の製造時において、絶縁層51，61と熱膨張率の差に起因して、製造時の加熱(たとえば半導体素子3の実装時のハンダリフロー時の加熱)により応力が作用したとしても、下地層52，62と導体層50，60との間に応力が集中しにくくなっている。その結果、下地層52，62と導体層50，60との間は剥離し難く、クラックの発生を抑制することができる。

【0060】

下地層52，62と導体層50，60との間の金属結晶は、必ずしも下地層52，62と導体層50，60との仮想界面70の全体において形成されている必要はなく、仮想界面70の55%以上の領域で形成されればよい。このような範囲に金属結晶を形成することにより、下地層52，62と導体層50，60との間に応力が集中することを充分に抑制し、クラックの発生を適切に抑制することができる。

【0061】

ビア導体53，63は、上下の導体層50，60を電気的に接続するためのものであり、絶縁層51，61を厚み方向に貫通しているとともに、絶縁層51，61の上下の導体層50，60の間に形成されている。ビア導体53，63は、たとえば銅、銀、金、アルミニウム、ニッケルあるいはクロムの金属材料により形成されている。ビア導体53，63は、下地層52，62との接触部分において、金属結晶を形成している。すなわち、ビア導体53，63と下地層52，62との間は、原子配列に乱れがなく、明確な界面が実質的に存在しないものとなっている。なお、図4においては、ビア導体53，63と下地

10

20

30

40

50

層 5 2 , 6 2 との間に金属結晶が形成されなかった場合の仮想界面を二点鎖線 7 1 で示している。

#### 【 0 0 6 2 】

配線基板 2 において、ビア導体 5 3 , 6 3 と下地層 5 2 , 6 2 との間に金属結晶が形成されていれば、ビア導体 5 3 , 6 3 と下地層 5 2 , 6 2 との間は原子配列に乱れのない連続的な結晶構造となり、絶縁層 5 1 , 6 1 と熱膨張率の差に起因した加熱時の応力が、ビア導体 5 3 , 6 3 と下地層 5 2 , 6 2 との間に応力が集中しにくくなる。その結果、ビア導体 5 3 , 6 3 と下地層 5 2 , 6 2 との間は剥離し難く、クラックの発生を抑制することができる。

#### 【 0 0 6 3 】

ビア導体 5 3 , 6 3 と下地層 5 2 , 6 2 との間の金属結晶は、必ずしもビア導体 5 3 , 6 3 と下地層 5 2 , 6 2 との仮想界面 7 1 の全体において形成されている必要はなく、仮想界面 7 1 の 5 5 % 以上の領域で形成されればよい。このような範囲に金属結晶を形成することにより、ビア導体 5 3 , 6 3 と下地層 5 2 , 6 2 との間に応力が集中することを充分に抑制し、クラックの発生を適切に抑制することができる。

#### 【 0 0 6 4 】

以上のように、実装構造体 1 は、加熱時におけるクラックの発生が抑制された配線基板 2 を備えていることから、半導体素子 3 を駆動して、配線基板 2 が加熱されたとしても、配線基板 2 における下地層 5 2 , 6 2 と、これに接する導体部分 5 0 , 6 0 ( 5 3 , 6 3 ) との間への応力が集中ないしクラックの発生を抑制することができる。

#### 【 0 0 6 5 】

本発明に係る実装構造体 1 および配線基板 2 は、上述した例には限定されず、種々に変更可能である。たとえば、配線基板 2 におけるコア基板 4 を省略し、ビルドアップ配線のみにより配線基板としてよい。

#### 【 0 0 6 6 】

次に、図 1 ないし図 4 を参照して説明した配線基板 2 の製造方法を、図 5 ないし図 8 を参照しつつ説明する。

#### 【 0 0 6 7 】

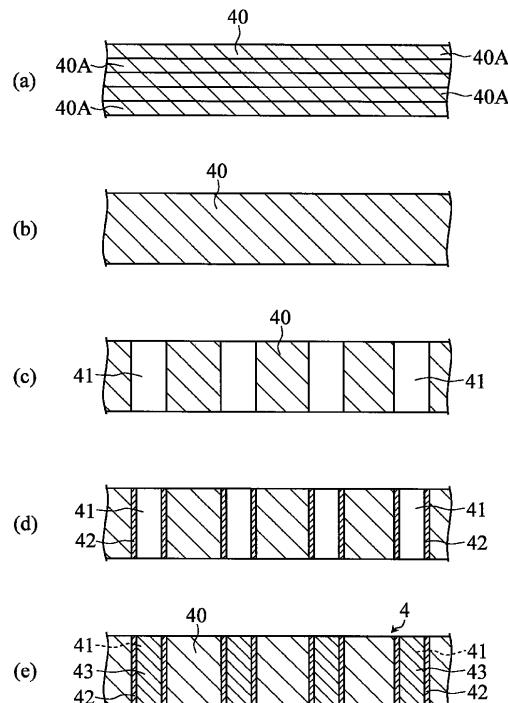

図 5 ( a ) ないし図 5 ( e ) に示したように、まず、コア基板 4 を作製する。コア基板 4 は、絶縁体 4 0 の形成工程、絶縁体 4 0 に貫通孔 4 1 を形成する工程、貫通孔 4 1 にビア導体 4 2 を形成する工程を経て作製される。

#### 【 0 0 6 8 】

図 5 ( a ) および図 5 ( b ) に示したように、絶縁体 4 0 の形成工程は、織布に熱硬化性樹脂を含浸させた樹脂シート 4 0 A を熱プレスして硬化することによって行なわれる。織布としては、たとえばポリパラフェニレンベンズオキサゾール樹脂などの繊維を縦横に織り込んだものを使用することができる。繊維としては、径が 0 . 8 mm 以上 1 . 2 mm 以下 ( 携帯電話など小型化が必要な分野では 0 . 4 mm 以上 0 . 5 mm 以下の範囲であってもよい ) の単纖維を数百本束ねたものを使用することができる。熱硬化性樹脂としては、エポキシ樹脂、ビスマレイミドトリアジン樹脂あるいはシアネート樹脂を使用することができる。

#### 【 0 0 6 9 】

絶縁体 4 0 は、1 枚の樹脂シートにより形成しても、複数枚の樹脂シートにより形成してもよく、たとえば厚みが 0 . 3 mm 以上 1 . 5 mm 以下に形成される。

#### 【 0 0 7 0 】

図 5 ( c ) に示したように、貫通孔 4 1 を形成する工程は、従来周知のドリル加工あるいはレーザ加工によって行なわれる。貫通孔 4 1 は、たとえば直径が 0 . 1 mm 以上 1 . 0 mm 以下に形成される。レーザ加工は、たとえば Y A G レーザ装置あるいは C O<sub>2</sub> レーザ装置を用いて行なうことができる。

#### 【 0 0 7 1 】

図 5 ( d ) に示したように、ビア導体 4 2 を形成する工程は、たとえば電解めっきによ

10

20

30

40

50

り貫通孔41の内面に導体層を膜形成することにより行なわれる。電解めっき液としては、たとえば金、銀、銅、錫、ニッケルなどの被着金属イオンを含むものが使用される。ビア導体42の厚みは、たとえば厚みが3μm以上50μm以下とされる。

#### 【0072】

ビア導体42の形成後においては、貫通孔41の内部に空間が存在するが、この空間は、図5(e)に示したように樹脂材料43により充填される。この場合の樹脂材料43としては、たとえばポリイミド樹脂などを用いることができる。

#### 【0073】

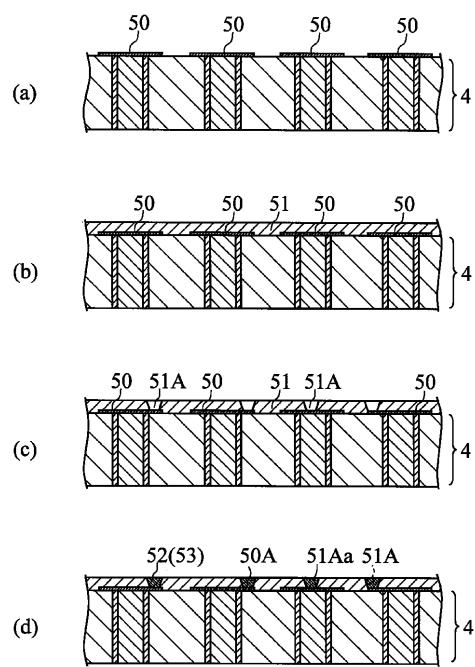

次に、コア基板4の上面及び下面に、ビルドアップ配線層5,6を形成する。

#### 【0074】

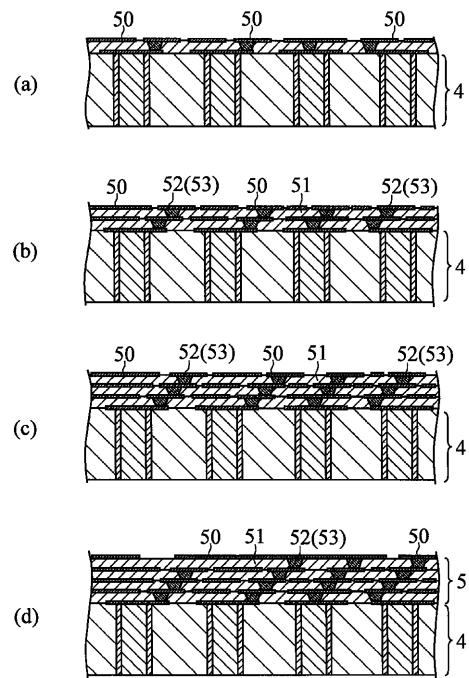

まず、図6(a)に示したように、コア基板4の上面に導体層50を形成する。この導体層50は、従来周知の蒸着法、CVD法又はスパッタリング法等によって金属材料を被着させた後、フォトリソグラフィ法によりパターン形成することにより形成される。導体層50の厚みは、たとえば3μm以上50μm以下とされる。

#### 【0075】

次いで、図6(b)に示したように、導体層50の上面に絶縁層51を形成する。絶縁層51は、従来周知のスピンドルコート法等によって、樹脂層を形成した後に、樹脂層を加熱・固化させることにより形成することができる。絶縁層51の厚みは、たとえば7μm以上50μm以下とされる。

#### 【0076】

なお、絶縁層51の形成は、真空条件下あるいは不活性ガス雰囲気下で行なうのが好ましい。このような条件下において絶縁層51を形成することにより、導体層50が絶縁層51によって覆われるまでの間に、導体層50が酸化してしまうことを抑制することができる。

#### 【0077】

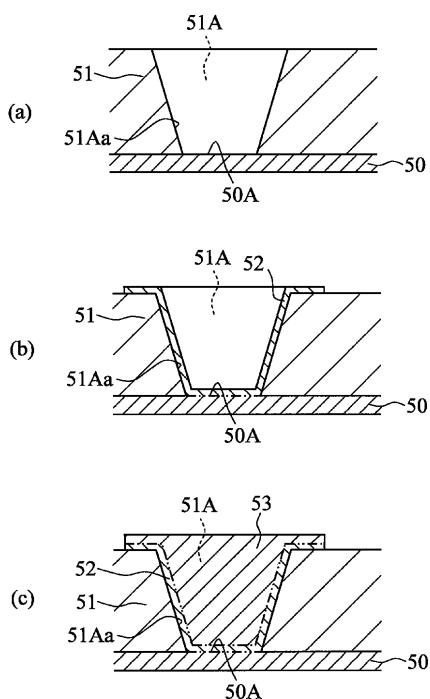

次に、図6(c)および図7(a)に示したように、絶縁層51に貫通孔51Aを形成し、導体層50の一部を露出させる。この貫通孔51Aは、内径が5μm以上60μm以下であるテーパ状に形成される。このような貫通孔51Aは、たとえばレーザ加工により形成することができる。レーザ加工としては、たとえばエキシマレーザ、YAGレーザ(5倍高調波、4倍高調波、3倍高調波)あるいは炭酸ガスレーザを採用することができる。

#### 【0078】

なお、絶縁層51に対する貫通孔51Aの形成は、真空条件下あるいは不活性ガス雰囲気下で行なうのが好ましい。このような条件下において貫通孔51Aを形成することにより、導体層50の一部が貫通孔51Aを介して露出したとしても、この露出面50Aが酸化してしまうことを抑制することができる。

#### 【0079】

次いで、貫通孔51Aの内面51Aaおよび導体層50における貫通孔51Aから露出した部分50Aに対して粗面化処理を行なう。

#### 【0080】

粗面化処理は、下地層52と導体層50との接着力を高めるため、あるいは貫通孔51Aの内面51Aaとビア導体53との接着力を高めるために行われるものである。粗面化処理を行う方法としては、たとえば放電処理、UV処理、プラズマ処理などのドライプロセスによるもの、エッチング液を用いたウェットプロセスによるものがある。

#### 【0081】

本発明における表面粗面化処理は、導体層50における露出面50Aおよび貫通孔50Aの内面50Aaの表面粗さRzが1μm以下(好ましくは30nm以上300nm以下)となるように行なわれる。このような表面粗さは、たとえば表面粗さRzを2μm以上3μm以下とするために行なう従来の粗面化処理よりも、処理時間を短くすることにより達成することができる。

10

20

30

40

50

**【 0 0 8 2 】**

ここで本発明における表面粗さは、十点平均粗さ（ $R_z$ ）であり、「JIS B 0601 - 1994」の計算方法に基づいて算出したものである。

**【 0 0 8 3 】**

本発明の技術分野、すなわち配線基板の分野において、粗面粗化処理は、生産効率の観点から、通常はエッティング液を用いたウェットプロセスにより行われる。ウェットプロセスによるエッティングは空気環境下で行うことができ、ドライプロセスによる処理に比べ、比較的短時間に大量処理できる。粗面化処理をエッティング液を用いて行うには、たとえば所定の温度に加熱した過マンガン酸水溶液に、樹脂層51が形成されたコア基板4を所定時間浸漬し、導体層50の露出面50Aおよび貫通孔51Aの内面51Aaをエッティングすることにより行なわれる。従来このような粗面化処理は、導体層50の露出面50Aおよび貫通孔51Aの内面51Aaにおける十点平均粗さ $R_z$ が2μm以上3μm以下となるように行われる。このように比較的粗い面となすことで、アンカー効果により下地層52と導体層50との接着力、あるいは貫通孔50Aの内面51Aaとビア導体53との接着力を高めることができると考えられる。10

**【 0 0 8 4 】**

一方、本発明における表面粗化処理は、アンカー効果とは別の観点から接着力を高めることを目的とするものであり、導体層50の露出面50Aおよび貫通孔51Aにおける内面51Aaの十点平均粗さ $R_z$ が1μm以下、より好ましくは30nm以上300nm以下とされている。このように導体層50の露出面50Aおよび貫通孔51Aの内面51Aaの十点平均粗さ $R_z$ を1μm以下とするには、通常よりも浸漬時間が短く設定され、あるいは過マンガン酸水溶液の温度が低めに設定される。20

**【 0 0 8 5 】**

また本発明における粗面化処理は、ウェットプロセスによる処理よりもドライプロセスによる処理で行なうことが好ましく、なかでもプラズマ処理により行なうことが好ましい。ドライプロセスはアルゴンガスなど所定の雰囲気化で行われるため、大気雰囲気で行われるウェットプロセスによる処理に比べ、導体層50の露出面50Aが酸化される量を少なくすることができる。また、プラズマ処理により粗面化すれば、貫通孔51Aの内面51Aaが粗面化されると同時に、導体層50の露出面50Aに堆積した樹脂残渣を取り除くことができる。そのため、樹脂残渣に起因するビアの接続不良の発生を抑制し、接続信頼性が高めることができる。ただし、プラズマ処理の時間が長くなると粗面化の程度が大きくなるため、プラズマ処理は出力500Wで、30秒以上120秒以下の範囲とするのが好ましい。30

**【 0 0 8 6 】**

次に、図6(d)、図7(b)および図7(c)に示したように、導体層50における露出面および貫通孔51Aの内面を覆うように下地層52を形成するとともに、下地層52を覆うようにビア導体53を形成する。

**【 0 0 8 7 】**

図7(b)に示したように、下地層52は、たとえばスパッタリング法、無電解めっき法あるいは蒸着法により金属材料を被着させた後、フォトリソグラフィ法によりパターン形成することにより形成される。下地層52は、たとえば銅、ニッケル、クロムおよびチタン、またはこれらの合金として形成される。40

**【 0 0 8 8 】**

下地層52は、必ずしも一層として形成する必要はなく、複数の層として形成してもよい。たとえば、下地層52は、導体層50とビア導体53との密着性を高めるための第1層と、貫通孔51Aの内面51Aaとビア導体53との密着性を高めるための第2層と、を含んでいてもよい。

**【 0 0 8 9 】**

第1層は、たとえば銅を用いたスパッタリングにより、厚みが100nm以上1000nm以下に形成される。スパッタ圧力は、たとえば0.01Pa以上10Pa以下、スパ

10

20

30

40

50

ツタ時の電力はスパッタされる合金の単位面積当たり  $3 \text{ W} / \text{cm}^2$  以上  $20 \text{ W} / \text{cm}^2$  以下とされる。

#### 【0090】

第2層は、たとえばニッケル・クロム合金を用いたスパッタリングにより、厚みが  $3 \text{ nm}$  以上  $100 \text{ nm}$  以下に形成される。ニッケル・クロム合金におけるクロムの含有量は、たとえば  $10\%$  重量以上  $30\%$  重量%以下とされる。スパッタ圧力は、たとえば  $0.01 \text{ Pa}$  以上  $10 \text{ Pa}$  以下、スパッタ時の電力はスパッタされる合金の単位面積当たり  $0.5 \text{ W} / \text{cm}^2$  以上  $3 \text{ W} / \text{cm}^2$  以下とされる。

#### 【0091】

このようにして形成された下地層52は、粗面化処理により、導体層50における露出面  $50 \text{ A}$  の十点平均粗さ  $R_z$  が  $1 \mu\text{m}$  以下（好ましくは  $30 \text{ nm}$  以上  $300 \text{ nm}$  以下）とされていることから、下地層52と導体層50との間は、原子配列に乱れのない連続的な結晶構造として金属結晶が形成される。そのため、下地層52と導体層50との間において応力が集中することを抑制できる。

#### 【0092】

また、露出面  $50 \text{ A}$  の十点平均粗さ  $R_z$  が  $1 \mu\text{m}$  以下とするとともに、貫通孔  $51 \text{ A}$  における内面  $51 \text{ A a}$  の十点平均粗さ  $R_z$  が  $1 \mu\text{m}$  以下（好ましくは  $30 \text{ nm}$  以上  $300 \text{ nm}$  以下）とすれば、下地層52の表面における表面粗さを小さくすることが可能となる。

#### 【0093】

なお、下地層52の形成は、真空条件下あるいは不活性ガス雰囲気下で行なうのが好ましい。このような条件下において下地層52を形成することにより、導体層50の露出面  $50 \text{ A}$  や下地層52が酸化してしまうことを抑制することができる。また、下地層52を形成する前に、貫通孔  $51 \text{ A}$  の内面および導体層50の露出部分を洗浄しておくのが好ましい。このような洗浄を行なうことにより、貫通孔  $51 \text{ A}$  の内面  $51 \text{ A a}$  および導体層50の露出面  $50 \text{ A}$  に付着した油脂などの汚れ除去できるため、下地層52と貫通孔  $51 \text{ A}$  の内面あるいは導体層50の露出面  $50 \text{ A}$  との間に汚れ（異物）が存在することに起因するクラックの発生を抑制することができる。

#### 【0094】

その一方で、洗浄工程を空気にさらされた環境下で行なう場合には、導体層50の露出面  $50 \text{ A}$  や下地層52が酸化されるのを極力抑制するのが好ましい。これは、導体層50や下地層52の表面に酸化膜が形成された場合には、クラックが発生しやすくなるおそれがあるからである。すなわち、導体層50や下地層52を形成する金属は、金属原子のみで固有の結晶構造を形成し、その結晶内では破壊の進行が少ない。その反面、導体層50や下地層52の表面に酸化膜が形成されると、酸化膜は金属原子と酸素原子が混在した結晶構造となる。この酸化膜の結晶構造は、金属原子のみで形成された結晶構造とは、構造が大きく異なるため、この部分で原子配列が不規則に乱れ、金属部分と酸化膜部分の結合が弱くなる。

#### 【0095】

ここで、貫通孔  $51 \text{ A}$  の内面  $51 \text{ A a}$  や導体層50の露出部分  $50 \text{ A}$  の洗浄は、たとえば界面活性剤および希硫酸により表面洗浄処理を行なった後に液成分を乾燥させることにより行なわれる。より具体的には、市販の界面活性剤入りの洗剤を溶解させた洗浄水、希硫酸およびイオン交換水を洗浄すべき部分に順次スプレーした後に液成分を乾燥させることにより行なわれる。一般に、洗浄は空気にさらされた環境下で行われるため、洗浄工程においては、下地層の表面に酸化膜が形成され得る環境下にある。そのため、洗浄工程において、上述のように酸化膜の形成をいかに少なくするかが問題である。そのためには、通常、高温の風（ $70 \sim 80$  ℃）を用いて行っている乾燥を比較的低い温度の風で行うといい。高温の風を使用すると基板温度が上昇し、酸化膜が形成されるやすくなるためである。具体的には、乾燥時間の効率も考慮して、 $20$  ℃以上  $40$  ℃以下で行うといい。このように  $20$  ℃以上  $40$  ℃の比較的低温に保持された風によって、 $3$  秒以上  $10$  秒以下の間、乾燥を行うことにより、通常の空気環境下において、酸化膜を  $80 \text{ nm}$  以下に抑えるこ

10

20

30

40

50

とができる。さらに酸化膜の形成を少なくするためには、希硫酸洗浄、イオン交換水洗浄の後、高圧(1.5気圧以上2.5気圧)の室温空気を吹き付けて乾燥させることで、酸化膜を50nm以下にすることができる。

#### 【0096】

一方、図7(c)に示したように、ビア導体53は、たとえばスパッタリング法、電解めっきにより金属材料を被着させた後、フォトリソグラフィ法によりパターン形成することにより形成される。ビア導体53は、たとえば銅、銀、金、アルミニウム、ニッケルおよびクロム、またはこれらの合金により形成される。

#### 【0097】

上述のように、下地層52は、導体層50における露出部分50Aおよび貫通孔51Aにおける内面51Aaの十点平均粗さRzが1μm以下とされているために、その表面における表面粗さを小さくされている。このような下地層52上に形成されたビア導体53は、下地層52との間が、原子配列に乱れのない連続的な結晶構造として金属結晶が形成される。そのため、ビア導体53と下地層52との間に応力が集中することを抑制できる。

#### 【0098】

なお、ビア導体53の形成は、真空条件下あるいは不活性ガス雰囲気下で行なうのが好ましい。このような条件下においてビア導体53を形成することにより、下地層52が酸化してしまうことを抑制することができる。また、ビア導体53を形成する前に、下地層52の表面を洗浄しておくのが好ましい。このような洗浄を行なうことにより、下地層52の表面の汚れ除去できるため、下地層52とビア導体53との間に汚れ(異物)が存在することに起因するクラックの発生を抑制することができる。下地層52の表面の洗浄においても、洗浄液を用いて空気に曝される雰囲気で洗浄を行なう場合には、下地層52への酸化膜の形成を抑制するために、上述した条件で乾燥を行なうのが好ましい。

#### 【0099】

さらに、図8(a)ないし図8(d)に示したように、上述した工程を所定回数繰り返し、導体層50、絶縁層51、下地層52およびビア導体53を所定層形成することにより、コア基板4の上面にビルドアップ配線層5を形成することができる。また、同様な手法により、コア基板4の下面にビルドアップ配線層6を形成することができる。ビルドアップ配線層6においても、下地層62と導体層60との間、および下地層62とビア導体63との間が、原子配列に乱れのない連続的な結晶構造(金属結晶)とされる。そのため、本発明の製造方法によれば、下地層52, 62と、これに接する導体部分50, 53, 60, 63との間に金属結晶を適切に形成するため、加熱によるクラックが発生しにくい配線基板2を提供することができる。

#### 【実施例】

#### 【0100】

本実施例では、温度変化によって配線基板のビア導体の近傍にクラックが発生するか否かを検討した。クラックの発生の有無は、温度サイクル試験前および試験後の配線基板について、ビア導体近傍の断面観察することにより確認した。また、断面観察において、導体層と下地層、および下地層とビア導体との間における金属結晶の有無、貫通孔の内面および導体層の表面粗さ、および導体層の表面での酸化膜の厚みを同時に確認した。

#### 【0101】

#### (配線基板の作製)

配線基板としては、3種類のサンプル1~3を作製した。これらのサンプルは、コア基板を形成した後に、コア基板の両面にビルドアップ配線を形成することにより作製した。

#### 【0102】

コア基板は、絶縁体に貫通孔を形成するとともに、貫通孔にビア導体した後に貫通孔に樹脂を充填することにより形成した。

#### 【0103】

絶縁体は、織布に熱硬化性樹脂を含浸させた樹脂シートを熱プレスして硬化することに

10

20

30

40

50

よって、厚みを0.3mmに形成した。織布としては、ポリパラフェニレンベンズビスオキサゾール樹脂製の単纖維(直径13μm)を300本束ねた纖維束を縦横に織り込んだものを使用した。熱硬化性樹脂としては、エポキシ樹脂を使用した。

#### 【0104】

貫通孔は、レーザ加工により、直径を50μmに形成した。レーザ加工は、波長266nmの4倍高調波YAGレーザ加工装置を用いて行った。レーザのスポット径は10μmとし、トレパン加工を行うことで直径を50μmのスルーホールに加工した。

#### 【0105】

ピア導体は、貫通孔の内面に無電解めっきおよび電解銅めっきにより、厚み15μmの銅めっきとして形成した。

#### 【0106】

無電解銅めっきは、市販のめっき液を使用し15分～30分間めっき液に浸すことにより行なった。

#### 【0107】

電解めっきは、3.5規定の硫酸に銅を25g/L溶解し、さらに塩素を55ppm添加しためっき液を使用し、1A/dm<sup>2</sup>の電流を30～120分印加することにより行なった。

#### 【0108】

貫通孔に対する樹脂の充填は、PET樹脂からなる離型フィルム上に未硬化の熱硬化性エポキシ樹脂を塗布したシートを準備し、このシートをコア基板に重ね、真空中で130

に加熱、20MPaの圧力を加えることで、貫通孔に充填した後に、表面の余剰の樹脂をブラシ研磨で除去し、その後、エポキシ樹脂を185で熱硬化させることにより行なった。

#### 【0109】

一方、ビルドアップ配線層は、コア基板の上面および下面に導体層および絶縁層を交互に形成するとともに、絶縁層に対して、貫通孔、下地層およびピア導体を形成することにより行なった。

#### 【0110】

導体層は、スパッタ装置(ULVAC製)を用いて厚みが50nmとなるようにコア基板(または絶縁層)の表面にニッケル-20%クロム合金を被着させた後、スパッタ装置(ULVAC製)を用いて厚みが200nmとなるように銅を被着させ、これらをベースにセミアディティブ法により、スパッタで被着させた銅に通電して電解めっきを行なって銅をパターン形成することにより厚さ15μmに形成した。最初のニッケル-20%クロム合金の被着は、樹脂と銅との密着を強固にするためのものである。次の銅の被着は、その次の工程で電解めっきをするため、導電性を持たせるためである。

#### 【0111】

絶縁層は、真空ラミネーターによって、厚みが20μmとなるように導体層の表面に樹脂層を形成した後に、樹脂層を加熱・固化させることにより形成した。絶縁層は、厚さ10μmのフィルム絶縁層と、厚さ10μmの接着層とを含むものとして形成した。フィルム絶縁層はポリパラフェニレンベンズビスオキサゾール樹脂により形成し、接着層はエポキシ樹脂により形成した。このフィルム絶縁層を接着剤が付いた状態で、コア基板上に重ね市販の真空ラミネーターで積層した。積層には110で5秒加熱し、2MPaの圧力で加圧して、絶縁層を密着させた。その後、基板を170に加熱して接着層を硬化させた。

#### 【0112】

貫通孔は、YAGレーザ加工により、波長を266nm、スポット径を15μm、1パルス当たりのエネルギーを2μJとし、1つの貫通孔につき、300ショットでトレパンング加工を行うことにより形成した。貫通孔は、底部の直径を40μm、上部の直径を50μmに設定した。

#### 【0113】

10

20

30

40

50

貫通孔は、その内面をプラズマ処理により粗面化した。プラズマ処理は、アルゴンガスを用いて、出力 500 W で行なった。プラズマ処理の時間は、サンプル 1 については 60 秒、サンプル 2, 3 については 360 秒とした。

#### 【0114】

下地層は、サンプル 1, 2 についてはスパッタリング法により、サンプル 3 については無電解銅めっきにより金属材料を被着させた後、フォトリソグラフィ法によりパターン形成することにより形成した。

#### 【0115】

サンプル 1, 2 におけるスパッタリング法による下地層は、ニッケル-クロム合金および Cu の二層に形成した。

10

#### 【0116】

ニッケル-クロム合金のスパッタリングは、まず装置内を真空にし、次にアルゴンガスを導入して、圧力を 0.1 ~ 1 Pa に調整した。電力はスパッタされる合金の面積当たり 1 W / cm<sup>2</sup>、スパッタ時間は 10 秒とし、クロムの含有量が 20%、厚さは 10 nm に形成した。

#### 【0117】

銅のスパッタリングは、電力をスパッタされる合金の面積当たり 8 W / cm<sup>2</sup>、スパッタ時間は 20 秒とし、厚さを 250 nm に形成した。

20

#### 【0118】

サンプル 3 における無電解銅めっきによる下地層は、市販の無電解めっき用の銅めっき液を使用し、処理時間を 15 ~ 30 分として形成した。

#### 【0119】

ビア導体 53 は、電解めっきにより金属材料を被着させた後、フォトリソグラフィ法によりパターン形成することにより形成した。電解めっきは 3.5 標準の硫酸に銅を 25 g / L 溶解し、さらに塩素を 55 ppm 添加しためっき液を使用し、1 A / dm<sup>2</sup> の電流を印加して 30 ~ 120 分間行なった。

#### 【0120】

##### ( 温度サイクル試験 )

温度サイクル試験は -55 ~ 125 °C の 15 分間冷却、室温での 10 分間放置、および 125 °C の 15 分間加熱を 1 サイクルとし、このサイクルを配線基板に対して 300 回繰り返すことにより行った。

30

#### 【0121】

##### ( 断面観察 )

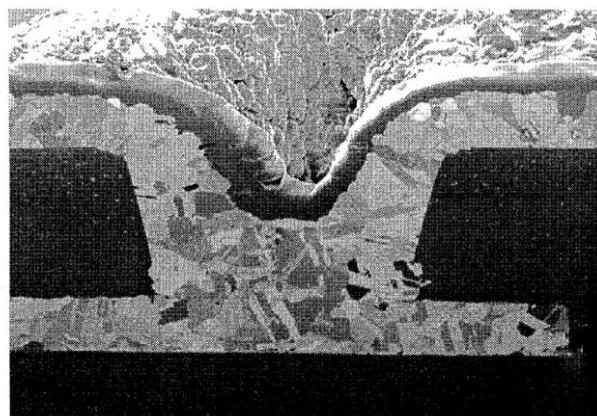

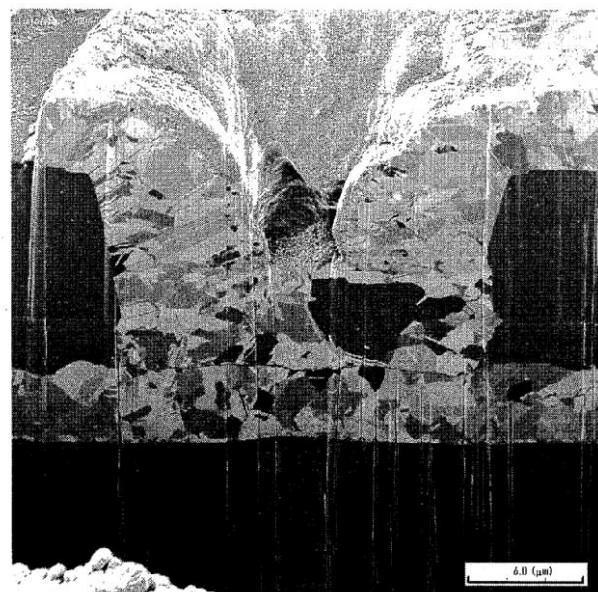

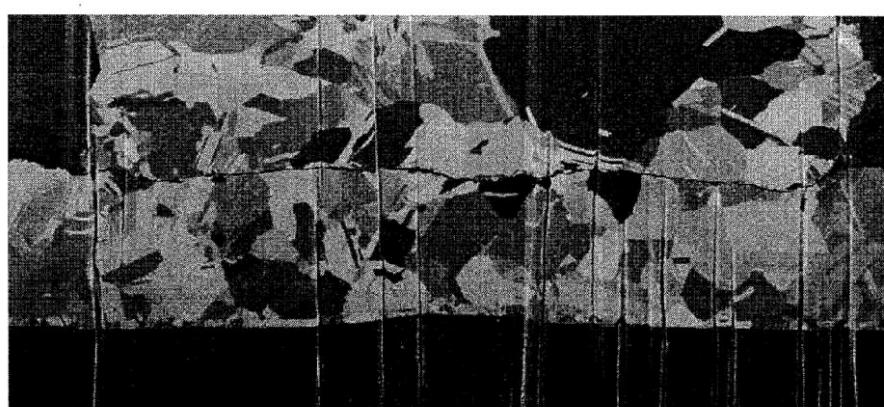

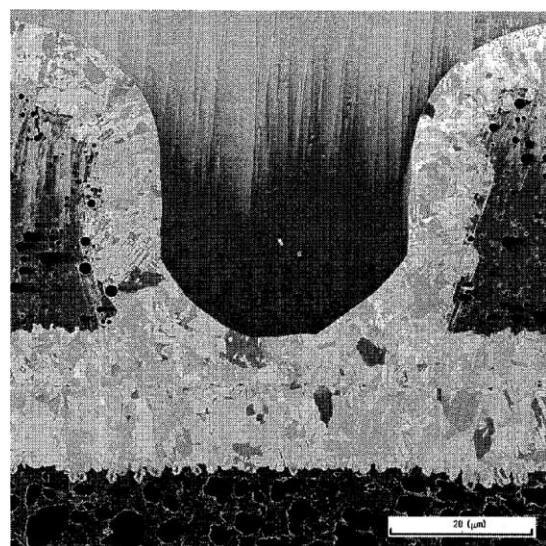

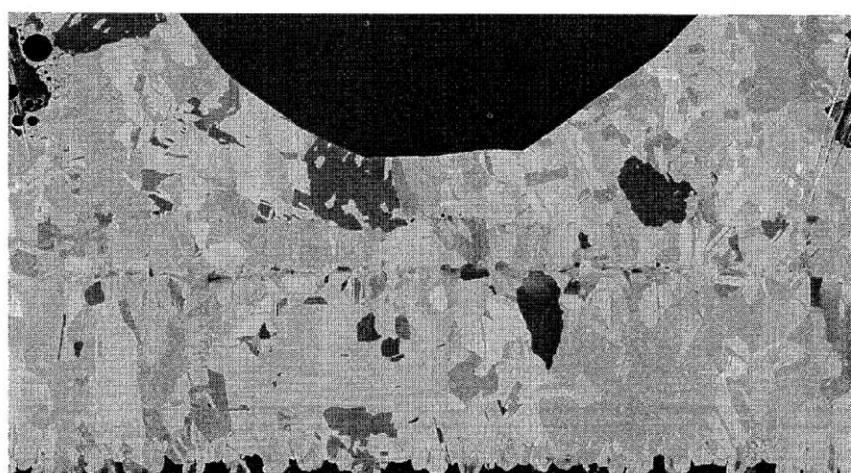

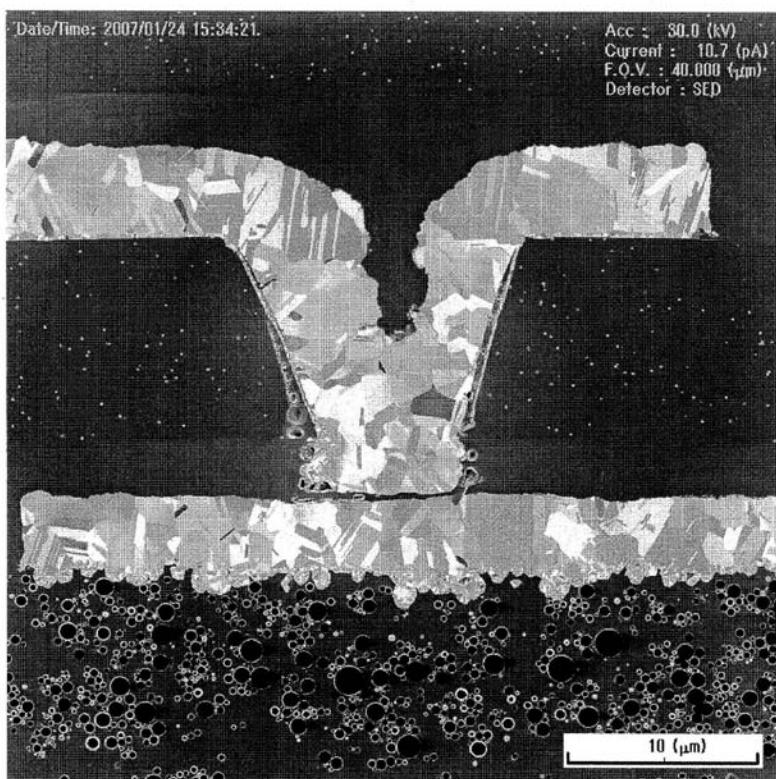

断面観察は、SIM (SIM3050; エスアイアイ・ナノテクノロジー株式会社製) を用いて行なった。サンプル 1 ~ 3 の温度サイクル試験前の断面 SIM 写真については、図 9 から図 11 にそれぞれ示した。また、サンプル 2 について、温度サイクル試験後の断面 SIM 写真を図 12 示した。

#### 【0122】

図 9 から分かるように、温度サイクル試験前のサンプル 1 については、下地層と導体層との間、および下地層と導体ビアとの間は、原子配列に乱れのない連続的な結晶構造（金属結晶）となっていた。

40

#### 【0123】

一方、図 10 および図 11 に示したように、温度サイクル試験前のサンプル 2, 3 では、下地層と導体層との間、および下地層と導体ビアとの間は、原子配列に乱れが生じてあり、不連続な結晶構造となっていた。

#### 【0124】

図 12 に示したように、温度サイクル試験後のサンプル 3 については、クラックが発生していた。SIM 写真の掲載は省略しているが、サンプル 1 については、温度サイクル試験後においてもクラックが発生しておらず、またサンプル 3 については、サンプル 2 と同様にクラックが確認された。したがって、下地層とこれに接する導体部分との間を金属結

50

晶とすることにより、クラックの発生が抑制できるものと考えられる。

【0125】

また、サンプル1～3について、絶縁層における貫通孔の内面および導体層の表面粗さ、および導体層表面の酸化膜の厚みを同時に確認したところ、下記表1に示した結果が得られた。

【0126】

また十点平均粗さ $R_z$ は、「JIS B 0601-1994」に準拠して計算したものである。ただし、基準長さ $L$ 、評価長さ $L_n$ をそれぞれ $5\text{ }\mu\text{m}$ 、 $50\text{ }\mu\text{m}$ とする。

【0127】

【表1】

|       | 貫通孔内面の $R_z$ | 導体層の $R_z$ | 酸化膜の厚み |

|-------|--------------|------------|--------|

| サンプル1 | 80nm         | 300nm      | 80nm   |

| サンプル2 | 1.3μm        | 1.2μm      | 170nm  |

| サンプル3 | 2.5μm        | 2.0μm      | 300nm  |

【0128】

表1から分かるように、金属結晶が形成されていたサンプル1は、貫通孔の内面および導体層の表面粗さが、それぞれ $80\text{ nm}$ および $300\text{ nm}$ と小さくなっていた。これに対して、下地層とこれを接する導体部分との間に金属結晶が形成されずにクラックが発生したサンプル2，3では、貫通孔の内面の表面粗さが、それぞれ $1.3\text{ }\mu\text{m}$ および $2.5\text{ }\mu\text{m}$ 、導体層の表面粗さが、それぞれ $1.2\text{ }\mu\text{m}$ および $2.0\text{ }\mu\text{m}$ であり、サンプル1よりも大きなものとなっていた。したがって、下地層に接する導体部分との間に金属結晶を形成させるためには、貫通孔の内面および導体層の表面粗さを小さくすればよく、たとえば表面粗さは $1\text{ }\mu\text{m}$ 以下とすればよいものと考えられる。

【0129】

また、下地層とこれを接する導体部分との間に金属結晶が形成されクラックが発生していないなかったサンプル1は、導体層の表面での酸化層の厚みが $80\text{ nm}$ と小さくなっていた。これに対して、下地層とこれを接する導体部分との間に金属結晶が形成されずに温度サイクル試験においてクラックが発生したサンプル2，3では、導体層の酸化膜の厚みが、それぞれ $170\text{ nm}$ および $300\text{ nm}$ であり、サンプル1よりも大きなものとなっていた。したがって、下地層に接する導体層の表面における酸化膜の厚みを $80\text{ nm}$ 以下に抑制することにより、クラックの発生が抑制できるものと考えられる。

【図面の簡単な説明】

【0130】

【図1】図1(a)は本発明に係る実装構造体の一例を示す全体斜視図であり、図1(b)は図1(a)に示した実装構造体を裏面側から見た全体斜視図である。

【図2】図1(a)のII-II線に沿う断面図である。

【図3】図1(a)に示した実装構造体における配線基板の要部を示す断面図である。

【図4】図3に示した配線基板における要部を拡大して示した断面図である。

【図5】図5(a)ないし図5(e)は図3に示した配線基板におけるコア基板を形成する方法を説明するための断面図である。

【図6】図6(a)ないし図6(d)は図3に示した配線基板におけるビルトアップ配線層を形成する方法を説明するための要部を示す断面図である。

【図7】図7(a)ないし図7(c)は下地層およびビア導体を形成する方法を説明するための要部を示す断面図である。

【図8】図8(a)ないし図8(d)は図3に示した配線基板におけるビルトアップ配線層を形成する方法を説明するための要部を示す断面図である。

【図9】実施例におけるサンプル1の温度サイクル試験を行なう前の断面写真である。

【図10】実施例におけるサンプル2の温度サイクル試験を行なう前の断面写真である。

【図11】実施例におけるサンプル3の温度サイクル試験を行なう前の断面写真である。

【図12】実施例におけるサンプル2の温度サイクル試験を行った後の断面写真である。

【図13】従来の配線基板を説明するための配線基板の要部を示す断面図である。

【図14】図13に示した配線基板の要部を拡大して示した断面図である。

【符号の説明】

【0131】

1 実装構造体

2 配線基板

3 半導体素子

50, 60 導体層

10

50A, 60A (導体層の) 露出面

51A, 61A 貫通孔

51Aa, 60Aa (貫通孔の) 内面

52, 62 下地層

53, 63 ピア導体

70, 71 仮想界面

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図13】

【図14】

【図9】

(a)

サンプル1

(b)

サンプル1

【図10】

(a)

サンプル2

(b)

サンプル2

【図 11】

(a)

サンプル3

(b)

サンプル3

【図12】

---

フロントページの続き

F ターム(参考) 4E351 AA03 AA04 AA05 BB01 BB30 BB33 BB36 BB38 CC06 DD04

DD05 DD06 DD10 DD11 DD17 DD19 DD21 GG02 GG03

5E317 AA24 BB02 BB03 BB12 BB13 BB14 BB15 BB16 BB17 BB18

BB19 CC32 CC33 CD27 GG09 GG11 GG20

5E343 AA07 AA17 AA18 AA19 BB17 BB23 BB24 BB25 BB28 BB35

BB38 BB39 BB40 BB44 DD33 DD43 EE02 ER31 GG04 GG13