등록특허 10-2147870

(19) 대한민국특허청(KR)

(12) 등록특허공보(B1)

(45) 공고일자 2020년08월25일

(11) 등록번호 10-2147870

(24) 등록일자 2020년08월19일

- (51) 국제특허분류(Int. Cl.)

*G06F 1/32* (2019.01) *H01L 21/336* (2006.01)

*H01L 21/822* (2006.01) *H01L 21/8242* (2006.01)

*H01L 21/8247* (2006.01) *H01L 27/04* (2006.01)

*H01L 27/10* (2006.01) *H01L 27/105* (2006.01)

*H01L 27/108* (2006.01) *H01L 27/115* (2017.01)

*H01L 29/786* (2006.01)

- (21) 출원번호 10-2014-7023583

- (22) 출원일자(국제) 2013년01월16일

심사청구일자 2018년01월08일

- (85) 번역문제출일자 2014년08월22일

- (65) 공개번호 10-2014-0124795

- (43) 공개일자 2014년10월27일

- (86) 국제출원번호 PCT/JP2013/051230

- (87) 국제공개번호 WO 2013/111757

국제공개일자 2013년08월01일

- (30) 우선권주장

JP-P-2012-011120 2012년01월23일 일본(JP)

(뒷면에 계속)

- (56) 선행기술조사문헌

JP2008251835 A\*

JP2011171723 A\*

US20090001814 A1\*

US20090144571 A1

\*는 심사관에 의하여 인용된 문헌

전체 청구항 수 : 총 19 항

심사관 : 손경완

## (54) 발명의 명칭 반도체 장치

**(57) 요 약**

회로들에 대한 전원 전압의 공급을 개별적으로 제어하기 위해, 반도체 장치는, CPU, CPU의 산술 연산에 이용되는 데이터를 판독 및 기입하는 메모리, CPU의 산술 연산에 의해 생성되는 데이터 신호를 변환하여 출력 신호를 생성하는 신호 처리 회로, CPU에 대한 전원 전압의 공급을 제어하는 제1 전원 공급 제어 스위치, 메모리에 대한 전원 (뒷면에 계속)

**대 표 도 - 도1**

전압의 공급을 제어하는 제2 전원 공급 제어 스위치, 신호 처리 회로에 대한 전원 전압의 공급을 제어하는 제3 전원 공급 제어 스위치, 및 입력 신호, 및 CPU와 신호 처리 회로로부터 입력되는 명령 신호들에 따라 제1 내지 제3 전원 공급 제어 스위치를 개별적으로 제어하는 기능을 적어도 갖는 콘트롤러를 포함한다.

(30) 우선권주장

JP-P-2012-011124 2012년01월23일 일본(JP)

JP-P-2012-105538 2012년05월03일 일본(JP)

---

## 명세서

### 청구범위

#### 청구항 1

반도체 장치로서,

제1 스위치에 전기적으로 접속된 CPU,

제2 스위치에 전기적으로 접속된 메모리,

제3 스위치에 전기적으로 접속된 신호 처리 회로, 및

콘트롤러를 포함하고,

상기 신호 처리 회로는 상기 CPU의 연산 데이터 신호를 출력 장치에 입력되는 출력 신호로 변환하고,

상기 제1 스위치, 상기 제2 스위치, 및 상기 제3 스위치 각각은 전원 공급선에 전기적으로 접속되고,

상기 CPU는 상기 콘트롤러에 입력되는 제1 신호를 출력하고,

상기 콘트롤러는 상기 제1 신호에 따라 상기 제1 스위치를 제어하고,

상기 신호 처리 회로는 상기 콘트롤러에 입력되는 제2 신호를 출력하고,

상기 콘트롤러는 상기 제2 신호에 따라 상기 제3 스위치를 제어하고,

상기 콘트롤러는 상기 제1 스위치, 상기 제2 스위치, 및 상기 제3 스위치를 개별적으로 제어하는, 반도체 장치.

#### 청구항 2

삭제

#### 청구항 3

삭제

#### 청구항 4

삭제

#### 청구항 5

삭제

#### 청구항 6

삭제

#### 청구항 7

제1항에 있어서,

상기 CPU는,

상기 CPU에 전원 전압이 인가되는 동안의 기간에 데이터를 유지하는 제1 메모리 회로, 및

상기 CPU에 상기 전원 전압이 인가되지 않는 동안의 기간에 데이터를 유지하는 제2 메모리 회로를 포함하고,

상기 제2 메모리 회로는 전계 효과 트랜지스터를 포함하는, 반도체 장치.

#### 청구항 8

제7항에 있어서,

상기 전계 효과 트랜지스터는 결정부(crystal portion)를 포함하는 산화물 반도체층을 포함하는, 반도체 장치.

#### 청구항 9

제8항에 있어서,

상기 결정부의 c축은 상기 산화물 반도체층의 표면의 법선 벡터에 평행한 방향으로 정렬되는, 반도체 장치.

#### 청구항 10

삭제

#### 청구항 11

삭제

#### 청구항 12

삭제

#### 청구항 13

반도체 장치로서,

제1 스위치에 전기적으로 접속된 제1 CPU,

제2 스위치에 전기적으로 접속된 메모리,

제3 스위치에 전기적으로 접속된 신호 처리 회로, 및

제2 CPU를 포함하고,

상기 신호 처리 회로는 상기 제1 CPU의 연산 데이터 신호를 출력 장치에 입력되는 출력 신호로 변환하고,

상기 제1 스위치, 상기 제2 스위치, 및 상기 제3 스위치 각각은 전원 공급선에 전기적으로 접속되고,

상기 제1 CPU는 상기 제2 CPU에 입력되는 제1 신호를 출력하고,

상기 제2 CPU는 상기 제1 신호에 따라 상기 제1 스위치를 제어하고,

상기 신호 처리 회로는 상기 제2 CPU에 입력되는 제2 신호를 출력하고,

상기 제2 CPU는 상기 제2 신호에 따라 상기 제3 스위치를 제어하고,

상기 제2 CPU는 상기 제1 스위치, 상기 제2 스위치, 및 상기 제3 스위치를 개별적으로 제어하는, 반도체 장치.

#### 청구항 14

제13항에 있어서,

상기 제1 CPU에 전원 전압이 인가되기 시작한 후, 상기 신호 처리 회로에 상기 전원 전압이 인가되기 시작하도록, 상기 제2 CPU가 상기 제3 스위치를 제어하는, 반도체 장치.

#### 청구항 15

제13항에 있어서,

상기 제1 CPU가 상기 연산 데이터 신호를 출력한 후, 상기 제1 CPU에 전원 전압이 인가되는 것을 정지하도록, 상기 제2 CPU가 상기 제1 스위치를 제어하는, 반도체 장치.

#### 청구항 16

제13항에 있어서,

상기 제1 스위치, 상기 제2 스위치, 및 상기 제3 스위치 각각은 상기 제2 CPU에 의해 사용되는 프로그램에 의해

제어되는, 반도체 장치.

#### 청구항 17

제1항 또는 제13항에 있어서,

상기 메모리는 전계 효과 트랜지스터를 포함하고,

상기 전계 효과 트랜지스터의 오프 전류는 채널 폭  $1 \mu\text{m}$ 당  $100\text{zA}$  이하인, 반도체 장치.

#### 청구항 18

제17항에 있어서,

상기 전계 효과 트랜지스터는 결정부를 포함하는 산화물 반도체층을 포함하는, 반도체 장치.

#### 청구항 19

제18항에 있어서,

상기 결정부의 c축은 상기 산화물 반도체층의 표면의 법선 벡터에 평행한 방향으로 정렬되는, 반도체 장치.

#### 청구항 20

제13항에 있어서,

상기 제1 CPU는,

상기 제1 CPU에 전원 전압이 인가되는 동안의 기간에 데이터를 유지하는 제1 메모리 회로, 및

상기 제1 CPU에 상기 전원 전압이 인가되지 않는 동안의 기간에 데이터를 유지하는 제2 메모리 회로를 포함하고,

상기 제2 메모리 회로는 전계 효과 트랜지스터를 포함하는, 반도체 장치.

#### 청구항 21

제20항에 있어서,

상기 전계 효과 트랜지스터는 결정부를 포함하는 산화물 반도체층을 포함하는, 반도체 장치.

#### 청구항 22

제21항에 있어서,

상기 결정부의 c축은 상기 산화물 반도체층의 표면의 법선 벡터에 평행한 방향으로 정렬되는, 반도체 장치.

#### 청구항 23

제1항 또는 제13항에 있어서,

상기 신호 처리 회로는,

상기 신호 처리 회로에 전원 전압이 인가되는 동안의 기간에 데이터를 유지하는 제1 메모리 회로, 및

상기 신호 처리 회로에 상기 전원 전압이 인가되지 않는 동안의 기간에 데이터를 유지하는 제2 메모리 회로를 포함하고,

상기 제2 메모리 회로는 전계 효과 트랜지스터를 포함하는, 반도체 장치.

#### 청구항 24

제23항에 있어서,

상기 전계 효과 트랜지스터는 결정부를 포함하는 산화물 반도체층을 포함하는, 반도체 장치.

**청구항 25**

제24항에 있어서,

상기 결정부의 c축은 상기 산화물 반도체층의 표면의 법선 벡터에 평행한 방향으로 정렬되는, 반도체 장치.

**청구항 26**

제7항에 있어서,

상기 CPU에 셀렉터를 더 포함하고,

상기 셀렉터는 상기 제1 메모리 회로 및 상기 제2 메모리 회로에 전기적으로 접속되는, 반도체 장치.

**청구항 27**

제20항에 있어서,

상기 제1 CPU에 셀렉터를 더 포함하고,

상기 셀렉터는 상기 제1 메모리 회로 및 상기 제2 메모리 회로에 전기적으로 접속되는, 반도체 장치.

**발명의 설명****기술 분야**

[0001]

본 발명은 반도체 장치에 관한 것이다.

**배경기술**

[0002]

최근, 마이크로컴퓨터 등의 반도체 장치의 전력 소비를 감소시키기 위한 기술 개발이 진행되고 있다.

[0003]

그러한 반도체 장치의 예는, 전원 공급이 불필요한 동안의 기간에 있어서 중앙 처리 유닛(central processing unit: CPU) 및 메모리 등에 대한 전원 전압의 공급을 정지할 수 있는 마이크로컴퓨터이다(예를 들어, 특허문헌 1).

**선행기술문헌****특허문헌**

[0004]

(특허문헌 0001) 일본 특허공개 제2009-116851호 공보

**발명의 내용****해결하려는 과제**

[0005]

그러나, 종래의 마이크로컴퓨터의 전력 소비를 감소시키는 것은 불충분했다. 예를 들어, 종래의 마이크로컴퓨터에서는, CPU 및 메모리 등의 회로들에 대한 전원 전압의 공급을 동일한 타이밍에 제어하기 때문에, 원래 전원 공급이 불필요한 회로에도 전원 전압이 공급되어버려, 그 결과, 마이크로컴퓨터는 불필요한 전력을 소비한다.

[0006]

본 발명의 일 실시 형태의 과제는 복수의 회로에 대한 전원 전압의 공급을 독립적으로 제어하는 것이다.

[0007]

본 발명의 일 실시 형태의 다른 과제는 전력 소비를 감소시키는 것이다.

**과제의 해결 수단**

[0008]

본 발명의 일 실시 형태에서는, 콘트롤러가 설치되어 CPU, 메모리, 및 신호 처리 회로에 대한 전원 전압의 공급을 개별적으로 제어함으로써, 각 회로에 대해 최적의 전원 공급 기간을 설정하여 낭비되는 전력 소비를 감소시킨다.

[0009]

구체적으로, 각각의 회로마다 전원 전압의 공급을 제어하는 스위치들(전원 공급 제어 스위치들 또는 파워 케이

트들이라고도 칭함)을 설치하고, 스위치들은 콘트롤러에 의해 제어된다. 이에 의해, 회로들에 대한 전원 전압의 공급을 개별적으로 제어할 수 있다.

- [0010] 본 발명의 일 실시 형태는, 입력 신호에 따라 산술 연산을 행하는 CPU, CPU의 산술 연산에 이용되는 데이터를 판독 및 기입하는 메모리, CPU의 산술 연산에 의해 생성되는 데이터 신호를 변환하여 출력 신호를 생성하는 신호 처리 회로, CPU에 대한 전원 전압의 공급을 제어하는 제1 전원 공급 제어 스위치, 메모리에 대한 전원 전압의 공급을 제어하는 제2 전원 공급 제어 스위치, 신호 처리 회로에 대한 전원 전압의 공급을 제어하는 제3 전원 공급 제어 스위치, 및 입력 신호, CPU로부터 입력되는 명령 신호, 및 신호 처리 회로로부터 입력되는 명령 신호에 따라 제1 내지 제3 전원 공급 제어 스위치를 개별적으로 제어하는 콘트롤러를 포함하는 반도체 장치이다.

- [0011] 본 발명의 일 실시 형태에 있어서, CPU 또는 신호 처리 회로의 레지스터를, 오프 전류가 낮은 트랜지스터를 포함하는 메모리 회로를 사용하여 형성할 수 있다.

- [0012] 본 발명의 일 실시 형태에 있어서, 메모리를, 오프 전류가 낮은 트랜지스터를 포함하는 메모리 셀을 구비하는 메모리 장치를 사용하여 형성할 수 있다.

- [0013] 본 발명의 일 실시 형태는 레지스터를 포함하는 CPU를 포함하는 반도체 장치이다. 레지스터는 메모리 회로를 포함한다. 메모리 회로에 있어서, 산화물 반도체를 포함하는 제1 트랜지스터의 소스 및 드레인 중 하나는, 실리콘을 포함하는 제2 트랜지스터의 게이트에 전기적으로 접속된다.

- [0014] 본 발명의 일 실시 형태에 있어서, 제1 트랜지스터와 제2 트랜지스터는 절연층을 사이에 두고 적층되는 것이 바람직하다.

- [0015] 본 발명의 일 실시 형태에 있어서, CPU, 메모리, 및 신호 처리 회로에 대한 전원 전압의 공급을, 상기의 CPU와는 다른 CPU를 사용하여 프로그램에 의해 개별적으로 제어함으로써, 각각의 회로에 대한 최적의 전원 공급 기간을 설정하여, 낭비되는 전력 소비를 감소시킨다.

- [0016] 구체적으로, 각각의 회로에 대해 전원 전압의 공급을 제어하는 스위치들(전원 공급 제어 스위치들)을 설치하고, 상기의 CPU와는 다른 CPU를 사용하여 프로그램에 의해 해당 스위치들을 제어한다. 이에 의해, 회로들에 대한 전원 전압의 공급을 개별적으로 제어할 수 있다.

- [0017] 본 발명의 일 실시 형태는, 입력 신호에 따라 산술 연산을 행하는 제1 CPU, 제1 CPU의 산술 연산에 이용되는 데이터를 판독 및 기입하는 메모리, 제1 CPU의 산술 연산에 의해 생성되는 데이터 신호를 변환하여 출력 신호를 생성하는 신호 처리 회로, 제1 CPU에 대한 전원 전압의 공급을 제어하는 제1 전원 공급 제어 스위치, 메모리에 대한 전원 전압의 공급을 제어하는 제2 전원 공급 제어 스위치, 신호 처리 회로에 대한 전원 전압의 공급을 제어하는 제3 전원 공급 제어 스위치를 포함하는 반도체 장치이다. 상기의 제1 CPU와는 다른 제2 CPU를 사용하여 프로그램에 의해 제1 내지 제3 전원 공급 제어 스위치를 개별적으로 제어한다.

- [0018] 제1 CPU에 대한 전원 전압의 공급이 개시된 후, 제1 CPU의 산술 연산의 결과를 나타내는 데이터가 신호 처리 회로에 입력되기 전에, 신호 처리 회로에 대한 전원 전압의 공급이 개시되도록 제3 전원 공급 제어 스위치가 제어되는 것이 바람직하다.

- [0019] 제1 CPU의 산술 연산의 결과를 나타내는 데이터가 신호 처리 회로에 입력된 후, 산술 연산의 결과를 나타내는 데이터의 변환 데이터가 출력 신호로서 신호 처리 회로로부터 출력되기 전에, 제1 CPU에 대한 전원 전압의 공급이 정지되도록 제1 전원 공급 제어 스위치가 제어되는 것이 바람직하다.

- [0020] 제1 CPU에 대한 전원 전압의 공급이 개시된 후, 제1 CPU의 산술 연산의 결과를 나타내는 데이터가 신호 처리 회로에 입력되기 전에, 신호 처리 회로에 대한 전원 전압의 공급이 개시되도록 제3 전원 공급 제어 스위치가 제어되는 것이 바람직하다. 또한, 제1 CPU의 산술 연산의 결과를 나타내는 데이터가 신호 처리 회로에 입력된 후, 산술 연산의 결과를 나타내는 데이터의 변환 데이터가 출력 신호로서 신호 처리 회로로부터 출력되기 전에, 제1 CPU에 대한 전원 전압의 공급이 정지되도록 제1 전원 공급 제어 스위치가 제어되는 것이 바람직하다.

- [0021] 본 발명의 일 실시 형태는 다음과 같이 구성되는 것이 바람직하다. 제1 CPU의 레지스터는 메모리 회로를 포함한다. 메모리 회로는, 제1 CPU에 대해 전원 전압이 공급되는 동안의 기간에 데이터를 유지하는 제1 메모리 회로, 및 제1 CPU에 대한 전원 전압의 공급이 정지되는 동안의 기간에 데이터를 유지하는 제2 메모리 회로를 포함한다. 제2 메모리 회로는, 데이터의 기입 및 유지를 제어하는 전계 효과 트랜지스터를 포함한다. 제2 메모리 회로에 포함되는 전계 효과 트랜지스터의 오프 전류는 채널 폭  $1\mu\text{m}$ 당  $100\text{zA}$  이하이다.

- [0022] 본 발명의 일 실시 형태는 다음과 같이 구성되는 것이 바람직하다. 제1 CPU의 레지스터에 포함되는 메모리 회로에 있어서, 제2 메모리 회로의 전계 효과 트랜지스터는, 채널이 형성되고 실리콘보다 밴드갭이 넓은 산화물 반도체를 함유하는 산화물 반도체층을 포함한다. 산화물 반도체층은, 결정부(crystal portion)들의 c축들이 산화물 반도체층이 형성되는 표면의 법선 벡터 또는 산화물 반도체층의 표면의 법선 벡터에 평행한 방향으로 정렬되고, a-b면에 수직인 방향으로부터 볼 때 삼각 형상 또는 육각 형상인 원자 배열을 갖는 상(phase)을 포함한다. 그 상에 있어서, c축에 수직인 방향으로부터 볼 때 금속 원자들이 층 형상으로 배열되거나, 또는 금속 원자들과 산소 원자들이 층 형상으로 배열된다.

- [0023] 본 발명의 일 실시 형태는 다음과 같이 구성되는 것이 바람직하다. 메모리는 메모리 장치를 포함한다. 메모리 장치는 메모리 셀을 포함한다. 메모리 셀은 데이터의 기입 및 유지를 제어하는 전계 효과 트랜지스터를 포함한다. 메모리 셀에 포함되는 전계 효과 트랜지스터의 오프 전류는 채널 폭  $1\mu\text{m}$ 당  $100\text{zA}$  이하이다.

- [0024] 본 발명의 일 실시 형태는 다음과 같이 구성되는 것이 바람직하다. 메모리 셀의 전계 효과 트랜지스터는, 채널이 형성되고 실리콘보다 밴드갭이 넓은 산화물 반도체를 함유하는 산화물 반도체층을 포함한다. 산화물 반도체층은, 결정부들의 c축들이 산화물 반도체층이 형성되는 표면의 법선 벡터 또는 산화물 반도체층의 표면의 법선 벡터에 평행한 방향으로 정렬되고, a-b면에 수직인 방향으로부터 볼 때 삼각 형상 또는 육각 형상인 원자 배열을 갖는 상을 포함한다. 그 상에 있어서, c축에 수직인 방향으로부터 볼 때 금속 원자들이 층 형상으로 배열되거나, 또는 금속 원자들과 산소 원자들이 층 형상으로 배열된다.

- [0025] 본 발명의 일 실시 형태는 다음과 같이 구성되는 것이 바람직하다. 신호 처리 회로는 레지스터를 포함한다. 신호 처리 회로에 포함되는 레지스터는 메모리 회로를 포함한다. 메모리 회로는, 신호 처리 회로에 대해 전원 전압이 공급되는 동안의 기간에 데이터를 유지하는 제1 메모리 회로, 및 신호 처리 회로에 대한 전원 전압의 공급이 정지되는 동안의 기간에 데이터를 유지하는 제2 메모리 회로를 포함한다. 제2 메모리 회로는, 데이터의 기입 및 유지를 제어하고, 채널 폭  $1\mu\text{m}$ 당  $100\text{zA}$  이하의 오프 전류를 갖는 전계 효과 트랜지스터를 포함한다.

- [0026] 본 발명의 일 실시 형태는 다음과 같이 구성되는 것이 바람직하다. 신호 처리 회로에 포함되는 레지스터에 있어서, 메모리 회로의 전계 효과 트랜지스터는, 채널이 형성되고 실리콘보다 밴드갭이 넓은 산화물 반도체를 함유하는 산화물 반도체층을 포함한다. 산화물 반도체층은, 결정부들의 c축들이 산화물 반도체층이 형성되는 표면의 법선 벡터 또는 산화물 반도체층의 표면의 법선 벡터에 평행한 방향으로 정렬되고, a-b면에 수직인 방향으로부터 볼 때 삼각 형상 또는 육각 형상인 원자 배열을 갖는 상을 포함한다. 그 상에 있어서, c축에 수직인 방향으로부터 볼 때 금속 원자들이 층 형상으로 배열되거나, 또는 금속 원자들과 산소 원자들이 층 형상으로 배열된다.

- [0027] 제2 CPU는 반도체 장치에 포함될 수 있다.

- ### 발명의 효과

- [0028] 본 발명의 일 실시 형태에 따르면, 개별 회로마다 전원 공급 기간을 최적화할 수 있으므로, 전력 소비를 감소시킬 수 있다.

- ### 도면의 간단한 설명

- [0029] 첨부 도면에 있어서,

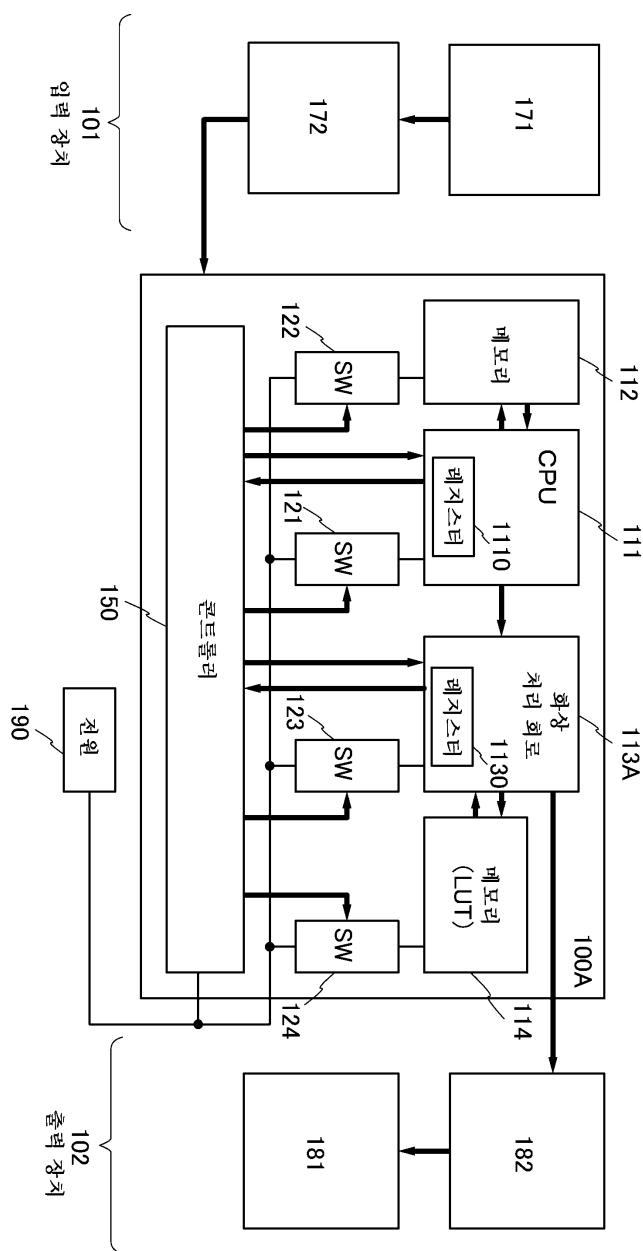

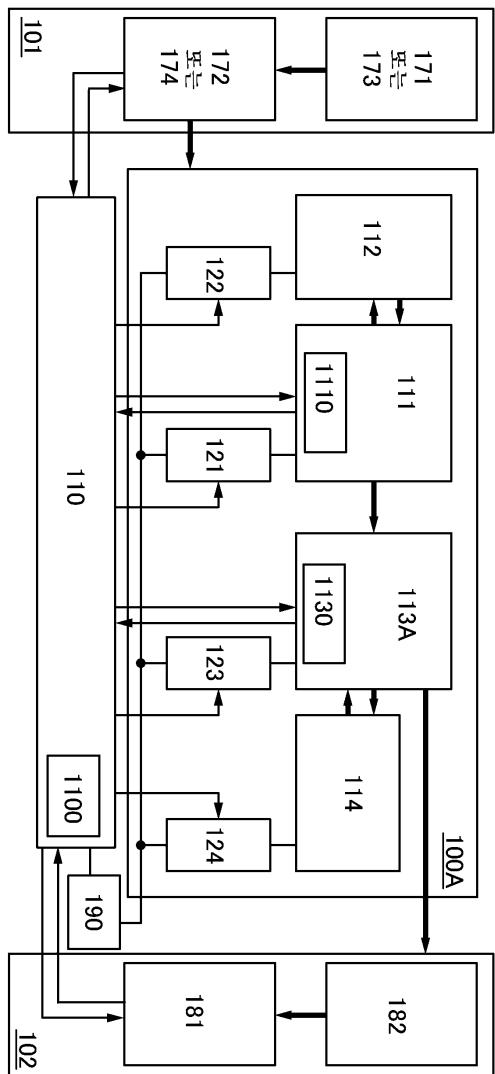

- 도 1은 반도체 장치의 예를 도시한다.

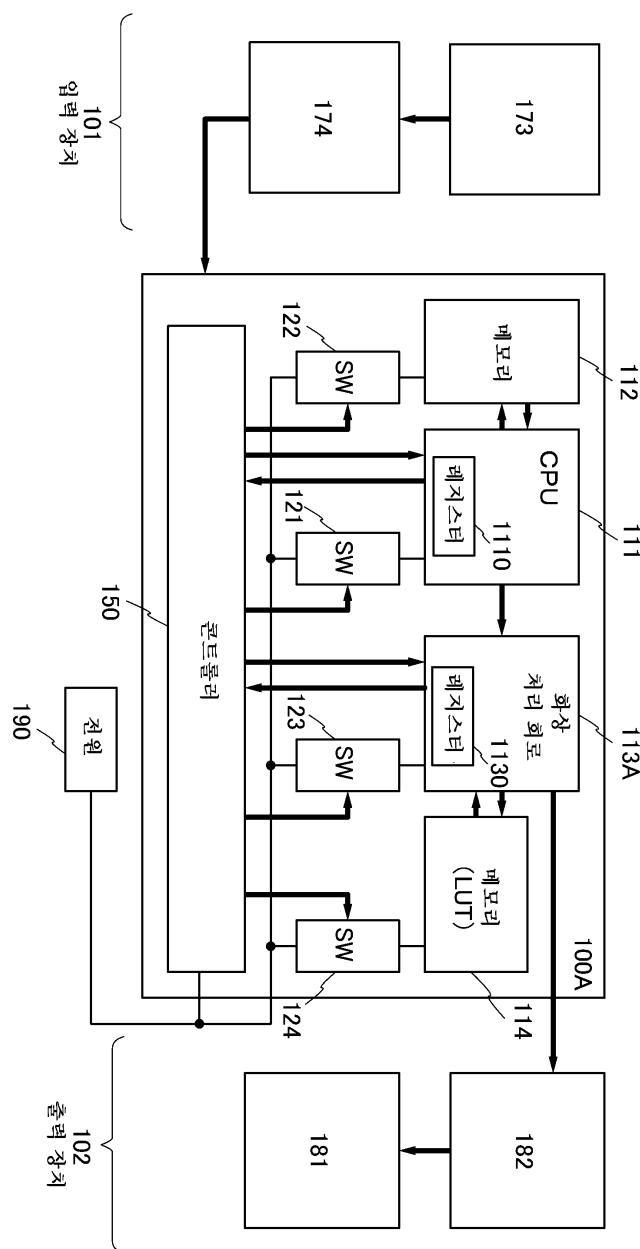

- 도 2는 반도체 장치의 예를 도시한다.

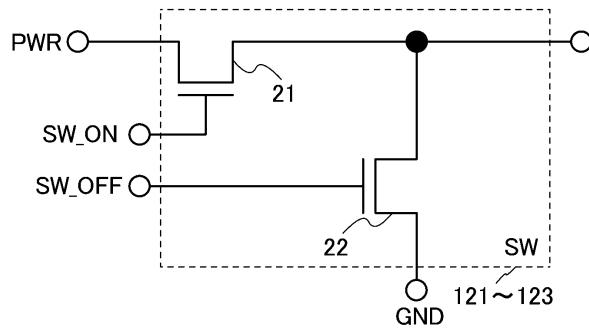

- 도 3은 전원 공급 제어 스위치의 구성의 예를 도시한다.

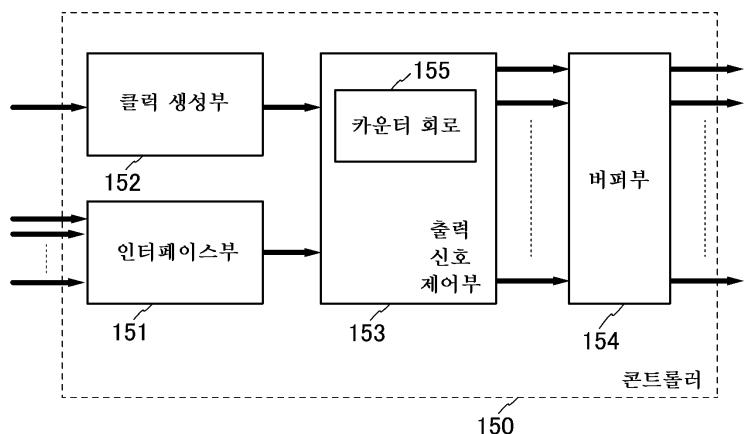

- 도 4는 콘트롤러의 구성의 예를 도시한다.

- 도 5는 반도체 장치의 예를 도시한다.

- 도 6은 반도체 장치의 예를 도시한다.

- 도 7은 반도체 장치의 예를 도시한다.

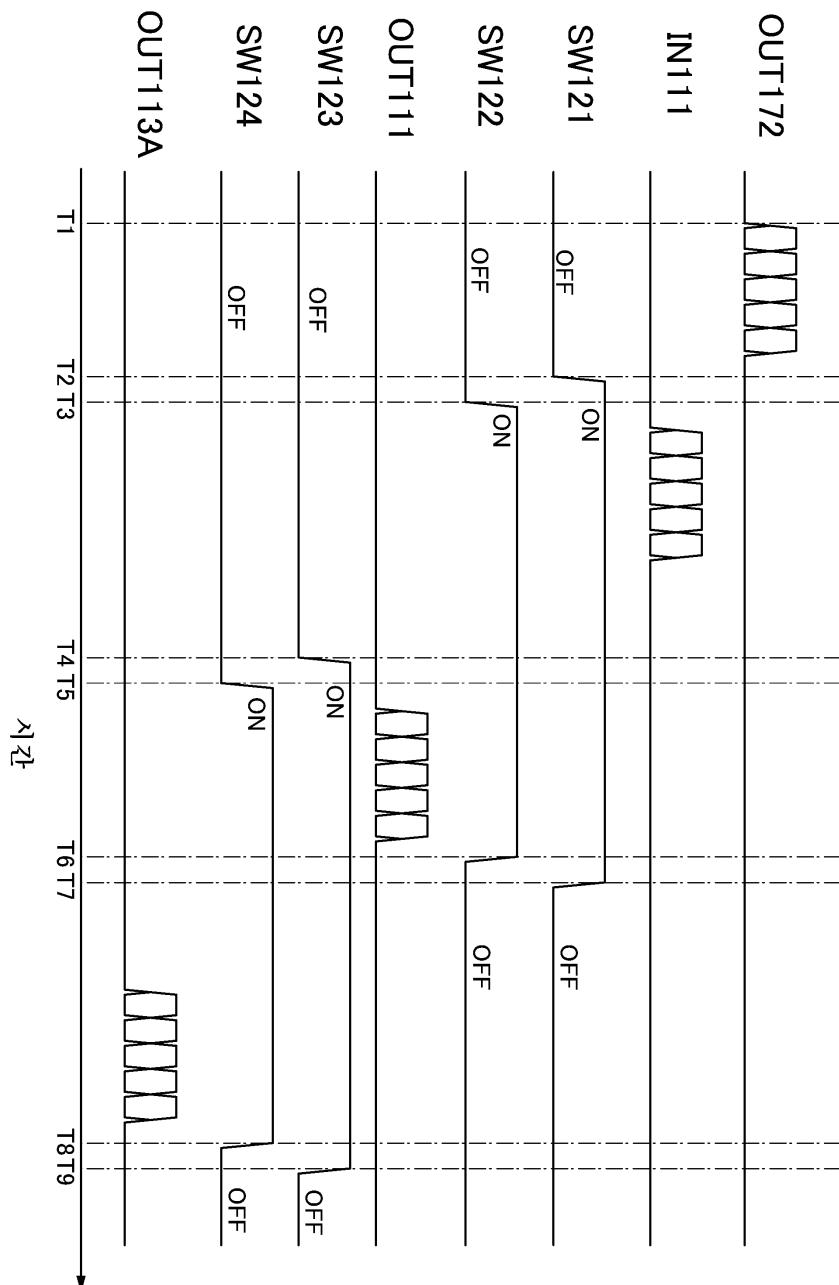

- 도 8은 반도체 장치의 구동 방법의 예를 설명하기 위한 타이밍 차트이다.

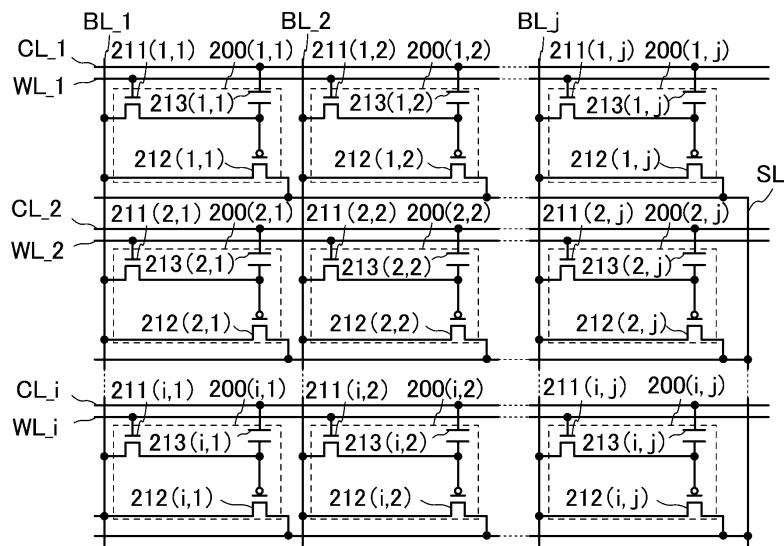

도 9는 메모리 장치의 구성의 예를 도시한다.

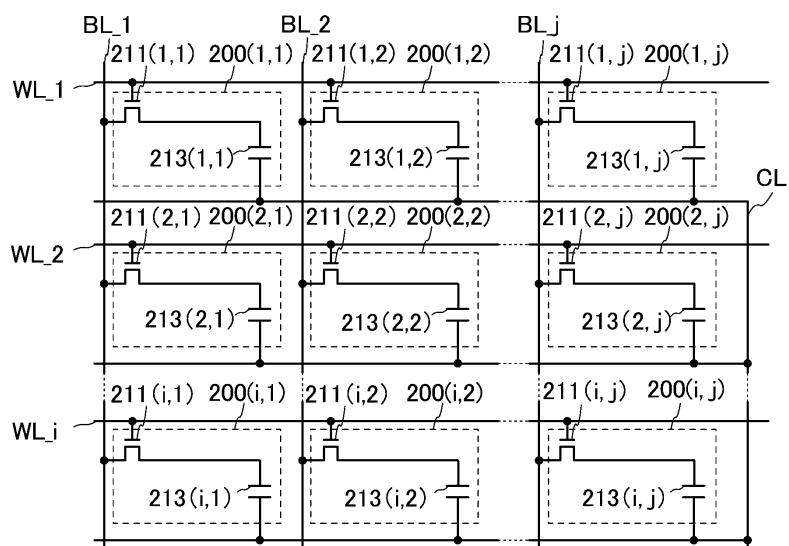

도 10은 메모리 장치의 구성의 예를 도시한다.

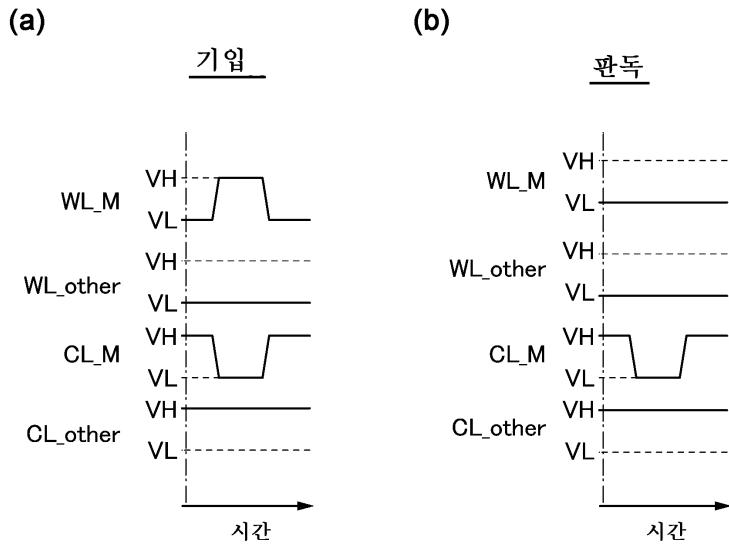

도 11의 (a) 및 도 11의 (b)는 메모리 장치의 구동 방법의 예를 설명하기 위한 타이밍 차트들이다.

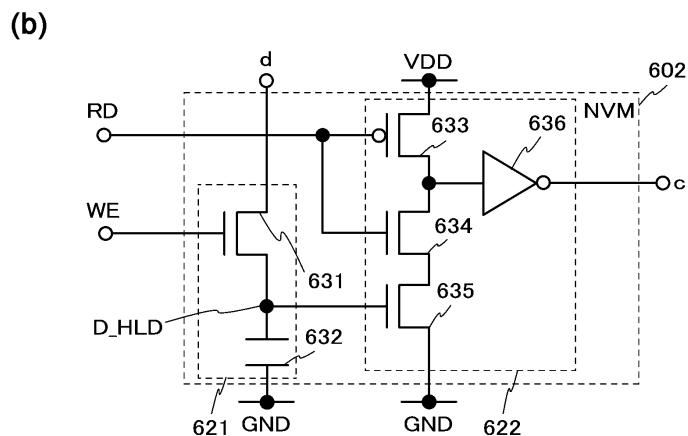

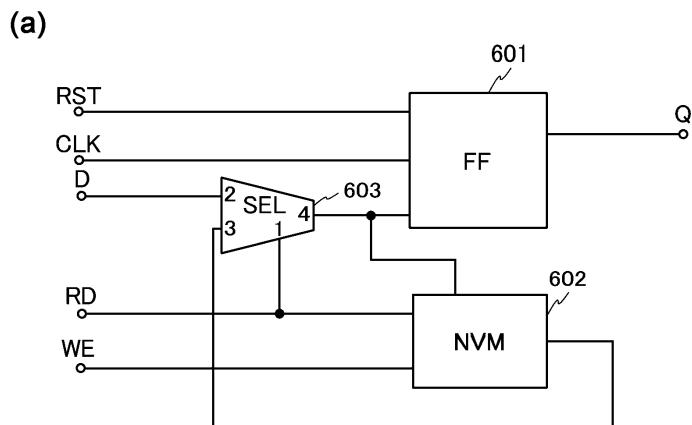

도 12의 (a) 및 도 12의 (b)는 메모리 회로의 구성의 예를 도시한다.

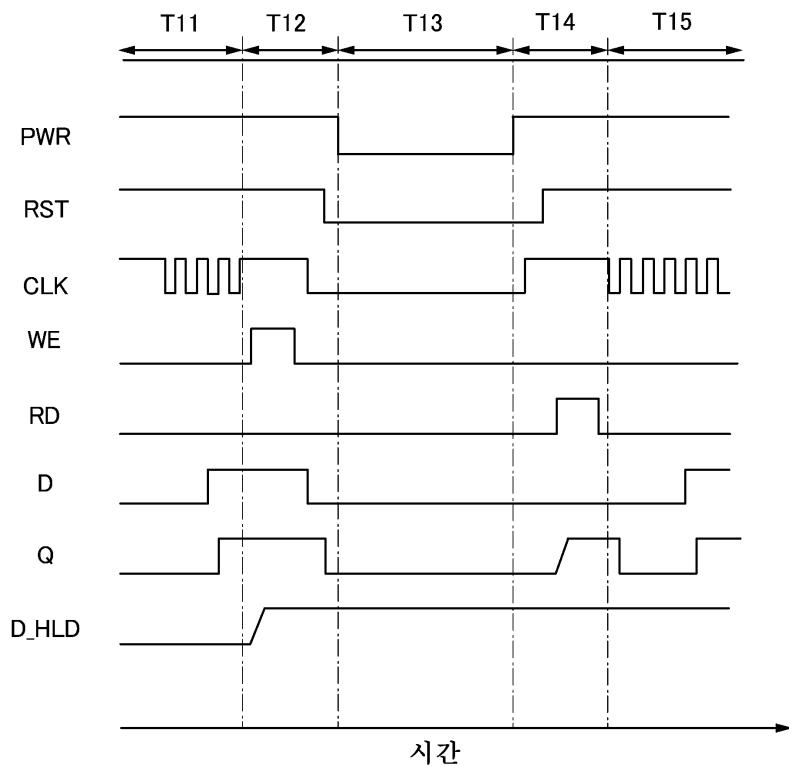

도 13은 메모리 회로의 구동 방법의 예를 설명하기 위한 타이밍 차트이다.

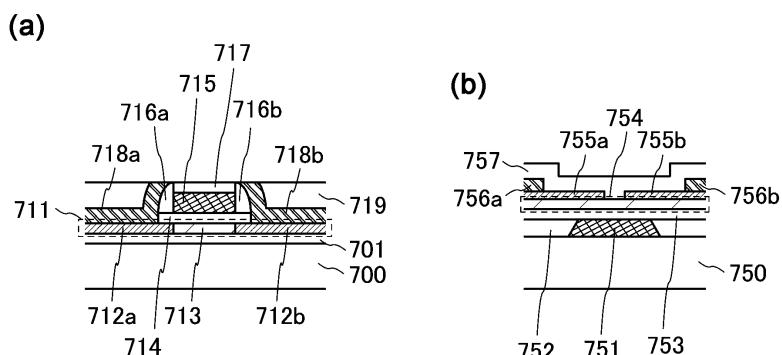

도 14의 (a) 및 도 14의 (b)는 각각 반도체 장치의 구조의 예를 설명하기 위한 단면 모식도이다.

도 15는 반도체 장치의 구조의 예를 설명하기 위한 단면 모식도이다.

도 16의 (a) 내지 도 16의 (f)는 각각 전자 기기의 예를 도시한다.

도 17은 CPU의 예를 도시한다.

도 18은 레지스터의 예를 도시한다.

도 19는 반도체 장치의 예를 도시한다.

도 20은 반도체 장치의 예를 도시한다.

도 21은 반도체 장치의 예를 도시한다.

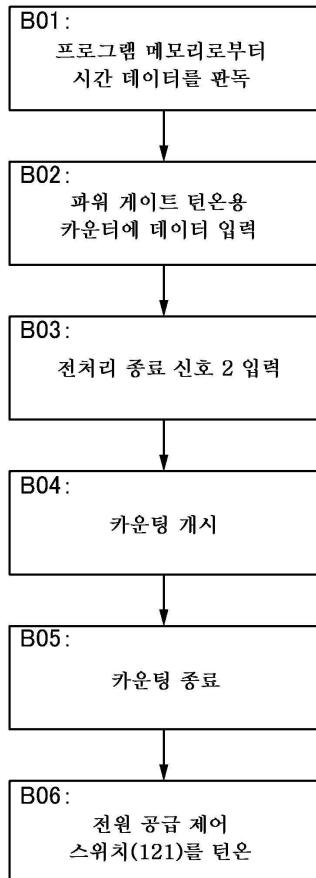

도 22의 (a) 및 도 22의 (b)는 반도체 장치의 예를 설명하기 위한 차트들이다.

### 발명을 실시하기 위한 구체적인 내용

[0030]

본 발명의 실시 형태들의 예들에 대해서 설명한다. 본 발명의 취지 및 범위로부터 일탈하지 않고 실시 형태들의 상세 사항들을 변경할 수 있다는 것은 당업자라면 용이하게 이해할 것임을 유의한다. 따라서, 본 발명은 하기의 실시 형태들의 기재 내용에 한정되지 않는다.

[0031]

본 명세서에서, 상이한 실시 형태들의 내용들을 서로 적절히 조합할 수 있다. 또한, 실시 형태들의 내용들을 서로 적절히 치환할 수 있다.

[0032]

"제1" 및 "제2" 등의 서수는 구성 요소들 간의 혼동을 피하기 위해 이용되고, 구성 요소들의 개수를 한정하지 않는다.

[0033]

(실시 형태 1)

[0034]

본 실시 형태에서는, 각각의 회로마다 전원 공급이 독립적으로 제어될 수 있는 반도체 장치의 예들에 대해서 설명한다.

[0035]

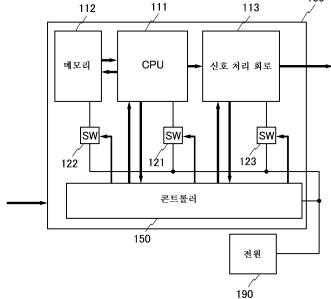

먼저, 반도체 장치의 구성의 예에 대해서 도 1을 참조하여 설명한다.

[0036]

도 1에 도시된 반도체 장치(100)는 CPU(111), 메모리(112), 신호 처리 회로(113), 전원 공급 제어 스위치들(SW로 표시됨)(121 내지 123), 및 콘트롤러(150)를 포함한다. CPU(111), 메모리(112), 신호 처리 회로(113), 및 콘트롤러(150)는 버스를 통해 서로 신호의 입출력을 행할 수 있다. 반도체 장치(100)에는 전원(190)으로부터 전원 공급선을 통해 전원 전압이 공급된다. 전원(190)이 이차 전지인 경우, 전원(190)은 반도체 장치(100) 내에 설치될 수 있다.

[0037]

CPU(111)는 입력 신호에 따라 산술 연산을 행하는 기능을 갖는다. 입력 신호의 예들은 클럭 신호, CPU(111)의 동작을 제어하기 위한 신호, 신호 처리 회로(113)의 동작을 제어하기 위한 신호, 및 입력 장치로부터 입력되는 신호이다. 본 명세서에서는 달리 지정하지 않는다면, 복수 종류의 신호가 간단히 "신호"로서 표기되는 일부 경우들이 있다는 것을 유의한다.

[0038]

CPU(111)의 레지스터는 예를 들어, 제1 메모리 회로와 제2 메모리 회로에 의해 구성된다. 이 경우에, CPU(111)에 대한 전원 공급을 정지시키기 직전에 제2 메모리 회로에 데이터를 저장한다. 그 후, 전원 공급을 재개시킨 직후에 제2 메모리 회로에 저장된 데이터를 제1 메모리 회로에 입력한다. 이에 의해, 전원 공급을 재개시킬 때 CPU(111)의 복귀가 빨라질 수 있다. 일 실시 형태는 상기의 구성에 한정되지 않고, 다른 메모리 회로에 의해 레지스터를 구성할 수 있다는 것을 유의한다.

- [0039] 제2 메모리 회로는 예를 들어, 오프 전류가 낮은 트랜지스터를 사용하여 형성된다. 이 경우에, 오프 전류가 낮은 트랜지스터는 제2 메모리 회로에의 데이터 기입 및 제2 메모리 회로의 데이터 유지를 제어하는 기능을 갖는다.

- [0040] 상기의 경우에, 오프 전류가 낮은 트랜지스터의 오프 전류는 채널 폭  $1\text{ }\mu\text{m}$ 당  $100\text{zA}$  이하이다.

- [0041] 오프 전류가 낮은 트랜지스터는 예를 들어, 실리콘보다 밴드갭이 넓은 산화물 반도체를 포함하고 실질적으로 i형인 채널 형성 영역을 포함하는 전계 효과 트랜지스터(field-effect transistor)일 수 있다. 산화물 반도체를 포함하는 전계 효과 트랜지스터는 예를 들어, 수소 또는 물 등의 불순물을 가능한 한 많이 감소시키고, 산소를 공급해서 산소 결손을 가능한 한 많이 감소시키는 방식으로 제작할 수 있다.

- [0042] 오프 전류가 낮은 트랜지스터를 사용하여 형성된 메모리 회로는, 그 트랜지스터를 단순히 턴오프하는 것에 의해 데이터를 장시간 동안 유지할 수 있다. 그 결과, 간략한 구성을 이용하여 메모리 회로를 구성할 수 있다.

- [0043] 메모리(112)는 CPU(111)의 연산 처리에 이용되는 데이터를 판독 및 기입한다.

- [0044] 메모리(112)는 예를 들어, 오프 전류가 낮은 트랜지스터를 각각 포함하는 복수의 메모리 셀을 구비하는 메모리 장치일 수 있다. 오프 전류가 낮은 트랜지스터는 메모리 셀의 데이터 기입 및 유지를 제어하는 기능을 갖는다. 메모리 장치는 전원 공급을 정지시킨 때에도, 데이터를 장시간 동안 유지할 수 있다. 이 때문에, 이 메모리 장치를 사용하여 메모리(112)를 형성함으로써, 데이터의 재기입 및 판독이 불필요한 동안의 기간에 메모리(112)에 대한 전원 전압의 공급을 정지하는 것이 가능함으로써, 전력 소비를 감소시킬 수 있다. 일 실시 형태는 이 구성에 한정되지 않고, 다른 메모리 장치에 의해 메모리(112)를 구성할 수 있다는 것을 유의한다.

- [0045] 신호 처리 회로(113)는 CPU(111)의 산술 연산 결과인 데이터 신호(연산 데이터 신호)를 변환해서 출력 신호를 생성하는 기능을 갖는다. 신호 처리 회로(113)는 예를 들어, 출력 장치용 신호를 생성하는 기능을 갖는다. 출력 장치의 예들은 디스플레이, 스피커, 및 프린터이다. 대안적으로, 신호 처리 회로(113)는 출력 장치 대신 터치 패널 등의 입력/출력 장치용 신호를 생성할 수 있다.

- [0046] 신호 처리 회로(113)는 예를 들어, 프로세서 및 레지스터를 사용하여 형성된다. 또한, 신호 처리 회로(113)는 신호 처리 회로(113)의 산술 연산에 사용되는 데이터를 저장하는 메모리를 별도로 포함할 수 있다. 일 실시 형태는 이러한 구성에 한정되지 않고, 다른 집적 회로를 사용하여 신호 처리 회로(113)를 형성할 수 있다는 것을 유의한다.

- [0047] 신호 처리 회로(113)에 포함된 레지스터는 예를 들어, CPU(111)의 레지스터에 사용될 수 있는 제1 메모리 회로 및 제2 메모리 회로에 의해 구성된다. 이에 의해, 전원 공급을 정지시키고 재개시킨 후의 신호 처리 회로(113)의 복귀가 빨라질 수 있다. 일 실시 형태는 상기의 구성에 한정되지 않고, 다른 메모리 회로에 의해 레지스터를 구성할 수 있다는 것을 유의한다.

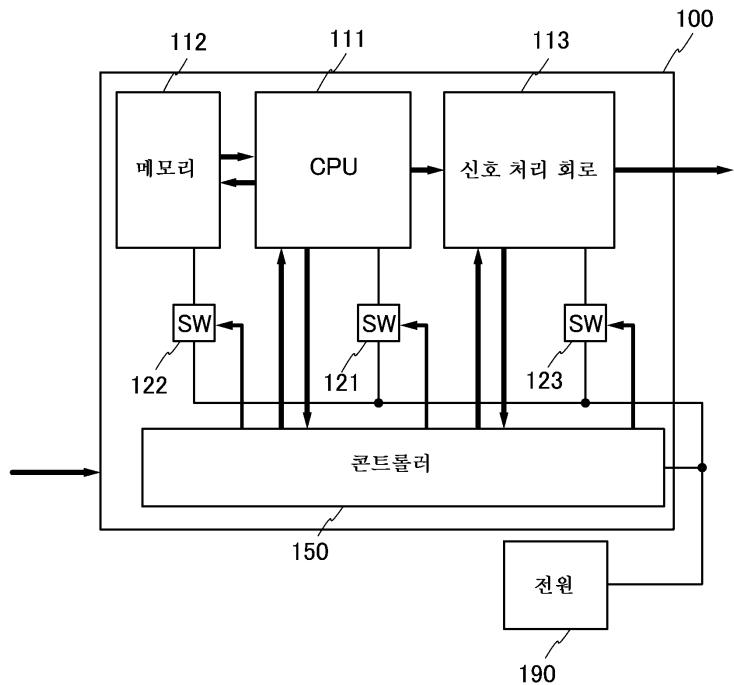

- [0048] 도 2는 반도체 장치(100), 제1 CPU인 CPU(110), 및 전원(190)을 도시한다. 도 2에 도시된 반도체 장치(100)는 제2 CPU인 CPU(111), 메모리(112), 신호 처리 회로(113), 전원 공급 제어 스위치(121 내지 123)를 포함한다. CPU(111), 메모리(112), 및 신호 처리 회로(113)는 버스를 통해 서로 신호의 입출력을 행할 수 있다. 반도체 장치(100)에는 전원(190)으로부터 전원 공급선을 통해 전원 전압이 공급된다. 전원(190)이 이차 전지인 경우, 전원(190)은 반도체 장치(100) 내에 설치될 수 있다.

- [0049] 전원 공급 제어 스위치들(121 내지 123)은 CPU(110)에 의해 제어된다. 전원 공급 제어 스위치들(121 내지 123) 각각은 유선 또는 무선에 의해 CPU(110)로부터 송신된 신호를 사용하여 프로그램에 의해 제어된다.

- [0050] CPU(110)는 반도체 장치(100)에 포함될 수 있다는 것을 유의한다. 즉, CPU(110)는 CPU(111), 메모리(112), 및 신호 처리 회로(113)와 동일한 칩에 설치될 수 있다.

- [0051] CPU(110)는 프로그램 메모리(1100)를 포함한다. 프로그램 메모리(1100)는 전원 공급 제어 스위치들(121 내지 123)을 제어하는 프로그램을 저장한다.

- [0052] 그러나, 일 실시 형태는 이 예에 한정되지 않고, 프로그램 메모리(1100)는 CPU(110) 내부에 설치되는 것 대신에 별도로 설치되고 CPU(110)에 접속될 수 있다.

- [0053] 프로그램 메모리(1100)는 휘발성 메모리 또는 불휘발성 메모리일 수 있다. 프로그램 메모리(1100)가 휘발성 메모리일 경우에는, 반도체 장치(100)의 동작을 개시할 때, 프로그램 메모리(1100)에 프로그램을 기입하기 위한 초기화가 필요하다. 한편, 프로그램 메모리(1100)가 불휘발성 메모리일 경우에는, 미리 프로그램을 저장시켜

둘 수 있다.

[0054] 또한, 프로그램 메모리(1100)는 재기입 가능한 메모리 또는 재기입 불가능한 메모리일 수 있고, 재기입 가능한 메모리인 것이 바람직하다. 이것은 왜냐하면, 프로그램 메모리(1100)로서 재기입 가능한 메모리를 이용함으로써, 예를 들어, 전원 공급 제어 스위치들(121 내지 123)을 제어하는 프로그램이 변경 또는 개선될 수 있게 해주기 때문이다.

[0055] 도 2에 도시된 바와 같이, CPU(110)와 CPU(111)는 유선 또는 무선 통신이 가능한 것이 바람직하다는 것을 유의한다. CPU(110)와 신호 처리 회로(113)도 유선 또는 무선 통신이 가능한 것이 바람직하다.

[0056] 전원 공급 제어 스위치(121)는 CPU(111)에 대한 전원 전압의 공급을 제어하는 기능을 갖는다.

[0057] 전원 공급 제어 스위치(122)는 메모리(112)에 대한 전원 전압의 공급을 제어하는 기능을 갖는다.

[0058] 전원 공급 제어 스위치(123)는 신호 처리 회로(113)에 대한 전원 전압의 공급을 제어하는 기능을 갖는다.

[0059] 전원 공급 제어 스위치들(121 내지 123) 각각은 전계 효과 트랜지스터를 사용하여 형성되고, 전계 효과 트랜지스터는 오프 전류가 낮은 트랜지스터일 수 있다.

[0060] 전원 공급 제어 스위치들(121 내지 123)의 구성의 예에 대해서 도 3을 참조하여 설명할 것이다.

[0061] 도 3에 도시된 전원 공급 제어 스위치는 트랜지스터(21)와 트랜지스터(22)를 포함한다.

[0062] 트랜지스터(21)는 전원(190)과 회로(CPU(111), 메모리(112), 또는 신호 처리 회로(113)) 사이에 설치되고, 그 회로에의 전원 공급은 전원 공급 제어 스위치(121, 122, 또는 123)에 의해 제어된다. 도 1에 도시된 구성에 있어서, 트랜지스터(21)의 게이트에는 콘트롤러(150)(또는 도 2의 구성에서는 CPU(110))로부터 제어 신호 SW\_ON이 공급된다. 트랜지스터(21)는 턴온 또는 턴오프됨으로써, CPU(111), 메모리(112), 또는 신호 처리 회로(113) 등의 회로에 전원 전압을 공급할 지의 여부를 제어한다.

[0063] 트랜지스터(22)의 게이트에는 콘트롤러(150)(또는 도 2의 구성에서는 CPU(110))로부터 제어 신호 SW\_OFF가 공급된다. 트랜지스터(22)는 턴온 또는 턴오프됨으로써, CPU(111), 메모리(112), 또는 신호 처리 회로(113) 등의 회로에 접지 전위(GND)를 공급할 지의 여부를 제어한다.

[0064] 트랜지스터(21)가 온 상태이고 트랜지스터(22)가 오프 상태일 때, 도 3의 전원 공급 제어 스위치는 온 상태로 된다. 트랜지스터(21)가 오프 상태이고 트랜지스터(22)가 온 상태일 때, 도 3의 전원 공급 제어 스위치는 오프 상태로 된다.

[0065] 이상이 도 3에 도시된 전원 공급 제어 스위치의 구성의 예의 설명이다.

[0066] 도 1에 도시된 콘트롤러(150)는 클럭 신호, CPU(111)로부터 입력되는 명령 신호, 및 신호 처리 회로(113)로부터 입력되는 명령 신호 등 전술한 입력 신호에 응답하여, 전원 공급 제어 스위치들(121 내지 123)을 개별적으로 제어하는 기능을 갖는다. 또한, 콘트롤러(150)는 CPU(111) 및 신호 처리 회로(113)의 구동을 제어하는 기능을 갖는다. 콘트롤러(150)에는 전원 전압이 공급된다.

[0067] 도 2에 도시된 CPU(110)는 전원 공급 제어 스위치들(121 내지 123)을 프로그램에 의해 개별적으로 제어한다. CPU(110)에는 전원(190)으로부터 전원 공급 전압이 공급된다. 일 실시 형태는 이 예에 한정되지 않고, CPU(110)는 전원(190)과는 다른 전원으로부터 전원 공급선을 통해 전원 전압이 공급될 수 있다는 것을 유의한다.

[0068] 콘트롤러(150)의 구성의 예에 대해서 도 4를 참조하여 설명한다.

[0069] 도 4에 도시된 콘트롤러(150)는 인터페이스부(151), 클럭 생성부(152), 출력 신호 제어부(153), 및 버퍼부(154)를 포함한다.

[0070] 상기의 입력 신호, CPU(111)로부터 입력되는 명령 신호, 및 신호 처리 회로(113)로부터 입력되는 명령 신호 등의 신호는 인터페이스부(151)를 통해 출력 신호 제어부(153)에 입력된다.

[0071] 클럭 생성부(152)는 입력된 클럭 신호를 사용하여 콘트롤러(150)에서 사용되는 클럭 신호를 생성하고, 생성된 클럭 신호를 (출력 신호 제어부(153)가 포함된) 회로들에 출력한다. 입력된 클럭 신호의 주파수를 분주해서 콘트롤러(150)에서 사용함으로써, 콘트롤러(150)의 전력 소비를 감소시킬 수 있다.

[0072] 출력 신호 제어부(153)는 카운터 회로(155)를 포함한다. 출력 신호 제어부(153)는 카운터 회로(155)에 의해 클

력 신호를 카운트하고, 콘트롤러(150)에 입력되는 신호에 따라 복수의 출력 신호의 (하이/로우) 상태를 설정하는 기능을 갖는다. 복수의 출력 신호의 예들은 전원 공급 제어 스위치들(121 내지 123)을 개별적으로 제어하기 위한 제어 신호들(예를 들어, 제어 신호들 SW\_ON 및 제어 신호들 SW\_OFF), CPU(111)의 동작을 제어하기 위한 신호, 및 신호 처리 회로(113)의 동작을 제어하기 위한 신호이다.

[0073] 출력 신호 제어부(153)에서 생성된 신호들은 버퍼부(154)를 통해 회로들에 출력된다.

[0074] 이상이 도 4에 도시된 콘트롤러의 구성의 예의 설명이다.

[0075] 도 1에 도시된 반도체 장치(100)에 있어서, 전원 공급 제어 스위치들(121 내지 123)이 설치되고 입력 신호, CPU(111)로부터 입력되는 명령 신호, 및 신호 처리 회로(113)로부터 입력되는 명령 신호에 응답하여 콘트롤러(150)에 의해 개별적으로 제어된다.

[0076] 도 2에 도시된 반도체 장치(100)에 있어서, 전원 공급 제어 스위치들(121 내지 123)이 설치되고 CPU(110)에 의해 개별적으로 제어된다.

[0077] CPU(111), 메모리(112), 및 신호 처리 회로(113) 간에 전원 공급의 최적 타이밍이 상이하다. 그 때문에, CPU(111), 메모리(112), 및 신호 처리 회로(113)에 대한 전원 공급의 타이밍을 개별적으로 최적화함으로써, 불필요한 전력의 소비를 감소시킬 수 있다.

[0078] 다음으로, 본 실시 형태의 반도체 장치의 구체예들에 대해서 도 5 내지 도 8을 참조하여 설명할 것이다. 도 1 또는 도 2의 것들과 동일한 참조 번호들로 표기된 회로들에 대해서는 도 1 또는 도 2의 설명을 적절히 원용할 수 있다는 것을 유의한다.

[0079] 도 5에 도시된 반도체 장치는 신호 처리 회로(113)의 일 예인 화상 처리 회로(113A)와, 도 1에 도시된 회로들 외에도, 메모리(114) 및 전원 공급 제어 스위치(124)를 포함한다. CPU(111), 메모리(112), 화상 처리 회로(113A)(신호 처리 회로(113)), 메모리(114), 전원 공급 제어 스위치들(121 내지 124), 및 콘트롤러(150)를 마이크로컴퓨터(100A)로서 기능하는 하나의 칩에 통합한다. 입력 장치(101)로서 터치 패널(171) 및 터치 패널 콘트롤러(172)가 설치될 수 있다. 일 실시 형태는 이러한 구성에 한정되지 않고, 예를 들어, 도 6에 도시된 바와 같이, 입력 장치(101)로서 키보드(173) 및 키보드 콘트롤러(174)가 설치될 수 있다는 것을 유의한다. 또한, 출력 장치(102)로서 디스플레이(181) 및 디스플레이 콘트롤러(182)가 설치될 수 있다. 디스플레이(181)의 예들은 액정 디스플레이 및 일렉트로루미네센스(electroluminescent: EL) 디스플레이이다.

[0080] 도 7에 도시된 반도체 장치는 신호 처리 회로(113)의 일 예인 화상 처리 회로(113A)와, 도 2에 도시된 회로들 외에도, 메모리(114) 및 전원 공급 제어 스위치(124)를 포함한다. 마이크로컴퓨터(100A)는 CPU(111), 메모리(112), 화상 처리 회로(113A)(신호 처리 회로(113)), 메모리(114), 및 전원 공급 제어 스위치들(121 내지 124)을 포함하는 하나의 칩으로 구성된다. 입력 장치(101)로서는 터치 패널(171) 및 터치 패널 콘트롤러(172)가 설치될 수 있다. 일 실시 형태는 이러한 구성에 한정되지 않고, 예를 들어, 입력 장치(101)로서 키보드(173) 및 키보드 콘트롤러(174)가 설치될 수 있다는 것을 유의한다. 또한, 출력 장치(102)로서는 디스플레이(181) 및 디스플레이 콘트롤러(182)가 설치될 수 있다. 디스플레이(181)의 예들은 액정 디스플레이 및 일렉트로루미네센스 디스플레이이다.

[0081] CPU(111)에 포함되는 레지스터(1110)는 제1 메모리 회로 및 제2 메모리 회로를 각각 포함하는 복수의 메모리 회로에 의해 구성된다.

[0082] 메모리(112)로서는, 오프 전류가 낮은 트랜지스터를 각각 포함하는 메모리 셀들을 구비하는 메모리 장치를 사용할 수 있다.

[0083] 화상 처리 회로(113A)는 CPU(111)의 산술 연산에 의해 생성되는 데이터 신호를 변환함으로써 출력 장치에 출력되는 화상 신호를 생성하는 기능을 갖는다.

[0084] 화상 처리 회로(113A)에 포함되는 레지스터(1130)는 예를 들어, 신호 처리 회로(113)에 사용될 수 있는 메모리 회로를 사용하여 형성된다.

[0085] 메모리(114)에서, 화상 처리 회로(113A)의 변환 처리에 의해 데이터의 판독 또는 기입이 행해진다. 메모리(114)에는 루업 테이블(lookup table: LUT)이 될 데이터가 저장된다. 메모리(114)는 예를 들어, ROM 및 RAM 중 적어도 하나에 의해 구성된다.

[0086] 메모리(114)는 예를 들어, 오프 전류가 낮은 트랜지스터를 각각 포함하는 메모리 셀들을 구비하는 메모리 장치

에 의해 구성된다.

[0087] 전원 공급 제어 스위치(124)는 메모리(114)에 대한 전원 전압의 공급을 제어하는 기능을 갖는다.

[0088] 콘트롤러(150)는 (입력 장치(101)로부터의 신호가 포함된) 입력 신호, CPU(111)로부터 입력되는 명령 신호, 및 신호 처리 회로(113)로부터 입력되는 명령 신호에 응답하여 전원 공급 제어 스위치들(121 내지 124)을 개별적으로 제어한다.

[0089] 도 7에 있어서, CPU(110)는 전원 공급 제어 스위치들(121 내지 124)을 프로그램을 사용하여 개별적으로 제어한다.

[0090] 전원 공급 제어 스위치(124)는 전계 효과 트랜지스터를 사용하여 형성된다. 예를 들어, 전원 공급 제어 스위치(124)는 도 3에 도시된 구성을 가질 수 있다.

[0091] 도 5 및 도 6에 도시된 반도체 장치들의 예들에 있어서, 전원 공급 제어 스위치들(121 내지 124)이 설치되고, 입력 장치(101)로부터의 입력 신호, CPU(111)로부터 입력되는 명령 신호, 및 신호 처리 회로(113)로부터 입력되는 명령 신호에 응답하여 콘트롤러(150)에 의해 개별적으로 제어된다. CPU(111)를 복수의 블록으로 나누고, 전원 공급 제어 스위치(121)와는 다른 전원 공급 제어 스위치를 설치하고, 콘트롤러(150)에 의해 복수의 전원 공급 제어 스위치를 개별적으로 제어하는 것이 가능하다는 것을 유의한다. 또한, 화상 처리 회로(113A)를 복수의 블록으로 나누고, 전원 공급 제어 스위치(123)와는 다른 전원 공급 제어 스위치를 설치하고, 콘트롤러(150)에 의해 복수의 전원 공급 제어 스위치를 개별적으로 제어하는 것이 가능하다.

[0092] 도 7에 도시된 반도체 장치의 예에서는, 전원 공급 제어 스위치들(121 내지 124)이 설치되고, CPU(110)는 프로그램을 사용하여 전원 공급 제어 스위치들(121 내지 124)을 개별적으로 제어한다. CPU(111)를 복수의 블록으로 나누고, 전원 공급 제어 스위치(121)와는 다른 전원 공급 제어 스위치를 설치하고, CPU(110)에 의해 프로그램을 사용하여 복수의 전원 공급 제어 스위치를 개별적으로 제어하는 것이 가능하다는 것을 유의한다. 또한, 화상 처리 회로(113A)를 복수의 블록으로 나누고, 전원 공급 제어 스위치(123)와는 다른 전원 공급 제어 스위치를 설치하고, CPU(110)에 의해 프로그램을 사용하여 복수의 전원 공급 제어 스위치를 개별적으로 제어하는 것이 가능하다.

[0093] 즉, 하나의 회로에 대해 그것에의 전원 공급을 제어하기 위해 복수의 전원 공급 제어 스위치가 설치될 수 있다.

[0094] 다음으로, 본 실시 형태의 반도체 장치의 구동 방법의 예로서, 도 5 및 도 7에 도시된 반도체 장치들의 전원 공급 방법의 예에 대해서 도 8의 타이밍 차트를 참조하여 설명할 것이다.

[0095] 도 8에 도시된 바와 같이, 예를 들어, 시각 T1에 터치 패널(171)을 조작하면, 터치 패널 콘트롤러(172)의 출력 신호(OUT172)의 데이터(OUT172의 펄스들)가 콘트롤러(150)(또는 도 7의 구성에서는 CPU(110))에 입력된다.

[0096] 이 경우에, 콘트롤러(150)(또는 도 7의 구성의 경우에는 CPU(110))는 시각 T2에 전원 공급 제어 스위치(121)를 터온(차트에서 ON이 온 상태를 나타냄)해서 CPU(111)에 대한 전원 전압의 공급을 개시하고, 시각 T3에 전원 공급 제어 스위치(122)를 터온해서 메모리(112)에 대한 전원 전압의 공급을 개시한다. 예를 들어, 콘트롤러(150)로부터 출력되는 제어 신호들(제어 신호들 SW\_ON 및 제어 신호들 SW\_OFF)의 레벨들이, 전원 공급 제어 스위치들(121, 122)을 터온하도록 설정된다. CPU(111) 및 메모리(112)에 대한 전원 전압의 공급을 동시에 개시할 수 있지만, 전원 공급 제어 스위치들(121, 122)을 개별적으로 제어함으로써, CPU(111)에 대해 전원 전압의 공급을 개시한 후, 메모리(112)에 대한 액세스가 필요해질 때까지는 메모리(112)에 대한 전원 전압의 공급을 개시하지 않도록 하여, 전력 소비를 더 감소시킬 수 있다.

[0097] CPU(111) 및 메모리(112)에 대한 전원 전압의 공급을 개시한 후에, 지연시킨 터치 패널 콘트롤러(172)의 출력 신호(OUT172)를 CPU(111)에 입력한다. 출력 신호(OUT172)는 지연 회로에 의해 지연될 수 있다는 것을 유의한다.

[0098] 이때, CPU(111)는, 터치 패널 콘트롤러(172)의 출력 신호(OUT172)를 포함하는 입력 신호(IN111)의 데이터(IN111의 펄스들)와 메모리(112)의 데이터에 기초하여 산술 연산을 행한다. 그 후, 시각 T4에 전원 공급 제어 스위치(123)를 터온해서 화상 처리 회로(113A)에 대한 전원 전압의 공급을 개시하고, 시각 T5에 전원 공급 제어 스위치(124)를 터온해서 메모리(114)에 대한 전원 전압의 공급을 개시한다. 예를 들어, CPU(111)로부터의 명령 신호는, 콘트롤러(150)로부터 출력되는 제어 신호들(제어 신호들 SW\_ON 및 제어 신호들 SW\_OFF)의 레벨들을, 전원 공급 제어 스위치들(123, 124)이 터온되도록 설정한다. 일 실시 형태는 이러한 구성에 한정되지 않고, 터치 패널 콘트롤러(172)의 출력 신호(OUT172)는 콘트롤러(150)로부터 출력되는 제어 신호들의 레벨들을, 전원 공급

제어 스위치들(123, 124)이 턴온되도록 설정할 수 있다는 것을 유의한다. 화상 처리 회로(113A) 및 메모리(114)에 대한 전원 전압의 공급을 동시에 개시할 수 있지만, 전원 공급 제어 스위치들(123, 124)을 개별적으로 제어함으로써, 화상 처리 회로(113A)에 대해 전원 전압의 공급을 개시한 후, 메모리(114)에 대한 액세스가 필요해질 때까지는 메모리(114)에 대한 전원 전압의 공급을 개시하지 않도록 하여, 전력 소비를 더 감소시킬 수 있다.

[0099] 그 후, CPU(111)는 산술 연산 결과를 나타내는 데이터(OUT111의 펠스들)를 포함하는 데이터 신호(OUT111)를 화상 처리 회로(113A)에 출력한다. 화상 처리 회로(113A)에 대한 데이터 신호의 출력이 끝나면, 시각 T6에 전원 공급 제어 스위치(122)를 턴오프(차트에서 OFF가 오프 상태를 나타냄)해서 메모리(112)에 대한 전원 전압의 공급을 정지하고, 시각 T7에 전원 공급 제어 스위치(121)를 턴오프로 해서 CPU(111)에 대한 전원 전압의 공급을 정지한다. 예를 들어, CPU(111)로부터의 명령 신호는 콘트롤러(150)로부터 출력되는 제어 신호들의 레벨들을, 전원 공급 제어 스위치들(121 및 122)이 턴오프되도록 설정한다. 일 실시 형태는 이러한 구성에 한정되지 않고, 화상 처리 회로(113A)로부터의 명령 신호에 의해 콘트롤러(150)로부터 출력되는 제어 신호들의 레벨들을, 전원 공급 제어 스위치들(121 및 122)이 턴오프되도록 설정할 수 있다는 것을 유의한다. CPU(111) 및 메모리(112)에 대한 전원 전압의 공급을 동시에 정지할 수 있지만, 다음의 방식으로, 즉, 전원 공급 제어 스위치들(121 및 122)을 개별적으로 제어하여, CPU(111)에 대한 전원 전압이 공급되고 있는 동안, 메모리(112)에 대한 액세스가 불필요하게 될 때 메모리(112)에 대한 전원 전압의 공급을 정지시킴으로써, 전력 소비를 더 감소시킬 수 있다. 또한, CPU(111)에 대한 전원 전압의 공급을 정지하기 직전에, 레지스터(1110)의 복수의 메모리 회로에 포함된 제2 메모리 회로들에 데이터를 저장시키고, 그 후, 전원 전압의 공급이 재개된 직후에, 제2 메모리 회로들에 저장된 데이터를 제1 메모리 회로들에 입력하는 경우, 전원 전압의 공급의 재개 후의 CPU(111)의 복귀가 빨라질 수 있다.

[0100] 화상 처리 회로(113A)는 입력된 CPU(111)의 출력 신호(OUT111)를 변환해서 디스플레이 콘트롤러(182)에 출력되는 신호를 생성한다. 변환 처리 후, 생성된 데이터(OUT113A의 펠스들)를 포함하는 신호(OUT113A)를 디스플레이 콘트롤러(182)에 출력하고, 시각 T8에 전원 공급 제어 스위치(124)를 턴오프해서 메모리(114)에 대한 전원 전압의 공급을 정지하고, 시각 T9에 전원 공급 제어 스위치(123)를 턴오프해서 화상 처리 회로(113A)에 대한 전원 전압의 공급을 정지한다. 예를 들어, 화상 처리 회로(113A)로부터의 명령 신호는, 콘트롤러(150)로부터 출력되는 제어 신호(제어 신호들 SW\_ON 및 제어 신호들 SW\_OFF)의 레벨들을, 전원 공급 제어 스위치들(123, 124)이 턴오프되도록 설정한다. 화상 처리 회로(113A) 및 메모리(114)에 대한 전원 전압의 공급을 동시에 정지할 수 있지만, 다음의 방식으로, 즉, 전원 공급 제어 스위치들(123, 124)을 개별적으로 제어하여, 화상 처리 회로(113A)에 대한 전원 전압이 공급되고 있는 동안, 메모리(114)에 대한 액세스가 불필요하게 될 때, 메모리(114)에 대한 전원 전압의 공급을 정지시킴으로써, 전력 소비를 더 감소시킬 수 있다. 또한, 화상 처리 회로(113A)에 대한 전원 전압의 공급을 정지하기 직전에, 레지스터(1130)의 제2 메모리 회로에 데이터를 저장시키고, 그 후, 전원 전압의 공급이 재개된 직후에, 제2 메모리 회로에 저장된 데이터를 제1 메모리 회로에 입력하는 경우, 전원 전압의 공급의 재개 후의 화상 처리 회로(113A)의 복귀가 빨라질 수 있다.

[0101] 이상이 도 5 및 도 7에 도시된 반도체 장치들의 전원 공급 방법의 예이다.

[0102] 도 1 내지 도 8을 참조하여 설명한 바와 같이, 본 실시 형태의 일 예에 따른 반도체 장치에 있어서, 각 회로마다 전원 공급 제어 스위치(제1 내지 제3 전원 공급 제어 스위치)를 설치하고, 입력 신호, CPU(제2 CPU)로부터 입력되는 명령 신호, 신호 처리 회로로부터 입력되는 명령 신호에 따라 콘트롤러 또는 제1 CPU로서 기능하는 CPU에 의해 복수의 전원 공급 제어 스위치를 개별적으로 제어한다.

[0103] 회로들(CPU, 메모리, 및 신호 처리 회로) 간에 있어서 전원 공급의 최적 타이밍이 상이하기 때문에, 회로들에 대한 전원 공급의 타이밍을 개별적으로 최적화함으로써, 불필요한 전력의 소비를 감소시킬 수 있다.

[0104] 예를 들어, CPU에 대한 전원 전압의 공급이 개시된 후, CPU의 산술 연산 결과를 나타내는 데이터가 신호 처리 회로에 입력되기 전에, 신호 처리 회로에 대한 전원 전압의 공급이 개시되도록 제3 전원 공급 제어 스위치를 제어함으로써, 전력 소비를 감소시킬 수 있다.

[0105] 또한, CPU의 산술 연산 결과를 나타내는 데이터가 신호 처리 회로에 입력된 후, 그 산술 연산 결과를 나타내는 데이터의 변환 데이터가 출력 신호로서 신호 처리 회로로부터 출력되기 전에, CPU에 대한 전원 전압의 공급이 정지되도록 제1 전원 공급 제어 스위치를 제어함으로써, 전력 소비를 감소시킬 수 있다.

[0106] (실시 형태 2)

- [0107] 본 실시 형태에서는, 실시 형태 1에 있어서의 반도체 장치의 메모리로서 이용될 수 있는 메모리 장치의 예들에 대해서 설명한다.

- [0108] 본 실시 형태의 메모리 장치의 예는 i행 ( $i$ 는 2 이상의 자연수) 및 j열( $j$ 는 자연수)의 매트릭스로 배열된 복수의 메모리 셀을 포함한 메모리 셀 어레이를 포함한다. 메모리 셀은 실시 형태 1의 반도체 장치에 있어서의 메모리 회로에 대응한다.

- [0109] 본 실시 형태의 메모리 장치에 있어서의 메모리 셀 어레이의 예에 대해서 도 9를 참조하여 설명한다.

- [0110] 도 9에 도시된 메모리 셀 어레이에는 i행 및 j열의 매트릭스로 배열된 복수의 메모리 셀(200), 제1 내지 제j 비트선 BL, 제1 내지 제i 워드선 WL, 제1 내지 제i 용량선 CL, 및 소정의 전위가 인가되는 소스선 SL을 포함한다.

- [0111] 도 9에 도시된 메모리 셀 어레이에 있어서, 제M 행( $M$ 은 1 내지  $i$ 의 자연수임) 제N 열( $N$ 은 1 내지  $j$ 의 자연수임)의 메모리 셀(200), 즉, 메모리 셀(200( $M, N$ ))은 트랜지스터(211( $M, N$ )), 트랜지스터(212( $M, N$ )), 및 용량소자(213( $M, N$ ))를 포함한다.

- [0112] 트랜지스터(211( $M, N$ ))의 소스 및 드레인 중 하나는 비트선 BL\_N에 전기적으로 접속된다. 트랜지스터(211( $M, N$ ))의 게이트는 워드선 WL\_M에 전기적으로 접속된다.

- [0113] 트랜지스터(211( $M, N$ ))는 n 채널형 트랜지스터이고, 데이터의 기입 및 유지를 제어한다.

- [0114] 트랜지스터(211( $M, N$ ))로서, 실시 형태 1에 기재된 오프 전류가 낮은 트랜지스터를 사용할 수 있다.

- [0115] 트랜지스터(212( $M, N$ ))는 p 채널형 트랜지스터이다. 트랜지스터(212( $M, N$ ))의 소스 및 드레인 중 한쪽은 비트선 BL\_N에 전기적으로 접속된다. 트랜지스터(212( $M, N$ ))의 소스 및 드레인 중 다른 쪽은 소스선 SL에 전기적으로 접속된다. 트랜지스터(212( $M, N$ ))의 게이트는 트랜지스터(211( $M, N$ ))의 소스 및 드레인 중 다른 쪽에 전기적으로 접속된다.

- [0116] 트랜지스터(212( $M, N$ ))는 출력될 데이터의 전위를 설정하는 출력 트랜지스터로서 기능한다.

- [0117] 용량 소자(213( $M, N$ ))의 한 쌍의 전극 중 한쪽은 트랜지스터(211( $M, N$ ))의 소스 및 드레인 중 다른 쪽에 전기적으로 접속되고, 다른 쪽은 용량선 CL\_M에 전기적으로 접속된다.

- [0118] 용량 소자(213( $M, N$ ))는 데이터를 유지하는 저장 용량 소자로서 기능한다.

- [0119] 이상이 도 9에 도시된 메모리 셀 어레이의 구성의 예에 대한 설명이다.

- [0120] 트랜지스터(212)는 반드시 메모리 셀에 설치되지 않아도 된다는 것을 유의한다. 예를 들어, 메모리 셀은 도 10에 도시된 구성을 가질 수 있고, 이 경우에, 용량선들 CL은 소스선 SL의 대체물로서 기능하도록 한 개의 선으로 통합될 수 있다.

- [0121] 이어서, 도 9에 도시된 메모리 셀 어레이를 포함하는 메모리 장치의 구동 방법의 예에 대해서 도 11의 (a) 및 도 11의 (b)를 참조하여 설명한다. 도 11의 (a) 및 도 11의 (b)는 메모리 장치의 구동 방법의 예를 설명하기 위한 타이밍 차트이다. 여기에서는, 일 예로서 제M 행의 메모리 셀들(200)에 순차적으로 데이터를 기입하고, 그 후 기입된 데이터를 판독하는 경우에 대해서 설명하지만, 이 경우에 한정되지는 않는다. 예를 들어, 판독 동작을 행하지 않고 기입 동작을 반복적으로 행할 수 있다.

- [0122] 먼저, 제M 행의 메모리 셀들(200)에 데이터를 기입하기 위해("기입"을 위해), 도 11의 (a)에 도시된 바와 같이, 제M 워드선 WL\_M의 전위를 VH로 설정하고, 그 이외의 모든 워드선들 WL\_other의 전위를 VL로 설정한다.

- [0123] VH는 기준 전위(예를 들어, 접지 전위)보다 높은 전위이고, 예를 들어, 고 전원 전위라는 것을 유의한다. 또한, VL은 기준 전위 이하의 전위, 예를 들어, 저 전원 전위이다.

- [0124] 이때, 제M 행의 메모리 셀들(200) 각각에 있어서, 트랜지스터(211)가 턴온되어, 용량 소자(213)의 한 쌍의 전극 중 한쪽의 전위가 해당 비트선 BL의 전위와 동등하게 된다.

- [0125] 그 후, 트랜지스터(211)가 턴오프되고, 트랜지스터(212)의 게이트는 부유 상태로 되어, 트랜지스터(212)의 게이트 전위가 유지된다.

- [0126] 상기의 동작을 행마다 행함으로써, 모든 메모리 셀들(200)에 데이터를 기입할 수 있다.

- [0127] 또한, 제M 행의 메모리 셀들(200)로부터 데이터를 판독하기 위해("판독"을 위해), 도 11의 (b)에 도시된 바와

같이, 모든 워드선들 WL의 전위를 VL로 설정하고, 제M 용량선 CL\_M의 전위를 VL로 설정하고, 그 이외의 모든 용량선들 CL\_other의 전위를 VH로 설정한다.

[0128] 제M 행의 메모리 셀들(200) 각각에 있어서, 트랜지스터(212)의 소스와 드레인 사이의 저항은 트랜지스터(212)의 게이트 전압에 따라 결정된다. 또한, 트랜지스터(212)의 소스와 드레인 사이에 흐르는 전류의 양에 대응하는 전위를 데이터로서 메모리 셀(200)로부터 판독할 수 있다.

[0129] 상기의 동작을 행마다 반복적으로 행함으로써, 모든 메모리 셀들(200)로부터 데이터를 판독할 수 있다. 이상이 도 9에 도시된 반도체 장치의 구동 방법의 예의 설명이다.

[0130] 도 9, 도 10, 도 11의 (a), 및 도 11의 (b)를 참조하여 설명한 바와 같이, 본 실시 형태의 일 예에 따른 반도체 장치에서는, 데이터의 기입 및 유지를 제어하는 트랜지스터로서 오프 전류가 낮은 전계 효과 트랜지스터를 사용함으로써 데이터의 유지 시간을 연장할 수 있다. 따라서, 전원 전압의 공급을 정지한 때에도 데이터를 유지할 수 있다.

[0131] (실시 형태 3)

[0132] 본 실시 형태에서는, 실시 형태 1의 반도체 장치 내의 레지스터에 포함된 메모리 회로의 예에 대해서 설명한다.

[0133] 본 실시 형태의 메모리 회로의 구성의 예에 대해서 도 12의 (a) 및 도 12의 (b)를 참조하여 설명한다.

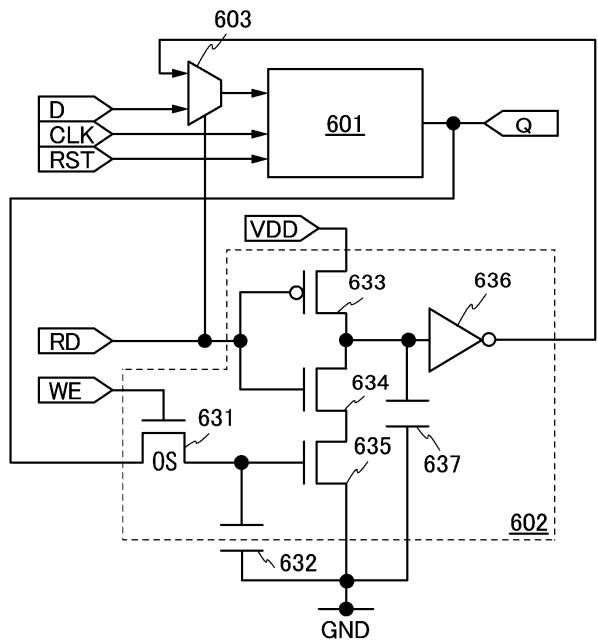

[0134] 도 12의 (a)에 도시된 바와 같이, 본 실시 형태의 메모리 회로는 플립 플롭(FF로 표기됨)(601), 메모리 회로(NVM)(602), 및 셀렉터(SEL)(603)를 포함한다.

[0135] 플립 플롭(601)에는 리셋 신호 RST, 클럭 신호 CLK, 및 셀렉터(603)에 의해 선택된 데이터 신호 D가 공급된다. 리셋 신호 RST 및 클럭 신호 CLK는 예를 들어, 실시 형태 1에 나타낸 반도체 장치의 콘트롤러(150)로부터 입력된다. 플립 플롭(601)은 클럭 신호 CLK에 응답하여 입력되는 데이터 신호 D의 데이터를 유지하고, 그 데이터를 데이터 신호 Q로서 출력하는 기능을 갖는다.

[0136] 메모리 회로(602)에는 기입 제어 신호 WE, 판독 제어 신호 RD, 및 셀렉터(603)에 의해 선택된 데이터 신호가 공급된다. 기입 제어 신호 WE 및 판독 제어 신호 RD는 예를 들어, 실시 형태 1에 나타낸 반도체 장치의 콘트롤러(150)로부터 입력된다. 도 2의 구성에서는, CPU(110)로부터의 명령에 의해, 반도체 장치에 설치된 신호 생성 회로로부터 기입 제어 신호 WE 및 판독 제어 신호 RD가 출력된다.

[0137] 메모리 회로(602)는 기입 제어 신호 WE에 따라, 입력되는 데이터 신호의 데이터를 저장하고, 저장된 데이터를 판독 제어 신호 RD에 따라, 데이터 신호로서 출력하는 기능을 갖는다.

[0138] 셀렉터(603)에는 제1 단자를 통해 판독 제어 신호 RD가 공급되고, 제2 단자를 통해 데이터 신호 D가 공급되고, 제3 단자를 통해 메모리 회로(602)로부터 출력되는 데이터 신호 D\_NVM이 공급된다.

[0139] 셀렉터(603)는 판독 제어 신호 RD에 따라, 데이터 신호 D 또는 데이터 신호 D\_NVM 중 어느 것을 제4 단자를 통해 출력할지 선택하는 기능을 갖는다.

[0140] 이어서, 메모리 회로(602)의 구성의 예에 대해서 도 12의 (b)를 참조하여 설명한다.

[0141] 도 12의 (b)에 도시된 바와 같이, 메모리 회로(602)는 데이터 유지부(621) 및 데이터 판독부(622)를 포함한다.

[0142] 데이터 유지부(621)는 트랜지스터(631) 및 용량 소자(632)를 포함한다.

[0143] 트랜지스터(631)는 n 채널형 트랜지스터이다. 트랜지스터(631)의 소스 및 드레인 중 한쪽은 셀렉터(603)의 출력 단자(제4 단자)에 전기적으로 접속된다. 트랜지스터(631)는 기입 제어 신호 WE에 따라 셀렉터(603)로부터 입력되는 데이터 신호의 유지를 제어하는 기능을 갖는다.

[0144] 트랜지스터(631)로서는, 실시 형태 1에 나타낸 오프 전류가 낮은 트랜지스터를 사용할 수 있다.

[0145] 용량 소자(632)의 한 쌍의 전극 중 한쪽은 트랜지스터(631)의 소스 및 드레인 중 다른 쪽에 전기적으로 접속되고, 다른 쪽에는 접지 전위(GND)가 공급된다. 용량 소자(632)는 입력되는 데이터 신호의 데이터 D\_HLD에 기초하는 전하를 유지하는 기능을 갖는다. 트랜지스터(631)의 오프 전류가 매우 낮기 때문에, 전원 전압의 공급이 정지될 때에도 용량 소자(632)의 전하는 유지되고, 따라서 데이터 D\_HLD가 유지된다.

[0146] 데이터 판독부(622)는 트랜지스터(633), 트랜지스터(634), 트랜지스터(635), 및 인버터(636)를 포함한다.

- [0147] 트랜지스터(633)는 p 채널형 트랜지스터이다. 트랜지스터(633)의 소스 및 드레인 중 한쪽에는 전원 전위(VDD)가 공급된다. 트랜지스터(633)의 게이트에는 판독 제어 신호 RD가 공급된다. 전원 전위와 접지 전위 간의 차가 전원 전압 PWR이 된다.

- [0148] 트랜지스터(634)는 n 채널형 트랜지스터이다. 트랜지스터(634)의 소스 및 드레인 중 한쪽은 트랜지스터(633)의 소스 및 드레인 중 다른 쪽에 전기적으로 접속된다. 트랜지스터(634)의 게이트에는 판독 제어 신호 RD가 공급된다.

- [0149] 트랜지스터(635)는 n 채널형 트랜지스터이다. 트랜지스터(635)의 소스 및 드레인 중 한쪽은 트랜지스터(634)의 소스 및 드레인 중 다른 쪽에 전기적으로 접속되고, 다른 쪽에는 접지 전위가 공급된다. 트랜지스터(635)의 게이트 전위는 데이터 D\_HLD가 된다.

- [0150] 인버터(636)의 입력 단자는 트랜지스터(633)의 소스 및 드레인 중 다른 쪽에 전기적으로 접속된다. 인버터(636)의 출력 단자는 셀렉터(603)의 입력 단자(제3 단자)에 전기적으로 접속된다. 인버터(636)의 출력 신호는 데이터 신호 D\_NVM이 된다.

- [0151] 이어서, 도 12의 (a)에 나타낸 메모리 회로의 구동 방법의 예에 대해서 도 13의 타이밍 차트를 참조하여 설명한다.

- [0152] 먼저, 통상 동작 기간인 기간 T11에 있어서, 전원 전압 PWR, 리셋 신호 RST, 및 클럭 신호 CLK는 메모리 회로에 공급된다. 이때, 셀렉터(603)는 데이터 신호 D의 데이터를 플립 플롭(601)에 출력한다. 플립 플롭(601)은 클럭 신호 CLK에 따라 입력되는 데이터 신호 D의 데이터를 유지한다.

- [0153] 이어서, 전원 전압 PWR의 공급을 정지하기 직전에 제공되는 백업 기간인 기간 T12에 있어서, 기입 제어 신호 WE의 펄스에 따라 메모리 회로(602)에 데이터 신호 D의 데이터를 저장시키고, 메모리 회로(602)는 그 데이터를 데이터 D\_HLD로서 유지한다. 그 후, 메모리 회로에 대한 클럭 신호 CLK의 공급을 정지하고, 그 후, 메모리 회로에 대한 리셋 신호 RST의 공급을 정지한다.

- [0154] 이어서, 전원 정지 기간인 기간 T13에 있어서, 메모리 회로에 대한 전원 전압 PWR의 공급을 정지한다. 이 기간 동안, 메모리 회로(602)에 있어서, 트랜지스터(631)의 오프 전류가 낮기 때문에, 데이터 D\_HLD의 값이 유지된다.

- [0155] 다음에, 통상 동작 기간 직전에 배치되는 리커버리 기간인 기간 T14에 있어서, 메모리 회로에 대한 전원 전압 PWR의 공급을 재개하고, 그 후 클럭 신호 CLK의 공급을 재개하고, 그 후 리셋 신호 RST의 공급을 재개한다. 또한, 판독 제어 신호 RD의 펄스에 따라 메모리 회로(602)의 데이터 판독부(622)로부터 데이터 D\_HLD에 대응하는 값을 갖는 데이터 신호 D\_NVM이 셀렉터(603)에 출력된다. 셀렉터(603)는 판독 제어 신호 RD의 펄스에 따라 데이터 신호 D\_NVM을 플립 플롭(601)에 입력한다. 이에 의해, 전원 정지 기간의 직전 상태로 플립 플롭(601)을 복귀시킬 수 있다.

- [0156] 그 후, 통상 동작 기간인 기간 T15에 있어서, 다시 플립 플롭(601)의 통상 동작을 행한다.

- [0157] 이상이 메모리 회로의 구동 방법의 예이다.

- [0158] 도 12의 (a) 및 도 12의 (b) 및 도 13을 참조하여 설명한 바와 같이, 본 실시 형태의 메모리 회로는 제1 메모리 회로(플립 플롭), 및 오프 전류가 낮은 트랜지스터를 포함하는 제2 메모리 회로를 포함한다. 전원 공급을 정지하기 직전에 제2 메모리 회로에 데이터를 저장시키고, 그 후 전원 공급을 재개시킬 때 그 데이터를 제1 메모리 회로에 입력함으로써, 제1 메모리 회로를 전원 공급을 정지하기 직전의 상태로 복귀시킬 수 있다. 이와 같이 하여, 전원 공급을 재개시킨 후의 메모리 회로의 복귀가 빨라질 수 있다.

- [0159] (실시 형태 4)

- [0160] 본 실시 형태에서는 본 발명의 일 실시 형태인 반도체 장치의 구조의 예에 대해서 설명한다.

- [0161] 먼저, 본 발명의 일 실시 형태인 반도체 장치에 이용될 수 있는 트랜지스터의 구조의 예들에 대해서 도 14의 (a) 및 도 14의 (b)의 단면 모식도들을 참조하여 설명한다. 또한, 도 14의 (a) 및 도 14의 (b)에 도시된 구성 요소들은 실제의 치수와 상이한 경우들이 있다는 것을 유의한다.

- [0162] 도 14의 (a)에 도시된 트랜지스터는 반도체층(711), 절연층(714), 도전층(715), 절연층들(716a, 716b), 절연층(717), 도전층들(718a, 718b), 및 절연층(719)을 포함한다.

- [0163] 반도체층(711)은 절연층(701)을 개재해서 소자 형성층(700) 위에 설치된다. 반도체층(711)은 반드시 절연층(701) 위에 설치될 필요는 없고, 소자 형성층(700) 위에 직접 설치되어도 된다는 것을 유의한다.

- [0164] 반도체층(711)은, 이격되어 있으며 도편트가 첨가된 영역들(712a, 712b), 및 영역들(712a, 712b) 사이의 채널 형성 영역(713)을 포함한다.

- [0165] 절연층(714)은 반도체층(711)의 일부 위에 설치된다.

- [0166] 도전층(715)은 절연층(714)을 개재해서 반도체층(711)에 중첩하도록 설치된다.

- [0167] 절연층(716a)은 도전층(715)의 한 쪽의 측면 중 한쪽에 접해서 설치되고, 절연층(716b)은 그 한 쪽의 측면 중 다른 쪽에 접해서 설치된다.

- [0168] 절연층(717)은 도전층(715) 위에 설치된다.

- [0169] 도전층(718a)은 영역(712a)에 접해서 설치되고, 도전층(718b)은 영역(712b)에 접해서 설치된다. 도전층(718a)은 절연층(716a)의 측면에 접하고, 도전층(718b)은 절연층(716b)의 측면에 접한다.

- [0170] 절연층(719)은 도전층들(718a, 718b) 위에 설치된다.

- [0171] 도전층들(718a, 718b) 및 절연층(719)은 예를 들어, 도전막과 절연층의 적층에 대하여 평탄화 처리(예를 들어, CMP 처리)를 행함으로써 형성된다.

- [0172] 도 14의 (b)에 도시된 트랜지스터는 도전층(751), 절연층(752), 절연층(753), 반도체층(754), 도전층들(755a, 755b), 도전층들(756a, 756b), 및 절연층(757)을 포함한다.

- [0173] 도전층(751)은 소자 형성층(750) 위에 설치된다.

- [0174] 절연층(752)은 소자 형성층(750) 위에 설치된다. 절연층(752) 및 도전층(751)의 표면들은 평탄한 것이 바람직하다.

- [0175] 도전층(751) 및 절연층(752)은 예를 들어, 도전막과 절연층의 적층에 대하여 평탄화 처리(예를 들어, CMP 처리)를 행함으로써 형성된다.

- [0176] 절연층(753)은 도전층(751) 및 절연층(752) 위에 설치된다.

- [0177] 반도체층(754)은 절연층(753)을 개재해서 도전층(751)에 중첩하도록 설치된다.

- [0178] 도전층들(755a, 755b)은 서로 이격되고, 반도체층(754)에 접해서 설치된다. 도전층들(755a, 755b) 간의 간격은 트랜지스터의 채널 길이에 상당하고, 예를 들어, 50nm 미만인 것이 바람직하다. 예를 들어, 전자빔으로 노광해서 형성한 레지스트 마스크를 사용하여 도전막의 일부를 에칭함으로써, 도전층들(755a, 755b) 간의 간격을 50nm 미만으로 할 수 있다. 또한, 예를 들어, 도전층들(755a, 755b) 간의 간격은 도전층들(756a, 756b) 간의 간격보다 짧은 것이 바람직하다.

- [0179] 도전층(756a)은 도전층(755a)의 일부 위에 접해서 설치되고, 도전층(756b)은 도전층(755b)의 일부 위에 접해서 설치된다. 도전층들(756a, 756b)의 전기 저항은 도전층들(755a, 755b)의 전기 저항보다 낮은 것이 바람직하다.

- [0180] 절연층(757)은 반도체층(754)의 상면을 덮도록 반도체층(754) 위에 설치된다.

- [0181] 구성 요소들에 대해서 하기에서 더 설명한다. 구성 요소들 각각은 단층으로 한정되지 않고, 층들의 적층이어도 된다.

- [0182] 절연층(701)은 하지층이다. 절연층(701)은 예를 들어, 산화 실리콘, 질화 실리콘, 산화질화 실리콘, 질화 산화 실리콘, 산화 알루미늄, 질화 알루미늄, 산화질화 알루미늄, 질화 산화 알루미늄, 또는 산화 하프늄 등의 재료를 포함하는 층일 수 있다.

- [0183] 절연층(752)은 절연층(701)과 마찬가지의 재료를 포함하는 층일 수 있다.

- [0184] 반도체층들(711, 754) 각각은 트랜지스터의 채널이 형성되는 층(채널 형성층이라고도 칭함)으로서 기능한다. 여기서, 도 14의 (a)의 반도체층(711) 및 도 14의 (b)의 반도체층(754)에 대해서 설명한다.

- [0185] 반도체층들(711, 754)로서는 예를 들어, 산화물 반도체층을 사용할 수 있다.

- [0186] 산화물 반도체층은 단결정, 다결정(폴리크리스탈이라고도 칭함), 또는 비정질 상태 등을 취한다. 대안적으로,

산화물 반도체층은 비정질층과, 결정을 포함하는 층과의 적층이어도 된다.

[0187] 산화물 반도체의 예는 인듐 및 갈륨 중 적어도 하나와 아연을 포함하는 금속 산화물, 및 그 금속 산화물에 포함되는 갈륨의 일부 또는 전부가 다른 금속 원소로 대체되는 금속 산화물이다.

[0188] 금속 산화물로서는 예를 들어, In계 금속 산화물, Zn계 금속 산화물, In-Zn계 금속 산화물, 또는 In-Ga-Zn계 금속 산화물을 사용할 수 있다. 대안적으로, In-Ga-Zn계 금속 산화물 내의 Ga(갈륨)의 일부 또는 전부 대신에 다른 금속 원소를 포함하는 금속 산화물을 사용해도 된다.

[0189] 상기의 다른 금속 원소로서는 예를 들어, 갈륨보다 더 많은 산소 원자와 결합이 가능한 금속 원소를 사용할 수 있고, 구체적으로는 예를 들어, 티타늄, 지르코늄, 하프늄, 게르마늄, 및 주석 중 하나 이상의 원소를 사용할 수 있다. 대안적으로, 상기의 다른 금속 원소로서는 란탄, 세륨, 프라세오디뮴, 네오디뮴, 사마륨, 유로퓸, 가돌리늄, 테르븀, 디스프로슘, 헐뮴, 에르븀, 툴륨, 이테르븀, 및 루테튬 중 하나 이상의 원소를 사용할 수 있다. 이 금속 원소들은 스테빌라이저(stabilizer)로서 기능한다. 이러한 금속 원소의 첨가량은 금속 산화물이 반도체로서 기능할 수 있도록 결정된다는 것을 유의한다. 갈륨보다 더 많은 산소 원자와 결합이 가능한 금속 원소를 사용하고 금속 산화물에 산소를 공급할 때, 금속 산화물 내의 산소 결합을 감소시킬 수 있다.

[0190] 예를 들어, In-Ga-Zn계 금속 산화물에 포함되는 Ga(갈륨)의 전부 대신 주석을 사용하면, In-Sn-Zn계 금속 산화물이 얻어진다. In-Ga-Zn계 금속 산화물에 포함되는 Ga(갈륨)의 일부 대신 Ti(티타늄)을 사용하면, In-Ti-Ga-Zn계 금속 산화물이 얻어진다.

[0191] 산화물 반도체층은 c-축 정렬 결정 산화물 반도체(c-axis aligned crystalline oxide semiconductor: CAAC-OS)를 포함하는 산화물 반도체층일 수 있다.

[0192] CAAC-OS는 완전한 단결정이 아니고, 완전한 비정질이 아니며, 비정질 상에 결정부들을 포함하는 결정-비정질 혼합 상 구조를 갖는 산화물 반도체이다. CAAC-OS에 포함되는 결정부들 각각에서는, c축이 CAAC-OS막이 형성되는 표면의 법선 벡터 또는 CAAC-OS막의 표면의 법선 벡터에 평행한 방향으로 정렬되고, a-b면에 수직인 방향으로부터 볼 때 삼각 형상 또는 육각 형상의 원자 배열이 형성되고, c축에 수직인 방향으로부터 볼 때 금속 원자들이 층 형상으로 배열되거나, 또는 금속 원자들과 산소 원자들이 층 형상으로 배열된다. 본 명세서에 있어서, "수직"이란 용어는 85°로부터 95° 까지의 범위를 포함하고, "평행"이란 용어는 -5°로부터 5° 까지의 범위를 포함한다.

[0193] CAAC-OS를 포함하는 산화물 반도체층을 채널 형성층으로서 포함하는 전계 효과 트랜지스터에서는, 가시광 및 자외광의 조사로 인한 전기 특성의 변동이 적기 때문에, 신뢰성이 높다.

[0194] 반도체층들(711, 754)로서 산화물 반도체층을 사용하는 경우, 예를 들어, 다음과 같이, 즉, 탈수화 또는 탈수소화를 행하여, 산화물 반도체층으로부터 수소, 물, 수산기, 및 수소화물(수소 화합물이라고도 칭함) 등의 불순물을 제거하고, 산화물 반도체층에 산소를 공급하는 방식으로, 산화물 반도체층을 고순도화시킬 수 있다. 예를 들어, 산화물 반도체층에 접하는 층으로서 산소를 포함하는 층을 사용하고, 가열 처리를 행함으로써, 산화물 반도체층을 고순도화시킬 수 있다.

[0195] 또한, 성막 직후의 산화물 반도체층은 화학양론적 조성보다 산소의 비율이 많은 산소 과포화 상태인 것이 바람직하다. 예를 들어, 스퍼터링법을 사용하는 경우에, 산화물 반도체층은 성막 가스의 산소의 비율이 큰 조건에서 성막하는 것이 바람직하고, 특히 산소 분위기(산소 가스: 100%)에서 성막하는 것이 바람직하다. 또한, 산화물 반도체층을 산소로 과포화시키도록 충분한 산소를 공급하기 위해, 산화물 반도체층에 접하는 절연층(예를 들어, 절연층(701, 714, 753, 757))으로서 과잉 산소를 포함하는 절연층(예를 들어, SiO<sub>x</sub>층, 여기서 x>2)을 설치할 수 있다.

[0196] 과잉 산소를 포함하는 절연층은 플라즈마 CVD(PCVD) 또는 스퍼터링의 성막 조건을 적절히 설정해서 산소를 많이 포함하도록 형성한다. 또한, 보다 많은 과잉 산소를 절연층에 포함시키기 위해, 이온 주입법, 이온 도핑법, 또는 플라즈마 처리에 의해 산소를 첨가한다. 또한, 산화물 반도체층에 산소를 첨가해도 된다.

[0197] 스퍼터링 장치에 있어서, 성막실 내의 잔류 수분의 양은 적은 것이 바람직하기 때문에, 흡착형 진공 펌프(entrapment vacuum pump)를 사용하는 것이 바람직하다. 또한, 콜드 트랩(cold trap)을 사용해도 된다.

[0198] 산화물 반도체층은 바람직하게는 350°C 이상이고 기판의 왜곡점 미만인 기판 온도, 보다 바람직하게는 350°C 이상 450°C 이하의 범위의 기판 온도에서 가열 처리를 받는다. 또한, 나중의 공정에 있어서 가열 처리를 더 행해도 된다. 사용될 가열 처리 장치에는 특별히 제한이 없고, 전기로, 또는 GRTA(Gas Rapid Thermal Annealing:

가스 급속 열 어닐링) 장치나 LRTA(Lamp Rapid Thermal Annealing: 램프 급속 열 어닐링) 장치 등의 RTA(Rapid Thermal Annealing: 급속 열 어닐링) 장치를 사용해도 된다. 가열 처리는 복수회 행해도 된다.

[0199] 가열 처리를 행한 후, 그 가열 온도를 유지하면서, 또는 그 가열 온도로부터 강온(降溫)하면서 해당 가열 처리를 행하는 로(furnace)에 고순도의 산소 가스, 고순도의 N<sub>2</sub>O 가스, 또는 초-건조 에어(노점이 -40°C 이하, 바람직하게는 -60°C 이하임)를 도입하는 것이 바람직하다. 이 경우에, 산소 가스 또는 N<sub>2</sub>O 가스가 물 및 수소 등을 포함하지 않는 것이 바람직하다. 가열 처리 장치에 도입되는 산소 가스 또는 N<sub>2</sub>O 가스의 순도는 바람직하게 6N 이상이고, 더 바람직하게는 7N 이상이다. 즉, 산소 가스 또는 N<sub>2</sub>O 가스 중의 불순물 농도는 바람직하게 1ppm 이하, 더 바람직하게는 0.1ppm 이하이다. 이 공정에 의해, 산화물 반도체층에 산소가 공급되어, 산화물 반도체 층 내의 산소 결핍에 기인하는 결함을 감소시킬 수 있다. 고순도의 산소 가스, 고순도의 N<sub>2</sub>O 가스, 또는 초-건조 에어는 상기의 가열 처리시에 도입될 수 있다는 것을 유의한다.

[0200] 고순도화시킨 산화물 반도체층의 수소 농도의 SIMS 측정값은  $5 \times 10^{19} \text{ atoms/cm}^3$  이하, 바람직하게는  $5 \times 10^{18} \text{ atoms/cm}^3$  이하, 보다 바람직하게는  $5 \times 10^{17} \text{ atoms/cm}^3$  이하이다.

[0201] 고순도화시킨 산화물 반도체를 사용함으로써, 전계 효과 트랜지스터의 산화물 반도체층의 캐리어 밀도를  $1 \times 10^{14}/\text{cm}^3$  미만, 바람직하게는  $1 \times 10^{12}/\text{cm}^3$  미만, 보다 바람직하게는  $1 \times 10^{11}/\text{cm}^3$  미만으로 감소시킬 수 있다. 이렇게 낮은 캐리어 밀도는, 채널 폭 1 마이크로미터당의 전계 효과 트랜지스터의 오프 전류를  $1 \times 10^{-19} \text{ A}$  (100zA) 이하, 보다 바람직하게는  $1 \times 10^{-22} \text{ A}$  (100yA) 이하까지 감소시킬 수 있다. 전계 효과 트랜지스터의 오프 전류는 가능한 한 낮은 것이 바람직하지만, 전계 효과 트랜지스터의 오프 전류의 하한값은 약  $1 \times 10^{-30} \text{ A}/\mu\text{m}^2$ 라고 추정된다.

[0202] 영역들(712a, 712b)에 포함되는 도편트로서는 예를 들어, 원소 주기율표에 있어서 13족의 원소(예를 들어, 붕소), 원소 주기율표에 있어서 15족의 원소(예를 들어, 질소, 인, 및 비소 중 하나 이상), 및/또는 희ガ스 원소(예를 들어, 헬륨, 아르곤, 및 크세논 중 하나 이상)를 사용하는 것이 가능하다. 도편트는 이 그룹들 중 적어도 하나로부터 선택된다.

[0203] 절연층들(714, 753) 각각은 트랜지스터의 게이트 절연층으로서 기능한다. 절연층들(714, 753) 각각은 예를 들어, 산화 실리콘, 질화 실리콘, 산화질화 실리콘, 질화 산화 실리콘, 산화 알루미늄, 질화 알루미늄, 산화질화 알루미늄, 질화 산화 알루미늄, 또는 산화 하프늄 등의 재료를 포함하는 층일 수 있다.

[0204] 도전층들(715, 751)은 각각 트랜지스터의 게이트로서 기능한다. 도전층들(715, 751) 각각은 예를 들어, 몰리브덴, 티타늄, 크롬, 탄탈륨, 마그네슘, 은, 텉스텐, 알루미늄, 구리, 네오디뮴, 또는 스칸듐 등의 금속 재료를 포함하는 층일 수 있다.

[0205] 절연층들(716a, 716b, 717) 각각은 예를 들어, 산화 실리콘, 질화 실리콘, 산화질화 실리콘, 질화 산화 실리콘, 산화 알루미늄, 질화 알루미늄, 산화질화 알루미늄, 질화 산화 알루미늄, 또는 산화 하프늄 등의 재료를 포함하는 층일 수 있다.

[0206] 도전층들(718a, 718b), 도전층들(755a, 755b), 및 도전층들(756a, 756b) 각각은 트랜지스터의 소스 또는 드레인으로서 기능한다. 도전층들(718a, 718b), 도전층들(755a, 755b), 및 도전층들(756a, 756b) 각각은 예를 들어, 몰리브덴, 티타늄, 크롬, 탄탈륨, 마그네슘, 은, 텉스텐, 알루미늄, 구리, 네오디뮴, 스칸듐, 또는 루테늄 등의 금속 재료를 포함하는 층일 수 있다.

[0207] 절연층들(719, 757) 각각은 보호층으로서 기능한다. 절연층들(719, 757) 각각은 예를 들어, 산화 실리콘, 질화 실리콘, 산화질화 실리콘, 질화 산화 실리콘, 산화 알루미늄, 질화 알루미늄, 산화질화 알루미늄, 질화 산화 알루미늄, 또는 산화 하프늄 등의 재료를 포함하는 층일 수 있다.

[0208] 이상이 도 14의 (a) 및 도 14의 (b)에 도시된 트랜지스터들의 구조의 예들의 설명이다.

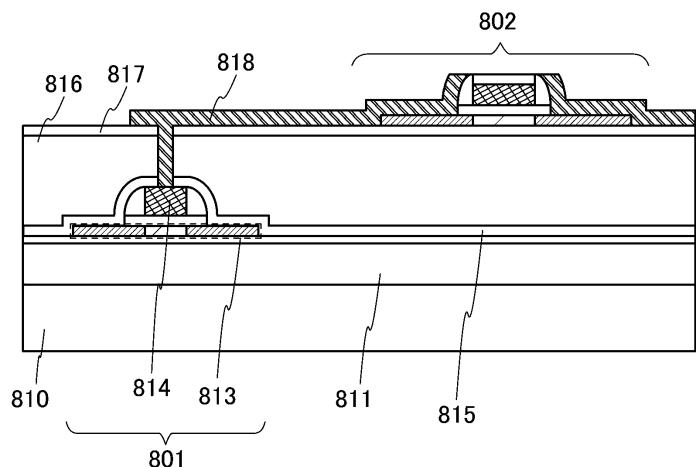

[0209] 이어서, 도 14의 (a)에 도시된 트랜지스터를 포함하는 반도체 장치의 구조의 예에 대해서 도 15를 참조하여 설명한다. 도 15는 본 실시 형태의 반도체 장치의 구조의 예를 도시하는 단면 모식도이다. 일 실시 형태는 이 구성에 한정되지 않고, 도 14의 (b)에 도시된 트랜지스터를 대안적으로 사용해도 된다는 것을 유의한다.

- [0210] 도 15에 도시된 반도체 장치는 채널 형성층인 단결정 실리콘층(813)을 포함하는 트랜지스터(801), 및 절연층들(815 내지 817)을 개재해서 트랜지스터(801) 위에 적층되어 도 14의 (a)에 도시된 구조를 갖는 트랜지스터(802)를 포함한다. 도 14의 (a)에 도시된 트랜지스터의 설명을 트랜지스터(802)에 적절히 원용할 수 있다는 것을 유의한다.

- [0211] 단결정 실리콘층(813)은 절연층(811)(BOX층이라고도 칭함)을 개재해서 기판(810) 위에 설치된다. 기판(810), 절연층(811), 및 단결정 실리콘층(813) 대신에, 단결정 반도체 기판에 있어서 매립 절연 영역으로 둘러싸인 반도체 영역을 사용하여 트랜지스터(801)를 구성할 수 있다는 것을 유의한다.

- [0212] 절연층(815)은 보호층으로서 기능한다. 절연층(816)은 보호층 및 평탄화층 둘 다로서 기능한다. 절연층(817)은 하지층이다. 절연층들(815 내지 817) 각각은 절연층(701)과 마찬가지의 재료를 포함하는 층일 수 있다.

- [0213] 트랜지스터(802)의 소스 또는 드레인으로서 기능하는 도전층(818)은 트랜지스터(801)의 게이트로서 기능하는 도전층(814)에 접속된다. 도전층(818)과 도전층(814)은 복수의 도전층을 통해 서로 접속될 수 있다는 것을 유의한다.

- [0214] 트랜지스터(802)로서 오프 전류가 낮은 트랜지스터를 사용함으로써, 메모리 셀의 데이터 유지 시간을 증가시킬 수 있다.

- [0215] 트랜지스터(801)를 사용하여, CPU 또는 신호 처리 회로 등의 논리 회로(메모리 회로를 포함함)를 구성할 수 있음으로써, 동작 속도를 증가시킬 수 있다.

- [0216] 이상이 도 15에 도시된 반도체 장치의 구성의 예의 설명이다.

- [0217] 도 14의 (a) 및 도 14의 (b) 및 도 15를 참조하여 설명한 바와 같이, 본 실시 형태의 반도체 장치에서는 레지스터 또는 다른 메모리 장치에 있어서의 데이터의 기입 및 유지를 제어하는 트랜지스터가 산화물 반도체층을 포함하고, CPU 또는 신호 처리 회로 등에 사용되는 논리 회로의 트랜지스터는 단결정 실리콘층을 포함한다. 이에 의해, 반도체 장치의 동작 속도를 증가시키면서, 레지스터 또는 다른 메모리 장치에 있어서의 데이터의 유지 시간을 증가시킬 수 있다.

- [0218] (실시 형태 5)

- [0219] 본 실시 형태에서는 본 발명의 일 실시 형태인 반도체 장치를 포함하는 전자 기기들의 예들에 대해서 도 16의 (a) 내지 도 16의 (f)를 참조하여 설명한다.

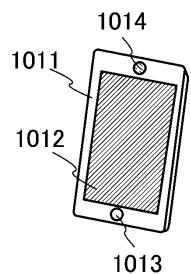

- [0220] 도 16의 (a)에 도시된 전자 기기는 휴대형 정보 단말기의 예이다.

- [0221] 도 16의 (a)에 도시된 전자 기기는 하우징(1011), 하우징(1011)에 통합된 패널(1012), 버튼(1013), 및 스피커(1014)를 포함한다.

- [0222] 하우징(1011)에는 전자 기기를 외부 기기에 접속하기 위한 접속 단자, 및 전자 기기를 조작하기 위한 버튼이 설치될 수 있다.

- [0223] 패널(1012)은 표시 패널(디스플레이)이고, 터치 패널의 기능을 갖는 것이 바람직하다.

- [0224] 버튼(1013)은 하우징(1011)에 설치된다. 버튼(1013)이 전원 버튼이면, 버튼(1013)을 누름으로써 전자 기기를 터온 또는 터오프할 수 있다.

- [0225] 스피커(1014)는 하우징(1011)에 설치된다. 스피커(1014)는 음향을 출력한다.

- [0226] 하우징(1011)에는 마이크가 설치될 수 있는데, 이 경우에, 예를 들어 도 16의 (a)의 전자 기기는 전화기로서 기능할 수 있다.

- [0227] 도 16의 (a)의 전자 기기에 있어서, 하우징(1011) 내에 실시 형태 1에서 설명한 CPU(CPU(111)), 메모리, 화상 처리 회로, 및 콘트롤러 등이 설치된다. 콘트롤러 대신에 제1 CPU로서 기능하는 CPU가 설치될 수 있다는 것을 유의한다.

- [0228] 도 16의 (a)의 전자 기기는 예를 들어, 전화기, 전자 서적, 퍼스널 컴퓨터, 및 게임 머신 중 적어도 하나로서 기능한다.

- [0229] 도 16의 (b)에 도시된 전자 기기는 절첩식의 정보 단말기의 예이다.

- [0230] 도 16의 (b)에 도시된 전자 기기는 하우징(1021a), 하우징(1021b), 하우징(1021a)에 통합된 패널(1022a), 하우징(1021b)에 통합된 패널(1022b), 힌지(1023), 베튼(1024), 접속 단자(1025), 저장 매체 삽입부(1026), 및 스피커(1027)를 포함한다.

- [0231] 하우징(1021a)과 하우징(1021b)은 힌지(1023)에 의해 연결된다.

- [0232] 패널(1022a) 및 패널(1022b) 각각은 표시 패널(디스플레이)이고, 터치 패널의 기능을 갖는 것이 바람직하다.

- [0233] 도 16의 (b)의 전자 기기는 힌지(1023)를 포함하기 때문에, 패널(1022a)과 패널(1022b)을 서로 대향하도록 접을 수 있다.

- [0234] 베튼(1024)은 하우징(1021b)에 설치된다. 하우징(1021a)에 베튼(1024)을 설치해도 된다는 것을 유의한다. 예를 들어, 전원 베튼의 기능을 갖는 베튼(1024)을 설치하는 경우에, 베튼(1024)을 누름으로써 전자 기기내의 회로에 전력을 공급할 지의 여부를 제어할 수 있다.

- [0235] 접속 단자(1025)는 하우징(1021a)에 설치된다. 하우징(1021b)에 접속 단자(1025)가 설치되어도 된다는 것을 유의한다. 대안적으로, 복수의 접속 단자(1025)가 하우징(1021a) 및 하우징(1021b) 중 한쪽 또는 양쪽에 설치되어도 된다. 접속 단자(1025)는 도 16의 (b)의 전자 기기를 다른 기기에 접속하기 위한 단자이다.

- [0236] 저장 매체 삽입부(1026)는 하우징(1021a)에 설치된다. 하우징(1021b)에 저장 매체 삽입부(1026)가 설치되어도 된다. 대안적으로, 복수의 저장 매체 삽입부(1026)가 하우징(1021a) 및 하우징(1021b) 중 한쪽 또는 양쪽에 설치되어도 된다. 예를 들어, 저장 매체 삽입부(1026)에 카드형 기록 매체를 삽입할 때, 데이터가 카드형 저장 매체로부터 판독될 수 있고 전자 기기에 전송될 수 있거나, 또는 전자 기기 내에 저장된 데이터가 카드형 기록 매체에 기입될 수 있다.

- [0237] 스피커(1027)는 하우징(1021b)에 설치된다. 스피커(1027)는 음향을 출력한다. 스피커(1027)는 하우징(1021a)에 설치되어도 된다.

- [0238] 하우징(1021a) 또는 하우징(1021b)에 마이크가 설치되어도 되고, 이 경우에, 예를 들어, 도 16의 (b)의 전자 기기는 전화기로서 기능할 수 있다.

- [0239] 도 16의 (b)의 전자 기기에 있어서, 하우징(1021a) 또는 하우징(1021b) 내에 실시 형태 1에서 설명한 CPU(CPU(111)), 메모리, 화상 처리 회로, 및 콘트롤러 등을 설치할 수 있다. 콘트롤러 대신에 제1 CPU로서 기능하는 CPU가 설치되어도 된다는 것을 유의한다.

- [0240] 도 16의 (b)의 전자 기기는 예를 들어, 전화기, 전자 서적, 퍼스널 컴퓨터, 및 게임 머신 중 임의의 것으로서 기능한다.

- [0241] 도 16의 (c)에 도시된 전자 기기는 거치형 정보 단말기의 예이다. 도 16의 (c)에 도시된 거치형 정보 단말기는 하우징(1031), 하우징(1031)에 통합된 패널(1032), 베튼(1033), 및 스피커(1034)를 포함한다.

- [0242] 패널(1032)은 표시 패널(디스플레이)이고, 터치 패널의 기능을 갖는 것이 바람직하다.

- [0243] 하우징(1031)의 상판(1035) 위에 패널(1032)과 마찬가지인 패널이 설치되어도 되고, 이 경우 그 패널은 터치 패널의 기능을 갖는 것이 바람직하다는 것을 유의한다.

- [0244] 또한, 하우징(1031)에는 티켓 등을 출력하는 티켓 출력부, 동전 투입부, 및/또는 지폐 삽입부 등이 설치되어도 된다.

- [0245] 베튼(1033)은 하우징(1031)에 설치된다. 예를 들어, 베튼(1033)이 전원 베튼이면, 베튼(1033)을 누름으로써 전자 기기 내의 회로에 전력을 공급할 지의 여부를 제어할 수 있다.

- [0246] 스피커(1034)는 하우징(1031)에 설치된다. 스피커(1034)는 음향을 출력한다.

- [0247] 도 16의 (c)의 전자 기기에 있어서, 하우징(1031) 내에 실시 형태 1에서 설명한 CPU(CPU(111)), 메모리, 화상 처리 회로, 및 콘트롤러 등을 설치한다. 콘트롤러 대신 제1 CPU로서 기능하는 CPU가 설치되어도 된다는 것을 유의한다.

- [0248] 도 16의 (c)의 전자 기기는 예를 들어, 현금 자동 입출금기, 티켓 등의 주문을 하기 위한 정보 통신 단말기(멀티미디어 스테이션이라고도 칭함), 또는 게임 머신으로서 기능한다.

- [0249] 도 16의 (d)는 거치형 정보 단말기의 예를 도시한다. 도 16의 (d)의 전자 기기는 하우징(1041), 하우징(1041)

에 통합된 패널(1042), 하우징(1041)을 지지하는 지지대(1043), 버튼(1044), 접속 단자(1045), 및 스피커(1046)를 포함한다.

[0250] 하우징(1041)에 도 16의 (d)의 전자 기기를 외부 기기에 접속시키기 위한 접속 단자가 설치되어도 되고, 그리고 /또는 도 16의 (d)의 전자 기기를 조작하기 위한 버튼이 설치되어도 된다는 것을 유의한다.

[0251] 패널(1042)은 표시 패널(디스플레이)로서 기능한다.

[0252] 버튼(1044)은 하우징(1041)에 설치된다. 예를 들어, 버튼(1044)이 전원 버튼인 경우, 버튼(1044)을 누름으로써 전자 기기 내의 회로에 전력을 공급할 지의 여부를 제어할 수 있다.

[0253] 접속 단자(1045)는 하우징(1041)에 설치된다. 접속 단자(1045)는 도 16의 (d)의 전자 기기를 다른 기기에 접속하기 위한 단자이다. 예를 들어, 접속 단자(1045)에 의해 도 16의 (d)의 전자 기기와 퍼스널 컴퓨터를 접속하는 경우에, 패널(1042)은 퍼스널 컴퓨터로부터 입력되는 데이터 신호에 대응하는 화상을 표시할 수 있다. 예를 들어, 도 16의 (d)의 전자 기기의 패널(1042)이 그에 접속되는 다른 전자 기기의 패널보다 크면, 다른 전자 기기의 표시 화상을 확대할 수 있어서, 복수의 시청자가 동시에 화상을 용이하게 시인할 수 있다.

[0254] 스피커(1046)는 하우징(1041)에 설치된다. 스피커(1046)는 음향을 출력한다.

[0255] 도 16의 (d)의 전자 기기에 있어서, 하우징(1041) 내에 실시 형태 1에서 설명한 CPU(CPU(111)), 메모리, 화상 처리 회로, 및 콘트롤러 등을 설치한다. 콘트롤러 대신 제1 CPU로서 기능하는 CPU가 탑재되어도 된다는 것을 유의한다.

[0256] 도 16의 (d)의 전자 기기는 예를 들어, 출력 모니터, 퍼스널 컴퓨터, 또는 텔레비전 장치로서 기능한다.

[0257] 도 16의 (e)는 전기 냉장고-냉동고의 예를 도시한다. 도 16의 (e)에 도시된 전자 기기(1050)는 하우징(1051), 냉장고 도어(1052), 및 냉동고 도어(1053)를 포함한다.

[0258] 도 16의 (e)의 전자 기기에 있어서, 하우징(1051) 내에 실시 형태 1에서 설명한 CPU(CPU(111)), 메모리, 화상 처리 회로, 및 콘트롤러 등을 설치한다. 콘트롤러 대신 제1 CPU로서 기능하는 CPU가 설치되어도 된다는 것을 유의한다. 이 구성에 의해, 예를 들어, 냉장고 도어(1052) 및 냉동고 도어(1053)의 개폐에 응답하여 하우징(1051) 내의 CPU, 메모리, 및 신호 처리 회로에 대한 전원 공급을 제어할 수 있다.

[0259] 도 16의 (f)는 에어 컨디셔너의 예를 도시한다. 도 16의 (f)에 도시된 전자 기기는 실내기(1060) 및 실외기(1064)를 포함한다.

[0260] 실내기(1060)는 하우징(1061)과 송풍구(1062)를 포함한다.

[0261] 도 16의 (f)의 전자 기기에 있어서, 하우징(1061) 내에 실시 형태 1에서 설명한 CPU(CPU(111)), 메모리, 화상 처리 회로, 및 콘트롤러 등을 설치한다. 콘트롤러 대신 제1 CPU로서 기능하는 CPU가 설치되어도 된다는 것을 유의한다. 이 구성에 의해, 예를 들어, 리모트 콘트롤러로부터의 신호에 응답하여 하우징(1061) 내의 CPU, 메모리, 및 신호 처리 회로에 대한 전원 공급을 제어할 수 있다.

[0262] 도 16의 (f)에는 실내기와 실외기를 포함하는 분리형 에어 컨디셔너를 예로서 도시하지만, 대안적으로 실내기와 실외기의 기능들을 1개의 하우징에 통합시킨 에어 컨디셔너일 수 있다는 것을 유의한다.

[0263] 전자 기기의 예들은 상기의 것에 한정되지 않고, 전자레인지 등의 고주파 가열 장치, 및 전기 밥솥 등에도 실시 형태 1 내지 실시 형태 4 중 임의의 반도체 장치를 적용할 수 있다.

[0264] 이상이 도 16의 (a) 내지 도 16의 (f)에 도시된 전자 기기들의 설명이다.

[0265] 도 16의 (a) 내지 도 16의 (f)를 참조하여 설명한 바와 같이, 본 실시 형태의 전자 기기는 실시 형태 1 내지 실시 형태 4 중 임의의 반도체 장치를 사용함으로써 전력을 덜 소비한다.

[0266] (실시 형태 6)

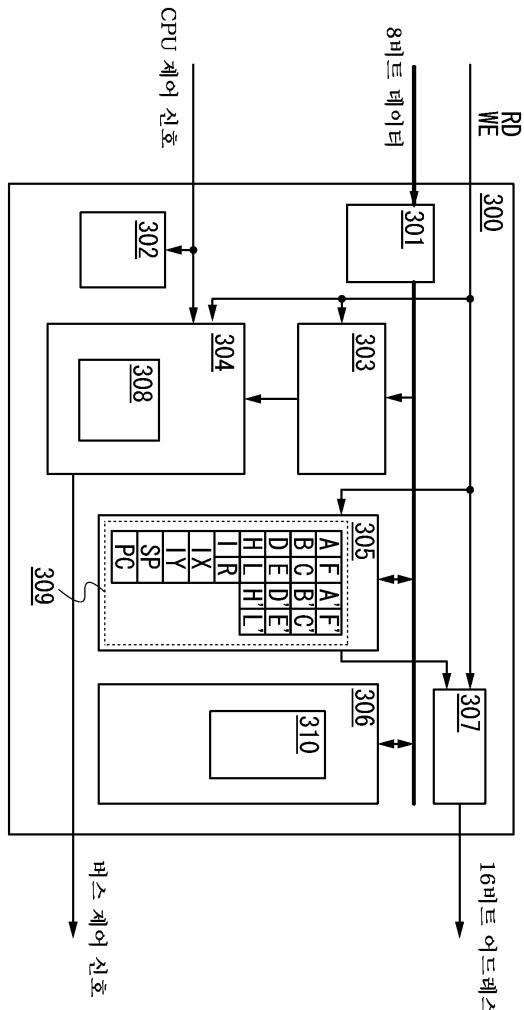

[0267] 실시 형태 1에서 설명한 CPU의 구체적인 실시 형태에 대해서 설명한다. 도 17은 CPU의 블록도의 예이다.

[0268] CPU(300)는 데이터 래치 및 셀렉터의 기능을 갖는 회로(301), 내부 클럭 생성부 및 리셋 콘트롤러의 기능을 갖는 회로(302), 명령 레지스터 및 디코드부의 기능을 갖는 회로(303), CPU 제어부(304), 레지스터 세트(305), 계산 유닛(306), 및 어드레스 버퍼(307)를 포함한다.

- [0269] CPU 제어부(304)는 스테이트 생성부(308)를 포함한다. 레지스터 세트(305)는 복수의 레지스터(309)를 포함한다. 계산 유닛(306)은 산술 논리 연산부(arithmetic logic unit: ALU)(310)를 포함한다.

- [0270] CPU(300)에는 기입 제어 신호 WE 및 판독 제어 신호 RD가 입력된다. 또한, CPU(300)에는 데이터 버스를 통해 8비트 데이터가 입력된다. CPU(300)에는 CPU 제어 신호도 입력된다.

- [0271] CPU(300)로부터 16비트 어드레스 및 버스 제어 신호가 출력된다.

- [0272] 기입 제어 신호 WE 및 판독 제어 신호 RD는 회로(303), CPU 제어부(304), 레지스터 세트(305), 및 어드레스 버퍼(307)에 입력된다. 8비트 데이터가 데이터 버스를 통해 회로(303), 레지스터 세트(305), 및 계산 유닛(306)에 입력된다. CPU 제어 신호는 회로(302) 및 CPU 제어부(304)에 입력된다.

- [0273] 16비트 어드레스가 어드레스 버퍼(307)로부터 출력된다. 버스 제어 신호는 CPU 제어부(304)로부터 출력된다.

- [0274] 명령 레지스터 및 디코드부의 기능을 갖는 회로(303)는 8비트 레지스터들을 포함한다.

- [0275] CPU 제어부(304)는 3비트 레지스터들을 포함한다.

- [0276] 어드레스 버퍼(307)는 16비트 레지스터들을 포함한다.

- [0277] 스테이트 생성부(308)는 24비트 레지스터들을 포함한다.

- [0278] 레지스터 세트(305)는 복수의 레지스터(309)로서 204비트 레지스터들을 포함한다. 레지스터(309)는 프로그램 카운터, 범용 레지스터, 및 산술연산 레지스터로서 기능한다. 도 17에 있어서, 레지스터들(309)에 나타낸 A, F, A', F', B, C, B', C', D, E, D', E', H, L, H', L', I, R, IX, IY, SP, 및 PC는 레지스터들을 나타낸다.

- [0279] 본 실시 형태의 일 예로서 설명하는 CPU(300)는 총 255개의 레지스터를 포함한다.

- [0280] CPU(300)의 회로들 각각은 데이터 버스뿐만 아니라 어드레스 버스 및 컨트롤 버스를 통해 데이터, 어드레스, 및 CPU 제어 신호를 입력 및 출력할 수 있다.

- [0281] 도 17에 도시된 CPU(300)에 있어서, 명령 레지스터 및 디코드부의 기능을 갖는 회로(303), CPU 제어부(304), 스테이트 생성부(308), 및 레지스터 세트(305)에 포함되는, 총 255개의 레지스터로서 산화물 반도체를 사용한 레지스터를 이용할 수 있다는 것을 유의한다.

- [0282] 도 18은 1비트 데이터를 유지할 수 있는 레지스터의 구성의 예를 도시한다. 도 18에 도시된 구성은 실시 형태 3의 도 12의 (b)의 메모리 회로에 회로들을 추가한 구성이다. 그로 인해, 중복되는 구성 요소들에 관해서는 간단하게만 설명하고, 그러한 구성 요소들에 대해서는 실시 형태 3의 설명을 원용한다.

- [0283] 도 18에 도시된 레지스터는 플립 플롭(601), 메모리 회로(602), 및 셀렉터(603)를 포함한다.

- [0284] 플립 플롭(601)에는 리셋 신호 RST, 클럭 신호 CLK, 및 데이터 신호 D가 공급된다. 플립 플롭(601)은 클럭 신호 CLK에 응답하여 입력되는 데이터 신호 D의 데이터를 유지하고, 그 데이터를 데이터 신호 Q로서 출력하는 기능을 갖는다.

- [0285] 메모리 회로(602)에는 기입 제어 신호 WE, 판독 제어 신호 RD, 및 데이터 신호가 공급된다.

- [0286] 메모리 회로(602)는 기입 제어 신호 WE에 따라, 입력되는 데이터 신호의 데이터를 저장하고, 판독 제어 신호 RD에 따라, 저장된 데이터를 데이터 신호로서 출력하는 기능을 갖는다.

- [0287] 셀렉터(603)는 판독 제어 신호 RD에 따라, 데이터 신호 D 또는 메모리 회로(602)로부터 출력되는 데이터 신호를 선택하고, 선택된 신호를 플립 플롭(601)에 입력한다.

- [0288] 도 18에 도시된 바와 같이 메모리 회로(602)는 트랜지스터(631) 및 용량 소자(632)를 포함한다.

- [0289] 트랜지스터(631)는 n 채널형 트랜지스터이다. 트랜지스터(631)의 소스 및 드레인 중 한쪽은 플립 플롭(601)의 출력 단자에 전기적으로 접속된다. 트랜지스터(631)는 기입 제어 신호 WE에 따라, 플립 플롭(601)으로부터 출력되는 데이터 신호의 유지를 제어하는 기능을 갖는다.

- [0290] 트랜지스터(631)는 실시 형태 1에 설명된 트랜지스터일 수 있고, 산화물 반도체를 포함하고, 따라서 오프 전류가 낮다.

- [0291] 용량 소자(632)의 한 쌍의 전극 중 한쪽은 트랜지스터(631)의 소스 및 드레인 중 다른 쪽에 전기적으로 접속되

고, 다른 쪽에는 접지 전위(GND)가 공급된다. 용량 소자(632)는 입력되는 데이터 신호의 데이터에 기초하는 전하를 유지하는 기능을 갖는다. 트랜지스터(631)의 오프 전류가 매우 낮기 때문에, 전원 전압의 공급이 정지될 때에도 용량 소자(632)의 전하가 유지됨으로써, 데이터가 유지된다.

[0292] 트랜지스터(633)는 p 채널형 트랜지스터이다. 트랜지스터(633)의 소스 및 드레인 중 한쪽에는 전원 전위(VDD)가 공급된다. 트랜지스터(633)의 게이트에는 판독 제어 신호 RD가 공급된다. 전원 전위와 접지 전위 간의 차가 전원 전압 PWR이 된다.

[0293] 트랜지스터(634)는 n 채널형 트랜지스터이다. 트랜지스터(634)의 소스 및 드레인 중 한쪽은 트랜지스터(633)의 소스 및 드레인 중 다른 쪽에 전기적으로 접속된다. 트랜지스터(634)의 게이트에는 판독 제어 신호 RD가 공급된다.

[0294] 트랜지스터(635)는 n 채널형 트랜지스터이다. 트랜지스터(635)의 소스 및 드레인 중 한쪽은 트랜지스터(634)의 소스 및 드레인 중 다른 쪽에 전기적으로 접속되고, 다른 쪽에는 접지 전위가 공급된다.

[0295] 인버터(636)의 입력 단자는 트랜지스터(633)의 소스 및 드레인 중 다른 쪽에 전기적으로 접속된다. 인버터(636)의 출력 단자는 셀렉터(603)의 입력 단자에 전기적으로 접속된다.

[0296] 용량 소자(637)의 한 쌍의 전극 중 한쪽은 인버터(636)의 입력 단자에 전기적으로 접속되고, 다른 쪽에는 접지 전위가 공급된다. 용량 소자(637)는 인버터(636)에 입력되는 데이터 신호의 데이터에 기초하는 전하를 유지하는 기능을 갖는다.

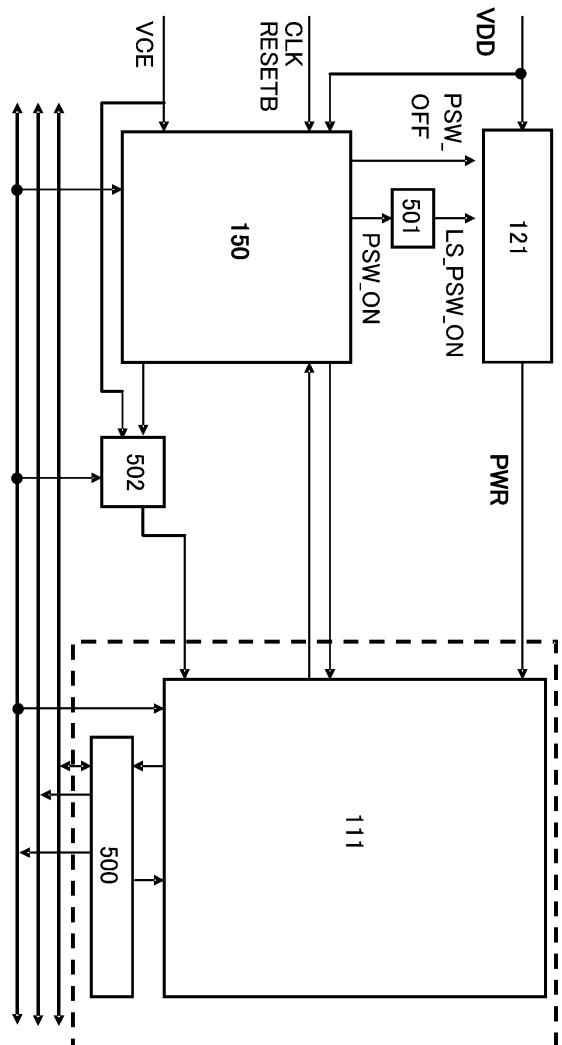

[0297] 도 19는 CPU(111), 전원 공급 제어 스위치(121), 및 콘트롤러(150) 사이의 신호의 흐름의 예를 모식적으로 도시한다.

[0298] 도 19는 CPU(111), 콘트롤러(150), 및 전원 공급 제어 스위치(121) 외에도, CPU(111)와 전원 공급 제어 스위치(121) 사이에 설치된 레벨 시프터(501), 콘트롤러(150)와 CPU(111) 사이에 설치된 레벨 시프터(502), 및 CPU(111)에 있어서의 각종 데이터의 전송 경로에 상당하는 버퍼(BUF)(500)를 또한 도시한다.

[0299] 콘트롤러(150)는 CPU(111)의 제어 신호, 및 노멀리 오프 상태와 통상 상태 간의 전환 명령을 포함하는 VCE 신호에 따라, 노멀리 오프 상태와 통상 상태 간의 전환을 제어하는 신호를 CPU(111)에 송신하는 기능을 갖는다. VCE 신호의 전압 레벨은 레벨 시프터(502)에 의해 조정되고, 그 결과의 VCE 신호가 CPU(111)에 입력된다. "노멀리 오프"란, 콘트롤러(150)로부터의 전원 전압 및 제어 신호의 공급이 정지됨으로써, CPU(111)가 작동을 정지하는 상태를 의미한다는 것을 유의한다. CPU(111)는 콘트롤러(150)로부터의 전원 전압 및 제어 신호가 공급됨으로써, 동작 상태, 즉 통상 상태로 될 수 있다.

[0300] 구체적으로, VCE 신호에 의해 노멀리 오프 상태로의 CPU(111)의 상태의 전환이 명령되면, CPU(111)에서는 레지스터의 NVM에 데이터가 저장된다. 또한, 콘트롤러(150)는 전원 공급 제어 스위치(121)를 터온하기 위한 제어 신호 SW\_ON과, 전원 공급 제어 스위치(121)를 터오프하기 위한 제어 신호 SW\_OFF를 생성하는 기능을 갖는다. 제어 신호 SW\_ON은 레벨 시프터(501)에 의해 그것의 전압 레벨이 조정된 후, CPU(111)에 입력된다. 전원 공급 제어 스위치(121)가 온 상태인 동안, 전원 전압 PWR은 전원 공급 제어 스위치(121)를 통해 CPU(111)에 공급되지만, 전원 공급 제어 스위치(121)가 오프 상태인 동안, 전원 전압 PWR은 CPU(111)에 공급되지 않는다.

[0301] 콘트롤러(150)는 또한 반도체 장치(100)에 입력된 클럭 신호 CLK 및 리셋 신호 RESETB로부터, CPU(111)에 사용되는 클럭 신호 C-CLK를 생성하는 기능을 갖는다.

[0302] 본 실시 형태는 다른 실시 형태들 중 임의의 것과 적절히 조합해서 실시될 수 있다.

[0303] (실시 형태 7)

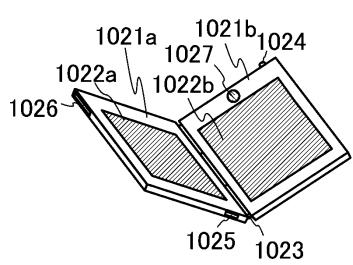

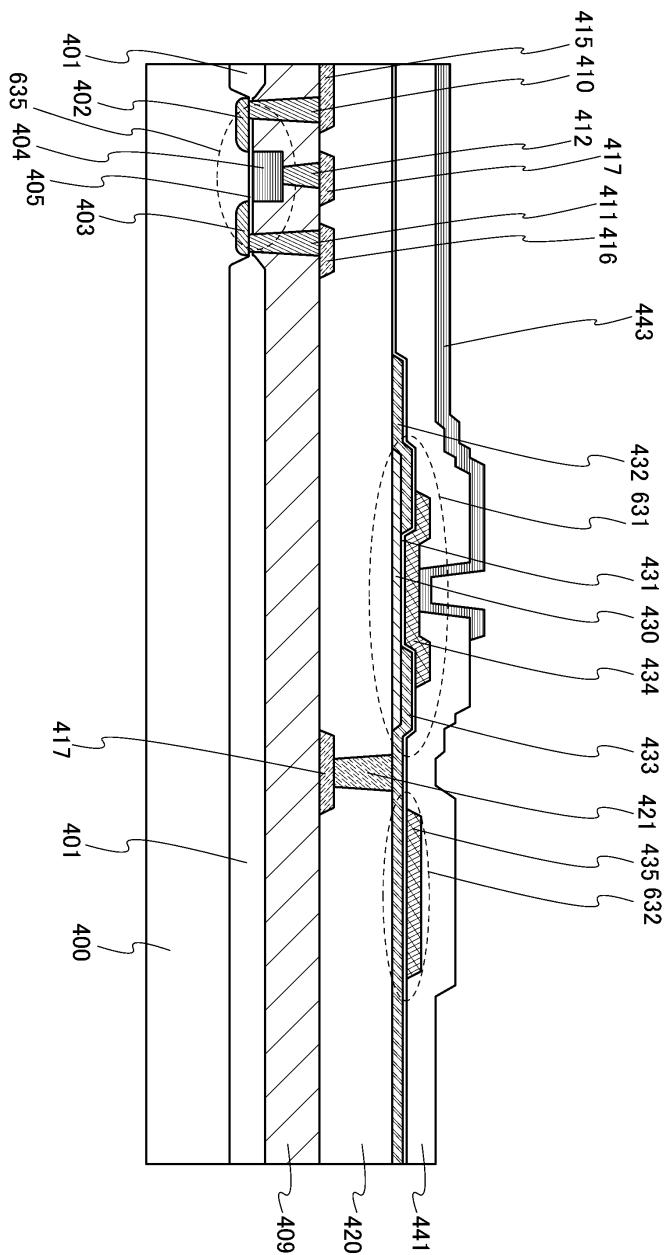

[0304] 도 20은 본 발명의 일 실시 형태에 따른 반도체 장치의 단면 구조의 일부의 예를 도시한다. 도 20은 트랜지스터(631), 용량 소자(632), 및 트랜지스터(635)를 예로서 도시한다.

[0305] 본 실시 형태에서는 트랜지스터(635)가 단결정의 실리콘 기판 위에 형성되고, 산화물 반도체를 함유하는 활성층을 포함하는 트랜지스터(631), 및 용량 소자(632)가 트랜지스터(635) 위에 형성되는 경우를 나타낸다. 트랜지스터(635)에 있어서, 활성층은 비정질, 미결정, 다결정, 또는 단결정 상태인 실리콘 또는 게르마늄 등의 반도체 박막일 수 있다. 대안적으로, 트랜지스터(635) 내의 활성층은 산화물 반도체를 사용하여 형성될 수 있다. 모든 트랜지스터의 활성층들에 산화물 반도체를 사용하는 경우에, 트랜지스터(631)는 반드시 트랜지스터(635) 위에 적층될 필요는 없고, 트랜지스터들(631, 635)은 동일한 층에 형성되어도 된다.

- [0306] 실리콘 박막을 사용하여 트랜지스터(635)를 형성하는 경우, 다음 중, 즉, 예를 들면, 플라즈마 CVD 등의 기상 성장 또는 스피터링에 의해 형성된 비정질 실리콘, 비정질 실리콘을 레이저 어닐링 등에 의해 결정화시킨 다결정 실리콘, 및 단결정 실리콘 웨이퍼에 수소 이온 등을 주입한 후 그 실리콘 웨이퍼의 표층부를 박리하는 방식으로 얻어지는 단결정 실리콘 중 임의의 것을 사용할 수 있다.

- [0307] 실시 형태 6에 설명한 메모리 회로인 레지스터에 포함되는 트랜지스터들 중에서, 트랜지스터(631)가 산화물 반도체를 사용하여 형성되고, 트랜지스터(635)를 포함한 다른 트랜지스터들이 실리콘을 사용하여 형성되는 경우에, 실리콘을 사용한 트랜지스터의 수보다, 산화물 반도체를 사용한 트랜지스터의 수가 적다. 따라서, 실리콘을 사용한 트랜지스터 위에 트랜지스터(631)를 적층시킴으로써, 트랜지스터(631)의 디자인 률을 완화시킬 수 있다.

- [0308] 이와 같이 실리콘을 사용한 트랜지스터와 산화물 반도체를 사용한 트랜지스터를 적층한 구조의 레지스터를 이용함으로써 CPU의 칩 면적을 축소시킬 수 있다. 하나의 회로 블록에 있어서, 실리콘을 사용한 트랜지스터의 수가 산화물 반도체를 사용한 트랜지스터의 수보다 많기 때문에, 실제의 CPU의 칩 면적은 실리콘을 사용한 트랜지스터의 수에 따라 결정된다. 실시 형태 6에 나타낸 구성을 갖는 레지스터에서, 실리콘을 사용한 트랜지스터의 수와 산화물 반도체를 사용한 트랜지스터의 수의 비는 20:1 내지 40:1이다.

- [0309] 도 20에 있어서, 반도체 기판(400) 위에 n 채널형 트랜지스터(635)가 형성된다.

- [0310] 반도체 기판(400)의 예들은, n형 또는 p형 실리콘 기판, 게르마늄 기판, 실리콘 게르마늄 기판, 및 화합물 반도체 기판(예를 들면, GaAs 기판, InP 기판, GaN 기판, SiC 기판, GaP 기판, GaInAsP 기판, 및 ZnSe 기판)이다. 예로서, 도 20은 n형 단결정 실리콘 기판을 사용한 경우를 도시한다.

- [0311] 트랜지스터(635)는 소자 분리용 절연막(401)에 의해 다른 트랜지스터들로부터 전기적으로 분리된다. 소자 분리용 절연막(401)은 실리콘의 로컬 산화(Local Oxidation of Silicon: LOCOS) 방법 또는 트렌치 분리 방법(trench isolation method) 등에 의해 형성될 수 있다.

- [0312] 구체적으로, 트랜지스터(635)는 반도체 기판(400)에 형성된, 소스 영역 또는 드레인 영역으로서 기능하는 불순물 영역들(402, 403), 게이트 전극(404), 및 반도체 기판(400)과 게이트 전극(404) 사이에 설치된 게이트 절연막(405)을 포함한다. 게이트 전극(404)은 불순물 영역들(402, 403) 사이에 형성되는 채널 형성 영역과 중첩하고, 게이트 절연막(405)은 게이트 전극(404)과 채널 형성 영역 사이에 배치된다.

- [0313] 트랜지스터(635) 위에는 절연막(409)이 설치된다. 절연막(409)에는 개구부들이 형성된다. 개구부들에는, 불순물 영역(402)에 접하는 배선(410), 불순물 영역(403)에 접하는 배선(411), 및 게이트 전극(404)에 접하는 배선(412)이 형성된다.

- [0314] 배선(410)은 절연막(409) 위에 형성된 배선(415)에 접속된다. 배선(411)은 절연막(409) 위에 형성된 배선(416)에 접속된다. 배선(412)은 절연막(409) 위에 형성된 배선(417)에 접속된다.

- [0315] 배선(415 내지 417) 위에는 절연막(420)이 형성된다. 절연막(420)에는 개구부가 형성된다. 개구부에는 배선(417)에 접속되는 배선(421)이 형성된다.

- [0316] 도 20에 있어서, 절연막(420) 위에 트랜지스터(631) 및 용량 소자(632)가 형성된다.

- [0317] 트랜지스터(631)는 절연막(420) 위에, 산화물 반도체를 포함하는 반도체막(430), 반도체막(430) 위에 위치하고 소스 전극 또는 드레인 전극으로서 기능하는 도전막들(432, 433), 반도체막(430)과 도전막들(432, 433) 위의 게이트 절연막(431), 및 게이트 절연막(431) 위에 위치하고 도전막들(432, 433) 사이의 반도체막(430)과 중첩하는 게이트 전극(434)을 포함한다. 도전막(433)은 배선(421)에 접속된다는 것을 유의한다.

- [0318] 게이트 절연막(431) 위에는 도전막(433)과 중첩하도록 도전막(435)이 설치된다. 게이트 절연막(431)을 사이에 두고 도전막(433)과 도전막(435)이 중첩하는 부분이 용량 소자(632)로서 기능한다.

- [0319] 도 20은 용량 소자(632)가 트랜지스터(631)와 함께 절연막(420) 위에 설치되는 경우를 도시하지만, 대안적으로 용량 소자(632)는 트랜지스터(635)와 함께 절연막(420) 밑에 설치될 수 있다는 것을 유의한다.

- [0320] 트랜지스터(631)와 용량 소자(632) 위에 절연막(441)이 설치된다. 절연막(441)에는 개구부가 형성된다. 개구부에 있어서 게이트 전극(434)에 접하는 도전막(443)이 절연막(441) 위에 설치된다.

- [0321] 도 20에 있어서, 트랜지스터(631)는 게이트 전극(434)을 반도체막(430)의 적어도 한쪽(one side)에 포함한다.

대안적으로, 트랜지스터(631)는 반도체막(430)을 사이에 두고 존재하는 한 쌍의 게이트 전극을 포함할 수 있다.

[0322] 트랜지스터(631)가 반도체막(430)을 사이에 두고 존재하는 한 쌍의 게이트 전극들을 갖는 경우, 게이트 전극들 중 한쪽에는 트랜지스터(631)를 턴온 또는 오프하기 위한 신호가 공급되고, 게이트 전극들 중 다른 쪽은 플로팅 상태(즉, 전기적으로 절연됨)일 수 있거나, 또는 전위가 공급될 수 있다. 후자의 경우, 한 쌍의 전극에, 동일한 레벨의 전위가 공급될 수 있거나, 또는 게이트 전극들 중 다른 쪽에만 접지 전위 등 고정 전위가 공급될 수 있다. 게이트 전극들 중 다른 쪽에 공급되는 전위의 레벨을 제어함으로써, 트랜지스터(631)의 임계 전압을 제어할 수 있다.

[0323] 본 실시 형태는 다른 실시 형태들 중 임의의 것과 적절히 조합해서 실시될 수 있다.

[0324] (실시 형태 8)

[0325] 본 실시 형태는 회로마다 전원 전압의 공급을 독립적으로 제어하도록 해주는 파워 게이트를 프로그램에 의해 제어할 수 있는 구성에 대해서 설명한다.

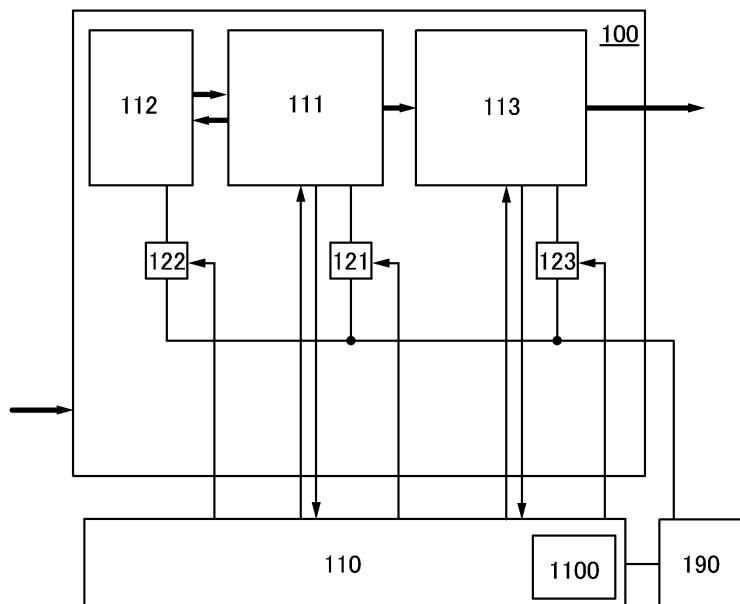

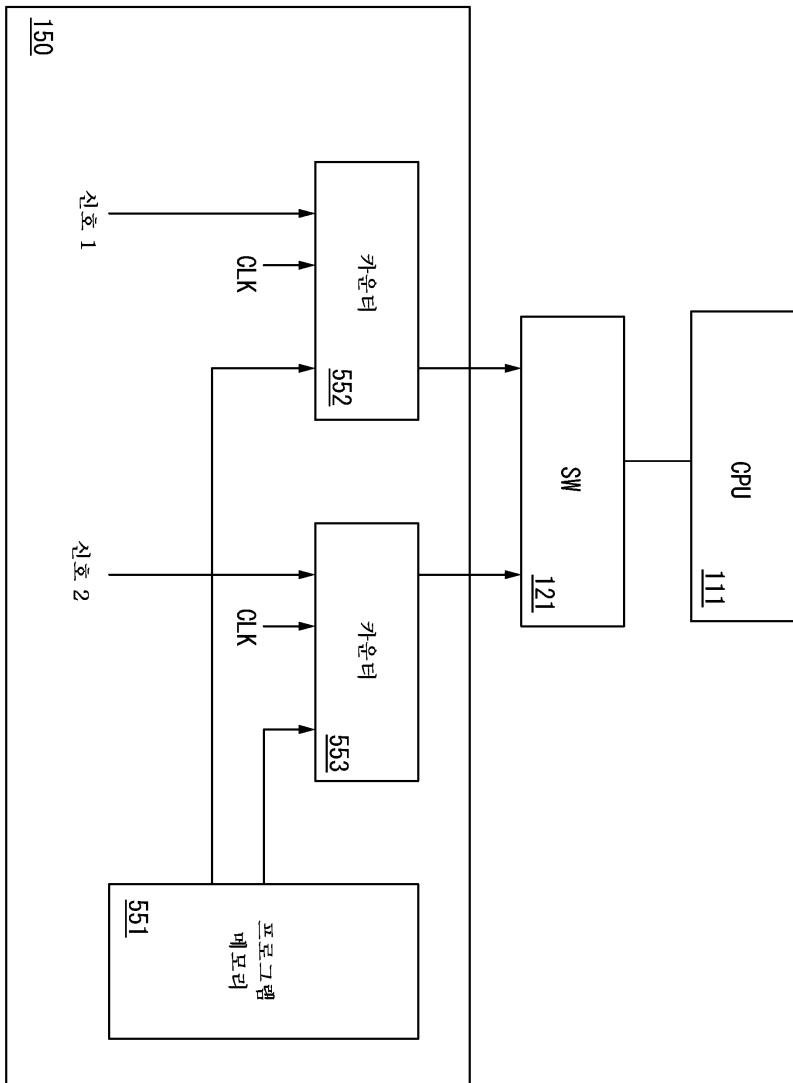

[0326] 도 21, 도 22의 (a) 및 도 22의 (b)는 프로그램에 의해 파워 게이트를 제어할 수 있는 구조의 예를 설명하기 위한 도면이다. 도 21은 도 1을 참조하여 설명한 CPU(111), 메모리(112), 및 신호 처리 회로(113)에의 전원 전압의 공급을, 파워 게이트들인 전원 공급 제어 스위치들(121, 122, 123)에 의해 제어하는 경우를 도시한다. 본 실시 형태에서는, CPU(111)에 전원 전압을 공급하는 전원 공급 제어 스위치(121)를 예로서 설명한다.

[0327] 프로그램은 실시 형태 1에서 설명한 콘트롤러(150)에 추가되는 프로그램 메모리(551)에 저장된다. 본 실시 형태에 있어서, 콘트롤러(150)는 프로그램 메모리(551) 외에도 파워 게이트 턴오프용 카운터(552) 및 파워 게이트 턴온용 카운터(553)를 포함한다.

[0328] 파워 게이트 턴오프용 카운터(552)에는 클럭 신호 CLK 및 전처리 종료 신호 1이 공급된다. 파워 게이트 턴온용 카운터(553)에는 클럭 신호 CLK 및 전처리 종료 신호 2가 입력된다.

[0329] 프로그램 메모리(551)는 외부로부터 프로그램이 입력되는 휘발성 메모리일 수 있거나, 또는 불휘발성 메모리일 수 있다.

[0330] 프로그램 메모리(551)에 저장된 프로그램에 의해 예를 들어, 전원 공급 제어 스위치들(121 내지 123) 및 그에 접속되는 CPU(111), 메모리(112), 및 신호 처리 회로(113) 등의 회로들의 상승(rising) 및 하강(falling)의 순서 및 준비 시간을 설정할 수 있다. 프로그램의 재기입에 의해 순서 및 준비 시간을 변경할 수 있으므로, 내부 회로의 변경 없이 설정의 유연성을 확보할 수 있다.

[0331] 여기에서는 준비 시간을 프로그램에 의해 변경하는 경우의 구성과 흐름도를 설명한다.

[0332] 먼저, 이 경우의 구성은, 도 21에 도시된 바와 같이 콘트롤러(150)가 프로그램 메모리(551), 파워 게이트 턴오프용 카운터(552), 및 파워 게이트 턴온용 카운터(553)를 포함한다.

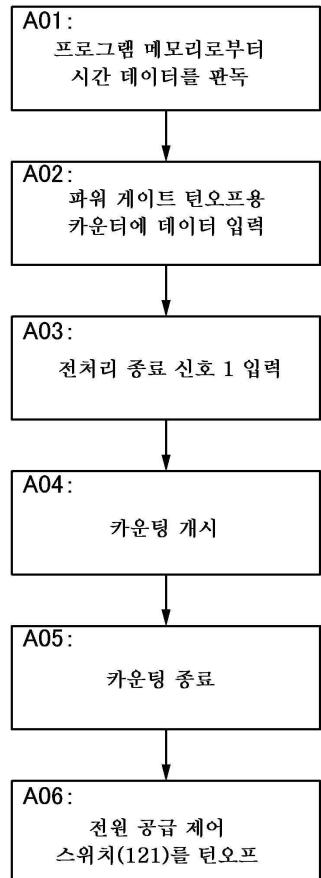

[0333] 이어서, 파워 게이트를 턴오프시킬 경우를 설명하기 위한 흐름도가 도 22의 (a)에 도시된다. 프로그램 메모리(551)로부터 준비 시간에 관한 데이터를 판독한다(A01: 프로그램 메모리로부터 시간 데이터를 판독). 이어서, 파워 게이트 턴오프용 카운터(552) 및 파워 게이트 턴온용 카운터(553)에 그 데이터를 입력한다(A02: 파워 게이트 턴오프용 카운터에 데이터 입력). 그 다음에, 전처리 종료 신호 1이 입력되면(A03: 전처리 종료 신호 1 입력), 파워 게이트 턴오프용 카운터(552)가 카운팅을 개시한다(A04: 카운팅 개시). 카운팅이 프로그램 메모리(551)로부터 입력된 카운트 수에 도달하면, 파워 게이트 턴오프용 카운터(552)가 카운팅을 정지하고(A05: 카운팅 종료), 전원 공급 제어 스위치(121)를 턴오프하기 위한 신호를 출력한다(A06: 전원 공급 제어 스위치(121)를 턴오프). 프로그램 메모리(551)의 콘텐츠를 변경함으로써, 준비 시간은 적절히 변경될 수 있다.

[0334] 전원 공급 제어 스위치(121)를 턴온할 경우를 설명하기 위한 흐름도가 도 22의 (b)에 도시된다. 프로그램 메모리(551)로부터 준비 시간에 관한 데이터를 판독한다(B01: 프로그램 메모리로부터 시간 데이터를 판독). 이어서, 파워 게이트 턴오프용 카운터(552) 및 파워 게이트 턴온용 카운터(553)에 그 데이터를 입력한다(B02: 파워 게이트 턴온용 카운터에 데이터 입력). 그 다음에, 전처리 종료 신호 2가 입력되면(B03: 전처리 종료 신호 2 입력), 파워 게이트 턴온용 카운터(553)가 카운팅을 개시한다(B04: 카운팅 개시). 카운팅이 프로그램 메모리(551)로부터 입력된 카운트 수에 도달하면, 파워 게이트 턴온용 카운터(553)가 카운팅을 정지하고(B05: 카운팅 종료), 전원 공급 제어 스위치(121)를 턴온하기 위한 신호를 출력한다(B06: 전원 공급 제어 스위치(121)를 턴온). 프로그램 메모리(551)의 콘텐츠를 변경함으로써, 준비 시간은 적절히 변경될 수 있다.

[0335] 흐름도들에 따라, 프로그램의 변경만으로 설정들을 적절히 바꿀 수 있다.

[0336] 본 출원은, 2012년 1월 23일, 2012년 1월 23일, 및 2012년 5월 3일자로 각각 일본 특허청에 출원된 일본 특허 출원 제2012-011120호, 제2012-011124호, 및 제2012-105538호에 기초하며, 그 전체 내용들이 본 명세서에 참조로 원용된다.

### 부호의 설명

[0337] 21: 트랜지스터, 22: 트랜지스터, 100: 반도체 장치, 100A: 마이크로 컴퓨터, 101: 입력 장치, 102: 출력 장치, 110: CPU, 111: CPU, 112: 메모리, 113: 신호 처리 회로, 113A: 화상 처리 회로, 114: 메모리, 121: 전원 공급 제어 스위치, 122: 전원 공급 제어 스위치, 123: 전원 공급 제어 스위치, 124: 전원 공급 제어 스위치, 150: 콘트롤러, 151: 인터페이스부, 152: 클럭 생성부, 153: 출력 신호 제어부, 154: 버퍼부, 155: 카운터 회로, 171: 터치 패널, 172: 터치 패널 콘트롤러, 173: 키보드, 174: 키보드 콘트롤러, 181: 디스플레이, 182: 디스플레이 콘트롤러, 190: 전원, 200: 메모리 셀, 211: 트랜지스터, 212: 트랜지스터, 213: 용량 소자, 300: CPU, 301: 회로, 302: 회로, 303: 회로, 304: CPU 제어부, 305: 레지스터 세트, 306: 계산 유닛, 307: 어드레스 버퍼, 308: 스테이트 생성부, 309: 레지스터, 310: ALU, 400: 반도체 기판, 401: 소자 분리용 절연막, 402: 불순물 영역, 403: 불순물 영역, 404: 게이트 전극, 405: 게이트 절연막, 409: 절연막, 410: 배선, 411: 배선, 412: 배선, 415: 배선, 416: 배선, 417: 배선, 420: 절연막, 421: 배선, 430: 반도체막, 431: 게이트 절연막, 432: 도전막, 433: 도전막, 434: 게이트 전극, 435: 도전막, 441: 절연막, 443: 도전막, 500: 버퍼, 501: 레벨 시프터, 502: 레벨 시프터, 551: 프로그램 메모리, 552: 파워 게이트 턴오프용 카운터, 553: 파워 게이트 턴온용 카운터, 601: 플립 플롭, 602: 메모리 회로, 603: 셀렉터, 621: 데이터 유지부, 622: 데이터 판독부, 631: 트랜지스터, 632: 용량 소자, 633: 트랜지스터, 634: 트랜지스터, 635: 트랜지스터, 636: 인버터, 637: 용량 소자, 700: 소자 형성층, 701: 절연층, 711: 반도체층, 712a: 영역, 712b: 영역, 713: 채널 형성 영역, 714: 절연층, 715: 도전층, 716a: 절연층, 716b: 절연층, 717: 절연층, 718a: 도전층, 718b: 도체층, 719: 절연층, 750: 소자 형성층, 751: 도전층, 752: 절연층, 753: 절연층, 754: 반도체층, 755a: 도전층, 755b: 도체층, 756a: 도전층, 756b: 도체층, 757: 절연층, 801: 트랜지스터, 802: 트랜지스터, 810: 기판, 811: 절연층, 813: 단결정 실리콘층, 814: 도전층, 815: 절연층, 816: 절연층, 817: 절연층, 818: 도전층, 1011: 하우징, 1012: 패널, 1013: 버튼, 1014: 스피커, 1021a: 하우징, 1021b: 하우징, 1022a: 패널, 1022b: 패널, 1023: 헌지, 1024: 버튼, 1025: 접속 단자, 1026: 저장 매체 삽입부, 1027: 스피커, 1031: 하우징, 1032: 패널, 1033: 버튼, 1034: 스피커, 1035: 상판, 1041: 하우징, 1042: 패널, 1043: 지지대, 1044: 버튼, 1045: 접속 단자, 1046: 스피커, 1050: 전자 기기, 1051: 하우징, 1052: 냉장고 도어, 1053: 냉동고 도어, 1060: 실내기, 1061: 하우징, 1062: 송풍구, 1064: 실외기, 1100: 프로그램 메모리, 1110: 레지스터, 1130: 레지스터

## 도면

## 도면1

## 도면2

## 도면3

## 도면4

도면5

도면6

도면7

도면8

## 도면9

## 도면10

## 도면11

## 도면12

도면13

도면14

도면15

## 도면16

(a)

(b)

(c)

(d)

(e)

(f)

도면17

도면18

도면19

도면20

도면21

## 도면22

(a)

(b)