(19) 日本国特許庁(JP)

## (12) 公開特許公報(A)

(11) 特許出願公開番号

特開2005-341663

(P2005-341663A)

(43) 公開日 平成17年12月8日(2005.12.8)

(51) Int.C1.<sup>7</sup>

H02H 3/08

G05F 1/10

H02H 3/087

H02H 7/20

F 1

H02H 3/08

G05F 1/10

H02H 3/087

H02H 7/20

テーマコード(参考)

5 G004

5 G053

5 H410

審査請求 未請求 請求項の数 3 O L (全 7 頁)

(21) 出願番号

特願2004-154341 (P2004-154341)

(22) 出願日

平成16年5月25日 (2004.5.25)

(71) 出願人 000006895

矢崎総業株式会社

東京都港区三田1丁目4番28号

(74) 代理人 100060690

弁理士 瀧野 秀雄

(74) 代理人 100097858

弁理士 越智 浩史

(74) 代理人 100108017

弁理士 松村 貞男

(74) 代理人 100075421

弁理士 垣内 勇

(72) 発明者 渡辺 修一

愛知県豊田市福受町上ノ切159-1 矢崎部品株式会社内

最終頁に続く

(54) 【発明の名称】過電流検出装置

## (57) 【要約】

【課題】脈動電流を発生する負荷が接続されている場合やノイズ発生時等に、誤検出の発生を防止することができる過電流検出装置を提供する。

【解決手段】所定の負荷3に流れる過電流を検出する装置であって、入力信号を所定の基準値と比較する比較回路CMP1と、負荷3に流れる電流に対応する信号をフィルタリングし、これを入力信号として比較回路CMP1に与える、RC積分回路で構成されるフィルタ回路R4、C1を含む。特に、負荷3に直列的に接続された第1FET、及びこの第1FETに並列的に接続されて、負荷3に流れる電流に対応する信号をセンスソース端子Sから出力する第2FET、で構成されるマルチソースFET回路1と、センスソース端子Sとアースとの間に介接された過電流検出閾値抵抗R5とを含み、過電流検出閾値抵抗R5にかかる電圧をフィルタ回路を通して検出し、これを比較回路CMP1に与えるようにしている。

【選択図】図1

## 【特許請求の範囲】

## 【請求項 1】

所定の負荷に流れる過電流を検出する装置であって、

前記過電流を検出するため、入力信号を所定の基準値と比較する比較回路と、

前記負荷に流れる電流に対応する信号をフィルタリングし、これを前記入力信号として

前記比較回路に与えるフィルタ回路と、

を含むことを特徴とする過電流検出装置。

## 【請求項 2】

請求項 1 記載の過電流検出装置において、

前記負荷に直列的に接続された第 1 F E T、及び前記第 1 F E T に並列的に接続されて

10

、前記負荷に流れる電流に対応する信号をセンスソース端子から出力する第 2 F E T、で

構成されるマルチソース F E T 回路と、

前記センスソース端子とアースとの間に介接された過電流検出閾値抵抗と、を含み、

前記過電流検出閾値抵抗にかかる電圧を前記フィルタ回路を通して検出し、これを前記

入力信号として前記比較回路に与える、

ことを特徴とする過電流検出装置。

## 【請求項 3】

請求項 1 又は請求項 2 記載の過電流検出装置において、

前記フィルタ回路を R C の積分回路で形成した、

ことを特徴とする過電流検出装置。

10

20

20

## 【発明の詳細な説明】

## 【技術分野】

## 【0001】

本発明は、所定の負荷に流れる過電流を検出する過電流検出装置に関し、特に、マルチ

ソース F E T 回路を用いた過電流検出装置に関する。

## 【背景技術】

## 【0002】

従来、ヒューズレスで関連する回路を保護するために、種々の過電流検出装置が提案さ

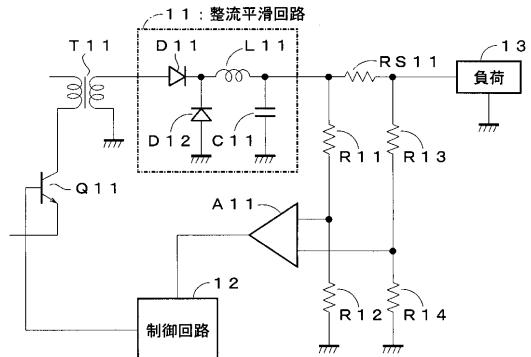

れている。図 2 は、この種の従来の過電流検出装置を示す回路図である。

30

## 【0003】

図 2 において、トランス T 1 1 の 2 次巻線に励起された電圧は、ダイオード D 1 1、D

1 2、チョークコイル L 1 1、コンデンサ C 1 1 からなる整流平滑回路 1 1 により、直流

電圧に変換されて負荷 1 3 に与えられる。負荷 1 3 に流れる電流に対応する、整流平滑回

路 1 1 と負荷 1 3 との間に介接された電流検出抵抗 R S 1 1 に発生する電圧は、分圧抵抗

R 1 1、R 1 2、分圧抵抗 R 1 3、R 1 4 を介して、オペアンプ A 1 1 に与えられる。

## 【0004】

オペアンプ A 1 1 は、電流検出抵抗 R S 1 1 に発生する電圧に応じた信号を制御回路 1

2 に帰還し、これに基づいて制御回路 1 2 がスイッチングトランジスタ Q 1 1 のオンオフ

比を制御することにより、負荷 1 3 に過電流が流れないようにしている。

30

## 【0005】

なお、このような先行技術文献情報としては次のものがある。

40

## 【特許文献 1】特開平 10 - 75526 号公報

## 【発明の開示】

## 【発明が解決しようとする課題】

## 【0006】

しかしながら、上述のような従来の過電流検出装置は、ヒューズレス化は達成するもの

の、過電流検出に電流検出抵抗 R S 1 1 を用いているため、種々の問題が発生する。すな

わち、負荷 1 3 に流れるピーク電流を検出することになるので、負荷 1 3 として、例えば

、ホーン等のような脈動電流を発生する負荷が接続されている場合には、適正電流と過電

流との判別ができず、誤検出が発生する。また、過電流閾値を超えるノイズが入力された

50

場合にも、誤検出が発生する。更に、負荷 13 に直列的に電流検出抵抗 R S 11 が接続しているため、発熱を引き起こす要因にもなる。

#### 【0007】

よって本発明は、上述した現状に鑑み、脈動電流を発生する負荷が接続されている場合やノイズ発生時等にも、誤検出の発生を防止することができる過電流検出装置を提供することを課題としている。

#### 【課題を解決するための手段】

#### 【0008】

上記課題を解決するためになされた請求項 1 記載の過電流検出装置は、所定の負荷に流れる過電流を検出する装置であって、前記過電流を検出するために、入力信号を所定の基準値と比較する比較回路と、前記負荷に流れる電流に対応する信号をフィルタリングし、これを前記入力信号として前記比較回路に与えるフィルタ回路と、を含むことを特徴とする。

#### 【0009】

請求項 1 記載の発明によれば、負荷に流れる電流に対応する信号をフィルタリングし、これを過電流を検出する比較回路の入力信号としている。これにより、ピーク電流ではなく、フィルタリングされた直流に近い入力信号が比較回路に与えられる。

#### 【0010】

上記課題を解決するためになされた請求項 2 記載の過電流検出装置は、請求項 1 記載の過電流検出装置において、前記負荷に直列的に接続された第 1 F E T、及び前記第 1 F E T に並列的に接続されて、前記負荷に流れる電流に対応する信号をセンスソース端子から出力する第 2 F E T、で構成されるマルチソース F E T 回路と、前記センスソース端子とアースとの間に介接された過電流検出閾値抵抗と、を含み、前記過電流検出閾値抵抗にかかる電圧を前記フィルタ回路を通して検出し、これを前記入力信号として前記比較回路に与える、ことを特徴とする。

#### 【0011】

請求項 2 記載の発明によれば、マルチソース F E T 回路のセンス端子とアースとの間に介接された過電流検出閾値抵抗と、を含み、過電流検出閾値抵抗にかかる電圧をフィルタ回路を通して検出し、これを入力信号として比較回路に与えるようにしている。

#### 【0012】

上記課題を解決するためになされた請求項 3 記載の過電流検出装置は、請求項 1 又は請求項 2 記載の過電流検出装置において、前記フィルタ回路を R C の積分回路で形成した、ことを特徴とする。

#### 【0013】

請求項 3 記載の発明によれば、フィルタ回路を R C の積分回路で形成しているので、接続される負荷に合わせたフィルタ定数を適宜設定することができる。

#### 【発明の効果】

#### 【0014】

請求項 1 記載の発明によれば、負荷に流れる電流に対応する信号をフィルタリングし、これを過電流を検出する比較回路の入力信号としている。これにより、ピーク電流ではなく、フィルタリングされた直流に近い入力信号が比較回路に与えられる。したがって、脈動電流を発生する負荷が接続されている場合やノイズ発生時にも、誤検出の発生を防止することができる。

#### 【0015】

請求項 2 記載の発明によれば、マルチソース F E T 回路のセンス端子とアースとの間に介接された過電流検出閾値抵抗と、を含み、過電流検出閾値抵抗にかかる電圧をフィルタ回路を通して検出し、これを入力信号として比較回路に与えるようにしている。したがって、誤検出の発生を防止できるうえに、発熱量も軽減できる。

#### 【0016】

請求項 3 記載の発明によれば、フィルタ回路を R C の積分回路で形成しているので、接

10

20

30

40

50

続される負荷に合わせたフィルタ定数を適宜設定することができる。したがって、適用範囲を広げることができる。

【発明を実施するための最良の形態】

【0017】

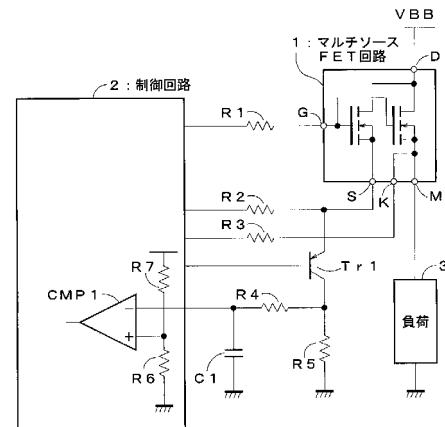

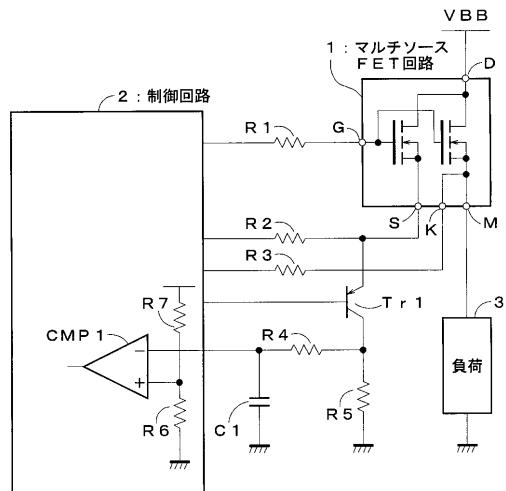

以下、本発明の実施の形態を図面に基づいて説明する。図1は、本発明の一実施形態に係る過電流検出装置を示す回路図である。

【0018】

図1に示すように、この過電流検出装置は、負荷3に接続されたマルチソースFET回路1、制御回路2、抵抗R4及びコンデンサC1からなるフィルタ回路を含んで構成される。

【0019】

マルチソースFET回路1は、詳しくは、電源VBBと負荷3との間に介接されている。マルチソースFET回路1は、メインソース端子Mに接続された負荷3に直列的に接続された第1FET、及びこの第1FETに並列的に接続されて、負荷3に流れる電流に対応する信号をセンスソース端子Sから出力する第2FET、で構成される。このような回路構成によると、センスソース端子Sからは、メインソース端子Mに接続された負荷3に流れる電流を分流して取り出すことができる。なお、Dはドレイン端子、Gはゲート端子、Kはケルビンソース端子を示す。

【0020】

マルチソースFET回路1のセンスソース端子S及びケルビンソース端子Kにはそれぞれ、抵抗R2及びR3が接続されている。センスソース端子Sと抵抗R2との間には、トランジスタTr1が並列的に接続され、そのコレクタ側とアースとの間には過電流検知閾値抵抗R5が介接されている。このコレクタ側及び抵抗R5の接続点と比較回路CMP1の入力端子との間には、フィルタ用抵抗R4及びフィルタ用コンデンサC1からなるフィルタ回路が接続されている。また、ゲート端子Gにはゲート抵抗R1が接続されている。

【0021】

このように、マルチソースFET回路のセンス端子Sとアースとの間に過電流検出閾値抵抗R5を介接し、過電流検出閾値抵抗R5にかかる電圧を比較回路CMP1に与えるようにしているので、発熱量を大きく軽減できる。

【0022】

制御回路2は、基準抵抗R6及びR7が基準端子に接続された過電流検出用の比較回路CMP1を含んで構成される。制御回路2は、例えば、IC化されており、図示しないチャージポンプ回路やドライバ回路を含んで構成するようにしてもよい。

【0023】

このような構成において、センスソース端子Sから出力される負荷3に流れる電流に対応する電流は、トランジスタTr1のエミッタ側に出力される。トランジスタTr1がオンされると、そのコレクタ側に接続された過電流検出閾値抵抗R5にかかる電圧は、抵抗R4及びコンデンサC1からなるフィルタ回路を通して検出され、比較回路の入力端子に与えられる。そして、比較回路CMP1において、基準抵抗R6及びR7で分圧された基準端子にかかる基準電圧と比較されて、比較回路CMP1から比較結果に応じた制御信号が出力される。

【0024】

この制御信号は、例えば、図2で示したように接続されたスイッチングトランジスタのオンオフ比を制御するために利用可能である。これにより、ヒューズレスで関連する回路を過電流から保護することができるようになる。

【0025】

このように、負荷3に流れる電流に対応する信号をフィルタリングし、これを過電流を検出する比較回路CMP1の入力信号としているので、ピーク電流ではなく、フィルタリングされた直流に近い入力信号が比較回路CMP1に与えられることになる。したがって、脈動電流を発生する負荷が接続されている場合やノイズ発生時にも、誤検出の発生を防

止することができる。

【0026】

特に、フィルタ回路をRCの積分回路で形成しているので、接続される負荷に合わせたフィルタ定数を適宜設定することができる。上述のように、直流に近い信号になるようにフィルタリングするのみならず、ピーク電流に近い電流も検出可能なように、RC時定数を変更して検出感度を上げることも可能である。したがって、フィルタ回路をRCの積分回路で形成することにより、この過電流検出装置の適用範囲を広げることができる。標準化促進の一助ともなる。

【0027】

また、比較回路CMP1の出力信号は、IC化された制御回路2の内部に出されるので、多機能化に適している。例えば、制御回路2内でロジックを組むことにより、過電流検出してから必要な時間だけ遅延させたり、所定のゲート入力と比較してから、過電流を示す制御信号を出力するというような誤検出防止機能を付加することも可能となる。

【0028】

以上のように、本発明の実施形態によれば、脈動電流を発生する負荷が接続されている場合やノイズ発生時等にも、誤検出の発生を防止することができる過電流検出装置を提供することができる。また、トランジスタ回路を用いているので、ヒューズレス、メンテナンスフリーであり、スペース効率もよいことはいうまでもない。

【図面の簡単な説明】

【0029】

【図1】本発明の一実施形態に係る過電流検出装置を示す回路図である。

【図2】従来の過電流検出装置を示す回路図である。

【符号の説明】

【0030】

- 1 マルチソースFET回路

- 2 制御回路

- 3 負荷

- R4、C1 フィルタ回路

10

20

【図1】

【図2】

---

フロントページの続き

F ターム(参考) 5G004 AA04 AB02 BA03 BA04 DA04 DB03 DC01

5G053 AA01 BA01 BA04 CA04 DA01 EC03

5H410 BB01 BB05 CC02 DD02 EA11 EA32 EA38 FF05 FF25 GG05

HH01 LL06 LL15 LL20