(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第5325446号

(P5325446)

(45) 発行日 平成25年10月23日(2013.10.23)

(24) 登録日 平成25年7月26日(2013.7.26)

(51) Int.Cl.

H01L 29/786 (2006.01)

F 1

H01L 29/78 618 F

H01L 29/78 618 B

請求項の数 6 (全 14 頁)

(21) 出願番号 特願2008-106586 (P2008-106586)

(22) 出願日 平成20年4月16日 (2008.4.16)

(65) 公開番号 特開2009-260002 (P2009-260002A)

(43) 公開日 平成21年11月5日 (2009.11.5)

審査請求日 平成23年2月4日 (2011.2.4)

(73) 特許権者 000005108

株式会社日立製作所

東京都千代田区丸の内一丁目6番6号

(74) 代理人 100075959

弁理士 小林 保

(72) 発明者 河村 哲史

東京都国分寺市東恋ヶ窪一丁目280番地

株式会社 日立製作所 中央研究所内

(72) 発明者 佐藤 健史

東京都国分寺市東恋ヶ窪一丁目280番地

株式会社 日立製作所 中央研究所内

(72) 発明者 波多野 瞳子

東京都国分寺市東恋ヶ窪一丁目280番地

株式会社 日立製作所 中央研究所内

最終頁に続く

(54) 【発明の名称】半導体装置及びその製造方法

## (57) 【特許請求の範囲】

## 【請求項 1】

金属酸化物膜をチャネルに用いる半導体装置が同一の基板上に複数形成され、

しきい値電圧の高い第1群の半導体装置としきい値電圧の低い第2群の半導体装置を備え、

前記第1群の半導体装置および前記第2群の半導体装置は、基板上に、ゲート電極、ゲート絶縁膜、前記金属酸化物膜が順次形成され、その上にソース電極及びドレイン電極が形成されたボトムゲート型薄膜トランジスタであって、

前記第1群の半導体装置および前記第2群の半導体装置における前記金属酸化物膜中に、前記ソース電極を重畳する領域とするソース領域と、前記ドレイン電極を重畳する領域とするドレイン電極と、前記ドレイン領域と前記ソース領域の間の領域とするチャンネル領域と、を有し、

少なくとも前記第1群の半導体装置において、前記チャンネル領域は、半導体性を示し、かつ表面から深さが増すにつれて酸素濃度が低くなっている、

少なくとも前記第1群の半導体装置において、前記ソース領域および前記ドレイン領域は、前記チャネル領域に比べて酸素濃度が低く導電性の高いものであり、前記表面からの深さ方向に対して酸素濃度が一定となっている、

前記第2群の半導体装置におけるチャンネル領域上には、さらに、保護膜が形成されている

ことを特徴とする半導体装置。

10

20

## 【請求項 2】

請求項 1 に記載の半導体装置が基板に形成されていることを特徴とする表示装置。

## 【請求項 3】

請求項 1 に記載の半導体装置が基板に形成されていることを特徴とする記憶装置。

## 【請求項 4】

しきい値電圧の高い第 1 群の半導体装置としきい値電圧の低い第 2 群の半導体装置を同一基板上に形成させた請求項 1 に記載の半導体装置の製造方法であって、

基板上に第 1 および第 2 のゲート電極を形成する工程と、

前記第 1 および前記第 2 のゲート電極と前記基板の表面とを覆うようにゲート絶縁膜を形成する工程と、

前記ゲート絶縁膜上に前記第 1 および前記第 2 のゲート電極を跨るように第 1 および第 2 の金属酸化物膜を形成する工程と、

前記第 1 の金属酸化物膜上に第 1 のソース電極と第 1 のドレイン電極を形成し、前記第 2 の金属酸化物膜上に第 2 のソース電極と第 2 のドレイン電極を形成する工程と、

前記第 2 のソース電極と前記第 2 のドレイン電極の間の前記第 2 の金属酸化物膜上に保護膜を形成する工程と、

前記第 1 のソース電極及び前記第 1 のドレイン電極をマスクにして、前記第 1 のソース電極と前記第 1 のドレイン電極の間の前記第 1 の金属酸化物膜に酸素を導入する工程と、

を有することを特徴とする半導体装置の製造方法。

## 【請求項 5】

前記酸素導入は、酸素プラズマ照射、酸素雰囲気アニール、ラジカル酸化のうちいずれかを用いて行う

ことを特徴とする請求項 4 に記載の半導体装置の製造方法。

## 【請求項 6】

前記第 1 および前記第 2 のソース電極と前記第 1 および前記第 2 のドレイン電極とを形成する工程の後であり、前記保護膜を形成する工程の前にて、

前記第 1 および前記第 2 のソース電極と前記第 1 および前記第 2 のドレイン電極とをマスクにして、前記第 1 のソース電極と前記第 1 のドレイン電極の間の前記第 1 の金属酸化物膜および前記第 2 のソース電極と前記第 2 のドレイン電極の間の前記第 2 の金属酸化物膜のそれぞれに対して酸素を導入する工程と、

をさらに有することを特徴とする請求項 4 または 5 に記載の半導体装置の製造方法。

## 【発明の詳細な説明】

## 【技術分野】

## 【0001】

本発明は半導体装置及びその製造方法に係り、特に、金属酸化物膜をチャネルに用いる電界効果型トランジスタ及びその製造方法に関する。

## 【背景技術】

## 【0002】

近年、金属酸化物膜をチャネル層に用いて電界効果型トランジスタ (Field Effect Transistor : 以下、この明細書では単に FET と称する場合がある) を形成しようとする試みが行なわれている。特に、ZnO、InGaZnO、ZnSnOなどをチャネル層に用いた薄膜トランジスタ (Thin Film Transistor : 以下、この明細書では単に TFT と称する場合がある) の開発が行なわれているが、その主な原動力は、製造工程が低温かつ簡易であることがある。この低温、簡易という特長を活かし、プラスチックフィルムなどのいわゆるフレキシブル基板上に直接 TFT を形成する研究開発も活発に進められている。

## 【0003】

現在最も広く使われている TFT は、アモルファスまたは多結晶シリコンをチャネル層に用いたものである。しかしながら、シリコン TFT はデバイス作製に高温プロセスが不可欠で、フレキシブル基板上への作製に不向きという問題がある。

## 【0004】

10

20

30

40

50

酸化物 TFT では、通常、金属や ITO (Indium Tin Oxide) などチャネル層とは異なる材料からなる導電膜をチャネル層に直付けすることで、ソース電極及びドレイン電極を形成する。そのため、半導体である金属酸化物膜と導電膜との間のコンタクト抵抗や、チャネル領域とソース電極あるいはドレイン電極との間の寄生抵抗が TFT 特性の向上を妨げる原因になっている。また、コンタクト抵抗や寄生抵抗が大きいと、そのばらつきは TFT 特性ばらつきの大きな要因になり、回路や表示装置などを形成した際の性能向上を妨げる原因となる。特に、TFT をアナログ的に用いる有機 LED (Organic Light Emitting Diode : OLED) 表示装置では、TFT のばらつきが画質を大きく劣化させる。

#### 【0005】

これらの理由より、酸化物 TFT では、コンタクト抵抗及び寄生抵抗を低減すること、並びにそれらのばらつきを低減することが求められている。

10

#### 【0006】

上記課題を解決するため、特許文献 1 及び特許文献 2 では、金属酸化物膜中の所望の領域の導電性を高めてソース領域及びドレイン領域を形成することで、コンタクト抵抗及びそのばらつきを低減する方法が開示されている。同時に、自己整合的にソース領域及びドレイン領域を形成し、寄生抵抗及びそのばらつきも低減する方法が開示されている。

#### 【0007】

金属酸化物膜の導電性は膜中の酸素濃度や不純物水素の濃度で制御可能なことが知られており、上記特許文献 1 及び特許文献 2 ではこれを応用している。金属酸化物膜中では、酸素欠損あるいは不純物水素が n 型ドナーとして作用し膜中にキャリア電子を生成するため、酸素濃度が低いほど、あるいは水素濃度が高いほど、導電性が高まり膜の抵抗が低くなる。

20

【特許文献 1】特開 2007-073699 号

【特許文献 2】特開 2007-250983 号

#### 【発明の開示】

#### 【発明が解決しようとする課題】

#### 【0008】

特許文献 1 では、金属酸化物膜中の所望の領域に短波長光または高エネルギーの粒子を照射して酸素欠損を生じさせることでソース領域及びドレイン領域を形成し、コンタクト抵抗及びそのばらつきを低減する方法が開示されている。開示されているトップゲート型 TFT の製造方法によれば、ゲート電極に対して自己整合的にソース領域及びドレイン領域が形成されるため、寄生抵抗及びそのばらつきも低減することができる。

30

#### 【0009】

しかし、特許文献 1 に開示の方法では、金属酸化物膜成膜時にチャネル領域のキャリア濃度が決まるため、その後の工程、たとえばソース領域及びドレイン領域、あるいはソース電極及びドレイン電極を形成した後に、TFT の閾値電圧 (Vth) を調整することができないという問題がある。そのため、TFT 量産時に歩留りの低下を起こしやすいという問題や、たとえば TFT を適用する製品種が変わったときのプロセス修正が困難という問題がある。また、同一基板上に閾値電圧 (Vth) の異なる TFT を作り分けることができず、回路設計の自由度が低いという問題もある。さらに、一般的にボトムゲート型 TFT の方が製造が容易で量産には適しているが、開示されている方法ではボトムゲート型 TFT を製造することができないという問題もある。

40

#### 【0010】

一方、特許文献 2 では、金属酸化物膜中の所望の領域に水素または重水素を導入することでソース領域及びドレイン領域を形成し、コンタクト抵抗及びそのばらつきを低減する方法が開示されている。開示されているトップゲート型 TFT の製造方法の場合、ゲート電極に対して自己整合的にソース領域及びドレイン領域が形成され、またボトムゲート型 TFT の場合、ソース電極及びドレイン電極に対して自己整合的にソース領域及びドレイン領域が形成されるため、寄生抵抗及びそのばらつきも低減することができる。

#### 【0011】

50

しかし、特許文献 2 に開示の方法でも、金属酸化物膜成膜時にチャネル領域のキャリア濃度が決まるため、その後の工程、たとえばソース領域及びドレイン領域、あるいはソース電極及びドレイン電極を形成した後に、TFT の閾値電圧 (V<sub>th</sub>) を調整することができないという問題がある。そのため、TFT 量産時に歩留りの低下を起こしやすいという問題や、たとえば TFT を適用する製品種が変わったときのプロセス修正が困難という問題もある。また、トップゲート型、ボトムゲート型いずれの構造においても、同一基板上に V<sub>th</sub> の異なる TFT を作り分けることができず、回路設計の自由度が低いという問題もある。さらに、開示されているボトムゲート型 TFT の場合、リフトオフ工程においてチャネル領域が有機溶媒にさらされるため、特性の劣化やばらつきの増大を免れないものとなっている。特に、有機溶媒との化学反応によりチャネル領域表面から酸素が引き抜かれたり、有機溶媒中の水素がチャネル領域に侵入したりすることによる、バックチャネルの形成が懸念される。バックチャネルとは、チャネル領域内のゲート電極とは反対側の面に形成される電流経路のことで、オフリーカ電流増大の原因になる。

【0012】

本発明は、このような事情に基づいてなされたものであり、その目的は、次に示すようになっている。

【0013】

本発明の第 1 の目的は、コンタクト抵抗と寄生抵抗、並びにそれらのばらつきが小さい半導体装置及びその製造方法を提供することにある。

【0014】

本発明の第 2 の目的は、ソース領域及びドレイン領域、あるいはソース電極及びドレイン電極を形成した後に、V<sub>th</sub> を調整することができる半導体装置及びその製造方法を提供することにある。

【0015】

本発明の第 3 の目的は、同一基板上に V<sub>th</sub> の異なる酸化物 FET を作り分けることができる半導体装置及びその製造方法を提供することにある。

【0016】

本発明の第 4 の目的は、バックチャネルの形成を抑制し得る半導体装置及びその製造方法を提供することにある。

【課題を解決するための手段】

【0017】

本願において開示される発明のうち、代表的なものの概要を簡単に説明すれば、以下のとおりである。

【0018】

(1) 本発明による半導体装置は、たとえば、金属酸化物膜をチャネルに用いる半導体装置が同一の基板上に複数形成され、

しきい値電圧の高い第 1 群の半導体装置としきい値電圧の低い第 2 群の半導体装置を備え、

前記第 1 群の半導体装置および前記第 2 群の半導体装置は、基板上に、ゲート電極、ゲート絶縁膜、前記金属酸化物膜が順次形成され、その上にソース電極及びドレイン電極が形成されたボトムゲート型薄膜トランジスタであって、

前記第 1 群の半導体装置および前記第 2 群の半導体装置における前記金属酸化物膜中に、前記ソース電極を重畳する領域とするソース領域と、前記ドレイン電極を重畳する領域とするドレイン電極と、前記ドレイン領域と前記ソース領域の間の領域とするチャンネル領域と、を有し、

少なくとも前記第 1 群の半導体装置において、前記チャンネル領域は、半導体性を示し、かつ表面から深さが増すにつれて酸素濃度が低くなっている、

少なくとも前記第 1 群の半導体装置において、前記ソース領域および前記ドレイン領域は、前記チャネル領域に比べて酸素濃度が低く導電性の高いものであり、前記表面からの深さ方向に対して酸素濃度が一定となっており、

10

20

30

40

50

前記第2群の半導体装置におけるチャンネル領域上には、さらに、保護膜が形成されていることを特徴とする。

【0023】

(2) 本発明による表示装置は、(1)に記載の半導体装置が基板に形成されていることを特徴とする。

【0024】

(3) 本発明による記憶装置は、(1)または(2)に記載の半導体装置が基板に形成されていることを特徴とする。

【0025】

(4) 本発明による半導体装置の製造方法は、しきい値電圧の高い第1群の半導体装置としきい値電圧の低い第2群の半導体装置を同一基板上に形成させた請求項1に記載の半導体装置の製造方法であって、

基板上に第1および第2のゲート電極を形成する工程と、

前記第1および前記第2のゲート電極と前記基板の表面とを覆うようにゲート絶縁膜を形成する工程と、

前記ゲート絶縁膜上に前記第1および前記第2のゲート電極を跨るように第1および第2の金属酸化物膜を形成する工程と、

前記第1の金属酸化物膜上に第1のソース電極と第1のドレイン電極を形成し、前記第2の金属酸化物膜上に第2のソース電極と第2のドレイン電極を形成する工程と、

前記第2のソース電極と前記第2のドレイン電極の間の前記第2の金属酸化物膜上に保護膜を形成する工程と、

前記第1のソース電極及び前記第1のドレイン電極をマスクにして、前記第1のソース電極と前記第1のドレイン電極の間の前記第1の金属酸化物膜に酸素を導入する工程と、

を有することを特徴とする。

【0028】

(5) 本発明による半導体装置の製造方法は、(4)の半導体装置の製造方法にあって、前記酸素導入は、酸素プラズマ照射、酸素雰囲気アニール、ラジカル酸化のうちいずれかを用いて行うことを特徴とする。

【0029】

(6) 本発明による半導体装置の製造方法は、前記第1および前記第2のソース電極と前記第1および前記第2のドレイン電極とを形成する工程の後であり、前記保護膜を形成する工程の前ににおいて、

前記第1および前記第2のソース電極と前記第1および前記第2のドレイン電極とをマスクにして、前記第1のソース電極と前記第1のドレイン電極の間の前記第1の金属酸化物膜および前記第2のソース電極と前記第2のドレイン電極の間の前記第2の金属酸化物膜のそれぞれに対して酸素を導入する工程と、

をさらに有する(4)または(5)に記載されていることを特徴とする。

【0031】

なお、本発明は以上の構成に限定されず、本発明の技術思想を逸脱しない範囲で種々の変更が可能である。

【発明の効果】

【0032】

このような半導体装置及びその製造方法によれば、コンタクト抵抗と寄生抵抗、並びにそれらのばらつきの低減することで、酸化物FETの特性向上とばらつき低減を図ることができる。

【0033】

また、ソース領域及びドレイン領域、あるいはソース電極及びドレイン電極を形成した後にVthを調整することで、TFT量産時の歩留り低下を抑制したり、プロセス修正を容易化したりすることができる。

【0034】

10

20

30

40

50

また、同一基板上に  $V_t h$  の異なる酸化物 FET を作り分けることで、回路設計の自由度を高めることができる。

【0035】

さらには、ボトムゲート型酸化物 TFT のバックチャネルの形成を抑制しオフリード電流を低減することで、半導体装置の消費電流を低減することができる。

【0036】

なお、本発明によるその他の効果については、明細書全体の記載から明らかにされるようになる。

【発明を実施するための最良の形態】

【0037】

以下、本発明による半導体装置及びその製造方法の実施例について図面を用いて説明をする。

【0038】

実施例 1

(構成及び製造方法)

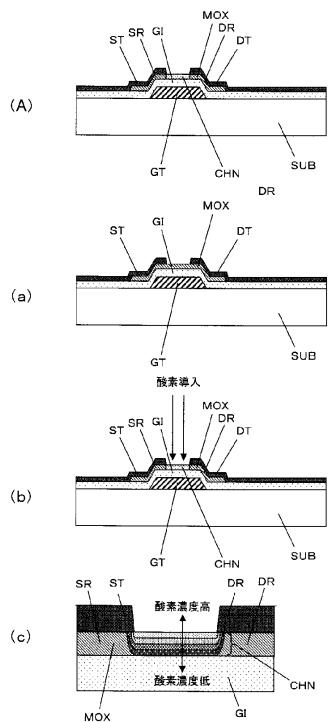

図 1 (A) は、本発明による半導体装置の実施例 1 を示した構成図である。半導体装置としていわゆるボトムゲート型酸化物 TFT を掲げている。図 1 (A) に示すように、基板 SUB 上にゲート電極 GT が形成されている。そして、該基板 SUB の上面に前記ゲート電極 GT をも被ってゲート絶縁膜 GI が形成されている。また、前記ゲート絶縁膜 GI 上に少なくとも前記ゲート電極 GT を跨るようにして金属酸化物膜 MOX が形成されている。さらに、前記金属酸化物膜 MOX に直接に接触させてソース電極 ST 及びドレイン電極 DT が形成されている。前記ソース電極 ST とドレイン電極 DT は、少なくともゲート電極 GT の直上で分離され、この分離部を間にて対向するように形成されている。ここで、前記金属酸化物膜 MOX は、前記ソース電極 ST とドレイン電極 DT の間の領域においてチャネル領域 CHN を構成し、このチャネル領域 CHN には半導体性を示し、かつ表面から深さが増すにつれて酸素濃度が低くなるように構成されている。

【0039】

図 1 (a)、(b) は、図 1 (A) に示した半導体装置の製造方法の実施例 1 を示した説明図である。まず、一般的な製造プロセスを用いて図 1 (a) に示す構造を作製する。すなわち、基板 SUB 上にゲート電極 GT を形成する。そして、該基板 SUB の上面に前記ゲート電極 GT をも被ってゲート絶縁膜 GI を形成する。その後、前記ゲート絶縁膜 GI 上に少なくとも前記ゲート電極 GT を跨るようにして金属酸化物膜 MOX を形成する。さらに、前記金属酸化物膜 MOX に直接に接触させてソース電極 ST 及びドレイン電極 DT を形成する。前記ソース電極 ST とドレイン電極 DT は、少なくともゲート電極 GT の直上で分離され、この分離部を間にて対向するように形成されている。これにより、金属酸化物膜 MOX は、前記ソース電極 ST とドレイン電極 DT の分離部において、外部に露出された状態になっている。

【0040】

次に、図 1 (b) に示すように、ソース電極 ST、ドレイン電極 DT の前記分離部を通して金属酸化物膜 MOX の一部に酸素を導入する。この場合、前記ソース電極 ST およびドレイン電極 DT はマスクとなり、該ソース電極 ST とドレイン電極 DT の間の前記金属酸化物膜 MOX にはチャネル領域 CHN が形成されるようになる。酸素を導入する方法としては、たとえば、酸素プラズマ照射、酸素雰囲気アニール、ラジカル酸化などが挙げられるが、その他の方法を用いてもよい。酸素を導入することで、金属酸化物膜 MOX 内の外部に露出された領域は、より酸素濃度の高い状態に変わる。金属酸化物膜中では、酸素欠損が n 型ドナーとして作用し、膜中にキャリア電子を生成するようになり導電性は低くなる。こうして形成された酸素濃度の高い領域が半導体性を示し、酸化物 TFT のチャネル領域として機能できる。前記チャネル領域 CHN を除く金属酸化物膜 MOX 内の領域は、前記ソース電極 ST と接続されるソース領域 SR、前記ドレイン電極 DT と接続されるドレイン領域 DR として形成される。

## 【0041】

なお、上述のように金属酸化物膜M O X内にチャネル領域C H Nを形成する場合、該金属酸化物膜M O Xの外側（上側）から酸素を導入するようにしていることから、前記チャネル領域C H Nの拡大図である図1（c）に示すように、外部に露出されている側で相対的に酸素濃度が高く、ゲート絶縁膜G I側にいくにつれて酸素濃度が低くなる。なお、図1（c）では、金属酸化物膜M O Xの深さ方向に沿って酸素濃度の変化していく過程を便宜上段差的に描画しているが、実際には滑らかな勾配を有して変化している。T F T動作の際にはゲート絶縁膜G Iとチャネル領域C H Nとの界面がチャネルの主要部分になり、主にここで電流が流れる。このため、本実施例のT F Tでは界面の酸素濃度を最適化できるようになる。この場合、界面より上方では必然的に酸素濃度がより高くなる。金属酸化物膜M O Xの膜厚や成膜条件などにもよるが、酸素濃度が最も高い領域（チャネル領域C H Nの上層）では、界面に比べて2倍以上酸素濃度が高いことが望ましい。また、ソース領域S R及びドレイン領域D Rに比べても2倍以上酸素濃度が高いことが望ましい。さらには、界面での酸素濃度はソース領域S R及びドレイン領域D Rでの酸素濃度の10倍以上、したがって、チャネル領域C H Nの上層での酸素濃度はソース領域S R及びドレイン領域D Rでの酸素濃度の20倍以上であるようにすることがより望ましい。10

## 【0042】

本実施例における基板S U Bは、たとえば、ガラス、石英、プラスチックフィルムなどの絶縁体からなり、必要に応じてゲート電極G Tが形成される側の表面に絶縁体膜のコーティングがなされている。ゲート電極G T、ソース電極S T、ドレイン電極D Tは、たとえば、モリブデン、クロム、タンクスチタン、アルミニウム、銅、チタン、ニッケル、タンタル、銀、亜鉛、あるいはその他の金属の単膜、それらの合金膜、それらの積層膜、あるいはITOなどの金属酸化物導電膜、あるいは前述の金属と金属酸化物導電膜の積層膜によって形成されている。ゲート電極G T、ソース電極S T、ドレイン電極D Tは、同一の材料から形成されても良いし、異なる材料から形成されても良い。絶縁膜G Iは、たとえば、SiO<sub>2</sub>、SiN、Al<sub>2</sub>O<sub>3</sub>、あるいはその他の絶縁膜によって形成されている。金属酸化物膜M O Xは、たとえば、ZnO、InGaZnO、ZnInO、ZnSnO、あるいは導電性を示すその他の金属酸化物によって形成されている。20

## 【0043】

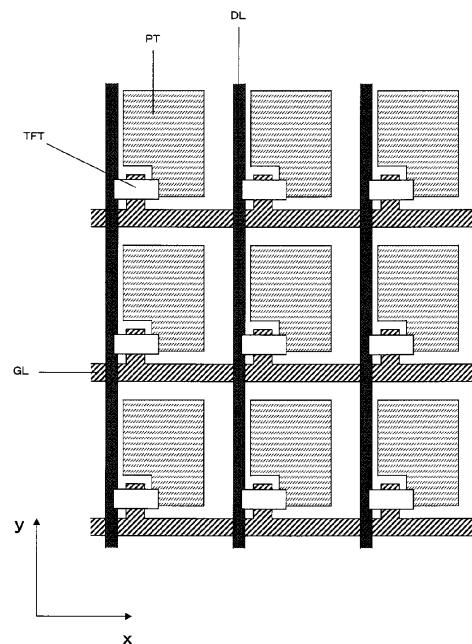

本実施例のT F Tは、たとえば図2に示すように、アクティブマトリクス型液晶表示装置のスイッチングトランジスタとして用いられる。図中x方向に延在するゲート線G Lに走査信号が供給されるとT F Tがオンし、このオンされたT F Tを通して、図中y方向に延在するデータ線D Lからの映像信号が画素電極P Tに供給される。なお、ゲート線G Lは図中y方向に並設され、データ線D Lは図中x方向に並設され、隣接する一対のゲート線G Lと隣接する一対のドレイン線D Lで囲まれる領域（画素領域）に前記画素電極P Tが配置されている。この場合、たとえばデータ線D Lがソース電極S Tと電気的に接続され、画素電極P Tがドレイン電極D Tと電気的に接続される。あるいは、データ線D Lがソース電極S Tを兼ね、画素電極P Tがドレイン電極D Tを兼ねても良い。また、液晶表示装置に限らずO L E D表示装置などの画素回路を構成するトランジスタとして用いても良い。30

## 【0044】

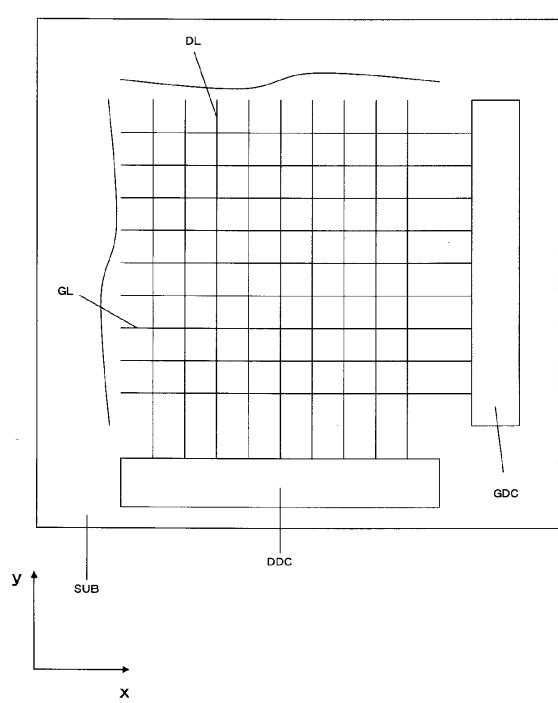

また、図3に示すように、基板S U B 1上に形成される表示装置や記憶装置などにおいて、その素子がアレイ状に複数配置されている場合、各素子のスイッチングや駆動用のトランジスタに前記酸化物T F Tを用いるのはもちろん、該酸化物T F Tのゲート電極G Tにつながるゲート線G Lに信号を送るゲート線駆動回路G D Cや、該酸化物T F Tのソース電極S Tにつながるデータ線D Lに信号を送るデータ線駆動回路D D Cを構成するトランジスタに用いても良い。この場合、各素子の酸化物T F Tと前記ゲート線駆動回路G D Cあるいは前記データ線駆動回路D D C内の酸化物T F Tを並行して形成することができる。

## 【0045】

10

20

30

40

50

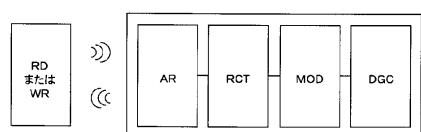

また、上述した酸化膜TFTを、たとえば図4に示す構成、すなわち、アンテナ共振回路AR、整流器RCT、変調器MOD、デジタル回路DGC、からなる無線タグを構成する各トランジスタに用いても良い。なお、無線タグはリーダRDまたはライタWRと無線で通信を行うことができるようになっている。酸化物TFTが低温で形成できることを活かして表示装置や記憶装置、無線タグなどをプラスチックフィルムなどのいわゆるフレキシブル基板上に形成した構成においても適用できる。

【0046】

(効果)

本実施例において、たとえば、金属酸化物膜MOXをあらかじめ導電性の高い膜として成膜しておけば、ソース領域SR及びドレイン領域DRでの寄生抵抗、並びにソース領域SRとソース電極ST、ドレイン領域DRとドレイン電極DTとの間のコンタクト抵抗を低くすることができる。これにより、良好な電気接続が得られ、酸化物FETの特性を向上することができる。

【0047】

また、ソース電極ST及びドレイン電極DTに対して、ソース領域SR、チャネル領域CHN、ドレイン領域DRが自己整合的に形成されるため、コンタクト抵抗と寄生抵抗のばらつきを低減し、ひいてはTFTのばらつきを低減することができる。

【0048】

また、ソース領域SR及びドレイン領域DR、並びにソース電極ST及びドレイン電極DTを形成した後に、チャネル領域CHNの形成、及びVth調整を行なうことができる。このため、TFT量産時の歩留り低下を抑制したり、プロセス修正を容易化したりすることができる。

【0049】

さらに、ゲート絶縁膜GIとチャネル領域CHNとの界面で酸素濃度が最適化され、それより上方では酸素濃度はより高くなっているため、いわゆるバックチャネルの形成を抑制し、オフリーケ電流を低減することができる。したがって、半導体装置の消費電流を低減することができる。

【0050】

実施例2

(構成及び製造方法)

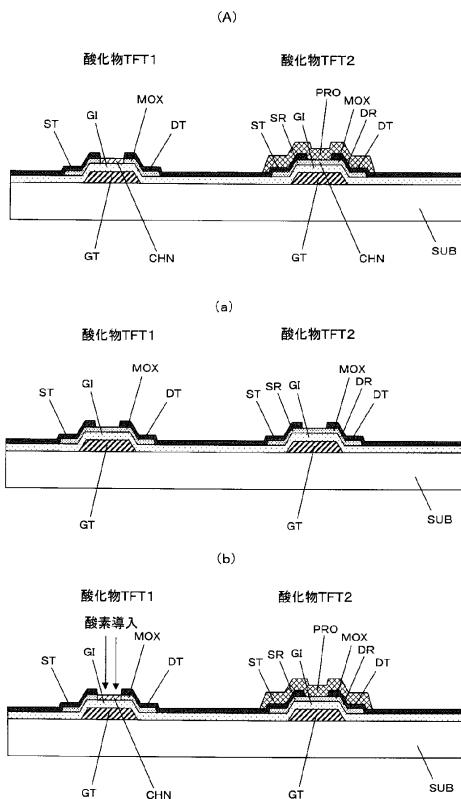

図5(A)は、本発明による半導体装置の実施例2を示す断面図である。図5(A)は、同一基板上にVthの異なる2種のボトムゲート型酸化物TFTを形成することを示した図となっている。

【0051】

すなわち、基板SUB1の上面に酸化物TFT1および酸化物TFT2が形成されている。これら酸化物TFT1および酸化物TFT2は、それらを構成する材料層の積層構造がほぼ同じとなっており、前記酸化物TFT1においてそのVthが高く形成され、前記酸化物TFT2においてそのVthが低く形成されている。すなわち、前記酸化物TFT1は、そのチャネル領域CHNにおいて、ソース領域SR、ドレイン領域DRに比べて酸素濃度が高く導入され、前記酸化物TFT2は、そのチャネル領域CHNにおいて、ソース領域SR、ドレイン領域DRに比べて酸素濃度差がなく構成されている。

【0052】

図5(a)、(b)は、図5(A)に示した半導体装置の製造方法の実施例1を示した説明図である。まず、一般的な製造プロセスを用いて、前記酸化物TFT1および酸化物TFT2を図5(a)に示した構造に形成する。この段階では、まだ、前記酸化物TFT1および酸化物TFT2の各チャネル領域に酸素が導入されていないものとなっている。次に、図5(b)に示すように、酸化物TFT2の金属酸化物膜MOXの少なくともチャネル形成領域上に保護膜PROを被って形成する。そして、酸化物TFT1において、その金属酸化物MOXに酸素を導入する。これにより、酸化物TFT1は、そのチャネル領域CHNにおいてソース領域SRおよびドレイン領域DRに比べて酸素濃度が高く、Vth

10

20

30

40

50

$h$  が高い特性として得られ、酸化物 TFT 2 は、ソース領域、チャネル領域、およびドレイン領域間で酸素濃度の差がほとんどなく、 $V_{th}$  が低い特性として得られるようになる。

### 【0053】

なお、図 5 (A) においては、基板 SUB 1 において、酸化物 TFT 1 と酸化物 TFT 2 からなる 2 個の酸化物 TFT を示したものである。しかし、前記酸化物 TFT 1 と同一の  $V_{th}$  を有するようにする複数の酸化物 TFT 群、前記酸化物 TFT 2 と同一の  $V_{th}$  を有するようにする複数の酸化物 TFT 群を備え、これら群ごとに上述した工程を得る製造を行うようにしてもよい。このような製造は実施例 3 以降の実施例においても同様に適用できる。

10

### 【0054】

#### (効果)

実施例 2 においては、同一基板上に  $V_{th}$  の異なる酸化物 TFT を作り分けることができ、回路設計の自由度を高めることができる。また、 $V_{th}$  の高い酸化物 TFT 1 では実施例 1 に示した効果も得られる。

### 【0055】

#### 実施例 3

#### (構成及び製造方法)

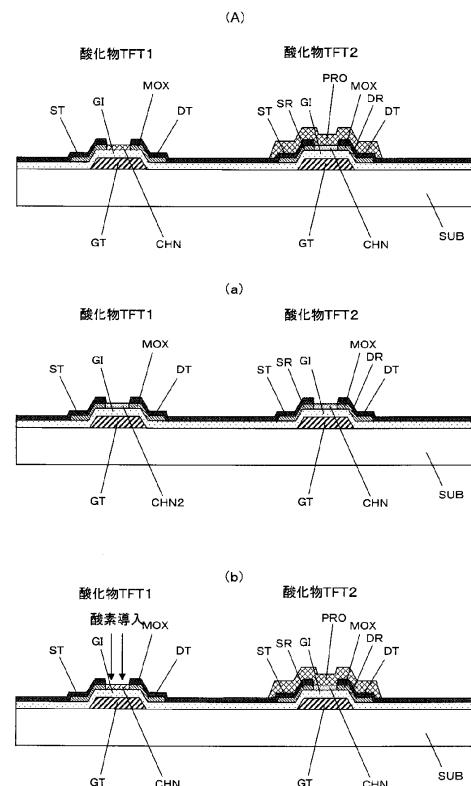

図 6 (A) は、本発明による半導体装置の実施例 3 を示す断面図で、図 5 (A) と対応した図となっている。図 6 (A) は、図 5 (A) の場合と同様、同一基板上に  $V_{th}$  の異なる 2 種のボトムゲート型酸化物 TFT を形成していることを示した図である。図 5 (A) の場合と比較して異なる構成は、酸化物 TFT 2 においても、そのチャネル領域 CHN に酸素が導入され、その濃度は、酸化物 TFT 1 のチャネル領域 CHN の酸素濃度よりも低く構成されていることがある。

20

### 【0056】

図 6 (a)、(b) は、図 6 (A) に示した半導体装置の製造方法の実施例を示した説明図である。まず、一般的な製造プロセスおよび本明細書に開示の製造プロセスを用いて、前記酸化物 TFT 1 および酸化物 TFT 2 を図 6 (a) に示した構造に形成する。この段階では、前記酸化物 TFT 1 および酸化物 TFT 2 の各チャネル領域に同量の酸素が導入されているものとする。次に、図 6 (b) に示すように、酸化物 TFT 2 の金属酸化物膜 MOX の少なくともチャネル形成領域上に保護膜 PRO を被って形成する。そして、酸化物 TFT 1 において、その金属酸化物 MOX に酸素を導入する。これにより、酸化物 TFT 1 のチャネル領域は、ソース領域 SR、ドレイン領域 DR に比べて酸素濃度を高くでき、酸化物 TFT 2 のチャネル領域も、ソース領域 SR、ドレイン領域 DR に比べて酸素濃度を高くできる。そして、酸化物 TFT 1 のチャネル領域 CHN は、酸化物 TFT 2 のチャネル領域 CHN に比べて酸素濃度を高くできる。

30

### 【0057】

#### (効果)

本実施例においては、同一基板上に  $V_{th}$  の異なる酸化物 TFT を作り分けることができ、回路設計の自由度を高めることができる。また、実施例 2 に比べ、酸化物 TFT 1、酸化物 TFT 2 のいずれにおいても、実施例 1 に示した効果が得られるという利点がある。

40

### 【0058】

#### 実施例 4

#### (構成及び製造方法)

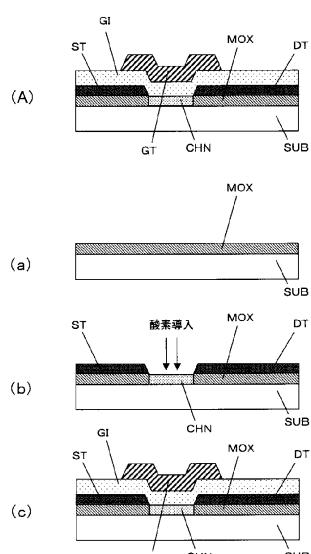

図 7 (A) は、本発明による半導体装置の実施例 4 を示す断面図である。図 7 (A) は、トップゲート型酸化物 TFT を示している。図 7 (A) において、基板 SUB があり、その上面に金属酸化物膜 MOX が形成されている。該金属酸化物膜 MOX はたとえば導電性の高い膜として成膜され、そのチャネル領域 CHN には酸素が導入されている。該チャネル領域 CHN の両脇に形成されるソース領域およびドレイン領域には、それぞれ、ソ-

50

ス電極 S T およびドレイン電極 D T が重畠されて形成されている。そして、前記チャネル領域 C H N 、ソース電極 S T 、およびドレイン電極 D T をも被ってゲート絶縁膜 G I が形成され、このゲート絶縁膜 G I の上面には少なくとも前記チャネル領域 C H N に重畠するようにしてゲート電極 G T が形成されている。

【 0 0 5 9 】

このように構成された半導体装置はたとえば次のようにして製造される。図 7 ( a ) に示すように、基板 S U B の上面に金属酸化物膜 M O X を形成する。次に、図 7 ( b ) に示すように、前記金属酸化物膜 M O X の上面に金属膜を形成し、この金属膜をパターン化することによって、ソース電極 S T 、ドレイン電極 D T を形成する。そして、前記ソース電極 S T と前記ドレイン電極 D T をマスクとし、前記ソース電極 S T と前記ドレイン電極 D T の間のチャネル領域 C H N に酸素を導入する。次に、図 7 ( c ) に示すように、前記チャネル領域 C H N 、ソース電極 S T 、およびドレイン電極 D T をも被ってゲート絶縁膜 G I を形成し、前記ゲート絶縁膜 G I の上面に前記チャネル領域 C H N に重畠するようにしてゲート電極 G T を形成する。

【 0 0 6 0 】

( 効果 )

実施例 4 においては、たとえば、金属酸化物膜 M O X をあらかじめ導電性の高い膜として成膜しておけば、ソース領域 S R 及びドレイン領域 D R での寄生抵抗、並びにソース領域 S R とソース電極 S T 、ドレイン領域 D R とドレイン電極 D T との間のコンタクト抵抗を低くすることができる。したがって、良好な電気接続が得られ、酸化物 F E T の特性を向上させることができる。また、ソース電極 S T 及びドレイン電極 D T に対して、ソース領域 S R 、チャネル領域 C H N 、ドレイン領域 D R を自己整合的に形成できるため、コンタクト抵抗と寄生抵抗のばらつきを低減し、ひいては T F T のばらつきを低減することができる。さらに、ソース領域 S R 及びドレイン領域 D R 、並びにソース電極 S T 及びドレイン電極 D T を形成した後に、チャネル領域 C H N の形成、及び V t h 調整を行なうことができる。これにより、T F T 量産時の歩留り低下を抑制でき、プロセス修正を容易にできる。

【 0 0 6 1 】

実施例 5

( 構成及び製造方法 )

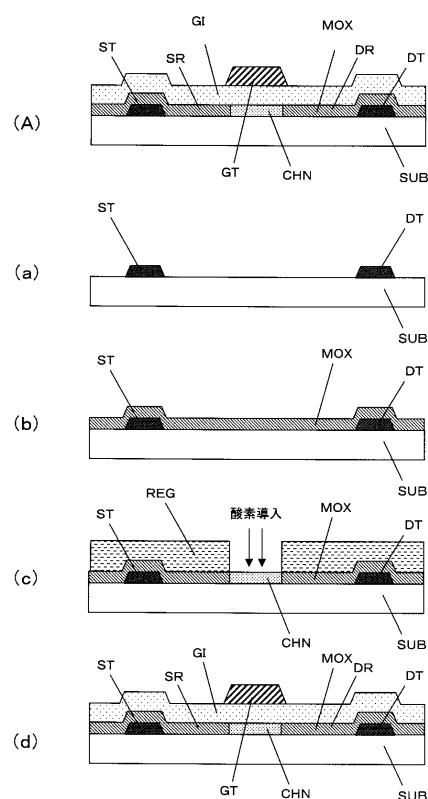

図 8 ( A ) は、本発明による半導体装置の実施例 5 を示す断面図である。図 8 ( A ) は、トップゲート型酸化物 T F T を示している。図 8 ( A ) において、基板 S U B があり、その上面にソース電極 S T およびドレイン電極 D T が形成されている。そして、前記ソース電極 S T およびドレイン電極 D T を被い前記ソース電極 S T およびドレイン電極 D T の間の領域に金属酸化物膜 M O X が形成されている。該金属酸化物膜 M O X はたとえば導電性の高い膜として成膜され、前記ソース電極 S T およびドレイン電極 D T の間の領域の一部にチャネル領域 C H N が形成されている。該チャネル領域 C H N には酸素が導入されている。そして、前記チャネル領域 C H N 、ソース電極 S T 、およびドレイン電極 D T をも被ってゲート絶縁膜 G I が形成され、このゲート絶縁膜 G I の上面には少なくとも前記チャネル領域 C H N に重畠するようにしてゲート電極 G T が形成されている。

【 0 0 6 2 】

このように構成された半導体装置はたとえば次のようにして製造される。図 8 ( a ) に示すように、基板 S U B の上面にソース電極 S T 、ドレイン電極 D T を形成する。次に、図 8 ( b ) に示すように、ソース電極 S T 、ドレイン電極 D T を被い、該ソース電極 S T およびドレイン電極 D T の間の領域に金属酸化物膜 M O X を成膜する。次に、図 7 ( c ) に示すように、フォトレジスト膜 R E G を形成する。このフォトレジスト膜 R E G は、前記金属酸化物膜 M O X のチャネル領域 C H N に相当する領域を露出させる開口を有する。そして、前記開口を通して前記金属酸化物膜 M O X に酸素を導入し、チャネル領域 C H N を形成する。その後、図 8 ( d ) に示すように、前記フォトレジスト膜 R E G を除去し、ゲート絶縁膜 G I 及びゲート電極 G T を順次形成して完了する。なお、図 8 ( d ) では、

10

20

30

40

50

前記フォトレジスト膜 R E G を除去した場合を示しているが、前記フォトレジスト膜 R E G は、必ずしも除去する必要はなく、残したままにしてもよい。絶縁膜として機能させることができるからである。

【 0 0 6 3 】

(効果)

実施例 5 においては、たとえば、金属酸化物膜 M O X をあらかじめ導電性の高い膜として成膜しておけば、ソース領域 S R 及びドレイン領域 D R での寄生抵抗、並びにソース領域 S R とソース電極 S T 、ドレイン領域 D R とドレイン電極 D T との間のコンタクト抵抗を低くすることができる。したがって、良好な電気接続が得られ、酸化物 F E T の特性を向上することができる。

10

【 0 0 6 4 】

また、ソース電極 S T 及びドレイン電極 D T に対して、ソース領域 S R 、チャネル領域 C H N 、ドレイン領域 D R が自己整合的に形成されるため、コンタクト抵抗と寄生抵抗のばらつきを低減し、ひいては T F T のばらつきを低減することができる。

【 0 0 6 5 】

また、ソース領域 S R 及びドレイン領域 D R 、並びにソース電極 S T 及びドレイン電極 D T を形成した後に、チャネル領域 C H N の形成、及び V t h 調整を行なうことができる。したがって、T F T 量産時の歩留り低下を抑制したり、プロセス修正を容易化したりすることができる。

20

【 0 0 6 6 】

以上、実施例を用いて本発明を説明してきたが、これまでの各実施例で説明した構成はあくまで一例であり、本発明は、技術思想を逸脱しない範囲内で適宜変更が可能である。また、それぞれの実施例で説明した構成は、互いに矛盾しない限り、組み合わせて用いてもよい。

【 産業上の利用可能性】

【 0 0 6 7 】

上述した各実施例の半導体装置及びその製造方法は、透過型、反射型、半透過型の各液晶表示装置、並びに O L E D 表示装置などの各画素を駆動するトランジスタや周辺回路に適用できる。また、記憶素子アレイ、無線タグなどにも適用できる。

【 図面の簡単な説明】

30

【 0 0 6 8 】

【図 1】本発明による半導体装置の構成及びその製造方法の一実施例を示す図である。

【図 2】本発明による半導体装置を適用した表示装置の一実施例を示す構成図である

【図 3】本発明による半導体装置を適用したアレイの一実施例を示す構成図である。

【図 4】本発明による半導体装置を適用した無線タグの一実施例を示す構成図である。

【図 5】本発明による半導体装置の構成の別の実施例を示す図である。

【図 6】本発明による半導体装置の構成の別の実施例を示す図である。

【図 7】本発明による半導体装置の構成及びその製造方法の別の実施例を示す図である。

【図 8】本発明による半導体装置の構成及びその製造方法の別の実施例を示す図である。

【 符号の説明】

40

【 0 0 6 9 】

S U B . . . . . 基板、 M O X . . . . . 金属酸化物膜、 C H N . . . . . チャネル領域、 S R . . . . . ソース領域、 D R . . . . . ドレイン領域、 S T . . . . . ソース電極、 D T . . . . . ドレイン電極、 G T . . . . . ゲート電極、 G I . . . . . ゲート絶縁膜、 T F T . . . . . 薄膜トランジスタ、 D L . . . . . データ線、 G L . . . . . ゲート線、 D D C . . . . . データ線駆動回路、 G D C . . . . . ゲート線駆動回路、 R D . . . . . リーダ、 W R . . . . . ライタ、 A R . . . . . アンテナ共振回路、 R C T . . . . . 整流器、 M O D . . . . . 変調器、 D G C . . . . . デジタル回路。

【図1】

【図2】

【図3】

【図4】

【 四 5 】

【 四 6 】

【 义 7 】

【 図 8 】

---

フロントページの続き

(72)発明者 内山 博幸

東京都国分寺市東恋ヶ窪一丁目280番地 株式会社 日立製作所 中央研究所内

審査官 竹口 泰裕

(56)参考文献 特開2008-053356 (JP, A)

特開2008-042088 (JP, A)

特開2005-268724 (JP, A)

(58)調査した分野(Int.Cl., DB名)

H01L 21/336, 29/786