(19) **日本国特許庁(JP)**

# (12) 特 許 公 報(B2)

(11) 特許番号

特許第5286717号 (P5286717)

(45) 発行日 平成25年9月11日 (2013.9.11)

(24) 登録日 平成25年6月14日 (2013.6.14)

(51) Int .Cl. F.1

**HO2M 3/155 (2006.01)** HO2M 3/155 HO2M 3/155 F

請求項の数 3 (全 9 頁)

(21) 出願番号 特願2007-229318 (P2007-229318) (22) 出願日 平成19年9月4日 (2007.9.4)

(65) 公開番号 特開2009-65740 (P2009-65740A)

(43) 公開日 平成21年3月26日 (2009. 3. 26) 審査請求日 平成22年3月24日 (2010. 3. 24)

(73) 特許権者 000006747

株式会社リコー

東京都大田区中馬込1丁目3番6号

||(74)代理人 100082670

弁理士 西脇 民雄

(72) 発明者 井上 由幸

東京都大田区中馬込1丁目3番6号 株式

会社リコー内

審査官 塩治 雅也

(56)参考文献 特開2003-312517 (JP, A

特開2003-319643 (JP, A

最終頁に続く

(54) 【発明の名称】 昇圧型DC/DCコンバータ

## (57)【特許請求の範囲】

# 【請求項1】

直流電源と、前記直流電源の正極に接続されたインダクタと、前記インダクタとGND間に接続された第1のスイッチング素子と、前記インダクタに第2のスイッチング素子を介して接続された平滑コンデンサと、前記第1及び第2のスイッチング素子のON/OFF制御を行うドライバ制御部と、負荷電流に応じて前記ドライバ制御部の制御動作を切り替える制御切り替え手段とを備え、

前記第2のスイッチング素子が直列に2個接続されて構成され、一方のスイッチング素子はバックゲートをインダクタ側、他方のスイッチング素子はバックゲートを前記平滑コンデンサ側に接続され、

前記制御切り替え手段からの指示に応じて、前記ドライバ制御部は、前記第2のスイッチング素子をON/OFF制御またはOFF制御に切り替え、

前記昇圧型 D C / D C コンバータのスタンバイ時に第 2 のスイッチ素子が O F F している際に、前記平滑コンデンサに直流電流の電荷の充電を防止するように制御したことを特徴とする昇圧型 D C / D C コンバータ。

# 【請求項2】

直流電源と、前記直流電源の正極に接続されたインダクタと、前記インダクタとGND間に接続された第1のスイッチング素子と、前記インダクタに第2のスイッチング素子を介して接続された平滑コンデンサと、前記第1及び第2のスイッチング素子のON/OFF制御を行うドライバ制御部と、負荷電流に応じて前記ドライバ制御部の制御動作を切り

替える制御切り替え手段とを備え、前記制御切り替え手段からの指示に応じて、前記ドライバ制御部は、前記第2のスイッチング素子をON/OFF制御またはOFF制御に切り替え、

前記トライバ制御部は、2つの第2のスイッチング素子のうち一方の第2のスイッチング素子をONさせるとともに、他方の第2のスイッチング素子を負荷電流が小さいときOFF制御に切り替え、負荷電流が大きいときON/OFF制御に切り替えることを特徴とする昇圧型DC/DCコンバータ。

# 【請求項3】

前記ドライバ制御部は、前記負荷電流が小さいとき前記第2のスイッチング素子をOFF制御に切り替え、前記負荷電流が大きいとき前記第2のスイッチング素子をON/OFF制御に切り替えることを特徴とする請求項1または請求項2に記載の昇圧型DC/DCコンバータ。

【発明の詳細な説明】

【技術分野】

[0001]

本発明は、昇圧型 D C / D C コンバータに関し、特に、第 1 のスイッチング素子と第 2 のスイッチング素子の制御を同期させることで、入力側の電力を出力側に供給する昇圧型 D C / D C コンバータに関するものである。

【背景技術】

[0002]

電源装置の中で、入力電圧を所定の出力電圧に変換する方法として、スイッチング型 DC/DCコンバータを用いて電力を高変換効率で変換する方法が広く用いられている。

[0003]

このスイッチング型 D C / D C コンバータは、第 1 のスイッチング素子と第 2 のスイッチング素子を同期して制御することによってスイッチング素子がチャネルを形成できるため、スイッチング素子の O N 抵抗を小さくでき、重負荷時にも高効率な電力変換が可能となる。しかし、重負荷時には高い電力変換効率が得られるが、軽負荷時には第 2 のスイッチング素子のスイッチング時に発生する充放電電流が無視できなくなるため、全体として変換効率が低下してしまう。

[0004]

特許文献1には、第1のスイッチング素子と第2のスイッチング素子を同期して制御することによってスイッチング素子のON抵抗を小さくすることで、重負荷時にも高効率な電力変換が得られる方法が開示されている。

【特許文献1】特開2001-197727号公報

【発明の開示】

【発明が解決しようとする課題】

[0005]

特許文献1に記載のような昇圧DC/DCコンバータの制御方法では、重負荷時には高効率な電力変換が得られるが、軽負荷時には第1のスイッチング素子と第2のスイッチング素子が共にスイッチングしてしまうので、回路内スイッチング素子抵抗は小さくできるが、前記スイッチング素子を充放電するための消費電流が無視できなくなるため、軽負荷時に高効率な電力変換を得ることが難しいという難点がある。

[0006]

本発明は、負荷電流が重負荷時と軽負荷時での第2のスイッチング素子の制御方法を切り替えることで、重負荷時、軽負荷時共に重負荷時に高効率な電力変換が得られる昇圧型 DC/DCコンバータを提供することを目的とする。

【課題を解決するための手段】

[0007]

本発明の昇圧型 D C / D C コンバータは、直流電源と、前記直流電源の正極に接続されたインダクタと、前記インダクタとG N D 間に接続された第 1 のスイッチング素子と、前

10

20

30

40

記インダクタに第2のスイッチング素子を介して接続された平滑コンデンサと、前記第1及び第2のスイッチング素子のON/OFF制御を行うドライバ制御部と、負荷電流に応じて前記ドライバ制御部の制御動作を切り替える制御切り替え手段とを備え、

前記第2のスイッチング素子が直列に2個接続されて構成され、一方のスイッチング素子はバックゲートをインダクタ側、他方のスイッチング素子はバックゲートを前記平滑コンデンサ側に接続され、

前記制御切り替え手段からの指示に応じて、前記ドライバ制御部は、前記第2のスイッチング素子をON/OFF制御またはOFF制御に切り替え、

前記昇圧型 D C / D C コンバータのスタンバイ時に第 2 のスイッチ素子が O F F している際に、前記平滑コンデンサに直流電流の電荷の充電を防止するように制御したことを特徴とする。

[0008]

上記の構成によれば、重負荷時には第1のスイッチング素子と第2のスイッチング素子を同期して制御することによってスイッチング素子がチャネルを形成できるため、スイッチング素子のON抵抗を小さくでき、重負荷時にも高効率な電力変換が可能となる。そして、軽負荷時には第2のスイッチング素子をOFFし続ける制御に切り替えることで軽負荷時に前記第2のスイッチング素子制御のための充放電電流を削減し、軽負荷時にも高効率な電力変換が得られる。

[0010]

上記した構成のように、第2のスイッチング素子を直列に2個接続し、1方はバックゲートをインダクタ側、他方はバックゲートを平滑コンデンサ側に接続することで、前記昇圧型DC/DCコンバータがOFFしているときに出力側端子に電圧が見えないように制御できる。

【発明の効果】

[0011]

上記したように、負荷電流に応じ第2のスイッチング素子の制御方法を切り替えることで、軽負荷時には第2のスイッチをOFFし続けることで第2のスイッチング素子がスイッチングする時に発生する充放電電流を削減し、軽負荷時消費電流の低減を図り、軽負荷時効率向上を達成できる。

【発明を実施するための最良の形態】

[0012]

この発明の実施の形態について図面を参照しながら詳細に説明する。なお、図中同一または相当部分には同一符号を付し、説明の重複を避けるためにその説明は繰返さない。

[0013]

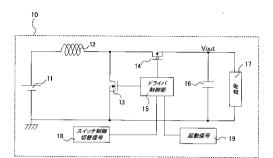

図 1 は、この発明の第 1 実施形態にかかる昇圧型 D C D C コンバータの構成を示すブロック回路図である。

[0014]

この実施形態の昇圧型 D C D C コンバータ 1 0 は、入力電源 1 1 の正極側端子とインダクタ 1 2 の一端が直列に接続される。そして、入力電源 1 1 の負極側の端子は接地(G N D ) されている。インダクタンス 1 2 の他端は、N M O S で構成された第 1 のスイッチング素子 1 3 及び P M O S で構成された第 2 のスイッチング素子 1 4 が接続されている。第 1 のスイッチング素子 1 3 は、入力電源 1 1 の負極側に接続されている。

[0015]

一方、第2のスイッチング素子14は出力用の平滑用コンデンサ16に直列に接続される。第1のスイッチング素子13及び第2のスイッチング素子14のゲートには、ドライバ制御部15からの制御信号が与えられる。ドライバ制御部15は、出力電圧に応じて、第1のスイッチング素子13及び第2のスイッチング素子14の与える周期の電圧を制御し、第1のスイッチング素子13及び第2のスイッチング素子14をそれぞれ駆動する。

[0016]

ドライバ制御部15には、スイッチ制御切替信号18及び起動信号19が与えられる。

20

10

30

40

#### [0017]

起動信号19によってドライバ制御部15が制御を始め、スイッチ制御切替信号18によって、第2のスイッチング素子14の制御方法が切り替えられる。スイッチ制御切替信号18は、軽負荷時モードの時にはオン(ON)、重負荷時モードの時にはオフ(OFF)となり、負荷状態により、第2のスイッチング素子14の制御方法を切り替える。

#### [0018]

制御方法は、ドライバ制御部15から所定の周期の電圧が第1のスイッチング素子13及び第2のスイッチング素子14のゲートに印加され、電圧が第1のスイッチング素子13のゲートに印加されているときに第1のスイッチング素子13はオン(ON)状態となり、ドレイン・ソース間は通電されインダクタ12にエネルギーが蓄えられる。第1のスイッチング素子13がオン(ON)状態からオフ(OFF)状態になったときに、第2のスイッチング素子14がオフ(OFF)状態からオン(ON)状態になり、インダクタ12に蓄えられたエネルギーから発生した電圧を第2のスイッチング素子14を介してVoutに出力され、負荷17に電流が流れる。そして、同時に平滑コンデンサ16を充電する。また、第1のスイッチング素子13がオン(ON)状態のときは、第2のスイッチング素子14はオフ(OFF)状態となり平滑コンデンサ16の放電により負荷17に電流が流れる。

## [0019]

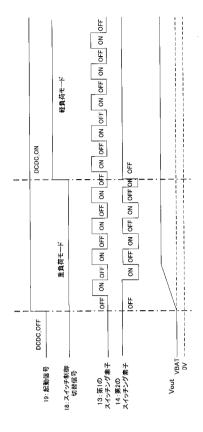

図2は、図1に示す昇圧型DCDCコンバータ10の動作タイミングチャートである。 ドライバ制御部15は、起動信号19がオン(ON)すると、動作制御が始まり、起動信号19がオフ(OFF)している場合、第1のスイッチング素子13及び第2のスイッチング素子14はオフ(OFF)している。

#### [0020]

重負荷時には、起動信号 1 9 がオン ( O N ) しているときにスイッチ制御切替信号 1 8 はオフ ( O F F ) となり、第 1 のスイッチング素子 1 3 と第 2 のスイッチング素子 1 4 が同期して制御される。この結果、スイッチング素子 1 3、 1 4 がチャネルを形成できるため、スイッチング素子のオン ( O N ) 抵抗を小さくでき、重負荷時にも高効率な電力変換が可能となる。

#### [0021]

軽負荷時には、起動信号19がオン(ON)しているときに、スイッチ制御切替信号18がオン(ON)し、ドライバ制御部15の制御が切り替わり、第1のスイッチング素子13はON/OFF制御、第2のスイッチング素子14はオフ(OFF)しつづける制御になる。

#### [0022]

このように、軽負荷時には、第2のスイッチング素子14をオフ(OFF)し続ける制御に切り替えることで、軽負荷時に第2のスイッチング素子14の制御のための充放電電流を削減し、軽負荷時にも高効率な電力変換が得られる。

# [0023]

Vout電圧は、起動信号19がオフ(OFF)しているときは電源電圧11の電圧になり、起動信号19がオン(ON)すると昇圧型DCDCコンバータ10が動作するため、所望のVout電圧で安定する。

# [0024]

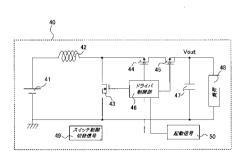

次に、この発明の第2の実施形態につき、図3および図4に従い説明する。図3は、この発明の第2の実施形態にかかる昇圧型DCDCコンバータの構成を示すブロック回路図である。この第2の実施形態の昇圧型DCDCコンバータ40は、入力電源41の正極側端子とインダクタ42の一端が直列に接続される。そして、入力電源41の負極側の端子は接地されている。インダクタンス42の他端は、NMOSで構成された第1のスイッチング素子43及びPMOSで構成された2つの直列接続の第2のスイッチング素子44、45が接続されている。第1のスイッチング素子43は、入力電源41の負極側に接続されている。

# [0025]

10

20

30

一方、第2のスイッチング素子45は出力用の平滑用コンデンサ47に接続される。第1のスイッチング素子43及び第2のスイッチング素子44、45のゲートには、ドライバ制御部46からの制御信号が与えられる。

#### [0026]

ドライバ制御部46には、スイッチ制御切替信号49及び起動信号50が与えられる。

#### [0027]

起動信号 5 0 によってドライバ制御部 4 6 が制御を始め、スイッチ制御切替信号 4 9 によって、第 2 のスイッチング素子 4 4 、 4 5 の制御方法が切り替えられる。

## [0028]

第1の実施形態と同様に、スイッチ制御切替信号49は、軽負荷時モードの時にはオン(ON)、重負荷時モードの時にはオフ(OFF)となり、負荷状態により、第2のスイッチング素子14の制御方法を切り替える。

## [0029]

上記したように、この第2の実施形態は、図1に示した第1の実施形態と基本構成は同様である。が、第2のスイッチング素子44、45をインダクタ42とVoutの間に直列に2つ接続している。

## [0030]

スイッチング素子 4 4 はバックゲートをインダクタ 4 2 側に接続し、スイッチング素子 4 5 はバックゲートを V o u t 側に接続している。

## [0031]

図1の構成は、昇圧型DCDCコンバータがオフ(OFF)しているとき、第1のスイッチング素子及び第2のスイッチング素子はオフ(OFF)しているが、Voutと第2のスイッチング素子のインダクタ側電位を比較すると、後者の方が電位が高くなるため、バックゲートをVout側に接続している場合、基板を介して電荷がVout側へ流れてしまい、負荷に電圧がみえてしまう。そこで、この第2の実施形態では、第2のスイッチング素子44、45のバックゲートをインダクタ42側に接続したスイッチング素子を直列に繋げ、昇圧型DCDCコンバータがオフ(OFF)しているとき、負荷に電圧が見えない構成にしたものである。

# [0032]

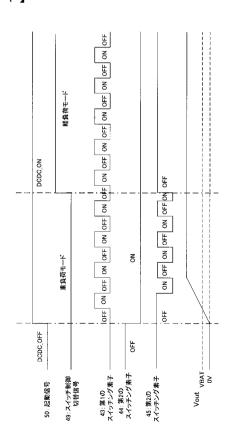

図4は、図3に示す昇圧型DCDCコンバータ40の動作タイミングチャートである。

#### [0033]

起動信号 5 0 がオフ ( O F F ) している場合、第 1 のスイッチング素子 4 3 及び第 2 のスイッチング素子 4 4 、 4 5 はオフ ( O F F ) している。

#### [0034]

ドライバ制御部46は、起動信号50がオン(ON)すると動作制御が始まり、負荷時には、起動信号50がオン(ON)しているときにスイッチ制御切替信号49はオフ(OFF)となり、第1のスイッチング素子43と第2のスイッチング素子45が同期して制御される。また、第2のスイッチング素子44はオン(ON)状態が維持される。

# [0035]

また、軽負荷時は、ドライバ制御部 4 6 は、起動信号 5 0 がオン(ON)しているときに、スイッチ制御切替信号 4 9 がON(軽負荷時)すると、ドライバ制御部 4 6 の制御が切り替わり、第 1 のスイッチング素子 4 3 はON / OFF制御、第 2 のスイッチング素子 4 4 はオン(ON)し続け、第 2 のスイッチング素子 4 5 オフ(OFF)し続ける制御になる。 V o u t 電圧は、起動信号 5 0 がオフ(OFF)しているときは 0 V になり、起動信号 5 0 がオン(ON)すると昇圧型 DCDCコンバータ 4 0 が動作するため、所望の V o u t 電圧で安定する。

#### [0036]

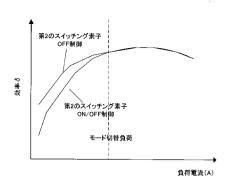

図5は、昇圧型DCDCコンバータ効率を縦軸、負荷電流を横軸に、第2のスイッチング素子の制御方法別に表したものである。点線で示した負荷以上の場合には、重負荷状態であり、スイッチ制御切替信号18(49)がオフ(OFF)している。このときの効率

10

20

30

40

曲線にほとんど差は無い。これに対して、点線で示した負荷より小さい場合には軽負荷の状態であり、スイッチ制御切替18(49)信号がオン(ON)している。このときには、第2のスイッチング素子14(45)をオフ(OFF)している制御方法の方が高くなる。これは、負荷電流が少ない状態で、第2のスイッチング素子をON/OFF制御させる時に発生する第2のスイッチング素子のゲート電圧充放電電流損失より第2のスイッチング素子をオフ(OFF)してスイッチング素子のダイオード特性で出力電圧を安定させる時に発生する損失少なくなるためである。この発明は、前記効果を利用し、軽負荷時にも高効率な電力変換が得られる昇圧型DC/DCコンバータを達成することができる。

## [0037]

今回開示された実施の形態はすべての点で例示であって制限的なものではないと考えられるべきである。この発明の範囲は、上記した実施の形態の説明ではなくて特許請求の範囲によって示され、特許請求の範囲と均等の意味および範囲内でのすべての変更が含まれることが意図される。

【図面の簡単な説明】

## [0038]

- 【図1】この発明の第1の実施の形態に関わる昇圧型DCDCコンバータの構成を示すブロック回路図である。

- 【図2】図1に示す昇圧型DCDCコンバータのスイッチ制御切替信号毎のスイッチング素子制御方法とタイミング及び出力電圧を示したタイミングチャートである。

- 【図3】この発明の第2の実施の形態に関わる昇圧型DCDCコンバータの構成を示すブロック回路図である。

- 【図4】図2に示す昇圧型DCDCコンバータのスイッチ制御切替信号毎のスイッチング素子制御方法とタイミング及び出力電圧を示したタイミングチャートである。

- 【図5】第2のスイッチング素子の制御方法別の効率曲線を示した特性図である。

#### 【符号の説明】

## [0039]

10、40 昇圧型DCDCコンバータ、11、41 入力電源、12、42 インダクタ、13、43 第1のスイッチング素子、14、44、45 第2のスイッチング素子、15 ドライバ制御部、16、47 平滑用コンデンサ、18、49 スイッチ制御切替信号、19、50 起動信号。

30

20

【図1】

【図2】

【図3】

【図4】

# 【図5】

# フロントページの続き

(58)調査した分野(Int.CI., DB名) H02M 3/155