(10) **DE 10 2007 016 461 B4 2012.03.08**

(12)

## Patentschrift

(21) Aktenzeichen: **10 2007 016 461.2**

(22) Anmelddatag: **29.03.2007**

(43) Offenlegungstag: **29.11.2007**

(45) Veröffentlichungstag

der Patenterteilung: **08.03.2012**

(51) Int Cl.: **H04L 25/06 (2006.01)**

**H04L 25/49 (2011.01)**

**H03M 5/14 (2011.01)**

Innerhalb von drei Monaten nach Veröffentlichung der Patenterteilung kann nach § 59 Patentgesetz gegen das Patent Einspruch erhoben werden. Der Einspruch ist schriftlich zu erklären und zu begründen. Innerhalb der Einspruchsfrist ist eine Einspruchsgebühr in Höhe von 200 Euro zu entrichten (§ 6 Patentkostengesetz in Verbindung mit der Anlage zu § 2 Abs. 1 Patentkostengesetz).

(30) Unionspriorität:

**10-2006-0030752 04.04.2006 KR**

(72) Erfinder:

**Bae, Seung-Jun, Daejeon, KR; Jang, Seong-Jin, Seongnam, Kyonggi, KR**

(73) Patentinhaber:

**Samsung Electronics Co., Ltd., Suwon, Kyonggi, KR**

(56) Für die Beurteilung der Patentfähigkeit in Betracht gezogene Druckschriften:

(74) Vertreter:

**Patentanwälte Ruff, Wilhelm, Beier, Dauster & Partner, 70174, Stuttgart, DE**

**US 5 387 911 A**

**US 6 026 124 A**

**US 4 486 739 A**

(54) Bezeichnung: **Verfahren zum Übertragen DC-balance-kodierter Daten, Verfahren zum Reduzieren von Simultaneous Switching Noise, Datensender, Datenempfänger und Daten-Sender/ Empfänger**

(57) Hauptanspruch: Verfahren zum Übertragen DC-balance-kodierter Daten (D1~D3), beinhaltend:

Übertragen eines Vorspanns (Pre) aus Dummy-Daten, der dazu ausgebildet ist, eine Zwischenanzahl von Bits eines gegebenen Logikwerts bereitzustellen, die wenigstens ein Bit des gegebenen Logikwerts beträgt, jedoch kleiner als eine Maximalanzahl von Bits des gegebenen Logikwerts in den DC-balance-kodierten Daten ist; und anschließend Übertragen der DC-balance-kodierten Daten (D1~D3), wobei das Übertragen des Vorspanns aus Dummy-Daten ein serielles Übertragen einer Mehrzahl von Vorspannwörtern aus Dummy-Daten beinhaltet, dadurch gekennzeichnet, dass die Mehrzahl von Vorspannwörtern aus Dummy-Daten ein erstes Vorspannwort aus Dummy-Daten und ein zweites Vorspannwort aus Dummy-Daten umfasst, wobei das zweite Vorspannwort mehr Bits des gegebenen Logikwerts als das erste Vorspannwort aufweist.

## Beschreibung

**[0001]** Die Erfindung betrifft ein Verfahren zum Übertragen DC-balance-kodierter Daten, ein Verfahren zum Reduzieren von Simultaneous Switching Noise, einen Datensender, einen Datenempfänger und einen bidirektionalen Sender/Empfänger für DC-balance-kodierte Daten.

**[0002]** Datensende- und -empfangssysteme sowie entsprechende Verfahren werden in zunehmendem Maße eingesetzt, um immer größere Datenmengen mit immer höheren Geschwindigkeiten zu übertragen. In Daten-Sende-/Empfangssystemen und entsprechenden Verfahren kann es erwünscht sein, die Daten zu kodieren oder zu verschlüsseln, um die Übertragung zu erleichtern, und die kodierten Daten, die empfangen werden, später zu dekodieren oder zu entschlüsseln. Eine Art von Kodierung oder Verschlüsselung, die weitläufig eingesetzt wird, ist die DC-balance-Kodierung. Wie dem Fachmann bekannt ist, handelt es sich bei der DC-balance-Kodierung um eine Technik zum Kodieren von Daten, die ausreichend Zustandswechsel für eine sinnvolle Taktrückgewinnung bietet, während sie einen Gleichspannungsausgleich (DC balance) und eine begrenzte so genannte „Disparity“ zwischen benachbarten Datensignalen erreicht.

**[0003]** Eine weitläufig verwendete Form der DC-balance-Kodierung wird als „8B/10B-Kodierung“ bezeichnet. Wie durch den Namen nahe gelegt, werden bei der 8B/10B-Kodierung acht Datenbits als eine 10-Bit-Einheit übertragen, die oft als ein Symbol oder Zeichen („character“) bezeichnet wird. Die fünf am wenigsten bedeutsamen Datenbits werden in einer 6-Bit-Gruppe kodiert und die drei am meisten bedeutsamen Bits werden in einer 4-Bit-Gruppe kodiert. Diese Kodierungsgruppen werden zusammengefasst („concatenated“), um das 10-Bit-Symbol zu bilden, welches übertragen wird. Da die 8B/10B-Kodierung 10-Bit-Symbole verwendet, um 8-Bit-Wörter zu kodieren, kann jedes der 256 möglichen 8-Bit-Worte auf zwei unterschiedliche Weisen kodiert werden, von denen eine die bitweise Inverse der anderen darstellt. Unter Verwendung dieser alternativen Kodierungen ist das Schema in der Lage, einen langfristigen Gleichspannungsausgleich zu erreichen. Die 8B/10B-Kodierung kann im Zusammenhang mit IEEE 1394b, Gigabit Ethernet, Audiospeichergeräten, wie Digital Audio Tape, und anderen weitläufig eingesetzten Schnittstellen/Geräten verwendet werden.

**[0004]** Die 8B/10B-DC-balance-Kodierung ist in der US-Patentschrift 4,486,739 beschrieben. Wie in der Zusammenfassung der US-Patentschrift 4,486,739 angegeben, wird dort ein binärer Gleichspannungsausgleichscode und eine Kodierschaltung zum Ausführen dieses Codes beschrieben, wobei ein 8-Bit-Byte an Informationen für eine Übertragung über

elektromagnetische oder optische Übertragungsleitungen, die zeitlichen und niederfrequenten Zwängen unterliegen, in zehn binäre Digits übersetzt wird. Die Bedeutung dieses Codes liegt darin, dass er niedrige Implementierungsanforderungen hinsichtlich der Schaltung mit einer ausgezeichneten Leistungsfähigkeit in der Nähe der theoretischen Grenzen vereint, wenn diese mit den gemeinhin akzeptierten Kriterien gemessen wird. Der 8B/10B-Kodierer ist in einen 5B-/6B- und einen 3B-/4B-Kodierer unterteilt. Die Eingabecodepunkte werden den Ausgabecodepunkten zugeordnet, so dass die Anzahl von Bitänderungen, die für die Übersetzung erforderlich sind, minimiert ist und die Bitänderungen in einige wenige Klassen eingeteilt werden können.

**[0005]** Ein weiteres Beispiel für 8B/10B-Kodierung ist in der US-Patentschrift 5,387,911 beschrieben. Wie in der Zusammenfassung der US-Patentschrift 5, 387,911 angegeben, werden ein Verfahren und eine Vorrichtung offenbart, die ein modifiziertes 8B/10B-System zum Übertragen von zehn Bit breiten Datenpaketen in einem 12-Bit-Code verwenden, wobei 5B-/6B-Kodierer/Decodierer die zehn Bit breiten Daten in zwei 5-Bit-„Nibbels“ unterteilen. Einzigartige Spezialcodes werden angegeben, die zu keinem Alias-Effekt mit anderen 12-Bit-Codewörtern führen können, um verlässliche Byte-Grenzen zu schaffen.

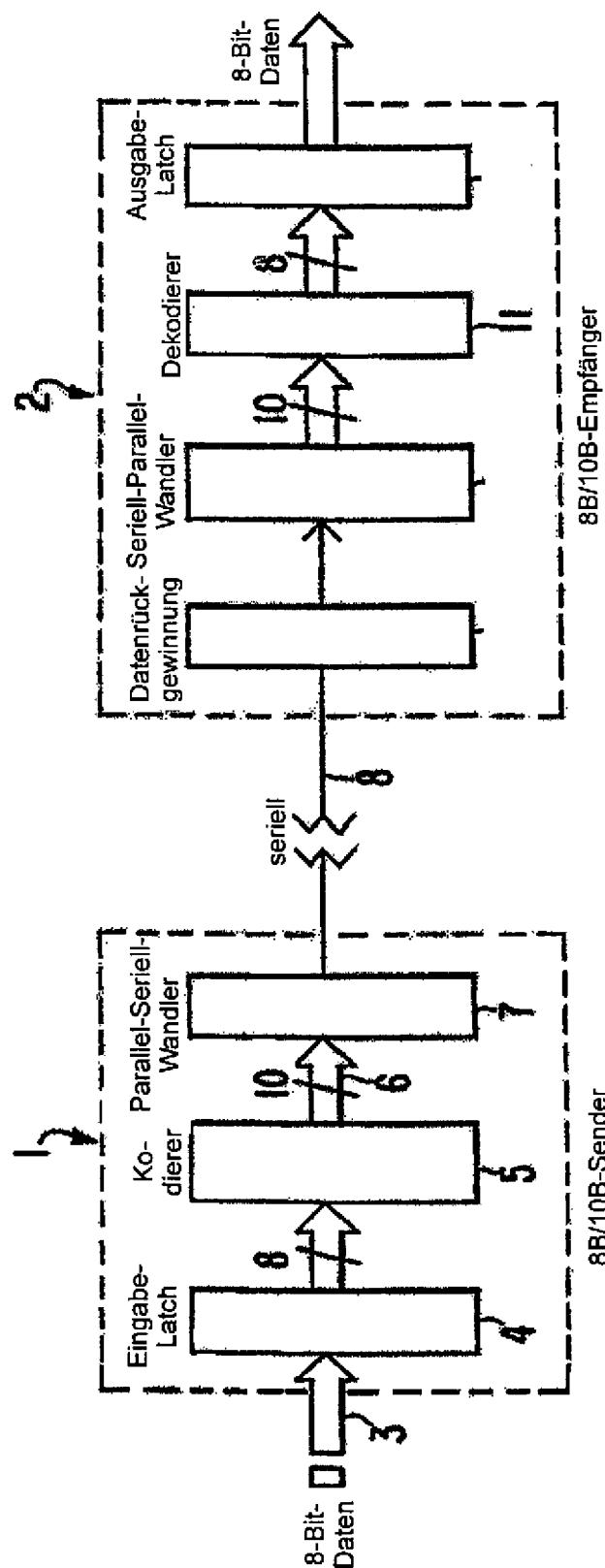

**[0006]** [Fig. 1](#) ist eine Reproduktion der [Fig. 1](#) der US-Patentschrift 5,387,911. Wie in der US-Patentschrift 5,387,911 im oberen Bereich der Spalte 6 angegeben, ist [Fig. 1](#) ein Blockschaltbild einer herkömmlichen 8B-breiten Architektur sowohl eines 8B/10B-Senders **1** als auch eines 8B/10B-Empfängers **2**. Ein Latch **4** und ein Kodierer **5** des Senders **1** sind dazu ausgebildet, nur 8-Bit-breite Rohdaten zu akzeptieren, und der Kodierer **5** wurde dazu ausgebildet, die 8-Bit-Rohdaten in einen 10-Bit-Parallelcode umzuwandeln, der dann in einem Schieber **7** in serielle Daten umgewandelt und über die Sendeverbindung **8** zu dem Empfänger **2** gesendet wird. Der Empfänger ist nach dem Dekodieren des 10-Bit-Codes in einem Decodierer **11** ebenfalls auf eine 8-Bit-Architektur beschränkt.

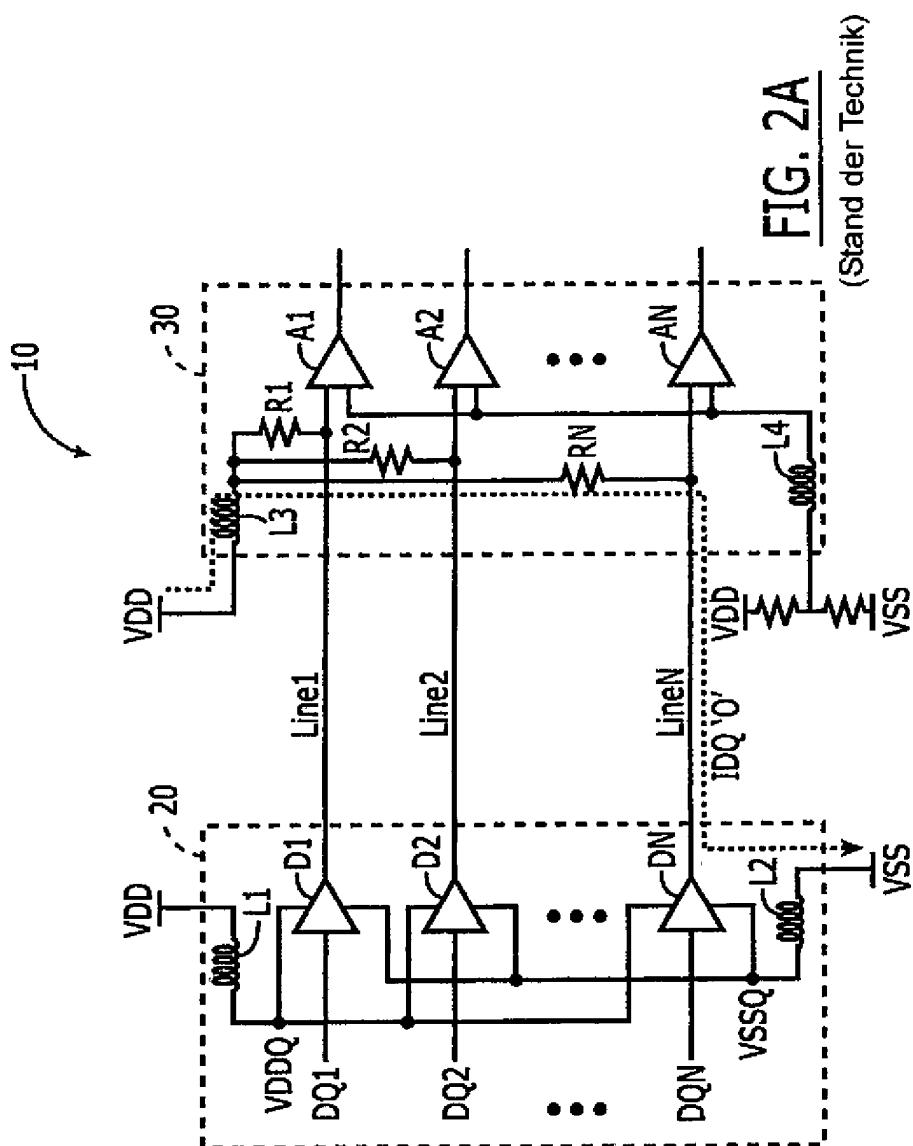

**[0007]** [Fig. 2A](#) ist ein Schaltungsdiagramm eines herkömmlichen Datenübertragungs-/Empfangssystems, das auch als ein Schnittstellensystem **10** bezeichnet wird, das eine Sendereinheit **20** und eine Empfängereinheit **30** umfasst. Datenbits DQ1...DQN werden an Treiber D1-DN angelegt, um eine Mehrzahl von Signal- oder Übertragungsleitungen Line1-LineN zu treiben. Bei der Empfängereinheit **30** können eine Mehrzahl von Eingabepuffern A1-AN Abschlusswiderstände R1-RN enthalten, die mit einer Versorgungsspannung VDD verbunden sein können. Weiterhin kann an den Eingabepuffern A1-AN eine Referenzspannung anliegen. Die Referenzspannung kann durch einen oder mehrere Widerstände,

die zwischen die Versorgungsspannung VDD und eine Massespannung VSS geschaltet sind, oder unter Verwendung anderer herkömmlicher Techniken erzeugt werden. Interne Versorgungsspannungen und Massespannungen sind in [Fig. 2A](#) mit VDDQ bzw. VSSQ bezeichnet.

**[0008]** Wie ebenfalls in [Fig. 2A](#) dargestellt, können parasitäre Induktivitäten L1–L4 in dem Schnittstellensystem **10** existieren. Diese und/oder andere parasitäre Induktivitäten können Simultaneous Switching Noise (SSN) erzeugen, indem sie einen Strompfad schaffen, wie mittels der mit IDQ '0' bezeichneten punktierten Linie in [Fig. 2A](#) gezeigt, wenn sie einen Logikpegel ZERO (Null) übertragen. Auf diese Weise fungieren die Treiber D1–DN, wie in [Fig. 2A](#) gezeigt, als Inverter. Wenn die Daten ONE (Eins) betragen, wird möglicherweise kein parasitärer Strompfad erzeugt. Wenn jedoch die Daten ZERO betragen, wird ein Strompfad IDQ '0' durch die Übertragungsleitungen Line1–LineN erzeugt. In Abhängigkeit von dem Datenpegel kann der Gesamtstromverbrauch der Treiber dadurch variieren, was SSN erzeugen kann. Die parasitären Induktivitäten L1–L4 erzeugen das Rauschen (Jitter) und können den Spannungsabstand und/oder Zeitabstand des Datensignals verringern. Das Rauschen kann darüber hinaus die Datenfrequenz und/oder Leistungsfähigkeit des Systems herabsetzen. SSN kann auch in einer Schnittstelle **10'** gemäß [Fig. 2B](#) erzeugt werden, wenn die Abschlusswiderstände R1–RN der Empfängereinheit **30'** mit Masse (VSS) verbunden sind, wenn die Daten ONE betragen, wie durch die punktierte Linie IDQ '1' gezeigt. Da das SSN durch parasitäre Induktivitäten hervorgerufen werden kann, wird das SSN auch als L(di/dt)-Rauschen bezeichnet.

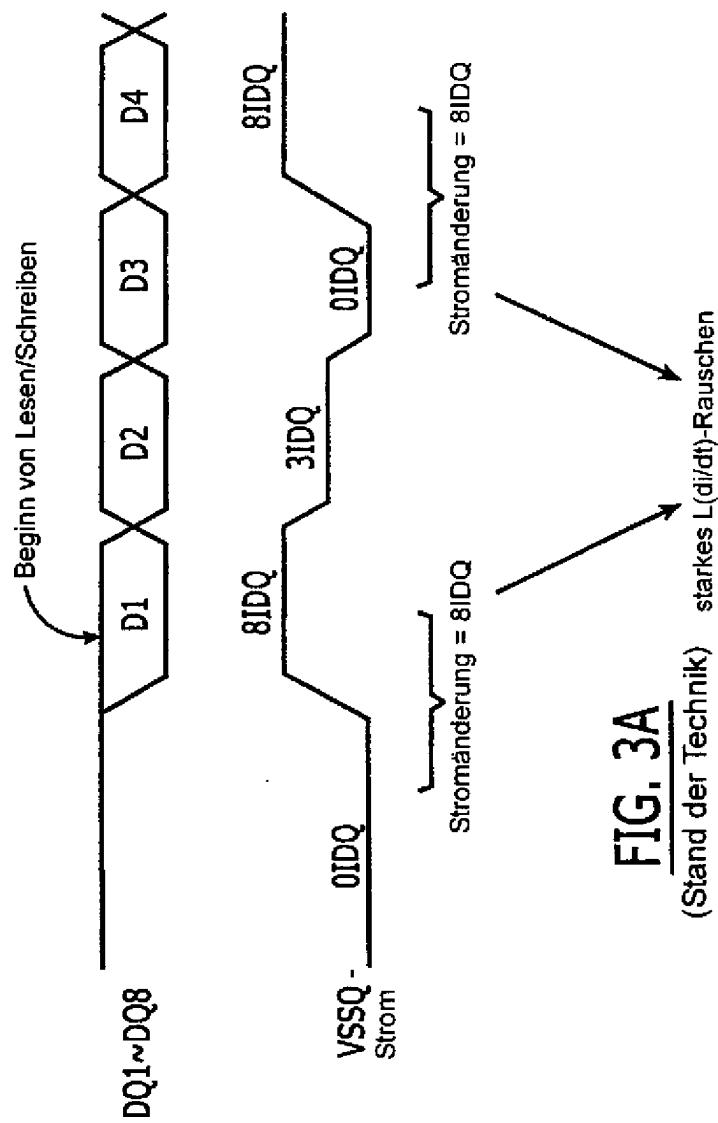

**[0009]** DC-balance-Kodierung kann das oben beschriebene SSN reduzieren. Wie insbesondere in [Fig. 3A](#) gezeigt, kann eine große Stromänderung in VSSQ während der Datenübertragung von parallelen 8-Bit-Daten, die nicht DC-balance-kodiert sind, hervorgerufen werden. Wie beispielsweise in [Fig. 3A](#) gezeigt, werden Datenworte D1–D4 mit Datenbits DQ1–DQ8 seriell übertragen, was auch als eine Les-/Schreib-Operation bezeichnet werden kann. Zwischen zwei beliebigen benachbarten Worten kann der Unterschied an Datenbits bis zu acht betragen (ein Übergang von lauter ZEROs zu lauter ONEs oder umgekehrt), wie durch die Stromänderungen von 8IDQ in [Fig. 3A](#) gezeigt. Diese Stromänderungen können starkes SSN oder L(di/dt)-Rauschen erzeugen, wie in [Fig. 3A](#) gezeigt. Wie der Fachmann versteht, bezeichnet in [Fig. 3A](#) die Terminologie XIDQ, wobei X = 0...8, die Anzahl von ZEROs oder ONEs in dem 8-Bit-Wort. Somit bezeichnet 3IDQ, drei ZEROs und fünf ONEs (oder umgekehrt), und 8IDQ bezeichnet acht ZEROs und keine ONEs (oder umgekehrt).

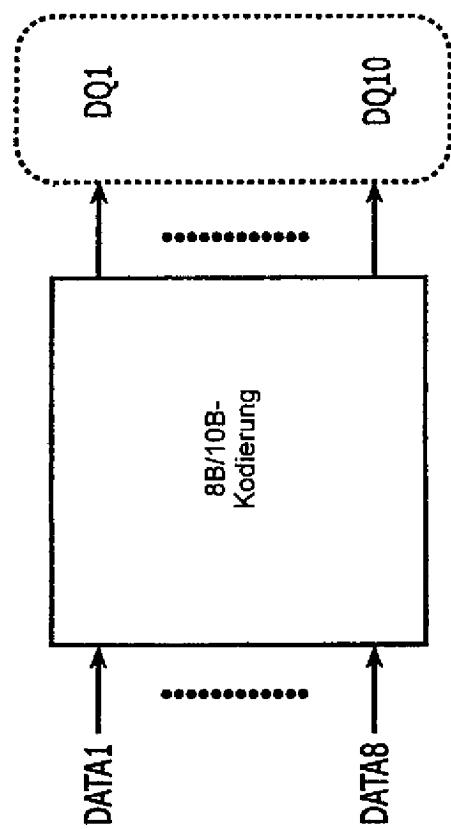

**[0010]** [Fig. 3B](#) illustriert die DC-balance-Kodierung unter Verwendung von 8B/10B-Kodierungsschemata, wobei die minimale Anzahl von ONEs in einem gegebenen Wort vier beträgt und wobei die maximale Anzahl von ONEs in einem gegebenen Wort sechs beträgt. Wie in [Fig. 3B](#) gezeigt, umfasst somit ein 8B/10B-DC-balance-kodiertes Wort zehn Bits, wobei die Anzahl von ONEs vier, fünf oder sechs und die entsprechende Anzahl von ZEROs sechs, fünf oder vier beträgt. Durch Verringerung der Stromänderung zwischen benachbarten Worten von 8B/10B-DC-balance-kodierten Daten kann L(di/dt)-Rauschen oder SSN reduziert werden.

**[0011]** Dementsprechend kann DC-balance-Kodierung, wie 8B/10B-DC-balance-Kodierung, Simultaneous Switching Noise verringern, das durch parasitäre Induktivitäten hervorgerufen wird, um auf diese Weise Hochgeschwindigkeitsübertragungen zu ermöglichen. Da jedoch Übertragungsgeschwindigkeiten weiterhin zunehmen, kann es wünschenswert sein, Simultaneous Switching Noise weiter zu reduzieren, selbst wenn DC-balance-Kodierungssysteme und -verfahren verwendet werden, wie 8B/10B-DC-balance-Kodierungssysteme und -verfahren.

**[0012]** Die US 6,026,124 zeigt ein Verfahren und eine Vorrichtung zum Erzeugen einer übergangsgesteuerten, DC-balancierten Sequenz von Zeichen aus einer Eingangssequenz von Datenbytes.

**[0013]** Der Erfindung liegt das technische Problem zugrunde, ein Verfahren zum Übertragen DC-balance-kodierter Daten, ein Verfahren zum Reduzieren von Simultaneous Switching Noise, einen Datensender, einen Datenempfänger und einen bidirektionalen Sender/Empfänger für DC-balance-kodierte Daten anzugeben, bei denen Simultaneous Switching Noise weiter reduziert ist.

**[0014]** Die Erfindung löst diese Aufgabe mittels eines Verfahrens zum Übertragen DC-balance-kodierter Daten mit den Merkmalen des Patentanspruchs 1, mittels eines Verfahrens zum Reduzieren von Simultaneous Switching Noise mit den Merkmalen des Patentanspruchs 12, mittels eines Datensenders mit den Merkmalen des Patentanspruchs 19, mittels eines Datenempfängers mit den Merkmalen des Patentanspruchs 29 und mittels eines bidirektionalen Senders/Empfängers für DC-balance-kodierte Daten mit den Merkmalen des Patentanspruchs 35.

**[0015]** Vorteilhafte Ausgestaltungen der Erfindung sind in den Unteransprüchen angegeben, deren Wortlaut hiermit durch Bezugnahme in die Beschreibung aufgenommen wird, um unnötige Textwiederholungen zu vermeiden.

**[0016]** DC-balance-kodierte Daten werden gemäß einigen Ausgestaltungen der vorliegenden Erfindung

übertragen, indem ein Vorspann aus Dummy-Daten übertragen wird, der dazu ausgebildet ist, eine Zwischenanzahl von Bits mit einem gegebenen Logikwert bereitzustellen, wobei es sich um wenigstens ein Bit des gegebenen Logikwerts, jedoch um weniger als eine maximale Anzahl von Bits eines gegebenen Logikwerts in den DC-balance-kodierten Daten handelt. Die DC-balance-kodierten Daten werden dann gesendet. Gemäß einigen Ausgestaltungen der vorliegenden Erfindung wurde festgestellt, dass der Vorspann aus Dummy-Daten einen Zwischenpegel an Simultaneous Switching Noise (SSN) erzeugen kann, der starker ist als ZERO-SSN, jedoch schwächer als ein maximales SSN, das durch die DC-balance-kodierten Daten hervorgerufen wird. Durch Übertragen eines ersten Worts DC-balance-kodierter Daten hervorgerufenes SSN kann dadurch reduziert werden.

**[0017]** In einigen Ausgestaltungen beinhaltet der Vorspann aus Dummy-Daten einen festen Vorspann aus Dummy-Daten, der dazu ausgebildet ist, eine feste Zwischenanzahl von Bits eines gegebenen Logikwerts bereitzustellen, die unabhängig von einer Anzahl von Bits des gegebenen Logikwerts in einem ersten Wort der DC-balance-kodierten Daten ist. Beispielsweise entspricht in einigen Ausgestaltungen der feste Vorspann aus Dummy-Daten der halben Maximalanzahl von Bits des gegebenen Logikwerts in den DC-balance-kodierten Daten. In anderen Ausgestaltungen, wenn es sich bei den DC-balance-kodierten Daten um 8B/10B-DC-balance-kodierte Daten handelt, beträgt die feste Zwischenanzahl von Bits eines gegebenen Logikwertes wenigstens ein Bit, jedoch weniger als sechs Bits des gegebenen Logikwerts. In anderen Ausgestaltungen, die 8B/10B-DC-balance-kodierte Daten verwenden, beträgt die feste Zwischenanzahl von Bits eines gegebenen Logikwerts drei Bits des gegebenen Logikwerts.

**[0018]** In weiteren Ausgestaltungen umfasst der Vorspann aus Dummy-Daten einen veränderbaren Vorspann aus Dummy-Daten, der dazu ausgebildet ist, eine veränderbare Zwischenanzahl von Bits des gegebenen Logikwerts bereitzustellen, die von der Anzahl von Bits des gegebenen Logikwerts der DC-balance-kodierten Daten abhängt. In einigen Ausgestaltungen kann der veränderbare Vorspann die halbe Anzahl von Bits des gegebenen Logikwerts enthalten, die in dem ersten Wort der DC-balance-kodierten Daten enthalten sind.

**[0019]** In einigen Ausgestaltungen wird ein einzelnes Vorspannwort aus Dummy-Daten bereitgestellt. In anderen Ausgestaltungen werden eine Mehrzahl von Vorspannwörtern aus Dummy-Daten seriell übertragen. Die mehrzähligen Vorspannwörter aus Dummy-Daten können ein erstes Vorspannwort aus Dummy-Daten und ein zweites Vorspannwort aus Dummy-Daten umfassen, das mehr Bits des gegebenen Logikwerts als das erste Vorspannwort aufweist.

**[0020]** Zudem können mehrzählige feste Vorspannwörter und/oder mehrzählige veränderbare Vorspannwörter gemäß verschiedene Ausgestaltungen der Erfindung bereitgestellt werden. Bei den mehrzähligen festen Vorspannwörtern stellen sowohl die ersten als auch die zweiten Vorspannwörter eine feste Zwischenanzahl von Bits des gegebenen Logikwerts zur Verfügung, die unabhängig von der Anzahl von Bits des gegebenen Logikwerts in dem ersten Wort der DC-balance-kodierten Daten sind. Im Gegensatz dazu sind bei den mehrzähligen veränderbaren Wortvorspänen das erste Vorspannwort und das zweite Vorspannwort dazu ausgebildet, eine veränderbare Zwischenanzahl von Bits des gegebenen Logikwerts bereitzustellen, die von der Anzahl von Bits des gegebenen Logikwerts in dem ersten Wort der DC-balance-kodierten Daten abhängen. Kombinationen von festen und veränderbaren Vorspänen können auch bereitgestellt werden. Beispielsweise kann bei einigen Ausgestaltungen, wenn es sich bei den DC-balance-kodierten Daten um 8B/10B-DC-balance-kodierte Daten handelt, das erste feste Vorspannwort zwei Bits des gegebenen Logikwerts beinhalten und das zweite feste Vorspannwort kann vier Bits des gegebenen Logikwerts beinhalten. In mehrzähligen veränderbaren Wortvorspänen kann das erste veränderbare Vorspannwort ein Viertel der Anzahl von Bits des gegebenen Logikwerts in dem ersten Wort der DC-balance-kodierten Daten aufweisen, und das zweite Vorspannwort kann eine Hälfte der Anzahl von Bits des gegebenen Logikwerts des ersten Worts der DC-balance-kodierten Daten aufweisen.

**[0021]** DC-balance-kodierte Daten können auch gemäß anderen Ausgestaltungen der vorliegenden Erfindung empfangen werden. Insbesondere können der Vorspann aus Dummy-Daten und die DC-balance-kodierten Daten empfangen werden. Die Dummy-Daten werden verworfen und die DC-balance-kodierten Daten, die empfangen wurden, werden dekodiert. Der Vorspann aus Dummy-Daten kann gemäß einer beliebigen, weiter oben beschriebenen Ausgestaltung der Erfindung ausgebildet sein.

**[0022]** Weitere Ausgestaltungen der Erfindung schaffen Verfahren zum Reduzieren von Simultaneous Switching Noise (SSN), das durch DC-balance-kodierte Daten hervorgerufen wird, indem ein Vorspann übertragen wird, der dazu ausgebildet ist, einen Zwischenpegel von SSN zu erzeugen, der höher liegt als ZERO-SSN, der jedoch schwächer ist als ein maximales SSN, das durch die DC-balance-kodierten Daten hervorgerufen wird, bevor die DC-balance-kodierten Daten übertragen werden. Der Vorspann kann ein fester Vorspann oder ein veränderbarer Vorspann sein und kann ein einzelnes Vorspannwort oder mehrere Vorspannwörter umfassen.

**[0023]** Weitere Ausgestaltungen der vorliegenden Erfindung schaffen Datensender für DC-balance-k-

dierte Daten. Diese Sender können eine Datenkodiereinheit, einen Vorspanncodeerzeuger, einen Multiplexer und einen Ausgabetreiber umfassen. Die Datenkodiereinheit ist dazu ausgebildet, Daten in DC-balance-kodierte Daten zu kodieren. Der Vorspannungscoderzeuger ist dazu ausgebildet, einen Vorspann aus Dummy-Daten zu erzeugen, der dazu ausgebildet ist, eine Zwischenanzahl von Bits eines gegebenen Logikwerts bereitzustellen, wobei es sich um wenigstens ein Bit des gegebenen Logikwerts, jedoch um weniger als eine Maximalanzahl von Bits des gegebenen Logikwerts in den DC-balance-kodierten Daten handelt. Der Multiplexer wird durch die Datenkodiereinheit und den Vorspannerzeuger gesteuert und ist dazu ausgebildet, den Vorspann aus Dummy-Daten gefolgt von den DC-balance-kodierten Daten zu liefern. Schließlich wird der Ausgabetreiber durch den Multiplexer gesteuert und ist dazu ausgebildet, den Vorspann aus Dummy-Daten gefolgt von den DC-balance-kodierten Daten zu übertragen. Wie oben unter Bezugnahme auf einige Ausgestaltungen der vorliegenden Erfindung beschrieben wurde, können ein fester Vorspann, ein veränderbarer Vorspann, ein Einzelwortvorspann und/oder Mehrwortvorspanne erzeugt und übertragen werden.

**[0024]** Weitere Ausgestaltungen der vorliegenden Erfindung schaffen Datenempfänger. Diese Datenempfänger umfassen einen Dateneingabepuffer und eine Datenkodiereinheit. Der Dateneingabepuffer ist dazu ausgebildet, Daten zu empfangen, die einen Vorspann aus Dummy-Daten gefolgt von DC-balance-kodierten Daten enthalten, und die Dummy-Daten zu erkennen und zu verwerfen. Die Dekodiereinheit ist dazu ausgebildet, die DC-balance-kodierten Daten zu dekodieren, die durch den Dateneingabepuffer empfangen wurden. Der Dateneingabepuffer kann einen Vorspanncodedetektor, der dazu ausgebildet ist, die Dummy-Daten zu erkennen, sowie einen Demultiplexer aufweisen, der dazu ausgebildet ist, selektiv die Dummy-Daten zu verwerfen und selektiv die DC-balance-kodierten Daten an die Dekodiereinheit zu liefern. Wie bei allen oben beschriebenen Ausgestaltungen kann der Vorspann aus Dummy-Daten einen festen Vorspann, einen veränderbaren Vorspann, einen Einzelwortvorspann und/oder einen Mehrwortvorspann aus Dummy-Daten umfassen. Des Weiteren können Datensender und Datenempfänger gemäß Ausgestaltungen der vorliegenden Erfindung kombiniert sein, um einen bidirektionalen Sender/Empfänger bereitzustellen, der sowohl Daten übertragen als auch Daten empfangen kann, einschließlich der oben beschriebenen Vorspanne.

**[0025]** Schließlich nahmen alle oben beschriebenen Ausgestaltungen Bezug auf eine Anzahl von Bits eines gegebenen Logikwerts. In einigen Ausgestaltungen kann dies einer Anzahl von ZEROs (Nullen) entsprechen, wohingegen dies bei anderen Ausgestaltungen einer Anzahl von ONEs (Einsen) ent-

sprechen kann. Bei einigen Ausgestaltungen, bei denen der Datenempfänger einen Abschlusswiderstand aufweist, der mit einer Versorgungsspannung verbunden ist, sind die Bits des gegebenen Logikwerts ZEROs. Demgegenüber ist bei anderen Ausgestaltungen, bei denen der Datenempfänger einen Abschlusswiderstand umfasst, der mit Masse verbunden ist, die Anzahl von Bits des gegebenen Logikwerts ONE.

**[0026]** Vorteilhafte Ausgestaltungen der Erfindung, die nachfolgend detailliert beschrieben sind, sowie die weiter oben zur Erleichterung des Verständnisses der Erfindung erläuterten Ausgestaltungen des Standes der Technik sind in der Zeichnung dargestellt. Es zeigt/zeigen:

**[0027]** [Fig. 1](#) eine Reproduktion der [Fig. 1](#) der US-Patentschrift 5,387,911;

**[0028]** [Fig. 2A](#) und [Fig. 2B](#) Schaltungsdiagramme herkömmlicher Schnittstellensysteme mit einer Sendereinheit und einer Empfängereinheit;

**[0029]** [Fig. 3A](#) ein Zeitablaufdiagramm von Stromänderungen während herkömmlicher Datenübertragung;

**[0030]** [Fig. 3B](#) ein Blockschaltbild einer herkömmlichen DC-balance-Kodierung unter Verwendung eines 8B/10B-Codierschemas;

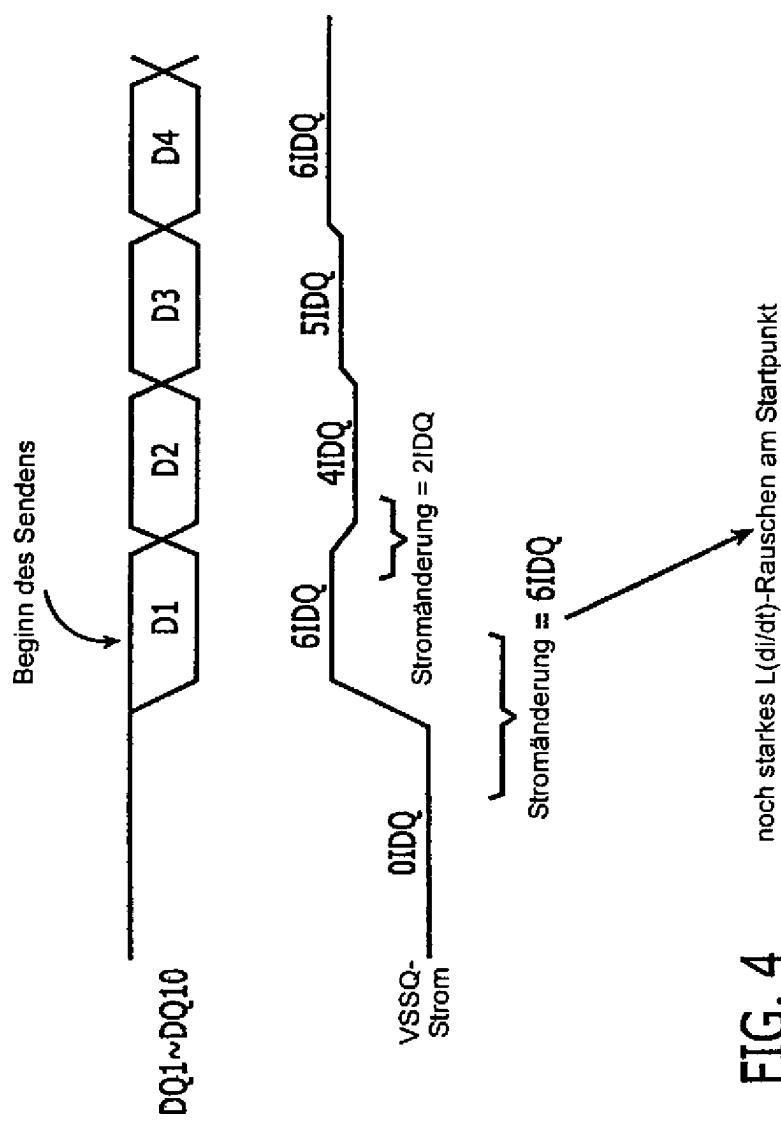

**[0031]** [Fig. 4](#) ein Zeitablaufdiagramm einer DC-balance-Kodierung gemäß einigen Ausgestaltungen der vorliegenden Erfindung;

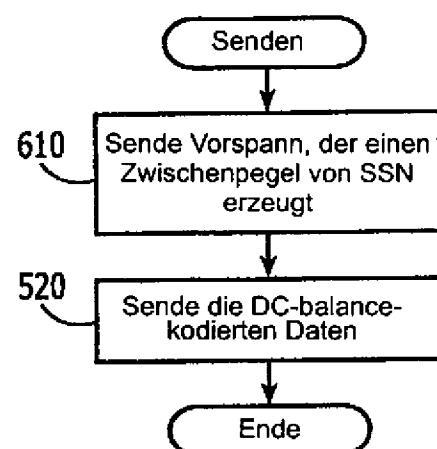

**[0032]** [Fig. 5](#) und [Fig. 6](#) Flussdiagramme von Operationen, die durchgeführt werden können, um Daten gemäß einigen Ausgestaltungen der vorliegenden Erfindung zu übertragen;

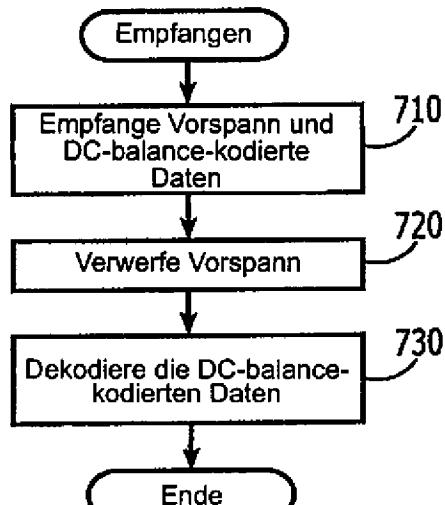

**[0033]** [Fig. 7](#) ein Flussdiagramm von Operationen, die durchgeführt werden können, um Daten gemäß einigen Ausgestaltungen der vorliegenden Erfindung zu empfangen;

**[0034]** [Fig. 8](#) ein Blockschaltbild zur Darstellung von Datenübertragung und -empfang gemäß unterschiedlichen Ausgestaltungen der vorliegenden Erfindung.

**[0035]** [Fig. 9](#) ein Blockschaltbild eines Vorspann-codeerzeugers gemäß einigen Ausgestaltungen der vorliegenden Erfindung;

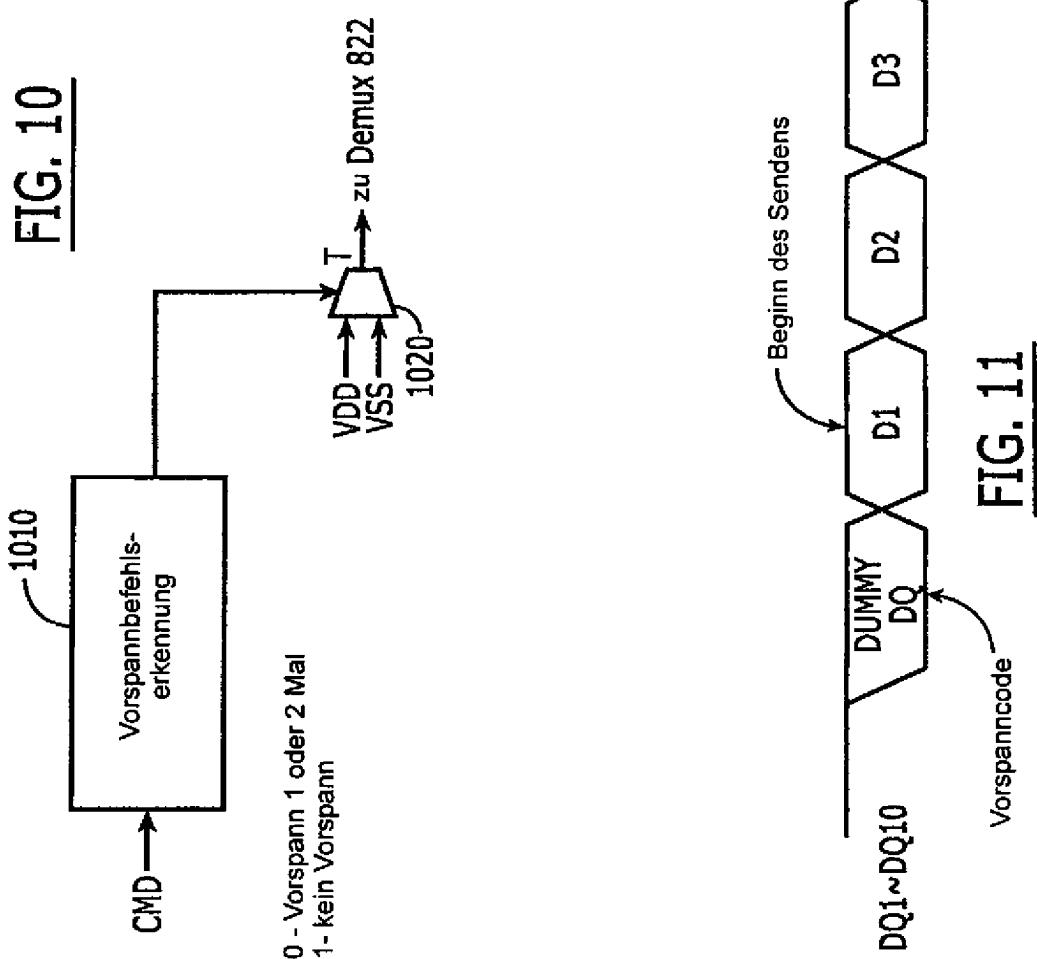

**[0036]** [Fig. 10](#) ein Blockschaltbild eines Vorspann-codeerzeugers gemäß einigen Ausgestaltungen der vorliegenden Erfindung;

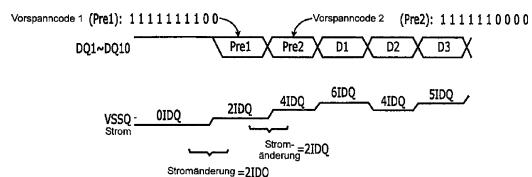

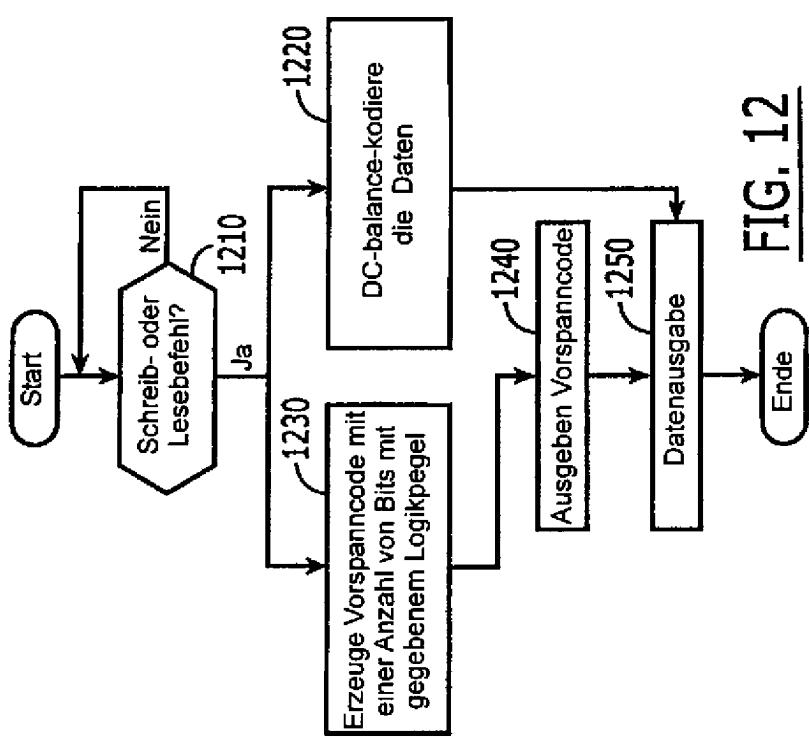

[0037] [Fig. 11](#) ein Zeitablaufdiagramm zur Darstellung einer Übertragung DC-balance-kodierter Daten gemäß einigen Ausgestaltungen der vorliegenden Erfindung;

[0038] [Fig. 12](#) ein Flussdiagramm von Operationen, die durchgeführt werden können, um DC-balance-kodierte Daten gemäß einigen Ausgestaltungen der vorliegenden Erfindung zu übertragen;

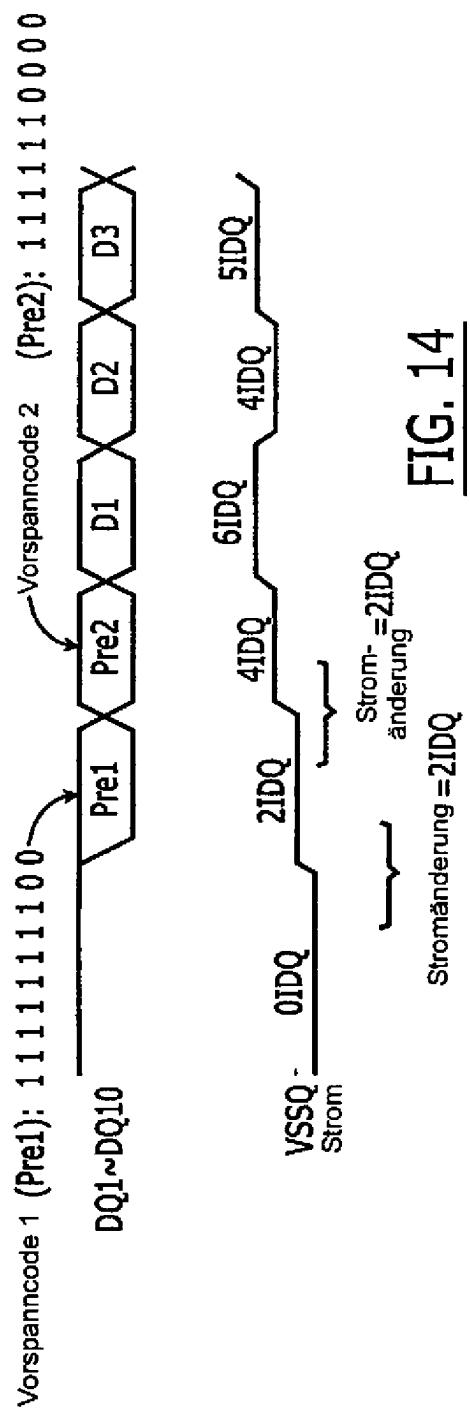

[0039] [Fig. 13](#) ein Zeitablaufdiagramm gemäß einem speziellen Beispiel in [Fig. 11](#);

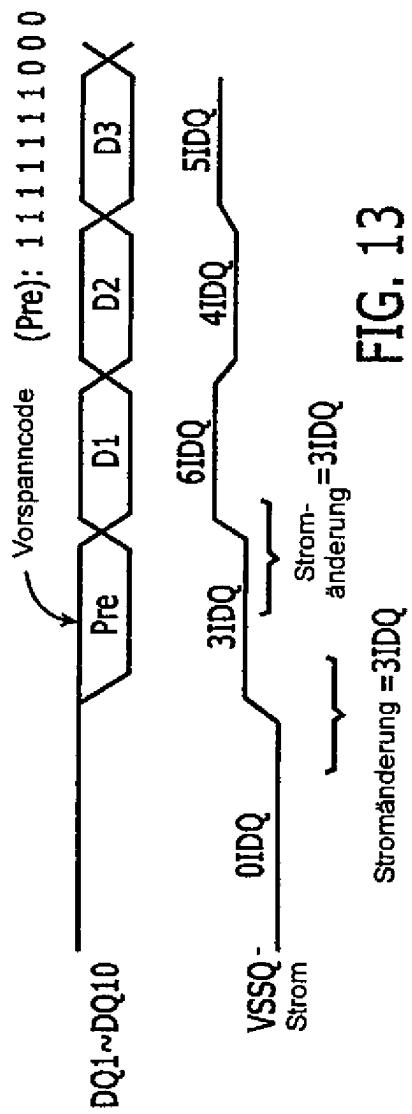

[0040] [Fig. 14](#) ein Zeitablaufdiagramm zum Empfangen zweier fester Vorspannwörter gemäß einigen Ausgestaltungen der vorliegenden Erfindung;

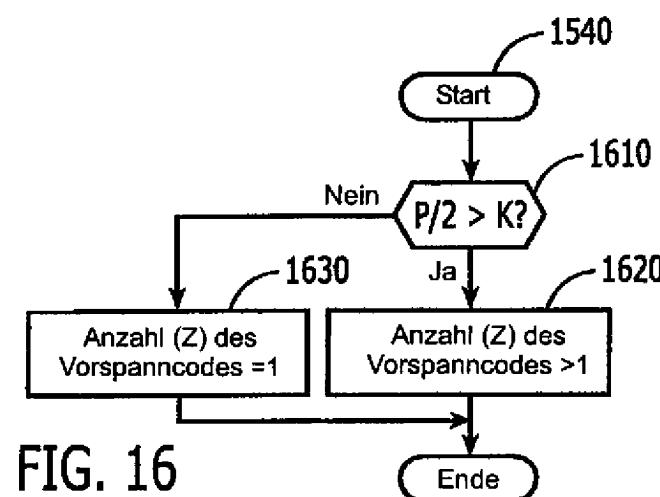

[0041] [Fig. 15](#) ein Flussdiagramm von Operationen zum Empfangen von Daten gemäß einigen Ausgestaltungen der vorliegenden Erfindung;

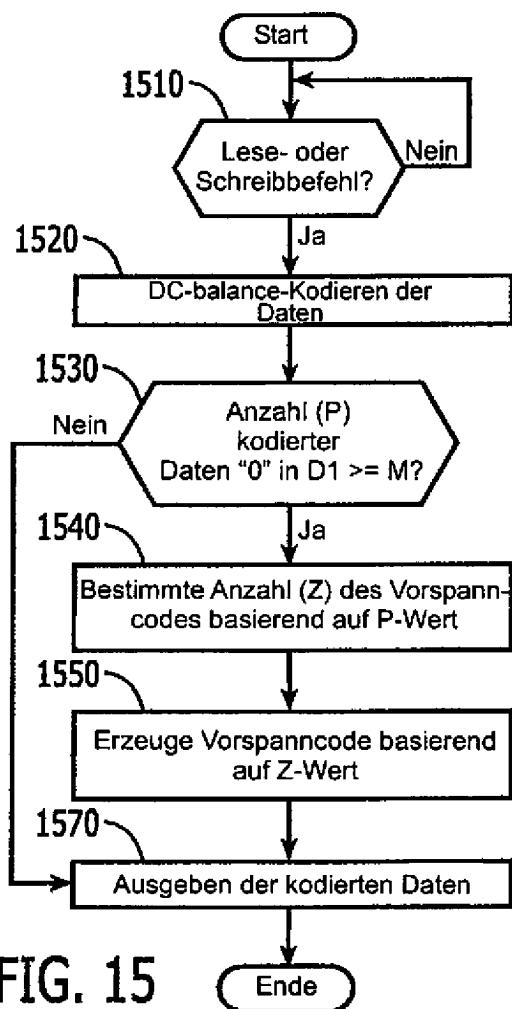

[0042] [Fig. 16](#) ein Flussdiagramm von Operationen, die durchgeführt werden können, um eine Anzahl zu verwendender Vorspanncodewörter gemäß einigen Ausgestaltungen der vorliegenden Erfindung zu bestimmen; und

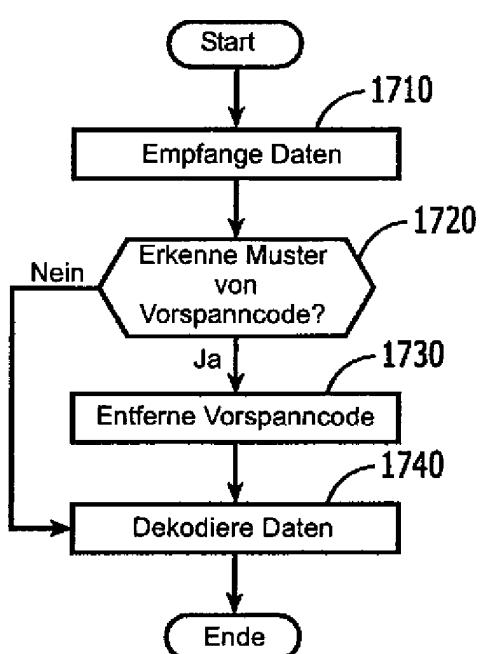

[0043] [Fig. 17](#) ein Flussdiagramm von Operationen, die durchgeführt werden können, um Daten gemäß einigen Ausgestaltungen der vorliegenden Erfindung zu empfangen.

[0044] Es sei darauf hingewiesen, dass ein Element oder eine Schicht, das bzw. die als mit einem anderen Element „verbunden“, „gekoppelt“ oder von diesem „abhängig“ oder „gesteuert“ (und/oder Varianten hiervon) beschrieben ist, direkt mit dem anderen Element verbunden oder gekoppelt oder von diesem abhängig sein kann oder dass Zwischenelemente vorhanden sein können. Wenn dagegen ein Element als mit einem anderen Element „direkt verbunden“, „direkt gekoppelt“ oder von diesem „direkt abhängig“ (und/oder Varianten hiervon) beschrieben ist, sind keine Zwischenelemente vorhanden. Gleiche Nummern bezeichnen durchgängig dieselben Elemente.

[0045] Die vorliegende Erfindung wird nachfolgend unter Bezugnahme auf Blockschaltbilder und/oder Flussdiagramme beschrieben, die Illustrationen von Verfahren und/oder Vorrichtungen (Systemen) gemäß Ausgestaltungen der Erfindung darstellen. Es sei angenommen, dass ein Block der Blockdiagramme und/oder Flussdiagramme sowie Kombinationen von Blöcken in den Blockdiagrammen und/oder Flussdiagrammen Vorrichtungen/Systeme (Struktur), Mittel (Funktion) und/oder Schritte (Verfahren) zum Implementieren der Funktionen/Tätigkeiten darstellen können, die in den Blockdiagrammen und/oder dem Block oder den Blöcken von Flussdiagrammen angegeben sind.

[0046] Es sei darauf hingewiesen, dass in einigen alternativen Implementierungen, die in den Blöcken abgegebene Funktionen/Tätigkeiten in einer anderen Reihenfolge stattfinden können, als in den Flussdiagrammen angegeben. Beispielsweise können zwei Blöcke, die nacheinander dargestellt sind, tatsächlich im Wesentlichen gleichzeitig ausgeführt werden oder die Blöcke können gelegentlich in der umgekehrten Reihenfolge ausgeführt werden, was von den betreffenden Funktionen/Tätigkeiten abhängt. Des Weiteren kann die Funktion eines gegebenen Blocks in den Flussdiagrammen und/oder Blockdiagrammen in mehrere Blöcke unterteilt sein und/oder die Funktion zweier oder mehrerer Blöcke der Flussdiagramme und/oder Blockdiagramme kann zumindest teilweise zusammengefasst sein.

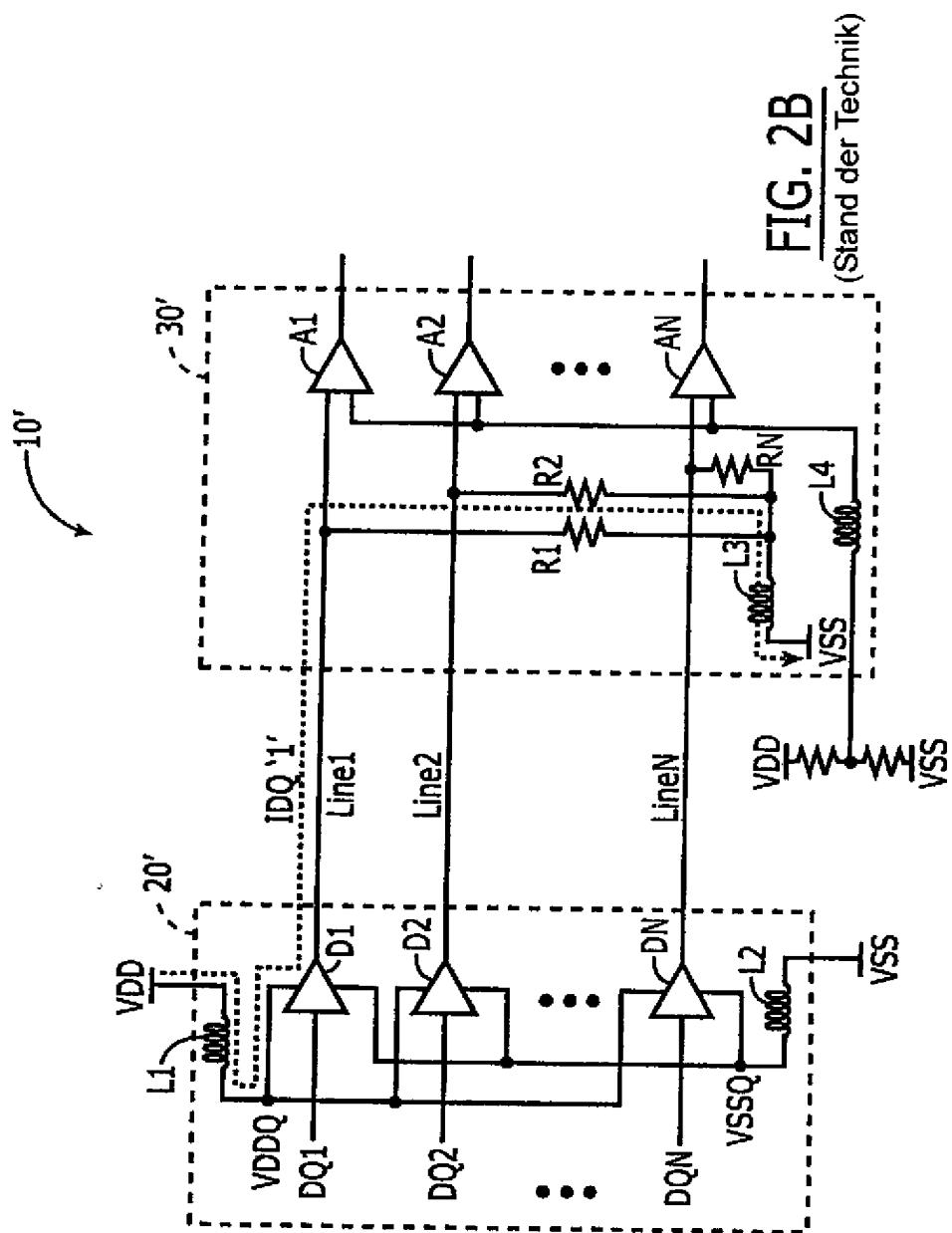

[0047] Einige Ausgestaltungen der vorliegenden Erfindung können sich aus der Erkenntnis ergeben, dass trotz der Tatsache, dass DC-balance-kodierte Daten, wie 8B/10B-DC-balance-kodierte Daten, Simultaneous Switching Noise (SSN) zwischen benachbarten Datenwörtern reduzieren können, starkes SSN beim Übertragen eines ersten Datenworts erzeugt werden kann. [Fig. 4](#) illustriert diese Erkenntnis. Wie in dem oberen Zeitablaufdiagramm in [Fig. 4](#) gezeigt, wird eine Mehrzahl von Wörtern aus 8B/10B-DC-balance-kodierten Daten übertragen, wie durch Worte D1, D2, D3 und D4 angezeigt. Jedes Wort umfasst zehn Bits DQ1–DQ10. Die untere Spur in [Fig. 4](#) zeigt den Schaltstrom an, der durch jedes Wort erzeugt wird, wobei eine Schaltstromeinheit (VSSQ-Strom) mit IDQ bezeichnet und zu der Anzahl von Bits des gegebenen Logikwerts, vorliegend ZEROs, proportional ist. Somit erzeugt, wie anhand der unteren Spur in [Fig. 4](#) gezeigt ist, der Übergang zwischen dem ersten Wort D1 und dem zweiten Wort D2 eine Stromänderung von 2IDQ, der Übergang zwischen dem zweiten Wort D2 und dem dritten Wort D3 erzeugt eine Stromänderung von 1IDQ und der Übergang zwischen dem dritten Wort D3 und dem vierten Wort D4 erzeugt gemäß dem vorliegenden Fall eine Stromänderung von 1IDQ. Wie ebenfalls dargestellt, beträgt die maximale Stromänderung zwischen benachbarten Wörtern aufgrund der 8B/10B-Kodierung 2IDQ und einige benachbarte Worte erzeugen aufgrund der 8B/10B-Kodierung nur eine Stromänderung von 1IDQ oder keine Stromänderung.

[0048] Wie jedoch ebenfalls in [Fig. 4](#) gezeigt, wird vor dem Übertragen des ersten Wortes D1 kein Schaltstrom erzeugt, so dass die Stromänderung beim Übertragen des ersten Wortes D1 bis zu 6IDQ betragen kann, was der dreifachen maximalen Stromänderung entspricht, die zwischen benachbarten Wörtern der DC-balance-kodierten Daten gegeben ist. Es hat sich gemäß einigen Ausgestaltungen der Erfindung gezeigt, dass diese große Stromänderung am Startpunkt der Datenübertragung star-

kes SSN erzeugt, was auch als L(di/dt)-Rauschen bezeichnet wird.

**[0049]** Ausgestaltungen der vorliegenden Erfindung können dieses starke SSN beim Beginn der Datenübertragung reduzieren, indem ein Vorspann aus Dummy-Daten am Beginn der Übertragung hinzugefügt wird. [Fig. 5](#) ist ein Flussdiagramm der Operationen, die gemäß einigen Ausgestaltungen der Erfindung durchgeführt werden können.

**[0050]** Bezugnehmend auf [Fig. 5](#) werden in Block **510** die DC-balance-kodierten Daten übertragen, indem zuerst ein Vorspann aus Dummy-Daten übertragen wird, der dazu ausgebildet ist, eine Zwischenanzahl von Bits eines gegebenen Logikwerts bereitzustellen. Die Zwischenanzahl von Bits ist größer als ein Bit des gegebenen Logikwerts, jedoch kleiner als eine Maximalanzahl von Bits des gegebenen Logikwerts in den DC-balance-kodierten Daten. Dann werden in Block **520** die DC-balance-kodierten Daten selbst übertragen. Indem der Übertragung der DC-balance-kodierten Daten ein Vorspann aus Dummy-Daten vorausgeht, der eine Zwischenanzahl von Bits umfasst, kann verglichen mit einem Fehlen der Vorspanndaten SSN reduziert werden.

**[0051]** In einem Beispiel können 8B/10B-DC-balance-kodierte Daten immer vier, fünf oder sechs ZEROs enthalten. Bei diesen Ausgestaltungen kann der Vorspann zwischen einer und fünf ZEROs enthalten. Weitere Beispiele sind weiter unten beschrieben.

**[0052]** Wie weiter unten detailliert beschrieben, kann bei einigen Ausgestaltungen der Vorspann aus Dummy-Daten immer dieselbe Zwischenanzahl an Bits aufweisen (ein fester Vorspann), die unabhängig von der Anzahl von Bits des gegebenen Logikwerts in dem ersten Wort der DC-balance-kodierten Daten ist. Bei anderen Ausgestaltungen kann der Vorspann eine veränderbare Anzahl von Bits des gegebenen Logikwerts umfassen, die von der Anzahl von Bits des gegebenen Logikwerts in dem ersten Wort der DC-balance-kodierten Daten abhängt. Wie weiter unten detailliert beschrieben, kann ein einzelnes Vorspannwort (fest oder veränderbar) oder mehrere Vorspannwörter (fest und/oder veränderbar) bereitgestellt werden. Die mehrzähligen Vorspannwörter können eine stärker abgestufte Stromänderung bereitstellen und können daher verglichen mit der Verwendung eines einzelnen Vorspannworts SSN weiter reduzieren. Jede/s dieser Ausgestaltungen und Beispiele dafür sind weiter unten im Detail beschrieben.

**[0053]** [Fig. 6](#) ist ein Flussdiagramm von Operationen, die gemäß anderen Ausgestaltungen der vorliegenden Erfindung durchgeführt werden können, um SSN zu reduzieren, wenn DC-balance-kodierte Daten übertragen werden. Wie in [Fig. 6](#) gezeigt, wird in Block **610** ein Vorspann übertragen, der dazu aus-

gebildet ist, einen Zwischenpegel an SSN zu erzeugen, der höher liegt als kein SSN, jedoch niedriger als ein maximales SSN, das durch die DC-balance-kodierten Daten erzeugt wird. Anschließend werden die DC-balance-kodierten Daten übertragen, wie im Block **520** beschrieben. Wie oben beschrieben, kann der Vorspann ein fester Vorspann, der unabhängig von dem Inhalt eines ersten Worts der DC-balance-kodierten Daten ist, ein veränderbarer Vorspann, der von einem Inhalt des ersten Worts der DC-balance-kodierten Daten abhängt, ein einzelnes Vorspannwort und/oder mehrere Vorspannwörter sein. Dementsprechend können auch Vorspanne bereitgestellt werden, die Konfigurationen aufweisen, die von einer Zwischenanzahl von Bits des gegebenen Logikwerts abweichen, solange sie einen Zwischenpegel an SSN erzeugen.

**[0054]** [Fig. 7](#) ist ein Flussdiagramm von Operationen, die gemäß unterschiedlichen Ausgestaltungen der vorliegenden Erfindung durchgeführt werden können, um DC-balance-kodierte Daten zu empfangen. Wie in [Fig. 7](#) gezeigt, werden in Block **710** ein Vorspann gemäß einer der oben beschriebenen Ausgestaltungen und die DC-balance-kodierten Daten empfangen. Der Vorspann wird in Block **720** verworfen und die DC-balance-kodierten Daten werden in Block **730** dekodiert.

**[0055]** Vielfältige Ausgestaltungen der vorliegenden Erfindung werden nun unter Bezugnahme auf die [Fig. 8](#) bis [Fig. 17](#) beschrieben. Bei all diesen Ausgestaltungen handelt es sich bei den DC-balance-kodierten Daten um 8B/10B-DC-balance-kodierte Daten und die Bits des gegebenen Logikwerts sind ZEROs. Diese Ausgestaltungen können mit Datenempfängern verwendet werden, die Abschlusswiderstände aufweisen, die mit einer Versorgungsspannung verbunden sein können. Es versteht sich, dass auch zu 8B/10B-DC-balance-kodierten Daten analog DC-balance-kodierte Daten bereitgestellt werden können und analoge Ausgestaltungen bereitgestellt werden können, wenn die Bits des gegebenen Logikwerts ONEs sind, beispielsweise wenn die Abschlusswiderstände mit Masse verbunden sind.

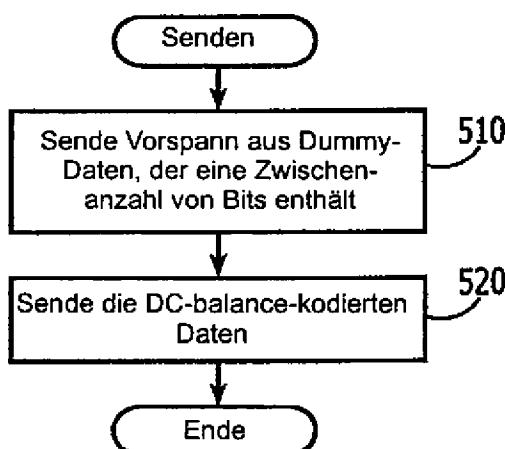

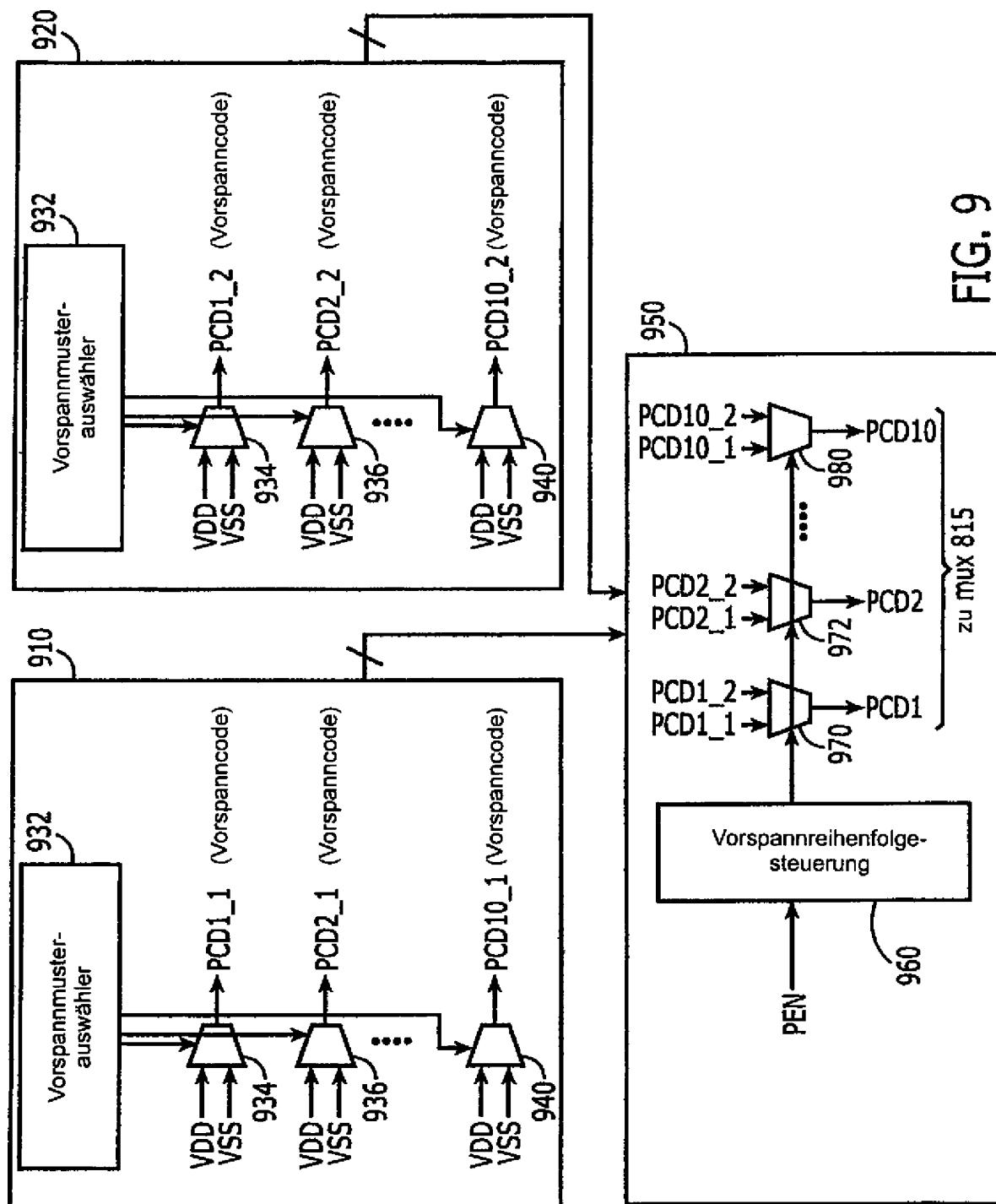

**[0056]** [Fig. 8](#) ist ein Blockschaltbild eines Datenübertragungs- und -empfangssystems **800** gemäß unterschiedlichen Ausgestaltungen der vorliegenden Erfindung. Das Übertragungs- und Empfangssystem **800** ist gemäß [Fig. 8](#) als ein einendiges (single ended) paralleles N-Bit-Datenschnittstellensystem ausgebildet, das einen Sender **810** und einen Empfänger **820** umfasst. Es sei jedoch betont, dass trotz der Darstellungen in [Fig. 8](#), wonach die Übertragung von dem Sender **810** zu dem Empfänger **820** erfolgt, auch bidirektionale Systeme bereitgestellt werden können, bei denen jedes Ende einen Sender und einen Empfänger umfasst.

**[0057]** Weiter bezugnehmend auf [Fig. 8](#) umfasst der Datensender **810** eine Datenkodiereinheit **814**, die dazu ausgebildet ist, Daten, beispielsweise N-Bit-Daten, in DC-balance-kodierte Daten, beispielsweise M-Bit-Daten, zu kodieren. Ein Vorspanncodeerzeuger **812** ist dazu ausgebildet, einen Vorspann aus Dummy-Daten (PCD1–PCD10) zu erzeugen, der dazu ausgebildet ist, eine Zwischenanzahl von Bits eines gegebenen Logikwerts (vorliegend ZEROs), der wenigstens einer ZERO entspricht, jedoch kleiner ist als eine Maximalanzahl von ZEROs in den DC-balance-kodierten Daten, bereitzustellen. Ein Multiplexer **815** wird durch die Datenkodiereinheit **814** und den Vorspanncodeerzeuger **812** gesteuert und ist dazu ausgebildet, ein oder mehrere M-Bit-Vorspannwörter aus Dummydaten gefolgt von einem oder mehreren M-Bit-Wörtern der DC-balance-kodierten Daten bereitzustellen. Ein Ausgabetreiber **816** wird durch den Multiplexer **815** gesteuert und ist dazu ausgebildet, das Vorspannwort bzw. die Vorspannwörter aus Dummy-Daten gefolgt von dem Wort bzw. den Wörtern aus DC-balance-kodierten Daten zu senden. Wie weiterhin in [Fig. 8](#) gezeigt, kann der Sender **810** weiterhin eine Datenspeichereinheit **813**, die die mittels DC-balance zu kodierenden Originaldaten speichert, sowie eine Befehls-Dekodiereinheit **811** umfassen, welche einen Befehl RD dekodiert und welche die Datenspeichereinheit **813** (IRD-Befehl), den Vorspanncodeerzeuger **812** und den Multiplexer **815** (PEN-Befehl) steuert.

**[0058]** Bei fortgesetzter Beschreibung der [Fig. 8](#) umfasst der Datenempfänger **820** einen Dateneingabepuffer **825**, eine Dekodiereinheit **823** und eine Datenspeichereinheit **824**. Der Dateneingabepuffer **825** ist dazu ausgebildet, die Daten zu empfangen, die einen Vorspann aus Dummy-Daten gefolgt von DC-balance-kodierten Daten beinhalten, und die Dummy-Daten zu erkennen und zu verwerfen. Die Dekodiereinheit **823** ist dazu ausgebildet, die DC-balance-kodierten Daten zu dekodieren, die durch den Eingabedatenpuffer **825** empfangen wurden.

**[0059]** Wie speziell in [Fig. 8](#) gezeigt, kann der Dateneingabepuffer **825** einen Vorspanncodedetektor **821** umfassen, der durch einen Befehl CMD gesteuert ist, um die Dummy-Daten zu erkennen. Ein Demultiplexer **822** wird von dem Vorspanncodedetektor **821** (Befehl T) gesteuert und ist dazu ausgebildet, selektiv die Dummy-Daten zu verwerfen und selektiv DC-balance-kodierte Daten (M-Bits) an die Dekodiereinheit **823** zu liefern. Die dekodierten Daten (N-Bits) werden in der Datenspeichereinheit **824** gespeichert. Wie der Fachmann weiterhin erkennt, können gemäß vielfältigen anderen Ausgestaltungen der vorliegenden Erfindung andere Konfigurationen von Sendern **810** und Empfängern **820** angegeben werden.

**[0060]** M-Signalleitungen werden verwendet, um die digitalen Signale zwischen dem Sender **810** und dem

Empfänger **820** zu übertragen. Bei den Signalleitungen kann es sich um „on-chip“-Signalleitungen handeln, welche die verschiedenen Subsysteme auf einem einzelnen integrierten Schaltungsschip verbinden. Beispielsweise können On-Chip-Signalleitungen ein Subspeichersystem mit einem Prozessor- oder Hostsubsystem auf einem einzelnen integrierten Schaltungsschip verbinden. Die digitalen On-Chip-Signale können beispielsweise Datensignale von einem Subspeichersystem sein, die oft als „DQ-Signale“ bezeichnet werden. Die Signalleitungen können auch „off-chip“-Signalleitungen sein, wobei Ausgabetreiber ein digitales Signal außerhalb eines integrierten Schaltungsschips über eine Signalleitung treiben, die einen gegebenen Chip mit einem anderen Chip, einem anderen Package-Level und/oder mit einem externen System verbinden.

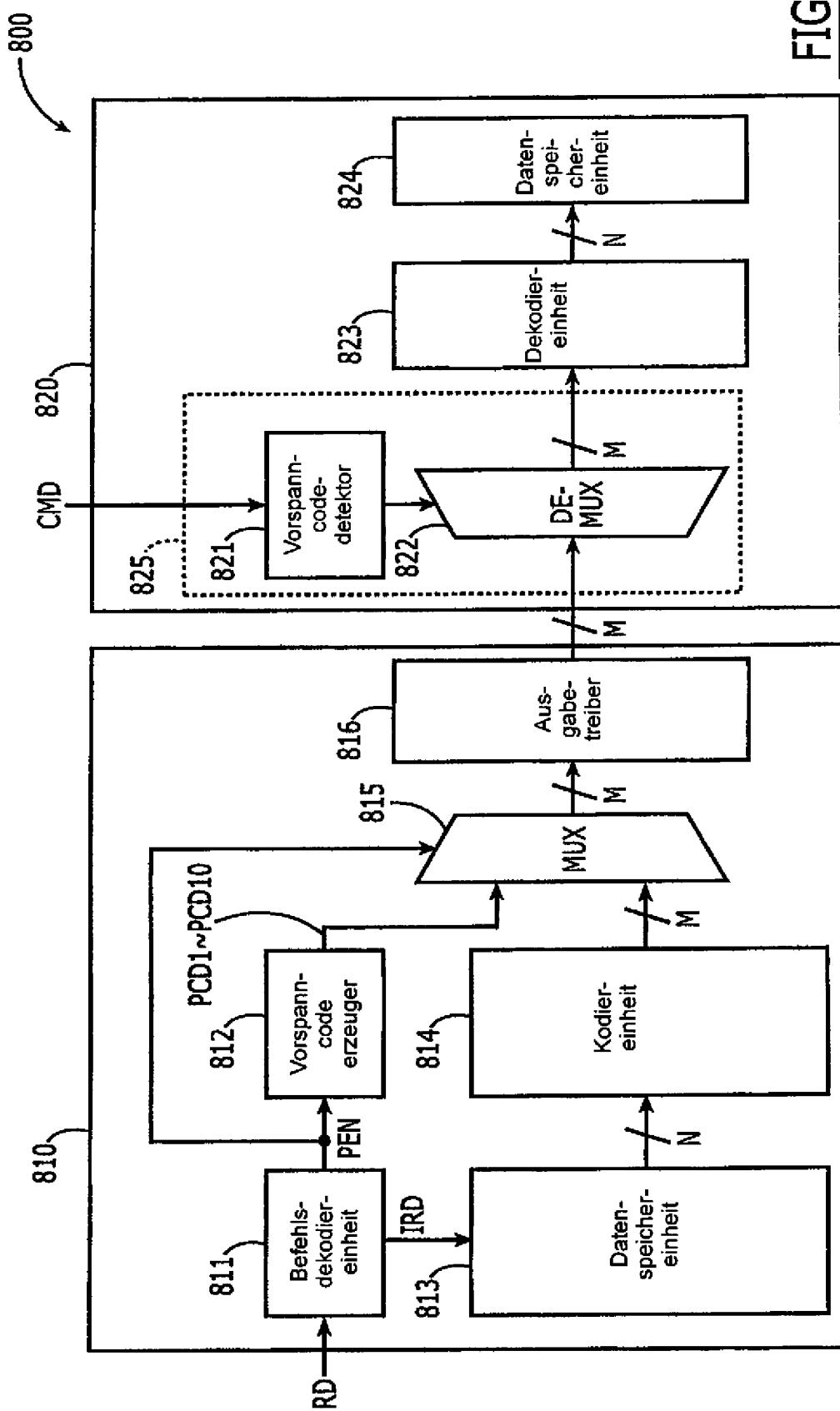

**[0061]** [Fig. 9](#) ist ein Blockschaltbild eines Vorspanncodeerzeugers, der dem Vorspanncodeerzeuger **812** in [Fig. 8](#) entsprechen kann. Bezugnehmend auf [Fig. 9](#) können bei einigen Ausgestaltungen der vorliegenden Erfindung zwei Vorspannwörter erzeugt werden, so dass Ausgestaltungen gemäß [Fig. 9](#) zwei Vorspannmustererzeugungseinheiten **910**, **920** beinhalten. Bei anderen Ausgestaltungen, bei denen immer ein einzelnes Vorspannwort erzeugt wird, kann nur eine einzelne Vorspannmustererzeugungseinheit bereitgestellt sein. Jede Vorspannmustererzeugungseinheit **910**, **920** umfasst eine Vorspannmusterauswahleinheit **932** und eine Mehrzahl von Auswählern **934–940**, die ein Vorspanncodewort-Bit PCD1\_1–PCD10\_1 oder PCD1\_2 PCD10\_2 auswählen, dass ein ONE (VDD) oder ein ZERO (VSS) ist. Ein Vorspannwortauswähler **950** erzeugt dann das geeignete Vorspannwort oder die geeigneten Vorspannwörter in Abhängigkeit von einem Befehl PEN, der an eine Vorspannreihenfolgesteuereinheit **960** angelegt wird und der durch eine Mehrzahl von Auswählern **970–980** ausgewählt wird, deren Ausgaben an den Multiplexer **815** geliefert werden. Wie der Fachmann erkennt, können viele andere Ausgestaltungen von Vorspanncodererzeugern gemäß unterschiedlichen weiteren Ausgestaltungen der vorliegenden Erfindung bereitgestellt werden.

**[0062]** [Fig. 10](#) ist ein Blockschaltbild eines Vorspanncodedetektors, der dem Vorspanncodedetektor **821** in [Fig. 8](#) entsprechen kann, gemäß einigen Ausgestaltungen der vorliegenden Erfindung. Wie in [Fig. 10](#) gezeigt, arbeitet eine Vorspannbefehlserkennungseinheit **1010** abhängig von einem Befehl CMD, der anzeigen, ob ein Vorspann vorhanden ist. Die Vorspannbefehlserkennungseinheit **1010** steuert einen Auswähler **1020**, der den Befehl T für den Demultiplexer **822** in [Fig. 8](#) bereitstellt. Insbesondere kann der Demultiplexer **822** den Vorspann verwerfen oder die empfangenen Daten an die Dekodiereinheit **823** senden. Es sei darauf hingewiesen, dass viele andere Ausgestaltungen von Vorspanncodedetekto-

ren gemäß unterschiedlichen anderen Ausgestaltungen der vorliegenden Erfindung bereitgestellt werden können.

[0063] [Fig. 11](#) ist ein Zeitablaufdiagramm von Systemen und Verfahren zum Übertragen DC-balance-kodierter Daten gemäß einigen Ausgestaltungen der vorliegenden Erfindung. Wie in [Fig. 11](#) gezeigt, wird ein Vorspanncodewort aus Dummy-Daten (auch als DUMMY DQ bezeichnet) vor dem Übertragen der DC-balance-kodierten Datenworte D1–D3 übertragen. Der Vorspann aus Dummy-Daten ist dazu ausgebildet, eine Zwischenanzahl von Bits eines gegebenen Logikwerts (vorliegend ZERO) bereitzustellen und enthält wenigstens ein oder eine ZERO, jedoch weniger als die maximale Anzahl von ZEROS in den DC-balance-kodierten Daten. Für 8B/10B-DC-balance-kodierte Daten, bei denen die maximale Anzahl von ZEROS sechs beträgt, können einige Ausgestaltungen der vorliegenden Erfindung einen Vorspann bereitstellen, der aus 2–5 ZEROS besteht. Bei einigen Ausgestaltungen sind die halbe maximale Anzahl von ZEROS oder drei ZEROS in dem Vorspanncode enthalten. Wie weiter unten detaillierter beschrieben ist, kann der Vorspanncode fest, das heißt unabhängig von der Anzahl von ZEROS in dem ersten Datenwort D1 sein, so dass er beispielsweise immer drei ZEROS enthält. In anderen Ausgestaltungen kann der Vorspann ein veränderbarer Vorspann sein, der von der Anzahl von ZEROS in dem ersten Wort D1 der DC-balance-kodierten Daten abhängt. Wenn somit beispielsweise das erste Wort D1 aus nur vier ZEROS besteht, kann der Vorspann zwischen einem/einer ZERO und drei ZEROS bestehen, und in einigen Ausgestaltungen kann der Vorspann die halbe Anzahl von ZEROS in dem ersten Wort oder zwei ZEROS enthalten.

[0064] [Fig. 12](#) ist ein Flussdiagramm von Operationen, die durchgeführt werden können, um DC-balance-kodierte Daten gemäß einigen Ausgestaltungen der vorliegenden Erfindung zu übertragen, und zeigt detailliertere Operationen als die Flussdiagramme der [Fig. 5](#) und [Fig. 6](#). Unter besonderer Bezugnahme auf [Fig. 12](#) beginnen die Operationen mit einem Sendebefehl, wie einem Lese- oder Schreibbefehl, der in Block **1210** empfangen wird. Nach dem Empfangen eines Sendebefehls in Block **1210** wird ein Vorspanncode mit der Zwischenanzahl von Bits des gegebenen Logikpegels erzeugt. Des Weiteren werden die DC-balance-kodierten Daten in Block **1220** kodiert. Die Operationen der Blöcke **1220** und **1230** können – wie gezeigt – zeitgleich oder in einer beliebigen Reihenfolge einschließlich einer teilweise überlappenden Reihenfolge erfolgen. Der Vorspanncode wird in Block **1240** ausgegeben, gefolgt von den DC-balance-kodierten Daten in Block **1250**.

[0065] [Fig. 13](#) ist ein Zeitablaufdiagramm zur Darstellung eines speziellen Beispiels gemäß [Fig. 11](#).

Wie in [Fig. 13](#) gezeigt, wird ein fester Einwortvorspann(Pre)-Code, der drei ZEROS enthält, vor dem Übertragen des ersten Datenworts D1 erzeugt und übertragen. Ein Worst-Case-Zustand ist in [Fig. 13](#) gezeigt, bei dem das erste Datenwort D1 sechs ZEROS (die maximale Anzahl bei 8B/10B-Kodierung) enthält. Wie in [Fig. 4](#) gezeigt wurde, wäre die Stromänderung beim Übertragen des ersten Wortes D1 ohne den Vorspann 6IDQ. Wie in [Fig. 13](#) gezeigt, ergibt sich jedoch mit dem Vorspann eine Stromänderung von 3IDQ beim Senden des Vorspanns und eine Stromänderung von 3IDQ wird zwischen dem Vorspann und dem ersten Wort D1 erzeugt. Dementsprechend kann das SSN um die Hälfte reduziert werden, indem eine maximale Stromänderung von 3IDQ anstelle von 6IDQ erzeugt wird.

[0066] [Fig. 14](#) zeigt zwei feste Vorspannwörter Pre1 und Pre2, wobei das erste feste Vorspannwort Pre1 zwei ZEROS und das zweite Vorspannwort Pre2 vier ZEROS aufweist. Wie gezeigt, wurde in diesem Worst-Case-Szenario die Stromänderung auf ein Maximum von 2IDQ reduziert, verglichen mit einem Maximum von 3IDQ in [Fig. 13](#) und einem Maximum von 6IDQ in [Fig. 4](#).

[0067] [Fig. 13](#) und [Fig. 14](#) können auch dazu verwendet werden, Ausgestaltungen der vorliegenden Erfindung zu illustrieren, bei denen veränderbare Vorspäne basierend auf der Anzahl von ZEROS in dem ersten Wort D1 verwendet werden. Insbesondere für einen einzelnen Vorspanncode ([Fig. 13](#)) kann der einzelne Vorspanncode die halbe Anzahl von ZEROS in dem ersten Wort enthalten. Wenn beispielsweise das erste Wort D1 sechs ZEROS enthält, kann der veränderbare Vorspann drei ZEROS enthalten, wie in [Fig. 13](#) gezeigt. Wenn jedoch das erste Wort nur vier ZEROS enthält, kann das veränderbare Vorspannwort lediglich zwei ZEROS enthalten. Wenn bei einigen Ausgestaltungen das erste Wort fünf ZEROS enthält, kann der variable Vorspann zwei oder drei ZEROS enthalten.

[0068] In gleicher Weise kann [Fig. 14](#) auch dazu verwendet werden, veränderbare Mehrfachvorspannwörter gemäß einigen Ausgestaltung der vorliegenden Erfindung zu illustrieren. Bei einigen Ausgestaltungen, wenn das erste Wort D1 sechs ZEROS enthält, können die Vorspäne zwei und vier ZEROS enthalten, wie in [Fig. 14](#) gezeigt. Wenn das erste Wort nur vier ZEROS enthält, können die ersten und zweiten Vorspannwörter nur eine bzw. zwei ZEROS enthalten. Wenn das erste Datenwort fünf ZEROS enthält, kann der Vorspann den Vorspänen für sechs ZEROS oder für vier ZEROS entsprechen, oder er kann ein anderer Vorspann sein. Dementsprechend können gemäß unterschiedlichen Ausgestaltungen der vorliegenden Erfindung feste oder veränderbare Einzelwort- und/oder Mehrfachwortvorspäne bereitgestellt werden.

**[0069]** Weiterhin können bei noch weiteren Ausgestaltungen der Erfindung ein oder zwei Vorspannwörter selektiv basierend auf der Anzahl von ZEROs in dem ersten Datenwort verwendet werden. Wenn beispielsweise das erste Datenwort sechs ZEROs enthält, können zwei Vorspannwörter verwendet werden, wohingegen dann, wenn das erste Datenwort nur vier ZEROs enthält, lediglich ein einzelnes Vorspannwort verwendet werden kann. Bei weiteren Ausgestaltungen, wenn die Anzahl von ZEROs in dem ersten Datenwort vier beträgt, kann ganz ohne Vorspann gearbeitet werden.

**[0070]** [Fig. 15](#) ist ein Flussdiagramm von Operationen zum Übertragen von Daten gemäß unterschiedlicher Ausgestaltungen der vorliegenden Erfindung, wobei die Anzahl von Vorspannwörtern in Abhängigkeit von dem Inhalt des ersten Datenworts variieren kann. Wie beispielsweise in [Fig. 15](#) gezeigt, beginnen die Operationen, wenn ein Sendebefehl, wie ein Lese- oder Schreibbefehl, in Block **1510** empfangen wird, und die DC-balance-Kodierung wird in Block **1520** durchgeführt. Dann wird in Block **1530** ein Test durchgeführt, um zu bestimmen, ob die Anzahl (P) kodierter Daten-ZEROs in dem ersten Datenwort D1 größer oder gleich einer Zahl M ist. Bei einigen Ausgestaltungen ist M = 5. Wenn die Anzahl nicht gleich oder größer als M ist, wird kein Vorspann benötigt und die DC-balance-kodierten Daten werden in Block **1570** ausgegeben. Wenn andererseits die Anzahl in Block **1530** größer oder gleich M ist, wird in Block **1540** die Anzahl (Z) von Vorspannwörtern basierend auf dem Wert von P bestimmt. Wenn dementsprechend die Differenz klein ist, kann ein einzelnes Vorspannwort verwendet werden, wohingegen bei einer großen Differenz mehrere Vorspannwörter verwendet werden. In Block **1550** wird ein Vorspanncode basierend auf dem Wert von Z erzeugt. Der Vorspanncode wird in Block **1570** ausgegeben.

**[0071]** [Fig. 16](#) ist ein Flussdiagramm detaillierter Operationen, die gemäß einigen Ausgestaltungen der vorliegenden Erfindung durchgeführt werden können, um die Anzahl (Z) von Vorspanncodewörtern basierend auf dem Wert von P (der Anzahl von ZEROs in dem ersten Datenwort D1) zu bestimmen, was Block **1540** in [Fig. 15](#) entsprechen kann. Wie insbesondere in Block **1610** gezeigt, wird ein Test durchgeführt, um zu bestimmen, ob die durch zwei geteilte Zahl P in den kodierten Daten größer als eine Konstante K ist. Beispielsweise sei angenommen, dass K = 2 beträgt. Falls ja, dann ist in Block **1620** die Anzahl (Z) von Vorspanncodewörtern größer als 1. Beispielsweise ist die Anzahl von Vorspanncodewörtern gleich 2. Wenn der Test in Block **1610** ein negatives Ergebnis liefert, dann ist in Block **1630** die Anzahl von Vorspanncodewörtern gleich 1. In einem speziellen Beispiel kann die Anzahl von ZEROs in dem ersten Datenwort vier, fünf oder sechs betragen. Es sei angenommen, dass K = 2 ist, woraufhin für

fünf oder sechs ZEROs zwei Vorspanncodewörter in Block **1620** zugewiesen werden, wohingegen für vier ZEROs nur ein Vorspanncodewort in Block **1630** zugewiesen wird.

**[0072]** Schließlich ist [Fig. 17](#) ein Flussdiagramm von Operationen, die durchgeführt werden können, um Daten gemäß verschiedener Ausgestaltungen der vorliegenden Erfindung zu empfangen, und zeigt detailliertere Operationen als das Flussdiagramm in [Fig. 7](#). Unter besonderer Bezugnahme auf [Fig. 17](#) werden in Block **1710** die Daten einschließlich des Vorspanns und der DC-balance-kodierten Daten empfangen. In Block **1720** wird ein Muster des Vorspanncodes detektiert. Wenn kein Vorspanncode vorhanden ist, fährt die Datenentschlüsselung mit Block **1740** fort. Alternativ wird ein gemäß Block **1720** vorhandener Vorspanncode in Block **1730** entfernt oder verworfen und anschließend wird die Datenentschlüsselung mit Block **1740** fortgesetzt.

**[0073]** Dementsprechend kann Simultaneous Switching Noise, das am Beginn der Übertragung DC-balance-kodierter Daten erzeugt wird, reduziert werden, indem ein Vorspann aus Dummy-Daten hinzugefügt wird, der einen Zwischenpegel von SSN erzeugt, der geringer ist als ein maximales SSN, das durch die DC-balance-kodierten Daten erzeugt wird. Der Vorspann kann selektiv in Abhängigkeit von dem Wert des ersten Datenworts verwendet werden. Des Weiteren kann der Vorspann ein festes Vorspannwort und/oder ein veränderbares Vorspannwort sein und/oder kann ein Wort oder mehrere Wörter aus festen und/oder veränderbaren Dummy-Daten enthalten.

## Patentansprüche

1. Verfahren zum Übertragen DC-balance-kodierter Daten (D1~D3), beinhaltend:

Übertragen eines Vorspanns (Pre) aus Dummy-Daten, der dazu ausgebildet ist, eine Zwischenanzahl von Bits eines gegebenen Logikwerts bereitzustellen, die wenigstens ein Bit des gegebenen Logikwerts beträgt, jedoch kleiner als eine Maximalanzahl von Bits des gegebenen Logikwerts in den DC-balance-kodierten Daten ist; und anschließend Übertragen der DC-balance-kodierten Daten (D1~D3), wobei das Übertragen des Vorspanns aus Dummy-Daten ein serielles Übertragen einer Mehrzahl von Vorspannwörtern aus Dummy-Daten beinhaltet, **dadurch gekennzeichnet**, dass die Mehrzahl von Vorspannwörtern aus Dummy-Daten ein erstes Vorspannwort aus Dummy-Daten und ein zweites Vorspannwort aus Dummy-Daten umfasst, wobei das zweite Vorspannwort mehr Bits des gegebenen Logikwerts als das erste Vorspannwort aufweist.

2. Verfahren nach Anspruch 1,

wobei dem Übertragen eines Vorspanns aus Dummy-Daten ein Erzeugen des Vorspanns aus Dummy-Daten vorhergeht, der dazu ausgebildet ist, die Zwischenanzahl von Bits des gegebenen Logikwerts bereitzustellen; und

wobei dem Übertragen der DC-balance-kodierten Daten das DC-balance-Kodieren der Daten vorhergeht.

3. Verfahren nach Anspruch 1 oder 2, dadurch gekennzeichnet, dass der Vorspann aus Dummy-Daten, der dazu ausgebildet ist, die Zwischenanzahl von Bits des gegebenen Logikwerts bereitzustellen, einen festen Vorspann aus Dummy-Daten umfasst, der dazu ausgebildet ist, eine feste Zwischenanzahl von Bits des gegebenen Logikwerts bereitzustellen, die unabhängig von einer Anzahl von Bits des gegebenen Logikwerts in einem ersten Wort der DC-balance-kodierten Daten ist.

4. Verfahren nach Anspruch 1 oder 2, dadurch gekennzeichnet, dass der Vorspann aus Dummy-Daten, der dazu ausgebildet ist, die Zwischenanzahl von Bits des gegebenen Logikwerts bereitzustellen, eine veränderbare Zwischenanzahl von Bits des gegebenen Logikwerts aufweist, die von einer Anzahl von Bits des gegebenen Logikwerts in einem ersten Wort der DC-balance-kodierten Daten abhängt.

5. Verfahren nach einem der Ansprüche 1 bis 4, dadurch gekennzeichnet, dass die Zwischenanzahl von Bits des gegebenen Logikwerts die Hälfte der maximalen Anzahl von Bits des gegebenen Logikwerts in den DC-balance-kodierten Daten ist.

6. Verfahren nach einem der Ansprüche 1 bis 5, dadurch gekennzeichnet, dass die DC-balance-kodierten Daten 8B/10B-DC-balance-kodierte Daten sind und dass die Zwischenanzahl von Bits des gegebenen Logikwerts wenigstens ein Bit aber weniger als sechs Bits des gegebenen Logikwerts beträgt.

7. Verfahren nach einem der Ansprüche 1 bis 6, dadurch gekennzeichnet, dass die DC-balance-kodierten Daten 8B/10B-DC-balance-kodierte Daten sind und dass die Zwischenanzahl von Bits des gegebenen Logikwerts drei Bits des gegebenen Logikwerts beträgt.

8. Verfahren nach einem der vorhergehenden Ansprüche, dadurch gekennzeichnet, dass das erste Vorspannwort aus Dummy-Daten ein festes erstes Vorspannwort aus Dummy-Daten aufweist, das dazu ausgebildet ist, eine feste Zwischenanzahl von Bits des gegebenen Logikwerts bereitzustellen, die unabhängig von einer Anzahl von Bits des gegebenen Logikwerts in einem ersten Wort der DC-balance-kodierten Daten ist, und dass das zweite Vorspannwort aus Dummy-Daten ein festes zweites Vorspannwort aus Dummy-Daten aufweist, das dazu ausgebil-

det ist, eine feste Zwischenanzahl von Bits des gegebenen Logikwerts bereitzustellen, die unabhängig von der Anzahl von Bits des gegebenen Logikwerts in dem ersten Wort der DC-balance-kodierten Daten ist.

9. Verfahren nach einem der Ansprüche 1 bis 7, dadurch gekennzeichnet, dass das erste Vorspannwort aus Dummy-Daten ein veränderbares erstes Vorspannwort aus Dummy-Daten aufweist, das dazu ausgebildet ist, eine veränderbare Zwischenanzahl von Bits des gegebenen Logikwerts bereitzustellen, die abhängig von einer Anzahl von Bits des gegebenen Logikwerts in einem ersten Wort der DC-balance-kodierten Daten ist, und dass das zweite Vorspannwort aus Dummy-Daten ein veränderbares zweites Vorspannwort aus Dummy-Daten aufweist, das dazu ausgebildet ist, eine veränderbare Zwischenanzahl von Bits des gegebenen Logikwerts bereitzustellen, die abhängig von der Anzahl von Bits des gegebenen Logikwerts in dem ersten Wort der DC-balance-kodierten Daten ist.

10. Verfahren nach einem der Ansprüche 1 bis 8, dadurch gekennzeichnet, dass die DC-balance-kodierten Daten 8B/10B-DC-balance-kodierte Daten sind, wobei das erste Vorspannwort aus zwei Bits des gegebenen Logikwerts besteht und wobei das zweite Vorspannwort aus vier Bits des gegebenen Logikwerts besteht.

11. Verfahren nach einem der Ansprüche 1 bis 10, gekennzeichnet durch:

Empfangen des Vorspanns aus Dummy-Daten und der DC-balance-kodierten Daten;

Verwerfen der Dummy-Daten; und

Dekodieren der DC-balance-kodierten Daten, die empfangen worden sind.

12. Verfahren zum Reduzieren von Simultaneous Switching Noise, das durch DC-balance-kodierte Daten (D3~D1) verursacht wird, beinhaltend:

Senden eines Vorspanns (Pre), der dazu ausgebildet ist, einen Zwischenpegel von Simultaneous Switching Noise zu erzeugen, der stärker als kein Simultaneous Switching Noise jedoch geringer als ein maximales Simultaneous Switching Noise ist, das durch die DC-balance-kodierten Daten (D1~D3) erzeugt wird, vor dem Senden der DC-balance-kodierten Daten (D1~D3),

dadurch gekennzeichnet, dass der Vorspann, der dazu ausgebildet ist, den Zwischenpegel des Simultaneous Switching Noise zu erzeugen, einen veränderbaren Vorspann aufweist, der dazu ausgebildet ist, einen veränderbaren Zwischenpegel von Simultaneous Switching Noise zu erzeugen, der von einem Inhalt eines ersten Worts der DC-balance-kodierten Daten abhängt.

13. Verfahren nach Anspruch 12, dadurch gekennzeichnet, dass das Übertragen eines Vorspanns ein

Übertragen eines einzelnen Vorspannworts beinhaltet.

14. Verfahren nach Anspruch 12, dadurch gekennzeichnet, dass das Übertragen eines Vorspanns ein serielles Übertragen einer Mehrzahl von Vorspannwörtern beinhaltet.

15. Verfahren nach Anspruch 14, dadurch gekennzeichnet, dass die Mehrzahl von Vorspannwörtern ein erstes Vorspannwort und ein zweites Vorspannwort aus Dummy-Daten beinhaltet.

16. Verfahren nach Anspruch 15, dadurch gekennzeichnet, dass das erste Vorspannwort ein festes erstes Vorspannwort aufweist, das dazu ausgebildet ist, einen festen Zwischenpegel von Simultaneous Switching Noise zu erzeugen, der unabhängig von einem Inhalt eines ersten Worts der DC-balance-kodierten Daten ist, und dass das zweite Vorspannwort ein festes zweites Vorspannwort aufweist, das dazu ausgebildet ist, einen festen Zwischenpegel von Simultaneous Switching Noise zu erzeugen, der unabhängig von dem Inhalt des ersten Worts der DC-balance-kodierten Daten ist.

17. Verfahren nach Anspruch 15, dadurch gekennzeichnet, dass das erste Vorspannwort ein erstes veränderbares Vorspannwort aufweist, dass dazu ausgebildet ist, einen veränderbaren Zwischenpegel von Simultaneous Switching Noise zu erzeugen, der abhängig von einem Inhalt eines ersten Worts der DC-balance-kodierten Daten ist, und dass das zweite Vorspannwort ein zweites veränderbares Vorspannwort aufweist, das dazu ausgebildet ist, einen veränderbaren Zwischenpegel von Simultaneous Switching Noise zu erzeugen, der abhängig von dem Inhalt des ersten Worts der DC-balance-kodierten Daten ist.

18. Verfahren nach einem der Ansprüche 12 bis 17, gekennzeichnet durch:

Empfangen des Vorspanns und der DC-balance-kodierten Daten; Verwerfen des Vorspanns; und Dekodieren der DC-balance-kodierten Daten, die empfangen worden sind.

19. Datensender, aufweisend:

eine Datenkodiereinheit (814), die dazu ausgebildet ist, Daten in DC-balance-kodierte Daten zu kodieren; einen Vorspanncodererzeuger (812), der dazu ausgebildet ist, einen Vorspann aus Dummy-Daten (PCD1~PCD10) zu erzeugen, der dazu ausgebildet ist, eine Zwischenanzahl von Bits eines gegebenen Logikwerts bereitzustellen, die wenigstens ein Bit des gegebenen Logikwerts, jedoch weniger als eine maximale Anzahl von Bits des gegebenen Logikwerts in den DC-balance-kodierten Daten beträgt; einen Multiplexer (815), der von der Datenkodiereinheit (814) und von dem Vorspanncodeerzeuger (812)

gesteuert ist und der dazu ausgebildet ist, den Vorspann aus Dummy-Daten (PCD1~PCD10) gefolgt von den DC-balance-kodierten Daten bereitzustellen; und einen Ausgabetreiber (816), der von dem Multiplexer (815) gesteuert und der dazu ausgebildet ist, den Vorspann aus Dummy-Daten (PCD1~PCD10) gefolgt von den DC-balance-kodierten Daten zu senden, dadurch gekennzeichnet, dass der Vorspann aus Dummy-Daten, der dazu ausgebildet ist, die Zwischenanzahl von Bits des gegebenen Logikwerts bereitzustellen, einen veränderbaren Vorspann aus Dummy-Daten aufweist, der dazu ausgebildet ist, eine veränderbare Zwischenanzahl von Bits des gegebenen Logikwerts bereitzustellen, die abhängig von einer Anzahl von Bits des gegebenen Logikwerts in einem ersten Wort der DC-balance-kodierten Daten ist.

20. Datensender nach Anspruch 19, dadurch gekennzeichnet, dass die Zwischenanzahl von Bits des gegebenen Logikwerts halb so groß wie die maximale Anzahl von Bits des gegebenen Logikwerts in den DC-balance-kodierten Daten ist.

21. Datensender nach Anspruch 19 oder 20, dadurch gekennzeichnet, dass die DC-balance-kodierten Daten 8B/10B-DC-balance-kodierte Daten sind und dass die Zwischenanzahl von Bits des gegebenen Logikwerts wenigstens ein Bit, jedoch weniger als sechs Bits des gegebenen Logikwerts ist.

22. Datensender nach einem der Ansprüche 19 bis 21, dadurch gekennzeichnet, dass die DC-balance-kodierten Daten 8B/10B-DC-balance-kodierte Daten sind und dass die Zwischenanzahl von Bits des gegebenen Logikwerts drei Bits des gegebenen Logikwerts ist.

23. Datensender nach einem der Ansprüche 19 bis 22, dadurch gekennzeichnet, dass der Vorspanncodeerzeuger dazu ausgebildet ist, ein einzelnes Vorspannwort aus Dummy-Daten zu erzeugen.

24. Datensender nach einem der Ansprüche 19 bis 22, dadurch gekennzeichnet, dass der Vorspanncodeerzeuger dazu ausgebildet ist, eine Mehrzahl von Vorspannwörtern aus Dummy-Daten zu erzeugen.

25. Datensender nach Anspruch 24, dadurch gekennzeichnet, dass die Mehrzahl von Vorspannwörtern aus Dummy-Daten ein erstes Vorspannwort aus Dummy-Daten und ein zweites Vorspannwort aus Dummy-Daten aufweist, wobei das zweite Vorspannwort mehr Bits des gegebenen Logikwerts als das erste Vorspannwort aufweist.

26. Datensender nach Anspruch 25, dadurch gekennzeichnet, dass das erste Vorspannwort aus Dummy-Daten ein festes erstes Vorspannwort aus Dummy-Daten aufweist, das dazu ausgebildet ist, eine feste Zwischenanzahl von Bits des gegebenen Logikwerts bereitzustellen, die unabhängig von einer Anzahl von Bits des gegebenen Logikwerts in einem ersten Wort der DC-balance-kodierten Daten ist, und dass das zweite Vorspannwort aus Dummy-Daten ein festes zweites Vorspannwort aus Dummy-Daten aufweist, das dazu ausgebildet ist, eine feste Zwischenanzahl aus Bits des gegebenen Logikwerts bereitzustellen, die unabhängig von der Anzahl von Bits des gegebenen Logikwerts in dem ersten Wort der DC-balance-kodierten Daten ist.

27. Datensender von Anspruch 25, dadurch gekennzeichnet, dass das erste Vorspannwort aus Dummy-Daten ein veränderbares erstes Vorspannwort aus Dummy-Daten aufweist, das dazu ausgebildet ist, eine veränderbare Zwischenanzahl von Bits des gegebenen Logikwerts bereitzustellen, die abhängig von einer Anzahl von Bits des gegebenen Logikwerts in einem ersten Wort der DC-balance-kodierten Daten ist, und dass das zweite Vorspannwort aus Dummy-Daten ein veränderbares zweites Vorspannwort aus Dummy-Daten aufweist, das dazu ausgebildet ist, eine Zwischenanzahl von Bits des gegebenen Logikwerts bereitzustellen, die abhängig von der Anzahl von Bits des gegebenen Logikwerts in dem ersten Wort der DC-balance-kodierten Daten ist.

28. Datensender nach Anspruch 27, dadurch gekennzeichnet, dass die DC-balance-kodierten Daten 8B/10B-DC-balance-kodierte Daten sind, wobei das erste Vorspannwort aus zwei Bits des gegebenen Logikwerts besteht und wobei das zweite Vorspannwort aus vier Bits des gegebenen Logikwerts besteht.

29. Datenempfänger, der dazu ausgebildet ist, Daten zu empfangen und zu dekodieren, die einen Vorspann aus Dummy-Daten gefolgt von DC-balance-kodierten Daten enthalten, dadurch gekennzeichnet, dass der Vorspann aus Dummy-Daten, der dazu ausgebildet ist, eine Zwischenanzahl von Bits eines gegebenen Logikwerts bereitzustellen, einen veränderbaren Vorspann aus Dummy-Daten aufweist, der dazu ausgebildet ist, eine veränderbare Zwischenanzahl von Bits des gegebenen Logikwerts bereitzustellen, die abhängig von einer Anzahl von Bits des gegebenen Logikwerts in einem ersten Wort der DC-balance-kodierten Daten ist.

30. Datenempfänger nach Anspruch 29, aufweisend:

einen Dateneingabepuffer, der dazu ausgebildet ist, Daten zu empfangen, die einen Vorspann aus Dummy-Daten gefolgt von DC-balance-kodierten Daten enthalten, und die Dummy-Daten zu erkennen und zu verwerfen; und

eine Dekodiereinheit, die dazu ausgebildet ist, die DC-balance-kodierten Daten zu dekodieren, die durch den Dateneingabepuffer empfangen wurden.

31. Datenempfänger nach Anspruch 30, dadurch gekennzeichnet,

dass der Dateneingabepuffer aufweist:

einen Vorspanncodedetektor, der dazu ausgebildet ist, die Dummy-Daten zu erkennen; und

einen Demultiplexer, der dazu ausgebildet ist, selektiv die Dummy-Daten zu verwerfen und selektiv die DC-balance-kodierten Daten an die Dekodiereinheit zu liefern.

32. Datenempfänger nach einem der Ansprüche 29 bis 31, dadurch gekennzeichnet, dass der Vorspann aus Dummy-Daten dazu ausgebildet ist, eine Zwischenanzahl von Bits des gegebenen Logikwerts bereitzustellen, die wenigstens ein Bit des gegebenen Logikwerts, jedoch weniger als eine maximale Anzahl von Bits des gegebenen Logikwerts in den DC-balance-kodierten Daten beträgt.

33. Datenempfänger nach einem der Ansprüche 29 bis 32, gekennzeichnet durch einen Abschlusswiderstand, der mit einer Versorgungsspannung verbunden ist, wobei die Bits des gegebenen Logikwerts Nullen sind.

34. Datenempfänger nach einem der Ansprüche 29 bis 32, gekennzeichnet durch einen Abschlusswiderstand, der mit einer Massespannung verbunden ist, wobei die Bits des gegebenen Logikwerts Einsen sind.

35. Bidirekionaler Sender/Empfänger für DC-balance-kodierte Daten, aufweisend:

einen Datensender nach einem der Ansprüche 19 bis 28 und

einen Datenempfänger nach einem der Ansprüche 29 bis 34.

Es folgen 13 Blatt Zeichnungen

## Anhängende Zeichnungen

**FIG. 1**

(Stand der Technik)

**FIG. 2A**

(Stand der Technik)

1's: 0's

= 4:6, 5:5, 6:4

Reduziere L(d/dt)-Rauschen

**FIG. 3B**

(Stand der Technik)

FIG. 4

FIG. 7

FIG. 8

FIG. 9

FIG. 10FIG. 11FIG. 12

FIG. 17