등록특허 10-2087337

(19) 대한민국특허청(KR)

(12) 등록특허공보(B1)

(45) 공고일자 2020년03월11일

(11) 등록번호 10-2087337

(24) 등록일자 2020년03월04일

(51) 국제특허분류(Int. Cl.)

*H01L 21/48* (2006.01) *H01L 21/18* (2006.01)

*H01L 21/768* (2006.01) *H01L 21/8258* (2006.01)

*H01L 23/498* (2006.01) *H01L 23/538* (2006.01)

*H01L 51/00* (2006.01)

(52) CPC특허분류

*H01L 21/4857* (2013.01)

*H01L 21/185* (2013.01)

(21) 출원번호 10-2017-7037238(분할)

(22) 출원일자(국제) 2007년09월06일

심사청구일자 2018년01월25일

(85) 번역문제출일자 2017년12월26일

(65) 공개번호 10-2018-0002083

(43) 공개일자 2018년01월05일

(62) 원출원 특허 10-2016-7032797

원출원일자(국제) 2007년09월06일

심사청구일자 2016년11월25일

(86) 국제출원번호 PCT/US2007/077759

(87) 국제공개번호 WO 2008/030960

국제공개일자 2008년03월13일

(30) 우선권주장

60/824,683 2006년09월06일 미국(US)

60/944,626 2007년06월18일 미국(US)

(56) 선행기술조사문현

US6743982 B2

(뒷면에 계속)

전체 청구항 수 : 총 28 항

심사관 : 정구원

(54) 발명의 명칭 인장 가능한 가요성 장치의 제조 방법

**(57) 요약**

일 측면에서, 본 발명은 인장되거나, 압축되거나, 휘어지거나 또는 달리 변형될 때에도 우수한 성능을 제공할 수 있는 반도체 또는 전자 회로들과 같은 인장 가능하고, 또한 선택적으로는 인쇄 가능한, 구성 부품들, 및 그러한 인장 가능한 구성 부품들을 제조하거나 조절할 수 있는 관련 방법들을 제공한다. 일부 응용들에 있어서 선호되는 (뒷면에 계속)

**대 표 도 - 도1**

는 인장 가능한 반도체들과 전자 회로들은 인장 가능할 뿐만 아니라, 가요성이고, 따라서 상당한 신장, 휩, 구부림, 또는 하나 또는 그 이상의 축을 따르는 다른 변형도 가능하다. 또한, 본 발명의 인장 가능한 반도체들 및 전자 회로들은 완전히 가요성인 전자 및 광학전자 장치들을 제공하기 위하여 광범위한 장치 구성에 적용된다.

## (52) CPC특허분류

*H01L 21/76832* (2013.01)*H01L 21/8258* (2013.01)*H01L 23/4985* (2013.01)*H01L 23/5387* (2013.01)*H01L 51/0097* (2013.01)

## (72) 발명자

## 션 위강

미국 일리노이 60565 네이퍼빌 밴더빌트 코트 2021

## 고 홍조

미국 일리노이 61801 어바나 사우쓰 굿원 애비뉴

300 #515

## 칼슨 앤드류

미국 일리노이 61801 어바나 노쓰 링컨 애비뉴

1901 #115

## 최 원목

미국 일리노이 61820 샘페인 히쓰로우 드라이브

2403 #8

## 스토이코비치 마크

미국 뉴햄프셔 03820-4321 도버 웨스트우드 서클

35

## 지양 한청

미국 일리노이 어바나 랜캐스터 드라이브 1306

## 후양 용강

미국 일리노이 60022 글렌코 스트로우베리 헬 드라이브 758

## 누조 랄프 쥐.

미국 일리노이 61821 샘페인 노팅엄 코트 노쓰 2413

## 이 건재

일본 도쿄 코토쿠 히가시스나 8-18-22-1017

## 강 성준

대전광역시 유성구 도룡동 1번지

## 쭈 쟁타오

미국 사우쓰다코타 57702 래피드 시티 씨머셋 드라이브 4924

## 메나르 에띠엔느

미국 노쓰캐롤라이나 27713 더럼 뉴홀 로드 5215

## 안 종현

경기도 수원시 장안구 장안로 232 110동 601호 (정자동, 동신아파트)

## 김 훈식

미국 일리노이 61822 샘페인 베이타운 드라이브 1125 아파트먼트 16

## 강 달영

서울특별시 동작구 노량진로32길 156 103동 702호 (본동, 경동원초리버아파트)

## (56) 선행기술조사문헌

US6317175 B1

US6989185 B2

KR1020060083916 A\*

US20020094701 A1\*

\*는 심사관에 의하여 인용된 문헌

## 명세서

### 청구범위

#### 청구항 1

인장 가능한 가요성 장치의 제조 방법으로서,

수용 표면을 갖는 가요성 기판을 제공하는 단계; 및

상기 수용 표면에 복수의 장치 구성 부품들을 결합하는 단계;

를 포함하고,

적어도 하나의 장치 구성 부품은 하나 이상의 상호 접속부에 의하여 다른 장치 구성 부품에 연결되고,

적어도 하나의 상호 접속부는 상기 가요성 기판으로부터 물리적으로 이격되고 굴곡진 영역을 갖고,

적어도 두 개의 상호 접속부들이 제 1 장치 구성 부품에 전기적으로 연결되고,

상기 결합하는 단계를 수행하는 동안 상기 적어도 두 개의 상호 접속부들이 상기 수용 표면의 평면에서 상기 제 1 장치 구성 부품으로부터 적어도 두 개의 상이한 방향들을 따라 연장되어 2차원 장치 어레이를 형성하고, 상기 적어도 두 개의 상호 접속부들의 각각은 골곡지고 상기 가요성 기판으로부터 물리적으로 이격된 영역을 갖는,

인장 가능한 가요성 장치의 제조 방법.

#### 청구항 2

제 1 항에 있어서,

상기 상호 접속부는 전기 상호 접속부이고,

상기 적어도 하나의 장치 구성 부품은 콘택 패드, 광 다이오드, 발광 다이오드, 전극, 트랜지스터, 집적 회로, 바이오 센서, 화학 센서, 가속계, 압력 센서, 또는 트랜스듀서 중의 하나 이상인 것을 특징으로 하는 인장 가능한 가요성 장치의 제조 방법.

#### 청구항 3

제 1 항에 있어서,

상기 굴곡진 영역은 상기 가요성 기판으로부터 100 nm 내지 1 mm의 이격 거리를 갖는 것을 특징으로 하는 인장 가능한 가요성 장치의 제조 방법.

#### 청구항 4

제 1 항에 있어서,

상기 가요성 기판 수용 표면에서 제 1 수준의 변형으로부터 제 2 수준의 변형까지 변형 수준에 있어서의 변화를 생성하는 단계;

를 더 포함하고,

상기 적어도 하나의 장치 구성 부품은 상기 제 1 수준의 변형으로 상기 가요성 기판에 결합되고, 상기 변형에서의 변화가 상기 적어도 하나의 장치 구성 부품의 일부의 구부림 및 상기 가요성 기판으로부터의 분리를 초래하는 것을 특징으로 하는 인장 가능한 가요성 장치의 제조 방법.

#### 청구항 5

삭제

#### 청구항 6

제 1 항에 있어서,

상기 가요성 기판 수용 표면에서 제 1 방향 및 제 2 방향으로 변형 수준에 있어서의 변화를 생성하는 단계;

를 더 포함하고,

상기 적어도 하나의 장치 구성 부품은 제 1 수준의 변형에서 상기 가요성 기판에 결합되고,

상기 변형 수준에 있어서의 변화는, 제1 상호 접속부의 일부가 구부러지고 상기 제 1 방향으로 상기 가요성 기판으로부터 이격되고 제2 상호 접속부의 일부가 구부러지고 상기 제 2 방향으로 상기 가요성 기판으로부터 이격되는 것을 초래하는 것을 특징으로 하는 인장 가능한 가요성 장치의 제조 방법.

### 청구항 7

제 6 항에 있어서,

상기 적어도 두 개의 상호 접속부들의 굴곡진 영역들 각각은 상기 가요성 기판으로부터 100 nm 내지 1 mm의 이격 거리를 갖는 것을 특징으로 하는 인장 가능한 가요성 장치의 제조 방법.

### 청구항 8

제 1 항에 있어서,

상기 적어도 두 개의 상호 접속부들의 각각은 제 1 단부 및 제 2 단부를 갖고, 상기 가요성 기판으로부터 물리적으로 이격되고 굴곡진 상기 영역은 상기 제 1 단부와 상기 제 2 단부 사이의 중앙 영역이고,

상기 적어도 두 개의 상호 접속부들 각각의 상기 제 1 단부는 상기 제 1 장치 구성 부품과 전기적으로 소통되고,

상기 적어도 두 개의 상호 접속부들 각각의 상기 중앙 영역은 적어도 두 개의 구부림(bent) 구성 영역들 및 상기 적어도 두 개의 구부림 구성 영역들 사이에 배치된 적어도 하나의 콘택 포인트를 포함하고,

상기 적어도 하나의 콘택 포인트의 각각은 상기 가요성 기판의 수용 표면과 물리적으로 소통하는 것을 특징으로 하는 인장 가능한 가요성 장치의 제조 방법.

### 청구항 9

제 8 항에 있어서,

상기 적어도 하나의 콘택 포인트는 상기 가요성 기판의 수용 표면에 결합되는 것을 특징으로 하는 인장 가능한 가요성 장치의 제조 방법.

### 청구항 10

제 1 항에 있어서,

상기 제 1 장치 구성 부품은 금속, 반도체, 절연체, 압전(piezoelectric) 물질, 강유전체(ferroelectric) 물질, 자기변형성(magnetostrictive) 물질, 전자변형성(electrostrictive) 물질, 초전도체, 강자성(ferromagnetic) 물질, 및 열전성(thermoelectric) 물질로 구성된 군으로부터 선택된 하나 이상의 물질을 포함하는 것을 특징으로 하는 인장 가능한 가요성 장치의 제조 방법.

### 청구항 11

제 1 항에 있어서,

상기 제 1 장치 구성 부품은 전자 장치, 광학 장치, 광-전자(opto-electronic) 장치, 기계적 장치, 미세전자기계 시스템들(microelectromechanical systems), 나노전자기계 시스템들(nanoelectromechanical systems), 미세 유동(microfluidic) 장치들, 또는 열적 장치인 것을 특징으로 하는 인장 가능한 가요성 장치의 제조 방법.

### 청구항 12

제 11 항에 있어서,

상기 적어도 두 개의 상호 접속부들은 조정 가능한 장치 구성 부품이며, 상기 조정 가능한 장치 구성 부품의 각각은 상기 굴곡진 영역의 변형의 수준에 따라 선택적으로 변화하는 전기적 성질, 광학적 성질, 또는 기계적 성

질 중 적어도 하나를 갖는 것을 특징으로 하는 인장 가능한 가요성 장치의 제조 방법.

### 청구항 13

제 1 항에 있어서,

상기 적어도 두 개의 상호 접속부들은 복수의 인장 가능한 상호 접속부들이고, 상기 복수의 인장 가능한 상호 접속부들 중 적어도 하나는 상기 가요성 기판 수용 표면과 물리적으로 소통하는 적어도 하나의 콘택 포인트 및 상기 적어도 하나의 콘택 포인트로부터 연장되는 셋 이상의 구부림 구성 영역들을 포함하는 것을 특징으로 하는 인장 가능한 가요성 장치의 제조 방법.

### 청구항 14

제 8 항에 있어서,

상기 적어도 두 개의 상호 접속부들의 각각은, 상기 제 1 단부, 상기 제 2 단부, 또는 상기 제 1 단부 및 상기 제 2 단부의 모두와 전기적으로 접촉하는 하나 이상의 콘택 패드들을 더 포함하는 것을 특징으로 하는 인장 가능한 가요성 장치의 제조 방법.

### 청구항 15

제 14 항에 있어서,

상기 제 1 장치 구성 부품은 상기 하나 이상의 콘택 패드들과 전기적으로 접촉하는 것을 특징으로 하는 인장 가능한 가요성 장치의 제조 방법.

### 청구항 16

제 1 항에 있어서,

상기 적어도 두 개의 상호 접속부들의 각각은

코일화된(coiled) 형태, 주름진 형태, 베클링된 형태 및 웨이브진 구성 중 적어도 하나를 갖는 것을 특징으로 하는 인장 가능한 가요성 장치의 제조 방법.

### 청구항 17

제 1 항에 있어서,

상기 적어도 두 개의 굴곡진 영역들의 각각은 접힘 영역(folded region), 볼록 영역, 오목 영역, 또는 이들의 임의의 조합을 포함하는 것을 특징으로 하는 인장 가능한 가요성 장치의 제조 방법.

### 청구항 18

제 1 항에 있어서,

상기 가요성 기판은 엘라스토머 물질을 포함하는 것을 특징으로 하는 인장 가능한 가요성 장치의 제조 방법.

### 청구항 19

제 1 항에 있어서,

상기 적어도 하나의 장치 구성 부품은 복수의 장치 구성 부품들이고, 상기 적어도 두 개의 상호 접속부들은 복수의 상호 접속부들인 것을 특징으로 하는 인장 가능한 가요성 장치의 제조 방법.

### 청구항 20

제 19 항에 있어서,

상기 2차원 장치 어레이가 그리드 구성, 꽃모양 구성, 브리지 구성 또는 이들의 임의의 조합을 갖는 것을 특징으로 하는 인장 가능한 가요성 장치의 제조 방법.

### 청구항 21

제 19 항에 있어서,

상기 복수의 장치 구성 부품들 중 하나 이상은 상기 복수의 상호 접속부들에 의하여 이웃하는 장치 구성 부품들에 연결되는 것을 특징으로 하는 인장 가능한 가요성 장치의 제조 방법.

### 청구항 22

제 21 항에 있어서,

상기 복수의 상호 접속부들 중 적어도 하나는 상기 복수의 상호 접속부들 중 다른 것과 상이한 방향으로 배향된 것을 특징으로 하는 인장 가능한 가요성 장치의 제조 방법.

### 청구항 23

제 19 항에 있어서,

상기 2차원 장치 어레이의 적어도 일부는 상기 복수의 상호 접속부들 중 서로 평행한 방향으로 배열된 둘 이상 또는 상기 복수의 상호 접속부들 중 둘 이상의 상이한 방향들로 배향된 둘 이상을 포함하는 것을 특징으로 하는 인장 가능한 가요성 장치의 제조 방법.

### 청구항 24

제 19 항에 있어서,

상기 2차원 장치 어레이는 둘 이상의 장치를 포함하고, 각 장치 층은 복수의 장치 구성 부품들 및 복수의 상호 접속부들을 포함하는 것을 특징으로 하는 인장 가능한 가요성 장치의 제조 방법.

### 청구항 25

제 19 항에 있어서,

상기 가요성 기판의 상기 수용 표면의 적어도 일부는 굴곡지거나, 불록하거나, 오목하거나, 또는 반구형인 것을 특징으로 하는 인장 가능한 가요성 장치의 제조 방법.

### 청구항 26

제 19 항에 있어서,

상기 2차원 장치 어레이는 광 감지기, 광 다이오드 어레이, 디스플레이, 발광 장치, 광전지 장치(photovoltaic device), 센서 어레이, 시트 스캐너, LED 디스플레이, 반도체 레이저 어레이, 광학 이미징 시스템, 대면적 전자 장치, 트랜지스터 어레이, 논리 게이트 어레이, 마이크로프로세서, 접적 회로, 또는 이들의 임의의 조합 중 하나 이상을 포함하는 것을 특징으로 하는 인장 가능한 가요성 장치의 제조 방법.

### 청구항 27

제 19 항에 있어서,

상기 2차원 장치 어레이는 꽃모양 구성을 갖고, 상기 적어도 두 개의 상호 접속부들은 복수의 상호 접속부들이고, 상기 복수의 상호 접속부들 중 적어도 하나는 상기 수용 표면과 물리적으로 소통하는 적어도 하나의 콘택 포인트 및 상기 적어도 하나의 콘택 포인트로부터 연장되는 셋 이상의 구부림 구조 영역들을 포함하는 것을 특징으로 하는 인장 가능한 가요성 장치의 제조 방법.

### 청구항 28

제 4 항에 있어서,

상기 제 1 수준의 변형은 상기 수용 표면을 신장시키고

상기 변형 수준에 있어서의 변화를 생성하는 단계는 신장된 상기 수용 표면을 적어도 부분적으로 릴랙스시키는 것을 특징으로 하는 인장 가능한 가요성 장치의 제조 방법.

### 청구항 29

제 6 항에 있어서,

상기 제 1 방향 및 상기 제 2 방향으로의 상기 변형 수준에 있어서의 상기 변화의 각각은 상기 제 1 방향 및 상기 제 2 방향에 있어서 상기 수용 표면을 신장시키고,

상기 변형 수준에 있어서의 변화를 생성하는 단계는 상기 제 1 방향 및 상기 제 2 방향으로 신장된 상기 수용 표면을 적어도 부분적으로 릴랙스시키는 것을 특징으로 하는 인장 가능한 가요성 장치의 제조 방법.

## 발명의 설명

### 기술 분야

[0001] 본 발명은 인장 가능한 구성 부품들과 그의 제조 방법에 관한 것이다.

[0002] 본 출원은 2007년 6월 18일 출원된 미합중국 가출원 제60/944,626호 및 2006년 9월 6일 제출된 미합중국 가출원 제60/824,683호의 이익을 주장한다.

### 배경 기술

[0003] 1994년, 전체가 폴리머인 인쇄된 트랜지스터가 처음 시연된 이후, 플라스틱 기판 상의 플렉서블(flexible)한 집적된 전자 소자들을 포함하는 유망한 새로운 종류의 전자 시스템이 많은 관심을 받아왔다. [Garnier, F., Hajlaoui, R., Yassar, A. and Srivastava P., Science, Vol. 265, pgs 1684-1686] 최근, 물질에 관한 연구는 플렉서블 플라스틱 전자 소자들을 위한 전도체, 유전체 및 반도체 요소들을 위한, 용액 가공이 가능한 새로운 물질들을 개발하는 쪽으로 방향지워져 왔다. 그러나, 플렉서블 전자공학 분야에서의 발전은 용액 공정이 가능한 새로운 물질의 개발에 의해서 뿐만 아니라 소자 부품의 신규한 기하구조, 효율적인 소자 및 소자 부품의 처리 방법들 및 플렉서블 전자공학 시스템에 적용할 수 있는 고해상도의 패터닝 기술들에 의해서도 구동된다. 그러한 물질들, 소자 구성들 및 제조 방법들은 급속하게 떠오르는 새로운 종류의 플렉서블 집적 전자 소자들, 시스템들 및 회로들에 있어서 핵심적인 역할을 담당할 것으로 기대된다.

[0004] 플렉서블 전자공학 기술에 의하여 제공되는 몇 가지 중요한 장점들이 플렉서블 전자공학 분야에 대한 관심을 자아낸다. 예를 들면, 이들 기판 물질들의 내재적인 플렉서블한 성질은 깨어지기 쉬운 종래의 실리콘계 전자 소자들에 있어서는 가능하지 않은 수많은 유용한 소자 구성을 제공하는 많은 형태들로 이들 기판 물질들이 집적되는 것을 가능하게 한다. 또한, 용액 공정이 가능한 부품 물질들과 플렉서블 기판들의 결합은 연속적이면서도 고속인, 대면적 기판 위에 저렴하게 전자 소자들을 생성할 수 있는 프린팅 기술에 의한 제조를 가능하게 한다.

[0005] 그러나, 우수한 전자적 성능을 보이는 플렉서블 전자 소자들의 설계와 제조는 많은 중요한 도전 과제들을 제공한다. 첫째, 종래의 실리콘계 전자 소자들을 제조하는 잘 발전된 방법들이 대부분의 플렉서블 물질들과는 양립하지 않는다. 예를 들면, 단결정 실리콘 또는 저매뉴 반도체들과 같은 전통적인 고순도 무기 반도체 구성요소들은 대부분의 플라스틱 물질들의 녹는점 또는 분해 온도를 현저히 초과하는 온도(> 1000°C)에서 박막 성장에 의하여 통상 처리된다. 또한, 대부분의 무기 반도체들은 용액 기반의 처리와 운반을 가능하게 하는 편리한 용매들에 본질적으로 용해되지 않는다. 둘째, 많은 비정질 실리콘, 유기 또는 하이브리드 유-무기 반도체들이 플렉서블 물질들 내부로 통합되어 양립할 수 있고, 비교적 저온들에서 처리될 수 있지만, 이들 물질들은 우수한 전자적 성능을 제공할 수 있는 집적 전자 소자들을 제공할 수 있는 전자적 성질들을 갖지 않는다. 예를 들면, 이들 물질로 만들어진 반도체 요소들을 갖는 박막 트랜지스터들은 상보적인 단결정 실리콘계 소자들보다 대략 세 개의 차수(order)의 크기만큼 더 작은 전계 효과 이동도를 보인다. 이러한 한계들의 결과, 플렉서블 전자 소자들은 현재 비방출성 화소들을 갖는 액티브 매트릭스 평판 디스플레이용 스위칭 요소들 및 발광 다이오드들에서의 사용과 같이 고성능을 요구하지 않는 특정 응용들에 한정된다.

[0006] 플렉서블 전자 회로는 플렉서블 디스플레이, 전자 센서 및 전자 피부와 같이 임의의 형태를 갖는 전자-활성(electro-active) 표면들을 포함하는 수많은 분야에서 활발하게 연구되고 있는 분야이다. 이들 회로들은 대개 전도성 부품들이 형태(conformation) 변화들에 대응하여 인장될 수 없기 때문에 주변 환경에 충분히 정합할 수 없다. 따라서, 그러한 플렉서블 회로들은 손상되기 쉽고, 전자적 열화가 일어나기 쉬우며 격렬한 및/또는 반복적인 형태 변화에 있어서 신뢰도가 저하될 수 있다. 플렉서블 회로들은 인장과 이완을 통한 사이클 동안 손상 없이 그대로 유지하는, 인장 가능하고 구부릴 수 있는 상호 접속부를 요구한다.

[0007] 구부림이 가능하면서 탄성을 구비하는 전도체들은 일반적으로 실리콘(silicone)과 같은 엘라스토머 내에 금속 입자들을 끼워 넣음으로써 제조된다. 그러한 전도성 고무들은 기계적으로 탄성을 구비하고 전기적 전도성을 갖는다. 전도성 고무의 단점들은 전기적 저항률이 높고, 인장되었을 때 저항 변화가 현저하며, 그에 의하여 전체적으로 열약한 상호 접속 성능 및 신뢰성을 초래하는 것을 포함한다.

[0008] Gray 등은 전도성을 유지하면서 54%까지 선형 인장이 가능한 실리콘(silicone) 엘라스토머 내에 싸여진 미세 가공된 구불구불한(tortuous) 와이어들을 이용하여 엘라스토머 전자 장치들을 제조하는 것을 논의한다. 그 연구에서, 와이어들은 나선형의 스프링 형태와 같이 형성된다. 낮은 변형에서 (예를 들면, 2.4%) 파괴되는 직선형 와이어에 대조적으로, 구불구불한 와이어들은 매우 높은 변형에서도 (예를 들면, 27.2%) 전도성을 유지하였다. 그러한 와이어 기하구조는 인장보다는 구부림에 의하여 신장되는 와이어의 능력에 의존한다. 상기 시스템은 추가적인 평판 내에 상이한 형태로 정확하게 그리고 제어 가능하게 패터닝하는 능력상의 한계로 곤란을 겪고 있으며, 그에 의하여 상이한 변형 및 구부림 영역에 시스템을 맞춤하는 능력상의 한계로 곤란을 겪는다.

[0009] 탄성적으로 인장 가능한 금속 상호 접속부들은 기계적 변형에 대하여 저항이 증가하는 것을 경험한다는 것이 연구들을 통해 암시되고 있다. (Mandlik 등, 2006) Mandlik 등은 피라미드 형태로 미세 패터닝된 표면 위에 금속 막을 증착함으로써 이러한 저항의 변화를 최소화하고자 시도하였다. 그러나, 그 연구는 가는 금속선에 인장 가능성을 부여하는 마이크로크랙(microcrack)들을 생성하기 위한 양각 구조물에 의존한다. 상기 마이크로크랙들은 평면을 벗어나는 트위스팅과 변형을 통해 금속이 탄성 변형되는 것을 용이하게 한다. 그러나, 그러한 금속 크랙들은 두꺼운 금속막과는 양립할 수 없고, 대신에 패터닝된 엘라스토머의 상부 위에 증착된 금속 박막의 좁은 범위(예를 들면, 30 nm 미만의 차수인)와 오히려 양립될 수 있다.

[0010] 금속 상호 접속부에 인장 가능성을 부여하는 한 가지 방법은 전도체(예를 들면, 금속)를 적용하는 동안 기판을 사전 변형시키고(예를 들면, 15% - 25%), 이어서 사전 변형의 자발적인 양각화를 가져오고, 그에 의하여 상기 금속 전도체 상호 접속부에 웨이브를 유발하는 것이다. (예를 들면, Lacour 등 (2003); (2005); (2004), Jones 등 (2004); Huck 등 (2000); Bowden 등 (1998) 참조) Lacour 등(2003)은 자발적으로 주름지는 골드 스트라이프들을 생성하기 위하여 골드 스트라이프들을 처음에 압축함으로써 (탄성 기판 상의 골드 막질의 파괴 변형이 수 퍼센트인 것과 비교하여) 22%까지의 변형 하에서도 전기적인 연속성이 유지됨을 보고하고 있다. 그러나, 그 연구에서는 비교적 얇은 층의 금속 막(예를 들면, 약 105 nm)을 사용하였고, 또한 상기 시스템이 약 10% 만큼 인장될 수 있는 전기 전도체를 잠재적으로 만들 수 있다는 점에서 상대적으로 제한된다.

[0011] 이상으로부터, 다양한 상이한 구성을 갖는 인장 가능한 상호 접속부들을 신속하고도 신뢰성 있게 제조하기 위해, 개선된 인장 가능성, 전기적 성질 및 관련 공정들을 갖는 소자 구성부품들 및 상호 접속부들에 대한 필요가 있음이 명백하다. 플렉서블 전자공학 분야에서의 발전은 수많은 중요한 신흥 기술 및 확립된 기술들에 있어서 결정적인 역할을 담당할 것으로 기대된다. 그러나, 플렉서블 전자공학 기술의 이러한 응용의 성공은 습곡되고(flexed), 변형되며 구부러진 형태에서 우수한 전자적, 기계적 및 광학적 성질을 보이는 소자들과 접적 전자 회로들을 제조하기 위한 신규한 물질들, 소자 구성들 및 상업적으로 실행 가능한 제조 경로의 계속적인 개발에 강하게 의존한다. 특히, 고성능의, 기계적으로 연장 가능한 물질들과 소자 구성들은 인장되거나 수축된 형태에서, 유용한 전자적 및 기계적 성질들을 보일 것이 요구된다.

## 발명의 내용

### 해결하려는 과제

[0012] 본 발명은 반도체들 및 인장 가능한 전자 소자들, 및 회로들과 같은 인장 가능한 장치들과 장치 부품들을 제공한다.

### 과제의 해결 수단

[0013] 인장 가능하고, 구부릴 수 있으며 정합될 수 있는(conformable) 전자 장치들과 장치 부품들은 전자 장치들을 다양한 곡면 상에 인쇄하기에 적합하게 만들 것이 요구된다. 형태 정합적인(shape-conforming) 장치들은 플렉서블 디스플레이 및 전자 섬유들로부터 정합될 수 있는 생물학적 및 물리적 센서들에 이르기까지 다양한 응용을 갖는다. 따라서, 본 발명의 구현에는 플렉서블하면서 구부릴 수 있는(bendable) 전자 장치들, 장치의 구성 부품들, 및 플렉서블하면서 구부릴 수 있는 장치들을 제조하기 위한 관련 방법들이다. 그러한 플렉서블함과 구부릴 수 있음은 웨이브가 지거나(wavy) 베클링된(buckled) 기하 구조를 갖는 상호 접속부 또는 반도체 막을 제공함으로써 이루어질 수 있다. 그러한 기하 구조는 격렬하고도 반복적인 인장 및/또는 구부림 사이클 하에서도

성능에 부정적인 영향을 미치지 않으면서도 시스템이 인장 가능하고 또한 구부릴 수 있도록 하는 것을 보장하는 수단을 제공한다. 또한, 상기 방법들은 장치 및/또는 장치의 구성 부품의 물리적 성질들(예를 들면, 인장성, 구부림성)이 상기 시스템의 작동 조건들에 맞춤화될 수 있도록, 정밀하고도 정확한 기하 구조의 구축 능력을 제공한다. 본 발명의 다른 측면은 구성 부품의 변형의 변화량의 적용에 의하여 파라미터가 조절될 수 있도록 변형과 적어도 부분적으로 결합된 물리적 성질을 갖는 인장 가능한 구성 부품들이다.

[0014] 장치 구성부품들의 배열은 장치 구성 부품들의 서로에 대한 상대적인 독립적 움직임을 용이하게 하기 위하여 베클링된 구성 부품들 또는 상호 접속부들에 의하여 서로 접속될 수 있다. 그러나, 상기 배열 내의 국부적 영역들은 다른 영역들에 비하여 상이한 구부림 또는 인장 요구 사항을 가질 수 있다. 예를 들어, 제공된 장치들과 방법들은 상호 접속부의 치수, 주기성, 진폭(amplitude), 배향 및 영역 내에서의 구성 부품 또는 상호 접속부의 총 수를 포함하는 베클링된 구성부품 또는 상호 접속부의 기하 구조에 있어서의 국부화된 편차를 가질 수 있는 플렉서블 시스템의 구축을 용이하게 한다. 제어된 배향을 갖는 다중의 구성 부품들 또는 상호 접속부들을 생성하는 것은 구성 부품들 또는 상호 접속부들을 상기 장치의 작동 조건에 맞춤화하는 것을 용이하게 한다.

[0015] 일 구현예에서, 본 발명은 장치의 인장 가능한 구성 부품으로서, 상기 구성 부품은 제 1 단부, 제 2 단부 및 상기 제 1 단부와 상기 제 2 단부 사이에 위치하는 중앙 영역을 포함한다. 상기 구성 부품은 기판에 의하여 지지되고, 상기 구성 부품의 제 1 단부 및 제 2 단부는 상기 기판에 결합되고, 상기 구성 부품의 중앙 영역의 적어도 일부분이 구부러진 구성(bent configuration)을 갖는다. 일 측면에 있어서, 상기 구성 부품의 중앙 영역은 상기 기판과 물리적으로 접촉되지 않는다. 다른 측면에 있어서, 상기 구성 부품의 중앙 영역은 변형되어 있다. 일 측면에 있어서, 상기 중앙 영역에 있어서의 상기 변형은 10% 미만이거나, 0.1% 내지 5% 사이이거나, 0.1% 내지 2% 사이이거나 또는 이들의 임의의 부범위(sub-range)이다.

[0016] 일 구현예에서, 상기 인장 가능한 구성 부품의 중앙 부분은 곡선을 이루거나 또는 원호(arc)-형태일 수 있다. 일 측면에 있어서, 상기 곡선은 약 100 nm 내지 1 mm 사이와 같은 진폭을 갖는다. 일 측면에 있어서, 구별되는 구성 부품 또는 상호 접속 결합 영역들의 수는, 예를 들면, 셋, 넷, 또는 다섯과 같이 둘보다 많을 수 있다. 이 측면에 있어서, 상기 제 1 구성 부품 단부와 상기 제 2 구성 부품 단부 사이에 있는 상기 중앙 부분은 상기 기판과 물리적으로 접촉하지 않는 구별되는 복수의 곡선 부분 영역들이 형성되도록 수많은 구부러진 구성의 영역들로 실제로 세분(subdivide)된다. 그러한 구성에 있어서, 상기 진폭 및/또는 주기성은 일정할 수도 있고, 또는 상기 구성 부품 또는 상호 접속부의 전체 길이 방향 길이에 걸쳐 변화할 수도 있다. 상기 구성 부품 그 자체는 막, 와이어, 또는 리본과 같이, 임의의 형태일 수 있다. 상기 구성 부품이 리본인 경우에 있어서는, 상기 리본은 약 300 nm 내지 1 mm 사이의 두께를 가질 수 있다.

[0017] 추가적인 소자 구성 부품을 용이하게 위치시키기 위하여, 상기 구성 부품의 단부가 전기적으로 연결되는 장치 구성 부품은 콘택 패드일 수 있다. 일 측면에 있어서, 추가적인 장치 구성 부품이 상기 콘택 패드와 전기적으로 접촉된다.

[0018] 인장 가능한 상기 구성 부품은 선택적으로, 금속, 반도체, 절연체, 압전체(piezoelectric), 강유전체(ferroelectric), 자기변형성(magnetostrictive) 물질, 전자변형성(electrostrictive) 물질, 초전도체, 강자성(ferromagnetic) 물질, 또는 열전성(thermoelectric) 물질인 물질을 하나 또는 그 이상 포함한다.

[0019] 또 다른 측면에 있어서, 상기 인장 가능한 구성 부품은 전자 장치, 광학 장치, 광-전자(opto-electronic) 장치, 기계적 장치 및 열적 장치로 구성되는 군으로부터 선택되는 장치의 구성 부품을 포함한다.

[0020] 언급한 바와 같이, 상기 구성 부품들을 지지하는 기판은 상기 구성 부품이 통합되는 장치에 따라 임의의 바람직한 물질로 될 수 있다. 일 구현예에서, 상기 기판은 PDMS와 같은 엘라스토머 물질을 포함한다. 상기 기판은 가역적으로 변형될 수 있는 것(예를 들면, PDMS)일 수도 있고, 또는 비가역적으로 변형될 수 있는 것(예를 들면, 플라스틱)일 수도 있다. 구현예에서, 상기 기판 그 자체는 층(layer)이거나 또는 코팅이다.

[0021] 구현예에서, 상기 장치들은 그들의 물리적인 특성들에 근거하여 더 설명될 수 있다. 예를 들면, 장치의 구성 부품과의 전기적인 접촉 및 전기 전도성을 유지하면서 25%까지의 변형을 견딜 수 있는 구성 부품들 및/또는 상호 접속부들이 여기에 제공된다. 이 경우에 있어서, "유지한다"는 의미는 변형을 수용하는 동안 전기 전도도가 20% 미만, 10% 미만, 또는 5% 미만으로 감소하는 것을 가리킨다.

[0022] 다른 구현예에서, 본 발명은 장치의 구성 부품들과 전기적 접촉을 형성하기 위한 인장 가능한 구성 부품 또는 상호 접속부를 제공한다. 상기 구성 부품 또는 상호 접속부는 제 1 단부, 제 2 단부 및 상기 제 1 단부와 상기

제 2 단부 사이에 위치하는 중앙 부분을 갖는다. 상기 단부들은 플렉서블(예를 들면, 인장 가능한) 기판, 엘라스토머 기판, 강체(rigid) 기판, 엘라스토머가 아닌 기판, 또는 전자 장치들, 장치 구성 부품들, 또는 이들의 어레이들을 인쇄하고자 하는 기판과 같은 기판에 결합된다. 상기 구성 부품 또는 상호 접속부의 각 단부는, 상기 기판에 의하여 그 자신이 지지되는 상이한 장치 구성 부품에 부착될 수 있다. 상기 구성 부품 또는 상호 접속부의 중앙 부분은 구부러진 구성을 갖고 상기 기판과 물리적으로 접촉하지 않는다(예를 들면, 결합되지 않는다). 일 측면에 있어서, 이 구부러진 구성을 중앙 부분이 변형 하에 있게 된 결과이다. 본 측면에 있어서, 상기 구부러진 구성을 하나 또는 그 이상의 장치 구성 부품들에 (또는 그 하부에 놓인 기판에) 상기 장치 구성 부품들을 분리하는 방식으로 힘이 가해지면, 상기 장치 구성 부품들 사이의 전기적 접촉은 유지하면서 상기 구성 부품 또는 상호 접속부의 곡선 부분이 적어도 부분적으로 직선화되면서 상기 장치 구성 부품들 사이의 상대적인 움직임을 수용할 수 있도록 전체적으로 만곡된다. 상기 구성 부품들 또는 상호 접속부들은 선택적으로 브리지, 꽂모양과 같은 수많은 기하구조 중의 임의의 하나에 의하여 및/또는 다중 구성 부품들 또는 상호 접속부들에 의하여 이웃하는 아일랜드(island)들 또는 콘택 패드들을 전기적으로 접속시킨다. 일 측면에 있어서, 장치 구성 부품은 콘택 패드와 전기적 접촉을 이룬다.

[0023] 여기에 개시된 인장 가능한 구성 부품들은 모두 전자 장치의 조정 가능한 장치 구성 부품을 선택적으로 더 포함한다. 상기 조정 가능한 구성 부품은 상기 구부러짐 구성을 위하여 제공되는 상기 중앙 영역의 변형에 따라 선택적으로 변화하는 적어도 하나의 전자적 성질을 갖는다. 예를 들면, 상기 전자적 성질은 선택적으로, 전자 이동도, 공진 주파수, 컨덕턴스(conductance), 및 저항 중의 하나 또는 그 이상이다. 일 측면에 있어서, 상기 조정 가능한 장치 구성 부품은 트랜지스터의 반도체 채널을 포함한다.

[0024] 일 구현예에서, 상기 조정 가능한 구성 부품이 상기 구부러짐 구성을 위하여 제공되는 상기 중앙 영역의 변형 수준에 따라 선택적으로 변화하는 적어도 하나의 광학적 성질을 갖는 경우에 상기 구성 부품은 변형 계수 광학 결합(strain coefficient optical coupling)을 갖는다. 변형 계수 광학 결합의 예는 상기 조정 가능한 장치 구성 부품의 굴절률 또는 상기 인장 가능한 구성 부품의 중앙 영역의 표면에 대하여 전자기 방사 입사빔의 입사각을 포함하지만 여기에 한정되는 것은 아니다. 다른 구현예에 있어서, 상기 조정 가능한 장치 구성 부품은 도파로(waveguide), 광학 변조기, 광학 스위치 또는 광학 필터를 포함한다.

[0025] 다른 구현예에서, 상기 인장 가능한 구성 부품은 상기 구부러짐 구성을 위하여 제공되는 상기 중앙 영역의 변형 수준에 따라 선택적으로 변화하는 열 전도도를 갖는 장치의 조정 가능한 장치 구성 부품이다.

[0026] 다른 구현예에서, 상기 인장 가능한 구성 부품은 장치의 열적 절연 구성 부품이고, 상기 중앙 영역이 상기 기판과 물리적인 접촉을 하지 않는다. 이 구현예의 일 측면에 있어서, 상기 중앙 영역은 상기 기판과 열적으로 접촉하지 않으며, 상기 중앙 영역은 하나 또는 그 이상의 장치 구성 부품들을 지지하고, 그에 의하여 상기 중앙 영역에 의하여 지지되는 하나 또는 그 이상의 장치 구성 부품들을 상기 기판으로부터의 열적 절연을 제공한다. 이러한 측면을 위한 유용한 응용은 장파장 이미징 시스템인 장치용이다.

[0027] 또 다른 구현예에서, 상기 인장 가능한 구성 부품은 기계적 장치의 액츄에이터로서, 상기 중앙 영역이 만곡되고 상기 인장 가능한 구성 부품을 압축하거나 신장시킴으로써 또는 상기 중앙 영역에 전기적 전위를 인가함으로써 변조될 수 있는 진폭을 갖는다. 본 구현예의 유용한 응용은 미세전자기계 장치, 나노전자기계 장치, 및 미세유동 장치로 구성되는 군으로부터 선택되는 기계 장치이다.

[0028] 일 구현예에서, 여기에 개시된 임의의 인장 가능한 구성 부품들을 복수의 구성 부품들과 셋 이상의 장치 구성 부품들을 갖는 장치 어레이에 통합함으로써 다중-축(multi-axial) 인장 및 구부림이 제공된다. 본 구현예에서, 각 구성 부품은 한 쌍의 장치 구성 부품들 사이에 전기적 접촉을 제공한다. 원하는 인장, 구부림 및/또는 압축 동작 조건들에 따라서, 상기 장치 어레이는 그리드, 꽂모양, 브리지 또는 이들의 임의의 조합(예를 들면, 한 영역에서는 그리드, 다른 영역에서는 브리지)을 갖는 기하학적 구성을 가질 수 있다. 또한, 이웃하는 장치 구성 부품들을 둘, 셋, 또는 네 개의 구성 부품들과 같이 하나보다 많은 구성 부품들(예를 들면, 다중 상호 접속부들)에 접속시키는 능력에 의하여 추가적인 인장 및 구부림성 제어가 제공된다. 예를 들면, 정사각형 또는 직사각형인 장치 구성 부품 하나가 네 개의 다른 장치 구성 부품들에 이웃할 수 있다. 만일 각 이웃하는 쌍이 두 개의 상호 접속부들로 접속되면, 상기 장치 구성 부품은 자신으로부터 연장되는 여덟 개의 상호 접속부들을 가질 것이다.

[0029] 일 구현예에서, 장치 어레이는 적어도 두 개의 상이한 방향으로 배향된 구성 부품들의 세트들을 갖는다. 예를 들면, 그리드 구성에서 구성 부품들은 두 방향으로의 인장될 수 있는 능력을 제공하기 위하여 서로 직교하거나 수직인 두 방향을 가질 수 있다. 다른 구현예에서, 장치 어레이는 서로에 대하여 모두 정렬된 구성 부품들을

포함할 수 있다. 이 구현에는 인장 또는 구부림이 단일한 방향으로 한정되는 (예를 들면, 전자 장치 조직(fabric)을 실린더 표면으로 구부리는) 경우에 유용할 수 있다. 구성 부품들을 셋 또는 그 이상의 방향들, 예를 들면, 세 방향들 또는 네 방향들로 배향시킴으로써 추가적인 구부림 및/또는 인장 능력이 제공된다. 일 구현예에서, 서로 이웃하는 두 층들과 같이, 임의의 수의 상이한 층들 내에 위치된 장치 어레이의 구성 부품들을 가짐으로써 추가적인 제어 및 안정성이 제공된다.

[0030] 일 구현예에서, 장치 어레이는 약 150%까지의 변형을 파괴됨이 없이 견딜 수 있다. 파괴되기 위한 변형은 상호 접속 기하 구조, 배향, 진폭, 주기성, 동작 조건에 관한 수(예를 들면, 단일축 대 다중축 인장 및/또는 구부림)를 맞춤화함으로써 최대화된다.

[0031] 상기 상호 접속부 또는 장치 어레이가 지지된 기판은 오목, 볼록, 반구형, 또는 이들의 조합과 같은 곡면인 부분을 적어도 가질 수 있다. 일 구현예에서, 상기 구성 부품들이 통합된 상기 장치는 하나 또는 그 이상의 인장 가능한: 광감지기, 디스플레이, 발광기, 광전지(photovoltaic), 시트 스캐너, LED 디스플레이, 반도체 레이저, 광학 시스템, 대면적 전자 장치, 트랜ジ스터, 또는 집적 회로이다.

[0032] 또 다른 구현예에서, 본 발명은 장치의 인장 가능한 구성 부품의 성질을 조정하기 위한 다양한 방법들에 관련된다. 예를 들면, 조정 방법은 여기에 개시된 바와 같은 인장 가능한 구성 부품을 갖는 장치를 제공하는 단계를 포함할 수 있다. 상기 인장 가능한 구성 부품은 제 1 단부; 제 2 단부; 및 상기 제 1 단부와 상기 제 2 단부 사이에 위치하고 기판에 의하여 지지되는 중앙 영역을 갖는 구성 부품과 같은은 것일 수 있다. 특히, 상기 구성 부품의 제 1 단부 및 제 2 단부는 상기 기판에 결합되고, 또한 상기 구성 부품의 중앙 영역의 적어도 일부는 구부러진 구성을 가지며 소정 수준의 변형 하에 있다. 상기 변형의 수준은 상기 인장 가능한 구성 부품을 압축, 신장 및/또는 구부림으로써 상기 인장 가능한 부품 내에서 변조되고, 그에 의하여 상기 장치의 인장 가능한 구성 부품의 성질을 조정한다.

[0033] 일 측면에 있어서, 상기 성질은 광학적, 기계적, 또는 전기적으로 결합된 변형 파라미터와 같이 광학적 성질, 전기적 성질, 및 기계적 성질 중의 하나 또는 그 이상이다. 여기서, 상기 각 성질의 크기는 적어도 부분적으로 변형에 의존한다. 다른 측면에 있어서, 상기 성질은 공진 주파수, 전자 이동도, 저항, 컨덕턴스, 굴절률, 열전도도, 및 상기 인장 가능한 구성 부품의 중앙 영역의 표면에 대한 전자기 방사 입사빔의 입사각으로 구성되는 군으로부터 선택된다.

[0034] 일 구현예에서, 장치의 인장 가능한 구성 부품의 제조 방법이 제공된다. 본 구현예에서, 제 1 수준의 변형을 갖는 수용 표면을 갖는 엘라스토머 기판이 제공되며, 상기 변형은 선택적으로 0이거나 압축 변형이거나 신장 변형이다. 하나 또는 그 이상의 장치 구성 부품들이 상기 제 1 수준의 변형을 갖는 수용 표면에 결합된다. 상기 제 1 수준의 변형으로부터 상이한 제 2 수준의 변형으로 변형의 수준 상의 변화를 생성하도록 상기 엘라스토머 기판에 힘이 가해진다. 제 1 수준으로부터 제 2 수준으로의 상기 기판 내의 상기 변형의 수준 상의 변화가 상기 구성 부품이 구부러지는 것을 유발하고, 그에 의하여 하나 또는 그 이상의 인장 가능한 구성 부품들을 생성하는 한, 이러한 변화의 크기, 또는 그러한 변화가 달성되는 방법은 특별히 중요하지 않다. 상기 인장 가능한 구성 부품들은 각각 상기 기판에 결합된 제 1 단부 및 제 2 단부와 구부러진 구성을으로 제공되는 중앙 영역을 갖는다.

[0035] 상기 기판에 상기 장치 구성 부품들을 결합하는 것은 임의의 적합한 수단들에 의할 수 있다. 일 구현예에서, 상기 결합하는 단계는 상기 인장 가능한 구성 부품의 결합되는 영역과 결합되지 않는 영역의 패턴을 생성하는 단계를 포함한다. 여기서, 상기 인장 가능한 구성 부품의 결합되는 영역은 엘라스토머 기판에 결합되고, 상기 인장 가능한 구성 부품의 결합되지 않는 영역은 엘라스토머 기판에 결합되지 않는다.

[0036] 다른 측면에서, 결합되지 않는 영역들은 상기 인장 가능한 구성 부품들의 중앙 영역들에 대응되고, 상기 엘라스토머 기판에 힘을 가하는 단계는 인장 가능한 구성 부품 각각의 중앙 영역의 적어도 일부분이 기판과 물리적으로 접촉하지 않도록 상기 중앙 영역이 구부러지게 한다. 일 측면에 있어서, 상기 엘라스토머 기판에 힘을 가하는 단계는, 인장 가능한 구성 부품 각각의 중앙 영역의 적어도 일부분이 기판과 물리적으로 접촉하지 않도록 중앙 영역들이 구부러지게 한다.

[0037] 일 구현예에서, 인장 가능한 구성 부품을 제조하기 위한 임의의 방법들은 상기 인장 가능한 부품 위에, 상기 엘라스토머 기판의 수용 표면 위에, 또는 상기 인장 가능한 구성 부품과 상기 엘라스토머 기판의 수용 표면 모두의 위에 결합 위치의 패턴을 형성하는 단계를 더 포함한다.

[0038] 또 다른 구현예에서, 임의의 방법들 또는 장치들은 복수의 연질(compliant) 영역들과 복수의 경질(rigid) 영역

들을 갖는 엘라스토머 기판을 갖는다. 그러한 기판은 상기 연질 영역에 굴곡에 있어서의 강성(rigidity)을 제공하는데 이는 상기 경질 영역들의 그것보다 낫다. 선택적으로 상기 기판은 상기 경질 영역들의 적어도 하나에 결합된 인장 가능한 구성 부품들 각각의 제 1 단부 및 제 2 단부와, 상기 연질 영역들의 적어도 하나에 결합된 인장 가능한 구성 부품들 각각의 중앙 영역을 갖는다. 이러한 유형의 기판의 사용은 하부에 놓인 기판의 연질 성의 패턴에 근거하여 상기 구성 부품의 베클링을 제어 가능하도록 하는 능력을 제공한다.

[0039] 일 구현예에서, 상기 엘라스토머 기판에 가해지는 힘은 기계적으로 달성된다. 본 구현예의 일 측면에 있어서, 제 1 수준의 변형, 제 2 수준의 변형 또는 이를 모두는 상기 엘라스토머 기판의 신장 또는 압축에 의하여, 상기 엘라스토머 기판의 경화에 의하여, 또는 상기 엘라스토머 기판의 온도를 승온 또는 하강시키는 것과 같은 열적 수단에 의하여, 또는 상기 엘라스토머 기판의 열팽창 또는 열적으로 유발된 수축에 의하여 생성된다.

[0040] 다른 구현예에서, 상기 엘라스토머 기판의 상기 수용 표면에 하나 또는 그 이상의 장치 구성 부품을 결합하는 단계는, 상기 제 1 수준의 변형으로부터 상기 제 1 수준과 상이한 제 2 수준의 변형으로 상기 기판의 변형의 수준의 변화를 생성하는 힘을 상기 엘라스토머 기판에 적용하는 단계 이전에 수행된다. 선택적으로, 결합하는 단계는 상기 제 1 수준의 변형으로부터 상기 제 1 수준과 상이한 제 2 수준의 변형으로 상기 기판의 변형의 수준의 변화를 생성하는 힘을 상기 엘라스토머 기판에 적용하는 단계 이후에 수행된다.

[0041] 일 구현예에서, 임의의 제 1 수준의 변형 및 제 2 수준의 변형은 0과 동일하다. 일 측면에 있어서, 임의의 장치 구성 부품들은 상호 접속부 또는 전극을 포함한다.

[0042] 다른 구현예에 있어서, 본 발명은 장치의 구성 부품들과 전기적 접촉을 형성할 수 있는 상호 접속부 또는 베클링된 구성 부품을 제조하기 위한 다양한 방법들에 관한 것이다. 일 측면에 있어서, 결합 위치들의 패턴은 엘라스토머 기판 표면, 구성 부품들 또는 상호 접속부들, 또는 이를 모두에 적용된다. 상기 기판 및 상기 기판과 접촉되는 상호 접속부들 또는 구성 부품들을 변형시키기 위해 힘이 작용된다. 결합 위치들의 패턴은 특정 구성 부품들 또는 상호 접속부 위치들과 기판 사이의 결합을 제공한다. (상기 힘을 제거함으로써) 상기 기판을 릴랙스하여, 베클링된 구성 부품들 또는 상호 접속부들이 생성된다. 사전 변형(prestain)의 크기, 결합 위치 패터닝, 기하 구조 및 간격 중의 하나 또는 그 이상의 변경은 상이한 베클링되거나 웨이브진 기하 구조를 갖는 구성 부품들 또는 상호 접속부들을 생성한다. 예를 들면, 이웃하는 구성 부품들 또는 상호 접속부들이 상이한 위치들에서 기판에 결합하도록 결합 위치들이 엇갈리게(staggering) 위치하면 "비동조적인(out-of-phase)" 상호 접속부 기하 구조가 제공된다. 결합 위치 패터닝은 상기 엘라스토머 기판 표면에 경화 가능한 광 중합체를 적용하는 것에 의하는 것과 같이 당 기술분야에 알려진 임의의 수단들에 의한다. 구성 부품들 또는 상호 접속부들은 상기 구성 부품들 또는 상호 접속부들의 적어도 일부분을 엘라스토머 물질과 같은 봉지(encapsulation) 물질 내에 봉지함으로써 선택적으로 보호된다. 상기 베클링된 구성 부품들 또는 상호 접속부들은 응용에 적합한 임의의 패턴을 가질 수 있다. 일 구현예에서, 상기 패턴은 그리드 구성, 꽂모양 구성, 브리지 구성, 또는 이들의 임의의 조합이다.

[0043] 방법들과 장치들은 수십 나노미터 내지 약 1 밀리미터의 범위의 두께 또는 약 300 nm보다 큰 두께와 같은 임의의 치수의 구성 부품들을 가질 수 있다. 일 측면에 있어서, 상기 베클링된 구성 부품은 상기 상호 접속부의 상기 기판으로부터의 최대 수직 범위에 대응하는 진폭을 가지며, 상기 진폭은 100 nm 내지 1 mm 사이의 범위로부터 선택된다. 길이와 폭을 갖는 구성 부품 리본에 있어서, 상기 폭, 진폭 또는 상기 폭 및 진폭은 상호 접속부의 길이를 따라 선택적으로 변화한다. 진폭에 영향을 미치는 인자의 하나는 구성 부품을 결합시키기 전에 또는 상기 구성 부품을 결합시킨 후에 상기 엘라스토머 기판에 적용되는 변형이다. 일반적으로, 변형이 더 클수록 진폭이 더 크다. 일 구현예에서, 힘이 가해져서 엘라스토머 기판에 변형이 생성되고, 상기 변형은 20% 내지 100% 사이의 범위로부터 선택된다.

[0044] 일 구현예에서, 상기 구성 부품은 장치 구성 부품에 전기적으로 접속된 상호 접속부이다. 여기에 제공된 임의의 시스템들 및 공정들은 구성 부품의 파괴(fracture) 없이 약 100%까지 인장이 가능하거나, 약 50%까지 압축이 가능하거나, 또는 곡률 반경이 겨우 5 mm가 되도록 구부리는 것이 가능한 기판을 선택적으로 제공한다. 상기 구성 부품은 금속, GaAs 또는 Si를 포함하는 반도체, 절연체, 압전체(piezoelectric), 강유전체(ferroelectric), 자기변형성(magnetostriuctive) 물질, 전자변형성(electrostrictive) 물질, 초전도체, 강자성(ferromagnetic) 물질, 또는 열전성(thermoelectric) 물질과 같은 임의의 적합한 물질로부터 제조된다. 일 구현예에 있어서, 상기 방법들은 베클링된 구성 부품들이 스템프와 같은 엘라스토머 기판으로부터, 예를 들면, 곡면의 장치 기판과 같은 장치 기판으로 인쇄되어 전사되는 것을 제공한다.

[0045] 엘라스토머 기판에 힘 또는 변형을 적용하는 것을 통해 팝-업(pop-up) 또는 베클링된 구성 부품들을 생성하는

대신에, 웨이브진 표면과 같은 양각 구조물을 갖는 수용 표면과 같은 수용 표면에 구성 부품 물질을 적용함으로써 인장 가능하고 구부릴 수 있는 상호 접속부가 제조될 수 있다.

[0046] 일 구현예에서, 인장 가능하고 구부릴 수 있는 구성 부품을 제조하기 위하여, 리세스 구조물을 부분적으로 매립하기 위하여 중합체를 스피-코팅하는 것과 같이 표면상에 웨이브 구조물을 갖는 기판을 매끈하게 한다 (smoothed). 상기 부분적인 매립은 매끈하게-웨이브진 기판을 생성한다. 그런 후 구성 부품들이 상기 매끈하게-웨이브진 기판 위에 증착되고, 원하는 바에 따라 패터닝된다. 상기 구성 부품들은 금속 구조물을 포함하지만 그에 한정되는 것은 아니다. 상기 수용 표면 기판 위의 구성 부품들은 상기 구성 부품으로 적어도 부분적으로 코팅된 기판에 대하여 중합체 스템프를 후속적으로 주조하기(casting) 위하여 동원 가능하다. 상기 구성 부품은 인장 가능하고 구부릴 수 있는 구성 부품을 제조하기 위하여 상기 기판으로부터 상기 중합체 스템프를 제거함으로써 상기 중합체 기판에 전사된다. 일 구현예에서, 상기 구성 부품과 기판 사이의 계면은 Au/Su-8에 폭시 포토레지스트이다. 상기 구성 부품은 충상의 금속, 예를 들면, Au/Al일 수 있다. 상기 기판은, 예를 들면, Su-8 충을 지지하는 유리층과 같이, Au/Su-8인 상기 기판과 상기 금속 사이에 실제 계면으로 적층될 수 있다.

[0047] 스템프 표면 위에 팝-업(pop-up) 상호 접속부와 같은 팝-업 구성 부품을 제조하기 위한 대안적인 방법은 굴곡진 기판 표면을 평탄화하는 단계, 상기 평탄화된 표면에 구성 부품들을 접촉시키는 단계, 및 상기 기판 표면이 릴랙스되어 자신의 굴곡진 기하 구조로 복원되도록 허용하는 단계에 따른다. 일 구현예에서, 상기 방법은 여기에 개시된 바와 같은 접촉 이전에 결합 위치들의 공간적 패터닝을 더 제공한다. 본 구현예에 있어서, 상기 방법은 상호 접속부들과 장치 구성 부품들을 대응하는 제 2 굴곡 기판 표면으로 전사하기 위하여 특히 적합하다. 일 측면에 있어서, 접착제 또는 접착 전구체와 같은 결합 수단들은 엘라스토머 스템프가 제거된 후에도 상기 제 2 굴곡 기판과 상기 제 1 굴곡 기판 위의 상호 접속 시스템 사이에 상호 접속부를 제 2 기판으로 전사하는 것을 허용하기에 충분한 결합을 생성한다.

[0048] 일 측면에 있어서, 본 발명에 따른 임의의 방법들 및 장치들은 약 40%까지의 변형에 대하여 선형의 탄성 응답을 갖는 PDMS인 스템프 또는 엘라스토머 기판을 갖는다. 선택적으로, 본 발명의 상호 접속부는 인장 가능한 전극, 인장 가능한 수동 매트릭스 LED 디스플레이, 또는 광감지 어레이의 일부이다. 일 구현예에 있어서, 본 발명은 본 발명의 방법들에 의하여 제조된 임의의 하나 또는 그 이상의 상호 접속부들을 갖는 인장 가능한 전자 장치에 관한 것이다. 이 때 상기 전자 장치는 인장 가능하거나 구부릴 수 있는: 전극, 수동 매트릭스 LED, 태양 전지, 광학 접속 어레이(optical collector arrays), 바이오 센서, 화학 센서, 광 다이오드 어레이, 또는 반도체 어레이이다. 일 측면에 있어서, 베클링된 상호 접속부에 전기적으로 접속된 장치 구성 부품은 박막, 센서, 회로 요소, 제어 요소, 마이크로프로세서, 트랜스듀서, 또는 이들의 조합들이다. 일 측면에 있어서, 상호 접속부들은 장치 구성 부품에 상호 접속부의 일 단부를 전기적으로 접속함으로써 접근된다.

[0049] 일 구현예에 있어서, 본 발명은 웨이브가 진 반도체 나노막과 같이, 웨이브가 진 나노막을 갖는 구조와 방법들에 관한 것이다. 이러한 웨이브가 진 나노막은 (장치 구성 부품들을 연결하는 상호 접속부들의 가요성과는 대조적으로) 장치 구성 부품 그 자체 내에 가요성(flexibility)을 통합하는 것을 용이하게 한다. 일 측면에 있어서, 본 발명은 반도체 나노막 물질을 제 1 기판으로부터 변형된 제 2 기판으로 전사하는 이축(biaxially) 인장 가능한 반도체 막의 제조 방법에 관한 것이다. 이 때 전사 후에는, 변형된 상기 기판이 릴랙스되어 그의 휴지기 구성(resting configuration)으로 복원되는 것이 허용된다. 일 측면에 있어서, 반도체 물질의 두께는 약 40 nm 내지 600 nm 사이이다. 2차원 변형을 일으킨 힘의 해제는 2차원으로 웨이브진 구조물을 갖는 나노막을 생성한다. 일 측면에서, 상기 변형력은 플렉서블한 기판의 온도를 변화시킴으로써 생성된다.

[0050] 일 구현예에 있어서, 양각 구조물을 갖는 수용 표면을 갖는 기판을 제공하는 단계; 상기 수용 표면을 적어도 부분적으로 정합적으로 코팅하기 위하여 폴리머를 스피-코팅함으로써 상기 양각 구조물을 매끈하게 하는 단계; 스피-코팅된 상기 기판 위에 폴리머 스템프를 주조하는(casting) 단계; 양각 구조물을 갖는 폴리머 스템프를 노출시키기 위하여 상기 기판으로부터 폴리머 스템프를 제거하는 단계; 및 양각 구조물을 갖는 상기 폴리머 스템프 표면 위로 장치 구성 부품을 증착하는 단계를 포함하는 인장 가능하고 구부릴 수 있는 장치의 제조를 위한 방법이 제공되며, 그에 의하여 인장 가능하고 구부릴 수 있는 장치에서 사용하기 위한 인장 가능하고 구부릴 수 있는 구조 부품을 제조할 수 있다. 일 측면에 있어서, 상기 양각 구조물들은 웨이브가 진 것이다.

[0051] 일 구현예에 있어서, 상기 구성 부품은 금속을 포함하고, 상기 금속은 전착(electrodeposition)에 의하거나, 또는, 새도우 마스크를 제공하는 단계; 상기 새도우 마스크를 웨이브진 표면과 접촉시키는 단계; 및 상기 웨이브진 표면 위에 새도우 마스크에 대응하는 금속 패턴을 생성하기 위해 상기 새도우 마스크를 통하여 금속을 증발

시키는(evaporating) 단계에 의하여 증착된다. 웨이브 구조물을 갖는 상기 기판은 Si (100)의 비등방 식각에 의하여 또는 SU-8의 염보싱에 의하여 선택적으로 제조된다. 선택적으로 상기 웨이브진 표면은 50 nm 내지 1 mm 사이에서 선택된 범위를 갖는 파장; 100 nm 내지 1 mm 사이에서 선택된 범위를 갖는 진폭;을 갖고, 또한 100%까지 파괴됨 없이 인장될 수 있다. 선택적으로, 상기 구성 부품은 장치 기판으로 전사된다. 일 측면에 있어서, 상기 장치 구성 부품은 상호 접속부를 포함하고, 상기 방법은 추가적인 장치 구성 부품을 제공하는 단계 및 상기 상호 접속부의 일 단부와 상기 추가적인 장치 구성 부품 사이에 전기적 접촉을 형성하는 단계를 더 포함한다.

[0052] 다른 측면에 있어서, 본 발명은 물질 수준 이종 접적(heterogeneous integration) 및/또는 장치 수준 이종 접적 기술을 통하여 장치를 제조하는 방법을 제공한다. 장치를 제조하기 위한 본 발명의 방법은 (i) 기판으로서, 상기 기판의 수용 표면에 의하여 지지되는 하나 또는 그 이상의 장치 구성 부품들로 사전-패터닝된(pre-patterned) 기판을 제공하는 단계; 및 (ii) 상기 기판의 수용 표면 위에 또는 그 위에 제공된 하나 또는 그 이상의 구조물들 위에 인쇄 가능한 반도체 요소들을 접촉 인쇄함으로써 상기 기판 위에 복수의 인쇄 가능한 상기 반도체 요소들을 조립하는 단계를 포함한다. 이 때, 상기 인쇄 가능한 반도체 요소들의 적어도 일부는 이들이 상기 기판에 의하여 지지되는 하나 또는 그 이상의 장치 구성 부품들과 공간적으로 정렬되거나, 전기적으로 접촉하거나, 또는 이들 둘 모두를 만족하도록 배치된다. 일 구현예에서, 상기 인쇄 가능한 반도체 요소들 각각은 약 100 nm 내지 약 1000 마이크론의 범위로부터 선택되는 길이, 약 100 nm 내지 약 1000 마이크론의 범위로부터 선택되는 폭, 및 약 10 nm 내지 약 1000 마이크론의 범위로부터 선택되는 두께를 갖는 단일(unitary) 무기 반도체 구조물을 포함한다.

[0053] 다른 측면에 있어서, 본 발명은 물질 수준 이종 접적(heterogeneous integration) 및/또는 장치 수준 이종 접적 기술을 통하여 다중 수준(multilevel) 장치 구조물을 제조하는 방법들을 제공한다. 장치를 제조하기 위한 본 발명의 방법은 (i) 기판으로서, 상기 기판의 수용 표면에 의하여 지지되는 하나 또는 그 이상의 장치 구성 부품들로 사전-패터닝된(pre-patterned) 기판을 제공하는 단계; (ii) 상기 기판의 수용 표면 위에 또는 그 위에 제공된 하나 또는 그 이상의 구조물들 위에 인쇄 가능한 반도체 요소들을 접촉 인쇄함으로써 상기 기판 위에 제 1 세트의 인쇄 가능한 상기 반도체 요소들을 조립하고, 그에 의하여 제 1 장치층을 생성하는 단계; (iii) 상기 제 1 세트의 인쇄 가능한 반도체 요소들 위에 수용 표면을 갖는 중간층을 제공하는 단계; 및 (iv) 상기 중간층의 수용 표면 위에 또는 그 위에 제공된 하나 또는 그 이상의 구조물들 위에 인쇄 가능한 반도체 요소들을 접촉 인쇄함으로써 상기 중간층 위에 제 2 세트의 인쇄 가능한 상기 반도체 요소들을 조립하고, 그에 의하여 제 2 장치층을 생성하는 단계를 포함한다. 일 구현예에 있어서, 상기 제 1 장치층에 있는 인쇄 가능한 반도체 요소들의 적어도 일부분은 상기 제 2 장치층에 있는 인쇄 가능한 반도체 요소들의 적어도 일부분과 공간적으로 정렬되거나, 전기적으로 접촉하거나, 또는 이들 둘 모두를 이룬다. 본 발명의 이러한 측면의 구체적인 방법은 상기 제 1 장치층 내의 인쇄 가능한 반도체 요소들의 적어도 일부분과 상기 제 2 장치층 내의 인쇄 가능한 반도체 요소들의 적어도 일부분 사이에 전기적인 접촉을 형성하는 단계를 더 포함한다.

[0054] 본 방법들에 있어서 인쇄 가능한 반도체 요소들을 조립하고, 조직화하고 및/또는 접적하기 위한 유용한 접촉 인쇄 방법들은 건식 전사 접촉 인쇄(dry transfer contact printing), 마이크로 접촉(microcontact) 또는 나노 접촉(nanocontact) 인쇄, 마이크로 전사(microtransfer) 또는 나노 전사(nanotransfer) 인쇄, 및 자기조립 보조 인쇄(self assembly assisted printing)를 포함한다. 접촉 인쇄는 복수의 인쇄 가능한 반도체를 서로에 대하여 선택된 상대적인 방향과 위치로 조립하고 접적하는 것을 가능하게 하기 때문에, 접촉 인쇄를 사용하는 것이 본 발명에 유리하다. 또한, 본 발명에 있어서 접촉 인쇄는 반도체들(예를 들면, 무기 반도체들, 단결정 반도체들, 유기 반도체들, 탄소 나노물질들 등), 유전체들 및 도전체들을 포함하는 다양한 부류의 물질들과 구조들을 효과적으로 전사하고, 조립하고, 또한 접적하는 것을 가능하게 한다. 선택적으로 본 발명의 접촉 인쇄 방법들은 장치 기판 위에 미리 패터닝된 하나 또는 그 이상의 장치 구성 부품들에 대하여 미리 선택된 상대적인 위치들 및 공간적 배향들에 인쇄 가능한 반도체 요소들이 고정밀도로 일치되는 전사 및 조립을 제공한다. 또한, 접촉 인쇄는 유리, 세라믹, 및 금속과 같은 통상의 경질 또는 반-경질 기판들 및 가요성 기판들, 구부릴 수 있는 기판들, 성형가능한(shapeable) 기판들, 정합될 수 있는(conformable) 기판들, 및/또는 인장 가능한 기판들과 같이 특정 응용들에 대하여 매력적인 물리적 및 기계적 성질들을 갖는 기판들을 포함하는 광범위한 유형의 기판과 양립할 수 있다. 인쇄 가능한 반도체 구조들의 접촉 인쇄 조립은, 예를 들면, 저온 공정(예를 들면, 298K 이하)과 양립할 수 있다. 이 속성은 폴리머 및 플라스틱 기판들과 같이 고온에서 분해되거나 열화되는 것들을 포함하는 소정 범위의 기판 물질들을 이용하여 본 광학 시스템이 실행되는 것을 가능하게 한다. 장치 요소들의 콘택 인쇄 전사, 조립, 및 접적은 롤-투-롤 인쇄(roll-to-roll printing) 및 플렉소 인쇄(flexographic printing) 방법들 및 시스템들과 같이 비용이 저렴하고 높은-쓰루풋을 갖는 인쇄 기술들을 통해 적용될 수 있기

때문에 유리하다.

[0055] 장치들을 제조하는 본 방법들의 특정 구현예들에 있어서, 인쇄 가능한 반도체 요소들의 적어도 일부분은 이종의 반도체 요소들을 포함한다. 소정 범위의 이종 반도체 요소들은 본 발명에 있어서 유용하다. 일 구현예, 또는 일 실시예에 있어서, 상기 이종의 반도체 요소들은 무기 반도체 구조; 및 상기 무기 반도체 구조와 상이한 조성을 갖는 무기 반도체, 상기 무기 반도체 구조와 상이한 도핑을 갖는 무기 반도체, 탄소 나노물질 또는 그의 필름, 유기 반도체, 유전 물질, 및 도전체로 구성되는 군으로부터 선택되는 물질을 포함하는 하나 또는 그 이상의 구조들;의 결합을 포함한다. 예를 들면, 일 구현예에서, 상기 이종 반도체 요소들은 단결정 실리콘, Si, Ge, SiC, AlP, AlAs, AlSb, GaN, GaP, GaAs, GaSb, InP, InAs, GaSb, InP, InAs, InSb, ZnO, ZnSe, ZnTe, CdS, CdSe, ZnSe, ZnTe, CdS, CdSe, CdTe, HgS, PbS, PbSe, PbTe, AlGaAs, AlInAs, AlInP, GaAsP, GaInAs, GaInP, AlGaAsSb, AlGaInP, SiGe 및 GaInAsP으로 구성되는 군으로부터 선택되는 상이한 두 반도체 물질들의 조합을 포함한다. 예를 들면, 일 구현예에 있어서, 상기 이종 반도체 요소들은 유전 물질, 도전체, 또는 유전 물질과 도전체 모두와 결합된 무기 반도체 구조를 포함한다.

[0056] 또한, 유용한 이종 반도체 요소들은 인쇄 가능한 장치 구성 요소들과 인쇄 가능한 장치들을 포함한다. 일 구현 예에서, 예를 들면, 상기 인쇄 가능한 반도체 요소들은 전자 장치, 전자 장치의 어레이, 광학 장치, 전자-광학 장치, 미세 유동 장치, 미세전자기계 시스템, 나노전자기계 시스템, 센서, 집적 회로, 마이크로프로세서, 및 메모리 장치로 구성되는 군으로부터 선택되는 장치의 하나 또는 그 이상의 구성 부품들을 포함한다.

[0057] 특정 방법들에 있어서, 상기 이종 반도체 요소들의 적어도 일부분은 다이오드, 트랜지스터, 광전지 (photovoltaic cell), 발광 다이오드, 레이저, P-N 접합, 박막 트랜지스터, 고 전자이동도 트랜지스터, 광 다이오드, 금속-산화물-반도체 전계효과 트랜지스터, 금속-반도체 전계효과 트랜지스터, 광 감지기, 논리 게이트 장치, 및 수직-공동 표면-발광 레이저로 구성되는 군으로부터 선택되는 하나 또는 그 이상의 인쇄 가능한 반도체 장치들을 포함한다. 일 구현예에 있어서, 예를 들면, 상기 인쇄 가능한 반도체 장치들의 적어도 일부분은 상기 인쇄 가능한 반도체 장치들과 기판 위에 사전-페터닝된 전극들과의 전기적인 접촉이 제공되도록 콘택 인쇄를 통해 상기 기판 위에 조립된다.

[0058] 본 발명의 방법들은 인쇄 가능한 반도체 요소들을 기판 또는 그 위에 제공된 장치 구성 부품 구조들, 충간 구조 및/또는 평탄화 또는 봉지층들과 같은 구조(들) 위에 조립하는 단계들을 다중적(multiple)으로, 그리고 선택적으로는 반복적으로 더 포함할 수 있다. 일 구현예에 있어서, 예를 들면, 본 발명의 방법은 추가적인 인쇄 가능한 반도체 요소들을 기판의 수용 표면 위에 제공된 반도체 요소들 위에, 또는 상기 기판의 상기 수용 표면 위에 제공된 반도체 요소들과 상기 추가적인 인쇄 가능한 반도체 요소들 사이에 제공된 또는 하나 또는 그 이상의 중간 구조들 위에 접촉 인쇄함으로써 추가적인 인쇄 가능한 반도체 요소들을 상기 기판 위에 조립하는 단계를 더 포함한다.

[0059] 본 방법들에 의하여 제조된 다중층 장치 구조는 하나 또는 그 이상의 중간층(interlayer)들에 의하여 분리된 복수의 장치 층(device layer)들을 포함할 수 있다. 여기서, 상기 장치 층들은 인쇄 가능한 반도체 요소들을 포함한다. 일부 구현예들에 있어서, 예를 들면, 상기 장치 층들은 1 마이크론보다 작거나 같은 두께들을 갖고, 상기 중간층들은 1.5 마이크론보다 작거나 같은 두께들을 갖는다. 일부 구현예들에 있어서, 본 측면의 방법들은 상이한 장치 층들 내에 제공된 인쇄 가능한 반도체들 사이에 전기적인 콘택을 형성하는 단계를 더 포함한다.

[0060] 본 측면의 구체적인 방법은: (i) 상기 기판의 수용 표면 위에 또는 그 위에 제공된 하나 또는 그 이상의 구조들 위에 인쇄된 인쇄 가능한 반도체 요소들의 상부 위에 중간층을 제공하는 단계; 및 (ii) 상기 중간층의 수용 표면 위에 인쇄 가능한 반도체 요소들을 접촉 인쇄함으로써 추가적인 인쇄 가능한 반도체 요소들을 조립하는 단계의 단계들을 더 포함한다. 예를 들면, 일 구현예에서, 상기 중간층의 수용 표면 위에 제공된 추가적인 인쇄 가능한 반도체 요소들의 적어도 일부분은 상기 기판의 수용 표면 위에 제공된 인쇄 가능한 반도체 요소들과 공간적으로 정렬되거나, 전기적으로 접촉하거나, 또는 이들 둘 모두가 달성되도록 위치된다. 본 측면의 방법들은 선택적으로, (i) 중간층 내에 하나 또는 그 이상의 개구부를 패터닝하는 단계로서, 그에 의하여 상기 기판의 수용 표면 위에 또는 상기 수용 표면 위에 제공된 하나 또는 그 이상의 구조들 위에 제공된 인쇄 가능한 반도체 요소들의 하나 또는 그 이상의 영역들을 노출시키는 단계; 및 (ii) 상기 기판의 수용 표면 위에 또는 상기 수용 표면 위에 제공된 하나 또는 그 이상의 구조들 위에 제공된 인쇄 가능한 반도체 요소들과 상기 중간층의 수용 표면 위에 제공된 상기 반도체 요소들 사이에 상기 중간층 내의 개구부들을 관통하는 전기적 콘택을 형성하는 단계의 단계들을 더 포함할 수 있다.

[0061] 본 발명의 방법들은 수많은 선택적인 공정 단계들을 포함할 수 있다. 본 발명의 한 방법은 수용 표면 위에 접

착총을 제공하는 단계를 더 포함한다. 여기서, 상기 인쇄 가능한 반도체 요소들은 상기 접착층 위에 인쇄된다. 본 발명의 한 방법은 상기 기판의 수용 표면 위에 또는 상기 수용 표면 위에 제공된 하나 또는 그 이상의 구조들 위에 인쇄된 인쇄 가능한 반도체 요소들 위에 봉지층 또는 평탄화층(planarizing layer)을 제공하는 단계를 더 포함한다. 본 발명의 한 방법은 상기 기판의 수용 표면 위에 또는 상기 수용 표면 위에 제공된 하나 또는 그 이상의 구조들 위에 인쇄된 하나 또는 그 이상의 인쇄 가능한 반도체 요소들 또는 상기 기판의 수용 표면을 증착 방법을 통해 하나 또는 그 이상의 도전성의 흰색 필름들과 함께 패터닝하는 단계를 더 포함한다. 본 발명의 방법들은 가용성 기판들; 폴리머 기판들, 플라스틱 기판들, 인장 가능한 기판들; 경질 기판들; 반도체 웨이퍼들 및 콘투어된 기판(contoured substrate)을 포함하는 소정 범위의 기판들에 적용될 수 있지만 이들에 한정되는 것은 아니다.

[0062] 본 발명은 본 방법들을 이용하여 제조된 장치들과 시스템들도 포함한다. 본 발명의 장치들 및 시스템들은 전자 장치들, 광학 장치들, 전자-광학 장치들, 미세유동(microfluidic) 장치들, 미세전자기계 시스템들 (microelectromechanical systems), 나노전자기계 시스템들(nanoelectromechanical systems), 센서들, 접적 회로들, 마이크로프로세서들 및 메모리 장치들을 포함하지만 여기에 한정되는 것은 아니다.

[0063] 다른 구현예에 있어서, 본 발명은 2차원의 인장가능하고 구부릴 수 있는 장치이다. 본 측면에 있어서, 상기 장치는 접촉 표면을 갖는 기판을 포함한다. 여기서, 상기 기판 접촉 표면의 적어도 일부분에 구성 부품이 결합되고, 상기 구성 부품은 적어도 하나의 양각 구조물 영역과 적어도 하나의 실질적으로 편평한 영역을 갖는다. 여기서, 상기 양각 구조물 영역은 상기 기판과 분리된 영역을 갖고, 상기 실질적으로 편평한 영역은 상기 기판에 적어도 부분적으로 결합된다. 일 측면에 있어서, 상기 적어도 하나의 양각 구조물 영역은 기판 위에, 상기 기판 접촉 영역과 접촉하는 복수의 접촉 영역들을 갖는 웨이브 패턴과 같은, 양각 구조물들의 2차원 패턴을 갖는다.

[0064] 상기 기판에 상기 구성 부품을 결합하는 것을 용이하게 하기 위하여, 상기 구성 부품 또는 기판 수용 표면 중의 임의의 하나 또는 이들 둘 모두는 활성화된 영역들의 패턴과 같은, 패터닝된 영역들을 가질 수 있다. "활성 영역들"은 상기 기판 접촉 표면 또는 상기 구성 부품 위의 접착 위치들의 패턴; 각각이 공간적 변화를 갖는 기판 또는 구성 부품의 두께, 모듈러스, 온도, 조성 중의 하나 또는 그 이상으로부터 선택된 상기 기판 또는 구성 부품의 물리적 파라미터들의 선택된 패턴; 기판 표면의 화학적 개질; 및 상기 기판 접촉 표면 위의 구성 부품의 자유 에지(free edge)들에 인접하는 영역; 중의 하나 또는 그 이상에 의하는 것과 같은 결합하기 위한 수단들 및/또는 베클링을 제공하기 위한 수단들을 지칭하기 위해 널리 사용된다. 이들 파라미터들 각각의 공통된 주제는 이들이 상기 구성 부품과 상기 기판 사이의 결합을 용이하게 하거나 또는 상기 구성 부품의 공간적으로 제어된 베클링을 생성하기 위한 기구를 제공한다는 것이다. 예를 들면, 상기 실질적으로 편평한 영역 또는 상기 양각 구조물 영역의 일부분을 활성 기판 영역에 위치시킴으로써 상기 구성부품은 인장 가능한 구성 부품을 제공하기 위해 제어 가능하게 베클링될 수 있다.

[0065] 여기에 개시된 임의의 방법들 및 장치들은 금속, 반도체, 절연체, 압전체(piezoelectric), 강유전체(ferroelectric), 자기변형성(magnetostrictive) 물질, 전자변형성(electrostrictive) 물질, 초전도체, 강자성(ferromagnetic) 물질, 또는 열전성(thermoelectric) 물질인 물질 중의 하나 또는 그 이상으로 구성되는 군으로부터 선택되는 구성 부품을 선택적으로 갖는다. 여기에 개시된 임의의 방법들 및 장치들은 선택적으로 전자 장치, 광학 장치, 광학-전자 장치(opto-electronic device), 기계 장치, 및 열적 장치로 구성되는 군으로부터 선택되는 장치를 위한 것이다.

[0066] 일 측면에 있어서, 2차원적으로 인장 가능하고 구부릴 수 있는 임의의 장치들은, 적어도 두 개의 아일랜드들을 전기적으로 연결하는 상호 접속 양각 구조와 같이 장치 구성 부품들을 수용하기 위한 아일랜드(island)를 포함하는 실질적으로 편평한 영역을 갖는다.

[0067] 일 구현예에 있어서, 임의의 기판 콘택 또는 수용 표면은 편평하거나, 실질적으로 편평하거나, 양각 구조물을 갖거나, 굴곡진 부분을 갖거나, 웨이브 부분을 갖거나 또는 PDMS 기판 또는 기판층과 같이 엘라스토머성이다.

### 발명의 효과

[0068] 형태 정합적인(shape-conforming) 장치들은 플렉서블 디스플레이 및 전자 섭유들로부터 정합될 수 있는 생물학적 및 물리적 센서들에 이르기까지 다양한 응용을 갖는다

### 도면의 간단한 설명

[0069]

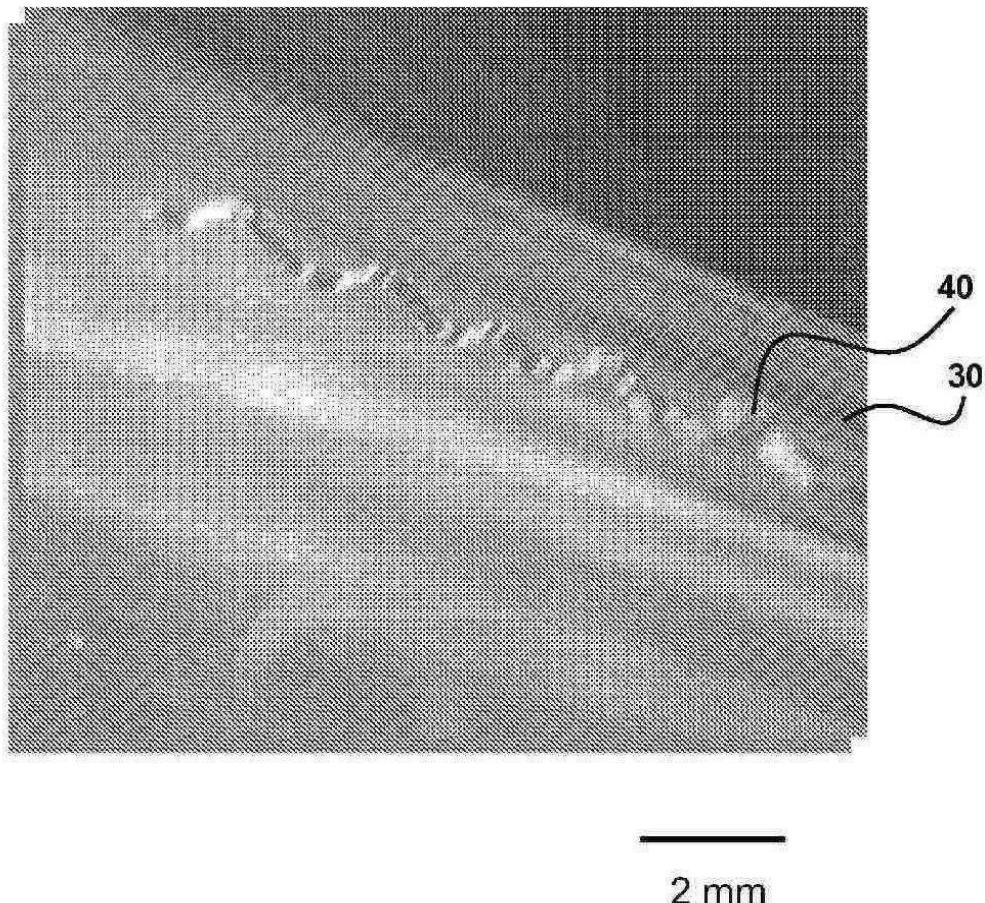

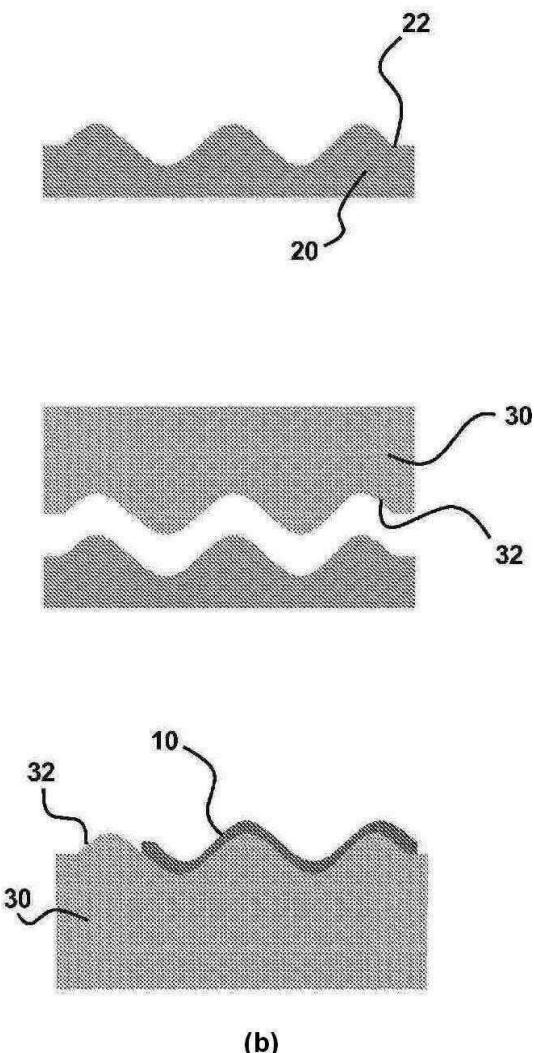

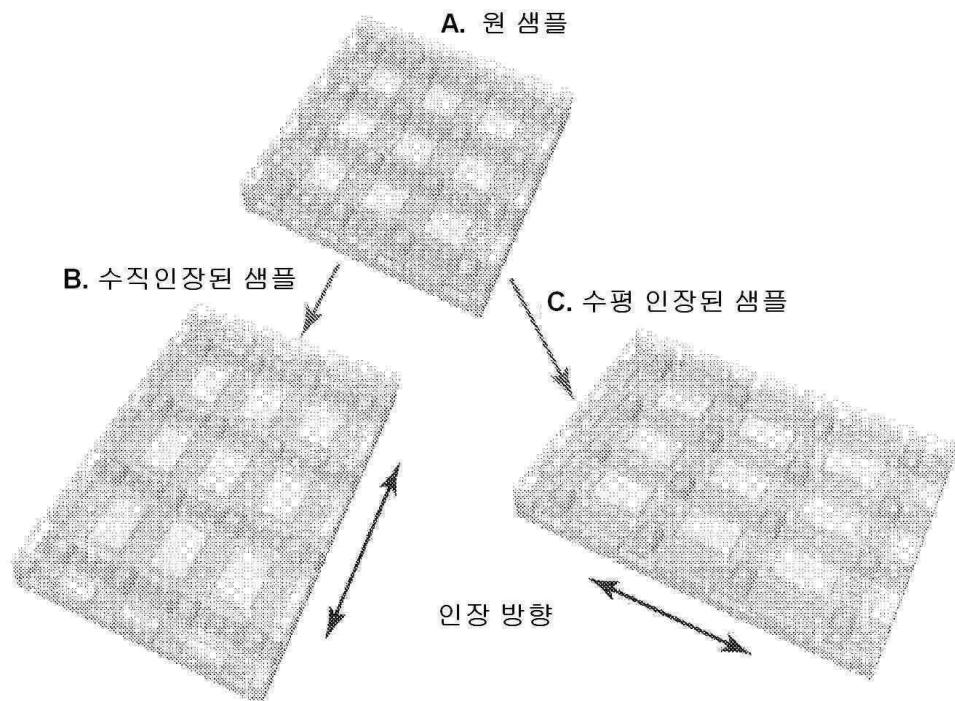

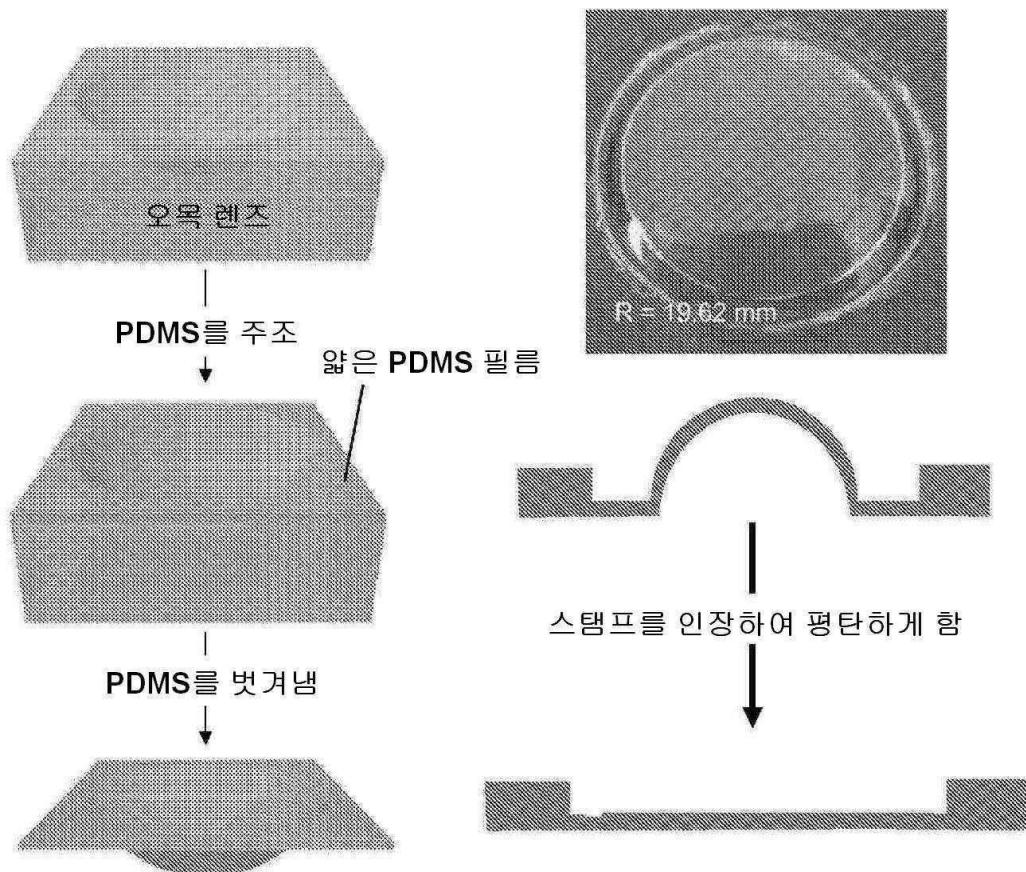

도 1은 웨이브지거나 또는 베클링된, 인장 가능한 금속 상호 접속부의 한 제조 방법을 요약한다. (a)는 순서도 요약이고, (b)는 순서도 단계들을 도시한다.

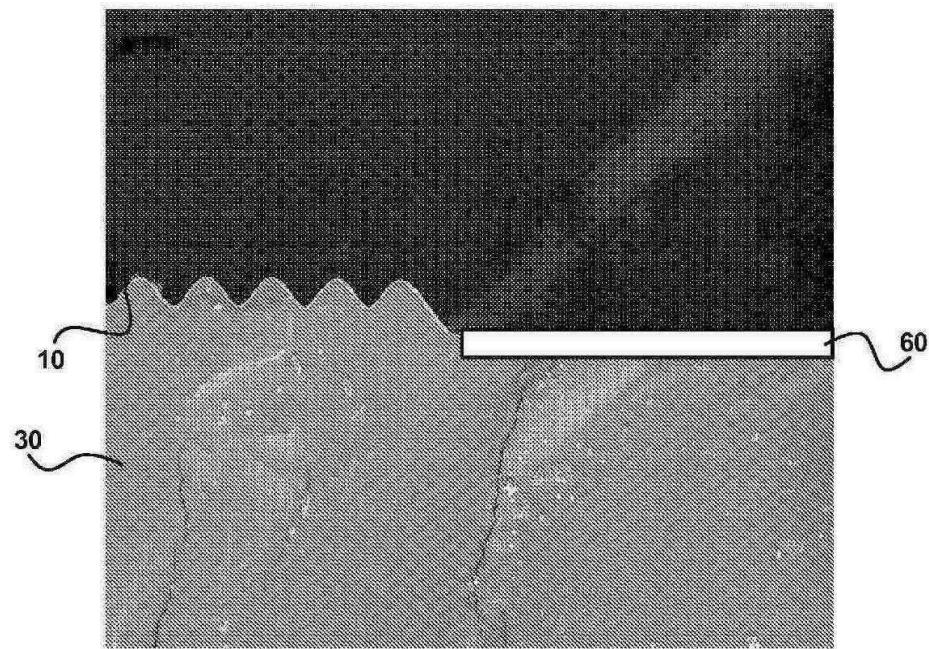

도 2는 강체 기판으로부터 사전-변형되고 인장 가능한 PDMS 고무 기판 위로 회수되고, 이어서 변형을 해제하여 베클링을 유발함으로써 형성된, 인장 가능하고 웨이브진/베클링된 전기 상호 접속부의 사진이다.

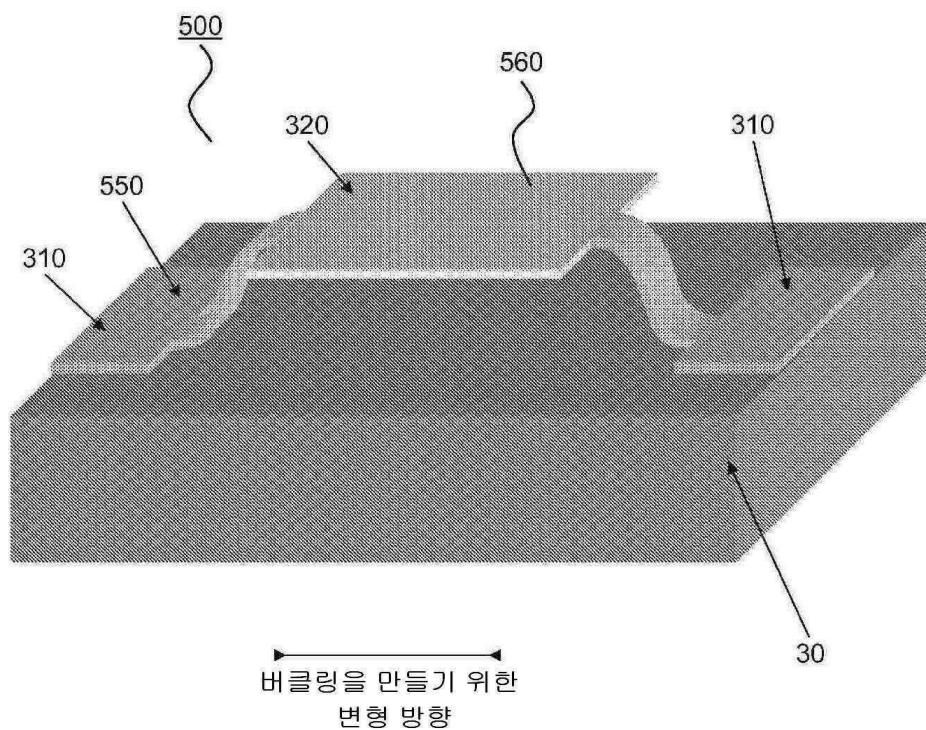

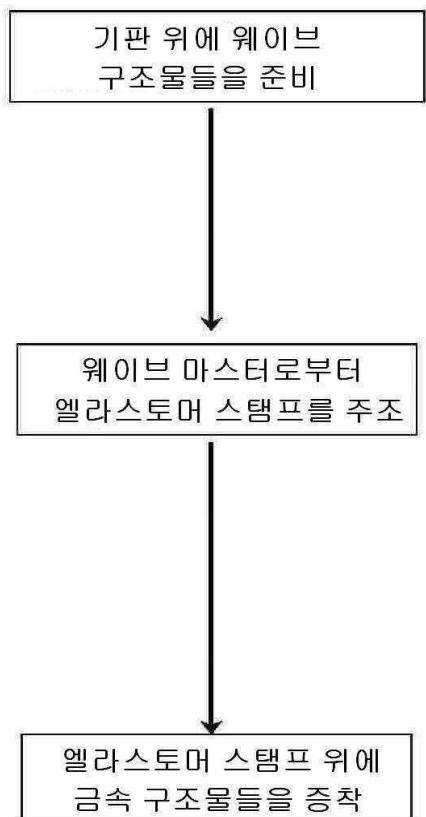

도 3은 웨이브 구조의 엘라스토머 기판 위에 증착을 통해 웨이브진 인장 가능한 전극들의 한 제조 방법을 요약한다.

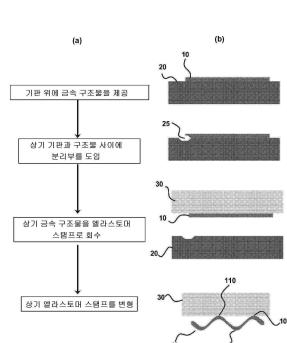

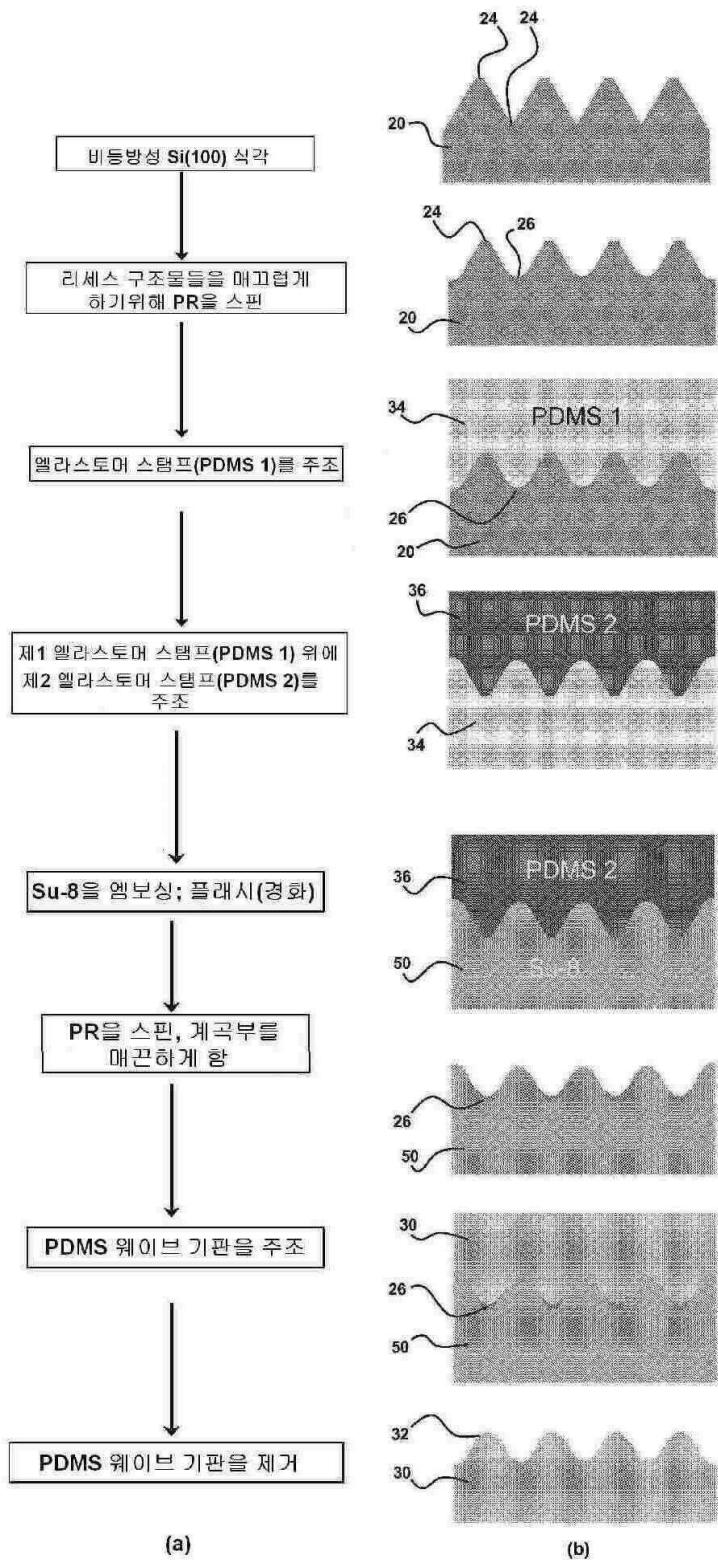

도 4는 매끈한 웨이브진 엘라스토머 기판을 제조하기 위한 한 방법을 제공한다. (a)는 순서도 요약이고, (b)는 순서도 단계들을 도시한다.

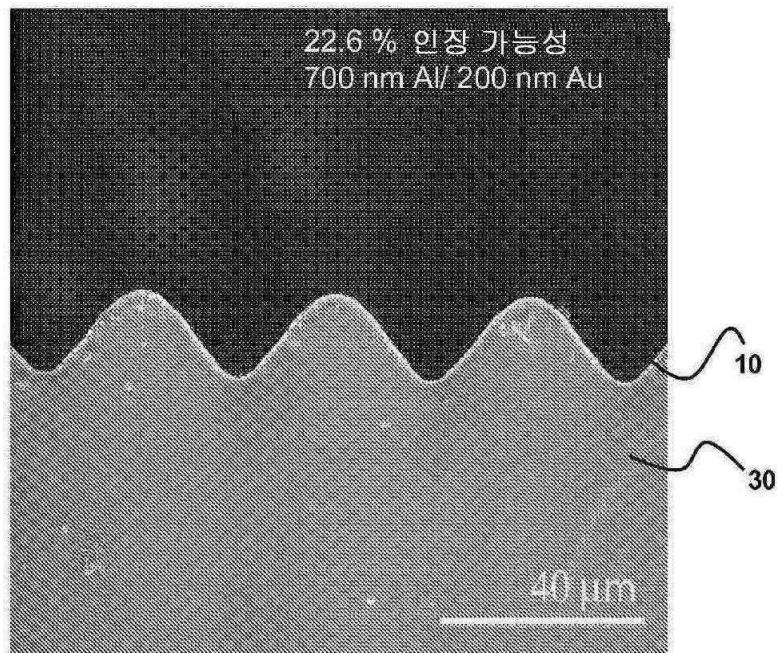

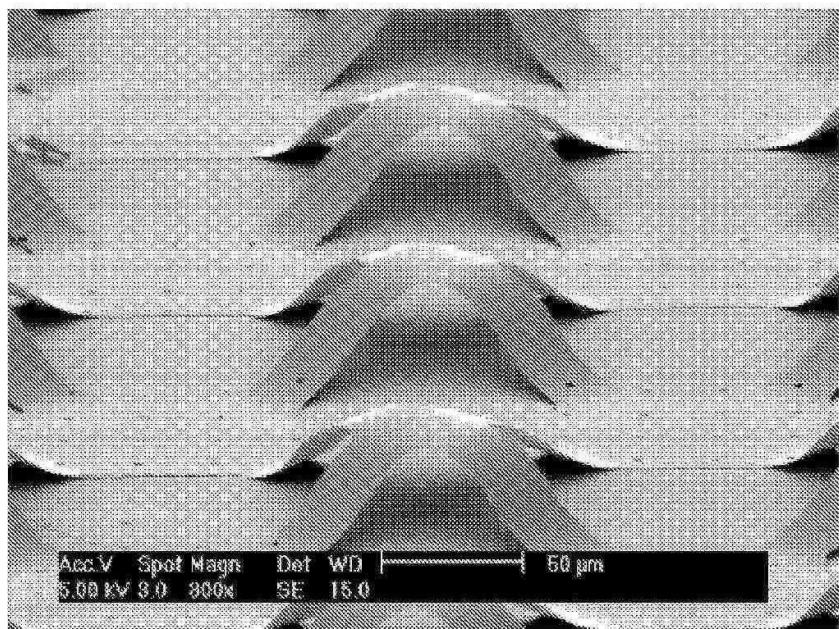

도 5는 도 3 내지 도 4에 대략 나타낸 방법들에 의하여 생성된, 매끈하게 웨이브진 PDMS 기판의 이미지를 제공한다. 나타내어진 상호 접속부는 22.6% 인장 가능하고, 약 900 nm의 두께(700 nm Al / 200 nm Au), 약 38 마이크론의 파장 및 약 15.6 마이크론의 진폭(피크로부터 계곡까지의 거리)을 갖는 금속 상호 접속부를 갖는다.

도 6a는 첨단부(cusp)들을 갖고 (Edmund Optics로부터) 상용으로 입수 가능한 렌즈상 어레이이다. 도 6b는 매끈하게 웨이브진 기판을 만들기 위하여 광경화성 에폭시를 스판-코팅한 것이다. 도 6c는 매끈한 구조물을 갖는 웨이브진 엘라스토머 스템프를 생성하기 위하여 도 6b로부터 기판에 대하여 PDMS 스템프를 주조한 것이다.

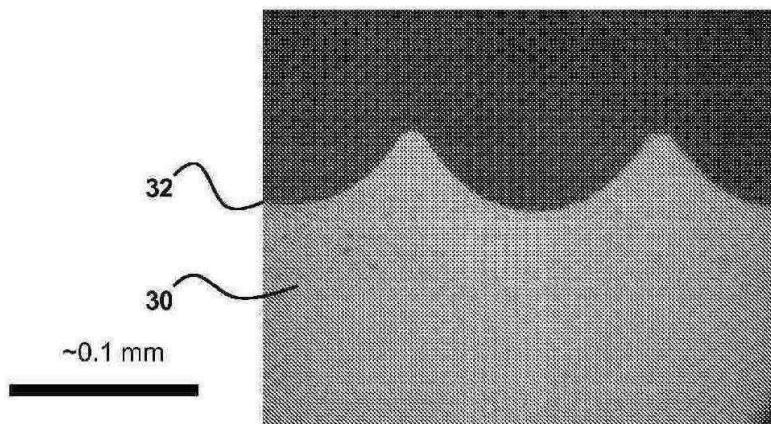

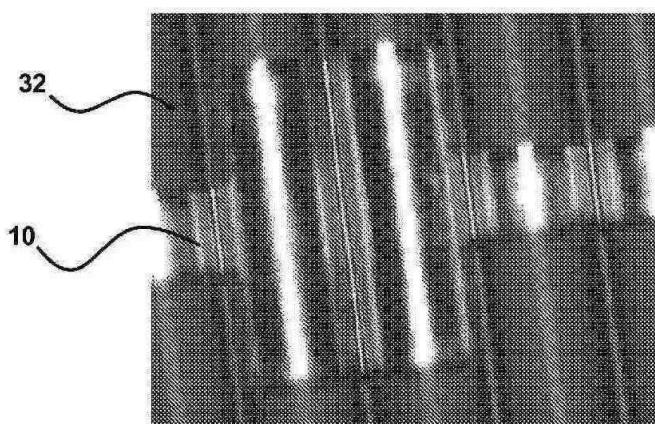

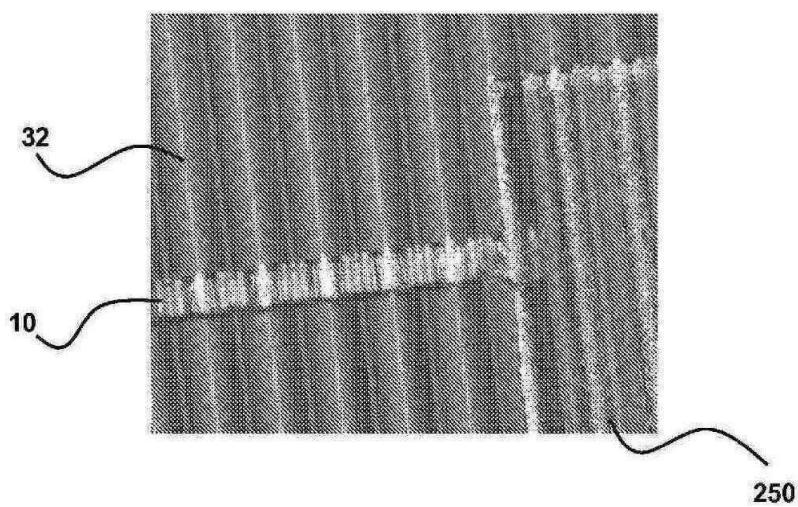

도 7a 내지 도 7c는 증발(evaporation)에 의하여 새도우 마스크를 통해 매끈하게 웨이브진 엘라스토머 기판 위로 증착된 인장 가능한 전극들이다. 상기 전극들은 장력에 의하여 ~10%까지 인장되는 동안 전도성과 접속성을 유지한다. 스케일 바는 약 0.1 mm이다. 도 7a는 엘라스토머 기판 위의 웨이브의 단면이다. 도 7b는 증발하여 상기 웨이브진 엘라스토머 기판 위에 증착된 전극의 평면을 나타낸 현미경 사진이다. 초점면은 상기 웨이브진 양각의 피크 위에 있다. 도 7c는 증발하여 상기 웨이브진 엘라스토머 기판 위에 증착된 전극의 평면을 나타낸 현미경 사진이다. 초점면은 상기 웨이브진 양각의 계곡 위에 있다.

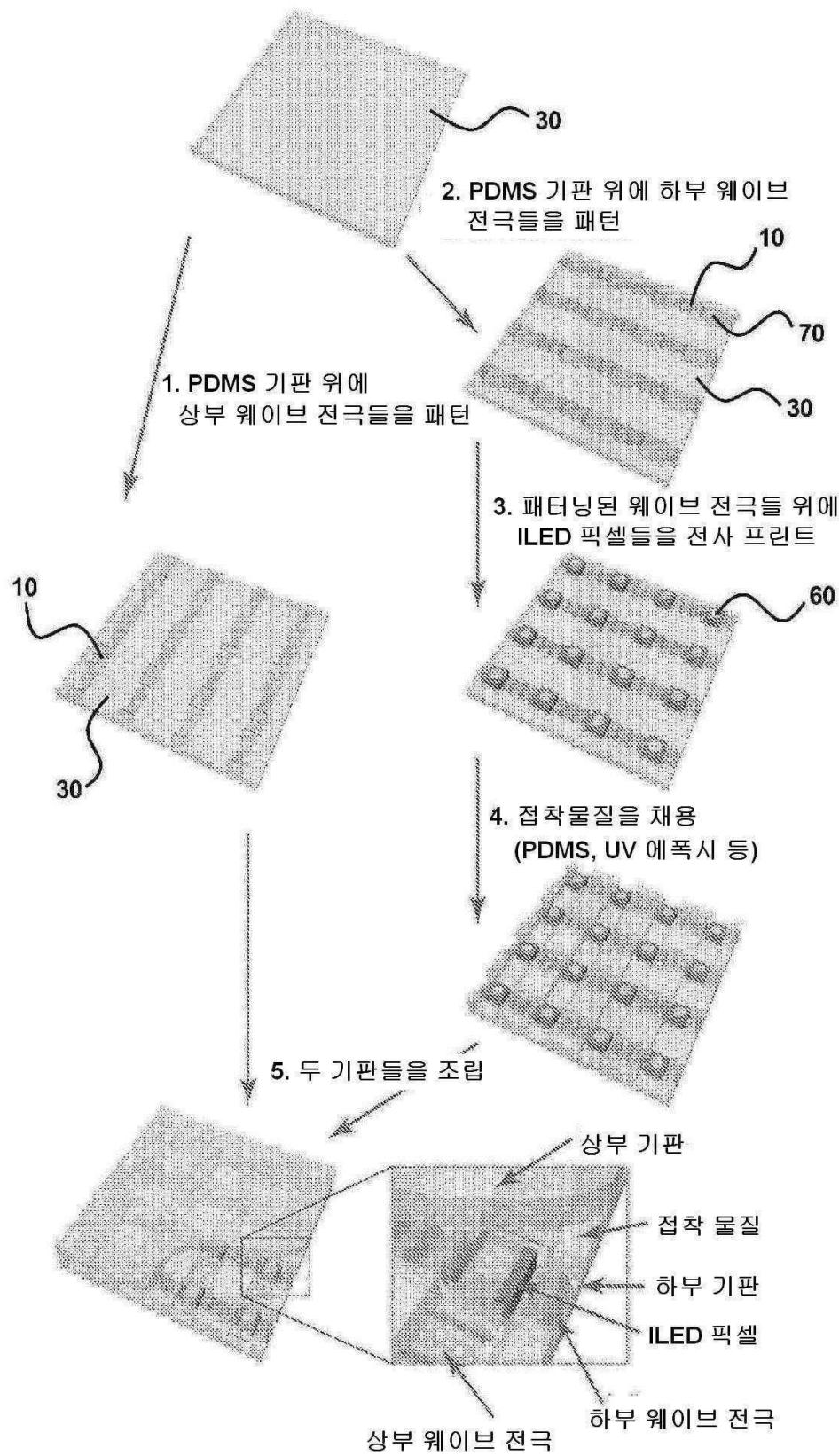

도 8은 인장 가능한 전극들을 이용하여 인장 가능한 수동 매트릭스 LED 디스플레이를 제조하는 공정을 개략적으로 나타낸 도면이다.

도 9는 웨이브진 전극들을 갖는 수동 매트릭스 LED 디스플레이의 기계적인 인장 가능성을 나타낸다.

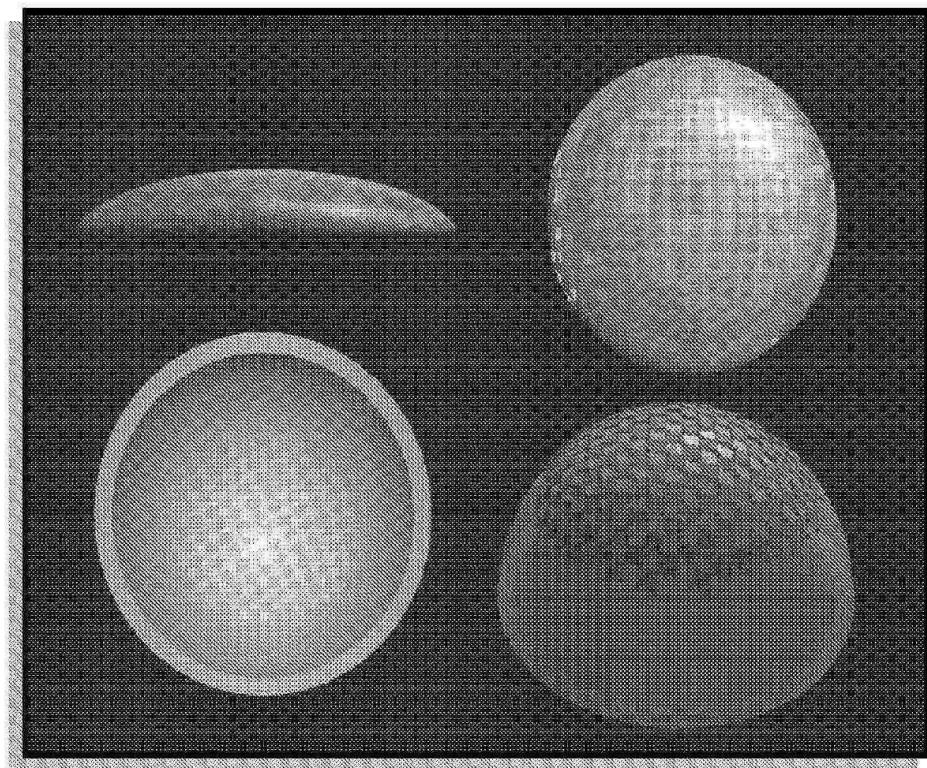

도 10은 반구 만곡부를 갖는 렌즈 위에 분포된 무기 광 다이오드 어레이들을 나타낸다. 다양한 렌즈 형태들과 각도들을 나타낸다.

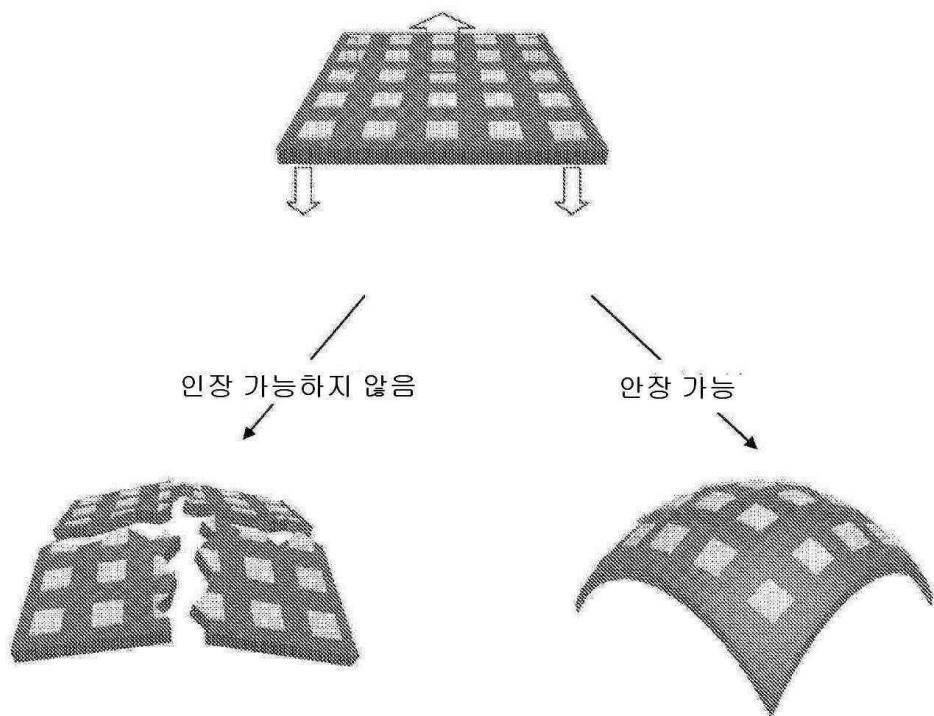

도 11은 평면 시트를 구면 주위에 쌀 때 인장 가능성이 요구되는 것을 도시한다.

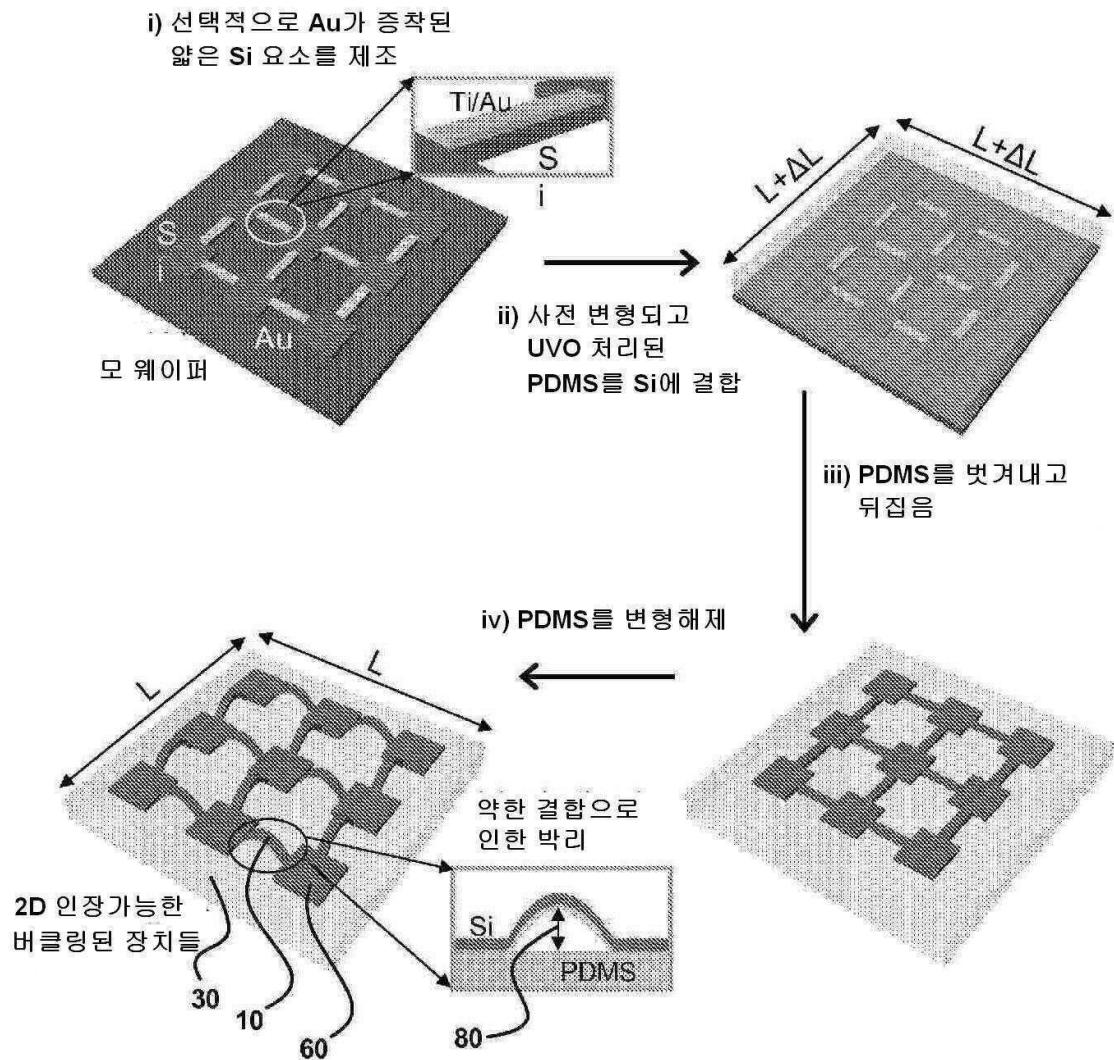

도 12는 구형의 곡면에 정합될(conform) 수 있는 인장 가능하고 베클링된 반도체 어레이들을 제조하는 한 방법을 요약한다.

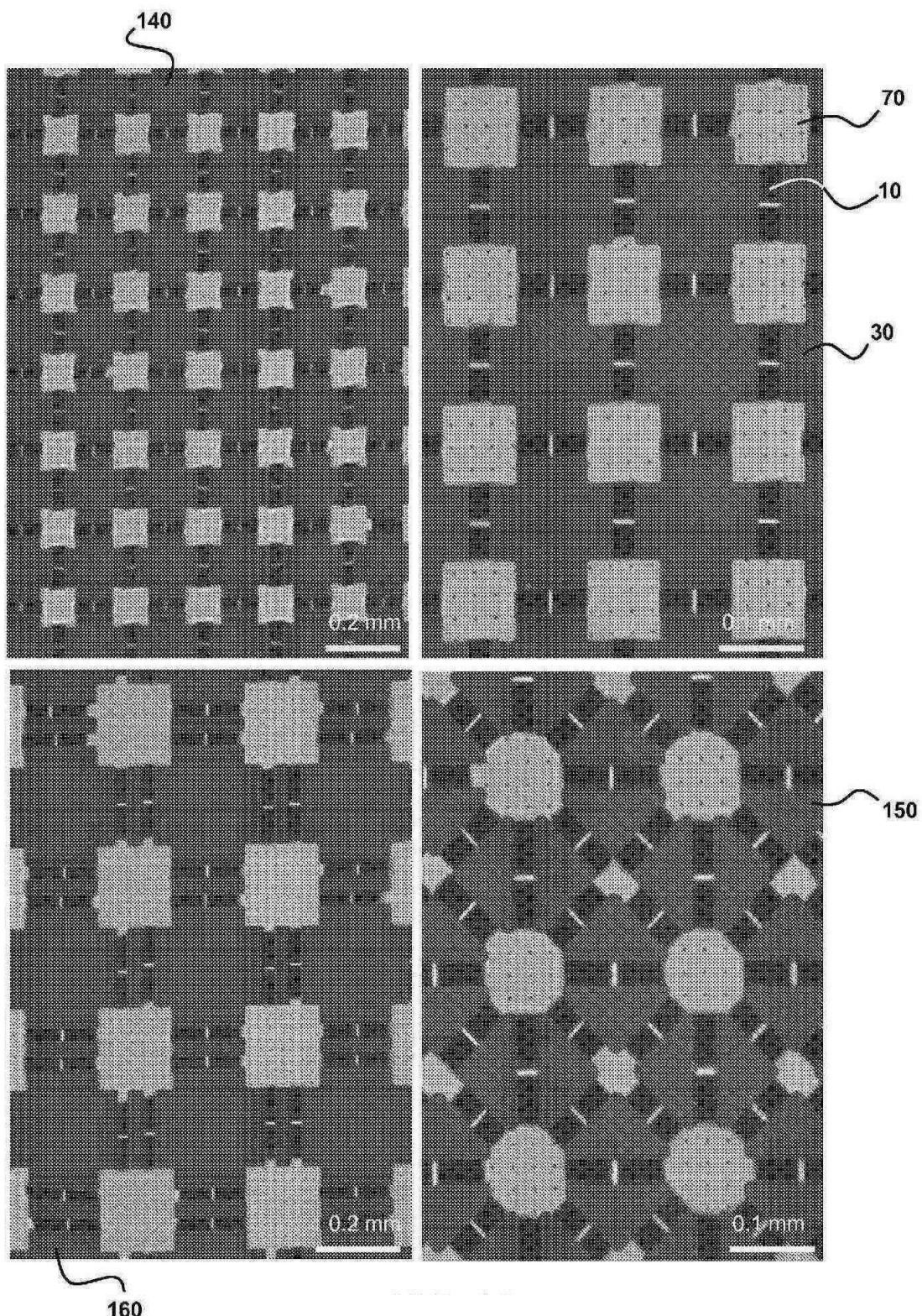

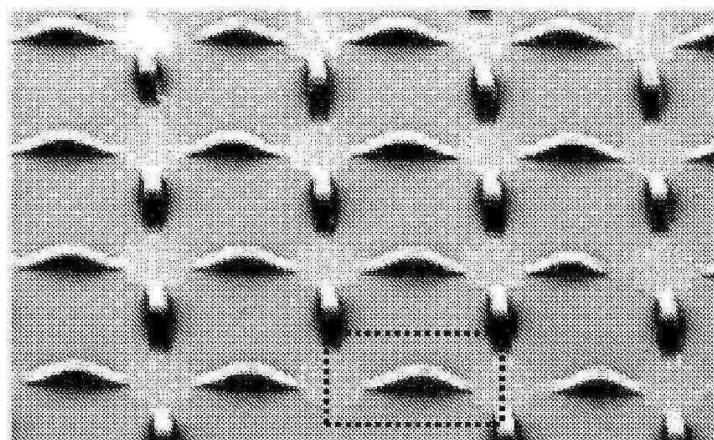

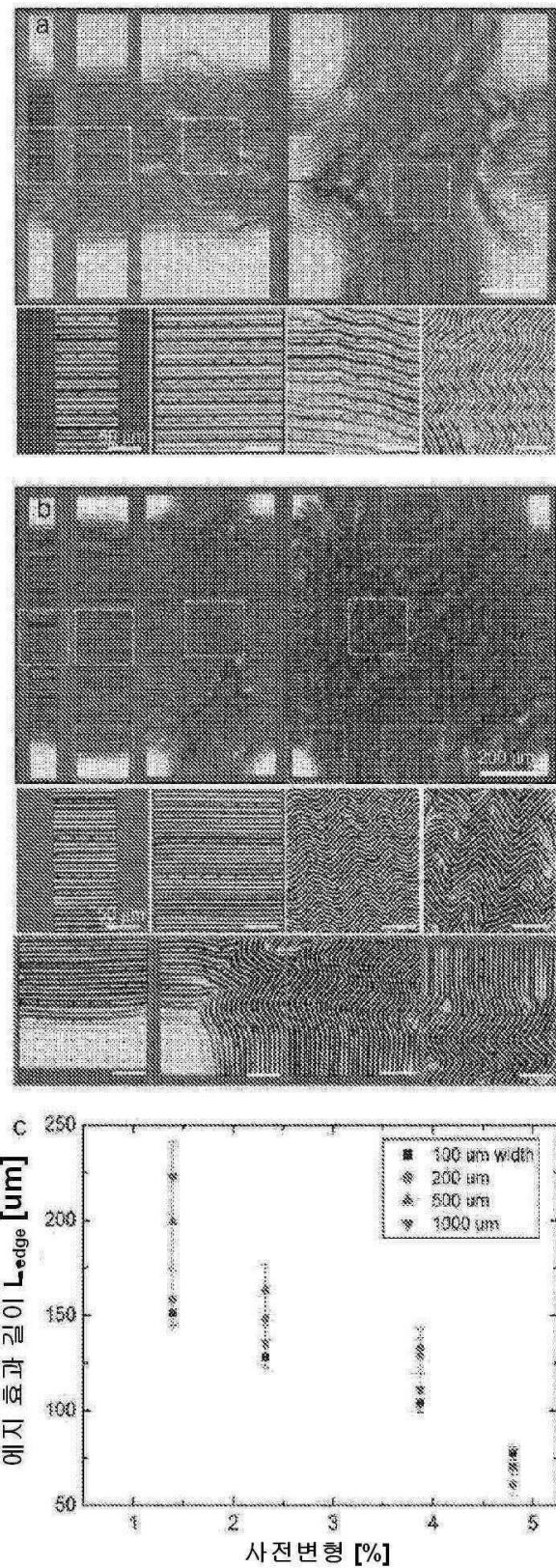

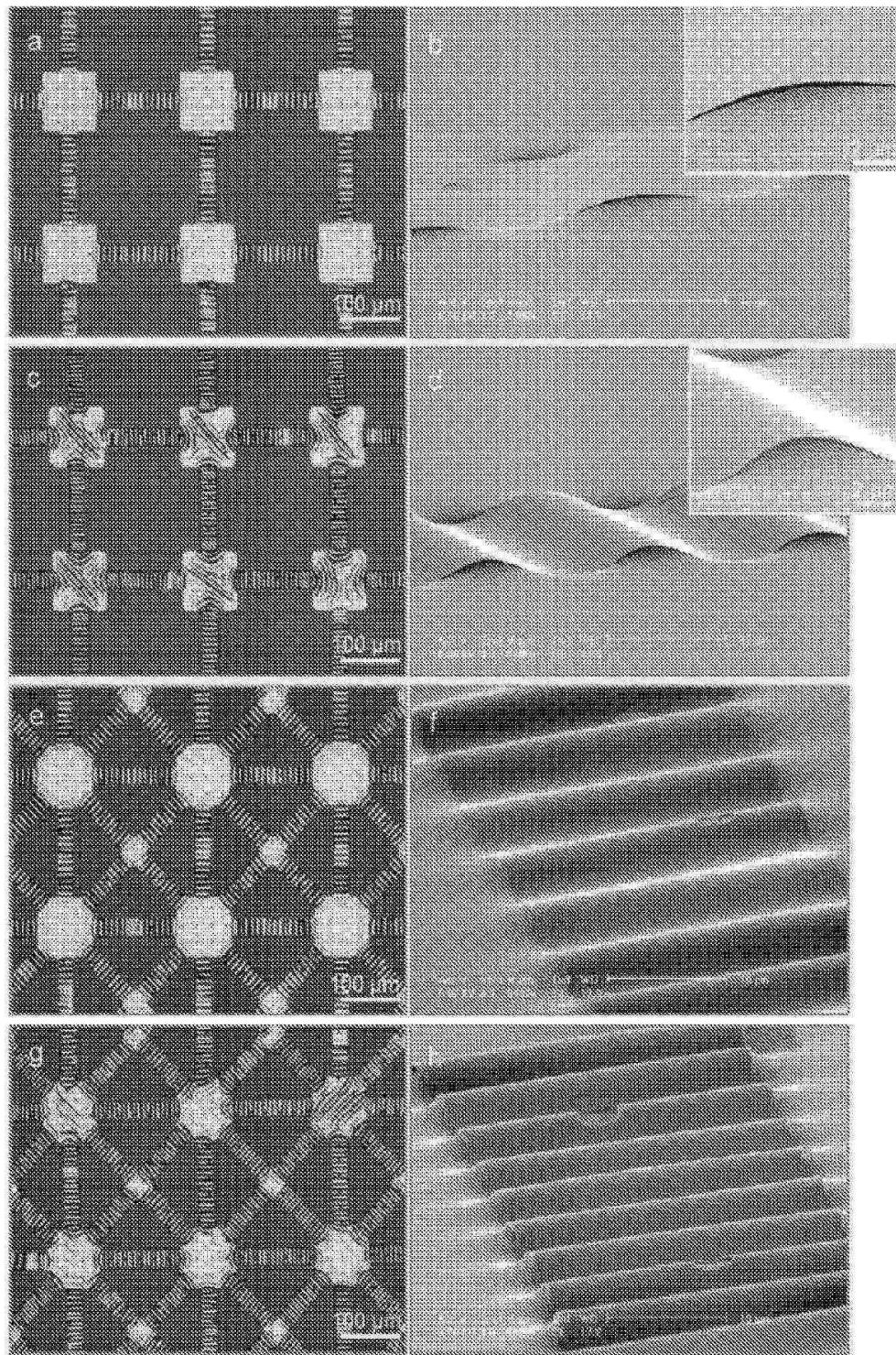

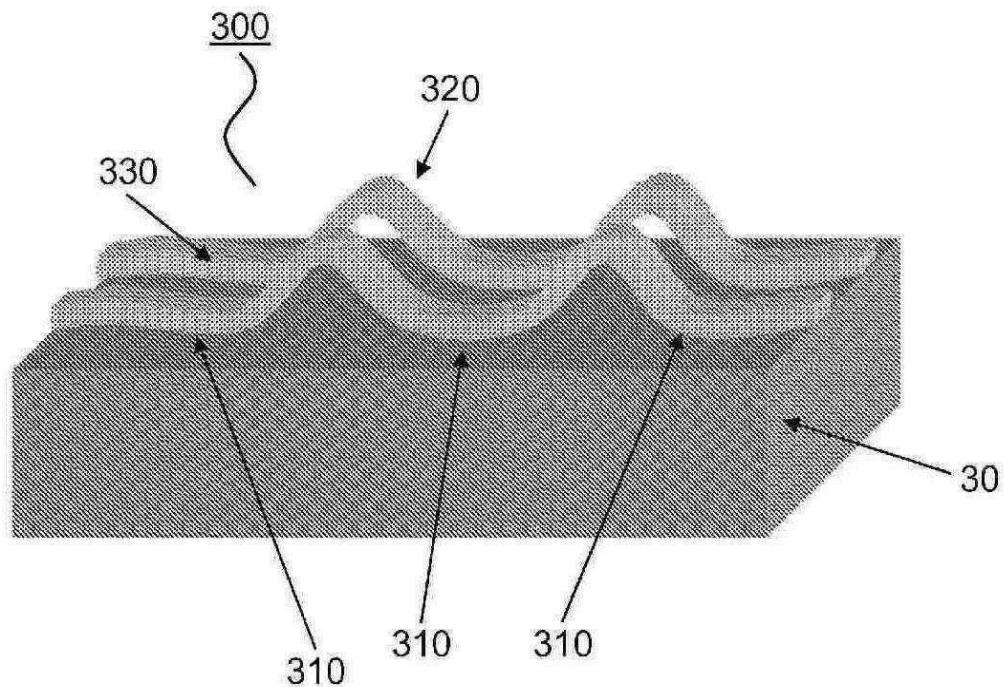

도 13은 단일 접속 그리드 구성(A 및 B), 다중 접속 (예를 들면, 이중) 그리드 구성(C), 및 꽃모양 접속 구성(D)를 갖는, 베클링되고 인장 가능한 실리콘 어레이들의 광학 현미경 이미지이다. 상기 인장 가능한 상호 접속부들은 광 다이오드, 접광/광감지 소자들, 및 다른 소자 구성 부품들을, 예를 들면, 콘택 패드 영역들에서 전기적으로 접속할 수 있다. 이들 시스템들은 곡면에 정합될 수 있다. 도 13의 A 내지 D에 나타내어진 구성들은 PDMS 기판 위에 있다.

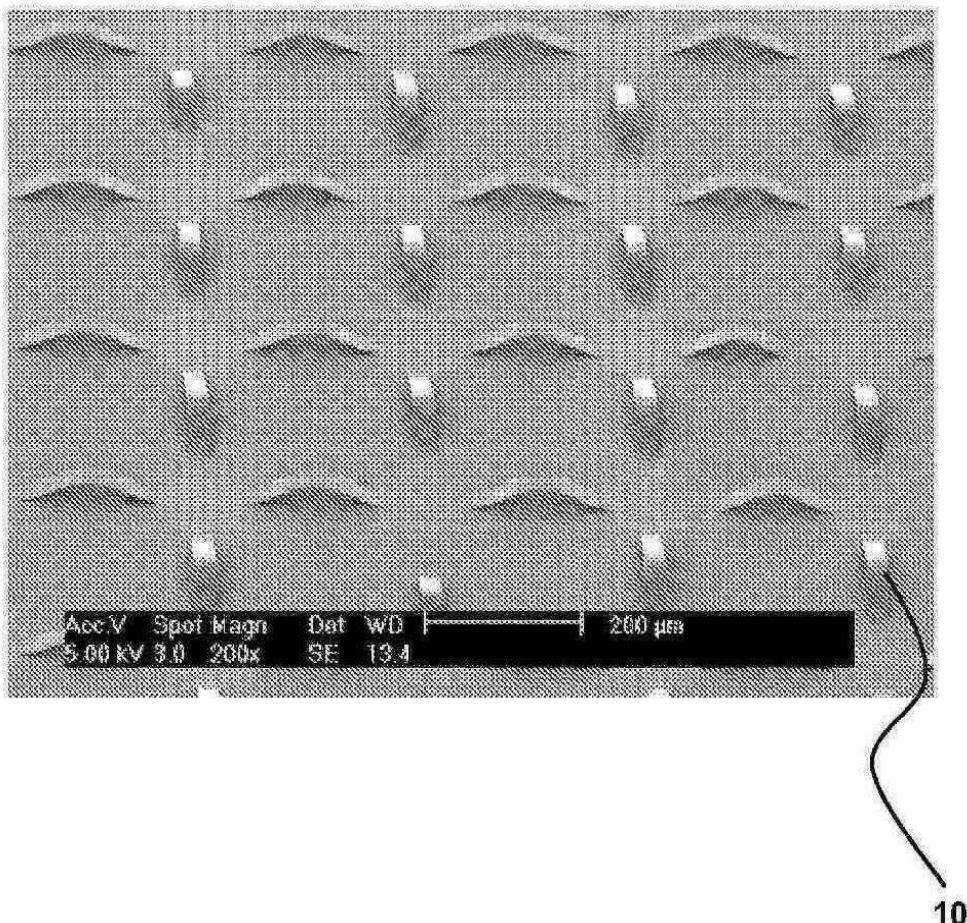

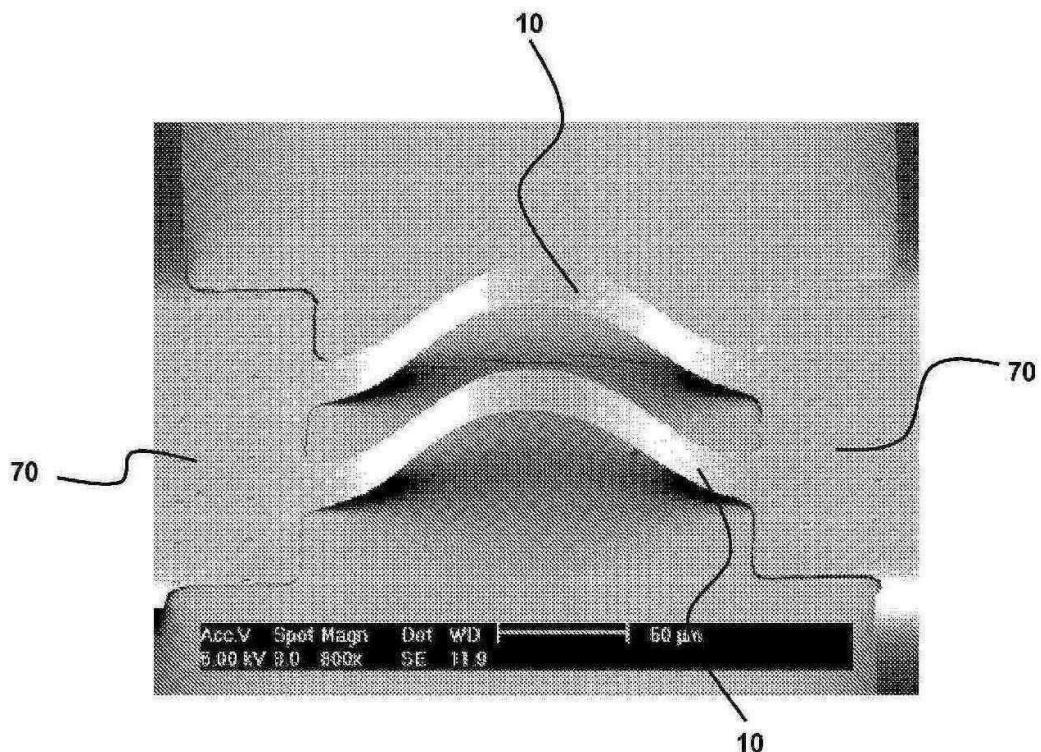

도 14는 그리드 구성의 베클링되고 인장가능한 실리콘 어레이들의 전자 현미경 이미지들이다. 상기 베클링되고 인장가능한 실리콘 어레이들은 장치 구성 부품들을 지지할 수 있고 곡면에 정합할 수 있다. 스케일 바는 A에서 200  $\mu\text{m}$ 이고 B에서 50  $\mu\text{m}$ 이다.

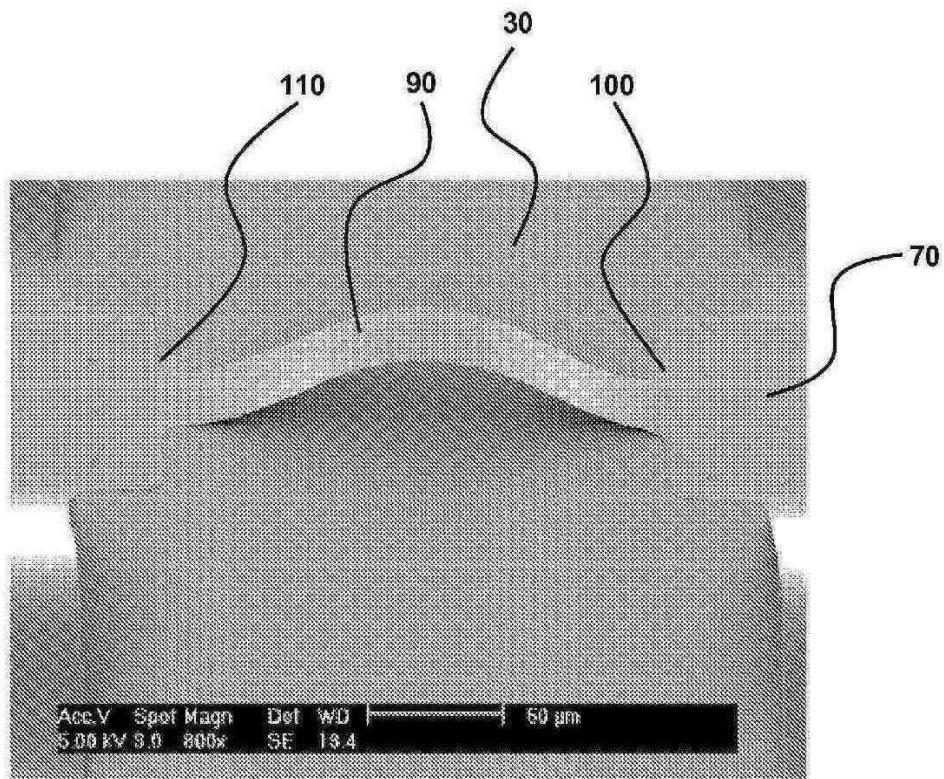

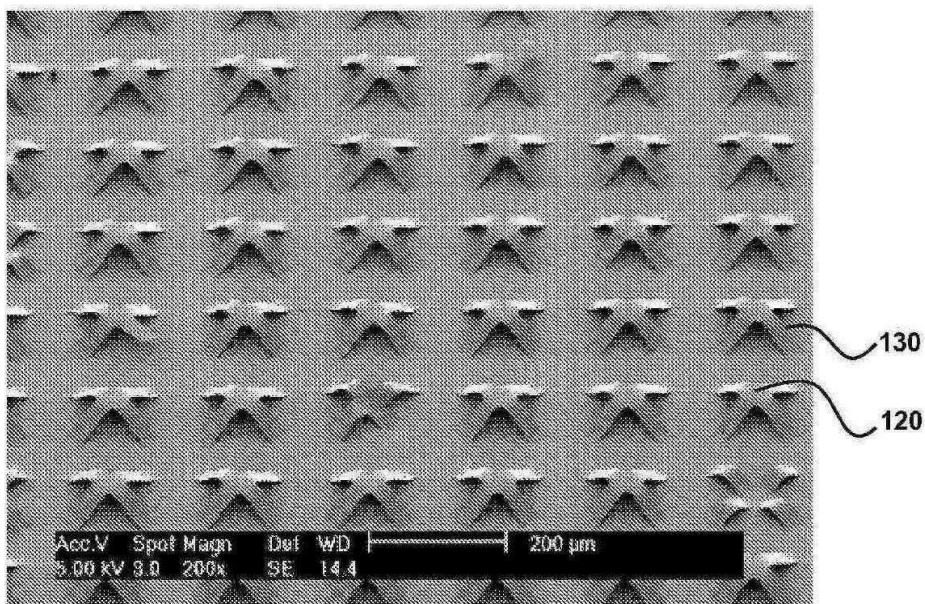

도 15는 복수의 (예를 들면 두 개의) 상호 접속부들에 의하여 서로 접속되는 이웃하는 콘택 패드들과 그리드 구성을 이루는 베클링되고 인장 가능한 실리콘 어레이들의 전자 현미경 이미지이다. 상기 베클링되고 인장가능한 실리콘 어레이들은 장치 구성 부품들을 지지할 수 있고 곡면에 정합할 수 있다. 스케일 바는 A에서 200  $\mu\text{m}$ 이고 B에서 50  $\mu\text{m}$ 이다.

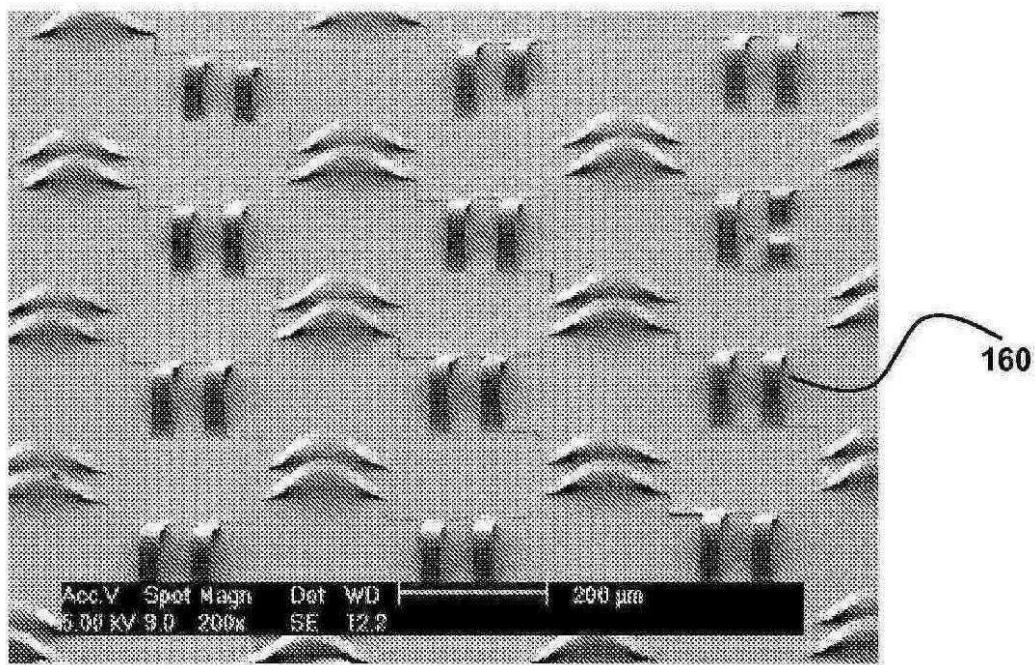

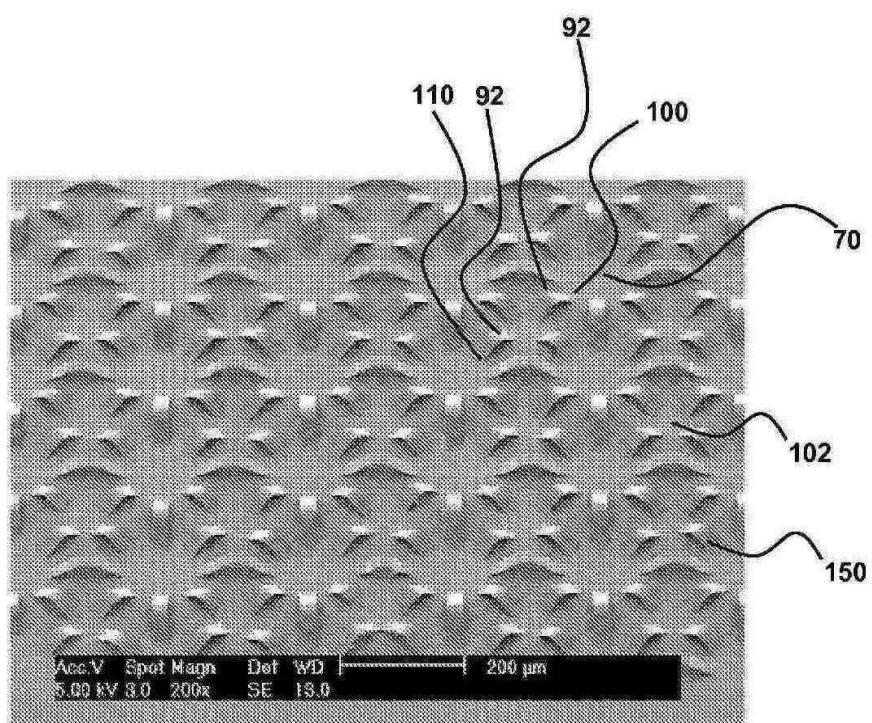

도 16은 꽃모양(floral) 구성의 베클링되고 인장가능한 실리콘 어레이들의 전자 현미경 이미지들이다. 상기 베클링되고 인장가능한 실리콘 어레이들은 장치 구성 부품들을 지지할 수 있고 곡면에 정합할 수 있다. 스케일 바는 A에서 200  $\mu\text{m}$ 이고 B에서 50  $\mu\text{m}$ 이다.

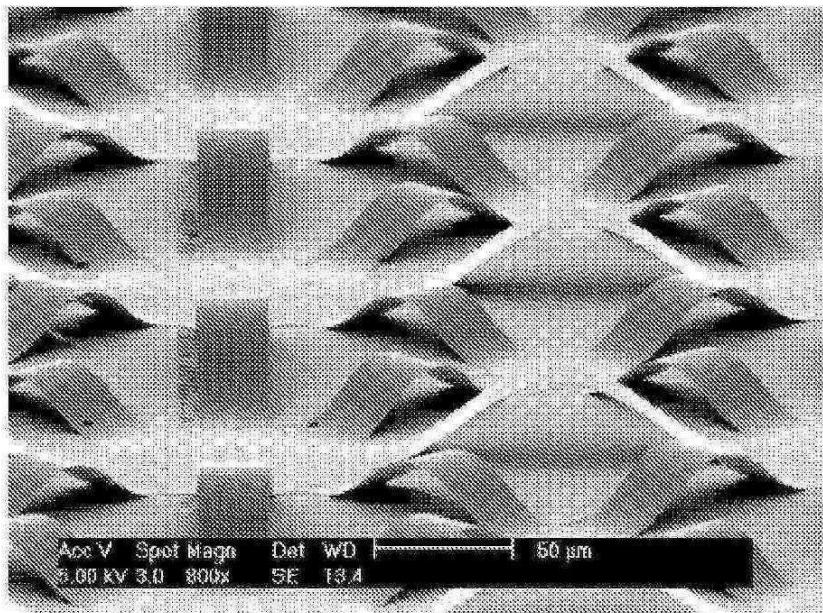

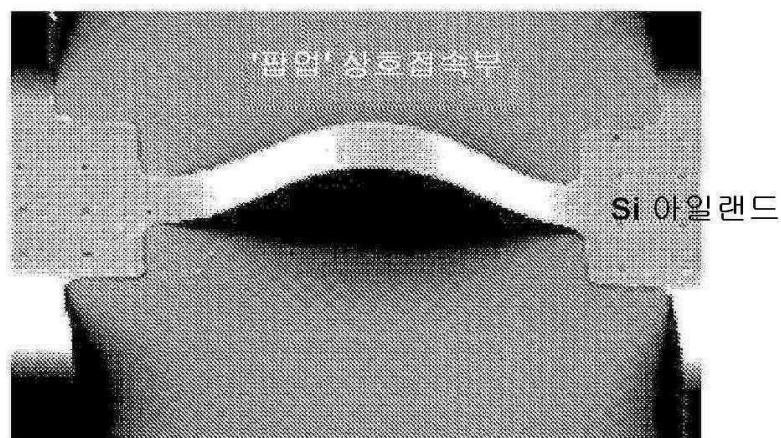

도 17은 브리지(bridge) 구성의 베클링되고 인장가능한 실리콘 어레이들의 전자 현미경 이미지들이다. 상기 베

클링되고 인장가능한 실리콘 어레이들은 장치 구성 부품들을 지지할 수 있고 곡면에 정합할 수 있다. 스케일 바는 A에서  $200 \mu\text{m}$ 이고 B에서  $50 \mu\text{m}$ 이다.

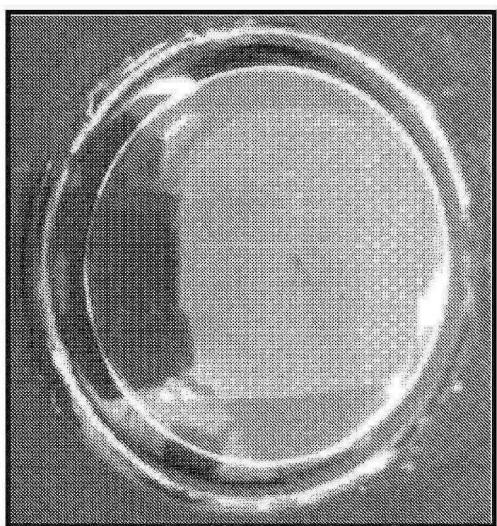

도 18은 PDMS 상의 인장 가능하고 베클링된 실리콘 어레이 위에 그리드 어레이 구성을 갖는 광 다이오드들의 사진이다.

도 19는 인장 및 릴랙스(relaxation) 동안 상기 인장 가능한 상호 접속부들의 가역적인 거동을 실증한다. 상기 시스템은 패널 1에 릴랙스된다. 상기 시스템은 패널 2, 3 및 4에 인장 화살표에 의하여 표시된 바와 같이 인장된다. 패널 4에서 최대 인장은 약 10%이고, 상기 인장력의 방향으로 정렬된 상호 접속부에 대하여는 실질적으로 편평한 상호 접속부를 초래한다. 상기 시스템은 패널 5 내지 8에서는 해제되며, 패널 8은 패널 1에 나타낸 것과 동등한 기하 구조 및 구성을 갖는다. 스케일 바는 0.2 mm이다.

도 20은 편평한 기판들뿐만 아니라 곡률을 갖는 기판들에도 정합적인(conformal) 접촉이 가능한 "베블 스템프" 또는 "풍선 스템프" 장치이다.

도 21 구면으로 굴곡진 표면과 편평한 표면에 모두 정합할 수 있는 또 다른 장치는 인장 가능한 구면-몰딩된 스템프이다. 상기 스템프는 굴곡진 표면(본 예에서는 오목한 렌즈) 위에 주조되어 제거된다. 상기 스템프는 상호 접속부들이 전사될 자신의 표면을 실질적으로 편평하게 하기 위해 인장된다.

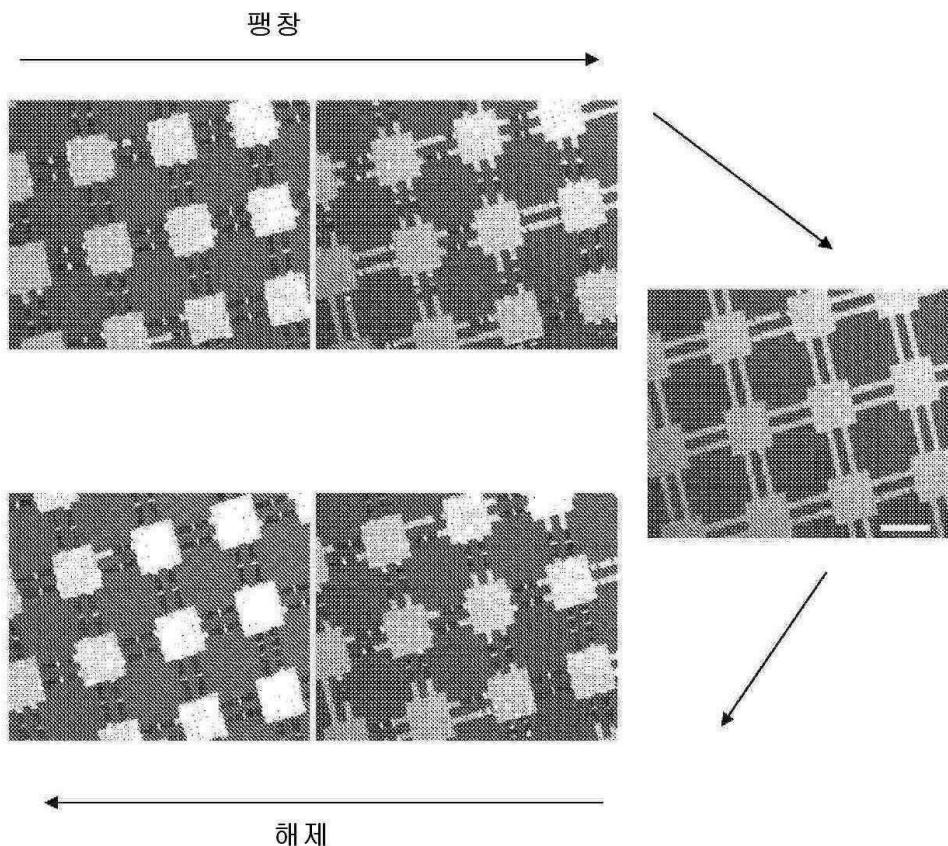

도 22는 "베블" 또는 "풍선" 스템프 위에서 인장 사이를 동안 인장될 수 있는 베클링된 실리콘 어레이들을 나타낸다. 본 실시예에서, 인접하는 콘택 패드들 사이의 상호 접속부는 두 개의 웨이브진 상호 접속부들(Si 두께  $290 \text{ nm}$ )을 포함한다. 인장 테스트는 여러 방향으로의 인장을 제공하기 위하여 베블 팽창을 이용한다. 가장 오른쪽의 패널은 최대로 인장된 상태이며, 하부의 두 패널들은 인장력이 제거되었을 때, 상기 상호접속부들이 릴랙스되어 위의 왼쪽 패널에 나타낸 사전 인장된 구성을 돌아가는 것을 보여 준다.

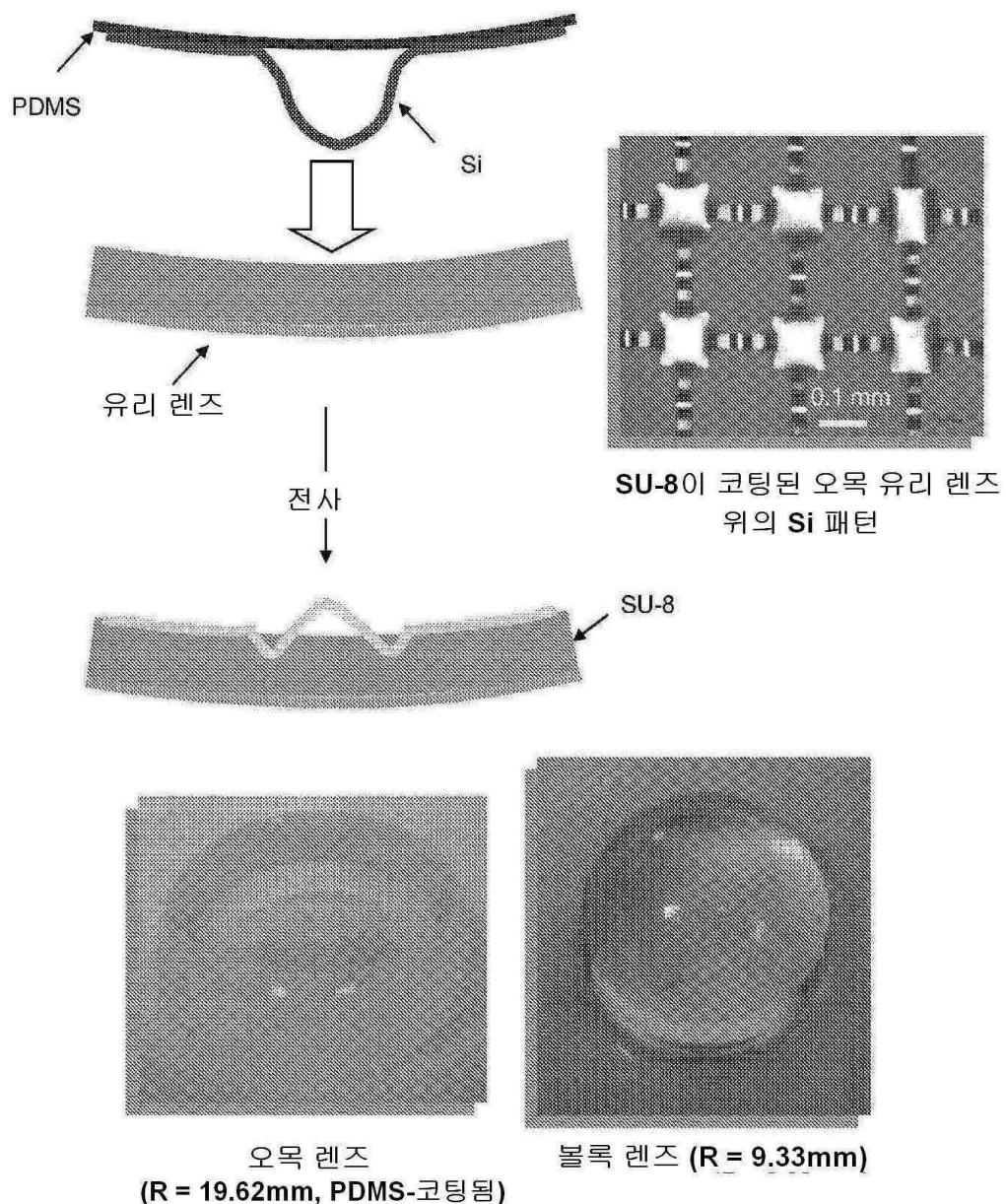

도 23은 풍선 스템프를 통해 접착제(PDMS 또는 SU-8)가 코팅된 유리 렌즈들 위로 프린트되는 실리콘을 나타낸다.

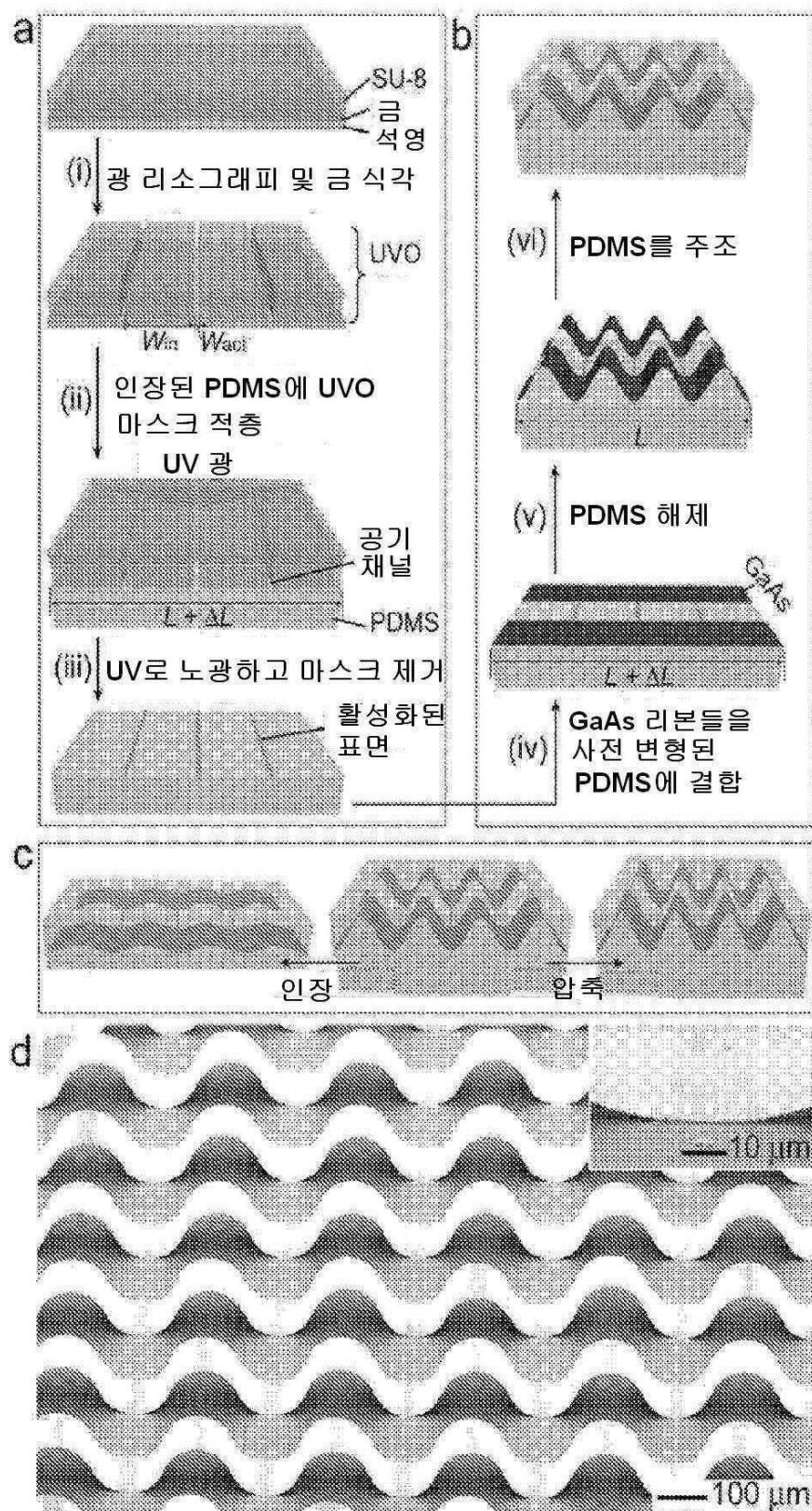

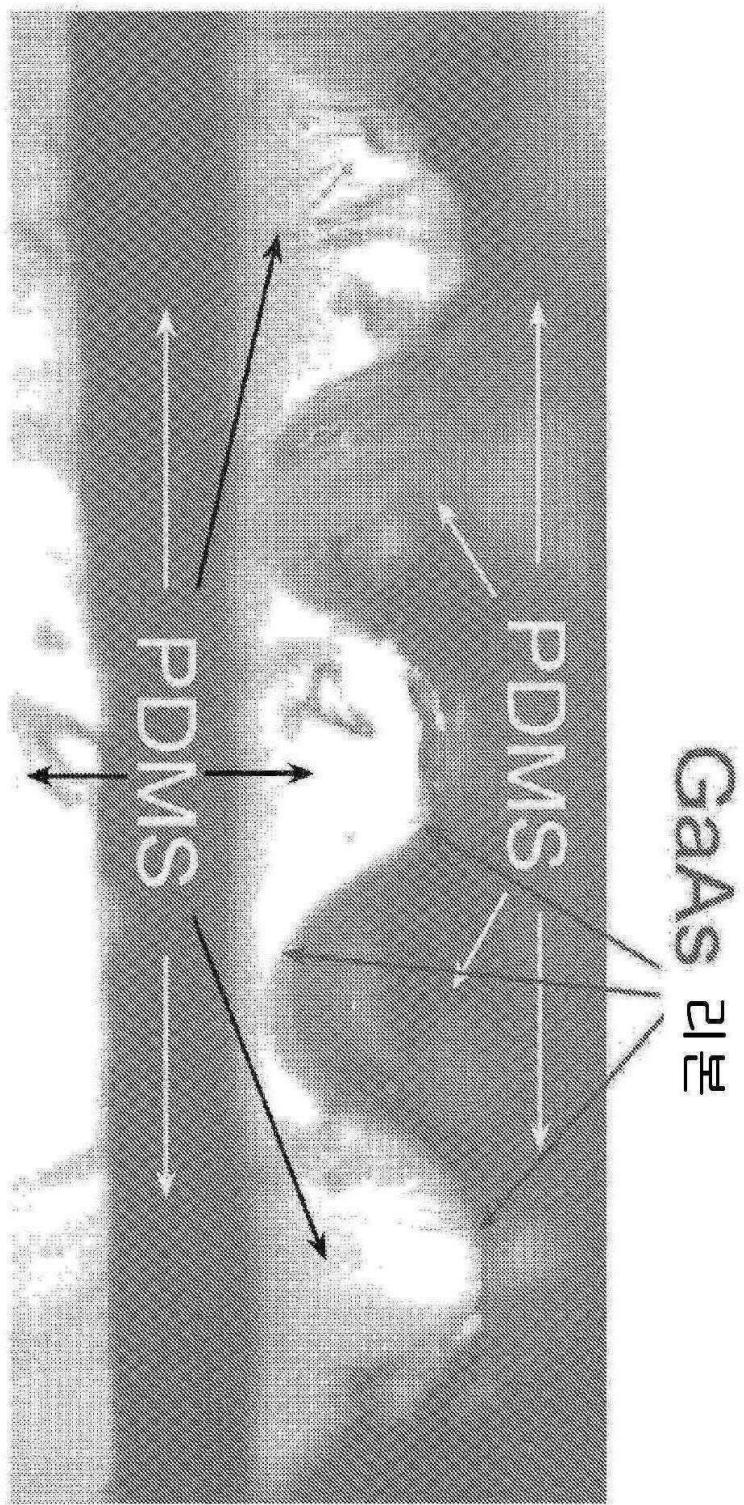

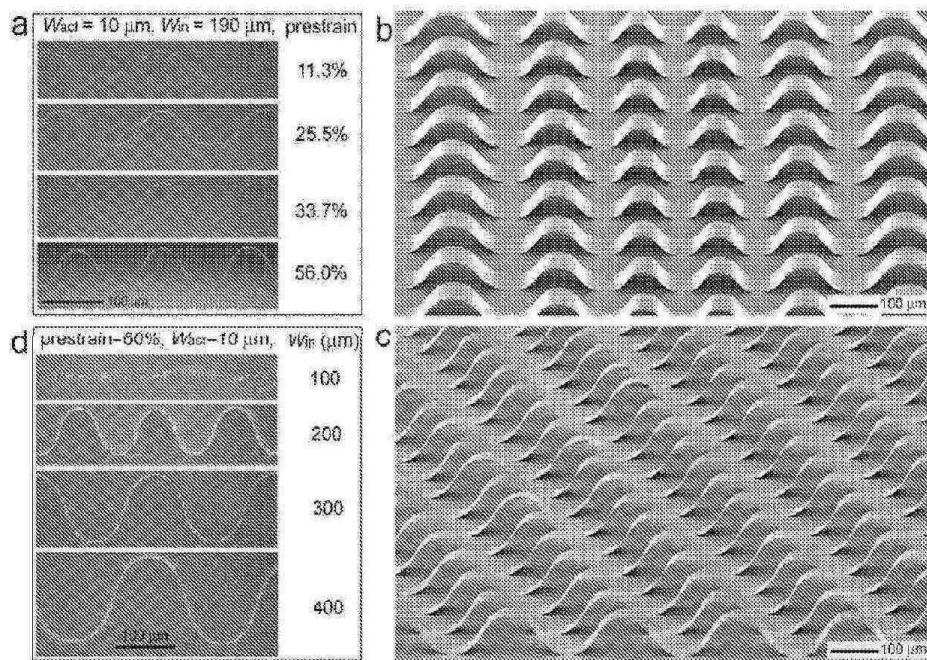

도 24는 반도체 나노리본들 내의 3D 베클링된 모양들을 제조하기 위한 공정 단계들을 요약한다. A는 UV-O 마스크를 제조하고, 이를 이용하여 PDMS 기판 위에 표면 화학을 패터닝하기 위해 사용하는 것을 나타낸다. B는 베클링된 GaAs 리본들을 형성하고 이들을 PDMS 내에 내장(embed)시키는 것을 나타낸다. C는 인장 및 압축에 대한 베클링된 GaAs의 응답을 나타낸다. D는 a 및 b에서의 절차들을 사용하여 형성된 샘플의 SEM 이미지이다. 본 샘플을 제조하기 위하여 사용된 사전 변형을 60%이었으며,  $W_{act} = 10 \mu\text{m}$ , 그리고  $W_{in} = 400 \mu\text{m}$ 이었다.

도 25는 PDMS 기판들 위에 33.7%의 사전 변형과 (A)  $W_{act} = 10 \mu\text{m}$ , 그리고  $W_{in} = 190 \mu\text{m}$ ; 및 (B)  $W_{act} = 100 \mu\text{m}$ , 그리고  $W_{in} = 100 \mu\text{m}$ 을 이용하여 형성된 베클링의 프로파일들의 측면도이다. 두 샘플들은 모두 리본들이 PDMS로부터 탈착됨에 기인하는 비활성화된 영역들의 베클링들을 나타낸다. 작은 피크들을 갖는 사인파들은  $W_{act} = 100 \mu\text{m}$ 을 갖는 활성화된 영역들에서만 형성되었다. 이들 두 샘플들의 비교는  $W_{act}$ 를 임계값보다 작게 선택함으로써 작은 웨이브의 구조가 형성되는 것을 피할 수 있음을 나타낸다.

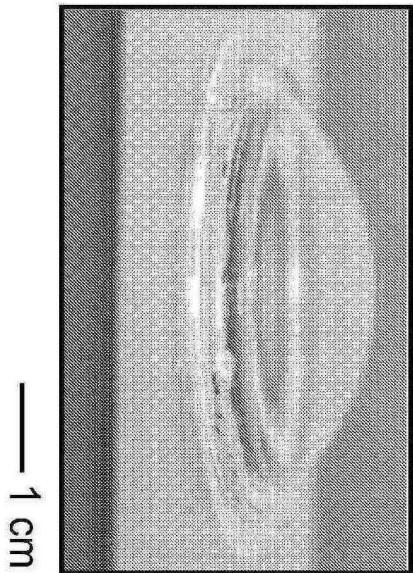

도 26은 PDMS 내에 내장된 베클링된 GaAs 리본을 마이크로토밍(microtoming)한 후의 측면 이미지이다. 본 이미지는 PDMS가 리본들과 그 하부에 놓인 기판들 사이의 갭을 완전히 채우고 있음을 보여준다. 이 경우에 있어서, 상기 베클링들은 60%의 사전변형과  $W_{act} = 10 \mu\text{m}$ , 그리고  $W_{in} = 300 \mu\text{m}$ 에 대하여 형성되었다. 이들 베클링된 리본들의 표면 위에 주조된 PDMS 프리폴리머는  $65^\circ\text{C}$ 의 오븐에서 4시간 동안 경화된다.

도 27은 베클링된 (A 및 D) GaAs와 (B, C) Si 리본들의 측면 프로파일들의 광학 현미경 사진이다. A는 상이한 사전 변형(11.3%, 25.5%, 33.7% 및 56.0% (위에서 아래로))과  $W_{act} = 10 \mu\text{m}$ , 그리고  $W_{in} = 190 \mu\text{m}$ 에 대하여 패터닝된 PDMS 위에 형성된 GaAs 리본 구조물들이다.  $\varepsilon_{pre} = 33.7\%$  및 56.0%에 대한 점선들은 수학적으로 예측된 상호 접속부 기하 형태이다. B는 50%로 사전 변형되고,  $W_{act} = 15 \mu\text{m}$ , 그리고  $W_{in} = 350, 300, 250, 250, 300$ , 및  $350 \mu\text{m}$ (왼쪽에서 오른쪽)에 대하여 패터닝된 PDMS 기판 위에 형성된 Si 리본 구조물들이다. 본 이미지는 샘플을  $45^\circ$  기울여서 촬영되었다. C는 50% 사전 변형되고, 리본의 길이 방향에 대하여  $30^\circ$ 의 각도로 방향을 갖는 접착 위치들( $W_{act} = 15 \mu\text{m}$ , 그리고  $W_{in} = 250 \mu\text{m}$ )과 평행한 선들로 패터닝된 PDMS 기판 위에 형성된 Si 리본 구조물들이다. 본 이미지는 샘플을  $75^\circ$  기울여서 촬영되었다. D는 60% 사전 변형되고  $W_{act} = 10 \mu\text{m}$ 이며 상이한  $W_{in}$

= 100, 200, 300, 및 400  $\mu\text{m}$ (위에서 아래로)에 대한 PDMS 기판 위에 형성된 GaAs 리본 구조물들이다.

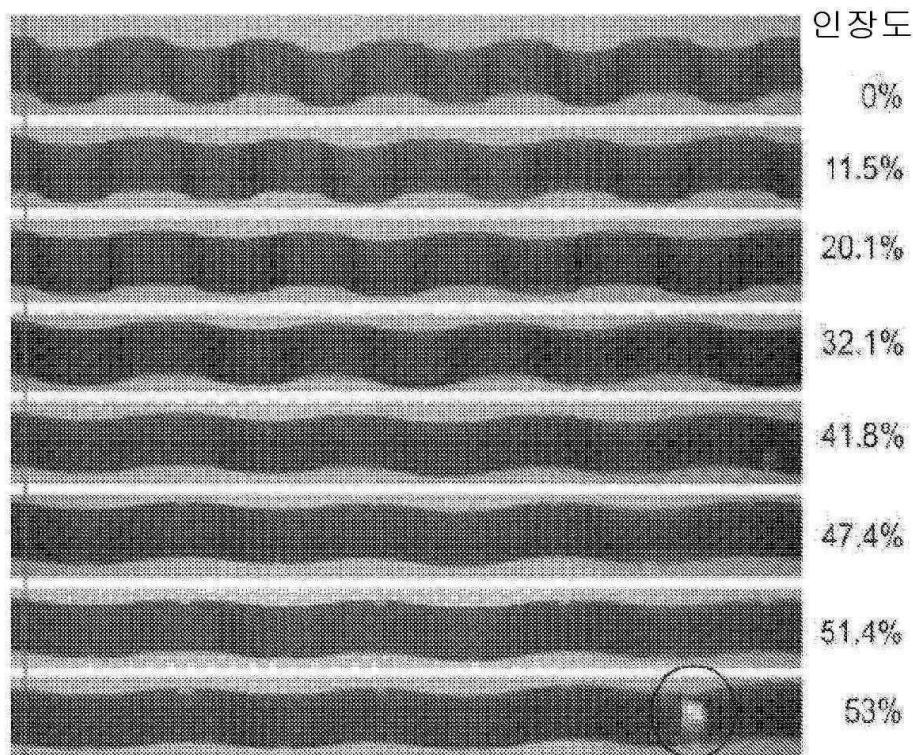

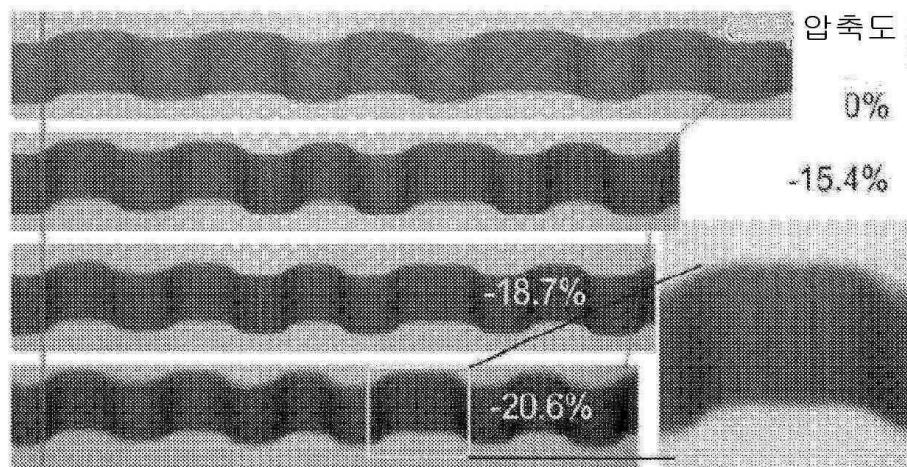

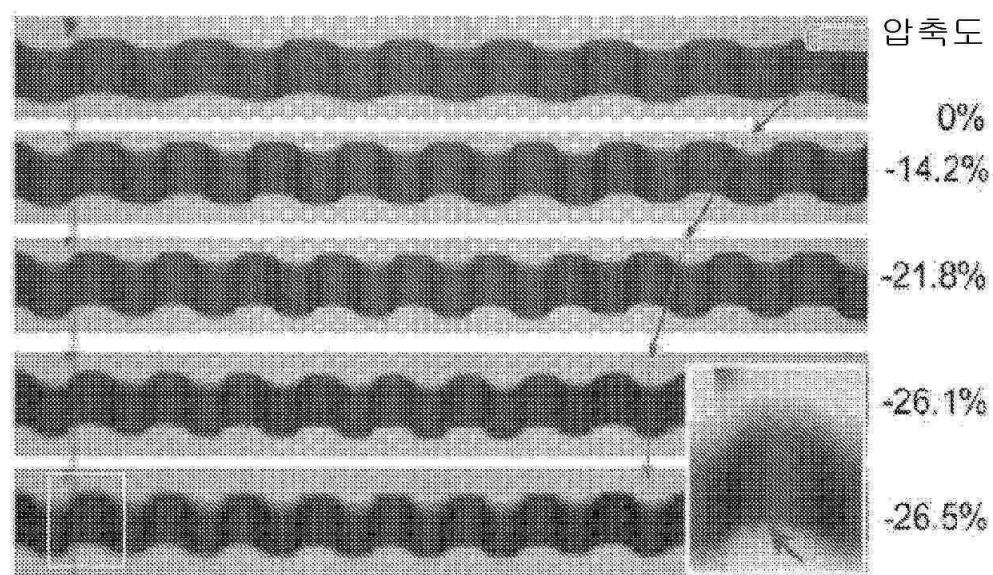

도 28은 PDMS 내에 내장된 베클링된 GaAs 리본들의 인장 및 압축을 나타낸다. A는 상이한 수준의 인장 변형(양의 %)만큼 인장된 단일 베클링 리본의 이미지이다. 거의 50% 파괴가 발생한다. B는 상이한 수준의 압축 변형(음의 %)만큼 압축된 단일 베클링 리본의 이미지이다. ~-15%보다 큰 압축 변형에 대하여 베클링들의 피크에 작고, 짧은 주기를 갖는 웨이브의 기하구조들이 나타난다. C는 상이한 수준의 압축 변형으로 압축된 단일 베클링 리본의 이미지이다. 이들 경우에 있어서 상기 베클링들은 60%의 사전 변형과,  $W_{act} = 10 \mu\text{m}$ , 그리고  $W_{in} = 400 \mu\text{m}$ (A, B) 그리고  $W_{act} = 10 \mu\text{m}$ , 그리고  $W_{in} = 300 \mu\text{m}$ (C)에 대하여 형성되었다. 각 패널에서의 적색선과 화살표들은 기계적인 변형을 강조하기 위하여 동일한 리본들 위의 동일한 위치들을 표시한다. 삽입 사진들은 흰색상자로 표시한 부분의 확대 이미지를 제공하며 고압축 변형들에서의 크랙들의 발생을 명확하게 보여준다. 인장 및 압축도에 대응되는 숫자들은 하기 식에 따라 계산되었다.

$$\left| \frac{L_{projected}^{\max} - L_{projected}^0}{L_{projected}^0} \right| * 100\%$$

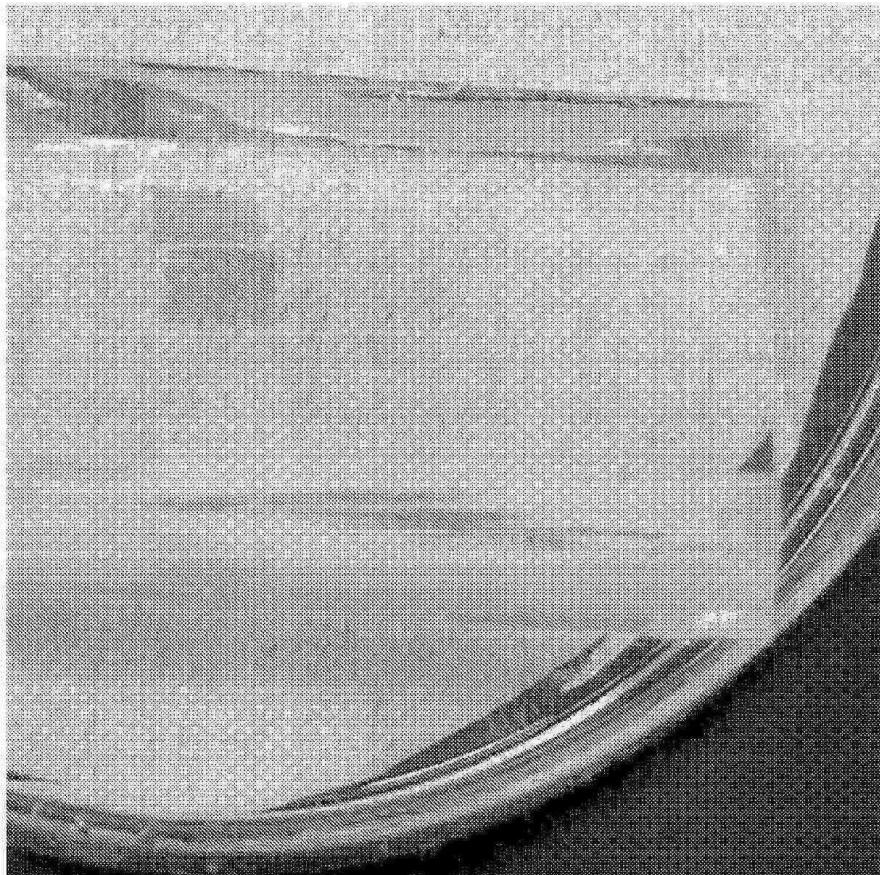

도 29는 2층의 베클링된 GaAs 리본 어레이를 갖는 샘플의 사진이다. 본 구조는 순차 적층(layer by layer) 방식으로 제조된다. GaAs 리본의 제 1 층(60%의 사전 변형과,  $W_{act} = 10 \mu\text{m}$ , 그리고  $W_{in} = 400 \mu\text{m}$ 로 정의된 베클링된 기하 구조)은 PDMS 내에 내장된다. 베클링된 리본들의 제 2 층은 50%의 사전 변형과  $W_{act} = 10 \mu\text{m}$ , 그리고  $W_{in} = 300 \mu\text{m}$ 를 이용하여 이 기판의 표면 위에 형성된다.

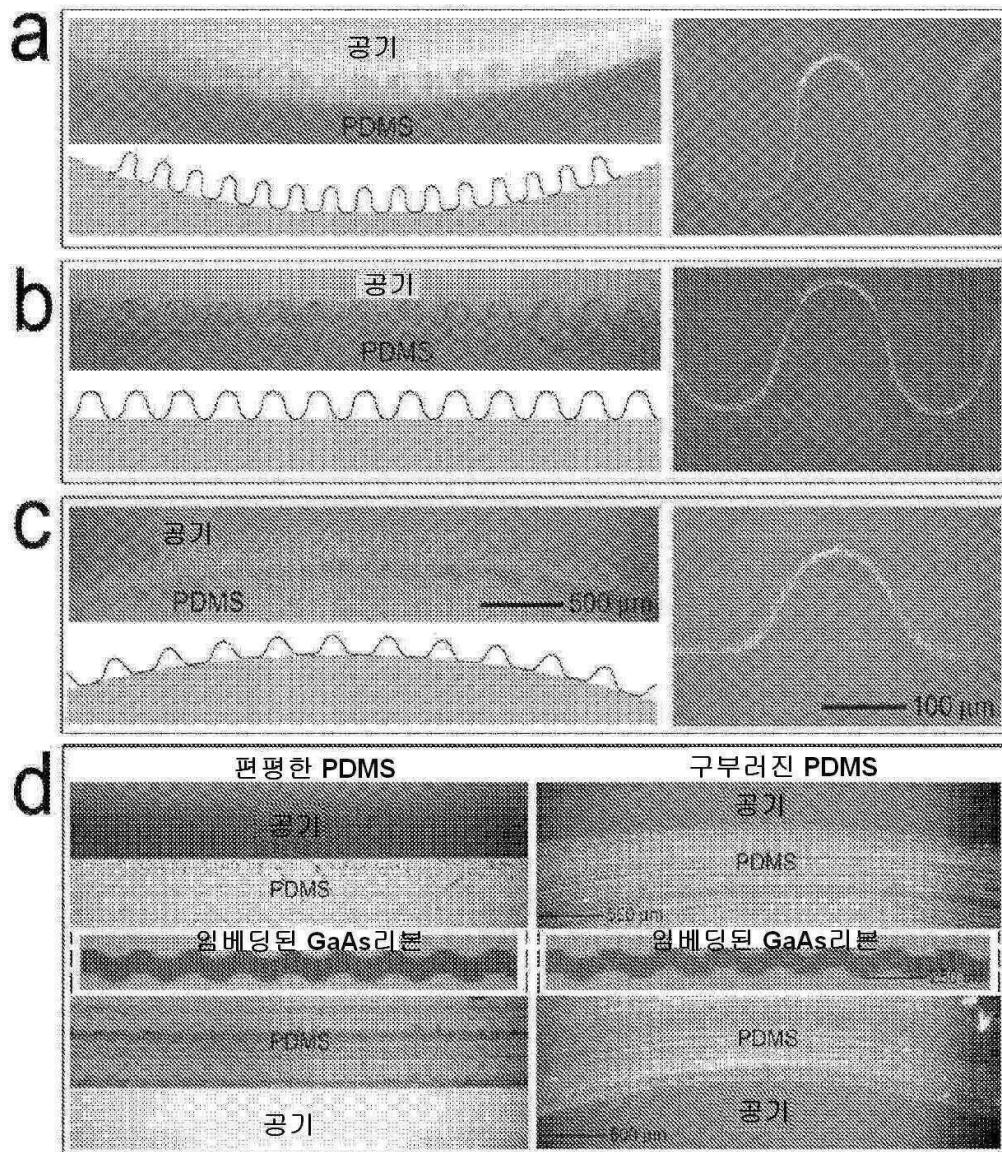

도 30은 PDMS의 표면들 위와 매트릭스 내의 베클링된 리본들의 구부림을 나타낸다. A-C는 오목하거나(A), 편평하거나(B) 또는 볼록한(C)의 표면들을 갖는 PDMS 위에 있는 베클링된 GaAs 리본들의 낮은 배율(왼쪽 위쪽 프레임) 및 고배율(오른쪽 프레임), 그리고 개략도(왼쪽 아래 프레임)의 광학 현미경 이미지들이다. c에 있는 스케일바는 a 및 b에도 적용된다. d는 (왼쪽) 구부리기 전의 그리고 (오른쪽) 구부린 후의 PDMS 내에 내장된 베클링된 리본들의 이미지들이다. 오른쪽 이미지에 있는 스케일바는 왼쪽 이미지들에도 적용된다. 베클링된 상기 리본들은 60%의 사전 변형과  $W_{act} = 10 \mu\text{m}$ , 그리고  $W_{in} = 400 \mu\text{m}$ 로 형성되었다.

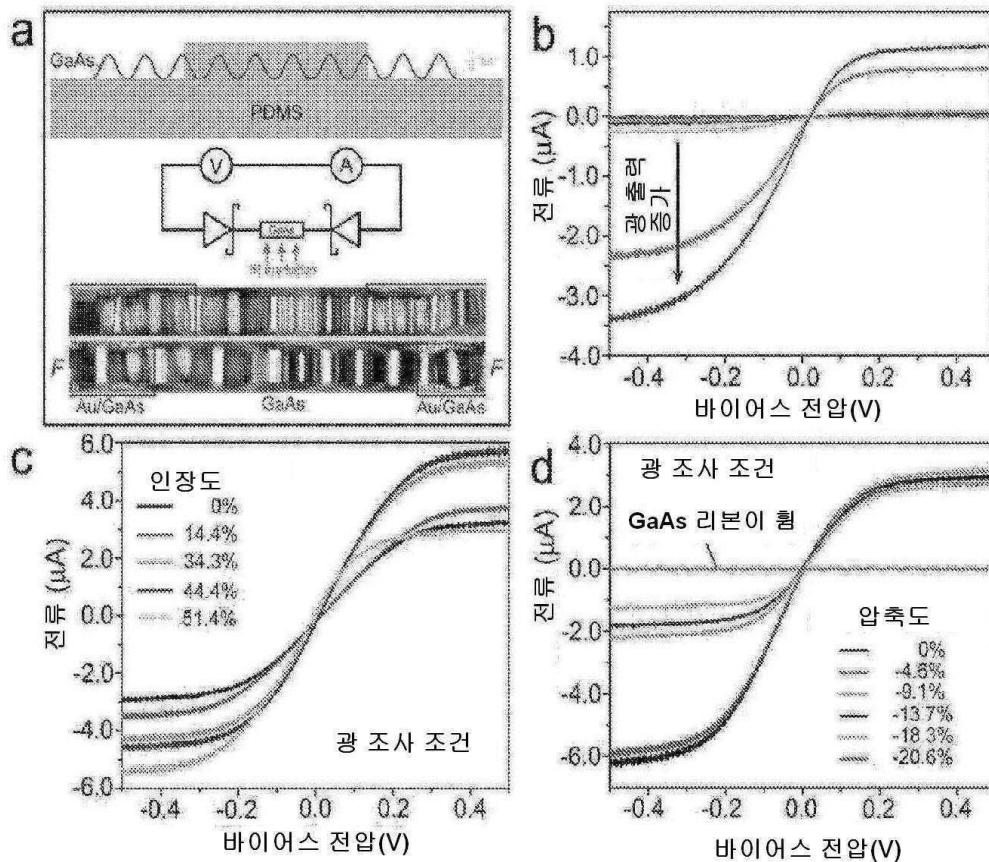

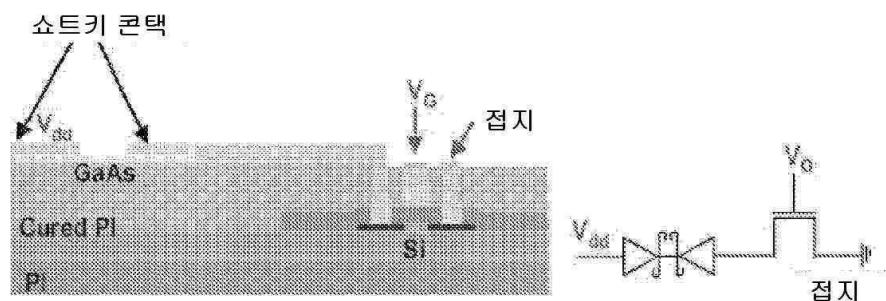

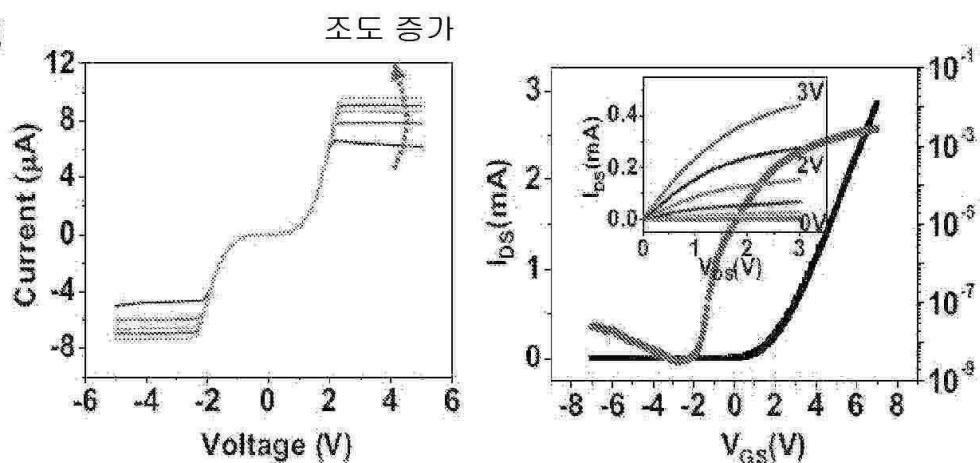

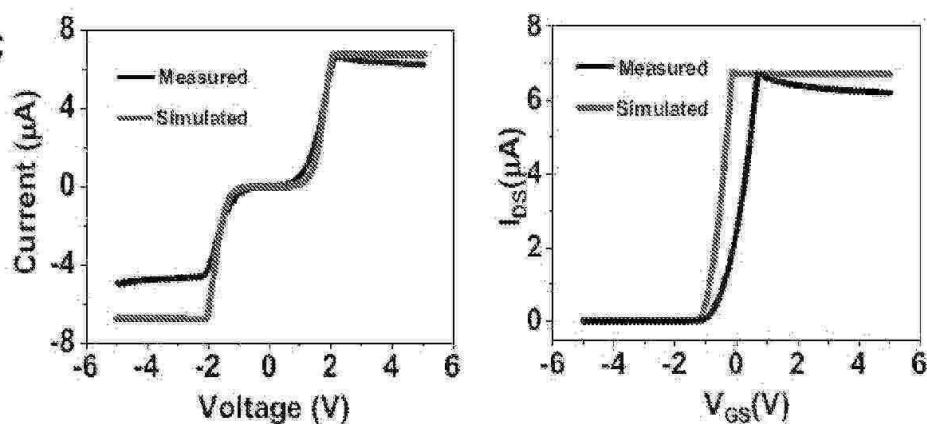

도 31은 인장 가능한 금속-반도체-금속 광 감지기(MSM PDs: metal-semiconductor-metal photodetectors)를 특성화한 것이다. A는 기하 구조를 개념적으로 도시한 것(위), 동등한 회로(중간), 및 인장하기 전과 인장된 동안의 베클링된 PD의 광학 이미지(아래)이다. B는 상이한 출력 세기를 갖는 IR 램프에 의하여 조사된 베클링된 PD로부터 기록된 전류(I)-전압(V) 곡선들이다. 일정한 회도로 조사된 PD가 상이한 정도로 인장되거나(C) 또는 압축되었을 때(D)의 I-V 특성들이다.

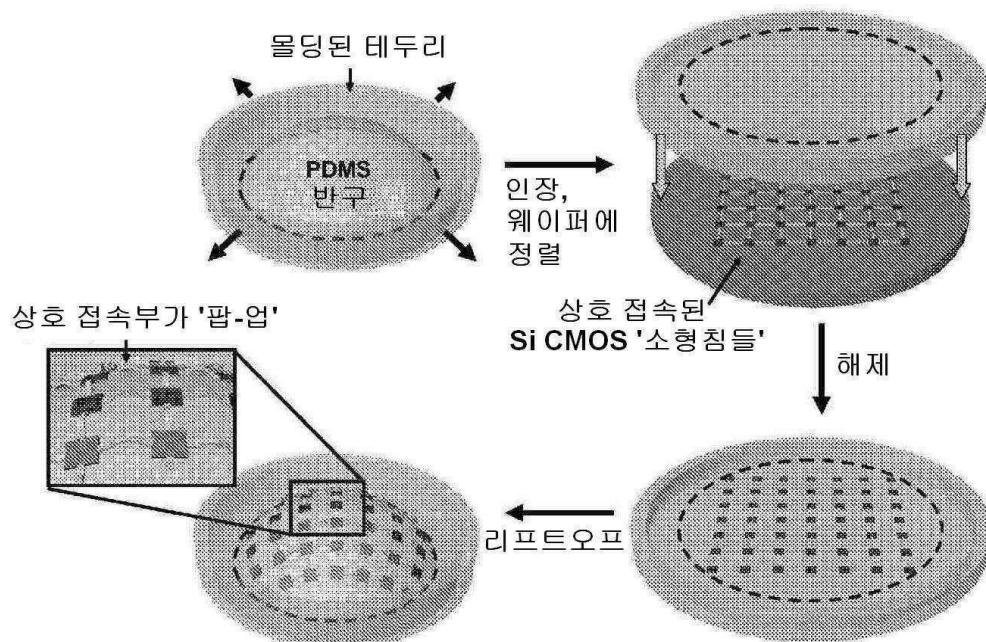

도 32는 반구형 엘라스토머 전사 '스탬프'가 통상의 웨이퍼로부터 상호 연결된 Si CMOS '칩렛(chiplet)'들을 리프트오프(liftoff) 시키고, 그 후 그들의 기하 구조를 반구형 모양으로 전환할 수 있음을 나타낸다. 상기 칩렛들 사이의 '팝-업' 상호 접속부들은 이러한 평면으로부터 곡면으로의 전환과 관련된 변형들을 수용한다.

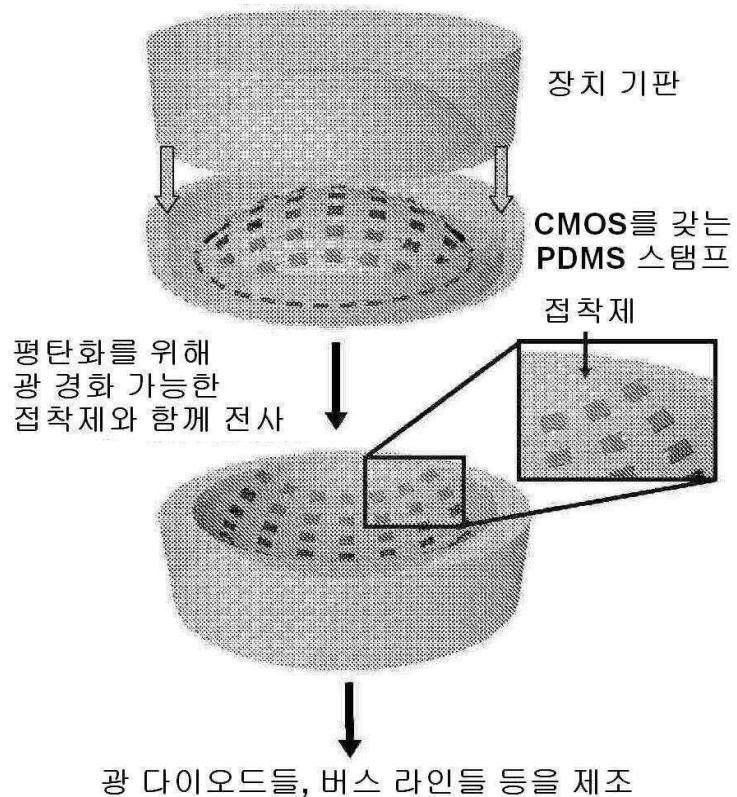

도 33은 상호 접속된 CMOS 칩렛들을 반구형 스탬프로부터, 그에 매치되는 반구형 장치 기판으로 전사하는 것을 나타낸다. 광 경화성 접착층이 상기 CMOS를 장치 기판에 결합하며, 상기 표면을 평탄화한다.

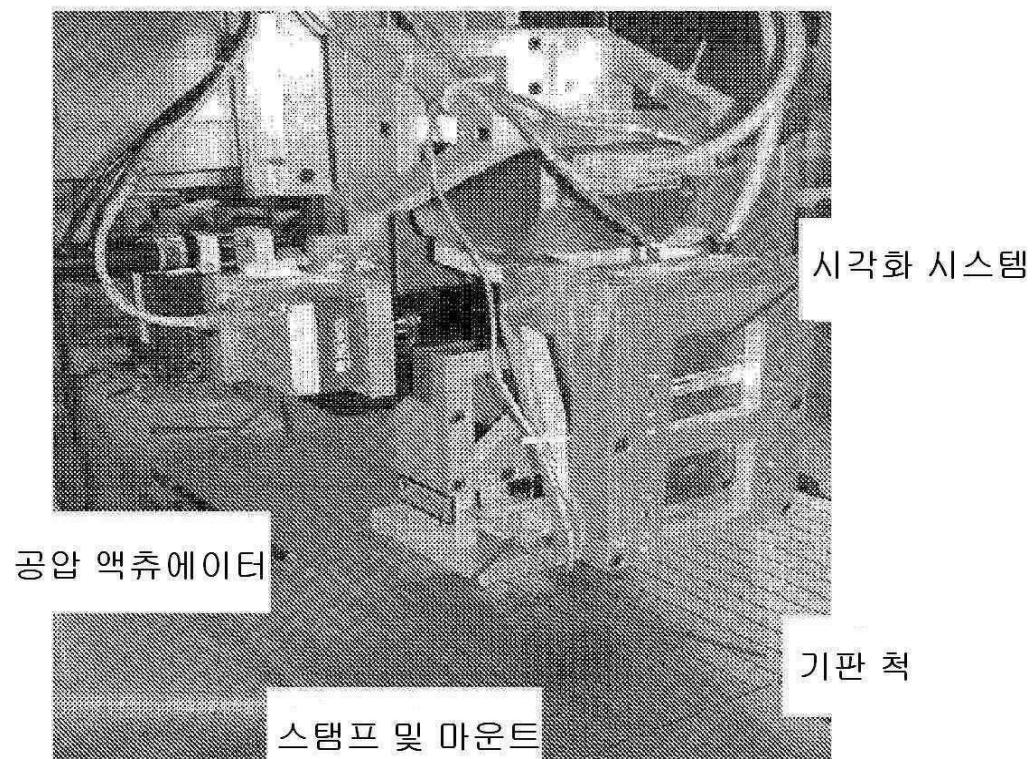

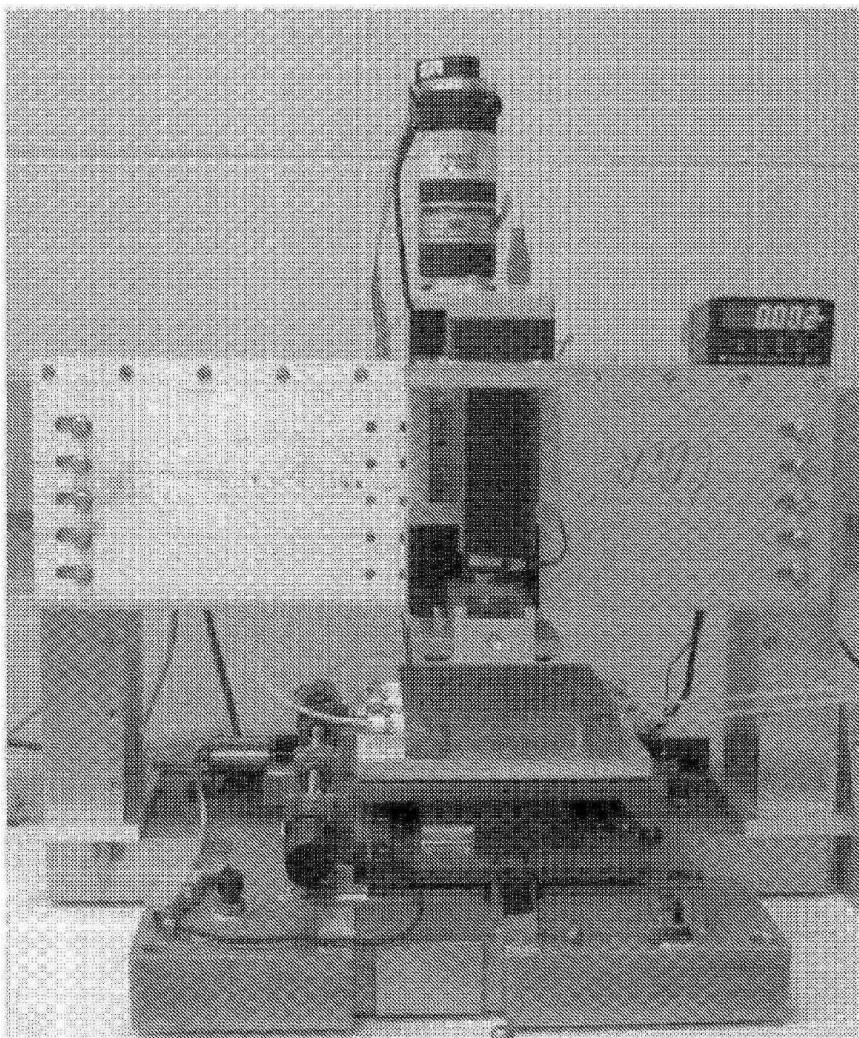

도 34는 반구형 스탬프와 양립 가능한 고정물(fixturing), 액츄에이터 및 시각화 시스템을 갖는 프린터 장치를 나타낸다.

도 35는 반구형 스탬프 위의, '팝업' 리본 상호 접속부들에 의하여 전기적으로 연결되는 단결정 실리콘 아일랜드들의 압축 가능한 어레이를 나타낸다.

도 36은 ~ 2 cm의 곡률 반경을 갖는 반구형 스탬프의 표면 위로 '링크된' 상호 접속된 단결정 실리콘 아일랜드 어레이의 광학 이미지이다.

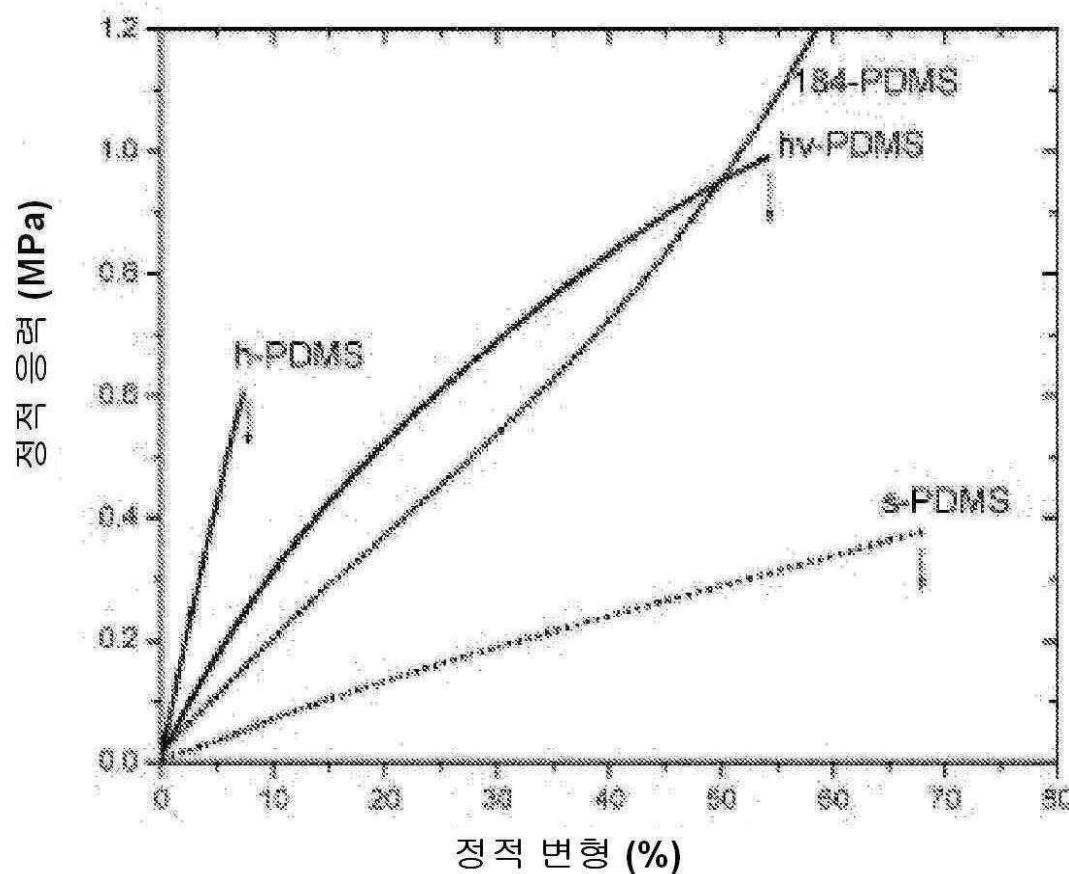

도 37은 반구형 스탬프들에 대하여 사용될 수 있는 다양한 실리콘 엘라스토머에 대한 응력/변형 곡선들이다. 20% 미만의 변형에 대하여 선형이며, 완전히 탄성인 응답들이 중요하다.

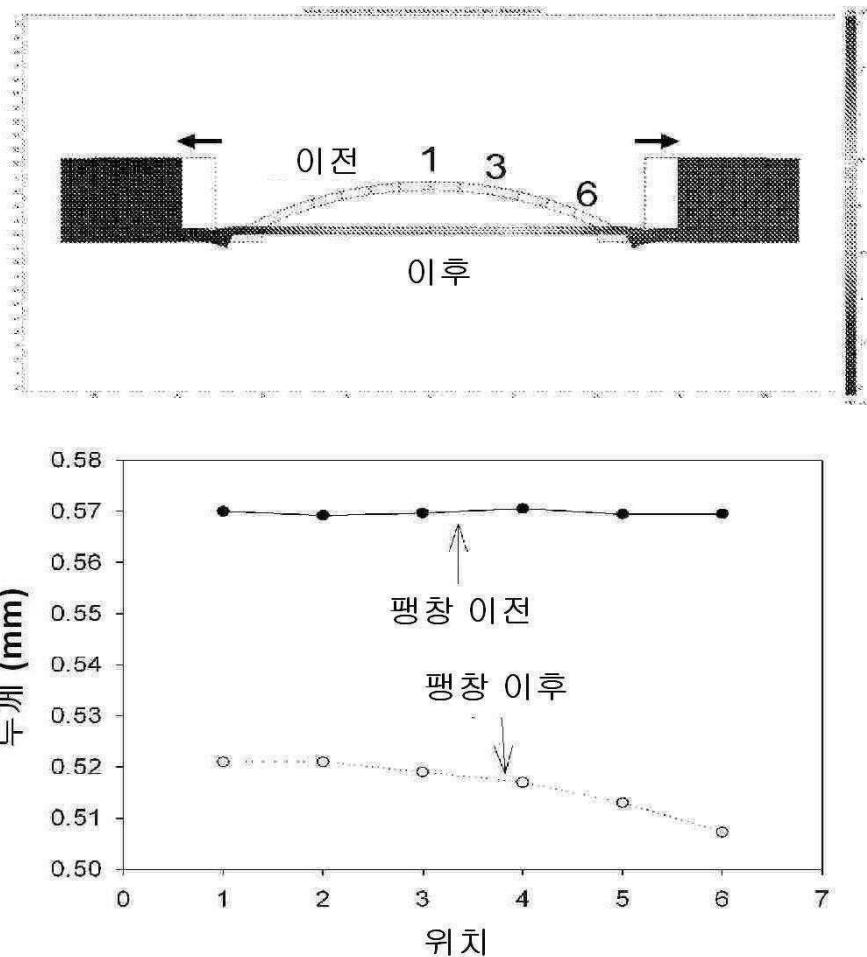

도 38은 초기에 0.57 mm의 균일한 두께를 갖는 반구형 스탬프에서의 구형으로부터 평면으로의 변환을 유한 요소 모델링한 것이다.

도 39는 탄성 지지체 위의 2차원의 "웨이브진" 반도체 나노막을 제조하기 위한 단계들을 개념적으로 나타낸 것이다.

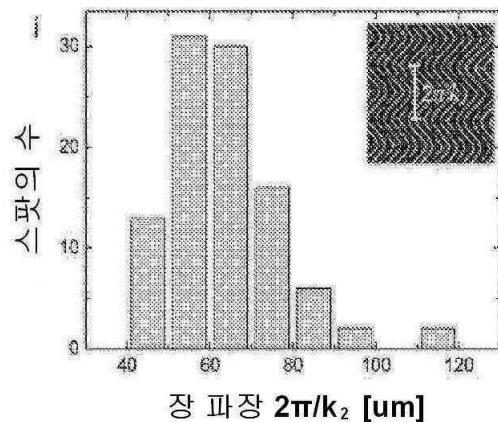

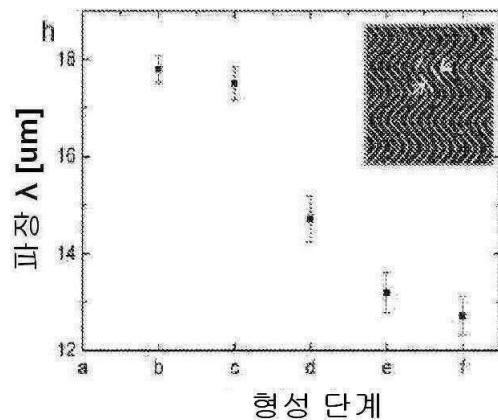

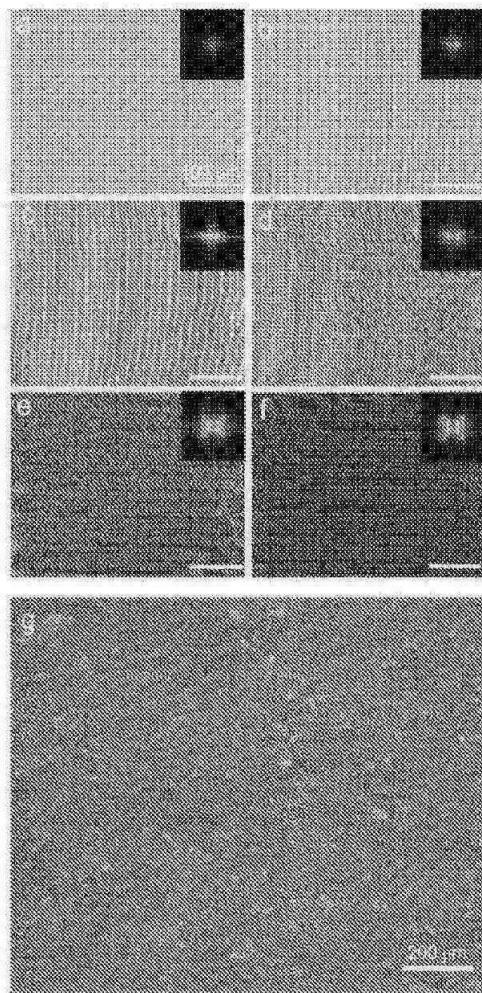

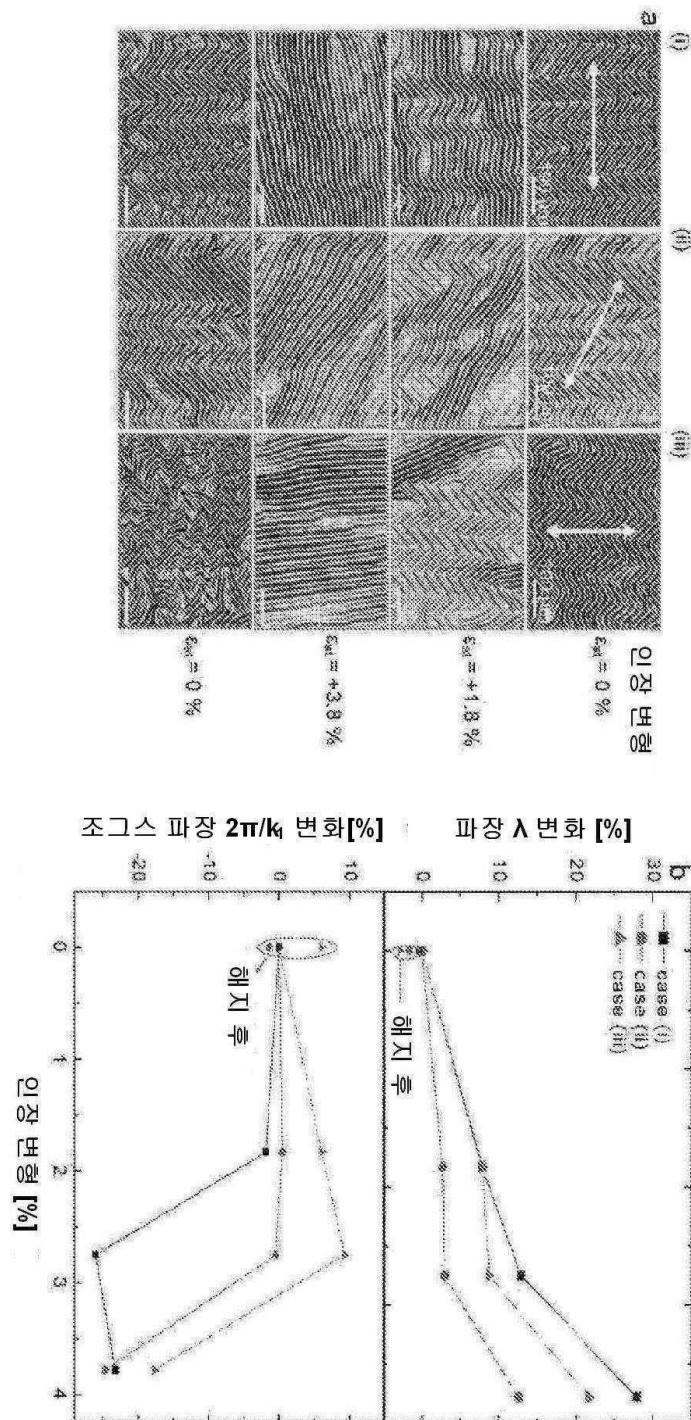

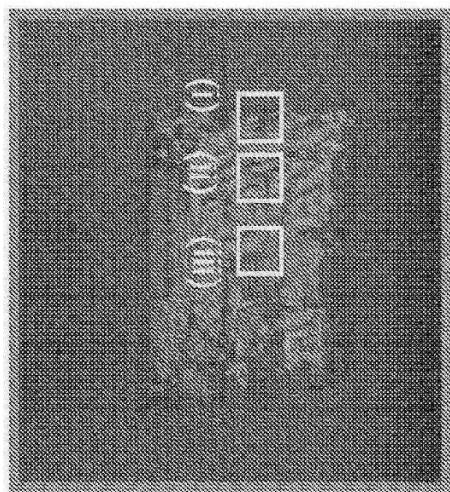

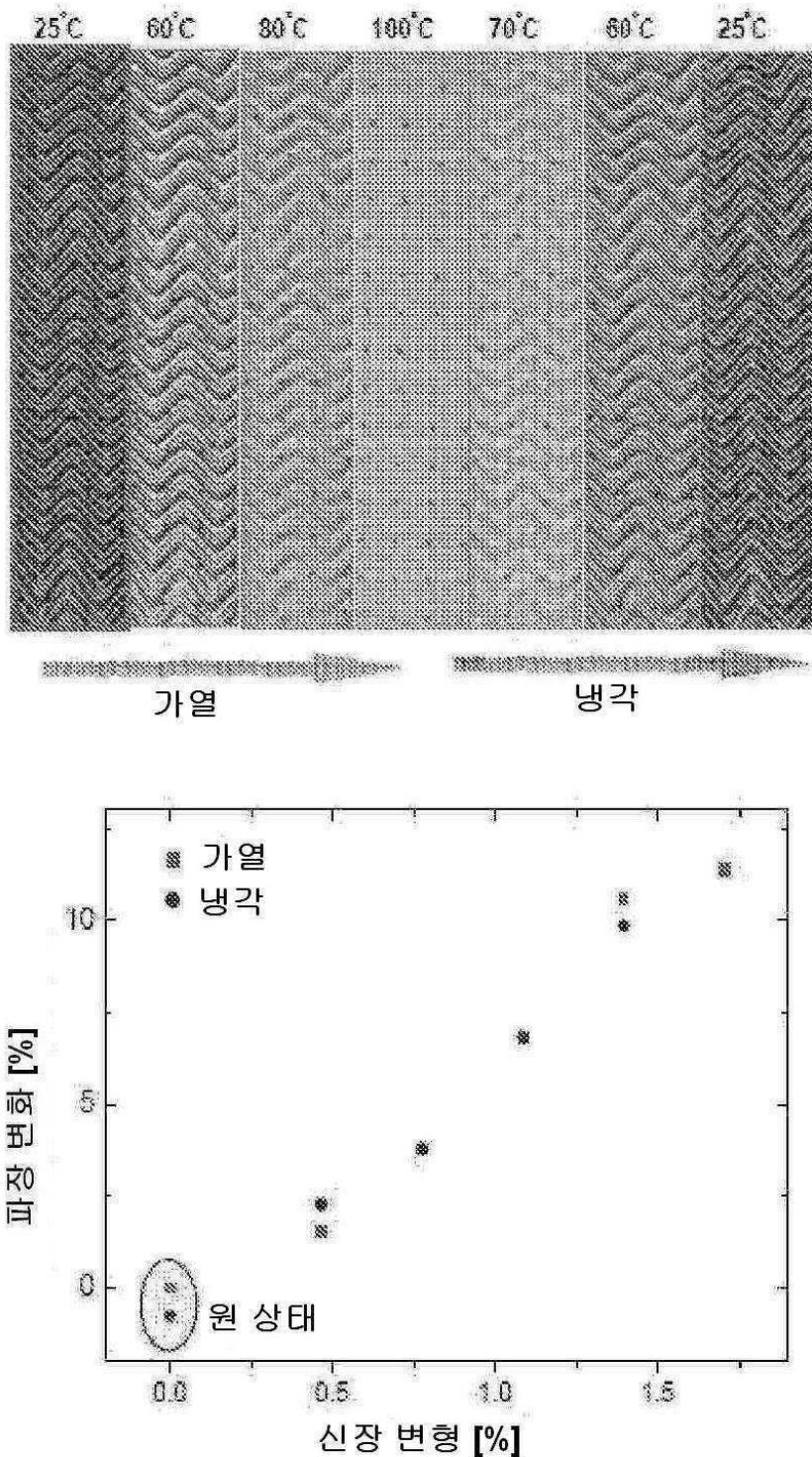

도 40의 (a 내지 f)는 실리콘 나노막들을 형성하는 과정에서 다양한 단계들에서의 2D 웨이브진 구조물들의 광학 현미경 사진들이다. 삽입 사진들은 2차원 파워 스펙트럼들을 보여 준다. (g)는 완전히 발전된 구조물의 저배율 이미지이다. 이 샘플에 대하여 실리콘의 두께는 100 nm이고, 측방향 치수는 ca.  $4 \times 4 \text{ mm}^2$ 이고, 기판은 PDMS이고, 열적으로 유발된 사전 변형은 3.8%이다. (h)는 프레임 (a 내지 f)에 대응되는 단파장의 플롯이고, (i)는 프레임 (g)의 다양한 지점에서 평가된 장파장의 히스토그램이다.

도 41은 PDMS 위의 2D 웨이브진 Si 나노막의 (a) AFM 이미지이고 (b 내지 d) SEM 이미지들(경사 각도 60°)이다. 상기 실리콘의 두께는 100 nm이고, 열적 사전 변형은 3.8%이다. 이들 이미지에서는 상기 웨이브 패턴의 고도로 주기적인 성질, Si에 식각된 구멍들 근처의 PDMS와 Si의 가장자리에서 볼 수 있는 밀접한 접촉에 의하여 증명되는 바와 같은 Si와 PDMS 사이의 우수한 결합, 및 웨이브 구조물들과 이들 구멍들의 위치들 사이의 상호 무관련성이 흥미롭다.

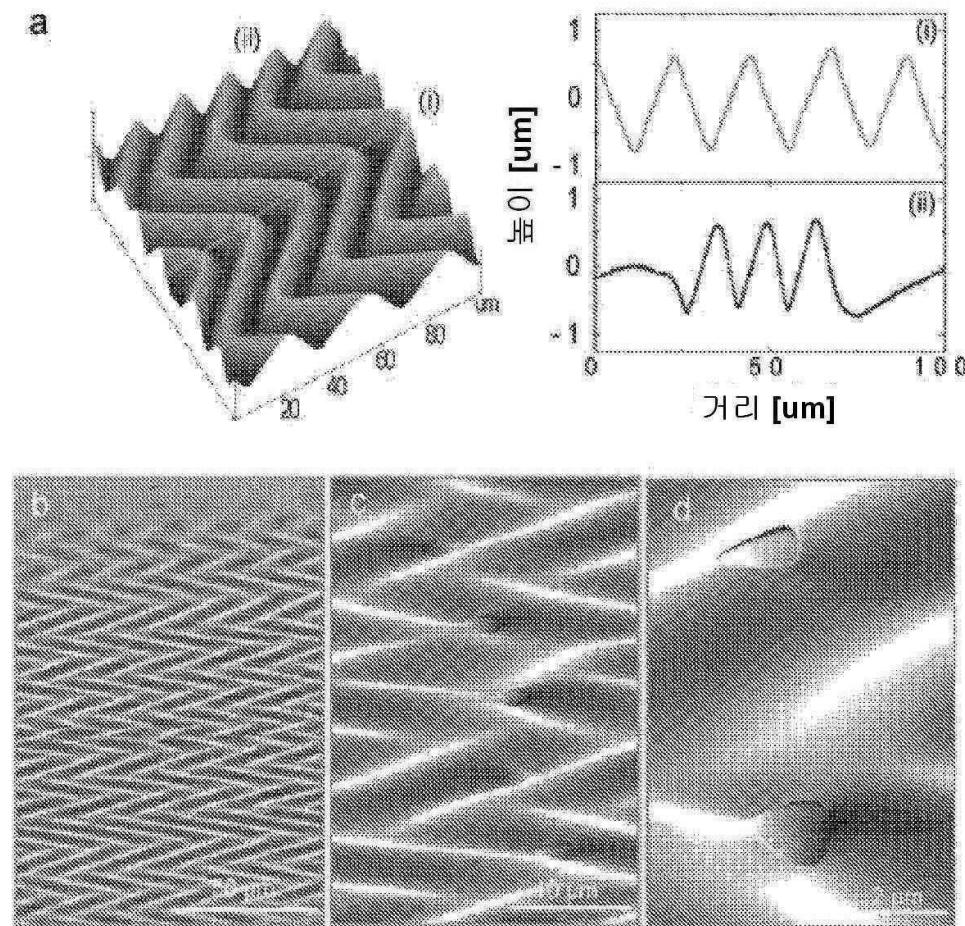

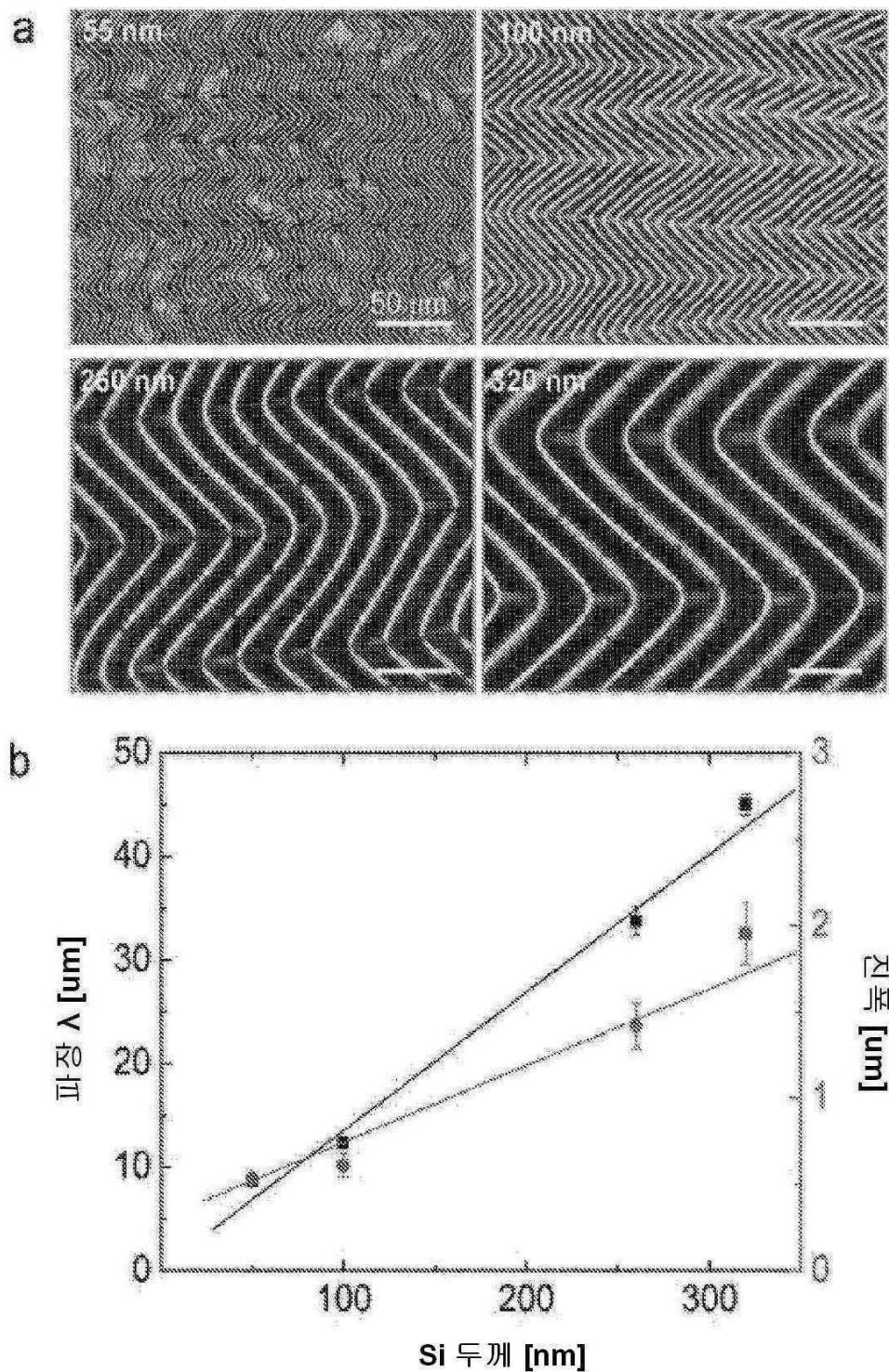

도 42의 (a)는 3.8%의 열적 사전 변형으로 형성되고 PDMS 위에 다양한 두께(55, 100, 260, 320 nm)를 갖는 2D 웨이브진 Si 나노막들의 광학 현미경 사진들이고, (b)는 Si 두께에 대한 단파장과 진폭의 의존성을 나타낸다.

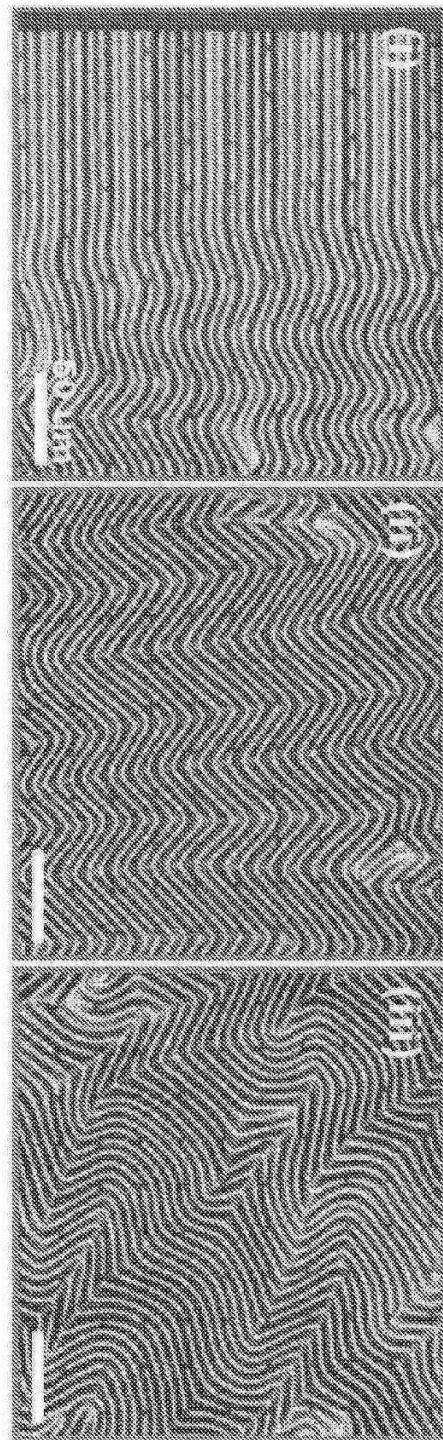

도 43의 (a)는 세 개의 상이한 방향들에서 적용된, 상이한 일축성 변형들 하에서의 2D 웨이브진 Si 나노막들의 광학 현미경 사진들이다. 이들 샘플들은 PDMS 위의 100 nm의 두께를 갖고, 3.8%의 열적 사전 변형으로 형성되는 Si 막들로 구성된다. 상기 이미지들은 인장하기 전의 릴랙스된 상태(최상부 프레임들), 인장한 후에 릴랙스된 상태(최하부 프레임들), 그리고 일축성으로 적용된 인장 변형이 1.8%일 때(위에서 두 번째 프레임), 및 3.8% 일 때(아래에서 두 번째 프레임) 수집되었다. (b)는 상이한 세 방향으로 적용된 변형에 대한 단파장의 의존성을 나타낸다.

도 44는 2D 웨이브진 Si 나노막의 상이한 영역들의 AFM 이미지들로서, 상기 막의 가장자리 근처의 영역(상부 프레임), 이 가장자리 영역으로부터 약간 떨어진 영역(가운데 프레임), 및 상기 막의 중앙 근처의 영역(하부 프레임)의 1D 웨이브진 기하학적인 특성을 보여준다. 본 샘플은 PDMS 위의 100 nm의 두께를 갖는, 3.8%의 열적 사전 변형으로 형성된 Si 막으로 구성된다.

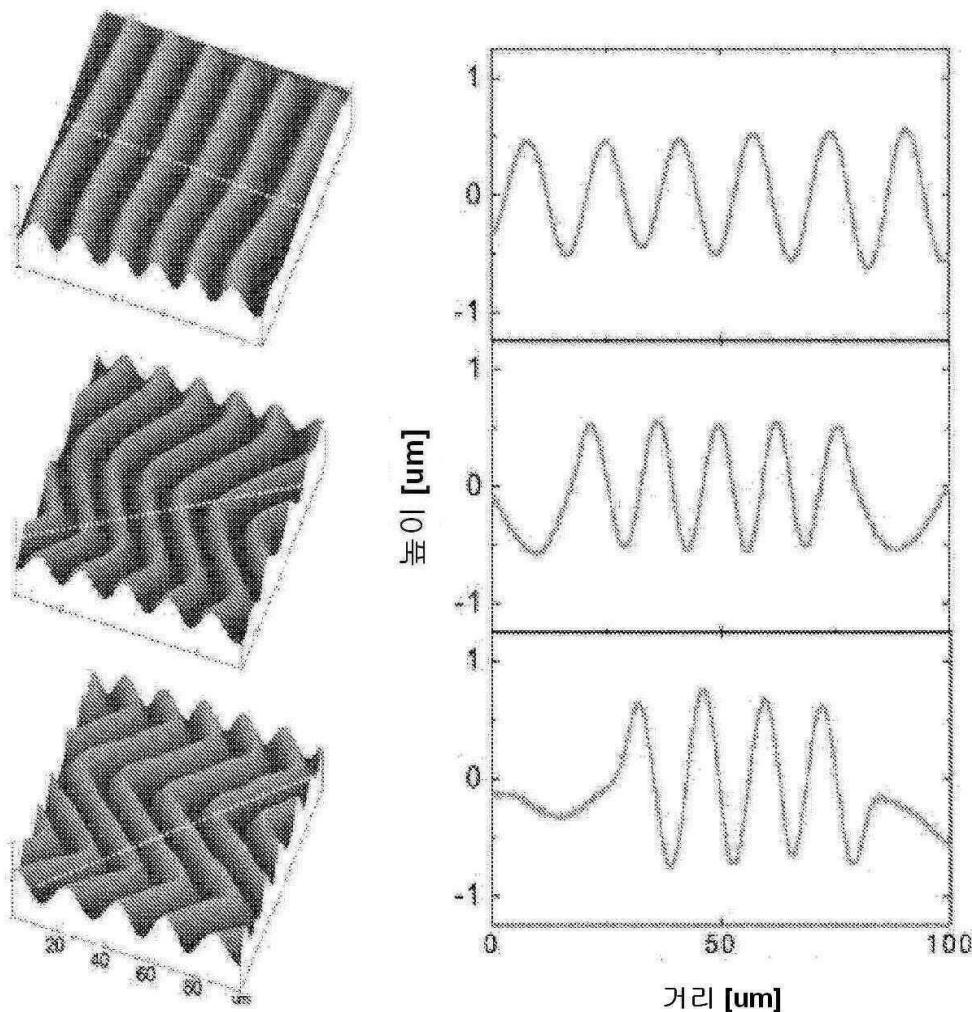

도 45는 1000  $\mu\text{m}$ 의 길이와 100, 200, 500, 및 1000  $\mu\text{m}$ 의 폭들을 갖는 2D 웨이브진 Si 나노막들의 광학 현미경 사진들이다. 이들 막들은 모두 100 nm의 두께를 가지며, 동일한 PDMS 기판 위에, (a) 2.3% 및 (b) 4.8%의 열적 사전 변형으로 형성되었다. (c)는 유사 막들에 있어서 사전 변형에 대한 가장자리 효과 길이의 의존성을 나타낸다.

도 46은 (a) 원형, (b) 타원형, (c) 육각형, 및 (d) 삼각형의 상이한 모양들을 갖는 2D 웨이브진 Si 나노막들의 광학 현미경 사진들이다. 이들 막들은 모두 100 nm의 두께를 갖고, PDMS 위에 4.8%의 열적 사전 변형으로 형성되었다.

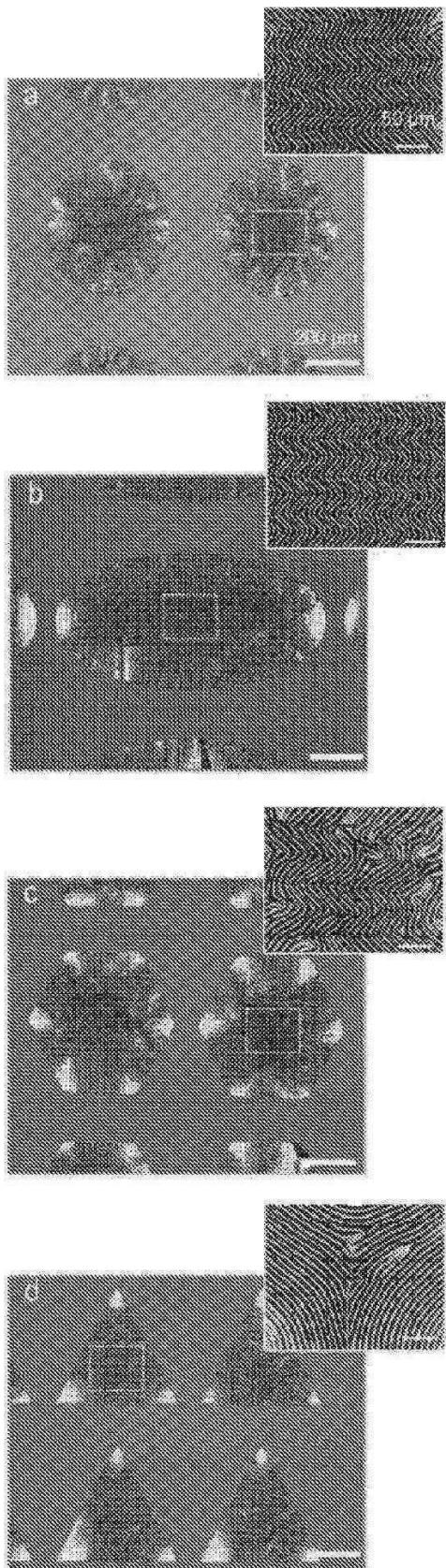

도 47은 상호 접속된 편평한 아일랜드들의 어레이에 2D 인장 가능성을 부여하기 위하여 가장자리 효과들을 이용하도록 설계된 모양들을 갖는 Si 나노막들의 웨이브진 구조들을 보여주는 광학 현미경 사진들이다. 여기에 도시된 두 경우들 모두에 있어서, 상기 Si는 100 nm 두께를 갖고, 정사각형들은  $100 \times 100 \mu\text{m}$ 이고, 리본 접속부들은  $30 \times 150 \mu\text{m}$  라인들이다. 사전 변형은 (a, e) 2.3%, 그리고 (c, g) 15%이다. (a, c, e, g)의 리본들과 정사각형들을 보여주는 선택된 영역들의 SEM 이미지들(경사 각도 75°)은 각각 (b, d, f, h)에 보여진다. 고배율 SEM 이미지들의 삽입 사진들은 b 및 d에서 웨이브들의 상승된 영역들을 보여준다.

도 48은 PDMS 기판 웨이브 상의 2D 웨이브 Si 나노막 (100 nm 두께,  $4 \times 5 \text{ mm}^2$ , 및 3.8% 열적 사전 변형) 샘플의 사진이고(상부 프레임), 그리고 (i) 가장자리에서의 1D 웨이브들, (ii) 더 안쪽 영역에서의 헤링본(herringbone) 웨이브들, 그리고 (iii) 중앙에서의 무질서한 헤링본 웨이브들이다. 스케일 바는 50  $\mu\text{m}$ 이다.

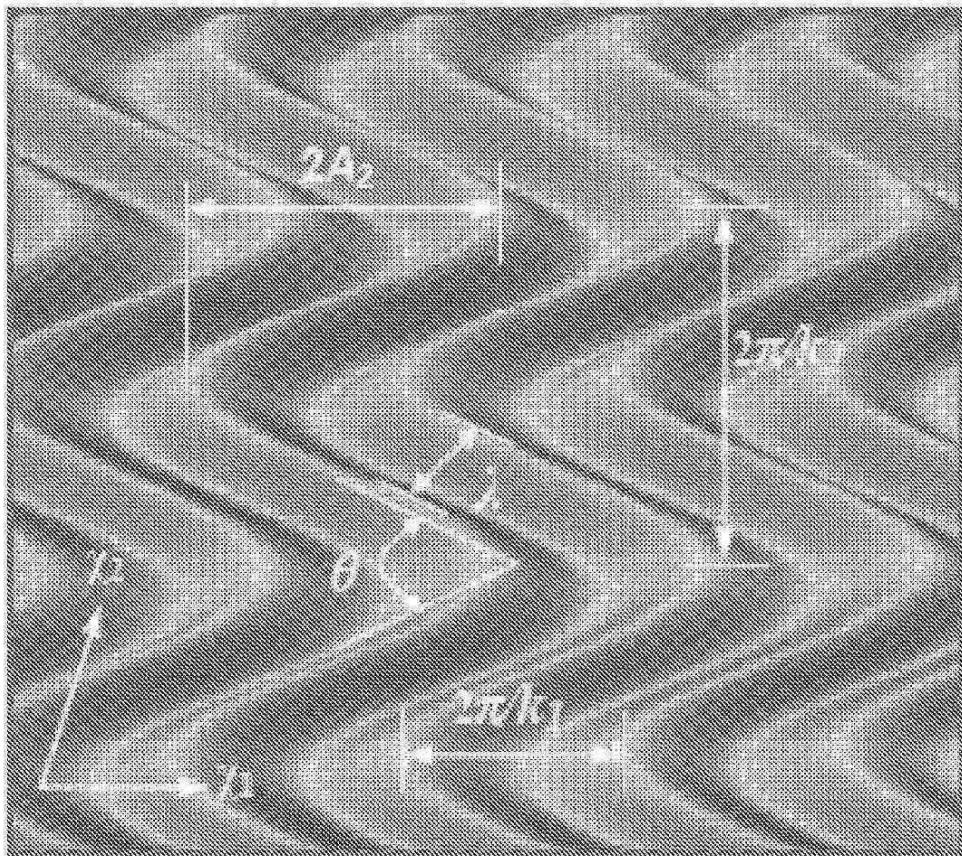

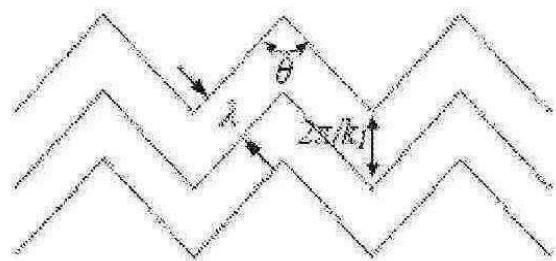

도 49는 헤링본 웨이브 구조물들에서 특성 길이들(characteristic lengths)을 나타내는 개략도이다.

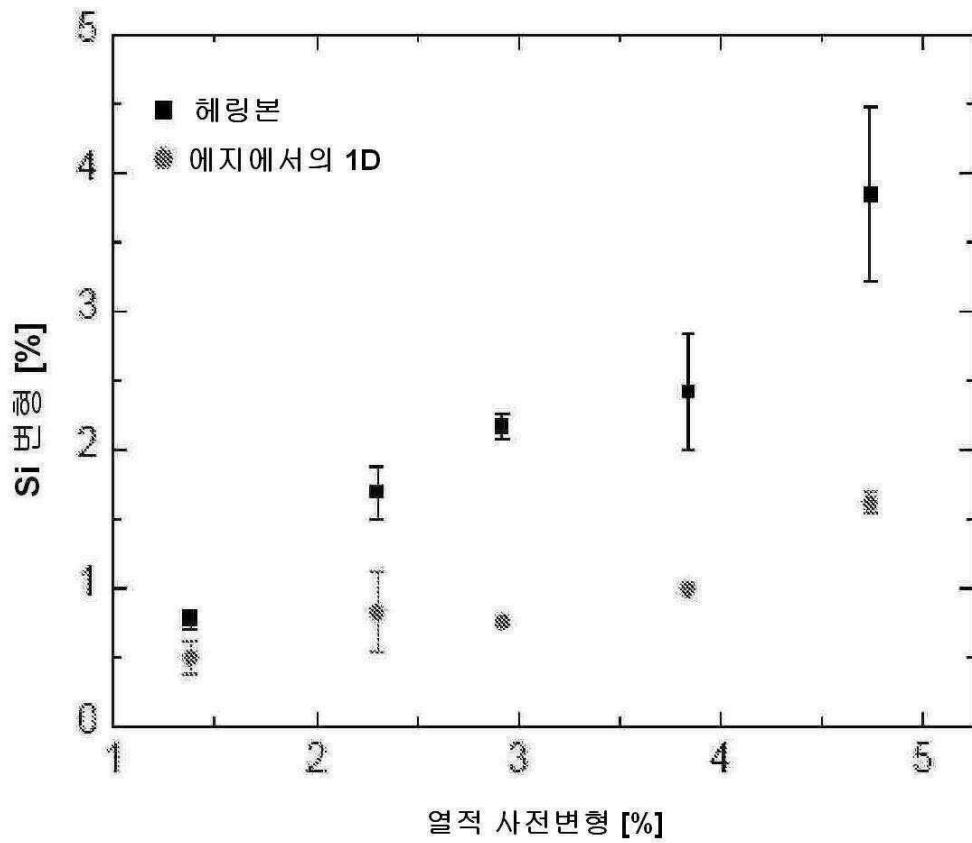

도 50은 Si 변형을 헤링본 및 1D 웨이브들에서 적용된 열적 사전 변형의 함수로 나타낸 것이다. Si 변형은  $\varepsilon_{\text{Si}} = (L - \lambda) / \lambda$ 에 의하여 실험적으로 측정되었고, 여기서 L 및  $\lambda$ 는 AFM 표면 프로파일에서 표면 및 수평 거리이다.

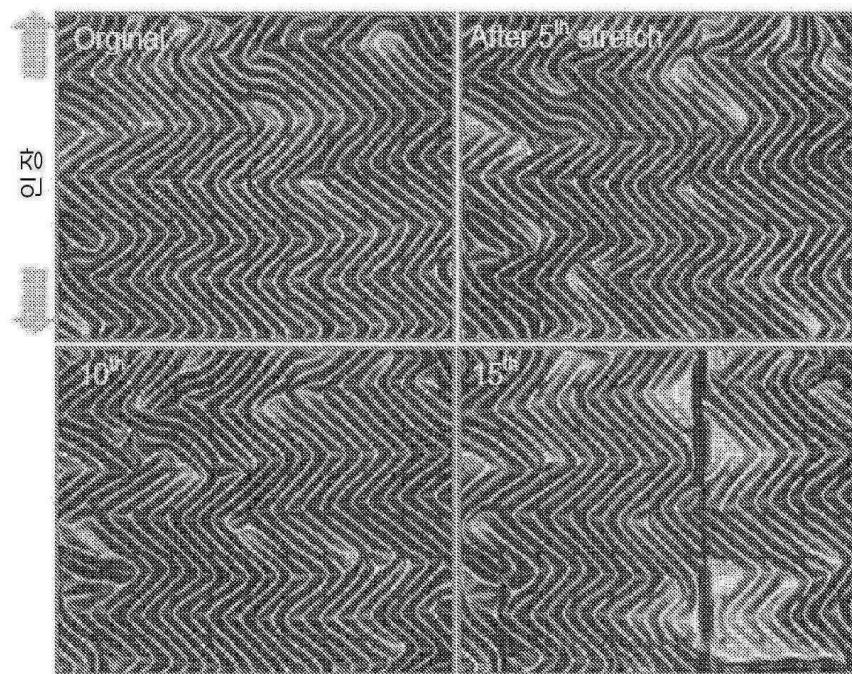

도 51은 인장 시험( $\sim \varepsilon_{st} = 4.0\%$ )의 사이클들 후의 헤링본 웨이브들의 광학 현미경 이미지들이다. 상기 테스트 샘플은 100 nm 두께의 Si 막과 3.8% 이축성(biaxial) 열적 사전 변형으로 준비되었다. 헤링본 웨이브들은 15회 까지의 인장 테스트 사이클 후에도 막의 크랙에 기인하는 일부 결함들을 제외하고는 최초와 거의 유사한 구조를 갖도록 복원되었다.

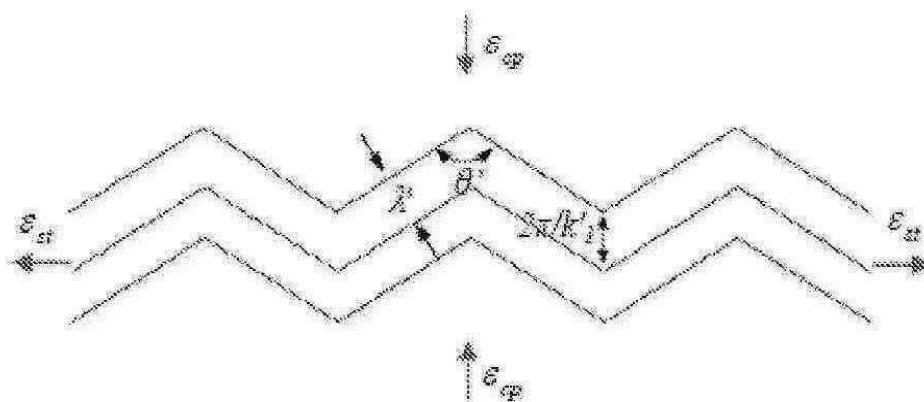

도 52는 일축성 인장 변형의 적용에 따른 헤링본 웨이브들의 '펼쳐짐(unfolding)'을 개략적으로 도시한 것이다. 압축성 변형  $\varepsilon_{cp}$ 는 인장 변형  $\varepsilon_{st}$ 과 관련된 포아송 효과(Poisson effect)에 기인한다.

도 53은 이축성 인장 테스트로서의 가열 및 냉각 과정 동안 헤링본 웨이브들의 모폴로지 변화의 광학 현미경 이미지들이다. 테스트 샘플은 100 nm 두께의 Si 막과 2.9% 이축성 열적 사전 변형으로 준비되었다.

도 54는 구조화되어 웨이브진 마스터 위에 증착하고, 이어서 상기 마스터 위에 스템프를 캐스트(cast)하고, 상기 스템프를 경화시키고, 그리고 그에 의하여 해제와 함께 상기 전극들을 마스터로 전사함으로써 웨이브지고 인장가능한 전극들을 제조하는 한 방법을 요약한다.

도 55는 도 54의 방법과 조합된 도 4의 방법들에 의하여 제조된 웨이브진 PDMS 위의 인장 가능한 금속 전극들(Au, 300 nm 두께)의 이미지를 제공한다. 아래쪽 패널은 상기 인장 가능하고 웨이브진 금속 전극들의 전기 저항 측정 데이터를 적용된 인장 변형(30%까지)의 함수로서 나타낸 그래프이다.

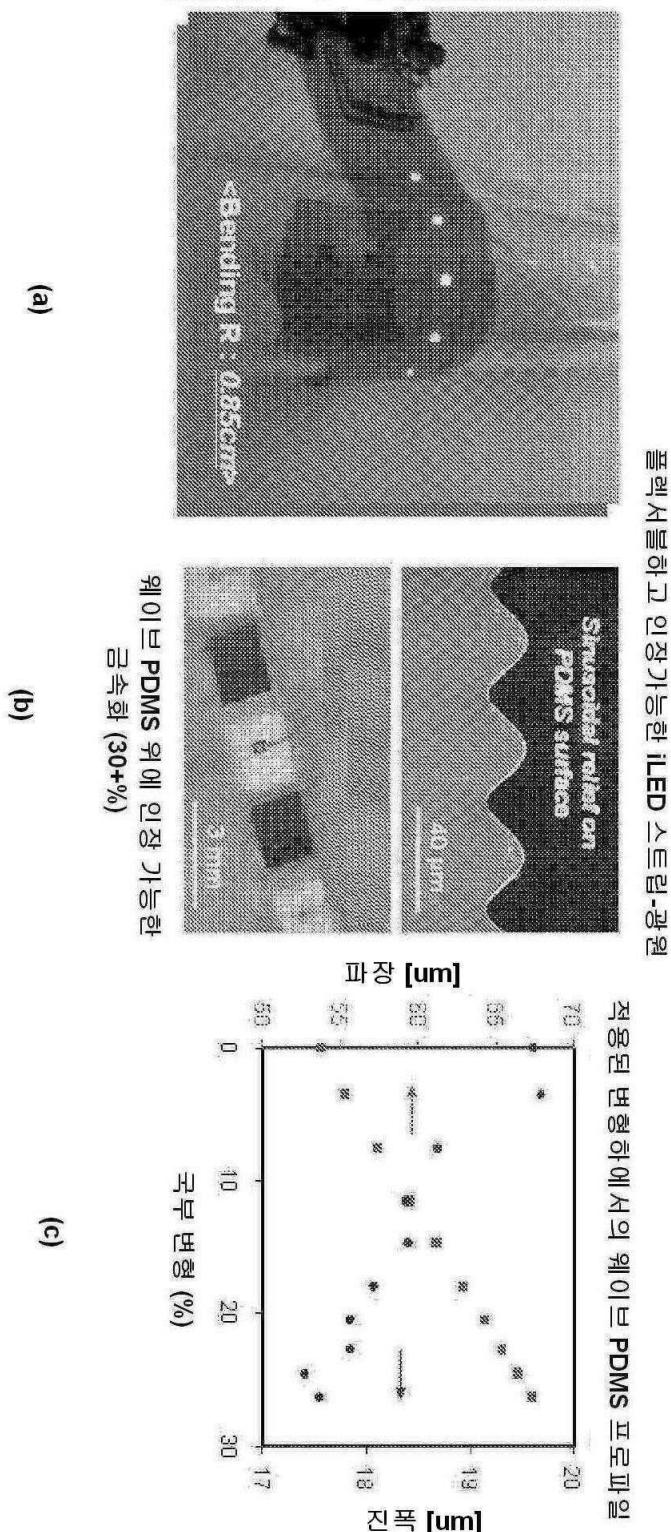

도 56은 플렉서블하고 인장가능한 iLED 스트립-광원을 제조하기 위한 본 방법의 응용 실시예이다. (a)는 상기 장치가 크게 구부릴 수 있음을 나타내는 마이크로 사진이고, 이 실시예에서는 구부림 반경이 0.85 cm이다. (b)는 웨이브진 PDMS 기판 위의 인장 가능한 금속의 단면(위쪽 패널, 스케일바는 40  $\mu\text{m}$ )과 평면(아래쪽 패널, 스케일바는 3 mm)을 제공한다. 상기 금속은 물리적 성질의 심각한 열화 없이 약 30% 인장 가능하다. (c)는 ((b)에 나타낸) PDMS 위의 사인파로 웨이브진 금속 상호 접속부들의 진폭(원, 오른쪽 축)과 파장(정사각형, 원쪽 축)에 대한 국부적인 변형의 영향을 나타낸 그래프이다. 변형이 증가함에 따라 이에 대응하여 금속의 파장이 증가하고 진폭이 감소한다.

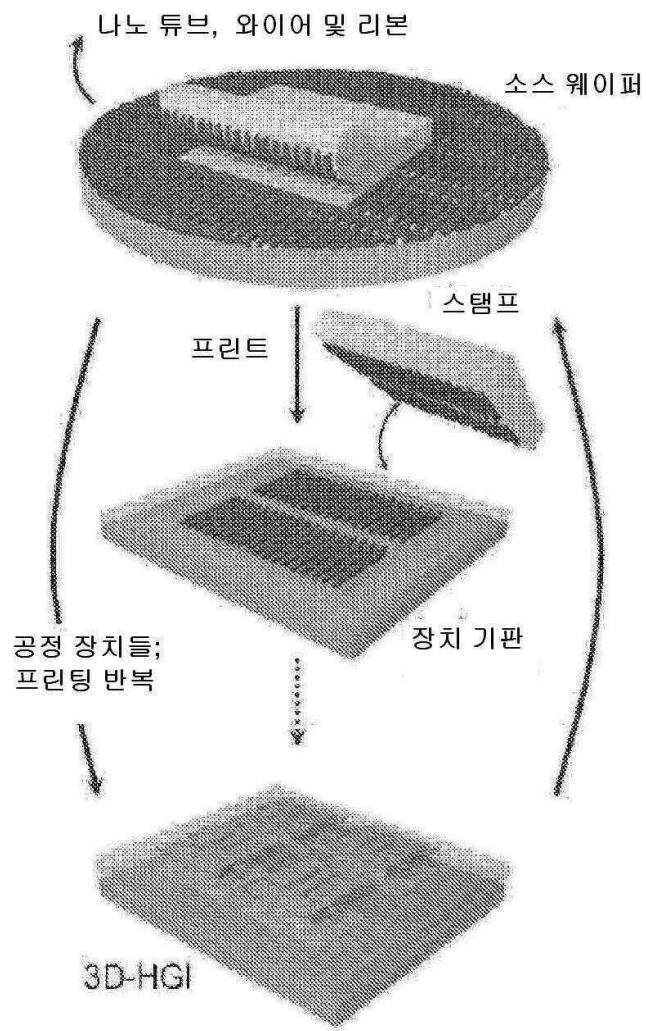

도 57은 이종의 3차원 전자 장치를 위한 인쇄된 반도체 나노 물질들에 기반한 접근을 개략적으로 나타낸 것이다. 상기 공정은 소스 기판들 위에 개별적으로 형성된 나노튜브류, 나노와이어류, 나노리본류 또는 다른 활성 나노 물질들의 집합을 공통 장치 기판 위로 반복적으로 전사 인쇄하여 극초박형의 다층 적층 기하 구조를 갖는 상호 접속된 전자 장치를 생성하는 것을 수반한다.

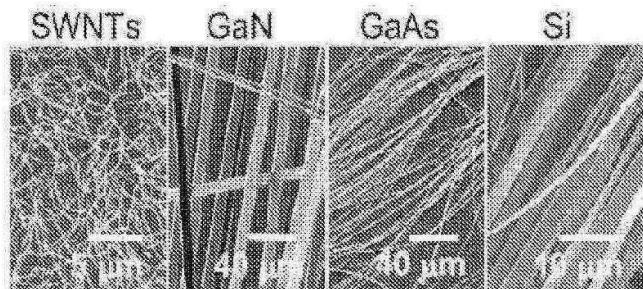

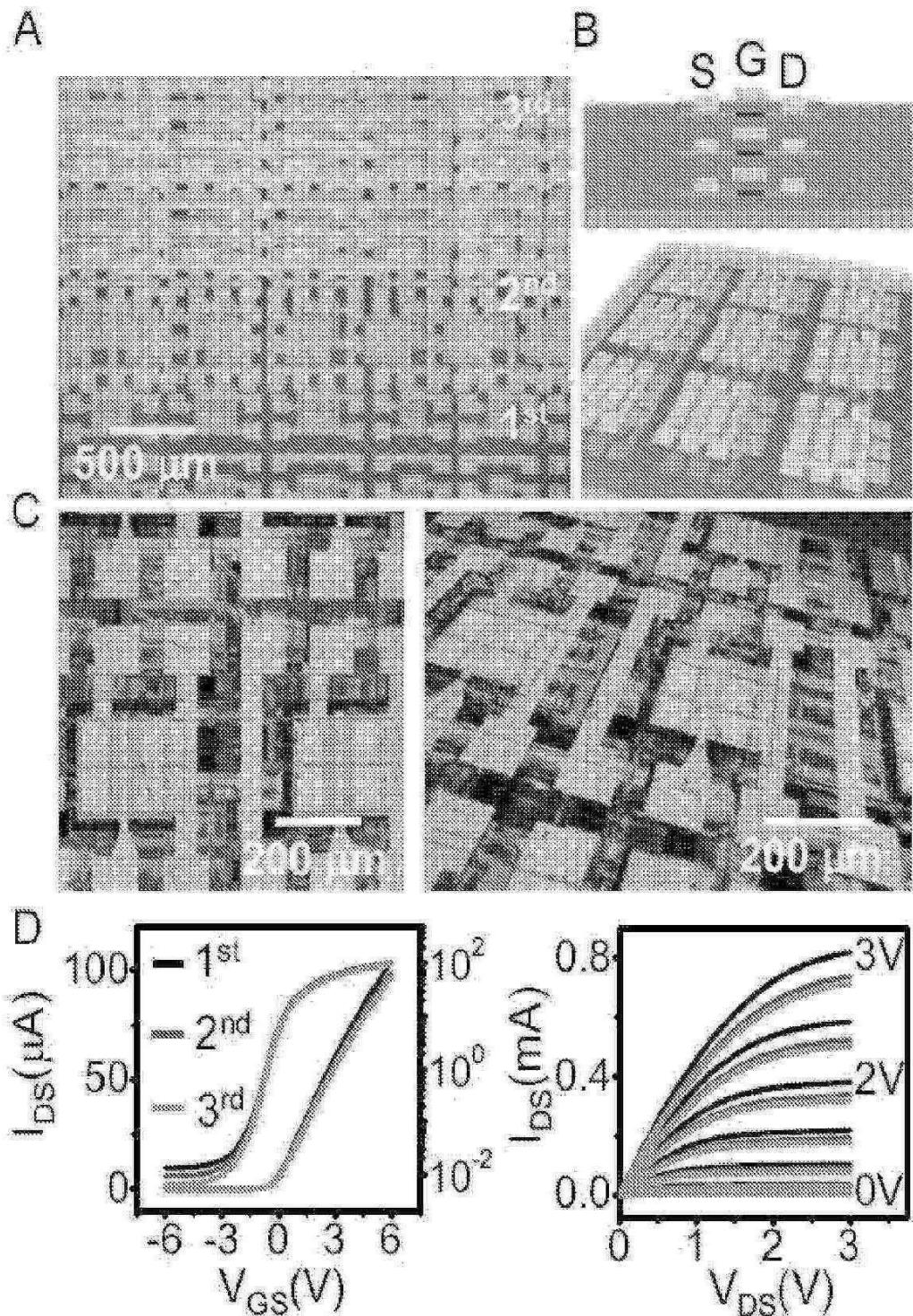

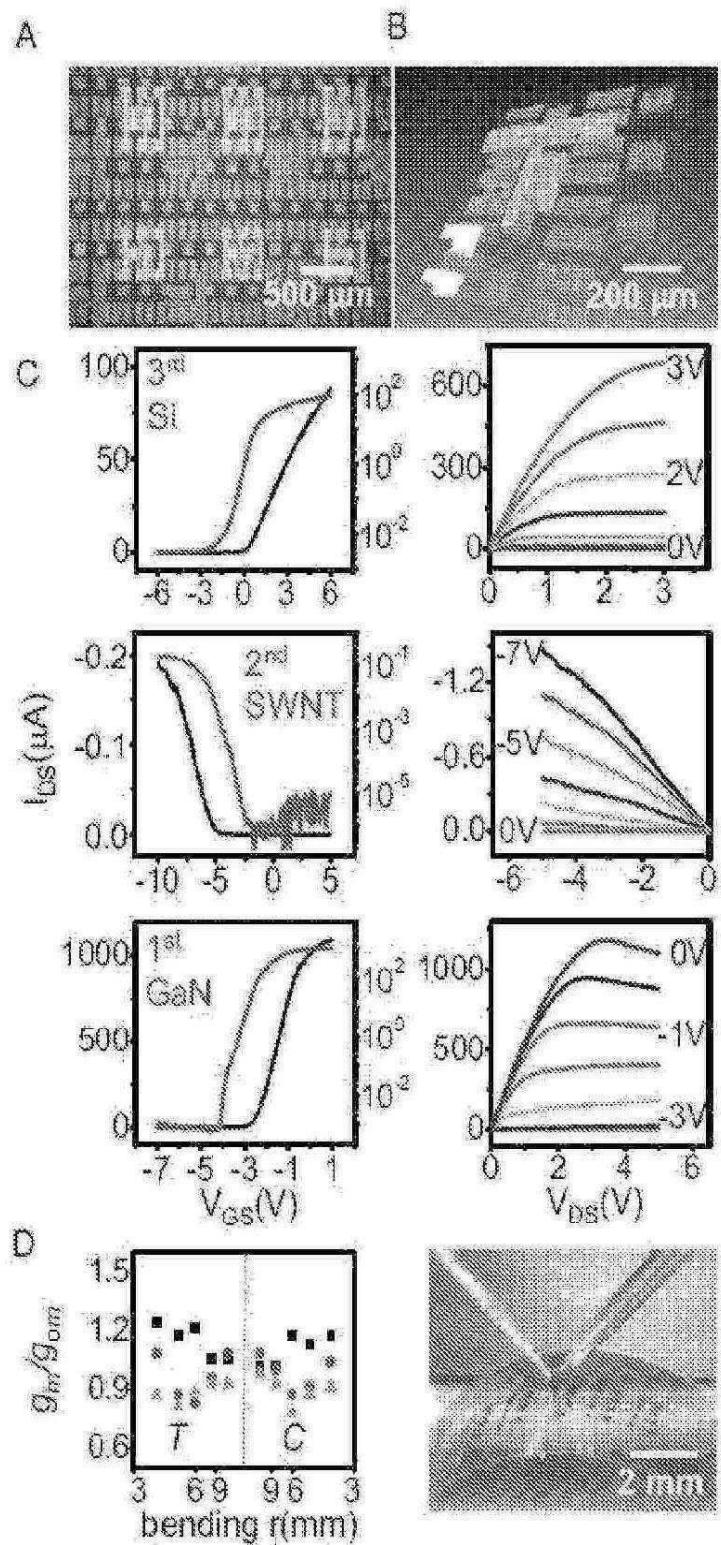

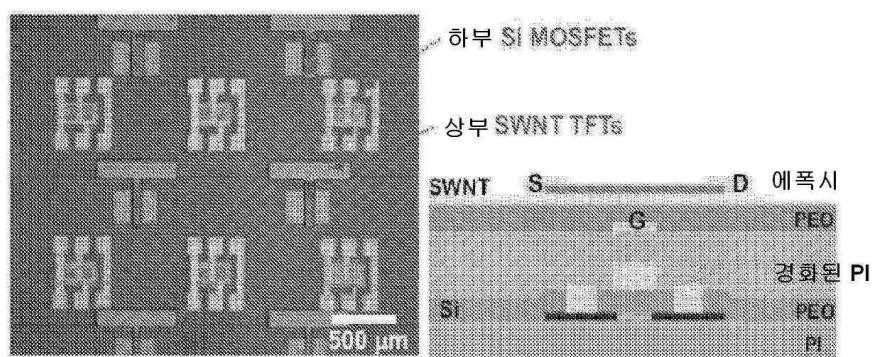

도 58의 (A)는 반도체를 위해 인쇄된 실리콘 나노리본들을 사용하는 단결정 실리콘 금속 산화물 전계 효과 트랜지스터들(MOSFETs: metal oxide field effect transistors)의 어레이의 3차원 다층 적층체의 광학 현미경 사진이다. 이 이미지의 (1st라고 표시된) 아래쪽, (2nd라고 표시된) 중간, 그리고 (3rd라고 표시된) 위쪽 부분은 장치의 하나, 둘 또는 세 층들을 갖는 영역들에 각각 대응된다. (B)는 개략적인 단면도(위) 및 사시도(아래)이다. S, D 및 G는 각각 소스, 드레인, 및 게이트 전극(모두 금색으로 나타냄)을 가리킨다. 밝고 어두운 청색 영역들은 실리콘 리본들의 도핑되고 도핑되지 않은 영역들에 대응되고; 자주색 층은  $\text{SiO}_2$  게이트 유전체이다. (C)는 (A) 및 (B)에 나타낸 것과 같은 장치 기판 위에 공초점 현미경(confocal microscopy)에 의해 수집된 3차원 이미지들이다(왼쪽 프레임: 평면도; 오른쪽 프레임: 사시도). 상기 층들은 식별의 편의를 위해 색채화되었다(금색: 상부층; 적색: 중간층; 청색: 하부층; 실리콘: 회색). (D)는 각 층에 있는 Si MOSFET의 전류-전압 특성으로서, 우수한 성능( $470 \pm 30 \text{ cm}^2/\text{Vs}$ 의 이동도)과 성질들의 양호한 균일성을 보인다. 채널 길이와 폭은 각각 19 및 200  $\mu\text{m}$ 이다.

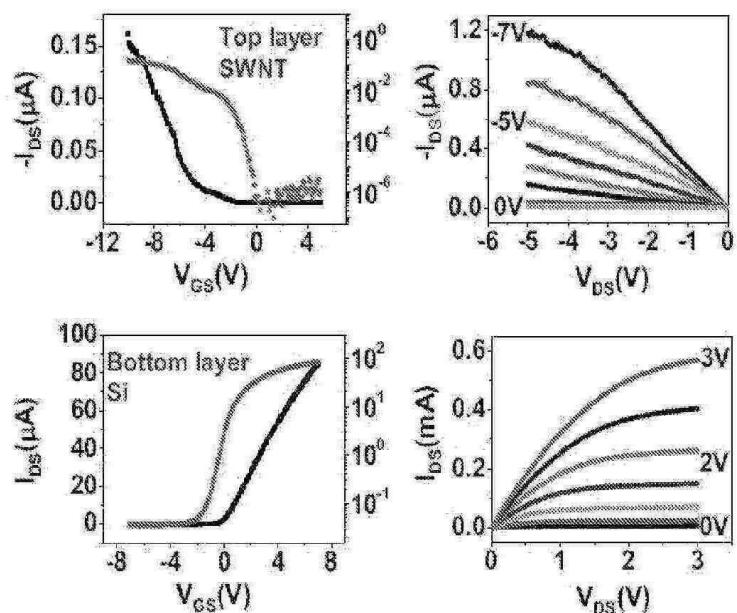

도 59의 (A)는 3층으로 적층된 GaN 나노리본 HEMT들, Si 나노리본 MOSFET들 및 SWNT 네트워크 TFT들을 포함하는 3차원적인 이종 집적된 전자 장치의 광학 현미경 사진이다. (B)는 공초점 현미경에 의하여 수집된 3차원 이미지이다. 층들은 식별의 편의를 위해 색채화되었다(금색: 상부층, Si MOSFET들; 적색: 중간층, SWNT TFT들; 청색: 하부층). (C)는 상기 제 1 층 위의 GaN 소자들(채널 길이, 폭 및 게이트 폭은 각각 20, 170, 및 5  $\mu\text{m}$ ), 제 2 층 위의 SWNT 소자들(채널 길이 및 폭은 각각 50, 및 200  $\mu\text{m}$ ), 및 제 3 층 위의 Si 소자들(채널 길이 및 폭은 각각 19 및 200  $\mu\text{m}$ )의 전기적 특성들이다. (D)는 각 층의 소자들(검은 정사각형: Si MOSFET들; 적색 원: SWNT TFT들; 녹색 삼각형: GaN HEMT들)의 정규화된 트랜스컨덕턴스(transconductance)( $g_m/g_{0m}$ )를 플라스틱 기판의 구부림 반경의 함수로 나타낸 것이다(왼쪽). 구부려진 시스템 및 프로빙 장치의 이미지이다(오른쪽).

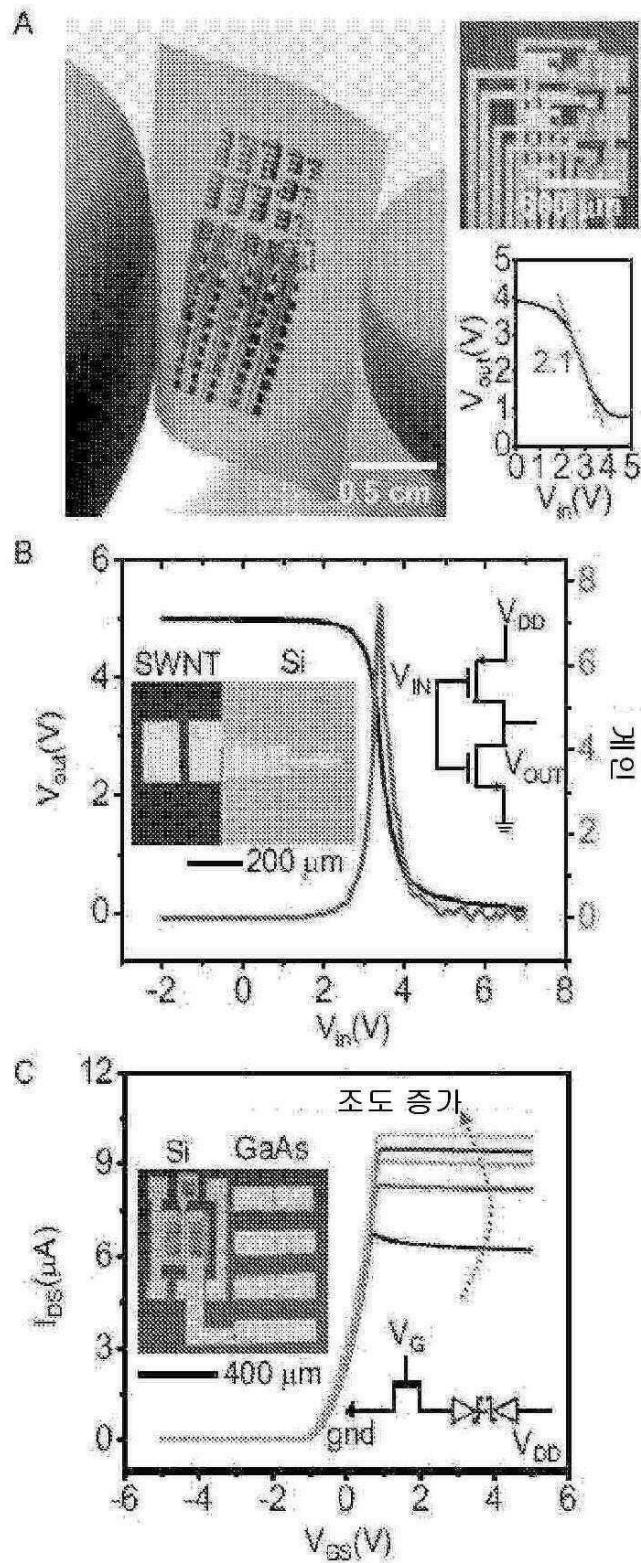

도 60의 (A)는 폴리이미드 기판 위의 3D 실리콘 NMOS 인버터들의 인쇄된 어레이의 이미지이다. 상기 인버터들

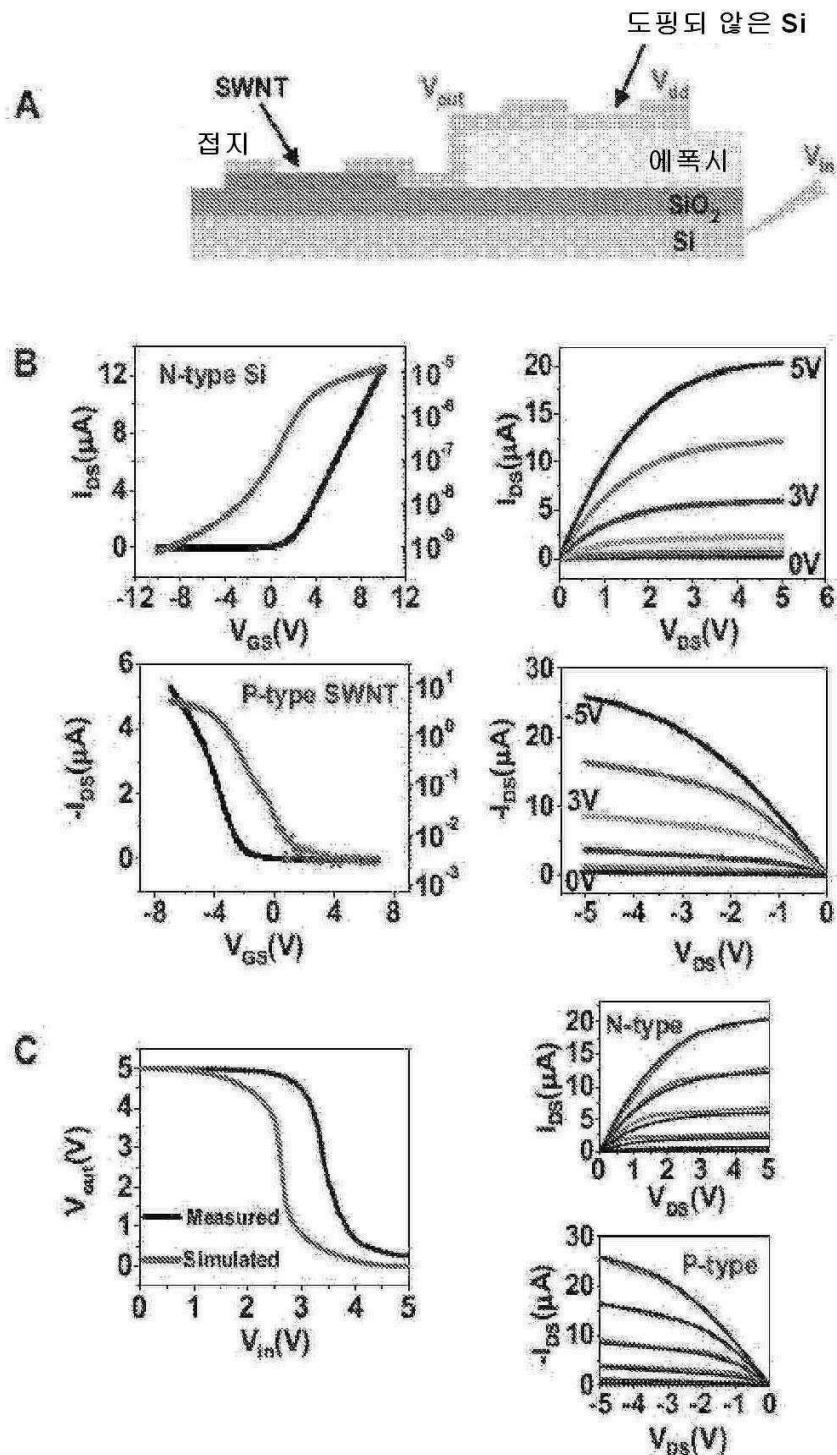

은 상이한 두 수준 상에 있고 전기적 비아(via) 구조물에 의하여 상호접속된 MOSFET들(채널 길이는  $4 \mu\text{m}$ , 부하-구동부(load-to-driver) 폭 비율은 6.7, 및 구동부 폭은  $200 \mu\text{m}$ )로 구성된다. 오른쪽 위쪽의 이미지는 왼쪽 프레임의 적색 상자로 표시된 영역의 확대도를 제공한다. 오른쪽 아래의 그래프는 통상의 인버터의 전달 특성을 나타낸다. (B)는 p 채널 SWNT TFT(채널 길이와 폭이 각각 30 및  $200 \mu\text{m}$ )와 n 채널 Si MOSFET(채널 길이와 폭이 각각 75 및  $50 \mu\text{m}$ )을 이용하는 인쇄된 상보적인 인버터의 전달 특성이다. 삽입된 사진은 인버터의 광학 현미경 사진(왼쪽)과 회로의 개념도(오른쪽)이다. (C)는 어두움으로부터 850 nm의 적외선 광원으로  $11 \mu\text{W}$ 까지 상이한 수준에서의 Si MOSFET(채널 길이와 폭은 각각 9 및  $200 \mu\text{m}$ )과 접적된 GaAs MSM(채널 길이와 폭은 각각 10 및  $100 \mu\text{m}$ )의 전류-전압 응답이다. 삽입 사진은 광학 이미지와 회로도를 나타낸다.

도 61은  $\sim 1 \mu\text{m}$ 까지 인쇄 정합(registration)이 가능한, 자동화된 전사-인쇄용 스테이지의 이미지이다.

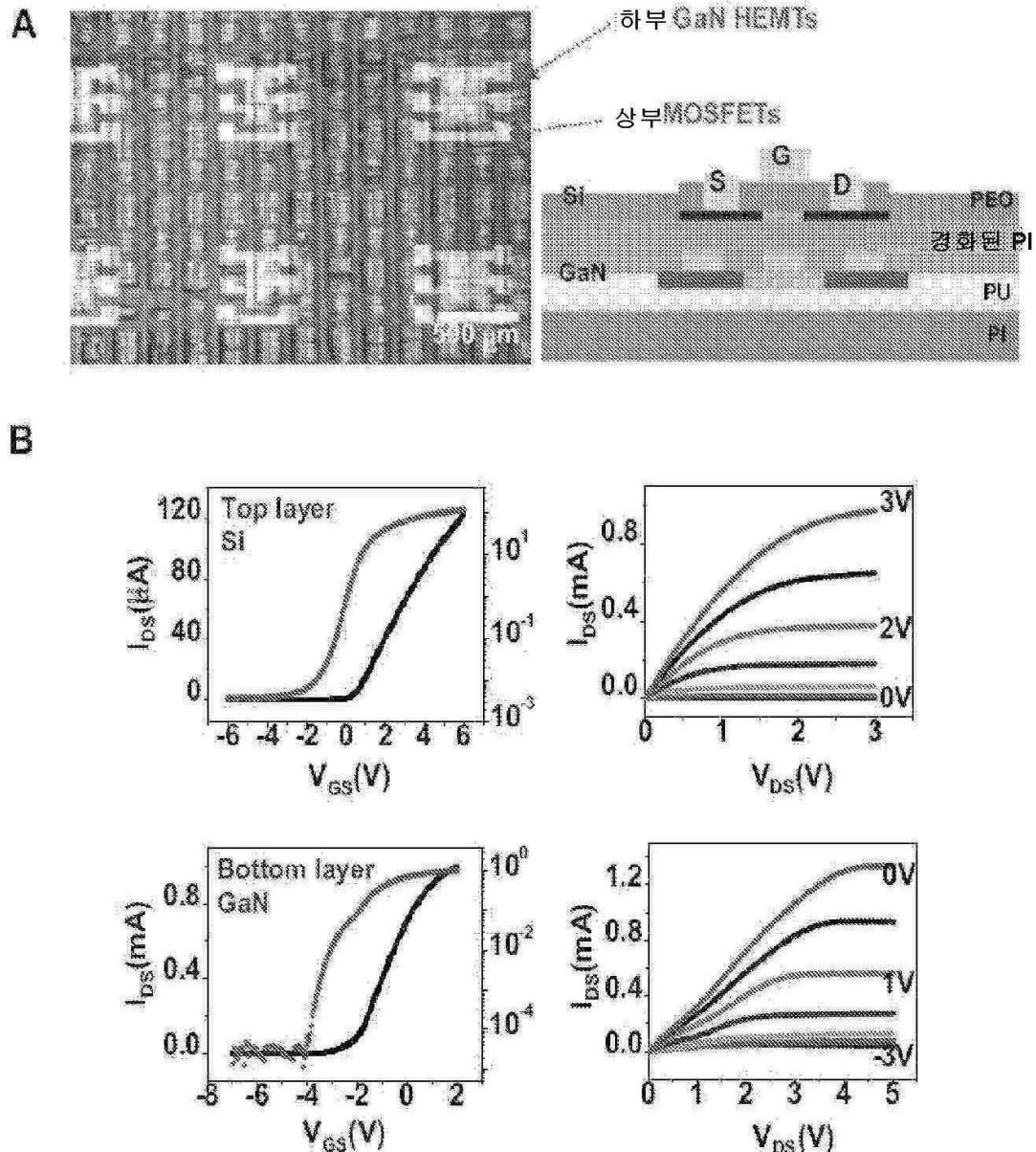

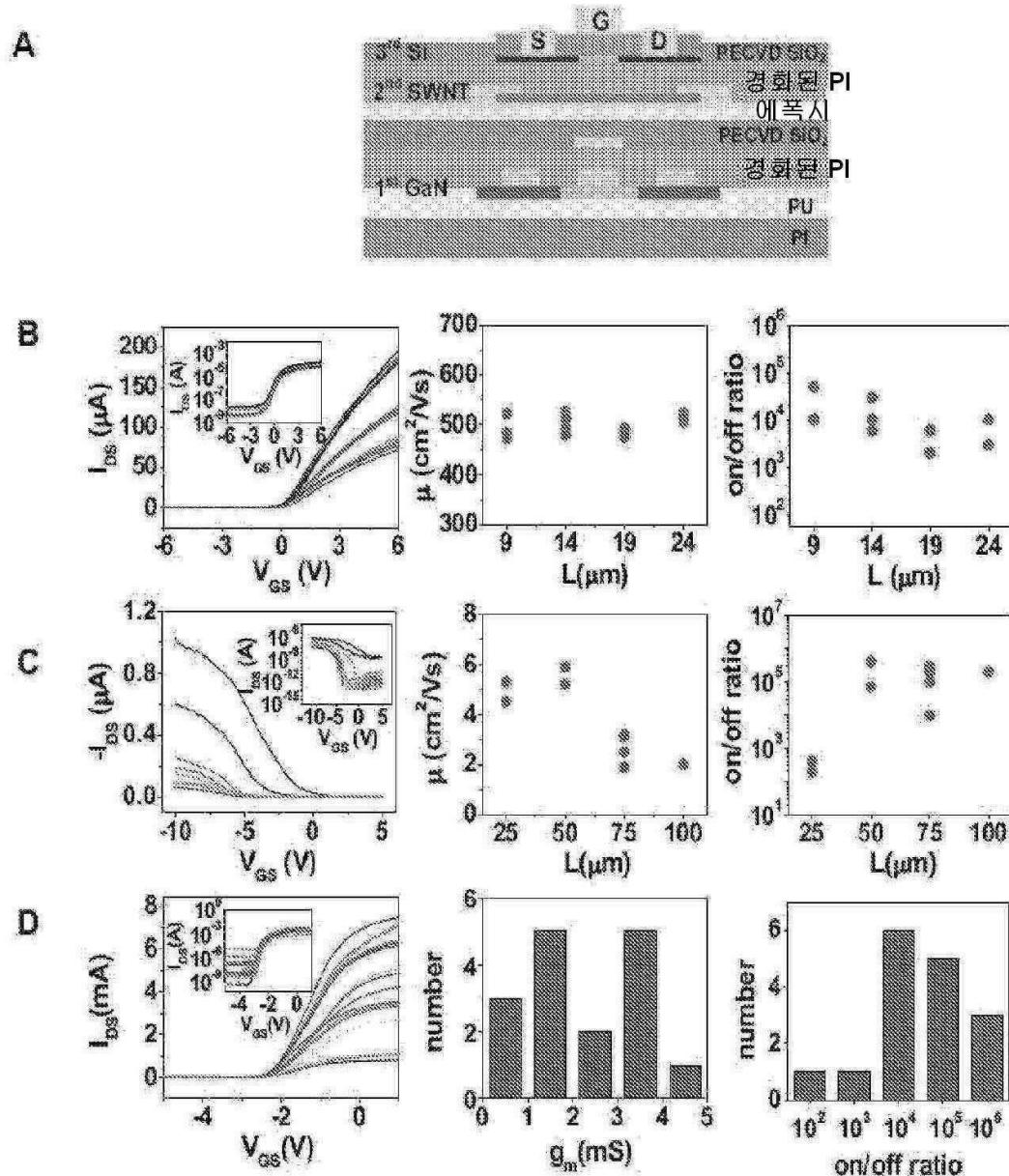

도 62의 (A)는 폴리이미드 기판 위에 Si MOSFET들 및 GaN HEMT가 3차원적으로 이종 접적된 어레이의 광학 현미경 사진이다. 오른쪽 삽입도는 개략 단면도이다. 전극들(금색),  $\text{SiO}_2$ (PEO; 자주색), Si(밝은 청색: 도핑되지 않은 부분; 어두운 청색: 도핑된 부분), GaN(어두운 녹색: 오믹 콘택트들; 밝은 녹색: 채널), 폴리이미드(PI: 갈색) 및 폴리우레탄(PU; 황갈색)이 모두 도시된다. (B)는 통상의 Si MOSFET(채널 길이 및 폭은 각각 19 및  $200 \mu\text{m}$ )과 GaN HEMT(채널 길이, 폭 및 게이트 폭은 각각 20,  $170 \mu\text{m}$  및  $5 \mu\text{m}$ )의 전류-전압 특성들을 나타낸다. 왼쪽 프레임들에 있는 Si 및 GaN에 대한 데이터들은 각각  $V_{dd} = 0.1\text{V}$  및  $V_{dd} = 2\text{V}$ 에서 측정되었다.

도 63의 (A)는 폴리이미드 기판 위에 Si MOSFET들 및 SWNT TFT가 3차원적으로 이종 접적된 어레이의 광학 현미경 사진이다. 오른쪽 삽입도는 개략 단면도이다. 전극들(금색), 에폭시(청록색),  $\text{SiO}_2$ (PEO; 자주색), Si(밝은 청색: 도핑되지 않은 부분; 어두운 청색: 도핑된 부분), SWNT(회색), 폴리이미드(PI: 갈색) 및 경화된 폴리이미드(황갈색)이 모두 도시된다. (B)는 통상의 SWNT TFT(채널 길이 및 폭은 각각 75 및  $200 \mu\text{m}$ )와 Si MOSFET(채널 길이 및 폭은 각각 19 및  $200 \mu\text{m}$ )의 전류-전압 특성들을 나타낸다. 왼쪽 프레임들에 있는 SWNT 및 Si에 대한 데이터들은 각각  $V_{dd} = -0.5\text{V}$  및  $V_{dd} = 0.1\text{V}$ 에서 측정되었다.

도 64의 (A)는 폴리이미드 기판 위에 Si MOSFET들, SWNT TFT 및 GaN HEMT가 3차원적으로 이종 접적된 어레이의 단면 개략도이다. (B)는 여러 Si MOSFET들(채널폭 =  $200 \mu\text{m}$ , 흑색선: 채널길이 =  $9 \mu\text{m}$ , 적색:  $14 \mu\text{m}$ , 녹색:  $19 \mu\text{m}$ , 청색:  $24 \mu\text{m}$ )에 대한 전달 특성들, 유효 이동도 및 온/오프 비율을 나타낸다. (C)는 SWNT TFT들(채널폭 =  $200 \mu\text{m}$ , 흑색선: 채널길이 =  $25 \mu\text{m}$ , 적색:  $50 \mu\text{m}$ , 녹색:  $75 \mu\text{m}$ , 청색:  $100 \mu\text{m}$ )이다. 그리고 (D)는 GaN HEMT들(채널 길이, 폭, 및 게이트 폭은 각각  $20 \mu\text{m}$ ,  $170 \mu\text{m}$ , 및  $5 \mu\text{m}$ )에 대한 전달 특성들, 트랜스컨덕턴스들, 및 온/오프 비율을 나타낸다.

도 65의 (A)는 실리콘 웨이퍼 기판 상에 제조된 SWNT-Si CMOS 인버터의 개략적인 단면 구조이다. (B)는 CMOS 인버터를 형성하는 n-채널 Si MOSFET과 p-채널 SWNT TFT의 전달 및 I-V 특성들이다. (C)는 인버터의 계산된 전달 특성들과 Si 및 SWNT 트랜지스터들의 I-V 특성들이다.

도 66의 (A)는 폴리이미드 기판 위에 제조된 GaAs MSM-Si MOSFET IR 감지기의 개념적인 단면 구조와 개략적인 회로도이다. (B)는 3V 공급에 대한 GaAs MSM IR 감지기( $L = 10 \mu\text{m}$ ,  $W = 100 \mu\text{m}$ )의 전류-전압 특성과 Si MOSFET( $L = 9 \mu\text{m}$ ,  $W = 200 \mu\text{m}$ )의 전달 및 I-V 특성들이다. (C)는 3V 공급에 대한 GaAs MSM의 계산된 IV 특성과 Si MOSFET과 접적된 GaAs MSM의 I-V 응답이다.

도 67은 변형 가능한 기판에 부분적으로 접착된 광학적 미세 구조의 제어된 베클링을 통해 제조된 광학 장치(도파관 어레이)를 개념적으로 나타낸다.

도 68은 변형 가능한 기판에 부분적으로 접착된 전도성 미세 구조의 제어된 베클링을 통해 제조된 기계적 장치(예를 들면, 가속도/압력 센서)를 개념적으로 나타낸다.

도 69는 변형 가능한 기판에 부분적으로 접착된 내열성 미세 구조의 제어된 베클링을 통해 제조된 열적 장치(미세 볼로미터: microbolometer)를 개념적으로 나타낸다.

### 발명을 실시하기 위한 구체적인 내용

[0070] "인장 가능하다(stretchable)"는 것은 물질, 구조, 장치, 또는 장치 구성 부품이 파괴 없이 변형될 수 있는 능력을 가리킨다. 전형적인 구현예에 있어서, 인장 가능한 물질, 구조, 장치 또는 장치 구성 부품은 파괴 없이 약 0.5%보다 큰 변형을 견딜 수 있고, 바람직하게는 일부 응용들에 있어서 약 1%보다 큰 변형을 견딜 수 있고,

그리고 더욱 바람직하게는 일부 응용들에 있어서 약 3%보다 큰 변형을 견딜 수 있다.

[0071] "구성 부품(component)"은 장치에 사용되는 물질 또는 개별 구성 부품을 가리키기 위하여 널리 사용된다. "상호 접속부(interconnect)"는 구성 부품의 한 예로서 구성 부품과 또는 구성 부품들 사이에 전기적인 연결을 형성할 수 있는 전기 전도성의 물질을 가리킨다. 특히, 상기 상호 접속부는 분리되고 및/또는 상호간에 대하여 움직일 수 있는 구성 부품들 사이에 전기적인 접촉을 형성할 수 있다. 상기 상호 접속부는 원하는 장치의 명세, 동작 및 응용에 따라 적절한 물질로 제조된다. 높은 전도도가 요구되는 응용들에 대하여, 은, 금, 알루미늄 등과 이들의 합금들을 포함하여 통상의 상호 접속 금속들이 이용될 수 있지만 여기에 한정되는 것은 아니다. 적절한 도전성 물질들은 실리콘, 인듐 주석 산화물, 또는 GaAs와 같은 반도체를 포함할 수 있다.

[0072] "반도체(semiconductor)"는 매우 낮은 온도에서 절연체이지만 약 300 켈빈(Kelvin)의 온도에서는 상당한 전기 전도성을 지니는 임의의 물질을 지칭한다. 본 발명의 상세한 설명에서는, 반도체라는 용어는 미세 전자공학 및 전자 장치들의 기술 분야에서 본 용어를 사용하는 것과 일치하게 사용할 것이 의도된다. 본 발명에 있어서 유용한 반도체들은 실리콘, 저매듭, 및 다이아몬드와 같은 원소 반도체들(element semiconductor)과 SiC 및 SiGe 와 같은 IV족 화합물 반도체들, AlSb, AlAs, AlIn, AlP, BN, GaSb, GaAs, GaN, GaP, InSb, InAs, InN, 및 InP과 같은 III-V족 반도체들,  $\text{Al}_x\text{Ga}_{1-x}\text{As}$ 와 같은 III-V족 삼원계 반도체 합금들, CsSe, CdS, CdTe, ZnO, ZnSe, ZnS, 및 ZnTe와 같은 II-VI족 반도체들, CuCl과 같은 I-VII족 반도체들, PbS, PbTe 및 SnS과 같은 IV-VI족 반도체들, PbI<sub>2</sub>, MoS<sub>2</sub> 및 GaSe와 같은 층상 반도체들, CuO 및 Cu<sub>2</sub>O와 같은 산화물 반도체들과 같은 화합물 반도체들을 포함할 수 있다. 반도체라는 용어는 진성 반도체와, 주어진 응용 또는 장치에 유용한 유리한 전자적 성질을 제공하기 위하여 p-형 도핑 물질들 및 n-형 도핑 물질들을 갖는 반도체를 포함하는 하나 또는 그 이상의 선택된 물질들로 도핑된 외인성 반도체(extrinsic semiconductor)을 포함한다. 반도체라는 용어는 반도체들 및/또는 도편트들의 혼합물을 포함하는 복합 물질들을 포함한다. 본 발명의 일부 응용들에 있어서 유용한 구체적인 반도체 물질들은 Si, Ge, SiC, AlP, AlAs, AlSb, GaN, GaP, GaAs, GaSb, InP, InAs, GaSb, InP, InAs, InSb, ZnO, ZnSe, ZnTe, CdS, CdSe, ZnSe, ZnTe, CdS, CdSe, CdTe, HgS, PbS, PbSe, PbTe, AlGaAs, AlInAs, AlInP, GaAsP, GaInAs, GaInP, AlGaAsSb, AlGaInP, 및 GaInAsP를 포함하지만 여기에 한정되는 것은 아니다. 다공성 실리콘 반도체 물질들은 센서들 및 발광 다이오드(LEDs) 및 고체 상태 레이저들과 같은 발광 물질들의 분야에서 본 발명의 응용에 대하여 유용하다. 반도체 물질들의 불순물들은 반도체 물질(들) 자신들 또는 상기 반도체 물질에 제공된 임의의 도편트들이 아닌 원자들, 원소들, 이온들 및/또는 분자들이다. 불순물들은 반도체 물질들 내에 존재하며 반도체 물질들의 전자적 성질들에 부정적인 영향을 미치는 바람직하지 않은 물질들로서, 산소, 탄소, 및 중금속들을 포함하는 금속들을 포함하지만 여기에 한정되는 것은 아니다. 중금속 불순물들은 주기율표 상에서 구리와 납 사이의 원소들의 족, 칼슘, 나트륨, 및 이들의 모든 이온들, 화합물들, 및/또는 착화합물들(complexes)을 포함하지만 여기에 한정되는 것은 아니다.

[0073] "반도체 원소(semiconductor element)" 및 "반도체 구조(semiconductor structure)"는 본 상세한 설명에서 동의어적으로 사용되며, 임의의 반도체 물질, 조성 또는 구조를 널리 지칭하고, 고품질의 단결정성 및 다결정성 반도체들, 고온 공정을 통해 제조된 반도체 물질들, 도핑된 반도체 물질들, 유기 및 무기 반도체들 및 하나 또는 그 이상의 추가적인 반도체 구성 물질들 및/또는 유전체 층들 또는 물질들 및/또는 도전성 층들 또는 물질들과 같은 비-반도체 구성 물질들을 갖는 복합 반도체 물질들 및 구조들을 명시적으로 포함한다.

[0074] "인장 가능한(stretchable)" 상호 접속부는 장치 구성 부품으로 전기적 접속 또는 장치 구성부품으로부터의 전기적 전도에 부정적으로 영향을 미침이 없이, 하나 또는 그 이상의 방향으로의 인장, 구부림 및/또는 압축과 같은 다양한 변형들 및 힘들을 견딜 수 있는 상호 접속부를 널리 지칭하기 위해 여기에서 사용된다. 따라서, 인장 가능한 상호 접속부는 GaAs와 같이 상대적으로 깨어지기 쉬운 물질로 형성될 수도 있으며, 상기 상호 접속부의 기하학적 구성으로 인해 상당한 변형력(deformatory force)(예를 들면, 인장, 구부림, 압축)에 노출되었을 때에도 계속하여 기능을 수행할 수 있도록 남을 수 있다. 전형적인 구현예에서, 인장 가능한 상호 접속부는 약 1%, 10% 또는 약 30%보다 큰 변형을 파괴 없이 견딜 수 있다. 일 실시예에 있어서, 상기 변형은 상기 상호 접속부의 적어도 일부분이 결합된, 하부에 놓인 엘라스토머 기판이 인장됨으로써 생성된다.

[0075] "장치 구성 부품(device component)"은 전기적, 광학적, 기계적 또는 열적 장치 내의 개별 구성 부품을 널리 지칭하기 위하여 사용된다. 구성 부품은 하나 또는 그 이상의 광 다이오드, LED, TFT, 전극, 반도체, 다른 광-접속/감지 구성 부품들, 트랜지스터, 접착 회로, 장치 구성 부품을 수용할 수 있는 콘택 패트, 박막 소자들, 회로 요소들, 제어 요소들, 마이크로프로세서들, 트랜스듀서들 및 이들의 조합들 중에서 하나 또는 그 이상일 수 있다. 장치 구성 부품은 예를 들면, 금속 증착(metal evaporation), 와이어 본딩, 고체 또는 도전성 페이스트들

의 적용과 같은 당 기술분야에서 알려진 바에 따라 하나 또는 그 이상의 콘택 패드들에 연결될 수 있다. 전기 장치는 복수의 장치 구성 부품들을 포함하는 장치를 일반적으로 지칭하며, 대면적 전자 장치, 인쇄된 와이어 기판, 접착 회로들, 장치 구성 부품들의 어레이, 생물학적 및/또는 화학적 센서들, 물리적 센서들(예를 들면, 온도, 광, 방사선, 등), 태양 전지 또는 광전지(photovoltaic) 어레이들, 디스플레이 어레이들, 광학 접속기들(collectors), 시스템들 및 디스플레이들을 포함한다.

[0076] "기판(substrate)"은 장치 구성 부품 또는 상호 접속부를 포함하는 구성 부품을 지지할 수 있는 표면을 지닌 물체를 가리킨다. 상기 기판에 "결합된" 상호 접속부는 상기 기판과 물리적인 접촉을 하는 상호 접속의 일부분으로서, 그것이 결합된 기판 표면에 대하여 실질적으로 상대적으로 움직일 수 없는 부분을 가리킨다. 대조적으로, 결합되지 않은 부분들은 상기 기판에 대하여 상대적인 실질적인 움직임이 가능하다. 상호 접속부의 상기 결합되지 않은 부분은 변형-유도된 상호 접속부 구부러짐에 의하는 것과 같은 "구부러짐 구성"을 갖는 부분에 일반적으로 대응된다.

[0077] 기판과의 "정합 접촉(conformal contact)"을 이루는 구성 부품은 기판을 덮으면서 3차원적 양각 구조를 유지해, 상기 3차원적 양각 구조의 패턴이 상기 기판 위의 양각 구조들의 패턴에 의하여 지배되는 구성 부품을 가리킨다.

[0078] 본 상세한 설명의 맥락에 있어서, "구부림 구성(bent configuration)"은 힘을 가함으로 인하여 야기되는 굴곡진 형태를 갖는 구조를 가리킨다. 본 발명에 있어서 구부러짐 구조들은 접힘 영역(folded region), 불룩 영역, 오목 영역, 및 이들의 임의의 조합들 중 하나 또는 그 이상을 가질 수 있다. 본 발명에 있어서 유용한 구부러짐 구조들은, 예를 들면, 코일화된(coiled) 형태, 주름진 형태, 베클링된 형태 및/또는 웨이브진(즉, 웨이브 모양을 갖는) 구성으로 제공될 수 있다.

[0079] 인장 가능한 구부러짐 상호 접속부들과 같은 구부러짐 구조들은 폴리머 및/또는 탄성 기판과 같은 플렉서블 기판에, 상기 구부러짐 구조가 변형되어 있는 형태로 결합될 수 있다. 일부 구현예들에 있어서, 구부러진 리본 구조와 같은 구부러짐 구조는 일부 응용들에 대하여 바람직한 구현예들에서 약 30%보다 작거나 같은 변형을, 또는 약 10%보다 작거나 같은 변형을, 약 5%보다 작거나 같은 변형을, 및 약 1%보다 작거나 같은 변형을 이룬다. 일부 구현예들에 있어서, 구부러진 리본 구조와 같은 구부러짐 구조는 약 0.5% 내지 약 30%의 범위로부터 선택된 변형, 약 0.5% 내지 약 10%의 범위로부터 선택된 변형, 약 0.5% 내지 약 5%의 범위로부터 선택된 변형을 이룬다. 선택적으로, 인장 가능한 구부러짐 상호 접속부들은 그 자체가 플렉서블하지 않은 기판을 포함하여 장치 구성 부품의 기판인 기판에 결합될 수 있다. 상기 기판 그 자체는 편평하거나, 실질적으로 편평하거나, 굴곡지거나, 날카로운 가장자리, 또는 이들의 임의의 조합일 수 있다. 인장 가능한 구부러진 상호 접속부들은 이들 복잡한 기판 표면 형태들 중의 임의의 하나 또는 그 이상에 전사하기 위해 이용될 수 있다.

[0080] "열적 접촉(thermal contact)"은 전도와 같이 고온 물질로부터 저온 물질로 실질적인 열전달이 가능한 두 물질들의 능력을 가리킨다. 기판 위에 놓인 구부러진 구조들은 상기 기판과 열적 접촉을 이루는 영역들(예를 들면, 결합 영역들)과 열적 접촉을 이루지 않는 다른 영역들(예를 들면, 상기 기판으로부터 절연되거나 및/또는 물리적으로 이격된 영역들)을 제공하는 데 특히 유용하다.

[0081] 상호 접속부들은 임의의 수의 기하 구조들 또는 형태들을, 상기 기하 구조들 또는 형태들이 상기 상호 접속부의 파손 없이 구부림 또는 인장되는 것을 용이하게 하는 한 가질 수 있다. 일반적인 상호 접속부의 기하 구조는 "베클링된(buckled)" 또는 "웨이브진(wavy)" 것으로 설명될 수 있다. 일 측면에 있어서, 그러한 기하 구조는, 상기 상호 접속부의 부분들은 상기 기판에 결합되고 상기 결합된 부분들 사이의 영역들은 결합되지 않았기 때문에, 하부에 놓인 기판의 치수의 변화가 상기 상호 접속부에 베클(buckle)들 또는 웨이브들을 생성하도록 하부에 놓인 변형 가능한 기판에 힘을 작용하여 상기 상호 접속부에 힘(예를 들면 변형)을 작용함으로써 얻어질 수 있다. 따라서, 개별 상호 접속부는 기판에 결합된 단부들 및 상기 단부들 사이의, 기판에 결합되지 않은 굴곡진 중앙 부분에 의하여 정의될 수 있다. "굴곡진(curved)" 또는 "베클링된(buckled)"은 상기 중앙 부분에 하나 또는 그 이상의 추가적인 결합 영역들을 갖는 상호 접속부에 의하는 것과 같이 비교적 복잡한 형태들을 가리킨다. "호-모양의(arc-shaped)"는 진폭을 갖는 일반적인 사인 곡선 형태를 가리키며, 여기서 상기 진폭은 상호 접속부와 상기 기판 표면 사이의 최대 이격 거리에 대응된다.

[0082] 상기 상호 접속부는 임의의 단면 형태를 가질 수 있다. 상기 상호 접속부의 한 형태는 리본-모양의 상호 접속부이다. "리본(ribbon)"은 두께와 폭을 갖는 실질적으로 직사각형-모양의 단면을 가리킨다. 구체적인 치수들은 원하는 상기 상호 접속부를 통하는 전도도, 상기 상호 접속부의 조성, 및 이웃하는 장치 구성 부품들을 전기적으로 연결하는 상호 접속부들의 수에 의존한다. 예를 들면, 이웃하는 구성 부품들을 연결하는 브리지 구성의

상호 접속부는 이웃하는 구성 부품들을 연결하는 단일 상호 접속부와 상이한 치수를 가질 수 있다. 따라서, 상기 치수들은 약 10  $\mu\text{m}$  내지 1 cm 사이의 폭들, 및 약 50 nm 내지 1 사이의 두께들과 같이, 또는 약 0.001 내지 0.1 사이의 범위의 두께에 대한 폭의 비율, 또는 약 0.01인 두께에 대한 폭의 비율과 같이 적절한 전기 전도도가 생성되는 한, 임의의 적합한 값들을 가질 수 있다.

[0083] "엘라스토머성(elastomeric)"은 인장되거나 변형된 후, 실질적인 영구 변형 없이 자신의 원래 상태로 적어도 부분적으로 복원될 수 있는 폴리머성 물질을 가리킨다. 엘라스토머성 물질들은 통상 실질적으로 탄성의 변형들을 견딘다. 본 발명에서 유용한 전형적인 엘라스토머성 물질들은 엘라스토머류와 엘라스토머류의 복합 물질들 또는 혼합물들, 그리고 탄성을 보이는 폴리머들과 코폴리머들을 포함하지만 여기에 한정되는 것은 아니다. 일부 방법들에 있어서, 상기 엘라스토머 기판은 하나 또는 그 이상의 주축들(principle axes)을 따라 상기 탄성 기판의 팽창을 제공하는 메커니즘을 통해 사전-변형된다(prestrained). 예를 들면, 사전 변형은 반구형 표면을 편평한 표면으로 전환하기 위하여 반지름 방향의 신장을 포함하여 제 1 축들을 따라 상기 탄성 기판을 신장시킴으로써 제공될 수 있다. 선택적으로, 상기 탄성 기판은 여러 개의 축들을 따라 신장될 수 있으며, 예를 들면, 서로에 대하여 수직으로 위치하는 제 1 축 및 제 2 축을 따라 신장될 수 있다. 상기 탄성 기판의 신장을 제공하는 메커니즘을 통해 탄성 기판들을 사전 변형시키는 수단들은 구부림(bending), 롤링(rolling), 습곡화(flexing), 평탄화(flattening), 신장(expanding) 또는 상기 탄성 기판을 달리 변형시키는 것을 포함한다. 상기 사전 변형시키는 수단들은 상기 탄성 기판의 온도를 상승시키고, 그에 의하여 상기 탄성 기판의 열팽창을 제공함으로써 제공된 사전 변형도 포함한다. 본 발명에 유용한 엘라스토머들은 열가소성 엘라스토머류, 스티렌계(styrenic) 물질들, 올레핀계 물질들, 폴리올레핀, 폴리우레탄 열가소성 엘라스토머류, 폴리아미드류, 합성 고무들, PDMS, 폴리부타디엔, 폴리이소부틸렌, 폴리(스티렌-부타디엔-스티렌), 폴리우레탄류, 폴리클로로프렌 및 실리콘(silicone)류를 포함할 수 있지만 여기에 한정되는 것은 아니다.

[0084] 변형(strain)은 길이가  $L$ (휴지기)로부터  $L + \Delta L$ (힘이 가해진 상태)로 변화된 것에 대하여  $\varepsilon = \Delta L/L$ 로 정의된다. 여기서,  $\Delta L$ 은 휴지기로부터 변위된 거리이다. 축방향 변형은 변위  $\Delta L$ 을 생성하기 위해 상기 기판의 축에 가해진 힘을 가리킨다. 변형은 구부림 힘, 압축 힘, 전단(shear) 힘, 및 이들의 임의의 조합과 같은 다른 방향으로 작용되는 힘들에 의해서도 생성된다. 변형 또는 압축은 굴곡진 표면을 편평한 표면으로 인장함으로써 또는 그 반대로 함으로써 생성될 수도 있다. "변형의 수준(level of strain)"은 변형의 크기를 가리키며, 음수(압축에 대응)로부터 0으로(릴랙스 상태) 양수(신장 또는 인장에 대응)까지의 범위를 가질 수 있다.

[0085] "영 모듈러스(Young's modulus)"는 물질, 장치 또는 층의 기계적인 성질로서, 주어진 물체에 대하여 변형에 대한 응력의 비를 가리킨다. 영 모듈러스는 다음 표현에 의하여 제공될 수 있다.

[0086] <수학식 2>

$$E = \frac{\text{(응력)}}{\text{(변형)}} = \left( \frac{L_0}{\Delta L} \times \frac{F}{A} \right)$$

[0087] 여기서,  $E$ 는 영 모듈러스이고,  $L_0$ 은 평형 길이이고,  $\Delta L$ 은 가해진 응력 하에서의 길이 변화이고,  $F$ 는 가해진 힘이고,  $A$ 는 힘이 가해지는 면적이다. 또한, 영 모듈러스는 하기 수학식 3을 통해 라메 상수들(Lame constants)의 항들로도 표현될 수 있다.

[0089] <수학식 3>

$$E = \frac{\mu(3\lambda + 2\mu)}{\lambda + \mu}$$

[0090] 여기서,  $\lambda$ 와  $\mu$ 는 라메 상수들이다. 영 모듈러스가 높은 것(또는 "고 모듈러스")과 영 모듈러스가 낮은 것(또는 "저 모듈러스")은 주어진 물질, 층 또는 장치에서 영 모듈러스의 크기를 상대적으로 기술하는 것이다. 본 발명에 있어서, 영 모듈러스가 높은 것은 영 모듈러스가 낮은 것에 비하여 일부 응용에 있어서는 약 10배 더 큰 것이 바람직하고, 다른 응용들에 있어서는 약 100배 더 큰 것이 더욱 바람직하고, 또 다른 응용들에 있어서는 약 1000배 더 큰 것이 더더욱 바람직하다. 복잡한 표면 모양들은 공간적으로 변화하는 영 모듈러스를 갖는 엘라스토머를 중합함으로써 및/또는 다중 층들을 갖는 엘라스토머를 상이한 탄성을 지니는 다양한 위치들에 적층함으로써 얻어진다.

- [0092] 압축은 여기서 변형과 유사한 방식으로 사용되지만,  $\Delta L < 0$ 이 되도록 기판의 특성 길이 또는 부피를 감소시키게 작용하는 힘을 특히 가리킨다.

- [0093] "파괴됨(fracturing)" 또는 "파괴(fracture)"는 상기 상호 접속부가 실질적인 전기 전도를 할 수 없도록 하는 상기 상호 접속부 내의 물리적 파손을 가리킨다.

- [0094] "결합 위치들의 패턴(pattern of bond sites)"은 지지된 상호 접속부가 기판과의 결합 영역들 및 비결합 영역들을 갖도록, 결합 수단들을 지지 기판 표면에 및/또는 상기 상호 접속부들에 공간적으로 적용하는 것을 가리킨다. 예를 들면, 그 단부가 상기 기판에 결합되고, 중앙 부분은 결합되지 않은 상호 접속부. 상기 결합되지 않은 영역이 두 개의 구별되는 중앙 부분들로 나뉘어질 수 있도록, 중앙 부분 내에 추가적인 결합 위치를 제공함으로써 추가적인 모양의 조절이 가능하다. 결합 수단들은 접착제들, 접착 전구체들, 용접, 광 리소그래피, 광경화가 가능한 폴리머를 포함할 수 있다. 일반적으로, 결합 위치들은 다양한 기술들에 의하여 패터닝될 수 있고, 기판과 구조물(예를 들면, 상호 접속부) 사이에 강한 접착력을 제공할 수 있는 표면-활성화된( $W_{act}$ ) 면적들과 접착력이 비교적 약한 표면-비활성화된( $W_{in}$ ) 면적들의 항들로 표현될 수 있다. 접착 패터닝이 선들로 된 기판은  $W_{act}$ 와  $W_{in}$ 의 치수들의 항들로서 표현될 수 있다. 그들 변수들은 사전 변형의 크기  $\epsilon_{pre}$ 와 함께 상호 접속부의 기하 구조에 영향을 미친다.

- [0095] "공간적 변화(spatial variation)"는 표면을 따라 변화하는 크기를 갖는 파라미터를 가리키고 구성 부품 양각 구조물들의 2차원 제어를 제공하고, 그에 의하여 장치 또는 장치 구성 부품의 구부림 가능성(bendability)에 공간적 제어를 제공하기 위하여 특히 유용하다.

- [0096] "탄소 나노물질(carbon nanomaterial)"은 탄소 원자들을 포함하는 구조물들의 부류를 가리키고, 1 나노미터와 1 마이크론 사이에서 적어도 하나의 치수를 갖는다. 일 구현예에서, 상기 탄소 나노물질의 적어도 하나의 치수는 2 nm와 1000 nm 사이이다. 탄소 나노물질들은 단일벽 나노튜브류(SWNTs: single walled nanotubes), 다중벽 나노튜브류(MWNTs: multiwalled nanotubes), 그라파이트, 그래핀(graphene), 탄소 섬유류, 탄소 필름류, 탄소 휀스커류(whiskers), 및 다이아몬드, 및 이들의 모든 유도체들과 같은 탄소의 동소체들을 포함한다.

- [0097] "공간적으로 정렬된(spatially aligned)" 것은 둘 또는 그 이상의 구조들의 서로에 대하여 정의된 위치들 및/또는 배향들(orientations)을 가리킨다. 공간적으로 정렬된 구조들은 서로에 대하여 사전 선택된(preselected), 예를 들면, 1 마이크론 이내로 사전 선택되고, 일부 응용들에 대하여는 500 나노미터 이내로 바람직하게 사전 선택되고, 일부 응용들에 대하여는 50 나노미터 이내로 더욱 바람직하게 선택된 위치들 및/또는 배향들을 가질 수 있다.

- [0098] "이종 반도체 요소들(heterogeneous semiconductor elements)"은 하나 또는 그 이상의 다른 물질들 또는 구조들과 결합된 반도체를 포함하는 다중 구성 부품 구조들이다. 본 설명의 문장에서 다른 물질들 또는 구조들은, 상이한 화학 조성들 및/또는 물리적 상태들(예를 들면, 결정질, 반결정질 또는 비결정질 상태)을 지니는 물질들 및/또는 구조들과 같이 이들이 결합되는 반도체와 상이한 원소들, 분자들, 및 착화합물들, 용접물 및 이들의 임자들을 포함할 수 있다. 본 발명의 본 측면에 있어서 유용한 이종 반도체 요소들은 무기 반도체 구조와 결합된 다른 반도체 물질들을 포함하며, 상기 다른 반도체 물질들은 도핑된 반도체들(예를 들면, N-형 및 P-형 도편트들) 및 탄소 나노물질들 또는 그들의 필름들, 유전 물질들 및/또는 구조들, 및 도전성 물질들 및/또는 구조들을 포함한다. 본 발명의 이종 반도체 요소들은 균일하게 도핑된 반도체 구조들과 같이 공간적으로 균일한 조성을 갖는 구조들을 포함하고, 그리고 1차원, 2차원 또는 3차원 상의 공간적으로 농도가 변화하는 도편트를 갖는 반도체 구조와 같이 공간적으로 불균일한 조성들을 갖는(즉, 반도체 요소 내에서 공간적으로 불균일한 도편트 분포) 구조들을 포함한다.

- [0099] 본 발명은 다음의 비한정적인 실시예들에 의하여 더 이해될 수 있다. 여기에 인용된 모든 참조문헌들은 여기에 개시된 바와 불일치하지 않는 범위 내에서 여기에 인용되어 통합된다. 여기의 설명들은 많은 구체적인 사항들을 포함하지만, 이들은 본 발명의 범위를 한정하는 것으로 해석되어서는 안되며 본 발명의 현재 바람직한 구현 예들의 일부의 예시를 제공하는 것일 뿐인 것으로 해석되어야 한다. 따라서, 본 발명의 범위는 주어진 실시예들에 의해서리기보다는 첨부된 특허청구범위와 그들의 균등 범위에 의하여 결정되어야 한다.

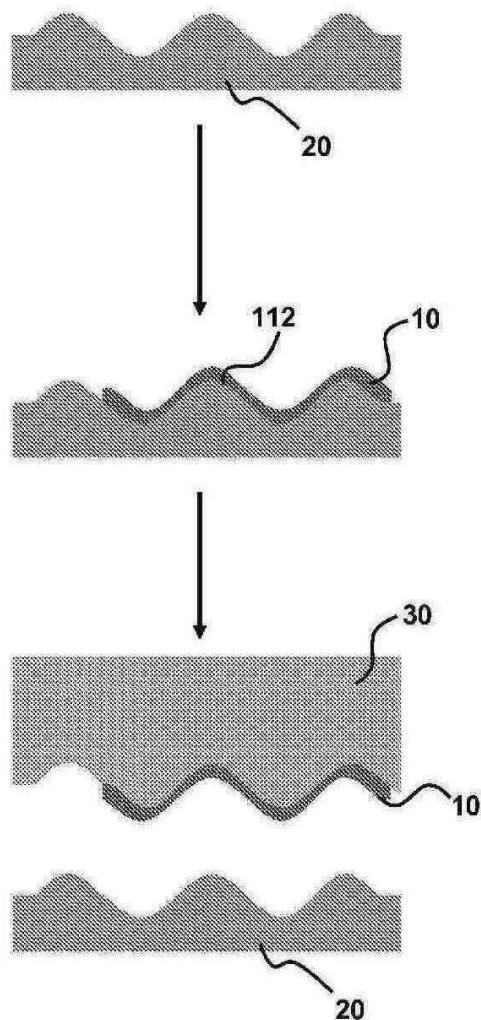

- [0100] 베클링되거나 또는 웨이브진 상호 접속부들을 제조하기 위한 방법의 하나가 도 1에 개괄적으로 요약되어 있다. (상호 접속부가 될 금속 구조물과 같은) 금속 구조물(10)이 기판(20) 위에 제공된다. 접촉하는 상기 금속 구조물 및/또는 기판 표면들은 광 리소그래피에 의하거나 또는 새도우 마스크로 접착도가 감소하도록 선택적으로 처

리된다. 상기 구조물(10)과 상기 기판(20) 사이에는 마이크로 머시닝(micromachining), 식각 및/또는 기계적 스크라이빙(scribing)과 같은 것에 의하여 분리부(크랙)(25)가 도입된다. 상기 금속 구조물(10)은 유연한 (compliant) 엘라스토머 스템프(30)로 회수된다. 상기 스템프(30)의 후속적인 변형은 상기 금속 구조물(10)에 웨이브지거나(wavy) 또는 베클링된 기하 구조(40)를 생성한다. 상기 베클링된 기하 구조(40)를 생성하는 것은 상기 금속 구조물(10)이 회수될 때 변형되고 적용된 장력을 후속적으로 해제하는 스템프(30)에 의하여, 또는 상기 금속 구조물이 회수된 후에 스템프(30)를 압축하는 것에 의하여 제공된다.

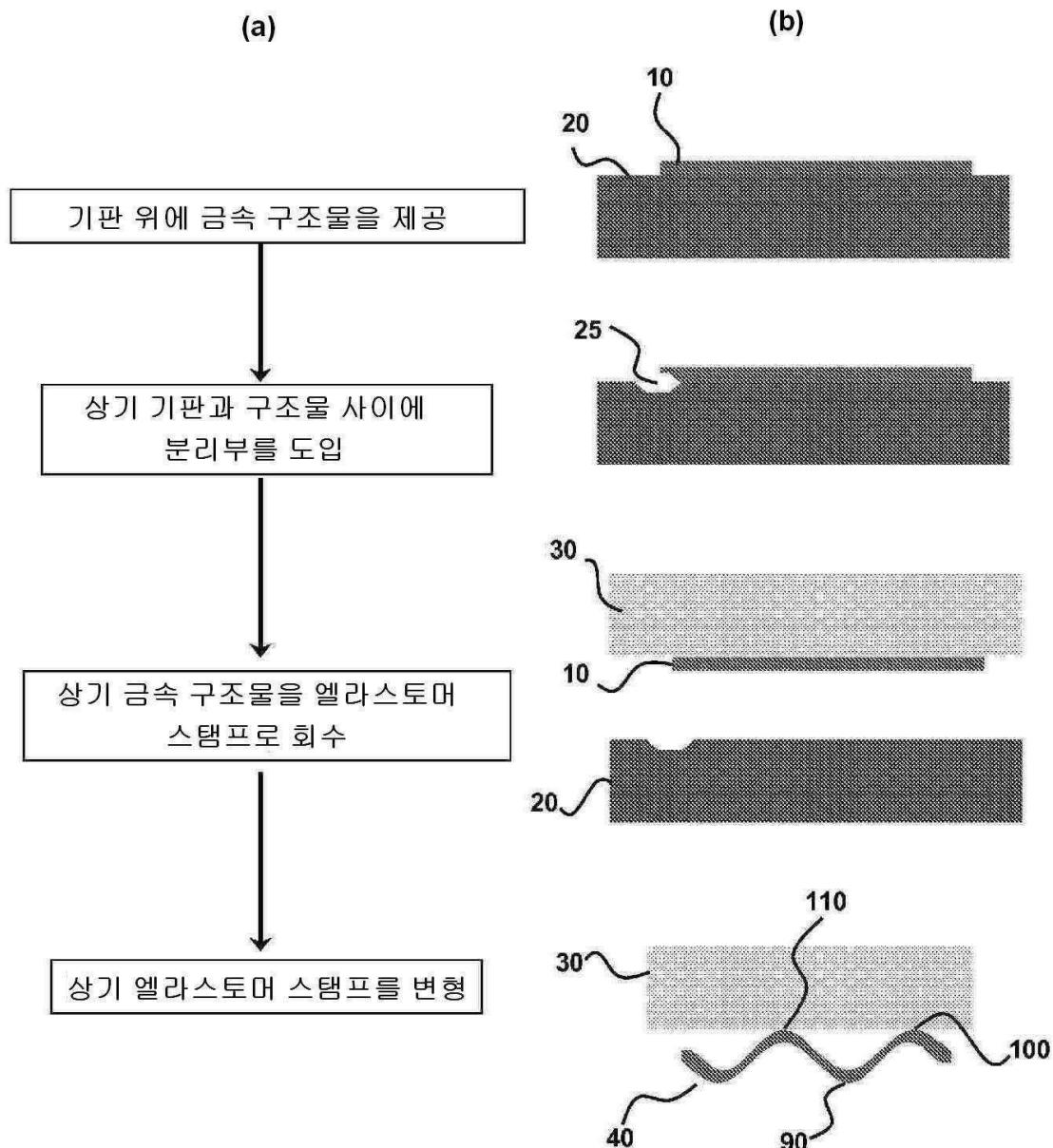

[0101] 도 1에 요약된 방법에 의하여 생성된, 베클링되거나 웨이브진 금속 구조물의 한 실시예가 도 2에 도시된다. 도 2는 인장 가능한, 웨이브진/베클링된 전기 상호 접속부(40)의 사진이다. 상기 상호 접속부(40)는 경질 기판으로부터 사전-변형되고 인장 가능한 PDMS 고무 기판(30) 위로 회수하고, 이어서 변형을 해제하고 그에 의하여 베클링을 유발함으로써 형성된다.

[0102] 웨이브지고 인장 가능한 전극들 및/또는 상호 접속부들을 생성하기 위한 방법이 도 3에 제공된다. 도 3의 (a)에 나타낸 바와 같이, 웨이브진 구조물들(22)이, 예를 들면, 마이크로 머시닝 공정들과 같은 것에 의하여 기판(20) 위에 준비된다. 웨이브진 구조물들(22)을 지닌 표면을 갖는 상기 기판(20)은 대응하는 웨이브진 표면(32)을 갖는 엘라스토머 스템프들(30)을 몰딩하기 위한 마스터로서의 역할을 한다. 금속 구조물들(10)은 새도우 마스크를 통한 증발(evaporation) 및/또는 전착(electrodeposition)과 같은 것에 의하여 상기 웨이브진 표면(32) 위에 증착된다.

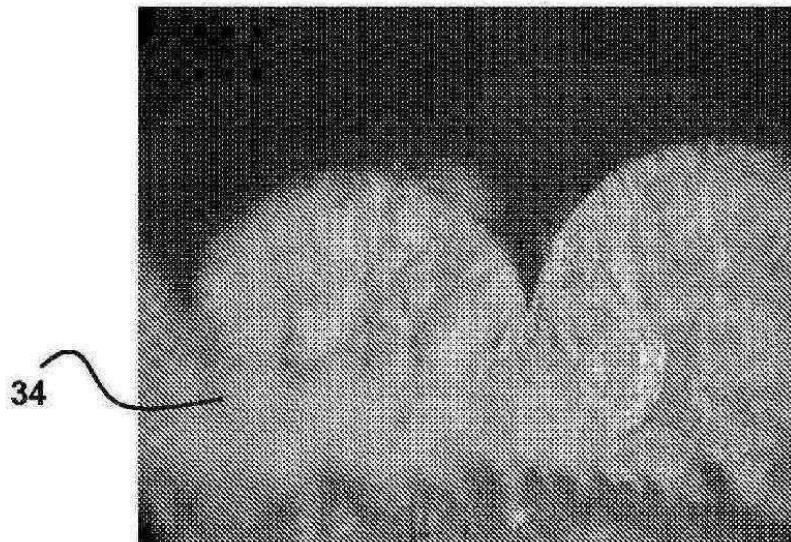

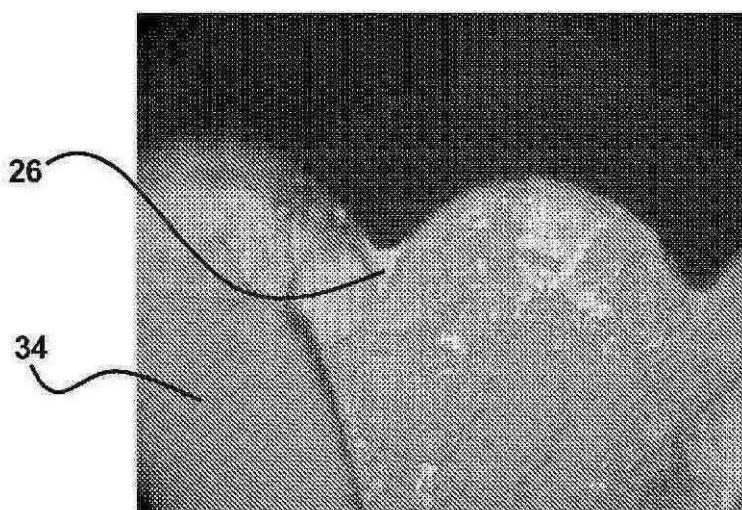

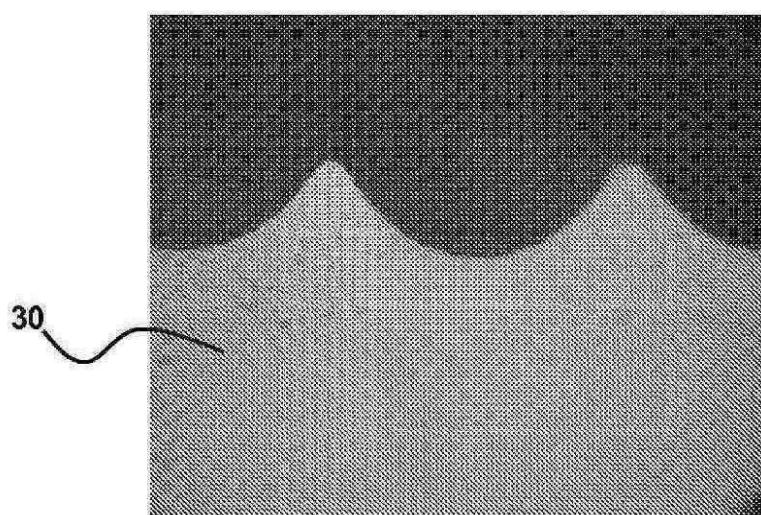

[0103] 도 4는 매끈하게 웨이브진 엘라스토머 기판을 제조하기 위한 한 방법을 제공한다. 비등방성 Si (1 0 0)의 식각은 날카로운 가장자리(24)들을 갖는 기판(20)을 제공한다(도 4의 (b) - 최상부 패널). PR의 스피너는 기판(20)의 날카로운 가장자리를 갖는 계곡들(24) 내에 PR(26)을 증착함으로써 상기 날카로운 가장자리를 갖는 계곡들을 매끈하게 한다. 엘라스토머 스템프(34)가 기판(20) 위에 주조된다. 스템프(34)는 날카로운 가장자리를 갖는 리세스 구조물들을 갖는다. 날카로운 가장자리를 갖는 피크들을 갖는 스템프를 생성하기 위하여 스템프(34) 위에 제 2 엘라스토머 스템프(36)가 주조된다. 스템프(36)는 SU-8(50)로 엠보싱되며, 적절할 때 경화된다. 스피너 PR(26)은 (50)의 날카로운 가장자리를 갖는 계곡들을 매끈하게 한다. 엘라스토머 기판(30)은 매끈한 계곡들을 갖는 (50) 위에 주조된다. 기판(30)은 분리되어 웨이브지고 매끈한 표면(32)을 드러낸다.

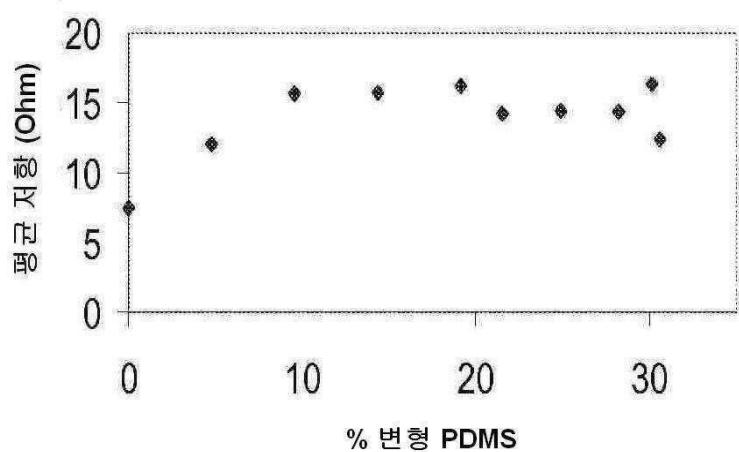

[0104] 도 54는 웨이브진 마스터 위에 증착하고, 이어서 상기 마스터 위에 스템프를 주조하고, 상기 스템프를 경화시키고, 그에 의하여 전극들을 해제(release)와 함께 마스터로 전사하는 것에 의하여 웨이브지고 인장 가능한 전극들을 제조하는 방법의 하나를 요약한다. 도 55는 도 4에 나타낸 방법들을 도 54에 나타낸 방법들과 결합함으로써 제조되는 웨이브진 PDMS 위의 인장 가능한 금속 전극들(Au, 300 nm 두께)의 이미지들을 나타낸다. 계면(112)은 금속 구조물(10)과 기판(20) 사이에 도시된다. 계면(112)은 하부 패널에 도시된 스템프(30)에 의하여 금속 구조물들(10)의 제거를 용이하게 하는 물질을 포함할 수 있다. 간단히 말해서, 한 방법은 다음을 이용한다: 미리 세정된 2"×3" 유리 슬라이드 위에 유리 표면이 완전히 덮이도록 SU-8 10의 얇은 코팅을 스피너온(spin on)한다. 슬라이드/SU-8을 원하는 웨이브진 표면 구조물(매끈한 계곡과 날카로운 피크들)들을 갖는 PDMS 스템프와 접촉시키고, 모든 공기 방울들이 제거되도록 서서히 압력을 가한다. 스템프/몰드 구조물을 UV 램프 하에서 앞면에 대하여 30초 동안 플래시(flash) 경화시키고, 뒤집어서 뒷면에 대하여 추가로 40초 동안 경화시킨다. 경화 후에는 핫 플레이트 위에서 65 °C로 5분 동안 베이킹을 한다. 베이킹을 한 후에는 샘플이 실온까지 냉각되도록 한 후 SU-8 몰드를 PDMS 마스터로부터 벗겨서 분리한다. 이제 SU-8은 날카로운 가장자리를 갖는 계곡들을 갖는 웨이브진 표면 양각 구조를 가질 것이다. 이를 계곡들을 매끈하게 하기 위하여 SU-8 2의 일부분을 더 물은 SU-8의 일부분과 혼합하고, 높은 RPM으로 90초간 스피너온 한다. 20초 동안 UV광에 노광시켜 경화시키고, 3분 동안 65 °C에서 포스트 베이킹을 한다. 일단 냉각되면, 금속 라인들 또는 콘택들이 전착, 광 리소그래피, 및 식각/리프트-오프, 및/또는 새도우 마스크를 통한 증발을 통해 증착된다. SU-8 위의 금속을 MPTMS로 1시간 동안 처리하고, 그런 후 그 위에 엘라스토머 기판을 주조한다. PDMS는 제거될 때, 전사된 금속 구조물들과 함께 매끈하게 된 피크들과 계곡들을 갖는 웨이브진 표면 양각 구조물을 갖는다. 도 55는 도 54에 요약된 공정에 의하여 제조된 웨이브지고 인장 가능한 전극의 사진이다. 또한, 도 55는 상기 인장 가능하고 웨이브진 금속 전극들의 측정된 전기 저항 데이터를 적용된 인장 변형(30%까지)의 함수로 제공한다.

[0105] 도 4에 요약된 방법에 의하여 제조된 매끄럽게 웨이브진 PDMS 기판(30)의 실시예가 도 5에 제공된다. 장치 구성 부품(60)은 웨이브진 기판(30)의 웨이브진지 않은 영역(예를 들면, 실질적으로 편평한 부분)에 지지되어 원하는 바에 따라 상호 접속부(10)와 연결될 수 있다.

[0106] 날카로운 가장자리를 갖는 계곡 또는 리세스 구조 내에 스무딩 층(smoothing layer)을 스피너 코팅하는 실시예가

도 6에 도시된다. 날카로운 가장자리를 갖는 기판(34)(도 6a)은 매끈하게 웨이브진 기판을 생성하기 위하여 광경화성 에폭시(26)을 스판-코팅함으로써 매끈하게 된다. 도 6b의 기판 위에 PDMS 스템프를 주조하고 이어서 상기 기판(34)으로부터 상기 스템프(30)을 제거함으로써, 매끈하게 웨이브진 표면(32)을 갖는 엘라스토머(예를 들면, PDMS) 스템프(30)가 얻어진다.

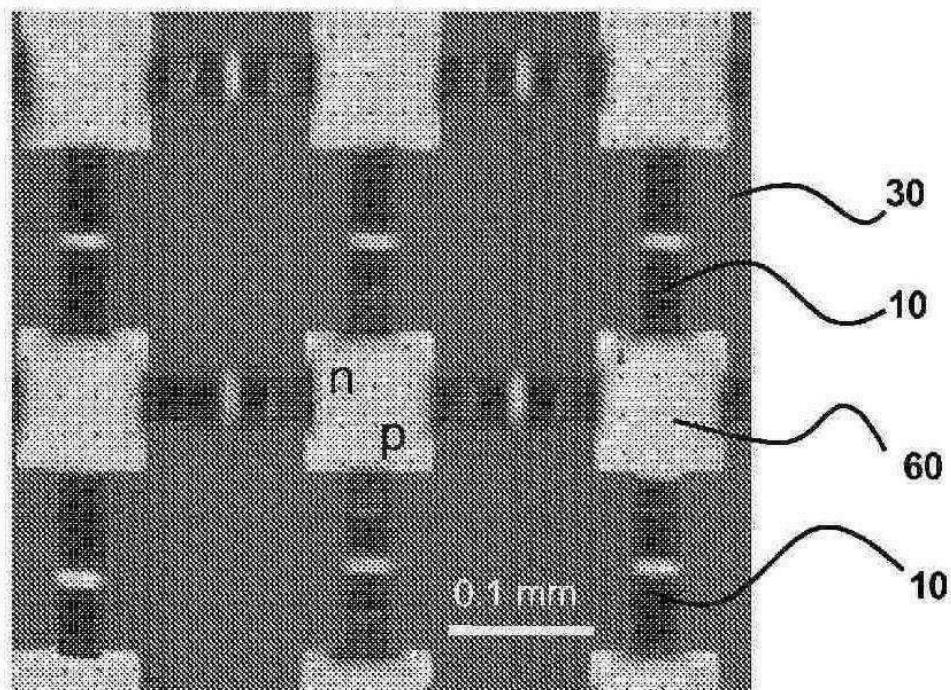

[0107] 도 7은 인장 가능한 전극의 사진들이다. 도 7a는 웨이브진 표면(32)을 갖는 엘라스토머 기판(30)의 단면 사진이다. 도 7b는 상기 웨이브진 엘라스토머 기판 표면(32) 위에 금속(10)의 증발에 의하여 제조된 전극을 위에서 본 현미경 사진이다. 상기 이미지의 초점면(focal plane)은 웨이브진 양각 구조물의 피크들 위에 있다. 도 7c에서 상기 초점면은 상기 웨이브진 양각 구조물의 계곡 위에 있고, 상기 금속 상호 접속부(10)는 상기 전극(250)과 전기적으로 접촉하고 있다. 상기 인장 가능한 전극은 매끈하게 웨이브진 엘라스토머 기판 위에 새도록 마스크를 통한 증발에 의하여 증착된다. 이 실시예에서, 상기 전극(250)은 장력(tension)에 있어서 약 10%까지 인장하는 동안 상호 접속부들(10)을 통한 전도도와 접속도(connectivity)을 유지한다.

[0108] 여기에 개시된 방법들 및 장치들은, 예를 들면, 인장 가능한 수동 매트릭스 LED 디스플레이(도 8 참조)를 포함하여 다양한 전자 장치들을 제조하기 위하여 사용될 수 있다. 웨이브진 전극들(예를 들면, 상호 접속부들(10) 및 콘택 패드(70))은 두 개의 엘라스토머 기판들(30) 위에 패터닝된다. 장치 구성 부품(60)(이 경우에 있어서는 ILED 픽셀들)은 전사 인쇄(transfer printing)에 의하여 웨이브진 전극들 위에 콘택 패드(70)에서 패터닝된다. 상기 두 기판들(30)은 상기 상호 접속부(10)들이 상이한 방향으로(본 실시예에서는 수직으로) 달리도록 그에 알맞게 조립된다. 이러한 수동 매트릭스 LED 디스플레이의 2-D 기계적 인장 가능성은 도 9에 도시된다. 상기 디스플레이에는 일축적으로(uniaxially) 및 이축적으로(biaxially) 인장될 수 있을 뿐만 아니라, 파손 없이 실질적인 구부림이 가능하다. 그러한 다축(multi-axial) 구부림은 굴곡진 전자 장치들을 생산하고 또한 스마트 전자 패브릭(fabric) 또는 디스플레이들에 통합하기 위해 전자 장치들을 굴곡진 표면들에 몰딩할 수 있는 능력을 제공한다.

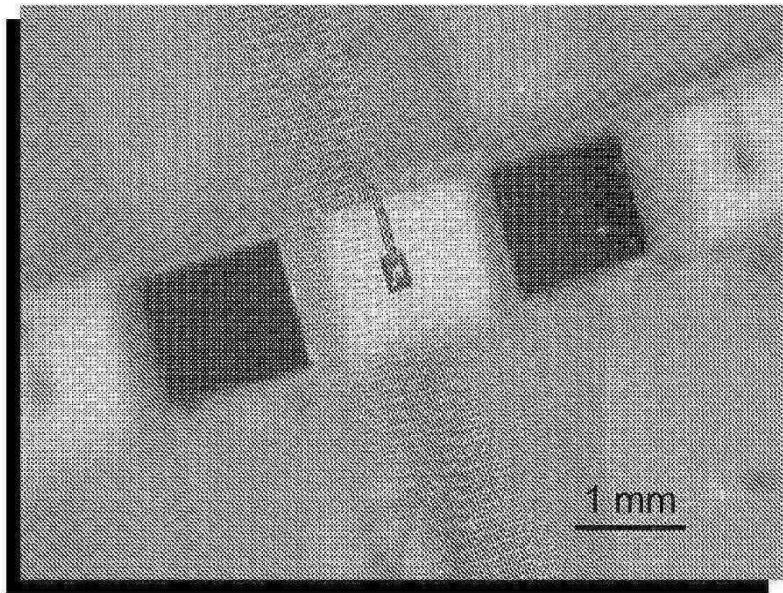

[0109] 그러한 굴곡진 전자 장치의 한 실시예가 도 10에 제공된다. 도 10은 구면의 국면을 이루는 렌즈 위에 분포된 무기 광 다이오드 어레이를 포함하는 "인공 눈(artificial eye)"을 나타낸다. 상기 인공 어레이의 네 가지 상이한 관점들이 도시된다. 인장 가능한 평면 전자 장치들을 위한 요건은 도 11에 개념적으로 도시된다. 구의 표면 주위에 평면 시트를 싸기 위하여 상기 시트는 두 방향 이상으로 인장되어야 한다.

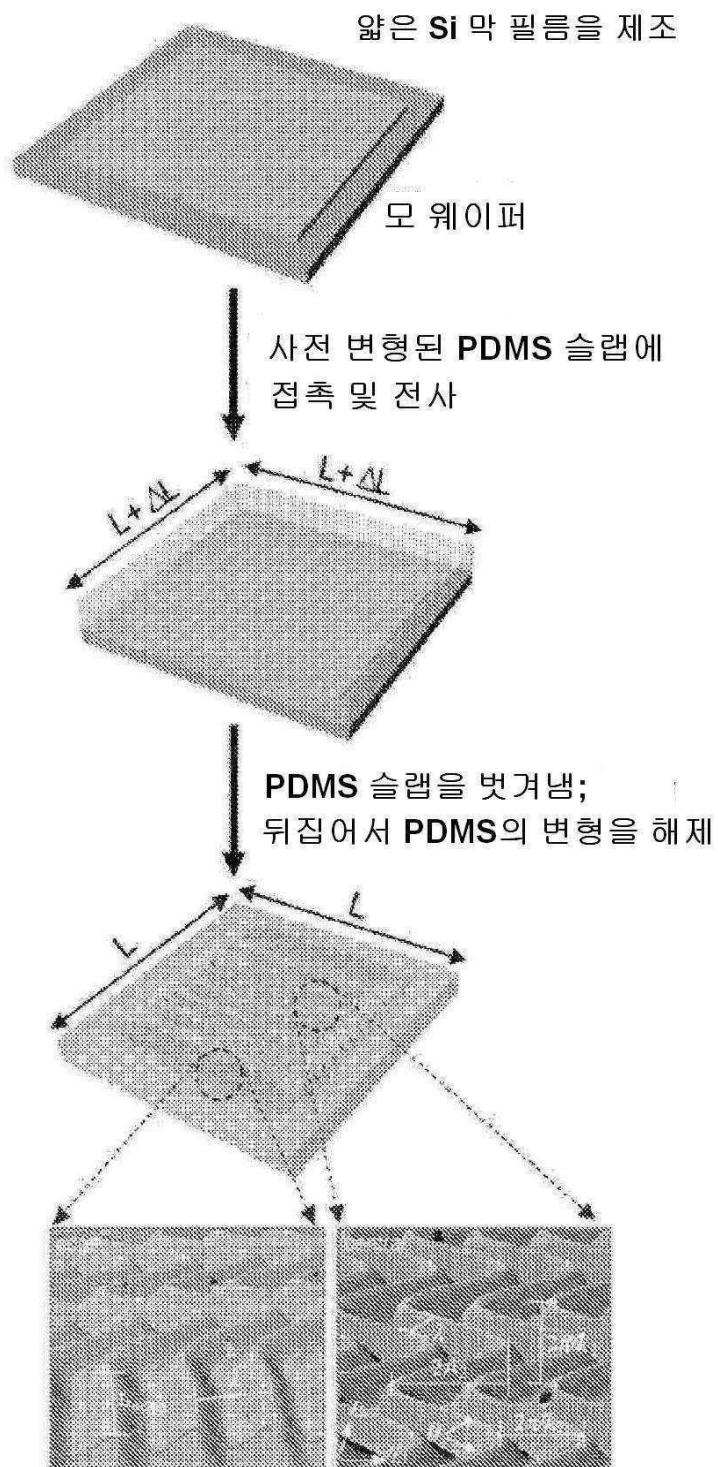

[0110] 도 12는 굴곡진 표면에 정합할 수 있는 인장 가능한 베클링된 반도체 어레이를 제조하기 위한 제조 방법이다. 얇은 Si 요소들은 패널 (i)에서 "모 웨이퍼(mother wafer)"로 도시된 바와 같이 기판 위에 Au 또는 Ti/Au의 선택적인 증착으로 제조된다. Si는 사전 변형되고(L+ $\Delta$ L로 표시) UVO 처리된 PDMS(패널 (ii))에 결합된다. 사전 변형은 도시된 바와 같이 두 방향으로 제공된다. 상기 결합은, 예를 들면, 상기 Si 요소, 상기 기판에, 또는 이들 둘 모두에 적용된 접착제와 같이 당 기술 분야에서 알려진 임의의 수단들에 의한다. 상기 결합 수단들은 상기 Si가 (변형 후에) 상기 기판과 물리적으로 접촉한 채 남아 있게 될 결합된 영역들과 상기 기판과 물리적 접촉을 하지 않는 구부러짐 구성인 다른 영역들(예를 들면, 상기 결합 영역들에서의 접착력에 비하여 상대적으로 약하게 결합되거나 또는 결합되지 않은 영역들)을 가지도록 선택된 패턴으로 적용된다. 상기 사전 변형된 기판은 상기 웨이퍼 기판으로부터 제거되어 반도체 어레이들(패널 (iii))의 편평한 그리드를 드러낸다. 상기 기판이 L+ $\Delta$ L로부터 L로 헐ックス됨과 함께, 상기 장치 구성 부품(60)(예를 들면, 반도체 Si 콘택 패드)은 상기 기판(30)에 결합된 채 남는 반면, 상기 상호 접속부(10)들은 상기 약하게 결합된 영역들(패널 (iv) 참조)에서 구부러짐 구성으로 베클링된다. 따라서, 베클링된 상호 접속부(10)들은 전체 어레이에 인장 가능성을 부여하고, 특히 구성 부품들(60) 사이의 전기적인 접촉을 파손하지 않으면서 구성 부품(60)의 다른 구성 부품들(60)에 대한 상대적인 운동의 능력을 부여하고, 그에 의하여 굴곡진 표면 또는 구부릴 수 있는 표면에 정합하는 능력을 제공한다.

[0111] 도 13은 단일 그리드 구성(140)(위쪽 두 패널들), 복수의 접속된 상호 접속부들(160)을 갖는 그리드 구성(아래쪽 왼쪽 패널), 및 꽃모양(floral) 구성(150)(아래쪽 오른쪽 패널)을 갖는 베클링되고 인장 가능한 실리콘 어레이의 광학 현미경 이미지를 제공한다. 이를 실시예들 각각에 있어서, 상호 접속부(10)는 중앙 부분에서 베클링되고, 상호 접속부의 단부들은 콘택 패드(70)에 부착된다. 상기 상호 접속부들과 콘택 패드(70)는 PDMS 기판(30) 위에 지지된다. 많은 상이한 상호 접속부의 기하 구조들의 근접 모습들은 도 14 내지 도 17에 더 제공된다. 도 14는 제 1 단부(100) 및 제 2 단부(110)와 함께 중앙 부분(90)을 갖는 기본적인 베클링되거나 또는 웨이브진 상호 접속부(10)를 보여 주는 전자 현미경 이미지들을 제공한다. 상기 중앙 부분은 구부러진 구성을 갖는다. 단부들(100 및 110)은 장치 구성 부품에 연결되며, 이 경우에 있어서는 장치 구성 부품과 전기적인 접촉을 형성할 수 있는 콘택 패드(70)에 연결된다. 상기 상호 접속부(10) 및 콘택 패드(70)는 엘라스토머 PDMS 기

판과 같은 기판(30) 위에 지지된다.

[0112] 도 15는 복수(둘)의 상호 접속부들(160)에 의하여 서로 연결된 이웃하는 장치 구성 부품들(예를 들면, 콘택 패드(70))의 전자 현미경 이미지이다. 도 15를 도 14와 비교하면 이웃하는 장치 구성 부품들(70)은 상기 전자 장치에 추가적인 유연성을 제공하기 위하여 하나 또는 그 이상의 상호 접속부들(10)에 의하여 서로 연결될 수 있음이 입증된다. 예를 들면, 비교적 큰 면적(footprint)을 갖는 장치 구성 부품 또는 콘택 패드(70)는 다중의 상호 접속부들에 의하여 다른 장치 구성 부품에 선택적으로 연결된다.

[0113] 도 16은 꽂모양 구성(150)의 상호 접속부들의 전자 현미경 이미지이다. 꽂모양 구성은, 그리드(grid) 구성과는 대조적으로, 세 이상의 길이 방향들(longitudinal directions)을 갖게 배향된 상호 접속부들을 갖는다. 본 실시예에 있어서, 콘택 패드(70)와 같은 장치 구성 부품이 대각선 방향으로 이웃하는 장치 구성 부품들과 접촉할 수 있도록 네 개의 구별되는 방향들이 있다. 본 실시예에 있어서, 상기 상호 접속부(10)는 장치 구성 부품(미도시)에 전기적으로 연결되고 그에 의하여 중앙 영역(90)을 각각 구부림 구성을 갖는 두 개의 비결합 영역들(92)로 나누는 상기 상호 접속부 단부(100)와 단부(110) 사이 내에 선택적인 결합 영역(102)를 갖는다.

[0114] 도 17은 브리지 구성(130)으로 배열된 상호 접속부들의 전자 현미경 이미지이다. 브리지 구성에 있어서, 세 또는 그 이상의 상호 접속부 단부들이 브리지 중앙 부분 퍼크(120)로부터 연장되어 나온다. 예를 들면, 결합되지 않은 영역에서 교차하는 두 개의 상호 접속부들은, 네 개의 상호 접속부 단부들이 그로부터 연장되는 퍼크(120)를 가져온다. 장치 구성 부품들이 엇갈리게 배열된 상황에 있어서, 상기 퍼크(120)는 그로부터 연장되는 세 개의 단부들을 가질 수 있다. 장치 구성 부품들 사이의 다중 상호 접속 연결의 경우에 있어서, 넷보다도 많은 단부들이 퍼크(120)로부터 연장될 수 있다.

[0115] 여기에 제공된 도면들 중 많은 도면들이 콘택 패드(70)인 장치 구성 부품을 보이지만, 여기서 청구되는 방법들 및 장치들은 인장 가능하고 따라서 형태 정합적인(shape-conforming) 전자 장치들을 제공하기 위하여 수많은 장치 구성 부품들을 연결할 수 있다. 예를 들면, 도 18은 장치 구성 부품(60)으로서, 엘라스토머 기판(30) 위에 지지된 베클링된 상호 접속부들(10)에 의하여 어레이 구성으로 다른 광 다이오드에 연결된 광 다이오드이다.

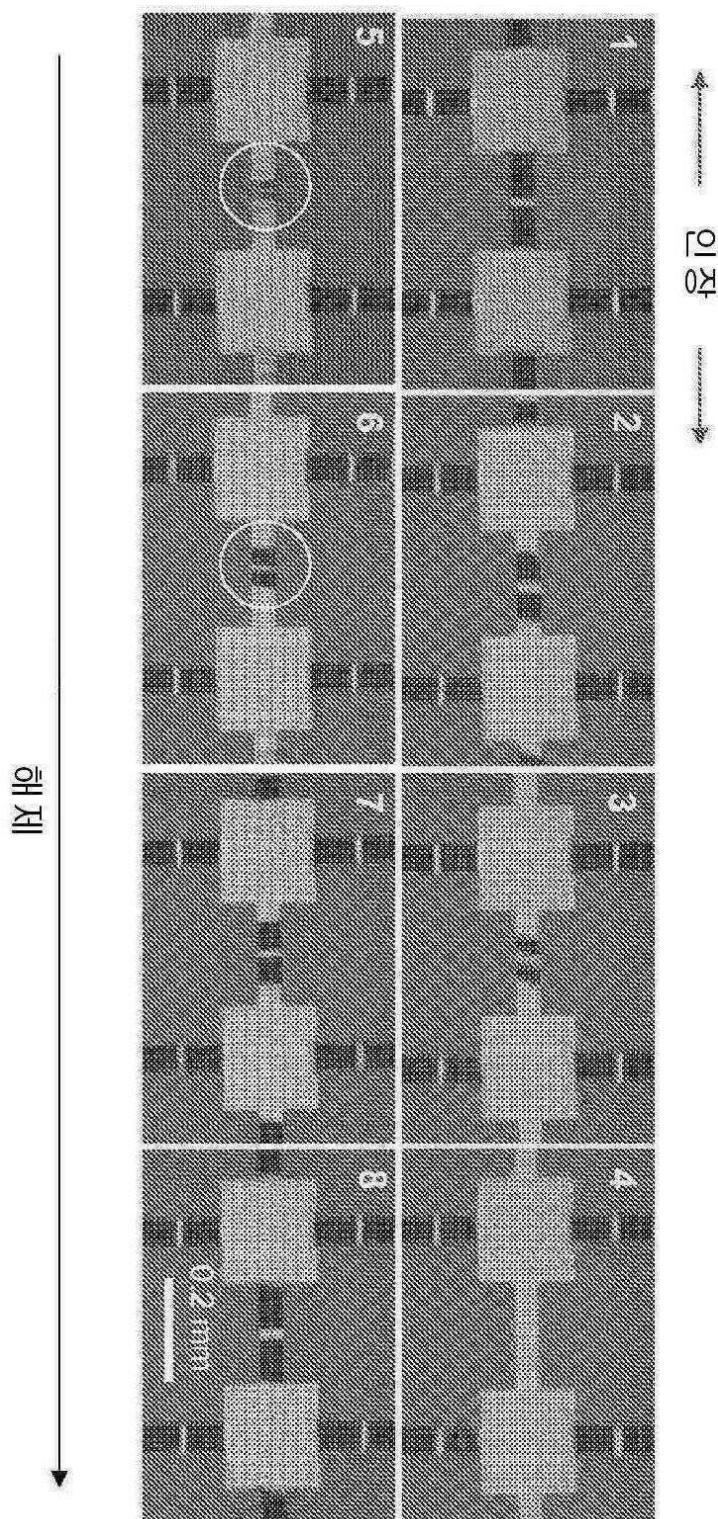

[0116] 도 19는 베클링된 실리콘 어레이의 1차원적으로 인장되는 거동을 묘사한다. 패널 (i)은 적용되는 변형력이 없는 베클링된 실리콘 어레이의 그림이다. (패널 (i)의 위의 화살표로 나타내어진 바와 같이) 인장력이 가해져서 상기 어레이를 한 방향으로 인장한다. 패널 (2) 내지 (4)에 나타낸 바와 같이, 상기 베클링된 상호 접속부는 편평하게 된다. 패널 (5)에서 상기 인장시키는 힘이 해제되면, 상기 어레이는 자신의 베클링된 구성으로 되돌아간다(패널 (6) 내지 패널 (8) 참조). 패널 (1)과 패널 (8)을 비교하면, 인장하기 전과 후의 베클 구성이 동일함을 보여주고 있으며, 이는 상기 과정이 가역적임을 나타낸다.

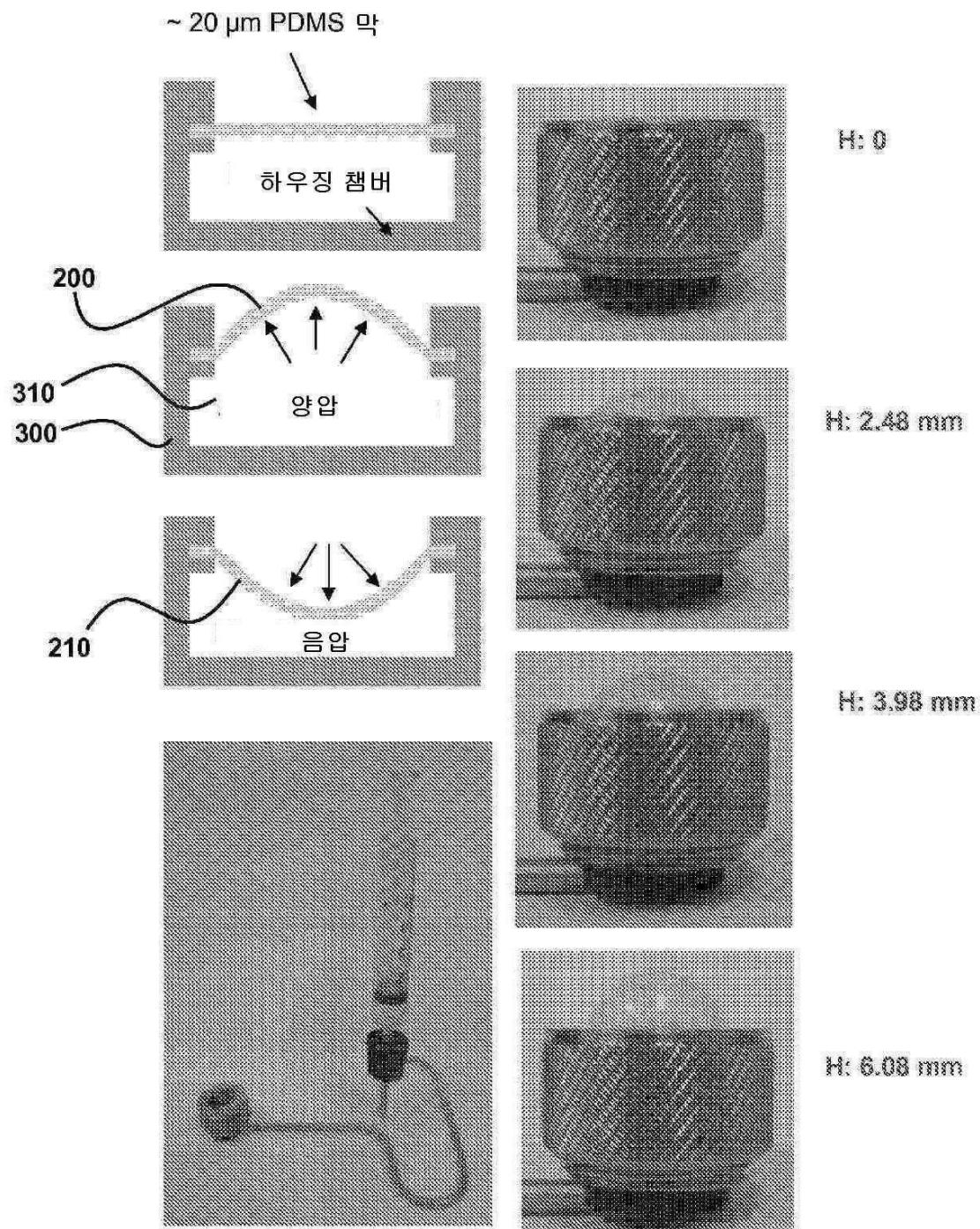

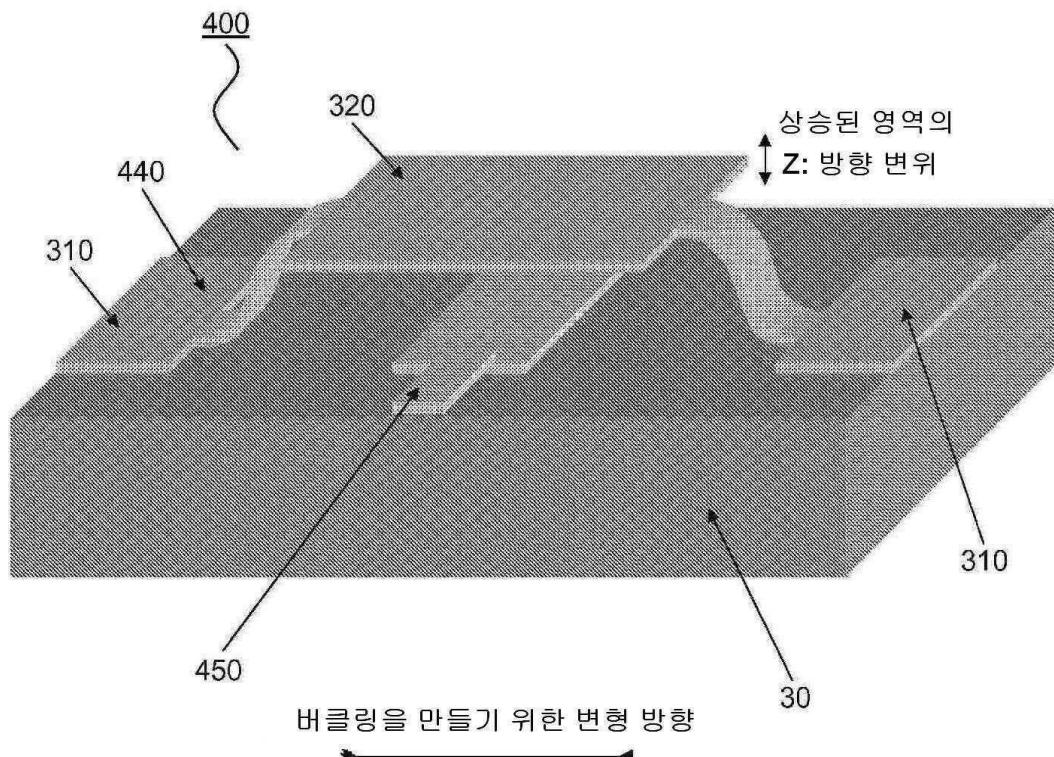

[0117] 장치 구성 부품들의 베클링된 어레이들은 경질 또는 비탄성적 곡률 표면들을 포함하는 굴곡 표면들에 용이하게 전사될 수 있다. 굴곡진 표면들에 정합 접촉을 용이하게 하기 위한 장치 및 방법의 한 실시예가 도 20의 베블 또는 풍선 스템프(400)에 의하여 제공된다. 이 실시예에서는 약 20  $\mu\text{m}$  두께의 PDMS 막인 엘라스토머 기판(30)은 하우징 캠버 및 내부를 향한 기판벽에 의하여 정의되는 캠버 부피(310)를 제공하는 하우징 캠버(300)에 고정된다. 양압(예를 들면, 외부 압력보다 높은 캠버(300) 내의 압력)을 적용하면 오목한 형태의 수용 기판과 정합적 접촉을 이를 수 있는 볼록(200) 기판 표면을 생성한다. 대조적으로, 음압은 볼록한 형태의 수용 기판과 정합적 접촉을 이를 수 있는 오목 표면(210)을 생성한다. 상기 기판의 국부적 탄성(예를 들면, 영 모듈러스)의 공간적인 조작은 복합적으로 굴곡진 기하 구조의 생성을 가능하게 한다. 도 20의 아래 왼쪽 패널은 캠버(310)에 가스를 도입하거나 또는 그로부터 가스를 제거하는 주사기에 의하여 하우징 부피(310) 내의 압력을 조절하기 위한 수단의 하나를 나타낸다. 상기 그림의 오른쪽에 있는 이미지들은 양압의 수준을 증가시킴에 따라 반응하는 PDMS 막의 상이한 곡률들이다. 엘라스토머 기판 위에 베클링된 상호 접속부들을 제공하기 위한 임의의 방법들과 장치들이, 굴곡진 기판으로의 전사 인쇄를 위한 장치들과 함께 이용될 수 있다.

[0118] 굴곡진 표면 위에 베클링된 상호 접속부 또는 팝-업 상호 접속부들을 생성하기 위한 다른 수단들이 도 21에 요약되어 있다. 굴곡진 부분을 적어도 갖는 엘라스토머 기판을 생성하기 위하여 형태를 갖는 표면 위에 얇은 엘라스토머 필름이 주조된다. 상기 기판이 굴곡진 표면과 편평한 표면 모두에 정합할 수 있도록, 상기 기판은 인장되어서 상기 표면을 편평하게 할 수 있다. 상기 편평한 스템프 위에 상호 접속부가 적용되고 인장력의 해제와 함께 상기 기판 표면은 릴랙스되어 굴곡진 기하 형태로 되돌아오고, 상기 상호 접속부에 변형이 생성되는데, 이는 상기 상호 접속부 중앙 부분의 팝-업에 의하여 수용된다.

[0119] 도 20에 나타낸 장치에 의하여 베클링된 실리콘 어레이를 "2차원적으로" 인장하는 실시예가 도 22에 제공된다.

이 실시예에 있어서, 상기 상호 접속부는 그리드 구성의 베클링된 상호 접속부 연결들을 복수개 포함한다. 상기 상호 접속부들은 290 nm 두께의 Si로 만들어진다. 초기에 편평한 베클링된 실리콘 어레이(위쪽 원쪽 이미지)는 하우징 내에 위치되고, 상기 어레이를 베를 또는 풍선 구성(예를 들면, 굴곡진 표면) 내로 팽창시키기 위해 양압이 작용된다. 최대 팽창이 가장 오른쪽 이미지에 나타내어져 있고, 이어서 상기 양압이 제거된다.

[0120] 편평한 기판의 일축 인장에 대한 결과와 유사하게도, 이 "구부림" 인장은 가역적이다. 굴곡진 표면과의 정합적 접촉을 최대화시키는 팽창의 여여한 단계에서든 상기 어레이는 당 기술 분야에 알려진 임의의 수단들에 의하여 상기 굴곡진 표면으로 전사될 수 있다. 접착제들(엘라스토머 기판 또는 SU-8)이 코팅된 유리 렌즈들 위에 풍선 스템프들에 의하여 실리콘 인쇄하는 실시예가 도 23에 도시된다. 상기 렌즈들은 볼록일 수도 있고 오목일 수도 있다. 이 실시예에서 각각 R=19.62 mm 및 9.33 mm였다.

[0121] 실시예 1: 반도체 나노리본들에서의 제어된 베클링 구조들과 인장 가능한 전자 장치들에서의 응용 실시예

[0122] 반도체 나노구조들의 조성, 모양, 공간적 위치 및/또는 기하학적 구성에 대한 제어는 이들 물질의 거의 모든 응용들에 있어서 중요하다. 나노와이어들 및 나노리본들의 물질 조성, 지름, 길이, 및 위치들을 정의하기 위한 방법들이 존재하지만, 이들의 2차원 및 3차원(2D 및 3D) 구성을 제어하기 위한 접근 방법은 상대적으로 거의 없었다. 나노리본들에서 다른 방법으로는 생성해 내기 어려웠을 소정 클래스의 3D 형태들을 창조하기 위한 기계적 전략이 여기에 제공된다. 본 실시예는 접착 위치에 대한 공간적인 제어를 제공하기 위한 리소그래피적으로 패터닝된 표면 화학과 잘 제어된 국부 변위들을 유발하기 위한 지지 기판의 탄성 변형을 조합하여 사용하는 것을 수반한다. 정밀하게 엔지니어링된 베클링 기하 구조들은 이러한 방식으로 GaAs 및 Si의 나노리본들에서 생성되고 또한 이들 구조들은 역학적 해석 모델로 정량적으로 설명될 수 있다. 하나의 응용 실시예로서, 특정 구조들은 극도로 높은 수준의 인장 가능성(~100%까지), 압축성(~25%까지) 및 구부림성(bendability)(~5 mm까지의 곡률 반경)을 갖는 전자 장치(및 광 전자장치)에 이를 수 있는 길을 제공한다.

[0123] 상기 2D 및 3D 구조의 나노리본들 및 와이어들은 코일, 고리, 및 가지친 레이아웃과 같이 특정 기하 구조들을 갖도록 그들이 성장하는 동안 제어된다. 또는 그들의 성장 이후에, 층상 시스템 내에 내재된(built-in) 잔여 응력들을 이용하여 인장된 엘라스토머 기판 또는 튜브-형(또는 나선형) 구조들에 이들 요소들을 결합함으로써, 예를 들면 사인파와 같은 구조를 생성하기 위하여 제어된다. 웨이브진 기하 구조들을 갖는 반도체 나노리본들은 구형 곡선 초점면 어레이들, 지능형 고무 수술 장갑 및 정합 가능한 구조의 건강 모니터들과 같은 잠재적 응용을 위한 고성능의 인장 가능한 전자 시스템 가능하게 하기 때문에 어느 정도 흥미롭다. 상기 전자 장치들 자체가 인장 가능한 이러한 접근은 인장 가능한 금속 상호 접속부들과 함께 경질 장치 아일랜드들을 사용하는 동일한 이들 응용들과는 상이하고 또한 보완적인 내지는 대안적인 것이다. 앞서 설명한 웨이브진 나노리본들은 크게 두 가지 단점들이 있다: (i) 그들은 물질의 모듈러스 및 리본들의 두께에 의해 정의되는 진폭들과 고정된 주기들을 가지면서, 웨이브의 기하 구조 또는 위상에 대한 제어를 거의 허용하지 않는 방식으로 자발적으로 형성되는 것과 (ii) 그들이 수용할 수 있는 최대 변형들은 20-30%의 범위로서 이러한 공정에 의하여 얻어지는 비최적의 웨이브진 기하 구조들에 의하여 제한되는 것이다. 여기에 소개된 절차들은 그들의 구조에 대한 결정론적 제어로 베클링 구조들을 달성하기 위하여 지지 기판의 탄성 변형과 함께 리소그래피적으로 정의된 표면 접착 위치들을 이용한다. 그러한 구조들의 대규모 조직화된 어레이들의 개별 나노리본들의 임의의 선택된 세트에 대하여, 주기적인 또는 비주기적인 설계가 가능하다. 인장 가능한 전자 장치에 대하여 설계된 특수한 기하 구조들이 GaAs와 같은 깨어지기 쉬운 물질에서 조차 거의 150%까지의 변형 범위를 가능하게 하는데, 이는 역학적 해석 모델과 일치하면서, 이전에 보고된 결과에 비하여 무려 10배나 더 크다.

[0124] 도 24는 이러한 절차에서의 단계들을 나타낸다. 폴리(디메틸실록산)(PDMS: poly(dimethylsiloxane)) 엘라스토머 기판 위에 표면 화학 접착 위치들을 패터닝하기 위한 마스크의 제조와 함께 제조가 시작된다. 본 공정은 UV-O 마스크라고 불리는 특수한 유형의 (단계 i를 통해 제조한) 진폭 광마스크를 상기 PDMS와 정합 접촉을 시킨 채 상기 광마스크를 통해 심자외선(deep UV)(240-260 nm)을 통과시키는 단계를 수반한다. 상기 UV-O 마스크는 UV에 노출시키면 PDMS의 표면 근방에 오존의 패터닝된 영역들을 생성하도록 투명 영역에 양각된 리세스 구조물을 갖는다. 상기 오존은 개질되지 않은, -CH<sub>3</sub> 및 -H로 종결된 기들이 압도적인 소수성 표면을 -OH 및 -O-Si-0- 작용기들로 종결되는 고도로 극성이면서 반응성인 표면(즉, 활성화된 표면)으로 전환시킨다. 노출되지 않은 영역들은 개질되지 않은 표면 화학 작용(즉, 비활성화된 표면)을 유지한다. 여기에 소개된 절차들은 일축성의(uniaxial) 큰 사전 변형(L에서 L+ΔL까지의 길이 변화에 대하여  $\varepsilon_{pre} = \Delta L/L$ ) 하에서 PDMS 기판들 (두께 ~4 mm) 위로의 노광을 수반한다(단계 ii). 단순하고 주기적인 라인 패턴들을 갖는 마스크에 대하여, 도 24의 (a)

의 단계 (iii)에서 ("활성화된 표면"의 표시가 붙은 선으로 지시되는) 활성화된 띠와 비활성화된 띠(예를 들면, 이웃하는 활성화된 띠들 사이의 거리)의 폭들을 단계 (i)에서  $W_{act}$ 와  $W_{in}$ 으로 각각 표시한다. 상기 활성화된 영역들은 표면에 -OH 또는 -Si-O 기들을 노출시키는 다른 물질들과 강하면서도 비가역적으로 결합할 수 있다. 이하에서 개괄하는 바와 같이, 이들 패터닝된 접착 위치들은 나노 리본들 내에 잘 정의된 3D 기하 구조들을 생성하기 위해 이용된다. 선택적으로, 상기 기판과 접촉하기 전에 상호 접속부들을 유사하게 패터닝함으로써 유사한 접착성 결합 위치의 패턴이 제공된다.

[0125] 본 실시예에 있어서, 나노리본들은 단결정 Si 및 GaAs 모두로 구성된다. 실리콘 리본들은 앞서 설명한 절차들을 이용하여 SOI(silicon-on-insulator) 웨이퍼로부터 제조된다(Khang et al. Science 311, 208-212 (2006) 참조). 상기 GaAs 리본들은 분자빔 에피택시(MBE: molecular-beam epitaxy)에 의하여 (100) SI-GaAs 웨이퍼 위에 형성된 Si-도핑된 n-형 GaAs ( $120\text{ nm}$ ;  $4 \times 10^{17}\text{ cm}^{-3}$ 의 캐리어 농도), 반-절연(semi-insulating) GaAs (SI-GaAs;  $150\text{ nm}$ ) 및 AlAs ( $200\text{ nm}$ )의 다중층을 수반한다. 상기 에피층들을 식각 마스크와 같이 (0 1 1) 결정 방향을 따라 패터닝된 포토레지스트의 선들을 이용하여  $\text{H}_3\text{PO}_4$  및  $\text{H}_2\text{O}_2$ 의 수용성 식각제 내에서 화학 식각하여 상기 리본들을 정의한다. 상기 포토레지스트를 제거한 후 웨이퍼를 HF의 에탄올 용액(에탄올과 49% HF 수용액 사이에 2:1 부피비)에 적셔서 상기 AlAs 층을 제거하고, 그에 의하여 상기 포토레지스트에 의하여 결정된 폭(도 24의 (d)의 실시예에 있어서는  $\sim 100\text{ }\mu\text{m}$ )을 갖는 GaAs(n-GaAs/SI-GaAs)의 리본을 풀어낸다. 상기 HF 용액 내에 에탄올을 첨가하는 것은 건조하는 동안 모세관 힘의 작용으로 인하여 파손되기 쉬운 리본들에 크랙이 발생할 확률을 감소시킨다. (물에 비하여) 낮은 표면 장력은 상기 GaAs 리본들의 공간적 배치에서 건조로 인해 유발되는 무질서를 최소화할 수도 있다. 마지막 단계에서, 상기 PDMS의 활성화된 영역에 결합되기 위해 필요한 -Si-OH 표면 화학 작용을 제공하기 위하여  $\text{SiO}_2$ 의 박막( $\sim 30\text{ nm}$ )이 증착된다.

[0126] UVo 처리되고 사전-인장된 PDMS 기판(사전 변형의 방향에 평행하게 리본들이 배향됨) 위에 상기 처리된 SOI 또는 GaAs 웨이퍼들을 적층하고,  $90^\circ\text{C}$ 의 오븐에서 수분동안 베이킹하고, 그리고 모든 리본들이 PDMS의 표면으로 전사된 웨이퍼를 제거한다(단계 (iv)). 가열은 상기 PDMS의 활성화된 영역과 Si 리본들 위의 내인성(native)  $\text{SiO}_2$ 층 또는 상기 GaAs 리본들 위의 증착된  $\text{SiO}_2$ 층 사이에 정합적 접촉과 강한 실록산 결합(즉, -O-Si-O-)을 형성하는 것을 용이하게 한다. 상대적으로 약한 반데르발스(van der Waals) 힘은 상기 리본들을 상기 PDMS의 비활성화된 표면 영역들에 결합시킨다. 상기 PDMS 내의 변형을 릴랙스시키는 것은 상기 리본들이 상기 PDMS의 비활성화된 영역들로부터 물리적으로 분리되는 것을 통하여 베클링을 생성한다(단계 (v)). 상기 리본들은 상기 활성화된 영역들에서는 강력한 화학 결합으로 인하여 상기 PDMS에 속박된 채 유지된다. 결과로서 얻어지는 3D 리본 기하 구조들(즉, 베클링의 공간적으로 변화하는 패턴)은 사전 변형의 크기와 표면 활성화의 패턴들(예를 들면,  $W_{in}$ 과  $W_{act}$ 의 모양과 치수들)에 의존한다. (유사한 결과들이 상기 리본들 위에 패터닝된 결합 위치들을 통해서 달성될 수 있다). 단순한 라인 패턴의 경우에 있어서,  $W_{in}$ 과 사전 변형이 상기 베클링들의 폭과 진폭을 결정한다.  $W_{act}$ 가  $> 100\text{ }\mu\text{m}$ 이었을 때 '웨이브진' 실리콘을 생성하는 유형의 기계적 불안정성으로 인하여 동일한 리본들 내에 상기 베클링보다 훨씬 작은 파장과 진폭을 갖는 사인파(sinoidal wave)들이 형성되었다. (도 25 참조, 상이한  $W_{act}$ 에 대하여 형성된 샘플들의 이미지). 제조의 마지막 단계로서, 상기 3D 리본 구조들은 액체 프리폴리머(prepolymer)를 주조하고 경화시킴으로써 PDMS 내에 봉지될 수 있다(도 24 참조, 단계(vi)). 상기 액체는 낮은 점도와 낮은 표면 에너지로 인하여 흘러서 상기 리본들과 기판 사이에 형성된 틈을 메운다(도 26 참조).

[0127] 도 24의 (d)는 PDMS 위에 베클링된 GaAs 리본들의 경사-시각(tilted-view) 주사 전자 현미경(SEM: scanning electron microscope)의 이미지를 나타낸다. 이 때,  $\varepsilon_{pre} = 60\%$ 이고,  $W_{act} = 10\text{ }\mu\text{m}$ 이고,  $W_{in} = 400\text{ }\mu\text{m}$ 이다. 상기 이미지는 어레이 내의 모든 리본들이 공통의 기하 구조와 공간적으로 일치하는(coherent) 위상들을 갖는, 균일하고 주기적인 베클링들을 보여준다. 고정시키는 점들(anchor points)은 리소그래피적으로 정의된 부착 위치들에 잘 맞추어져 있다. 삽입 사진은 결합된 영역의 SEM 이미지이다. 폭은  $\sim 10\text{ }\mu\text{m}$ 로서  $W_{act}$ 와 일치한다. 상기 이미지들은 PDMS의 표면이 결합 위치들에서도 편평함을 나타낸다. 이전에 보고된 바 있던 강하게 결합된 웨이브 구조물들과는 크게 상이한 이러한 거동은 여기에 설명된 케이스에 있어서, PDMS가 변위를 유발하지만 베클링 과정에 밀접하게 관여하는 것은 아님(즉, 그의 모듈러스는 리본들의 기하 구조에 영향을 미치지 않음)을 암시한다. 이러한 의미에서, PDMS는 부착 위치들에 가해진 힘을 통해 리본들을 조작할 수 있는 연질의 비파괴적인 도구를 대표한다.