(19) 日本国特許庁(JP)

## (12) 公開特許公報(A)

(11) 特許出願公開番号

特開2005-184003

(P2005-184003A)

(43) 公開日 平成17年7月7日(2005.7.7)

(51) Int.Cl.<sup>7</sup>

H01C 7/12

H01L 23/62

F 1

H01C 7/12

H01L 23/56

テーマコード(参考)

5E034

A

審査請求 未請求 請求項の数 37 O L 外国語出願 (全 66 頁)

(21) 出願番号 特願2004-369990 (P2004-369990)

(22) 出願日 平成16年12月21日 (2004.12.21)

(31) 優先権主張番号 10/746,020

(32) 優先日 平成15年12月23日 (2003.12.23)

(33) 優先権主張国 米国(US)

(71) 出願人 501246662

リッテルフューズ, インコーポレイティド

アメリカ合衆国, イリノイ 60016,

デス プレインズ, イースト ノースウエ

スト ハイウェイ 800

(74) 代理人 100064908

弁理士 志賀 正武

(74) 代理人 100089037

弁理士 渡邊 隆

(74) 代理人 100108453

弁理士 村山 靖彦

(74) 代理人 100110364

弁理士 実広 信哉

最終頁に続く

(54) 【発明の名称】電圧可変材料、これを含む組成物、及びこれを用いた装置

## (57) 【要約】

【課題】 導電及び非導電表面に固有に付着するよう構成された絶縁バインダーを含む電圧可変材料(“VV M”)を提供することである。

【解決手段】 導電及び非導電表面に固有に付着するよう構成された絶縁バインダーを含む電圧可変材料(“VV M”)を提供する。バインダー及びVV Mは使用前に乾燥する拡がり可能な形態で自己硬化性を有しあつ付けることができる。バインダーは、分離した装置にVV Mを配置する必要性、及び、VV Mに電気的に接続する分離したプリント配線板パッドを提供する必要性を除去するものである。バインダー及びVV Mは、リジッド(FR-4)ラミネート、ポリイミド、又はポリマーのような異なる種類の基板に直接付けることができる。一実施形態では、VV Mはシリコンであり得るコアと、酸化物であり得る不活性コーティングとを有するドープされた半導体粒子を含む。

【選択図】 図2

**【特許請求の範囲】****【請求項 1】**

電気過大応力に対する保護を提供する組成物であつて：

絶縁性バインダーと；

ドープされたコアとそのコア上に備えたコーティングとを有する半導体粒子であつて、

バインダーに保持された半導体粒子と；

バインダーに保持された導電性粒子と；

を備えた組成物。

**【請求項 2】**

前記絶縁性バインダーはポリマー樹脂を含む請求項 1 に記載の組成物。

10

**【請求項 3】**

前記のドープされたコアはシリコンとドーパント材料とを含む請求項 1 に記載の組成物。

。

**【請求項 4】**

前記ドーパント材料は、アンチモン、ヒ素、リン、及びボロンから成る群から選択された少なくとも一のコンポーネントを含む請求項 3 に記載の組成物。

**【請求項 5】**

前記のドープされたコアは約 5  $\mu\text{m}$  から約 100  $\mu\text{m}$  の平均サイズを有する請求項 1 に記載の組成物。

**【請求項 6】**

前記コーティングは約 100 から約 10,000 の平均厚さを有する請求項 1 に記載の組成物。

20

**【請求項 7】**

前記コーティングは、二酸化シリコン、エピタキシャルシリコン、及び、ガラスから成る群から選択された少なくとも一の材料を含む請求項 1 に記載の組成物。

**【請求項 8】**

前記導電性粒子は単一材料から成る請求項 1 に記載の組成物。

**【請求項 9】**

前記導電性粒子は酸化物コーティングを含む請求項 1 に記載の組成物。

**【請求項 10】**

前記導電性粒子は、アルミニウム、真ちゅう、カーボンブラック、銅、グラファイト、金、鉄、ニッケル、銀、ステンレス鋼、すず、亜鉛、及びこれらの合金を含む群から選択された少なくとも一の材料を含む請求項 1 に記載の組成物。

30

**【請求項 11】**

前記導電性粒子は約 5  $\mu\text{m}$  から約 50  $\mu\text{m}$  の平均サイズを有する請求項 1 に記載の組成物。

**【請求項 12】**

装置内に封入されることなく、使用に際して直接付けられるように配備された請求項 1 に記載の組成物。

**【請求項 13】**

装置内に備えられるように配備された請求項 1 に記載の組成物。

40

**【請求項 14】**

絶縁性粒子、半導体粒子及びタンクステンパウダーから成る群から選択された少なくとも一の添加粒子を含む請求項 1 に記載の組成物。

**【請求項 15】**

電気過大応力に対する保護用組成物であつて：

絶縁性バインダーと；

バインダーに保持されたドープされた半導体粒子と；

バインダーに保持され、単一材料から成る導電性粒子と；を備え、

前記バインダーと、前記半導体粒子と、前記導電性粒子とが電極ギャップ内に積層されるように配備されている組成物。

50

## 【請求項 1 6】

前記ドープ半導体粒子はコアとシェルとを含む請求項 1 5 に記載の組成物。

## 【請求項 1 7】

前記導電性粒子は、アルミニウム、真ちゅう、カーボンブラック、銅、グラファイト、金、鉄、ニッケル、銀、ステンレス鋼、すず、亜鉛、及びこれらの合金を含む群から選択された少なくとも一の材料を含む請求項 1 5 に記載の組成物。

## 【請求項 1 8】

装置内に封入されることなく、使用に際して直接付けられるように配備された請求項 1 5 に記載の組成物。

## 【請求項 1 9】

装置内に備えられるように配備された請求項 1 5 に記載の組成物。 10

## 【請求項 2 0】

絶縁性粒子、半導体粒子及びタンクステンパウダーから成る群から選択された少なくとも一の添加粒子を含む請求項 1 5 に記載の組成物。

## 【請求項 2 1】

電気過大応力組成物において使用される粒子であつて：

ドープされた半導体コアと；

該コアを囲繞する不活性コーティングと；を備えた粒子。

## 【請求項 2 2】

前記のドープされたコアがシリコンとドーパント材料とを含む請求項 2 1 に記載の粒子 20

。

## 【請求項 2 3】

前記ドーパント材料は、アンチモン、ヒ素、リン、及びボロンから成る群から選択された少なくとも一のコンポーネントを含む請求項 2 2 に記載の組成物。

## 【請求項 2 4】

前記のドープされたコアは約 5  $\mu\text{m}$  から約 100  $\mu\text{m}$  の平均サイズを有する請求項 2 1 に記載の組成物。

## 【請求項 2 5】

前記コーティングは約 100 から約 10,000 の平均厚さを有する請求項 2 1 に記載の組成物。 30

## 【請求項 2 6】

前記コーティングは、二酸化シリコン、エピタキシャルシリコン、及び、ガラスから成る群から選択された少なくとも一の材料を含む請求項 2 1 に記載の組成物。

## 【請求項 2 7】

電気過大応力組成物において使用される粒子であつて：

シリコン内側部と；

二酸化シリコン、エピタキシャルシリコン、及び、ガラスから成る群から選択された少なくとも一の材料を含む外側部と；を備えた粒子。

## 【請求項 2 8】

前記外側部は熱制御環境で成長させた請求項 2 7 に記載の粒子。

## 【請求項 2 9】

前記外側部は流動床プラズマ炉を用いて付けられた請求項 2 7 に記載の粒子。

## 【請求項 3 0】

電気過大応力組成物を作製する方法であつて：

シリコンに所望の抵抗率となるまでドープする段階と；

ドープされたシリコンを、ドープされたシリコン上に酸化物層を成長させる時間全体にわたって加熱させる段階と；

形成されたシリコンと酸化物材料とにバインダーを混ぜる段階と；を備えた方法。

## 【請求項 3 1】

溶媒においてポリマーを溶解することによって絶縁性バインダーを準備する段階を含む 50

請求項 3 0 に記載の方法。

【請求項 3 2】

ドープされたシリコンを適當な粒子サイズまでつぶす段階を含む請求項 3 0 に記載の方法。

【請求項 3 3】

ドープされたシリコンを約 500 から約 1500 の温度にさらす請求項 3 0 に記載の方法。

【請求項 3 4】

ドープされたシリコンを、約 15 分から約 3 時間の時間全体にわたって加熱する請求項 3 0 に記載の方法。

【請求項 3 5】

ドープされたシリコンを、多段の加熱及び冷却のインターバルにさらすことを含む請求項 3 0 に記載の方法。

【請求項 3 6】

ドープされたシリコンを真空下で冷却することを含む請求項 3 5 に記載の方法。

【請求項 3 7】

バインダー内の形成されたシリコン及び酸化物材料を、導電性粒子、導電性コア / シェル粒子、絶縁性粒子、半導体粒子、及び、タンゲステンパウダーから成る群から選択された少なくとも一の添加コンポーネントに混ぜることを含む請求項 3 5 に記載の方法。

【発明の詳細な説明】

【技術分野】

【0 0 0 1】

本発明は回路保護に関する。本発明は特に、電圧可変材料に関する。

【背景技術】

【0 0 0 2】

本願は、“直接的応用又はこれを用いた電圧可変材料 (Voltage Variable Materials for Electrostatic Discharge Protection)”の発明の名称で 2003 年 4 月 8 日に出願された米国特許出願第 10 / 410,393 号明細書に基づく優先権の効果を奏し、これらの記載の内容は本明細書に組み込まれている。

本願は以下の同じ出願人の係属出願に関するものである：“静電放電保護用のポリマー・コンポジット材料”シリアル番号 09 / 232,387 号、アトニードケット番号 0112690-020；“電圧可変基板材料”シリアル番号 09 / 976,964 号、アトニードケット番号 0112690-098。

【0 0 0 3】

電気的過大応力 (“EOS”) 過渡電流は、高電界と、通常、回路又は回路における高感度電気的コンポーネントを一時的に又は不变に非機能的にすることができる高ピークパワーとを生成する。EOS 過渡電流は、回路動作を遮断し、又は、回路を徹底的に破壊することができる過渡電圧を含むことができる。EOS 過渡電流は例えば、電磁気パルス、静電放電、稲光、静電気の蓄積 (ビルドアップ) から生じてもよいし、又は、他の電子的若しくは電気的コンポーネントの作動によって誘起されてもよい。EOS 過渡電流は、サブナノ秒、又はマイクロ秒で最大の振幅を生じ、繰り返し振幅ピークを有し得る。

【0 0 0 4】

材料は EOS 過渡電流に対する保護用に存在し、非常に迅速に反応して (理想的には過渡電流波がそのピークに達する前に)、送出される電圧を EOS 過渡電流の継続時間での非常に小さな値にまで低減するように構成されている。EOS 材料は低いか又は通常の作動電圧における高電気抵抗値によって特徴づけられている。EOS 過渡電流に応答して、材料は低電気抵抗状態にまで非常に迅速にスイッチする。EOS が散逸するとき、これらの材料はその高電気抵抗状態に戻る。EOS 材料はまた、EOS 過渡電流の散逸の際に元々の高電気抵抗値に非常に迅速に回復する。

【0 0 0 5】

10

20

30

40

50

EOS 材料は高抵抗状態と低抵抗状態との間を繰り返しスイッチすることができる。EOS 材料は数1000のESD 事象に耐え、個々のESD 事象からの保護を行った後に所望のオフ状態に回復できる。

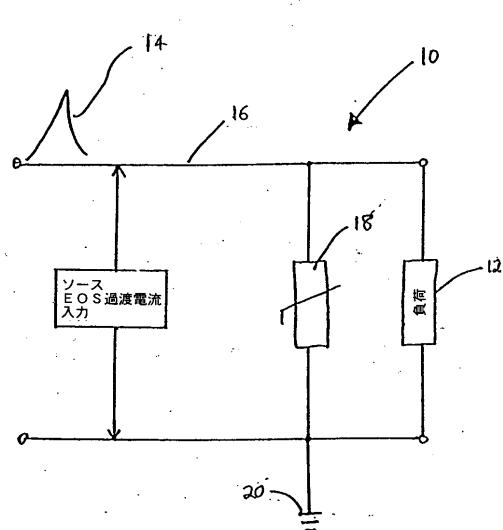

#### 【0006】

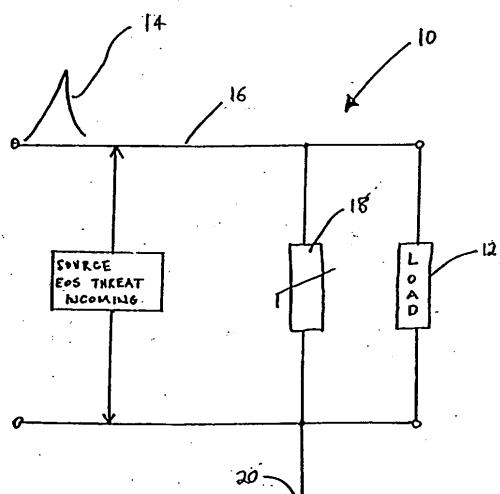

EOS 材料を用いた回路は、EOS 過渡電流による過剰電圧若しくは電流の一部をグラントに分路して、電気回路及びそのコンポーネントを保護することができる。脅威（スレット）過渡電流の他の一部は、脅威のソース（源）へ反射する。反射された波はソースによって減衰され、放射され、又は、脅威エネルギーが安全レベルまで低下するまで同じやり方でそれぞれパルスを戻すように応答する、電圧サージ防護デ装置へ向け直す。EOS 過渡電流装置を用いる典型的な回路を図1に示す。

10

#### 【0007】

図1に、典型的な電気回路10を示す。回路10における回路負荷12は通常の作動電圧で作動する。十分な継続時間有する通常の作動電圧の実質的に2~3倍以上のEOS 過渡電流は負荷12及びこれに含まれるコンポーネントを損傷し得る。典型的には、EOS 脅威は、通常作動で見られる電圧の数10、数100、あるいは数1000倍だけ通常作動電圧を超えることができる。

#### 【0008】

回路10では、EOS 過渡電流電圧14はライン16に沿って回路10にはいるところを示している。EOS 過渡電流電圧14が生じる際、EOS 保護装置18は高抵抗状態から低抵抗状態へスイッチし、これによって安全な低い値でEOS 過渡電流電圧14をクランプする。EOS 保護装置18は電子ライン16からシステムのグラント20へ過渡電流脅威の一部を分路する。上述のように、EOS 保護装置18は大部分の脅威を脅威のソースへ反射し返す。

20

#### 【0009】

EOS 保護装置は典型的には、電圧可変材料（“VVM”）を用いる。多くのVVMは、それらが所望のいくつかのハウジング又は封入を有するように、整合性及びメークアップであった。すなわち、VVM材料は従来、プリントボード（“PCB”）に実装された表面マウント装置のような装置に備えられている。VVM装置は典型的には、保護を要求する回路の装置から離散的に実装されてきた。これが多くの問題を発生させている。

30

#### 【0010】

第1に、VVM装置を、PCBに実装されることが要求されるコンポーネントの数に加えられる。VVM装置は貴重なボードスペース（空間）を消耗し、欠陥の可能性を高める。VVM装置は典型的には、追加されたパッドがPCBに固定され、追加される回路トレースをPCB装置から又はVVMパッドへのグラント面からルートとなることを要する。コスト、スペーシング／フレキシビリティ、及び信頼性の観点から、PCBへ実装されるコンポーネントの数を低減することが常に求められる。

30

#### 【0011】

第2に、存在するPCBにコンポーネントを追加することにより、ボードの再設計又は他のタイプの現在の設計への組み込みを要求し得る。すでに製品が製造中であれば、かなりの時間が、VVM装置を集積する余裕を残すか残さないかであるボードスペースの最適化に用いられそうである。

40

#### 【0012】

第3に、EOS 過渡電流はPCB外で生じ、ケーブル及びワイヤを通ってPCBに流れ込む。例えば、ネットワークを形成したコンピュータ及びテレフォンシステムを、環境及び処理作動によって生じた種々の過渡電流にさらされる。これらの状況では、過渡電流がPCBに達する前に、過渡電圧を除去することが望ましい。

#### 【発明の開示】

#### 【発明が解決しようとする課題】

#### 【0013】

本発明は、過電圧回路保護を提供する。特に、本発明は、導電及び非導電表面に固有に

50

付着するように構成された絶縁バインダーを含む電圧可変材料（“VVM”）を提供する。バインダー及びVVMは自己硬化性を有する（自己硬化可能な）ものであり、最終的な使用の態様で乾燥するものであるがインク状の製品に応用されてもよい。バインダーは独立の装置においてVVMを配置する必要性、又は、VVMに電気的に接続する分離したプリント配線板パッドの必要性を除去するものである。バインダー及びVVMは、リジッド（FR-4）ラミネート、ポリイミド、ポリマー、ガラス及びセラミックのような多くの異なる種類の基板に直接付けることができる。VVMは電気的な装置（例えば、コネクタ）の一片内に配備された異なる種類の基板に直接付けることもできる。

#### 【0014】

VVMのバインダーは、溶媒に溶解されたポリエステル等のポリマーを含む。ポリマーを溶解する一の適当な溶媒はジエチレングリコールモノエチルエステルアセテートであり、通常“カルビトールアセテート”と称される。一の実施形態では、ヒュームド・シリカのような増粘剤を絶縁バインダーに添加して絶縁バインダーの粘度を向上させる。次いで、多くの異なる種類の粒子をバインダーに混合して、所望のクランプ電圧及び応答時間を作り出す。この異なる種類の粒子は：導電性粒子、絶縁粒子、半導体粒子、ドープ半導体粒子（コア及びシェルドープ半導体粒子を含む）及びこれらの組み合わせを含む。

#### 【課題を解決するための手段】

#### 【0015】

一の実施形態における導電粒子は内側コア（インナーコア）及び外側シェル（アウターシェル）を含む。コア及びシェルは異なる導電率又は抵抗率を有する。シェルはコアより導電性が高く、コアはシェルより導電性が高いかいずれかである。コア及びシェルはそれぞれ、上述の異なる種類の粒子のうちのいずれかから成り得る。一の好適な実施形態では、導電粒子はアルミニウムコアと酸化アルミニウムシェルを含む。他の実施形態では、導電粒子はシェルやコーティングを含まない。ここで、導電粒子は実質的に単一の材料から成る。

#### 【0016】

一の好適な実施形態では、VVMは導電粒子及びドープ半導体粒子を含む。導電粒子は実質的にピュアなニッケル粒子を含むことができ、ドープ半導体はドープシリコンを含む。

#### 【0017】

本発明のバインダーを有するVVMは、種々の回路又は製品を作製する基板に付けることができる。第1の用途では、複数の電極又は導体を公知の技術を用いてプリント配線板上に固定する。各電極はギャップによってプリント配線板上で分離されている。VVMは電極及びギャップにおける基板に付けられ、本質的に（固有の性質で）付着している。第2の用途では、電極は基板に固定されるが、VVMだけが本質的に電極に付着している。すなわち、VVMは基板に付着しておらず、ギャップに配置しているだけである。、

#### 【0018】

第3の用途では、VVMは基板に本質的に付着しており、電極はVVM上に配置して本質的に付着している。すなわち、VVMは電極を基板に固定している。第4の用途では、複数の電極のうちの少なくとも一つは基板に固定されており、VVMは固定された電極に本質的に付着している。少なくとも他の一つの電極はVVMの頂部上に在る。VVMの頂部上に在る電極も基板に固定している部分を有することができる。

#### 【0019】

VVMがプリント配線板上のような回路に付けられているとき、多量のVVMが基板保護被覆を必要としない最終形態で自己硬化する。VVMは製造、シッピング及び使用を通して環境に触れるかもしれない。基板は、プリント配線板で使用される剛性ラミネート（例えば、FR-4）、フレキシブル回路（例えば、カプトン（Kapton：登録商標）と共に用いられるポリイミドのような材料、ポリマー、セラミック、ガラス又はこれらの組み合わせのような種々の基板でもよい。

#### 【0020】

10

20

30

40

50

他の実施形態では、基板を被覆すること、あるいは保護することができる。例えば、上述の用途のいずれかはコーティングによって被覆してもよい。コーティングは以下を含む種々の異なる材料のうちの一つであってもよい：従来公知の乾燥膜写真画像可能力バーレイ、スプレー液体写真画像可能力バーレイ、又は、“グロブ・トップ”型コーティング。代替として、上述の用途のいずれかを多層プリント配線板（“PCB”）に埋め込むことができる。他の実施形態では、少なくとも一の追加の電極又は導体を上部基板の下側に固定する。ここで、VVMは上部基板と下部基板との間に配置し、少なくとも上部電極及び下部電極に本質的に付着し、上部基板及び下部基板のうちの少なくとも一つ以上に付着され得る。

## 【0021】

10

回路は装置中に備えられても備えられなくてもよい。例えば、実施形態における装置は、例えばRJ-45又はRJ-11コネクターのような通信装置である。他の実施形態では、装置はドイチェ・インスティチュート・フュア・ノームング e V (Deutsches Institut für Normung; “DIN”)コネクタ、又は、リボンケーブルコネクタのような入力／出力コネクタである。これらの各装置において、VVMは、信号導体をグランド導体若しくはシールドに接続することによって過渡電圧スパイクから一又は二以上の信号線を保護する。

## 【0022】

20

一の実施形態では、RJタイプコネクタは複数の信号導体を含む。コネクタはグランドされた導体シールドも含む。シールドは切断され又はスタンプして導体側へ下方にバイアスされた少なくとも一のタブを作製する。一の実施形態では、シールドは各導体について分離したタブを画定する。コネクタは導体上のタブを圧縮するハウジングを含む。VVMはRJコネクタに過電圧保護を付与するようにシールドタブと導体との間に付ける。一の実施形態では、VVMは上述の本質的に固定しているVVMであるが、装置に備えられた公知のVVMを用いることも可能である。他の実施形態では、VVMと導体及びシールドのうちの一つとの間にキャパシタを配備して、高ポテンシャル(HI-POT)テスト中に印加される電圧のような高DC電圧をブロックする。

## 【0023】

従って、本発明の利点は本質的に付着性（接着性）のVVMを提供することである。

## 【0024】

30

本発明の他の利点は、分離（独立）している装置にハウジングする必要がないVVMを提供することである。

## 【0025】

本発明の他の利点は、自己硬化性のVVMを提供することである。

## 【0026】

40

本発明の他の利点は、VVMに実装（マウント）される基板上に分離している電気パッドを提供する必要なしでプリント配線板に直接付着するVVMを提供することである。

## 【0027】

本発明の他の利点は、ポリマー又はプラスチックに直接付着するVVMを提供することである。

## 【0028】

本発明の他の利点は、装備の一片又はコネクターのような電気機器に備えられた基板にVVMを直接付けることである。

## 【0029】

本発明の他の利点は、過電圧保護を有するRJタイプのコネクタを提供することである。

## 【0030】

本発明の他の利点は、過電圧保護を有する入力／出力コネクタを提供することである。

## 【0031】

50

さらに、本発明の他の利点は、RJタイプのコネクタにおける複数の異なる信号線にV

V Mを電気的に接続する装置を提供することである。

【0032】

さらに、本発明の他の利点は、ハウジングの必要性の排除を介して、プラスチックインピーダンスの低下により電気的性能が改善され得る低コストの製造容易の回路保護材料を提供することである。

【発明を実施するための最良の形態】

【0033】

本発明の他の特徴及び利点は、以下の発明の詳細な説明及び図面から明らかになるだろう。

【0034】

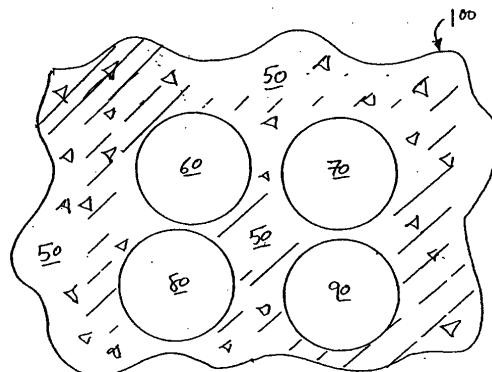

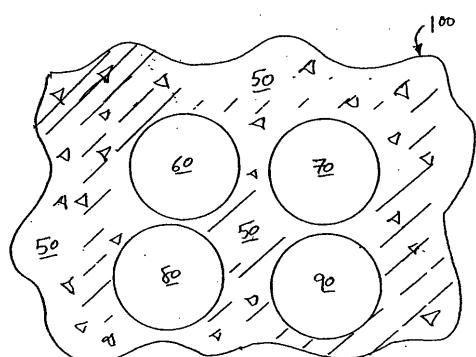

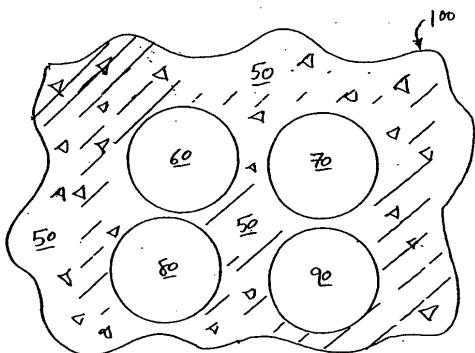

図2に示したように、本発明の電圧可変材料（“VVM”）100は絶縁性バインダー50を含む。バインダー50は、絶縁性粒子60、半導体粒子70、ドープ半導体粒子80、導電性粒子90及びこれらの組み合わせのような異なる種類の粒子の一若しくは二以上又は全てを固定する。絶縁性バインダー50は本質的な（固有の、イントリンシック）付着特性を有し、導電性金属表面又は非導電性絶縁表面のような表面に自ら付着する。絶縁性バインダー50は自己硬化性の特性を有し、このため、VVM100は回路又は製品に付くことができ、その後、VVM100及び絶縁性バインダー50を加熱若しくは硬化することなく使用できる。しかしながら、バインダー50を有するVVM100を用いる回路又は製品を加熱又は硬化して硬化工程を加速させてもよい。

【0035】

一実施形態におけるVVM100の絶縁性バインダー50は、溶媒中で溶解されたポリエステルのようなポリマー又は熱可塑性樹脂を含む。一実施形態では、ポリエステル樹脂は、6から80の範囲のガラス転移温度及び15,000から23,000原子質量単位の間の分子量を有する。ポリマーを溶解する適当な溶媒の一つは通常、“カルビトールアセテート”と称されるジエチレングリコールモノエチルエステルアセテートである。一の実施形態では、増粘剤を絶縁性バインダー50に添加し、絶縁性バインダー50の粘度を向上させる。例えば、増粘剤は、商品名Cabil-Sil TS-720で知られるようなヒュームド・シリカであってもよい。

【0036】

実施形態における絶縁性バインダー50は、高い絶縁破壊強度、高い電気抵抗率、及び、高いトラッキング抵抗を有する。絶縁性バインダー50は、導電性粒子90、絶縁性粒子60、半導体粒子70、及び、ドープ半導体粒子80のような、VVM100の他の可能なコンポーネントの間に十分な粒子間距離（スペーシング）を提供し、維持する。粒子間距離は高抵抗を提供する。絶縁性バインダー50の抵抗率及び絶縁破壊強度は高抵抗状態にも影響する。一の実施形態では、絶縁性バインダー50は少なくとも $10^9 \cdot \text{cm}$ の体積抵抗率を有する。バインダー50において異なるポリマーを混ぜ、それらを架橋することが可能である。

【0037】

一の実施形態では、絶縁性粒子60はVVM100のバインダー50に分散される。一の実施形態における絶縁性粒子60は、約200～約1000オングストローム（“”）の範囲の平均粒子サイズ、及び、 $10^{-6} (\cdot \text{cm})^{-1}$ を有する。一の実施形態では、絶縁性粒子60は約50～約200の範囲の平均粒子サイズを有する。

【0038】

商品名Cabil-Sil TS-720で入手できるバインダー50のヒュームド・シリカが絶縁性粒子60を構成する。しかしながら、他の絶縁性粒子をヒュームド・シリカに加えて用いてもよい。例えば、ガラス球、炭酸カルシウム、硫酸カルシウム、硫酸バリウム、アルミニウム三水和物、カオリン及びカオリナイト、超高密度ポリエチレン（“UHDP”）、及び、二酸化チタンのような金属酸化物を本発明における絶縁性粒子60として使用してもよい。例えば、ナノフェーズ・テクノロジー社（Nanophase Technology）製の約300～400の範囲の平均粒子サイズを有する二酸化チタンは適当な絶縁性粒

10

20

30

40

50

子 60 を提供する。

【 0 0 3 9 】

絶縁性粒子 60 は、 V V M 1 0 0 において使用するならば、 V V M 1 0 0 の約 1~15 重量パーセントの実施形態において存在するヒュームド・シリカに加えて、鉄、アルミニウム、亜鉛、チタン、銅、及び粘度の酸化物も含むことができる。

【 0 0 4 0 】

一実施形態では、半導体粒子 70 は V V M 1 0 0 のバインダー 50 内に分散される。一実施形態における半導体粒子 70 は、 $5 \mu\text{m}$  以下の平均粒子サイズ、及び、 $10 \sim 10^{-6}$  ( $\cdot \text{cm}^{-1}$ ) の範囲のバルク導電率を有する。粒子パッキング密度を最大にし、最適クランプ電圧及びスイッチング電圧を得るために、一の好適な実施形態における半導体粒子 70 の平均粒子サイズは約  $3 \mu\text{m}$  ~ 約  $5 \mu\text{m}$  の範囲、又は、 $1 \mu\text{m}$  以下である。100 nm 程度及びそれ以下の半導体粒子サイズも本発明における使用に適している。

【 0 0 4 1 】

一実施形態における半導体粒子 70 の材料は炭化ケイ素（シリコンカーバイド）を含む。半導体粒子は以下を含むことができる：ビスマス、銅、亜鉛、カルシウム、バナジウム、鉄、マグネシウム、カルシウム、及びチタンの酸化物；シリコン、アルミニウム、クロム、チタン、モリブデン、ベリリウム、ボロン、タンゲステン、及びバナジウムの炭化物；カドミウム、亜鉛、鉛、モリブデン、及び銀の硫化物；窒化ボロン、窒化シリコン、窒化アルミニウム等の窒化物；モリブデン及びクロムのケイ化物；クロム、モリブデン、ニオブ、及びタンゲステンのホウ化物。

【 0 0 4 2 】

一実施形態では、半導体粒子 70 には例えば、#1200 グリットで、約  $3 \mu\text{m}$  の平均粒径サイズを有し得るアグスト社 (Agsto) 製のシリコンカーバイドを含まれる。シリコンカーバイドはその替わりに、#10,000 グリットで、約  $0.3 \mu\text{m}$  の平均粒径サイズを有するノートン社 (Norton) 製であり得る。他の実施形態では、半導体粒子 70 はシリコンカーバイド及び / 又は少なくとも以下のうちの一つを含む：チタン酸バリウム、窒化ボロン、リン化ボロン、リン化カドミウム、硫化カドミウム、窒化ガリウム、リン化ガリウム、ゲルマニウム、リン化インジウム、酸化マグネシウム、シリコン、酸化亜鉛、硫化亜鉛。

【 0 0 4 3 】

一実施形態では、ドープ半導体粒子 80 は V V M 1 0 0 のバインダー 50 に分散されている。不純物（ドーパント）の付加は半導体の電気伝導度に影響を与える。半導体材料にドープする不純物又は材料は電子ドナー又は電子アクセプターであってもよい。いずれの場合においても、不純物は真性半導体のエネルギー・バンドギャップ内のエネルギー準位を占有する。ドープ半導体における不純物濃度を増減することによって、材料の電気伝導度が変化する。真性半導体の電気伝導度は伝導電子濃度を増大することによって高い方へ（半金属又は金属の範囲へ）拡張され、又は、伝導電子濃度を低減することによって低い方へ（絶縁体の範囲へ）拡張されてもよい。

【 0 0 4 4 】

一の実施形態では、半導体粒子 70 及びドープ半導体粒子 80 は、標準混合技術によって V V M 1 0 0 の絶縁性バインダー 50 に混合される。他の実施形態では、異なる電気伝導体にドープされた種々の異なるドープ半導体粒子 80 は、V V M 1 0 0 の絶縁性バインダー 50 に分散されている。これらの実施形態のいずれかは絶縁性粒子 60 でもあり得る。

【 0 0 4 5 】

一実施形態では、V V M 1 0 0 は電気伝導性を有するようにするために材料にドープされた半導体粒子を用いる。ドープ半導体粒子 80 は、以下のものを含む従来の半導体材料から成ってもよい：窒化ボロン、リン化ボロン、リン化カドミウム、硫化カドミウム、窒化ガリウム、リン化ガリウム、ゲルマニウム、リン化インジウム、シリコン、炭化シリコン（シリコンカーバイド）、酸化亜鉛、硫化亜鉛、及び、ポリピロール若しくはポリアニリンのような導電ポリマー。これらの材料は例えば、リン、ヒ素若しくはアンチモンのよ

10

20

30

40

50

うな適当な電子ドナー、又は、鉄、アルミニウム、ボロン若しくはガリウムのような電子アクセプターでドープして、所望のレベルの電気伝導度を達成する。

【0046】

一実施形態では、ドープ半導体粒子80は電気伝導性（導電性）を付与するために、アルミニウムでドープしたシリコンパウダー（約0.5重量%のドープ半導体粒子）を含む。このような材料は商品名Si-100-Fでアトランチック・イクイップメント・エンジニア（Atlantic Equipment Engineers）によって市販されている。他の実施形態では、ドープ半導体粒子はZelc 3010-XCの商品名で市販されているアンチモンドープ酸化すずを含む。

【0047】

一実施形態では、VV M 100のドープ半導体粒子80は10μm以下の平均粒子サイズを有する。しかしながら、粒子パッキング密度を最大にし、最適なクランプ電圧及びスイッチング特性を得るために、半導体粒子の平均粒子サイズは約1μm～約5μmの範囲、又は、1μm以下であってもよい。

【0048】

一の好適なVV Mコンポーネント

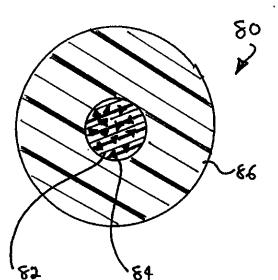

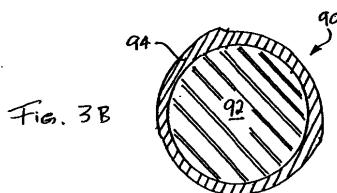

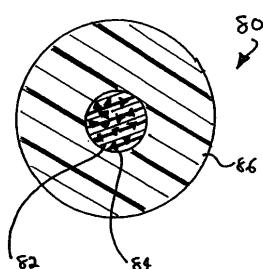

一の好適なドープ半導体粒子80を図3Aに示す。半導体粒子80は少なくとも一のドーパント84でドープされた内部コア82を含む。内部コアは外部シェル（外殻）又はコーティング86によって囲繞されている。

【0049】

一実施形態では、コア材料82は粒子状若しくはパウダー状シリコンを含む。シリコン82をドープして低抵抗値にし（例えば、1cm以下）、パウダーにグランドする。粒子82の平均サイズは適したサイズであり、一実施形態ではコア粒子はそれぞれ5～100μmである。一実施形態では、シェル又はコーティングの平均サイズは約100～約10,000オングストローム（“ ”）である。

【0050】

コア材料82又はシリコンはアンチモン、ヒ素、リン、ボロン又は他の本明細書で挙げたドーパントのような適したドーパントでドープする。コア材料82は、シリコンカーバイド、ガリウムヒ素等の適した半導体材料であり得る。一実施形態では、一種類のドーパントが使用される。しかしながら、異なる種類のドーパントを同じ粒子に用いられることも評価されるべきである。

【0051】

ドープ半導体粒子80のシェル又はコーティング86は多数の異なる材料からなり得る。例えば、コーティングは以下の材料のうちのひとつであり得る：二酸化シリコン、エピタキシャルシリコン又はガラス。これらの材料はそれぞれ不活性であり、本発明のVV Mの他のコンポーネントと反応しない。

【0052】

コーティング又はシェル86のタイプは、コーティング又はシェルを形成するのに用いられる工程を決定する。例えば、コーティング又はシェル86が酸化物例えば、二酸化シリコンであるならば、層は、一実施形態における特定された又は変動する時間にわたって一又は二以上の温度での加熱を介して成長される。適したシリコン酸化物層は、コアドープシリコン粒子82を加熱することによって形成できることがわかっている。特に、粒子は、約15分～約3時間の間、酸化時間中に約500～約1500の温度で加熱できる。加熱は、加熱及び冷却の多段のインターバルにわたって実施する。一の実施形態では、冷却は、粒子を約10～100mTorrの真空にさらしながら実施する。真空冷却は、VV Mが湿気にさらされることを防止できるので好都合である。一実施形態における粒子を約30分間加熱し、次いで、一晩真空冷却される。この工程を繰り返す。

【0053】

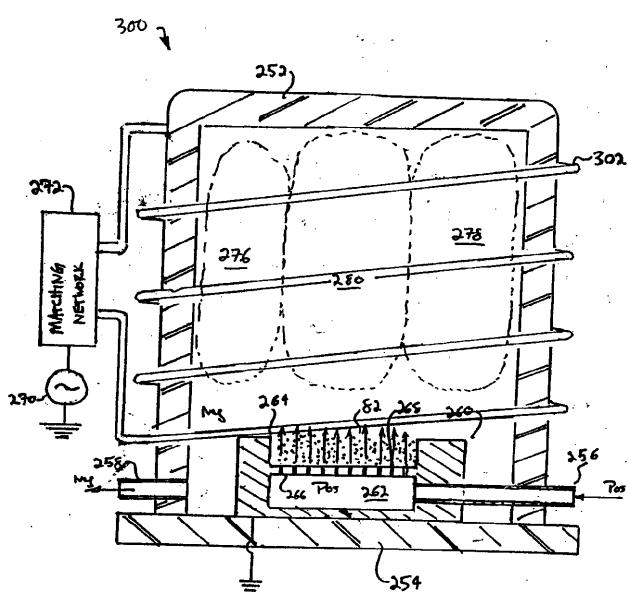

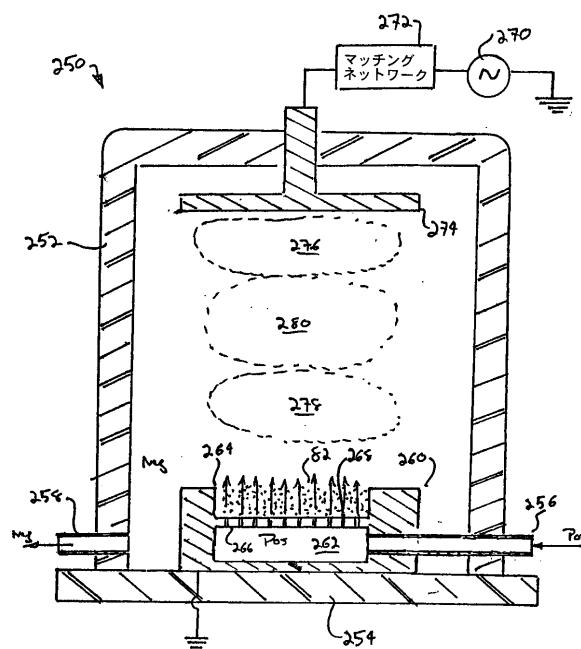

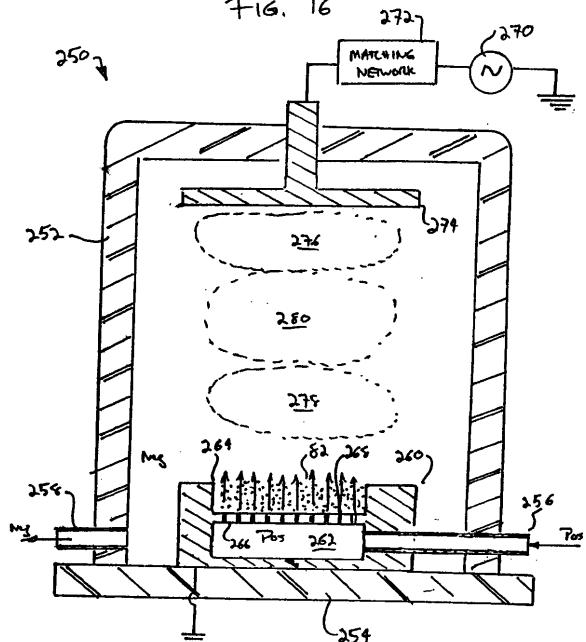

図16及び図17に、コア粒子82上にコーティング86を形成するための、本発明で意図している他の方法及び装置を、流動床プラズマ炉250（図16）及び炉300（図

10

20

30

40

50

17) によって示した。流動床炉 250 は簡略して概略的に示した。炉 250 はハウジング 252 とベース 254 を含む。ハウジング 252 とベース 254 は、一実施形態においてガラス若しくはプラスチックのような絶縁性若しくは誘電材料から成る。

#### 【0054】

ハウジング 252 は図示したように、注入圧力ポート 256 と排気真空ポート 258 とに取り付けられ、又は、それらを画定する。注入圧力ポート 256 は圧力チャンバー 260 まで延びている。圧力チャンバー 260 は圧力プレナム 262 を画定し、又は含む。圧力プレナム 262 は、ポート 256 からの反応ガスがプレナム 262 内の圧力下で入ること及び安定化できるようにする。プレナム 262 を介してハウジング 252 の内部に入る反応ガスは、ハウジング 252 によって画定され、又はそれに取り付けられたポート 258 からの負の圧力下で除去される。

#### 【0055】

チャンバー 260 は、ドープコア粒子のようなコア粒子 82 を保持するベッド 264 を画定し又は含む。ベッド 264 の底部壁 266 はプレナム 262 の頂部壁でもある。壁 266 は、比較的一様で、安定し、堅実な方式で圧縮された反応ガス壁 266 を介して逃がすことができる穴あきの又は焼結された開口 268 を画定する。プレナム 262 内の圧力が十分ならば、粒子 82 を通るガスフローが粒子をガスに取り込むことができる。その後粒子は液体状で保持され、粒子 82 のサスペンションの頂部は液体がベッド 264 に注がれる場合のように重力のために比較的平坦である。グランドされた導体 260 を組み合わせた電圧を印加した導体 274 は、プラズマシート領域 276 及び 278、とこれらのプラズマシート領域 276 及び 278 間に配置するグロー放電領域 280 とを生成する。ガス流において浮遊する粒子 82 は、プラズマグロー放電 280 と適当に混同することが確保されている。

#### 【0056】

ポート 256 に入る反応ガスは、窒素、アルゴン、ヘリウム、二酸化炭素、酸素およびこれらの組み合わせ等のキャリヤガスを介して運搬される。反応ガスは、トリエチルアルミニウム (T E A L)、四塩化炭素、シラン、ジボラン及びその組み合わせのような当業者に公知の適当なプラズマガスであり得る。

#### 【0057】

炉 250 も、一対の電極 274 及び 260 に電力を供給するマッチングネットワーク 272 を介して作動する高周波電源 270 に結合される。マッチングネットワーク 272 は電源及び炉チャンバーのインピーダンスにマッチさせて、チャンバーに最適なエネルギーの移送を提供する。圧力チャンバー 260 及び特にプレート 266 は、電極 274 と組み合わせて第 2 の電極として付加的に機能することに留意されたい。従って、圧縮されたチャンバー 260 は導電材料から成る。

#### 【0058】

電源 270 は高周波電源であり、一実施形態では誘導的に結合された高周波 ( " R F " ) 電源である。電源 270 から高周波エネルギーは、プレナム 266 を通ってハウジング 252 に入る反応ガス分子を励起し、分子をイオン化する。流動床はコア粒子の反応が一様になるように、上述のような粒子をイオン化ガスと連続して混合させる。

#### 【0059】

一実施形態では、炉 250 は、上述のようなドープコアシリコン 82 上に酸化物層を形成するのに用いられる。ドープコア粒子がチャンバー内に滞在する時間と、電極 274 及び 260 に供給される電力の量及び周波数と、選択されたガスとのすべてが酸化物成長率及び量を制御する。しかしながら、炉 250 は、酸化物シェル以外の粒子 80 のための他のコーティング又はシェルを形成するために使用することができる。例えば、システムは、プラズマエンハンス化学気相堆積法 ( " P E C V D " ) で異なる種類のコーティングを付けるのに用いることが可能である。

#### 【0060】

炉 250 は、一の好適な実施形態では、酸化物層又は他のコーティングをドープ半導体

10

20

20

30

40

50

コア 8 2 に付けるために使用され、他方、装置及び方法はコーティングを、ドーパントなしの半導体コア材料、絶縁材料及び導電材料のような他のコア材料に付けるために使用できることは評価されたい。実際、炉 5 0 は、図 3 B と併せて、以下に記載するコアシェル導電性粒子 9 0 を生成するのに用いることができる。

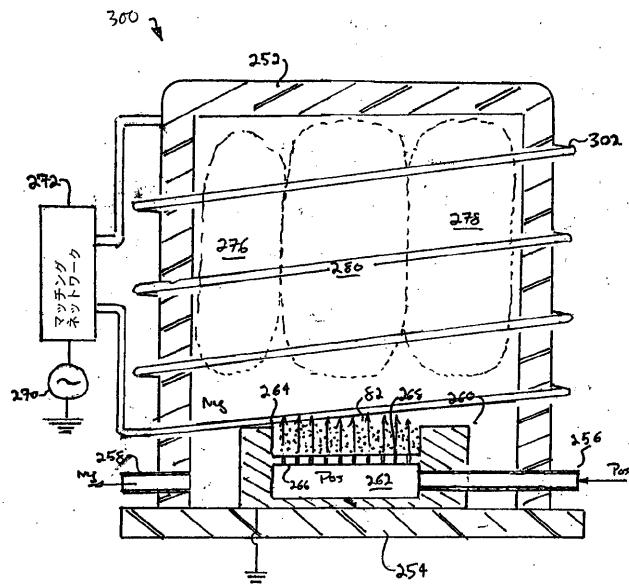

#### 【 0 0 6 1 】

図 17 に代替の炉 3 0 0 を示す。代替の炉 3 0 0 はその中に炉 2 5 0 の上述のような同じ機能を有する多くの同じコンポーネントを含む。これらのコンポーネントは同じ要素番号でマークされている。炉 3 0 0 は、ハウジング 2 5 2 に巻き付く誘導コイル 3 0 2 を含む。電源 2 7 0 からのエネルギーはコイル 3 0 2 を介して炉に誘導的に結合される。暗い又はシート状領域 2 7 6 及び 2 7 8 は代替の炉 3 0 0 の側部に沿って生成し、グロー放電領域 2 8 0 は、プラズマシート領域 2 7 6 と 2 7 8 との間に配置する。また、粒子 8 2 を取り込むガスフローは、粒子とプラズマグロー放電 2 8 0 との間の適当な混合を保証する。

#### 【 0 0 6 2 】

絶縁性粒子 6 0 、半導体粒子 7 0 及びドープ半導体粒子 8 0 のそれぞれは、VV M 1 0 0 のバインダー 5 0 に任意で分散する。バインダー 5 0 のヒュームド・シリカ、又は Ca b - o - Si 1 は絶縁性粒子を構成する。好適な実施形態では、VV M 1 0 0 は導電性粒子 9 0 を含む。一の実施形態における導電性粒子 9 0 は、 $10(\text{ } \cdot \text{ cm})^{-1}$  以上特に、 $100(\text{ } \cdot \text{ cm})^{-1}$  以上のバルク導電率（電気伝導率）を有する。しかしながら、ドープ半導体粒子を用いることによって、VV M 1 0 0 は導電性粒子 9 0 は含まないことも可能である。

#### 【 0 0 6 3 】

一実施形態における導電性粒子 9 0 は、 $60 \mu\text{m}$  の最大平均粒子サイズを有する。一実施形態では、導電性粒子 9 0 の 95% は  $20 \mu\text{m}$  以下の直径を有する。他の実施形態では、導電性粒子 9 0 の 100% が直径  $10 \mu\text{m}$  以下である。他の実施形態では、サブミクロン範囲例えば、 $1 \mu\text{m} \sim n\text{m}$  の平均粒子サイズを有する導電性粒子 9 0 を用いる。

#### 【 0 0 6 4 】

V V M 1 0 0 の導電性粒子 9 0 に適した材料は以下を含む：アルミニウム、真ちゅう、カーボンブラック、銅、グラファイト、金、鉄、ニッケル、銀、ステンレス鋼、すず、亜鉛、及びこれらの合金、さらには他の金属合金。また、ポリピロール又はポリアニリンのような真性の導電性ポリマー粉末を、これらが安定な電気的特性を示す限りは用いてもよい。

#### 【 0 0 6 5 】

一実施形態では、導電性粒子 9 0 は、アトランチック・イクリップメント・エンジニア (Atlantic Equipment Engineers) 製であって商品名 N i - 1 2 0 で市販され、 $10 \sim 30 \mu\text{m}$  の範囲の平均粒子サイズを有するニッケルを含む。他の実施形態では、導電性粒子 9 0 はアルミニウムを含み、 $1 \sim 30 \mu\text{m}$  の範囲の平均粒子サイズを有する。

#### 【 0 0 6 6 】

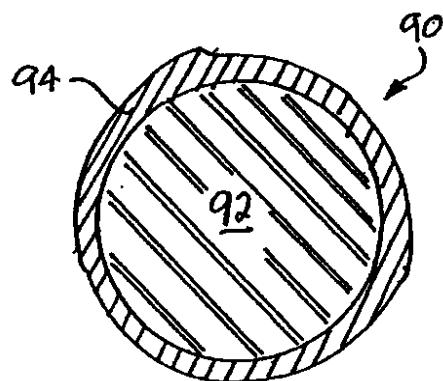

一実施形態における導電性粒子 9 0 はコーティングされず、本質的に单一材料から成る。図 3 B に示したように、他の実施形態では、導電性粒子は、外側シェル 9 4 に囲繞された内部コア 9 2 を含む。粒子 9 0 のコア 9 2 及びシェル 9 4 は異なる電気伝導度を有する。一実施形態では、コア及びシェル粒子 9 0 は実質的に球形状であり、約  $25 \sim 50 \mu\text{m}$  の範囲である。

#### 【 0 0 6 7 】

一実施形態では、導電性粒子 9 0 の内部コア 9 2 は絶縁材料を含み、外側シェル 9 4 は以下の材料のうちの一つを含む：(i) 導体；(ii) ドープ半導体；又は、(iii) 半導体。他の実施形態では、導電性粒子 9 0 の内部コア 9 2 は半導体材料を含み、外側シェル 9 4 は以下の材料のうちの一つを含む：(i) 導体；(ii) ドープ半導体；又は、(iii) 内部コアの半導体材料以外の半導体。他の実施形態では、内部コア 9 2 は導電材料を含み、外側シェル 9 4 は以下の材料のうちの一つから成ってもよい：(i) 絶縁材料；(ii) 半

10

20

30

40

50

導体；(iii) ドープ半導体；又は、(iv) 内部コアの導電材料以外の半導体。

【0068】

導電コア-シェル粒子で用いるのに適した導電材料は以下の金属及びその合金を含む：アルミニウム、銅、金、ニッケル、パラジウム、プラチナ、チタン、及び亜鉛。カーボンブラックをVVM100内の導電材料として用いてもよい。上述の絶縁材料60、半導体粒子70、及びドープ半導体粒子80は、本発明のVVM100のバインダー50における導電コア-シェル粒子90と混合してもよい。

【0069】

一の好適な実施形態では、コア-シェル粒子90はアルミニウムコア92と酸化アルミニウムシェル94を含む。アルミニウムコア92と酸化アルミニウムシェル94を含む粒子90は、追加の絶縁性粒子60、半導体粒子70半導体粒子70又はドープ半導体粒子80なしでヒュームド・シリカを有する本質的に付着性のバインダーに含めることができる。

【0070】

他の実施形態において、コア-シェル粒子90は、二酸化チタン(絶縁体)コア92と、アンチモンドープ酸化すず(ドープ半導体)シェル94を含む。これらの後者の粒子は商品名Zelec 1410-Tで市販されている。他の適したコア-シェル粒子90は商品名Zelec 1610-Tで市販され、ホローシリカ(絶縁体)コア92とアンチモンドープ酸化すず(ドープ半導体)シェル94を含む。

【0071】

フライアッシュ(絶縁体)コア92とニッケル(導体)シェル94を含む粒子、及び、ニッケル(導体)コア92及び銀(導体)を有する粒子はノバメット(Novamet)から市販されており、本発明における使用に適している。他の適した代替は、商品名ビスマルチ Ti-9115でペンシルバニア州アレントンのコンポジット・パーティクル社(Composite Particles, Inc)によって市販されている。これらの導電性コア-シェル粒子は、超高密度ポリエチレン(UHDPPE)の絶縁性シェル92と炭化チタン(TiC)の導電性コア材料94とを有する。また、商品名オイノックス(Eeonyx)F-40-10DGでマーテック社(Martek Corporation)から市販されている、カーボンブラック(導体)コア92とポリアニリン(ドープ半導体)シェル94を含むを有する粒子90を、本発明のVVM200において用いてもよい。

【0072】

VVM100の一実施形態では、本質的な(真性の)付着性絶縁バインダー50は、全組成物の約20重量%～約60重量%、特に約25重量%～約50重量%を構成する。一実施形態における導電粒子90は、全組成物の約5重量%～約80重量%、特に約50重量%～約70重量%を構成する。これらの範囲は、VVM100が追加の絶縁性粒子60、半導体粒子70、及び/又は、ドープ半導体粒子80を含むか否かを決める。存在する場合は、半導体粒子70は全組成物の約2重量%～約60重量%、特に約2重量%～約10重量%を構成する。

【0073】

VVM100の他の実施形態では、真性の付着性絶縁バインダー50は、全組成物の約30体積%～約65体積%、特に約35体積%～約50体積%を構成する。ドープ半導体粒子80は、全組成物の約10体積%～約60体積%、特に約15体積%～約50体積%を構成する。半導体粒子70は、全組成物の約5体積%～約45体積%、特に約10体積%～約40体積%を構成する。絶縁性粒子60は、全組成物の約1体積%～約15体積%、特に約2体積%～約10体積%を構成する。

【0074】

VVM100のスイッチング特性は、絶縁性、半導体性、ドープ半導体性、及び導電性粒子の性質と、粒子サイズ及び粒子分散と、粒子間距離によって決定される。粒子間距離は、絶縁性、半導体性、ドープ半導体性、及び導電性粒子の装填比と、そのサイズ及びサイズ分散に依存する。本発明の組成物においては、粒子間距離は一般に1,000以上である。

10

20

30

40

50

## 【0075】

真性付着性絶縁バインダー50及び上述の他の粒子を用いるVVM100の使用を介して、本発明の組成物を、約30ボルトから2,000ボルト以上のクランプ電圧の範囲を提供するよう調整され得る。回路ボードレベル保護をするための本発明のある実施形態は、100~200ボルトの範囲、特に100ボルト以下、さらには50ボルト以下のクランプ電圧を示し、特別には、約25~約50ボルトの範囲のクランプ電圧を示す。

## 【0076】

真性の付着性絶縁バインダー50を有するVVM100は、導電材料及び絶縁材料に自己硬化し、又は、自己固定する。絶縁バインダー50は、種々の絶縁材料、ラミネート又は基板に付着又は硬化する。例えば、絶縁バインダー50は、プリント配線板材料、フレキシブル配線板材料、ポリマー、ガラス、及びセラミックに付着又は硬化する。

## 【0077】

一実施形態では、VVM100の絶縁バインダー50は、公知のFR-4ラミネートに付着又は硬化する。FR-4ラミネートは通常、メッシュ形成され又は穴開きにされた織物又は非織物を含む。VVM100の絶縁バインダー50は多層PCBのFR-4層に固定されてもよい。他の実施形態では、VVM100の絶縁バインダー50はポリイミド材料に付着又は硬化する。絶縁バインダー50が本質的に固定されるポリイミド材料の一種はデュポン社製であり、“カプトン(Kapton)”と称される。カプトン(登録商標)材料の3種類の変型態様がある。第1のカプトン(登録商標)材料はアクリル主成分接着剤を含むが、難燃剤ではない。第2のカプトン(登録商標)材料はアクリル主成分接着剤を含み、難燃剤である。第3のカプトン(登録商標)材料は接着剤なしである。VVM100の絶縁バインダー50は各変型態様に付着又は硬化できる。

## 【0078】

VVM100の絶縁バインダー50はさらにリジッド(剛性)-フレキシブル材料に固定できる。その名前は暗示するが、リジッド-フレキシブル材料は2つの異なる材料(一方はフレキシブル(ピララックス(Pyralux)のような)で他方はリジッド(FR-4))のコンポジットである。この種の材料は、可動又は曲がり部分への接続を要し、また、コンポーネント用の安定なプラットフォームを要する用途に特に有効である。

## 【0079】

## 一の好適なVVM

図3Aに示したドープ半導体コアシェル粒子は、EOS過渡電流に対抗するのに適した電圧可変材料を製造するのに多くの異なる種類の組み合わせに適している。一実施形態では、図3Aの粒子80は、ここに記載された導電性粒子90のいずれかと共に、上述のバインダー50のような絶縁バインダーにおいて混合される。一実施形態では、導電性粒子90は、実質的に酸化されていないピュアニッケルのような実質的にピュアな材料を含む。しかしながら、図3Aの粒子は、図3Bと関連して以下のコアシェル型の導電性粒子と共に用いることができる。さらに、図3Aに関連して図示された粒子80は、非ドープ半導体粒子70、導電性粒子90、及び、絶縁性粒子60と組み合わせて備えることができる。一実施形態では、ナノタンクステンパウダーをさらに加える。

## 【0080】

一の好適な実施形態では、VVM100は図3Aに関連して記載した粒子をニッケルと組み合わせて用いて作製する。ここで、ドープ半導体粒子は約40体積%~約80体積%の濃度で備えられ、ニッケル粒子は約5体積%~約25体積%の濃度で備えられる。この濃度は、VVM100が上述の加熱・冷却の多段階を介して適当に硬化されたときのものである。すなわち、VVM100を製品につけたときのものである。これらの粒子は、ここに記載した直接適用特性を有するようにカルビトールアセテートを介して溶解されるポリマーである絶縁バインダー50で混合される。できたVVM100は約1400~約 $14 \times 10^6$ cmの抵抗を有する。

## 【0081】

## VVMの直接適用

10

20

30

40

50

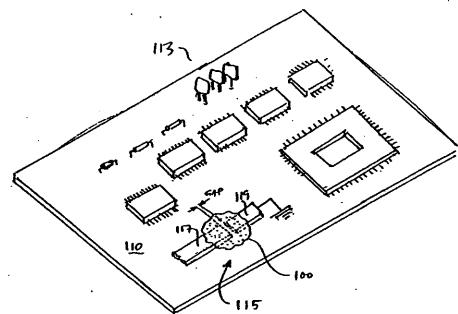

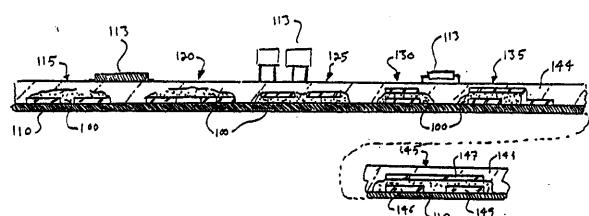

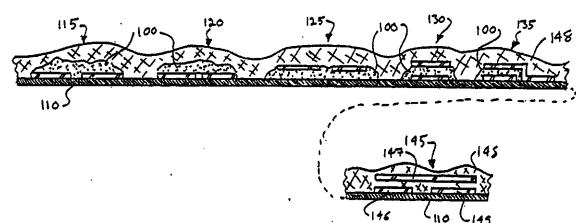

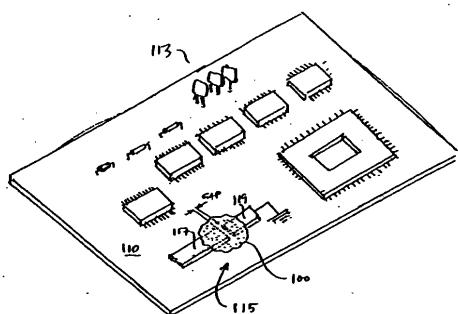

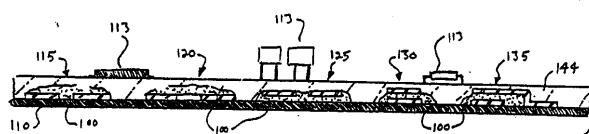

図4に、本質的に付着性のVVM100用の可能な一の構成115を示す。この例においては、この構成115がリジッドPCBである基板上に配備されている。PCB基板110を最終形態にするときにVVM100をオープンにし露出することを示すが多くの他の電気装置113を図示している。電気装置113は、スルーホール及び表面実装装置の両方を含むPCBに共通に結合された種々の電気装置を含む。電気装置113は、抵抗又はキャパシタのような電気的コンポーネントを含む。電気装置113は、種々の集積回路、コネクタ、フィルタ等も含む。

#### 【0082】

構成115は、PCB基板110上で他の電気的コンポーネント113の隣りに配置する。構成115は当業者に公知の方法によってそれぞれPCB基板110に固定された2つの電極117及び119を有するように示した。2つの電極117及び119を示したが、構成115は多数の電極を有することもできる。構成115では、VVM100の量は本質的に電極117及び119と、基板110とに固定される。この斜視図に示した電極117及び119の間にギャップが存在する。というのは、これを一定塊のVVM100によって覆うからである。一実施形態におけるギャップ幅は2ミル程度であるが、より広い又はより狭い幅にしてもよい。電極117及び119は通常、互いに電気的にはつながっていない。EOS過渡電流の事象の際に、VVM100は高インピーダンス状態から低インピーダンス状態へスイッチし、ここで、過渡電流スパイクは電極117からVVM100を通って、図示したようにシールドグランド又は接地に接続されている電極119へ分路する。

#### 【0083】

便宜上図示したような電極117は寸断された端部で終端している。電極117はいかなる電気的装置につながることができることを評価すべきである。一実施形態では、電極117は、例えば通信伝達から信号を運ぶPCB上のトレースである。この場合、電極117は通信入力ラインを受けるコネクタ又はある種のトランシーバにつながってもよい。

#### 【0084】

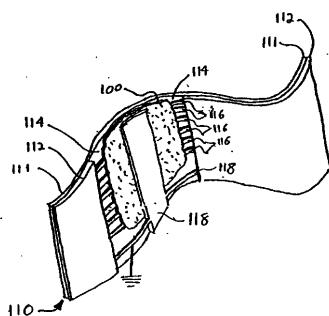

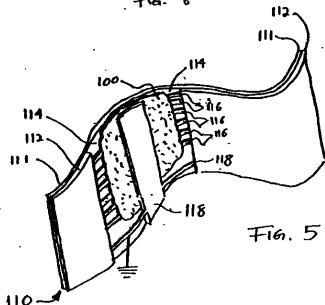

図5に示したように、“Z”方向構成を基板上に示したが、一実施形態においては多層フレキシブルリボン又は回路である。フレキシブル基板110は複数のフレキシブル層111及び112を含む。上述のように、フレキシブル基板110はポリイミドから成る層111及び112を含んでもよい。例えば、層111及び112はカプトン（登録商標）であってもよい。他の実施形態では、層111及び112の一方又は両方はマイラー層である。グランド導体118と共に、多くの信号導体116を示すために、基板110の層112の部分を分断している。導体116及びグランド導体118を露出して、自己硬化可能バインダー50を有する自己付着性VVM100は、導体116のそれぞれに付けることができる。

#### 【0085】

図示したように、導体116及びグランド導体118のそれぞれは、導体が通常は互いに電気的につながっていないようにギャップで分離されている。一実施形態では、グランド導体（便宜上示した部分のみ）118はVVM100の頂部に配置している。従って、ギャップは“Z”方向にあると称する。ここで、導体116間のギャップはX-Y面にある。VVM層の層厚は信号導体116間のスペーシングより小さい。従って、EOS過渡電流は導体116の一つから他の導体116への替わりにグランド118へジャンプする。他の実施形態では、分離したグランドトレース118は、過渡電流が信号トレース116からグランドトレース118へジャンプするように、各信号トレースに隣接して配置することができる。いずれにしても、VVM100の層は、過電圧を受けるいずれの信号導体116も、それをグランド導体118に分路する。

#### 【0086】

図4のリジッドPCB用途のように、導体又は電極116（及び118）を基板の表面に固定する。ここで、導体116は、当業者の公知の方法によってフレキシブル層111の内面に固定する。“Z”方向実施形態では、グランド導体はVVM100の層の最上面

10

20

30

40

50

にくつつく。導体 116 及びグランド導体 118 も、多層 111 及び 112 によって適所で圧縮され保持される。しかしながら、VVM100 はフレキシブル層 111 及び 112 のいずれか一つの外側で露出されることが可能である。図示したように VVM100 が導体 116 のそれぞれを覆い、本質的に層 111 の内面 114 に付着する。VVM100 の層は複数の導体 116 及び層 111 の内面 114 に追加の硬化又は加熱段階を必要とすることなく自己硬化する。しかしながら、他の実施形態では、VVM100 の層は、所定長さの時間フレキシブル回路を加熱することによってより迅速に硬化してもよい。

#### 【0087】

上述のバインダー 50 は、VVM100 が、フレキシブル基板 110 が曲がり又は動くときにさえ、クラック又はスプリットしないような様式で硬化する。それさえ、好適な実施形態では、内面 114 及びグランド面 118 の露出領域は、電気的絶縁のために覆う。一実施形態では、VVM100、導体 116 及びグランド導体 118 はシルバーインクコーティングによって被覆されている。一実施形態では、VVM は、VVM100 の散逸能力をエンハンスするために、トレース 116 及びグランドトレースの全面を被覆することができる。他の実施形態では、ドライ膜写真画像可能（フォトイメージャブル）カバーレイ、スプレー液体のような写真画像可能カバーレイ、又は、“グロブ・トップ”コーティングのような介在絶縁コーティングを、信号トレース 116 と外側絶縁（例えば、プラスチック）層 111 の内面 114 との間に配備することができる。

#### 【0088】

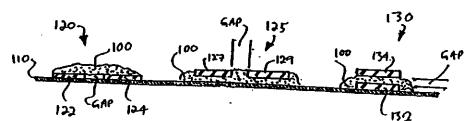

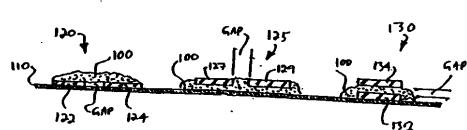

図 6 に、VVM100 のための 3 個の代替製品 120、125、及び 130 を示す。代替製品 120、125、及び 130 はいずれも、2 個しか導体を有しない簡単な形で示している。しかしながら、ここに開示した製品はいずれも、図 5 に示したように、電気的に接続することができ、多数の導体を保護することができることは評価されたい。図示しないが、導体の一つはグランド若しくはシールド導体であり、又は、導体の少なくとも他の一つは信号若しくはライン導体であることを仮定すべきである。ここで、VVM100 は過電圧過渡電流を信号若しくはライン導体からグランド若しくはシールド導体へ分路する。さらに、製品 120、125 及び 130 は最終形態で図示しており、VVM100 は環境に対してオーブンであり、露出している。

#### 【0089】

構成 120 は、ギャップによって離隔された導体 122 及び 124 を有する回路を示している。導体 122 及び 124 のそれぞれは、当業者に公知の方法によって基板 110 に固定されている。基板 110 は、リジッド PCB 基板又はフレキシブル回路型基板のような上述の基板のいずれかであり得る。製品又は回路 120 は、VVM100 が基板 110 に固定しない回路 115 と異なる。このような回路を作製するために、VVM100 が適所で硬化し乾燥するまで、ギャップの上方で VVM100 を支持することが必要だろう。他の実施形態では、トップ層又はコーティングは VVM100 に固定されてもよい。ここで、コーティングが半硬化状態の VVM100 を導体 122 及び 124 上に配置することができる。重要なことには、VVM100 は、VVM100 が適当に機能するために、ギャップ領域において基板 110 を付着する必要はない。回路 120 は、VVM100 の分路能力について、図 4 で示したような回路 115 と全く同じように機能する。

#### 【0090】

回路又は構成 125 は、VVM100 は本質的に基板 110 に固定し、これによって、導体 127 及び 129 が配置するバッファ若しくはベッドを形成することができる。電極 127 及び 129 はギャップによって分離されている。電極は図示したように VVM100 にわずかに沈んでいてもよく、又は、電極 127 及び 129 は導体の重量のため、又は、付け工程のために変形しなくなるまで、VVM が硬化するときに VVM100 上に配置してもよい。

#### 【0091】

回路又は構成 130 は、導体の一つすなわち、導体 132 は基板 110 に固定し、第 2 の導体 134 を、構成 125 の電極 127 及び 129 と同様に VVM100 の層の最上面

10

20

30

40

50

に備えた実施形態を示している。回路 130 のギャップは垂直に配備したギャップである。構成 115, 120 及び 125 のギャップは水平に配備されている。VVM100 は、ギャップが構成 115, 120 及び 125 と同様に “XY” 方向型のギャップであるか、又は、ギャップが構成 130 で示したように “Z” 方向型のギャップであるかによらず、等しく機能することは評価されたい。

#### 【0092】

図 6 の構成のそれぞれは、ある電気的構成において、及び、ある電気的コンポーネントで望ましい。本発明の絶縁バインダー 50 を有する VVM100 は、基板 110 について異なる様式で電極を配置する融通性を提供する。ここで、VVM100 は、VVM100 を機械的に保持し、又は、それを導体に電気的に接続するための特別の装置若しくはハウジングを必要としない。例えば、多くの VVM 装置は、VVM を適所に保持するハウジング又はシェルを要しない。多くの VVM のものは、基板の表面上に形成された一対のパッドにハンダ付けしなければならないハウジング又はシェル上に配備された一対のターミナルも含む。パッドから、信号ライン又はグランドラインの接続へ延長するのには追加のトレース又はボンドワイヤを要する。

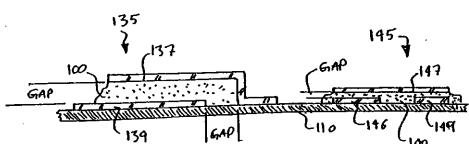

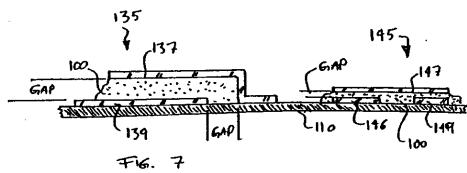

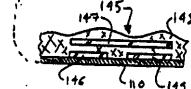

#### 【0093】

図 7 に、追加の回路又は構成 135 及び 145 を示す。構成 135 は、上部電極 137 と下部電極 139 との間の “Z” 方向ギャップを有する構成 130 と同様である。ここで、下部電極 139 は基板 110 に固定する。しかしながら、構成 135 では、上部電極 137 が、下部電極 139 から横方向又は水平方向に延びて、下方へ方向を変え、基板 110 に固定される。水平オフセットは第 2 のギャップを形成する。過電圧が形成されるとき、過渡電流スパイクが、経路 (パス) がどのくらい低いインピーダンスを有するかに依存して “Z” 方向又は “XY” 方向のいずれかに VVM100 を介して伝導する。構成 135 は他の構成と同様に作動する。

#### 【0094】

構成 145 は、導体 146 及び 149 が剛性基板 110 上に配備する以外は、図 5 のフレックス回路実施形態と同じである。一実施形態では、フローティング導体 147 はグランド導体であり、完全に “Z” 方向製品にするものである。他の実施形態では、導体 146 と 149 のいずれかは、製品を “Z” 方向及び “XY” 方向製品にするグランド導体であり、ここで、電圧は導体 146 から 149 のうちの一つからフローティング導体 147 へ、及び、さらに下のグランド導体である他の導体へ放電できる。

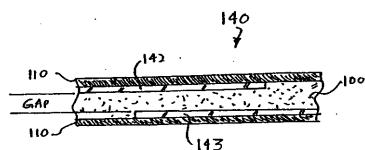

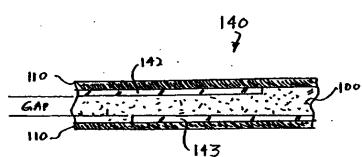

#### 【0095】

図 8 に、他の代替の構成又は回路 140 を示す。回路 140 は、FR-4 ボードのようなリジッドな基板、又は、ポリイミド若しくはカプトン (登録商標) のようなフレキシブルな基板であってもよい 2 つの基板を含む。第 1 の電極 142 は上部基板 110 に固定され、第 2 の基板 143 は下部基板 110 に固定されている。電極 142 と電極 143 とは、VVM 塊 110 によって “Z” 方向に離間して配備されている。構成 140 は例えば、フレキシブル基板において有効である。ここで、基板 110 がカプトン (登録商標) 若しくはマイラー樹脂の外側層であり、上部基板 142 は例えば、信号導体であり、下部基板 143 はグランド導体である。ここで、多数の信号導体を上部若しくは下部基板 110 のいずれかにつけることができ、ここで、過度電流スパイクが、過度電流スパイクを有する信号トレースがグランド導体に対してどこに配置しているかに依存して垂直又は水平に伝わる。

#### 【0096】

図 9 に、前述の構成又は回路 115, 120, 125, 130, 135, 及び 145 は多層 PCB 内に埋め込まれているように示している。すなわち、基板 110 は多層 PCB の一層を構成する。第 2 の基板 144 は (寸法通りではない)、多層 PCB の他の層を構成する。層 144 は、電気的コンポーネント 113 及び回路配線板トレースを実装するのに適した滑らかな外面を形成するために種々の回路の周りに形成されている。図 9 の構成は、基板 110 及び 144 の外面によって回路保護によって抑制されていないので特に有

10

20

30

40

50

効である。図9に示した構成は2層以上を含むことができ、この様態は、構成115, 120, 125, 130, 135, 及び145の一又は二以上を有する異なる多数の基板を含むことができる。

#### 【0097】

図10は、回路115, 120, 125, 130, 135, 及び145を有する同様な構成を示すが、多層PCBの一部である構成の代わりに、構成は保護コーティング148によって被覆されている。たとえ、VVM100がある箇所において種々の電極及び基板110に自己固定しても、多くの理由のために保護コーティング148をつけることは望ましい。例えば、図5で示したフレキシブル回路と同様に、導体はある点で露出され、電気的絶縁を必要とする。保護コーティング148は当業者には公知の種類のコーティングであり得る。一実施形態では、コーティングは、銀インク、乾燥膜(ドライフィルム)写真画像可能バーレイ、スプレー液体写真画像可能バーレイ、若しくは“グロブ・トップ”コーティングのような図5におけるフレキシブル回路のような上述のコーティングを含む。

#### 【0098】

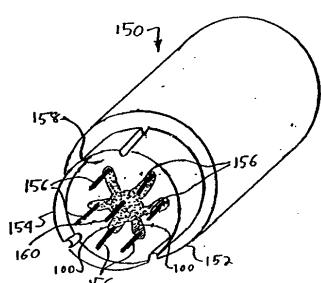

##### 直接VVMを含む装置

図11に、本発明のVVM100は装置内で用いてもよい。図11に示す装置の一種類は、ドイチェ・インスティチュート・フュア・ノームング(Deutsches Institut für Normung) e.V.(“DIN”)標準を含む。本発明は、小型DINコネクタ、二重列延伸DINコネクタ、シールドDINコネク等用に対して適用される。本発明はプラグ若しくはリセプタクルに組み込まれてもよい。ケーブルに取り付けられた垂直、水平及びインラインコネクタを用いてもよい。さもなければ、DINコネクタはパネル実装されてもよい。

#### 【0099】

コネクタ150は、適当な材料からなるボディ152を含む。プラグ及びコンセントの組み込まれたボディは、複数の信号導体156を少なくとも囲繞する円形壁若しくは複数の(図示しない)ストレートな壁を固定する。導体156は、壁154と実質的に平行な方向に基板158から延伸している。壁154及び156は、周知の合わせ(メーティング)雌DINコネクタにプラグインしている。

#### 【0100】

図示した実施形態では、ボディ152はプラグであり、導体156はピンである。(図示しない)他の実施形態では、ボディはリセプタクルであり、信号導体は合わせコネクタからピンを受けるソケットである。一又は二以上の外側信号導体156はグランド導体であってもよい。しかしながら、通常は離隔した(ここでは中央の)グランド若しくはシールドグランド導体160を備える。過度電圧スパイクをグランド導体160に適切に分路する図示の実施形態では、入力/出力導体156とグランド導体160との間の距離は、入力/出力導体156間の距離よりも小さくあるべきである。

#### 【0101】

一実施形態では、基板158はFR-4ボードのようなPCBである。他の実施形態では、基板158はポリイミド若しくはプラスチックのような他の種類の絶縁材料を含む。基板158はボディ152内にフィットされて、コネクタ150は合わせコネクタ内に適切に配置される。一実施形態では、基板158は、導体156が基板158の裏側から図示の表側を貫通可能とするアパーチャーを画定する。

#### 【0102】

少なくとも一つのVVM100は基板158に直接付着され、硬化される。図示したように、本発明のVVM100は、トレース若しくはボンドワイヤを必要とせずに、信号導体156をグランド導体160に直接結合する。他の実施形態では、一又は二以上の導体156若しくは代替としてグランド導体160は個々のVVM100にコンタクトする。ここで、一又は二以上のトレース若しくはボンドワイヤは個々にVVM100を他のVVM100若しくは他の導体に固定する。一実施形態におけるトレースは周知のPCB基板158上にエッティングされる。信号トレースは、单一信号導体156及び/又はグランド

導体 160 のいずれか又は両方と連通することができる。

【0103】

グランド導体 160 は複数の形態をとり得、中央に配置したピン 160 のようにここに図示している。グランド導体 160 は所望の回路グランド若しくはシールドグランドのいずれかとして機能してもよい。

【0104】

図示したように、少なくとも一つの VVM100 は過度電圧スパイクから一又は二以上の信号導体 156 を保護する。保護された導体 150 は、コネクタ 150 から電気的に上流若しくは下流のいずれかにある他の電気装置を保護することができる。

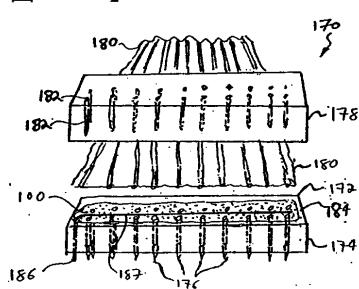

【0105】

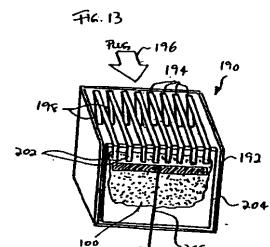

図 12 に、一体の付着性バインダー 50 を有する VVM100 は、リボンケーブルコネクタ 179 と共に用いる。VVM100 はあらゆる種類のリボンケーブルコネクタと共に用いることができる。例えば、ソケットコネクタの雄、雌、ストレートリード、直角、ストレートリード / ワイヤラップ、及び直角 / ワイヤラップ版、D コネクタ、PCB コネクタ、カードエッジコネクタ、ディップコネクタ、ピンコネクタ、又は、ターミネーションジャンパー。VVM100 は、リボンコネクタ 170 のプラグ若しくはリセプタクルに組み込んでもよい。

【0106】

リボンコネクタ 170 は、適した材料からなり、一実施形態においてプラスチックであるボディ 172 を含む。プラグ及びリセプタクルに組み込んだボディ 172 は少なくとも部分的に複数の導体 176 を囲繞する。導体 176 はボディ 172 の壁に実質的に平行である。ボディ 172 がプラグであれば、導体 176 はピンである。ボディ 172 がリセプタクルであれば、導体 176 はピンを受けるソケットである。リボンコネクタ 170 が多くの入力 / 出力信号導体 176 を固定してもよい。一又は二以上の導体 176 はグランド導体であってもよい。通常は、離隔した回路グランド若しくはシールドグランド 186 を備える。グランドストリップ 187 はグランドピン 186 に接続し、適したスペーシング (距離) を提供して、電圧過度電流が信号導体 176 の一つから他の信号導体 176 でなくグランドストリップ 187 へ散逸するようとする。

【0107】

ボディ 172 と第 2 の合わせボディ 178 との間にリボンケーブル 180 を備える。リボンケーブル 180 は、グレイフラットケーブル、カラーコードフラットケーブル、ねじれペアフラットケーブル、ラウンド (丸め) ジャケット / シールドフラットケーブルを含むいかなるケーブルであってもよい。図示した実施形態では、第 2 のボディ 178 はリセプタクルボディ 172 全体にフィットするプラグである。プラグボディ 178 内にハウジングされたプラグ 182 は、ケーブル 180 の絶縁を貫き、ケーブル内の導体に電気的コンタクトを形成する。

【0108】

図示した実施形態では、少なくとも一つの、可能なら複数の VVM100 は、バインダー 50 の本質的な付着特性を介してリセプタクル 172 及び導体 176 に直接固定する。リセプタクルボディ 172 は、ポリマー、FR-4 のような PCB 材料、又はポリイミドであり得る基板 184 を含む。VVM100 は、基板 184 の頂部若しくは下部基板 184 のいずれかにつけることができる。他の実施形態では、トレースは適した方法によって基板 184 につけられる。トレースは信号導体 176 を VVM100 に電気的に接続し、又は、VVM100 をグランド導体 186 に接続し、又はそれらの両方を行う。

【0109】

図示したように、少なくとも一つの VVM100 は、リボンケーブルコネクタ 170 の一又は二以上の信号導体 176 を過度電流スパイクから保護する。すなわち、信号導体 176 は過電圧をグランドピン 176 に分路できる。リボンコネクタ 170 は、電気的に上流の若しくは下流の電気装置をリボンコネクタ 170 から保護することができる。

【0110】

10

20

30

40

50

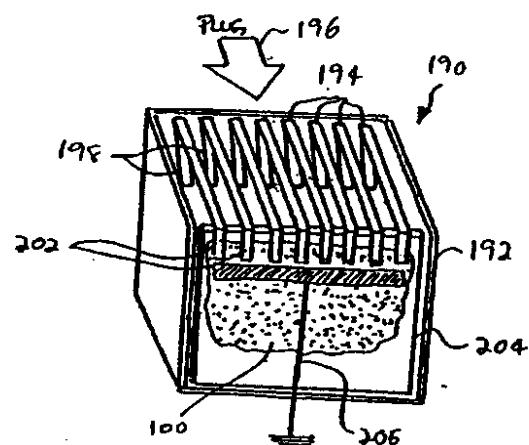

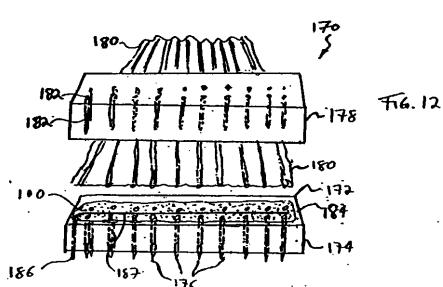

図13に示すように、一体に付着するバインダー50を有するVVM100はデータ若しくは通信コネクタ190と共に用いる。VVM100は、いかなるデータ／通信コネクタ190と共に用いることもできる。一実施形態では、導体190は、ローカルエリアネットワーク（“LAN”）、ワイドエリアネットワーク（“WAN”）等のデータネットワークにおいて通常用いられている8導体RJ-45導体である。他の実施形態では、導体190はレジデンシャル型で及び市販の電話システムにおいて通常使用されている6導体RJ-11導体である。

#### 【0111】

導体190はボディ190を含む。その大部分はVVM100による回路保護を示すために切開している。ボディ190は適した材料からなり、一実施形態ではプラスチックである。ボディは多くの信号導体194を固定する。信号導体194は適当に曲げられ、（図示しない）プラグの合わせ信号導体に係合される。プラグは矢印196の方向でデータ／通信ボディ192に挿入される。プラグをボディ192に挿入するとき、信号導体194のバネ部198は、弾性力が合わせ導体の間の電気的接続にかかるように曲げられている。

#### 【0112】

図示した実施形態では、導体194の反対側の端部202は一又は二以上のVVM100に直接電気的に通じている。ここで、VVMは本質的な付着性バインダー50を介して基板204に直接つけられている。VVM100は信号導体194をグランド導体206に直接電気的に結合している。上述のように、グランド導体206は、信号導体194のそれ同士よりも信号導体194のそれぞれにより近く離隔されて適当に配置されている。他の実施形態では、導体194の端部202は、VVM100が付着するトレースに電気的に接続している。他の実施形態では、VVM100はワイヤボンドを介して信号導体194の端部202に電気的に接続している。

#### 【0113】

同様に、一実施形態におけるVVM100はグランド導体206に直接付着している。他の実施形態では、グランド導体206は、基板204に固定されている一又は二以上のトレースを介してVVM100に電気的に通じている。他の実施形態では、VVM100はボンドワイヤを介してグランド導体に電気的に通じている。

#### 【0114】

上述のように、一若しくは二以上又は全ての信号導体194は過度電圧から保護されてもよい。LAN又はWANは接地点の間の大きな距離を囲繞しているので、接地点間のESD及びEOS過度電流は深刻な問題である。エアコンディショナー、ヒーター、エレベータ、コピー、レーザープリンター等の装置は、LANを有するビルにおいて高いレベルのスパイク及び過度電流を生じ得る。保護されたデータ／通信コネクタ190は、導体190を介してネットワークに接続された装置をネットワークのデータ線にかかる過度電圧から保護する。同様に、コネクタ190は、ネットワークに接続された装置から発せされる過電圧現象からデータ線を保護する。

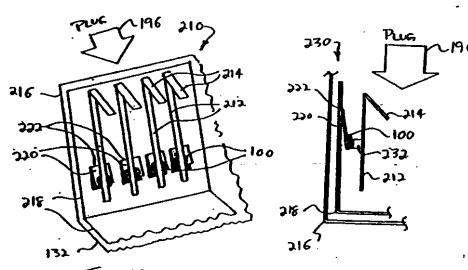

#### 【0115】

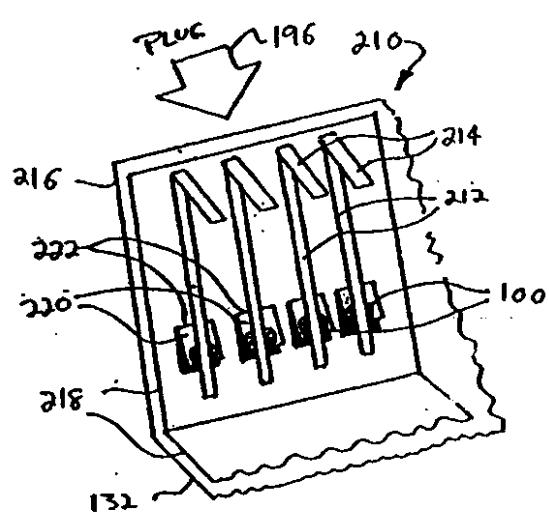

図14及び図15に、通信コネクタに付けられたVVM100の他の実施形態を示す。図14及び図15に示した構成は、種々のタイプのデータ／通信コネクタを表す。図14には、コネクタ210の関連部分だけを示した。コネクタ210は曲がり端部214を有する複数の信号導体212を含む。ここで、曲がり端部214は導体又は上述の（図示していない）データ／通信プラグと係合する。プラグは、コネクタ210に挿入される矢印196の方向に動く。

#### 【0116】

図示のために切開したボディ216は、適当な導電性材料から成るシールド218をハウジングする。図14は、図13で示したコネクタを下から見たものである。シールド218は、導体212の頂部上及び裏側にフィットする。

#### 【0117】

10

20

30

40

50

シールドは一又は二以上の切断されたバネタブ 220 を画定する。すなわち、薄い金属シールド 218 は各タブ 220 の 3 つの側部に沿ってスタンプされ又は切断されている。ここで、タブ 220 はエッジ 222 に沿って内側に曲がっている。タブ 220 は、90° より小さな所望の角度で内側に曲げられてもよい。シールド 218 をコネクタ 212 全体に配置するとき、タブ 220 は導体 212 に接触し、0° の方へ戻すように曲げられる。これによって、タブ 220 は導体 212 との電気的なコンタクトを維持するように付勢されている。

#### 【 0118 】

自己硬化性で本質的に付着性のバインダー 50 を有する一塊りの VVM100 は、タブ 220 と導体 212 との間においてタブ 220 に直接付けられる。VVM100 は高インピーダンス状態において開回路として作用し、これによって、導体 212 からグランド 218 へ通常ほとんど電流は流れない。ESD 過渡電流が生ずるときは、VVM100 は低インピーダンス状態にスイッチし、これによって、過渡電流スパイクはシールドグランド 218 へ分路される。

#### 【 0119 】

一実施形態では、ステンシルを用いて、複数の VVM100 塊を複数のタブ 220 に付ける。他の実施形態では、ステンシルを用いて、複数の VVM100 塊を、バネを利用して力を付与し、複数の導体 212 を用いてコンタクトさせる複数のタブ 220 に付ける。さらに他の実施形態では、VVM100 材料の層をシールド 218 の大きな領域（エリア）にまず自己付着させ、ついで、複数のタブ 220 はそれぞれが個々の VVM100 塊を有するようにスタンプされる。さらに他の実施形態では、VVM100 の層をシールド 218 の大きな領域（エリア）にまず自己付着させ、それぞれが複数の導体 212 に接触する一又は二以上のタブ 220 がスタンプされる。

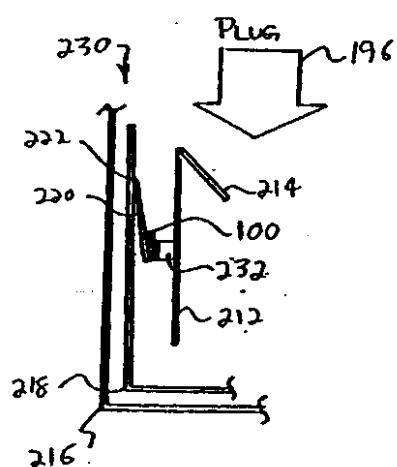

#### 【 0120 】

図 14 の側面図である図 15 に、図 14 のコネクタの変形態様を新しいコネクタ 230 として示す。前述のように、ボディ 216 はシールド 218 の一部が見えるように切開されている。シールド 218 は、タブ 220 がシールド 218 と導体 212 との間でエッジ 222 に沿って内側に曲がるようにスタンプされている。タブは、本発明の自己付着性バインダー 50 を有する VVM 塊 100 を有する。

#### 【 0121 】

信号導体 212 は、（図示していない）プラグの導体に係合するように適用された曲がりバネ部 214 を有し、ここで、プラグは矢印 196 で示した方向にコネクタ 230 に挿入する。一実施形態では、カップリングキャパシタ 232 をタブ 220 上の 100 と信号導体 212 との間に配置されている。一の好適な実施形態では、タブ 220、VVM100、キャパシタ 232 と信号導体 212 を直列につなぐ。キャパシタ 232 は、2500 ボルトの DC 電圧を扱うのに適したキャパシタンス及び定格電圧を有する。すなわち、カップリングキャパシタ 232 は、LAN 又はイーサネット（登録商標）システムがさらされることになるかもしれない、高ポテンシャル（HI-POT）テスト中に課される電圧のような高レベルの DC 電圧を遮断するように構成されている。

#### 【 0122 】

VVM100 は、キャパシタ 232 に付着して電気的に接触する。キャパシタ 232 は導体 212 にハンダ付けされ、もしくは、電気的に接続してもよい。タブ 220 のバネ弾性力によってキャパシタ 232 は適所に保持される。キャパシタ 232 及び VVM100 のオーダーは反転してもよい。図 14 及び図 15 において、スタンプされたタブ 200 を、当業者に公知の VVM を用いる（図示しない）VVM 装置と共に代替して使用されてもよいことは評価されたい。

#### 【 0123 】

図 11 から図 15 は、バインダー 50 を介した VVM100 は基板に直接付けることができ、基板はコネクタのような電気的装備の一部において用いられている。図示した種々のコネクタ以外に、基板は、オーディオヘッドセット、カムコーダー、テレビ、ラジオ、

10

20

30

40

50

個人メール装置、コンピュータ等の他の種類の装備と同様に、デジタルビデオインターフェース（“DVI”）コネクタ、アナログ/デジタル変換（“ADC”）コネクタ等の他のタイプのコネクタにおいて配置できることは評価されたい。

【0124】

ここに示した好適な実施形態に対する変形や変更は当業者には明らかであることは理解されたい。このような変形や変更は本発明の精神及び範囲から逸脱することなく、かつ、本発明の利点を減じることなく可能である。

【図面の簡単な説明】

【0125】

【図1】電気過大応力過渡電流の典型的な波形を模式的に示す図である。 10

【図2】本発明の電圧可変材料（“VVM”）用の可能なコンポーネントの断面模式である。

【図3A】本発明のVVMと共に用いられるコア及びシェルドープ半導体粒子の断面模式である。

【図3B】本発明のVVMと共に用いられるコア及びシェルドープ導電性粒子の断面模式である。

【図4】本発明の本質的に付着性のVVMについての一回路構成を示すリジッドな（剛性の）プリント配線板（“PCB”）の斜視図である。

【図5】本発明の本質的に付着性のVVMを有するフレキシブル基板の斜視図である。

【図6】本発明の本質的に付着性のVVMについての3個の追加の回路構成を示す断面立面図である。 20

【図7】本発明の本質的に付着性のVVMについての2個の“Z”方向型回路構成を示す断面立面図である。

【図8】本発明の本質的に付着性のVVMについての他の回路構成を示す断面立面図である。

【図9】多層PCBに積層された図4から図7の回路構成を示す断面立面図である。

【図10】保護コーティングで被覆された図4から図7の回路構成を示す断面立面図である。

【図11】直接付けられた本発明のVVMを有するDINの一実施形態を示す斜視図である。 30

【図12】直接付けられた本発明のVVMを有するリボンケーブルコネクタの一実施形態を示す斜視図である。

【図13】直接付けられた本発明のVVMを有するデータ/通信RJ型コネクタの一実施形態を示す斜視図である。

【図14】直接付けられた本発明のVVMを有するデータ/通信RJ型コネクタの一実施形態の多数の信号導体とシールドとを示す切開斜視図である。

【図15】直接付けられた本発明のVVMを有するデータ/通信RJ型コネクタの一実施形態の信号導体と、シールドと、キャパシタとを示す側立面図である。

【図16】本明細書に記載した電圧可変材料の粒子を被覆するのに用いるのに適した本発明の種々の流動床プラズマ炉の断面図である。

【図17】本明細書に記載した電圧可変材料の粒子を被覆するのに用いるのに適した本発明の種々の流動床プラズマ炉の断面図である。 40

【符号の説明】

【0126】

50 バインダー

60 絶縁性粒子

70 半導体粒子

80 ドープ半導体粒子

82 コア

84 ドーパント

## 8 6 コーティング

1 0 0 V V M

1 1 0 基板

1 1 5、1 2 0、1 2 5、1 3 0 回路又は構成

1 2 7、1 2 9 導体

1 3 0

1 3 2、1 3 4 導体

2 5 0 炉

2 5 2 ハウジング

2 5 4 ベース

10

【図 1】

【図 2】

【図 3 A】

【図3B】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【図16】

【 図 17 】

---

フロントページの続き

(72)発明者 エドウイン・ジェームス・ハリス

アメリカ合衆国・イリノイ・60015-3691・ディアフィールド・バンティング・コート・

283

(72)発明者 トウシャー・ヴィアス

アメリカ合衆国・イリノイ・60107・ストリームウッド・トレイル・リッジ・コート・5

(72)発明者 スティーヴン・ジェイ・ウィットニー

アメリカ合衆国・イリノイ・60047-7123・レイク・ズーリック・ウォリック・レーン・

942

F ターム(参考) 5E034 EA08 EA09 EB02 EB10 EC03 EC06

【外国語明細書】

## SPECIFICATION

### TITLE OF THE INVENTION

#### **“DIRECT APPLICATION VOLTAGE VARIABLE MATERIAL, COMPONENTS THEREOF AND DEVICES EMPLOYING SAME”**

### PRIORITY CLAIM

This application claims the benefit of U.S. Patent Application No. 10/410,393, filed April 8, 2003, entitled “Voltage Variable Material For Direct Application And Devices Employing Same”, the entire contents of which are hereby incorporated by reference and relied upon.

### CROSS-REFERENCE TO RELATED APPLICATIONS

This application is related to the following commonly-owned co-pending patent applications: “Polymer Composite Materials for Electrostatic Discharge Protection,” Serial No. 09/232,387, Attorney Docket No. 0112690-020; “Voltage Variable Substrate Material,” Serial No. 09/976,964, Attorney Docket No. 0112690-098.

### BACKGROUND OF THE INVENTION

The present invention generally relates to circuit protection. More specifically, the present invention relates to voltage variable materials.

Electrical overstress (“EOS”) transients produce high electric fields and usually high peak power that can render circuits or the highly sensitive electrical components in the circuits, temporarily or permanently non-functional. EOS transients can include transient voltages capable of interrupting circuit operation or destroying the circuit outright. EOS transients may arise, for example, from an electromagnetic pulse, an electrostatic discharge, lightning, a build-up of static electricity or be induced by the operation of other electronic or electrical components. An EOS transient can rise to its maximum amplitude in subnanosecond to microsecond times and have repeating amplitude peaks.

Materials exist for the protection against EOS transients, which are designed to respond very rapidly (ideally before the transient wave reaches its peak) to reduce the transmitted voltage to a much lower value for the duration of the EOS transient. EOS materials are characterized by high electrical resistance values at low or normal

operating voltages. In response to an EOS transient, the materials switch very rapidly to a low electrical resistance state. When the EOS dissipates, these materials return to their high resistance state. EOS materials also recover very rapidly to their original high resistance value upon dissipation of the EOS transient.

EOS materials are capable of repeated switching between the high and low resistance states. EOS materials can withstand thousands of ESD events and recover to desired off-status after providing protection from each of the individual ESD events.

Circuits employing EOS materials can shunt a portion of the excessive voltage or current due to the EOS transient to ground, protecting the electrical circuit and its components. Another portion of the threat transient reflects back towards the source of the threat. The reflected wave is attenuated by the source, radiated away, or redirected back to the surge protection device, which responds in kind to each return pulse until the threat energy is reduced to safe levels. A typical circuit employing an EOS transient device is illustrated in Fig. 1.

With reference to Fig. 1, a typical electrical circuit 10 is illustrated. The circuit load 12 in the circuit 10 operates at a normal operating voltage. An EOS transient of substantially more than two to three times the normal operating voltage having a sufficient duration can damage the load 12 and the components contained therein. Typically, EOS threats can exceed the normal operating voltage by tens, hundreds or even thousands of times the voltages seen in normal operation.

In the circuit 10, an EOS transient voltage 14 is shown entering the circuit 10 along line 16. Upon the occurrence of the EOS transient voltage 14, an EOS protection device 18 switches from the high resistance state to a low resistance state thus clamping the EOS transient voltage 14 at a safe, low value. The EOS protection device 18 shunts a portion of the transient threat from the electronic line 16 to the system ground 20. As stated above, the EOS protection device 18 reflects a large portion of the threat back towards the source of the threat.

EOS protection devices typically employ a voltage variable material ("VVM"). Many VVM's have been of a consistency and make-up that they have required some type of housing or encapsulation. That is, the VVM materials have heretofore been provided in a device, such as a surface mount device, mounted to a printed circuit

board (“PCB”). The VVM devices typically have been mounted discretely from the devices of the circuit that require protection. This presents a variety of problems.

First, VVM devices add to the number of components that are required to be mounted to the PCB. The VVM devices consume valuable board space and add to the potential for defects. The VVM devices typically require that additional pads be secured to the PCB and that additional circuit traces be routed from PCB devices or from a ground plane to the VVM pads. It is always desirable for cost, spacing/flexibility and reliability purposes, to reduce the number of components mounted to a PCB.

Second, adding components to an existing PCB can require a board redesign or other type of incorporation into a currently pending design. If the application is already in production, it is likely that a considerable amount of time has been spent optimizing board space, which may or may not leave room to integrate a VVM device.

Third, many EOS transients occur outside of the PCB and are transmitted to the PCB through cables and wires. For instance, networked computer and telephone systems are subject to a variety of transients caused by environmental and handling activities. In these situations, it would be desirable to eliminate voltage transients before they reach the PCB.

#### SUMMARY OF THE INVENTION

The present invention provides overvoltage circuit protection. Specifically, the present invention provides a voltage variable material (“VVM”) that includes an insulative binder that is formulated to intrinsically adhere to conductive and non-conductive surfaces. The binder and thus the VVM is self-curable and may be applied to an application in the form of an ink, which dries in a final form for use. The binder eliminates the need to place the VVM in a separate device and for separate printed circuit board pads on which to electrically connect the VVM. The binder and thus the VVM can be directly applied to many different types of substrates, such as a rigid (FR-4) laminate, a polyimide, a polymer, glass and ceramic. The VVM can also be directly applied to different types of substrates that are placed inside a piece of electrical equipment (e.g., a connector).

The binder of the VVM includes a polymer, such as polyester, which is dissolved in a solvent. One suitable solvent for dissolving the polymer is diethylene glycol monoethyl ether acetate, commonly referred to as "carbitol acetate". In an embodiment, a thickening agent, such as a fumed silica, is added to the insulative binder, which increases the viscosity of the insulative binder. A number of different types of particles are then mixed in the binder to produce a desired clamping voltage and response time. The different types of particles include: conductive particles, insulating particles, semiconductive particles, doped semiconductive particles (including core and shell doped semiconductor particles) and any combination thereof.

The conductive particles in an embodiment include an inner core and an outer shell. The core and the shell have different conductivities or resistivities. Either the shell is more conductive than the core or the core is more conductive than the shell. The core and shell can each individually consist of any of the different types of particles listed above. In one preferred embodiment, the conductive particles include an aluminum core and an aluminum oxide shell. In an alternative embodiment, the conductive particles do not include a shell or coating. Here, conductive particles can consist substantially of a single material.

In one preferred embodiment, the VVM includes conductive particles and doped semiconductive particles. The conductive particles can be substantially pure nickel particles, while the doped semiconductive particles include doped silicon.

The VVM having the binder of the present invention can be applied to a substrate to form various circuits or applications. In a first application, a plurality of electrodes or conductors secure to a printed circuit board via any known technique. The electrodes are each separated on the printed circuit board by a gap. The VVM is applied to and intrinsically adheres to the electrodes and the substrate in the gap. In a second application, the electrodes are again secured to the substrate, but the VVM only intrinsically adheres to the electrodes. That is, the VVM does not adhere to the substrate but is placed across the gap.

In a third application, the VVM intrinsically adheres to a substrate, wherein the electrodes are placed on and intrinsically adhere to the VVM. That is, the VVM secures the electrodes to the substrate. In a forth application, at least one of a plurality of electrodes is secured to the substrate, wherein the VVM intrinsically adheres to the

secured electrode. At least one other electrode resides on top of the VVM. The gap between the electrodes is formed by the thickness of the VVM. Here, the VVM may or may not additionally, intrinsically secure to the substrate. The electrode that resides on top of the VVM can also have a portion that secures to the substrate.

When the VVM is applied to a circuit, such as on a printed circuit board, the quantity of VVM self-cures in a finished form that does not require a separate protective covering. The VVM may be left open to the environment through manufacture, shipping and use. The substrate can be any type of substrate, such as a rigid laminate (e.g., FR-4) used with printed circuit boards, a material such as a polyimide used with flexible circuits (e.g., Kapton®), a polymer, ceramic or glass as well as any combination of these.

In another embodiment, the substrate can be coated or otherwise protected. For example, any of the applications described above can be covered with a coating. The coating can be any one of a variety of different materials including: a dry film photo-imagable overlay, a spray liquid photo-imagable overlay or a “glob-top” type coating as it is known in the art. Alternatively, any of the applications described above can be embedded in a multilayered printed circuit board (“PCB”). In another embodiment, at least one additional electrode or conductor secures to an underside of an upper substrate, wherein the VVM exists between the upper and lower substrates and intrinsically adheres to at least the upper and lower electrodes and possibly to one or more of the upper and lower substrates.

The circuit may or may not be provided in a device. For example, the device in an embodiment is a telecommunications device, such as an RJ-45 or RJ-11 connector. In another embodiment, the device is an input/output connector, such as a Deutsches Institut für Normung eV (“DIN”) connector or ribbon cable connector. In each of these devices, the VVM protects one or more signal lines from transient voltage spikes by connecting the signal conductors to a ground conductor or shield.

In one embodiment, an RJ type connector includes a plurality of signal conductors. The connector also includes a grounded conductive shield. The shield is cut or stamped to yield at least one tab that is biased downwards towards the conductors. In one embodiment, the shield defines a separate tab for each of the conductors. The connector includes a housing that compresses the tabs onto the

conductors. VVM is applied between the shield tabs and the conductors to provide overvoltage protection to the RJ connector. In an embodiment, the VVM is the intrinsically securing VVM described above, however, a known VVM provided in a device could also be used. In another embodiment, a capacitor is placed between the VVM and one of the conductors and the shield tab to block high DC voltages, such as those imposed during high potential [HI-POT] testing.

It is therefore an advantage of the present invention to provide an intrinsically adhesive VVM.

Another advantage of the present invention is to provide a VVM that does not need to be housed in a separate device.

A further advantage of the present invention is to provide a VVM that is self-curing.

Yet another advantage of the present invention is to provide a VVM that adheres directly to a printed circuit board without the need for providing separate electrical pads on the substrate on which to mount the VVM.

Yet a further advantage of the present invention is to provide a VVM that adheres directly to a polymer or plastic.

Still another advantage of the present invention is to directly apply a VVM to a substrate, wherein the substrate is provided in an electrical device, such as a piece of equipment or a connector.

Still a further advantage of the present invention is to provide RJ type connectors having overvoltage protection.

Moreover, an advantage of the present invention is to provide input/output connectors having overvoltage protection.

Further still, an advantage of the present invention is to provide an apparatus for electrically connecting VVM (and alternatively additionally a capacitor) to a plurality of different signal lines in an RJ type connector.

Moreover, an advantage of the present invention is, via the elimination of the need for a housing, to provide a lower cost, readily produced circuit protection material that can result in improved electrical performance due to the reduction of parasitic impedance.

Additional features and advantages of the present invention will be described in, and apparent from, the following Detailed Description of the Preferred Embodiments and the Drawings.

#### BRIEF DESCRIPTION OF THE DRAWINGS

Fig. 1 is a schematic illustration of a typical waveform of an electrical overstress transient.

Fig. 2 is a schematic illustration of certain possible components for the voltage variable material (“VVM”) of the present invention.

Fig. 3A is a sectional schematic illustration of a core and shell doped semiconductive particle used with the VVM of the present invention.

Fig. 3B is a sectional schematic illustration of a core and shell conductive particle of the VVM of the present invention.

Figs. 4 is a perspective view of a rigid printed circuit board (“PCB”) substrate that illustrates one circuit arrangement for the intrinsically adhesive VVM of the present invention.

Figs. 5 is a perspective view of a flexible substrate having the intrinsically adhesive VVM of the present invention.

Fig. 6 is a sectioned elevation view illustrating three additional circuit arrangements for the intrinsically adhesive VVM of the present invention.

Fig. 7 is a sectioned elevation view illustrating two “Z” direction type circuit arrangements for the intrinsically adhesive VVM of the present invention.

Fig. 8 is a sectioned elevation view illustrating still a further circuit arrangement for the intrinsically adhesive VVM of the present invention.

Fig. 9 is a sectioned elevation view illustrating the circuit arrangements of Figs. 4 to 7 laminated in a multilayer PCB.

Fig. 10 is a sectioned elevation view illustrating the circuit arrangements of Figs. 4 to 7 covered with a protective coating.

Fig. 11 is a perspective view of one embodiment of a DIN connector having the directly applied VVM of the present invention.

Fig. 12 is a perspective view of one embodiment of a ribbon cable connector having the directly applied VVM of the present invention.

Fig. 13 is a cutaway perspective view of one embodiment of a data/telecommunications RJ type connector having the directly applied VVM of the present invention.

Fig. 14 is a cutaway perspective view of a number of signal conductors and a shield of one embodiment of a data/telecommunications RJ type connector having the directly applied VVM of the present invention.

Fig. 15 is a side elevation view of a signal conductor, a shield and a capacitor of one embodiment of a data/telecommunications RJ type connector having the directly applied VVM of the present invention.

Figs. 16 and 17 are schematic views of various fluidized bed plasma reactors of the present invention suitable for use to coat particles of the voltage variable materials described herein.

#### **DETAILED DESCRIPTION OF THE INVENTION**

Referring now to Fig. 2, a voltage variable material ("VVM") 100 of the present invention includes an insulative binder 50. The binder 50 secures one or more or all of certain different types of particles, such as insulating particles 60, semiconductive particles 70, doped semiconductive particles 80, conductive particles 90 and various combinations of these. The insulative binder 50 has intrinsically adhesive properties and self-adheres to surfaces, such as a conductive, metal surface or a non-conductive, insulative surface. The insulative binder 50 has a property of being self-curing, so that the VVM 100 can be applied to a circuit or application and be used thereafter without heating or otherwise curing the VVM 100 and the insulative binder 50. It should be appreciated, however, that the circuit or application employing the VVM 100 with the binder 50 may be heated or cured to accelerate the curing process.

The insulative binder 50 of the VVM 100 in an embodiment includes a polymer or thermoplastic resin, such as polyester, which is dissolved in a solvent. In one embodiment, the polyester resin has a glass transition temperature in the range of 6° C to 80°C and a molecular weight between 15,000 and 23,000 atomic mass units ("AMU's"). One suitable solvent for dissolving the polymer is diethylene glycol monoethyl ether acetate, commonly referred to as "carbitol acetatate". In an embodiment, a thickening agent is added to the insulative binder 50, which increases

the viscosity of the insulative binder 50. For example, the thickening agent can be a fumed silica, such as that found under the trade name Cab-o-Sil TS-720.

The insulative binder 50 in an embodiment has a high dielectric breakdown strength, a high electrical resistivity and high tracking resistance. The insulative binder 50 provides and maintains sufficient interparticle spacing between the other possible components of VVM 100, such as the conductive particles 90, the insulating particles 60, the semiconductive particles 70 and the doped semiconductive particles 80. The interparticle spacing provides a high resistance. The resistivity and dielectric strength of the insulative binder 50 also affects the high resistance state. In an embodiment, the insulative binder 50 has a volume resistivity of at least  $10^9$  ohm-cm. It is possible to blend different polymers in the binder 50 and to cross-link same.

In an embodiment, insulating particles 60 are dispersed into the binder 50 of the VVM 100. The insulating particles 60 in an embodiment have an average particle size in a range of about 200 to about 1000 Angstroms ("Å") and a bulk conductivity of less than  $10^{-6}$  (ohm-cm)<sup>-1</sup>. In one embodiment, the insulating particles 60 have an average particle size in a range of about 50 Å to about 200 Å.

The fumed silica of the binder 50, such as that available under the trade name Cab-o-Sil TS-720, constitutes an insulating particles 60. Other insulative particles, however, can be used in addition to the fumed silica. For example, glass spheres, calcium carbonate, calcium sulphate, barium sulphate, aluminum trihydrate, kaolin and kaolinite, ultra high-density polyethylene ("UHDPE") and metal oxides such as titanium dioxide may also be used as insulating particles 60 in the present invention. For example, titanium dioxide having an average particle size from about 300 to 400 Å, manufactured by Nanophase Technologies, provides a suitable insulating particle 60.

The insulating particles 60 can also include oxides of iron, aluminum, zinc, titanium, copper and clay such as a montmorillonite type produced by Nanocor, Inc. Insulating particles 60 in addition to the fumed silica, if employed in the VVM 100, are present in an embodiment from about one to about fifteen percent by weight of the VVM 100.

In an embodiment, semiconductive particles 70 are dispersed into the binder 50 of the VVM 100. The semiconductive particles 70 in an embodiment include an average particle size of less than 5 microns and bulk conductivities in the range of 10

to  $10^{-6}$  (ohm-cm) $^{-1}$ . In order to maximize particle packing density and obtain optimum clamping voltages and switching characteristics, the average particle size of the semiconductive particles 70 in one preferred embodiment is in a range of about 3 to about 5 microns, or even less than 1 micron. Semiconductive particle sizes down to the 100-nanometer range and less are also suitable for use in the present invention.

The material of the semiconductive particles 70 in an embodiment includes silicon carbide. The semiconductive particle materials can also include: oxides of bismuth, copper, zinc, calcium, vanadium, iron, magnesium, calcium and titanium; carbides of silicon, aluminum, chromium, titanium, molybdenum, beryllium, boron, tungsten and vanadium; sulfides of cadmium, zinc, lead, molybdenum, and silver; nitrides such as boron nitride, silicon nitride and aluminum nitride; barium titanate and iron titanate; suicides of molybdenum and chromium; and borides of chromium, molybdenum, niobium and tungsten.

In an embodiment, the semiconductive particles 70 include silicon carbide for example, manufactured by Agsco, which can be of #1200 grit and have an average particle size of approximately 3 microns. The silicon carbide can alternatively be manufactured by Norton, be of #10,000 grit, and have an average particle size of approximately 0.3 microns. In another embodiment, the semiconductive particles 70 include silicon carbide and/or at least one other material including: barium titanate, boron nitride, boron phosphide, cadmium phosphide, cadmium sulfide, gallium nitride, gallium phosphide, germanium, indium phosphide, magnesium oxide, silicon, zinc oxide, and zinc sulfide.

In an embodiment, doped semiconductive particles 80 are dispersed into the binder 50 of the VVM 100. The addition of certain impurities (dopants) affects the electrical conductivity of a semiconductor. The impurity or material used to dope the semiconductor material may be either an electron donor or an electron acceptor. In either case, the impurity occupies the energy level within the energy band gap of an otherwise pure semiconductor. By increasing or decreasing the impurity concentration in a doped semiconductor, the electrical conductivity of the material is varied. The electrical conductivity of a pure semiconductor may be extended upward (into the range of a semimetal or metal) by increasing the conduction electron concentration, or

may be extended downward (into the range of an insulator) by decreasing the conduction electron concentration.

In one embodiment, the semiconductive particles 70 and doped semiconductive particles 80 are mixed into the insulative binder 50 of the VVM 100 via standard mixing techniques. In another embodiment, various different doped semiconductive particles 80 that have been doped to different electrical conductivities are dispersed into the insulative binder 50 of the VVM 100. Either of these embodiments can also include insulating particles 60.

In one embodiment, the VVM 100 employs a semiconductive particle doped with a material to render it electrically conductive. The doped semiconductive particles 80 may be comprised of any conventional semiconductor material including: boron nitride, boron phosphide, cadmium phosphide, cadmium sulfide, gallium nitride, gallium phosphide, germanium, indium phosphide, silicon, silicon carbide, zinc oxide, zinc sulfide as well as electrically conducting polymers, such as polypyrole or polyaniline. These materials are doped with suitable electron donors for example, phosphorous, arsenic, or antimony or electron acceptors, such as iron, aluminum, boron, or gallium, to achieve a desired level of electrical conductivity.

In an embodiment, the doped semiconductive particles 80 include a silicon powder doped with aluminum (approximately 0.5% by weight of the doped semiconductive particle 80) to render it electrically conductive. Such a material is marketed by Atlantic Equipment Engineers under the trade name Si-100-F. In another embodiment, the doped semiconductive particles include an antimony doped tin oxide marketed under the trade name Zelec 3010-XC.

In an embodiment, the doped semiconductive particles 80 of the VVM 100 have an average particle size less than 10 microns. In order to maximize particle-packing density and obtain optimum clamping voltages and switching characteristics, however, the average particle size of the semiconductive particles may be in a range of about 1 to about 5 microns, or even less than 1 micron.

#### One Preferred VVM Component

One preferred doped semiconductive particle 80 is illustrated in Fig. 3A. Semiconductive particle 80 includes an inner core 82 that is doped with at least one dopant 84. The inner core is then surrounded by an outer shell or coating 86.

In one embodiment, the core material 82 includes particle or powdered silicon. The silicon 82 is doped to a low resistivity value (e.g., below 1 ohm-cm) and thereafter ground to a powder. The average size of the particles 82 is any suitable size and in one embodiment, the core particles are each between five and 100 microns. In one embodiment, the average thickness of the shell or coating is about 100 to about 10,000 Angstroms ("A").

The core material 82 or silicon is doped with a suitable dopant, such as antimony, arsenic, phosphorus, boron or any of the other dopants listed herein. Core material 82 can be any suitable semiconductive material, such as silicon carbide, germanium, gallium arsenide and the like. In one embodiment, only a single type of dopant is used. It should be appreciated, however, that different types of dopants could be used in the same particle.

The shell or coating 86 of doped semiconductive particle 80 can be made of a multitude of different materials. For example, the coatings can be any one of the following materials: silicon dioxide, epitaxial silicon or glass. Each of those materials is inert, so that they do not react with other components of the VVM of the present invention.

The type of coating or shell 86 dictates the process used for forming the coating or shell. For example, if the coating or shell 86 is an oxide, e.g., silicon dioxide, the layer is grown via heating at one or more temperatures over a specified or variable time in one embodiment. It has been found that suitable silicon oxide layers can be formed by subjecting the core doped silicon particles 82 to heat and temperature. In particular, the particles can be heated at a temperature of about 500°C to about 1500°C over an oxidation time from about 15 minutes to about three hours. The heating is performed over multiple intervals of heating and cooling. In one embodiment, the cooling is performed while subjecting the particles to a vacuum of about ten to 100 millitorr. Vacuum cooling is advantageous because it tends to prevent exposure of the VVM to moisture. The particles in one embodiment are heated for about thirty minutes and then vacuum cooled overnight. That process is then repeated.

Referring now to Figs. 16 and 17, another method and apparatus contemplated by the present invention for forming the coating 86 on the core particle 82 is illustrated by a fluidized bed plasma reactor 250 (Fig. 16) and a reactor 300 (Fig. 17). Fluidized

bed reactor 250 is shown schematically for ease of illustration. Reactor 250 includes a housing 252 and base 254. Housing 252 and base 254 are made of an electrically insulative or dielectric material, such as glass or plastic, in one embodiment.

Housing 252 attaches to or defines an inlet pressure port 256 and an outlet vacuum port 258 as illustrated. Inlet pressure port 256 extends to a pressure chamber 260. Pressure chamber 260 defines or includes a pressure plenum 262. Pressure plenum 262 enables a reactant gas from port 256 to enter and stabilize under pressure within plenum 262. Reactant gas entering the inside of housing 252 through plenum 262 is removed under negative pressure from port 258 defined by or attached to housing 252.

Chamber 260 also defines or includes a bed 264 for holding core particles 82, such as doped core particles. The bottom wall 266 of bed 264 is also the top wall of plenum 262. Wall 266 defines perforated or sintered openings 268 that enable the pressurized reactant gas to escape through wall 266 in a relatively uniform, steady and consistent manner. If the pressure within plenum 262 is sufficient, the gas flow through particles 82 will cause the particles to become entrained in the gas. The particles are thereafter held in a liquid-like state, wherein the top of the suspension of particles 82 is relatively flat due to gravity, as would be the case if liquid were poured into bed 264. Energized conductor 274 in combination with grounded conductor 260 creates plasma sheeting regions 276 and 278, as well as a glow discharge region 280 located between plasma sheeting regions 276 and 278. Particles 82 suspended in the gas stream are thereby ensured to be mixed properly with the plasma glow discharge 280.

The reactant gas entering port 256 is carried via a carrier gas, such as nitrogen, argon, helium, carbon dioxide, oxygen, other gases and combinations thereof. The reactant gas can be any suitable plasma gas known to those of skill in the art, such as triethylaluminum (TEAL), carbon tetrachloride, Silane, Diborane and any combination thereof.

The reactor 250 is also coupled to a high frequency power supply 270 that operates through a matching network 272 to supply power to a pair of electrodes 274 and 260. Matching network 272 matches the impedances of the power supply and the reactor chamber to provide for an optimal transfer of energy to the chamber. It should

be noted that pressure chamber 260, and in particular plate 266, function additionally as a second electrode in combination with electrode 274. Pressurized chamber 260 is therefore made of a conductive material.

Power supply 270 is a high frequency power supply and is an inductively coupled radio frequency ("RF") power supply in one embodiment. The high frequency energy from supply 270 excites the reactant gas molecules entering housing 252 through plenum wall 266, causing the molecules to become ionized. The fluidized bed continuously mixes the particles as described above with the ionized gas so that the reaction of the core particles is uniform.

In one embodiment, reactor 250 is used to provide the oxide layer on the doped core silicon 82 particles described above. The time that the doped core particles spend in the chamber, the amount and frequency of power supplied to the electrodes 274 and 260 and the gases selected all control the oxide growth rate and amount. It should be appreciated, however, that reactor 250 can be used to create other coatings or shells for particle 80 other than oxide shells. For example, the system could be used to apply different types of coatings with plasma-enhanced chemical vapor deposition ("PECVD").

It should be appreciated that while reactor 250 is used in one preferred embodiment to apply an oxide layer or other coating to doped semiconductive core 82, the apparatus and method can be used to apply coatings to other types of core materials, such as semiconductive core materials without dopants, insulative materials and conductive materials. Indeed, reactor 50 can be used to produce the core shell conductive particle 90 described below in connection with Fig. 3B.

Fig. 17 illustrates an alternative reactor 300. Alternative reactor 300 includes many of the same components herein. The same functionality as described above for reactor 250. Those components are marked with the same element numbers. Reactor 300 includes an inductive coil 302 that is wrapped about housing 252. Energy from power supply 270 is inductively coupled to the reactor through coil 302. The dark or sheeting regions 276 and 278 occur along the sides of alternative reactor 300, and the glow discharge region 280 is located between plasma sheeting regions 276 and 278. Again, the gas stream entraining particles 82 ensures the proper mixing of the particles with the plasma glow discharge 280.

Each of the insulating particles 60, semiconductive particles 70 and doped semiconductive particles 80 are optionally dispersed into the binder 50 of the VVM 100. The fumed silica, or Cab-o-Sil, of the binder 50 constitutes an insulating particle 60. In a preferred embodiment, the VVM 100 includes conductive particles 90. The conductive particles 90 in an embodiment have bulk conductivities of greater than 10 (ohm-cm)<sup>-1</sup> and especially greater than 100 (ohm-cm)<sup>-1</sup>. It is possible, however, that by using doped semiconductive particles the VVM 100 does not include conductive particles 90.

The conductive particles 90 in an embodiment have a maximum average particle size less than 60 microns. In an embodiment, ninety-five percent of the conductive particles 90 have diameters no larger than 20 microns. In another embodiment, one hundred percent the conductive particles 90 are less than 10 microns in diameter. In a further embodiment, conductive particles 90 with average particle sizes in the submicron range, for example one micron down to nanometers, are used.

Suitable materials for the conductive particles 90 of the VVM 100 include: aluminum, brass, carbon black, copper, graphite, gold, iron, nickel, silver, stainless steel, tin, zinc and alloys thereof as well as other metal alloys. In addition, intrinsically conducting polymer powders, such as polypyrrole or polyaniline may also be employed, as long as they exhibit stable electrical properties.

In an embodiment, the conductive particles 90 include nickel manufactured by Atlantic Equipment Engineering and marketed under the trade name Ni-120, which have an average particle size in the range of 10-30 microns. In another embodiment, the conductive particles 90 include aluminum and have an average particle size in the range of 1 to 30 microns.

The conductive particles 90 in one embodiment are not coated and consist essentially of a single material. Referring to Fig. 3B, in another embodiment, the conductive particles include an inner core 92 surrounded by an outer shell 94. The core 92 and the shell 94 of the particles 90 have different electrical conductivities. In an embodiment, the core and the shell particles 90 are substantially spherical in shape and range from about 25 to about 50 microns.

In one embodiment, the inner core 92 of the conductive particles 90 includes an electrically insulating material, wherein the outer shell 94 includes one of the

following materials: (i) a conductor; (ii) a doped semiconductor; or (iii) a semiconductor. In another embodiment, the inner core 92 of the conductive particles 90 includes a semiconductive material, wherein the outer shell 94 includes one of the following materials: (i) a conductor; (ii) a doped semiconductor; or (iii) a semiconductive material other than the semiconductive material of the inner core. In a further embodiment, the inner core 92 includes a conductive material, wherein the outer shell 94 may be comprised of one of the following materials: (i) an insulating material; (ii) a semiconductor; (iii) a doped semiconductor; or (iv) a conductive material other than the conductive material of the inner core.

Conductive materials suitable for use in the conductive core-shell particles 90 include the following metals and alloys thereof: aluminum, copper, gold, nickel, palladium, platinum, silver, titanium and zinc. Carbon black may also be used as a conductive material in the VVM 100. The insulating materials 60, semiconductive particles 70 and doped semiconductor particles 80 described above may be mixed with the conductive core-shell particles 90 in the binder 50 of the VVM 100 of present invention.

In one preferred embodiment, the core-shell particles 90 include an aluminum core 92 and an aluminum oxide shell 94. The particles 90 having the aluminum core 92 and the aluminum oxide shell 94 can then be provided in the intrinsically adhesive binder having formed silica without additional insulating particles 60, semiconductive particles 70 or doped semiconductive particles 80.

In another embodiment, the core-shell particles 90 include a titanium dioxide (insulator) core 92 and an antimony doped tin oxide (doped semiconductor) shell 94. These latter particles are marketed under the trade name Zelec 1410-T. Another suitable core-shell particle 90 is marketed under the trade name Zelec 1610-S and includes a hollow silica (insulator) core 92 and an antimony doped tin oxide (doped semiconductor) shell 94.

Particles having a fly ash (insulator) core 92 and a nickel (conductor) shell 94, and particles having a nickel (conductor) core 92 and silver (conductor) shell 94 are marketed by Novamet are also suitable for use in the present invention. Another suitable alternative is marketed under the trade name Vistamer Ti-9115 by Composite Particles, Inc. of Allentown, PA. These conductive core-shell particles have an

insulative shell 92 of ultra high-density polyethylene (UHDPE) and a conductive core 94 material of titanium carbide (TiC). Also, particles 90 having a carbon black (conductor) core 92 and a polyaniline (doped semiconductor) shell 94 marketed by Martek Corporation under the trade name Eeonyx F-40-10DG may be used in the VVM 100 of the present invention.

In one embodiment of the VVM 100, the intrinsically adhesive insulative binder 50 constitutes from about 20 to about 60%, and more specifically from about 25 to about 50%, by weight of the total composition. The conductive particles 90 in an embodiment constitute from about 5 to about 80%, and more specifically from about 50 to about 70%, by weight of the total composition. These ranges apply whether or not VVM 100 includes additional insulative particles 60, semiconductive particles 70 and/or doped semiconductive particles 80. The semiconductive particles 70, if present, constitute from about 2 to about 60%, and more specifically from about 2 to about 10%, by weight of the total composition.