(12) INTERNATIONAL APPLICATION PUBLISHED UNDER THE PATENT COOPERATION TREATY (PCT)

(19) World Intellectual Property Organization

International Bureau

(43) International Publication Date

21 December 2000 (21.12.2000)

PCT

(10) International Publication Number

WO 00/78103 A1

(51) International Patent Classification<sup>7</sup>: H05K 1/02, H01L 21/56

(74) Agents: MALLIE, Michael, J. et al.; Blakely, Sokoloff, Taylor & Zafman LLP, 7th floor, 12400 Wilshire Boulevard, Los Angeles, CA 90025 (US).

(21) International Application Number: PCT/US00/40107

(22) International Filing Date: 5 June 2000 (05.06.2000)

(25) Filing Language: English

(26) Publication Language: English

(30) Priority Data:

09/330,373 11 June 1999 (11.06.1999) US

(71) Applicant (for all designated States except US): INTEL CORPORATION [US/US]; 2200 Mission College Boulevard, Santa Clara, CA 95052 (US).

(81) Designated States (national): AE, AG, AL, AM, AT, AU, AZ, BA, BB, BG, BR, BY, CA, CH, CN, CR, CU, CZ, DE, DK, DM, DZ, EE, ES, FI, GB, GD, GE, GH, GM, HR, HU, ID, IL, IN, IS, JP, KE, KG, KP, KR, KZ, LC, LK, LR, LS, LT, LU, LV, MA, MD, MG, MK, MN, MW, MX, MZ, NO, NZ, PL, PT, RO, RU, SD, SE, SG, SI, SK, SL, TJ, TM, TR, TT, TZ, UA, UG, US, UZ, VN, YU, ZA, ZW.

(84) Designated States (regional): ARIPO patent (GH, GM, KE, LS, MW, MZ, SD, SL, SZ, TZ, UG, ZW), Eurasian patent (AM, AZ, BY, KG, KZ, MD, RU, TJ, TM), European patent (AT, BE, CH, CY, DE, DK, ES, FI, FR, GB, GR, IE, IT, LU, MC, NL, PT, SE), OAPI patent (BF, BJ, CF, CG, CI, CM, GA, GN, GW, ML, MR, NE, SN, TD, TG).

(72) Inventors; and

(75) Inventors/Applicants (for US only): RAMALINGAM, Suresh [IN/US]; 34276 Dunhill Drive, Fremont, CA 94555 (US). VODRAHALLI, Nagesh [US/US]; 1607 S. 13th Avenue, Phoenix, AZ 85045 (US). COSTELLO, Michael, J. [US/US]; 16013 S. Desert Foothills Parkway #2050, Phoenix, AZ 85048 (US). LOKE, Mun, Leong [MY/US]; 601 N. Rita Lane #236, Chandler, AZ 85226 (US). MAHAJAN, Ravi, V. [IN/US]; 1957 E. Divot Drive, Tempe, AZ 85283 (US).

Published:

- With international search report.

- Before the expiration of the time limit for amending the claims and to be republished in the event of receipt of amendments.

For two-letter codes and other abbreviations, refer to the "Guidance Notes on Codes and Abbreviations" appearing at the beginning of each regular issue of the PCT Gazette.

(54) Title: INTEGRATED CIRCUIT PACKAGE HAVING A SUBSTRATE VENT HOLE

WO 00/78103 A1

(57) Abstract: The present invention involves a method of providing an integrated circuit package (10) having a substrate with a vent opening (15). The integrated circuit package includes a substrate (12) having an opening and an integrated circuit mounted (18) to the substrate. An underfill material is dispensed between the substrate and the integrated circuit.

## INTEGRATED CIRCUIT PACKAGE

### HAVING A SUBSTRATE VENT HOLE

#### BACKGROUND

##### **1. Field of the Invention**

This invention relates in general to an integrated circuit package, and more particularly, to an integrated circuit package having a substrate vent hole.

##### **2. Description of Related Art**

Integrated circuits are typically assembled into a package that is soldered to a printed circuit board. Figure 1 illustrates a type of integrated circuit package that is commonly referred to as flip chip or C4 package. The integrated circuit 1 contains a number of solder bumps 2 that are soldered to a top surface of a substrate 3.

The package may include an underfill material 4 that is located between the integrated circuit 1 and the substrate 3. The underfill material 4 is typically an epoxy which strengthens the solder joint reliability and the thermo-mechanical moisture stability of the IC package.

The package may have hundreds of solder bumps 2 arranged in a two-dimensional array across the bottom of the integrated circuit 1. The epoxy 4 is typically applied to the solder bump interface by dispensing a single line of uncured epoxy material along one side of the integrated circuit. The epoxy then flows between the solder bumps. The epoxy then flows between the solder bumps. The epoxy must be dispensed in a manner that covers all of the solder bumps 2.

It is desirable to dispense the epoxy 4 at only one side of the integrated circuit to insure that air voids are not formed in the underfill. Air voids weaken the structural integrity of the integrated circuit/substrate interface. Such air voids are typically formed from trapped air or from gasses released during the underfill cure process. Moisture released during the underfill process may also be absorbed by the substrate, resulting in delamination and other reliability-related failures during the surface mount process. Moreover, the bumps may extrude into the voids during thermal loading, particularly for packages with a relatively high bump density.

Accordingly, there is a need in the technology for an apparatus and method for providing an integrated circuit package that avoids the aforementioned problems.

### **SUMMARY**

The present invention involves a method of providing an integrated circuit package having a substrate with a vent opening. The integrated circuit package includes a substrate having an opening and an integrated circuit mounted to the substrate. An underfill material is dispensed between the substrate and the integrated circuit.

### **BRIEF DESCRIPTION OF THE DRAWINGS**

The features and advantages of the present invention will become apparent from the following detailed description of the present invention in which:

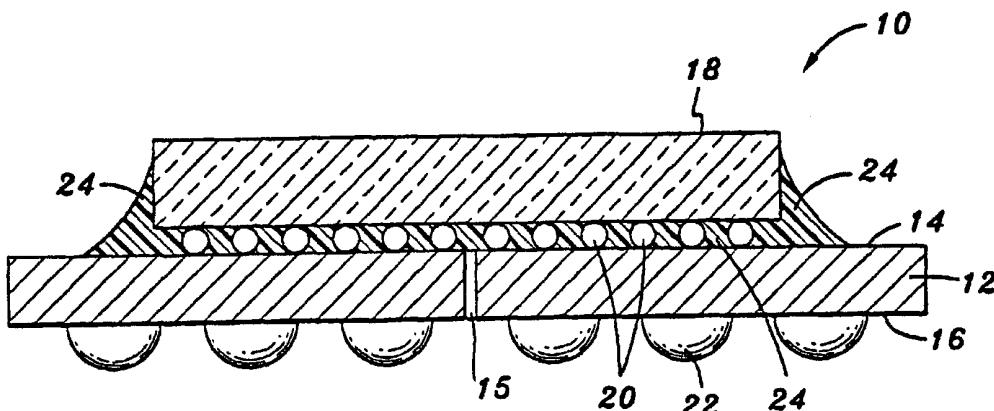

Figure 1 is a side view of an integrated circuit package of the prior art.

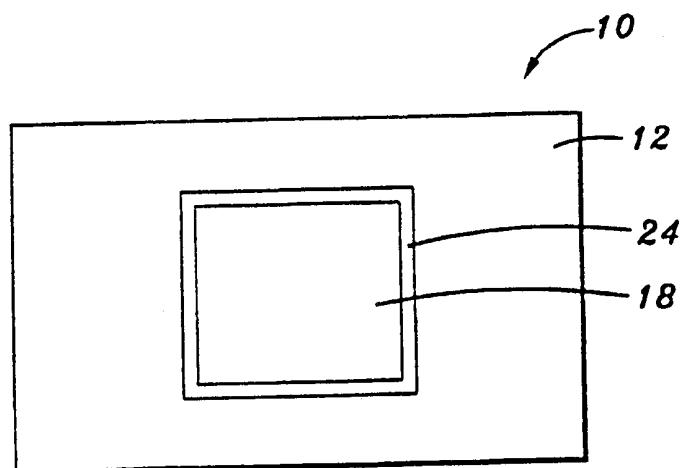

Figure 2A is a top view of an embodiment of an integrated circuit package of the present invention.

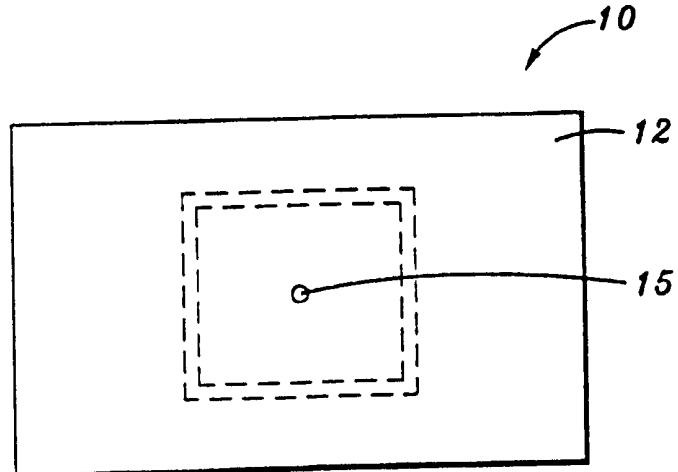

Figure 2B is a bottom view of the integrated circuit package as shown in Figure 2A.

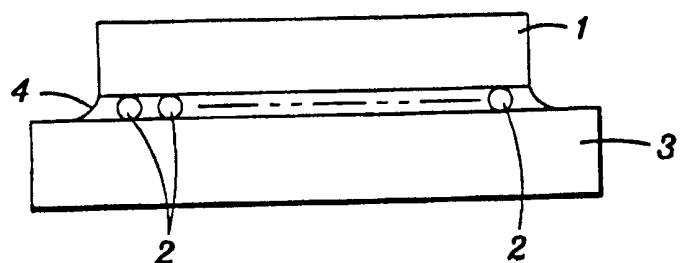

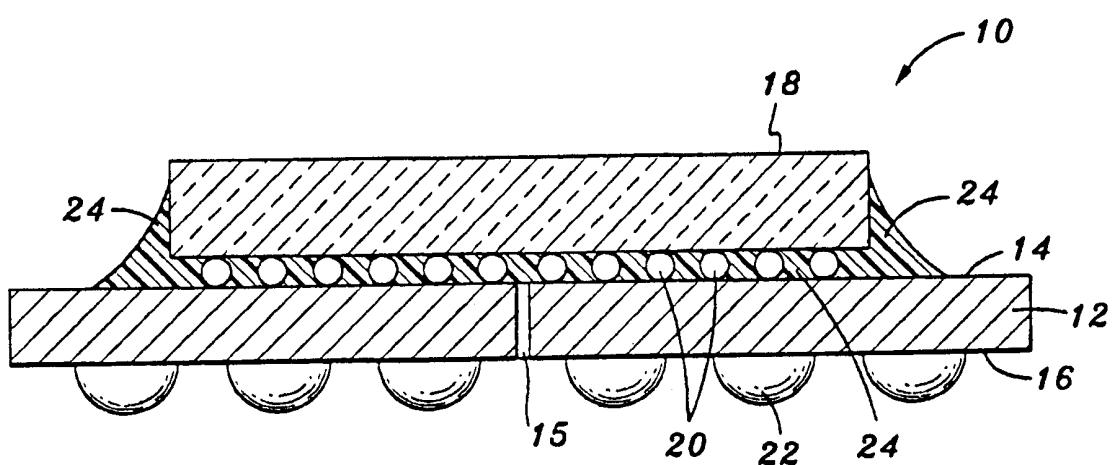

Figure 3 is an enlarged side view of one embodiment of the integrated circuit package of Figures 2A and 2B.

Figures 4A-D are schematics showing a process for assembling the integrated circuit package of Figures 2A and 2B.

### DESCRIPTION

In the following description, for purposes of explanation, numerous details are set forth in order to provide a thorough understanding of the present invention. However, it will be apparent to one skilled in the art that these specific details are not required in order to practice the present invention. In other instances, well-known electrical structures and circuits are shown in block diagram form in order not to obscure the present invention unnecessarily.

Figures 2A and 2B are respectively, a top and bottom view of an integrated circuit package of the present invention. Figure 3 is an enlarged side view of one embodiment of the integrated circuit package of Figures 2A and 2B. With reference to Figures 2A-2B and 3, the package 10 may include a substrate 12 which has a first surface 14 and a second opposite surface 16. An integrated circuit 18 may be attached to the first surface 14 of the substrate 12 by a plurality of solder bumps 20. The solder bumps 20 may be arranged in a two-dimensional array across the integrated circuit 18 and to the substrate 12 with a process commonly referred to as controlled collapse chip connection (C4).

The solder bumps 20 may carry electrical current between the integrated circuit 18 and the substrate 12. In one embodiment the substrate 12 may include an organic dielectric material. The package 10 may include a plurality of solder balls 22 that are attached to the second surface 16 of the substrate 12. The solder

balls 22 can be reflowed to attach the package 10 to a printed circuit board (not shown).

The substrate 12 may contain routing traces, power/ground planes, vias, etc., which electrically connect the solder bumps 20 on the first surface 14 to the solder balls 22 on the second surface 16. The substrate 12 also includes a substrate vent opening 15 that is provided through the substrate at a predetermined location. In one embodiment, the substrate vent opening 15 is located at a low stress area of the substrate. In another embodiment, the substrate vent opening 15 is located at the center of the substrate 12. In a further embodiment, the substrate vent opening 15 is sized to provide efficient out-gassing of moisture, while preserving the stability and integrity of the substrate 12. In one embodiment, the substrate opening is selected from a range from 20-62 mm in diameter, although in alternate embodiments, the size of the substrate vent opening 15 may be determined according to need and other design specifications.

The package 10 may include an underfill material 24 that is located between the integrated circuit 18 and the substrate 12. The underfill material 24 may form a circumferential fillet that surrounds and seals the edges of the IC 18. The uniform sealing function of the underfill material 24 may inhibit moisture migration, and cracking of the IC 18. The seal process may also reduce delamination. The underfill material 24 also reduces stresses on the solder bumps 20. In one embodiment, the underfill material 24 is an epoxy. The integrated circuit 18 may be encapsulated by an encapsulant (not shown). The encapsulant may be an injection molded material. Additionally, the package 10 may incorporate a thermal element (not shown) such as a heat slug or a heat sink to remove heat generated by the integrated circuit 18.

Figures 4A-D illustrates a process for assembling the package 10. In one embodiment, the process is a single pass four-sided dispensing process. In

particular, the use of a vent hole 15 in implementing the IC package 10 facilitates the use of a single pass four-sided dispensing process.

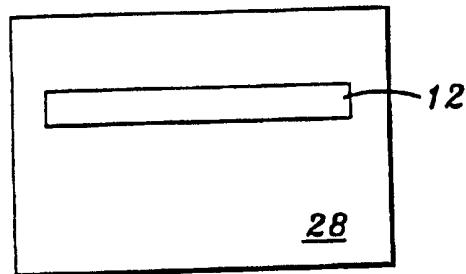

A substrate vent opening 15 is first drilled or lazed into the substrate 12 at a predetermined location during the substrate manufacturing process. The substrate 12 may then be baked in an oven 28 to remove moisture from the substrate material, as shown in Figure 4A. The substrate 12 is preferably baked at a temperature greater than the process temperatures of the underfill process steps to insure that moisture is not released from the substrate 12 in the subsequent steps. By way of example, the substrate 12 may be baked at 163 degrees Centigrade (C).

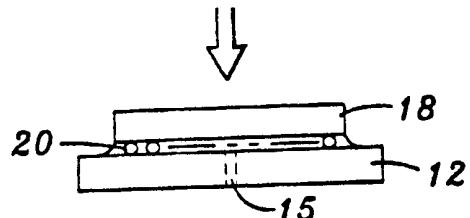

The integrated circuit 18 may then be mounted onto the substrate 12, as shown in Figure 4B. The integrated circuit 18 is typically mounted by reflowing the solder bumps 20.

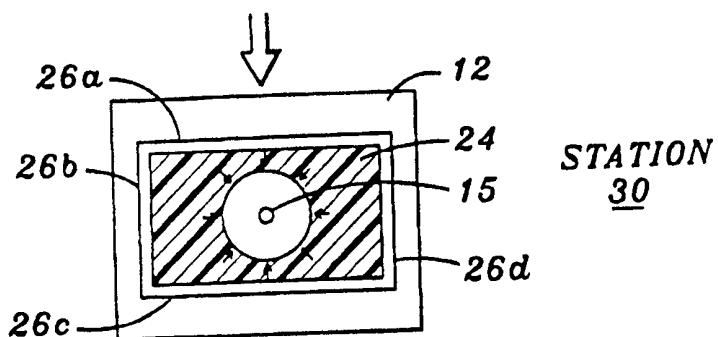

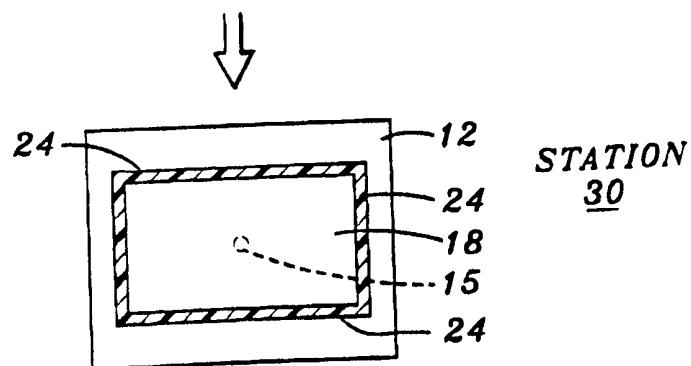

The underfill material 24 may be dispensed onto the substrate 12 along all four sides 26a-d of the IC 18 at a dispensing station 30, as shown in Figures 4C and 4D. Figure 4C illustrates the flow of a typical underfill material 24 when the underfill material 24 is dispensed along all four sides 26a-d of the IC 18. Figure 4D illustrates a top view of the underfilled IC package 10 having a substrate vent hole 15.

The underfill material 24 may be dispersed in a manner which creates a fillet that encloses and seals the IC 18. One advantage of using the four-sided dispense pattern is that it is able to form a uniform fillet at all four sides of the IC 18. A non-uniform fillet can result to cracking of the IC 18. In addition, the use of a four sided dispense process typically results in a fillet that provides a tight seal, so that delamination between the IC 18 and the underfill material 24 and/or between the underfill material 24 and the substrate 12 does not occur. This in turn results in strong adhesion between the IC 18 and the underfill material 24 and/or between the underfill material 24 and the substrate 12. The process

control for forming this uniform fillet is simple and the process yield is high. By way of example, the underfill material 24 may be dispensed at a temperature of approximately 80°-120°C.

The use of a single pass dispense pattern reduces the underfill material interaction effects of multiple passes. During multiple passes, the underfill material is subjected to heating and gelling before subsequent passes. The use of a single pass dispense process results in a more robust process, reduced processing time and eliminates the need for tight material gelling control.

The underfill material 24 may be cured into a hardened state. The underfill material 24 may be cured at a temperature of approximately 150° C. After the underfill material 24 is cured, solder balls 22 can then be attached to the substrate 12, typically with a reflow process, to complete the package 10.

The implementation of the present invention reduces void formation by allowing out-gassing of trapped air from the center of the substrate 12 when the underfill material 24 is dispensed at four sides of the IC 18. In addition, the vent hole 15 allows the underfill material 24 to flow under capillary effect before and during the curing process. As a result, the time control of the underfill material 24 is not as critical as compared to existing processes in which multiple passes are required. This provides the opportunity for eliminating infra red (IR) and/or convective heating, which are typically required in processes utilizing multiple passes, so as to enhance the underfill material 24 flow for subsequent dispense passes.

The use of a substrate vent hole 15 also shortens the flow travel distance to half, since a four sided dispense process may be used, as described above. This in turn reduces the time needed for providing a full underfill and thus provides the opportunity for eliminating a flow enhancement heating process, such as the IR and BTU heating processes, after underfill dispensing. The use of a vent hole 15 reduces the characterization work needed for underfill process

development, which in turn reduces the intense handling and timing interaction associated with the equipment and process. As a result, operational costs are reduced, while manufacturing yields are increased.

While this invention has been described with reference to illustrative embodiments, this description is not intended to be construed in a limiting sense. Various modifications of the illustrative embodiments, as well as other embodiments of the invention, which are apparent to persons skilled in the art to which the invention pertains are deemed to lie within the spirit and scope of the invention.

What is claimed is:

1. An integrated circuit package, comprising:

a substrate having an opening;

an integrated circuit mounted to said substrate;

an underfill material mounted to said substrate and said integrated circuit.

2. The package of Claim 1, wherein said opening is located at a predetermined position on said substrate.

3. The package of Claim 2, wherein said predetermined position is a center of said substrate.

4. The package of Claim 2, wherein said predetermined position is a low-stress area of said substrate.

5. The package of Claim 1, wherein said opening has a predetermined size.

6. The package of Claim 5, wherein said opening has a diameter selected from a range of 20 mm – 62 mm.

7. The package of Claim 1, wherein said underfill material is an epoxy.

8. The package of Claim 1, further comprising a solder bump that attaches said integrated circuit to said substrate.

9. A process for assembling an integrated circuit, comprising:

providing an opening through a substrate;

attaching an integrated circuit to said substrate;

filling a space between said integrated circuit and said substrate with an underfill material.

10. The process of Claim 9, wherein the act of providing comprises: drilling said opening through said substrate.

11. The process of Claim 9, wherein the act of providing comprises lazing said opening through said substrate.

12. The process of Claim 9, wherein the act of providing comprises providing said opening of a predetermined size through said substrate.

13. The process of Claim 12, wherein in the act of providing, said predetermined size is substantially circular, with a diameter selected from a range between 20mm to 62mm.

14. The process of Claim 9, wherein the act of providing comprises providing said opening at a predetermined location of said substrate.

15. The process of Claim 13, wherein the act of providing comprises providing said opening at a low-stress location of said substrate.

16. The process of Claim 13, wherein the act of providing comprises providing said opening at a center of said substrate.

17. The process of Claim 9, further comprising attaching a solder ball to said substrate.

18. A process for underfilling an integrated circuit, comprising:

providing a substrate having a vent opening;

mounting the integrated circuit to the substrate; and

dispensing an underfill material that becomes attached to the

integrated circuit and the substrate having the vent opening.

19. The process of Claim 18, further comprising:

curing said underfill material.

20. The process of Claim 19, wherein the act of dispensing further

comprises:

dispensing an underfill material along four sides of the integrated

circuit.

1/3

*FIG. 1*

(PRIOR ART)

*FIG. 2A*

*FIG. 2B*

2/3

FIG. 3

3/3

FIG. 4A

FIG. 4B

FIG. 4C

FIG. 4D

# INTERNATIONAL SEARCH REPORT

Int'l. Jonal Application No

PCT/US 00/40107

**A. CLASSIFICATION OF SUBJECT MATTER**

IPC 7 H05K1/02 H01L21/56

According to International Patent Classification (IPC) or to both national classification and IPC

**B. FIELDS SEARCHED**

Minimum documentation searched (classification system followed by classification symbols)

IPC 7 H05K H01L

Documentation searched other than minimum documentation to the extent that such documents are included in the fields searched

Electronic data base consulted during the international search (name of data base and, where practical, search terms used)

EPO-Internal, WPI Data, PAJ

**C. DOCUMENTS CONSIDERED TO BE RELEVANT**

| Category <sup>°</sup> | Citation of document, with indication, where appropriate, of the relevant passages                   | Relevant to claim No.             |

|-----------------------|------------------------------------------------------------------------------------------------------|-----------------------------------|

| X                     | EP 0 805 486 A (LUCENT TECHNOLOGIES INC)<br>5 November 1997 (1997-11-05)<br><br>claims 1-10<br>----- | 1-3, 5,<br>7-10, 12,<br>14, 16-20 |

| X                     | US 5 311 059 A (BANERJI KINGSUK ET AL)<br>10 May 1994 (1994-05-10)<br>the whole document<br>-----    | 1, 9, 18                          |

| A                     | US 5 218 234 A (THOMPSON KENNETH R ET AL)<br>8 June 1993 (1993-06-08)<br>the whole document<br>----- | 1-20                              |

Further documents are listed in the continuation of box C.

Patent family members are listed in annex.

° Special categories of cited documents :

- "A" document defining the general state of the art which is not considered to be of particular relevance

- "E" earlier document but published on or after the international filing date

- "L" document which may throw doubts on priority claim(s) or which is cited to establish the publication date of another citation or other special reason (as specified)

- "O" document referring to an oral disclosure, use, exhibition or other means

- "P" document published prior to the international filing date but later than the priority date claimed

"T" later document published after the international filing date or priority date and not in conflict with the application but cited to understand the principle or theory underlying the invention

"X" document of particular relevance; the claimed invention cannot be considered novel or cannot be considered to involve an inventive step when the document is taken alone

"Y" document of particular relevance; the claimed invention cannot be considered to involve an inventive step when the document is combined with one or more other such documents, such combination being obvious to a person skilled in the art.

"&" document member of the same patent family

Date of the actual completion of the international search

10 October 2000

Date of mailing of the international search report

18/10/2000

Name and mailing address of the ISA

European Patent Office, P.B. 5818 Patentlaan 2

NL - 2280 HV Rijswijk

Tel. (+31-70) 340-2040, Tx. 31 651 epo nl.

Fax: (+31-70) 340-3016

Authorized officer

Van Reeth, K

# INTERNATIONAL SEARCH REPORT

## Information on patent family members

International Application No

PCT/US 00/40107

| Patent document<br>cited in search report | Publication<br>date | Patent family<br>member(s) |    |            | Publication<br>date |

|-------------------------------------------|---------------------|----------------------------|----|------------|---------------------|

| EP 0805486                                | A                   | 05-11-1997                 | CA | 2198305 A  | 02-11-1997          |

|                                           |                     |                            | JP | 10041350 A | 13-02-1998          |

|                                           |                     |                            | US | 6074897 A  | 13-06-2000          |

| US 5311059                                | A                   | 10-05-1994                 | EP | 0623242 A  | 09-11-1994          |

|                                           |                     |                            | JP | 2570499 B  | 08-01-1997          |

|                                           |                     |                            | JP | 7503579 T  | 13-04-1995          |

|                                           |                     |                            | KR | 138966 B   | 30-04-1998          |

|                                           |                     |                            | WO | 9315521 A  | 05-08-1993          |

| US 5218234                                | A                   | 08-06-1993                 | JP | 2746035 B  | 28-04-1998          |

|                                           |                     |                            | JP | 5283478 A  | 29-10-1993          |

|                                           |                     |                            | KR | 9602490 B  | 17-02-1996          |