# (19) United States

## (12) Patent Application Publication (10) Pub. No.: US 2008/0017924 A1 MATSUMOTO et al.

Jan. 24, 2008 (43) Pub. Date:

## (54) SEMICONDUCTOR DEVICE AND METHOD OF MANUFACTURING THE SAME

(75) Inventors: **Takuji MATSUMOTO**, Tokyo (JP); Shigenobu MAEDA, Tokyo (JP); Toshiaki IWAMATSU, Tokyo (JP); Takashi IPPOSHI, Tokyo (JP)

> Correspondence Address: OBLON, SPIVAK, MCCLELLAND MAIER & NEUSTADT, P.C. 1940 DUKE STREET ALEXANDRIA, VA 22314 (US)

(73) Assignee: Renesas Technology Corp., Tokyo (JP)

(21) Appl. No.: 11/830,321

(22) Filed: Jul. 30, 2007

### Related U.S. Application Data

(62) Division of application No. 10/841,469, filed on May 10, 2004, now Pat. No. 7,256,463, which is a division of application No. 09/986,004, filed on Nov. 7, 2001, now Pat. No. 6,794,717.

#### (30)Foreign Application Priority Data

Feb. 13, 2007 (JP) ...... 2001-035180

### **Publication Classification**

(51) Int. Cl.

H01L 27/12 (2006.01)

#### (57)ABSTRACT

A semiconductor device having an SOI structure including a semiconductor substrate, a buried insulating layer and an SOI layer, including first and second semiconductor regions of a predetermined conductivity type provided in an element formation region of said SOI layer, and a partial insulating film provided in an upper layer portion of said element formation region and a partial insulating film lower semiconductor region of a predetermined conductivity type to be a part of said element formation region in a lower layer portion of said element formation region wherein said partial insulating film lower semiconductor region is electrically connected to said first and second semiconductor regions to constitute a resistive element.

F | G . 2

F1G.3

$\bigcirc$ ய

F1G.5

F | G . 9

F I G . 10

F - G . 1

FIG. 12

F | G . 13

F I G . 14

FIG. 15

F I G . 16

F I G . 17

F | G . 18

FIG.19

F I G . 2 0

FIG. 21

F | G . 2 2

F I G . 23

F I G . 2 4

FIG. 25

$\infty$ 0

F I G . 2 9

F I G . 3 1

F1G.32

F I G . 3 3

F I G . 3 4

FIG. 35

FIG.36

F I G . 3 7

FIG. 38

FIG. 39

F I G . 4 0

FIG. 41

F I G . 4 2

ന 4  $\Omega$ Щ

G

F I G . 4 5

4  $\mathcal{O}$ ட

Ш

FIG. 48

FIG. 49

FIG.50

FIG. 51

FIG. 52

FIG. 53

FIG. 54

FIG. 55

FIG. 56

F | G . 5 7

FIG. 58

FIG. 59

# SEMICONDUCTOR DEVICE AND METHOD OF MANUFACTURING THE SAME

# CROSS REFERENCE TO RELATED APPLICATION

[0001] This application is a divisional and claims the benefit of priority under 35 U.S.C. § 120 from U.S. application Ser. No. 10/841,469, filed May 10, 2004 which is a divisional of U.S. application Ser. No. 09/986,004, filed Nov. 7, 2001 and claims the benefit of priority under 35 U.S.C. § 119 of Japanese Patent Application No. 2001-035180, filed on Feb. 13, 2001. The entire contents of these applications are incorporated herein by reference.

## BACKGROUND OF THE INVENTION

[0002] 1. Field of the Invention

[0003] The present invention relates to a semiconductor device having an SOI structure and a method of manufacturing the semiconductor device.

[0004] 2. Description of the Background Art

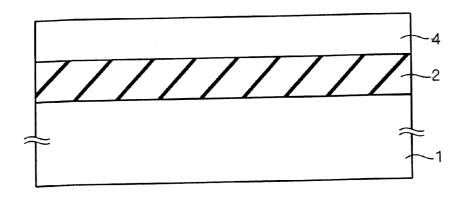

[0005] Attention has recently been paid to a semiconductor device referred to as an SOI (Silicon-On-Insulator) device to be a high-speed device having low power consumption.

[0006] The SOI device is fabricated on an SOI substrate having an SOI structure in which a buried oxide film is interposed between an SOI layer and a silicon substrate. In particular, an SOI device in which an SOI layer to be an upper silicon layer has a small thickness (up to approximately several µm) is referred to as a thin film SOI device to which attention has been paid and has been expected for application to an LSI for mobile equipment. Conventionally, an SOI element (a (semiconductor) element formed on an SOI layer having an SOI structure) penetrates through Si (silicon) of the SOI layer and is completely isolated through an oxide film for isolation formed over the buried oxide film.

[0007] The complete isolation technique is characterized by latch up free (latch-up is not caused), a resistance to noises and the like because the element is electrically isolated completely from other elements. However, since a transistor is operated in an electrical floating state, there is a problem in that a frequency dependency is caused on a delay time and a floating-body effect, for example, a kink effect in which a hump is generated on a drain current-drain voltage characteristic or the like is produced. In order to suppress the floating-body effect, an isolation oxide film (partial oxide film) is formed in an upper layer portion so as not to come in contact with the buried oxide film and constitutes a partial isolation region together with a part of an SOI layer in a lower layer portion and a body terminal is provided in a body region formed in a region isolated in the partial isolation region. Consequently, a partial isolation technique capable of fixing s substrate potential (body potential) through the SOI layer provided under the partial oxide film is effective. However, there is a problem in that the partial isolation technique does not have the latch up free which is the advantage of the complete isolation technique.

[0008] Therefore, there has been developed a partial isolation and complete isolation combination technique having both advantages. In the partial and complete isolation com-

bination technique, trench depths are varied for the partial isolation and complete isolation combination. For this reason, after an oxide film of an isolation oxide film is provided and is then subjected to a CMP processing, dishing is generated in a complete isolation portion having a great trench depth differently from the partial isolation. Accordingly, there is a problem in that the shape of an important isolation edge for the reliability of a gate oxide film is varied between the partial isolation and the complete isolation. In the combination process, moreover, the isolation edge of the complete isolation is lowered so that a threshold voltage of a MOS transistor is locally dropped in an edge portion. Therefore, there is a problem in that a leakage current might be increased.

[0009] In only the conventional device, moreover, a distance from the body terminal is varied for each transistor. Therefore, there is a problem in that a body resistance is varied, resulting in a variation in a threshold voltage.

[0010] In addition, there is a problem in that a body potential cannot always be fixed with a high stability by the partial isolation technique for fixing the body potential through the SOI layer provided under the partial oxide film.

## SUMMARY OF THE INVENTION

[0011] A first aspect of the present invention is directed to a semiconductor device including an SOI structure having a semiconductor substrate, a buried insulating layer and an SOI layer, comprising a MOS transistor provided in an element formation region of the SOI layer, and a partial isolation region provided in the SOI layer and serving to isolate the element formation region, the partial isolation region including a partial insulating film provided in an upper layer portion of the SOI layer and a partial insulating film lower semiconductor region to be a part of the SOI layer present in a lower layer portion of the SOI layer, the MOS transistor including source and drain regions of a first conductivity type selectively formed in the SOI layer, respectively, a gate electrode having a gate electrode main part formed through a gate oxide film on a region of the SOI layer between the source and drain regions, and a body region having a body region main part to be a region of a second conductivity type of the SOI layer between the source and drain regions and a body region potential setting portion electrically connected from the body region main part in the element formation region and capable of externally fixing an electric potential.

[0012] A second aspect of the present invention is directed to the semiconductor device according to the first aspect of the present invention, wherein the body region potential setting section includes a body region source/drain adjacent portion in a gate width direction adjacently to the source and drain regions and extended in a gate length direction from the body region main part, and the gate electrode further has a gate extension region extended in the gate length direction from an end of the gate electrode main part and formed on a part of the body region source/drain adjacent portion, and serving to electrically block the body region source/drain adjacent portion and the source and drain regions through the gate extension region.

[0013] A third aspect of the present invention is directed to the semiconductor device according to the second aspect of the present invention, wherein the body region source/drain adjacent portion includes a first body region source/drain adjacent portion extended in a first direction from the body region main part and a second body region source/drain adjacent portion extended in a second direction opposite to the first direction from the body region main part, and the gate extension region includes a first gate extension region formed on a vicinity of the first body region source/drain adjacent portion and a second gate extension region extended on the second body region source/drain adjacent portion.

[0014] A fourth aspect of the present invention is directed to the semiconductor device according to the second aspect of the present invention, wherein the body region source/drain adjacent portion includes one body region source/drain adjacent portion, and the gate extension region includes one gate extension region formed on a vicinity of the body region source/drain adjacent portion.

[0015] A fifth aspect of the present invention is directed to the semiconductor device according to the second aspect of the present invention, wherein the body region source/drain adjacent portion has a high concentration region having a higher impurity concentration of a second conductivity type than that in other regions over a region provided apart from the gate extension region by a predetermined distance.

[0016] A sixth aspect of the present invention is directed to the semiconductor device according to the second aspect of the present invention, wherein the gate extension region includes a gate extension region having an impurity concentration of the second conductivity type of  $5\times10^{18}$  cm<sup>-3</sup> or less

[0017] A seventh aspect of the present invention is directed to the semiconductor device according to the first aspect of the present invention, wherein the body region potential setting portion includes a semiconductor region for body fixation of the second conductivity type formed together with the source region.

[0018] An eighth aspect of the present invention is directed to the semiconductor device according to the first aspect of the present invention, wherein the partial isolation film lower semiconductor region has the second conductivity type and is formed in contact with the body region, the semiconductor device further comprising an element formation region outside body region of a first conductivity type provided outside the element formation region of the SOI layer and being capable of externally fixing an electric potential, the element formation region outside body region being formed in contact with the partial insulating film lower semiconductor region.

[0019] A ninth aspect of the present invention is directed to the semiconductor device according to the first aspect of the present invention, wherein the source and drain regions have such depths as to reach the buried insulating layer.

[0020] A tenth aspect of the present invention is directed to the semiconductor device according to the first aspect of the present invention, wherein the source and drain regions have such depths that a depletion layer extended from the source and drain regions does not reach the buried insulating layer during a normal operation.

[0021] An eleventh aspect of the present invention is directed to the semiconductor device according to the first

aspect of the present invention, wherein the source and drain regions have such depths that the buried insulating layer is not reached and a depletion layer extended from the drain region reaches the buried insulating layer during a normal operation.

[0022] A twelfth aspect of the present invention is directed to the semiconductor device according to the first aspect of the present invention, wherein the drain region has a greater depth than that of the source region and has such a depth that a depletion layer extended from the drain region reaches the buried insulating layer during a normal operation.

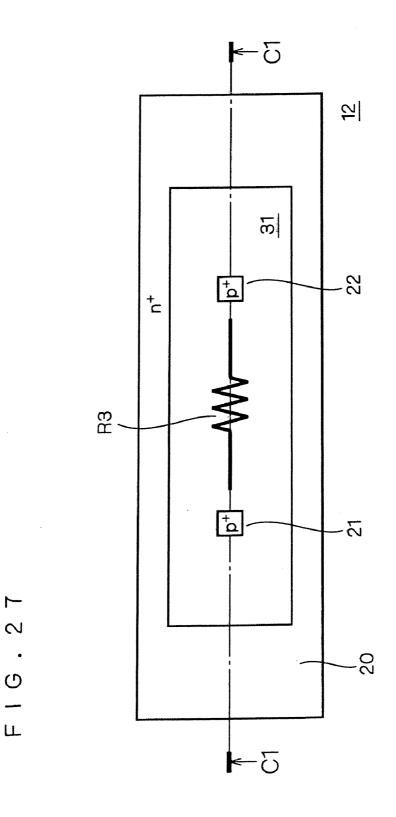

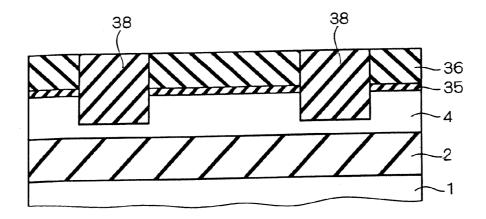

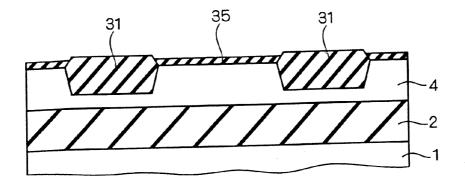

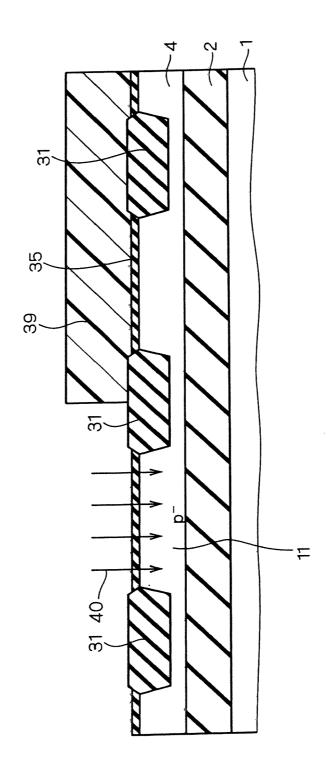

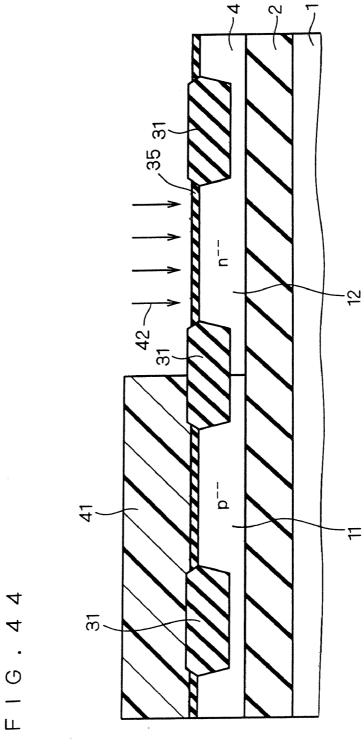

[0023] A thirteenth aspect of the present invention is directed to a semiconductor device having an SOI structure including a semiconductor substrate, a buried insulating layer and an SOI layer, comprising first and second semiconductor regions of a predetermined conductivity type provided in an element formation region of the SOI layer, and a partial insulating film provided in an upper layer portion of the element formation region and a partial insulating film lower semiconductor region of a predetermined conductivity type to be a part of the element formation region in a lower layer portion of the element formation region, wherein the partial insulating film lower semiconductor region is electrically connected to the first and second semiconductor regions to constitute a resistive element.

[0024] A fourteenth aspect of the present invention is directed to the semiconductor device according to the thirteenth aspect of the present invention, further comprising a complete insulating film provided through the SOI layer for isolating the element formation region.

[0025] A fifteenth aspect of the present invention is directed to the semiconductor device according to the thirteenth aspect of the present invention, wherein the element formation region other than the partial insulating film and the first and second semiconductor regions is a part of a region where the resistive element is to be formed.

[0026] A sixteenth aspect of the present invention is directed to the semiconductor device according to the thirteenth aspect of the present invention, wherein the resistive element includes a load resistor of an SRAM memory cell.

[0027] A seventeenth aspect of the present invention is directed to a semiconductor device having an SOI structure including a semiconductor substrate, a buried insulating layer and an SOI layer, comprising first and second element formation regions provided in the SOI layer, a partial isolation region including a partial insulating film provided in an upper layer portion of the SOI layer and a semiconductor region to be a part of the SOI layer which is provided under the partial insulating film and serving to isolate the first and second element formation regions from each other, and first and second MOS transistors formed in the first and second element formation regions, respectively, wherein at least one of a structure of a body region, a structure of a gate electrode and presence/absence of body potential fixation in the first and second MOS transistors is varied to make transistor characteristics of the first and second MOS transistors different from each other.

[0028] An eighteenth aspect of the present invention is directed to a semiconductor device having an SOI structure including a semiconductor substrate, a buried insulating layer and an SOI layer, comprising first and second element

formation regions provided in the SOI layer, a partial isolation region including a partial insulating film provided in an upper layer portion of the SOI layer and a semiconductor region to be a part of the SOI layer which is provided under the partial insulating film and serving to isolate the first element formation region from other regions, a complete isolation region including a complete insulating film provided through the SOI layer and serving to isolate the second element formation region from other regions, a first MOS transistor formed in the first element formation region, and a second MOS transistor formed in the second element formation region, wherein the first and second MOS transistors have different transistor characteristics.

[0029] A nineteenth aspect of the present invention is directed to a method of manufacturing a semiconductor device comprising the steps of (a) preparing an SOI substrate including an SOI structure having a semiconductor substrate, a buried insulating layer and an SOI layer, (b) selectively forming a partial insulating film in an upper layer portion of the SOI layer, the partial insulating film constituting a partial isolation region for isolating first and second element isolation regions in the SOI layer together with a semiconductor region to be a part of the SOI layer which is provided under the partial insulating film, and (c) forming first and second MOS transistors in the first and second element formation regions, wherein at the step (c), at least one of a structure of a body region, a structure of a gate electrode and presence/absence of body potential fixation in the first and second MOS transistors is varied to make transistor characteristics of the first and second MOS transistors different from each other.

[0030] A twentieth aspect of the present invention is directed to a method of manufacturing a semiconductor device comprising the steps of (a) preparing an SOI substrate including an SOI structure having a semiconductor substrate, a buried insulating layer and an SOI layer, (b) selectively forming a partial insulating film in an upper layer portion of the SOI layer, the partial insulating film constituting a partial isolation region for isolating the first element isolation region from other regions together with a semiconductor region to be a part of the SOI layer which is provided under the partial insulating film, (c) selectively forming a complete insulating film through the SOI layer, the complete isolating film constituting a complete isolation region for isolating the second element formation region from other regions, (d) forming a first MOS transistor in the first element formation region, and (e) forming a second MOS transistor in the second element formation region, wherein the steps (d) and (e) are performed such that the first and second MOS transistors have different transistor characteristics.

[0031] According to the first aspect of the present invention, the body region potential setting portion capable of externally fixing an electric potential is provided in the element formation region. Therefore, it is possible to fix a body potential to be an electric potential of the body region main part with a high stability.

[0032] According to the second aspect of the present invention, the body region source/drain adjacent portion and the source and drain regions are electrically blocked by the gate extension region of the gate electrode. Consequently, the presence of the body region source/drain adjacent por-

tion does not affect the operation of the MOS transistor and the body potential can be fixed with a high stability.

[0033] According to the third aspect of the present invention, the body potential can be fixed in the first and second body region source/drain adjacent portions, respectively. Correspondingly, it is possible to fix the body potential with a higher stability.

[0034] According to the fourth aspect of the present invention, it is possible to fix the body potential with a high stability by one body region source/drain adjacent portion while minimizing a gate capacitance in one gate extension region.

[0035] According to the fifth aspect of the present invention, the body region source/drain adjacent portion has a high concentration region having a higher impurity concentration than that in other regions over the region provided apart from the gate extension region by a predetermined distance. Therefore, when the impurity of the second conductivity type for the formation of a high concentration region is to be implanted, it is possible to reliably prevent the impurity of the second conductivity type from being implanted into the gate extension region.

[0036] According to the sixth aspect of the present invention, the gate extension region includes a gate extension region having an impurity concentration of the second conductivity type of 5×10<sup>18</sup> cm<sup>-3</sup> or less. Therefore, it is possible to prevent a threshold voltage of the MOS transistor from being varied.

[0037] According to the seventh aspect of the present invention, the electric potential is fixed in the semiconductor region for body potential fixation of the second conductivity type which is formed together with the source region. Consequently, it is possible to fix the body potential with a high stability. The presence of the semiconductor region for body potential fixation does not affect the MOS transistor for being operated by setting the body region and the source region to have the same electric potential.

[0038] According to the eighth aspect of the present invention, it is possible to fix the electric potential of the body region from the element formation region outside body region through the partial isolating film lower semiconductor region in addition to the body region potential setting portion.

[0039] According to the ninth aspect of the present invention, the source and drain regions in the MOS transistor have such depths as to reach the buried insulating layer. Therefore, a pn junction is not formed on respective bottom faces. Consequently, a junction leakage can be suppressed.

[0040] According to the tenth aspect of the present invention, the source and drain regions in the MOS transistor have such depths that the depletion layer extended from the source and drain regions does not reach the buried insulating layer during the normal operation. Therefore, in the case in which the electric potential of the body region is to be fixed on the outside of the element formation region, the body potential fixation can be carried out with a high stability.

[0041] According to the eleventh aspect of the present invention, the source and drain regions in the MOS transistor do not reach the buried insulating layer and the depletion layer extended from the drain region has such a depth as to

reach the buried insulating layer during the normal operation. Therefore, it is possible to fix the body potential on the outside of the element formation region while reducing a junction capacitance.

[0042] According to the twelfth aspect of the present invention, the drain region has a greater depth than that of the source region and has such a depth that a depletion layer extended from the drain region reaches the buried insulating layer during a normal operation. Therefore, it is possible to reduce a junction capacitance in the drain region while fixing the body potential through the source region on the outside of the element formation region.

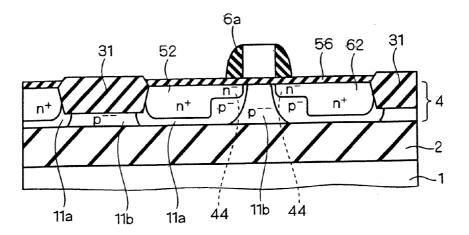

[0043] According to the thirteenth aspect of the present invention, the partial insulating film lower semiconductor region of a predetermined conductivity type to be a part of the SOI layer provided under the partial insulating film is a component of a resistive element. Therefore, it is possible to obtain a resistive element having a high resistance value with a comparatively small formation area. As a result, it is possible to constitute a semiconductor integrated circuit having a high degree of integration.

[0044] According to the fourteenth aspect of the present invention, it is possible to completely isolate the resistive element from the outside through the complete insulating film

[0045] According to the fifteenth aspect of the present invention, the element formation region other than the partial insulating film and the first and second semiconductor regions is a part of a region where the resistive element is to be formed. Consequently, it is possible to prevent the resistance value of the resistive element from being varied.

[0046] According to the sixteenth aspect of the present invention, the resistive element is used as the load resistor of an SRAM. Consequently, it is possible to constitute an SRAM having a high degree of integration.

[0047] According to the seventeenth aspect of the present invention, at least one of a structure of a body region, a structure of a gate electrode and presence of body potential fixation in the first and second MOS transistors is varied to make transistor characteristics of the first and second MOS transistors different from each other. Consequently, it is possible to constitute a high functional semiconductor integrated circuit comprising first and second MOS transistors.

[0048] According to the eighteenth aspect of the present invention, the transistor characteristic is varied between the first MOS transistor isolated by the partial isolation region and the second transistor isolated by the complete isolation region. Consequently, it is possible to constitute a high functional semiconductor integrated circuit comprising first and second MOS transistors.

[0049] According to the nineteenth aspect of the present invention, at least one of a structure of a body region, a structure of a gate electrode and presence of body potential fixation in the first and second MOS transistors is varied to make transistor characteristics of the first and second MOS transistors different from each other. Consequently, it is possible to constitute a high functional semiconductor integrated circuit comprising first and second MOS transistors.

[0050] According to the twentieth aspect of the present invention, the transistor characteristic is varied between the

first MOS transistor isolated by the partial isolation region and the second transistor isolated by the complete isolation region. Consequently, it is possible to constitute a high functional semiconductor integrated circuit comprising first and second MOS transistors.

[0051] In order to solve the above-mentioned problems, it is an object of the present invention to provide a semiconductor device having an SOI structure which can fix a body potential with a high stability in a body region over an element formation region isolated by a partial isolation region and a semiconductor device capable of constituting a high functional semiconductor integrated circuit for a partial isolation or a partial isolation and complete isolation combination, and a method of manufacturing the semiconductor device.

[0052] These and other objects, features, aspects and advantages of the present invention will become more apparent from the following detailed description of the present invention when taken in conjunction with the accompanying drawings.

#### BRIEF DESCRIPTION OF THE DRAWINGS

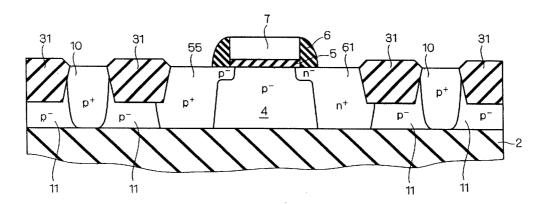

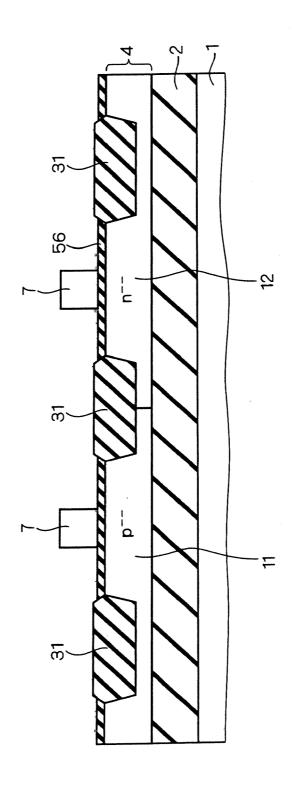

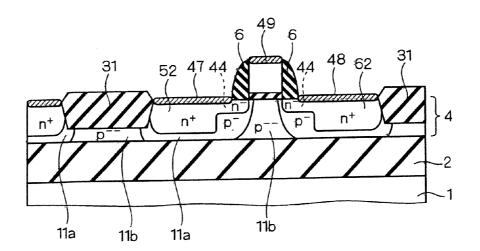

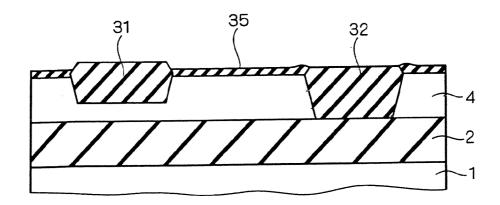

[0053] FIG. 1 is a sectional view showing an example of a conventional PDSOI-MOSFET,

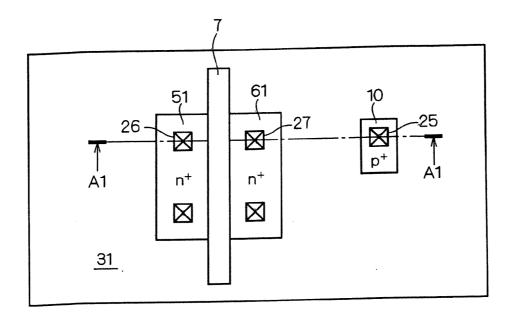

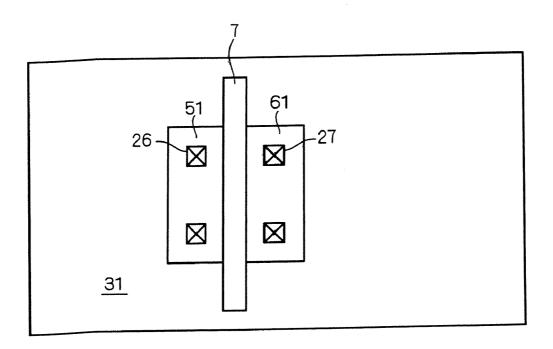

[0054] FIG. 2 is a plan view showing an example of the conventional PDSOI-MOSFET,

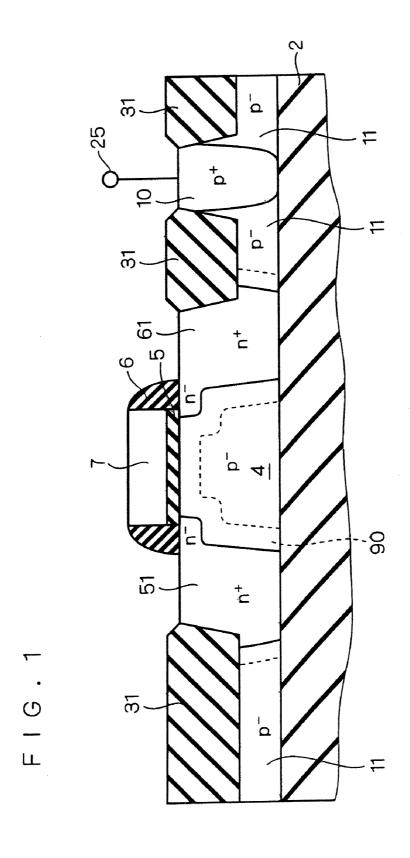

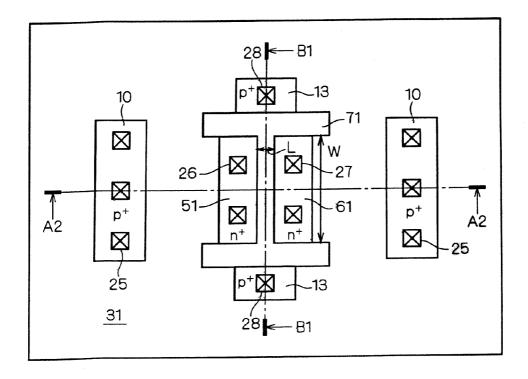

[0055] FIG. 3 is a plan view showing a planar structure of a semiconductor device according to a first embodiment (first mode) of the present invention,

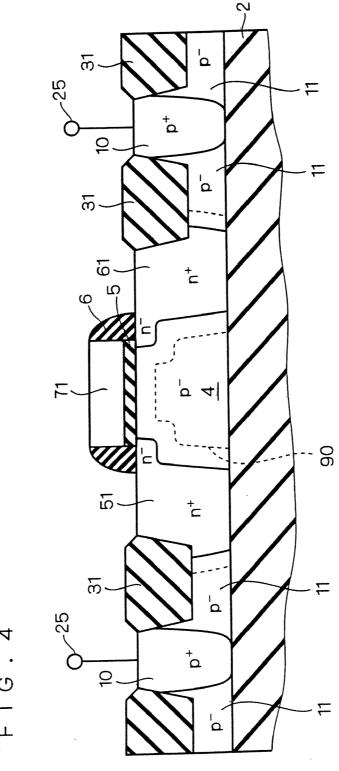

[0056] FIG. 4 is a sectional view showing a section taken along a line A2-A2 in FIG. 3,

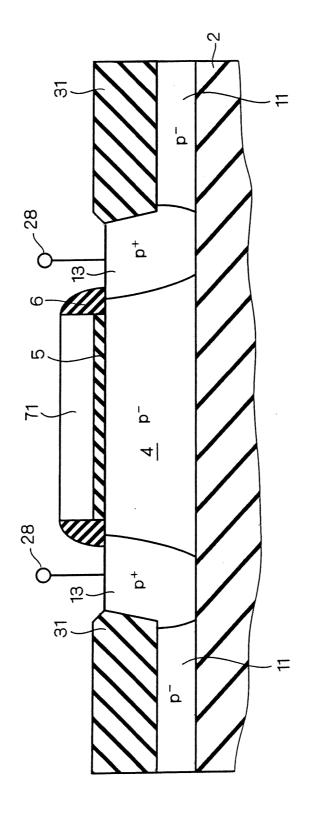

[0057] FIG. 5 is a sectional view showing a section taken along a line B1-B1 in FIG. 3,

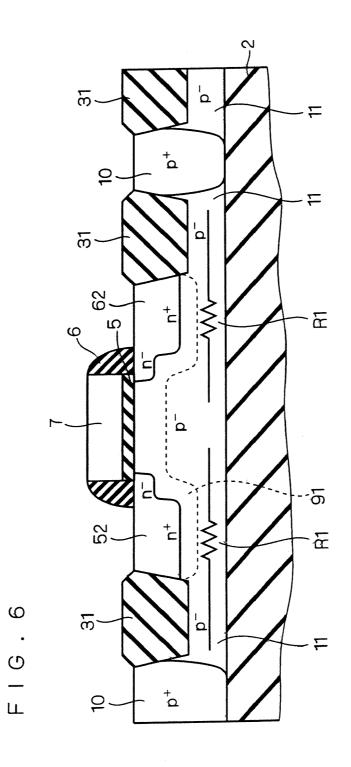

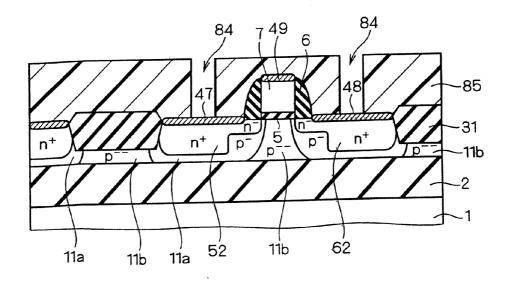

[0058] FIG. 6 is a sectional view showing a second mode of the first embodiment,

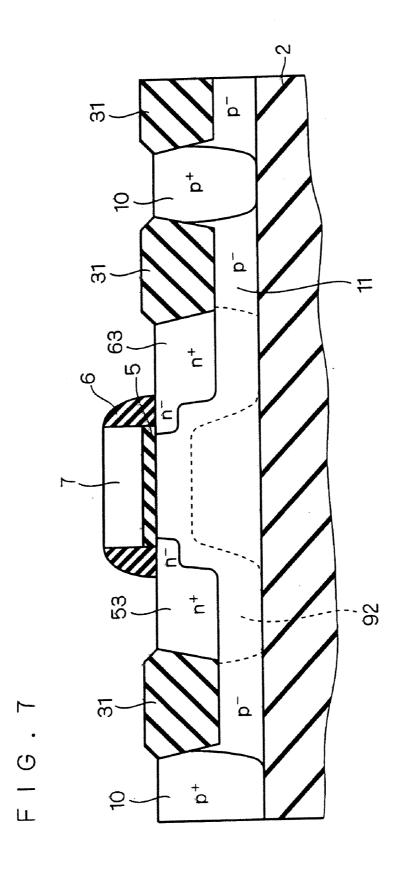

[0059] FIG. 7 is a sectional view showing a third mode of the first embodiment,

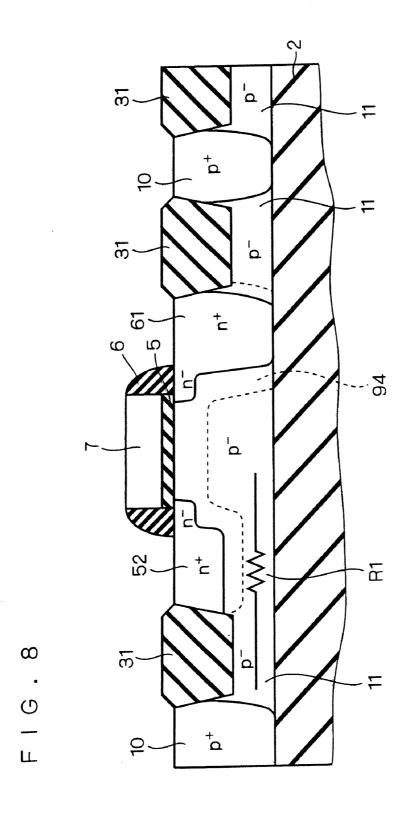

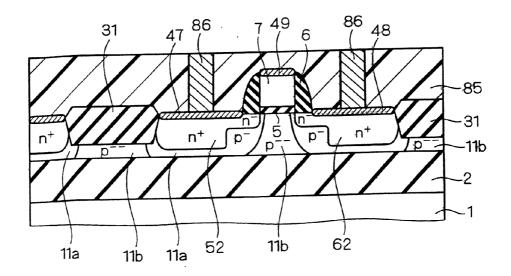

[0060] FIG. 8 is a sectional view showing a fourth mode of the first embodiment,

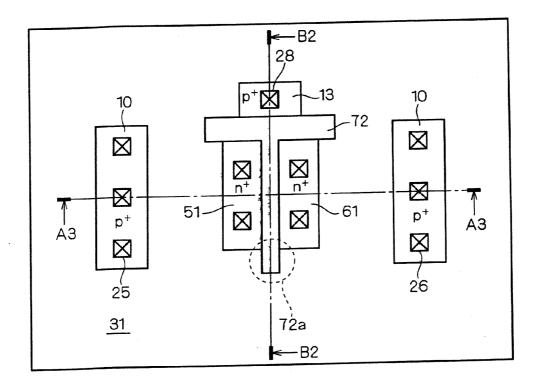

[0061] FIG. 9 is a plan view showing a planar structure of a semiconductor device according to a second embodiment of the present invention,

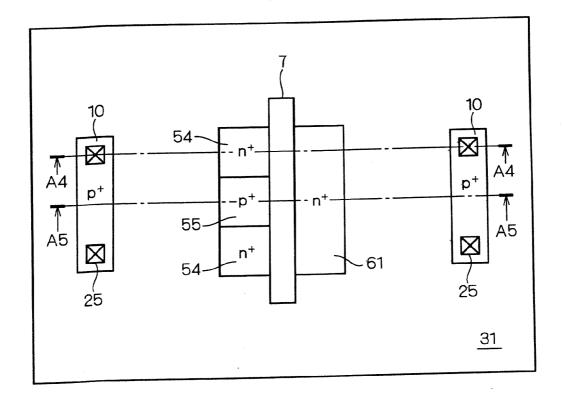

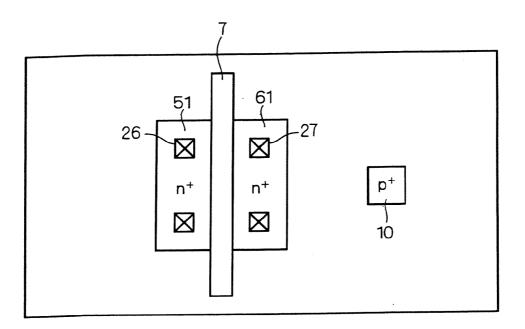

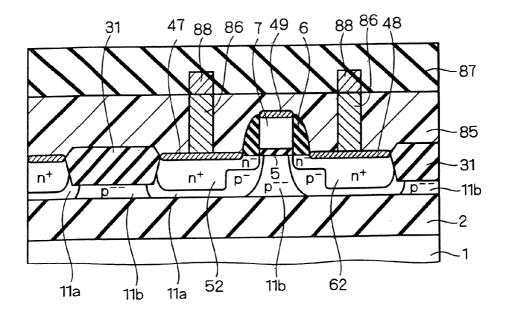

[0062] FIG. 10 is a plan view showing a planar structure of a semiconductor device according to a third embodiment of the present invention,

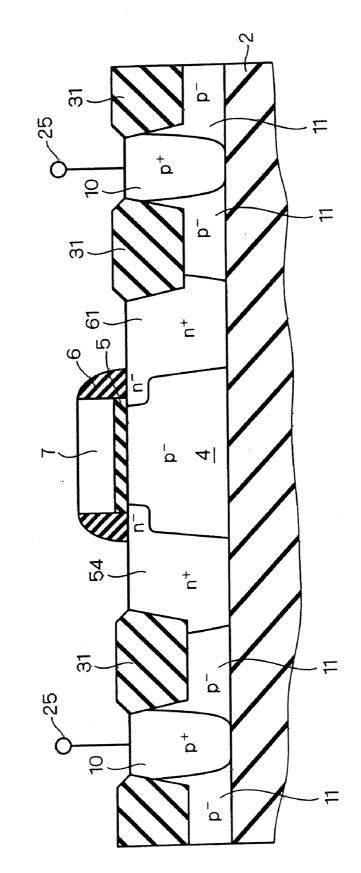

[0063] FIG. 11 is a sectional view showing a section taken along a line A4-A4 in FIG. 10,

[0064] FIG. 12 is a sectional view showing a section taken along a line A5-A5 in FIG. 11,

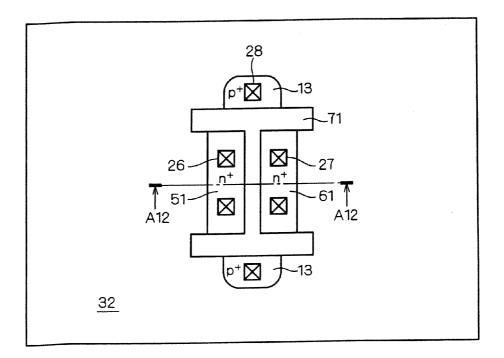

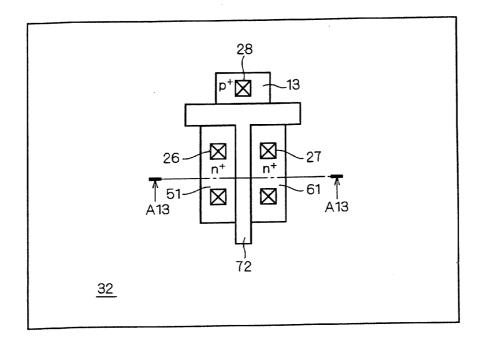

[0065] FIG. 13 is a plan view showing a planar structure of a semiconductor device according to a first mode of a fourth embodiment of the present invention,

[0066] FIG. 14 is a plan view showing a planar structure of a semiconductor device according to a second mode of the fourth embodiment of the present invention,

[0067] FIG. 15 is a plan view showing a planar structure of a semiconductor device according to a third mode of the fourth embodiment of the present invention,

[0068] FIG. 16 is a plan view showing a planar structure of a type 5 (No. 1) of a PDSOI-MOSFET,

[0069] FIG. 17 is a plan view showing a planar structure of the type 5 (No. 2) of the PDSOI-MOSFET,

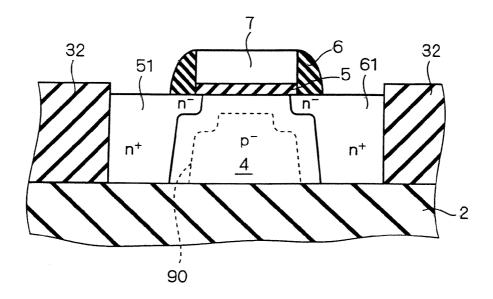

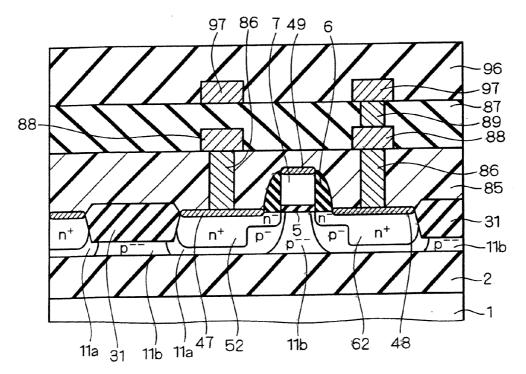

[0070] FIG. 18 is a sectional view showing a sectional structure of a PDSOI-MOSFET of a type A,

[0071] FIG. 19 is a plan view showing a planar structure of the PDSOI-MOSFET of the type A,

[0072] FIG. 20 is a plan view showing a planar structure of a PDSOI-MOSFET of a type B,

[0073] FIG. 21 is a plan view showing a planar structure of a PDSOI-MOSFET of a type D,

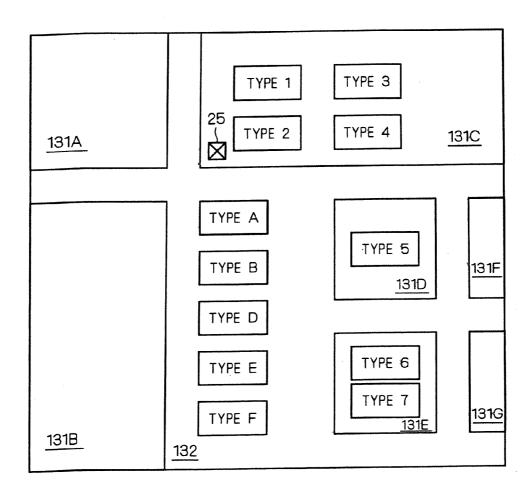

[0074] FIG. 22 is a view conceptually showing a planar structure of a semiconductor device according to a sixth embodiment,

[0075] FIG. 23 is a circuit diagram showing a first applied example of the semiconductor device according to the sixth embodiment,

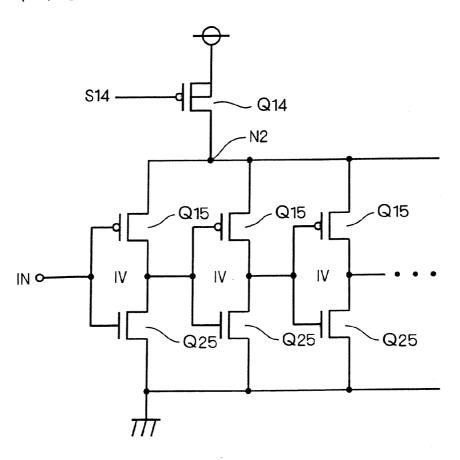

[0076] FIG. 24 is a circuit diagram showing a second applied example of the semiconductor device according to the sixth embodiment,

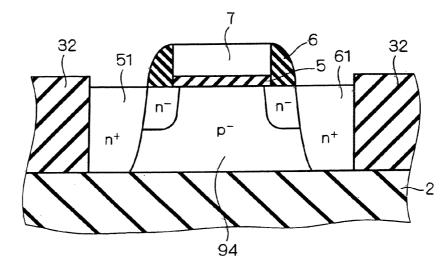

[0077] FIG. 25 is a sectional view showing a structure of a complete isolated PDSOI-MOSFET,

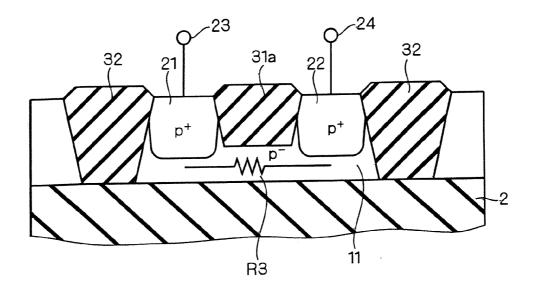

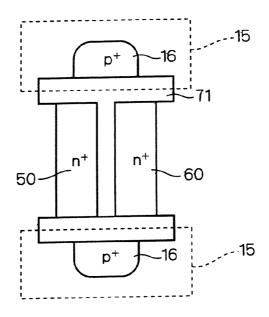

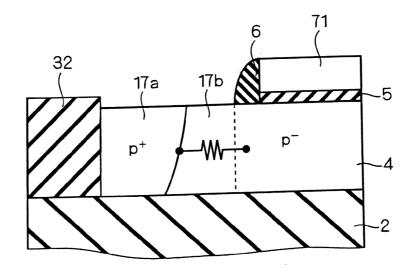

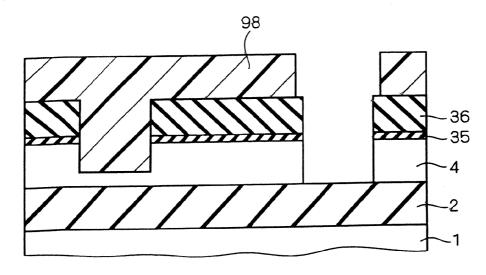

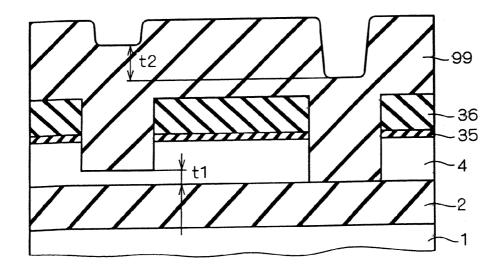

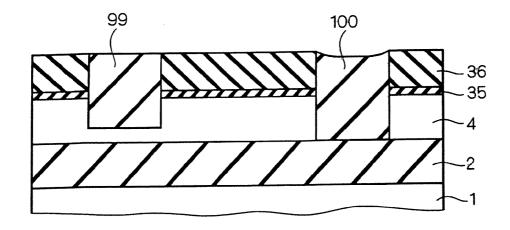

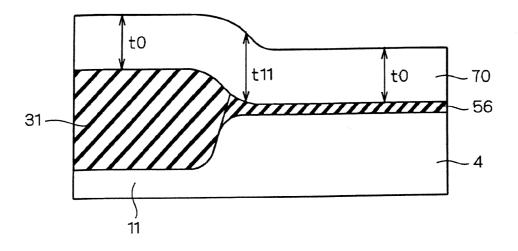

[0078] FIG. 26 is a sectional view showing a resistive element formation region of a semiconductor device according to a first mode of a seventh embodiment of the present invention.

[0079] FIG. 27 is a plan view showing the first mode of the seventh embodiment,

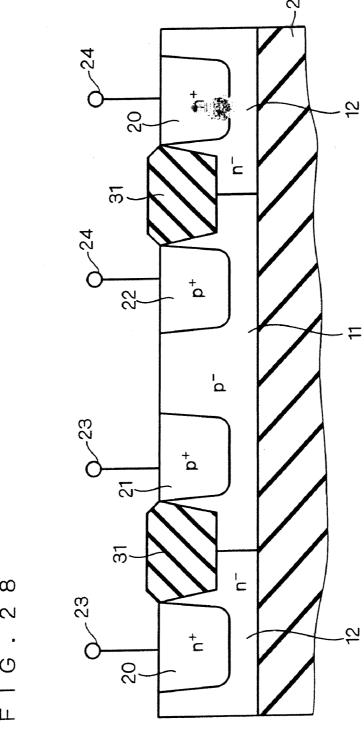

[0080] FIG. 28 is a sectional view showing a general resistive element formation region,

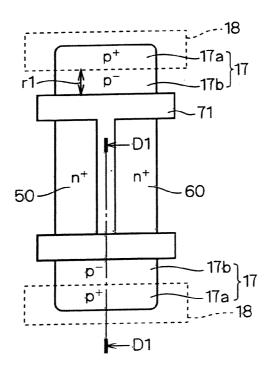

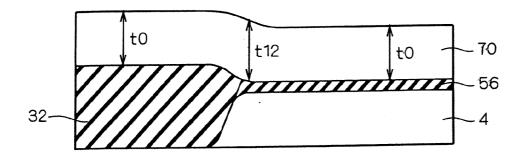

[0081] FIG. 29 is a sectional view showing a resistive element formation region of a semiconductor device according to a second mode of the seventh embodiment,

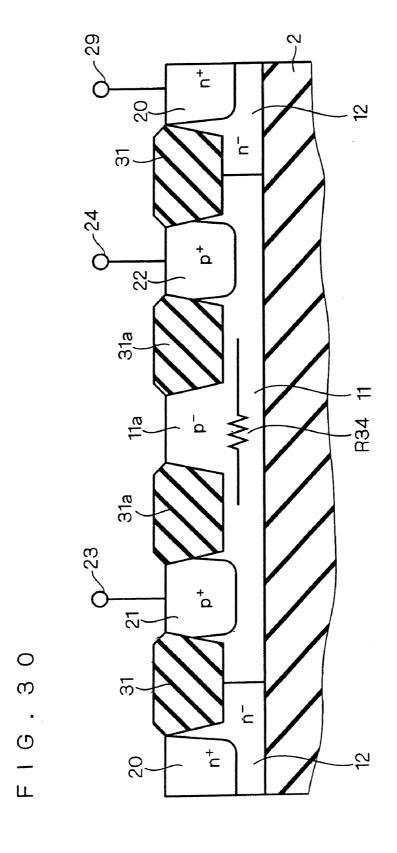

[0082] FIG. 30 is a sectional view showing a resistive element formation region of a semiconductor device according to a third mode of the seventh embodiment,

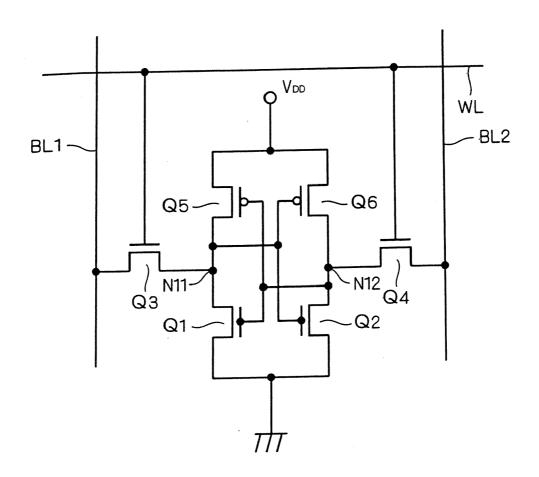

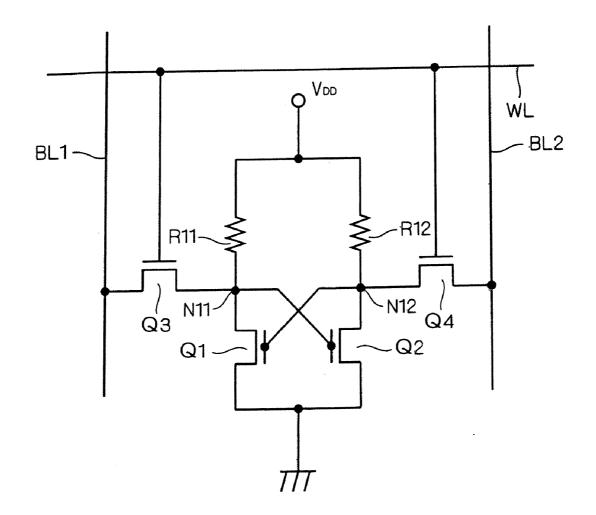

[0083] FIG. 31 is a circuit diagram showing an SRAM cell having a 6-transistor CMOS structure,

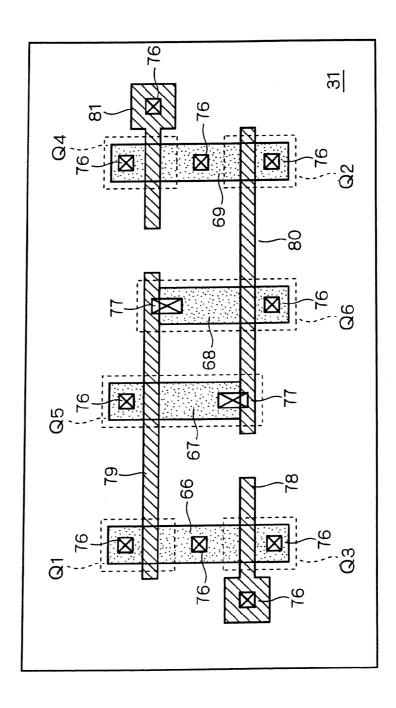

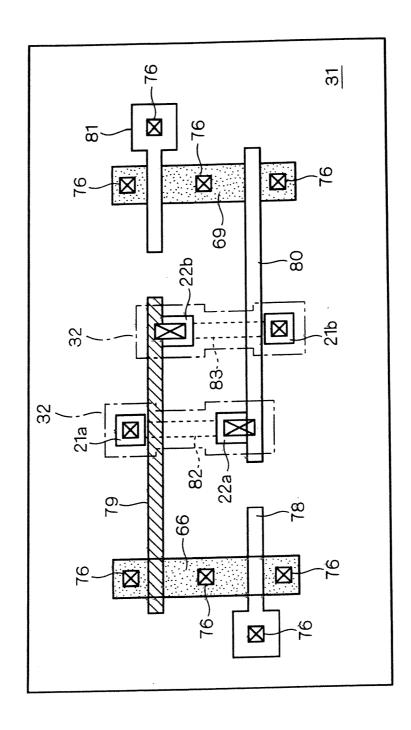

[0084] FIG. 32 is a plan view showing a layout structure for implementing the SRAM cell illustrated in FIG. 31,

[0085] FIG. 33 is a circuit diagram showing an SRAM cell having a high resistance load type cell structure,

[0086] FIG. 34 is a plan view showing a layout structure for implementing the SRAM cell illustrated in FIG. 33,

[0087] FIG. 35 is a plan view showing a general H gate electrode,

[0088] FIG. 36 is a plan view showing a planar structure of a semiconductor device according to an eighth embodiment of the present invention,

[0089] FIG. 37 is a sectional view showing a section taken along a line D1-D1 in FIG. 36,

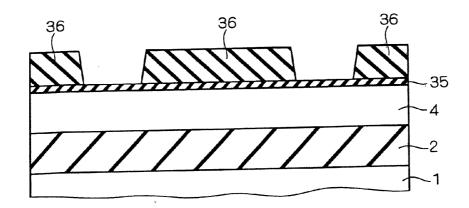

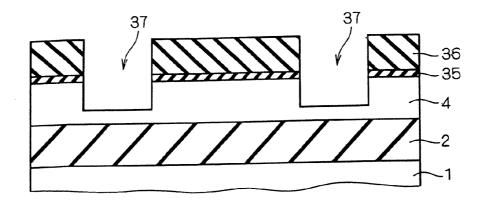

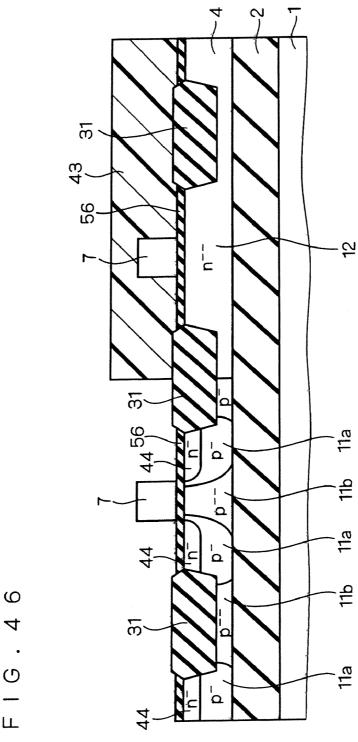

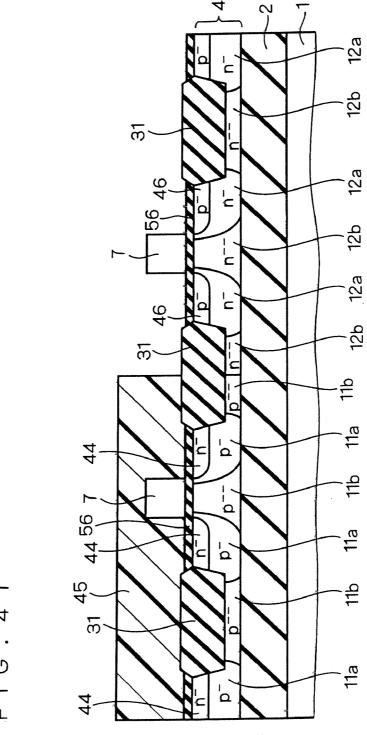

[0090] FIGS. 38 to 52 are sectional views showing a partial isolation flow,

[0091] FIGS. 53 to 57 are sectional views showing a complete isolation flow,

[0092] FIG. 58 is a sectional view showing a peripheral region of a partial isolation region in formation of a polysilicon layer for a gate electrode, and

[0093] FIG. 59 is a sectional view showing a peripheral region of a complete isolation region in the formation of the polysilicon layer for the gate electrode.

# DESCRIPTION OF THE PREFERRED EMBODIMENTS

Summary of the Invention

(Technical Background)

[0094] A partial isolation technique has an advantage in that an electric potential of a body region provided outside an element formation region through a partial isolation region can be set externally and a substrate potential can be thereby fixed through an SOI layer provided under a partial oxide film. The advantage is not always sufficient for a high breakdown voltage element or a device requiring high reliability of a hot carrier. Since the SOI layer provided under the partial oxide film has a small thickness, a finite body resistance is present. Also in the device, therefore, a kink is sometimes generated through the body resistance in a high voltage region. Consequently, the partial isolation technique has a technical background in which the reliability of a hot carrier and the frequency dependency of a delay time are not always sufficient.

[0095] In the partial isolation technique or a partial isolation and complete isolation combination technique, an H gate electrode and a T gate electrode which will be described below in detail are used in a portion where the reliability is particularly required in order to prevent the reliability of a gate oxide film from being reduced due to a variation in an isolation edge. Consequently, it is necessary to provide a semiconductor device capable of enhancing the reliability for body potential fixation, and furthermore, increasing an edge leakage current.

(Single Kind of Transistor)

[0096] In a partial isolation having a body terminal, a single kind of transistor using one of an H gate electrode, a T gate electrode and a source-tied structure which will be described below in detail is utilized so that a stability for fixing a body potential can be further enhanced and the problems of a hot carrier and the frequency dependency of a delay time can be further improved. By such a method, however, a speed of a circuit is reduced. Therefore, it is desirable that a conventional device (a device using a gate electrode having an ordinary structure or the like) should be utilized in a portion where a high speed is required.

(Combination of Plural Kinds of Transistors)

[0097] Moreover, when a body terminal is not partially provided and a transistor is operated in a floating state, a threshold voltage can be dropped. Therefore, a transistor

having a large drain current can be fabricated. Accordingly, a transistor having a body floating structure is provided in a circuit together with a transistor having a body fixing structure through the body terminal so that a high-speed circuit having low power consumption can be fabricated.

[0098] In the partial isolation technique, moreover, a variation in a threshold due to a difference in a distance from the body terminal can be suppressed by using the H gate electrode, the T gate electrode and the source-tied structure in which the body terminal is to be provided in respective transistors. Furthermore, when a floating structure using no body terminal is utilized, it is apparent that a variation in a threshold due to a body resistance can be suppressed. The floating structure has a disadvantage in that a threshold voltage has a frequency dependency.

[0099] By a combination of plural kinds of transistors having various features, thus, it is possible to provide a high functional device in respect of design.

## First Embodiment

#### (Conventional PDSOI-MOSFET)

[0100] FIG. 1 is a sectional view showing an example of a PD (Partially-Depleted) SOI-MOSFET to be one of conventional MOS transistors, and FIG. 2 is a plan view showing an example of the conventional PDSOI-MOSFET. A sectional taken along a line A1-A1 in FIG. 2 corresponds to FIG. 1.

[0101] The PDSOI-MOSFET has such a feature that a depletion layer 90 provided under a gate electrode 7 does not reach a buried oxide film 2 as shown in FIG. 1. Because of such a feature, the PDSOI-MOSFET has an excellent controllability of a threshold voltage.

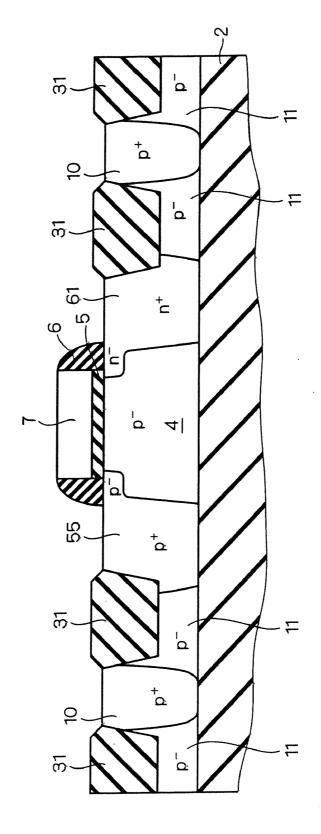

[0102] As shown in FIGS. 1 and 2, an SOI layer 4 is formed on the buried oxide film 2 provided on a semiconductor substrate (not shown). Consequently, an SOI substrate having an SOI structure can be implemented. The SOI layer 4 is isolated through a partial isolation region including a partial oxide film 31 and a p well region 11 provided under the partial oxide film 31.

[0103] A source region 51 and a drain region 61 which are selectively formed on the SOI layer 4 have such depths as to reach a back face of the SOI layer 4 (a surface of the buried oxide film 2) from a surface thereof, respectively.

[0104] A gate oxide film 5 is formed on the SOI layer 4 between the source region 51 and the drain region 61, and a gate electrode 7 is formed on the gate oxide film 5. Moreover, a side wall 6 is formed on a side wall of the gate electrode 7. Then, a source terminal 26 and a drain terminal 27 are provided on the source region 51 and the drain region 61, respectively.

[0105] Moreover, a body region 10 (a body region outside an element formation region) is isolated by the partial oxide film 31 an the p well region 11 provided thereunder and is formed from the surface of the SOI layer 4 to the back face thereof. The body region 10 is electrically connected to a main part of the body region to be the SOI layer 4 provided under the gate electrode 7 through the p well region 11.

[0106] Accordingly, a predetermined electric potential is applied to a body terminal 25 provided on the body region

10 to fix a body of the PDSOI-MOSFET shown in FIG. 1 (to fix a channel potential in the SOI layer 4 provided under the gate oxide film 5). Consequently, the above-mentioned floating-body effect can be suppressed.

(PDSOI-MOSFET according to First Embodiment)

[0107] FIG. 3 is a plan view showing a planar structure of a semiconductor device according to a first embodiment of the present invention, FIG. 4 is a sectional view showing a section taken along a line A2-A2 in FIG. 3, and FIG. 5 is a sectional view showing a section taken along a line B1-B1 in FIG. 3.

[0108] The semiconductor device according to the first embodiment is provided on an SOI layer isolated partially and provides body fixation through a PDSOI-MOSFET having an H gate electrode.

[0109] As shown in FIG. 3, an H gate electrode 71 electrically isolates a body region 13 formed in a gate width W direction adjacently to a source region 51 and a drain region 61 from the drain region 61 and the source region 51 through "I" (a gate extension region, and source/drain adjacent portions of first and second body regions) in a transverse direction (a vertical direction in the drawing), and a central "-" (a main part of a gate electrode) functions as a gate electrode of an original MOS transistor. A p<sup>-</sup> body region is formed under the "I" of the H gate electrode 71 in the transverse direction (the vertical direction in the drawing) through an insulating film.

[0110] As shown in FIGS. 3 and 5, two body regions 13 and 13 (the source/drain adjacent portions of the first and second body regions) are extended in a first direction along a gate length direction and a second direction opposite thereto from the main part of the body region to be the SOI layer 4 provided under the main part of the gate electrode of the H gate electrode 71 in a gate width direction adjacently to the source region 51 and the drain region 61.

[0111] Accordingly, the source region 51 and drain region 61 and the body regions 13 and 13 are electrically blocked through the "I" of the H gate electrode 71 in the transverse direction and a body potential obtained from a body terminal 28 is not directly transmitted to the drain region 61 and the source region 51.

[0112] The source region 51 and the drain region 61 which are selectively formed on the SOI layer 4 have such depths as to reach a back face of the SOI layer 4 from a surface thereof, respectively.

[0113] A gate oxide film 5 is formed on the SOI layer 4 between the source region 51 and the drain region 61, the central "-" portion of the H gate electrode 71 is formed on the gate oxide film 5, and a side wall 6 is formed on a side wall of the gate electrode 71. Then, a source terminal 26 and a drain terminal 27 (which are not shown in FIG. 4) are provided on the source region 51 and the drain region 61, respectively.

[0114] Moreover, a body region 10 is isolated by a partial isolation region of a partial oxide film 31 and a p well region 11 provided thereunder and is formed from the surface of the SOI layer 4 to the back face thereof. The body region 10 is electrically connected to the main part of the body region to be the SOI layer 4 provided under the gate electrode 71 through the p well region 11.

[0115] As described above, furthermore, the body region 13 is formed adjacently to the main part of the body region (the channel region) to be the SOI layer 4 provided under the gate oxide film 5.

[0116] Accordingly, a predetermined electric potential is applied to the body terminal 28 provided on the body region 13 in addition to a body terminal 25 provided on the body region 10. Consequently, the body fixation of the PDSOI-MOSFET according to the first embodiment can be carried out. Therefore, a body potential to be the electric potential of the main part of the body region can be fixed stably so that the floating-body effect can be suppressed considerably.

[0117] The PDSOI-MOSFET having the above-mentioned structure according to the first embodiment has such a feature that a depletion layer 90 provided under the central "-" portion of the H gate electrode 71 does not reach a buried oxide film 2. Because of such a feature, the PDSOI-MOSFET has an excellent controllability of a threshold voltage.

[0118] Therefore, the semiconductor device according to the first embodiment has the H gate electrode structure and is provided with the body regions 13 and 13 in a region where the PDSOI-MOSFET is to be formed. Consequently, it is possible to decrease a body resistance than that in the conventional PDSOI-MOSFET shown in FIGS. 1 and 2 and to fix a body potential having a high stability. This respect will be described below in detail.

[0119] In the conventional PDSOI-MOSFET shown in FIGS. 1 and 2, the body terminal 25 and the channel region are electrically connected through the thin p well region 11 provided under a partial isolation. Therefore, the body resistance is comparatively high and a transistor characteristic is easily varied depending on a distance from the body terminal 25.

[0120] On the other hand, in the structure according to the first embodiment, the body terminal 28 can be provided on the body region 13 formed in the vicinity of the source region 51 and the drain region 61 in the PDSOI-MOSFET formation region in addition to the body terminal 25 on the body region 10 provided through the partial isolation regions (the partial oxide film 31 and the p well region 11 provided thereunder). These two types of body terminals 25 and 28 can reduce the body resistance value and can effectively suppress a variation in the transistor characteristic.

[0121] Moreover, a reduction in the body resistance can raise a drain breakdown voltage. To the contrary, in the case in which the thickness of the p well region 11 provided under the partial oxide film 31 is proportional to that of the SOI layer 4 and the same body resistance is set, the thickness of the SOI layer 4 can be reduced by employing the H gate electrode structure.

[0122] When the thickness of the SOI layer 4 is reduced, there is a possibility that a junction capacitance of a line component of a source-drain (a longitudinal component) might be reduced, resulting in an increase in a speed. Moreover, the H gate electrode structure can reduce an edge leakage (edge parasitic MOS) caused by the isolation. Furthermore, it is possible to prevent the reliability of the gate oxide film from being deteriorated due to the isolation edge. The edge leakage caused by the isolation and the deterioration in the reliability of the gate oxide film will be described below in detail.

[0123] The PDSOI-MOSFET according to the first embodiment having the above-mentioned features can be used particularly effectively for an I/O circuit, an analog circuit (a PLL, a sense amplifier circuit), a timing circuit, a dynamic circuit and the like in which the fixation of the body potential is greatly required.

[0124] (Classification according to Source-Drain Region)

(First Mode: a structure in which both a source region and a drain region are directly provided in contact with a buried oxide film 2 (the structure shown in FIGS. 3 to 5)

[0125] As shown in FIG. 4, the source region 51 and the drain region 61 are directly provided in contact with the buried oxide film 2. Therefore, the effect of fixing the body potential through the body terminal 25 provided on the body region 10 is reduced.

[0126] According to the structure of the first mode, however, a pn junction is not formed on the bottom surfaces of the source region 51 and the drain region 61. Correspondingly, the area of a pn junction interface is reduced so that a junction leakage can be suppressed. Moreover, a junction capacitance can be reduced.

[0127] (Second Mode: a structure in which a depletion layer extended from a source region and a drain region, as well as the source region and the drain region, are not provided in contact with a buried oxide film)

[0128] FIG. 6 is a sectional view showing a second mode of the first embodiment. FIG. 6 corresponds to a section taken along a line A2-A2 in FIG. 3.

[0129] As shown in FIG. 6, a source region 52 and a drain region 62 do not reach a buried oxide film 2 but is formed in an SOI layer 4. Furthermore, a depletion layer 91 extended from the source region 52 and the drain region 62 during a normal operation does not reach the buried oxide film 2. Other structures are the same as those in the first mode.

[0130] According to the second mode, thus, the source region 52 and the drain region 62, and the depletion layer 91 extended from the source region 52 and the drain region 62 do not reach the buried oxide film 2. Therefore, it is possible to reduce a body resistance R1 reaching a channel region from the body terminal 25, and there is an advantage that the effect of fixing the body potential through the body terminal 25 is the greatest. However, there is a disadvantage that the pn junction capacitance is increased.

[0131] (Third Mode: a structure in which a drain region is not provided in contact with a buried oxide film but a depletion layer extended from the drain region is not provided in contact with the buried oxide film)

[0132] FIG. 7 is a sectional view showing a third mode of the first embodiment. FIG. 7 corresponds to the section taken along the line A2-A2 in FIG. 3.

[0133] As shown in FIG. 7, a source region 53 and a drain region 63 do not reach a buried oxide film 2 but is formed in an SOI layer 4. However, a depletion layer 92 extended from the source region 53 and the drain region 63 during a normal operation does not reach the buried oxide film 2. Other structures are the same as those in the first mode.

[0134] In the third mode, the drain region 63 is not directly provided in contact with the buried oxide film 2 and the effect of fixing a body potential is therefore greater than that in the first mode. In addition, the depletion layer 92 is provided in contact with the buried oxide film 2. Therefore, a pn junction capacitance is also reduced. In the case in which the depletion layer 92 extended from the drain region 63 is provided in contact with the buried oxide film 2 at a voltage of 0 V, there is a greater advantage that the pn junction capacitance can be reduced. While the depletion layer 92 extended from the source region 53 is also provided in contact with the buried oxide film 2 in the example of FIG. 7, the same effects can be obtained even if the depletion layer 92 is not provided in contact with the buried oxide film 2.

[0135] (Fourth Mode: an asymmetrical structure in which a drain region is formed more deeply than a source region and the drain region or a depletion layer extended from the drain region is provided in contact with a buried oxide film)

[0136] FIG. 8 is a sectional view showing a fourth mode of the first embodiment. FIG. 8 corresponds to the section taken along the line A2-A2 in FIG. 3.

[0137] As shown in FIG. 8, although the source region 52 and a depletion layer 94 extended from the source region 52 do not reach the buried oxide film 2, it has a source-drain asymmetrical structure in which the drain region 61 is directly provided in contact with the buried oxide film 2. Other structures are the same as those in the first mode.

[0138] The source-drain asymmetrical structure can be fabricated by separately implanting ions into a source and a drain using a resist mask.

[0139] In the fourth mode having such a structure, the junction capacitance of the source region 52 rarely affects an operating speed of a circuit. Therefore, even if the depletion layer 94 extended from the source region 52 is not provided in contact with the buried oxide film 2, there is no bad influence. Since the depletion layer 94 extended from the source region is not provided in contact with the buried oxide film 2, a body resistance value R1S provided under a region from a channel region to the vicinity of the source region 52 can be reduced. Moreover, while the source region may be formed with a structure in which the depletion layer 94 is provided in contact with the buried oxide film 2, it is more desirable that the depletion 94 should not reach the buried oxide film 2 because the area of the pn junction interface can be reduced.

[0140] Since the drain region 61 is provided in contact with the buried oxide film 2. Therefore, the junction capacitance and the area of the pn junction interface can be reduced. Furthermore, if the drain region 61 is not provided in contact with the buried oxide film 2 but the depletion layer extended from the drain region 61 during a normal operation is provided in contact with the buried oxide film 2, the body resistance value can be reduced.

## Second Embodiment

[0141] FIG. 9 is a plan view showing a planar structure of a semiconductor device according to a second embodiment of the present invention. A section taken along a line A3-A3 in FIG. 9 is the same as the shape shown in FIG. 4 and a

section taken along a line B1-B1 in FIG. 9 is the same as the shape shown in FIG. 5 except that a body region 13 is formed on one of sides.

[0142] As shown in FIG. 9, a PDSOI-MOSFET according to the second embodiment has a structure in which a T gate electrode 72 is employed in place of the H gate electrode 71 according to the first embodiment. More specifically, while the H gate electrode 1 according to the first embodiment has the body region 13 provided in the vicinity of "I" on the right and left sides respectively, the T gate electrode 72 according to the second embodiment has the body region 13 provided in the vicinity of "I" on one of the sides in the same manner as the H gate electrode 71. Since other structures are the same as those in the first embodiment, description will be omitted.

[0143] In the T gate electrode 72 according to the second embodiment, accordingly, body fixation is carried out through body terminals 25 and 28 provided on body regions 10 and 13 of two types in the same manner as in the first embodiment. Consequently, a body resistance value can be reduced and a variation in a transistor characteristic can be suppressed effectively.

[0144] In the T gate electrode 72 according to the second embodiment, moreover, an area covering an edge of an active region (a source region 51, a drain region 61 or the like where a partial oxide film 31 is not formed) can be reduced. Therefore, a gate capacitance can be more reduced than that in the H gate electrode 71. Consequently, an operation of a circuit can be carried out more quickly than that in the PDSOI-MOSFET according to the first embodiment.

[0145] Moreover, the problem of an isolation edge can be solved effectively in the second embodiment having the T gate electrode 72 in the same manner as that in the first embodiment.

[0146] Accordingly, the PDSOI-MOSFET according to the second embodiment can be used particularly effectively for an I/O circuit, an analog circuit (a PLL, a sense amplifier circuit), a timing circuit, a dynamic circuit and the like in which the fixation of a body potential is greatly required.

[0147] The structure according to the second embodiment is classified into first to fourth modes depending on a junction position of a source-drain region in the same manner as that in the first embodiment.

#### Third Embodiment

[0148] FIG. 10 is a plan view showing a planar structure of a semiconductor device according to a third embodiment of the present invention, FIG. 11 is a sectional view showing a section taken along a line A4-A4 in FIG. 10, and FIG. 12 is a sectional view showing a section taken along a line A5-A5 in FIG. 11.

[0149] As shown in these drawings, a source region according to the third embodiment presents a source-tied structure in which a p<sup>+</sup> region 55 (a semiconductor region for body fixation) is provided in a source region 54 isolated into two portions.

[0150] Moreover, the source region 54, the p<sup>+</sup> region 55 and a drain region 61 are formed to have such depths as to reach a back face of an SOI layer 4 from a surface thereof, respectively.

[0151] A gate oxide film 5 is formed on the SOI layer 4 between the source region 54 ( $p^+$  region 55) and the drain region 61, a gate electrode 7 is formed on the gate oxide film 5, and a side wall 6 is formed on side surfaces of the gate electrode 7.

[0152] Moreover, a body region 10 is isolated by a partial oxide film 31 and a p well region 11 provided thereunder and is formed from the surface of the SOI layer 4 to the back face thereof. The body region 10 is electrically connected to a main part of the body region to be the SOI layer 4 provided under the gate electrode 7 through the p well region 11 provided under the partial oxide film 31.

[0153] In such a source-tied structure in a PDSOI-MOS-FET according to the third embodiment, electric potentials of a source and a body can be fixed simultaneously in a source junction region as shown in FIGS. 10, 11 and 12. More specifically, a part of the source region acts as the p<sup>+</sup> region 55. Therefore, the source region 54 and the p<sup>+</sup> region 55 are set to have the same electric potential so that the body potential can be fixed with a high stability. As a matter of course, the body potential can also be fixed through the body region 10.

[0154] Accordingly, the PDSOI-MOSFET according to the third embodiment having the above-mentioned features can be used particularly effectively for an I/O circuit, an analog circuit (a PLL, a sense amplifier circuit), a timing circuit, a dynamic circuit and the like in which the fixation of the body potential is greatly required.

[0155] Moreover, the structure according to the third embodiment is classified into a first mode to a fourth mode depending on a junction position of a source-drain region in the same manner as that in the first embodiment.

## Fourth Embodiment

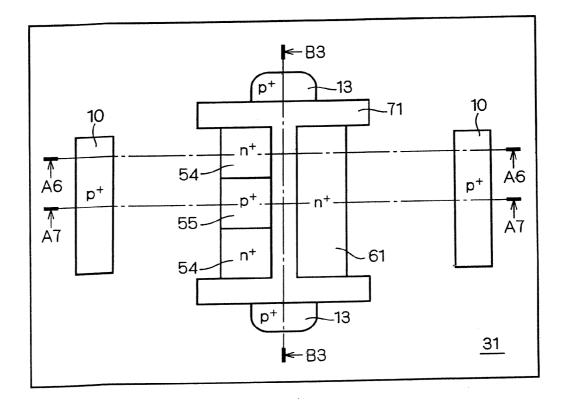

[0156] FIG. 13 is a plan view showing a planar structure of a semiconductor device according to a first mode of a fourth embodiment of the present invention. A section taken along a line A6-A6 in FIG. 13 is the same as the shape shown in FIG. 11, a section taken along a line A7-A7 in FIG. 13 is the same as the shape shown in FIG. 12, and a section taken along a line B3-B3 in FIG. 13 is the same as the shape shown in FIG. 5.

[0157] The structure according to the first mode of the fourth embodiment is obtained by a combination of the H gate electrode 71 according to the first embodiment and the source-tied structure according to the third embodiment, and the respective body potential fixations according to the first and third embodiments (the body potential fixations through the body region 10, the two body regions 13 and the p<sup>+</sup> region 55) are combined so that the body potential fixation can be intensified still more.

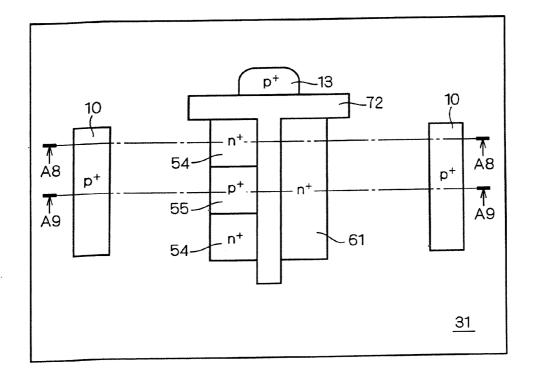

[0158] FIG. 14 is a plan view showing a planar structure of a semiconductor device according to a second mode of a fourth embodiment of the present invention. A section taken along a line A8-A8 in FIG. 14 is the same as the shape shown in FIG. 11 and a section taken along a line A9-A9 in FIG. 14 is the same as the shape shown in FIG. 12.

[0159] The structure according to the second mode of the fourth embodiment is obtained by a combination of the T gate electrode 72 according to the second embodiment and

the source-tied structure according to the third embodiment, and the respective body potential fixations according to the second and third embodiments (the body potential fixations through the body region 10, the body region 13 and the p<sup>+</sup> region 55) are combined so that the body potential fixation can be intensified still more.

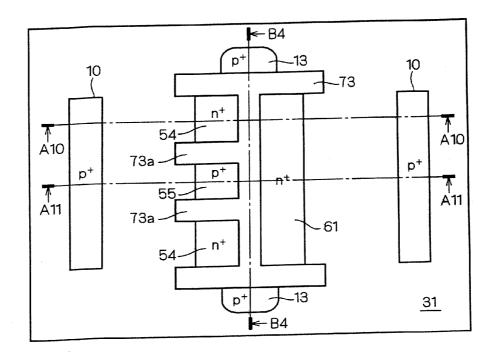

[0160] FIG. 15 is a plan view showing a planar structure of a semiconductor device according to a third mode of a fourth embodiment of the present invention. A section taken along a line A10-A10 in FIG. 15 is the same as the shape shown in FIG. 11, a section taken along a line A11-A11 in FIG. 15 is the same as the shape shown in FIG. 12, and a section taken along a line B4-B4 in FIG. 15 is the same as the shape shown in FIG. 5.

[0161] The structure according to the third mode of the fourth embodiment is obtained by a combination of the special H gate electrode 73 obtained by improving the H gate electrode 71 according to the first embodiment and the source-tied structure according to the third embodiment, and the respective body potential fixations according to the first and third embodiments are combined so that the body potential fixation can be intensified still more.

[0162] In the third mode according to the fourth embodiment, furthermore, a source region 54 and a  $p^+$  region 55 are isolated by an isolating portion 73a in the special H gate electrode 73.

[0163] The gate electrode according to the third embodiment and the first and second modes of the fourth embodiment does not have a portion corresponding to the isolating portion 73a. Therefore, when a silicide region is to be formed on the source region 54, the source region 54 and the p<sup>+</sup> region 55 are short-circuited. For this reason, the actions of the source and the drain cannot be utilized reversely.

[0164] On the other hand, in the third mode according to the fourth embodiment, the isolating portion 73a is present. Therefore, even if the silicide region is formed on the source region 54, the source region 54 and the  $p^+$  region 55 are not short-circuited through the isolating portion 73a. Consequently, the actions of the source and the drain can be utilized reversely. However, a gate capacitance is increased corresponding to the presence of the isolating portion 73a. Thus, an operation speed is lower than that in the first mode. A  $p^-$ body region is formed under the isolating portion 73a through an oxide film.

[0165] Accordingly, the PDSOI-MOSFET according to the first to third modes of the fourth embodiment described above can be used particularly effectively for an I/O circuit, an analog circuit (a PLL, a sense amplifier circuit), a timing circuit, a dynamic circuit and the like in which the fixation of the body potential is greatly required.

[0166] Moreover, the structure according to the fourth embodiment is classified into a first mode to a fourth mode depending on a junction position of a source-drain region in the same manner as that in the first embodiment.

## Fifth Embodiment

[0167] While the semiconductor device has a single PDSOI-MOSFET to be isolated by the partial isolation region in each of the first to fourth embodiments, a semi-

conductor device according to a fifth embodiment has plural kinds of PDSOI-MOSFETs to be isolated by a partial isolation region.

[0168] Type 1: A body potential is fixed with a normal gate structure (see FIGS. 1 and 2).

[0169] Type 2: The body potential is fixed with an H gate electrode structure (the first embodiment).

[0170] Type 3: The body potential is fixed with a T gate electrode structure (the second embodiment).

[0171] Type 4: The body potential is fixed with a source-tied structure (the third embodiment).

[0172] In some cases, the type 4 and the type 2 or the type 3 are used repetitively (the fourth embodiment).

[0173] (Body Floating Type)

[0174] FIG. 16 is a plan view showing a planar structure of a type 5 (No. 1) of the PDSOI-MOSFET. As shown in FIG. 16, a main part of a body region of the PDSOI-MOSFET is also brought into a floating state with such a structure that an electric potential is not fixed through a body terminal even if a body region 10 is provided.

[0175] FIG. 17 is a plan view showing a planar structure of the type 5 (No. 2) of the PDSOI-MOSFET. As shown in FIG. 17, the body region of the PDSOI-MOSFET is brought into the floating state with such a structure that the potential fixation is not carried out through the body terminal even if the body region 10 is provided.

[0176] Thus, such a type as to bring the body region into a floating state is classified as a new kind. A PDSOI-MOSFET of the type 5 can produce effects in that a threshold voltage can be set to be lower than that in the types 1 to 4 in which the body potential is to be fixed.

[0177] In such a body floating type, the normal electrode structure such as a gate electrode 7 is classified into the type 5, and such a type as to bring the body floating with the H gate electrode structure and the T gate electrode structure in place of the gate electrode 7 in the same manner as the types 2 and 3 is classified into types 6 and 7. In the types 6 and 7, it is a matter of course that the body potential fixation is not carried out through a body terminal 28 provided on a body region 13.

[0178] The floating type of the PDSOI-MOSFET will be listed below.

[0179] Type 5: The body floating is brought with the normal gate structure (a linked-body structure in which the body region 15 shown in FIG. 15 is not usually provided).

[0180] Type 6: The body floating is brought with the H gate electrode structure.

[0181] Type 7: The body floating is brought with the T gate electrode structure.

[0182] The body region has a size with a relationship of the type 6>the type 7>the type 5. Therefore, if other conditions are identical, a threshold voltage has a relationship of the type 5<the type 7<the type 6 depending on the easiness to cause carriers to go away to the body region.

[0183] The semiconductor device according to the fifth embodiment is formed in two or more element formation

regions obtained by isolating the PDSOI-MOSFETs of two of the type 1 to the type 7 or more are isolated by a partial isolation region.

[0184] In the semiconductor device according to the fifth embodiment having such a structure, plural kinds of PDSOI-MOSFETs having different transistor characteristics such as a threshold voltage can be provided in a plurality of element formation regions isolated by the partial isolation region through a variation in at least one of the structure of the body region, the structure of the gate electrode and the presence of the body potential fixation.

[0185] As a result, it is possible to constitute a semiconductor integrated circuit having a high function by using any of the PDSOI-MOSFETs which correspond to the transistor characteristic.

[0186] Furthermore, it is possible to set the threshold voltage of the respective PDSOI-MOSFETs to have different values by changing a channel concentration, a thickness of an SOI layer 4, a thickness and a material of a gate oxide film 5 and the like.

[0187] Moreover, it is also possible to set the PDSOI-MOSFETs of two of the types 1 to the type 4 or more to have different threshold voltages by setting respective substrate biases (body potential fixing voltages) to have different values.

#### Sixth Embodiment

[0188] A semiconductor device according to a sixth embodiment is of a partial isolation-complete isolation combination type having a first element formation region isolated by a partial isolation region, and furthermore, a second element formation region isolated by a complete isolation region (an insulating film for isolation reaching a back face (a buried oxide film 2) of an SOI layer 4 from a surface thereof).

[0189] The kind of a PDSOI-MOSFET to be isolated by the complete isolation region will be listed below.

[0190] FIG. 18 is a sectional view showing a sectional structure of a PDSOI-MOSFET of a type A. As shown in FIG. 18, the PDSOI-MOSFET is formed in a region isolated by a complete oxide film 32 to be the complete isolation region provided to reach the back face (the buried oxide film 2) of the SOI layer 4 from the surface thereof. The sectional structure is the same as the planar structure according to the first embodiment shown in FIG. 4 except a partial oxide film 31 is replaced with the complete oxide film 32 and the body region 10 and the body region 25 are not present.

[0191] FIG. 19 is a plan view showing a planar structure of a PDSOI-MOSFET of a type A. A section taken along a line A12-A12 in FIG. 19 corresponds to FIG. 18.

[0192] As shown in FIG. 19, the planar structure is the same as the planar structure according to the first embodiment shown in FIG. 4 except that the partial oxide film 31 is replaced with the complete oxide film 32 and the body region 10 is not present.

[0193] In the PDSOI-MOSFET of the type A, accordingly, body potential fixation is carried out through two body terminals 28 provided on two body regions 13. Consequently, the body resistance value can be reduced and a

variation in a transistor characteristic can be suppressed effectively. Differently from the first embodiment, however, it is impossible to carry out the body potential fixation through the body terminal 25 provided on the body region 10

[0194] FIG. 20 is a plan view showing a planar structure of a PDSOI-MOSFET of a type B. As shown in FIG. 20, the planar structure is the same as the planar structure according to the second embodiment except that the partial oxide film 31 is replaced with the complete oxide film 32 and the body region 10 is not present. Moreover, a section taken along a line A13-A13 in FIG. 20 is the same as the sectional structure shown in FIG. 18.

[0195] In the PDSOI-MOSFET of the type B, accordingly, body potential fixation is carried out through the body terminal 28 provided on the body region 13. Consequently, the body resistance value can be reduced and a variation in a transistor characteristic can be suppressed effectively. Differently from the second embodiment, however, it is impossible to carry out the body potential fixation through the body terminal 25 provided on the body region 10.

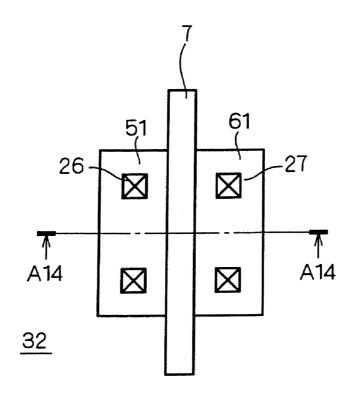

[0196] Referring to a type C, the body potential fixation is carried out with a source-tied structure in the complete isolation region as that in the third embodiment.

[0197] FIG. 21 is a plan view showing a planar structure of a PDSOI-MOSFET of a type D. As shown in FIG. 21, the planar structure is the same as the planar structure of the PDSOI-MOSFET of the type 5 which is partially isolated as shown in FIG. 16 except that the partial oxide film 31 is replaced with the complete oxide film 32. Moreover, a section taken along a line A14-A14 in FIG. 21 is the same as the sectional structure shown in FIG. 18.

[0198] Similarly, PDSOI-MOSFETs of types E and F have the same structures as those of the PDSOI-MOSFETs of the types 6 and 7 except that the partial oxide film 31 is replaced with the complete oxide film 32.

[0199] In the case in which other conditions are identical for the same reasons of the types 5 to 7, a threshold voltage has a relationship of the type D<the type F<the type E.

[0200] As described above, the types A to F are set to a PDSOI-MOSFET to be formed in a second region isolated by a complete isolation region. The above-mentioned types A to F can be summarized as follows.

[0201] Type A: A body potential is fixed with an H gate electrode structure (which is similar to that in the first embodiment, and the body potential fixation is not carried out through the body region 10).

[0202] Type B: The body potential is fixed with a T gate electrode structure (which is similar to that in the second embodiment, and the body potential fixation is not carried out through the body region 10).

[0203] Type C: The body potential is fixed with a sourcetied structure (which is similar to that in the third embodiment, and the body potential fixation is not carried out through a p<sup>+</sup> region 55).

[0204] Type D: The body floating is brought with a normal gate structure.

[0205] Type E: The body floating is brought with the H gate electrode structure.

[0206] Type F: The body floating is brought with the T gate electrode structure.

[0207] The PDSOI-MOSFETs of the types A to F are formed in a second element formation region isolated by a complete isolation region. Therefore, an advantage of latch up free can be obtained.

[0208] By employing the H gate electrode structure and the T gate electrode structure as in the types A and B or the source-tied structure as in the type C, moreover, the body potential can be fixed to suppress a floating-body effect.

[0209] On the other hand, the PDSOI-MOSFET to be formed in the first element formation region isolated by the partial isolation region is classified into the types 1 to 7 described in the fifth embodiment.

[0210] In the case in which other conditions are identical for the threshold voltage of the PDSOI-MOSFET, the following relationship is established: "complete isolation floating structure (type D to type F)partial isolation floating structure (type 5 to type 7)

body potential fixing structure (type A, type B, type 1 to type 4).

[0211] A threshold voltage in the partial isolation floating structure is greater than that in the complete isolation floating structure for the following reason. Since the body region in the partial isolation floating structure is greater than that in the complete isolation floating structure, it is possible to obtain the effect of annihilating a carrier (a hole in an NMOS and an electron in a PMOS) to produce a floating-body effect.

[0212] The semiconductor device according to the sixth embodiment has the partial isolation-complete isolation combination structure in which the PDSOI-MOSFET of one of the types 1 to 7 or more is (are) formed in the first element formation region isolated by the partial isolation region and the PDSOI-MOSFET of one of the types A to F or more is (are) formed in the second element formation region isolated by the complete isolation region.

[0213] The semiconductor device according to the sixth embodiment having such a structure comprises plural kinds of PDSOI-MOSFETs. Therefore, it is possible to provide the PDSOI-MOSFETs applicable to respective uses.

[0214] In plural kinds of PDSOI-MOSFETs, furthermore, it is possible to set the threshold voltage of the respective PDSOI-MOSFETs to have different values by changing a channel concentration, a thickness of an SOI layer 4, a thickness and a material of a gate oxide film 5 and the like.

[0215] Moreover, it is also possible to set the PDSOI-MOSFETs of two of the types 1 to the type 4 or more to have different threshold voltages by setting respective substrate biases (body potential fixing voltages) to have different values.

[0216] FIG. 22 is a view conceptually showing a planar structure of the semiconductor device according to the sixth embodiment. As shown in FIG. 22, a partial isolation region 131 (131A to 131G) isolated by the partial oxide film 31 and a complete isolation region 132 isolated by the complete oxide film 32 are provided together. In the example of FIG. 22, PDSOI-MOSFETs of body potential fixing types 1 to 4

are provided in a partial isolation region 131B, PDSOI-MOSFETs of a type A, a type B and types D to F are provided in a complete isolation region 132, a body floating type PDSOI-MOSFET of a type 5 is provided in a partial isolation region 131D, and body floating type PDSOI-MOSFETs of types 6 and 7 are provided in a partial isolation region 131 E.

## FIRST APPLIED EXAMPLE

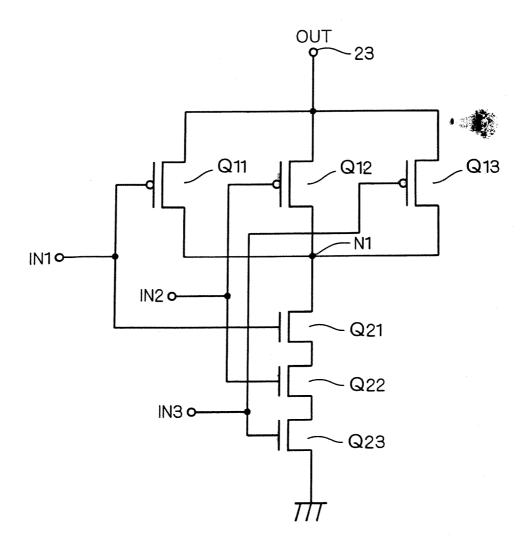

[0217] FIG. 23 is a circuit diagram showing a first applied example of the semiconductor device according to the sixth embodiment. As shown in FIG. 23, a 3-input NAND gate (a semiconductor integrated circuit) is constituted by PMOS transistors Q11 to Q13 and NMOS transistors Q21 to Q23.

[0218] The NMOS transistors Q21 to Q23 are connected in series in this order between a node N1 and a ground, and the PMOS transistors Q11 to Q13 are connected in parallel between an output terminal 33 and the node N1. An input signal IN1 is input to gates of the PMOS transistor Q11 and the NMOS transistor Q21, an input signal IN2 is input to gates of the PMOS transistor Q22, and an input signal IN3 is input to gates of the PMOS transistor Q13 and the NMOS transistor Q13 and the NMOS transistor Q23.

[0219] With such a structure, a complete isolation floating structure (for example, the type D) is used for the NMOS transistor Q21, a linked-body structure (the type 5) having the partial isolation floating structure and having neither the body region nor the body terminal is used for the NMOS transistor Q22, and a partial isolation body potential fixing structure (any of the types 1 to 4) is used for the NMOS transistor Q23.

[0220] Thus, plural kinds of PDSOI-MOSFETs are used properly for the NMOS transistors Q21 to Q23 and are provided over the NMOS transistors Q21 to Q23 such that a substrate bias effect is increased.

[0221] More specifically, it is possible to effectively suppress a reduction in a speed due to the substrate bias effect by using MOS transistors having such a character as to be influenced by the substrate bias effect in order of Q21 to Q23 for the NMOS transistors Q21 to Q23 set in such a situation as to be influenced by the substrate bias effect in order of Q21 to Q23.

#### SECOND APPLIED EXAMPLE

[0222] FIG. 24 is a circuit diagram showing a second applied example of the semiconductor device according to the sixth embodiment. A shown in FIG. 24, a plurality of inverters IV are connected in series to implement an inverter chain (or a ring oscillator).

[0223] Each inverter IV is constituted by a PMOS transistor Q15 and an NMOS transistor Q25. The PMOS transistor Q15 has a drain connected to a node N2 in common and the node N2 is connected to a source voltage VDD through a PMOS transistor Q14, and a control signal S14 is applied to a gate of the PMOS transistor Q14. Moreover, the NMOS transistor Q25 has a source grounded in common.

[0224] In a state in which the PMOS transistor Q14 is OFF, each inverter IV is brought into an inactive state. In a state in which the PMOS transistor Q14 is ON, each inverter IV is brought into an active state.

[0225] With such a structure, a complete isolation floating structure (the types D to F) or a partial isolation linked-body structure (the type 5) are used for the PMOS transistor Q15 and the NMOS transistor Q25 which constitute the inverter IV. These structures can set a threshold voltage to be lower than that in the body potential fixing structure. Therefore, the inverter IV can be operated at a high speed.

[0226] On the other hand, it is possible to increase the threshold voltage by using the partial isolation body potential fixing structure (the types 1 to 4) in the PMOS transistor Q14 for switching control of the inverter IV. Therefore, it is possible to reduce power consumption in the power-OFF state.

[0227] Thus, it is possible to increase the speed and to reduce the power consumption by properly using plural kinds of PDSOI-MOSFETs for the MOS transistors Q15 and Q25 constituting the inverter IV and the PMOS transistor Q14 to change threshold voltages thereof.

[0228] (Supplement)

[0229] FIG. 25 is a sectional view showing a structure of an FD (Fully-Depleted) SOI-MOSFET structure isolated by a complete isolation region. As shown in FIG. 25, an apparent structure is the same as the complete isolation body floating structure shown in FIG. 16.

[0230] The FDSOI-MOSFET is different from the PDSOI-MOSFET in that a depletion layer 94 provided under a gate electrode 7 reaches a buried oxide film 2. Moreover, the FDSOI-MOSFET may have such a structure that an n-region of a source-drain reaches the buried oxide film 2.

[0231] The FDSOI-MOSFET shown in FIG. 25 can implement all the types A to F of the complete isolation structure and all the types 1 to 7 of the partial isolation structure.

[0232] The FDSOI-MOSFET has an advantage that a subthreshold coefficient is good, that is, a switching speed is good. However, there is also a disadvantage that a threshold is varied due to a variation in a thickness of an SOI layer 4. In this respect, the PDSOI-MOSFET has a high controllability of a threshold voltage because the depletion layer provided under the gate does not come in contact with the buried oxide film.

[0233] It is also possible to further diversify the type of transistors to be used by adding the FDSOI-MOSFET shown in FIG. 25 to the type of transistors used in the fifth embodiment or the sixth embodiment.

[0234] While the structure of the NMOS transistor has mainly been described in the first to sixth embodiments, it is apparent that the present invention can also be applied to a PMOS transistor and a CMOS transistor.

## Seventh Embodiment

(First Mode)

[0235] FIG. 26 is a sectional view showing a resistive element of a semiconductor device according to a first mode of the second embodiment of the present invention, and FIG. 27 is a plan view. A section taken along a line C1-C1 in FIG. 27 corresponds to FIG. 26.