(19) 대한민국특허청(KR)

(12) 공개특허공보(A)

(11) 공개번호 10-2012-0112059

(43) 공개일자 2012년10월11일

(51) 국제특허분류(Int. Cl.)

*G09G 5/39* (2006.01)

(21) 출원번호 10-2012-0029400

(22) 출원일자 2012년03월22일

심사청구일자 없음

(30) 우선권주장

JP-P-2011-074348 2011년03월30일 일본(JP)

(71) 출원인

**소니 주식회사**

일본국 도쿄도 미나토구 코난 1-7-1

(72) 발명자

**이시이 미끼오**

일본 도쿄도 미나토구 코난 1-7-1 소니 주식회사

내

**다케 마사히로**

일본 도쿄도 미나토구 코난 1-7-1 소니 주식회사

내

**고스케 쇼지**

일본 도쿄도 미나토구 코난 1-7-1 소니 주식회사

내

(74) 대리인

**박충범, 장수길, 이중희**

전체 청구항 수 : 총 16 항

#### (54) 발명의 명칭 신호 처리 회로, 신호 처리 방법 및 표시 장치

(57) 요약

신호 처리 회로는, 영상 신호를 저장하는 메모리와; 입력 영상 신호에 동기하는 기록 제어 신호와 프레임 식별 정보를 생성하고, 그 기록 제어 신호에 기초하여 상기 입력 영상 신호가 상기 프레임 식별 정보에 대응하도록 상기 입력 영상 신호를 상기 메모리에 저장하는 기록 제어부; 출력 수평 주파수의 타이밍 신호에 기초하여 외부로부터 공급된 수직 동기 신호를 취득하여 판독 제어 신호를 생성하고, 그 판독 제어 신호와 외부로부터 공급된 프레임 식별 정보에 기초하여 그 프레임 식별 정보에 대응하는 영상 신호를 상기 메모리로부터 판독하는 판독 제어부를 포함한다.

## 대 표 도

## 특허청구의 범위

### 청구항 1

신호 처리 회로로서,

영상 신호를 저장하는 메모리;

입력 영상 신호에 동기하는 기록 제어 신호와 프레임 식별 정보를 생성하고, 상기 기록 제어 신호에 기초하여 상기 입력 영상 신호가 상기 프레임 식별 정보에 대응하도록 상기 입력 영상 신호를 상기 메모리에 저장하는 기록 제어부; 및

출력 수평 주파수의 타이밍 신호에 기초하여, 외부로부터 공급된 수직 동기 신호를 취득하여 판독 제어 신호를 생성하고, 상기 판독 제어 신호와 외부로부터 공급된 프레임 식별 정보에 기초하여, 상기 프레임 식별 정보에 대응하는 영상 신호를 상기 메모리로부터 판독하는 판독 제어부

를 포함하는, 신호 처리 회로.

### 청구항 2

제1항에 있어서,

복수의 신호 처리 회로를 동시에 이용하여 영상 표시를 수행하는 경우, 상기 판독 제어부는 상기 판독 제어 신호를 생성하고 상기 판독 제어 신호와 상기 프레임 식별 정보에 기초하여 상기 프레임 식별 정보에 대응하는 상기 영상 신호를 상기 메모리로부터 판독하는, 신호 처리 회로.

### 청구항 3

제1항에 있어서,

상기 판독 제어부는, 상기 출력 수평 주파수의 상기 타이밍 신호에 기초하여 생성된 수직 동기 신호와 외부로부터 공급된 상기 수직 동기 신호 간의 위상차와, 상기 출력 수평 주파수의 상기 타이밍 신호와 외부로부터 공급된 수평 동기 신호 간의 위상차를 검출하여, 상기 위상차들이 미리 결정된 값보다 작도록 상기 출력 수평 주파수의 상기 타이밍 신호와 이 타이밍 신호에 기초하여 생성된 상기 수직 동기 신호의 위상들을 조정하고, 조정 후의 신호를 이용하여 상기 판독 제어 신호를 생성하는, 신호 처리 회로.

### 청구항 4

제1항에 있어서,

상기 입력 영상 신호와 또 다른 신호 처리 회로에 입력되는 입력 영상 신호가 스ueue(skew)를 일으키더라도, 상기 판독 제어 신호와 상기 프레임 식별 정보에 기초하여 상기 프레임 식별 정보에 대응하는 상기 영상 신호를 상기 메모리로부터 판독할 수 있도록, 외부로부터 공급된 동기 신호를 지연시키는 스ueue 보상부(skew compensation unit)를 더 포함하는, 신호 처리 회로.

### 청구항 5

제1항에 있어서,

표시 정지 지시 신호가 공급될 때 입력 래치 신호(latch signal)에 기초하여 상기 표시 정지 지시 신호를 취득하고 취득된 상기 표시 정지 지시 신호를 상기 기록 제어부와 상기 판독 제어부에 출력하는 표시 정지 제어부(display stop control unit)를 더 포함하고,

상기 기록 제어부는 상기 표시 정지 지시 신호에 기초한 표시 정지 기간 동안에 상기 메모리로의 상기 입력 영상 신호의 저장을 정지하며,

상기 판독 제어부는, 상기 표시 정지 지시 신호에 기초한 표시 정지 기간 동안에, 표시 정지 이전에 판독된 상기 프레임 식별 정보에 대응하는 상기 영상 신호를 판독하는, 신호 처리 회로.

**청구항 6**

제5항에 있어서,

상기 표시 정지 제어부는 프레임 단위 또는 복수의 프레임 단위로 상기 입력 래치 신호에 기초하여 상기 표시 정지 지시 신호를 취득하는, 신호 처리 회로.

**청구항 7**

제5항에 있어서,

상기 판독 제어부는 외부로부터 공급된 상기 프레임 식별 정보에 기초하여 상기 프레임 식별 정보에 대응하는 상기 영상 신호를 상기 메모리로부터 판독하고, 판독된 상기 영상 신호를 포착 영상 신호로서 외부에 출력하는, 신호 처리 회로.

**청구항 8**

제5항에 있어서,

상기 기록 제어부는 외부로부터 공급된 상기 프레임 식별 정보에 기초하여 상기 프레임 식별 정보에 대응하는 교체 영상 신호를 상기 메모리에 저장하는, 신호 처리 회로.

**청구항 9**

제8항에 있어서, 상기 판독 제어부는 외부로부터 공급된 상기 프레임 식별 정보에 기초하여 상기 프레임 식별 정보에 대응하여 상기 메모리에 저장된 상기 교체 영상 신호를 판독하는, 신호 처리 회로.

**청구항 10**

제5항에 있어서,

상기 표시 정지 제어부는 프레임 단위 또는 복수의 프레임 단위로 상기 입력 래치 신호에 기초하여 상기 표시 정지 지시 신호를 취득하는, 신호 처리 회로.

**청구항 11**

제1항에 있어서,

상기 메모리는 신호 처리에 이용되는 상기 영상 신호를 저장하는, 신호 처리 회로.

**청구항 12**

신호 처리 방법으로서,

입력 영상 신호에 동기하는 기록 제어 신호와 프레임 식별 정보를 생성하고, 상기 기록 제어 신호에 기초하여 상기 입력 영상 신호가 상기 프레임 식별 정보에 대응하도록 상기 입력 영상 신호를 상기 메모리에 저장하는 단계; 및

출력 수평 주파수의 타이밍 신호에 기초하여, 외부로부터 공급된 수직 동기 신호를 취득하여 판독 제어 신호를 생성하고, 상기 판독 제어 신호와 외부로부터 공급된 프레임 식별 정보에 기초하여, 상기 프레임 식별 정보에 대응하는 영상 신호를 상기 메모리로부터 판독하는 단계

를 포함하는, 신호 처리 방법.

**청구항 13**

표시 장치로서,

한 화면을 구성하는 복수의 표시 영역 각각마다, 대응하는 표시 영역의 영상 신호를 처리하는 신호 처리 회로를 포함하고,

상기 신호 처리 회로들 각각은,

영상 신호를 저장하는 메모리,

입력 영상 신호에 동기하는 기록 제어 신호와 프레임 식별 정보를 생성하고, 상기 기록 제어 신호에 기초하여 상기 입력 영상 신호가 상기 프레임 식별 정보에 대응하도록 상기 입력 영상 신호를 상기 메모리에 저장하는 기록 제어부, 및

출력 수평 주파수의 타이밍 신호에 기초하여, 외부로부터 각 신호 처리 회로에 공통으로 공급된 수직 동기 신호를 취득하여 판독 제어 신호를 생성하고, 상기 판독 제어 신호와 외부로부터 각 신호 처리 회로에 공통으로 공급된 프레임 식별 정보에 기초하여, 상기 프레임 식별 정보에 대응하는 영상 신호를 상기 메모리로부터 판독하는 판독 제어부

를 포함하는, 표시 장치.

#### 청구항 14

제13항에 있어서,

기준 주파수 신호를 생성하는 발진부를 더 포함하고,

상기 발진부는 생성된 상기 기준 주파수 신호를 각 신호 처리 회로에 공급하고,

상기 신호 처리 회로의 판독 제어부는, 상기 출력 수평 주파수의 상기 타이밍 신호에 기초하여 생성된 수직 동기 신호와 외부로부터 공급된 수직 동기 신호 간의 위상차와, 상기 출력 수평 주파수의 상기 타이밍 신호와 외부로부터 공급된 수평 동기 신호 간의 위상차를 검출하여, 상기 위상차들이 미리 결정된 값보다 작도록, 상기 출력 수평 주파수의 상기 타이밍 신호와 이 타이밍 신호에 기초하여 생성된 상기 수직 동기 신호의 위상들을 조정하고, 조정 후의 신호를 이용하여 상기 판독 제어 신호를 생성하는, 표시 장치.

#### 청구항 15

제13항에 있어서,

복수의 상기 신호 처리 회로는, 상기 복수의 신호 처리 회로에 입력되는 상기 입력 영상 신호들이 상기 신호 처리 회로들 간에 스큐를 일으키더라도, 상기 판독 제어 신호와 상기 프레임 식별 정보에 기초하여 상기 프레임 식별 정보에 대응하는 상기 영상 신호가 상기 메모리로부터 판독될 수 있도록, 외부로부터 공급된 동기 신호를 지연시키는 스큐 보상부를 포함하는, 표시 장치.

#### 청구항 16

제13항에 있어서,

복수의 상기 신호 처리 회로는, 표시 정지 지시 신호가 공급될 때 입력 래치 신호에 기초하여 표시 정지 지시 신호를 취득하고 취득된 상기 표시 정지 지시 신호를 상기 기록 제어부와 상기 판독 제어부에 출력하는 표시 정지 제어부를 더 포함하고,

상기 기록 제어부는 상기 표시 정지 지시 신호에 기초한 표시 정지 기간 동안에 상기 메모리로의 상기 입력 영상 신호의 저장을 정지하며,

상기 판독 제어부는, 상기 표시 정지 지시 신호에 기초한 표시 정지 기간 동안에, 표시 정지 이전에 판독된 상기 프레임 식별 정보에 대응하는 상기 영상 신호를 판독하는, 표시 장치.

### 명세서

#### 기술 분야

[0001]

본 개시물은 신호 처리 회로, 신호 처리 방법 및 표시 장치에 관한 것이다. 더 구체적으로는, 본 개시물은 복수의 신호 처리 회로를 이용한 멀티 침 구성으로 고해상도 영상 표시를 수행할 때 낮은 지연 및 회로 크기의 축소를 가능케 하는 신호 처리 회로, 신호 처리 방법 및 표시 장치에 관한 것이다.

#### 배경 기술

[0002]

종래, 고해상도의 영상 표시가 타일링 처리(tiling process)를 이용하여 수행되고 있다. 예를 들어, JP-A-

2001-195053호에 따르면, 표시 영역이 복수의 서브 스크린으로 가상적으로 분할되는 스크린을 갖추고, 각 서브 스크린마다 그래픽 어댑터가 제공되고 있다. 그래픽 어댑터는 2개의 프레임 버퍼를 가진다. 그래픽 어댑터는 하나의 버퍼에 영상 신호를 기록하면서 다른 버퍼에 저장되어 있는 영상 신호를 판독하고, 영상 신호의 판독이 완료된 버퍼에 대해서 다음 프레임의 영상 신호를 기록한다.

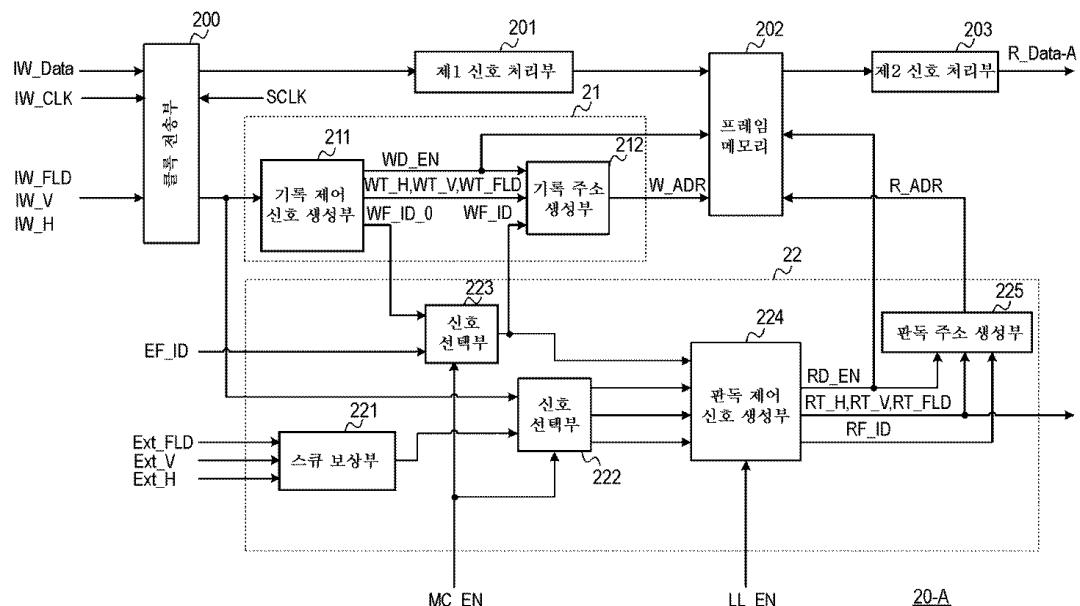

[0003] 도 1은 복수의 신호 처리 회로를 이용한 멀티 칩 구성으로 고해상도의 영상 표시를 수행하는 종래의 표시 장치의 구성을 예시하고 있다. 표시 장치(50)는, 신호 처리 회로(60-A 내지 60-D), 프레임 버퍼(70-A 내지 70-D), 타이밍 제어 회로(T-Con)(75-A 내지 75-D), 프레임 버퍼 제어부(80) 및 발진기(85-A 내지 85-D)를 포함한다.

[0004] 신호 처리 회로(60-A)에는, 영상 신호(IW\_Data), 영상 신호(IW\_Data)에 대응하는 클록 신호(IW\_CLK), 수평 동기 신호(IW\_H), 수직 동기 신호(IW\_V) 및 프레임 신호(IW\_FLD)가 공급되고 있다. 또한, 프레임 신호는, 인터레이스 신호에 기초한 네이티브 표시(native display)를 수행하는 경우에는 제1 프레임과 제2 프레임을 식별하는데 이용되고, 예를 들어 왼쪽 시점 영상(viewpoint image)과 오른쪽 시점 영상 신호를 이용하여 3D 표시를 수행할 때에는 각 시점의 영상 신호를 식별하는데 이용된다. 신호 처리 회로(60-A)는 표시 영역에 대응하는 영상 신호의 신호 처리를 수행한다.

[0005] 또한, 신호 처리 회로(60-A)와 유사한 방식으로, 신호 처리 회로(60-B 내지 60-D)에도, 영상 신호, 수평 동기 신호, 수직 동기 신호, 프레임 신호가 공급되고, 각각의 표시 영역에 대응하는 영상 신호의 신호 처리가 수행된다. 예를 들어, 1개 화면을 상하 좌우측 4개 화면으로 분할하고, 신호 처리 회로(60-A)는, 예를 들어, 좌측 상부의 표시 영역에 대응하는 영상 신호의 신호 처리를 수행한다. 마찬가지로, 신호 처리 회로(60-B)는, 예를 들어, 우측 상부의 표시 영역에 대응하는 영상 신호의 신호 처리를 수행하고, 신호 처리 회로(60-C)는, 예를 들어, 좌측 하부의 표시 영역에 대응하는 영상 신호의 신호 처리를 수행하고, 신호 처리 회로(60-D)는, 예를 들어, 우측 하부의 표시 영역에 대응하는 영상 신호의 신호 처리를 수행한다.

[0006] 신호 처리 회로(60-A)에 의해 처리된 영상 신호는 프레임 버퍼(70-A)에 저장된다. 또한, 신호 처리 회로(60-B 내지 60-D)에 의해 처리된 영상 신호는 프레임 버퍼(70-B 내지 70-D)에 저장된다.

[0007] 프레임 버퍼(70-A 내지 70-D)에 저장된 영상 신호는 동기 판독되어 타이밍 제어 회로(75-A 내지 75-D)에 공급된다. 타이밍 제어 회로(75-A)는 프레임 버퍼(70-A)로부터 판독된 영상 신호를 수신하여, 수신된 신호를 타이밍 신호로서 미리 결정된 포맷으로 표시 장치의 드라이버(미도시)에 출력한다. 마찬가지로, 타이밍 제어 회로(75-B 내지 75-D)는, 프레임 버퍼(70-B 내지 70-D)로부터 판독된 영상 신호를 수신하여, 타이밍 신호로서 미리 결정된 포맷으로 표시 장치의 드라이버(미도시)에 각각 출력한다.

[0008] 프레임 버퍼 제어부(80)는 각 프레임 버퍼(70-A 내지 70-D)의 동작을 제어한다. 프레임 버퍼 제어부(80)는, 신호 처리 회로(60-A)로부터 공급된 동기 신호나 프레임 신호에 기초하여 기록 신호(WCT)를 생성한다. 프레임 버퍼 제어부(80)는, 생성된 기록 신호(WCT)를 프레임 버퍼(70-A)에 공급해 신호 처리 회로(60-A)로부터 출력된 영상 신호를 저장한다. 마찬가지로, 프레임 버퍼 제어부(80)는, 신호 처리 회로(60-B 내지 60-D)로부터 공급된 동기 신호나 프레임 신호에 기초하여 기록 신호를 생성한다. 프레임 버퍼 제어부(80)는, 생성된 기록 신호(WCT)를 프레임 버퍼(70-B 내지 70-D)에 공급해 신호 처리 회로(60-B 내지 60-D)로부터 출력된 영상 신호를 저장한다. 또한, 프레임 버퍼 제어부(80)는, 판독 신호(RCT)를 생성해 각 프레임 버퍼(70-A 내지 70-D)에 공급하고, 저장된 영상 신호를 동기 판독하여 타이밍 제어 회로(75-A 내지 75-D)에 출력한다.

[0009] 발진기(85-A)는 신호 처리 회로(60-A)를 동작시키기 위한 기준 주파수 신호인 시스템 클록 신호를 생성한다. 마찬가지로, 발진기(85-B 내지 85-D)는, 신호 처리 회로(60-B 내지 60-D)를 동작시키기 위한 기준 주파수 신호인 시스템 클록 신호를 생성한다.

## 발명의 내용

### 해결하려는 과제

[0010] 여기서, 멀티 칩 구성으로 고해상도의 영상 표시를 수행하는 경우, 전체로서 한 개 화면 표시가 수행될 뿐만 아니라, 독립된 프레임 주파수의 입력 신호가 각 신호 처리 회로마다 표시될 필요가 있다. 이 때문에, 프레임 버퍼(70-A 내지 70-D)는 대용량을 가져야 할 것이다. 예를 들어, 신호 처리 회로에 입력되는 영상 신호의 프레임 주파수가 48 Hz, 프레임 버퍼로부터 출력되는 영상 신호의 프레임 주파수가 60 Hz인 것으로 가정한다. 이 경우, 프레임 버퍼(70-A 내지 70-D) 각각은 2 프레임의 메모리 용량을 가지며, 한 프레임의 메모리 영역에는 영상 신호가 기록되는 반면 다른 한 프레임의 메모리 영역에는 영상 신호의 판독이 수행된다. 전술된 바와 같이,

프레임 버퍼를 대용량으로 만들었으므로, 독립된 프레임 주파수의 입력 신호를 표시하는 것이 가능해진다. 그러나, 대용량의 프레임 버퍼가 이용되기 때문에, 저비용화나 소규모 회로화가 곤란하다.

[0011] 따라서, 프레임 버퍼를 이용하지 않고 고해상도의 영상 표시를 수행할 수 있는 신호 처리 회로, 신호 처리 방법 및 표시 장치를 제공하는 것이 바람직하다.

### 과제의 해결 수단

[0012] 본 개시물의 실시예는, 영상 신호를 저장하는 메모리와; 입력 영상 신호에 동기하는 기록 제어 신호와 프레임 식별 정보를 생성하고, 기록 제어 신호에 기초하여 입력 영상 신호가 프레임 식별 정보에 대응하도록 입력 영상 신호를 메모리에 저장하는 기록 제어부; 출력 수평 주파수의 타이밍 신호에 기초하여 외부로부터 공급된 수직 동기 신호를 취득하여 판독 제어 신호를 생성하고, 판독 제어 신호와 외부로부터 공급된 프레임 식별 정보에 기초하여 프레임 식별 정보에 대응하는 영상 신호를 메모리로부터 판독하는 판독 제어부를 포함하는 신호 처리 회로에 관한 것이다.

[0013] 본 개시물의 실시예에 따른 신호 처리 회로에서는, 신호 처리에 이용되는 영상 신호가 메모리에 저장된다. 기록 제어부는, 입력 영상 신호에 동기하는 기록 제어 신호와 프레임 식별 정보를 생성하고, 기록 제어 신호에 기초하여 입력 영상 신호가 프레임 식별 정보에 대응하도록 입력 영상 신호를 메모리에 저장한다. 또한, 복수의 신호 처리 회로를 동시에 이용하여 영상 표시를 수행하는 경우, 판독 제어부는 출력 수평 주파수의 타이밍 신호에 기초하여 외부로부터 공급된 수직 동기 신호를 취득하여 판독 제어 신호를 생성한다. 판독 제어 신호의 생성에서, 출력 수평 주파수의 타이밍 신호에 기초하여 생성된 수직 동기 신호와 외부로부터 공급된 수직 동기 신호 간의 위상차와, 출력 수평 주파수의 타이밍 신호와 외부로부터 공급된 수평 동기 신호 간의 위상차를 검출하여, 위상차가 미리 결정된 값보다 작도록, 출력 수평 주파수의 타이밍 신호와 이 타이밍 신호에 기초하여 생성된 수직 동기 신호의 위상을 조정하고, 조정 후의 신호를 이용하여 판독 제어 신호를 생성한다. 판독 제어부는, 생성된 판독 제어 신호와 외부로부터 공급된 프레임 식별 정보에 기초하여 프레임 식별 정보에 대응하는 영상 신호를 메모리로부터 판독한다.

[0014] 스큐 보상부(skew compensation unit)가 설치되어, 입력 영상 신호와 또 다른 신호 처리 회로에 입력되는 입력 영상 신호가 스큐를 일으키더라도, 판독 제어 신호와 프레임 식별 정보에 기초하여 프레임 식별 정보에 대응하는 영상 신호를 메모리로부터 판독할 수 있도록 외부로부터 공급된 동기 신호를 지연시킨다.

[0015] 표시 정지 제어부(display stop control unit)가 설치되어, 표시 정지 지시 신호가 공급될 경우, 입력 래치 신호에 기초하여 표시 정지 지시 신호의 취득이 프레임 단위 또는 복수 프레임 단위로 수행되고, 취득된 표시 정지 지시 신호가 기록 제어부와 판독 제어부에 출력된다. 기록 제어부는, 표시 정지 지시 신호에 기초한 표시 정지 기간 동안에 메모리로의 입력 영상 신호의 저장을 정지한다. 또한, 판독 제어부는, 표시 정지 지시 신호에 기초한 표시 정지 기간 동안 표시 정지 이전에 판독된 영상 신호를 반복하여 판독한다. 또한, 외부로부터 공급된 프레임 식별 정보에 기초하여 프레임 식별 정보에 대응하는 영상 신호가 메모리로부터 판독되고, 판독된 신호는, 예를 들어, 외부 장치에 공급되어 정지 화상을 포착한다. 또한, 외부로부터 공급된 프레임 식별 정보에 기초하여 프레임 식별 정보에 대응하는 교체 영상 신호(replacement image signal)를 메모리에 저장한다. 그 후, 외부로부터 공급된 프레임 식별 정보에 기초하여 프레임 식별 정보에 대응하여 메모리에 저장되어 있는 교체 영상 신호를 판독함으로써, 멀티 칩 구성에서도 정지 화상을 외부 장치로부터 공급된 정지 화상으로 용이하게 교체할 수 있다.

[0016] 본 개시물의 또 다른 실시예는, 입력 영상 신호에 동기하는 기록 제어 신호와 프레임 식별 정보를 생성하고, 기록 제어 신호에 기초하여 입력 영상 신호가 프레임 식별 정보에 대응하도록 입력 영상 신호를 메모리에 저장하는 단계와; 출력 수평 주파수의 타이밍 신호에 기초하여 외부로부터 공급된 수직 동기 신호를 취득하여 판독 제어 신호를 생성하고, 판독 제어 신호와 외부로부터 공급된 프레임 식별 정보에 기초하여 프레임 식별 정보에 대응하는 영상 신호를 메모리로부터 판독하는 단계를 포함하는 신호 처리 방법에 관한 것이다.

[0017] 본 개시물의 역시 또 다른 실시예는, 한 화면을 구성하는 복수의 표시 영역마다, 대응하는 표시 영역에 대한 영상 신호를 처리하는 신호 처리 회로를 포함하는 표시 장치에 관한 것으로, 각 신호 처리 회로는, 영상 신호를 저장하는 메모리와; 입력 영상 신호에 동기하는 기록 제어 신호와 프레임 식별 정보를 생성하고, 기록 제어 신호에 기초하여 입력 영상 신호가 프레임 식별 정보에 대응하도록 입력 영상 신호를 메모리에 저장하는 기록 제어부와; 출력 수평 주파수의 타이밍 신호에 기초하여 외부로부터 각 신호 처리 회로에 공통으로 공급된 수직 동기 신호를 취득하여 판독 제어 신호를 생성하고, 판독 제어 신호와 외부로부터 각 신호 처리 회로에 공통으로

공급된 프레임 식별 정보에 기초하여 프레임 식별 정보에 대응하는 영상 신호를 메모리로부터 판독하는 판독 제어부를 포함한다.

[0018] 본 개시물의 실시예에 따른 표시 장치에서는, 한 화면을 구성하는 복수의 표시 영역마다 신호 처리 회로를 제공하고, 각 신호 처리 회로는 대응하는 표시 영역의 영상 신호를 처리한다. 각 신호 처리 회로에서는, 신호 처리에 이용되는 영상 신호가 메모리에 저장된다. 각 신호 처리 회로의 기록 제어부는, 입력 영상 신호에 동기하는 기록 제어 신호와 프레임 식별 정보를 생성하고, 그 기록 제어 신호에 기초하여 입력 영상 신호가 프레임 식별 정보에 대응하도록 입력 영상 신호를 메모리에 저장한다. 또한, 각 신호 처리 회로를 동시에 이용하여 영상 표시를 수행하는 경우, 각 신호 처리 회로의 기록 제어부는, 출력 수평 주파수의 타이밍 신호에 기초하여 외부로부터 각 신호 처리 회로에 공통으로 공급된 수직 동기 신호를 취득하여 판독 제어 신호를 생성한다. 판독 제어 신호의 생성에서는, 판독 제어부는, 출력 수평 주파수의 타이밍 신호에 기초하여 외부로부터 공급된 수직 동기 신호를 취득하여 판독 제어 신호를 생성한다. 판독 제어부는, 판독 제어 신호와 외부로부터 각 신호 처리 회로에 공통으로 공급된 프레임 식별 정보에 기초하여 프레임 식별 정보에 대응하는 영상 신호를 메모리로부터 판독한다.

[0019] 스큐 보상부가 설치되어, 입력 영상 신호와 또 다른 신호 처리 회로에 입력되는 입력 영상 신호가 스큐를 일으키더라도, 판독 제어 신호와 프레임 식별 정보에 기초하여 프레임 식별 정보에 대응하는 영상 신호를 메모리로부터 판독할 수 있도록 외부로부터 공급된 동기 신호를 지연시킨다.

[0020] 하나의 발진부에서 생성된 시스템 클록 신호가 각각의 신호 처리 회로에 공급되고, 각 신호 처리 회로의 판독 제어부는, 출력 수평 주파수의 타이밍 신호에 기초하여 생성된 수직 동기 신호와 외부로부터 공급된 수직 동기 신호 간의 위상차와, 출력 수평 주파수의 타이밍 신호와 외부로부터 공급된 수평 동기 신호 간의 위상차를 검출하여, 위상차가 미리 결정된 값보다 작도록, 출력 수평 주파수의 타이밍 신호와 이 타이밍 신호에 기초하여 생성된 수직 동기 신호의 위상을 조정하고, 조정 후의 신호를 이용하여 판독 제어 신호를 생성한다.

[0021] 표시 정지 제어부가 설치되어, 표시 정지 지시 신호가 공급될 경우, 입력 래치 신호에 기초하여 표시 정지 지시 신호의 취득이 프레임 단위 또는 복수 프레임 단위로 수행되고, 취득된 표시 정지 지시 신호가 기록 제어부와 판독 제어부에 출력된다. 기록 제어부는, 표시 정지 지시 신호에 기초한 표시 정지 기간 동안에 메모리로의 입력 영상 신호의 저장을 정지한다. 또한, 판독 제어부는, 표시 정지 지시 신호에 기초한 표시 정지 기간 동안 표시 정지 이전에 판독된 영상 신호를 반복하여 판독한다.

[0022] 본 개시물의 실시예들에 따르면, 입력 영상 신호와 동기하는 기록 제어 신호와 프레임 식별 정보가 생성되고, 기록 제어 신호에 기초하여 입력 영상 신호가 프레임 식별 정보에 대응하도록 입력 영상 신호를 메모리에 저장한다. 또한, 출력 수평 주파수의 타이밍 신호에 기초하여 외부로부터 공급된 수직 동기 신호를 취득하여 판독 제어 신호가 생성되고, 이 판독 제어 신호와 외부로부터 공급된 프레임 식별 정보에 기초하여 프레임 식별 정보에 대응하는 영상 신호가 메모리로부터 판독된다. 따라서, 외부로부터 공급된 동기 신호를 복수의 신호 처리 회로에 공급하는 경우, 신호 처리 회로로부터 출력되는 영상 신호들 간의 위상차가 작아진다. 이 때문에, 신호 처리 회로로부터 출력되는 영상 신호의 위상을 라인 버퍼를 이용하여 서로 일치시키는 것이 가능해져, 낮은 지연, 소규모 회로, 낮은 소비 전력 및 저비용으로 고해상도의 영상 표시를 수행할 수 있다.

## 도면의 간단한 설명

[0023] 도 1은 종래의 표시 장치의 구성을 예시하는 도면.

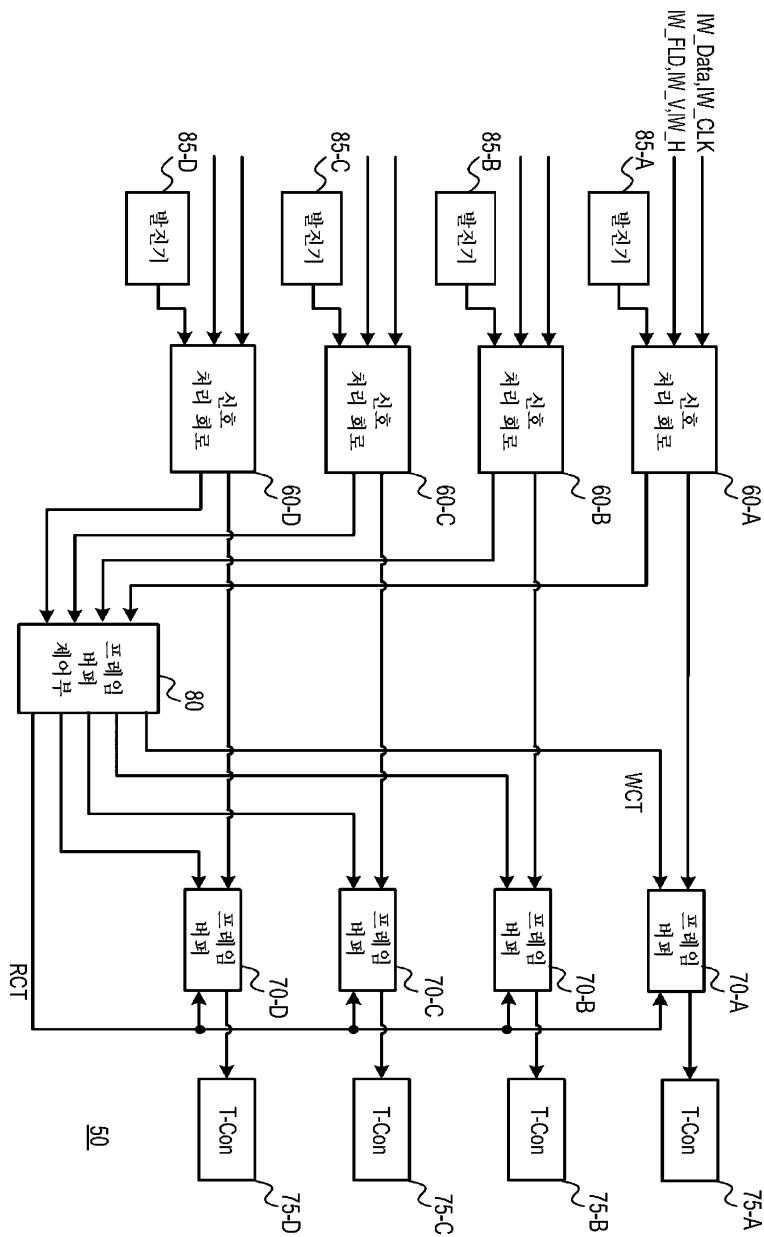

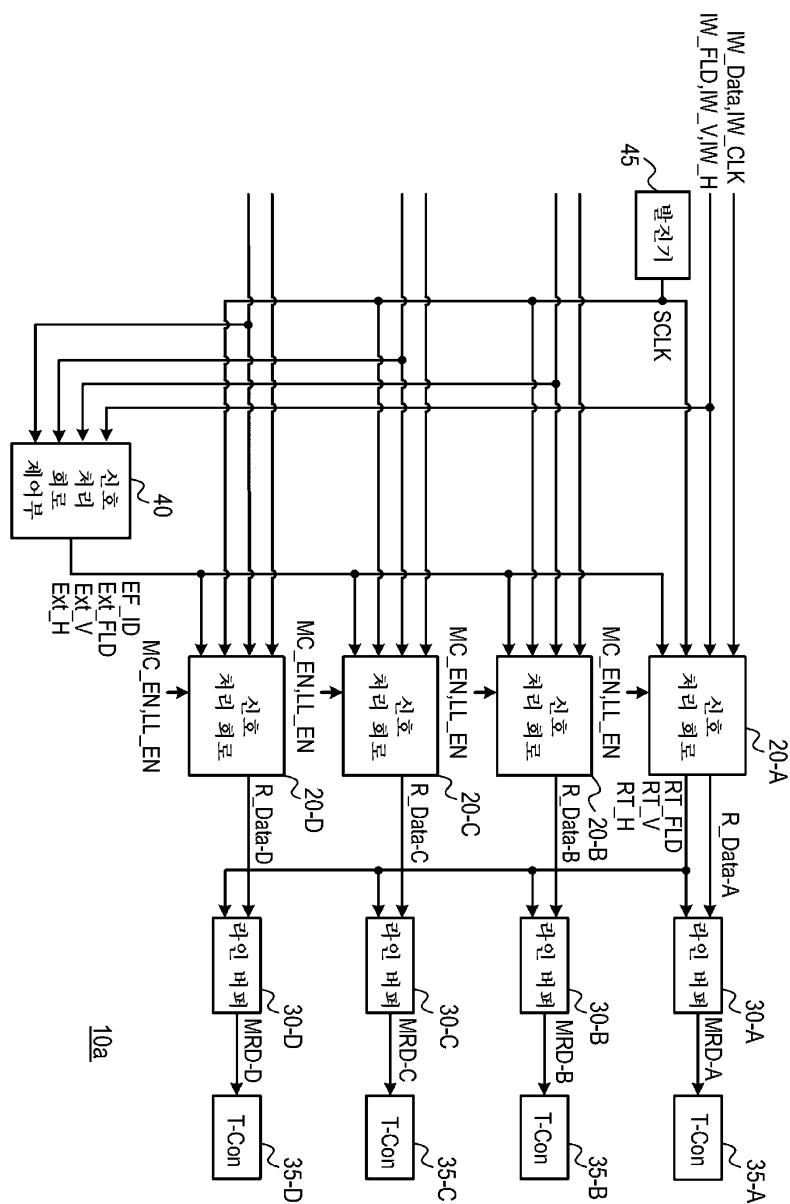

도 2는 제1 실시예의 구성을 나타내는 도면.

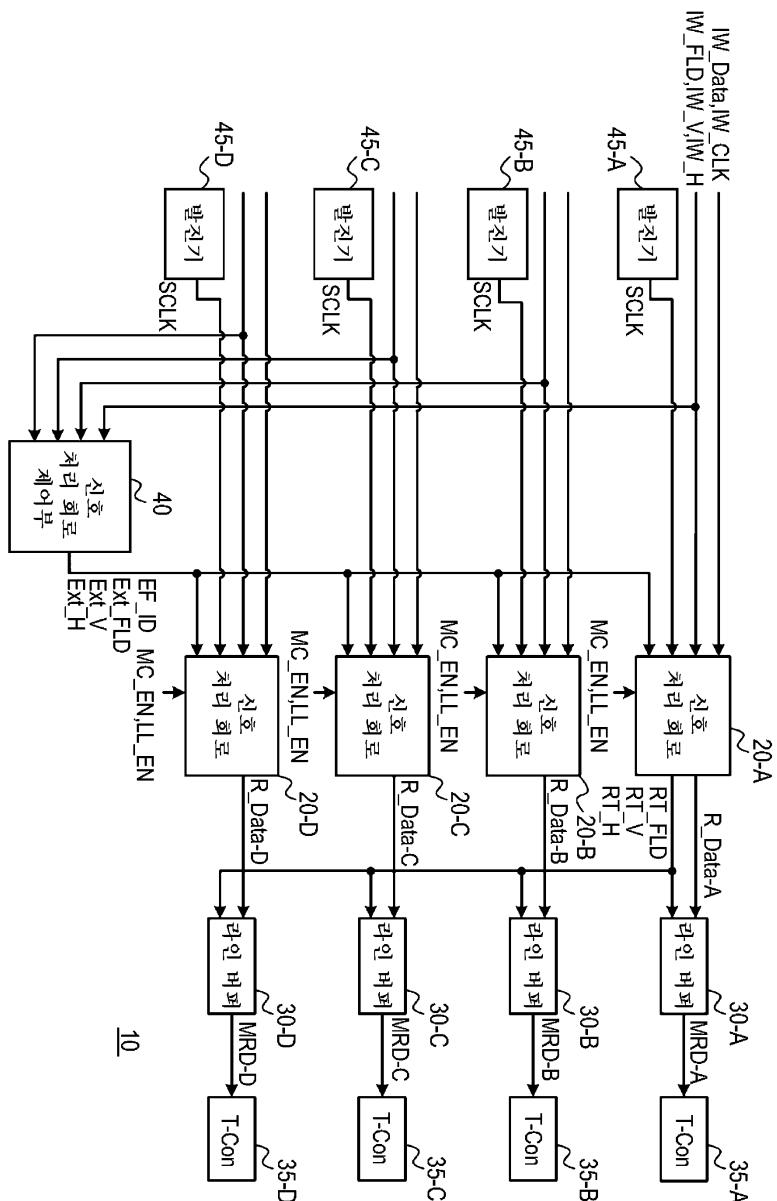

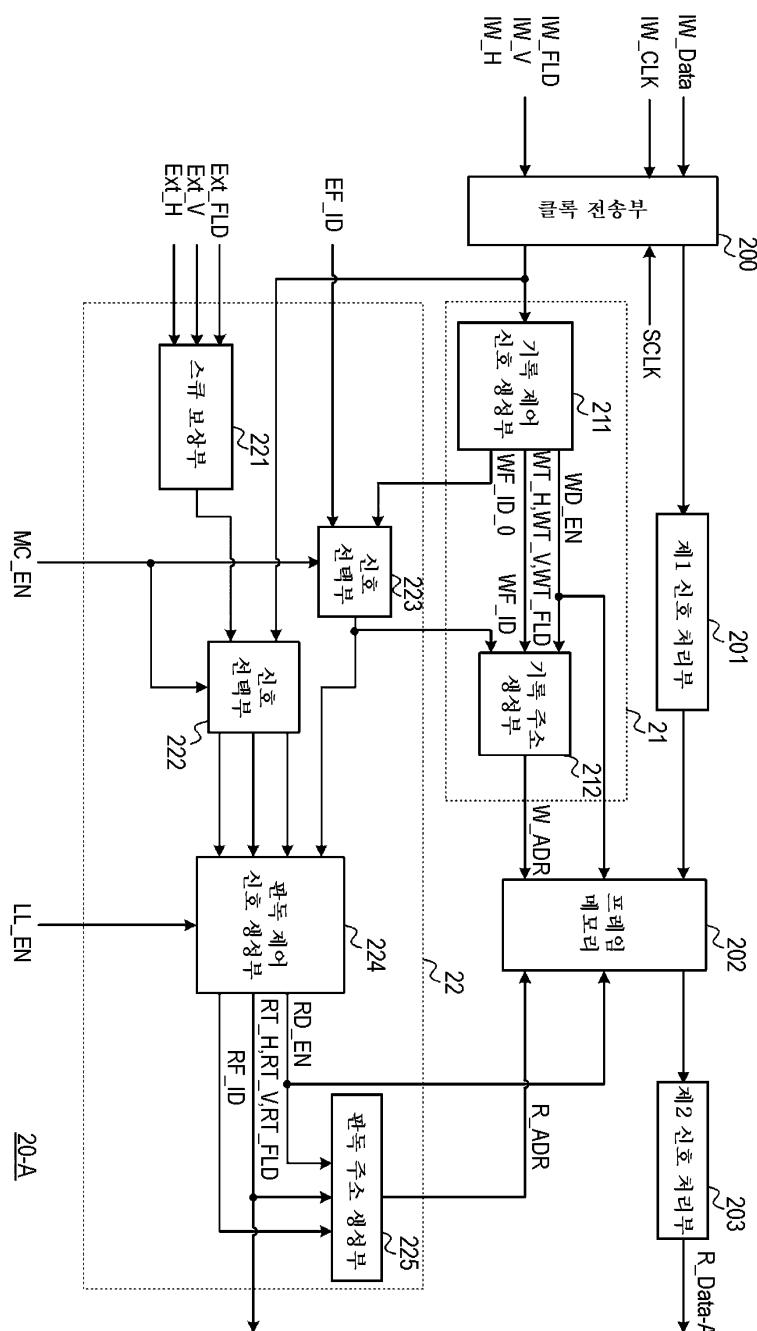

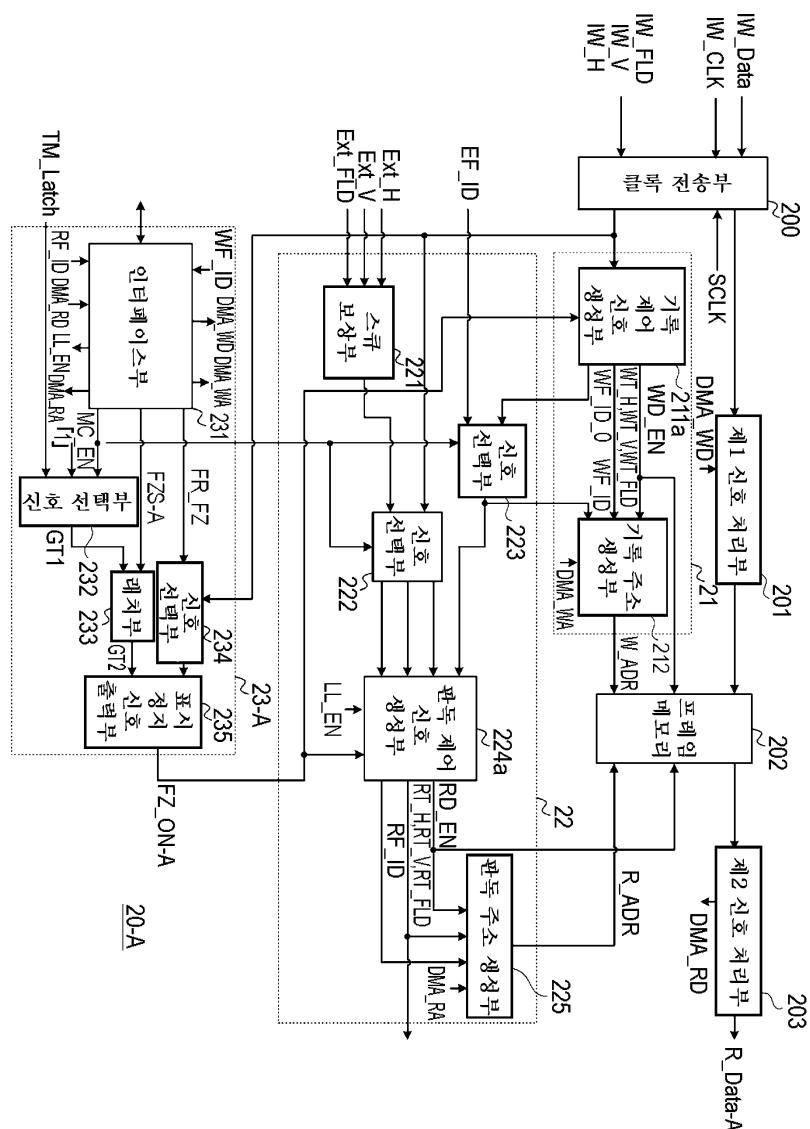

도 3은 신호 처리 회로의 구성을 나타내는 도면.

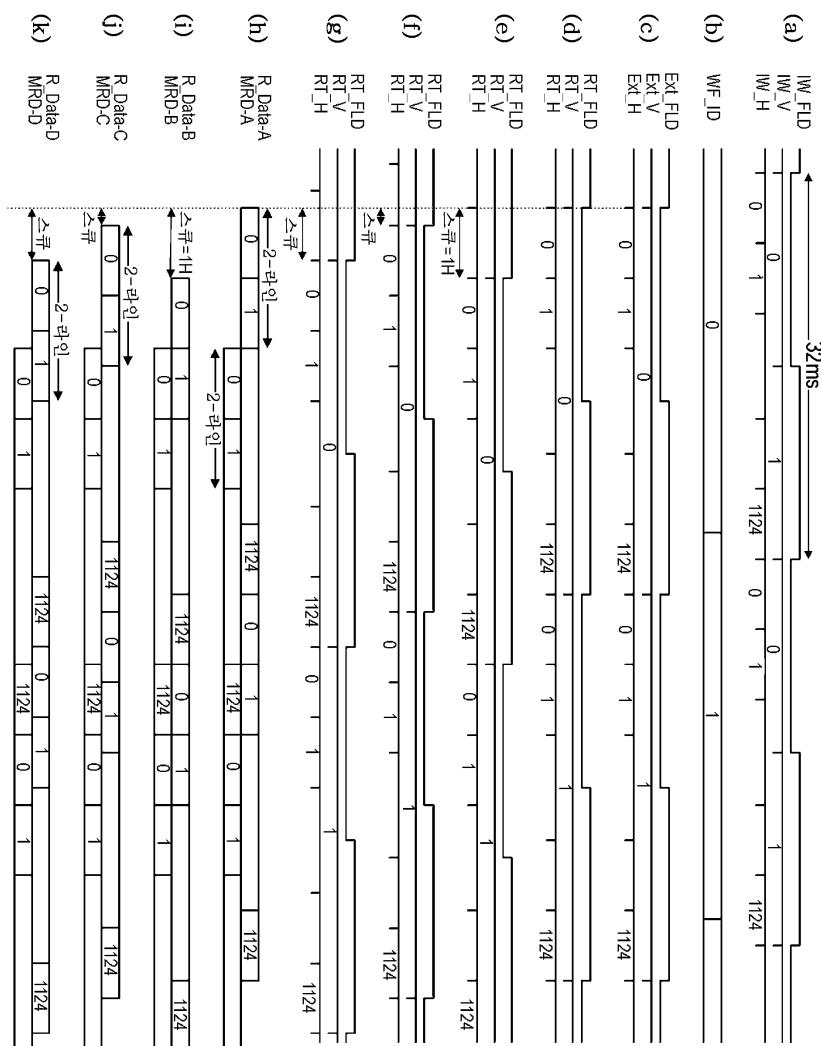

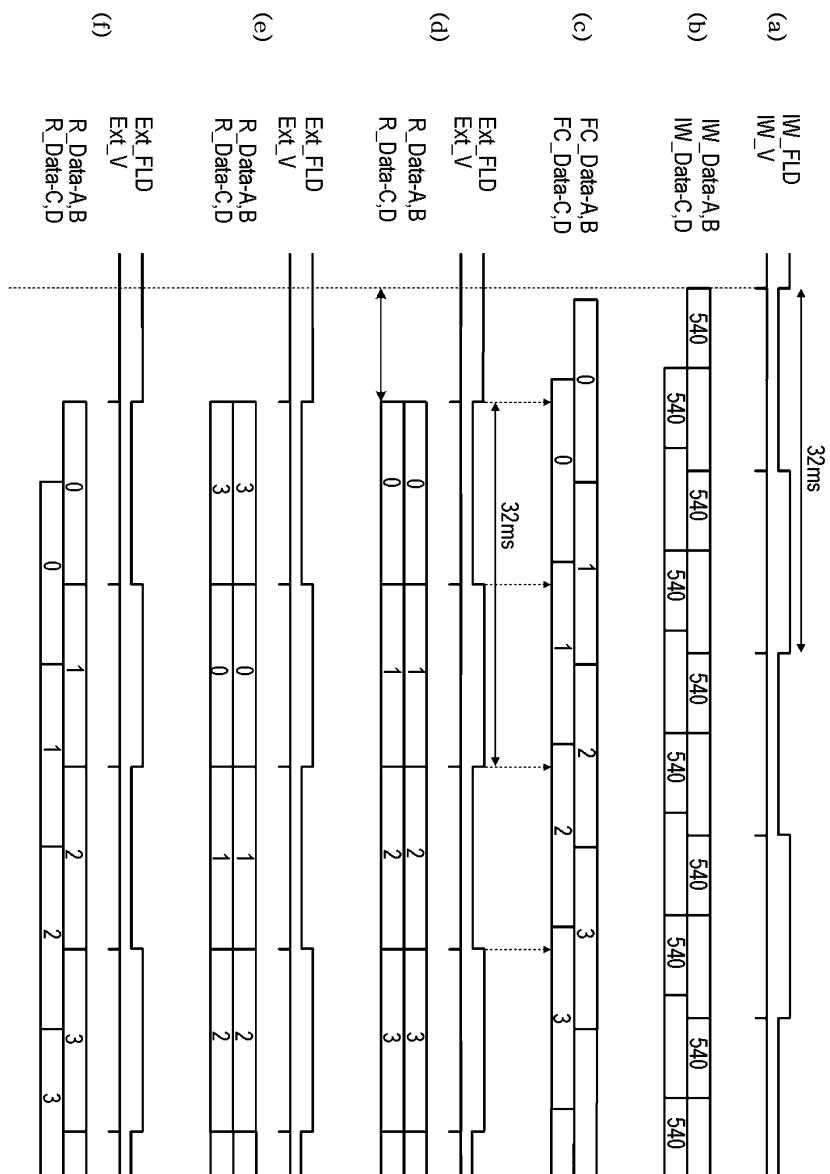

도 4의 (a) 내지 (k)는 신호 처리 회로의 동작을 나타내는 타이밍도.

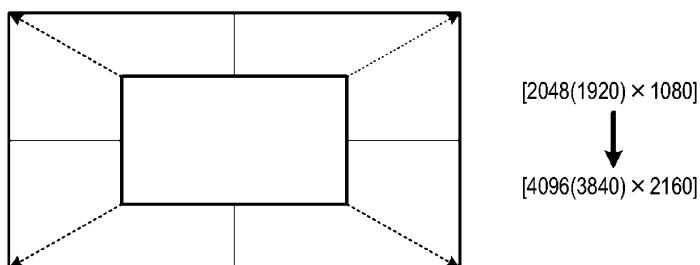

도 5의 (a) 내지 (c)는 표시 모드를 나타내는 도면.

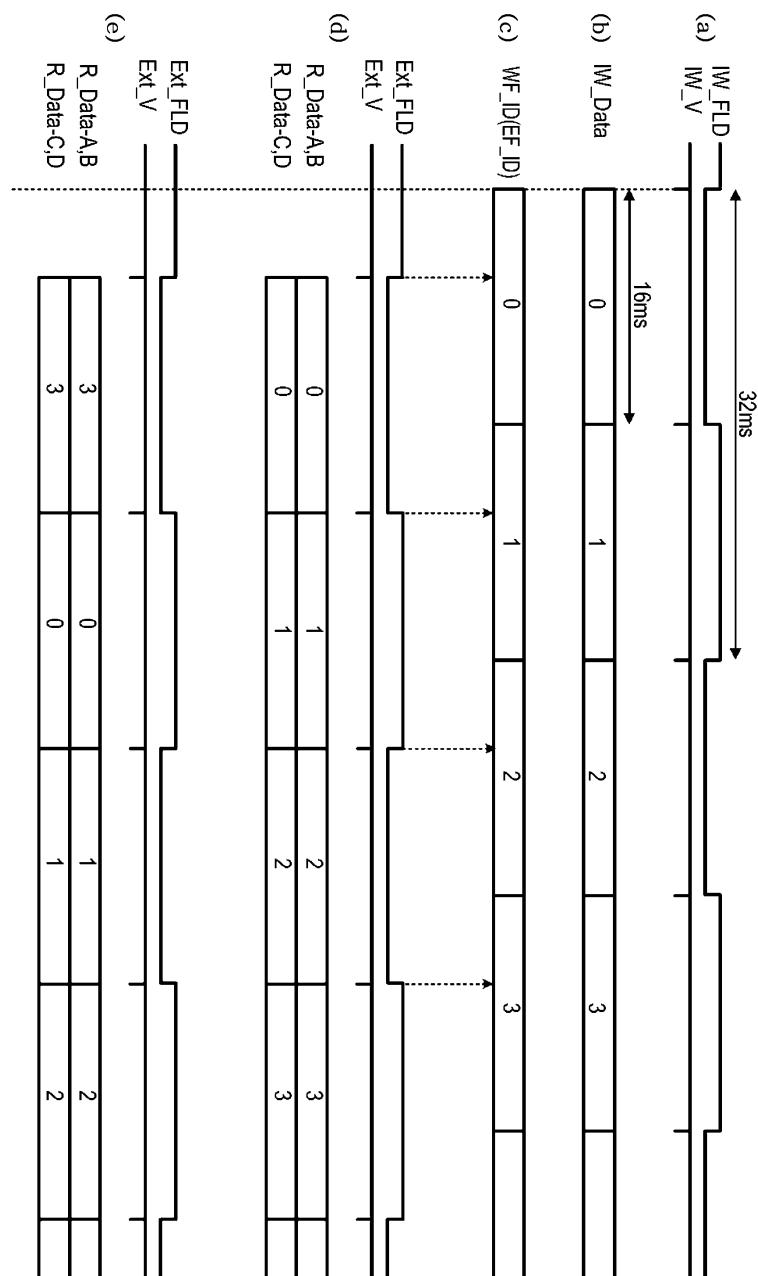

도 6의 (a) 내지 (e)는 제1 표시 모드의 동작을 나타내는 타이밍도.

도 7의 (a) 내지 (f)는 제2 표시 모드의 동작을 나타내는 타이밍도.

도 8은 제2 실시예의 구성을 나타내는 도면.

도 9는 표시 정지 기능을 갖는 신호 처리부의 구성을 나타내는 도면.

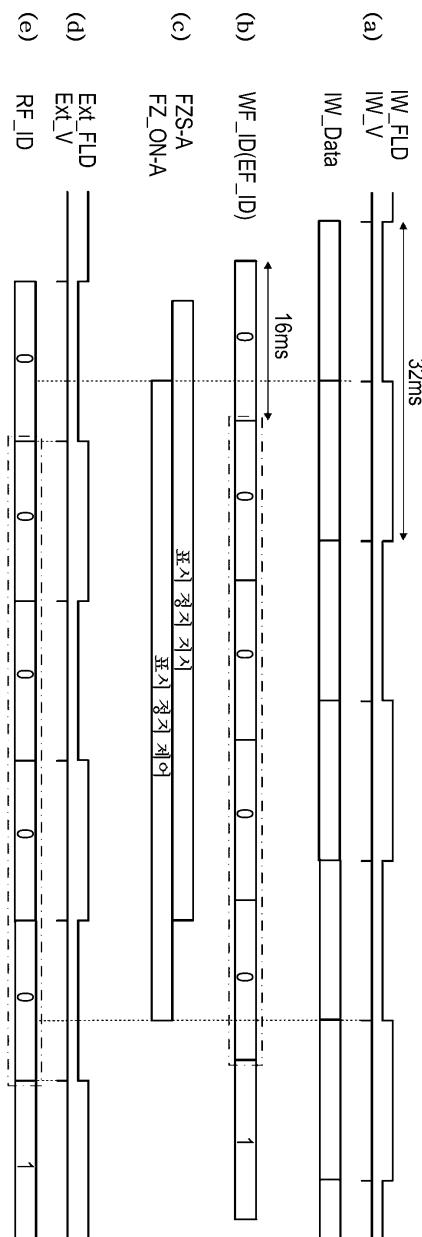

도 10의 (a) 내지 (e)는 표시 정지 기능을 갖는 신호 처리부의 동작을 나타내는 타이밍도.

도 11은 4개의 신호 처리 회로의 표시 정지 제어부를 나타내는 도면.

도 12의 (a) 내지 (d)는 4개의 신호 처리 회로의 동작을 나타내는 타이밍도.

도 13의 (a) 내지 (e)는 필드(프레임) 순차형 영상 신호가 신호 처리 회로에 입력되는 경우의 동작을 나타내는 타이밍도.

도 14의 (a) 내지 (d)는 정지 화상을 취득하는 경우의 타이밍도.

도 15의 (a) 내지 (d)는 정지 화상을 교체하는 경우의 타이밍도.

### 발명을 실시하기 위한 구체적인 내용

[0024] 이하에서, 본 개시물의 실시예가 설명될 것이다. 설명은 다음과 같은 순서로 이루어질 것이다.

[0025] 1. 제1 실시예

[0026] 1-1. 제1 실시예의 구성

[0027] 1-2. 제1 실시예의 동작

[0028] 2. 제2 실시예

[0029] 2-1. 제2 실시예의 구성

[0030] 2-2. 제2 실시예의 동작

[0031] 3. 제3 실시예

[0032] 3-1. 제3 실시예의 구성

[0033] 3-2. 제3 실시예의 동작

[0034] <1. 제1 실시예>

[0035] [1-1. 제1 실시예의 구성]

[0036] 도 2는 제1 실시예의構성을 나타내는 도면이다. 표시 장치(10)는, 신호 처리 회로(20-A 내지 20-D), 라인 버퍼(30-A 내지 30-D), 타이밍 제어 회로(35-A 내지 35-D), 신호 처리 회로 제어부(40) 및 발진기(45-A 내지 45-D)를 포함한다.

[0037] 신호 처리 회로(20-A 내지 20-D)는 각 표시 영역에 대응하는 영상 신호를 처리한다. 예를 들어, 1개 화면을 상하 좌우축에 4개 화면으로 분할하고, 신호 처리 회로(20-A)는, 예를 들어, 좌측 상부의 표시 영역에 대응하는 영상 신호를 처리한다. 마찬가지로, 신호 처리 회로(20-B)는, 예를 들어, 우측 상부의 표시 영역에 대응하는 영상 신호를 처리하고, 신호 처리 회로(20-C)는, 예를 들어, 좌측 하부의 표시 영역에 대응하는 영상 신호를 처리하고, 신호 처리 회로(20-D)는, 예를 들어, 우측 하부의 표시 영역에 대응하는 영상 신호를 처리한다.

[0038] 신호 처리 회로(20-A)에는, 영상 신호(IW\_Data), 영상 신호(IW\_Data)에 대응하는 클록 신호(IW\_CLK), 수평 동기 신호(IW\_H), 수직 동기 신호(IW\_V) 및 프레임 신호(IW\_FLD)가 공급되고 있다. 또한, 신호 처리 회로(20-A)에는, 후술되는 신호 처리 회로 제어부(40)로부터 수평 동기 신호(Ext\_H), 수직 동기 신호(Ext\_V), 프레임 신호(Ext\_FLD) 및 프레임 식별 신호(�F\_ID)가 공급되고 있다. 신호 처리 회로(20-A)에는, 시스템 제어부(미도시)로부터, 멀티 칩 구성에 대응하는 동작이 수행될 것인지 또는 싱글 칩 구성에 대응하는 동작이 수행될 것인지를 나타내는 칩 구성 제어 신호(MC\_EN)가 공급되고 있다. 신호 처리 회로(20-A)는, 클록 신호(IW\_CLK), 수평 동기 신호(IW\_H), 수직 동기 신호(IW\_V) 및 프레임 신호(IW\_FLD)에 기초하여 영상 신호(IW\_Data)를 포착하여 표시 영역에 대응하는 영상 신호를 처리한다. 칩 구성 제어 신호(MC\_EN)에 기초하여 멀티 칩 구성에 대응하는 동작을 수행하는 경우, 신호 처리 회로(20-A)는, 수평 동기 신호(Ext\_H), 수직 동기 신호(Ext\_V) 및 프레임 신호(Ext\_FLD)에 기초하여, 신호 처리 후의 영상 신호(R\_Data-A)를 라인 버퍼(30-A)에 출력한다.

[0039] 신호 처리 회로(20-A)와 마찬가지로, 신호 처리 회로(20-B 내지 20-D)도 각각의 표시 영역에 대응하는 영상 신호를 처리하여, 신호 처리 후의 영상 신호(R\_Data-B 내지 R\_Data-D)를 라인 버퍼(30-B 내지 30-D)에 출력한다. 또한, 칩 구성 제어 신호(MC\_EN)에 따라 싱글 칩 구성에 대응하는 동작을 수행하는 경우, 신호 처리 회로(20-A

내지 20-D)는, 수평 동기 신호(IW\_H), 수직 동기 신호(IW\_V) 및 프레임 신호(IW\_FLD)에 기초하여 영상 신호를 판독한다.

[0040] 라인 베피(30-A 내지 30-D)에 저장된 영상 신호는, 예를 들어, 신호 처리 회로(20-A)로부터 출력된 수평 판독 타이밍 신호(RT\_H), 수직 판독 타이밍 신호(RT\_V) 및 프레임 신호(RT\_FLD)에 기초하여 동기 판독되어, 타이밍 제어 회로(35-A 내지 35-D)에 공급된다.

[0041] 타이밍 제어 회로(35-A)는 라인 베피(30-A)로부터 판독된 영상 신호를 수신하여, 수신된 영상 신호를 타이밍 신호로서 미리 결정된 포맷으로 표시 장치의 드라이버(미도시)에 출력한다. 마찬가지로, 타이밍 제어 회로(35-B 내지 35-D)는, 라인 베피(30-B 내지 30-D)로부터 판독된 영상 신호를 수신하여, 수신된 신호를 타이밍 신호로서 미리 결정된 포맷으로 표시 장치의 드라이버(미도시)에 출력한다.

[0042] 신호 처리 회로를 멀티 칩 구성으로 이용하는 경우에, 신호 처리 회로 제어부(40)는, 수평 동기 신호(Ext\_H)와 수직 동기 신호(Ext\_V)와 프레임 신호(Ext\_FLD)와 프레임 식별 신호(Ext\_ID)를 생성하여, 신호 처리 회로(20-A 내지 20-D)에 공급한다.

[0043] 발진기(45-A)는 신호 처리 회로(20-A)를 동작시키기 위한 기준 주파수 신호인 시스템 클록 신호(SCLK)를 생성한다. 마찬가지로, 발진기(45-B 내지 45-D)는, 신호 처리 회로(20-B 내지 20-D)를 동작시키기 위한 시스템 클록 신호(SCLK)를 생성한다. 또한, 발진기(45-A 내지 45-D)에 의해 생성되는 시스템 클록 신호(SCLK)들은 동일한 주파수를 가진다.

[0044] 도 3은 신호 처리 회로의 구성을 예시한다. 신호 처리 회로(20-A 내지 20-D)는 동일한 구성을 갖는 것으로 간주되며, 이하에서는 신호 처리 회로(20-A)에 대해서만 설명한다.

[0045] 영상 신호(IW\_Data)는 클록 전송부(200)에 공급된다. 클록 전송부(200)는, 클록 신호의 전송을 수행하고, 영상 신호(IW\_Data), 수평 동기 신호(IW\_H), 수직 동기 신호(IW\_V) 및 프레임 신호(IW\_FLD)를, 클록 신호(IW\_CLK)로부터의 시스템 클록 신호(SCLK)와 동기화시킨다. 클록 전송부(200)는, 클록 전송 후의 영상 신호(IW\_Data)를 제1 신호 처리부(201)에 출력한다. 또한, 클록 전송부(200)는, 클록 전송 후의 수평 동기 신호(IW\_H)와 수직 동기 신호(IW\_V)와 프레임 신호(IW\_FLD)를, 기록 제어부(21)의 기록 제어 신호 생성부(211)와 판독 제어부(22)의 신호 선택부(222)에 출력한다.

[0046] 제1 신호 처리부(201)는 시스템 제어부로부터의 지시에 따라 영상 신호(IW\_Data)에 대해서 메모리를 이용하지 않는 다양한 처리, 예를 들어, 흑도 보정 및 색 보정 처리를 수행하고, 처리 후의 영상 신호를 프레임 메모리(202)에 공급한다. 프레임 메모리(202)는, 신호 처리에 이용되는 영상 신호, 예를 들어, 저장된 영상 신호를 이용하여 새로운 영상 신호를 생성하는 신호 처리에 이용되는 영상 신호를 저장하기 위한 것이다. 프레임 메모리(202)는 제2 신호 처리부(203)에 접속되고 있다. 제2 신호 처리부(203)는, 시스템 제어부로부터의 지시에 따라 프레임 메모리(202)에 저장된 영상 신호를 이용하여 다양한 신호 처리, 예를 들어, 인터레이스/프로그래시브 변환, 크기 변환 및 배속 변환 처리를 수행하고, 새로운 영상 신호를 생성한다.

[0047] 기록 제어부(21)의 기록 제어 신호 생성부(211)는 수평 동기 신호(IW\_H)와 수직 동기 신호(IW\_V)와 프레임 신호(IW\_FLD)에 기초하여 수평 기록 타이밍 신호(WT\_H)와 수직 기록 타이밍 신호(WT\_V)를 생성한다. 기록 제어 신호 생성부(211)는, 생성된 신호를, 이 신호에 동기하는 프레임 신호(WT\_FLD)와 함께 기록 주소 생성부(212)에 공급한다. 또한, 기록 제어 신호 생성부(211)는 기록 인에이블 신호(WD\_EN)를 생성하여 프레임 메모리(202)와 기록 주소 생성부(212)에 공급한다. 또한, 기록 제어 신호 생성부(211)는 프레임 신호(IW\_FLD)에 기초하여 기록 프레임 식별 신호(WF\_ID\_0)를 생성하고, 그 기록 프레임 식별 신호(WF\_ID\_0)를 신호 선택부(223)에 공급한다.

[0048] 기록 인에이블 신호(WD\_EN)에 의해 기록 허가가 수행되는 경우, 기록 주소 생성부(212)는, 수평 기록 타이밍 신호(WT\_H)와 수직 기록 타이밍 신호(WT\_V)와 프레임 신호(WT\_FLD)와 신호 선택부(223)으로부터 공급된 프레임 식별 신호(WF\_ID)에 기초하여 기록 주소 신호(W\_ADR)를 생성한다. 기록 주소 생성부(212)는, 생성된 기록 주소 신호(W\_ADR)를 프레임 메모리(202)에 공급하고, 제1 신호 처리부(201)로부터 출력된 영상 신호를 프레임 메모리(202)에 저장한다.

[0049] 복수의 신호 처리 회로를 이용한 멀티 칩 구성으로 영상 표시를 수행하는 경우, 판독 제어부(22)의 스큐 보상부(221)는, 각 신호 처리 회로 간의 입력 영상 신호에서 생성될 수 있는 스큐에 기인한 오동작을 방지한다. 스큐 보상부(221)는, 신호 처리 회로 제어부(40)로부터 공급된 수평 동기 신호(Ext\_H)와 수직 동기 신호(Ext\_V)와 프레임 신호(Ext\_FLD)에 기초하여, 신호 처리 후의 영상 신호가 각 신호 처리 회로로부터 위상차가 저감되어 출력

될 수 있도록 타이밍을 조정한다. 스큐 보상부(221)는 타이밍 조정 후의 각 신호를 신호 선택부(222)에 출력한다. 예를 들어, 만일 각 신호 처리 회로 간에 시스템 클록의 최대 4 클록에 대응하는 스큐가 발생하는 경우, 수평 동기 신호(Ext\_H)가 8개 클록만큼 지연된다. 이 경우, 지연 후의 수평 동기 신호(Ext\_H)의 타이밍은, 최대 4 클록의 스큐가 발생하더라도 동일한 수직 기간 및 필드 기간의 타이밍이 된다. 따라서, 지연된 수평 동기 신호(Ext\_H)의 엣지에서 수직 동기 신호(Ext\_V)와 프레임 신호(Ext\_FLD)의 취득이 수행되고, 취득된 신호들은 새로운 수직 동기 신호(Ext\_V)와 프레임 신호(Ext\_FLD)로서 출력된다. 이렇게 함으로써, 각 신호 처리 회로 간에 스큐가 발생하더라도 스큐의 영향을 방지할 수 있다. 또한, 수평 동기 신호(Ext\_H)의 지연은 발진기(45-A)로부터의 시스템 클록 신호(SCLK)에 기초하여 수행되기 때문에, 신호 처리 회로 제어부(40)가, 수평 동기 신호(Ext\_H), 수직 동기 신호(Ext\_V) 및 프레임 신호(Ext\_FLD)와 함께 클록 신호를 공급할 필요가 없다.

[0050] 칩 구성 제어 신호(MC\_EN)가 멀티 칩 구성에서의 동작을 나타내는 경우, 신호 선택부(222)는 스큐 보상부(221)로부터 공급된 수평 동기 신호(Ext\_H)와 수직 동기 신호(Ext\_V)와 프레임 신호(Ext\_FLD)를 선택하여, 선택된 신호를 판독 제어 신호 생성부(224)에 출력한다. 또한, 싱글 칩 구성에서의 동작이 표시된 경우, 신호 선택부(222)는 영상 신호(IW\_Data)에 대응하는 수평 동기 신호(IW\_H)와 수직 동기 신호(IW\_V)와 프레임 신호(IW\_FLD)를 선택하여 판독 제어 신호 생성부(224)에 출력한다.

[0051] 신호 선택부(223)에는, 기록 제어 신호 생성부(211)로부터의 기록 프레임 식별 신호(WF\_ID\_0)와 신호 처리 회로 제어부(40)로부터 프레임 식별 신호(EF\_ID)가 공급되고 있다. 시스템 제어부로부터 공급된 칩 구성 제어 신호(MC\_EN)에 의해 멀티 칩 구성으로 영상 표시를 수행할 것을 지시받은 경우, 신호 선택부(223)는 신호 처리 회로 제어부(40)로부터 공급된 프레임 식별 신호(EF\_ID)를 선택한다. 또한, 싱글 칩 구성으로 영상 표시를 수행할 것을 지시받은 경우, 신호 선택부(223)는 기록 프레임 식별 신호(WF\_ID\_0)를 선택한다. 신호 선택부(223)는, 선택된 프레임 식별 신호를 프레임 식별 신호(WF\_ID)로서 기록 주소 생성부(212)와 판독 제어 신호 생성부(224)에 출력한다. 또한, 후술되는 제3 표시 모드와 같이 신호 처리 회로(20-A 내지 20-D)에 공급되는 영상 신호들이 서로 비동기이고 또 다른 포맷이나 프레임 레이트에 대응할 수 있다면, 프레임 식별 신호(EF\_ID)는 신호 처리 회로(20-A 내지 20-D)에 공급되는 영상 신호와 동기하는 신호가 아닐 수도 있다. 따라서, 제3 표시 모드에서는 칩 구성 제어 신호(MC\_EN)에 의해 멀티 칩 구성으로 영상 표시를 수행할 것을 지시받은 경우에도, 신호 선택부(223)는 기록 프레임 식별 신호(WF\_ID\_0)를 선택한다.

[0052] 예를 들어, 칩 구성 제어 신호(MC\_EN)  $[1 : 0] = [x : 1]$  인 경우, 신호 선택부(222)는 수평 동기 신호(Ext\_H)와 수직 동기 신호(Ext\_V)와 프레임 신호(Ext\_FLD)를 선택한다. 칩 구성 제어 신호(MC\_EN)  $[1 : 0] = [x : 0]$  인 경우, 신호 선택부(222)는 수평 동기 신호(IW\_H)와 수직 동기 신호(IW\_V)와 프레임 신호(IW\_FLD)를 선택한다. 칩 구성 제어 신호(MC\_EN)  $[1 : 0] = [1 : x]$  인 경우, 신호 선택부(223)는 프레임 식별 신호(EF\_ID)를 선택한다. 칩 구성 제어 신호(MC\_EN)  $[1 : 0] = [0 : x]$  인 경우, 신호 선택부(223)는 기록 프레임 식별 신호(WF\_ID\_0)을 선택한다. 여기서, 멀티 칩 구성을 이용하는 경우, 제1 또는 제2 표시 모드에서는 칩 구성 제어 신호는 MC\_EN  $[1 : 0] = [1 : 1]$  이 되고, 제3 표시 모드에서는 칩 구성 제어 신호는 MC\_EN  $[1 : 0] = [0 : 1]$  이 된다.

[0053] 판독 제어 신호 생성부(224)는, 신호 선택부(222)에 의해 선택된 동기 신호에 기초하여 수평 판독 타이밍 신호(RT\_H)와 수직 판독 타이밍 신호(RT\_V)를 생성한다. 판독 제어 신호 생성부(224)는, 생성된 신호를 이 신호에 동기하는 프레임 신호(RT\_FLD)와 함께 판독 주소 생성부(225)에 공급한다. 또한, 판독 제어 신호 생성부(224)는, 판독 인에이블 신호(RD\_EN)를 생성하여 프레임 메모리(202)와 판독 주소 생성부(225)에 공급한다. 또한, 판독 제어 신호 생성부(224)는, 신호 선택부(223)로부터 공급된 프레임 식별 신호(WF\_ID)에 기초하여 판독 프레임 식별 신호(RF\_ID)를 생성하고, 생성된 판독 프레임 식별 신호(RF\_ID)를 판독 주소 생성부(225)에 공급한다. 또한, 라인 짜터(line jitter) 모드에서, 수평 판독 타이밍 신호(RT\_H)는 프리-런닝(free-running)에 의해 생성된다. 라인 짜터 모드는, 표시 장치가 넓은 주파수 범위의 프레임 레이트 신호를 취급하기 때문에, 출력 수평 주파수의 수평 판독 타이밍 신호(RT\_H)를 셀프-런닝(self-running)시키고 입력 수직 동기 신호를 수평 판독 타이밍 신호(RT\_H)로서 수신함으로써 출력의 수직 판독 타이밍 신호(RT\_V)를 생성하는 모드이다. 따라서, 라인 짜터 모드에서는, 프레임당 라인수가 변동한다. 또한, 판독 제어 신호 생성부(224)는, LowLatency 인에이블 신호(LL\_EN)에 기초하여 LowLatency 모드가 유효인지 아닌지에 따라 판독되는 프레임을 제어한다.

[0054] 영상 신호의 판독이 판독 인에이블 신호(RD\_EN)에 의해 허가되는 경우, 판독 주소 생성부(225)는 수평 판독 타이밍 신호(RT\_H)와 수직 판독 타이밍 신호(RT\_V)와 프레임 신호(RT\_FLD)와 판독 프레임 식별 신호(RF\_ID)에 기초하여, 판독 주소 신호(R\_ADR)를 생성한다. 판독 주소 생성부(225)는, 생성된 판독 주소 신호(R\_ADR)를 프레임 메모리(202)에 공급하고, 프레임 메모리(202)로부터 판독 프레임 식별 신호(RF\_ID)에 대응하는 영상 신호를

판독하여 영상 신호를 출력한다.

[0055] [1-2. 제1 실시예의 동작]

그 다음, 제1 실시예의 동작을 설명한다. 도 4의 (a) 내지 (k)는 신호 처리 회로의 동작을 나타내는 타이밍도이다. 도 4의 (a)는, 각 신호 처리 회로(20-A 내지 20-D)에 입력되는 영상 신호(IW\_Data)의 프레임 신호(IW\_FLD), 수직 동기 신호(IW\_V) 및 수평 동기 신호(IW\_H)를 도시하고 있다. 도 4의 (b)는 프레임 식별 신호(WF\_ID)를 도시하고 있다. 도 4의 (c)는, 신호 처리 회로 제어부(40)로부터 각 신호 처리 회로(20-A 내지 20-D)에 공급되는 수평 동기 신호(Ext\_H)와 수직 동기 신호(Ext\_V)와 프레임 신호(Ext\_FLD)를 나타내고 있다.

[0057] 라인 지터 모드에서, 신호 처리 회로의 판독 제어 신호 생성부(224)는 프리-런닝에 의해 수평 판독 타이밍 신호(RT\_H)를 생성한다. 따라서, 수평 판독 타이밍 신호(RT\_H)는 최대 1라인의 스큐를 생성할 수 있다. 도 4의 (d)는, 신호 처리 회로(20-A)의 판독 제어 신호 생성부(224)에 의해 생성된 프레임 신호(RT\_FLD), 수직 판독 타이밍 신호(RT\_V) 및 수평 판독 타이밍 신호(RT\_H)를 나타내고 있다. 여기서, 신호 처리 회로(20-A)에 의해 생성된 수평 판독 타이밍 신호(RT\_H)의 위상이 신호 처리 회로 제어부(40)로부터 공급된 수평 동기 신호(Ext\_H)의 위상과 일치하는 경우, 신호 처리 회로(20-A)로부터 출력되는 영상 신호는, 신호 처리 회로 제어부(40)로부터 각 신호 처리 회로에 공급되는 신호와 동기된다.

[0058] 도 4의 (e)는, 신호 처리 회로(20-B)의 판독 제어 신호 생성부(224)에 의해 생성된 프레임 신호(RT\_FLD), 수직 판독 타이밍 신호(RT\_V) 및 수평 판독 타이밍 신호(RT\_H)를 나타내고 있다. 만일 신호 처리 회로(20-B)에 의해 생성된 수평 판독 타이밍 신호(RT\_H)가, 공급된 수평 동기 신호(Ext\_H)에 대해서 최대 스큐를 생성한다면, 신호 처리 회로(20-B)로부터 출력되는 영상 신호는, 신호 처리 회로 제어부(40)로부터 공급된 신호에 대해서 1 라인 만큼 지연된 신호가 된다.

[0059] 도 4의 (f)는, 신호 처리 회로(20-C)의 판독 제어 신호 생성부(224)에 의해 생성된 프레임 신호(RT\_FLD), 수직 판독 타이밍 신호(RT\_V) 및 수평 판독 타이밍 신호(RT\_H)를 나타내고 있다. 도 4의 (g)는, 신호 처리 회로(20-D)의 판독 제어 신호 생성부(224)에 의해 생성된 프레임 신호(RT\_FLD), 수직 판독 타이밍 신호(RT\_V) 및 수평 판독 타이밍 신호(RT\_H)를 나타내고 있다. 신호 처리 회로(20-A 및 20-B)로부터 출력되는 영상 신호와 마찬가지로, 신호 처리 회로(20-C 및 20-D)로부터 출력되는 영상 신호도, 생성된 수평 판독 타이밍 신호(RT\_H)와 공급된 수평 동기 신호(Ext\_H)의 스큐에 따라 지연된 신호가 된다.

[0060] 도 4의 (h)는 라인 버퍼(30-A)의 동작을 나타내고 있다. 도 4의 (h)에 도시된 바와 같이, 라인 버퍼(30-A)는, 도 4의 (d)에 나타낸 타이밍에서 판독된 영상 신호(R\_Data-A)를 순차적으로 저장한다. 도 4의 (i)는 라인 버퍼(30-B)의 동작을 나타내고 있다. 도 4의 (i)에 도시된 바와 같이, 라인 버퍼(30-B)는, 도 4의 (e)에 나타낸 타이밍에서 판독된 영상 신호(R\_Data-B)를 순차적으로 저장한다. 도 4의 (j)는 라인 버퍼(30-C)의 동작을 나타내고 있다. 도 4의 (j)에 도시된 바와 같이, 라인 버퍼(30-C)는, 도 4의 (f)에 나타낸 타이밍에서 판독된 영상 신호(R\_Data-C)를 순차적으로 저장한다. 도 4의 (k)는 라인 버퍼(30-B)의 동작을 나타내고 있다. 도 4의 (j)에 도시된 바와 같이, 라인 버퍼(30-D)는, 도 4의 (g)에 나타낸 타이밍에서 판독된 영상 신호(R\_Data-D)를 순차적으로 저장한다.

[0061] 또한, 도 4의 (h) 내지 (k)에 도시된 바와 같이, 라인 버퍼(30-A 내지 30-D)에 저장된 영상 신호는, 신호 처리 회로(20-A)로부터 공급된 타이밍 신호에 기초하여, 영상 신호(R\_Data-A)의 기록으로부터 2 라인에 대응하는 시간의 경과 후에 판독된다. 전술된 바와 같이, 만일 라인 버퍼(30-A 내지 30-D)로부터 영상 신호를 판독한다면, 라인 버퍼(30-A 내지 30-D)로부터 출력된 영상 신호(MRD-A 내지 MRD-D)는 위상-일치 신호가 된다.

[0062] 즉, 2 프레임의 용량을 갖는 프레임 버퍼를 신호 처리 회로마다 설치할 필요가 없고, 2 라인의 용량을 갖는 라인 버퍼를 각 신호 처리 회로마다 설치하는 것만으로, 각 신호 처리 회로로부터 출력되는 영상 신호의 위상을 서로 일치시킬 수 있다. 예를 들어, 신호 처리 회로(20-A)의 출력에 대해서, 또 다른 신호 처리 회로의 출력이 최대 1 라인의 위상이 진행된 스큐를 일으키거나 또 다른 신호 처리 회로의 출력이 최대 1 라인의 위상이 늦은 스큐를 일으키더라도, 각 신호 처리 회로로부터 출력되는 영상 신호의 위상을 서로 일치시킬 수 있다.

[0063] 도 5의 (a) 내지 (c)는 타일링 처리의 예로서 표시 모드를 나타내고 있다. 도 5의 (a)는 제1 표시 모드를 도시하고, 도 5의 (b)는 제2 표시 모드를 도시하고, 도 5의 (c)는 제3 표시 모드를 도시한다.

[0064] 제1 표시 모드는, 1 화면을 각각 세로 방향과 가로 방향으로 2등분하여 4개의 표시 영역([2048(1920) 화소 × 1080 라인] × 4)으로 분할하고, 4K의 영상 신호를 4개의 분할된 영역의 각각의 신호 처리 회로에 공급하는 모드이다. 예를 들어, 좌측 상부의 표시 영역에 대응하는 영상 신호(IW\_Data-u1)는 신호 처리 회로(20-A)에 공급된

다. 또한, 우측 상부의 표시 영역에 대응하는 영상 신호(IW\_Data-ur)는 신호 처리 회로(20-B)에 공급되고, 좌측 하부의 표시 영역에 대응하는 영상 신호(IW\_Data-1l)는 신호 처리 회로(20-C)에 공급되고, 우측 하부의 표시 영역에 대응하는 영상신호(IW\_Data-1r)는 신호 처리 회로(20-D)에 공급된다.

[0065] 제2 표시 모드는, 2K의 영상 신호, 즉 [2048(1920) 화소×1080라인] 의 영상 신호가 각 신호 처리 회로에 공급되고, 표시 영역의 영상 신호를 잘라 확대하는 모드이다. 예를 들어, 신호 처리 회로(20-A)는, 2K의 영상 신호로부터 좌측 상부의 영역의 영상 신호를 잘라 각 종횡을 2배로 함으로써, 4K×2K의 영상 표시에 있어서의 좌측 상부 영역의 영상 표시를 수행한다.

[0066] 제3 표시 모드는, 독립된 2K의 영상 신호, 즉 [2048(1920) 화소×1080 라인] 의 영상 신호가 각 신호 처리 회로에 공급되고, 2K×1K의 표시가 수행되어, 전체적으로 4K×2K의 영상 표시가 수행되는 모드이다. 또한, 영상 신호(IW\_Data-1) 내지 (IW\_Data-4)는 상이한 영상 신호들이며, 각 영상 신호는 서로 비동기이거나 상이한 프레임 주파수를 가질 수도 있다.

[0067] 도 6의 (a) 내지 (e)는 제1 표시 모드의 동작을 나타내는 타이밍도이다. 도 6의 (a)는, 각 신호 처리 회로(20-A 내지 20-D)에 입력되는 영상 신호(IW\_Data)의 프레임 신호(IW\_FLD), 수직 동기 신호(IW\_V) 및 수평 동기 신호(IW\_H)를 나타내고 있다. 도 6의 (b)는 영상 신호(IW\_Data)를 나타내고 있다. 도 6의 (c)는 신호 선택부(223)에 의해 선택된 프레임 식별 신호(WF\_ID)(=EF\_ID)를 나타내고 있다.

[0068] 도 6의 (d)는 LowLatency 모드를 나타내며, 도 6의 (e)는 통상 모드에서의 동작을 나타내고 있다. 신호 처리 회로(20-A 및 20-B)와 신호 처리 회로(20-C 및 20-D)는, 신호 처리 회로 제어부(40)로부터 공급된 동기 신호나 프레임 신호에 기초하여 전술된 바와 같이 영상 신호를 판독한다. 즉, 도 4의 (a) 내지 (k)를 이용하여 설명된 바와 같이, 신호 처리 회로 간에 스큐가 생기는 경우, 신호 처리 회로 제어부(40)는 스큐를 고려하여 최대 스큐량보다 지연된 타이밍에서 수직 동기 신호(Ext\_V)를 수신한다. 각 신호 처리 회로는 스큐 보상 후의 수직 동기 신호(Ext\_V)를 비동기로 수신하고, 수신된 수직 동기 신호(Ext\_V)에 기초하여 수직 판독 타이밍 신호(RT\_V)를 생성하고, 프레임 메모리(202)로부터 영상 신호를 판독한다. 여기서, 도 6의 (d)에 나타낸 LowLatency 모드에서는, 한 프레임의 영상 신호의 기록이 완료되기 전에 기록된 영상 신호가 판독되어, 영상 신호의 지연이 저감된다. 또한, 도 6의 (e)에 나타낸 통상 모드에서는, 한 프레임의 영상 신호의 기록이 완료된 후에 기록된 영상 신호가 판독된다.

[0069] 전술된 바와 같이, 제1 표시 모드의 경우, 신호 처리 회로들 간에 입력 영상 신호의 스큐가 생기더라도, 수직 동기 신호(Ext\_V)와 수평 동기 신호(Ext\_H)와 프레임 신호(Ext\_FLD)의 위상이 조정되어, 조정 후의 동기 신호에 기초하여 영상 신호가 출력된다. 따라서, 스큐의 영향을 받지 않고 각 신호 처리 회로로부터 영상 신호가 출력될 수 있다.

[0070] 도 7의 (a) 내지 (f)는 제2 표시 모드의 동작을 나타내는 타이밍도이다. 도 7의 (a)는 각 신호 처리 회로(20-A 내지 20-D)에 입력되는 영상 신호(IW\_Data)의 프레임 신호(IW\_FLD)와 수직 동기 신호(IW\_V)를 나타내고 있다. 도 7의 (b)는 신호 처리 회로에 입력되는 영상 신호를 나타내고 있다. 신호 처리 회로(20-A 및 20-B)에는, 한 프레임 기간의 최초의 540개 라인의 영상 신호(IW\_Data-A 및 B)가 입력되고, 신호 처리 회로(20-C 및 20-D)에는, 그 후의 540개 라인의 영상 신호(IW\_Data-C 및 D)가 입력된다. 도 7의 (c)는 신호 처리 회로(20-A 및 20-B)에 의해 처리되는 영상 신호와, 신호 처리 회로(20-C 및 20-D)에 의해 처리되는 영상 신호를 나타내고 있다. 제2 표시 모드의 경우, 예를 들어, 540개 라인의 영상 신호를 확대하여 1 프레임의 영상 신호(FC\_Data-A, B, FC\_Data-C, D)로서 처리한다.

[0071] 도 7의 (d)는 LowLatency 모드를 나타내고, 도 7의 (e)는 통상 모드에서의 동작을 나타내고 있다. 신호 처리 회로(20-A 및 20-B)는, 확대된 영상 신호를 프레임 메모리에 기록하고, 신호 처리 회로 제어부(40)로부터 공급된 동기 신호나 프레임 신호에 기초하여 전술된 바와 같이 영상 신호를 판독한다. 마찬가지로, 신호 처리 회로(20-C 및 20-D)는, 확대된 영상 신호를 프레임 메모리에 기록하고, 신호 처리 회로 제어부(40)로부터 공급된 동기 신호나 프레임 신호에 기초하여 전술된 바와 같이 영상 신호를 판독한다. 또한, 신호 처리 회로 제어부(40)로부터 각 신호 처리 회로에 공급되는 신호의 위상이 조정되고, 영상 신호의 판독은, 확대된 영상 신호가 신호 처리 회로(20-C 및 20-D)에서 기록된 후에 신호 처리 회로(20-A 내지 20-D)에서 동기된 방식으로 수행된다. 여기서, LowLatency 모드에서는, 한 프레임의 영상 신호의 기록이 완료되기 전에 기록된 영상 신호가 판독되어, 영상 신호(R\_Data-A, B, R\_Data-C, D)의 지연이 저감된다. 또한, 통상 모드에서는, 한 프레임의 영상 신호의 기록이 완료된 후에 기록된 영상 신호가 판독되어, 영상 신호(R\_Data-A, B, R\_Data-C, D)가 출력된다. 또한, 도 7의 (f)는 종래의 신호 처리 회로로부터 출력되는 영상 신호와, 프레임 메모리로부터 판독된 영상 신호

(R\_Data-A, B, R\_Data-C, D)를 나타내고 있다. 종래의 신호 처리 회로에서는, 영상 신호(R\_Data-C 및 D)가 영상 신호(R\_Data-A 및 B)에 대해 1/2 프레임 기간의 지연을 가진다. 그러나, 본 개시물의 실시예에 따른 신호 처리 회로는, 도 7의 (d) 및 (e)에 나타낸 바와 같이 1/2 프레임 기간의 지연을 일으키지 않고 영상 신호를 출력할 수 있다.

[0072] 전술된 바와 같이, 본 개시물의 실시예에 따른 처리 회로를 이용하면, 제2 표시 모드의 경우, 신호 처리 회로는 1/2 수직 기간의 위상차를 일으키지 않고 영상 신호를 출력할 수 있다. 또한, 1/2 수직 기간의 위상차를 일으키지 않고 영상 신호가 출력될 수 있기 때문에, 전술된 LowLatency 모드의 동작이 가능해진다.

[0073] 또한, 제3 표시 모드의 경우에도, 종래와 같이 2 프레임의 프레임 베퍼를 설치할 필요가 없다. 또한, 신호 처리 회로(20-A 내지 20-D)에 공급되는 각 영상 신호가 서로 비동기이거나 상이한 프레임 주파수를 갖는 경우에도, 프레임 메모리에 기록된 신호는, 신호 처리 회로 제어부(40)로부터 각 신호 처리 회로에 공급되는 신호에 기초하여 동기 판독된다. 따라서, 영상 신호들은 신호 처리 회로(20-A 내지 20-D)로부터 동기 출력될 수 있다.

[0074] <2. 제2 실시예>

[0075] 제1 실시예에서는, 각 신호 처리 회로마다 설치된 발진기로부터 시스템 클록 신호가 공급되고 있다. 그러나, 본 실시예에서는, 각 신호 처리 회로에 공급되는 시스템 클록 신호를 동기화시킴으로써, 신호 처리 회로의 후단에 설치되는 라인 베퍼의 용량이 더욱 저감될 수 있다.

[0076] [2-1. 제2 실시예의 구성]

[0077] 그 다음, 제2 실시예로서 각 신호 처리 회로에 공급되는 시스템 클록 신호들이 서로 동기화되는 경우를 설명한다.

[0078] 도 8은 제2 실시예의 구성을 나타내는 도면이다. 표시 장치(10a)는, 신호 처리 회로(20-A 내지 20-D), 라인 베퍼(30-A 내지 30-D), 타이밍 제어 회로(35-A 내지 35-D), 신호 처리 회로 제어부(40) 및 발진기(45)를 포함한다.

[0079] 신호 처리 회로(20-A 내지 20-D)는 각 표시 영역에 대응하는 영상 신호를 처리한다. 예를 들어, 1개 화면을 상하 좌우측에 4개 화면으로 분할하고, 신호 처리 회로(20-A)는, 예를 들어, 좌측 상부의 표시 영역에 대응하는 영상 신호를 처리한다. 마찬가지로, 신호 처리 회로(20-B)는, 예를 들어, 우측 상부의 표시 영역에 대응하는 영상 신호를 처리하고, 신호 처리 회로(20-C)는, 예를 들어, 좌측 하부의 표시 영역에 대응하는 영상 신호를 처리하고, 신호 처리 회로(20-D)는, 예를 들어, 우측 하부의 표시 영역에 대응하는 영상 신호를 처리한다.

[0080] 신호 처리 회로(20-A)에는, 영상 신호(IW\_Data), 영상 신호(IW\_Data)에 대응하는 클록 신호(IW\_CLK), 수평 동기 신호(IW\_H), 수직 동기 신호(IW\_V) 및 프레임 신호(IW\_FLD)가 공급되고 있다. 또한, 신호 처리 회로(20-A)에는, 후술되는 신호 처리 회로 제어부(40)로부터 수평 동기 신호(Ext\_H), 수직 동기 신호(Ext\_V), 프레임 신호(Ext\_FLD) 및 프레임 식별 신호(EF\_ID)가 공급되고 있다. 신호 처리 회로(20-A)에는, 시스템 제어부(미도시)로부터, 멀티 칩 구성에 대응하는 동작이 수행될 것인지 또는 싱글 칩 구성에 대응하는 동작이 수행될 것인지를 나타내는 칩 구성 제어 신호(MC\_EN)가 공급되고 있다.

[0081] 신호 처리 회로(20-A)는, 클록 신호(IW\_CLK), 수평 동기 신호(IW\_H), 수직 동기 신호(IW\_V) 및 프레임 신호(IW\_FLD)에 기초하여 영상 신호(IW\_Data)를 포착하여 표시 영역에 대응하는 영상 신호를 처리한다. 칩 구성 제어 신호(MC\_EN)에 기초하여 멀티 칩 구성에 대응하는 동작을 수행하는 경우, 신호 처리 회로(20-A)는, 수평 동기 신호(Ext\_H), 수직 동기 신호(Ext\_V) 및 프레임 신호(Ext\_FLD)에 기초하여 처리 후의 영상 신호를 판독하고, 그 판독된 신호를 영상 신호(R\_Data-A)로서 라인 베퍼(30-A)에 출력한다.

[0082] 신호 처리 회로(20-A)와 마찬가지로, 신호 처리 회로(20-B 내지 20-D)도 각각의 표시 영역에 대응하는 영상 신호를 처리하여, 신호 처리 후의 영상 신호를 라인 베퍼(30-B 내지 30-D)에 출력한다. 또한, 칩 구성 제어 신호(MC\_EN)에 따라 싱글 칩 구성에 대응하는 동작을 수행하는 경우, 신호 처리 회로(20-A 내지 20-D)는, 수평 동기 신호(IW\_H), 수직 동기 신호(IW\_V) 및 프레임 신호(IW\_FLD)에 기초하여 영상 신호를 판독한다.

[0083] 라인 베퍼(30-A 내지 30-D)에 저장된 영상 신호는 수평 판독 타이밍 신호(RT\_H), 수직 판독 타이밍 신호(RT\_V) 및 프레임 신호(RT\_FLD)에 기초하여 동기 판독되어, 타이밍 제어 회로(35-A 내지 35-D)에 공급된다. 타이밍 제어 회로(35-A)는 라인 베퍼(30-A)로부터 판독된 영상 신호를 수신하고, 수신된 영상 신호를 타이밍 신호로서 미리 결정된 포맷으로 표시 장치의 드라이버(미도시)에 출력한다. 마찬가지로, 타이밍 제어 회로(35-B 내지 35-

D)는, 라인 버퍼(30-B 내지 30-D)로부터 판독된 영상 신호를 수신하여, 타이밍 신호로서 미리 결정된 포맷으로 표시 장치의 드라이버(미도시)에 출력한다.

[0084] 신호 처리 회로를 멀티 칩 구성으로 이용하는 경우에, 신호 처리 회로 제어부(40)는, 수평 동기 신호(Ext\_H)와 수직 동기 신호(Ext\_V)와 프레임 신호(Ext\_FLD)와 프레임 식별 신호(EF\_ID)를 생성하여, 신호 처리 회로(20-A 내지 20-D)에 공급한다.

[0085] 발진기(45)는 신호 처리 회로(20-A 내지 20-D)를 동작시키기 위한 기준 주파수 신호인 시스템 클록 신호(SCLK)를 생성한다.

[0086] [2-2. 제2 실시예의 동작]

[0087] 상기와 같이 구성된 표시 장치(10a)에서는, 신호 처리 회로는, 셀프-런닝에 의해 생성된 수평 판독 타이밍 신호(RT\_H)와 신호 처리 회로 제어부(40)로부터 공급된 수평 동기 신호(Ext\_H) 간의 위상 관계를 측정한다. 또한, 신호 처리 회로는, 수직 판독 타이밍 신호(RT\_V)와 신호 처리 회로 제어부(40)로부터 공급되는 수직 동기 신호(Ext\_V)의 위상 관계를 측정한다. 예를 들어, 신호 선택부(222)에 위상차 측정 기능을 설치하고, 측정 결과를 판독 제어 신호 생성부(224)에 출력한다.

[0088] 여기서, 시스템 클록 신호(SCLK)가 서로 동기인 경우, 신호 처리 회로 제어부(40)는 시스템 클록 신호에 기초하여 동기 신호 등을 생성하여, 측정된 위상차는 각 신호 처리 회로에 고정된다. 따라서, 판독 제어 신호 생성부(224)는, 위상차가 예를 들어 0.1 H보다 작도록 수평 판독 타이밍 신호(RT\_H) 및 수직 판독 타이밍 신호(RT\_V)를 생성하여, 각 신호 처리 회로로부터 출력되는 영상 신호의 위상차는 0.2 H보다 작게 된다. 따라서, 신호 처리 회로의 후단에 설치되는 라인 버퍼의 메모리 용량이 0.2 H에 상응하더라도, 각 신호 처리 회로로부터 출력되는 영상 신호의 위상은 서로 일치한다. 즉, 신호 처리 회로의 후단에 설치되는 라인 버퍼의 용량이 추가로 저감될 수 있다.

[0089] <3. 제3 실시예>

[0090] 제1 실시예와 제2 실시예에서는, 신호 처리 회로 제어부(40)로부터 공급되는 신호에 기초하여 프레임 메모리(202)로부터 각 신호 처리 회로로 영상 신호를 읽어냄으로써 신호 처리 회로로부터 출력되는 영상 신호들의 위상차가 저감되고 있다. 여기서, 프레임 메모리(202)로의 영상 신호의 기록이나 기록된 영상 신호의 판독을 제어함으로써, 표시 장치가 동영상으로부터 정지 화상으로 표시 영상을 전환함으로써 영상 표시가 정지될 수 있다.

[0091] <3-1. 제3 실시예의 구성>

[0092] 도 9는 제3 실시예에 따른 구성으로서 표시 정지 기능을 갖는 신호 처리 회로의 구성을 나타내는 도면이다. 또한, 도 9에서는, 도 3에 대응하는 부분들에는 동일한 참조 부호가 주어지고 있다. 신호 처리 회로(20-A 내지 20-D)는 동일한 구성을 갖는 것으로 간주되기 때문에, 이하에서는 신호 처리 회로(20-A)에 대해서만 설명한다.

[0093] 영상 신호(IW\_Data)는 클록 전송부(200)에 공급된다. 클록 전송부(200)는, 클록 신호의 전송을 수행하고, 영상 신호(IW\_Data), 수평 동기 신호(IW\_H), 수직 동기 신호(IW\_V) 및 프레임 신호(IW\_FLD)를, 클록 신호(IW\_CLK)로부터의 시스템 클록 신호(SCLK)와 동기화시킨다. 클록 전송부(200)는, 클록 전송 후의 영상 신호(IW\_Data)를 제1 신호 처리부(201)에 출력한다. 또한, 클록 전송부(200)는, 클록 전송 후의 수평 동기 신호(IW\_H)와 수직 동기 신호(IW\_V)와 프레임 신호(IW\_FLD)를, 기록 제어부(21)의 기록 제어 신호 생성부(211a)와 판독 제어부(22)의 신호 선택부(222)와 표시 정지 제어부(23-A)의 신호 선택부(234)에 출력한다.

[0094] 제1 신호 처리부(201)는, 시스템 제어부로부터의 지시에 따라 영상 신호(IW\_Data)에 대해서 메모리를 이용하지 않는 다양한 처리, 예를 들어, 휘도 보정 및 색 보정 처리를 수행하고, 처리 후의 영상 신호를 프레임 메모리(202)에 공급한다. 프레임 메모리(202)는, 저장된 영상 신호를 이용하여 새로운 영상 신호를 생성하는 제2 신호 처리부(203)에 접속되고 있다. 제2 신호 처리부(203)는, 시스템 제어부로부터의 지시에 따라 프레임 메모리(202)에 저장된 영상 신호를 이용하여 다양한 신호 처리, 예를 들어, 인터레이스/프로그래시브 변환, 크기 변환 및 배속 변환 처리를 수행한다.

[0095] 기록 제어부(21)의 기록 제어 신호 생성부(211a)는, 수평 동기 신호(IW\_H)와 수직 동기 신호(IW\_V)와 프레임 신호(IW\_FLD)에 기초하여 수평 기록 타이밍 신호(WT\_H)와 수직 기록 타이밍 신호(WT\_V)를 생성한다. 기록 제어 신호 생성부(211a)는, 생성된 신호를, 이 신호에 동기하는 프레임 신호(WT\_FLD)와 함께 기록 주소 생성부(212)에 공급한다. 또한, 기록 제어 신호 생성부(211a)는 기록 인에이블 신호(WD\_EN)를 생성하여 프레임 메모리

(202)와 기록 주소 생성부(212)에 공급한다. 또한, 기록 제어 신호 생성부(211a)는 프레임 신호(IW\_FLD)에 기초하여 셀프-런닝 방식으로 기록 프레임 식별 신호(WF\_ID\_0)를 생성하고, 그 기록 프레임 식별 신호(WF\_ID\_0)를 신호 선택부(223)에 공급한다. 또한, 표시 정지 신호에 의해 표시를 정지시키기 위한 지시가 후술되는 표시 정지 제어부(23)로부터 제공된 경우, 예를 들어, 기록 제어 신호 생성부(211a)는 기록 프레임 식별 신호(WF\_ID\_0)의 생성을 정지하고, 프레임 메모리(202)로의 영상 신호의 기록을 정지한다.

[0096] 기록 인에이블 신호(WD\_EN)에 의해 기록 허가가 수행되는 경우, 기록 주소 생성부(212)는, 수평 기록 타이밍 신호(WT\_H)와 수직 기록 타이밍 신호(WT\_V)와 프레임 신호(WT\_FLD)와 신호 선택부(223)으로부터 공급된 프레임 식별 신호(WF\_ID)에 기초하여 기록 주소 신호(W adr)를 생성한다. 기록 주소 생성부(212)는, 생성된 기록 주소 신호(W adr)를 프레임 메모리(202)에 공급하고, 제1 신호 처리부(201)로부터 출력된 영상 신호를 프레임 메모리(202)에 저장한다.

[0097] 복수의 신호 처리 회로를 이용한 멀티 칩 구성으로 영상 표시를 수행하는 경우, 판독 제어부(22)의 스큐 보상부(221)는, 각 신호 처리 회로 간의 입력 영상 신호에서 생성될 수 있는 스큐에 기인한 영상을 방지한다. 스큐 보상부(221)는, 신호 처리 회로 제어부(40)로부터 공급된 수평 동기 신호(Ext\_H)와 수직 동기 신호(Ext\_V)와 프레임 신호(Ext\_FLD)에 기초하여, 신호 처리 후의 영상 신호가 위상차가 저감되어 각 신호 처리 회로로부터 출력될 수 있도록 타이밍을 조정한다. 스큐 보상부(221)는 타이밍 조정 후의 각 신호를 신호 선택부(222)에 출력한다. 또한, 수평 동기 신호(Ext\_H)의 지연은 발진기(45-A)로부터의 시스템 클록 신호(SCLK)에 기초하여 수행되며, 신호 처리 회로 제어부(40)가, 수평 동기 신호(Ext\_H), 수직 동기 신호(Ext\_V) 및 프레임 신호(Ext\_FLD)와 함께 클록 신호를 공급할 필요가 없다.

[0098] 칩 구성 제어 신호(MC\_EN)가 멀티 칩 구성에서의 동작을 나타내는 경우, 신호 선택부(222)는 스큐 보상부(221)로부터 공급된 수평 동기 신호(Ext\_H)와 수직 동기 신호(Ext\_V)와 프레임 신호(Ext\_FLD)를 선택하고, 선택된 신호를 판독 제어 신호 생성부(224a)에 출력한다. 또한, 싱글 칩 구성에서의 동작이 표시된 경우, 신호 선택부(222)는 영상 신호(IW\_Data)에 대응하는 수평 동기 신호(IW\_H)와 수직 동기 신호(IW\_V)와 프레임 신호(IW\_FLD)를 선택하여 판독 제어 신호 생성부(224a)에 출력한다.

[0099] 신호 선택부(223)에는, 기록 제어 신호 생성부(211)로부터의 기록 프레임 식별 신호(WF\_ID\_0)와 신호 처리 회로 제어부(40)로부터 프레임 식별 신호(EF\_ID)가 공급된다. 시스템 제어부로부터 공급된 칩 구성 제어 신호(MC\_EN)에 의해 멀티 칩 구성으로 영상 표시를 수행할 것을 지시받은 경우, 신호 선택부(223)는 신호 처리 회로 제어부(40)로부터 공급된 프레임 식별 신호(EF\_ID)를 선택한다. 또한, 싱글 칩 구성으로 영상 표시를 수행할 것을 지시받은 경우, 신호 선택부(223)는 기록 프레임 식별 신호(WF\_ID\_0)를 선택한다. 신호 선택부(223)는 선택된 프레임 식별 신호를 프레임 식별 신호(WF\_ID)로서 기록 주소 생성부(212)와 판독 제어 신호 생성부(224)에 출력한다. 또한, 제3 표시 모드와 같이 신호 처리 회로(20-A 내지 20-D)에 공급되는 영상 신호들이 서로 비동기이고 또 다른 포맷이나 프레임 레이트에 대응할 수 있다면, 프레임 식별 신호(EF\_ID)는 신호 처리 회로(20-A 내지 20-D)에 공급되는 영상 신호와 동기하는 신호가 아닐 수도 있다. 따라서, 제3 표시 모드에서는 칩 구성 제어 신호(MC\_EN)에 의해 멀티칩 구성으로 영상 표시를 수행할 것을 지시받은 경우에도, 신호 선택부(223)는 기록 프레임 식별 신호(WF\_ID\_0)를 선택한다.

[0100] 판독 제어 신호 생성부(224a)는 신호 선택부(222)에 의해 선택된 동기 신호에 기초하여 수평 판독 타이밍 신호(RT\_H)와 수직 판독 타이밍 신호(RT\_V)를 생성한다. 판독 제어 신호 생성부(224a)는 생성된 신호를 이 신호에 동기하는 프레임 신호(RT\_FLD)와 함께 판독 주소 생성부(225)에 공급한다. 또한, 판독 제어 신호 생성부(224a)는 판독 인에이블 신호(RD\_EN)를 생성하여 프레임 메모리(202)와 판독 주소 생성부(225)에 공급한다. 또한, 판독 제어 신호 생성부(224a)는 신호 선택부(223)에 의해 선택된 프레임 식별 신호에 기초하여 판독 프레임 식별 신호(RF\_ID)를 생성하고, 생성된 판독 프레임 식별 신호(RF\_ID)를 판독 주소 생성부(225)에 공급한다. 또한, 라인 저터(line jitter) 모드에서, 수평 판독 타이밍 신호(RT\_H)는 프리-런닝에 의해 생성된다. 또한, 표시 정지 신호에 의해 표시를 정지시키기 위한 지시가 표시 정지 제어부(23)로부터 제공되는 경우, 판독 제어 신호 생성부(224a)는, 예를 들어, 동일한 판독 프레임 식별 신호(RF\_ID)의 생성을 반복함으로써 프레임 메모리(202)로부터 동일한 영상 신호의 판독을 반복한다. 또한, 판독 제어 신호 생성부(224a)는 LowLatency 인에이블 신호(LL\_EN)에 기초하여 LowLatency 모드가 유효인지 아닌지에 따라 판독되는 프레임을 제어한다.

[0101] 영상 신호의 판독이 판독 인에이블 신호(RD\_EN)에 의해 허가되는 경우, 판독 주소 생성부(225)는 수평 판독 타이밍 신호(RT\_H)와 수직 판독 타이밍 신호(RT\_V)와 프레임 신호(RT\_FLD)와 판독 프레임 식별 신호(RF\_ID)에 기초하여 판독 주소 신호(R adr)를 생성한다. 판독 주소 생성부(225)는 생성된 판독 주소 신호(R adr)를 프레임

메모리(202)에 공급하고, 프레임 메모리(202)로부터 판독 프레임 식별 신호(RF\_ID)에 대응하는 영상 신호를 판독하여 영상 신호를 출력한다.

[0102] 표시 정지 제어부(23-A)의 인터페이스(I/F)부(231)는, 시스템 제어부로부터 공급된 지시, 즉, 멀티 칩 구성에 대응하는 동작이 수행될 것인지 또는 싱글 칩 구성에 대응하는 동작이 수행될 것인지에 따라 칩 구성 제어 신호(MC\_EN)를 생성한다. 인터페이스부(231)는 생성된 칩 구성 제어 신호(MC\_EN)를 신호 선택부(222, 223 및 232)와 판독 제어 신호 생성부(224a)에 출력한다. 또한, 인터페이스부(231)는 시스템 제어부로부터의 지시에 따라 표시 정지 지시 신호(FZS)와 정지 설정 신호(FR\_FZ)를 생성한다. 인터페이스부(231)는 표시 정지 지시 신호(FZS)를 래치부(233)에 출력하고, 정지 설정 신호(FR\_FZ)를 신호 선택부(234)에 출력한다.

[0103] 칩 구성 제어 신호(MC\_EN)에 기초하여 멀티 칩 구성으로 영상 표시를 수행하는 경우, 신호 선택부(232)는 래치 신호(TM\_Latch)를 선택하고 그 래치 신호(TM\_Latch)를 게이트 신호(GT1)로서 래치부(233)에 출력한다. 또한, 싱글 칩 구성으로 영상 표시를 수행하는 경우, 신호 선택부(232)는 "1"을 선택하고, 선택된 신호를 게이트 신호(GT1)로서 래치부(233)에 출력한다.

[0104] 래치부(233)는 게이트 신호(GT1)에 기초하여 표시 정지 지시 신호(FZS)를 래치하고, 래치된 신호를 게이트 신호(GT2)로서 표시 정지 신호 출력부(235)에 출력한다.

[0105] 신호 선택부(234)는 정지 설정 신호(FR\_FZ)에 따라 수직 동기 신호(IW\_V) 또는 프레임 신호(IW\_FLD)를 선택하고, 선택된 신호를 표시 정지 신호 출력부(235)에 출력한다. 정지 설정 신호(FR\_FZ)가, 예를 들어, "0"이라고 간주되면, 신호 선택부(234)는 수직 동기 신호(IW\_V)를 선택해 출력한다. 또한, 정지 설정 신호(FR\_FZ)가, 예를 들어, "1"이라고 간주되면, 신호 선택부(234)는 프레임 신호(IW\_FLD)를 선택하여 출력한다.

[0106] 표시 정지 신호 출력부(235)는 신호 선택부(234)에 의해 선택된 신호의 타이밍에서 래치부(233)에 래치되고 있는 표시 정지 지시 신호(FZS)를 래치하고, 래치된 표시 정지 지시 신호(FZS)를 표시 정지 제어 신호(FZ\_ON)로서 기록 제어 신호 생성부(211a)와 판독 제어 신호 생성부(224a)에 출력한다.

[0107] [3-2. 제3 실시예의 동작]

[0108] 도 10의 (a) 내지 도 10의 (e)는 표시 정지 기능을 갖는 신호 처리부의 동작을 나타내는 타이밍도이다. 도 10의 (a)는 영상 신호(IW\_Data), 영상 신호(IW\_Data)의 프레임 신호(IW\_FLD) 및 수직 동기 신호(IW\_V)를 나타내고 있다. 도 10의 (b)는 기록 제어 신호 생성부(211a)에 의해 생성된 프레임 식별 신호(WF\_ID)를 나타내고 있다. 도 10의 (c)는 인터페이스부(231)로부터 출력되는 표시 정지 지시 신호(FZS)와, 표시 정지 신호 출력부(235)로부터 출력되는 표시 정지 제어 신호(FZ\_ON)를 나타내고 있다. 또한, 도 10의 (d)는 신호 처리 회로 제어부(40)로부터 공급된 수직 동기 신호(Ext\_V)와 프레임 신호(Ext\_FLD)를 나타내고 있다. 또한, 도 10의 (e)는, 판독 제어 신호 생성부(224a)에 의해 생성된 판독 프레임 식별 신호(RF\_ID)를 나타내고 있다.

[0109] 표시 정지 지시 신호(FZS)가 래치되어 표시 정지 신호 출력부(235)에 공급되면, 표시 정지 신호 출력부(235)는, 신호 선택부(234)에 의해 선택된 신호에 기초한 타이밍에서 표시 정지 지시 신호(FZS)를 표시 정지 제어 신호(FZ\_ON)로서 출력한다. 예를 들어, 정지 설정 신호(FR\_FZ)가 "0"이라고 간주되면, 신호 선택부(234)는 수직 동기 신호(IW\_V)를 선택하고, 표시 정지 신호 출력부(235)는 수직 동기 신호(IW\_V)에 동기하여 표시 정지 제어 신호(FZ\_ON)를 출력한다. 따라서, 기록 제어 신호 생성부(211a)는 도 10의 (b)의 점선으로 도시된 바와 같이 프레임 식별 신호(WF\_ID)의 갱신을 정지함으로써 프레임 메모리(202)로의 영상 신호의 기록을 정지한다. 또한, 표시 정지 제어 신호(FZ\_ON)의 출력에 의해, 판독 제어 신호 생성부(224a)는 판독 프레임 식별 신호(RF\_ID)의 갱신을 정지하고, 도 10의 (e)의 점선으로 도시된 바와 같이 판독 프레임 식별 신호(RF\_ID)가 "0"인 영상 신호를 반복하여 판독한다.

[0110] 그 후, 표시 정지 지시 신호(FZS)의 출력이 정지되면, 표시 정지 신호 출력부(235)는 수직 동기 신호(IW\_V)에 동기하여 표시 정지 제어 신호(FZ\_ON)의 출력을 정지한다. 또한, 표시 정지 제어 신호(FZ\_ON)의 출력이 정지되면, 기록 제어 신호 생성부(211a)는 프레임 식별 신호(WF\_ID)의 갱신을 재개하고, 판독 제어 신호 생성부(224a)는 판독 프레임 식별 신호(RF\_ID)의 갱신을 재개한다. 따라서, 기록 제어 신호 생성부(211a)는, 도 10의 (b)의 점선으로 표시된 기간 동안에 영상 신호의 기록을 정지하고, 그 후 영상 신호의 기록을 재개한다. 또한, 판독 제어 신호 생성부(224a)는, 도 10의 (e)의 점선으로 표시된 기간 동안에 동일한 판독 프레임 식별 신호(RF\_ID)에 대응하는 영상 신호를 반복하여 판독하고, 그 후, 판독 프레임 식별 신호(RF\_ID)의 순차적 갱신을 통해 새로운 영상 신호의 판독을 재개한다. 즉, 도 10의 (e)의 점선으로 표시된 기간 동안에 정지 화상이 표시될 수 있다.

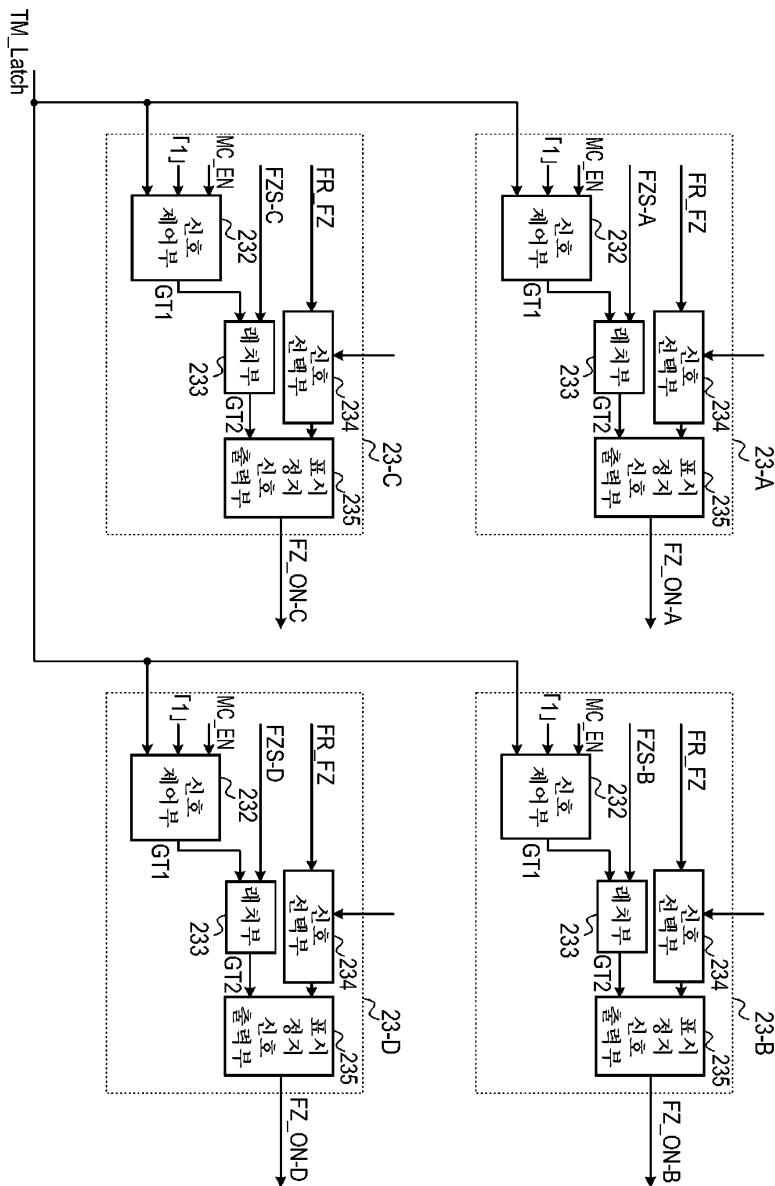

[0111] 도 11은 4개의 신호 처리 회로(20-A 내지 20-D)의 표시 정지 제어부(23-A 내지 23-D)를 나타내고 있다. 표시 정지 제어부(23-A 내지 23-D)에는 래치 신호(TM\_Latch)가 공급되고, 동일한 타이밍에서, 표시 정지 지시 신호(FZS)가 래치부(233)에 래치되어 표시 정지 신호 출력부(235)에 공급된다. 따라서, 신호 처리 회로(20-A 내지 20-D)의 표시 정지 처리가 동기로 수행될 수 있다.

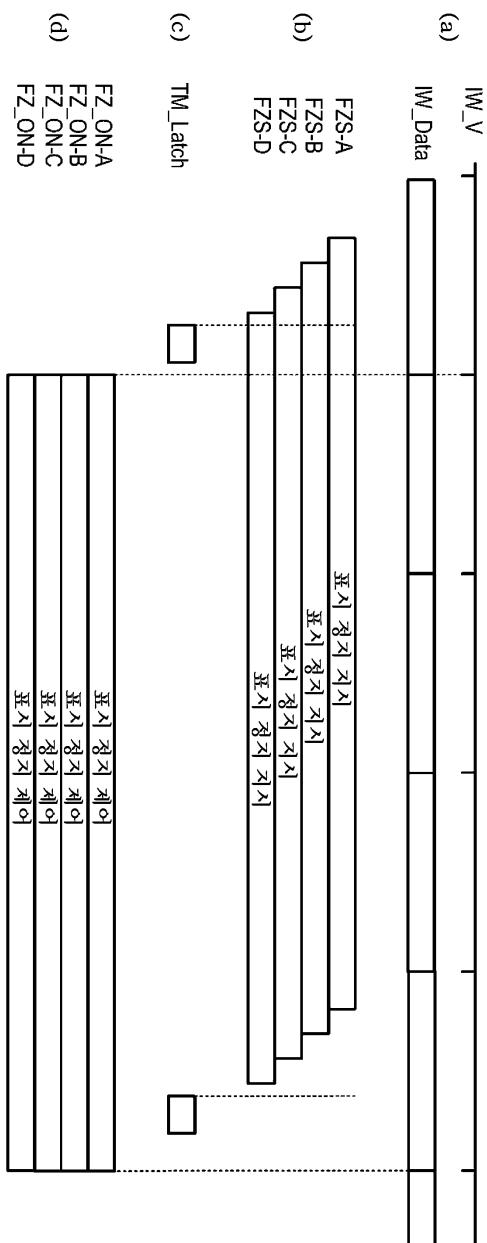

[0112] 도 12의 (a) 내지 (d)는 4개의 신호 처리 회로(20-A 내지 20-D)의 동작을 나타내는 타이밍도이다. 도 12의 (a)는 영상 신호(IW\_Data)와 수직 동기 신호(IW\_V)를 나타내고 있다. 도 12의 (b)는 신호 처리 회로(20-A 내지 20-D)에 공급된 표시 정지 지시 신호(FZS-A 내지 FZS-D)를 도시하고 있다. 표시 정지 지시 신호는 시스템 제어부로부터 비동기로 공급되어 도면에 도시된 바와 같은 위상차를 가진다. 도 12의 (c)는 래치 신호(TM\_Latch)를 나타내고 있으며, 신호 처리 회로(20-A 내지 20-D)는 래치 신호(TM\_Latch)에 의해 표시 정지 지시 신호(FZS)를 래치한다. 도 12의 (d)는 신호 처리 회로(20-A 내지 20-D)에 의해 생성되는 표시 정지 제어 신호(FZ\_ON-A 내지 FZ\_ON-D)를 나타내고 있다. 표시 정지 제어 신호는, 표시 정지 지시 신호, 예를 들어, 수직 동기 신호(IW\_V)에 동기한 타이밍에서 래치되는 신호이며, 각 신호 처리 회로에 의해 생성된 표시 정지 제어 신호(FZ\_ON-A 내지 FZ\_ON-D)는 도면에 도시된 바와 같은 동기 신호가 된다.

[0113] 따라서, 멀티 칩 구성으로 고해상도 표시를 수행하는 경우, 복수의 신호 처리 회로는 동기화를 통해 정지 화상 표시로 전환된다. 따라서, 정지 화상 신호가 표시 장치에 입력되지 않아도, 각 신호 처리 회로에 표시 정지 지시 신호를 공급한 후 래치 신호(TM\_Latch)를 공급함으로써 동기된 타이밍에서 각 영역마다 정지 화상이 표시될 수 있다. 또한, 표시 정지 지시 신호의 완료 후에 래치 신호(TM\_Latch)를 공급함으로써, 정지 화상 표시가 동영상 표시로 전환될 수 있다.

[0114] 또한, 정지 화상 표시는 다시점 영상에도 적용가능하다. 도 13의 (a) 내지 (e)는, 예를 들어, 필드(프레임) 순차형 영상 신호가 신호 처리 회로에 입력되는 경우의 동작을 나타내는 타이밍도이다.

[0115] 도 13의 (a)는 영상 신호(IW\_Data), 영상 신호(IW\_Data)의 프레임 신호(IW\_FLD) 및 수직 동기 신호(IW\_V)를 나타내고 있다. 도 13의 (b)는 기록 제어 신호 생성부(211a)에 의해 생성된 프레임 식별 신호(WF\_ID)를 나타내고 있다. 도 13의 (c)는 인터페이스부(231)로부터 출력되는 표시 정지 지시 신호(FZS)와, 표시 정지 신호 출력부(235)로부터 출력되는 표시 정지 제어 신호(FZ\_ON)를 나타내고 있다. 또한, 도 13의 (d)는 신호 처리 회로 제어부(40)로부터 공급된 수직 동기 신호(Ext\_V)와 프레임 신호(Ext\_FLD)를 나타내고 있다. 또한, 도 13의 (e)는 판독 제어 신호 생성부(224a)에 의해 생성된 판독 프레임 식별 신호(RF\_ID)를 나타내고 있다.

[0116] 표시 정지 지시 신호(FZS)가 래치되어 표시 정지 신호 출력부(235)에 공급되면, 표시 정지 신호 출력부(235)는 신호 선택부(234)에 의해 선택된 신호에 기초한 타이밍에서 표시 정지 지시 신호(FZS)를 표시 정지 제어 신호(FZ\_ON)로서 출력한다. 여기서, 다시점 영상으로 정지 화상 표시를 수행하는 경우, 예를 들어, 정지 설정 신호(FR\_FZ)는 "1"이라고 간주된다. 이 경우, 신호 선택부(234)는 프레임 신호(IW\_FLD)를 선택하고, 표시 정지 신호 출력부(235)는 프레임 신호(IW\_FLD)에 동기하여 표시 정지 제어 신호(FZ\_ON)를 출력한다. 따라서, 기록 제어 신호 생성부(211a)는 도 13의 (b)의 점선으로 도시된 바와 같이 프레임 식별 신호(WF\_ID)의 갱신을 정지함으로써 프레임 메모리(202)로의 영상 신호의 기록을 정지한다. 또한, 표시 정지 제어 신호(FZ\_ON)의 출력에 의해, 판독 제어 신호 생성부(224a)는 판독 프레임 식별 신호(RF\_ID)의 갱신을 정지하고, 도 13의 (e)의 점선으로 도시된 바와 같이 판독 프레임 식별 신호(RF\_ID)가 "0"과 "1"인 영상 신호를 반복하여 판독한다.

[0117] 그 후, 만일 표시 정지 지시 신호(FZS)의 출력이 정지되면, 표시 정지 신호 출력부(235)는 수직 동기 신호(IW\_V)에 동기하여 표시 정지 제어 신호(FZ\_ON)의 출력을 정지한다. 또한, 표시 정지 제어 신호(FZ\_ON)의 출력이 정지되면, 기록 제어 신호 생성부(211a)는 프레임 식별 신호(WF\_ID)의 갱신을 재개하고, 판독 제어 신호 생성부(224a)는 판독 프레임 식별 신호(RF\_ID)의 갱신을 재개한다. 따라서, 기록 제어 신호 생성부(211a)는 도 13의 (b)의 점선으로 표시된 기간 동안에 영상 신호의 기록을 정지하고, 그 후, 영상 신호의 기록을 재개한다. 또한, 판독 제어 신호 생성부(224a)는 도 13의 (e)의 점선으로 표시된 기간 동안에 갱신되지 않은 프레임 식별 신호(RF\_ID)에 대응하는 영상 신호를 반복하여 판독하고, 그 후, 판독 프레임 식별 신호(RF\_ID)의 순차적 갱신을 통해 새로운 영상 신호의 판독을 재개한다. 즉, 도 13의 (e)의 점선으로 표시된 기간 동안에, 오른쪽 시점 영상 신호와 왼쪽 시점 영상 신호가 반복하여 판독되어, 다시점 영상 표시를 수행하는 경우에도, 정지 화상이 표시될 수 있다.

[0118] 전술된 바와 같이, 프레임 신호에 동기하여 표시 정지 제어를 수행하고 한 프레임의 다시점 영상 신호의 판독을 반복함으로써, 다시점 정지 화상의 영상 신호가 표시 장치에 입력되지 않아도, 소망의 타이밍에 다시점 영상이

고해상도 정지 화상으로서 표시될 수 있다. 따라서, 예를 들어, 3D 영상 평가가 효율적으로 수행될 수 있다.

[0119] 제3 실시예에서는, 영상 신호(IW\_Data)에 기초하는 영상이 동영상으로부터 정지 화상으로 전환되는 경우가 예시된다. 그러나, 제1 표시 모드 또는 제2 표시 모드에서, 정지 화상을 포착해 포착 영상 신호로서 출력하거나 외부 장치로부터 소망 정지 화상의 영상 신호를 신호 처리 회로에 공급함으로써 정지 화상을 소망 정지 화상으로 용이하게 교체할 수 있다.

[0120] 도 9에서, 표시 정지 제어부(23-A)의 인터페이스부(231)로부터 판독 제어부(22)의 판독 주소 생성부(225)로 공급되는 정지 화상 판독 신호(DMA\_RA)는 프레임 메모리(202)에 저장된 정지 화상을 포착해 외부 장치에 출력하기 위한 신호이다. 제2 신호 처리부(203)로부터 인터페이스(I/F)부(231)로 공급되는 영상 신호(DMA\_RD)는 프레임 메모리(202)로부터 판독되어 외부 장치에 출력되는 포착 영상 신호이다.

[0121] 표시 정지 제어부(23-A)의 I/F부(231)로부터 제1 신호 처리부(201)에 공급되는 교체 영상 신호(DMA\_WD)는 외부 장치로부터 공급된 교체 영상 신호이다. 기록 제어부(21)의 기록 주소 생성부(212)에 공급되는 정지 화상 기록 신호(DMA\_WA)는 외부 장치로부터 공급된 교체 영상 신호(DMA\_WD)를 프레임 메모리(202)에 저장시키기 위한 신호이다.

[0122] 프레임 메모리(202)로부터의 영상 신호(DMA\_RD)의 판독 또는 프레임 메모리(202)로의 교체 영상 신호(DMA\_WD)의 기록은 DMA(Direct Memory Access) 방식을 이용하여 용이하게 수행할 수 있다.

[0123] 또한, 예를 들어, 멀티 칩 구성에서 제1 표시 모드로 영상 신호(DMA\_RD)를 판독하는 경우, 판독 프레임 식별 신호(RF\_ID)로서 프레임 식별 신호(EF\_ID)를 사용해 동일한 프레임 식별 신호를 각 신호 처리 회로에 유지해 둔다. 이렇게 함으로써, DMA 방식으로 프레임 메모리(202)의 영상 신호를 외부 장치 내에 포착할 경우, 프레임 식별 신호에 대응하는 주소가 서로 동일하게 된다. 따라서, 각 신호 처리 회로가 프레임 식별 신호를 관리할 필요가 없고, 판독 주소 신호(R\_ADR)의 생성이 간단해 진다. 또한, 프레임 식별 신호(EF\_ID)를 사용하지 않는 경우, 각 신호 처리 회로에 영상 신호를 기록할 때의 프레임 식별 신호가 서로 상이하기 때문에, 저장된 영상 신호를 판독하는 경우에도 프레임 식별 신호에 대응하는 주소가 서로 상이하게 된다. 따라서, 프레임 식별 신호(EF\_ID)를 사용하는 경우와 비교해, 판독 주소 신호(R\_ADR)의 생성이 간단하지 않다.

[0124] 또한, 예를 들어, 멀티 칩 구성에서 제1 표시 모드로 교체 영상 신호(DMA\_WD)의 기록을 수행하는 경우, 프레임 식별 신호(WF\_ID)로서 프레임 식별 신호(EF\_ID)를 사용하여 동일한 프레임 식별 신호를 각 신호 처리 회로에 유지해 둔다. 이렇게 함으로써, 외부 장치로부터의 영상 신호를 DMA 방식으로 프레임 메모리(202)에 저장할 경우, 프레임 식별 신호에 대응하는 주소가 서로 동일하게 된다. 따라서, 각 신호 처리 회로가 프레임 식별 신호를 관리할 필요가 없고, 판독 주소 신호(R\_ADR)의 생성이 간단해 진다.

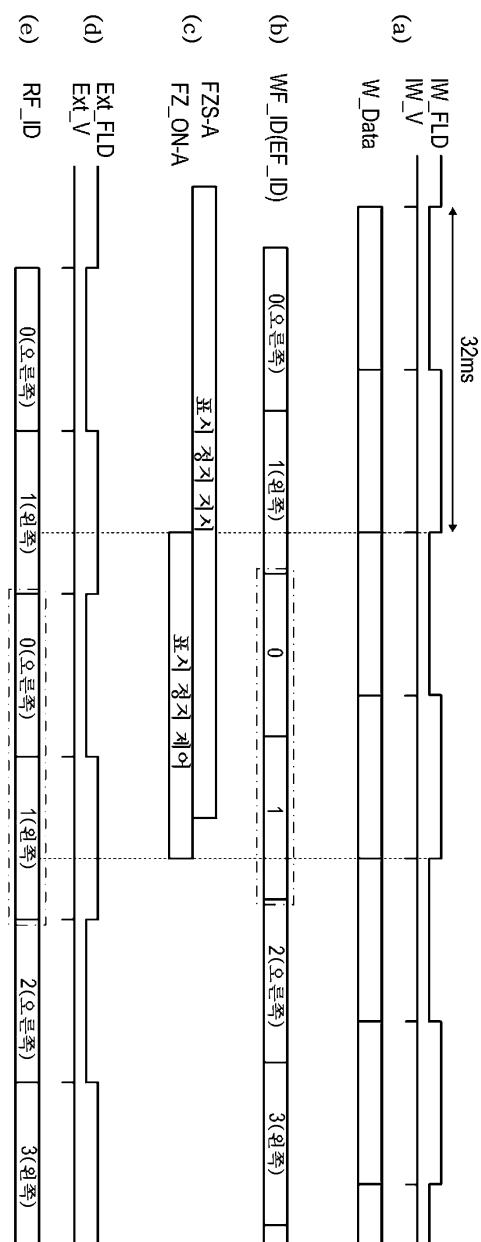

[0125] 도 14의 (a) 내지 (d)는 정지 화상을 취득하는 경우의 타이밍도이다. 도 14의 (a)는 표시 정지 지시 신호(FZ S)를 나타내고 있다. 도 14의 (b)는 판독 프레임 식별 신호(RF\_ID)(=EF\_ID)를 나타내고 있고, 도 14의 (c)는 판독 주소 신호를 나타내고 있으며, 도 14의 (d)는 판독된 영상 신호를 나타내고 있다. 여기서, 판독 주소 신호가 수평 판독 타이밍 신호(RT\_H)와 수직 판독 타이밍 신호(RT\_V)와 프레임 신호(RT\_FLD)에 기초한 주 판독 주소 신호라면, 영상 신호(R\_Data-A)가 출력된다. 또한, 판독 주소 신호가 정지 화상 판독 신호(DMA\_RA)에 기초한 DMA 판독 주소 신호라면, 프레임 메모리(202)로부터 판독된 영상 신호(DMA\_RD)가 포착 영상 신호로서 외부에 출력된다.

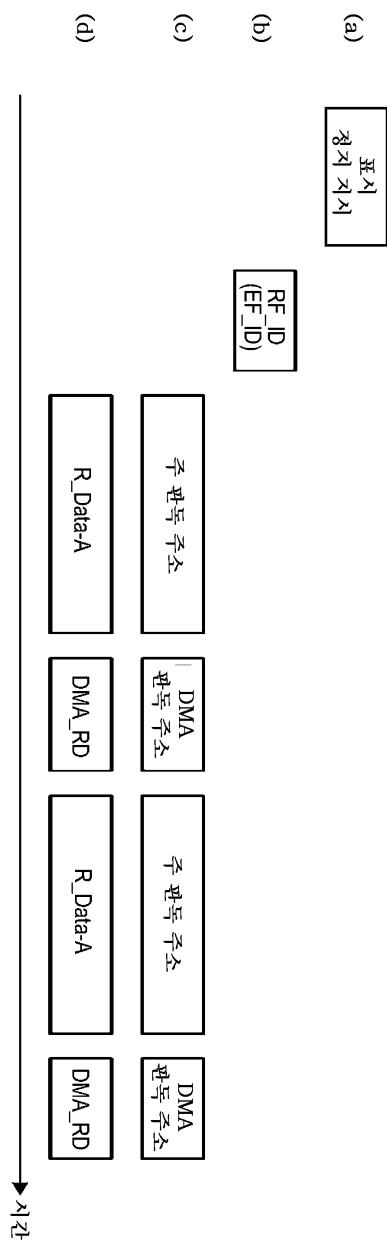

[0126] 도 15의 (a) 내지 (d)는 정지 화상을 교체하는 경우의 타이밍도이다. 도 15의 (a)는 표시 정지 지시 신호(FZ S)를 나타내고 있다. 도 15의 (b)는 프레임 식별 신호(WF\_ID)(=EF\_ID)를 도시하고, 도 15의 (c)는 기록 주소 신호와 판독 주소 신호를 도시하며, 도 15의 (d)는 프레임 메모리(202)에 기록된 영상 신호와 프레임 메모리(202)로부터 판독된 영상 신호를 도시하고 있다. 여기서, 기록 주소 신호가 정지 화상 기록 신호(DMA\_WA)에 기초한 기록 주소 신호이면, 프레임 메모리(202)에 교체 영상 신호(DMA\_WD)가 저장된다. 그 후, 프레임 식별 신호(EF\_ID)를 판독 프레임 식별 신호(RF\_ID)로서 이용하여 주 주소 신호에 기초하여 영상 신호를 판독함으로써, 외부 장치로부터 공급된 교체 영상 신호가 영상 신호(R\_Data-A)로서 출력된다. 즉, 외부 장치로부터 공급된 정지 화상은 멀티 칩 구성으로 표시되고 있는 정지 화상에 의해 용이하게 교체될 수 있다.

[0127] 전술된 바와 같이, 정지 화상의 포착 영상 신호를 멀티 칩 구성으로 외부 장치에 출력하는 경우 또는 외부 장치로부터 공급된 교체 영상 신호에 기초하여 정지 화상을 표시하는 경우, 프레임 식별 신호(EF\_ID)를 이용하여 영상 신호가 판독되거나 기록될 수 있다. 따라서, 각 신호 처리 회로가 프레임 식별 신호를 개별적으로 설정함으로써 영상 신호를 기록하거나 판독하는 경우와 같은 방식에서, 각 신호 처리 회로는 프레임 식별 신호를 관리할

필요가 없고, 전술된 바와 같이 주소가 용이하게 생성될 수 있다.

[0128] 또한, 본 개시물은 전술된 실시예로 한정되는 것으로 해석되어서는 안 된다. 본 개시물의 실시예들은 예시의 형태로 본 기술을 개시하고 있기 때문에, 본 개시물의 요지를 벗어나지 않고 다양한 수정이나 대안을 만들 수 있다는 것은 당업자에게 자명하다. 즉, 본 개시물의 요지를 판단하기 위해서는, 첨부된 특허 청구의 범위를 참조해야 한다.

[0129] 본 개시물은 이하와 같은 구성도 취할 수가 있다.

(1) 신호 처리 회로로서,

[0131] 영상 신호를 저장하는 메모리;

[0132] 입력 영상 신호에 동기하는 기록 제어 신호와 프레임 식별 정보를 생성하고, 상기 기록 제어 신호에 기초하여 상기 입력 영상 신호가 상기 프레임 식별 정보에 대응하도록 상기 입력 영상 신호를 상기 메모리에 저장하는 기록 제어부; 및

[0133] 출력 수평 주파수의 타이밍 신호에 기초하여, 외부로부터 공급된 수직 동기 신호를 취득하여 판독 제어 신호를 생성하고, 상기 판독 제어 신호와 외부로부터 공급된 프레임 식별 정보에 기초하여, 상기 프레임 식별 정보에 대응하는 영상 신호를 상기 메모리로부터 판독하는 판독 제어부를 포함하는, 신호 처리 회로.

[0134] (2) 복수의 신호 처리 회로를 동시에 이용하여 영상 표시를 수행하는 경우, 상기 판독 제어부는 상기 판독 제어 신호를 생성하고, 상기 판독 제어 신호와 상기 프레임 식별 정보에 기초하여 상기 프레임 식별 정보에 대응하는 상기 영상 신호를 상기 메모리로부터 판독하는 상기 (1)에 설명된 신호 처리 회로.

[0135] (3) 상기 판독 제어부는, 상기 출력 수평 주파수의 상기 타이밍 신호에 기초하여 생성된 수직 동기 신호와 외부로부터 공급된 상기 수직 동기 신호 간의 위상차와, 상기 출력 수평 주파수의 상기 타이밍 신호와 외부로부터 공급된 수평 동기 신호 간의 위상차를 검출하여, 상기 위상차들이 미리 결정된 값보다 작도록, 상기 출력 수평 주파수의 상기 타이밍 신호와 이 타이밍 신호에 기초하여 생성된 상기 수직 동기 신호의 위상들을 조정하고, 조정 후의 신호를 이용하여 판독 제어 신호를 생성하는, 상기 (1) 또는 (2)에 설명된 신호 처리 회로.

[0136] (4) 상기 입력 영상 신호와 또 다른 신호 처리 회로에 입력되는 입력 영상 신호가 스큐를 일으키더라도, 상기 판독 제어 신호와 상기 프레임 식별 정보에 기초하여 상기 프레임 식별 정보에 대응하는 상기 영상 신호를 상기 메모리로부터 판독할 수 있도록, 외부로부터 공급된 동기 신호를 지연시키는 스큐 보상부를 더 포함하는, (1) 내지 (3) 중 어느 하나에 설명된 신호 처리 회로.

[0137] (5) 표시 정지 지시 신호가 공급될 때 입력 래치 신호에 기초하여 상기 표시 정지 지시 신호를 취득하고 취득된 상기 표시 정지 지시 신호를 상기 기록 제어부와 상기 판독 제어부에 출력하는 표시 정지 제어부를 더 포함하고,

[0138] 상기 기록 제어부는 표시 정지 지시 신호에 기초한 표시 정지 기간 동안에 상기 메모리로의 상기 입력 영상 신호의 저장을 정지하며,

[0139] 상기 판독 제어부는, 상기 표시 정지 지시 신호에 기초한 표시 정지 기간 동안에, 표시 정지 이전에 판독된 상기 프레임 식별 정보에 대응하는 상기 영상 신호를 판독하는 상기 (1) 내지 (4) 중 어느 하나에 설명된 신호 처리 회로.

[0140] (6) 상기 표시 정지 제어부는 프레임 단위 또는 복수의 프레임 단위로 상기 입력 래치 신호에 기초하여 상기 표시 정지 지시 신호를 취득하는, 상기 (5)에 설명된 신호 처리 회로.

[0141] (7) 상기 판독 제어부는 외부로부터 공급된 상기 프레임 식별 정보에 기초하여 상기 프레임 식별 정보에 대응하는 상기 영상 신호를 상기 메모리로부터 판독하고, 판독된 상기 영상 신호를 포착 영상 신호로서 외부에 출력하는, 상기 (5)에 설명된 신호 처리 회로.

[0142] (8) 상기 기록 제어부는 외부로부터 공급된 상기 프레임 식별 정보에 기초하여 상기 프레임 식별 정보에 대응하는 교체 영상 신호를 상기 메모리에 저장하는, 상기 (5)에 설명된 신호 처리 회로.

[0143] (9) 상기 판독 제어부는 상기 외부로부터 공급된 상기 프레임 식별 정보에 기초하여 상기 프레임 식별 정보에 대응하여 상기 메모리에 저장된 교체 영상 신호를 판독하는, 상기 (8)에 설명된 신호 처리 회로.

[0144] (10) 상기 메모리는 신호 처리에 이용되는 영상 신호를 저장하는, 상기 (1) 내지 (9) 중 어느 하나에 설명된 신

호 처리 회로.

[0145] (11) 표시 장치로서,

[0146] 한 화면을 구성하는 복수의 표시 영역 각각마다, 대응하는 표시 영역의 영상 신호를 처리하는 신호 처리 회로를 포함하고,

[0147] 상기 신호 처리 회로를 각각은,

[0148] 영상 신호를 저장하는 메모리,

[0149] 입력 영상 신호에 동기하는 기록 제어 신호와 프레임 식별 정보를 생성하고, 상기 기록 제어 신호에 기초하여 상기 입력 영상 신호가 상기 프레임 식별 정보에 대응하도록 상기 입력 영상 신호를 상기 메모리에 저장하는 기록 제어부; 및

[0150] 출력 수평 주파수의 타이밍 신호에 기초하여, 외부로부터 상기 각각의 신호 처리 회로에 공통으로 공급된 수직 동기 신호를 취득하여 판독 제어 신호를 생성하고, 상기 판독 제어 신호와 외부로부터 상기 각각의 신호 처리 회로에 공통으로 공급된 프레임 식별 정보에 기초하여, 상기 프레임 식별 정보에 대응하는 영상 신호를 상기 메모리로부터 판독하는 판독 제어부를 포함하는, 표시 장치.

[0151] (12) 기준 주파수 신호를 생성하는 빌진부를 더 포함하고,

[0152] 상기 빌진부는 생성된 상기 기준 주파수 신호를 상기 각각의 신호 처리 회로에 공급하고,

[0153] 상기 신호 처리 회로의 판독 제어부는, 상기 출력 수평 주파수의 상기 타이밍 신호에 기초하여 생성된 수직 동기 신호와 외부로부터 공급된 상기 수직 동기 신호 간의 위상차와, 상기 출력 수평 주파수의 상기 타이밍 신호와 외부로부터 공급된 수평 동기 신호 간의 위상차를 검출하여, 상기 위상차들이 미리 결정된 값보다 작도록, 상기 출력 수평 주파수의 상기 타이밍 신호와 이 타이밍 신호에 기초하여 생성된 상기 수직 동기 신호의 위상들을 조정하고, 조정 후의 신호를 이용하여 판독 제어 신호를 생성하는, 상기 (11)에 설명된 표시 장치.

[0154] (13) 복수의 상기 신호 처리 회로는, 상기 복수의 신호 처리 회로에 입력되는 상기 입력 영상 신호들이 상기 신호 처리 회로들 간에 스큐를 일으키더라도, 상기 판독 제어 신호와 상기 프레임 식별 정보에 기초하여 상기 프레임 식별 정보에 대응하는 상기 영상 신호가 상기 메모리로부터 판독될 수 있도록, 외부로부터 공급된 동기 신호를 지연시키는 스큐 보상부를 포함하는, 상기 (11) 또는 (12)에 설명된 표시 장치.

[0155] (14) 복수의 상기 신호 처리 회로는, 표시 정지 지시 신호가 공급될 때 입력 래치 신호에 기초하여 표시 정지 지시 신호를 취득하고 취득된 상기 표시 정지 지시 신호를 상기 기록 제어부와 상기 판독 제어부에 출력하는 표시 정지 제어부를 더 포함하고,

[0156] 상기 기록 제어부는 상기 표시 정지 지시 신호에 기초한 표시 정지 기간 동안에 메모리로의 상기 입력 영상 신호의 저장을 정지하며,

[0157] 상기 판독 제어부는 상기 표시 정지 지시 신호에 기초한 표시 정지 기간 동안에, 표시 정지 이전에 판독된 상기 프레임 식별 정보에 대응하는 상기 영상 신호를 판독하는 상기 (11) 내지 (13) 중 어느 하나에 설명된 표시 장치.

[0158] 본 개시물의 실시예들에 따른 신호 처리 회로, 신호 처리 방법 및 표시 장치에서, 입력 영상 신호와 동기하는 기록 제어 신호와 프레임 식별 정보가 생성되고, 기록 제어 신호에 기초하여 입력 영상 신호가 프레임 식별 정보에 대응하도록 상기 입력 영상 신호를 메모리에 저장한다. 또한, 출력 수평 주파수의 타이밍 신호에 기초하여 외부로부터 공급된 수직 동기 신호를 취득하여 판독 제어 신호가 생성되고, 이 판독 제어 신호와 외부로부터 공급된 프레임 식별 정보에 기초하여 프레임 식별 정보에 대응하는 영상 신호가 메모리로부터 판독된다. 이를 통해, 외부로부터 공급된 동기 신호를 복수의 신호 처리 회로에 공급하는 경우, 신호 처리 회로로부터 출력되는 영상 신호들 간의 위상차가 작게 되어, 신호 처리 회로로부터 출력되는 영상 신호들의 위상을 라인 버퍼를 이용하여 서로 일치시키는 것이 가능하다. 따라서, 낮은 지연, 회로 크기의 축소, 낮은 소비 전력 및 낮은 비용으로 고해상도의 영상 표시가 수행될 수 있다. 본 개시물은 다양한 프레임 레이트를 갖는 영상 신호를 이용하여 고정밀 영상 표시를 수행하는 표시 장치 등에 적절하다.

[0159] 본 개시물은 2011년 3월 30일 일본 특허청에 출원된 일본 우선권 특허 출원 JP 2011-074348호에 개시된 주제를 포함하며, 그 전체 내용이 본 명세서에서 참조용으로 인용된다.

[0160]

첨부된 특허청구범위 또는 그 등가물의 범위 내에 있는 한, 설계 요건 및 기타의 요인들에 따라 다양한 수정, 조합, 부조합 및 변형이 이루어질 수 있다는 것을 당업자라면 이해할 것이다.

### 부호의 설명

[0161]

10, 10a, 50: 표시 장치, 20-A ~ 20-D, 60-A ~ 60-D: 신호 처리 회로, 21: 기록 제어부, 22: 판독 제어부, 23, 23-A ~ 23-D: 표시 정지 제어부, 30-A ~ 30-D: 라인 버퍼, 35-A ~ 35-D, 75-A ~ 75-D: 타이밍 제어 회로, 40: 신호 처리 회로 제어부, 45, 45-A ~ 45-D, 85-A ~ 85-D: 발진기, 70-A ~ 70-D: 프레임 버퍼, 80: 프레임 버퍼 제어부, 200: 클록 전송부, 201: 제1 신호 처리부, 202: 프레임 메모리, 203: 제2 신호 처리부, 211, 211a: 기록 제어 신호 생성부, 212: 기록 주소 생성부, 221: 스큐 보상부, 222, 223, 223, 232, 234: 신호 선택부, 224, 224a: 판독 제어 신호 생성부, 225: 판독 주소 생성부, 231: 인터페이스(I/F) 부, 233: 래치부, 235: 표시 정지 신호 출력부

### 도면

#### 도면1

## 도면2

도면3

## 도면4

## 도면5

(a)

|            |            |

|------------|------------|

| IW_Data-ul | IW_Data-ur |

| IW_Data-ll | IW_Data-lr |

[2048(1920) × 1080] × 4

(b)

(c)

|           |           |

|-----------|-----------|

| IW_Data-1 | IW_Data-2 |

| IW_Data-3 | IW_Data-4 |

[2048(1920) × 1080] × 4

도면6

도면7

## 도면8

## 도면9

도면10

## 도면11

도면12

## 도면13

도면14

도면15