## (19) **日本国特許庁(JP)**

# (12) 公 開 特 許 公 報(A)

(11)特許出願公開番号

特開2017-112134 (P2017-112134A)

(43) 公開日 平成29年6月22日(2017.6.22)

| (51) Int.Cl. |         |           | F I     |       |           | テーマコート   | ぶ (参考) |

|--------------|---------|-----------|---------|-------|-----------|----------|--------|

| HO1L         | 29/78   | (2006.01) | HO1L    | 29/78 | 652M      | 5F048    |        |

| HO1L         | 29/739  | (2006.01) | HO1L    | 29/78 | 653A      |          |        |

| HO1L         | 21/336  | (2006.01) | HO1L    | 29/78 | 655D      |          |        |

| HO1L         | 21/8234 | (2006.01) | HO1L    | 29/78 | 657D      |          |        |

| HO1L         | 27/06   | (2006.01) | HO1L    | 29/78 | 655F      |          |        |

|              |         |           | 審査請求 未請 | 求 請求項 | 質の数 10 OL | (全 23 頁) | 最終頁に続く |

(21) 出願番号 (22) 出願日 特願2015-243077 (P2015-243077) 平成27年12月14日 (2015.12.14) (71) 出願人 000005234

富士電機株式会社

神奈川県川崎市川崎区田辺新田1番1号

(74)代理人 110000877

龍華国際特許業務法人

(72) 発明者 内藤 達也

神奈川県川崎市川崎区田辺新田1番1号

富士電機株式会社内

Fターム(参考) 5F048 AC06 AC10 BA07 BB02 BB09

BB19 BC02 BC03 BC12 BD07

BE09 BF02 BF07 CB07

# (54) 【発明の名称】半導体装置

# (57)【要約】

【課題】ゲートトレンチ内のゲート電極と、エミッタ電極およびコレクタ電極とはゲート容量を形成する。半導体基板においてゲートトレンチを延伸させる場合、ゲート容量を調整することが困難であった。

【解決手段】半導体基板のおもて面側に設けられ、内部に設けられた電極にエミッタ電位が与えられる複数のダミートレンチ部と、半導体基板のおもて面側において複数のダミートレンチ部のうち2以上のダミートレンチ部に囲まれて設けられ、内部に設けられた電極にゲート電位が与えられるゲートトレンチ部とを備える半導体装置を提供する。

【選択図】図1

#### 【特許請求の範囲】

## 【請求項1】

半導体基板のおもて面側に設けられ、内部に設けられた電極にエミッタ電位が与えられ る複数のダミートレンチ部と、

前記半導体基板のおもて面側において複数のダミートレンチ部のうち2以上のダミート レン チ 部 に 囲 ま れ て 設 け ら れ 、 内 部 に 設 け ら れ た 電 極 に ゲ ー ト 電 位 が 与 え ら れ る ゲ ー ト ト レンチ部と

を備える

半導体装置。

## 【請求項2】

前 記 ゲ ー ト ト レ ン チ 部 の 少 な く と も 一 部 が 直 下 の 領 域 に 配 置 さ れ 、 前 記 エ ミ ッ タ 電 位 が 与えられるエミッタ電極と、

少なくとも一部が前記エミッタ電極の下に設けられ、前記ゲートトレンチ部の内部に設 けられた電極が電気的に接続するゲートランナーと

をさらに備え、

前 記 ゲ ー ト ラ ン ナ ー は 、 前 記 エ ミ ッ タ 電 極 の 直 下 の 領 域 か ら 外 周 方 向 に 延 伸 す る 請求項1に記載の半導体装置。

## 【請求項3】

前記ゲートトレンチ部と前記ダミートレンチ部とは、前記ゲートランナーの延伸方向に おいて交互に設けられる

請求項2に記載の半導体装置。

#### 【 請 求 項 4 】

前記ゲートトレンチ部は、前記ゲートランナーの延伸方向に伸びるゲート直線部を有し

前記ダミートレンチ部は、前記ゲートランナーの延伸方向に直交する方向に伸びるダミ - 直線部を有する

請求項2または3に記載の半導体装置。

#### 【 請 求 項 5 】

前記ゲートトレンチ部は、

前記ゲートランナーの延伸方向に伸びる第1のゲート直線部と、

前記ゲートランナーの延伸方向に直交する方向に伸びる第2のゲート直線部と

# を有し、

前記ダミートレンチ部は、

前記ゲートランナーの延伸方向に伸びる第1のダミー直線部と、

前記ゲートランナーの延伸方向に直交する方向に伸びる第2のダミー直線部と

# を有する

請求項2または3に記載の半導体装置。

## 【請求項6】

前 記 ダ ミ ー ト レン チ 部 の 内 部 に 設 け ら れ た 電 極 と 前 記 エ ミ ッ タ 電 極 と を 電 気 的 に 接 続 す るためのコンタクト部をさらに備え、

前記コンタクト部は、前記ダミートレンチ部上のうち、前記ゲートランナー上以外の位 置に設けられる

請求項4または5に記載の半導体装置。

# 【請求項7】

前記ゲートトレンチ部と前記ダミートレンチ部とは、最近接距離がトレンチ絶縁膜の厚 さ以上、ゲートトレンチ部の短手方向の幅以下である領域を有する

請求項1から6のいずれか一項に記載の半導体装置。

# 【請求項8】

前 記 ゲ ー ト ト レ ン チ 部 は 、 前 記 半 導 体 基 板 の お も て 面 に 対 し て 環 状 に 設 け ら れ る 請求項1から3のいずれか一項に記載の半導体装置。

10

20

30

40

#### 【請求項9】

前記ゲートトレンチ部と前記ダミートレンチ部とは、前記ゲートランナーの延伸方向に 直交する方向においても交互に設けられる

請求項3に記載の半導体装置。

## 【請求項10】

前記半導体基板のおもて面に対して、環状の前記ゲートトレンチ部を囲むように、環状の不純物注入領域をさらに備え、

前記ゲートトレンチ部の内部に設けられた電極が電気的に接続するゲートランナーの延伸方向に直交する方向において隣接する環状の前記不純物注入領域は、前記ゲートランナーの延伸方向に半ピッチずれて設けられる

請求項8に記載の半導体装置。

【発明の詳細な説明】

## 【技術分野】

# [0001]

本発明は、半導体装置に関する。

#### [00002]

従来、平面視において直線状に延伸している複数の第1のゲートトレンチと、当該複数の第1のゲートトレンチに対して平行に伸びているフローティング状態の第2のゲートトレンチとを設けていた(例えば、特許文献1)。また従来、内部にゲート電極を有するトレンチが平面視において三差路状のパターン形状を形成するように設けられ、当該トレンチの単位パターンはフローティング電位を有するダミー電極を囲んでいた(例えば、特許文献2の図18および図19参照)。このように、直線状または三差路状のゲートトレンチを、半導体基板内部において長距離に渡って延伸させていた。

[ 先行技術文献]

# [特許文献]

[特許文献 1 ] 特開 2 0 1 5 - 1 3 8 7 8 9 号公報

[特許文献2] 特開2012-190938号公報

# 【発明の概要】

【発明が解決しようとする課題】

#### [0003]

ゲートトレンチ内のゲート電極と、エミッタ電極およびコレクタ電極とはゲート容量を 形成する。半導体基板においてゲートトレンチを長距離に渡って延伸させる場合、設計段 階において柔軟にゲート容量を調整することが困難であった。

【課題を解決するための手段】

## [0004]

本発明の第1の態様においては、複数のダミートレンチ部と、ゲートトレンチ部とを備える半導体装置を提供する。複数のダミートレンチ部は、半導体基板のおもて面側に設けられてよい。複数のダミートレンチ部の内部には、電極が設けられてよい。当該電極には、エミッタ電位が与えられてよい。ゲートトレンチ部は、半導体基板のおもて面側において複数のダミートレンチ部のうち2以上のダミートレンチ部に囲まれて設けられてよい。ゲートトレンチ部の内部には、電極が設けられてよい。当該電極には、ゲート電位が与えられてよい。

[ 0 0 0 5 ]

半導体装置は、エミッタ電極と、ゲートランナーとをさらに備えてよい。ゲートトレンチ部の少なくとも一部は、当該エミッタ電極の直下の領域に配置されてよい。エミッタ電極には、エミッタ電位が与えられてよい。ゲートランナーは、少なくとも一部がエミッタ電極の下に設けられてよい。ゲートトレンチ部の内部に設けられた電極は、ゲートランナーに電気的に接続してよい。ゲートランナーは、エミッタ電極の直下の領域から外に延伸してよい。

[0006]

10

20

30

40

ゲートトレンチ部とダミートレンチ部とは、ゲートランナーの延伸方向において交互に 設けられてよい。

[0007]

ゲートトレンチ部は、ゲート直線部を有してよい。ゲート直線部は、ゲートランナーの延伸方向に伸びてよい。ダミートレンチ部は、ダミー直線部を有してよい。ダミー直線部は、ゲートランナーの延伸方向に直交する方向に伸びてよい。

[00008]

ゲートトレンチ部は、第1のゲート直線部と、第2のゲート直線部とを有してよい。第 1のゲート直線部は、ゲートランナーの延伸方向に伸びてよい。第2のゲート直線部は、 ゲートランナーの延伸方向に直交する方向に伸びてよい。ダミートレンチ部は、第1のダ ミー直線部と、第2のダミー直線部とを有してよい。第1のダミー直線部は、ゲートラン ナーの延伸方向に伸びてよい。第2のダミー直線部は、ゲートランナーの延伸方向に直交 する方向に伸びてよい。

[0009]

前記半導体装置は、コンタクト部をさらに備えてよい。コンタクト部は、ダミートレンチ部の内部に設けられた電極とエミッタ電極とを電気的に接続してよい。コンタクト部は、ダミートレンチ部上のうち、ゲートランナー上以外の位置に設けられてよい。

[0010]

ゲートトレンチ部とダミートレンチ部とは、最近接距離がトレンチ絶縁膜の厚さ以上、 ゲートトレンチ部の短手方向の幅以下である領域を有してよい。

[0011]

ゲートトレンチ部は、半導体基板のおもて面に対して環状に設けられてよい。

[ 0 0 1 2 ]

ゲートトレンチ部とダミートレンチ部とは、ゲートランナーの延伸方向に直交する方向 においても交互に設けられてよい。

[0013]

半導体装置は、環状の不純物注入領域をさらに備えてよい。環状の不純物注入領域は、 半導体基板のおもて面に対して、環状のゲートトレンチ部を囲んでよい。ゲートランナー の延伸方向に直交する方向において隣接する環状の不純物注入領域は、ゲートランナーの 延伸方向に半ピッチずれて設けられてよい。ゲートランナーは、ゲートトレンチ部の内部 に設けられた電極に電気的に接続してよい。

[0014]

なお、上記の発明の概要は、本発明の必要な特徴の全てを列挙したものではない。また これらの特徴群のサブコンビネーションもまた、発明となりうる。

【図面の簡単な説明】

- [0015]

- 【図1】第1実施形態における半導体装置100の上面を示す平面概略図である。

- 【図2】図1におけるII II′断面を示す図である。

- 【図3】図1におけるIII III 断面を示す図である。

- 【図4】図1におけるIV IV′断面を示す図である。

- 【図5】第1実施形態におけるトランジスタ部80を示す平面概略図である。

- 【 図 6 】 第 1 実 施 形 態 にお け る ト ラ ン ジ ス タ 部 8 0 の 領 域 A の 拡 大 図 で あ る 。

- 【図7】ゲートトレンチ部10およびダミートレンチ部20の最近接距離Lと電位分布との関係を説明する図である。

- 【 図 8 】 第 2 実 施 形 態 にお け る ト ラ ン ジ ス タ 部 8 0 を 示 す 平 面 概 略 図 で あ る 。

- 【図9】第3実施形態におけるトランジスタ部80を示す平面概略図である。

- 【 図 1 0 】 第 4 実 施 形 態 に お け る ト ラ ン ジ ス タ 部 8 0 を 示 す 平 面 概 略 図 で あ る 。

- 【図11】第5実施形態におけるトランジスタ部80を示す平面概略図である。

- 【 図 1 2 】 第 5 実 施 形 態 に お け る ト ラ ン ジ ス 夕 部 8 0 の 領 域 B の 拡 大 図 で あ る 。

- 【図13】第6実施形態におけるトランジスタ部80を示す平面概略図である。

10

20

30

30

40

- 【 図 1 4 】 第 7 実 施 形 態 に お け る ト ラ ン ジ ス タ 部 8 0 を 示 す 平 面 概 略 図 で あ る 。

- 【図15】第8実施形態におけるトランジスタ部80を示す平面概略図である。

- 【 図 1 6 】 第 9 実 施 形 態 に お け る ト ラ ン ジ ス タ 部 8 0 を 示 す 平 面 概 略 図 で あ る 。

- 【図17】第10実施形態におけるトランジスタ部80を示す平面概略図である。

- 【 図 1 8 】 第 1 1 実 施 形 態 に お け る ト ラ ン ジ ス タ 部 8 0 を 示 す 平 面 概 略 図 で あ る 。

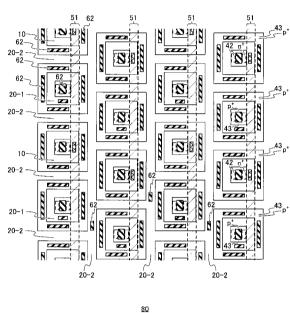

- 【 図 1 9 】 第 1 2 実 施 形 態 に お け る ト ラ ン ジ ス タ 部 8 0 を 示 す 平 面 概 略 図 で あ る 。

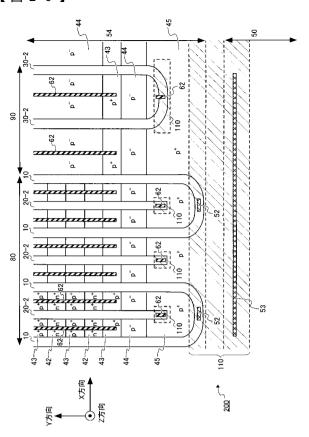

- 【図20】比較例における半導体装置200の上面を示す平面概略図である。

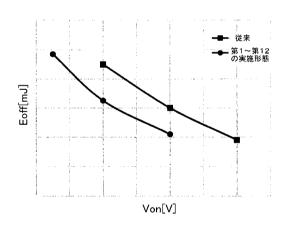

- 【図21】オン電圧(Von)とオフ損失(Eoff)との関係を示す図である。

- 【発明を実施するための形態】

## [0016]

以下、発明の実施の形態を通じて本発明を説明するが、以下の実施形態は特許請求の範囲にかかる発明を限定するものではない。また、実施形態の中で説明されている特徴の組み合わせの全てが発明の解決手段に必須であるとは限らない。

# [0017]

図1は、第1実施形態における半導体装置100の上面を示す平面概略図である。本例の半導体装置100は、IGBT(Insulated Gate Bipolar Transistor)等のトランジスタを含むトランジスタ部80、および、FWD(Free Wheel Diode)等のダイオードを含むダイオード部90を有する半導体基板である。なお、本例は、トランジスタ部80にIGBTを有する。なお、本例は、IGBTとFWDダイオードとを一体形成したRC IGBT(Reverse-Conducting IGBT)である。

#### [0018]

図1は半導体基板の端部周辺における活性領域を示しており、他の領域を省略している。ただし、半導体装置100は、平面視において活性領域を囲むエッジ終端部を有してよい。活性領域は、半導体装置100をオン状態にした場合に電流が流れる領域を指す。これに対して、エッジ終端部は、半導体基板のおもて面側の電界集中を緩和する機能を有する。エッジ終端部は、例えばガードリング、フィールドプレート、リサーフまたはこれらの2種類以上を組み合わせた構造を有してよい。

# [0019]

本例の半導体装置100は、半導体基板のおもて面側において、ゲートトレンチ部10、ダミートレンチ部20、エミッタトレンチ部30、 n <sup>+</sup>型のエミッタ領域42、 p <sup>+</sup>型のコンタクト領域43、 p <sup>-</sup>型のベース領域44、 p <sup>+</sup>型のウェル領域45、ゲート電極50、ゲートランナー51およびエミッタ電極54を備える。ゲート電極50およびエミッタ電極54と、半導体基板のおもて面との間には層間絶縁膜が設けられるが、図1では省略している。また、半導体装置100は、半導体基板のおもて面側において、層間絶縁膜を貫通して設けられるランナーコンタクト部52、ランナーコンタクト部53およびエミッタコンタクト部62を備える。

## [0020]

本例において、 n または p は、それぞれ電子または正孔が多数キャリアであることを意味する。また、 n または p の右肩に記載した + または - について、 + はそれが記載されていないものよりもキャリア濃度が高く、 - はそれが記載されていないものよりもキャリア濃度が低いことを意味する。

## [0021]

トレンチ部および不純物領域は半導体基板のおもて面側に設けられる。つまり、ゲートトレンチ部 1 0、ダミートレンチ部 2 0、エミッタトレンチ部 3 0、 n <sup>+</sup>型のエミッタ領域 4 2、 p <sup>+</sup>型のコンタクト領域 4 3、 p <sup>-</sup>型のベース領域 4 4、 p <sup>+</sup>型のウェル領域 4 5 は、半導体基板内部のおもて面側に形成される。これに対して、ゲート電極 5 0、ゲートランナー 5 1、ランナーコンタクト部 5 2、ランナーコンタクト部 5 3、エミッタ電極 5 4 およびエミッタコンタクト部 6 2 は、半導体基板のおもて面の上方に設けられる。

# [0022]

50

10

20

30

20

30

40

50

なお、 n <sup>†</sup> 型のエミッタ領域 4 2 がゲートトレンチ部 1 0 を跨ぐように記載されているが、これは図示上の便宜的な記載に過ぎず、ゲートトレンチ部 1 0 には n <sup>†</sup> 型のエミッタ領域 4 2 が設けられていない点に注意されたい。第 2 から第 8 の実施形態についても同様である。

# [0023]

本例において、 X 方向と Y 方向とは互いに垂直な方向である。 つまり、 X 方向と Y 方向とは互いに独立な方向である。 Z 方向は X Y 平面に垂直な方向である。 X 方向、 Y 方向および Z 方向は、 いわゆる右手系を成す。 本例において「上」および「上方」とは + Z 方向を意味し、「下」および「下方」とは - Z 方向を意味する。 Y 方向は、 ゲートランナー5 1 の長手方向でもある。

[0024]

ゲート電極 5 0 およびエミッタ電極 5 4 は、金属を含む材料で形成される。例えば、各電極の少なくとも一部の領域はアルミニウムまたはアルミニウムを含む合金で形成される。各電極は、タングステンを含む材料で形成される領域を有してもよい。ゲート電極 5 0 には、ゲート端子からゲート電位が与えられる。エミッタ電極 5 4 には、エミッタ端子からエミッタ電位が与えられる。エミッタ電極 5 4 は、ゲート電極 5 0 と分離して形成される。

[0025]

ゲートトレンチ部10およびダミートレンチ部20は、ダイオード部90の領域に設けられる。ゲートトレンチ部10およびダミートレンチ部20は、予め定められた形状を有してよい。本例のゲートトレンチ部10は、ゲート直線部としてのY方向に伸びる直線部を有する。ダミートレンチ部20は、十字形状のダミートレンチ部20 1と、U字形状のダミートレンチ部20 2とを有する。

[0026]

本例において、ドット形状のダミートレンチ部20に対してハイフンおよび1を付して「20 1」と表記する。また、U字形状の長手部のように、ドット形状に比べて長距離に渡って設けられるダミートレンチ部20に対して、ハイフンおよび2を付して「20 2」と表記する。なお、ダミートレンチ部20は、ダミートレンチ部20 1およびダミートレンチ部20 2の総称である。エミッタトレンチ部30についても同様に、ドット形状のエミッタトレンチ部30を「30 1」と表記し、U字形状の長手部のようにドット形状と比べて長距離に渡って設けられるエミッタトレンチ部30を「30 2」と表記する。また、エミッタトレンチ部30は、エミッタトレンチ部30 1およびエミッタトレンチ部30 2の総称である。

[0027]

十字形状のダミートレンチ部 2 0 1 は、第 1 のダミー直線部としての Y 方向に伸びる直線部と、第 2 のダミー直線部としての X 方向に伸びる直線部とを有する。十字形状のダミートレンチ部 2 0 1 において、第 1 のダミー直線部と第 2 のダミー直線部とは交差する。 U 字形状のダミートレンチ部 2 0 2 は、エミッタ電極 5 4 の下において Y 方向に伸びる長手部と、ゲート電極 5 0 の下において X 方向に伸びる短手部とを有する。

[0028]

一例において、ゲートトレンチ部10のY方向長さは約5μmであり、トレンチ幅(すなわち、X方向長さ)は約1.2μmである。すなわち、本例のゲートトレンチ部10は、ドット形状であると見なすことができる。本例のゲートトレンチ部10の形状は、ゲートトレンチを半導体基板内部において長距離に渡って延伸させる従来例に比べて、非常に小さい。なお、トレンチを長距離に渡って延伸させる場合、例えば5μmから50μm程度延伸させる。

[0029]

また、一例において、ダミートレンチ部 2 0 のトレンチ幅は約 1 . 2 μ m である。また、一例において、ダミートレンチ部 2 0 1 の X 方向および Y 方向の直線部の長さは各々約 5 μ m である。なお、トレンチ幅および各トレンチの長さは、素子耐圧および閾値等の

20

30

40

50

特性に応じて適宜調整してよい。本例のダミートレンチ部20 1の形状もまた、従来例のゲートトレンチに比べて非常に小さいドット形状であると見なすことができる。

### [0030]

複数のゲートトレンチ部10および複数のダミートレンチ部20は、トランジスタ部80の領域において所定の配列方向に沿って所定の間隔で配列されてよい。本例において、ゲートトレンチ部10と十字形状のダミートレンチ部20 1とは、Y方向において交互に設けられる。一例において、本例のゲートトレンチ部10およびダミートレンチ部20 1は、最近接距離が1μm未満となるようにY方向に沿って設けられる。また、一例において、複数のダミートレンチ部20 2は、直線形状部分のX方向周期が約4μmとなるように設けられる。また、当該周期と同じ周期で、ゲートトレンチ部10と十字形状のダミートレンチ部20 1とがX方向において周期的に設けられる。

## [0031]

エミッタトレンチ部30は、ダイオード部90の領域に設けられる。エミッタトレンチ部30は、ゲートトレンチ部10およびダミートレンチ部20と同様の形状を有してよい。ダイオード部90においては、p・型のベース領域44と当該p・型のベース領域44 の下に設けられるn型ドリフト層とのpn接合がダイオードとして機能する。それゆえ、エミッタトレンチ部30は積極的な機能を有さなくてもよいが、ゲートトレンチ部10およびダミートレンチ部20と同じ形状を有することにより、トランジスタ部80とダイオード部90の全体に亘って電位分布を均等にすることができるという効果を有する。さらに、トランジスタ部80とダイオード部90の全体に亘って、発生する熱を均一にするという効果も有する。

#### [0032]

エミッタ電極 5 4 の直下の領域には、ゲートトレンチ部 1 0 、ダミートレンチ部 2 0 の一部、エミッタトレンチ部 3 0 の一部、 n <sup>+</sup>型のエミッタ領域 4 2 、 p <sup>+</sup>型のコンタクト領域 4 3 、 p <sup>-</sup>型のベース領域 4 4 および p <sup>+</sup>型のウェル領域 4 5 の一部が設けられる。 p <sup>+</sup>型のウェル領域 4 5 は、ゲート電極 5 0 が設けられる半導体基板の Y 方向端部から、所定の範囲で形成される。ダミートレンチ部 2 0 2 およびエミッタトレンチ部 3 0 のゲート電極 5 0 側の一部の領域は、 p <sup>+</sup>型のウェル領域 4 5 に形成される。

## [0033]

各トレンチ部に挟まれる領域には、 p 型のベース領域 4 4 が設けられる。 なお、トランジスタ部 8 0 において、 p 型のベース領域 4 4 のほとんどは、 n 型のエミッタ領域 4 2 および p 型のコンタクト領域 4 3 の下に位置する。それゆえ、トランジスタ部 8 0 において、 p 型のベース領域 4 4 が半導体基板のおもて面に露出するのは、 p 型のウェル領域 4 5 の Y 方向に隣接する位置のみである。 なお、 ダイオード部 9 0 においては、 p 型のコンタクト領域 4 3 および p 型のウェル領域 4 5 を除いて p 型のベース領域 4 4 が半導体基板のおもて面に露出する。これにより、 R C - I G B T のダイオード部 9 0 が逆回復動作を行うときに、逆回復ピーク電流が増加するのを防ぐ効果を奏する。

## [0034]

トランジスタ部 8 0 において、 $n^+$ 型のエミッタ領域 4 2 および  $p^+$ 型のコンタクト領域 4 3 のそれぞれは、X方向に隣接する 2 つのダミートレンチ部 2 0 2 における長手部の一方から他方まで設けられる。また、 $n^+$ 型のエミッタ領域 4 2 および  $p^+$ 型のコンタクト領域 4 3 は Y 方向において交互に設けられる。 $n^+$ 型のエミッタ領域 4 2 は、ゲートトレンチ部 1 0 を X 方向において挟むようにかつゲートトレンチ部 1 0 に接するように設けられる。

# [0035]

エミッタコンタクト部 6 2 は、半導体基板のおもて面とエミッタ電極 5 4 とを電気的に接続するための層間絶縁膜の開口部である。エミッタコンタクト部 6 2 は、トランジスタ部 8 0 およびダイオード部 9 0 のうち、エミッタ電極 5 4 直下に設けられる。

## [0036]

トランジスタ部80において、エミッタコンタクト部62は、ゲートトレンチ部10と

ダミートレンチ部 2 0 1 の Y 方向直線部とを X 方向において挟んで設けられる。また、エミッタコンタクト部 6 2 は、ダミートレンチ部 2 0 1 の X 方向直線部における X 方向端部上と、ダミートレンチ部 2 0 の長手部の一部上とにおいても設けられる。これにより、エミッタ電極 5 4 からダミートレンチ部 2 0 の内部に設けられるトレンチ電極にエミッタ電位が与えられる。

# [0037]

ダイオード部90において、エミッタコンタクト部62は、直線形状のエミッタトレンチ部30 1 と十字形状のエミッタトレンチ部30 1 を X 方向において挟む。エミッタコンタクト部62は、直線形状のエミッタトレンチ部30 1 と、十字形状のエミッタトレンチ部30 1 の中央部と、U字形状のエミッタトレンチ部30 2 の長手部の一部とにも設けられる。これにより、エミッタトレンチ部30のトレンチ電極にエミッタ電位が与えられる。

#### [0038]

半導体基板のおもて面側において、ゲートトレンチ部 1 0 は、複数のダミートレンチ部 2 0 のうち 2 以上のダミートレンチ部 2 0 に囲まれて設けられる。ゲートトレンチ部 1 0 がダミートレンチ部 2 0 により形成される半導体基板のメサ領域に囲まれることを意味してよい。本例において、ゲートトレンチ部 1 0 は、 Y 方向において 2 つのダミートレンチ部 2 0 1 に挟まれ、かつ、 X 方向においてダミートレンチ部 2 0 2 の 2 つの対向する長手部に挟まれる。

# [0039]

ゲートランナー 5 1 は、少なくとも一部がエミッタ電極 5 4 の下に設けられる。ゲートランナー 5 1 は、エミッタ電極 5 4 の直下の領域と、エミッタ電極 5 4 の直下の領域から外に延伸する領域とを有する。本例のゲートランナー 5 1 は、エミッタ電極 5 4 の直下を Y 方向に延伸する領域と、ゲート電極 5 0 の直下において当該延伸する領域を X 方向に接続する領域とを有する。ゲートランナー 5 1 は、ポリシリコンを有する配線または金属配線であってよい。

# [0040]

ゲートランナー 5 1 は、ゲートトレンチ部 1 0 の Y 方向直線部の直上を延伸する。ゲートトレンチ部 1 0 の内部に設けられるトレンチ電極は、ランナーコンタクト部 5 2 を介してゲートランナー 5 1 に電気的に接続する。ゲートランナー 5 1 は、ランナーコンタクト部 5 3 を介してゲート電極 5 0 に電気的に接続する。これにより、ゲート電極 5 0 からゲートトレンチ部 1 0 の内部に設けられたトレンチ電極にゲート電位が与えられる。本例では、全てのゲートトレンチ部 1 0 がエミッタ電極 5 4 の直下の領域に設けられ、他はエミッタ電極 5 4 の直下の領域外に設けられてもよい。

#### [0041]

ゲートトレンチ部 1 0 において、ゲート電位を有するトレンチ電極とエミッタ電極 5 4 との間にゲート・エミッタ間容量 C <sub>G E</sub> が形成される。ゲート・エミッタ間容量 C <sub>G E</sub> は、ゲートトレンチ部 1 0 のサイズに依存する。ゲートトレンチ部 1 0 のサイズとは、ゲートトレンチ部 1 0 の X 方向、 Y 方向および Z 方向長さである。

# [0042]

ゲートオン時には、ゲートトレンチ部10のトレンチ電極に電位 $V_{GE}$ が印加されて、容量 $C_{GE}$ に電荷 $Q_g$ が充電される。電荷 $Q_g$ が所定の値まで充電されると、トランジスタ部80のIGBTがオンする。なお、IGBTに外付けされたドライブ回路がIGBTのゲート電極50へ電荷 $Q_g$ 供給することにより、IGBTは駆動されてコレクタ電極からエミッタ電極54に駆動電流が流れる。それゆえ、ドライブ回路の性能に適したゲート・エミッタ間容量 $C_{GE}$ を設ける必要がある。特に、車載用途においては、IGBTの駆動電流を変更することなくゲート・エミッタ間容量 $C_{GE}$ をドライブ回路の性能に適した値に変更することが求められる場合が想定される。

# [0043]

50

40

10

20

20

30

40

50

従来は、ゲートトレンチ部をドット形状とせずに半導体基板において長距離に渡って延伸させていた。長距離に渡って延伸させる理由の一つは、ゲートトレンチ部をゲート電極 50 が設けられる位置まで延伸させることによりゲートトレンチ部とゲート電極 50 とを電気的に接続するためである。この場合、そもそもゲートトレンチ部の必要最低限の長さが予め定まっているので、ゲートトレンチ部の長さをさらに減少させることはできない。つまり、ゲート・エミッタ間容量  $C_{GE}$  の総和を減少させることができない。すなわち、ドライブ回路の性能に応じてゲート・エミッタ間容量  $C_{GE}$  を調整した回路を設けることができなかった。

# [ 0 0 4 4 ]

これに対して本例では、ゲートトレンチ部10をトランジスタ部80の一の端部から他の端部まで長距離に渡って延伸させることなく、数 $\mu$ mのドット形状とする。また、ドット形状のゲートトレンチ部10とダミートレンチ部20 1とをX方向およびY方向に周期的に配置する。本例では、平面視におけるダミートレンチ部20に対するゲートトレンチ部10の面積比率を変えるだけで、半導体装置100のゲート・エミッタ間容量 $C_{GE}$ の総和を調整することができる。つまり、ゲート・エミッタ間容量 $C_{GE}$ の総和を増加させることも減少させることもできる。これにより、ドライブ回路の性能に応じて柔軟にゲート・エミッタ間容量 $C_{GE}$ を調整することができる。

#### [0045]

例えば、ランナーコンタクト部52を設けないことにより、ゲートトレンチ部10をゲートとして機能させなくすることできる。これにより、ダミートレンチ部20の面積割合に対してゲートトレンチ部10の面積割合が減少するので、ゲート・エミッタ間容量C<sub>G</sub>を減少させることができる。また、ダミートレンチ部20 1上のエミッタコンタクト部62に代えてダミートレンチ部20 1上にランナーコンタクト部52を設けることにより、ダミートレンチ部20 1をゲートトレンチ部10に変えることができる。これにより、ダミートレンチ部20の面積割合に対してゲートトレンチ部10の面積割合が増加するので、ゲート・エミッタ間容量C<sub>GF</sub>を増加させることができる。

# [0046]

加えて本例では、ドット形状のゲートトレンチ部10の X 方向および Y 方向を囲むようにダミートレンチ部20を設ける。これにより、ゲートトレンチ部10を長距離に渡って延伸させる場合と比較して、ゲート電極がオン状態でドリフト領域に蓄積するキャリア(電子、正孔)のキャリア密度を向上させることができる。つまり、キャリア蓄積効果を得ることができる。これにより、ゲートトレンチ部10を長距離に渡って延伸させる場合と比較して、オン電圧(Von)を低減することができる。

# [0047]

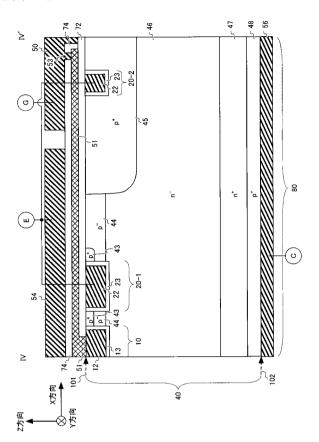

図 2 は、図 1 における I I I I I 断面を示す図である。図 2 は、トランジスタ部 8 0 のダミートレンチ部 2 0 1 と、ダイオード部 9 0 の十字形状のダミートレンチ部 2 0 2 とを通るように、X Z 平面に平行な平面で切断した断面図である。

## [0048]

図 2 に示すように、半導体装置 1 0 0 は、半導体基板 4 0 のおもて面 1 0 1 上にエミッタ電極 5 4 を有し、うら面 1 0 2 下にコレクタ電極 5 6 を有する。なお、エミッタ端子を円中の E で、コレクタ端子を円中の C で模式的にそれぞれ示す。エミッタ端子は、エミッタ電極 5 4 に電気的に接続する端子である。コレクタ端子は、コレクタ電極 5 6 に電気的に接続する端子である。

# [0049]

半導体基板 4 0 は、うら面 1 0 2 側に p <sup>+</sup>型のコレクタ層 4 8 および n <sup>+</sup>型のカソード層 4 9 を有する。トランジスタ部 8 0 のうら面 1 0 2 側には p <sup>+</sup>型のコレクタ層 4 8 が設けられ、ダイオード部 9 0 のうら面 1 0 2 側には n <sup>+</sup>型のカソード層 4 9 が設けられる。半導体基板 4 0 は、うら面 1 0 2 からおもて面 1 0 1 にかけて、 p <sup>+</sup>型のコレクタ層 4 8 および n <sup>+</sup>型のカソード層 4 9、 n <sup>+</sup>型のバッファ層 4 7、 n <sup>-</sup>型のドリフト層 4 6、 p <sup>-</sup>型のベース領域 4 4、 ならびに、 p <sup>+</sup>型のコンタクト領域 4 3 を有する。

#### [0050]

半導体装置100は、おもて面101上に第1の層間絶縁膜72を有する。第1の層間 絶縁膜72は、半導体基板40のおもて面101とエミッタ電極54との間に設けられる 。第1の層間絶縁膜72にはエミッタコンタクト部62が設けられる。エミッタコンタク ト部62を介して、ダミートレンチ部20 1のトレンチ電極22およびエミッタトレン チ部30のトレンチ電極32と、エミッタ電極54とが直接接続する。

#### [0051]

ダミートレンチ部20はトレンチ電極22とトレンチ絶縁膜23とを有する。トレンチ絶縁膜23は、ダミートレンチ部20の側壁および底部に接して形成された絶縁膜である。トレンチ絶縁膜23は、例えば酸化シリコンで形成される。トレンチ電極22は、トレンチ絶縁膜23に接してダミートレンチ部20の内部に設けられた電極である。トレンチ電極22は、エミッタコンタクト部62を介してエミッタ電極54に電気的に接続する。エミッタトレンチ部30も同様に、トレンチ電極32とトレンチ絶縁膜33とを有する。トレンチ電極32も、エミッタコンタクト部62を介してエミッタ電極54に電気的に接続する。

#### [0052]

十字形状のダミートレンチ部 2 0 1 で、 X 方向と Y 方向のトレンチが交差する箇所では、交差しない箇所に比べてエッチングレートが高くなり、トレンチの深さが深くなる。 そのため、交差箇所が無いゲートトレンチ部 1 0 の底部と比べて、ダミートレンチ部 2 0 1 の交差箇所の底部では、電界強度が周辺より高くできる。これにより、ゲートトレンチ部 1 0 の底部の電界強度増加を防ぐことができる。

#### [0053]

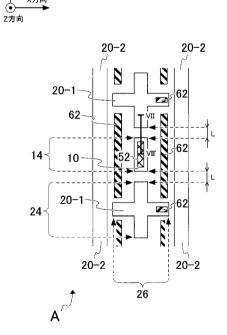

図3は、図1におけるIII III'断面を示す図である。図3は、トランジスタ部80のゲートトレンチ部10と、ダイオード部90のY方向直線部のエミッタトレンチ部30とを通るように、X Z平面に平行な平面で切断した断面図である。

## [0054]

ゲートトレンチ部10は、トレンチ電極12とトレンチ絶縁膜13とを有する。ダミートレンチ部20と同様に、トレンチ絶縁膜13はゲートトレンチ部10の側壁および底部に接して形成された絶縁膜である。トレンチ絶縁膜13は、例えば酸化シリコンで形成される。トレンチ電極12は、トレンチ絶縁膜13に接してゲートトレンチ部10に埋め込まれた電極である。トレンチ電極12は、例えばポリシリコンで形成される。

# [0055]

ゲートトレンチ部10上の第1の層間絶縁膜72は、ランナーコンタクト部52を有する。ゲートランナー51は、ランナーコンタクト部52を介してトレンチ電極12に電気的に接続する。ゲートランナー51の側部および上部には、第2の層間絶縁膜74が設けられる。第2の層間絶縁膜74により、ゲートランナー51はエミッタ電極54から電気的に絶縁される。なお、ゲート端子を円中のGで模式的に示す。ゲート端子は、ゲート電極50に電気的に接続する端子である。

## [0056]

エミッタ電極 5 4 およびコレクタ電極 5 6 には所定の電圧が印加される。例えば、コレクタ電極 5 6 には、エミッタ電極 5 4 の電位よりも高い正バイアスが印加される。また例えば、エミッタ電極 5 4 には、接地電位が印加される。ゲート電極 5 0 に所定の電圧が印加されると、ゲートトレンチ部 1 0 の側壁近傍の p 型のベース領域 4 4 にチャネルが形成される。このとき、 n 型のドリフト層 4 6 に電導度変調が生じて、コレクタ電極 5 6 からエミッタ電極 5 4 に電流が流れる。

# [0057]

ダミートレンチ部20においては、トレンチ電極22がエミッタ電極54に電気的に接続する。ダミートレンチ部20は、n<sup>・</sup>型のドリフト層46におけるキャリア注入促進効果(Injection Enhanced効果とも言う)を半導体装置100に付与する。

10

20

30

#### [0058]

図4は、図1におけるIV IV'断面を示す図である。図4は、トランジスタ部80において隣接するゲートトレンチ部10と十字形状のダミートレンチ部20 1とを通るように、Y Z平面に平行な平面で切断した断面図である。

## [0059]

図4のダミートレンチ部20 2は、図1におけるU字形状のダミートレンチ部20 2の短手部に対応する部分である。図4に示すように、p <sup>+</sup>型のウェル領域45は、ダミートレンチ部20 2よりも深い位置まで形成される。

## [0060]

図4に示すように、ダミートレンチ部20上の第1の層間絶縁膜72によりトレンチ電極22とゲートランナー51とは電気的に分離される。ゲートランナー51は、第1の層間絶縁膜72に設けられたランナーコンタクト部52によりゲートトレンチ部10のトレンチ電極12に電気的に接続する。ゲートランナー51上の第2の層間絶縁膜74によりゲートランナー51とエミッタ電極54とは電気的に分離される。ゲートランナー51は、第2の層間絶縁膜74に設けられたランナーコンタクト部53を介して、ゲート電極50に電気的に接続する。

## [0061]

(製造方法の例)次に、半導体装置 1 0 0 の製造方法の一例を説明する。ただし、半導体装置 1 0 0 の製造方法は本例に限定されない。なお、 E は 1 0 のべき乗を意味し、例えば 1 E + 1 6 c m  $^{-3}$  は 1 × 1 0  $^{1}$  6 c m  $^{-3}$  を意味する。

#### [0062]

まず、 n <sup>-</sup> 型のドリフト層 4 6 と同一の導電型の半導体基板 4 0 を準備する。

次に、半導体基板40の表面に所定のパターンのエッチングマスクを設け、ゲートトレンチ部10、ダミートレンチ部20およびエミッタトレンチ部30の溝部を形成する。

#### [0063]

このとき、各溝部を形成するためのマスク開口幅を、同じ幅とする。溝部を形成した後、各溝部の内壁にトレンチ絶縁膜13、トレンチ絶縁膜23およびトレンチ絶縁膜33を形成する。そして、内壁に形成された各トレンチ絶縁膜に接してトレンチ電極12、トレンチ電極22およびトレンチ電極32を充填して形成する。

## [0064]

## [0065]

次に、半導体基板 4 0 のおもて面 1 0 1 側から n 型不純物を選択的に注入する。これにより、 $n^+$ 型のエミッタ領域 4 2 を選択的に形成する。n 型不純物は、リン(P)およびヒ素(As)の 1 以上であってよい。 $n^+$ 型のエミッタ領域 4 2 には 5 E+1 9  $Cm^{-2}$  の不純物濃度で n 型不純物をドープしてよい。その後、半導体基板 4 0 のおもて面 1 0 1 側に第 1 の層間絶縁膜 7 2 を形成し、選択エッチングにより第 1 の層間絶縁膜 7 2 にランナーコンタクト部 5 2 およびエミッタコンタクト部 6 2 を設ける。

#### [0066]

次に、ゲートランナー 5 1 を成膜してパターニングする。さらに、ゲートランナー 5 1 上に第 2 の層間絶縁膜 7 4 を形成し、選択エッチングにより第 2 の層間絶縁膜 7 4 にランナーコンタクト部 5 3 を設ける。次に、電極材料を成膜してパターニングすることにより、ゲート電極 5 0 およびエミッタ電極 5 4 を形成する。

# [0067]

10

20

30

40

20

30

40

50

次に、半導体基板 4 0 のうら面 1 0 2 から n 型不純物をドープして n <sup>+</sup>型のバッファ層 4 7 を形成する。例えば、うら面 1 0 2 側から 1 . 0 E + 1 4 c m <sup>-2</sup>程度で、プロトンを異なるドーズ量で複数回イオン注入してもよい。続いて、 3 0 0 ~ 4 0 0 程度の温度で熱処理を行い、プロトンの注入により注入された水素と、半導体基板 4 0 中の酸素および空孔による V O H 欠陥を形成する。この V O H 欠陥がドナー(水素ドナー)となる。この水素ドナーが、 n <sup>+</sup>型のバッファ層 4 7 となる。

[0068]

次に、トランジスタ部80に対応する領域において、半導体基板40のうら面102から p 型不純物をドープする。これにより、 n <sup>+</sup>型のバッファ層47よりも薄い厚みで p <sup>+</sup>型のコレクタ層48を形成する。例えば、うら面102側から1.0E+13cm<sup>2</sup>以上4.0E+13cm<sup>2</sup>以下のドーズ量で p 型不純物をイオン注入する。また、ダイオード部90に対応する領域において、 n <sup>+</sup>型のカソード層49を形成するべく、半導体基板40のうら面102から n 型不純物をドープする。例えば、うら面102側から1.0×10<sup>14</sup>/cm<sup>2</sup>以上、1.0×10<sup>16</sup>/cm<sup>2</sup>以下のドーズ量で n 型不純物をイオン注入する。その後、注入面にレーザーアニールを行い、 p 型および n 型不純物を活性化させる。最後に、うら面102側にコレクタ電極56を形成する。

[0069]

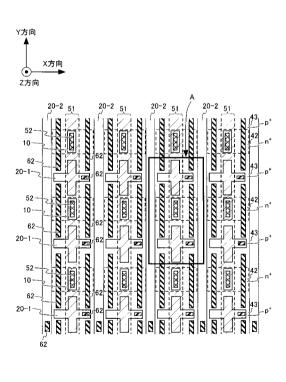

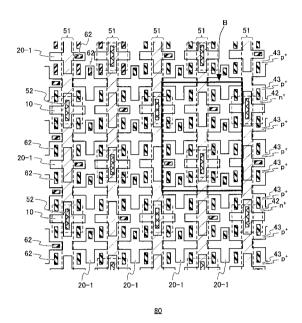

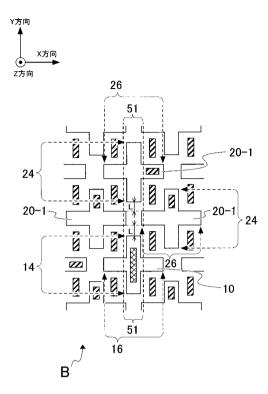

図 5 は、第 1 実施形態におけるトランジスタ部 8 0 を示す平面概略図である。図 5 の一部を領域 A とし、その拡大図を次図において説明する。

[0070]

図6は、第1実施形態におけるトランジスタ部80の領域Aの拡大図である。ゲートトレンチ部10は、Y方向に伸びる第1のゲート直線部14を有する。ダミートレンチ部201は、Y方向に伸びる第1のダミー直線部24とX方向に伸びる第2のダミー直線部26とを有する。隣接するゲートトレンチ部10とダミートレンチ部201とは、最近接距離Lが0.2µmである領域を有してよい。

[0071]

本例において、最近接距離しは、互いに平行である第1のゲート直線部14の・Y方向端部と第1のダミー直線部24の+Y方向端部との間の距離である。ただし、最近接距離しは、互いに平行な二つの直線間の距離に限定されるものではない。最近接距離しは、第1のゲート直線部14と第1のダミー直線部24との間の最小距離であってよい。なお、0.2μmは、アライメントマスクの位置合わせバラつき精度を考慮した上で、量産プロセスにおける現実的なコストの範囲において実現可能な最小長さである。例えば、最近接距離しは、トレンチ絶縁膜13の厚さ以下であってもよい。あるいは、最近接距離しは、トレンチ絶縁膜13の厚さ以上、ゲートトレンチ部10の短手方向の幅以下であってもよい。

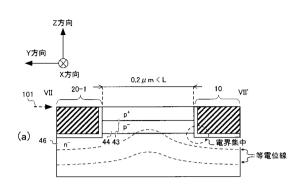

[0072]

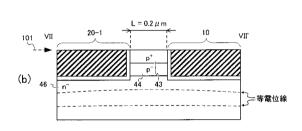

図 7 は、ゲートトレンチ部 1 0 およびダミートレンチ部 2 0 の最近接距離 L と電位分布 との関係を説明する図である。図 7 は、 I G B T のオフ時におけるおもて面 1 0 1 近傍の 等電位分布を概略的に示す。図 7 の ( a ) は最近接距離 L が 0 . 2  $\mu$  m よりも大きい場合を示す図である。図 7 の ( b ) は最近接距離 L が 0 . 2  $\mu$  m である場合を示す図であり、第 1 実施形態に対応する。

[0073]

IGBTのオフ時には、IGBTのボディーダイオードに逆バイアスが印加され、n型のドリフト層46とp型のベース領域44との間に空乏層が拡がる。図7の(a)のように、ゲートトレンチ部10がダミートレンチ部20 1から離れている場合、(b)の場合と比べて空乏層が拡がりやすい。それゆえ、等電位線が+Z方向に凸の形状となり、ゲートトレンチ部10の底部の角部に電界が集中しやすくなる。したがって、図7の(a)の方が(b)よりも絶縁破壊しやすくなる。

[ 0 0 7 4 ]

これに対して、図 7 の ( b ) のように、ゲートトレンチ部 1 0 がダミートレンチ部 2 0

20

30

40

50

1 に非常に接近している場合、空乏層が拡がりにくい。それゆえ、等電位分布も略平坦なままとなる。したがって、ゲートトレンチ部 1 0 の底部の角部における電界集中を防ぐことができる。好ましくは、最近接距離 L が、エミッタ電極 5 4 とコレクタ電極 5 6 間に電圧が印加されていないゼロバイアス時に n 型のドリフト層 4 6 に広がるビルトイン空乏層の幅よりも小さくてよい。

# [0075]

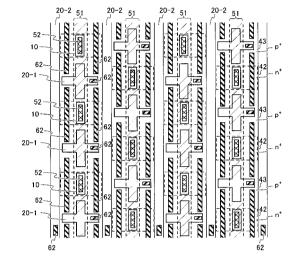

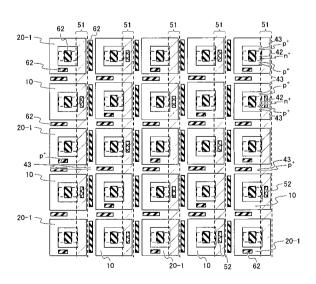

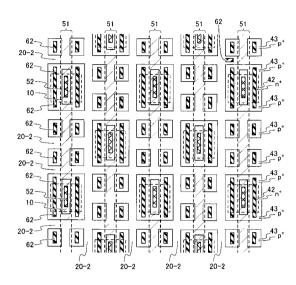

図8は、第2実施形態におけるトランジスタ部80を示す平面概略図である。本例において、ゲートトレンチ部10と十字形状のダミートレンチ部20 1とは、X方向においてもまた交互に設けられる。係る点が第1実施形態と異なる。本例においても第1実施形態と同じ効果を得ることができる。

[0076]

図9は、第3実施形態におけるトランジスタ部80を示す平面概略図である。本例は、第1実施形態における十字形状のダミートレンチ部20 1とU字形状のダミートレンチ部20 2の長手部とをつなげた構造を有する。つまり、本例は、図6における第2のダミー直線部26をY方向に伸ばすことにより、ダミートレンチ部20 1とダミートレンチ部20 2とした構造を有する。これにより、本例では、ドット形状を有するダミートレンチ部20 1が存在しない。係る点が第1実施形態と異なる。

[0077]

本例では、ランナーコンタクト部 5 2 を無くすことにより。ゲートトレンチ部 1 0 を無くすことができる。これにより、ダミートレンチ部 2 0 に対するゲートトレンチ部 1 0 の面積比率を減少させることができる。従って、ドライブ回路の性能に応じてゲート・エミッタ間容量 C G F を調整することができる。

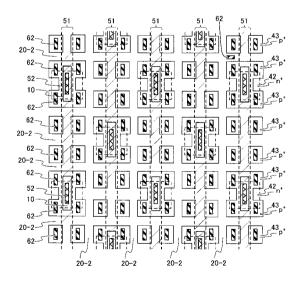

[0078]

図10は、第4実施形態におけるトランジスタ部80を示す平面概略図である。本例は X方向に隣接するゲートトレンチ部10を一列おきに、第3実施形態と比較してY方向に 半ピッチずらした構造を有する。係る点が第3実施形態と異なる。本例においても第3実 施形態と同じ効果を得ることができる。本例において1ピッチとは、Y方向において一列 に設けられた複数のゲートトレンチ部10において、隣接する2つのゲートトレンチ部1 0の各中央部分の間隔である。

[0079]

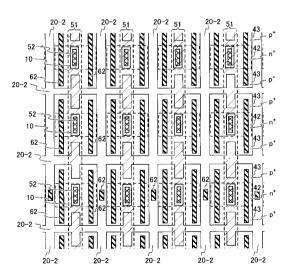

図11は、第5実施形態におけるトランジスタ部80を示す平面概略図である。本例は、ゲートトレンチ部10を直線形状から十字形状を有するドット形状に変形した。また、第1実施形態におけるU字形状のダミートレンチ部20 2の長手部を複数に分断して、十字形状を有するダミートレンチ部20 1とした。これに伴い、第1実施形態においてゲートトレンチ部10をX方向において挟んでいた2つのエミッタコンタクト部62を、Y方向において各々分断した。係る点が第1実施形態と異なる。

[0800]

図12は、第5実施形態におけるトランジスタ部80の領域Bの拡大図である。本例のゲートトレンチ部10は、第1のゲート直線部14と、第2のゲート直線部16とを有する。第1のゲート直線部14と第2のゲート直線部16とは交差する。第1のゲート直線部14は、ゲートランナー51の延伸方向であるY方向に伸びる。これに対して、第2のゲート直線部16は、ゲートランナー51の延伸方向に直交する方向であるX方向に伸びる。

[0081]

本例は、ゲートトレンチ部 1 0 と Y 方向において交互に設けられる第 1 のダミートレンチ部 2 0 1 を有する。また、ゲートトレンチ部 1 0 および第 1 のダミートレンチ部 2 0 1 に対して X 方向に隣接し、 Y 方向沿って配置される第 2 のダミートレンチ部 2 0 1 を有する。第 1 および第 2 のダミートレンチ部 2 0 1 の各々は、 X 方向に伸びる第 1 のダミー直線部 2 4 と、 Y 方向に伸びる第 2 のダミー直線部 2 6 とを有する。第 1 のダミー

20

30

40

50

直線部24と第2のダミー直線部26とは交差する。

## [0082]

第2のダミートレンチ部20 1は、互いに隣接してY方向に一列に設けられる。第2のダミートレンチ部20 1の第2のダミー直線部26は、Y方向においてゲートトレンチ部10と第1のダミートレンチ部20 1に挟まれる。本例では、第2のダミートレンチ部20 1の第2のダミー直線部26とゲートトレンチ部10の+Y方向端部との最近接距離しが0.2μmである。また、第2のダミートレンチ部20 1の第2のダミー直線部26と第1のダミートレンチ部20 1の・Y方向端部との最近接距離しが0.2μmである。これにより、図7の例と同様の効果を得ることができる。

## [0083]

本例では、ゲートトレンチ部10が十字形状を有する。十字形状の交差部の底部は、ダミートレンチ部20 1と同様に交差しない部分よりも深くなる。本例の場合、ゲートトレンチ部10の交差部は、周囲を囲むダミートレンチ部20 1の十字形状の交差部で囲まれる。そのため、ゲートトレンチ部10の交差部の底部より、ダミートレンチ部20 1の交差部の底部が多く配置される。これにより、交差部の底部における電界強度はゲートトレンチ部10に集中することなく、均等に分布することが可能となる。

## [0084]

ダミートレンチ部20 1上に設けられるエミッタコンタクト部62は、ダミートレンチ部20 1上のうち、ゲートランナー51上以外の位置に設けられる。本例のエミッタコンタクト部62は、ゲートランナー51上に位置する第2のダミー直線部26よりも+X方向に設けられる。これにより、ダミートレンチ部20 1のトレンチ電極22にエミッタ電位を供給することができる。また、エミッタコンタクト部62をゲートランナー51上に移動させることにより、エミッタコンタクト部62に代えてランナーコンタクト部52としてもよい。これとは逆に、ランナーコンタクト部52をゲートランナー51上以外の位置に移動させることにより、ランナーコンタクト部52に代えてエミッタコンタクト部62としてもよい。

# [0085]

このように、本例では、第1のダミートレンチ部20 1をゲートトレンチ部10に変形すること、および、ゲートトレンチ部10を第1のダミートレンチ部20 1に変形することが容易となる。つまり、コンタクト部の位置変更により、ダミートレンチ部20に対するゲートトレンチ部10の面積比率を変えることができる。本例では、面積比率を増加することも減少することもできる。これにより、ドライブ回路の性能に応じてゲート・エミッタ間容量 C 。 F を調整することができる。

# [0086]

図13は、第6実施形態におけるトランジスタ部80を示す平面概略図である。本例のゲートトレンチ部10は、半導体基板40のおもて面101に対して環状に設けられる。ダミートレンチ部20 1 も、ゲートトレンチ部10と同様に環状に設けられる。環状形状において、内周は8μmであってよく、外周は16μmであってよい。それゆえ、環状形状もドット形状であると見なすことができる。ゲートトレンチ部10とダミートレンチ部20 1 とは、X方向およびY方向において交互に設けられる。これにより、環状のゲートトレンチ部10は、四方を4つのダミートレンチ部20 1 により囲まれている。なお、本例では、長手部を有するダミートレンチ部20 2 を有さない。

## [0087]

20

30

40

50

#### [0088]

ゲートトレンチ部10とダミートレンチ部20 1との間における格子形状に連結された領域は、p + 型のコンタクト領域43である。p + 型のコンタクト領域43上には、エミッタコンタクト部62が設けられる。本例では、格子形状のp + 型のコンタクト領域43のうち、Y方向およびX方向の辺領域(すなわち、交点を除く領域)に、複数のエミッタコンタクト部62が設けられる。辺領域に設けられた複数のエミッタコンタクト部62は、互いに分断されていてよい。

## [0089]

本例においても、ゲートトレンチ部10のランナーコンタクト部52とダミートレンチ部20 1のエミッタコンタクト部62とを適切に入れ替えることにより、ダミートレンチ部20に対するゲートトレンチ部10の面積比率を変えることができる。これにより、ドライブ回路の性能に応じてゲート・エミッタ間容量 C G E を調整することができる。

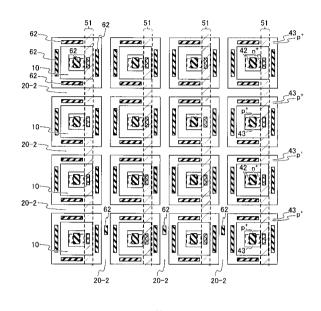

[0090]

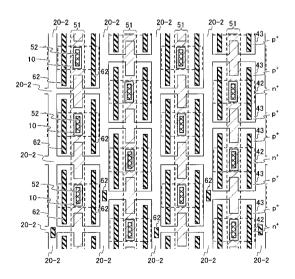

図14は、第7実施形態におけるトランジスタ部80を示す平面概略図である。本例は、第5実施形態の変形例に相当する。本例では、第5実施形態における第2のゲート直線部16とダミートレンチ部20 2に変更した。また、本例では、第5実施形態のダミートレンチ部20 2において、第1のダミー直線部24 2をY方向に伸ばし、第2のダミー直線部26 2をX方向に伸ばした。これにより、ダミートレンチ部20 2は分断されることなく全て連結された。本例においても、ドライブ回路の性能に応じてゲート・エミッタ間容量C<sub>GE</sub>を調整することができる。

[0091]

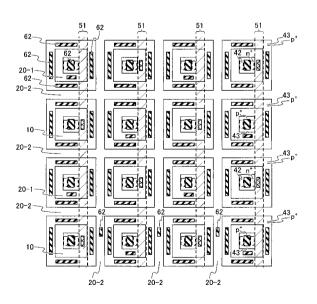

図15は、第8実施形態におけるトランジスタ部80を示す平面概略図である。本例は、第7実施形態の変形例である。本例では、第7実施形態のゲートトレンチ部10周りの p <sup>+</sup>型のコンタクト領域43を長方形とした。これに伴い、 p <sup>+</sup>型のコンタクト領域43上に設けられるエミッタコンタクト部62をY方向に伸ばして連結した。これにより、第7実施形態において4つであったゲートトレンチ部10周りのエミッタコンタクト部62を2つとした。本例においても、第7実施形態と同様の効果を得ることができる。

[0092]

図16は、第9実施形態におけるトランジスタ部80を示す平面概略図である。本例は、第6実施形態に類似する実施形態である。ただし、本例は、ダミートレンチ部20 1を設けずにダミートレンチ部20 2を設ける。また、本例では、長方形の環状を有するゲートトレンチ部10の周りを囲むように、長方形の環状の不純物注入領域としてのp<sup>†</sup>型のコンタクト領域43を設ける。さらに、環状のp<sup>†</sup>型のコンタクト領域43をユニットセルとして、複数のユニットセルをX方向およびY方向に行列状に複数配置した。加えて、各ユニットセルを分離するようにX方向およびY方向に延伸するダミートレンチ部20 2を設けた。これにより、1つのダミートレンチ部20 2が全てのゲートトレンチ部10を囲んでいる。

[0093]

本例においても、ゲートトレンチ部10のランナーコンタクト部52とダミートレンチ部20 1のエミッタコンタクト部62とを適切に入れ替えることにより、ダミートレンチ部20に対するゲートトレンチ部10の面積比率を変えることができる。これにより、ドライブ回路の性能に応じてゲート・エミッタ間容量C<sub>GE</sub>を調整することができる。

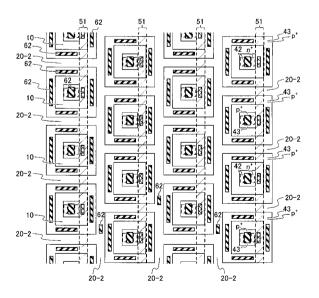

[0094]

図17は、第10実施形態におけるトランジスタ部80を示す平面概略図である。本例は、第9実施形態におけるゲートトレンチ部10の一部をダミートレンチ部20 1とした例である。特に本例では、ゲートトレンチ部10をX方向およびY方向において1つおきにダミートレンチ部20 1とした。係る点において、第9実施例と異なる。本例においても第9実施形態と同じ効果を有する。

[ 0 0 9 5 ]

図18は、第11実施形態におけるトランジスタ部80を示す平面概略図である。本例

20

30

40

50

では、 X 方向において隣接する環状の p <sup>†</sup> 型のコンタクト領域 4 3 が、 Y 方向に半ピッチずれて設けられる。係る点において第 9 実施形態と異なる。本例においても第 9 実施形態と同じ効果を有する。

[0096]

図 1 9 は、第 1 2 実施形態におけるトランジスタ部 8 0 を示す平面概略図である。本例では、X 方向において隣接する環状のp  $^{+}$  型のコンタクト領域 4 3 は、Y 方向に半ピッチずれて設けられる。係る点において第 1 0 実施形態と異なる。本例においても第 1 0 実施形態と同じ効果を有する。

[0097]

図20は、比較例における半導体装置200の上面を示す平面概略図である。本例のトランジスタ部80は、ゲートトレンチ部10とダミートレンチ部20 2とを有する。また、比較例のダイオード部90は、U字形状のエミッタトレンチ部30 2を有する。なお、p 型のベース領域44およびp 型のウェル領域45の配置パターンは、基本的には図1の例と同じである。ただし、n 型のエミッタ領域42およびp 型のコンタクト領域43は、Y方向において等間隔に交互に設けられている点が、図1の例と異なる。

[0098]

本例のゲートトレンチ部 1 0 は、U字形状の長手部および短手部を有する。本例のゲートトレンチ部 1 0 は、ドット形状ではない。ゲートトレンチ部 1 0 の長手部は、トランジスタ部 8 0 に渡って Y 方向に延伸する。ゲートトレンチ部 1 0 は、 Y 方向端部の短手部のランナーコンタクト部 5 2 において、ポリシリコン層 1 1 0 に直接接続する。ポリシリコン層 1 1 0 は、ランナーコンタクト部 5 3 において、ゲート電極 5 0 に直接接続する。

[0099]

ダミートレンチ部 2 0 2 は、ゲートトレンチ部 1 0 の 2 つの長手部の間を Y 方向に延伸する長手部を有する。ダミートレンチ部 2 0 2 もまた、ドット形状ではない。ダミートレンチ部 2 0 2 は、 Y 方向の端部のエミッタコンタクト部 6 2 においてポリシリコン層 1 1 0 を介してエミッタ電極 5 4 と直接接続する。

[0100]

エミッタトレンチ部 3 0 2 の U 字形状の短手部は、ポリシリコン層 1 1 0 よりも + Y 方向に設けられる。エミッタトレンチ部 3 0 2 は、エミッタコンタクト部 6 2 においてポリシリコン層 1 1 0 を介してエミッタ電極 5 4 に電気的に接続する。

[0101]

図 2 1 は、オン電圧(Von)とオフ損失(Eoff)との関係を示す図である。横軸はオン電圧[V]である。縦軸は、IGBTをスイッチングオフした場合の損失[mJ]である。第 1 から第 1 2 実施形態においては、比較例と比べてメサ幅を狭くすることによりIE効果を得ることができるので、比較例よりもオン電圧を低くすることができる。

[0102]

以上、本発明を実施の形態を用いて説明したが、本発明の技術的範囲は上記実施の形態に記載の範囲には限定されない。上記実施の形態に、多様な変更又は改良を加えることが可能であることが当業者に明らかである。その様な変更又は改良を加えた形態も本発明の技術的範囲に含まれ得ることが、特許請求の範囲の記載から明らかである。

[ 0 1 0 3 ]

特許請求の範囲、明細書、および図面中において示した装置、システム、プログラム、および方法における動作、手順、ステップ、および段階等の各処理の実行順序は、特段「より前に」、「先立って」等と明示しておらず、また、前の処理の出力を後の処理で用いるのでない限り、任意の順序で実現しうることに留意すべきである。特許請求の範囲、明細書、および図面中の動作フローに関して、便宜上「まず、」、「次に、」等を用いて説明したとしても、この順序で実施することが必須であることを意味するものではない。

【符号の説明】

[0104]

10・・ゲートトレンチ部、12・・トレンチ電極、13・・トレンチ絶縁膜、14・

・第1のゲート直線部、16・・第2のゲート直線部、20・・ダミートレンチ部、22・・トレンチ電極、23・・トレンチ絶縁膜、24・・第1のダミー直線部、26・・第2のダミー直線部、30・・エミッタトレンチ部、32・・トレンチ電極、33・・トレンチ絶縁膜、40・・半導体基板、42・・n・型のエミッタ領域、43・・p・型のコンタクト領域、44・・p・型のベース領域、45・・p・型のウェル領域、46・・n・型のドリフト層、47・・n・型のバッファ層、48・・p・型のコレクタ層、49・・n・型のカソード層、50・・ゲート電極、51・・ゲートランナー、52・・ランナーコンタクト部、53・・ランナーコンタクト部、54・・エミッタ電極、56・・コレクタ電極、62・・エミッタコンタクト部、72・・第1の層間絶縁膜、74・・第2の層間絶縁膜、80・・トランジスタ部、90・・ダイオード部、100・・半導体装置、101・・おもて面、102・・うら面、110・・ポリシリコン層、200・・半導体

【図2】

【図1】

【図3】

【図4】

【図5】

【図6】

# 【図7】

80

# 【図9】

【図10】

# 【図11】

# 【図12】

# 【図13】

# 【図14】

# 【図15】

【図16】

80

# 【図17】

【図18】

# 【図19】

# 【図20】

# 【図21】

# フロントページの続き

| (51) Int.CI. |        |           | FΙ      |        |         | テーマコード(参考) |

|--------------|--------|-----------|---------|--------|---------|------------|

| H 0 1 L      | 27/088 | (2006.01) | H 0 1 L | 29/78  | 6 5 2 S |            |

| H 0 1 L      | 21/265 | (2006.01) | H 0 1 L | 29/78  | 6 5 8 H |            |

|              |        |           | H 0 1 L | 29/78  | 6 5 8 A |            |

|              |        |           | H 0 1 L | 29/78  | 6 5 5 G |            |

|              |        |           | H 0 1 L | 27/06  | 102A    |            |

|              |        |           | H 0 1 L | 27/08  | 1 0 2 E |            |

|              |        |           | H 0 1 L | 29/78  | 6 5 2 K |            |

|              |        |           | H 0 1 L | 21/265 | 6 0 2 C |            |