(19) 대한민국특허청(KR)

(12) 등록특허공보(B1)

(45) 공고일자 2012년06월01일

(11) 등록번호 10-1150552

(24) 등록일자 2012년05월21일

- (51) 국제특허분류(Int. C1.)

*H01L 27/108* (2006.01)

- (21) 출원번호 10-2009-0120159

(22) 출원일자 2009년12월04일

심사청구일자 2009년12월04일

- (65) 공개번호 10-2011-0063204

(43) 공개일자 2011년06월10일

- (56) 선행기술조사문현

JP2003078033 A\*

KR100673133 B1

KR1020080089016 A

\*는 심사관에 의하여 인용된 문현

- (73) 특허권자

**에스케이하이닉스 주식회사**

경기도 이천시 부발읍 경충대로 2091

(72) 발명자

**김도형**

서울특별시 강남구 도곡로3길 13, 르메이에르

608호 (역삼동)

- (74) 대리인

**특허법인태평양**

전체 청구항 수 : 총 10 항

심사관 : 이우리

(54) 발명의 명칭 반도체 소자 및 그의 형성 방법

### (57) 요약

본 발명의 반도체 소자는 셀 영역에 형성된 소자분리막에 의해 정의되는 활성영역과 상기 활성영역상에 구비되며 상기 소자분리막 표면과 동일한 높이를 갖는 도전층 및 상기 소자분리막과 이웃한 상기 도전층에 접속되는 라인타입의 저장전극 콘택을 포함하는 것을 특징으로 함으로써, 활성영역과 저장전극의 전기적 접속을 원활하게 하여 저항의 증가를 방지하고, 저장전극이 접속되는 영역을 확보하여 구조적 안정성을 최대화함으로써 반도체 소자가 고집적화되어 미세한 피치를 갖더라도 성능이 저하되지 않는 효과를 제공한다.

**대 표 도 - 도2**

## 특허청구의 범위

### 청구항 1

셀 영역에 형성된 소자분리막에 의해 정의되는 활성영역;

상기 활성영역 및 상기 소자분리막 내에 구비되며, 상기 활성영역을 삼분할하는 매립형 게이트;

상기 활성영역 상에 구비되며 상기 소자분리막 표면과 동일한 높이를 갖는 도전층;

상기 삼분할된 상기 활성영역의 에지부 양측 상부에 구비된 상기 도전층에 접속되는 저장전극 콘택; 및

상기 삼분할된 상기 활성영역에 중앙부 상부에 구비된 상기 도전층과 접속되는 라인 타입의 다마신 비트라인

을 포함하는 것을 특징으로 하는 반도체 소자.

### 청구항 2

청구항 1에 있어서,

상기 도전층 상부의 양측에 구비되는 절연막을 포함하는 것을 특징으로 하는 반도체 소자.

### 청구항 3

청구항 2에 있어서,

상기 절연막은 실링질화막인 것을 특징으로 하는 반도체 소자.

### 청구항 4

청구항 1에 있어서,

상기 도전층은 랜딩플러그 패드인 것을 특징으로 하는 반도체 소자.

### 청구항 5

삭제

### 청구항 6

셀 영역에 형성된 소자분리막에 의해 정의되는 활성영역을 형성하는 단계;

상기 활성영역 및 상기 소자분리막 내에 구비되는 매립형 게이트를 형성하는 단계;

상기 활성영역상에 구비되며 상기 소자분리막 표면과 동일한 높이를 갖는 도전층을 형성하는 단계;

상기 도전층 상부에 절연막을 형성하는 단계;

상기 절연막을 노출시키는 제 1 저장전극 콘택 예정영역이 구비된 충간절연막을 형성하는 단계;

상기 제 1 저장전극 콘택 예정영역에 매립층을 형성하는 단계;

상기 도전층과 접속되는 다마신 비트라인을 형성하는 단계; 및

상기 도전층에 접속되며, 상기 매립형 게이트와 평행한 라인타입의 저장전극 콘택을 형성하는 단계

를 포함하는 것을 특징으로 하는 반도체 소자의 형성 방법.

### 청구항 7

청구항 6에 있어서,

상기 도전층을 형성하는 단계 이후

상기 도전층, 상기 소자분리막 및 상기 도전층 상부의 양측에 구비되는 절연막을 형성하는 단계를 포함하는

것을 특징으로 하는 반도체 소자의 형성 방법.

**청구항 8**

청구항 7에 있어서,

상기 절연막을 형성하는 단계는

실링질화막을 형성하는 것을 특징으로 하는 반도체 소자의 형성 방법.

**청구항 9**

삭제

**청구항 10**

청구항 6에 있어서,

상기 다마신 비트라인을 형성하는 단계는

상기 활성영역에 구비된 도전층이 노출되도록 상기 매립층 및 상기 층간절연막을 식각하여 다마신 트렌치를 형성하는 단계;

상기 다마신 트렌치 측벽에 스페이서를 형성하는 단계; 및

상기 스페이서 측벽에 구비되고 상기 도전층과 접속되는 비트라인 도전층을 형성하는 단계를 포함하는 것을 특징으로 하는 반도체 소자의 형성 방법.

**청구항 11**

청구항 10에 있어서,

상기 저장전극 콘택을 형성하는 단계는

상기 소자분리막과 이웃한 상기 도전층이 노출되도록 상기 매립층 및 상기 절연막을 식각하여 제 2 저장전극 콘택 예정영역을 형성하는 단계; 및

상기 제 2 저장전극 콘택 예정영역을 매립하는 도전층을 형성하는 단계를 포함하는 것을 특징으로 하는 반도체 소자의 형성 방법.

**청구항 12**

청구항 11에 있어서,

상기 제 2 저장전극 콘택 예정영역을 형성하는 단계는

상기 매립층 및 상기 층간절연막의 식각선택비를 이용하여 상기 매립층을 제거하는 것을 특징으로 하는 반도체 소자의 형성 방법.

**명세서****발명의 상세한 설명****기술 분야**

[0001] 본 발명은 반도체 소자 및 그의 형성 방법에 관한 것으로, 보다 자세하게는 저장전극 콘택의 마진을 향상시킬 수 있는 반도체 소자 및 그의 형성 방법에 관한 것이다.

**배경 기술**

[0002] 최근의 대부분의 전자 제품들(electronic appliances)은 반도체 장치(semiconductor devices)를 구비한다. 상기 반도체 장치는 트랜지스터, 저항 및 커패시터 등의 전자 부품(electronic element)들을 구비하며, 이들 전자 부품들은 상기 전자 제품들의 부분적 기능을 수행할 수 있도록 설계된 후, 반도체 기판 상에 접적된다. 예를 들면, 컴퓨터 또는 디지털 카메라 등의 전자 제품들은 정보 저장을 위한 메모리 칩(memory chip), 정보 처리를 위한 처리 칩(processing chip) 등의 반도체 장치들을 구비하고, 상기 메모리 칩 및 처리 칩은 반도체

기판 상에 접적된 상기 전자 부품들을 구비한다.

[0003] 한편, 상기 반도체 장치들은 소비자가 요구하는 우수한 성능 및 저렴한 가격을 충족시키기 위해, 점점 더 고접적화될 필요가 있다. 반도체 메모리 소자의 접적도가 높아지면서 디자인 룰(design rule)이 감소하게 되어 반도체 소자의 패턴도 미세화되고 있다. 반도체 소자의 극미세화 및 고접적화가 진행됨에 따라 메모리 용량의 증가에 비례하여 전체적인 칩(chip) 면적은 증가되고 있지만 실제로 반도체 소자의 패턴이 형성되는 셀(cell) 영역의 면적은 감소되고 있다. 따라서, 원하는 메모리 용량을 확보하기 위해서는 한정된 셀 영역 내에 보다 많은 패턴이 형성되어야만 하므로, 패턴의 선폭(critical dimension)이 감소된 미세 패턴을 형성하여야 한다.

[0004] 미세 패턴을 형성하는 방법에는 노광마스크(photo mask)로서 위상반전마스크(phase shift mask)를 사용하는 방법이나, 이미지 콘트라스트를 향상시킬 수 있는 별도의 박막을 웨이퍼 상에 형성하는 씨.이.엘(contrast enhancement layer; CEL) 방법이나, 두층의 감광막 사이에 에스.오.지(spin on glass; SOG)등의 중간층을 개재시킨 삼층레지스터(Tri layer resister; 이하 TLR이라 칭함) 방법 또는 감광막의 상측에 선택적으로 실리콘을 주입시키는 실리레이션 방법 등이 개발되어 분해능 한계치를 낮추고 있다.

[0005] 한편, 상하의 도전배선을 연결하는 콘택은 라인/스페이스 패턴에 비해 디자인률에 큰 영향을 받게 된다. 즉, 소자가 고접적화 되어감에 따라 자체의 크기와 주변배선과의 간격이 감소함에 따라 콘택의 지름과 깊이의 비인 에스팩트비(aspect ratio)가 증가하게 되어 콘택을 형성하는 공정은 점차 고접적화되는 반도체 소자의 형성 방법에서 중요하다. 따라서, 다층의 도전배선을 구비하는 고접적 반도체소자에서는 콘택 형성 공정에서 마스크들간의 정확하고 엄격한 정렬이 요구되어 공정여유도가 감소되거나, 여유없이 공정을 진행하여야하는 어려움이 있다.

[0006] 특히, 랜딩플러그 공정 시에 랜딩플러그와 게이트 또는 랜딩플러그와 리세스 게이트(recess gate)의 자기정렬 폐일(SAC Fail:Self align contact Fail)이 유발되어 수율을 저하시키는 문제를 유발한다. 따라서, 게이트 또는 리세스 게이트 구조에서 매립형 게이트(buried gate) 구조로 변화시켜 랜딩플러그와의 자기정렬폐일을 방지하는 기술이 제안되었다.

[0007] 그러나, 매립형 게이트 구조 또한 저장전극 콘택과 비트라인의 자기정렬폐일이 유발되거나 저장전극 콘택이 랜딩플러그와 접속되지 않는 문제가 여전히 발생하게 되었다.

## 발명의 내용

### 해결 하고자 하는 과제

[0008] 본 발명은 반도체 소자의 고접적으로 인하여 저장전극 콘택을 홀 타입으로 패터닝하는 경우 저장전극 콘택의 하부가 오픈되지 않거나 브릿지가 유발되고, 활성영역과 접속되는 면적이 줄어들어 저항이 증가되는 문제를 해결하고자 한다.

### 과제 해결수단

[0009] 본 발명의 반도체 소자는 셀 영역에 형성된 소자분리막에 의해 정의되는 활성영역과 상기 활성영역상에 구비되며 상기 소자분리막 표면과 동일한 높이를 갖는 도전층 및 상기 소자분리막과 이웃한 상기 도전층에 접속되는 라인타입의 저장전극 콘택을 포함하는 것을 특징으로 한다.

그리고, 상기 도전층 상부의 양측에 구비되는 절연막을 포함하는 것을 특징으로 한다.

그리고, 상기 절연막은 실링질화막인 것을 특징으로 한다.

[0010] 이때, 상기 도전층은 랜딩플러그 패드인 것을 특징으로 한다.

[0011] 그리고, 상기 소자분리막 및 상기 활성영역 내에 구비되는 매립형 게이트를 더 포함하는 것을 특징으로 한다.

[0012] 그리고, 상기 활성영역에 구비된 상기 도전층과 접속되는 다마신 비트라인을 포함하는 것을 특징으로 한다.

[0013] 삭제

[0014] 본 발명의 반도체 소자의 형성 방법은 셀 영역에 형성된 소자분리막에 의해 정의되는 활성영역을 형성하는 단계와 상기 활성영역상에 구비되며 상기 소자분리막 표면과 동일한 높이를 갖는 도전층을 형성하는 단계와 상기 소자분리막과 이웃한 상기 도전층에 접속되는 라인타입의 저장전극 콘택을 형성하는 단계를 포함하는 것을

특징으로 한다.

그리고, 상기 도전층을 형성하는 단계 이후 상기 도전층, 상기 소자분리막 및 상기 도전층 상부의 양측에 구비되는 절연막을 형성하는 단계를 포함하는 것을 특징으로 한다.

그리고, 상기 절연막을 형성하는 단계는 실링질화막을 형성하는 것을 특징으로 한다.

[0015]

삭제

[0016]

삭제

[0017]

그리고, 상기 도전층을 형성하는 단계 이후, 상기 도전층 상부에 상기 절연막을 형성하는 단계와 상기 절연막을 노출시키는 제 1 저장전극 콘택 예정영역이 구비된 충간절연막을 형성하는 단계와 상기 제 1 저장전극 콘택 예정영역에 매립층을 형성하는 단계 및 상기 도전층과 접속되는 다마신 비트라인을 형성하는 단계를 더 포함하는 것을 특징으로 한다.

[0018]

그리고, 상기 다마신 비트라인을 형성하는 단계는 상기 활성영역에 구비된 도전층이 노출되도록 상기 매립층 및 상기 충간절연막을 식각하여 다마신 트렌치를 형성하는 단계와 상기 다마신 트렌치 측벽에 스페이서를 형성하는 단계 및 상기 스페이서 측벽에 구비되고 상기 도전층과 접속되는 비트라인 도전층을 형성하는 단계를 포함하는 것을 특징으로 한다.

[0019]

그리고, 상기 저장전극 콘택을 형성하는 단계는 상기 소자분리막과 이웃한 상기 도전층이 노출되도록 상기 매립층 및 상기 절연막을 식각하여 제 2 저장전극 콘택 예정영역을 형성하는 단계 및 상기 제 2 저장전극 콘택 예정영역을 매립하는 도전층을 형성하는 단계를 포함하는 것을 특징으로 한다.

[0020]

그리고, 상기 제 2 저장전극 콘택 예정영역을 형성하는 단계는 상기 매립층 및 상기 충간절연막의 식각선택비를 이용하여 상기 매립층을 제거하는 것을 특징으로 한다.

## 효과

[0021]

본 발명은 활성영역과 저장전극의 전기적 접속을 원활하게 하여 저항의 증가를 방지하고, 저장전극이 접속되는 영역을 확보하여 구조적 안정성을 최대화함으로써 반도체 소자가 고집적화되어 미세한 퍼치를 갖더라도 성능이 저하되지 않는 효과를 제공한다.

## 발명의 실시를 위한 구체적인 내용

[0022]

이하에서는 본 발명에 따라 첨부된 실시예를 참조하여 상세히 설명하기로 한다.

[0023]

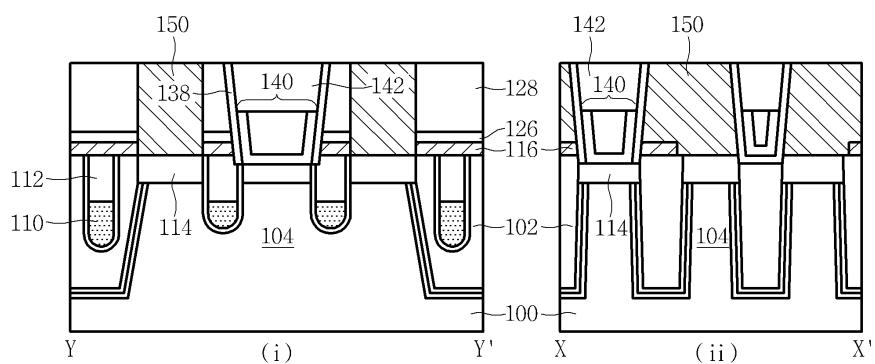

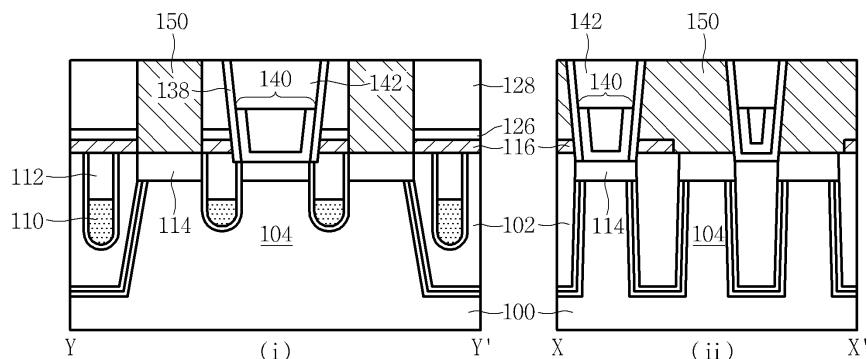

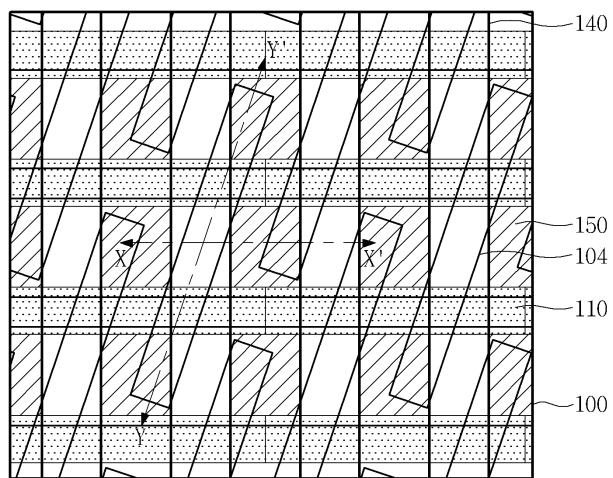

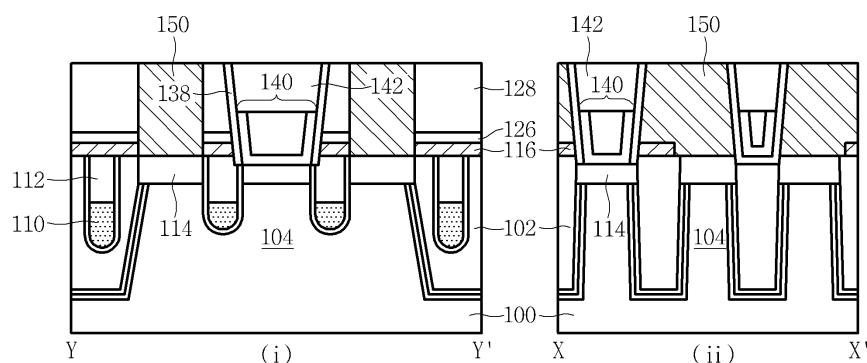

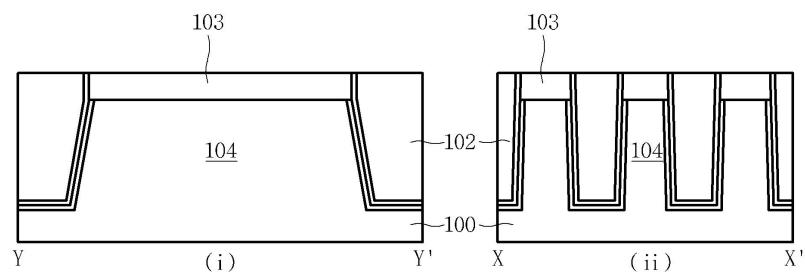

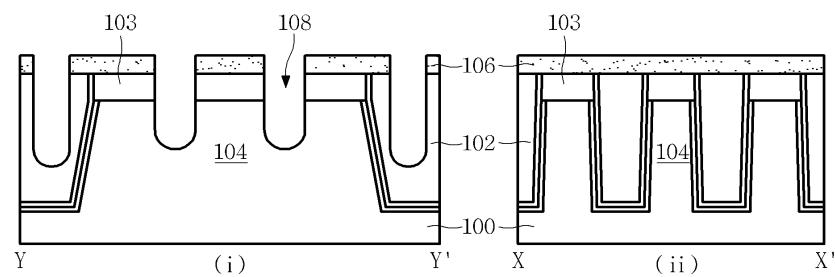

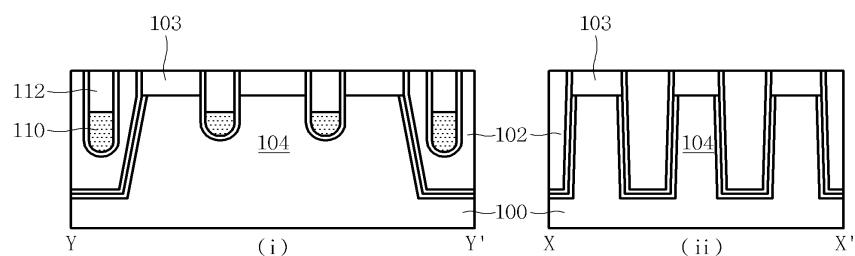

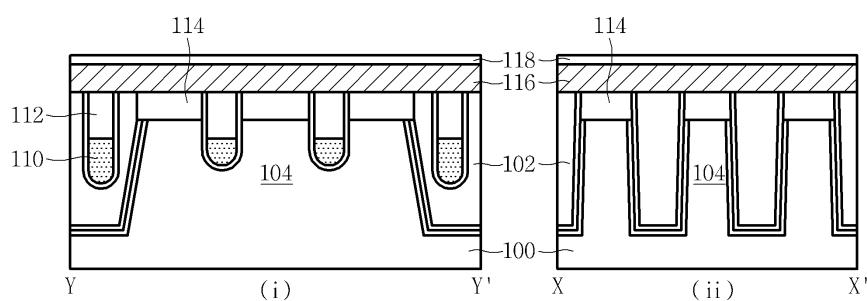

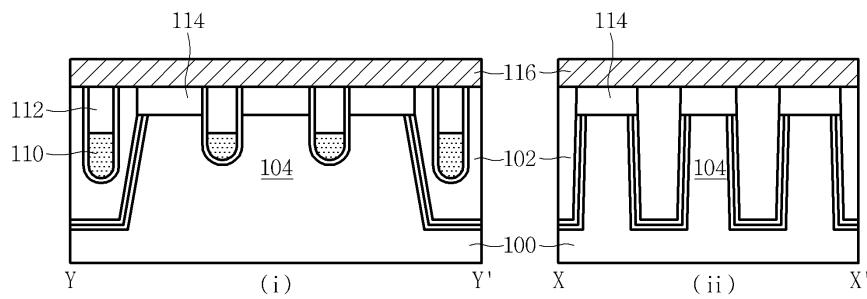

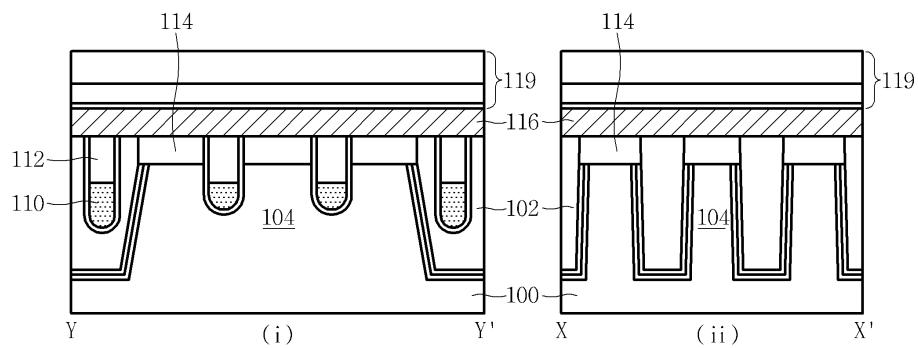

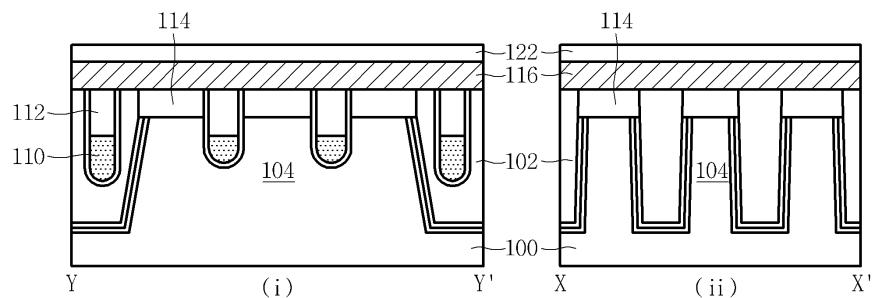

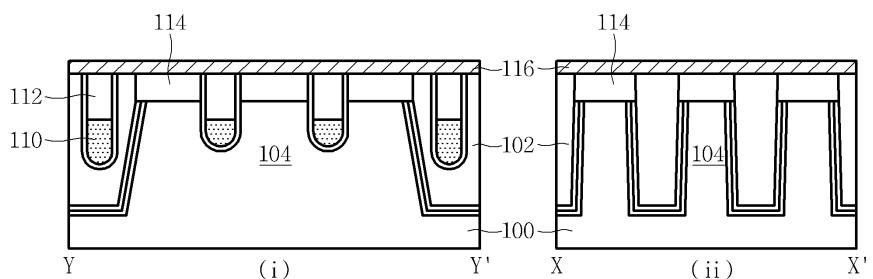

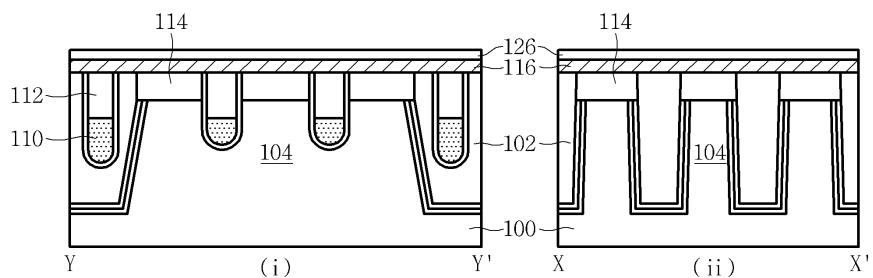

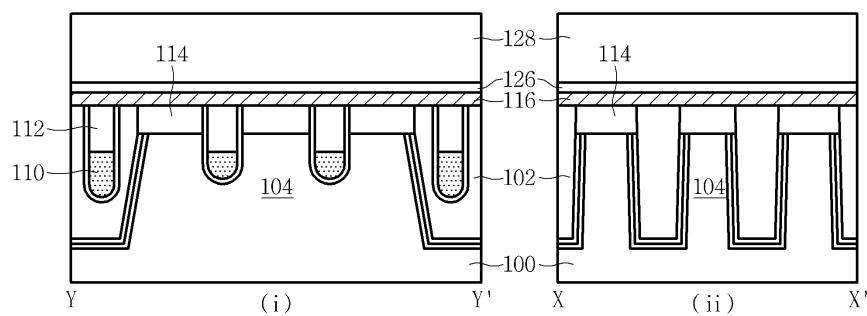

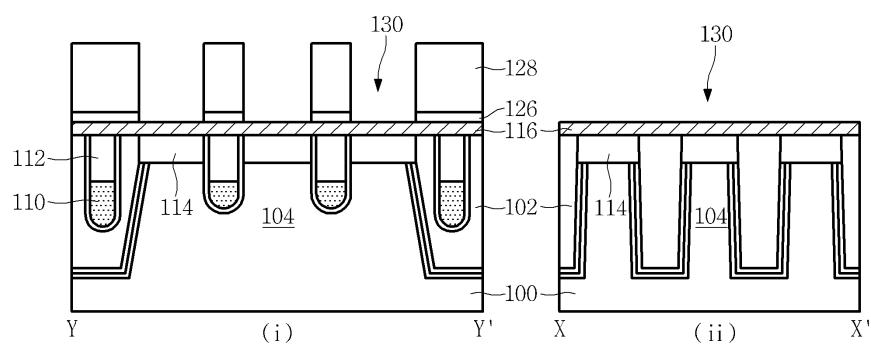

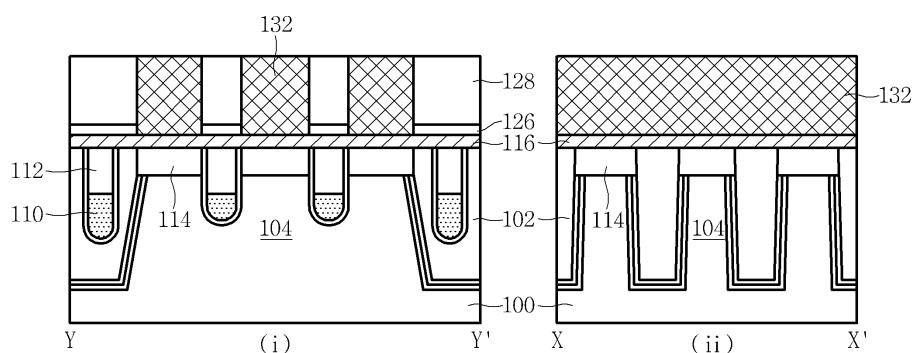

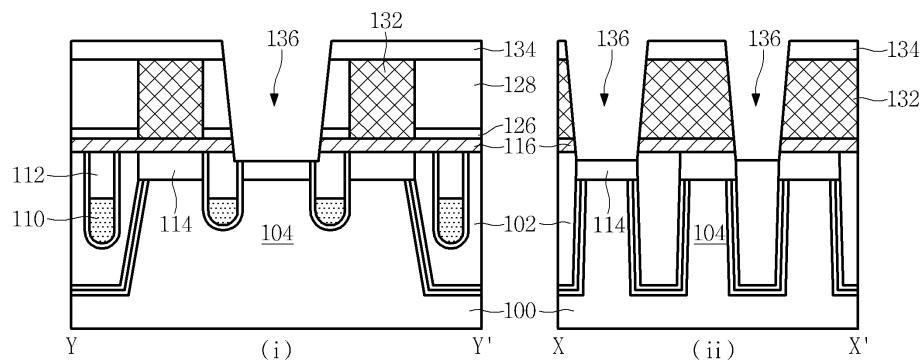

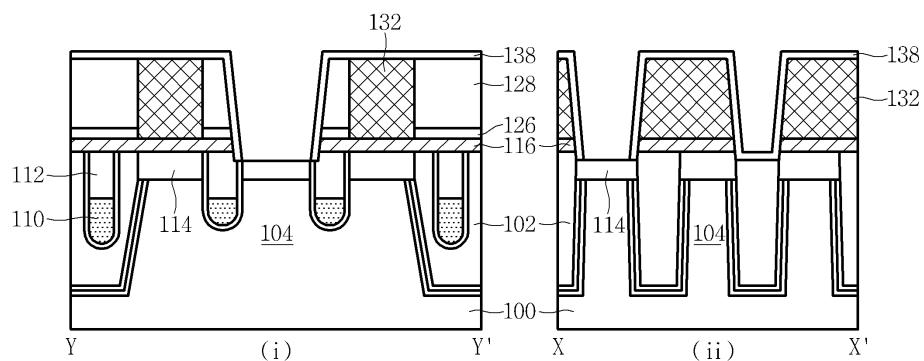

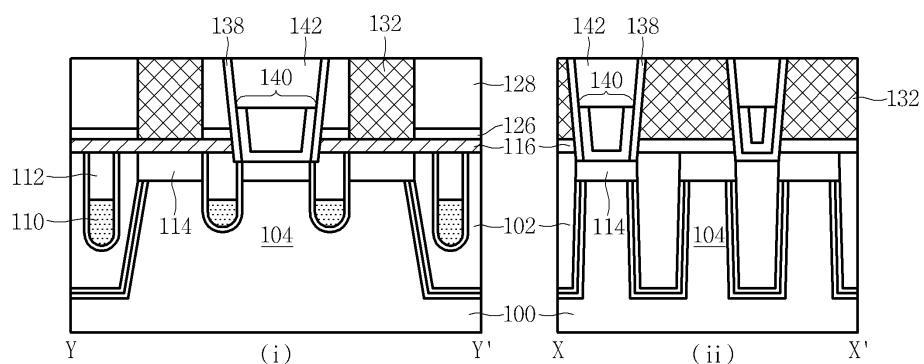

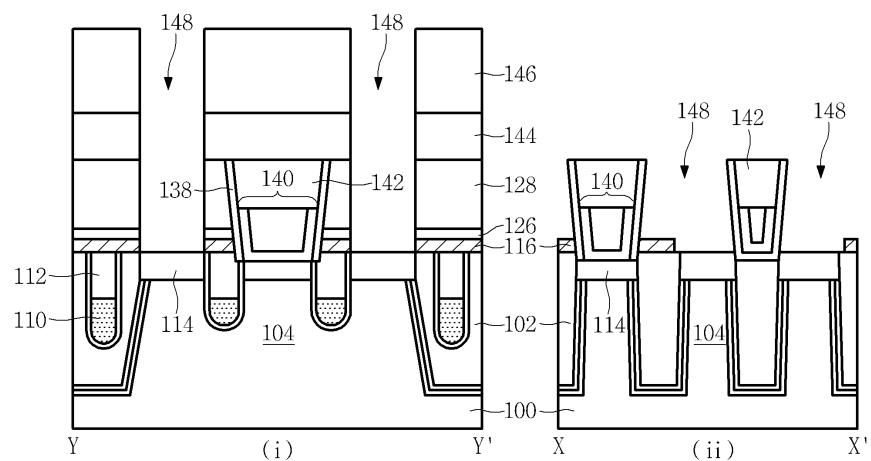

도 1은 본 발명에 따른 반도체 소자를 나타낸 평면도이고, 도 2는 본 발명에 따른 반도체 소자를 나타낸 단면도이며, 도 3a 내지 도 3q는 본 발명에 따른 반도체 소자의 형성 방법을 나타낸 단면도로서, (i)은 셀 영역을  $y-y'$ 로 자른 단면도이고, (ii)는 셀 영역을  $x-x'$ 로 자른 단면도이다.

[0024]

도 2에 도시된 바와 같이, 본 발명에 따른 반도체 소자는 반도체 기판(100)에 형성된 소자분리막(102)과, 소자분리막(102) 및 활성영역(104) 내에 구비되어 활성영역(104)을 삼분할하는 매립형 게이트(110)와, 매립형 게이트(110)에 의해 분할된 활성영역(104) 상에 형성되며 소자분리막(102) 표면과 동일한 높이를 갖는 도전층(114)과, 활성영역(104)의 중앙부에 구비된 도전층(114)에 접속되며 매립형 게이트(110)의 장축방향과 수직한 라인타입의 다마신 비트라인(140)과, 소자분리막(102)과 이웃한 도전층(114)에 접속되는 저장전극 콘택(150)을 포함한다.

[0025]

상술한 바와 같이, 본 발명에 따른 반도체 소자는 라인 타입의 저장전극 콘택(150)을 구비함으로써 저장전극과 용이하게 접속되도록 하여 반도체 소자의 특성을 향상시킬 수 있다.

[0026]

도 3a에 도시된 바와 같이, 반도체 기판(100) 상에 패드산화막(미도시) 및 패드질화막(103)을 형성한 후, 패드질화막(103), 패드산화막 및 반도체 기판(100)을 식각하여 소자분리막(102)을 정의하기 위한 트렌치(미도시)를 형성한다. 그리고, 트렌치(미도시)를 포함하는 전체 상부에 측벽산화막, 라이너 질화막, 라이너 산화막을 형성한 후, 트렌치(미도시)가 매립되도록 SOD막을 형성한 후, 평탄화 공정을 수행하여 소자분리막(102)을 완성하는 것이 바람직하다. 여기서, 반도체 기판(100) 내에 형성된 소자분리막(102)에 의해 활성

영역(104)이 정의된다.

[0027] 도 3b에 도시된 바와 같이, 소자분리막(102)을 포함하는 전체 상부에 하드마스크패턴(106)을 형성한 후, 하드마스크패턴(106)을 식각마스크로 활성영역(104) 및 소자분리막(102)을 식각하여 매립형 게이트를 형성하기 위한 리세스(108)를 형성한다. 이후, 하드마스크층(106)은 제거한다.

[0028] 도 3c에 도시된 바와 같이, 리세스(108)를 포함하는 전체 상부에 산화막을 형성하고, 도전층(110)을 매립한 후 도전층(110)에 에치백을 수행하여 리세스(108)의 일부만 매립되도록 한다. 여기서, 도전층(110)은 TiN 및 W의 적층구조인 것이 바람직하다. 그 다음, 리세스(108)가 완전히 매립되도록 캡핑산화막(112)을 형성한 후, 캡핑산화막(112)에 평탄화 식각 공정을 수행한다. 이때, 캡핑산화막(112)의 평탄화 식각 공정은 셀 오픈 마스크를 이용하여 셀 영역 (i, ii)의 캡핑산화막(112)만이 제거되도록 하는 것이 바람직하다. 이후, 셀 영역 (i, ii)에 노출된 패드질화막(103)을 제거한다.

[0029] 도 3d 및 도 3e에 도시된 바와 같이, 패드질화막(103)이 제거된 상부에 도전층(114)을 형성한 후, 캡핑산화막(112)이 노출되도록 도전층(114)에 평탄화 식각공정을 수행한다. 이어서, 전체 상부에 실링질화막(116) 및 실링산화막(118)을 형성한다(도 3d). 여기서, 도전층(114)은 랜딩플러그 패드(landing plug pad)인 것이 바람직하다. 이후, 평탄화 공정을 통하여 실링질화막(116)이 노출되도록 실링산화막(118)을 제거한다(도 3e).

[0030] 도 3f에 도시된 바와 같이, 전체 상부에 게이트층(119)을 형성한다. 여기서, 게이트층(119)은 배리어 메탈, 게이트도전층, 하드마스크층의 적층구조인 것이 바람직하다.

[0031] 도 3g에 도시된 바와 같이, 폐리 영역(미도시)의 게이트라인을 정의하기 위한 마스크를 이용하여 게이트층(119) 상부에 마스크 패턴(미도시)을 형성한 후, 이를 식각마스크로 게이트층(119)을 식각하여 폐리 영역에 게이트라인(미도시)을 정의한다. 이 과정에서 셀 영역(i, ii)에 형성된 게이트층(119)은 모두 제거되는 것이 바람직하다. 이어서, 게이트라인(미도시)을 포함하는 전체 상부에 스페이서용 산화막(122)을 형성한다.

[0032] 도 3h 및 도 3i에 도시된 바와 같이, 폐리영역(미도시)의 스페이서용 산화막(122)에 에치백 공정을 수행하여 게이트 스페이서(미도시)을 형성한다. 따라서, 셀 영역(i, ii)의 스페이서용 산화막(122)은 제거된다. 이어서, 도시되지는 않았지만 게이트 스페이서(미도시)을 마스크로 하여 폐리영역의 활성영역에 이온주입공정을 수행하는 것이 바람직하다(도 3h). 그 다음, 셀 영역(i, ii)에 산화막(126)을 형성하고, 폐리 영역(미도시)에는 스페이서 질화막(미도시)을 형성하는 것이 바람직하다(도 3i).

[0033] 도 3j 및 도 3k에 도시된 바와 같이, 전체 상부에 충간절연막(128)을 형성한 후, 폐리 영역의 게이트 상부가 노출되도록 평탄화 식각공정을 수행하는 것이 바람직하다(도 3j). 그 다음, 충간절연막(128) 상부에 저장전극 콘택을 정의하기 위한 마스크 패턴(미도시)을 형성한 후, 마스크 패턴(미도시)을 식각마스크로 실링질화막(116)이 노출되도록 충간절연막(128)을 식각하여 제 1 저장전극 콘택 예정영역(130)을 정의한다(도 3k). 여기서, 마스크 패턴은 라인 앤 스페이스 타입인 것이 바람직하며, 라인 타입으로 패터닝된 충간절연막(128) 사이의 스페이스(space)는 제 1 저장전극 콘택 예정영역(130)을 정의하는 것이 바람직하다. 이때, 실링질화막(116)이 노출되도록 제 1 저장전극 콘택 예정영역(130)이 정의되는 이유는 도전층(114)과 접속되지 않도록 함으로써 후속 공정에서 형성되는 비트라인이 오정렬되는 경우 비트라인과 저장전극 콘택 사이에 쇼트가 유발되는 것을 방지하기 위함이다.

[0034] 도 3l에 도시된 바와 같이, 저장전극 콘택 예정 영역(130)이 매립되도록 전체 상부에 매립층(132)을 형성한 후, 충간절연막(128)이 노출되도록 평탄화 식각 공정을 수행한다. 이때, 매립층(132)은 충간절연막(128)과 상이한 식각선택비를 갖는 것이 바람직하다. 이는 후속 공정에서 저장전극 콘택 예정영역을 정의할 때 충간절연막(128)과의 식각선택비를 이용하여 매립층(132)만이 용이하게 제거되도록 하기 위함이다.

[0035] 도 3m에 도시된 바와 같이, 전체 상부에 하드마스크층(134)을 형성한 후, 하드마스크층(134) 상부에 다마신 비트라인을 정의하기 위한 마스크 패턴(미도시)을 형성한다. 이어서, 마스크 패턴(미도시)을 식각마스크로 하드마스크층(134), 도전층(132) 및 충간절연막(128)을 식각하여 다마신 트렌치(136)를 형성한다. 여기서, 다마신 트렌치(136)는 하면보다 상변이 긴 사다리꼴형태인 것이 바람직하다. 이후, 하드마스크층(134)을 제거하는 것이 바람직하다.

[0036] 도 3n에 도시된 바와 같이, 전체 상부에 비트라인 스페이서 절연막(138)을 형성한다. 여기서, 비트라인 스페이서 절연막(138)은 산화막인 것이 바람직하다. 이어서, 비트라인 콘택 마스크를 이용하여 도전층(114)과 접속되는 다마신 트렌치(136) 저부에 형성된 비트라인 스페이서 절연막(138)을 제거한다.

[0037] 도 3o에 도시된 바와 같이, 다마신 트렌치 상부에 글루 TiN(Glue TiN)을 형성하고, 텅스텐을 형성한 후 텅스

텐에 에치백 공정을 수행하여 글루 TiN과 동일한 높이로 매립되도록 하여 비트라인 전극(140)을 형성한다. 여기서, 글루 TiN은 다마신 트렌치(136)의 표면에 형성된 비트라인 스페이서 절연막(138)을 따라 형성되며 도전층(114)과 접속되도록 U자 형상을 갖는 것이 바람직하다. 이어서, 다마신 트렌치(136)가 매립되도록 비트라인 전극(140) 상부에 하드마스크층(142)을 형성한 후, 층간절연막(138)이 노출되도록 평탄화 식각 공정을 수행한다.

[0038] 도 3p에 도시된 바와 같이, 도전층(132)에 에치백 공정을 수행하여 제거한 후, 도전층(132)이 제거된 영역에 하드마스크층(144)을 형성하고, 저장전극 콘택 마스크패턴(146)을 형성한다. 여기서, 저장전극 콘택 마스크패턴(146)은 라인 타입인 것이 바람직하다. 이어서, 저장전극 콘택 마스크패턴(146)을 식각마스크로 도전층(114)이 노출되도록 하드마스크층(144) 및 실링질화막(116)을 식각하여 제 2 저장전극 콘택 예정영역(148)을 형성한다. 즉, 제 2 저장전극 콘택 예정영역(148)은 실링질화막(116)에 의해 비트라인(140)과 이격되며 비트라인(140)과 접속되는 도전층(114)과 이격된다. 따라서, 비트라인(140)이 오정렬되어 비트라인(140)과 접속되는 도전층(114)이 노출된다하더라도 실링질화막(116)에 의해 제 2 저장전극 콘택 예정영역(148)에 형성되는 도전층(114)과의 브릿지를 방지할 수 있다. 가령, 저장전극 콘택 마스크의 오정렬로 인해 저장전극 콘택 마스크패턴(146)이 비트라인(140) 상부에 형성되더라도 제 2 저장전극 콘택 예정영역(148)은 비트라인(140)과 오버랩되지 않는다. 왜냐하면, 비트라인(140)이 다마신 형태이기 때문에 저장전극 콘택 마스크패턴(146)과 수직한 프로파일로 식각되지 않기 때문이다. 즉, 제 2 저장전극 콘택 예정영역(148)은 비트라인(140)의 스페이서(138)의 측벽을 따라 자기정렬(self align)된 상태로 식각되어 형성되므로 비트라인(140)과 직접 접속되지 않게된다. 이어서, 저장전극 콘택 마스크 패턴(146) 및 하드마스크층(144)을 제거한다.

[0039] 도 3q에 도시된 바와 같이, 제 2 저장전극 콘택 예정영역(148)과 하드마스크층(144)이 제거된 영역을 포함하는 전체 상부에 저장전극 콘택 도전층을 형성한 후, 평탄화 식각 공정을 수행하여 라인타입의 저장전극 콘택(150)을 형성한다. 저장전극 콘택(150)은 도전층(114)이 노출되도록 형성된 제 2 저장전극 콘택 예정영역(148, 도 3p참조)에 형성됨으로써 비트라인(140)과 저장전극 콘택(150)의 접속이 근본적으로 방지되고, 또한, 실링질화막(116)에 의해 비트라인(140)과 접속되는 도전층(114)이 저장전극 콘택(150)과 접속되는 것을 방지할 수 있다.

[0040] 상술한 바와 같이, 본 발명은 라인타입의 저장전극 콘택을 형성함으로써 다마신 비트라인 사이가 저장전극 콘택으로 매립되도록 함으로써 저장전극이 접속되는 면적을 충분히 확보되도록 하여 콘택저항이 증가되는 등의 문제가 발생하지 않도록 할 수 있다.

### 도면의 간단한 설명

[0041] 도 1은 본 발명에 따른 반도체 소자를 나타낸 평면도.

[0042] 도 2는 본 발명에 따른 반도체 소자를 나타낸 단면도.

[0043] 도 3a 내지 도 3q는 본 발명에 따른 반도체 소자의 형성 방법을 나타낸 단면도로서, (i)은 셀 영역을  $y-y'$ 로 자른 단면도이고, (ii)는 셀 영역을  $x-x'$ 로 자른 단면도.

## 도면

## 도면1

## 도면2

## 도면3a

## 도면3b

## 도면3c

## 도면3d

## 도면3e

## 도면3f

## 도면3g

## 도면3h

## 도면3i

## 도면3j

## 도면3k

## 도면3l

## 도면3m

## 도면3n

## 도면3o

## 도면3p

## 도면3q