(12)发明专利

(10)授权公告号 CN 105874594 B

(45)授权公告日 2019.06.04

(21)申请号 201480070185.1

(72)发明人 C·左 M·F·维纶茨 J·金

(22)申请日 2014.12.16

D·D·金 C·H·尹

(65)同一申请的已公布的文献号

(74)专利代理机构 上海专利商标事务所有限公司 31100

申请公布号 CN 105874594 A

代理人 袁逸

(43)申请公布日 2016.08.17

(51)Int.Cl.

H01L 23/522(2006.01)

(30)优先权数据

61/920,334 2013.12.23 US

(56)对比文件

14/177,620 2014.02.11 US

CN 1826671 A,2006.08.30,

(85)PCT国际申请进入国家阶段日

US 2008079115 A1,2008.04.03,

2016.06.21

CN 1669139 A,2005.09.14,

(86)PCT国际申请的申请数据

EP 1202296 A1,2002.05.02,

PCT/US2014/070517 2014.12.16

JP H10289921 A,1998.10.27,

(87)PCT国际申请的公布数据

审查员 秦晓彤

W02015/100067 EN 2015.07.02

(73)专利权人 高通股份有限公司

权利要求书3页 说明书5页 附图7页

(54)发明名称

三维线焊电感器

(57)摘要

在包括电容器的基板上提供电感器。该电感器包括一系列线环。该线环的一端线焊到该电容器。

1. 一种用于集成电路封装的装置,包括:

包括表面(150)的基板(102);

与所述基板集成的电容器(105),所述电容器包括毗邻所述表面的金属极板(115);以及

多个线环(135、145、140),所述多个线环各自配置为从所述表面伸出并串联耦合以形成电感器(110),所述电感器从所述线环中的第一线环的第一端(165)延伸到所述线环中的最后线环的一端(170),其中所述第一线环的所述第一端形成所述电感器的第一端子,并且一系列线环的最后线环的所述端形成所述电感器的第二端子,并且进一步,其中所述电感器的所述第一端子直接接合到所述电容器的所述金属极板。

2. 如权利要求1所述的装置,进一步包括,毗邻所述表面的第一电感器连接部分(155),其中所述第一线环的第二端线焊到所述第一电感器连接部分,并且其中所述线环中的第二线环(140)的第一端线焊到所述第一电感器连接部分。

3. 如权利要求2所述的装置,进一步包括,毗邻所述表面的第二电感器连接部分(160),其中所述第二线环的第二端线焊到所述第二电感器连接部分,并且其中所述线环中的第三线环(145)的第一端线焊到所述第二电感器连接部分。

4. 如权利要求1所述的装置,其特征在于,所述基板包括玻璃基板。

5. 如权利要求1所述的装置,其特征在于,所述基板包括有机基板。

6. 如权利要求1所述的装置,其特征在于,所述基板包括半导体基板。

7. 如权利要求1所述的装置,进一步包括在所述基板的所述表面上的焊盘,其中所述最后线环的所述端被线焊到所述焊盘。

8. 如权利要求1所述的装置,其特征在于,所述金属极板包括第二金属层(115),所述电容器进一步包括:

在所述基板的所述表面上的第一金属层(120);以及

布置在所述第一金属层和所述第二金属层之间的介电层(125),并且其中所述第一线环的所述第一端被线焊到所述金属极板。

9. 如权利要求1所述的装置,其特征在于,每个线环包括铜或金线环。

10. 如权利要求1所述的装置,其中所述装置被结合在以下至少一者中:蜂窝电话(400)、膝上型设备(405)、平板设备(410)、音乐播放器、通信设备、计算机和视频播放器。

11. 如权利要求1所述的装置,其特征在于,所述多个线环各自具有至少100微米的直径。

12. 如权利要求2所述的装置,其特征在于:

所述第一电感器连接部分具有至少20微米的第一厚度;以及

所述电容器的所述金属极板具有2微米和3微米之间的第二厚度。

13. 一种用于集成电路封装的方法,包括:

在基板(102)上形成电容器(105),其中形成所述电容器包括形成金属极板(115);

在所述基板上形成电感器(110),其中形成所述电感器包括在所述基板上形成从第一线环(135)的第一端(165)处的第一端子延伸到最后线环(145)的一端(170)处的第二端子的一系列线焊线环(135、140、145);以及

将所述第一线环的所述第一端直接接合到所述金属极板。

14. 如权利要求13所述的方法,其特征在于,形成所述电容器包括:

在所述基板的表面(150)沉积第一金属层(120);

在所述第一金属层上沉积介电层(125);以及

在所述介电层上沉积第二金属层(115),其中所述金属极板包括所述第二金属层。

15. 如权利要求13所述的方法,其特征在于,沉积所述第一和第二金属层包括喷溅,并且其中接合所述第一线环的所述第一端包括将所述电感器的所述第一端子线焊到所述金属极板并将所述电感器的所述第二端子线焊到焊盘。

16. 如权利要求15所述的方法,其特征在于,所述喷溅包括喷溅铝。

17. 如权利要求13所述的方法,进一步包括,在所述基板的表面上沉积介电层。

18. 如权利要求17所述的方法,进一步包括在所述介电层的表面上电镀电感器连接部分,其中形成所述电感器包括将所述第一线环的第二端线焊到所述电感器连接部分,以及将第二线环的第一端线焊到所述电感器连接部分。

19. 一种电路,包括:

基板(102);

与所述基板集成的电容器(105);

多个线环,包括具有第一端(165)的第一线环(135);以及

用于将所述多个线环耦合在一起以形成电感器的装置,其中所述第一线环的所述第一端形成所述电感器的第一端子,并且进一步,其中所述电感器的所述第一端子直接接合到所述电容器。

20. 如权利要求19所述的电路,其特征在于,所述电容器包括第一金属层(120)、第二金属层(115)和布置在所述第一和第二金属层之间的介电层(125),并且其中所述第一线环的所述第一端接合到所述第二金属层。

21. 如权利要求19所述的电路,其特征在于,所述装置包括至少一个平坦电感器连接部分(155、160)。

22. 如权利要求21所述的电路,其特征在于,所述至少一个平坦电感器连接部分包括多个平坦电感器连接部分。

23. 一种谐振储能电路,包括:

电容器(105);以及

电感器(110),包括串联安排成从具有第一端(165)的第一线环(135)到具有第二端(170)的最后线环(145)的多个线环(135、140、145),所述多个线环安排成形成具有所述第一端(165)和所述第二端(170)的电感器,所述第一端(165)形成所述电感器的第一端子,所述第二端(170)形成所述电感器的第二端子,其中所述电感器的所述第一端子直接接合到所述电容器。

24. 如权利要求23所述的谐振储能电路,进一步包括基板(102),其中所述电容器和所述电感器集成到所述基板上。

25. 如权利要求24所述的谐振储能电路,其特征在于,所述基板包括玻璃。

26. 如权利要求24所述的谐振储能电路,其特征在于,所述基板包括硅。

27. 如权利要求24所述的谐振储能电路,其特征在于,所述基板包括有机基板。

28. 如权利要求23所述的谐振储能电路,其特征在于,所述谐振储能电路是串联谐振电

路。

29. 如权利要求23所述的谐振储能电路,其特征在于,所述谐振储能电路是并联谐振储能电路。

30. 如权利要求24所述的谐振储能电路,进一步包括集成到所述基板上的至少一个电感器连接部分,其中所述线环线焊到所述至少一个电感器连接部分。

31. 如权利要求30所述的谐振储能电路,其特征在于,所述线环包括铜或金。

## 三维线焊电感器

[0001] 相关申请

[0002] 本申请要求于2013年12月23日提交的美国临时专利申请No.61/920,334的权益，本申请要求于2014年2月11日提交的美国专利申请S/N.14/177,620的权益，这两篇申请的全部内容通过援引整体纳入于此。

### 技术领域

[0003] 本申请涉及包括电感器的集成电路封装。

### 背景技术

[0004] 需要高品质(Q)因数电感器和电容器以实现高性能谐振储能电路。例如，使用高Q谐振储能电路能够在RF前端中改进效率并且降低失真和谐波，以及在滤波器和双工器中实现较低插入损耗和较高带外拒斥。此外，高Q谐振储能电路改进了RF敏感性和选择性。

[0005] 电感器或电容器的品质因数与其直流(DC)电阻(Rdc)逆相关。虽然在空间不是问题的非移动应用中使用分立常规电感器或电容器来实现高Q电感器或电容器相对简单，但是在紧凑的集成设计中没有用于此类分立组件的空间。由此，增加组件密度的一种办法是将期望的电感器和电容器集成到封装基板的金属层中。用来形成电容器的金属层通常很薄以降低其寄生电感。但是，所得电感器和电容器之间的互连常规上形成在这些相对薄的金属层中的一者中，这增加了DC电阻并且由此降低了所得的品质因数。替换地，无源组件可以被集成到管芯上，但是现代CMOS工艺中的金属层厚度太薄以至于所得无源组件的DC电阻也相对较高。因此，管芯集成或封装集成电感器、电容器和LC谐振储能电路的品质因数被局限于对于RF设计所需的高性能而言太低的值。

[0006] 相应地，本领域中需要具有改进的品质因数的集成谐振储能电路。

### 概述

[0008] 提供了包括多个线环或线拱的电感器。这些线环中的一者的一端线焊到电容器。该线焊引入了极少的寄生电阻，从而该电感器和该电容器之间的互连在实质上无损。用这种方式，由该电感器和该电容器形成所得的谐振储能电路的品质因数被有益地提高了。

### 附图简述

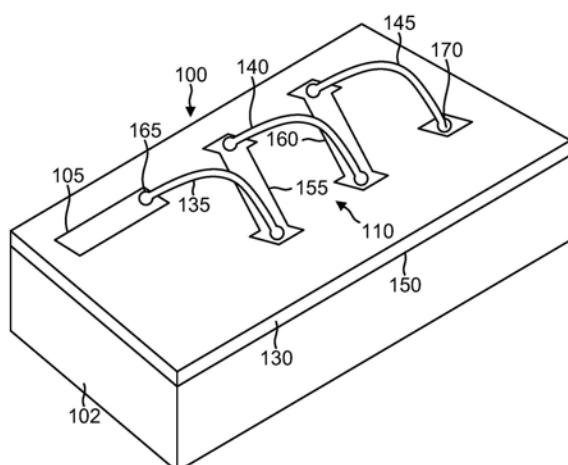

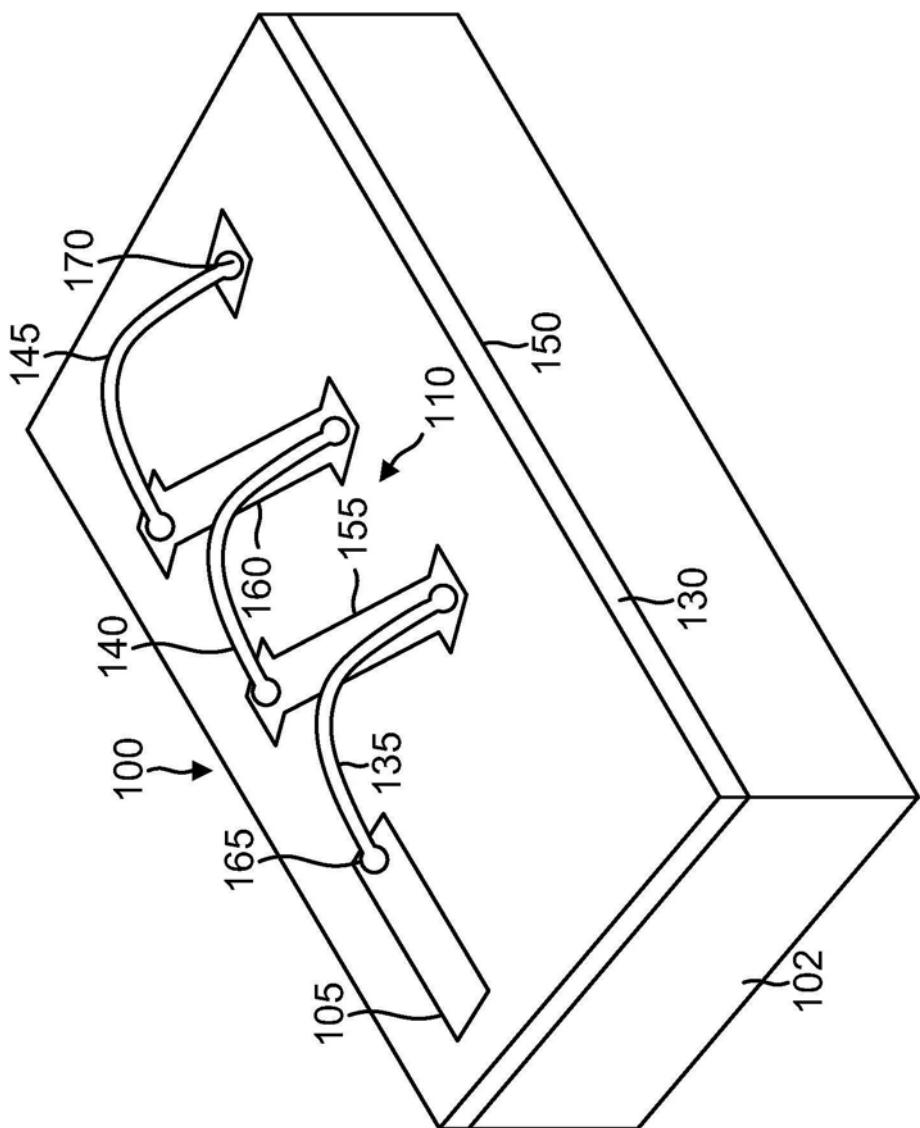

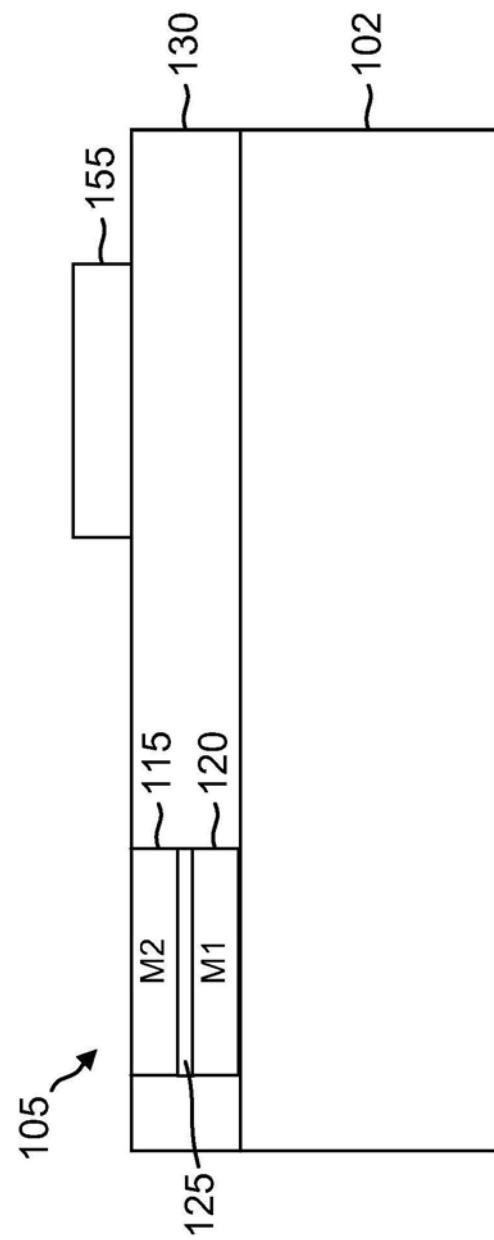

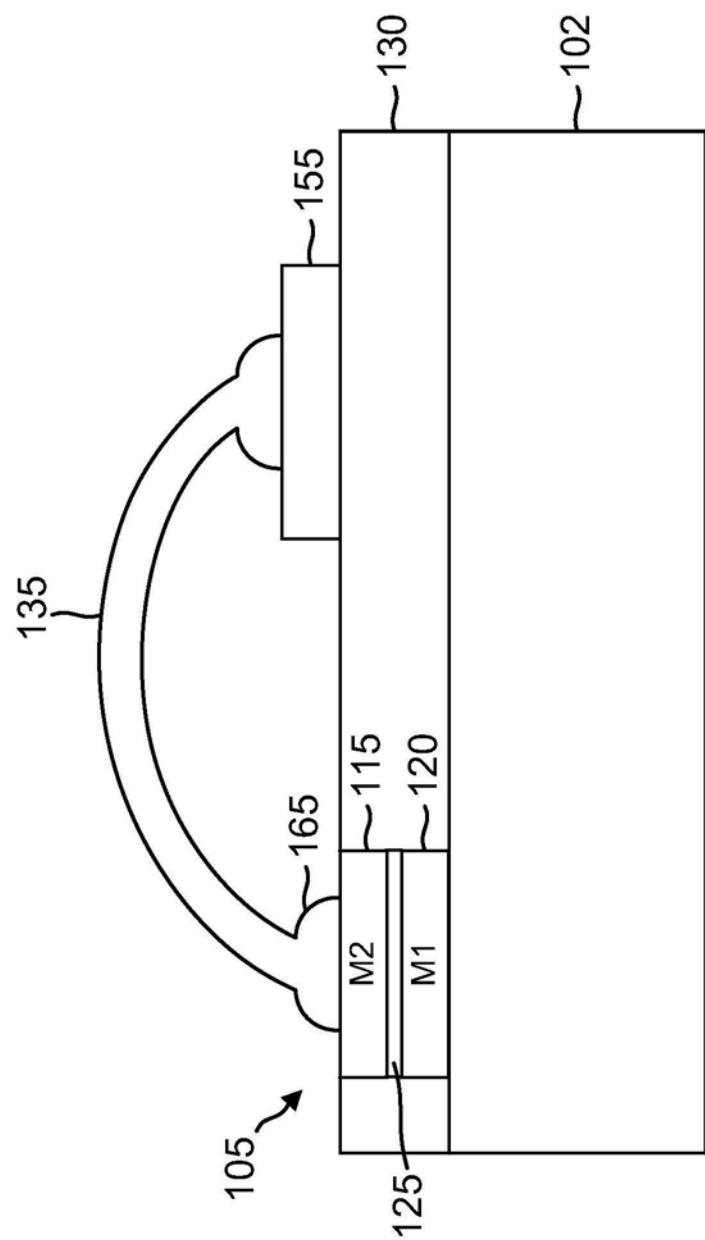

[0010] 图1A是根据本公开实施例的三维电感器的立体图。

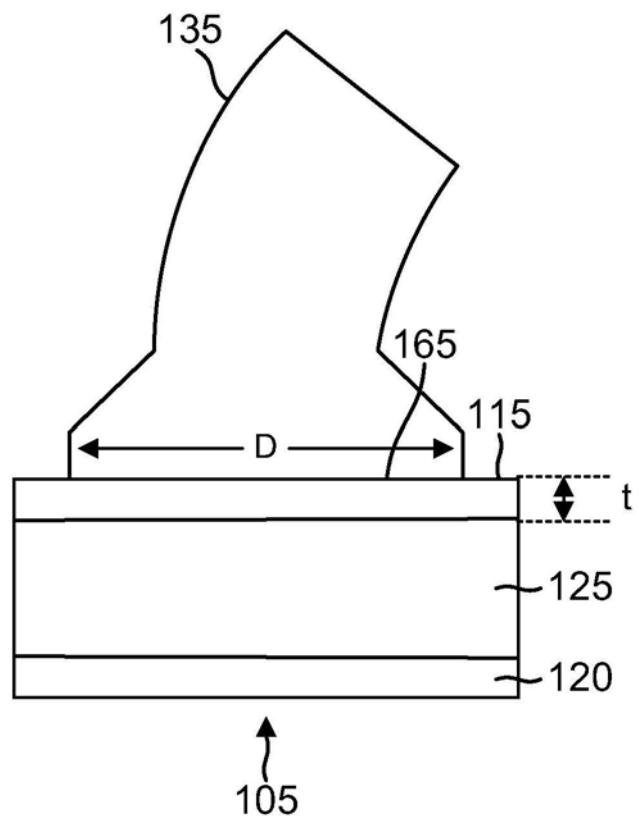

[0011] 图1B是图1A的电感器的线焊部分和毗邻金属绝缘体金属(MIM)电容器的放大横截面示图。

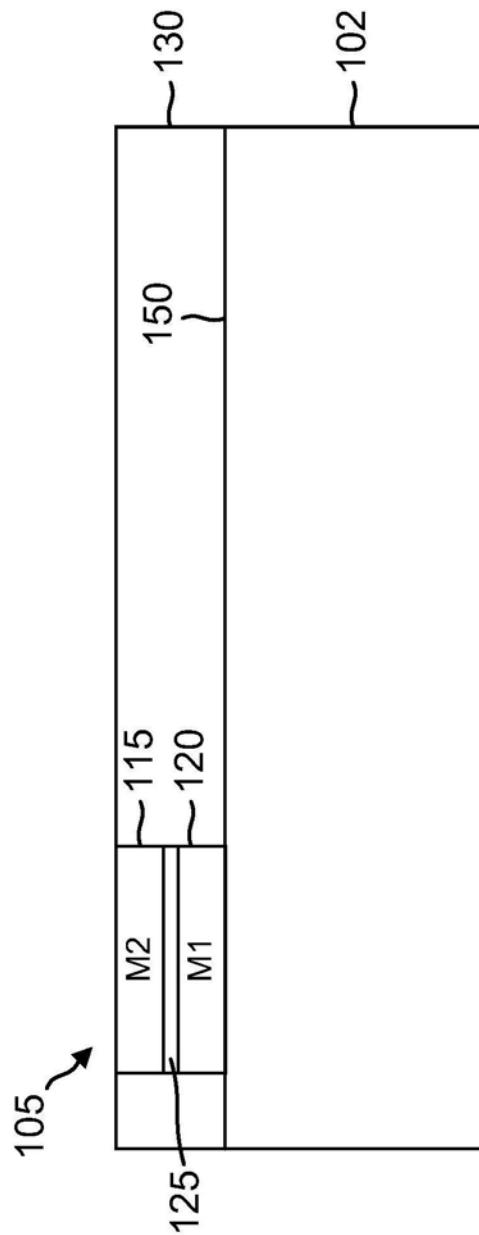

[0012] 图2A是形成MIM电容器之后且形成电感器之前的图1A的基板的横截面示图。

[0013] 图2B是形成电感器连接部分之后的图2A的基板的横截面示图。

[0014] 图2C是在将线拱或线环线焊到MIM电容器的金属层和电感器连接部分之后图2B的基板的横截面示图。

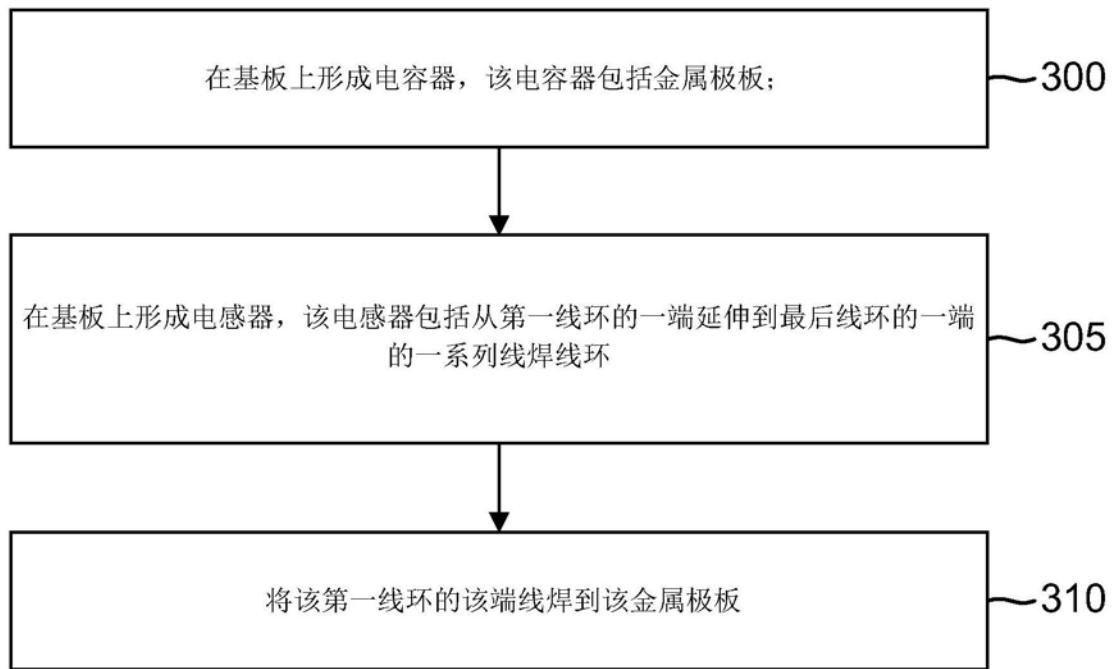

[0015] 图3是根据本公开的一实施例的三维电感器的制造方法的流程图。

[0016] 图4解说了根据本公开实施例的纳入嵌入式电感器封装的一些示例电子系统。

[0017] 本发明的各实施例及其优势通过参考以下详细描述而被最好地理解。应当领会，在一个或多个附图中，相同的参考标记被用来标识相同的元件。

[0018] 详细描述

[0019] 所提供的三维电感器可以被有益地纳入到谐振储能电路中以提供高Q因数。在常规集成谐振储能电路中，形成在图案化金属层中的互连(诸如导线或迹线)将电感器耦合到电容器。因为图案化金属层通常相对较薄，因而此类常规互连具有不期望的大量寄生电阻，并且由此降低了所得谐振储能电路的品质因数。相反，本文中公开的三维电感器解决了这一问题，并且为谐振储能电路的电感器(L)和电容器(C)组件之间的互连提供了降低的寄生电阻(例如，DC电阻，Rdc)。如本文中进一步描述的，电感器到电容器互连的寄生电阻被实质上消除了。

[0020] 三维(3D)电感器包括呈拱形远离基板的多个线圈或线环。线环由一个或多个电感器连接部分互连。电感器连接部分沉积或者以其他方式形成在基板的平坦表面上。使用两个笛卡尔维度定义平坦表面。相反，线圈或线环呈拱形远离基板的平坦表面，并且由此在第三笛卡尔维度中延伸。例如，平坦基板表面可以被视为在笛卡尔x和y维度中延伸，而线环也延伸到z维度中。所得的集成电感器可以由此被指定为与使用平坦结构形成的集成电感器相对的三维电感器。

[0021] 每个电感器连接部分耦合到一对线环。如名称所暗示的，每个电感器连接部分起到互连对应的线环对的作用。例如，若有三个线环，其范围从第一线环、第二线环，到最后是第三线环，那么就会有至少两个对应的电感器连接部分。在此类实施例中，第一线环的一端线焊到电感器连接部分中的第一电感器连接部分。类似地，第二线环的一端也线焊到第一电感器连接部分。第二线环的剩余端线焊到第二电感器连接部分。最后，第三线环的一端也线焊到第二电感器连接部分。更一般地，若三维电感器包括N个线环(N是大于等于2的整数)，那么至少有N-1个电感器连接部分。

[0022] 再次参见具有三个线环的示例三维电感器，将会领会第二线环的两端都被耦合到对应的电感器连接部分——一端耦合到第一电感器连接部分，而剩余一端耦合到第二电感器连接部分。第一线环的一端耦合到第一电感器连接部分，但是该第一线环肯定有另外一端。第一线环的这一“自由”端形成了所得三维电感器的第一端子。类似地，第三线环一端耦合到第二电感器连接部分，但是当然也有另一端。第三线环的这一剩余端形成了三维电感器的剩余第二端子。无论三维电感器实施例中使用的线环的数目是多少，一个线环可以被视为“开始”线环，其中其会具有自由端中的一者。类似地，另一线环可以被视为“结束”线环，其中其会具有剩余的自由端。正是这两个线环为三维电感器提供了第一和第二端子。

[0023] 支持三维电感器的基板还支持金属绝缘体金属(MIM)电容器。三维电感器的端子中的一者线焊到MIM电容器。就这一点而言，MIM电容器包括通过介电层与第二金属层分开的第一金属层。金属层也可以被指定为金属极板。第一金属层位于基板和介电层之间，而第二金属层在介电层上暴露。换言之，第二金属层可以被示为基板表面上的“最顶部”金属层。三维电感器的自由端中的一者线焊到MIM电容器的暴露的第二金属层。这是十分有益的，因为线焊导致三维电感器和MIM电容器之间实质上没有寄生互连电阻。互连的三维电感器和MIM电容器可以形成提供比常规集成谐振储能架构更高的品质因数的集成谐振储能电路。此外，该品质因数的改进是以低成本提供的，因为线焊工艺是经济且可靠的。此外，由于使

用了额外的维度,三维电感器的基板占用小于常规二维电感器。这些有益特征可通过以下对一些示例实施例的讨论来更好地领会。

[0024] **示例实施例**

[0025] 现在转向附图,图1A是集成无源器件(IPD)封装100内的示例三维电感器110的立体图。三维电感器110可以被集成到基板102(诸如玻璃基板、半导体基板或者有机基板)上以形成谐振储能电路。电感器110包括多个线环,包括线环135、线环140和线环145。电感器110还包括多个电感器连接部分,诸如电感器连接部分155和电感器连接部分160。与都呈拱形远离平坦基板表面150的线环135、140和145相反,电感器连接部分155和160是基本平行于基板表面150定义的平面的平坦结构。由此,如早前所讨论的,电感器110是“三维”电感器的实施例。同样如早前所讨论的,线环中的开始线环会具有不连接到任何电感器连接部分的一端。正是该自由端可以有益地线焊到MIM电容器。例如,线环135可以被视为开始线环,其具有线焊到MIM电容器105的端165。端165由此是电感器110的第一端子。电感器连接部分155将线环135与线环140串联耦合。类似地,电感器连接部分160将线环140与线环145串联耦合。线环145可以被视为电感器中的结束线环,从而线环145的一端170形成了电感器110的相对第二端子。端170可以线焊到焊盘或者去往电感器110的其他合适的互连。将会领会,线环的数目可以从针对电感器100所示的三个而改变。一般,线环的数目取决于期望的电感和其他因素。例如,仅具有两个线环的实施例会具有一个电感器连接部分。类似地,具有四个线环的实施例会具有三个电感器连接部分。由此可以看出,电感器连接部分的数目比线环的数目少一个。

[0026] 图1B是线环145的线焊端165和MIM电容器105的横截面示图。MIM电容器105可包括通过介电层125与第二金属层或极板115绝缘的第一金属层或极板120。由于线焊,线环135直接耦合到金属层115,并且由此跨绝缘介电层125电容性地耦合到金属层120。用这种方式,三维电感器100(图1A)通过第一线环135的线焊端165耦合到MIM电容器105。再次参见图1A,MIM电容器105可以位于基板102上的钝化层或介电层130内。在一个实施例中,MIM电容器105定义了基本平行于基板102的平坦表面150的平面。因为该平坦性,MIM电容器105可以被视为包括二维结构。类似地,电感器连接部分155和160也可以被视为包括二维结构。相反,线环或线圈135、140和145在基板表面150定义的平面上形成拱形。由此,与MIM电容器105相反,电感器110可以被视为包括三维结构。

[0027] 在一些实施例中,为了使得三维电感器110的所得电感最大化,每个线环的中心都可沿着电感器110的纵轴而对齐。用这种方式,流经每个线环的电流所感生的磁场增强了剩余线环所产生的磁场。给定此类对齐,电感器连接部分155和160也可以对齐从而彼此基本上平行。但是将会领会,在替换性实施例中,线环中心不需要被纵向对齐。例如,电感器连接部分160所具有的纵轴可相对于电感器连接部分155的纵轴倾斜。由此,存在其中与图1A的三维电感器相反,各电感器连接部分彼此不平行的替换性实施例。

[0028] 电感器连接部分155和160可包括图案化金属层,诸如图案化铜或镍金属层。例如,铜可以被电镀到基板102上以形成电感器连接部分155和160。与第一金属层120和第二金属层115相反,在一些实施例中,形成电感器连接部分155和160的金属层相对较厚(诸如,厚度至少20微米)从而增加电感器品质因数。相反,第一金属层115和第二金属层120在一些实施例中可以相对较薄。例如,第一金属层115和第二金属层120可以在厚度上仅有几微米(或更

少),从而它们的周界可以被精确地定义。用这种方式,在此类实施例中,电容器105的所得电容也被精确定义。此外,若与电感器连接部分155和160相比,金属层115和120相对较薄,那么电容器105的寄生电感就被降低。

[0029] 为了在MIM电容器105和三维电感器110之间提供有益的低寄生电阻,线环135的端165直接线焊到第二金属层115。替换地,金属焊盘(未解说)可以沉积在第二金属层115上,从而线环135的端165线焊到该焊盘而非直接线焊到第二金属层115。若第二金属层115太薄不能接受线焊,那么使用此类焊盘是有益的。例如,若第二金属层115比2到3微米还薄,那么它就太薄了,以至于线焊将会不成功。在此类实施例中,形成在附加金属层中的焊盘(未解说)会由此允许线环135的端165线焊到第二金属层115。

[0030] 线环135、140和145可以具有足够大的直径来提供低电阻。例如,在一些实施例中,线环135、140和145可以各自具有至少100微米的直径。由于线焊工艺,端165会被加宽,因为其与第二金属层115接合,从而端165会具有如图1B中所示的直径D,其甚至大于线环135的本体的直径。由此,线环145的端165的表面积相对较大,从而寄生电阻被最小化。相反,常规电感器到电容器互连可包括第二金属层115的图案化以还形成进而耦合到线圈135的端165的导线。如之前所讨论的,第二金属层115可以相对较薄,从而从这种类似的薄金属层形成的互连会比端165到第二金属层115的线焊的电阻大很多。

[0031] 供电流流过线环135的端165和第二金属层115之间的接口151的横截面积由 $\pi(D/2)^2 = (\pi/4)D^2$ 来大约给出,其中D是线环135的端165的直径。若第二金属层115形成长度为D的常规导线(未示出)以用于将电容器105互连到电感器110,所得电感器到电容器互连会具有 $D*t$ 的横截面积,其中t是第二金属层115的厚度。端165的横截面积与此类常规互连横截面积之比由此为 $\pi*D/t$ 。因为一般线圈的D可以大约为100微米或者更大,而厚度t可以相对薄,诸如3微米,线焊互连151提供了常规电感器到电容器互连的100倍的横截面积。由此,将三维电感器的自由端线焊到电容器的暴露金属层提供了与常规电感器到电容器互连相比显著降低的寄生电阻。电容器105和电感器110可以被认为是串联耦合或并联耦合的。如谐振储能领域中所公知的,此类耦合所得谐振频率与 $1/(L*C)$ 的平方根成正比,其中L是电感器110的电感,且C是电容器105的电容。出于以上所讨论的理由,所得谐振储能电路有益地具有高品质因数。此外,由于电感器的线焊,所以该构建是相对经济的。现在将讨论一些示例制造方法。

### [0032] 示例制造方法

[0033] 如图2A中所示,封装100的制造可以通过将第一金属层120沉积到基板102的表面150上开始。例如,铝或其他金属(诸如铜或镍)可以被喷溅或镀敷到表面150上,并且被图案化以形成第一金属层120。在一些实施例中,第一金属层120的厚度可以仅由几微米或更小以增强其图案化的精度。进而,此类精度降低了所得MIM电容器105的电容容限。

[0034] 可以随后使用例如介电材料(诸如 $Al_2O_3$ 、 $Ta_2O_5$ 、 $SiN_x$ 、 $ZrO_2$ 、 $Al_2O_3/ZrO_2$ 夹层、 $SrTiO_3$ 和 $Ba_xSr_{1-x}TiO_3$ )的原子层沉积来沉积介电层125。将会领会,各种各样的其他介电材料也可以适于形成介电层125。例如,介电层125可包括氧化钽。介电层125可以被相对薄地沉积以增强所得MIM电容器105的电容。例如,在一些实施例中,介电层125可以具有数十到数百埃的厚度。

[0035] 在介电层125被沉积且图案化之后,第二金属层115可以如类似于针对第一金属层

120所讨论的那样被沉积和图案化。可以随后诸如通过聚酰亚胺或其他类型的介电聚合物(诸如味之素构建膜或者基于苯并环丁烯的聚合物)的旋涂层沉积介电层130。替换地,介电层130可以被层压到基板102上。无论其如何沉积,介电层130随后不仅会覆盖基板102也会覆盖MIM电容器105。介电层130可以被图案化以暴露第二金属层115。替换地,MIM电容器105可以在介电层130沉积之前被遮蔽。

[0036] 如图2B中所示,电感器连接部分(诸如部分155)可以随后被沉积到介电层130上。例如,金属(诸如铜或镍)可以被电沉积或镀覆到介电层130上。在一些实施例中,电感器连接部分可以相对较厚(诸如厚度为数十微米),从而增强所得三维电感器的电感。

[0037] 随着电感器连接部分的形成,线环可以被线焊到电感器连接部分以及线焊到MIM电容器105。例如,如图2C中所示,线环135可以线焊到第二金属层115以及线焊到电感器连接部分155。剩余线环被类似地线焊以完成谐振储能封装。例如,再次参见图1A,线环140被线焊到电感器连接部分155和160。就这一点而言,线环140被线焊到毗邻电感器连接部分155的第一端的电感器连接部分,而线环135被线焊成毗邻于电感器连接部分155的相对第二端。类似地,线环145被线焊到电感器连接部分160,且也线焊到焊盘170。

[0038] 如图3的流程图中所示,可以概括一种制造方法实施例。该方法在步骤300以在基板上形成电容器开始,该电容器包括基板上的金属极板。此类步骤的一个示例是如针对图2A所讨论的MIM电容器105的形成。特别地,金属层115提供了步骤300中的金属极板的示例。

[0039] 该方法还包括在基板上形成电感器的步骤305,该电感器包括从第一线环的一端延伸向第二线环的一端的一系列线焊线环。此类步骤的一个示例在上文被诸如针对图2C的线环135讨论。

[0040] 最后,该方法包括将第一线环的该端接合到金属极板的动作315。此类动作的一个示例也在上文针对图2C的线环135讨论。用这种方式,包括电感器和电容器的谐振LC储能电路以非常经济且具有高品质因数的方式被集成到基板上。

[0041] 现在讨论示例电子系统。

[0042] 示例电子系统

[0043] 包括本文中公开的谐振储能电路的封装可以被纳入到各种各样的电子系统中。例如,如图4中所示,蜂窝电话400、膝上型设备405和平板PC 410都可以包括纳入根据本公开构建的谐振储能电路的集成电路封装。其他示例性电子系统(诸如音乐播放器、视频播放器、通信设备和个人计算机)也可以用根据本公开构建的集成电路封装来配置。

[0044] 如本领域普通技术人员至此将领会的并取决于手头的具体应用,可以在本公开的设备的材料、装置、配置和使用方法上做出许多修改、替换和变动而不会脱离本公开的精神和范围。有鉴于此,本公开的范围不应当被限定于本文中所解说和描述的特定实施例(因为其仅是作为本公开的一些示例),而应当与所附权利要求及其功能等同方案完全相当。

图1A

图1B

图2A

图2B

图2C

图3

图4