(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第6220614号

(P6220614)

(45) 発行日 平成29年10月25日(2017.10.25)

(24) 登録日 平成29年10月6日(2017.10.6)

(51) Int.Cl.

F 1

H01S 5/22 (2006.01)

H01S 5/22

H01S 5/343 (2006.01)

H01S 5/343

H01S 5/227 (2006.01)

H01S 5/227

前置審査

(21) 出願番号

特願2013-196093 (P2013-196093)

(22) 出願日

平成25年9月20日(2013.9.20)

(65) 公開番号

特開2015-61060 (P2015-61060A)

(43) 公開日

平成27年3月30日(2015.3.30)

審査請求日

平成28年2月16日(2016.2.16)

(73) 特許権者 302062931

ルネサスエレクトロニクス株式会社

東京都江東区豊洲三丁目2番24号

(74) 代理人 100080001

弁理士 筒井 大和

(72) 発明者 阿江 敬

神奈川県川崎市中原区下沼部1753番地

ルネサスエレクトロニクス株式会社内

(72) 発明者 北村 昌太郎

神奈川県川崎市中原区下沼部1753番地

ルネサスエレクトロニクス株式会社内

(72) 発明者 奥田 哲朗

神奈川県川崎市中原区下沼部1753番地

ルネサスエレクトロニクス株式会社内

最終頁に続く

(54) 【発明の名称】半導体装置の製造方法および半導体装置

## (57) 【特許請求の範囲】

## 【請求項1】

(a) InPよりなる基板の第1領域を囲む領域にマスクを形成する工程、

(b) 前記基板の第1領域に、第1半導体層を成長させる工程、

(c) 前記第1半導体層を覆うように第2半導体層を成長させる工程、

を有し、

前記基板の表面は、(100)面から[1-1-1]方向へ、0.5°～1.0°の範囲で傾斜しており、

前記基板、前記第1半導体層および前記第2半導体層は、III-V族化合物半導体よりなり、

前記第1半導体層は、InGaAlAsよりなり、前記(c)工程は、III族元素の原料ガスおよびV族元素の原料ガスを用いたエピタキシャル成長により、前記第2半導体層を形成する工程であり、

前記III族元素の原料ガスの流量に対する前記V族元素の原料ガスの流量の比であるV/III比が2000以上である、半導体装置の製造方法。

## 【請求項2】

請求項1記載の半導体装置の製造方法において、

前記第2半導体層は、InPよりなる、半導体装置の製造方法。

## 【請求項3】

請求項2記載の半導体装置の製造方法において、

10

20

前記第2半導体層の側面は、(0-11)面を有する、半導体装置の製造方法。

【請求項4】

請求項2記載の半導体装置の製造方法において、

(d) 前記(c)工程の後、前記第2半導体層の上方に、第1電極を形成し、前記基板の裏面に、第2電極を形成する工程、

を有する、半導体装置の製造方法。

【請求項5】

請求項2記載の半導体装置の製造方法において、

前記第1半導体層および前記第2半導体層の積層部は、第1方向に延在し、

前記積層部の前記第1方向と交差する第2方向の断面形状は、略矩形状である、半導体 10

装置の製造方法。

【請求項6】

請求項2記載の半導体装置の製造方法において、

前記第1半導体層および前記第2半導体層の積層部の側面は、前記(100)面に対し

てほぼ垂直である、半導体装置の製造方法。

【請求項7】

請求項2記載の半導体装置の製造方法において、

前記第1半導体層および前記第2半導体層は、第1方向に延在し、

前記第2半導体層の上面の前記第1方向と交差する第2方向の幅は、前記第1半導体層

の上面の前記第2方向の幅より大きい、半導体装置の製造方法。 20

【請求項8】

請求項4記載の半導体装置の製造方法において、

前記(c)工程と前記(d)工程との間に、

(e) 前記第1半導体層および前記第2半導体層の積層部の両側に、前記積層部より絶

縁性を有する半絶縁層を形成する工程、

を有する、半導体装置の製造方法。

【請求項9】

請求項8記載の半導体装置の製造方法において、

前記半絶縁層は、Feを含有するInPよりなる、半導体装置の製造方法。

【請求項10】

InPよりなる基板、前記基板の第1領域に配置された第1半導体層と、前記第1半導

体層を覆うように配置された第2半導体層と、を有し、

前記基板の表面は、(100)面から[1-1-1]方向へ、0.5°～1.0°の範

囲で傾斜しており、

前記基板、前記第1半導体層および前記第2半導体層は、II-V族化合物半導体よ

りなり、

前記第1半導体層は、InGaAlAsよりなる、半導体装置。

【請求項11】

請求項10記載の半導体装置において、

前記第2半導体層は、InPよりなる、半導体装置。 40

【請求項12】

請求項11記載の半導体装置において、

前記第2半導体層の側面は、(0-11)面を有する、半導体装置。

【請求項13】

請求項10記載の半導体装置において、

前記第2半導体層の上方に配置された第1電極および前記基板の裏面に配置された第2

電極を有する、半導体装置。

【請求項14】

請求項12記載の半導体装置において、

前記第1半導体層および前記第2半導体層の積層部は、第1方向に延在し、

50

前記積層部の前記第1方向と交差する第2方向の断面形状は、略矩形状である、半導体装置。

【請求項15】

請求項12記載の半導体装置において、

前記第1半導体層および前記第2半導体層の積層部の側面は、前記(100)面に対し

てほぼ垂直である、半導体装置。

【請求項16】

請求項12記載の半導体装置において、

前記第1半導体層および前記第2半導体層は、第1方向に延在し、

前記第2半導体層の上面の前記第1方向と交差する第2方向の幅は、前記第1半導体層

の上面の前記第2方向の幅より大きい、半導体装置。 10

【請求項17】

請求項12記載の半導体装置において、

前記第1半導体層および前記第2半導体層の積層部の両側に、Feを含有するInPよりなる層を有する、半導体装置。

【請求項18】

請求項12記載の半導体装置において、

前記第1半導体層および前記第2半導体層の第1積層部と離間して配置された第2積層部を有し、

前記第2積層部は、前記基板の第2領域に配置された第3半導体層および前記第3半導

体層上に配置された第4半導体層を有し、 20

前記第1半導体層の層厚は、前記第3半導体層の層厚より大きい、半導体装置。

【請求項19】

請求項18記載の半導体装置において、

前記第2半導体層の層厚は、前記第4半導体層の層厚より大きい、半導体装置。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、半導体装置の製造方法および半導体装置に関し、例えば、III-V族化合物半導体を用いた半導体装置に好適に利用できるものである。 30

【背景技術】

【0002】

10~40Gbpsの高速で動作する半導体レーザ(半導体装置)として、InGaAlAs系の半導体材料が用いられている。具体的には、光導波路として用いられる活性層に、InGaAlAs系の半導体材料が用いられる。しかしながら、活性層中のAlが酸化されやすく、Alの酸化により活性層が劣化しやすい。

【0003】

このため、Alの酸化防止対策のため、活性層を覆うカバー層を採用した構成の検討がなされている。

【0004】

例えば、下記特許文献1(特開平9-92925号公報)には、p型InP基板の上方にMQW層を有し、さらに、このMQW層上にn-InP層を有する半導体レーザが開示されている。

【0005】

また、下記特許文献2(特開2004-14821号公報)には、GaAsの(100)オフ基板を用いた半導体レーザが開示されている。

【0006】

また、下記非特許文献1および下記特許文献3(特開平5-110208号公報)には、選択成長により形成された半導体レーザが開示され、下記非特許文献2~4には、傾斜基板上のエピタキシャル成長膜の成長性についての記載がある。 50

## 【先行技術文献】

## 【特許文献】

## 【0007】

【特許文献1】特開平9-92925号公報

【特許文献2】特開2004-14821号公報

【特許文献3】特開平5-110208号公報

## 【非特許文献】

## 【0008】

【非特許文献1】Low Drive-Current and Wide Temperature Operation of  $1.3\mu\text{m}$  AlGa<sub>x</sub>As-MQW BH-DFB Lasers by Laterally Enhanced Cladding Layer Growth, R. Kobayashi et al., OFC2008 OTuK2

10

【非特許文献2】Optical property of InAsP/InP strained quantum wells grown on InP (111)B and (100) substrates, H. Q. Hou et al., J. Appl. Phys. 75, 4673 (1994)

【非特許文献3】Optical properties of In<sub>0.52</sub>Al<sub>0.48</sub>As layers and In<sub>0.53</sub>Ga<sub>0.47</sub>As/In<sub>0.52</sub>Al<sub>0.48</sub>As quantum well structures grown on (111)B InP substrates by molecular beam epitaxy, Y. Kawamura et al., IPRM1998 ThP-11

【非特許文献4】High CW output power InGaAs/InGaAsP/InGaP diode lasers: effect of substrate misorientation, L. J. Mawst et al., LD conference1995 SCL13.5

## 【発明の概要】

20

## 【発明が解決しようとする課題】

## 【0009】

本発明者は、上記のようなII-V族化合物半導体を用いた半導体レーザの研究開発に従事しており、その性能の向上について、鋭意検討している。その過程において、II-V族化合物半導体を用いた半導体レーザの性能を向上させるために、その製造方法および構造に関し、更なる改善の余地があることが判明した。

## 【0010】

その他の課題と新規な特徴は、本明細書の記述および添付図面から明らかになるであろう。

## 【課題を解決するための手段】

30

## 【0011】

本願において開示される実施の形態のうち、代表的なものの概要を簡単に説明すれば、次のとおりである。

## 【0012】

本願において開示される一実施の形態に示される半導体装置の製造方法は、基板の第1領域に、第1半導体層を成長させ、さらに、第1半導体層上に、第2半導体層を成長させる。そして、この基板は、(100)面から[1-1-1]方向へ、0.5°～1.0°の範囲で傾斜している。また、基板、第1半導体層および第2半導体層は、II-V族化合物半導体よりなる。

## 【0013】

40

本願において開示される一実施の形態に示される半導体装置は、基板の第1領域上に形成された第1半導体層と、第1半導体層上に形成された第2半導体層と、を有する。そして、基板は、(100)面から[1-1-1]方向へ、0.5°～1.0°の範囲で傾斜しており、基板、第1半導体層および第2半導体層は、II-V族化合物半導体よりなる。

## 【発明の効果】

## 【0014】

本願において開示される以下に示す代表的な実施の形態に示される半導体装置の製造方法によれば、特性の良好な半導体装置を製造することができる。

## 【0015】

50

本願において開示される以下に示す代表的な実施の形態に示される半導体装置によれば、半導体装置の特性を向上させることができる。

【図面の簡単な説明】

【0016】

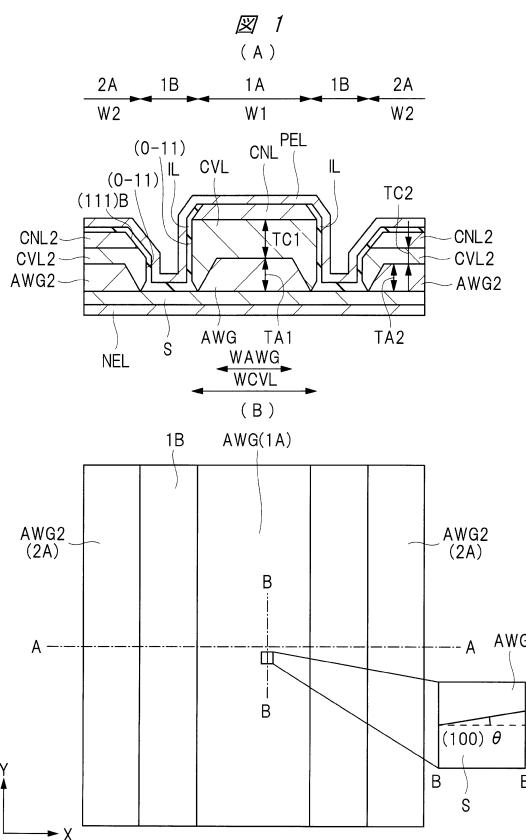

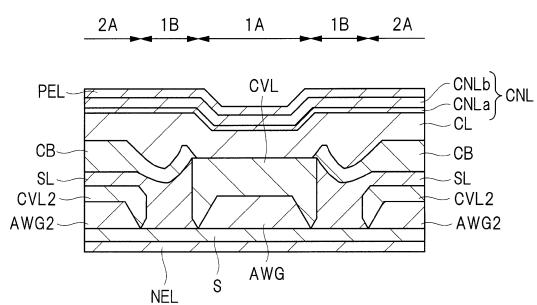

【図1】実施の形態1の半導体装置の構成を示す断面図および平面図である。

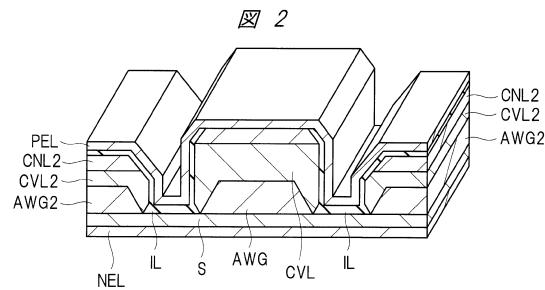

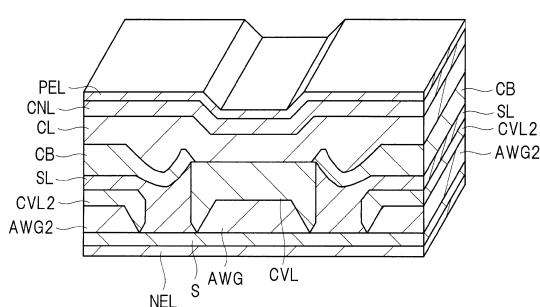

【図2】実施の形態1の半導体装置の構成を示す斜視図である。

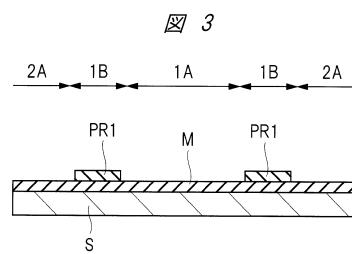

【図3】実施の形態1の半導体装置の製造工程を示す断面図である。

【図4】実施の形態1の半導体装置の製造工程を示す断面図であって、図3に続く製造工程を示す断面図である。

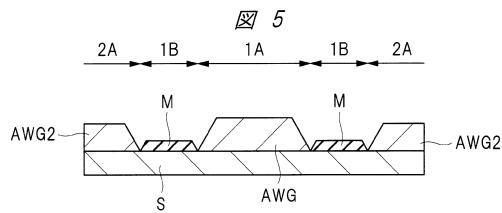

【図5】実施の形態1の半導体装置の製造工程を示す断面図であって、図4に続く製造工程を示す断面図である。

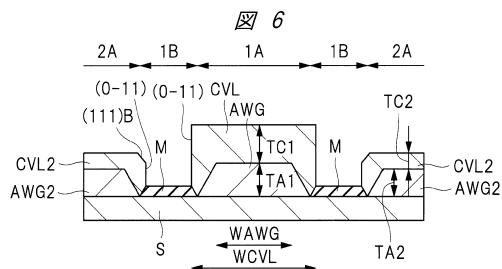

【図6】実施の形態1の半導体装置の製造工程を示す断面図であって、図5に続く製造工程を示す断面図である。

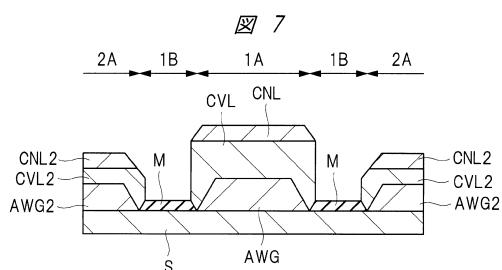

【図7】実施の形態1の半導体装置の製造工程を示す断面図であって、図6に続く製造工程を示す断面図である。

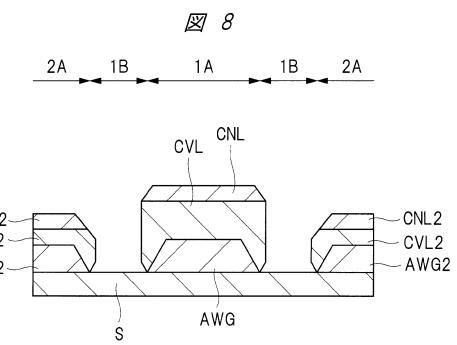

【図8】実施の形態1の半導体装置の製造工程を示す断面図であって、図7に続く製造工程を示す断面図である。

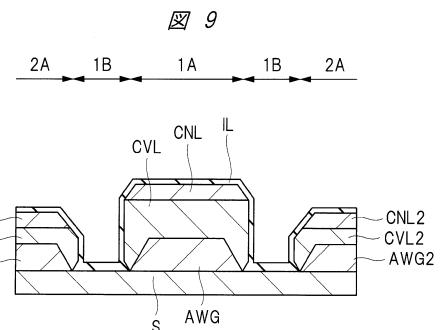

【図9】実施の形態1の半導体装置の製造工程を示す断面図であって、図8に続く製造工程を示す断面図である。

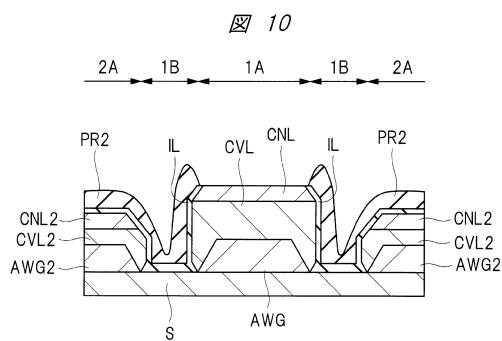

【図10】実施の形態1の半導体装置の製造工程を示す断面図であって、図9に続く製造工程を示す断面図である。

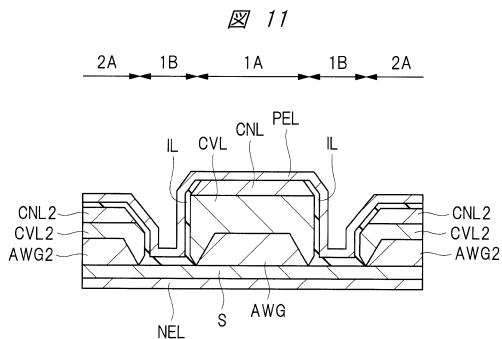

【図11】実施の形態1の半導体装置の製造工程を示す断面図であって、図10に続く製造工程を示す断面図である。

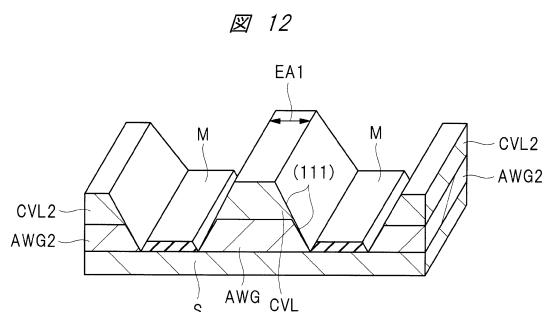

【図12】比較例の半導体装置の通電領域を示す斜視図である。

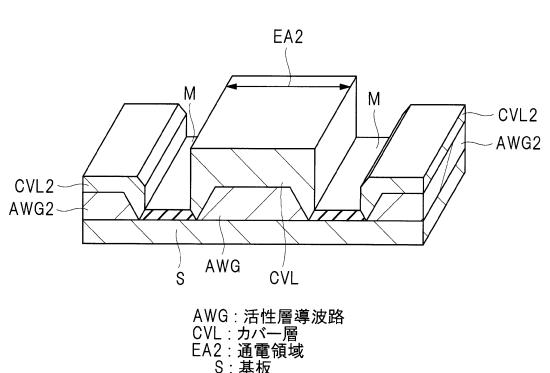

【図13】実施の形態1の半導体装置の通電領域を示す斜視図である。

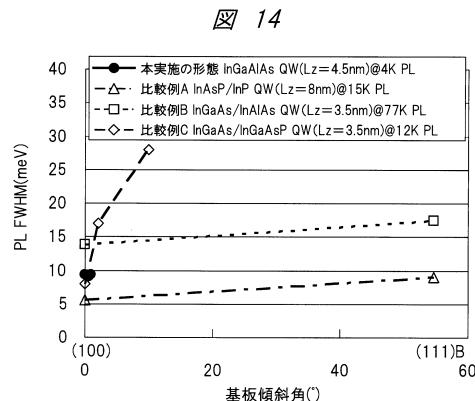

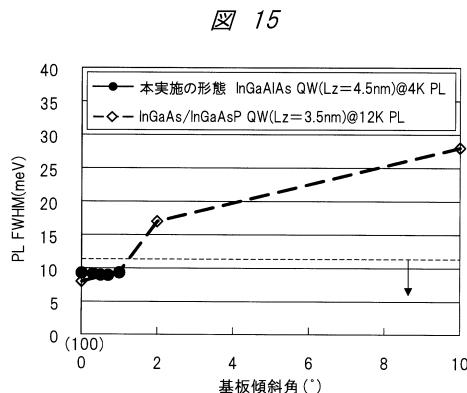

【図14】P L半値幅と基板傾斜角との関係を示すグラフである。

【図15】図14のグラフの部分拡大図である。

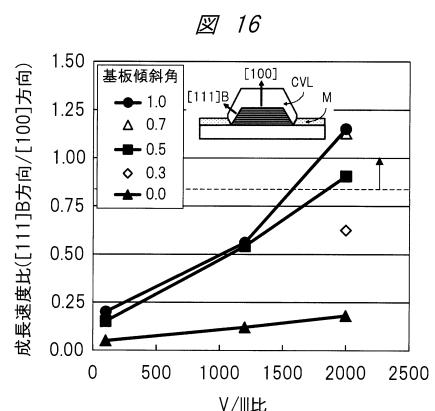

【図16】カバー層の形成時におけるV / I I I比と[100]方向の成長速度に対する[111]B方向の成長速度の比との関係を示すグラフである。

【図17】実施の形態2の半導体装置の構成を示す断面図である。

【図18】実施の形態2の半導体装置の構成を示す斜視図である。

【図19】実施の形態2の半導体装置の製造工程を示す断面図である。

【図20】実施の形態2の半導体装置の製造工程を示す断面図であって、図19に続く製造工程を示す断面図である。

【図21】実施の形態2の半導体装置の製造工程を示す断面図であって、図20に続く製造工程を示す断面図である。

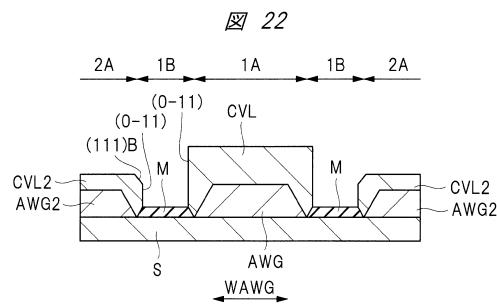

【図22】実施の形態2の半導体装置の製造工程を示す断面図であって、図21に続く製造工程を示す断面図である。

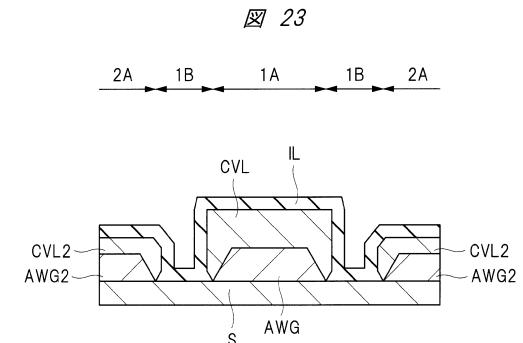

【図23】実施の形態2の半導体装置の製造工程を示す断面図であって、図22に続く製造工程を示す断面図である。

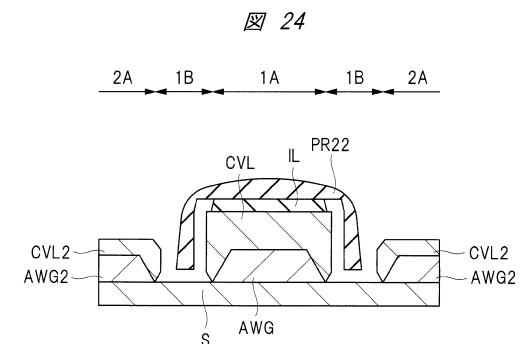

【図24】実施の形態2の半導体装置の製造工程を示す断面図であって、図23に続く製造工程を示す断面図である。

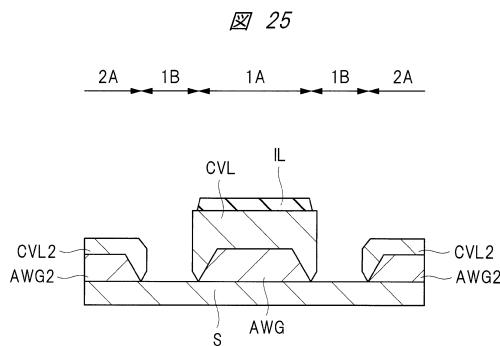

【図25】実施の形態2の半導体装置の製造工程を示す断面図であって、図24に続く製造工程を示す断面図である。

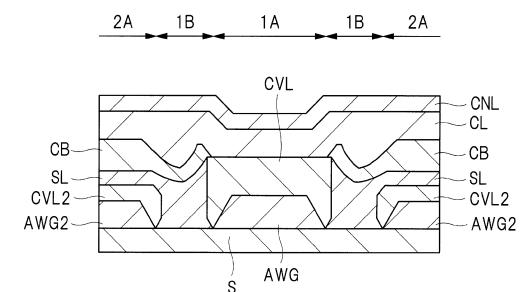

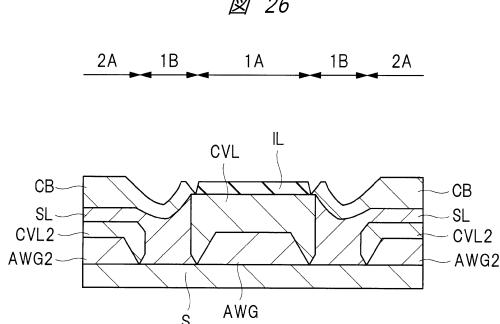

【図26】実施の形態2の半導体装置の製造工程を示す断面図であって、図25に続く製造工程を示す断面図である。

【図27】実施の形態2の半導体装置の製造工程を示す断面図であって、図26に続く製造工程を示す断面図である。

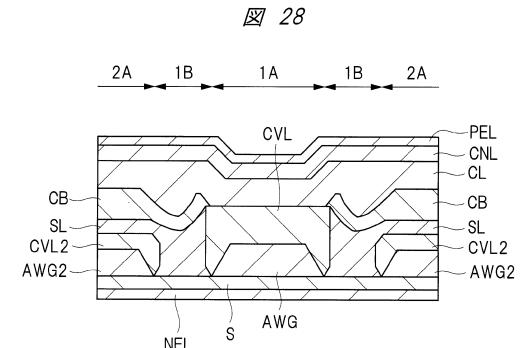

【図28】実施の形態2の半導体装置の製造工程を示す断面図であって、図27に続く製造工程を示す断面図である。

10

20

30

40

50

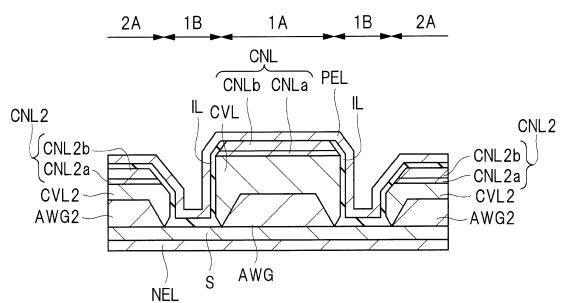

【図29】実施の形態1の半導体装置の変形例の構成を示す断面図である。

【図30】実施の形態2の半導体装置の変形例の構成を示す断面図である。

【発明を実施するための形態】

【0017】

以下の実施の形態においては便宜上その必要があるときは、複数のセクションまたは実施の形態に分割して説明するが、特に明示した場合を除き、それらはお互いに無関係なものではなく、一方は他方の一部または全部の変形例、応用例、詳細説明、補足説明等の関係にある。また、以下の実施の形態において、要素の数等（個数、数値、量、範囲等を含む）に言及する場合、特に明示した場合および原理的に明らかに特定の数に限定される場合等を除き、その特定の数に限定されるものではなく、特定の数以上でも以下でもよい。

10

【0018】

さらに、以下の実施の形態において、その構成要素（要素ステップ等も含む）は、特に明示した場合および原理的に明らかに必須であると考えられる場合等を除き、必ずしも必須のものではない。同様に、以下の実施の形態において、構成要素等の形状、位置関係等に言及するときは、特に明示した場合および原理的に明らかにそうでないと考えられる場合等を除き、実質的にその形状等に近似または類似するもの等を含むものとする。このことは、上記数等（個数、数値、量、範囲等を含む）についても同様である。

【0019】

以下、実施の形態を図面に基づいて詳細に説明する。なお、実施の形態を説明するための全図において、同一の機能を有する部材には同一または関連する符号を付し、その繰り返しの説明は省略する。また、複数の類似の部材（部位）が存在する場合には、総称の符号に記号を追加し個別または特定の部位を示す場合がある。また、以下の実施の形態では、特に必要なとき以外は同一または同様な部分の説明を原則として繰り返さない。

20

【0020】

また、実施の形態で用いる図面においては、断面図であっても図面を見易くするためにハッチングを省略する場合もある。また、平面図であっても図面を見易くするためにハッチングを付す場合もある。

【0021】

また、断面図および平面図において、各部位の大きさは実デバイスと対応するものではなく、図面を分かりやすくするため、特定の部位を相対的に大きく表示する場合がある。また、断面図と平面図が対応する場合においても、図面を分かりやすくするため、特定の部位を相対的に大きく表示する場合がある。

30

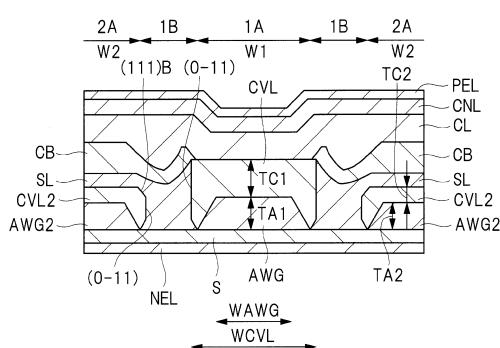

【0022】

（実施の形態1）

以下、図面を参照しながら本実施の形態の半導体装置について詳細に説明する。図1は、本実施の形態の半導体装置の構成を示す断面図および平面図である。図2は、本実施の形態の半導体装置の構成を示す斜視図である。図3～図11は、本実施の形態の半導体装置の製造工程を示す断面図である。

【0023】

〔構造説明〕

図1は、本実施の形態の半導体装置の構成を示す断面図であり、図1(A)は、断面図、図1(B)は、平面図である。図1(A)は、例えば、図1(B)のA-A断面に対応する。図1に示す半導体装置は、半導体レーザ（化合物半導体レーザともいう）である。この半導体装置は、III-V族化合物半導体、特に、InPを用いたリッジ型半導体レーザである。

40

【0024】

図1(A)および図2に示すように、本実施の形態の半導体装置は、基板S、基板Sの領域1A上に配置された活性層導波路（半導体光導波路ともいう）AWG、および活性層導波路AWG上に配置されたカバー層CVLを有する。カバー層CVL上には、コンタクト層CNLを介してp電極（p側電極、上部電極）PELが配置され、基板Sの裏面側に

50

は、n電極(n側電極、下部電極)NELが配置されている。基板S、カバー層CVLおよびコンタクト層CNLは、III-V族化合物半導体(半導体層)よりなる。

#### 【0025】

また、図1(B)に示すように、基板Sの領域1A、即ち、活性層導波路AWGの形成領域は、Y方向(図1(A)の奥行き方向)に延在する略矩形の領域である。言い換えれば、Y方向(図1(A)の奥行き方向、[1-1-1]方向)に長辺を有する領域である。この領域1Aの両端に領域1Bが配置されている。言い換えれば、領域1Bにより領域1Aが区画されている。領域1Bの外側には、領域2Aが配置されている。この領域2Aには、活性層導波路AWG2、カバー層CVL2およびコンタクト層CNL2が下から順に配置されている(図1(A)参照)。

10

#### 【0026】

基板Sは、n型(第1導電型)のInPよりなり、その表面が、(100)面から[1-1-1]方向へ、0.5°~1.0°の範囲で傾斜している傾斜基板である(図1(B)参照)。このような角度をオフ角(基板傾斜角ともいう)といい、この傾斜基板は、オフ角を有する基板である。また、基板Sの表面は、オフ角を有する表面である。図1(B)においては、オフ角を $\theta$ で示してある。即ち、図1(B)に示すように、B-B断面において、基板Sの表面は、(100)面に対しオフ角 $\theta$ を有する。

#### 【0027】

活性層導波路AWGは、ノンドープのInGaAlAsよりなる。この活性層導波路AWGは、エピタキシャル成長により形成される。この際、基板Sは、上記オフ角を有するため、成長後の活性層導波路AWGの表面は、(100)面から[1-1-1]方向へ、0.5°~1.0°の範囲で傾斜している。この活性層導波路AWGは、InGaAlAsで構成されるMQW(多重量子井戸)層とも呼ばれる。

20

#### 【0028】

カバー層CVLは、p型(第2導電型)のInP層よりなる。このカバー層CVLは、活性層導波路AWG上に、エピタキシャル成長により形成される。成長後のカバー層CVLおよび活性層導波路AWGの積層部(メサ部ともいう)の断面形状は、略矩形状となる。具体的には、カバー層CVLの表面の幅(WCVL)は、活性層導波路AWGの表面の幅(WAWG)より大きくなる。また、カバー層CVLおよび活性層導波路AWGの積層部の側面(側壁)は、基板Sの表面とほぼ垂直な(0-11)面を有する。このように、カバー層CVLおよび活性層導波路AWGの積層部の断面形状を略矩形状とすることで、通電領域を大きくすることができ(図13参照)、半導体装置の動作時の抵抗を低減することができる。

30

#### 【0029】

コンタクト層CNLは、III-V族化合物半導体よりなり、例えば、p型のInGaAs層よりなる。このコンタクト層CNLは、カバー層CVL上に配置されている。

#### 【0030】

誘電体膜ILは、酸化シリコン膜などの絶縁膜よりなる。この誘電体膜ILは、コンタクト層CNLの上面には配置されておらず、コンタクト層CNLの上面は、誘電体膜ILの開口部から露出している。

40

#### 【0031】

p電極PELは、例えば、パラジウム(Pd)膜とプラチナ( Pt)膜の積層膜よりなる。p電極PELは、誘電体膜ILの開口部から露出したコンタクト層CNLの上面に配置される。また、n電極NELは、例えば、チタン(Ti)膜と金(Au)膜の積層膜よりなる。n電極NELは、基板Sの裏面上に配置される。

#### 【0032】

活性層導波路AWG2は、活性層導波路AWGと同様に形成され、活性層導波路AWGと同じ材料よりなる。但し、活性層導波路AWG2が形成される領域2AのX方向の幅(W2)は、活性層導波路AWGが形成される領域1AのX方向の幅(W1)より大きいため、領域1Aにおいては、領域2Aより単位面積当たりの成長速度が大きくなる。よって

50

、活性層導波路 A W G の膜厚 T A 1 が、活性層導波路 A W G 2 の膜厚 T A 2 より大きくなる ( T A 1 > T A 2 )。同様に、カバー層 C V L 2 は、カバー層 C V L と同様に形成され、カバー層 C V L と同じ材料よりなるが、領域 2 A の X 方向の幅 ( W 2 ) が、領域 1 A の X 方向の幅 ( W 1 ) より大きいため、カバー層 C V L の膜厚 T C 1 が、カバー層 C V L 2 の膜厚 T C 2 より大きくなる ( T C 1 > T C 2 )。また、前述したように、カバー層 C V L の側面は、( 1 0 0 ) 面に垂直な ( 0 - 1 1 ) 面を有するのに対し、カバー層 C V L 2 の側面は、カバー層 C V L 2 の膜厚がカバー層 C V L より薄くなるために完全な略矩形状にはならず、( 0 - 1 1 ) 面の他に、( 1 1 1 ) B 面を有する。( 1 1 1 ) B 面とは、( 1 1 1 ) 面のうち、表面に主として V 族元素が露出する面である。

## 【 0 0 3 3 】

10

コンタクト層 C N L 2 は、コンタクト層 C N L と同様に形成され、コンタクト層 C N L と同じ材料よりなる。コンタクト層 C N L 2 上には、誘電体膜 I L を介して p 電極 P E L が配置されているため、コンタクト層 C N L 2 、活性層導波路 A W G 2 およびカバー層 C V L 2 は、後述する半導体装置（半導体レーザ）の動作には寄与しない。このように、領域 2 A の各層 ( A W G 2 、 C V L 2 、 C N L 2 ) は、半導体装置（半導体レーザ）の動作には寄与しない層であるが、領域 1 A の活性層導波路 A W G ( I n G a A l A s ) の組成の制御性やカバー層 C V L の平面形状（略矩形）の制御性を良好とするために必要になる。

## 【 0 0 3 4 】

20

次いで、半導体装置（半導体レーザ）の動作の一例について説明する。まず、 p 電極 P E L に正電圧を印加するとともに、 n 電極 N E L に負電圧を印加する。これにより、 p 電極 P E L から n 電極 N E L に向かって順方向電流が流れ、 p 電極 P E L からコンタクト層 C N L およびカバー層 C V L を介して活性層導波路 A W G に正孔が注入される。一方、 n 電極 N E L から基板 S を介して活性層導波路 A W G に電子が注入される。

## 【 0 0 3 5 】

活性層導波路 A W G においては、注入された正孔と電子によって反転分布が形成され、電子が伝導帯から価電子帯に遷移する誘導放出が起きる。これにより、位相の揃った光が発生する。そして、活性層導波路 A W G で発生した光は、活性層導波路 A W G よりも屈折率の低い周囲の半導体（カバー層 C V L や基板 S ）により、活性層導波路 A W G 内に閉じ込められる。そして、活性層導波路 A W G 内に閉じ込められた光は、半導体レーザに形成されている劈開面（レーザ端面）からなる共振器を往復することにより、さらなる誘導放出によって增幅される。その後、活性層導波路 A W G 内でレーザ光が発振して、半導体装置からレーザ光が射出される。

30

## 【 0 0 3 6 】

## [ 製法説明 ]

次いで、図 3 ~ 図 1 1 を参照しながら、本実施の形態の半導体装置の製造方法を説明するとともに、当該半導体装置の構成をより明確にする。図 3 ~ 図 1 1 は、本実施の形態の半導体装置の製造工程を示す断面図である。

## 【 0 0 3 7 】

40

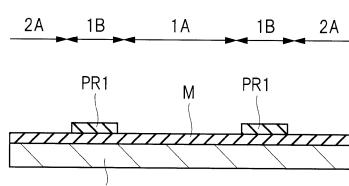

図 3 に示すように、基板 S 上に、誘電体マスク M を形成する。基板 S は、 n 型の I n P よりなり、前述したように、その表面が、( 1 0 0 ) 面から [ 1 - 1 - 1 ] 方向へ、 0 . 5 ° ~ 1 . 0 ° の範囲で傾斜している傾斜基板である（図 1 ( B ) 参照）。

## 【 0 0 3 8 】

このような傾斜基板である基板 S 上に、誘電体マスク M として、例えば、酸化シリコン膜を、 C V D ( Chemical Vapor Deposition ) 法などを用いて 1 0 0 n m 程度の膜厚で堆積する。次いで、誘電体マスク M 上に、フォトレジスト膜 P R 1 を形成し、露光・現像することにより、活性層導波路 A W G の形成領域である領域 1 A と、領域 2 A のフォトレジスト膜 P R 1 を除去する。言い換えれば、活性層導波路 A W G の形成領域である領域 1 A を囲む領域 1 B に、フォトレジスト膜 P R 1 を残存させる。

## 【 0 0 3 9 】

50

この活性層導波路 A W G の形成領域である領域 1 A は、 [ 0 - 1 - 1 ] 方向のストライプ形状である（図 1 ( B ) 参照）。

#### 【 0 0 4 0 】

次いで、フォトレジスト膜 P R 1 をマスクとして、誘電体マスク M をエッチングする。この後、フォトレジスト膜 P R 1 を除去する。これにより、図 4 に示すように、活性層導波路 A W G の形成領域である領域 1 A に開口部を有する誘電体マスク M が形成される。言い換えれば、活性層導波路 A W G の形成領域である領域 1 A を囲む領域 1 B に誘電体マスク M が形成される。この開口部の幅は、例えば、1.5 ~ 1.9  $\mu\text{m}$  程度である。この幅は、領域 1 A の X 方向の幅 W 1 と対応する。そして、この開口部からは、基板 S のオフ角を有する表面が露出する。また、残存する誘電体マスク M の幅は、5 ~ 15  $\mu\text{m}$  程度である。図 4 の断面図においては、活性層導波路 A W G の形成領域（領域 1 A ）の両側に、誘電体マスク M が残存している。言い換えれば、幅 5 ~ 15  $\mu\text{m}$  程度の誘電体マスク M が、1.5 ~ 1.9  $\mu\text{m}$  程度の間隔を置いて形成されている。また、領域 1 B の外側には領域 2 A が配置されている。図 4 等においては、領域 2 A の一部しか図示していないが、この領域 2 A の幅（X 方向の幅 W 2 ）は、例えば、250  $\mu\text{m}$  程度である。

#### 【 0 0 4 1 】

次いで、図 5 に示すように、上記開口部（領域 1 A ）、即ち、基板 S のオフ角を有する表面の露出部上に、活性層導波路 A W G を形成する。ここでは、活性層導波路 A W G として、I I I - V 族化合物半導体である I n P 層を、M O V P E (Metal Organic Vapor Phase Epitaxy) 法などを用いて形成する。M O V P E 法では、I I I 族元素の原料ガスと V 族元素の原料ガスとをキャリアガスを用いてチャンバー（処理室）内に導入し、開口部（領域 1 A ）に I n G a A 1 A s 層を成長させる。I n (インジウム)、G a (ガリウム)、A 1 (アルミニウム) の原料ガスとしては、T M I n (tri-methyl-indium)、T E G a (tri-ethyl-gallium)、T M A 1 (tri-methyl-aluminium) を用いることができる。また、A s (砒素) の原料ガスとしては、A s H 3 (アルシン) を用いることができる。混合された原料ガスが、加熱された基板 S の表面に到達すると、分解などの化学反応が生じ、下層の結晶情報を引き継いだ状態で、I n G a A 1 A s 層が成長（堆積）する。例えば、I I I 族元素の原料ガス（ここでは、T M I n、T E G a、T M A 1 ）の流量の和に対する V 族元素の原料ガス（ここでは、アルシン）の流量の比（V / I I I 比ともいう）を 200 以下として、活性層導波路（I n G a A 1 A s 層）A W G を形成する。この際、領域 2 A には、活性層導波路 A W G 2 が形成される。

#### 【 0 0 4 2 】

続いて、図 6 に示すように、活性層導波路 A W G 上にカバー層 C V L を形成する。ここでは、カバー層 C V L として、I I I - V 族化合物半導体である p 型の I n P 層を、M O V P E 法などを用いて形成する。即ち、活性層導波路 A W G を形成したチャンバー（処理室）内において、連続（継続）して p 型の I n P 層を形成する。この際、I n の原料ガスとしては、T M I n を用い、P（燐）の原料ガスとしては、P H 3 (ホスフィン) を用いるが、V / I I I 比を 200 以上とする。また、p 型不純物をドープしながら p 型の I n P 層を形成する。p 型不純物としては、Z n を用いることができ、例えば、原料ガス中に D E Z n (di-ethyl-zinc) を混合することにより、p 型の I n P 層を形成することができる。この際、領域 2 A には、カバー層 C V L 2 が形成される。

#### 【 0 0 4 3 】

次いで、図 7 に示すように、カバー層（p 型 I n P 層）C V L 上に、コンタクト層 C N L を形成する。ここでは、コンタクト層 C N L として、I I I - V 族化合物半導体である p 型の I n G a A s 層を、M O V P E 法などを用いて形成する。即ち、活性層導波路 A W G およびカバー層 C V L を形成したチャンバー（処理室）内において、連続して p 型の I n G a A s 層を形成する。この際、例えば、I n の原料ガスとしては、T M I n を用い、G a (ガリウム) の原料ガスとして、T M G a (tri-methyl-gallium) を用い、A s (砒素) の原料ガスとして A s H 3 (アルシン) を用いる。そして、V / I I I 比（ここでは、I I I 族元素の原料ガスである T M I n と T M G a の流量の和に対する V 族元素の原料ガ

10

20

30

40

50

スであるアルシンの流量の比)を100以下とする。また、p型不純物をドープしながらp型のInGaAs層を形成する。p型不純物としては、Znを用いることができ、例えば、原料ガス中にDEZnを混合することにより、p型のInGaAs層を形成することができる。この際、領域2Aには、コンタクト層CNL2が形成される。

#### 【0044】

上記のように、基板Sの領域1Aに、活性層導波路AWG、カバー層CVLおよびコンタクト層CNLを下から順に連続して一括で成長させる。この際、領域2Aには、活性層導波路AWG2、カバー層CVL2およびコンタクト層CNL2が、下から順に成長する。前述したように、領域2Aの幅(W2)は、領域1Aの幅(W1)より大きいため、領域1Aにおいては、単位面積当たりの成長速度が大きくなる。よって、活性層導波路AWGの膜厚TA1が、活性層導波路AWG2の膜厚TA2より大きくなる(TA1>TA2、図6参照)。同様に、カバー層CVLの膜厚TC1は、カバー層CVL2の膜厚TC2より大きくなる(TC1>TC2、図6参照)。また、カバー層CVL2の側面は、(0-11)面が露出する前の成長面である(111)B面が残存した状態となる。これにより、カバー層CVLの側面は、(100)面に垂直な(0-11)面を有するのに対し、カバー層CVL2の側面は、(0-11)面の他に、(111)B面を有している。なお、コンタクト層CNL、CNL2は、(100)面に垂直な(0-11)面や(111)B面上には成長せず、主に、カバー層CVL、CVL2の上面にコンタクト層CNL、CNL2が成長する。

#### 【0045】

このように、(100)面から[1-1-1]方向へ、0.5°~1.0°の範囲でオフ角を有する基板Sの表面上に、[0-1-1]方向に延在するように活性層導波路AWGを形成したので、活性層導波路AWGの膜厚(ウエル厚ともいう)の変動を低減し、良好なMQW(多重量子井戸)を得ることができる。また、活性層導波路AWG上に、III-V族化合物半導体よりなるカバー層CVLを、V/III比が2000以上の高V/III比で形成したので、誘電体マスクMの端部から基板Sの表面にほぼ垂直な(0-11)面が主として現れる側面を有するカバー層CVLを形成することができる。また、カバー層CVL、CVL2上に形成され、III-V族化合物半導体よりなるコンタクト層CNL、CNL2は、低V/III比で形成したので、基板Sにほぼ垂直な(0-11)面や(111)面上には、コンタクト層CNL、CNL2が成長せず、主に、カバー層CVL、CVL2の上面にコンタクト層CNL、CNL2が成長する。

#### 【0046】

次いで、図8に示すように、誘電体マスクMをエッティングにより除去する。次いで、図9に示すように、基板Sの上方に、誘電体膜ILとして、例えば、酸化シリコン膜を、CVD法などを用いて300nm程度の膜厚で堆積する。次いで、図10に示すように、誘電体膜IL上に、フォトレジスト膜PR2を形成し、露光・現像することにより、コンタクト層CNLの上方(領域1A)のフォトレジスト膜PR2を除去する。次いで、フォトレジスト膜PR2をマスクとして、誘電体膜ILをエッティングする。この後、フォトレジスト膜PR2を除去する。これにより、コンタクト層CNLの上面が誘電体膜ILの開口部から露出する。言い換えれば、コンタクト層CNLの上面以外の領域が誘電体膜ILで覆われる。即ち、カバー層CVL2が誘電体膜ILで覆われる。

#### 【0047】

次いで、図11に示すように、コンタクト層CNL上に、p電極PELを形成する。また、基板Sの裏面にn電極NELを形成する。例えば、コンタクト層CNLの露出部を含む誘電体膜IL上に、p電極PELとして、例えば、パラジウム(Pd)膜とプラチナ( Pt)膜の積層膜を形成する。これらの膜は、スパッタリング法や蒸着法などを用いて形成することができる。次いで、積層膜を所望の形状にパターニングすることにより、p電極PELを形成する。次いで、基板Sの裏面側を上面にして、基板Sの裏面を研磨することにより、基板Sを薄型化する。次いで、基板Sの裏面上に、n電極NELとして、例えば、チタン(Ti)膜と金(Au)膜の積層膜を形成する。これらの膜は、スパッタリン

10

20

30

40

50

グ法や蒸着法などを用いて形成することができる。なお、p電極P E Lやn電極N E Lとして、他の金属膜を用いてもよい。

【0048】

以上の工程により、図1に示す半導体装置を形成することができる。

【0049】

このように、本実施の形態によれば、オフ角を有する基板S上に、活性層導波路A W Gを形成し、その上に、カバー層C V Lを、高V / I I I比で形成したので、カバー層C V Lの成長断面が大きくなり、通電領域幅を確保することができる。よって、半導体素子の低抵抗化を図ることができる。

【0050】

図12は、比較例の半導体装置の通電領域を示す斜視図である。図13は、本実施の形態の半導体装置の通電領域を示す斜視図である。

【0051】

図12に示す半導体装置においては、オフ角を有さない基板Sの(100)面上に、活性層導波路A W Gを形成し、その上に、カバー層C V Lを形成している。この場合、活性層導波路A W Gおよびカバー層C V Lの側面は、基板Sの表面((100)面)に対して54.7°傾斜した(111)面となる。この際、カバー層C V Lの成長断面を大きくするために、その膜厚を大きくすると、成長断面に対してカバー層C V Lの上面、即ち、通電領域E A 1が小さくなる。これにより、半導体装置の動作時の抵抗が増加してしまう。また、抵抗の増加により、発熱が大きくなり、半導体装置の温度特性が低下してしまう。

【0052】

これに対し、本実施の形態においては、(100)面から[1-1-1]方向へ、0.5°～1.0°の範囲でオフ角を有する基板Sの表面の露出部上に、[0-1-1]方向に延在するように活性層導波路A W Gを形成し、さらに、その上部に、カバー層C V Lを、V / I I I比が2000以上の高V / I I I比で形成している。これにより、基板Sの表面にほぼ垂直な(0-11)面が主として現れる側面を有するようにカバー層C V Lを形成することができる。即ち、基板Sの表面に対してほぼ垂直な側面となるようにカバー層C V Lが成長するため、活性層導波路A W Gの形成領域(領域1A)に対応する通電領域E A 2を確保することができる。例えば、通電領域E A 2の幅を、1.5～1.9μm程度とすることができる。

【0053】

一方、基板Sの表面に対してほぼ垂直な側面を有するカバー層C V Lを形成するために、基板Sの表面を(111)面とする方法が考えられる(例えば、特許文献3参照)。しかしながら、(111)面や、(100)面から2°以上のオフ角を有する面上に、活性層導波路A W Gを形成した場合、結晶性が劣化し、PL半値幅が広がってしまう(非特許文献2、3、4参照)。

【0054】

この基板の傾斜角度とPL半値幅について、本発明者が検討した事項を以下に説明する。図14は、PL半値幅と基板傾斜角との関係を示すグラフである。図15は、図14のグラフの部分拡大図である。図14および図15の横軸は、基板傾斜角[°]であり、縦軸は、PL半値幅(P L F W H M、Photo Luminescence full width at half maximum)[m e V]である。

【0055】

本実施の形態の半導体装置の場合(黒丸の場合)は、図14および図15に示すように、基板傾斜角は、0°～1.0°の範囲であり、PL半値幅は、ほぼ9m e V程度で安定している。言い換えれば、PL半値幅の増加は見られない。

【0056】

これに対し、非特許文献2、3および4に記載の半導体装置の各種データに基づき本発明者が算出したところ、PL半値幅の増加が確認された。非特許文献2、3および4に記載の半導体装置をそれぞれ比較例A、比較例B、比較例Cとする。図14および図15に

10

20

30

40

50

示すように、比較例 A においては、PL 半値幅が、6 から 9 meV 程度に増加している。また、比較例 B においては、PL 半値幅が、14 から 17 meV 程度に増加している。また、比較例 C においては、PL 半値幅が、8 から 28 meV 程度に増加している。

#### 【0057】

なお、本実施の形態においては、活性層導波路 AWG を、層厚 (Lz) が 4.5 nm の InGaAlAs とした場合の温度 4 K における PL について PL 半値幅を測定した。また、比較例 A においては、活性層 (QW) が、層厚 (Lz) が 8 nm の InAsP / InP である場合の温度 15 K における PL について PL 半値幅を算出した。また、比較例 B においては、活性層が、層厚 (Lz) が 3.5 nm の InGaAs / InAlAs である場合の温度 77 K における PL について PL 半値幅を算出した。また、比較例 C においては、活性層が、層厚 (Lz) が 3.5 nm の InGaAs / InGaAsP である場合の温度 12 K における PL について PL 半値幅を算出した。

#### 【0058】

このように、材料や温度が異なるものではあるが、(100) 面からの傾斜角が 2° 以上のオフ角を有する基板においては、PL 半値幅が広がってしまうことが確認でき、本実施の形態のように、(100) 面からの傾斜角が 0° ~ 1.0° の範囲のオフ角を有する基板では、PL 半値幅の増加を抑制することが確認できた。

#### 【0059】

このように、本実施の形態においては、PL 半値幅の増加を抑える、即ち、活性層導波路 AWG の量子井戸幅の揺らぎが抑制されており、良好な結晶性を維持しつつ、通電領域 EA2 を大きくすることができていることが判明した。

#### 【0060】

さらに、カバー層 CVL を、高 V / III Ⅱ 比で形成することにより、カバー層 CVL の成長において、[100] 方向の成長速度に対する [111] B 方向の成長速度の比 ([111] B 方向の成長速度 / [100] 方向の成長速度) は、増大する。図 16 は、カバー層の形成時における V / III Ⅱ 比と [100] 方向の成長速度に対する [111] B 方向の成長速度の比との関係を示すグラフである。横軸は、V / III Ⅱ 比であり、縦軸は、成長速度比である。誘電体マスク M の開口部 (領域 1A) の幅は、例えば、1.5 ~ 1.9 μm 程度とし、誘電体マスク M の幅は、5 ~ 15 μm 程度とした。

#### 【0061】

高 V / III Ⅱ 比でカバー層 CVL を形成した場合、[100] 方向の成長速度に対する [111] B 方向の成長速度比 ([111] B 方向の成長速度 / [100] 方向の成長速度) は増大するが、誘電体マスク M 上へのかぶり成長はほとんど見られなかった。

#### 【0062】

また、図 16 に示すように、V / III Ⅱ 比を 2000 以上とすることで、[100] 方向に対する [111] B 方向の成長速度の比は、0.8 以上となり、高くなる。このように、[111] B 方向の成長が促進されるため、図 1 に示すように、カバー層 CVL の側面が、基板 S の表面に対してほぼ垂直となり、カバー層 CVL と活性層導波路 AWG の積層部の断面形状が略矩形の形状となる。即ち、図 12 に示すような、カバー層 CVL の側面が、斜面となり、カバー層 CVL と活性層導波路 AWG の積層部の断面形状が、短い上底を有する台形状となる場合と比較し、通電領域 (EA2 > EA1) を大きく確保することができる。これにより、半導体装置の動作時の抵抗を低減することができる。

#### 【0063】

##### (実施の形態 2)

以下、図面を参照しながら本実施の形態の半導体装置について詳細に説明する。図 17 は、本実施の形態の半導体装置の構成を示す断面図である。図 18 は、本実施の形態の半導体装置の構成を示す斜視図である。図 19 ~ 図 28 は、本実施の形態の半導体装置の製造工程を示す断面図である。

#### 【0064】

##### [構造説明]

10

20

30

40

50

図17に示す半導体装置は、半導体レーザである。この半導体装置は、III-V族化合物半導体、特に、InPを用いた埋め込み型半導体レーザである。本実施の形態の半導体装置は、活性層導波路AWGとカバー層CVLとの積層部（メサ部ともいう）の両側を、半絶縁性のIII-V族化合物半導体層で埋め込んだ構成を有する。

【0065】

図17および図18に示すように、本実施の形態の半導体装置は、基板S、基板Sの領域1A上に配置された活性層導波路AWG、および活性層導波路AWG上に配置されたカバー層CVLを有する。カバー層CVL上には、第2カバー層CLおよびコンタクト層CNLを介してp電極（p側電極、上部電極）PELが配置され、基板Sの裏面側には、n電極（n側電極、下部電極）NELが配置されている。また、活性層導波路AWGとカバー層CVLとの積層部の両側は、半絶縁層SLで埋め込まれている。そして、この半絶縁層SL上には電流ブロック層CBが配置され、さらに、半絶縁層SLおよびカバー層CVL上には、第2カバー層CLが配置されている。

【0066】

基板S、カバー層CVLおよびコンタクト層CNLは、III-V族化合物半導体（半導体層）よりなる。

【0067】

また、基板Sの領域1A、即ち、活性層導波路AWGの形成領域は、実施の形態1の場合と同様に、略矩形の領域である（図1（B）参照）。言い換えれば、Y方向（図17の奥行き方向、[1-1-1]方向）に長辺を有する略矩形の領域である。この領域1Aの両側に領域1Bが配置されている。言い換えれば、領域1Bにより領域1Aが区画されている。領域1Bの外側には、領域2Aが配置されている。この領域2Aには、活性層導波路AWG2およびカバー層CVL2が下から順に配置されている。そして、カバー層CVL2上は、半絶縁層SLで覆われている。よって、領域2Aの各層（AWG2、CVL2）は、半導体装置（半導体レーザ）の動作には寄与しない層となる。

【0068】

基板Sは、実施の形態1の場合と同様に、n型のInPよりなり、その表面が、（100）面から[1-1-1]方向へ、0.5°～1.0°の範囲で傾斜している傾斜基板である（図1（B）参照）。このような角度をオフ角という。

【0069】

活性層導波路AWGは、実施の形態1の場合と同様に、ノンドープのInPよりなる。この活性層導波路AWGは、エピタキシャル成長により形成される。この際、基板Sは、上記オフ角を有するため、成長後の活性層導波路AWGの表面は、（100）面から[1-1-1]方向へ、0.5°～1.0°の範囲で傾斜している。

【0070】

カバー層CVLは、実施の形態1の場合と同様に、p型（第2導電型）のInP層よりなる。このカバー層CVLは、活性層導波路AWG上に、エピタキシャル成長により形成される。成長後のカバー層CVLおよび活性層導波路AWGの積層部の断面形状は、略矩形状となる。具体的には、カバー層CVLの表面の幅（WCVL）は、活性層導波路AWGの表面の幅（WAWG）より大きくなる。また、カバー層CVLおよび活性層導波路AWGの積層部の側面（側壁）は、基板Sの表面とほぼ垂直な（0-11）面を有する。このように、カバー層CVLおよび活性層導波路AWGの積層部の断面形状を略矩形状とすることで、通電領域を大きくすることができ（図13参照）、半導体装置の動作時の抵抗を低減することができる。

【0071】

この半絶縁層SLは、活性層導波路AWGとカバー層CVLとの積層部の側面と接するように配置されている。半絶縁層SLは、例えば、Fe（鉄）を含有するInP層（半導体層）よりなる。このように、InP層にFeを含有させることにより、層の容量を低減しながら電子の流れをブロックすることができる。このために10Gbps以上の高速動作が可能となる。例えば、半絶縁層SLは、活性層導波路AWGとカバー層CVLとの積層

部より高い絶縁性を有する。

【0072】

電流ブロック層CBは、例えば、n型のInP層(半導体層)よりなる。この電流ブロック層CBは、半絶縁層SL上にのみ配置され、カバー層CVLの上面上には配置されない。

【0073】

第2カバー層CLは、例えば、p型のInP層(半導体層)よりなる。この第2カバー層CLは、電流ブロック層CBおよびカバー層CVLの上面上に配置されている。

【0074】

コンタクト層CNLは、III-V族化合物半導体よりなり、例えば、p型のInGaAs層よりなる。このコンタクト層CNLは、第2カバー層CL上に配置されている。

10

【0075】

p電極PELは、例えば、パラジウム(Pd)とプラチナ( Pt )の積層膜よりなる。p電極PELは、コンタクト層CNL上に配置される。また、n電極NELは、例えば、チタン(Ti)と金(Au)の積層膜よりなる。n電極NELは、基板Sの裏面上に配置される。

【0076】

活性層導波路AWG2は、活性層導波路AWGと同様に形成され、活性層導波路AWGと同じ材料よりなる。但し、活性層導波路AWG2が形成される領域2AのX方向の幅(W2)は、活性層導波路AWGが形成される領域1AのX方向の幅(W1)より大きいため、領域1Aにおいては、領域2Aより単位面積当たりの成長速度が大きくなる。よって、活性層導波路AWGの膜厚TA1が、活性層導波路AWG2の膜厚TA2より大きくなる(TA1 > TA2)。同様に、カバー層CVL2は、カバー層CVLと同様に形成され、カバー層CVLと同じ材料よりなるが、領域2AのX方向の幅(W2)が、領域1AのX方向の幅(W1)より大きいため、カバー層CVLの膜厚TC1が、カバー層CVL2の膜厚TC2より大きくなる(TC1 > TC2)。また、前述したように、カバー層CVLの側面は、(100)面に垂直な(0-11)面を有するのに対し、カバー層CVL2の側面は、(0-11)面の他に、(111)B面を有する。

20

【0077】

上記活性層導波路AWG2およびカバー層CVL2の積層部は、半絶縁層SLで覆われているため、半導体装置(半導体レーザ)の動作には寄与しない。

30

【0078】

なお、本実施の形態の半導体装置(半導体レーザ)の動作は、実施の形態1と同様であるため、その説明を省略する。

【0079】

[製法説明]

次いで、図19～図28を参照しながら、本実施の形態の半導体装置の製造方法を説明するとともに、当該半導体装置の構成をより明確にする。図19～図28は、本実施の形態の半導体装置の製造工程を示す断面図である。

【0080】

40

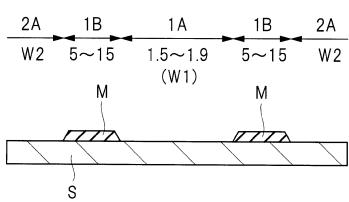

図19に示すように、基板S上に、誘電体マスクMを形成する。基板Sは、n型のInPよりなり、前述したように、その表面が、(100)面から[1-1-1]方向へ、0.5°～1.0°の範囲で傾斜している傾斜基板である(図1(B)参照)。

【0081】

このような傾斜基板である基板S上に、誘電体マスクMとして、例えば、酸化シリコン膜を、CVD法などを用いて100nm程度の膜厚で堆積する。次いで、誘電体マスクM上に、フォトレジスト膜PR1を形成し、露光・現像することにより、活性層導波路AWGの形成領域である領域1Aと、領域2Aのフォトレジスト膜PR1を除去する。言い換えれば、活性層導波路AWGの形成領域である領域1Aを囲む領域1Bに、フォトレジスト膜PR1を残存させる。

50

## 【0082】

この活性層導波路AWGの形成領域である領域1Aは、[0-1-1]方向のストライプ形状である(図1(B)参照)。

## 【0083】

次いで、フォトレジスト膜PR1をマスクとして、誘電体マスクMをエッチングする。この後、フォトレジスト膜PR1を除去する。これにより、図20に示すように、活性層導波路AWGの形成領域である領域1Aに開口部を有する誘電体マスクMが形成される。言い換れば、活性層導波路AWGの形成領域である領域1Aを囲む領域1Bに誘電体マスクMが形成される。この開口部の幅は、例えば、1.5~1.9μm程度である。この幅は、領域1AのX方向の幅W1と対応する。そして、この開口部からは、基板Sのオフ角を有する表面が露出する。また、残存する誘電体マスクMの幅は、5~15μm程度である。図20の断面図においては、活性層導波路AWGの形成領域(領域1A)の両側に、誘電体マスクMが残存している。言い換れば、幅5~15μm程度の誘電体マスクMが、1.5~1.9μm程度の間隔を置いて形成されている。また、領域1Bの外側には領域2Aが配置されている。図20等においては、領域2Aの一部しか図示していないが、この領域2Aの幅(X方向の幅W2)は、開口部の幅(1.5~1.9μm程度)よりも大きくなり大きく、例えば、250μm程度である。

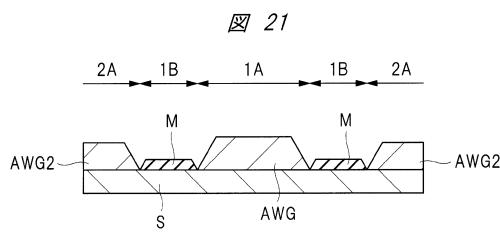

## 【0084】

次いで、図21に示すように、上記開口部(領域1A)、即ち、基板Sのオフ角を有する表面の露出部上に、活性層導波路AWGを形成する。ここでは、活性層導波路AWGとして、III-V族化合物半導体であるInGaAlAs層を、MOVPE法などを用いて形成する。MOVPE法では、III族元素の原料ガスとV族元素の原料ガスとをキャリアガスを用いてチャンバー(処理室)内に導入し、開口部(領域1A)にInGaAlAs層を成長させる。In(インジウム)の原料ガスとしては、TMIn、TEGa、TMA1を用いることができる。また、As(砒素)の原料ガスとしては、AsH<sub>3</sub>(アルシン)を用いることができる。混合された原料ガスが、加熱された基板Sの表面に到達すると、分解などの化学反応が生じ、下層の結晶情報を引き継いだ状態で、InGaAlAs層が成長(堆積)する。例えば、III族元素の原料ガス(ここでは、TMIn、TEGa、TMA1)の流量の和に対するV族元素の原料ガス(ここでは、アルシン)の流量の比(V/III比ともいう)を200以下として、活性層導波路(InGaAlAs層)AWGを形成する。この際、領域2Aには、活性層導波路AWG2が形成される。

## 【0085】

続いて、図22に示すように、活性層導波路AWG上にカバー層CVLを形成する。ここでは、カバー層CVLとして、III-V族化合物半導体であるp型のInP層を、MOVPE法などを用いて形成する。即ち、活性層導波路AWGを形成したチャンバー(処理室)内において、連続(継続)してp型のInP層を形成する。この際、活性層導波路(InP層)AWGの形成時と同様に、Inの原料ガスとしては、TMInを用い、Pの原料ガスとしては、ホスフィンを用いるが、V/III比を2000以上とする。また、p型不純物をドープしながらp型のInP層を形成する。p型不純物としては、Znを用いることができ、例えば、原料ガス中にDEZnを混合することにより、p型のInP層を形成することができる。この際、領域2Aには、カバー層CVL2が形成される。

## 【0086】

上記のように、基板Sの領域1Aに、活性層導波路AWGおよびカバー層CVLを下から順に連続して一括で成長させる。この際、領域2Aには、活性層導波路AWG2およびカバー層CVL2が、下から順に成長する。前述したように、領域2Aの幅(W2)は、領域1Aの幅(W1)よりも大きいため、領域1Aにおいては、単位面積当たりの成長速度が大きくなる。よって、活性層導波路AWGの膜厚TA1が、活性層導波路AWG2の膜厚TA2よりも大きくなる(TA1>TA2)。同様に、カバー層CVLの膜厚TC1は、カバー層CVL2の膜厚TC2よりも大きくなる(TC1>TC2)。また、カバー層CVL2の側面は、(0-11)面が露出する前の成長面である(111)B面が残存した状

10

20

30

40

50

態となる。これにより、カバー層 C V L の側面は、(100)面に垂直な(0-11)面を有するのに対し、カバー層 C V L 2 の側面は、(0-11)面の他に、(111)B面を有している。

【0087】

このように、(100)面から[1-1-1]方向へ、0.5°~1.0°の範囲でオフ角を有する基板 S の表面上に、[0-1-1]方向に延在するように活性層導波路 A W G を形成したので、活性層導波路 A W G の膜厚(ウエル厚ともいう)の変動を低減し、良好な M Q W (多重量子井戸)を得ることができる。また、活性層導波路 A W G 上に、I I I - V 族化合物半導体よりなるカバー層 C V L を、V / I I I 比が 2000 以上の高 V / I I I 比で形成したので、誘電体マスク M の端部から基板 S の表面上にほぼ垂直な(0-11)面が主として現れる側面を有するカバー層 C V L を形成することができる。 10

【0088】

次いで、図 23 に示すように、誘電体マスク M をエッティングにより除去し、基板 S の上方に、誘電体膜 I L として、例えば、酸化シリコン膜を、C V D 法などを用いて 300 nm 程度の膜厚で堆積する。

【0089】

次いで、図 24 に示すように、誘電体膜 I L 上に、フォトレジスト膜を形成し、露光・現像することにより、カバー層 C V L の上面および側面を、誘電体膜 I L 介して覆うフォトレジスト膜 P R 2 2 を形成する。次いで、フォトレジスト膜 P R 2 2 をマスクとして、誘電体膜 I L をウエットエッティングする。この際、カバー層 C V L の側面と接する誘電体膜 I L もエッティングされ、カバー層 C V L の上面にのみ誘電体膜 I L が残存する。この後、フォトレジスト膜 P R 2 を除去する。これにより、図 25 に示すように、カバー層 C V L の上面が誘電体膜 I L で覆われる。 20

【0090】

次いで、図 26 に示すように、基板 S の露出部上を含む、カバー層 C V L 2 上に、半絶縁層 S L として半絶縁型の I n P 層を、M O V P E 法などを用いて形成する。I n P 層を半絶縁化するために、層中に、例えば、F e を導入する。例えば、I I I 族元素の原料ガスと V 族元素の原料ガスとをキャリアガスを用いてチャンバー(処理室)内に導入し、I n P 層を成長させる。この際、F e を混入させるため、例えば、フェロセン(ferrocene)を原料ガスに混合することにより、半絶縁性を有する F e 含有 I n P 層を形成することができる。これにより、カバー層 C V L および活性層導波路 A W G の積層部の両側を、半絶縁層 S L で埋め込むことができる。また、カバー層 C V L 2 上を、半絶縁層 S L で覆うことができる。 30

【0091】

次いで、半絶縁層 S L 上に、電流ブロック層 C B として、I I I - V 族化合物半導体である n 型の I n P 層を、M O V P E 法などを用いて形成する。n 型不純物としては、S i を用いることができ、例えば、原料ガス中に S i <sub>2</sub> H <sub>6</sub> (ジシラン)を混合することにより、n 型の I n P 層を形成することができる。これにより、カバー層 C V L および活性層導波路 A W G の積層部の両側を、半絶縁層 S L と電流ブロック層 C B との積層膜で埋め込むことができる。 40

【0092】

次いで、図 27 に示すように、誘電体膜 I L を除去する。これにより、カバー層 C V L の上面が露出する。次いで、カバー層 C V L の露出部および電流ブロック層 C B 上に、第 2 カバー層 C L を形成する。ここでは、第 2 カバー層 C L として、I I I - V 族化合物半導体である p 型の I n P 層を、M O V P E 法などを用いて形成する。

【0093】

次いで、第 2 カバー層 C L 上に、コンタクト層 C N L を形成する。ここでは、コンタクト層 C N L として、I I I - V 族化合物半導体である p 型の I n G a A s 層を、M O V P E 法などを用いて形成する。

【0094】

次いで、図28に示すように、コンタクト層CNL上に、p電極PELを形成する。また、基板Sの裏面にn電極NELを形成する。例えば、コンタクト層CNL上に、p電極PELとして、例えば、パラジウム(Pd)膜とプラチナ(Pt)膜の積層膜を形成する。これらの膜は、スパッタリング法や蒸着法などを用いて形成することができる。次いで、積層膜を所望の形状にパターニングすることにより、p電極PELを形成する。次いで、基板Sの裏面側を上面にして、基板Sの裏面を研磨することにより、基板Sを薄型化する。次いで、基板Sの裏面上に、n電極NELとして、例えば、チタン(Ti)膜と金(Au)膜の積層膜を形成する。これらの膜は、スパッタリング法や蒸着法などを用いて形成することができる。なお、p電極PELやn電極NELとして、他の金属膜を用いてもよい。

10

## 【0095】

以上の工程により、図17に示す半導体装置を形成することができる。

## 【0096】

このように、本実施の形態においても、オフ角を有する基板S上に、活性層導波路AWGを形成し、その上に、カバー層CVLを、高V/III比で形成したので、実施の形態1の場合と同様に、カバー層CVLの成長断面が大きくなり、通電領域を大きく確保することができる。これにより、半導体装置の動作時の抵抗を低減することができる。

## 【0097】

特に、本実施の形態においては、カバー層CVLの側面を誘電体層よりも熱伝導性の良好な材料である、InPを用いた半絶縁層SLで埋め込んだので、放熱性が向上し、半導体装置の温度特性を向上させることができる。さらに、カバー層CVLの上面を熱伝導性の良好な材料（例えば、InP層）を用いた第2カバー層CLで覆うことにより、放熱性が向上し、半導体装置の温度特性を向上させることができる。

20

## 【0098】

## （変形例）

上記実施の形態1および2においては、コンタクト層CNLとして、p型のInGaAs層よりなる単層膜を用いたが、コンタクト層CNLを積層膜としてもよい。

## 【0099】

図29は、実施の形態1の変形例の半導体装置の構成を示す断面図である。コンタクト層CNL、CNL2以外の構成およびその製造工程は、実施の形態1（図1等）と同様であるため、その詳細な説明を省略する。

30

## 【0100】

図29に示すように、実施の形態1の変形例においては、コンタクト層CNLが、第1層CNLaと、その上部の第2層CNLbとの積層膜よりなる。

## 【0101】

第1層CNLaは、II - V族化合物半導体よりなり、例えば、p型のInGaAs層よりなる。また、第2層CNLbは、II - V族化合物半導体よりなり、例えば、p型のInGaAsP層よりなる。

## 【0102】

なお、コンタクト層CNL2も同様に、第1層（例えば、p型のInGaAs層）CNL2aと、その上部の第2層（例えば、p型のInGaAsP層）CNL2bとの積層膜よりなる。

40

## 【0103】

このような積層構造のコンタクト層CNL、CNL2は、MOVPE法などを用いて形成することができる。即ち、活性層導波路AWGおよびカバー層CVLを形成したチャンバー（処理室）内において、連続してコンタクト層CNL、CNL2を形成する。例えば、Inの原料ガスとしては、TMInを用い、Ga（ガリウム）の原料ガスとして、TMGaを用い、As（砒素）の原料ガスとしてAsH<sub>3</sub>（アルシン）用いたMOVPE法により、p型のInGaAs層（第1層CNLa、CNL2a）を形成する。そして、上記原料ガスに、Pの原料ガスとして、PH<sub>3</sub>（ホスフィン）を加え、p型のInGaAsP

50

層（第2層C N L b、C N L 2 b）を形成する。なお、p型不純物としては、D E Z nを用いることができ、例えば、原料ガス中にD E Z nを混合することにより、p型の層を形成することができる。

【0104】

図30は、実施の形態2の変形例の半導体装置の構成を示す断面図である。コンタクト層C N L、C N L 2以外の構成およびその製造工程は、実施の形態2（図17等）と同様であるため、その詳細な説明を省略する。

【0105】

図30に示すように、実施の形態2の変形例においては、コンタクト層C N Lが、第1層C N L aと、その上部の第2層C N L bとの積層膜よりなる。

10

【0106】

第1層C N L aは、I I I - V族化合物半導体よりなり、例えば、p型のI n G a A s層よりなる。また、第2層C N L bは、I I I - V族化合物半導体よりなり、例えば、p型のI n G a A s P層よりなる。

【0107】

このような積層構造のコンタクト層C N Lは、M O V P E法などを用いて形成することができる。即ち、活性層導波路A W Gおよびカバー層C V Lを形成したチャンバー内において、連続してコンタクト層C N Lを形成する。例えば、I nの原料ガスとしては、T M I nを用い、G aの原料ガスとして、T M G aを用い、A sの原料ガスとしてA s H <sub>3</sub>用いたM O V P E法により、p型のI n G a A s層（第1層C N L a）を形成する。そして、上記原料ガスに、Pの原料ガスとして、P H <sub>3</sub>を加え、p型のI n G a A s P層（第2層C N L b）を形成する。なお、p型不純物としては、Z nを用いることができ、例えば、原料ガス中にD E Z nを混合することにより、p型の層を形成することができる。

20

【0108】

ここで、上記実施の形態および変形例で説明した半導体装置（半導体レーザ）の適用部に制限はないが、例えば、1.25～1.65 μm帯の光通信用の半導体装置（半導体レーザ）として用いることができる。

【0109】

以上、本発明者によってなされた発明を実施の形態に基づき具体的に説明したが、本発明は上記実施の形態に限定されるものではなく、その要旨を逸脱しない範囲で種々変更可能であることはいうまでもない。

30

【符号の説明】

【0110】

1 A 領域

1 B 領域

2 A 領域

A W G 活性層導波路

A W G 2 活性層導波路

C B 電流ブロック層

C L 第2カバー層

40

C N L コンタクト層

C N L a 第1層

C N L b 第2層

C N L 2 コンタクト層

C N L 2 a 第1層

C N L 2 b 第2層

C V L カバー層

C V L 2 カバー層

E A 1 通電領域

E A 2 通電領域

50

I L 誘電体膜

M 誘電体マスク

N E L n 電極

P E L p 電極

P R 1 フォトレジスト膜

P R 2 フォトレジスト膜

P R 2 2 フォトレジスト膜

S 基板

S L 半絶縁層

T A 1 膜厚

10

T A 2 膜厚

T C 1 膜厚

T C 2 膜厚

W 1 幅

W 2 幅

W A W G 幅

W C V L 幅

【図 1】

【図 2】

【図 3】

【図 4】

【図5】

【図6】

【図7】

【図10】

【図11】

【図8】

【図9】

【図12】

【図13】

AWG: 活性層導波路

CVL: カバー層

EA2: 通電領域

S: 基板

【図14】

【図16】

【図15】

【図17】

図17

【図18】

図18

【図19】

図19

【図20】

図20

【図21】

【図22】

【図23】

【図24】

【図25】

【図27】

【図26】

【図28】

【図29】

図29

【図30】

図30

---

フロントページの続き

(72)発明者 加藤 豪

神奈川県川崎市中原区下沼部1753番地 ルネサスエレクトロニクス株式会社内

(72)発明者 渡邊 功

神奈川県川崎市中原区下沼部1753番地 ルネサスエレクトロニクス株式会社内

審査官 小濱 健太

(56)参考文献 特開2003-133647(JP, A)

特開2010-135506(JP, A)

特開2001-148542(JP, A)

特開平10-079349(JP, A)

(58)調査した分野(Int.Cl., DB名)

H01S 5/00 - 5/50