(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第5203293号

(P5203293)

(45) 発行日 平成25年6月5日(2013.6.5)

(24) 登録日 平成25年2月22日(2013.2.22)

(51) Int.Cl.

F 1

|      |        |           |      |        |      |

|------|--------|-----------|------|--------|------|

| G06F | 3/041  | (2006.01) | G06F | 3/041  | 330D |

| G02F | 1/1345 | (2006.01) | G02F | 1/1345 |      |

| G02F | 1/1333 | (2006.01) | G02F | 1/1333 |      |

| G09F | 9/30   | (2006.01) | G09F | 9/30   | 349Z |

| G09G | 3/36   | (2006.01) | G09G | 3/36   |      |

請求項の数 20 (全 32 頁) 最終頁に続く

(21) 出願番号

特願2009-123261 (P2009-123261)

(22) 出願日

平成21年5月21日 (2009.5.21)

(65) 公開番号

特開2010-271925 (P2010-271925A)

(43) 公開日

平成22年12月2日 (2010.12.2)

審査請求日

平成24年3月16日 (2012.3.16)

(73) 特許権者 598172398

株式会社ジャパンディスプレイウェスト

愛知県知多郡東浦町大字緒川字上舟木50

番地

(74) 代理人 100092152

弁理士 服部 毅巖

野口 幸治

東京都港区港南1丁目7番1号 ソニー株

式会社内

(72) 発明者 中西 貴之

東京都港区港南1丁目7番1号 ソニー株

式会社内

(72) 発明者 石崎 剛司

東京都港区港南1丁目7番1号 ソニー株

式会社内

最終頁に続く

(54) 【発明の名称】表示装置および電子機器

## (57) 【特許請求の範囲】

## 【請求項 1】

複数の表示画素電極と、

前記表示画素電極と対向して設けられた共通電極と、

画像表示機能を有する表示機能層と、

前記表示画素電極に画像信号に基づく画素電圧を印加すると共に、前記共通電極に画像表示制御の駆動周期と同期して極性が反転する共通駆動電圧を印加することにより、画像表示制御を行う表示制御回路と、

前記共通電極と協働して静電容量を形成するタッチ検出電極と、

前記共通電極への前記共通駆動電圧の印加に応じて前記タッチ検出電極から得られる検出信号に基づき、外部近接物体を検出するための検出動作を行うタッチ検出回路と

を備え、前記タッチ検出回路は、前記検出信号の取得時における前記画像信号の階調に基づいて

その検出信号を補正し、検出動作を行う

表示装置。

## 【請求項 2】

前記タッチ検出回路は、

前記画像信号の階調と、画像表示のためのその階調の画像信号の書き込み動作に起因した内部ノイズを含む検出信号の信号値とを対応付けてなるリファレンスノイズデータと、

前記画像信号とを用いて、前記タッチ検出電極から得られる検出信号を補正する

10

20

請求項 1 に記載の表示装置。

**【請求項 3】**

前記タッチ検出回路は、

所定の数の表示画素電極を含む画素領域ごとに、実際に入力された前記画像信号の階調と前記リファレンスノイズデータにおける検出信号の信号値とを対応付けてなる補正テーブルを作成し、

その補正テーブルを用いて、前記タッチ検出電極から得られる検出信号を補正する

請求項 2 に記載の表示装置。

**【請求項 4】**

前記タッチ検出回路は、

10

前記画素領域ごとに、前記補正テーブル内の検出信号の信号値と前記タッチ検出電極から得られる検出信号の信号値との間で、減算もしくは除算を行うことにより、前記タッチ検出電極から得られる検出信号の補正信号を生成する

請求項 3 に記載の表示装置。

**【請求項 5】**

前記共通電極および前記タッチ検出電極がそれぞれ、ストライプ状の複数の電極パターンに分割されており、

各画素領域は、前記タッチ検出電極を構成する電極パターンのストライプピッチに等しい水平方向長さと、前記共通電極を構成する電極パターンの幅に等しい垂直方向長さとを有し、

20

前記画素領域の前記水平方向長さの中心に、前記タッチ検出電極の電極パターンが位置している

請求項 3 または請求項 4 に記載の表示装置。

**【請求項 6】**

前記タッチ検出回路は、1つの水平ラインに沿ったすべての画素領域で個別に行われた補正の結果を加味して、その水平ライン内の各画素領域において、前記タッチ検出電極から得られる検出信号の再補正を行う

請求項 5 に記載の表示装置。

**【請求項 7】**

前記タッチ検出回路は、前記画素領域ごとに、前記画像信号の階調に応じた前記リファレンスノイズデータにおける検出信号の信号値を用いて、前記タッチ検出電極から得られる検出信号の信号値を規格化することにより、そのタッチ検出電極から得られる検出信号を補正する

30

請求項 2 に記載の表示装置。

**【請求項 8】**

前記共通電極および前記タッチ検出電極がそれぞれ、ストライプ状の複数の電極パターンに分割されており、

各画素領域は、前記タッチ検出電極を構成する電極パターンのストライプピッチに等しい水平方向長さと、前記共通電極を構成する電極パターンの幅に等しい垂直方向長さとを有し、

40

前記画素領域の前記水平方向長さの中心に、前記タッチ検出電極の電極パターンが位置している

請求項 7 に記載の表示装置。

**【請求項 9】**

前記タッチ検出回路は、1つの水平ラインに沿ったすべての画素領域で個別に行われた補正の結果を加味して、その水平ライン内の各画素領域において、前記タッチ検出電極から得られる検出信号の再補正を行う

請求項 8 に記載の表示装置。

**【請求項 10】**

前記リファレンスノイズデータが、有効表示期間同士の間に位置するブランкиング期間

50

において、前記表示制御回路によって前記画素電極に供給された所定の検出用パターン信号に応じて前記タッチ検出電極から得られる内部ノイズ検出信号を基に作成されたものである

請求項 2 ないし請求項 9 のいずれか 1 項に記載の表示装置。

**【請求項 1 1】**

前記表示制御回路は、前記検出用パターン信号として、所定階調の画像信号を前記画素電極に供給し、

前記タッチ検出回路は、前記所定階調に対応する前記内部ノイズ検出信号を取得する

請求項 1 0 に記載の表示装置。

**【請求項 1 2】**

前記表示制御回路は、複数回のブランкиング期間において、互いに異なる複数の階調の画像信号を前記検出用パターン信号として前記画素電極に供給し、

前記タッチ検出回路は、それぞれの階調に対応する前記内部ノイズ検出信号を取得する

請求項 1 1 に記載の表示装置。

**【請求項 1 3】**

前記リファレンスノイズデータが、所定の実験を行うことにより予め得られた実験データである

請求項 2 ないし請求項 9 のいずれか 1 項に記載の表示装置。

**【請求項 1 4】**

前記共通電極が、ストライプ状の複数の電極パターンに分割されている

請求項 1 ないし請求項 1 3 のいずれか 1 項に記載の表示装置。

**【請求項 1 5】**

前記表示制御回路は、前記複数の電極パターンのうちの一部の電極パターンを選択してそれらを同時に駆動すると共に、その選択すべき電極パターンを順次代えながら駆動する

請求項 1 4 に記載の表示装置。

**【請求項 1 6】**

前記表示制御回路が形成された回路基板と、

前記回路基板と対向して配設された対向基板と

を備え、

前記表示画素電極が、前記回路基板の、前記対向基板に近い側に配設され、

前記共通電極が、前記対向基板の、前記回路基板に近い側に配設され、

前記回路基板の前記表示画素電極と、前記対向基板の前記共通電極との間に、前記表示機能層が挿設されている

請求項 1 ないし請求項 1 5 のいずれか 1 項に記載の表示装置。

**【請求項 1 7】**

前記表示機能層が液晶層である

請求項 1 6 に記載の表示装置。

**【請求項 1 8】**

前記表示制御回路が形成された回路基板と、

前記回路基板と対向して配設された対向基板と

を備え、

前記回路基板に前記共通電極および前記表示画素電極が絶縁層を介して順に積層され、前記回路基板の前記表示画素電極と、前記対向基板との間に、前記表示機能層が挿設されている

請求項 1 ないし請求項 1 5 のいずれか 1 項に記載の表示装置。

**【請求項 1 9】**

前記表示機能層が液晶層であり、横電界モードでの液晶表示が行われる

請求項 1 8 に記載の表示装置。

**【請求項 2 0】**

タッチセンサ付きの表示装置を備え、

10

20

30

40

50

前記表示装置は、

複数の表示画素電極と、

前記表示画素電極と対向して設けられた共通電極と、

画像表示機能を有する表示機能層と、

前記表示画素電極に画像信号に基づく画素電圧を印加すると共に、前記共通電極に画像表示制御の駆動周期と同期して極性が反転する共通駆動電圧を印加することにより、画像表示制御を行う表示制御回路と、

前記共通電極と協働して静電容量を形成するタッチ検出電極と、

前記共通電極への前記共通駆動電圧の印加に応じて前記タッチ検出電極から得られる検出信号に基づき、外部近接物体を検出するための検出動作を行うタッチ検出回路と

を備え、

前記タッチ検出回路は、前記検出信号の取得時における前記画像信号の階調に基づいてその検出信号を補正し、検出動作を行う

電子機器。

#### 【発明の詳細な説明】

##### 【技術分野】

##### 【0001】

本発明は、液晶表示装置等の表示装置に係わり、特に、ユーザが指等で触れることにより情報入力が可能な静電容量式のタッチセンサを備えた表示装置、およびそのような表示装置を備えた電子機器に関する。 20

##### 【背景技術】

##### 【0002】

近年、いわゆるタッチパネルと呼ばれる接触検出装置（以下、タッチセンサという。）を液晶表示装置上に直接装着すると共に、液晶表示装置に各種のボタンを表示させることにより、通常のボタンの代わりとして情報入力を可能とした表示装置が注目されている。この技術は、モバイル機器の画面の大型化傾向の中にあって、ディスプレイとボタンの配置の共用化を可能にすることから、省スペース化や部品点数の削減という大きなメリットをもたらす。しかしながら、この技術には、タッチセンサの装着によって液晶モジュールの全体の厚さが厚くなるという問題があった。特にモバイル機器用途においては、タッチセンサの傷防止のための保護層が必要となることから、液晶モジュールが益々厚くなる傾向があり、薄型化のトレンドに反するという問題があった。 30

##### 【0003】

そこで、例えば特許文献1，2には、静電容量型のタッチセンサを形成したタッチセンサ付き液晶表示素子が提案され、薄型化が図られている。これは、液晶表示素子の観察側基板とその外面に配置された観察用偏光板との間にタッチセンサ用導電膜を設け、このタッチセンサ用導電膜と偏光板の外面との間に、偏光板の外面をタッチ面とした静電容量型タッチセンサを形成するようにしたものである。また、例えば特許文献3には、タッチセンサを表示装置に内蔵するようにしたものが提案されている。

##### 【先行技術文献】

##### 【特許文献】

##### 【0004】

【特許文献1】特開2008-9750号公報

【特許文献2】米国特許6057903号明細書

【特許文献3】特表昭56-500230号公報

##### 【発明の概要】

##### 【発明が解決しようとする課題】

##### 【0005】

しかしながら、上記特許文献1，2に開示されたタッチセンサ付き液晶表示素子では、原理的に、タッチセンサ用導電膜が利用者と同電位にあることが必要であり、利用者がきちんと接地されている必要がある。したがって、コンセントから電源を取っているような 50

据置型のテレビジョン受像機はともかく、モバイル機器用途に適用するのは現実的に見て困難である。また、上記技術では、タッチセンサ用導電膜が利用者の指に極めて接近していることが必要なので、液晶表示素子の例えは奥深い部分に配設することが無理である等、配設部位が制限される。すなわち、設計の自由度が小さい。さらに、上記技術では、その構成上、タッチセンサ駆動部や座標検出部といった回路部分を、液晶表示素子の表示駆動回路部とは別個に設けなければならず、装置全体としての回路の集積化が困難である。

#### 【0006】

そこで、元々表示用駆動電圧の印加用に設けられた共通電極に加えて、この共通電極との間に静電容量を形成するタッチ検出電極を新たに設けることが考えられる（新構造の静電容量型のタッチセンサを備えた表示装置）。この静電容量は物体の接触の有無によって変化するため、表示制御回路により共通電極に印加される表示用駆動電圧をタッチセンサ用駆動信号としても利用（兼用）するようにすれば、静電容量の変化に応じた検出信号がタッチ検出電極から得られるからである。そして、この検出信号を所定のタッチ検出回路に入力するようにすれば、物体の接触の有無が検出可能になる。また、この手法によれば、利用者の電位が不定であることが多いモバイル機器用途にも適合可能なタッチセンサ付き表示装置を得ることができる。さらに、表示機能層のタイプに応じて設計の自由度が高いタッチセンサ付き表示装置を得ることができると共に、表示用の回路とセンサ用の回路とを1つの回路基板上に一体に集積することが容易になり、回路の集積化も容易であるという利点がある。

#### 【0007】

ここで、上記特許文献1～3や上記新構造のものを含め、静電容量型のタッチセンサでは、各画素の表示素子への画素信号（画像信号）の書き込みの際に、その動作に起因したノイズ（内部ノイズ）が検出信号に付加されてしまうという問題がある。

#### 【0008】

そこで、上記特許文献2、3では、画像信号の書き込み動作に起因するノイズによる誤動作（誤検出）を防止するため、タッチセンサと表示素子との間に、透明な導電層（シールド層）を設けている。そして、この導電層を一定電位に固定することにより、上記した表示素子からのノイズをシールドすることが可能となっている。

#### 【0009】

ところが、この手法では、検出信号線とシールド層との間に大きな容量が形成されることから、検出信号線から得られる検出信号が大幅に減衰してしまったり、駆動線の容量が非常に大きくなつて消費電力等が大幅に増大するという問題があった。

#### 【0010】

また、上記特許文献3のように、表示用の駆動回路の一部を利用してタッチセンサ用の検出信号を生成している場合には、表示素子と検出電極との間にシールド層を配置すると、検出信号もシールドされてしまい、検出動作ができなくなってしまう。

#### 【0011】

更に、上記新構造の静電容量型のタッチセンサを備えた表示装置では、前述したように、表示パネルにおける書き込み波形を用いて位置を検出している。そのため、開口率や製造プロセスなどの観点から、有効表示エリア内にシールド層を設けて画像信号の書き込み動作に起因したノイズを取り除くのは難しいと考えられる。

#### 【0012】

このようにして、静電容量型のタッチセンサでは、シールド層を用いることなく、画像信号の書き込み動作に起因したノイズ（内部ノイズ）を除去して物体の検出精度を向上させるのは困難であった。

#### 【0013】

本発明はかかる問題点に鑑みてなされたもので、その目的は、シールド層を用いずに物体の検出精度を向上させることが可能な静電容量型のタッチセンサを備えた表示装置、およびそのような表示装置を備えた電子機器を提供することにある。

#### 【課題を解決するための手段】

10

20

30

40

50

## 【0014】

本発明の表示装置は、複数の表示画素電極と、この表示画素電極と対向して設けられた共通電極と、画像表示機能を有する表示機能層と、表示画素電極に画像信号に基づく画素電圧を印加すると共に、共通電極に画像表示制御の駆動周期と同期して極性が反転する共通駆動電圧を印加することにより、画像表示制御を行う表示制御回路と、共通電極と協働して静電容量を形成するタッチ検出電極と、共通電極への共通駆動電圧の印加に応じてタッチ検出電極から得られる検出信号に基づき、外部近接物体を検出するための検出動作を行うタッチ検出回路とを備えたものである。また、このタッチ検出回路は、検出信号の取得時における前記画像信号の階調に基づいてその検出信号を補正し、検出動作を行うようになっている。

10

## 【0015】

本発明の電子機器は、上記本発明の表示装置を備えたものである。

## 【0016】

本発明の表示装置および電子機器では、元々表示用駆動電圧の印加用に設けられた共通電極と、新たに設けたタッチ検出電極との間に、静電容量が形成される。この静電容量は、物体の接触の有無によって変化する。したがって、表示制御回路により共通電極に印加される共通駆動電圧を、タッチセンサ用駆動信号としても利用（兼用）することにより、静電容量の変化に応じた検出信号がタッチ検出電極から得られる。そして、この検出信号をタッチ検出回路に入力することにより、外部近接物体（物体の接触の有無等）が検出される。ここで、タッチ検出回路は、検出信号の取得時における画像信号の階調に基づいてその検出信号を補正し、検出動作を行う。これにより、画像表示制御の際の画像信号の書き込み動作に起因して検出信号に含まれるノイズ（内部ノイズ）の影響を低減しつつ、検出動作を行うことができる。

20

## 【発明の効果】

## 【0017】

本発明の表示装置および電子機器によれば、静電容量の変化に応じてタッチ検出電極から得られる検出信号に基づいて外部近接物体を検出すると共に、タッチ検出回路において、検出信号の取得時における画像信号の階調に基づいてその検出信号を補正して検出動作を行うようにしたので、従来のようなシールド層を用いることなく、上記内部ノイズの影響を低減しつつ検出動作を行うことができる。よって、静電容量型のタッチセンサを備えた表示装置において、シールド層を用いずに物体の検出精度を向上させることが可能となる。

30

## 【図面の簡単な説明】

## 【0018】

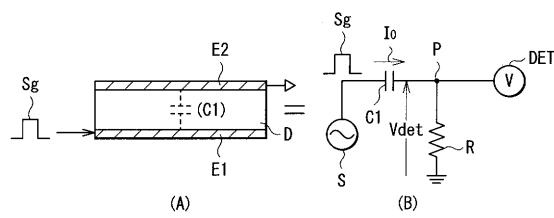

【図1】本発明に係るタッチセンサ付きの表示装置の動作原理を説明するための図であり、指非接触時の状態を示す図である。

【図2】本発明に係るタッチセンサ付きの表示装置の動作原理を説明するための図であり、指接触時の状態を示す図である。

【図3】本発明に係るタッチセンサ付きの表示装置の動作原理を説明するための図であり、タッチセンサの駆動信号および検出信号の波形の一例を示す図である。

40

【図4】本発明の第1の実施の形態に係るタッチセンサ付きの表示装置の概略断面構造を表す断面図である。

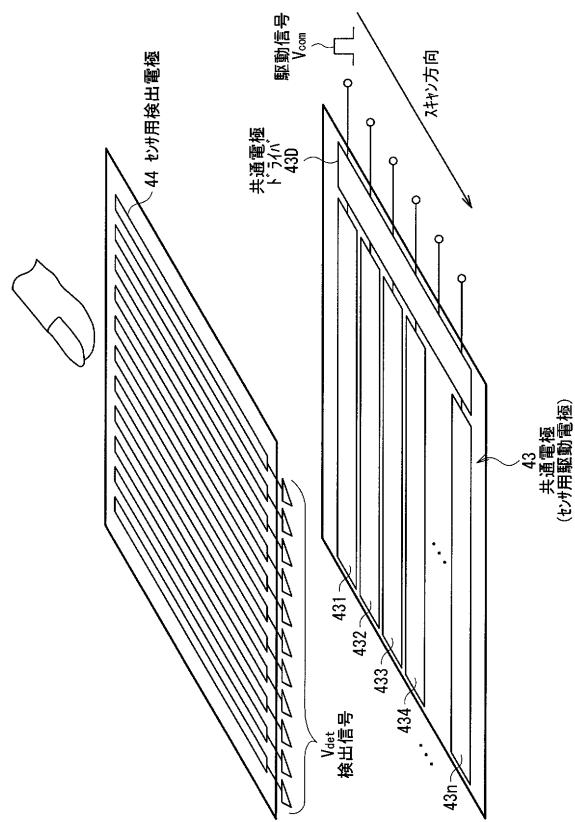

【図5】図4に示した表示装置の要部（共通電極およびセンサ用検出電極）の一構成例を示す斜視図である。

【図6】図4に示した表示装置における画素構造およびドライバの詳細構成の一例を表すプロック図である。

【図7】図4に示した表示装置における画素構造およびドライバの詳細構成の他の例を表すプロック図である。

【図8】図4に示した表示装置における検出回路等の一構成例を示す回路図である。

【図9】共通電極の線順次動作駆動の一例を表す模式図である。

50

【図10】表示装置における検出動作の際の表示書き込み動作に起因したノイズ（内部ノイズ）について説明するためのタイミング波形図である。

【図11】検出信号波形と検出期間との関係について説明するためのタイミング波形図である。

【図12】第1の実施の形態に係る内部ノイズの除去方法の一例（手法1）について説明するための流れ図である。

【図13】図12に示した手法1の詳細を説明するための模式図である。

【図14】信号線の書き込み電圧と検出信号電圧との関係を示す実験データの一例を表す特性図である。

【図15】図4に示した表示装置における単位補正領域について説明するための平面図である。 10

【図16】第1の実施の形態に係る内部ノイズの除去方法の他の例（手法2）について説明するための流れ図である。

【図17】図16に示した手法2の詳細を説明するための模式図である。

【図18】第1の実施の形態に係る内部ノイズの除去方法を用いた場合における各種の画像信号パターンに対する内部ノイズの除去効果の一例を表す図である。

【図19】第1の実施の形態の変形例に係る内部ノイズ量の算出手法（補正テーブルの作成手法）の一例について説明するための流れ図である。

【図20】垂直プランキング期間における内部ノイズ量の算出手法について説明するためのタイミング波形図である。 20

【図21】水平プランキング期間における内部ノイズ量の算出手法について説明するためのタイミング波形図である。

【図22】本発明の第2の実施の形態に係るタッチセンサ付きの表示装置の概略断面構造を表す断面図である。

【図23】図22に示した表示装置における画素基板の一部の詳細構成に表す断面図および平面図である。

【図24】図22に示した表示装置の要部の拡大斜視図である。

【図25】図22に示した表示装置の動作を説明するための断面図である。

【図26】第2の実施の形態の変形例に係るタッチセンサ付きの表示装置の概略断面構造を表す断面図である。 30

【図27】第2の実施の形態の他の変形例に係るタッチセンサ付きの表示装置の概略断面構造を表す断面図である。

【図28】上記各実施の形態等の表示装置の適用例1における（A）表側から見た外観、（B）裏側から見た外観を表す斜視図である。

【図29】（A）は適用例2の表側から見た外観を表す斜視図であり、（B）は裏側から見た外観を表す斜視図である。

【図30】適用例3の外観を表す斜視図である。

【図31】適用例4の外観を表す斜視図である。

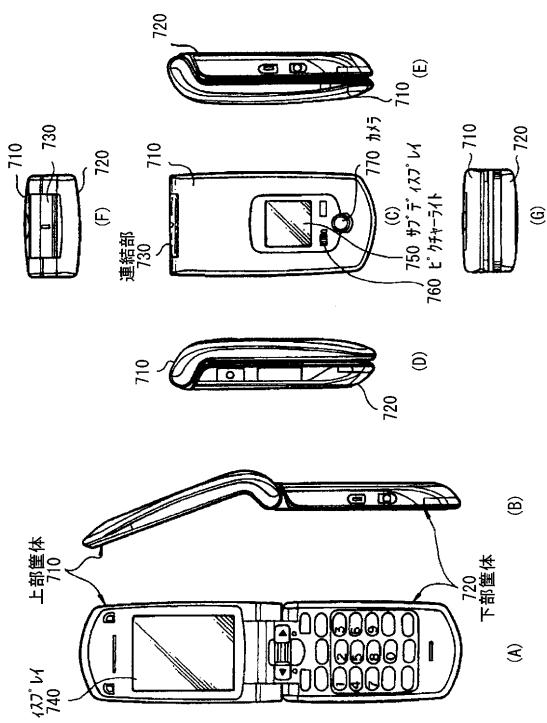

【図32】（A）は適用例5の開いた状態の正面図、（B）はその側面図、（C）は閉じた状態の正面図、（D）は左側面図、（E）は右側面図、（F）は上面図、（G）は下面図である。 40

### 【発明を実施するための形態】

#### 【0019】

以下、本発明の実施の形態について、図面を参照して詳細に説明する。なお、説明は以下の順序で行う。

##### タッチ検出方式の基本原理

1. 第1の実施の形態（表示の際の画像信号を利用した内部ノイズ除去方法の例）

变形例（プランキング期間を利用した内部ノイズ量の算出手法の例）

2. 第2の実施の形態（表示素子として横電界モードの液晶素子を用いた例）

3. 適用例（タッチセンサ付きの表示装置の電子機器への適用例）

50

#### 4. その他の変形例

##### 【0020】

<タッチ検出方式の基本原理>

まず最初に、図1～図3を参照して、本発明のタッチセンサ付きの表示装置におけるタッチ検出方式の基本原理について説明する。このタッチ検出方式は、静電容量型タッチセンサとして具現化されるものであり、例えば図1(A)に示したように、誘電体Dを挟んで互いに対向配置された一対の電極(駆動電極E1および検出電極E2)を用い、容量素子を構成する。この構造は、図1(B)に示した等価回路として表される。駆動電極E1、検出電極E2および誘電体Dによって、容量素子C1が構成される。容量素子C1は、その一端が交流信号源(駆動信号源)Sに接続され、他端Pは抵抗器Rを介して接地されると共に、電圧検出器(検出回路)DETに接続される。交流信号源Sから駆動電極E1(容量素子C1の一端)に所定の周波数(例えば数kHz～十数kHz程度)の交流矩形波Sg(図3(B))を印加すると、検出電極E2(容量素子C1の他端P)に、図3(A)に示したような出力波形(検出信号Vdet)が現れる。なお、この交流矩形波Sgは、後述するコモン駆動信号Vcomに相当するものである。

##### 【0021】

指を接触していない状態では、図1に示したように、容量素子C1に対する充放電に伴って、容量素子C1の容量値に応じた電流I0が流れる。このときの容量素子C1の他端Pの電位波形は、例えば図3(A)の波形V0のようになり、これが電圧検出器DETによって検出される。

##### 【0022】

一方、指を接触した状態では、図2に示したように、指によって形成される容量素子C2が容量素子C1に直列に追加された形となる。この状態では、容量素子C1,C2に対する充放電に伴って、それぞれ電流I1,I2が流れる。このときの容量素子C1の他端Pの電位波形は、例えば図3(A)の波形V1のようになり、これが電圧検出器DETによって検出される。このとき、点Pの電位は、容量素子C1,C2を流れる電流I1,I2の値によって定まる分圧電位となる。このため、波形V1は、非接触状態での波形V0よりも小さい値となる。電圧検出器DETは、後述するように、検出した電圧を所定のしきい値電圧Vthと比較し、このしきい値電圧以上であれば非接触状態と判断する一方、しきい値電圧未満であれば接触状態と判断する。このようにして、タッチ検出が可能となる。

##### 【0023】

<1. 第1の実施の形態>

##### [表示装置1の構成例]

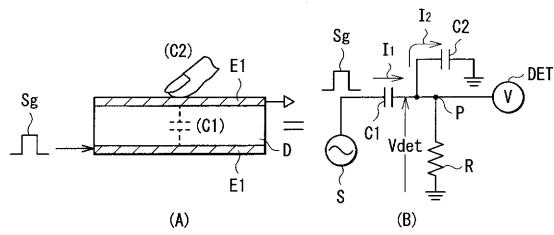

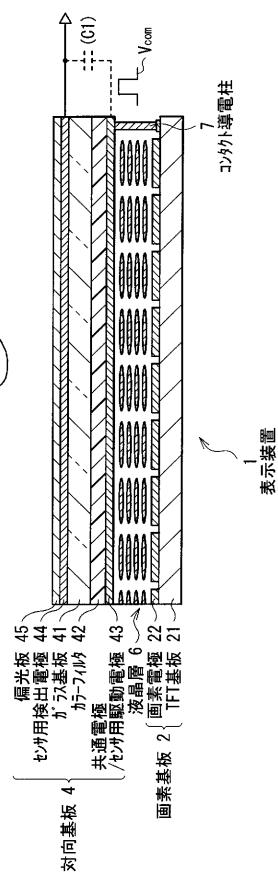

図4は、本発明の第1の実施の形態に係るタッチセンサ付きの表示装置1の要部断面構造を表すものである。この表示装置1は、表示素子として液晶表示素子を用いると共に、この液晶表示素子に元々備えられている電極の一部(後述する共通電極43)および表示用駆動信号(後述するコモン駆動信号Vcom)を兼用して静電容量型タッチセンサを構成したものである。

##### 【0024】

図4に示したように、この表示装置1は、画素基板2と、この画素基板2に対向して配置された対向基板4と、画素基板2と対向基板4との間に挿設された液晶層6とを備えている。

##### 【0025】

画素基板2は、回路基板としてのTFT基板21と、このTFT基板21上にマトリクス状に配設された複数の画素電極22とを有する。TFT基板21には、各画素電極22を駆動するための図示しない表示ドライバやTFT(薄膜トランジスタ)の他、各画素電極に画像信号を供給するソース線(後述するソース線25)や、各TFTを駆動するゲート線(後述するゲート線126)等の配線が形成されている。TFT基板21にはまた、後述するタッチ検出動作を行う検出回路(図8)が形成されていてもよい。

10

20

30

40

50

## 【0026】

対向基板4は、ガラス基板41と、このガラス基板41の一方の面に形成されたカラー フィルタ42と、このカラーフィルタ42の上に形成された共通電極43とを有する。カラーフィルタ42は、例えば赤(R)、緑(G)、青(B)の3色のカラーフィルタ層を周期的に配列して構成したもので、各表示画素(画素電極22)ごとにR、G、Bの3色が1組として対応付けられている。共通電極43は、タッチ検出動作を行うタッチセンサの一部を構成するセンサ用駆動電極としても兼用されるものであり、図1における駆動電極E1に相当する。

## 【0027】

共通電極43は、コンタクト導電柱7によってTFT基板21と連結されている。このコンタクト導電柱7を介して、TFT基板21から共通電極43に交流矩形波形のコモン駆動信号Vcomが印加されるようになっている。このコモン駆動信号Vcomは、画素電極22に印加される画素電圧とともに各画素の表示電圧を画定するものであるが、タッチセンサの駆動信号としても兼用されるものであり、図1の駆動信号源Sから供給される交流矩形波Sgに相当する。すなわち、このコモン駆動信号Vcomは、所定の周期ごとに極性反転するものとなっている。

10

## 【0028】

ガラス基板41の他方の面には、センサ用検出電極(タッチ検出電極)44が形成され、さらに、このセンサ用検出電極44の上には、偏光板45が配設されている。センサ用検出電極44は、タッチセンサの一部を構成するもので、図1における検出電極E2に相当する。

20

## 【0029】

液晶層6は、電界の状態に応じてそこを通過する光を変調するものであり、例えば、TN(ツイステッドネマティック)、VA(垂直配向)、ECB(電界制御複屈折)等の各種モードの液晶が用いられる。

## 【0030】

なお、液晶層6と画素基板2との間、および液晶層6と対向基板4との間には、それぞれ配向膜が配設され、また、画素基板2の下面側には入射側偏光板が配置されるが、ここでは図示を省略している。

## 【0031】

30

(共通電極43およびセンサ用検出電極44の詳細構成例)

図5は、対向基板4における共通電極43およびセンサ用検出電極44の一構成例を斜視状態にて表したものである。この例では、共通電極43は、図の左右方向に延在する複数のストライプ状の電極パターン(ここでは、一例としてn個(n:2以上の整数)の共通電極431~43nからなる)に分割されている。各電極パターンには、共通電極ドライバ43Dによってコモン駆動信号Vcomが順次供給され、後述するように時分割的に線順次走査駆動が行われるようになっている。一方、センサ用検出電極44は、共通電極43の電極パターンの延在方向と直交する方向に延びる複数のストライプ状の電極パターンから構成されている。センサ用検出電極44の各電極パターンからは、それぞれ、検出信号Vdetが出力され、図6~図8等に示す検出回路8に入力されるようになっている。

40

## 【0032】

(画素構造およびドライバの構成例)

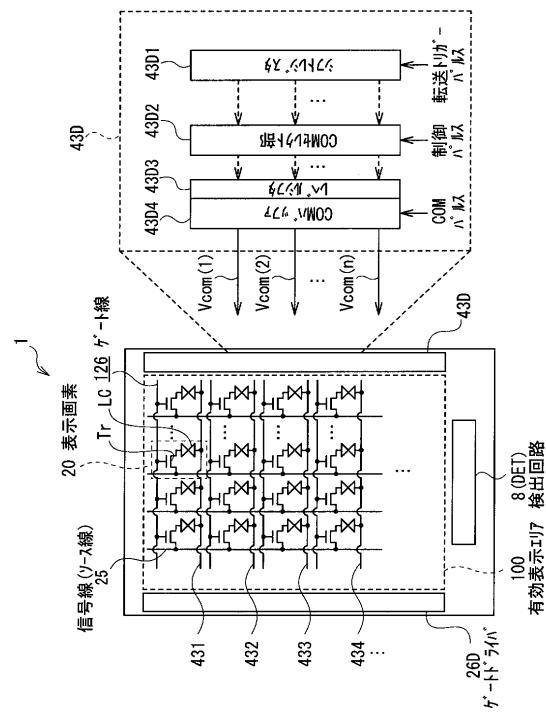

図6および図7は、表示装置1における画素構造および各種ドライバの構成例を表したものである。表示装置1では、有効表示エリア100内に、TFT素子Trと液晶素子LCとを有する複数の画素(表示画素20)がマトリクス状に配置されている。

## 【0033】

図6に示した例では、表示画素20には、ゲートドライバ26Dに接続されたゲート線126と、図示しないソースドライバに接続された信号線(ソース線)25と、共通電極ドライバ43Dに接続された共通電極431~43nとが接続されている。共通電極ドライバ43は、前述したように、共通電極431~43nに対してコモン駆動信号Vcom(

50

$V_{com}(1) \sim V_{com}(n)$  を順次供給するものである。この共通電極ドライバ43Dは、例えば、シフトレジスタ43D1と、COMセレクト部43D2と、レベルシフタ43D3と、COMバッファ43D4とを有している。

#### 【0034】

シフトレジスタ43D1は、入力パルスを順次転送するためのロジック回路である。具体的には、このシフトレジスタ43D1に対して転送トリガーパルス（スタートパルス）を入力することにより、クロック転送を開始するようになっている。また、1フレーム期間内で複数回のスタートパルスを入力するようにした場合には、その度に転送を繰り返すことができるようになっている。なお、シフトレジスタ43D1としては、複数個の共通電極431～43nをそれぞれ制御するために、各々独立した転送ロジック回路としてもよい。ただし、その場合には制御回路規模が大きくなるため、後述する図7に示したように、転送ロジック回路は、ゲートドライバと共に共通電極ドライバとで共用するようになることが好ましく、更には、共通電極43の個数に関わらず単一であることが好ましい。10

#### 【0035】

COMセレクト部43D2は、コモン駆動信号 $V_{com}$ を、有効表示エリア100内の各表示画素20に対して出力するか否かを制御するロジック回路である。すなわち、コモン駆動信号 $V_{com}$ の出力を、有効表示エリア100内の位置等に応じて制御している。さらに、詳細は後述するが、このCOMセレクト部43D2に対して入力する制御パルスを可変とすることにより、例えば1水平ラインごとにコモン駆動信号 $V_{com}$ の出力位置を任意に移動させたり、複数の水平期間後に出力位置を移動させたりすることが可能となっている。20

#### 【0036】

レベルシフタ43D3は、COMセレクト部43D2から供給されるコモン駆動信号 $V_{com}$ の電位を、制御するのに十分な電位レベルまでシフトさせるための回路である。

#### 【0037】

COMバッファ43D4は、コモン駆動信号 $V_{com}$  ( $V_{com}(1) \sim V_{com}(n)$ ) を順次供給するための最終出力ロジック回路であり、出力バッファ回路もしくはスイッチ回路等を含んで構成されている。

#### 【0038】

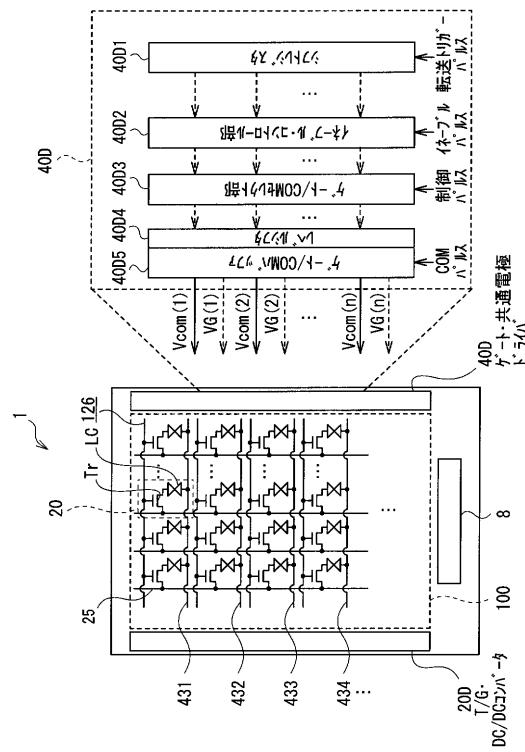

一方、図7に示した例では、表示画素20には、ゲート・共通電極ドライバ40Dに接続されたゲート線1\_2\_6および共通電極431～43nと、図示しないソースドライバに接続された信号線（ソース線）25とが接続されている。ゲート・共通電極ドライバ43は、ゲート線1\_2\_6を介して各表示画素20に対してゲート駆動信号を供給すると共に、共通電極431～43nに対してコモン駆動信号 $V_{com}$  ( $V_{com}(1) \sim V_{com}(n)$ ) を順次供給するものである。このゲート・共通電極ドライバ40Dは、例えば、シフトレジスタ40D1と、イネーブル・コントロール部40D2と、ゲート/COMセレクト部40D3と、レベルシフタ40D4と、ゲート/COMバッファ40D5とを有している。30

#### 【0039】

シフトレジスタ40D1は、ゲートドライバと共に共通電極ドライバとで共用されていること以外は、前述したシフトレジスタ43D1と同様の機能を有している。40

#### 【0040】

イネーブル・コントロール部40D2は、シフトレジスタ40D1から転送されたクロックパルスを利用してイネーブルパルスを取り込むことにより、ゲート線1\_2\_6を制御するためのパルスを生成するものである。

#### 【0041】

ゲート/COMセレクト部40D3は、コモン駆動信号 $V_{com}$ およびゲート信号 $V_G$ をそれぞれ、有効表示エリア100内の各表示画素20に対して出力するか否かを制御するロジック回路である。すなわち、コモン駆動信号 $V_{com}$ およびゲート信号 $V_G$ の出力をそれぞれ、有効表示エリア100内の位置等に応じて制御している。

#### 【0042】

10

20

30

40

50

レベルシフタ 4 0 D 4 は、ゲート / COM セレクト部 4 0 D 3 から供給されるコモン駆動信号 V com およびゲート信号 V G の電位をそれぞれ、制御するのに十分な電位レベルまでシフトさせるための回路である。

#### 【 0 0 4 3 】

ゲート / COM バッファ 4 0 D 5 は、コモン駆動信号 V com ( V com(1) ~ V com(n) ) およびゲート信号 V G ( V G(1) ~ V G(n) ) をそれぞれ順次供給するための最終出力ロジック回路であり、出力バッファ回路もしくはスイッチ回路等を含んで構成されている。

#### 【 0 0 4 4 】

なお、図 7 に示した例では、表示装置 1 内においてこれらの他に、T / G · DC / DC コンバータ 2 0 D が設けられている。この T / G · DC / DC コンバータ 2 0 D は、T / G (タイミング・ジェネレータ) および DC / DC コンバータとしての役割を果たすものである。

10

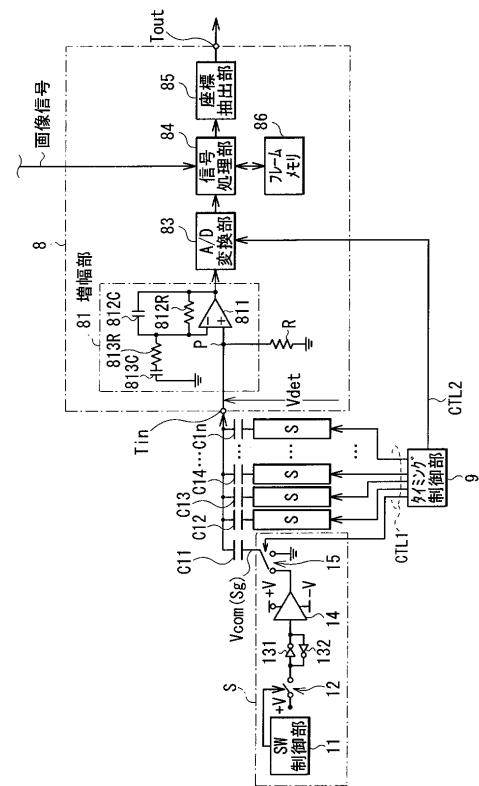

#### 【 0 0 4 5 】

( 駆動信号源 S および検出回路 8 の回路構成例 )

図 8 は、図 1 に示した駆動信号源 S とタッチ検出動作を行う検出回路 8 との回路構成例を、タイミング・ジェネレータとしてのタイミング制御部 9 とともに表したものである。この図において、容量素子 C 1 1 ~ C 1 n は、図 5 に示した各共通電極 4 3 1 ~ 4 3 n とセンサ用検出電極 4 4 との間に形成される（静電）容量素子に対応するものである。

#### 【 0 0 4 6 】

駆動信号源 S は、各容量素子 C 1 1 ~ C 1 n ごとに 1 つずつ設けられている。この駆動信号源 S は、SW 制御部 1 1 と、2 つのスイッチ素子 1 2 , 1 5 と、2 つのインバータ（論理否定）回路 1 3 1 , 1 3 2 と、オペアンプ 1 4 を有している。SW 制御部 1 1 は、スイッチ素子 1 2 のオン・オフ状態を制御するものであり、これにより電源 +V とインバータ回路 1 3 1 , 1 3 2 との間の接続状態が制御されるようになっている。インバータ回路 1 3 1 の入力端子は、スイッチ素子 1 2 の一端（電源 +V とは反対側の端子）およびインバータ回路 1 3 2 の出力端子に接続されている。インバータ回路 1 3 1 の出力端子は、インバータ回路 1 3 2 の入力端子およびオペアンプ 1 4 の入力端子に接続されている。これにより、これらのインバータ回路 1 3 1 , 1 3 2 が、所定のパルス信号を出力する発振回路として機能するようになっている。オペアンプ 1 4 は、2 つの電源 +V , -V に接続されている。スイッチ素子 1 5 は、タイミング制御部 9 から供給されるタイミング制御信号 CTL 1 に従ってオン・オフ状態が制御されるようになっている。具体的には、このスイッチ素子 1 5 によって、容量素子 C 1 1 ~ C 1 n の一端側（共通電極 4 3 1 ~ 4 3 n 側）が、オペアンプ 1 4 の出力端子側（コモン駆動信号 V com の供給源側）または接地に接続される。これにより、各駆動信号源 S から各容量素子 C 1 1 ~ C 1 n へ、コモン駆動信号 V com が供給されるようになっている。

20

30

#### 【 0 0 4 7 】

検出回路 8 （電圧検出器 DET ）は、増幅部 8 1 と、A / D ( アナログ / デジタル ) 変換部 8 3 と、信号処理部 8 4 と、フレームメモリ 8 6 と、座標抽出部 8 5 と、前述した抵抗器 R とを有している。なお、この検出回路 8 の入力端子 Tin は、各容量素子 C 1 1 ~ C 1 6 の他端側（センサ用検出電極 4 4 側）に共通して接続されている。

40

#### 【 0 0 4 8 】

増幅部 8 1 は、入力端子 Tin から入力される検出信号 V det を増幅する部分であり、信号増幅用のオペアンプ 8 1 1 と、2 つの抵抗器 8 1 2 R , 8 1 3 R と、2 つのキャパシタ 8 1 2 C , 8 1 3 C を有している。オペアンプ 8 1 1 の正入力端 ( + ) は、入力端子 Tin に接続され、出力端は後述する A / D 変換部 8 3 の入力端に接続されている。抵抗器 8 1 2 R およびキャパシタ 8 1 2 C の一端は、ともにオペアンプ 8 1 1 の出力端に接続され、抵抗器 8 1 2 R およびキャパシタ 8 1 2 C の他端は、ともにオペアンプ 8 1 1 の負入力端 ( - ) に接続されている。また、抵抗器 8 1 3 R の一端は、抵抗器 8 1 2 R およびキャパシタ 8 1 2 C の他端に接続され、抵抗器 8 1 3 R の他端は、キャパシタ 8 1 3 R を介して接地に接続されている。これにより、抵抗器 8 1 2 R およびキャパシタ 8 1 2 C が、高

50

域をカットし低域を通過させるローパスフィルタ（L P F）として機能すると共に、抵抗器 8 1 3 R およびキャパシタ 8 1 3 C が、高域を通過させるハイパスフィルタ（H P F）として機能する。

#### 【 0 0 4 9 】

抵抗器 R は、オペアンプ 8 1 1 の正入力端（+）側の接続点 P と、接地との間に配置されている。この抵抗器 R は、センサ用検出電極 4 4 がフローティング状態になってしまうのを回避して安定状態を保つためのものである。これにより、検出回路 8 において、検出信号 V<sub>det</sub> の信号値がふらついて変動してしまうのが回避されると共に、この抵抗器 R を介して静電気を接地に逃がすことができるという利点もある。

#### 【 0 0 5 0 】

A / D 変換部 8 3 は、増幅部 8 1 において増幅されたアナログの検出信号 V<sub>det</sub> を、デジタルの検出信号に変換する部分であり、図示しないコンパレータを含んで構成されている。このコンパレータは、入力された検出信号と所定のしきい値電圧 V<sub>th</sub>（図 3 参照）との電位を比較するものである。なお、この A / D 変換部 8 3 における A / D 変換の際のサンプリングタイミングは、タイミング制御部 9 から供給されるタイミング制御信号 C T L 2 によって制御されるようになっている。

#### 【 0 0 5 1 】

信号処理部 8 4 は、A / D 変換部 8 3 から出力されるデジタルの検出信号に対し、所定の信号処理（例えば、デジタル的なノイズ除去処理や、周波数情報を位置情報に変換する処理などの信号処理）を施すものである。この信号処理部 8 4 はまた、詳細は後述するが、後述する補正テーブル等を保持するフレームメモリ 8 6 とともに、画像信号の書き込み動作に起因したノイズ（内部ノイズ）の影響を除去（抑制）するための所定の演算処理を行うようになっている。

#### 【 0 0 5 2 】

座標抽出部 8 5 は、信号処理部 8 4 から出力される検出信号（上記した内部ノイズ除去後の検出信号）に基づいて、検出結果（タッチされたか否か、およびタッチされた場合にはその部分の位置座標）を求め、出力端子 T<sub>out</sub> から出力するものである。

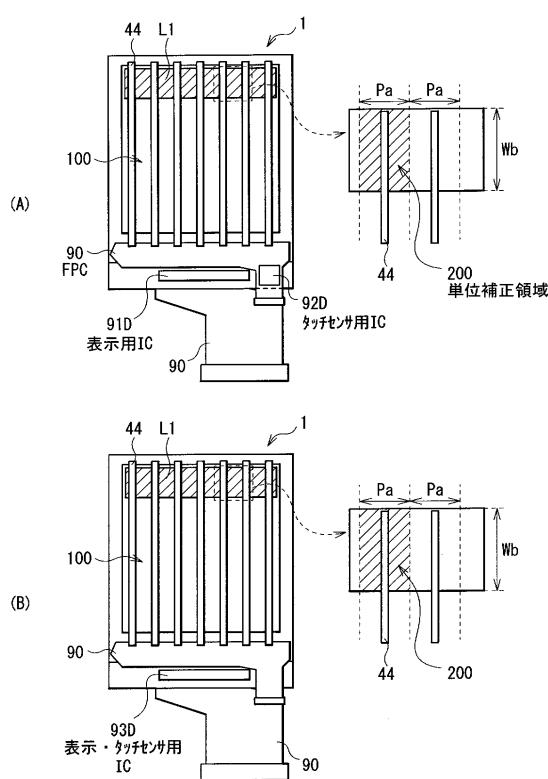

#### 【 0 0 5 3 】

なお、このような検出回路 8 は、外付け I C（Integrated Circuit）として F P C（Flexible Printed Circuit）上に実装したり、基板上に実装するようにしてもよい。更に、対向基板 4 上の周辺領域（非表示領域または額縁領域）に形成するようにしてもよいし、あるいは、画素基板 2 上の周辺領域に形成するようにしてもよい。但し、画素基板 2 上に形成すれば、元々画素基板 2 上に形成されている表示制御用の各種回路素子等との集積化が図れるので、回路の集積化による簡略化という観点でより好ましい。この場合には、コントラクト導電柱 7 と同様のコントラクト導電柱（図示せず）によって、センサ用検出電極 4 4 の各電極パターンと画素基板 2 の検出回路 8 との間を接続し、検出信号 V<sub>det</sub> をセンサ用検出電極 4 4 から検出回路 8 に伝送するようすればよい。

#### 【 0 0 5 4 】

##### [ 表示装置 1 の作用・効果 ]

次に、本実施の形態の表示装置 1 における作用および効果について説明する。

#### 【 0 0 5 5 】

##### ( 1 . 基本動作 )

この表示装置 1 では、画素基板 2 の表示ドライバ（共通電極ドライバ 4 3 D 等）が、共通電極 4 3 の各電極パターン（共通電極 4 3 1 ~ 4 3 n）に対してコモン駆動信号 V<sub>com</sub> を線順次で供給する。この表示ドライバはまた、ソース線 2 5 を介して画素電極 2 2 へ画素信号（画像信号）を供給すると共に、これに同期して、ゲート線 1 2 6 を介して各画素電極の T F T（T F T 素子 T r）のスイッチングを線順次で制御する。これにより、液晶層 6 には、表示画素 2 0 ごとに、コモン駆動信号 V<sub>com</sub> と各画像信号とにより定まる縦方向（基板に垂直な方向）の電界が印加され、液晶状態の変調が行われる。このようにして、いわゆる反転駆動による表示が行われる。

10

20

30

40

50

## 【0056】

一方、対向基板4の側では、共通電極43の各電極パターンと、センサ用検出電極44の各電極パターンとの交差部分にそれぞれ、容量素子C1（容量素子C11～C1n）が形成される。ここで、例えば図5中の矢印（スキャン方向）に示したように、共通電極43の各電極パターンに、コモン駆動信号Vcomを時分割的に順次印加していくと、以下のようになる。すなわち、印加された共通電極43の電極パターンとセンサ用検出電極44の各電極パターンとの交差部分に形成されている一列分の容量素子C11～C1nの各々に対し、充放電が行われる。その結果、容量素子C1の容量値に応じた大きさの検出信号Vdetが、センサ用検出電極44の各電極パターンからそれぞれ出力される。対向基板4の表面にユーザの指が触れられていない状態においては、この検出信号Vdetの大きさはほぼ一定となる。コモン駆動信号Vcomのスキャンに伴い、充放電の対象となる容量素子C1の列が線順次的に移動していく。

## 【0057】

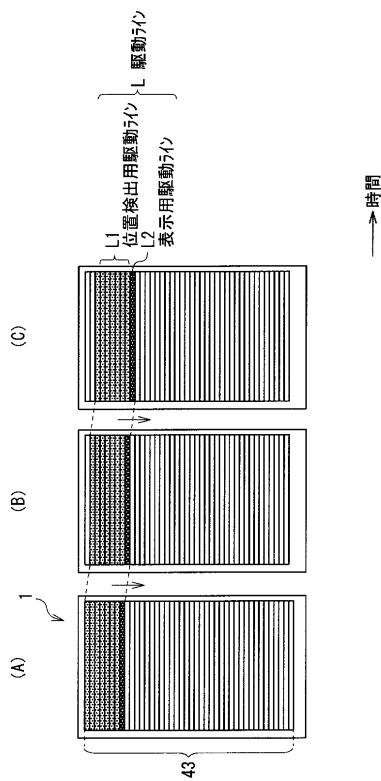

なお、このような共通電極43の各電極パターンの線順次駆動の際には、例えば図9(A)～(C)に示したように、共通電極43の各電極パターンのうちの一部の電極パターンを束ねて、線順次駆動動作を行うようにするのが好ましい。具体的には、この一部の電極パターンからなる駆動ラインLを、複数ラインの電極パターンからなる位置検出用駆動ラインL1と、少数ライン（ここでは1ライン）の電極パターンからなる表示用駆動ラインL2とから構成するようにする。これにより、共通電極43の電極パターンの形状に対応した筋や斑等が生ずることによる画質劣化を抑えることが可能となる。

## 【0058】

ここで、対向基板4の表面のいずれかの場所にユーザの指が触れると、そのタッチ箇所に元々形成されている容量素子C1に、指による容量素子C2が付加される。その結果、そのタッチ箇所がスキャンされた時点（すなわち、共通電極43の電極パターンのうち、そのタッチ箇所に対応する電極パターンにコモン駆動信号Vcomが印加されたとき）の検出信号Vdetの値が、他の箇所よりも小さくなる。検出回路8（図8）は、この検出信号Vdetをしきい値電圧Vthと比較して、しきい値電圧Vth未満の場合に、その箇所をタッチ箇所として判定する。このタッチ箇所は、コモン駆動信号Vcomの印加タイミングと、しきい値電圧Vth未満の検出信号Vdetの検出タイミングとから割り出すことができる。

## 【0059】

このようにして、本実施の形態のタッチセンサ付きの表示装置1では、液晶表示素子に元々備えられている共通電極43が、駆動電極と検出電極とからなる一対のタッチセンサ用電極のうちの一方として兼用されている。また、表示用駆動信号としてのコモン駆動信号Vcomが、タッチセンサ用駆動信号として共用されている。これにより、静電容量型のタッチセンサにおいて、新たに設ける電極はセンサ用検出電極44だけでよく、また、タッチセンサ用駆動信号を新たに用意する必要がない。したがって、構成が簡単である。

## 【0060】

また、従来のタッチセンサ付き表示装置（特許文献1）では、センサに流れる電流の大きさを正確に測定し、その測定値に基づいてタッチ位置をアナログ演算により求めるようしている。これに対し、本実施の形態の表示装置1では、タッチの有無に応じた電流の相対変化（電位変化）の有無をデジタル的に検知するだけでよいので、簡単な検出回路構成で検出精度を高めることができる。また、コモン駆動信号Vcomの印加用に元々設けられている共通電極43と、新たに設けたセンサ用検出電極44との間に静電容量を形成し、この静電容量が利用者の指の接触によって変化することを利用してタッチ検出を行うようしている。このため、利用者の電位が不定であることが多いモバイル機器用途にも適合可能である。

## 【0061】

更に、センサ用検出電極44が複数の電極パターンに分割されると共に、各電極パターンが個別に時分割的に駆動されるため、タッチ位置の検出も可能となる。

## 【0062】

10

20

30

40

50

(2. 特徴的部分の作用；ノイズ除去処理を用いた検出動作)

次に、図10～図18を参照して、本発明の特徴的部分の1つであるノイズ除去処理を用いた検出動作について、詳細に説明する。

**【0063】**

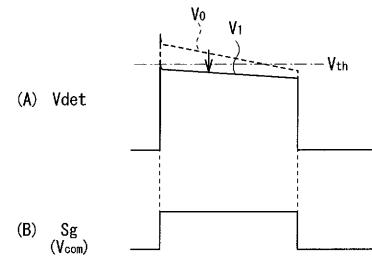

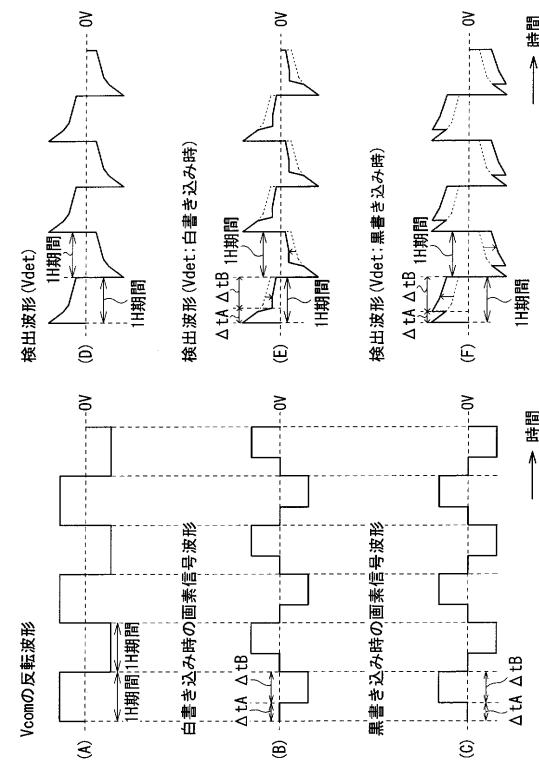

まず、図10(A)に示したように、コモン駆動信号Vcomが、図10(B),(C)に示したような画像表示制御の際の駆動周期(1H期間)と同期して極性反転を行う場合、検出信号Vdetの検出波形は、例えば図10(D)～(F)に示したようになる。すなわち、この極性反転と同期して極性反転を行うと共に、前述した抵抗器Rに流れるリーク電流に起因して、極性反転後に徐々に信号値が減衰していく。

**【0064】**

このとき、例えば図10(B),(C)に示したような白書き込み時や黒書き込み時等の画素信号(画像信号)の書き込み時には、検出信号Vdetの検出波形は、例えば図10(E),(F)に示したように、この書き込みに起因したノイズが含まれるようになる。具体的には、1H期間は、画像信号が印加されていない非書き込み期間tAと、画像信号が印加されている書き込み期間tBとから構成されているが、このうちの書き込み期間tBにおいて、画像信号の階調レベルに応じた検出波形の変動が生じている。すなわち、その時点での(極性反転後の)画像信号の階調レベルに応じて、図10(E),(F)中の矢印で示したような、極性反転後の画像信号に起因したノイズ(内部ノイズ)が、検出信号Vdetの検出波形に含まれている。具体的には、黒書き込み時にはコモン駆動信号Vcomと同相に、白書き込み時にはコモン駆動信号Vcomと逆相に反転後ノイズが含まれることになる。このようにして、書き込み期間tBでは、検出信号Vdetの検出波形が、内部ノイズによって画像信号の階調レベルに応じて変動してしまうため、物体の接触の有無等による検出波形の変化(図3)と切り分けるのが困難となってしまう。

**【0065】**

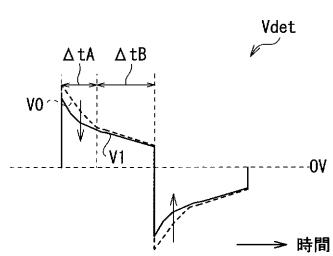

なお、例えば図11に示したように、コモン駆動信号Vcomの反転直後に対応する非書き込み期間tAでは、書き込み期間tBと比べ、物体の接触による電圧変化量が非常に大きくなっている。したがって、物体の接触の有無等の検出感度が高いという観点からは、極性反転後における検出動作は、その極性反転後の画像信号の書き込み動作の開始前のタイミング(非書き込み期間tA)で行うのが好ましいと言える。

**【0066】**

そこで、本実施の形態では、検出回路8内の信号処理部84、フレームメモリ86および座標抽出部85において、例えば図12～図17に示したようにして、上記したような内部ノイズを取り除いた物体検出を行っている。具体的には、信号処理部84およびフレームメモリ86では、検出信号Vdetの取得時における画像信号の階調に応じて、その検出信号Vdetを補正する。より具体的には、画像信号の階調とその画像信号の書き込み動作に起因したノイズ(内部ノイズ)を含む検出信号の信号値とを対応付けてなるノイズデータ(後述する図14参照)と、画像信号とを用いて、検出信号Vdetを補正している。そして、座標抽出部85では、そのような内部ノイズ除去(低減)後の検出信号を用いて検出動作を行う。これにより、以下説明するように、画像表示制御の際の画像信号の書き込み動作に起因して検出信号Vdetに含まれるノイズ(内部ノイズ)の影響を除去(低減)しつつ、検出動作を行うことができるようになっている。なお、このような内部ノイズの除去方法としては、例えば以下説明する2つの手法(手法1,2)が挙げられる。

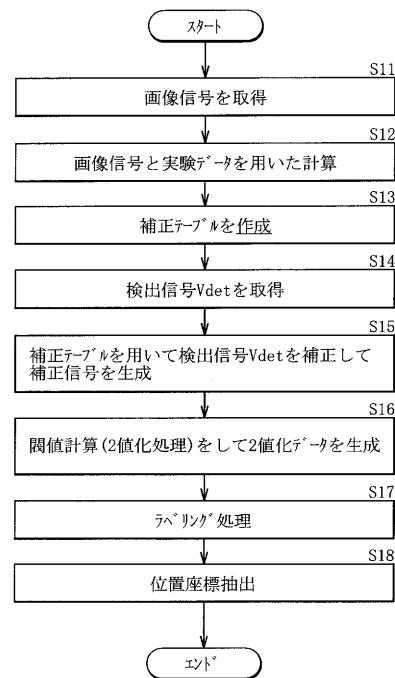

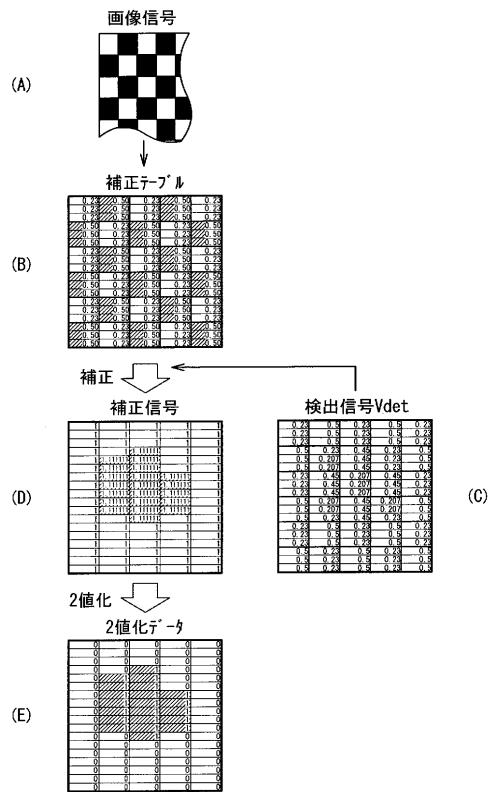

**【0067】**

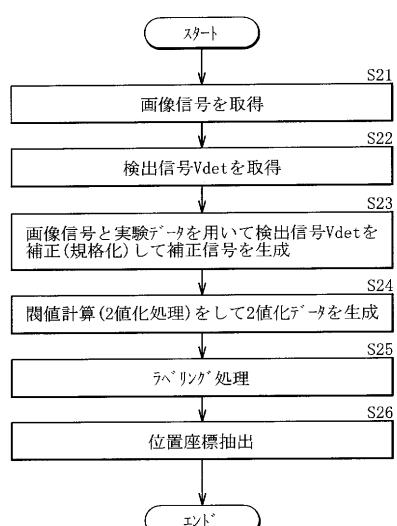

**(2-1. 手法1)**

図12は、内部ノイズの除去方法の一例(手法1)を流れ図で表したものである。この手法1では、フレームメモリ86内に後述する所定の補正テーブルが格納されており、この補正テーブルを用いて検出信号Vdetの補正を行っている。

**【0068】**

まず、信号処理部84およびフレームメモリ86は、例えば図13(A)に示したような、検出信号Vdetの取得時における画像信号を取得する(ステップS11)。なお、こ

10

20

30

40

50

こでは、図13(A)に示したような黑白の千鳥状の画像信号パターンを例にして以下説明する。

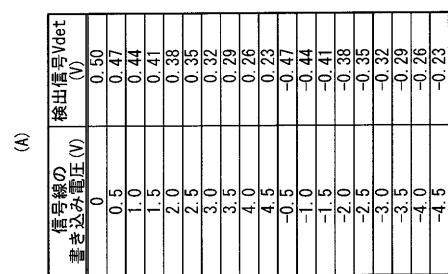

#### 【0069】

次に、信号処理部84は、ステップS11において取得した画像信号と、前述したノイズデータに対応する実験データとを用いて、所定の計算を行う(ステップS12)。この実験データは、所定の実験を行うことにより予め得られたものであり、例えば図14(A), (B)に示したようなデータである。すなわち、信号線25の書き込み電圧(画像信号の階調)と、画像表示制御の際のその階調の画像信号の書き込み動作に起因した内部ノイズを含む検出信号Vdetの信号値とを対応付けてなるノイズデータとなっている。このようにして、実験データからなるノイズデータを用いているのは、タッチセンサ内には種々の容量成分が存在することから、内部ノイズ量を定量化するには実験から見積もる必要があるためである。ここで、図14に示した実験データのように、コモン駆動信号Vcomの振幅と逆位相に振幅する場合には、内部ノイズを含む検出信号Vdetでは、振幅が小さくなる方向に変化する一方、同位相に振幅する場合の画像が多いときには、振幅が大きくなる方向に変化する。すなわち、この図14に示した実験データでは、信号線25の書き込み電圧と、内部ノイズを含む検出信号Vdetの信号値とが、簡単な1次式の関係となっている。これにより、取得した画像信号の階調に基づいて、容易に内部ノイズを含む検出信号Vdetの信号値を得ることができるのが分かる。

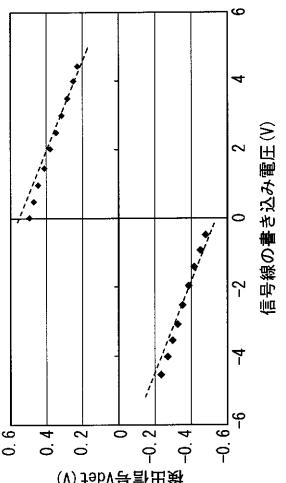

#### 【0070】

次に、信号処理部84およびフレームメモリ86は、ステップS12において取得した、実験データにおける内部ノイズを含む検出信号Vdetの信号値を用いて、画像信号の階調に応じて前述した補正テーブル内の検出信号の信号値を、随時作成(更新)(ステップS13)。具体的には、例えば図13(B)に示したようにして、複数の表示画素20を含む所定の画素領域ごとに、実験データにおける内部ノイズを含む検出信号Vdetの信号値を格納してなる補正テーブルを更新する。ここで、この所定の画素領域とは、例えば図15(A), (B)中に示した単位補正領域200に対応している。この単位補正領域200では、センサ用検出電極44の各電極パターンを、水平ライン方向の長さ(センサピッチPa)の中心位置に含んでいる。また、共通電極43の各電極パターンの幅(駆動ライン幅(位置検出用駆動ラインL1の幅)Wb)が、単位補正領域200における垂直ライン方向の長さに設定されている。すなわち、各単位補正領域200では、水平ライン方向の長さがセンサピッチPaとなっていると共に、垂直ライン方向の長さが駆動ライン幅Wbとなっている。そして、補正テーブル内の各単位補正領域200では、その領域内に位置する全ての表示画素20における画像信号の平均階調を基に、内部ノイズを含む検出信号Vdetの信号値を格納している。なお、図15(A)に示した例では、表示用IC91Dとタッチセンサ用IC92Dとが別個に設けられており、FPC90によって互いに配線接続されている。一方、図15(B)に示した例では、表示用ICとタッチセンサ用ICとが1チップ化されてなる表示・タッチセンサ用IC93Dが設けられている。なお、前述した検出信号Vdetの取得時における画像信号は、表示用ICからタッチセンサ用ICへ、FPC90を介して供給される(図15(A))か、もしくはIC内の配線により直接供給される(図15(B))ようになっている。

#### 【0071】

次に、信号処理部84およびフレームメモリ86は、例えば図13(C)に示したような、センサ用検出電極44により検出された検出信号Vdetを取得する(ステップS14)。

#### 【0072】

次に、信号処理部84およびフレームメモリ86は、ステップS13において作成(更新)された補正テーブルを用いて、ステップS14において取得した検出信号Vdetを補正することにより、補正信号を生成する(ステップS15)。具体的には、例えば図13(D)に示したように、前述した単位補正領域200ごとに、補正テーブル内の内部ノイズを含む検出信号Vdetの信号値と、取得した検出信号Vdetの信号値との間で、減算もし

10

20

30

40

50

くは除算（ここでは、除算）を行う。これにより、取得した検出信号  $V_{det}$  が補正され、補正信号が生成される。このとき、信号処理部 8 4 およびフレームメモリ 8 6 は、水平ライン方向に含まれる全単位補正領域 2 0 0 での補正結果を加味して、その水平ライン内の各単位補正領域 2 0 0 において、取得した検出信号  $V_{det}$  の補正を行うようになるのが好ましい。このように構成した場合、後述するように（図 18）、検出信号  $V_{det}$  に含まれる内部ノイズの影響をより低減することができ、検出精度をより向上させることができるからである。

#### 【 0 0 7 3 】

次に、信号処理部 8 4 およびフレームメモリ 8 6 は、ステップ S 1 5 において作成された補正信号に対して閾値計算（2 値化処理）を行うことにより、例えば図 13（E）に示したような 2 値化データを生成する（ステップ S 1 6）。 10

#### 【 0 0 7 4 】

そして、座標抽出部 8 5 では、そのような内部ノイズ除去（低減）後の検出信号（2 値化データ）に対してラベリング処理を行う（ステップ S 1 7）と共に、位置座標抽出を行うことにより、検出動作を行う（ステップ S 1 8）。以上により、図 12 に示した手法 1 による検出動作が終了となる。

#### 【 0 0 7 5 】

このようにして手法 1 では、フレームメモリ 8 6 内に所定の補正テーブルを格納すると共に、この補正テーブルを用いて検出信号  $V_{det}$  の補正を行っている。これにより、画像表示制御の際の画像信号の書き込み動作に起因して検出信号  $V_{det}$  に含まれるノイズ（内部ノイズ）の影響を除去（低減）しつつ、検出動作を行うことができる。 20

#### 【 0 0 7 6 】

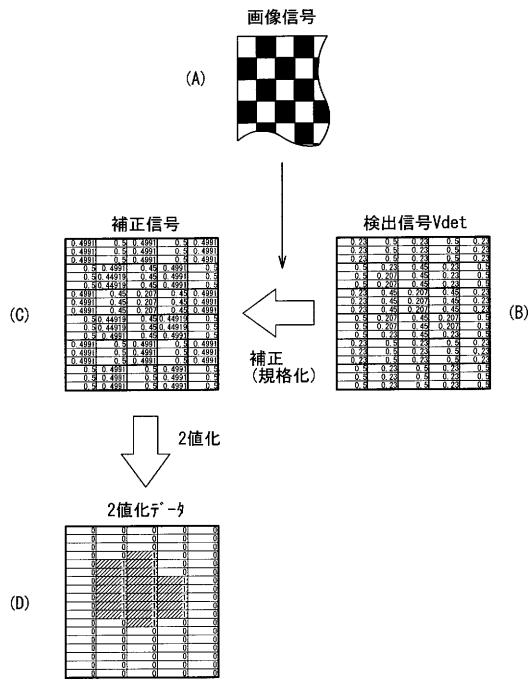

##### （2 - 2 . 手法 2 ）

図 16 は、内部ノイズの除去方法の他の例（手法 2）を流れ図で表したものである。この手法 2 では、上記手法 1 とは異なり、前述した補正テーブルを用いずに検出信号  $V_{det}$  の補正を行っている。すなわち、検出時の画像信号と検出信号  $V_{det}$  との間で以下説明する所定の演算を行うことにより、補正テーブルを用いずに直接的に検出信号  $V_{det}$  の補正を行っている。

#### 【 0 0 7 7 】

まず、信号処理部 8 4 は、手法 1 におけるステップ S 1 1 と同様に、例えば図 17（A）に示したような、検出信号  $V_{det}$  の取得時における画像信号を取得する（ステップ S 2 1）。なお、ここでも、図 17（A）に示したような黑白の千鳥状の画像信号パターンを例にして以下説明する。 30

#### 【 0 0 7 8 】

次に、信号処理部 8 4 は、手法 1 におけるステップ S 1 4 同様に、例えば図 17（B）に示したような、センサ用検出電極 4 4 により検出された検出信号  $V_{det}$  を取得する（ステップ S 2 2）。

#### 【 0 0 7 9 】

次に、信号処理部 8 4 は、ステップ S 2 1 において取得した画像信号と、例えば図 14 に示したような実験データにおける内部ノイズを含む検出信号  $V_{det}$  の信号値を用いて、ステップ S 2 2 において取得した検出信号  $V_{det}$  を補正する（ステップ S 2 3）。具体的には、例えば図 17（C）に示したように、前述した単位補正領域 2 0 0 ごとに、画像信号の階調に応じた内部ノイズを含む検出信号  $V_{det}$  の信号値を用いて、取得した検出信号  $V_{det}$  の信号値を規格化することにより、その検出信号  $V_{det}$  の補正を行う。これにより、検出信号  $V_{det}$  の補正信号が生成される。このとき、手法 1 と同様に、信号処理部 8 4 は、水平ライン方向に含まれる全単位補正領域 2 0 0 での補正結果を加味して、その水平ライン内の各単位補正領域 2 0 0 において、取得した検出信号  $V_{det}$  の補正を行うようになるのが好ましい。 40

#### 【 0 0 8 0 】

次に、信号処理部 8 4 は、ステップ S 2 4 において作成された補正信号に対して閾値計 50

算（2値化処理）を行うことにより、例えば図17(D)に示したような2値化データを生成する（ステップS24）。

#### 【0081】

そして、座標抽出部85では、そのような内部ノイズ除去（低減）後の検出信号（2値化データ）に対してラベリング処理を行う（ステップS25）と共に、位置座標抽出を行うことにより、検出動作を行う（ステップS26）。以上により、図16に示した手法2による検出動作が終了となる。

#### 【0082】

このようにして手法2では、検出時の画像信号と検出信号V<sub>det</sub>との間で所定の演算を行うことにより、補正テーブルを用いずに直接的に検出信号V<sub>det</sub>の補正を行っている。これにより、手法1における効果に加え、補正テーブルを持つ必要がなくなるという効果が得られる。

#### 【0083】

以上のように本実施の形態では、静電容量の変化に応じてタッチ検出電極から得られる検出信号V<sub>det</sub>に基づいて物体の接触位置を検出すると共に、検出回路8において、検出信号V<sub>det</sub>の取得時における画像信号の階調に応じてその検出信号V<sub>det</sub>を補正して検出動作を行うようにしたので、従来のようなシールド層を用いることなく、上記内部ノイズの影響を低減（除去）しつつ検出動作を行うことができる。よって、静電容量型のタッチセンサを備えた表示装置において、シールド層を用いずに物体の検出精度を向上させることが可能となる。

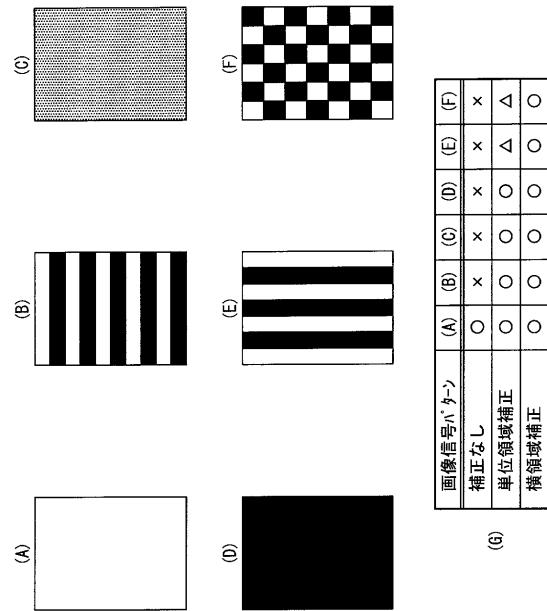

#### 【0084】

なお、図18は、本実施の形態に係る内部ノイズの除去方法を用いた場合における各種の画像信号パターン（図18(A)～(F)）に対する内部ノイズの除去効果（図18(G)）の一例を表したものである。図18(G)において、「単位領域補正」とは、単位補正領域200ごとに補正を行った場合を示している。また、「横領域補正」とは、前述したように、水平ライン方向に含まれる全単位補正領域200での補正結果を加味してその水平ライン内の各単位補正領域200の補正を行った場合を示している。また、検出信号V<sub>det</sub>に含まれる内部ノイズ量が大きくて位置検出ができない場合を「×」、若干の内部ノイズ量が含まれているものの位置検出ができる場合を「○」、内部ノイズについての問題がなく位置検出ができる場合を「■」で示している。この図18(G)の結果により、「補正なし」の場合では、(A)の画像信号パターンについては「×」であることを除き、他の画像信号パターンについては全て「×」となっていることが分かる。これに対し、「単位領域補正」を行った場合には、(E),(F)の画像信号パターンについては「○」であるものの、他の(A)～(D)の画像パターンについては全て「■」となっており、内部ノイズを低減して位置検出精度が向上していることが分かる。更に、「横領域補正」を行った場合には、(E),(F)の画像信号パターンについても「○」となっており、(A)～(F)の全ての画像信号パターンについて「○」となっていることが分かる。これにより、「横領域補正」を行った場合には、「単位領域補正」を行った場合と比べて内部ノイズをより低減することができ、位置検出精度が更に向上していることが分かる。

#### 【0085】

##### [第1の実施の形態の変形例]

なお、本実施の形態では、前述したノイズデータが、所定の実験を行うことにより予め得られた実験データである場合について説明したが、以下説明するような変形例も考え得る。本変形例では、ノイズデータが、後述するブランкиング期間において、表示制御回路（図示しないソースドライバ）によって所定の検出用パターン信号を供給することによりセンサ用検出電極44から得られる内部ノイズ検出信号を基に作成されたものとなっている。

#### 【0086】

具体的には、本変形例では、検出回路8内の信号処理部84、フレームメモリ86およ

10

20

30

40

50

び座標抽出部 85において、例えば図19～図21に示したようにして、画像信号の階調レベルに応じた内部ノイズ量の算出を行っている。より具体的には、信号処理部84およびフレームメモリ86では、有効表示期間T1同士の間に位置するプランキング期間(垂直(V)プランキング期間Tv bまたは水平(H)プランキング期間Th b)において、センサ用検出電極44から内部ノイズ検出信号を取得する。この内部ノイズ検出信号は、以下説明するように、これらのプランキング期間において、図示しないソースドライバによって所定の検出用パターン信号(後述する所定階調の画像信号)を供給することにより、センサ用検出電極44から得られるようになっている。

#### 【0087】

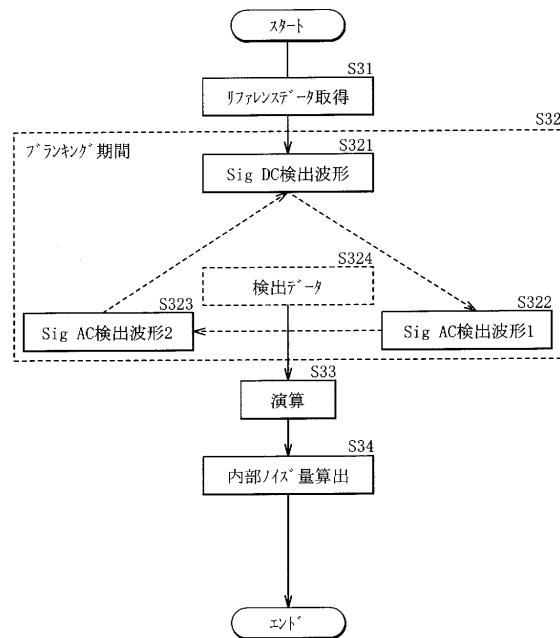

図19は、本変形例に係る内部ノイズ量の算出方法の一例を流れ図で表したものである。

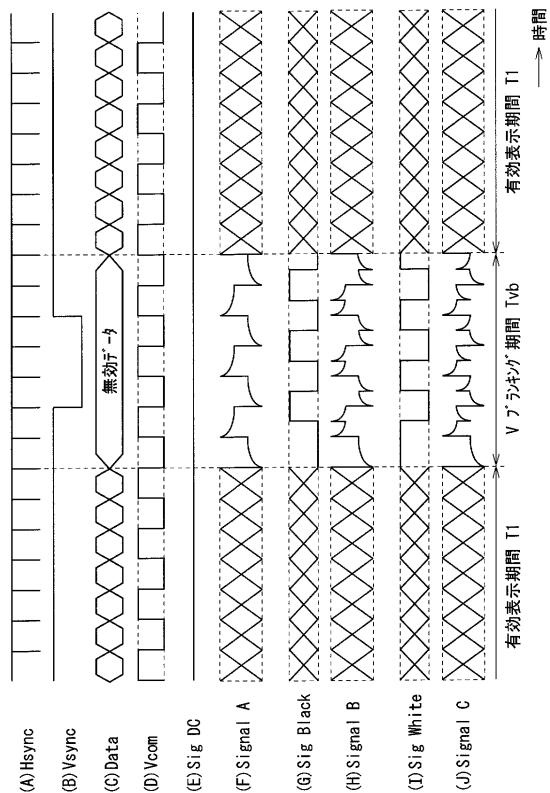

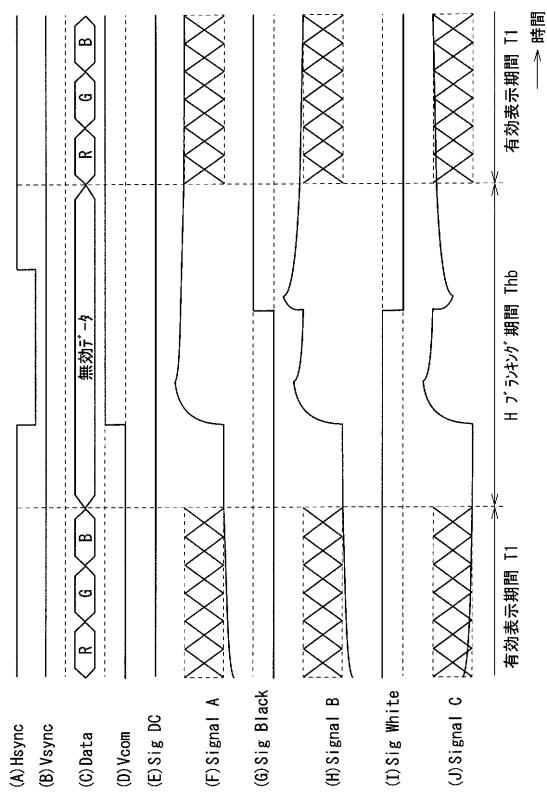

また、図20および図21は、以下説明する垂直(V)プランキング期間または水平(H)プランキング期間における内部ノイズ量の算出手法の一例をタイミング波形図で表したものである。これらの図において、(A)は水平同期信号H syncを、(B)は垂直同期信号V syncを、(C)は画像信号Dataを、(D)はコモン駆動信号V comを示している。また、(E)，(G)，(I)はそれぞれ、Vプランキング期間またはHプランキング期間に信号線(ソース線)25へ供給される検出用パターン信号(「Sig DC」：固定電位のDC信号、「Sig Black」：黒書き込み信号、「Sig White」：白書き込み信号)を示している。また、(F)，(H)，(J)はそれぞれ、Sig DC, Sig Black, Sig Whiteを供給したときに得られる検出信号Vdec(ノイズ検出信号)を示している。

#### 【0088】

まず、信号処理部84およびフレームメモリ86では、所定のリファレンスデータを取得する(図19のステップS31)。このリファレンスデータは、例えば、固定電位のDC信号「Sig DC」を用いた場合において、接触または隣接する非検出物が存在しなく、かつ外部環境に起因した外部ノイズが存在しない条件で得られる検出信号Vdetのデータである。

#### 【0089】

次に、信号処理部84およびフレームメモリ86では、プランキング期間(Vプランキング期間Tv bまたはHプランキング期間Th b)において、センサ用検出電極44から内部ノイズ検出信号を取得する(ステップS32)。具体的には、ここでは、複数回のプランキング期間において、互いに異なる複数の検出用パターン信号(固定電位信号および複数階調の画像信号)から、それに対応する内部ノイズ検出信号を取得している(ステップS321～S324)。

#### 【0090】

より具体的には、まず、プランキング期間において、ソース線25に対して固定電位のDC信号「Sig DC」を供給した場合、内部ノイズの主原因である信号線電位変動がないことから内部ノイズの影響を排除することができる。したがって、内部ノイズの影響のない検出波形(「Signal A」)を、センサ用検出電極44から取得することができる(ステップS321, S324、図20(E), (F)および図21(E), (F))。

#### 【0091】

一方、プランキング期間において、ソース線25に対して黒書き込み信号(黒階調の画像信号)「Sig Black」を供給した場合、ソース線25に影響のない検出信号Vdetの波形に加え、この黒階調の画像信号を表示した場合に対応する内部ノイズ量を取得することができる。すなわち、そのような階調に対応する内部ノイズ検出信号の検出波形(「Signal B」)を、センサ用検出電極44から取得することができる(ステップS322, S324、図20(G), (H)および図21(G), (H))。

#### 【0092】

同様に、プランキング期間において、ソース線25に対して白書き込み信号(白階調の画像信号)「Sig White」を供給した場合、ソース線25に影響のない検出信号Vdetの波形に加え、この白階調の画像信号を表示した場合に対応する内部ノイズ量を取得することができる。すなわち、そのような階調に対応する内部ノイズ検出信号の検出波形(「Sign

10

20

30

40

50

al C」)を、センサ用検出電極44から取得することができる(ステップS323,S324、図20(I),(J)および図21(I),(J))。

#### 【0093】

このようにして、ステップS32において、内部ノイズの影響がない波形(「Signal A」)、黒階調表示の際の内部ノイズ波形(「Signal B」)および白階調表示の際の内部ノイズ波形(「Signal C」)をそれぞれ切り分けることがき、以下の演算処理に利用できる。

#### 【0094】

次に、信号処理部84およびフレームメモリ86では、ステップS32において取得した検出波形(ここでは、「Signal A」~「Signal C」)に基づいて所定の演算(差分演算等)を行うことにより(ステップS33)、内部ノイズ量を算出する(ステップS34)。以上により、図19に示した内部ノイズ量の算出処理が終了となる。

#### 【0095】

このようにして本変形例では、ノイズデータが、ブランкиング期間において、表示制御回路によって所定の検出用パターン信号を供給することによりセンサ用検出電極44から得られる内部ノイズ検出信号を基に作成されたものであるようにしたので、上記第1の実施の形態と比べ、より適切な(タイムリーな)内部ノイズ量を取得することが可能となる。

#### 【0096】

<2. 第2の実施の形態>

20

次に、本発明の第2の実施の形態について説明する。本実施の形態は、上記第1の実施の形態の場合とは異なり、表示素子として横電界モードの液晶素子を用いるようにしたものである。

#### 【0097】

##### [表示装置1Bの構成例]

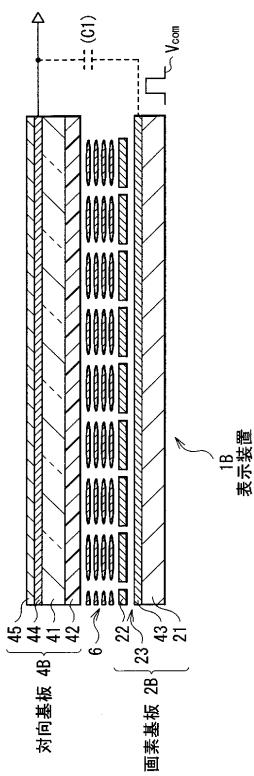

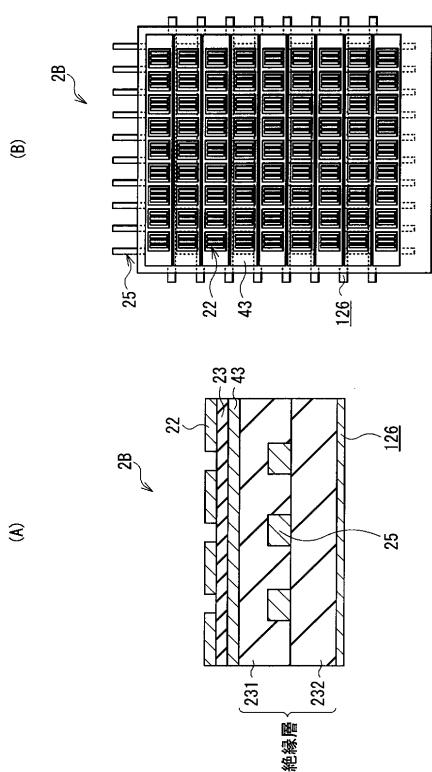

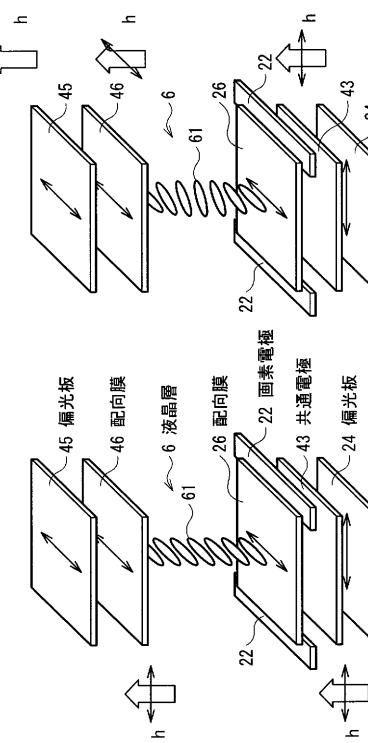

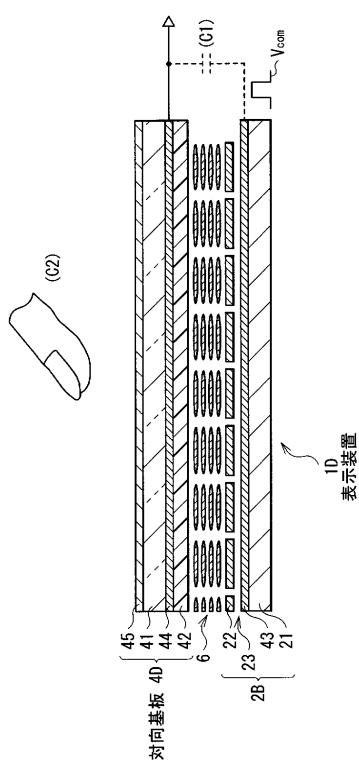

図22は、本実施の形態のタッチセンサ付きの表示装置1Bの要部断面構造を表すものである。図23は、この表示装置1Bにおける画素基板(後述する画素基板2B)の詳細構成を表すものであり、(A)は断面構成を、(B)は平面構成を示している。図24は、表示装置1Bの斜視構造を表すものである。なお、これらの図において、上記第1の実施の形態の図4等と同一部分には同一の符号を付し、適宜説明を省略する。

30

#### 【0098】

本実施の形態の表示装置1Bは、画素基板2Bと、この画素基板2Bに対向して配置された対向基板4Bと、画素基板2Bと対向基板4Bとの間に挿設された液晶層6とを備えている。

#### 【0099】

画素基板2Bは、TFT基板21と、このTFT基板21上に配設された共通電極43と、この共通電極43の上に絶縁層23を介してマトリクス状に配設された複数の画素電極22とを有する。TFT基板21には、各画素電極22を駆動するための図示しない表示ドライバやTFTのほか、絶縁層231, 232を介して、各画素電極に画像信号を供給する信号線(ソース線)25や、各TFTを駆動するゲート線<sub>1</sub>26等の配線が形成されている(図23)。TFT基板21にはまた、タッチ検出動作を行う検出回路8(図8)が形成されている。共通電極43は、タッチ検出動作を行うタッチセンサの一部を構成するセンサ用駆動電極としても兼用されるものであり、図1における駆動電極E1に相当する。

40

#### 【0100】

対向基板4Bは、ガラス基板41と、このガラス基板41の一方の面に形成されたカラーフィルタ42とを有する。ガラス基板41の他方の面には、センサ用検出電極44が形成され、さらに、このセンサ用検出電極44の上に偏光板45が配設されている。センサ用検出電極44は、タッチセンサの一部を構成するもので、図1における検出電極E2に相当する。センサ用検出電極44は、図5に示したように、複数の電極パターンに分割さ

50

れて構成される。センサ用検出電極 4 4 は、薄膜プロセスにより対向基板 4 B の上に直接形成してもよいが、間接的に形成してもよい。この場合には、タッチ検出電極 4 4 を図示しないフィルム基体上に形成すると共に、このタッチ検出電極 4 4 の形成されたフィルム基体を対向基板 4 B の表面に貼り付けるようにすればよい。この場合、ガラスと偏光板の間だけでなく偏光板の上面に貼り付けることも可能であり、さらには偏光板を構成するフィルム内に作成してもよい。

#### 【0101】

共通電極 4 3 は、TFT 基板 2 1 から交流矩形波形のコモン駆動信号  $V_{com}$  が印加されるようになっている。このコモン駆動信号  $V_{com}$  は、画素電極 2 2 に印加される画素電圧とともに各画素の表示電圧を画定するものであるが、タッチセンサの駆動信号としても兼用されるものであり、図 1 の駆動信号源 S から供給される交流矩形波  $S_g$  に相当する。

10

#### 【0102】

液晶層 6 は、電界の状態に応じてそこを通過する光を変調するものであり、例えば、FFS (フリンジフィールドスイッチング) モードや、IPS (インプレーンスイッチング) モード等の横電界モードの液晶が用いられる。

#### 【0103】

画素基板 2 B における共通電極 4 3 および対向基板 4 A におけるセンサ用検出電極 4 4 の構成は、例えば図 5 に示したものと同様であり、両方とも、互いに交差するように延在する複数の電極パターンとして形成されている。

20

#### 【0104】

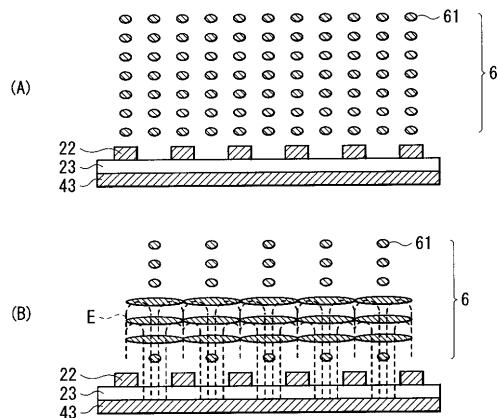

ここで、図 2 4 を参照して、より詳細に説明する。ここに示したような FFS モードの液晶素子においては、画素基板 2 B 上に形成された共通電極 4 3 の上に、絶縁層 2 3 を介して、櫛歯状にパターニングされた画素電極 2 2 が配置され、これを覆うように配向膜 2 6 が形成される。この配向膜 2 6 と、対向基板 4 B 側の配向膜 4 6との間に、液晶層 6 が挟持される。2 枚の偏光板 2 4 , 4 5 は、クロスニコルの状態で配置される。2 枚の配向膜 2 6 , 4 6 のラビング方向は、2 枚の偏光板 2 4 , 4 5 の一方の透過軸と一致している。ここでは、ラビング方向が出射側の偏光板 4 5 の透過軸と一致している場合を図示してある。さらに、2 枚の配向膜 2 6 , 4 6 のラビング方向および偏光板 4 5 の透過軸の方向は、液晶分子が回転する方向が規定される範囲で、画素電極 2 2 の延設方向 ( 櫛歯の長手方向 ) とほぼ平行に設定されている。

30

#### 【0105】

##### [表示装置 1 B の作用・効果]

次に、本実施の形態の表示装置 1 B における作用および効果について説明する。

#### 【0106】

最初に、図 2 4 および図 2 5 を参照して、FFS モードの液晶素子の表示動作原理について簡単に説明する。ここで、図 2 5 は液晶素子の要部断面を拡大して表したものである。これらの図で、(A) は電界非印加時、(B) は電界印加時における液晶素子の状態を示す。

#### 【0107】

共通電極 4 3 と画素電極 2 2 との間に電圧を印加していない状態では ( 図 2 4 ( A ) 、図 2 5 ( A ) ) 、液晶層 6 を構成する液晶分子 6 1 の軸が入射側の偏光板 2 4 の透過軸と直交し、かつ、出射側の偏光板 4 5 の透過軸と平行な状態となる。このため、入射側の偏光板 2 4 を透過した入射光  $h$  は、液晶層 6 内において位相差を生じることなく出射側の偏光板 4 5 に達し、ここで吸収されるため、黒表示となる。一方、共通電極 4 3 と画素電極 2 2 との間に電圧を印加した状態では ( 図 2 4 ( B ) 、図 2 5 ( B ) ) 、液晶分子 6 1 の配向方向が、画素電極間に生じる横電界  $E$  により、画素電極 2 2 の延設方向に対して斜め方向に回転する。この際、液晶層 6 の厚み方向の中央に位置する液晶分子 6 1 が約 45 度回転するように白表示時の電界強度を最適化する。これにより、入射側の偏光板 2 4 を透過した入射光  $h$  には、液晶層 6 内を透過する間に位相差が生じ、90 度回転した直線偏光となり、出射側の偏光板 4 5 を通過するため、白表示となる。

40

50

**【 0 1 0 8 】**

次に、表示装置 1 B における表示制御動作およびタッチ検出動作について説明する。これらの動作は、上記第 1 の実施の形態における動作と同様なので、適宜省略する。

**【 0 1 0 9 】**

画素基板 2 B の表示ドライバ（図示せず）は、共通電極 4 3 の各電極パターンに対してコモン駆動信号  $V_{com}$  を線順次で供給する。表示ドライバはまた、ソース線 2 5 を介して画素電極 2 2 へ画像信号を供給すると共に、これに同期して、ゲート線 1 2 6 を介して各画素電極の TFT のスイッチングを線順次で制御する。これにより、液晶層 6 には、画素ごとに、コモン駆動信号  $V_{com}$  と各画像信号とにより定まる横方向（基板に平行な方向）の電界が印加されて液晶状態の変調が行われる。このようにして、いわゆる反転駆動による表示が行われる。10

**【 0 1 1 0 】**

一方、対向基板 4 B の側では、共通電極 4 3 の各電極パターンに、コモン駆動信号  $V_{com}$  を時分割的に順次印加していく。すると、その印加された共通電極 4 3 の電極パターンとセンサ用検出電極 4 4 の各電極パターンとの交差部分に形成された一列分の容量素子  $C_1$  ( $C_{11} \sim C_{1n}$ ) の各々に対し、充放電が行われる。そして、容量素子  $C_1$  の容量値に応じた大きさの検出信号  $V_{det}$  が、センサ用検出電極 4 4 の各電極パターンからそれぞれ出力される。対向基板 4 A の表面にユーザの指が触れられていない状態においては、この検出信号  $V_{det}$  の大きさはほぼ一定となる。対向基板 4 B の表面のいずれかの場所にユーザの指が触れるとき、そのタッチ箇所に元々形成されている容量素子  $C_1$  に、指による容量素子  $C_2$  が付加される結果、そのタッチ箇所がスキャンされた時点の検出信号  $V_{det}$  の値が他の箇所よりも小さくなる。検出回路 8 (図 8) は、この検出信号  $V_{det}$  をしきい値電圧  $V_{th}$  と比較して、しきい値電圧  $V_{th}$  未満の場合に、その箇所をタッチ箇所として判定する。このタッチ箇所は、コモン駆動信号  $V_{com}$  の印加タイミングと、しきい値電圧  $V_{th}$  未満の検出信号  $V_{det}$  の検出タイミングとから割り出される。20

**【 0 1 1 1 】**

以上のように本実施の形態では、上記第 1 の実施の形態と同様に、液晶表示素子に元々備えられている共通電極 4 3 を、駆動電極と検出電極とからなる一対のタッチセンサ用電極のうちの一方として兼用すると共に、表示用駆動信号としてのコモン駆動信号  $V_{com}$  を、タッチセンサ用駆動信号として共用して静電容量型タッチセンサを構成したので、新たに設ける電極はセンサ用検出電極 4 4 だけでよく、また、タッチセンサ用駆動信号を新たに用意する必要がない。したがって、構成が簡単である。30

**【 0 1 1 2 】**

また、本実施の形態においても、上記第 1 の実施の形態で説明した検出回路 8 を設けるようにしたので、上記第 1 の実施の形態と同様の作用により同様の効果を得ることが可能となる。すなわち、静電容量型のタッチセンサを備えた表示装置において、シールド層を用いずに物体の検出精度を向上させることができるとなる。

**【 0 1 1 3 】**

特に、本実施の形態では、タッチセンサ用駆動電極としての共通電極 4 3 が画素基板 2 B の側 (TFT 基板 2 1 の上) に設けられた構造を有していることから、TFT 基板 2 1 から共通電極 4 3 にコモン駆動信号  $V_{com}$  を供給することが極めて容易であると共に、必要な回路や電極パターンおよび配線等を画素基板 2 に集中させることができ、回路の集積化が図られる。したがって、上記第 1 の実施の形態において必要であった、画素基板 2 側から対向基板 4 側へのコモン駆動信号  $V_{com}$  の供給経路 (コンタクト導電柱 7) が不要となり、構造がより簡単になる。40

**【 0 1 1 4 】**

また、上記のように、タッチセンサ用駆動電極としての共通電極 4 3 が画素基板 2 B の側に設けられると共に、この画素基板 2 B 上にソース線 2 5 やゲート線 1 2 6 も設けられているため、本実施の形態では特に前述した内部ノイズの影響を受けやすい構造となっている。このことから、本実施の形態の表示装置 1 B では、そのようは内部ノイズの影響を50

取り除いて検出動作を行う利点が特に大きいと言える。

**【0115】**

なお、検出回路8(図8)は、対向基板4B上の周辺領域(非表示領域または額縁領域)に形成するようにしてもよいが、画素基板2B上の周辺領域に形成するのが好ましい。画素基板2B上に形成すれば、元々画素基板2B上に形成されている表示制御用の各種回路素子等との集積化が図れるからである。

**【0116】**

[第2の実施の形態の変形例]

なお、本実施の形態では、センサ用検出電極44をガラス基板41の表面側(液晶層6と反対側)に設けるようにしたが、次のような変形が可能である。

10

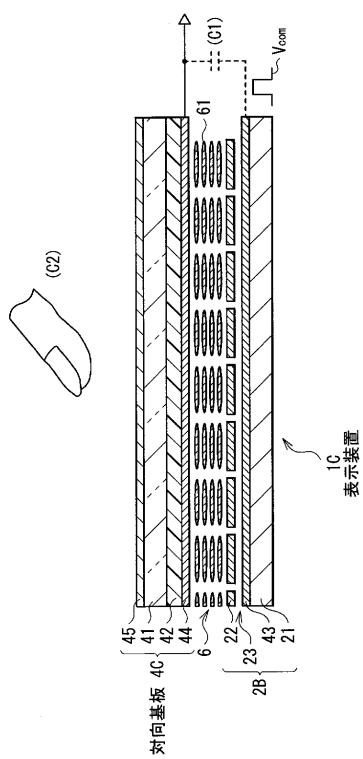

**【0117】**

例えば図26に示した表示装置1Cのように、対向基板4Cにおいて、センサ用検出電極44をカラーフィルタ42よりも液晶層6の側に設けるようにしてもよい。

**【0118】**

あるいは、図27に示した表示装置1Dのように、対向基板4Dにおいて、センサ用検出電極44をガラス基板41とカラーフィルタ42との間に設けるようにしてもよい。ここで、横電界モードの場合、縦方向に電極があると縦方向に電界がかかり、液晶が立ち上がりてしまい視野角等が大きく悪化してしまう。したがって、この表示装置1Dのように、カラーフィルタ42等の誘電体を挟んでセンサ用検出電極44を配置すれば、この問題は大きく低減することができる。

20

**【0119】**

<3. 適用例>

次に、図28～図32を参照して、上記実施の形態および変形例で説明したタッチセンサ付きの表示装置の適用例について説明する。上記実施の形態等の表示装置は、テレビジョン装置、デジタルカメラ、ノート型パーソナルコンピュータ、携帯電話等の携帯端末装置あるいはビデオカメラなどのあらゆる分野の電子機器に適用することが可能である。言い換えると、上記実施の形態等の表示装置は、外部から入力された映像信号あるいは内部で生成した映像信号を、画像あるいは映像として表示するあらゆる分野の電子機器に適用することが可能である。

30

**【0120】**

(適用例1)

図28は、上記実施の形態等の表示装置が適用されるテレビジョン装置の外観をしたものである。このテレビジョン装置は、例えば、フロントパネル511およびフィルターガラス512を含む映像表示画面部510を有しており、この映像表示画面部510は、上記実施の形態等に係る表示装置により構成されている。

**【0121】**

(適用例2)

図29は、上記実施の形態等の表示装置が適用されるデジタルカメラの外観をしたものである。このデジタルカメラは、例えば、フラッシュ用の発光部521、表示部522、メニュー/スイッチ523およびシャッター/ボタン524を有しており、その表示部522は、上記実施の形態等に係る表示装置により構成されている。

40

**【0122】**

(適用例3)

図30は、上記実施の形態等の表示装置が適用されるノート型パーソナルコンピュータの外観をしたものである。このノート型パーソナルコンピュータは、例えば、本体531、文字等の入力操作のためのキーボード532および画像を表示する表示部533を有しており、その表示部533は、上記実施の形態等に係る表示装置により構成されている。

**【0123】**

(適用例4)

50

図31は、上記実施の形態等の表示装置が適用されるビデオカメラの外観を表したものである。このビデオカメラは、例えば、本体部541、この本体部541の前方側面に設けられた被写体撮影用のレンズ542、撮影時のスタート/ストップスイッチ543および表示部544を有している。そして、その表示部544は、上記実施の形態等に係る表示装置により構成されている。

#### 【0124】

##### (適用例5)

図32は、上記実施の形態等の表示装置が適用される携帯電話機の外観を表したものである。この携帯電話機は、例えば、上側筐体710と下側筐体720とを連結部(ヒンジ部)730で連結したものであり、ディスプレイ740、サブディスプレイ750、ピクチャーライト760およびカメラ770を有している。そのディスプレイ740またはサブディスプレイ750は、上記実施の形態等に係る表示装置により構成されている。10

#### 【0125】

##### <4. その他の変形例>

以上、いくつかの実施の形態、変形例および適用例を挙げて本発明を説明したが、本発明はこれらの実施の形態等に限定されず、種々の変形が可能である。

#### 【0126】

例えば、上記第1の実施の形態の変形例において説明したノイズ低減手法では、内部ノイズ検出の際には、例えば検出信号V<sub>det</sub>における1点(1回のタイミング)のみで検出を行うようにしてもよい。その場合には、コモン駆動信号V<sub>com</sub>の極性反転直後において検出するようにするのが好ましい。20

#### 【0127】

また、上記第2の実施の形態では、横電界モードとしてFFSモードの液晶素子を例に説明したが、IPSモードの液晶について同様に適用可能である。

#### 【0128】

更に、上記実施の形態等では、表示素子として液晶表示素子を用いた表示装置について説明したが、それ以外の表示素子、例えば有機EL素子を用いた表示装置にも適用可能である。

#### 【0129】

加えて、上記実施の形態等では、タッチセンサを表示装置内に内蔵させた場合(タッチセンサ付きの表示装置)について説明したが、本発明のタッチセンサはこの場合には限られず、例えば表示装置の外側(外付け型のタッチセンサ)にも適用することが可能である。30

#### 【0130】

加えてまた、上記実施の形態等において説明した一連の処理は、ハードウェアにより行うこともできるし、ソフトウェアにより行うこともできる。一連の処理をソフトウェアによって行う場合には、そのソフトウェアを構成するプログラムが、汎用のコンピュータ等にインストールされるようになっている。このようなプログラムは、コンピュータに内蔵されている記録媒体に予め記録してさせておくようにしてもよい。

#### 【符号の説明】

#### 【0131】

1, 1B～1D…表示装置、100…有効表示エリア、11…SW制御部、12…スイッチ素子、131, 132…インバータ(論理否定)回路、14…オペアンプ、15…スイッチ素子、2, 2B…画素基板、20…表示画素、200…単位補正領域、20D…T/G・DC/DCコンバータ、21…TFT基板(回路基板)、22…画素電極、23, 231, 232…絶縁層、24…偏光板、25…信号線(ソース線)、26…ゲート線、4, 4B～4D…対向基板、40D…ゲート・共通電極ドライバ、41…ガラス基板、42…カラーフィルタ、43, 431～43n…共通電極(兼センサ用駆動電極)、43D…共通電極ドライバ、44…センサ用検出電極(タッチ検出電極)、45…偏光板、6…液晶層、7…コントラクト導電柱、8…検出回路、81…増幅部、83…A/D変換部、840

50

4 ... 信号処理部、85 ... 座標抽出部、86 ... フレームメモリ、9 ... タイミング制御部、90 ... FPC、91D ... 表示用IC、92D ... タッチセンサ用IC、93D ... 表示・タッチセンサ用IC、C1, C11~C1n, C2 ... 容量素子、Sg ... 交流矩形波、E1 ... 駆動電極、E2 ... 検出電極、S ... 交流信号源（駆動信号源）、Vcom, Vcom(1)~Vcom(n) ... コモン駆動信号、DET ... 電圧検出器（検出回路）、Vdet ... 検出信号、Vth ... しきい値電圧、Tr ... TFT素子、LC ... 液晶素子、Tin ... 入力端子、Tout ... 出力端子、R ... 抵抗器、CTL1, CTL2 ... タイミング制御信号、L ... 駆動ライン、L1 ... 位置検出用駆動ライン、L2 ... 表示用駆動ライン、tA ... 非書き込み期間、tB ... 書き込み期間、T1 ... 有効表示期間、Tv b ... V（垂直）プランキング期間、Th b ... H（水平）プランキング期間、Vsync ... V（垂直）同期信号、Hsync ... H（水平）同期信号、Pa ... センサピッチ（センサ用検出電極のピッチ）、Wb ... 駆動ライン幅（位置検出用駆動ラインの幅）。 10

【図1】

【図2】

【図3】

【図4】

【図5】

【 四 7 】

【 叁 6 】

【 図 8 】

【図 9】

43

【図 10】

【図 11】

【図 12】

【図13】

【図14】

【図15】

【図16】

【図17】

【図18】

【図19】

【図20】

【図 2 1】

【図 2 2】

電圧印加時 (白)

(A)

(B)

【図 2 3】

【図 2 4】

【図25】

【図26】

【図27】

【図28】

【図29】

【図30】

【図31】

【図32】

---

フロントページの続き

| (51)Int.Cl. |                 | F I                  |

|-------------|-----------------|----------------------|

| G 0 9 G     | 3/20 (2006.01)  | G 0 9 G 3/20 6 9 1 D |

| G 0 6 F     | 3/044 (2006.01) | G 0 9 G 3/20 6 1 2 T |

|             |                 | G 0 9 G 3/20 6 2 4 C |

|             |                 | G 0 9 G 3/20 6 1 1 C |

|             |                 | G 0 6 F 3/044 E      |

(72)発明者 竹内 剛也

東京都港区港南1丁目7番1号 ソニー株式会社内

(72)発明者 寺西 康幸

東京都港区港南1丁目7番1号 ソニー株式会社内

審査官 中田 剛史

(56)参考文献 特開2004-021327 (JP, A)

特開2009-110418 (JP, A)

特開2008-233315 (JP, A)

(58)調査した分野(Int.Cl., DB名)

|         |             |

|---------|-------------|

| G 0 6 F | 3 / 0 4 1   |

| G 0 2 F | 1 / 1 3 3 3 |

| G 0 2 F | 1 / 1 3 4 5 |

| G 0 6 F | 3 / 0 4 4   |

| G 0 9 F | 9 / 3 0     |

| G 0 9 G | 3 / 2 0     |

| G 0 9 G | 3 / 3 6     |