(12) 发明专利

(10) 授权公告号 CN 107845374 B

(45) 授权公告日 2021.10.01

(21) 申请号 201710860732.1

G·谢 I·利特奇马诺夫

(22) 申请日 2008.12.01

(74) 专利代理机构 北京戈程知识产权代理有限公司 11314

(65) 同一申请的已公布的文献号

代理人 程伟 王锦阳

申请公布号 CN 107845374 A

(51) Int.CI.

G09G 5/36 (2006.01)

(43) 申请公布日 2018.03.27

G09G 5/395 (2006.01)

(30) 优先权数据

G06T 1/20 (2006.01)

11/987,559 2007.11.30 US

G06F 3/14 (2006.01)

(62) 分案原申请数据

审查员 史孝波

200880125863.4 2008.12.01

(73) 专利权人 ATI技术无限责任公司

地址 加拿大,安大略省

(72) 发明人 J·程 T·拉维奥莱特 J·黄

R·扎布聚茨 J·朗 X·翁

S·马林科维奇 P·穆玛 M·简

M·特里西德 R·萨尔特切瓦

权利要求书1页 说明书11页 附图13页

(54) 发明名称

跨越高速外围互连总线的视频渲染

(57) 摘要

本发明涉及跨越高速外围互连总线的视频渲染。由一个图形处理器产生的图形经由高速互连总线而传送至帧缓冲器。来自该帧缓冲器的该渲染过的帧经由与该帧缓冲器通信的显示器接口而呈现在显示器上。另一个存在的(例如,集成的)图形适配器/子系统的显示器接口可用来将该渲染过的帧呈现于互连的显示器上。

1. 一种操作计算器件的方法,该计算器件包括存储器、包含第一图形处理器及显示器接口的第一图形适配器、以及含有第二图形处理器的第二图形适配器,且该存储器可被该第二图形适配器访问,该方法包括:

该第二图形适配器渲染该第一图形适配器的该存储器中的帧缓冲器中的图像,该帧缓冲器中的该图像被放置在与该第二图形适配器不关联的存储器中,其中,该渲染是一个基元一个基元地跨越总线而被引导至该帧缓冲器中,从而跨越该总线传送渲染的图像,并且该第一图形适配器的该第一图形处理器维持休眠或闲置;以及

该第一图形适配器的该显示器接口采样该存储器中的该帧缓冲器,以将由该存储器中的该帧缓冲器内的该第二图形适配器所渲染过的图像呈现在互连的显示器上。

2. 如权利要求1所述的方法,其中,该第二图形适配器不包含显示器接口,并且缺少界定帧缓冲器本地至该第二图形适配器的存储器。

3. 如权利要求1所述的方法,其中,该计算器件是便携式计算器件,以及该第二图形适配器形成系泊部位的一部分。

4. 一种计算器件,包括:

存储器;

第一图形适配器,包括第一图形处理器与显示器接口;以及

第二图形适配器,包括第二图形处理器,其中,该存储器可被该第二图形适配器访问;

其中,控制该第二图形适配器的操作的驱动器软件组构以渲染该第一图形适配器的该存储器中的帧缓冲器中的图像,该帧缓冲器中的该图像被放置在与该第二图形适配器不关联的存储器中,其中,该渲染是一个基元一个基元地跨越总线而被引导至该存储器的该帧缓冲器中,从而跨越该总线传送渲染的图像;

该第一图形适配器的驱动器组构以使该第一图形适配器的该显示器接口采样该存储器中的该帧缓冲器,以将由该存储器中的该帧缓冲器内的该第二图形适配器所渲染过的图像呈现在互连的显示器上。

5. 如权利要求4所述的计算器件,其中,该第一图形适配器的该驱动器将该第一图形适配器的该第一图形处理器引导为维持休眠或闲置。

6. 如权利要求4所述的计算器件,其中,该计算器件是便携式计算器件,以及该第二图形适配器形成系泊部位的一部分。

7. 如权利要求4所述的计算器件,其中,该第二图形适配器不包含显示器接口,并且缺少界定帧缓冲器本地至该第二图形适配器的存储器。

## 跨越高速外围互连总线的视频渲染

[0001] 本申请是申请号为200880125863.4,发明名称为“跨越高速外围互 连总线的视频渲染”,申请日为2008年12月1日的进入中国的PCT 专利申请的分案申请。

### 技术领域

[0002] 本发明通常涉及计算器件,特别是涉及包含图形处理器的计算器 件,该图形处理器互连于高速外围总线。

### 背景技术

[0003] 近年来,计算硬件已经变得越来越集成了。计算机外围通常形成 如集成芯片组中与中央处理器共同操作的部分。通常,计算机音讯、图形适配器和接口形成该集成芯片组的一部分。这种集成降低该计算 器件的成本和尺寸。

[0004] 在此同时,图形处理器是稳定地发展,以提供增强的效能和特征。先进的图形处理器已几乎与中央处理器同样复杂了。因此,尽管集成 的潮流,高效能图形处理器仍通常形成在外围卡上。集成图形处理器 比较起来相当简单,并且没有提供形成在外围卡上的高效能图形处理 器的特征或效能。在附加 (add-on) 外围卡出现的情况下,集成图形组 件(当出现时)通常是多余的并因此是失能的 (disabled)。

[0005] 类似地,当图形适配器(不论是集成的或外部的)升级时,较不 具效力的适配器通常没有适用余地,因此,这些会被抛弃或失能。

[0006] 因此,仍需降低组件的多余性。

### 发明内容

[0007] 依据本发明的方面,由一个图形处理器产生的图形是跨越高速扩充/互连总线传送至帧缓冲器。来自该帧缓冲器的该渲染过的帧是经由 与该帧缓冲器通信的显示器接口而呈现在显示器上。

[0008] 方便地,另一个现存的(集成的)图形适配器/子系统的显示器接 口可用来将该渲染过的帧呈现在互连显示器上。

[0009] 以这种方式,该图形处理器可形成图形适配器中不需包含显示器 接口或可能甚至帧缓冲器的部分。同样地,该图形处理器可被更流行 的图形处理器取代。

[0010] 该图形处理器可形成图形适配器中包含在外围扩充卡上的部分。

[0011] 在一个实施例中,计算器件可包含第一和第二图形适配器。将被 显示在显示器上的图像被传送至可被该第二图形适配器访问的存储 器。该第二适配器的显示器接口是用来将该第二图形适配器的存储器 中的图像呈现在该多个显示器中至少一者。以这种方式,形成该显示 器接口和该第二适配器的端口 (port) 的器件电子设备可因此利用。渲 染过的图形可以一次传送一帧或一图形基元 (primitive) 的方式被传送。在后者的例子中,图形是直接地由该第二图形适配器所访问的存储器 中被有效地渲染。该存储器可为系统存储器或适配器存储器。

[0012] 依据另一个实施例,该第二适配器的图形处理器可失能或置于低 电源模式,而该第一图形处理器则渲染跨越该高速互连总线传送的帧。

[0013] 依据本发明的另一个方面,形成第一图形适配器的一部分的图形 处理器是操作以分别在第一和第二显示器上绘制第一和第二图像。该 第一显示器可与该第一图形适配器的第一显示器接口互连。该第二显 示器可与第二图形适配器的第二显示器接口互连。该方法包含渲染该 第一图形适配器的存储器中的该第一和第二图像;将来自于该第一适 配器的该存储器的该第二图像传送至该第二图形适配器的帧缓冲器;以及,使用该第二图形适配器的该第二显示器接口,将来自于该第二 图形适配器的该帧缓冲器的该第二图像显示在该第二显示器上。

[0014] 依据本发明的另一个方面,计算器件包含:处理器;与该处理器 通信的计算机可读取存储器;第一图形适配器;与该第一图形适配器 通信的第一适配器存储器;用来将图 像呈现在第一显示器上的第一显 示器接口;第二图形适配器;用来将图像呈现在第二显示器上的第二 显示器接口;与该第一和第二图形适配器互连的高速总线。程序代码 是储存在该计算机可读取存储器中,并可被该处理器执行。该程序代 码当执行时,使该第一图形适配器渲染该第一适配器存储器中的第一 和第二图像;使来自于该第一适配器存储器的该第二图像传送至该第 二图形适配器的帧缓冲器;以及,使该第二图形适配器的该第二显 示器接口被编程以将来自于该第二图形适配器的该帧缓冲器的该第二图 像显示在该第 二显示器上。

[0015] 依据另一个方面,该第一适配器将第一图像直接渲染至可由该第 二适配器访问的该系统存储器中。该第二适配器将该第二图像渲染至 该相同的存储器中。该第二适配器显示来自于该系统存储器的图像。

[0016] 依据本发明的另一个方面,提供一种操作计算器件的方法,该计算 器件包含处理器、与该处理器通信的存储器、将该处理器互连至图形 处理器的外围互连总线、以及显示器接口。而该方法包含在该存储器 中建立帧缓冲器;指示该图形处理器渲染视频帧;将该视频帧经由该 外围互连总线传送至该帧缓冲器中;以及,将来自于该帧缓冲器的该 帧经由该显示器接口呈现在显示器上。

[0017] 依据本发明的再一个方面,提供一种计算器件。该计算器件包含 中央处理器、与 该中央处理器通信的存储器、将该中央处理器互连至 图形处理器的外围互连总线、显示器 接口、储存在该存储器中的计算 机可执行指令,适配该计算器件:使该图形处理器渲染视 频帧;将该 视频帧经由该外围互连总线传送至帧缓冲器中;以及将来自于该帧缓 冲器的 帧经由该显示器接口显示在显示器上。

[0018] 依据本发明的另一个方面,提供一种计算器件。该计算器件包含 中央处理器;与 该处理器通信的存储器;第一帧缓冲器;将该处理器 互连至图形子系统的外围互连总线, 该图形子系统缺少本地界定帧缓 冲器至该图形子系统的存储器;以及,与该存储器通信的 显示器接口。该存储器储存计算机可执行指令,该计算机可执行指令适配该图形处 理器渲染视频帧,并将该视频帧经由该外围互连总线传送至该第一帧 缓冲器中。

[0019] 依据本发明的另一个方面,提供一种图形子系统,包含:图形处 理器、及外围互连 总线接口,用来将该图形子系统互连至主处理器, 该图形子系统缺少本地界定帧缓冲器至 该图形子系统的存储器;以及, 该图形子系统操作以渲染视频帧,并将该视频帧经由该外

围互连总线 传送至帧缓冲器中。

[0020] 依据本发明的另一个方面，提供一种操作第一图形处理器以分别 在第一和第二显示器上绘制第一和第二图像的方法。该第二显示器是 与第二图形适配器的显示器接口互连。而该方法包含渲染与该第一图 形处理器通信的存储器中的该第一和第二图像；将该第二图像传送至 该第二图形适配器的帧缓冲器；以及，编程该第二图形适配器的该显示 器接口，以将来自于该第二图形适配器的该帧缓冲器的该第二图像 显示在该第二显示器上。

[0021] 本领域中具有通常技术者，在看过接下来的本发明特定实施例的 描述与伴随图 式后，本发明的其它方面和特征将变得明显。

## 附图说明

- [0022] 在以下仅通过范例来显示本发明的实施例的图式，其中，

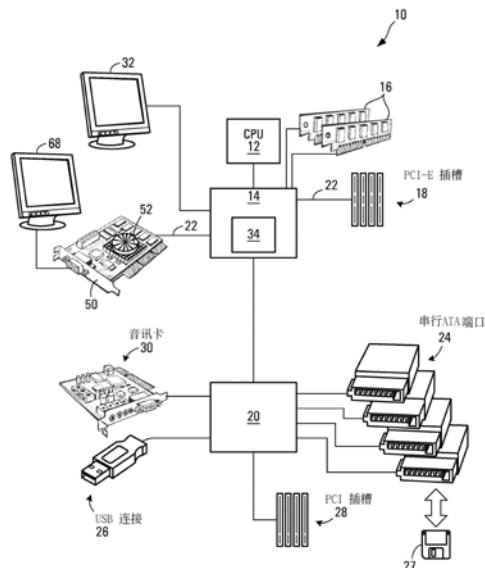

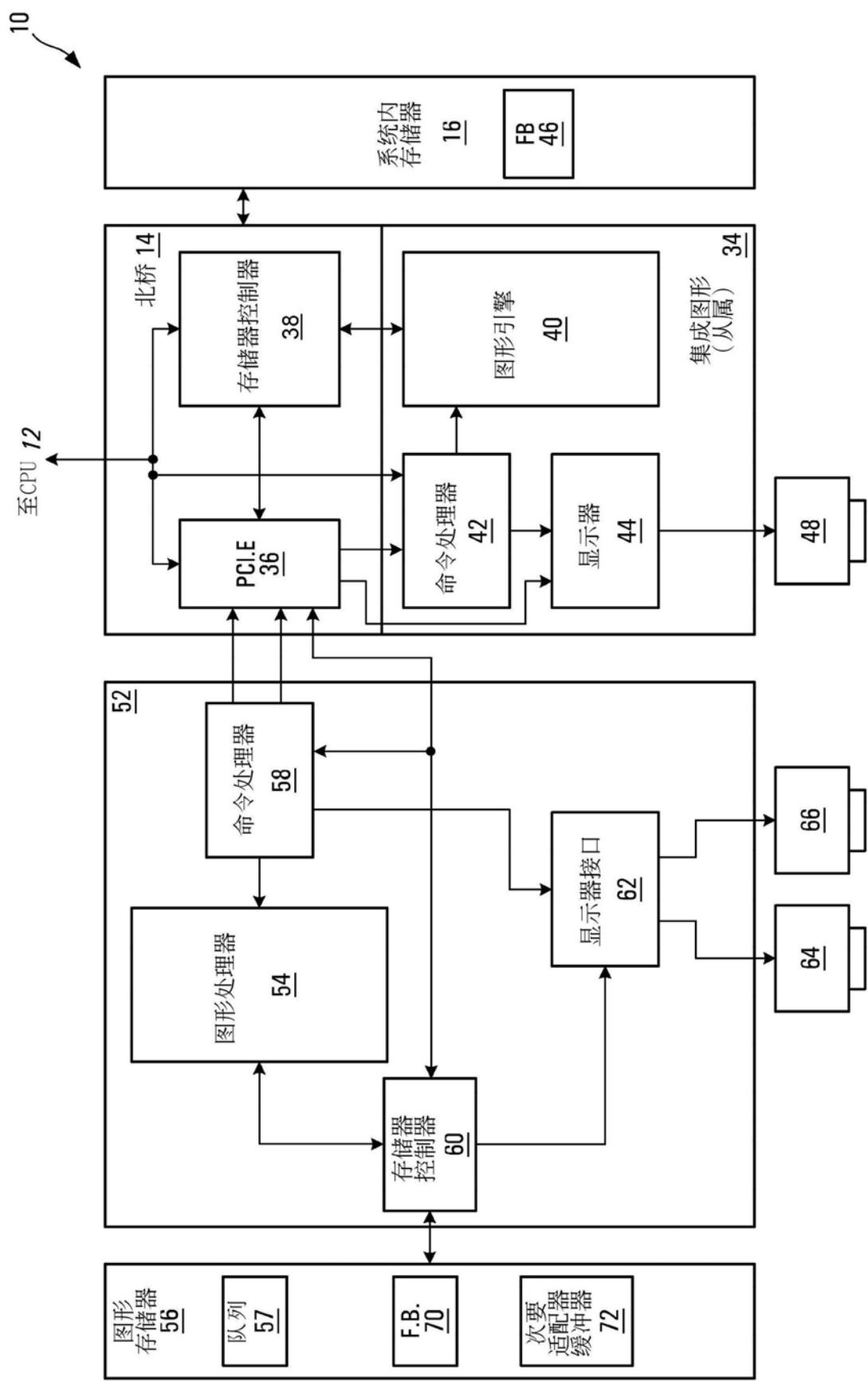

- [0023] 图1为计算器件的简化方框图，其为本发明的实施例的范例；

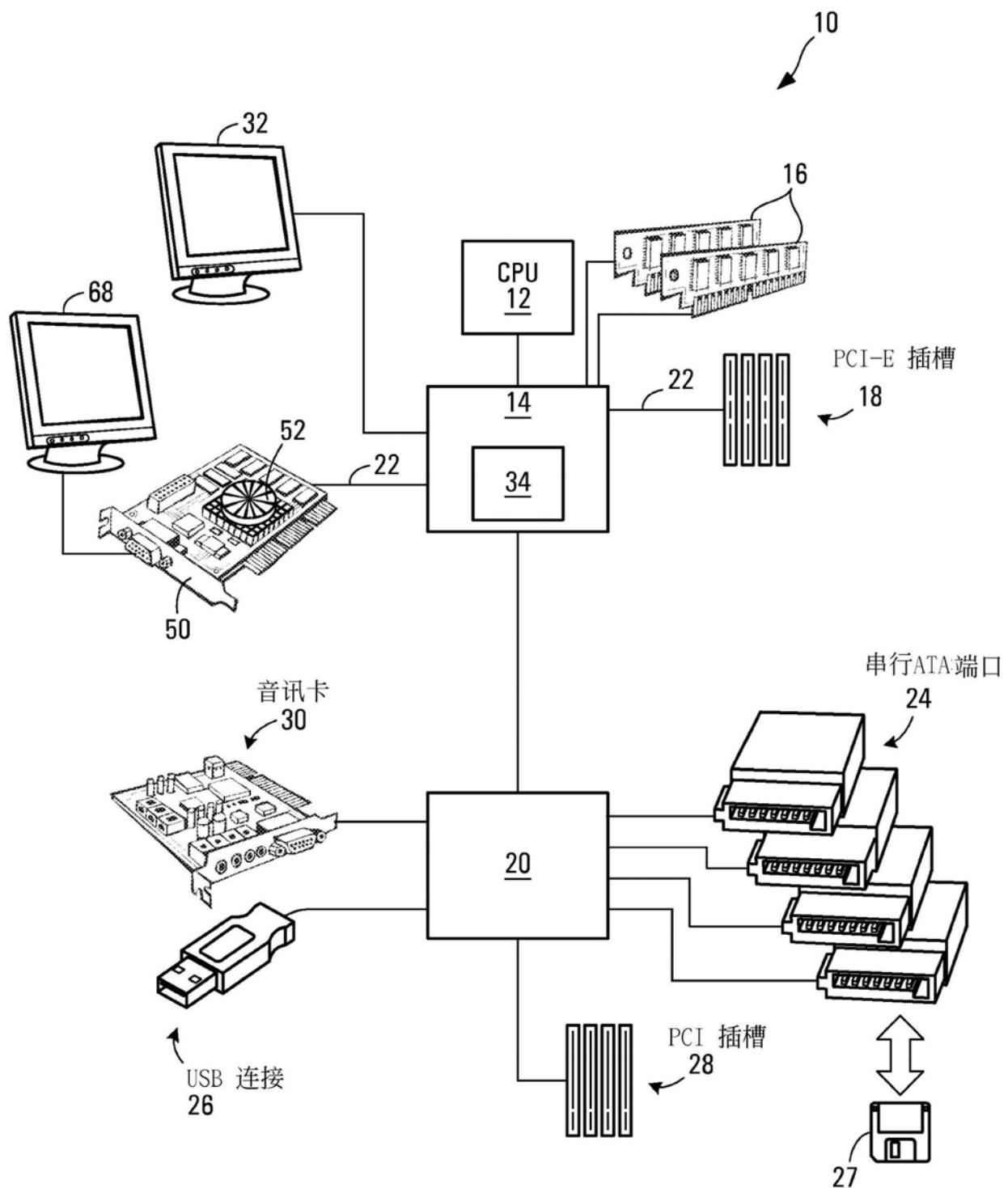

- [0024] 图2为图1的该计算器件的软件的简化逻辑方框图；

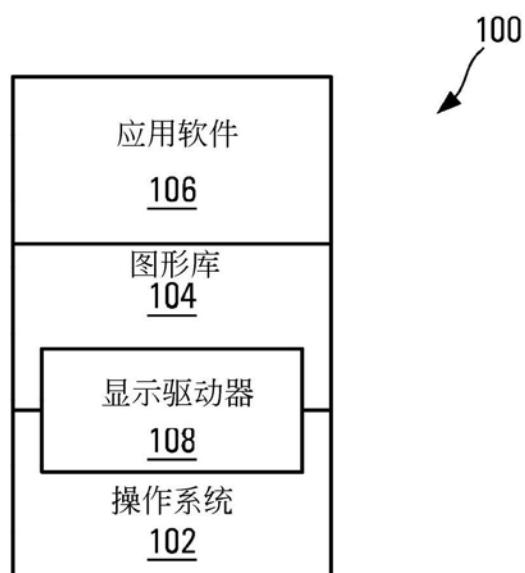

- [0025] 图3为图1的该计算器件的一部分的简化方框图；

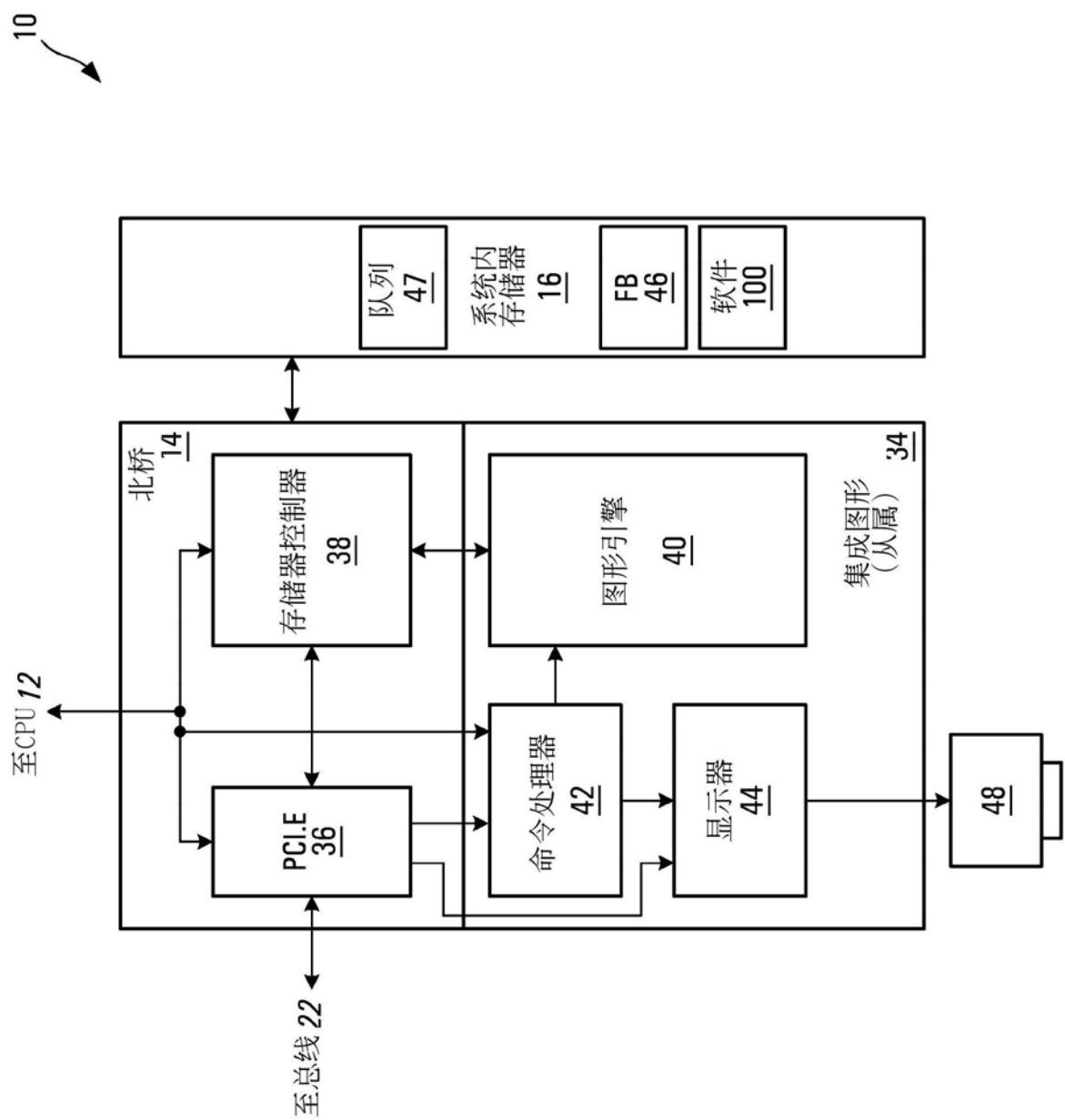

- [0026] 图4为图1的该计算器件的一部分的进一步示意方框图；

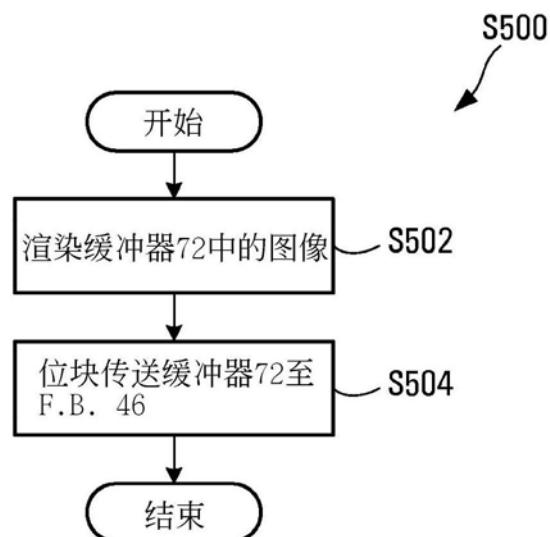

- [0027] 图5A为显示在图1的该计算器件所实施的步骤的流程图，其为本 发明的实施例的 范例；

- [0028] 图5B示意地描绘图5A的步骤在图1的器件的组件上的作用；

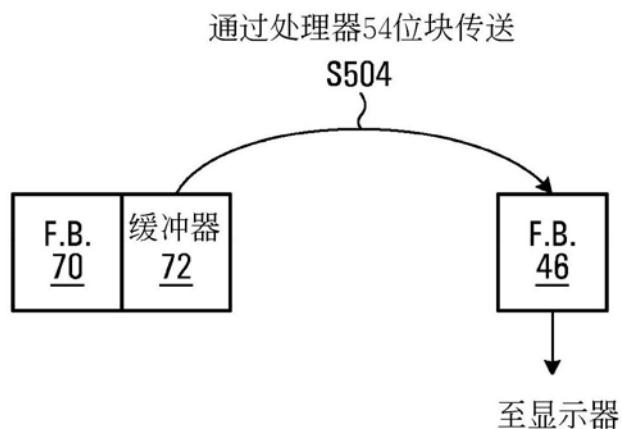

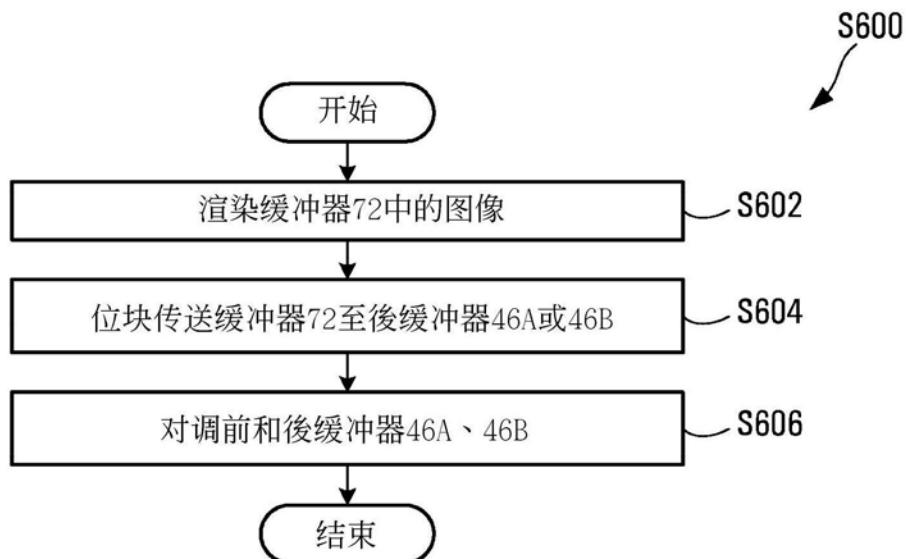

- [0029] 图6A为显示在图1的计算器件所实施的步骤的流程图，其为本发 明的实施例的范 例；

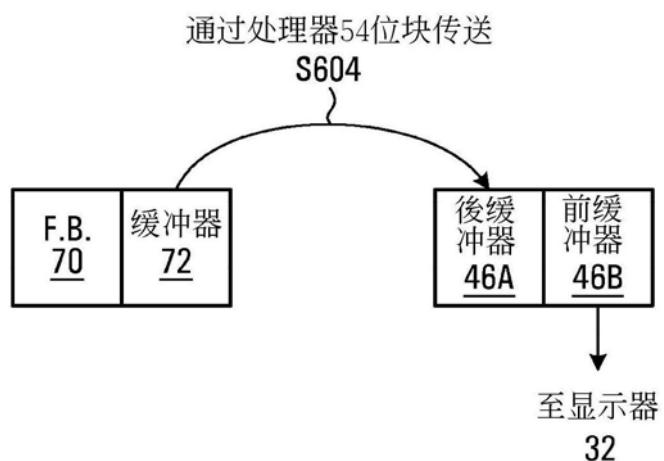

- [0030] 图6B和图6C示意地描绘图6A的步骤在图1的器件的组件上的 作用；

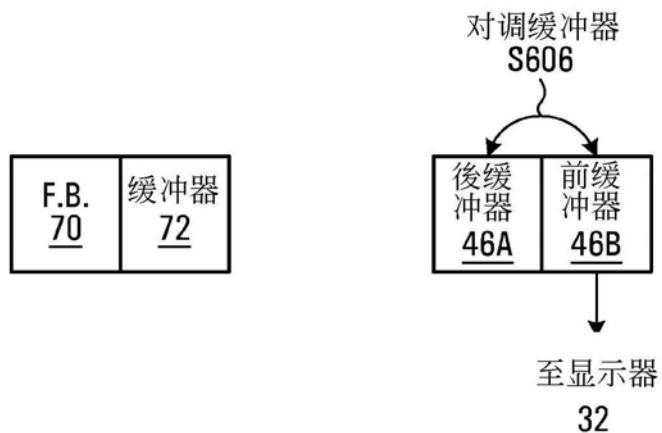

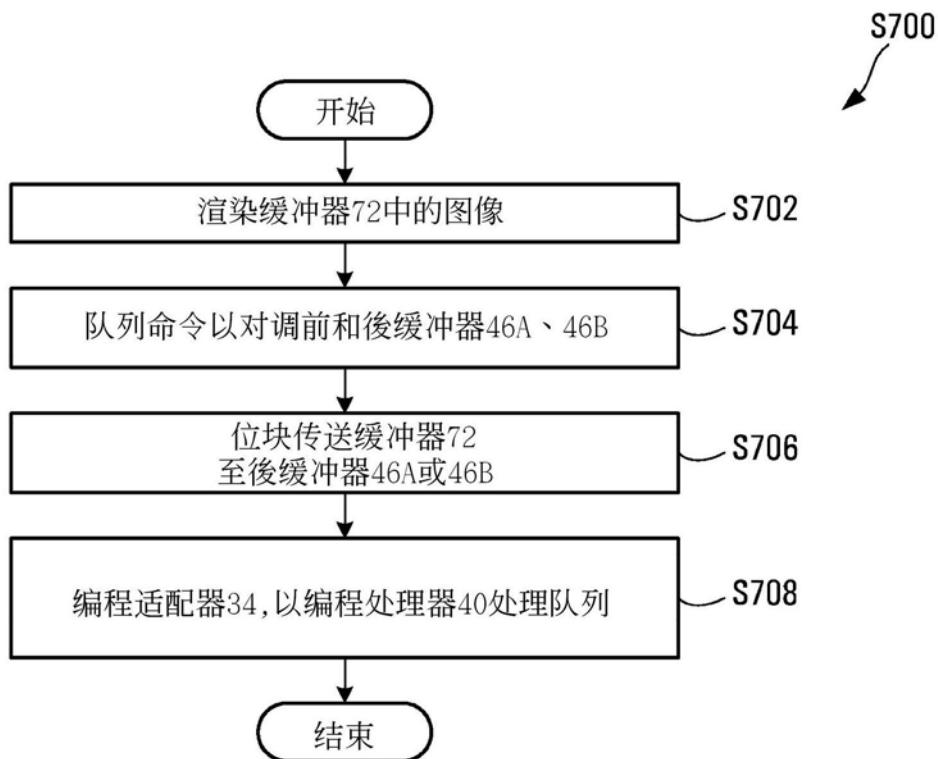

- [0031] 图7和图8为显示在图1的计算器件所实施的步骤的流程图，其 为本发明的进一步 实施例的范例；

- [0032] 图9为计算器件的一部分的进一步部分简化示意方框图，其为本 发明的进一步实 施例的范例；

- [0033] 图10显示在图9的计算器件所实施的步骤的流程图，其为本发明 的实施例的范 例；以及

- [0034] 图11A、图11B为显示图9的器件的操作的简化方框图；以及

- [0035] 图12为计算器件的一部分的进一步部分简化示意方框图，其为本 发明的进一步实 施例的范例。

## 具体实施方式

[0036] 图1为计算器件的简化示意方框图，其为本发明的实施例的范例。计算器件10是 基于传统的Intel x86架构。然而，将会变得明显，本发 明可容易地实作在具有PowerPC、 AMD x86或其它架构的的计算器件 中。

[0037] 计算器件10包含处理器12，通过集成接口电路14和20互连至系 统存储器16和外 围。

[0038] 在范例计算器件10中的处理器12为传统的中央处理单元，并且 可例如为与该

INTEL<sup>TM</sup>x86家族微处理器兼容的微处理器。

[0039] 集成接口电路14和20通常分别指北桥和南桥,且提供处理器12 至外围和存储器的接口。如所显示的,北桥14互连该处理器12;存储 器16;经由高速互连总线22的复数个扩充插槽18;以及南桥20。南 桥20互连至低速外围和互连,例如经由集成IDE/SATA 24的磁盘驱动 器、经由集成通用串行总线(USB) 端口26的通用串行总线器件;以 及,经由低速互连总线28的例如符合PCI或ISA标准的其它外围。南 桥20可包含集成音讯组件30、网络接口(未显示)、等等。

[0040] 范例的互连总线22为PCI express (PCIe) 总线,其带宽在每秒百 万字节的范围内,并允许数据传送在此带宽读取和写入。举例来说, 现有的PCIe总线速度允许双向数据在高达266MHz或533MHz的总线 速度下传送,以允许高达每秒2.1百万字节或每秒4.2百万字节的数据 速率。

[0041] 在绘示的实施例中,北桥14进一步包含集成图形适配器34,集成 图形适配器34适于将计算器件10互连至第一显示器32,第一显示器 32的形式为监视器、LCD面板、电视、等等。

[0042] 如以下所详述的,经由互连总线22互连且形成例如互连总线22 上的扩充插槽18 中的外围扩充卡50的一部分的额外图形适配器52可 进一步为计算器件10的一部分。

[0043] 在绘示的实施例中,计算器件10执行储存在存储器16中的软件。如图2所显示的,范例软件100包含储存在存储器16中的操作系统 102、图形库104和应用软件106。范例的操作系统包含Windows Vista、Windows XP;Windows NT4.0、Windows ME;Windows 98、Windows 2000、Windows 95、或Linux操作系统。范例的图形库包含Microsoft DirectX libraries和OpenGL libraries。计算机存储器16(图1) 和互连 的磁盘驱动器(未显示) 包含随机访问存储器、只读存储器和磁盘储 存存储器的适合组合,其被器件10用来以本发明的实施例的范例方式 储存和执行和器件10适配的操作系统和图形适配器驱动器程序。范例 的软件100(图2) 例如可储存在只读存储器中或从外在的外围(例如 与IDE/SATA端口24 通信的磁盘驱动器) 加载。计算机可读介质27 可为光学储存介质、磁性软盘(magnetic diskette)、磁带、ROM盒带 (cartridge)、等等。

[0044] 图形库104或操作系统102进一步包含图形驱动器软件108,用来 与图形适配器34 和52低阶通信。该软件具有数层,较高阶层使用较 低阶层以提供特定功能。应用可利用操作系统102和图形库104以渲 染2D或3D图形。渲染从上下文看是包含绘制、不然就是创造用于呈 现的图形图像,且可例如包含多边形渲染(polygon rendering)、光线追 踪(ray-tracing)、图像译码(image decoding)、线绘制(line drawing)、等等。将会变得明显,本 发明的实施例的软件范例可形成图形库104 和/或驱动器软件108的一部分。在范例实施例 中,范例软件可形成 OpenGL library和相关的驱动器的一部分。OpenGL在The Official Guide to Learning OpenGL,第1.1版有特别的详述,该内容并入于此作为参 考。然而,具有通常技术者将了解本发明的实施例的范例方法可形成 Microsoft Direct3D libraries、不使用惯用库或惯用程序的应用(例如游 戏)、或其它任何3D应用或库的一部 分。

[0045] 描绘集成图形适配器34的计算器件10的一部分(和尤其是北桥 14) 的进一步简化方框图是显示在图3。如所显示的,北桥14包含高 速总线接口36和存储器控制器38,将桥14

互连至互连总线22和系统 存储器16。北桥14进一步包含集成图形适配器34,集成图形适配器 34接着包含图形处理器40、命令处理器42和显示器接口44。

[0046] 图形处理器40可采用三维(3D)图形处理器的形式,该三维图形 处理器可渲染配置在系统存储器16内的帧缓冲器46中的三维图像, 并可包含用于加速渲染图形的多重管线(pipeline) 和管线阶段。

[0047] 在正常单一监视操作中,命令是以传统的方式由命令处理器42传 给图形处理器40。举例来说,命令处理器42可包含用来界定存储器 16中的命令队列(command queue) 47的寄存器47。应用软件106或操作 系统102使用库104来渲染图形图像。驱动器软件108产生图形处 理器特定的命令,并将这些放置在该命令队列47中,且同时更新命令 处理器42的寄存器,以反映该队列的尾端。图形处理器42以管线的 方式异步处理队列的命令,以为渲染帧缓冲器46内的图像。当图形 处理器40能够处理该队列中的下一个命令时,他提供讯号至命令处理 器42,命令处理器42接着抓取该队列47中的下一个命令,并将队列 指示字前进至命令处理器42的寄存器中。

[0048] 显示器接口44经由存储器控制器38采样该帧缓冲器46并将图像 呈现在具有VGA 端口、复合的视频端口、DVI端口、HDMI、显示器 端口、等形式的一个或多个视频输出端口 48上,用以在例如具有电 视、监视器、等形式的视频器件(例如图1的显示器32) 显示一个 或多个图像。以这种方式,可呈现帧缓冲器46中由图形处理器40所 渲染的图像。

[0049] 将会了解到,显示器接口44可为任何用来转换缓冲器中用以在显 示器器件上显示的数据的适合接口。举例来说,显示器接口44可采用 RAMDAC的形式。显示器接口44通常是可编程的,例如通过复数个 寄存器,以允许驱动器软件108或类似的软件或图形处理器 40设定存 储器16中的开始地址,以在其显示器输出呈现。同样地,接口44图 素深度(例如, 每图素有几个位) 和屏幕分辨率通常也是可编程的。

[0050] 将会了解到,可在存储器16中放置两个帧缓冲器,以取代放置单 一帧缓冲器46。该缓冲器可交替地使用以更平顺地呈现渲染过的图像。显示器接口44在任何时候仅显示 该两个缓冲器中的一个缓冲器的内 容。被显示的缓冲器通常称为前缓冲器。图形处理器40 渲染图像,以 显示至该所谓的后缓冲器,亦即没有被显示器接口44正在显示的帧缓 冲器。在渲染帧完成后,前和后缓冲器对调:显示器接口44被编程以 呈现该先前的后缓冲器。以 这种方式,由图形处理器40所渲染的接续 帧间的转换可看起来较平顺。

[0051] 值得注意的是,寄存器和被适配器34所使用的存储器46的帧缓 冲器均对应至全 存储器空间中的地址。

[0052] 本发明的范例;然而,计算器件10进一步包含形成在外围扩充卡 50上的图形适配器52,外围扩充卡50可经由高速互连总线22上的扩 充插槽插置于器件10中,以与北桥14通信,如图1所显示的。图形 适配器52当互连至北桥14时,是示意地显示于图4中。如所显示 的,图形适配器52包含图形处理器54、视频存储器56、命令处理器58、存储器控制器60、及 显示器接口62。一个或多个端口64、66允许适 配器52互连至一个或多个显示器器件,例如 显示器68(图1)。

[0053] 命令处理器58和显示器接口62分别与命令处理器42和显示器接 口44以相同的方式运作。图形处理器54与图形处理器40以相同的方式操作,以其正常的操作模式。图形适配器52包含其自己的存储器56 及存储器控制器60,以提供至存储器56和系统存储器16的

访问。本地存储器56是使用来保留一个或多个用于由图形处理器54所使用的图形适配器52的缓冲器70，缓冲器70可作为帧缓冲器。用于图形处理器54的命令队列57也可建立在系统存储器16中。

[0054] 再次地，本地存储器56可通过存储器控制器60寻址在全系统存储器空间中的地址。同样地，由命令处理器54和显示器接口62所使用的寄存器也可寻址在全地址空间的地址内。如已经注意到的，由适配器34所使用的寄存器和帧缓冲器46是对应至全存储器空间。因此，命令处理器58和图形处理器54可写入至由显示器接口44和命令处理器42所使用的帧缓冲器46和寄存器。

[0055] 此外，图形处理器54与存储器控制器60一起操作以实施块传送操作，以将数据在系统和适配器存储器16、56的存储器地址之间传送。

[0056] 为了努力提供节约的集成组件，集成图形适配器34提供有限的功能。举例来说，集成图形控制器的分辨率、3D图形能力、等等是相当的有限。因此，相较于图形适配器52，集成图形适配器34通常具有相当少的图形处理能力。举例来说，相较于适配器52，适配器34可更缓慢地操作，以提供较少的特征、等等。

[0057] 现在，集成适配器34或适配器52其自己可(也可不)允许经由多个端口(例如端口48)互连至多个实体显示器器件。然而，每一个适配器可互连至至少一个实体显示器。所以，本发明的实施例的范例，加载至存储器16的适配器驱动器软件108使图形适配器52作为主要(或第一)图形适配器，主要图形适配器渲染图形，以呈现在显示器32和68上，而图形适配器34则作为第二或从属适配器。

[0058] 将会变得明显，在此主要/从属操作模式中，集成图形适配器34实质上是失能的。然而，板上(on-board)图形适配器34的组件(和尤其是显示器接口44)仍可被使用来驱动互连的监视器和其它显示器器件。像这样，卡50不需包含多重显示器端口和显示器驱动器。取而代之的是，显示器接口44及其端口48可用来驱动至少一个监视器或显示器32，除了显示器68或由卡50所驱动的显示器68外。如果适配器52包含多重端口(例如端口64、66)，处理器52可额外地渲染图像，以通过这些端口来加以呈现。当然，驱动器软件108也可允许适配器34以其传统的操作模式操作，如上述。也可由或通过应用软件106来选择适配器34(和因此适配器52)的操作模式。

[0059] 具体言之，在主要/从属操作模式中，本发明的实施例的范例，存储器16中驱动器软件108将作用的帧缓冲器70和次要适配器缓冲器72放置于适配器52的存储器56中，如图4所示意地描绘。该作用的帧缓冲器70如用于适配器52的传统帧缓冲器作用着，并因此储存帧，以显示于适配器52的显示器68上。像这样，图形处理器54以传统的方式渲染存储器56中的作用的帧缓冲器70中的二维或三维图形。卡50的显示器接口62转换作用的帧缓冲器70的内容，以显示在互连的监视器或显示器器件上。选择性地，作用的帧缓冲器70可被前和后缓冲器所取代，如上述。

[0060] 图形处理器54进一步渲染图像，以在次要适配器帧缓冲器72的显示器器件32上显示。总结渲染次要适配器帧缓冲器72中的帧，次要适配器帧缓冲器72的内容被传送至帧缓冲器46，以由图形适配器34的显示器接口44呈现，如下述。

[0061] 在第一实施例中，存储器16中的图形适配器驱动器软件108实施图5A所描绘的步骤S500。具体言之，驱动器软件108产生命令，以在步骤S502中引导图形处理器54渲染存储

器56的次要适配器缓冲器 72。这些命令是放置在适配器52的命令队列57，并由图形处理器 54 以与命令将被队列于队列47内几乎相同的方式执行，如上述。一旦该 帧被渲染后，驱动器软件108进一步产生一个命令（或数个命令），以 使处理器54将次要适配器帧缓冲器72的内容位块传送（BITBLT）存 储器56中放置如用于图形适配器34的帧缓冲器46的那个区域中（步 骤S504）。

[0062] 图形适配器34的显示器接口44接着已经预编程以将其帧缓冲器 46的内容显示至互连的监视器或端口48处的显示器。方便地接下来，互连至端口48和端口46的显示器32和68上所显示的图像由图形处 理器54渲染或绘制。步骤S504在缓冲器72和帧缓冲器46上的效应 是显示于图5B中。

[0063] 在第二实施例中，实施描绘于图6A中的步骤S600。起初，前和 后帧缓冲器是放置在适配器52的存储器16中。为了方便起见，这些 是指定为缓冲器46a和46b，并且绘示在图 6B中。在步骤S602中，处理器54再次地渲染任何帧，以由如上述参考步骤S502的存储器56的次要适配器帧缓冲器72中的显示器接口44所呈现。

[0064] 总结渲染帧以显示于器件32上，驱动器软件108编程图形处理器 54，以将存储器 56中次要适配器帧缓冲器72的内容位块传送（BITBLT）至存储器16的该之后现在的后缓冲器，以用于步骤S604 中的图形适配器34。在该BITBLT完成后，驱动器编程处理器54，以 编程显示器接口44的寄存器对调适配器34的后缓冲器和前缓冲器（也 就是，使用该后缓冲器作为该前缓冲器），在步骤S606中。此可藉由 直接地再编程显示器接口44的寄存器、以确认由显示器接口44用来 呈现数据所使用的起始地址来加以完成。图形适配器34的显示器接 口 44接着将其缓冲器的内容呈现至在端口48处的互连监视器（也就是， 显示器68）。该之前的前缓冲器接着使用作为用于适配器34的后缓冲 器，而由处理器54所渲染用于显示于显示器32上的下一个帧将初始 地被传送至步骤S604的此后缓冲器。当然，驱动器软件108 维持每 一个缓冲器46a和46b的起始位置作为前和后缓冲器。步骤S604和S606 在缓冲器 46a和46b上的效应是示意地显示在图6B中。

[0065] 在没有同步的情况下，使用单一缓冲器46或直接编程适配器34 的显示器接口44 可导致看得见的撕裂。也就是，显示器接口44的寄 存器编程的垂直回扫期间（vertical blanking interval）以外的任何时间，均看得到撕裂，这是因为显示器参数在由接口44所输出的帧的中间会 改变。

[0066] 因此，在第三实施例中，可实施图7中所描绘的步骤S700。再次 地，前和后缓冲器 46a、46b是初始地放置在由适配器34所使用的存 储器16中。处理器54再次地渲染图像，以在本地存储器56的缓冲器 72内的器件32显示，如上述关于步骤S502和S602。

[0067] 在完成渲染帧以显示在显示器32上后，存储器16中的驱动器软 件108编程图形处理器54，以将存储器56中次要适配器帧缓冲器72 的内容位块传送至步骤S704的图形适配器34的存储器16中的之后现 有后缓冲器。驱动器软件108进一步将命令置放在适配器34的命 令队 列47中，以对调前和后缓冲器（步骤S706）。然而，命令处理器42 的寄存器并非由驱动器软件108更新，以反映命令队列47中尚未处理 的命令。取而代之的是，驱动器软件108 提供命令至图形处理器54（步 骤S708），以在步骤S706中所启动的位块传送完成时更新命 令处理器 42的命令队列寄存器。此接着使命令处理器42提供指令至处理器40，以将其后 缓冲器对调成前缓冲器。图形处理器40接着执行队列的命令，以对调适配器34的后和前缓

冲器(也就是,藉由再编程显示器接口44 的寄存器,以将其之前后缓冲器的内容呈现至互连监视器或端口48处 的显示器)。

[0068] 在第四实施例中,实施图8中所描绘的步骤S800。再次地,前和 后缓冲器初始是放置在适配器34的存储器16中。处理器54再次地渲染图像,以用于本地存储器56的缓冲器72中的显示器32,如上述。

[0069] 驱动器软件108进一步将命令放置在适配器34的队列47中,以 使图形处理器40将存储器56中次要帧缓冲器72的内容位块传送 (BITBLT) 至系统存储器16中放置作为用于图形适配器34的现有后 帧缓冲器的那个区域。驱动器软件108也将命令放置在队列47中,以使图形处理器40通过编程显示器接口44以对调适配器34的前和后缓 冲器,以使用该后缓冲器作为前缓冲器。然而,命令处理器42中界定 该队列指示字的寄存器直到帧已经在缓冲器72中被渲染后才更新。

[0070] 所以,在总结渲染用于显示器32的帧,图形处理器54提供命令 来更新界定用于命令处理器42的该队列指示字的命令寄存器,以反映 适配器34的命令队列中的尚未处理的命令。图形处理器40接着执行 该队列的命令,以将缓冲器72的内容位块传送至其后缓冲器,以对调 其后和前缓冲器(也就是,藉由再编程显示器接口44的寄存器,以将 其之前的后缓冲器的内容呈现至互连监视器或端口48处的显示器)。

[0071] 如将要了解到的,上述实施例允许主图形处理器担负在多重独立 的帧缓冲器上绘制二或三维图形图像的责任。从属图形适配器可用来 显示在一个帧缓冲器中所创造的图像。驱动额外的显示器所需要的器 件电子组件和端口可由从属图形适配器34提供。以这种方式,包含在 从属图形控制器中的电子组件可有效地用来允许驱动多重显示器。

[0072] 传统上,缓冲器70和72可用来界定单一表面,在该单一表面上,应用软件106可将单一图形图像渲染成显示跨越两个或更多个与图形 适配器52和34互连的显示器48和64 上。驱动器软件108可相应地 将可用的屏幕尺寸报告给应用软件106,相当于缓冲器70和缓冲器72 的尺寸。因此,如果缓冲器70的分辨率为 $m_1 \times n$ ,而缓冲器72的分辨 率为 $m_2 \times n$ ,则驱动器软件108可将可用的屏幕尺寸  $(m_1+m_2) \times n$ 报告 给应用软件106的应用。如果缓冲器70和72 占据存储器56中相邻的  $(m_1+m_2) \times n$ 个图素位置,则由驱动器软件108所实施的渲染会被简化。应用软件106可接着使用驱动器软件108,以使图形处理器40渲 染较大的图像,该较大的图像的分辨率为组成由缓冲器70和72所界 定的平面的  $(m_1+m_2) \times n$ 个图素。缓冲器70和72 因此储存图像对, 其中,该图像对的每个图像形成该较大的图像中由该应用所渲染的一部分。总结渲染每一个较大的图像,驱动器软件108可依据上述的步 骤S500、S600、S700或 S800将缓冲器72中的图像传送给帧缓冲器 46,用于显示在显示器32上。缓冲器70中的该图像可以正常的方式 显示在显示器68上。观看放置在一起的显示器32和68的最后用户认 识到由应用106所渲染的该较大的图像。将会了解到,具有游戏形成 的应用106可利用多重显示器,而不需要修正。

[0073] 如果前和后缓冲器为显示器68所使用,则可放置和使用两个不同 的缓冲器,以代替缓冲器72,以确保保留将被显示在显示器32上的该 表面部分的该缓冲器在存储器56中 是邻接该缓冲器,其中,将被显示 在显示器68上的该表面部分会被渲染。步骤S602、S604、S702、S704 或S802、S704可相应地被修正为将保留该刚完成的图像的该缓冲器位 块传送至后缓冲器46a或46b。方便地,现有的应用软件106不需修正。取而代之的是,该应用软件

可只是依赖该报告的较大的屏幕尺寸。驱动器软件108使该渲染表面跨越多重显示器。

[0074] 也将会被了解到,虽然该描绘的实施例利用集成图形控制器作为从属图形适配器,但该从属图形适配器可轻易地是经由总线(该总线具有足够的带宽,以允许将图形帧传送至该从属帧缓冲器内)而与图形适配器52通信的另一个图形适配器。像这样,该从属图形处理器可形成如另一个与PCIe兼容的扩充卡。所以,举例来说,当图形卡升级时,较旧的扩充卡可能仍被使用,以他们的能力来驱动互连的显示器。类似地,该互连总线不需要是PCIe互连总线,但可为任何其它适合的总线,只要该总线的带宽允许数据以与显示器接口44所使用的刷新率的速率在帧缓冲器之间传送即可。同样地,虽然帧缓冲器46(和前和后缓冲器46a和46b)已经描述成为形成在系统存储器16中,他们可容易地形成如存储器中本地至适配器34的一部分。

[0075] 在本发明的又一个实施例中,渲染跨越总线22可允许由高速总线22所互连的图形适配器(或子系统)取代集成适配器/子系统。

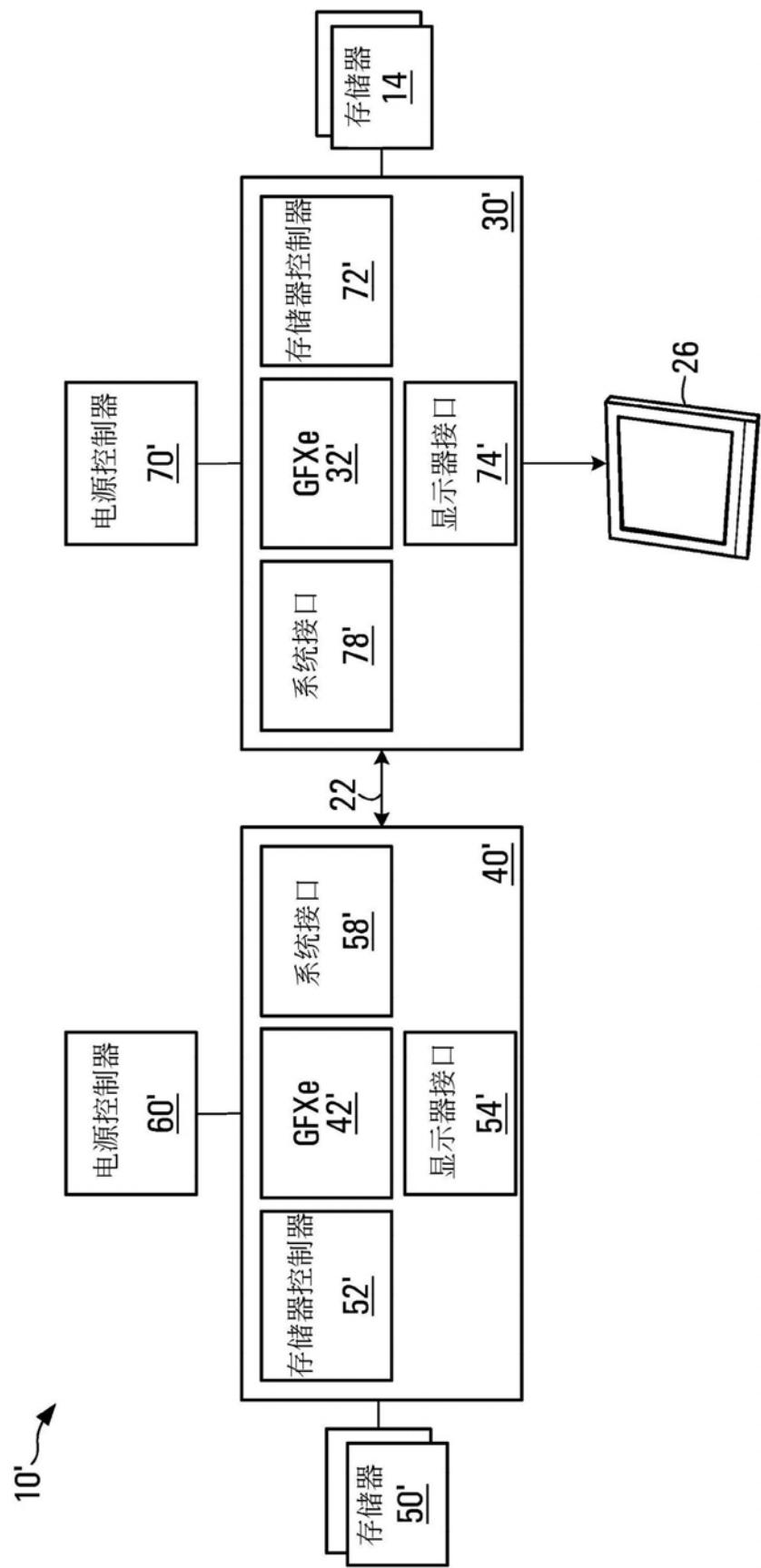

[0076] 为了达到此目的,图9为本发明的另一个实施例的计算器件10'范例的一部分的简化方框图范例。计算器件10'详述于美国专利申请案第11/421,005号。

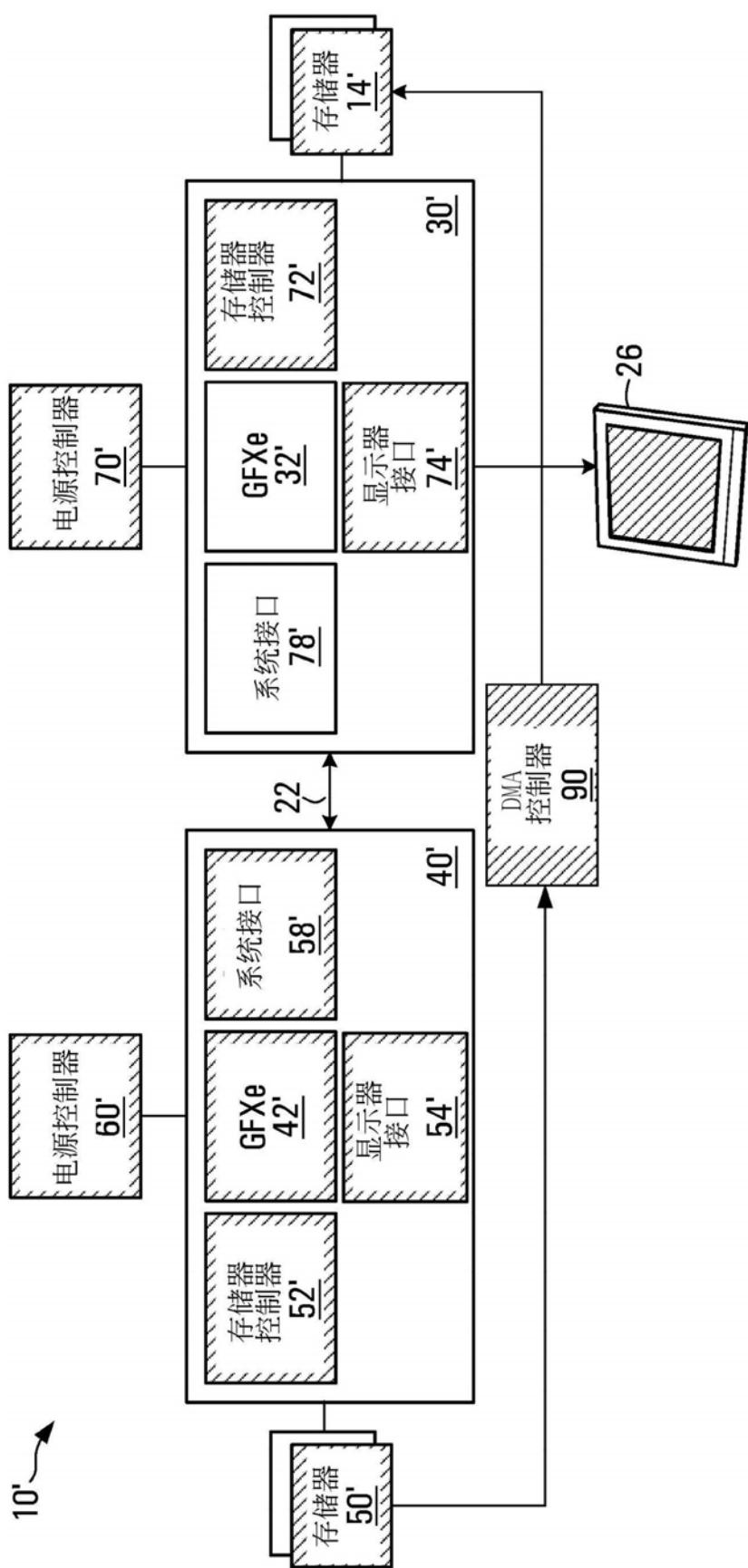

[0077] 简言之,然而,器件10'包含两个图形子系统30'和40'。图形子系统30'包含图形引擎/处理器32'、存储器控制器72'、显示器接口74'和总线接口78'。第二图形子系统40'是经由高速总线22'(例如PCIe总线)而与图形子系统30'通信。图形子系统40'包含其自己的图形引擎/处理器42';存储器控制器52';显示器接口54'。图形子系统40'进一步与图形存储器50'通信。将会变得明显,子系统40'是适配来将图形渲染跨越总线22'而至存储器14'。

[0078] 器件10'可方便地形成如具有膝上型或较小计算器件的形式的便携式计算器件。像这样,单一外罩可包含DC电源、显示器26'和上述的主机板和组件。该第二图形子系统40'可附加至罩住该计算器件的其余部分的单一外罩,或可形成系泊部位(docking station)中只形成部分器件10'的一部分(当器件10'实体互连至该部分时)。

[0079] 器件10'可操作在至少两种电源消耗模式:较高电源消耗模式和较低电源消耗模式。在描绘的实施例中,当器件10'是由连接至AC(主要)供应器的电源供应电源时,器件10'可假定为较高电源模式;当器件10'是由使用一个或多个电池、燃料电池、等等的DC电源供应电源时,器件10'是假定为较低电源消耗模式。或者,电源消耗模式可依据例如,用户偏好、被执行的软件应用的类型、电池电位、等等或其它选择,而由用户选择或由软件控制。

[0080] 控制器件10'的操作的软件的机构是揭露在美国专利申请案第11/421,005号,并且分享类似的软件100,如上述。

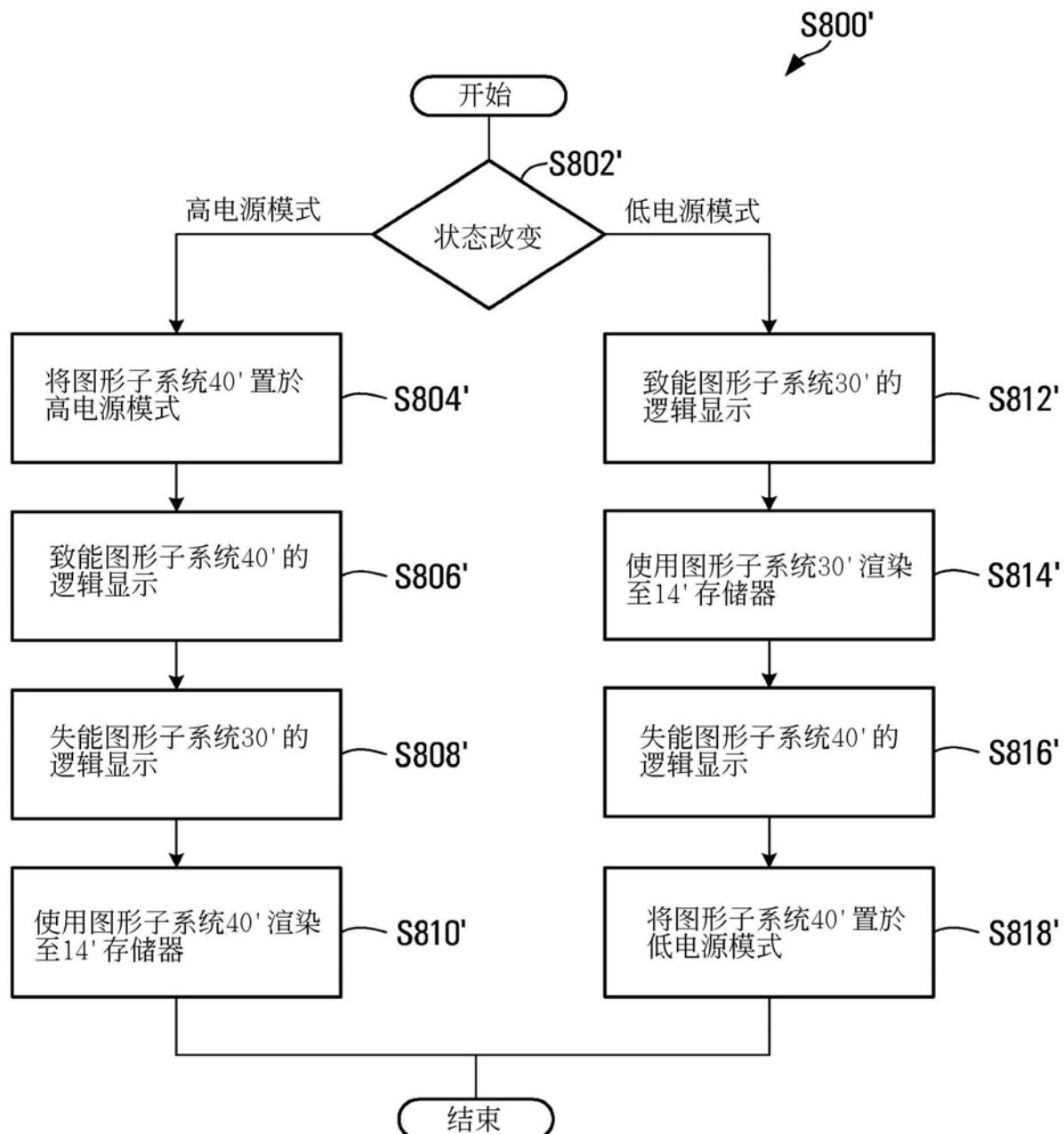

[0081] 部分该软件控制器件10'的操作如同器件10'在高和低电源消耗状态转换。具体言之,图10绘示本发明的实施例的范例软件方框S800',软件方框S800'由器件10'的系统存储器中的软件控制的中央处理器(例如图1中的处理器12)所实施。方框S800'可在每一次器件10'进行状态改变时实施,因此,其子系统30'和40'应相应地组构。如所显示的,在方框S802'中,该软件判定器件10'是否应假定为较高电源消耗模式、或为其较低电源消耗模式。

[0082] 当器件10'假定(或转换)为其高电源消耗模式时,执行方框S804'-S810'。在方框

S804中,图形子系统40'是置于其全操作(高电源消耗)模式,如果其尚未在此模式。此可通过将适当的讯号经由控制图形子系统40'的驱动器提供给电源控制器60'而加以执行。接下来,图形子系统40'在方框S806和S808中致能。再次地,此可通过将互连关联于图形子系统30'的任何显示器逻辑地失能(方框S804)、及将连接于图形子系统40'的该显示器逻辑地致能(方框S808)而加以执行。方框S806和S808可再次地由适当的操作系统API calls(例如,美国专利申请案第11/421,005号所描述的EnumDisplayDevices()和ChangeDisplaySettingsEX()calls)来加以执行、或透过与硬件直接通信来加以执行。

[0083] 需注意的是,没有实体的显示器是连接至图形子系统40'。控制图形子系统40'的操作的驱动器软件是组构以渲染图形子系统30'的缓冲器中的图像,而非渲染步骤S810'中的关联存储器50'中的图像。方便地,在高速总线22'(实作为例如PCIe总线)出现的情况下,这种渲染有可能跨越总线22',部分是因为由该总线所致能的传送速度。

[0084] 该渲染可一个基元一个基元地跨越该总线而被引导至该帧缓冲器中,以因此跨越总线22'传送该渲染的图像。此可通过将缓冲器14'放置在可由子系统40'访问的存储器、及提供缓冲器14'的地址给用于子系统40'的该驱动器软件来加以促成。或者,将会变得明显,该帧可在一 个缓冲器中被渲染,并由直接存储器访问(等等)而传送跨越总线22'。

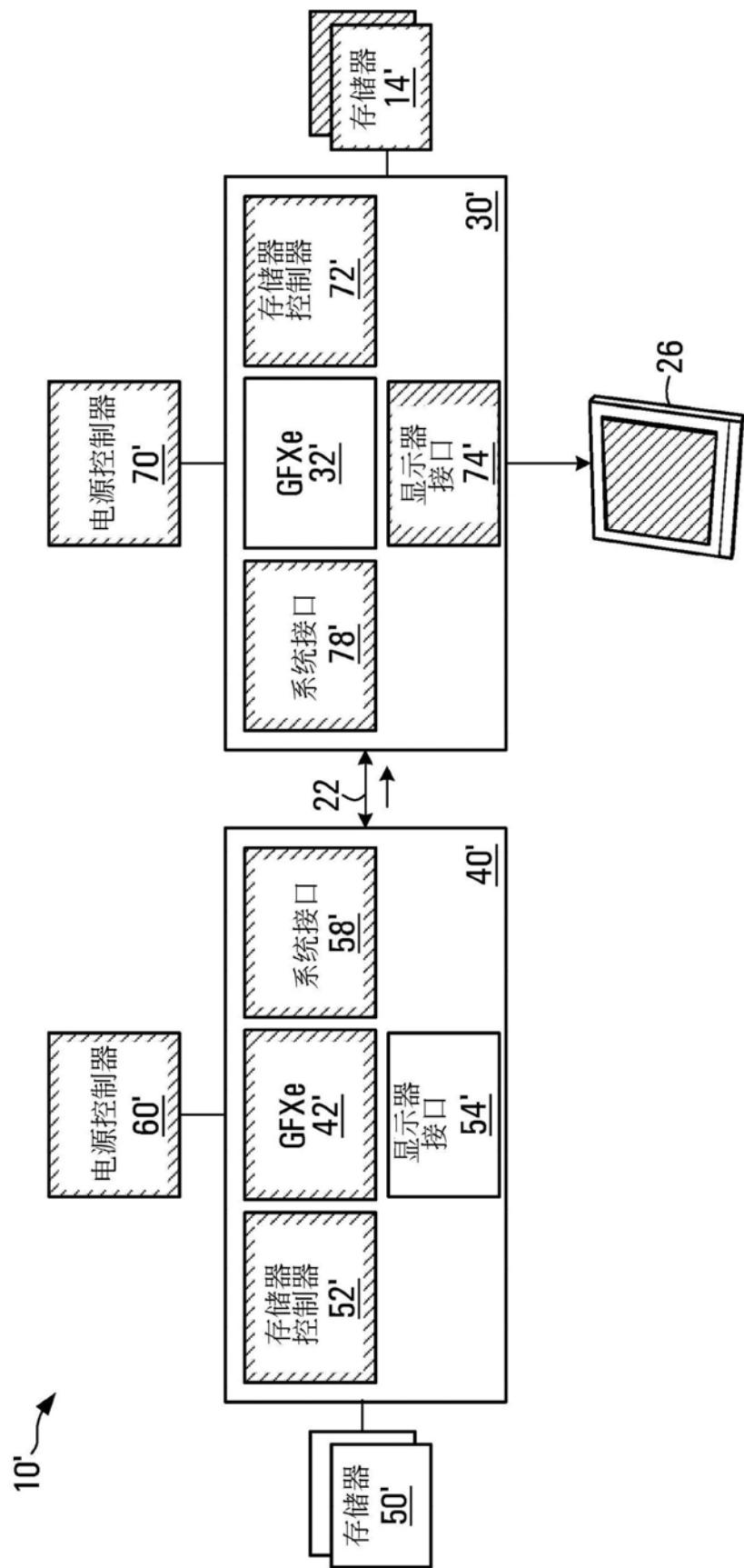

[0085] 并且,用于图形子系统30'的驱动器进一步组构以使图形子系统30'的显示器接口74'采样存储器14'中的该帧缓冲器,以将由存储器14'中的该帧缓冲器内的图形子系统40'所渲染的图像呈现在互连的显示器26'上。同时,用于图形子系统30'的驱动器可引导图形子系统30'的图形引擎32'维持实质的休眠或闲置。此操作模式是示意地显示在图11A中,其中,仅图形子系统40'和图形子系统30'的作用的方框划有斜线。

[0086] 将为明显的,在图11A的实施例中,没有使用存储器50'和显示器接口54'。像这样,这些功能方框可从子系统40'消除,以允许成本降低。该结果的子系统40'不需包含显示器接口,并且将缺少界定帧缓冲器本地至子系统40'的存储器。制造这种图形子系统可能是有利的,因为子系统40'可被制造以补足由子系统30'所提供的功能。举例来说,子系统可提供有提供三维图形或视频译码能力的图形引擎42'。图形引擎32'可不包含这些能力。同时,由图形引擎32'所提供的二维图形能力不需要包含在子系统40'中。消费者接着可于需要额外功能时才附加图形子系统30'。

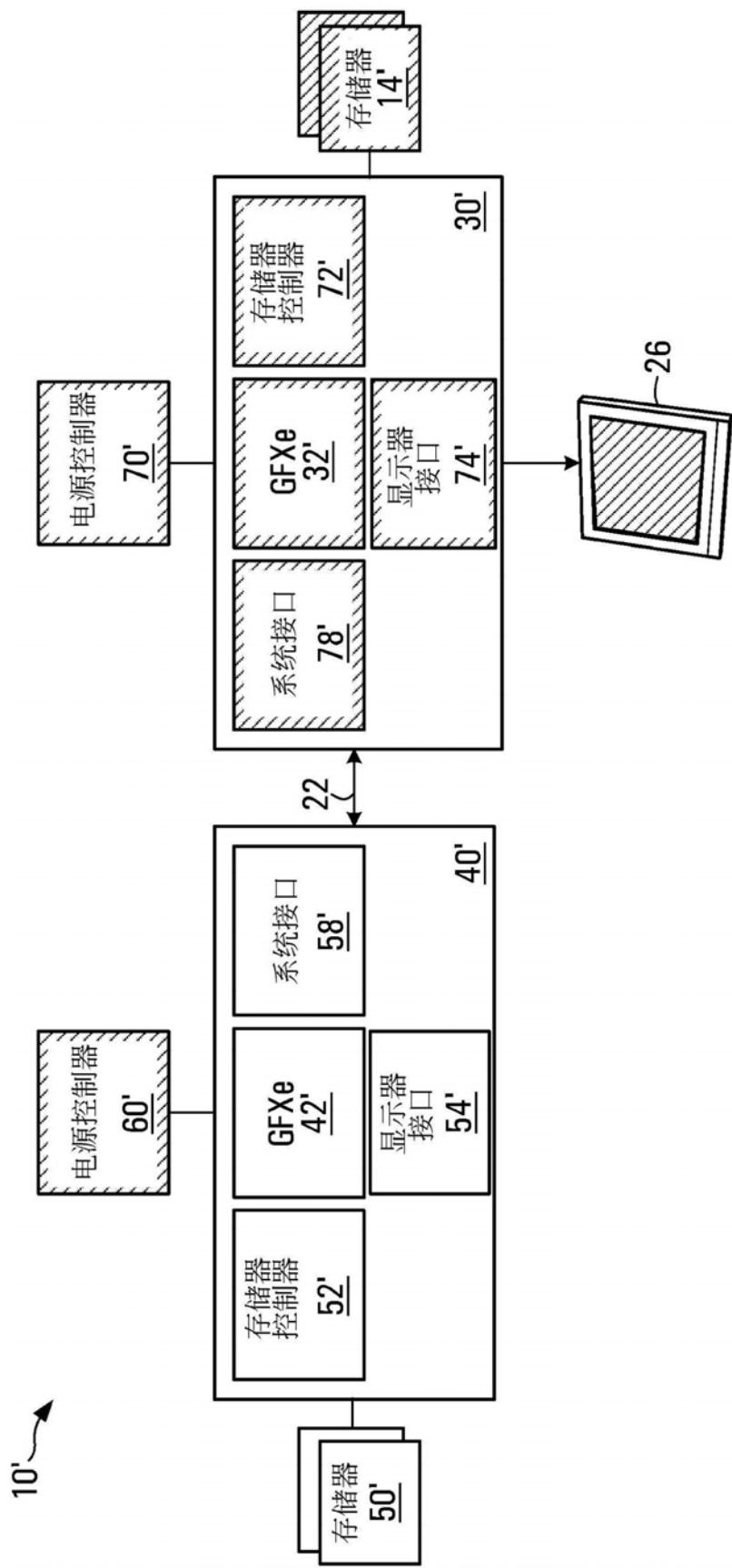

[0087] 当器件10'转换至、或假定为其低电源消耗模式时,执行方框S812'-S818'。广义言之,图形子系统40'是部分地或完全地失能,并且是置于其低电源消耗模式,而渲染是再次地由图形子系统30'所实施。这样做后,互连关联于图形子系统30'的任何显示器可在方框S812'中致能,而实体地连接至图形子系统40'的任何显示器则可在方框S814'中逻辑地失能。接下来,控制图形子系统30'的操作的驱动器软件再次地被组构,以使图形子系统30'渲染存储器14'中的图像。显示器接口74'继续采样存储器14',以将图像呈现在与端口78'互连的显示器26'上。同样的,处理器12'首先提供适当的讯号至电源控制器60'(方框S818'),以将图形子系统40'置于其低电源状态。以其最简单的形式,电源控制器(未显示)断开至图形子系统40'的电源、或将图形子系统40'置于较低电源睡眠模式。再次地,在此较低电源消耗模式中,电压被节流(throttled),和/或所有或部分的图形子系统40'的电源下降和/或由图形子系统40'所使用的选择的时钟减慢。具体言之,图形子系统40'的图形引擎42'维持闲置或实质地闲置(例如,其可被减慢、失能或降低电源)。此操作模式是示

意地绘示在图11B中,其中,仅适配器 40' 和图形子系统30' 的作用的功能方框划有斜线。该不作用/闲置的功 能方框可完全地失能、或操作在降低的电压或时钟速度。

[0088] 选择性地,一部分的图形子系统30' 可于图形引擎32' 没有使用时失 能。在图形子系统40' 负责渲染图像的任何时刻,此可通过将图形引擎 32' 和其它组件置于一个或多个电压岛(该电压岛可通过GPIO或类似 电路来加以失能) 来加以促成。

[0089] 其它的变化也应是明显的。举例来说,在图11A中所绘示的高电 源模式中,图形子系统30' 和图形子系统40' 两者均可渲染至存储器14' 或存储器50'。以这种方式,该两个图形子系统30' 和40' 可和谐地操作,每一者渲染存储器14' 中交替的图像或渲染存储器14' 中每一帧的交替 部分(例如,扫描线)。

[0090] 在其它实施例中,额外的显示器可连接至图形子系统30' 和40' ,以 允许同时使用以高电源消耗模式操作的多重显示器,如上述。以这种 方式,显示器接口54' 可使用来驱动第二显示器。在转换至较低电源消 耗模式后,器件10' 可组构为如图11B所绘示的操作。

[0091] 类似地,器件10' (或10) 可包含连接至总线22' (或22) 的多重 额外的图形子系统,所有这些图形子系统均可作用在该高电源消耗模 式,并且可通过图形子系统30' 的显示器接口74' 渲染图形。在转换至该 较低电源消耗模式后,这些可被失能,而渲染可留给图形子系统30' 的 图形引擎32' 。

[0092] 在图12所绘示的另一个实施例中,计算器件10' 可包含直接存储 器访问 (DMA) 控制器90。DMA控制器90可将数据从存储器50' 传 送至存储器14'。以这种方式,在较高电源消耗模式的器件10' 中,图形 子系统40' 可渲染图像至存储器50'。这些渲染的图像可接着由 DMA控 制器90传送至存储器14' 中的帧缓冲器。DMA控制器90' 可形成部分 的图形子系统 30' 或40' (例如图形引擎32' 或42'的DMA引擎),或为 置放于计算器件10' 中。数据可从存储器50' 经由跨越总线20' 或直接传 送至存储器14'。显示器接口74' 将继续如上述的操作,以 采样存储器 14' 中的帧缓冲器,以将该渲染的图像呈现在显示器26' 上。再次地,以 其较高电源消耗模式操作的图10的器件10' 的作用方框在图12中划有 斜线。

[0093] 当然,上述的实施例只是用来显示,而决不是用来限制的。实现 本发明的该描述的实施例可接受许多形式的修正、部件的配置、操作 的细节或顺序。而本发明意欲将所有这种修正涵盖在其范围中,如权 利要求书所界定的。

图1

图2

图3

图4

图5A

图5B

图6A

图6B

图6C

图7

图8

图10

图11A

图11B

图12