(19) 대한민국특허청(KR)

(12) 등록특허공보(B1)

(45) 공고일자 2010년11월05일

(11) 등록번호 10-0992065

(24) 등록일자 2010년10월29일

(51) Int. Cl.

*HO4N 5/217* (2006.01) *HO4N 5/335* (2006.01)

*HO4N 5/213* (2006.01) *HO1L 27/146* (2006.01)

(21) 출원번호 10-2008-0035522

(22) 출원일자 2008년04월17일

심사청구일자 2008년06월02일

(65) 공개번호 10-2008-0096391

(43) 공개일자 2008년10월30일

(30) 우선권주장

JP-P-2007-00117562 2007년04월26일 일본(JP)

(56) 선행기술조사문현

JP2006093816 A

JP2004165467 A

JP2006319951 A

JP2007104241 A

전체 청구항 수 : 총 2 항

심사관 : 강철수

(54) 활상장치

### (57) 요 약

활상장치는 행 방향 및 열 방향으로 배열된 복수의 광전변환부와, 상기 복수의 광전변환부의 (n-1)번째 행(단, n은 2이상의 정수)으로부터 판독한 신호를 기억하는 제 1의 기억부와, 상기 복수의 광전변환부의 n번째 행으로부터 판독한 신호를 기억하는 제 2의 기억부를 포함하는 활상소자와, 상기 활상소자를 제어하는 제어부를 구비한다. 상기 제어부는, 상기 제 1의 기억부에 기억된 (n-1)번째 행의 신호를 상기 제 1의 기억부로부터 판독하는 기간에 상기 활상소자 내에서 발생한 소정의 구동 펄스의 레벨이 변화할 때, 상기 제 1의 기억부에 기억된 (n-1)번째 행의 신호를 상기 제 1의 기억부로부터 출력하지 않도록 제어한다.

대 표 도 - 도1

## 특허청구의 범위

### 청구항 1

촬상장치로서,

행 방향 및 열 방향으로 배열된 복수의 광전변환부와, 상기 복수의 광전변환부로부터 수직 방향으로 신호를 판독하는 수직주사회로와, 상기 수직주사회로에 의해 판독된 신호를 수평 방향으로 판독하는 수평주사회로를 가지는 촬상소자; 및

상기 촬상소자를 구동하는 구동 펠스의 에지 부분 근방에서 상기 수평주사회로에 의한 수평 주사를 위한 주사 신호의 출력을 정지하도록 제어하는 제어부를 포함하는 것을 특징으로 하는 촬상장치.

### 청구항 2

제1항에 있어서,

상기 촬상소자에서 출력된 신호를 디지털 신호로 변환하는 A/D 변환기; 및

상기 디지털 신호를 처리하는 디지털 신호 처리부를 더 포함하고,

상기 제어부는 상기 수평 주사를 위한 주사 신호가 정지될 때 상기 A/D 변환기에 의해 변환된 디지털 신호가 상기 디지털 신호 처리부에 입력되지 않도록 제어하는 것을 특징으로 하는 촬상장치.

### 청구항 3

삭제

### 청구항 4

삭제

### 청구항 5

삭제

## 명세서

### 발명의 상세한 설명

#### 기술 분야

[0001] 본 발명은, 디지털 카메라 등의 촬상장치 및 그 제어방법에 관한 것이다.

#### 배경 기술

[0002] 종래로부터, X-Y 어드레스식의 촬상소자로서, CMOS 이미지 센서가 이용되고 있다(예를 들면, "IEEE Transactions on Electron Devices", Vol.41, pp. 452~453, 1994 참조). CMOS 이미지 센서는, 높은 신호 대 잡음비 및 저소비 전력을 특징으로 하고, 또한 그 주변회로를 온 칩화할 수 있는 등의 이점이 있다. 이러한 CMOS 이미지 센서를 사용했을 경우에, 화소의 1행분으로부터 출력된 신호를 전송 용량까지 판독하는 동작과, 전송용량으로부터 촬상소자 외부로 신호를 출력하는 수평주사기간을 중복시킨다. 이러한 동작을 통해서, 촬상소자로부터의 판독시간을 단축시키는 촬상소자 및 그 판독방법이 개시되어 있다(일本国 공개특허공보 특개2001-45375호 참조).

[0003] 그렇지만, 일본국 공개특허공보 특개2001-45375호에 개시된 판독방법에 따르면, 촬상소자에 인가되는 구동펠스의 영향으로 인해, 전송용량에 기억된 신호 또는 수평 출력선에 있어서의 출력신호에 노이즈가 발생하는 문제가 있다.

#### 발명의 내용

### 해결 하고자하는 과제

[0004] 본 발명은, 상기의 문제점을 감안하여 이루어진 것으로서, 활상소자에 인가되는 구동펄스가 원인이 되는 노이즈를 방지하는 동시에, 활상소자로부터의 판독시간을 단축시키는 것을 목적으로 한다.

### 과제 해결수단

[0005] 본 발명의 제 1의 측면은, 행 방향 및 열 방향으로 배열된 복수의 광전변환부들과, 상기 복수의 광전변환부들의 (n-1)번째 행(단, n은 2이상의 정수)으로부터 판독한 신호를 기억하는 제 1의 기억부와, 상기 복수의 광전변환부들의 n번째 행으로부터 판독한 신호를 기억하는 제 2의 기억부를 포함하는 활상소자와; 상기 활상소자를 제어하는 제어부를 구비하고, 상기 제어부는, 상기 제 1의 기억부에 기억된 (n-1)번째 행의 신호를 상기 제 1의 기억부로부터 판독하는 기간에 상기 활상소자 내에서 발생한 소정의 구동 펄스의 레벨이 변화할 때, 상기 제 1의 기억부에 기억된 (n-1)번째 행의 신호를 상기 제 1의 기억부로부터 출력하지 않도록 제어하는 것을 특징으로 하는 활상장치를 지향한다.

[0006] 본 발명의 제 2의 측면은, 행 방향 및 열 방향으로 배열된 복수의 광전변환부들과, 상기 복수의 광전변환부들의 (n-1)번째 행(단, n은 2이상의 정수)으로부터 판독한 신호를 기억하는 제 1의 기억부와, 상기 복수의 광전변환부들의 n번째 행으로부터 판독한 신호를 기억하는 제 2의 기억부를 구비하는 활상소자의 제어방법으로서, 상기 제 1의 기억부에 기억된 (n-1)번째 행의 신호를 상기 제 1의 기억부로부터 판독하는 기간에 상기 활상소자 내에서 발생한 소정의 구동 펄스의 레벨이 변화할 때, 상기 제 1의 기억부에 기억된 (n-1)번째 행의 신호를 상기 제 1의 기억부로부터 출력하지 않도록 제어하는 제어 스텝을 포함한 것을 특징으로 하는 활상장치의 제어방법을 지향한다.

### 효과

[0007] 본 발명에 의하면, 활상소자에 인가되는 구동 펄스가 원인이 되는 노이즈를 방지하는 동시에, 활상소자로부터의 판독시간을 단축시킬 수 있다.

[0008] 본 발명의 그 외의 특징들은 (첨부된 도면을 참조하면서) 이하의 예시적인 실시 예의 설명으로부터 밝혀질 것이다.

### 발명의 실시를 위한 구체적인 내용

[0009] 이하, 본 발명의 바람직한 실시 예에 따른 활상장치 및 그 제어방법에 대해서, 도면을 참조해서 상세히 설명한다.

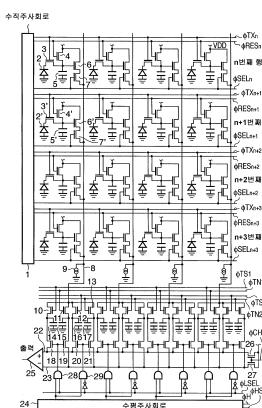

[0010] 도 1은, 본 발명의 바람직한 실시 예에 따른 활상소자의 구성을 나타내는 도면이다.

[0011] 도 1에 있어서, 참조번호 1은 수직주사회로이고, 참조번호 2는 피사체 상을 광전 변환하기 위한 포토다이오드 등의 광전변환소자이고, 참조번호 3은 광전변환소자(2)에 의해 생성된 전하를 후술하는 플로팅 디퓨전 앰프(floating diffusion amplifier)에 포함한 축적 용량(5)에 전송하기 위한 전송 스위치다. 참조번호 4는 광전변환소자(2), 축적 용량(5) 등에 축적되어 있는 불필요한 전하를 클리어(clear)하는 리셋 스위치다. 참조번호 6은 축적 용량(5)에 축적된 신호 전하를 증폭해 전압으로 변환하는 소스 팔로우 앰프(source follower amplifier)이고, 참조번호 7은 소스 팔로우 앰프(6)의 출력단자를 수직 출력선(8)에 접속하는 행 선택 스위치다. 상술한 플로팅 디퓨전 앰프는 리셋 스위치(4), 축적용량(5), 및 소스 팔로우 앰프(6)로 구성되어 있다. 참조번호 9는 행 선택 스위치(7)에 의해 선택된 행의 소스 팔로우 앰프(6)를 구동하기 위한 부하 전류원이다. 참조번호 10, 11, 12, 13은 수직 출력선(8)에 출력된 신호들을 제 1 및 제 2의 기억부로서의 역할을 하는 전송용량 14, 15, 16, 17에, 각각 전송하기 위한 전송 게이트다. 참조번호 18 및 20은 전송 용량 14 및 16에 기억된 신호들을 수평 판독선 22에 출력하는데 이용되는 판독 스위치다. 한편, 참조번호 19 및 21은 전송 용량 15, 17에 기억된 신호들을 수평 판독선 23에 출력하는데 이용되는 판독 스위치다. 참조번호 24는 전송 용량 14, 15, 16, 17로부터 수평 판독선 22, 23에 신호들을 순차 출력하기 위한 구동수단으로서의 역할을 하는 수평주사회로다. 참조번호 25는 수평 판독선 22에 출력된 신호와 수평 판독선 23에 출력된 신호와의 차를 활상소자의 외부에 출력하는 출력 앰프다. 참조번호 26 및 27은, 수평 판독선 22, 23을, 소정전압으로 리셋하기 위한 리셋 스위치다. 참조번호 28 및 29는, 수평주사회로(24)에 접속된 AND 게이트다. 활상장치는, 도 3을 참조하여 후술하는 시스템 제어 CPU(111)를 구비하고, 이 활상장치는 시스템 제어 CPU(111)를 이용해 활상소자를 제어한다. 또한, 도 1에 있어서, 설명의 사정상, 다른 화소의 각 구성소자의 참조번호에 부호 '(')을 부가하고 있다. 다시 말해, 참조번호

2'은 광전변환소자, 참조번호 3'은 전송 스위치, 참조번호 4'은 리셋 스위치, 참조번호 5'은 축적 용량, 참조번호 6'은 소스 팔로우 앰프, 참조번호 7'은 행 선택 스위치에 각각 대응한다.

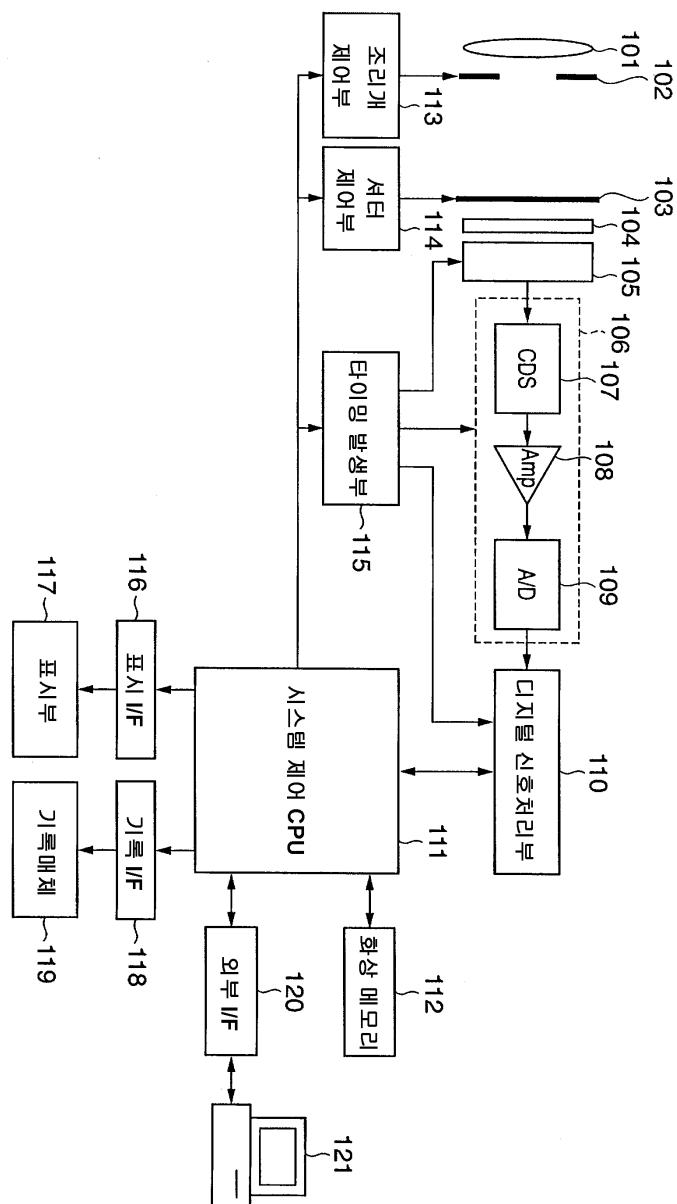

[0012] 도 6은, 종래의 활상소자의 구동 타이밍을 도시한 도면이다. 또한, 도 6에서는, 도 1에 나타내는 활상소자와 구성이 동일한 활상소자를 동작시키고 있다.

[0013] 시각 t1에서는, 수평구동신호 HD,  $\phi HST$ , 및  $\phi LSEL$ 이 로우 레벨(이하, "로우"라고 한다.)로 된다.  $\phi HST$  신호가 로우 레벨에서 하이 레벨(이하, "하이"라고 한다.)로 반전할 때, 수평 판독선 23에 판독되어야 할 열이 각 수평주사 클록  $\phi H$ 의 리딩 에지(leading edge)에서 시프트한다. t1~t9까지의 1행분의 신호를 판독하는 수평주사기간에서는,  $\phi LSEL$ 이 로우이기 때문에, AND 게이트 28의 출력은 로우가 되고, AND 게이트 29의 출력은 하이가 된다. 이것이 의해, 판독 스위치 18, 19가 오프되고, 하이 AND 게이트 29에 대응하는 판독 스위치 20, 21은 온 된다. 따라서, 수평주사회로(24)에 입력되는 수평주사 클럭  $\phi H$ 에 동기하여, 전송용량(16)에 기억된 신호가 판독 스위치(20)를 통해서 수평 판독선 22에 순차 판독된다. 또한, 전송 용량(17)에 기억된 신호가, 판독 스위치(21)를 거쳐서 수평 판독선 23에 순차 판독된다. 이때, 전송 용량 14, 15에 기억된 신호는, 판독 스위치 18, 19가 오프되어 있기 때문에, 판독되지 않는다. 그리고, 출력 앰프(25)는, 수평 판독선 22와 수평 판독선 23과의 차분 신호를 외부에 출력하는 출력 동작을 행한다. 이때, 출력되는 신호는 (n-1)번째 행(n은 2이상의 정수; 이하도 동일하게 적용)의 신호가 된다.

[0014] 다음에, 상술한 외부에의 신호의 출력과 동시에 행해지는, n번째 행의 광전변환소자(2)에 축적된 신호 전하의 전송 용량에의 전송에 관하여 설명한다.

[0015] 우선, 시각 t2에서는,  $\phi SELn$ 이 하이가 되어서, 행 선택 스위치(7)가 온 되어, n번째 행의 화소 회로가 수직 출력선(8)에 접속된다. 마찬가지로,  $\phi RESn$ 이 하이가 되어서, 리셋 스위치(4)가 온 되어, 축적 용량(5)에 축적된 불필요한 전하가 클리어된다. 이때, 구동되는 리셋 스위치(4)의 개수는, 활상소자의 수평방향의 화소 수와 동일하다. 따라서, 리셋 스위치(4)를 구동하기 위한 펄스는, 다수의 리셋 스위치(4)의 게이트 용량을 구동하기에 충분한 전류를 흘려보낼 필요가 있다. 그렇지만, 활상소자 내에 그러한 큰 전류의 펄스가 존재하면, 활상소자에 포함된 회로에 있는 기생 용량이나 기생 저항 등에 의해, 활상소자의 기준전위와 접지전위가 불안정하게 되어, 출력 신호에 노이즈가 혼입한다. 이러한 현상은, 특히, 펄스의 에지(즉, 펄스가 변화할 때)에서 발생한다.

[0016] 시각 t3에서는,  $\phi RESn$ 이 로우가 되어서 리셋이 종료하는 동시에,  $\phi TN1$ 이 하이가 되어서, 전송 게이트(11)가 온 되고, n번째 행의 각 화소 회로에서 발생하는 노이즈 성분이 전송용량(15)에 기억된다. 여기에서, 구동 펄스  $\phi TN1$ 의 영향에 의해, (n-1)번째 행의 전송 용량(17)에 기억된 신호들, 또는, 수평 출력선에 있어서의 (n-1)번째 행의 출력 신호들에 노이즈가 혼입한다.

[0017] 시각 t4에서는,  $\phi TN1$ 이 로우가 되어서, 전송 게이트(11)가 오프되고, n번째 행의 각 화소 회로에서 발생하는 노이즈 성분은 전송 용량(15)에 기억되었다.

[0018] 시각 t5에서는,  $\phi TXn$ 이 하이가 되어서, n번째 행의 각 화소 회로의 전송 스위치(3)가 온 되고, 광전변환소자(2)에 축적된 신호 전하가, 축적 용량(5)에 전송된다.

[0019] 시각 t6에서는,  $\phi TS1$ 이 하이가 되어서, 전송 게이트(10)가 온 되어, 축적 용량(5)의 신호 전하가 소스 팔로우 앰프(6)에 의해 증폭되어 전압으로 변환되어, 전송 용량(14)에 기억된다. 여기에서, 구동 펄스  $\phi TS1$ 의 영향으로 의해, (n-1)번째 행의 전송용량(16)에 기억된 신호, 또는 수평 출력선에 있어서의 (n-1)번째 행의 출력 신호에 노이즈가 혼입한다.

[0020] 시각 t7에서는,  $\phi TS1$ 이 로우가 되어서, 전송 게이트(10)가 오프되고, 전송 용량(14)에의 기억을 종료한다.

[0021] 그 후에, n번째 행의 신호들은, 시각 t9로부터 개시되는 다음 수평주사기간에서, 출력 앰프(25)로부터 출력된다.

[0022] 이와 같이, n번째 행의 신호들의 전송 용량에의 기억과, (n-1)번째 행의 신호들의 출력(즉, 수평주사)을 동시에 행한다. 이것이 의해, 활상소자로부터의 판독 시간이 단축되지만, 시각 t3, 시각 t6 등에서 설명한 바와 같이, (n-1)번째 행의 전송 용량에 기억된 신호들, 또는 수평 출력선에 있어서의 (n-1)번째 행의 신호 출력에 노이즈가 혼입한다.

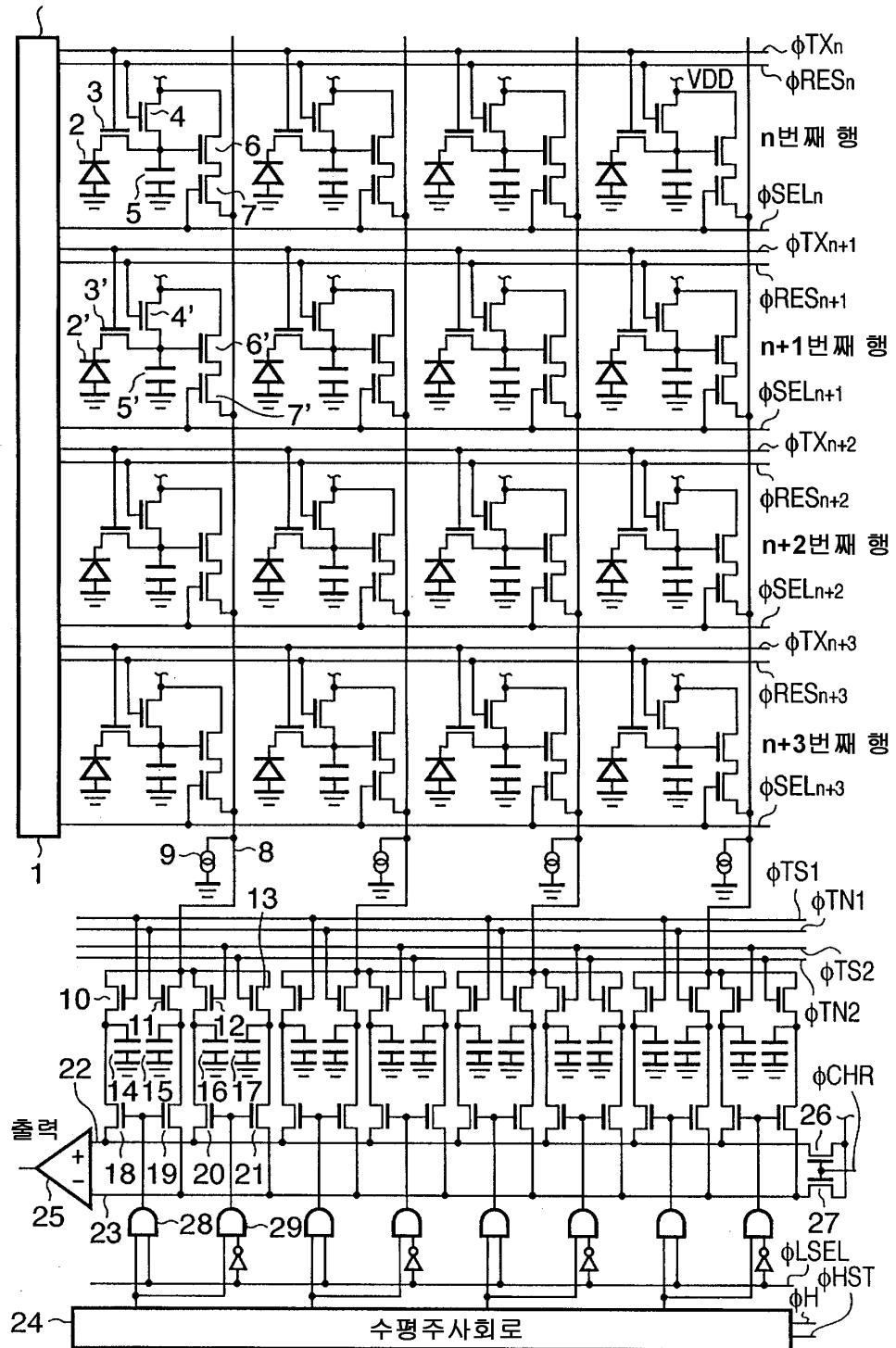

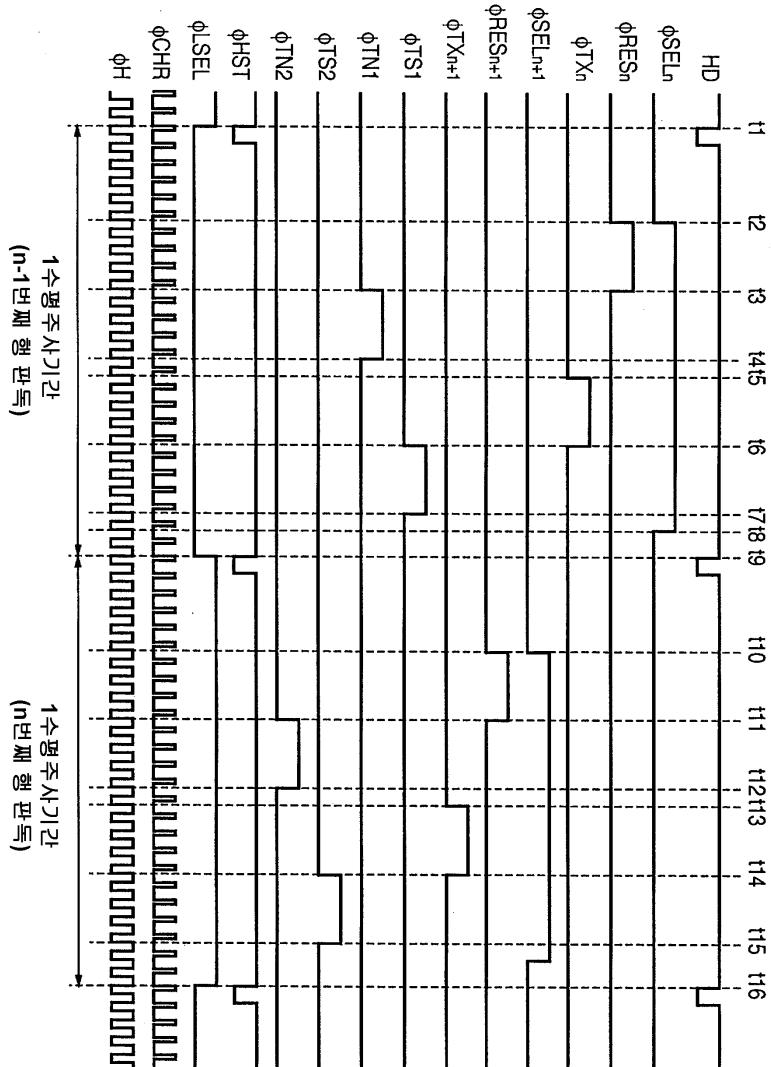

[0023] 도 2는, 본 발명의 바람직한 실시 예에 따른 활상소자의 구동 타이밍을 도시한 도면이다. 도 1 및 도 2를 이용해서 본 실시 예에 따른 활상소자의 동작을 설명한다.

- [0024] 시각 t1에서, 수평구동신호 HD,  $\phi$ HST, 및  $\phi$ LSEL가 로우가 된다. 이때,  $\phi$ HST 신호가 로우에서 하이로 반전하면, 각 수평주사를록  $\phi$ H의 리딩 에지에서 수평판독선 22 및 23에 판독되어야 하는 열이 시프트한다. t1~t9까지의 수평주사기간에서는,  $\phi$ LSEL이 로우이기 때문에, AND 게이트 28의 출력이 로우가 되고, AND 게이트 29의 출력이 하이가 된다. 이에 따라, 판독 스위치 18, 19는 오프되고, 하이 AND 게이트 29에 대응하는 판독 스위치 20, 21은 온 된다. 따라서, 수평주사회로(24)에 입력되는 수평주사 클록  $\phi$ H에 동기하여, 전송 용량(16)에 기억된 신호들이, 판독 스위치(20)를 거쳐서 수평 판독선 22에 순차 판독된다. 또한, 전송 용량(17)에 기억된 신호들이, 판독 스위치(21)를 거쳐서 수평 판독선 23에 순차 판독된다. 이때, 전송 용량 14 및 15에 기억된 신호들은, 판독 스위치 18 및 19가 오프되어 있기 때문에, 판독되지 않는다.

- [0025] 출력 앰프(25)는, 수평 판독선 22와 수평 판독선 23과의 사이의 차분 신호를 외부에 출력한다. 이때, 출력된 신호는 n-1번째 행의 신호가 된다. 본 실시 예에서는, 수평주사를록  $\phi$ H는, 도 2에 나타나 있는 바와 같이 후술하는 소정의 시간에서 선별된다.

- [0026] 다음에, 전술한 외부에의 신호의 출력과 동시에 행해지는, n번째 행의 광전변환소자(2)에 축적된 신호 전하의 전송 용량에의 전송에 관하여 설명한다.

- [0027] 우선, 시각 t2에서는,  $\phi$ SELn이 하이가 되어서, 행 선택 스위치(7)가 온 되어, n번째 행의 화소 회로가 수직 출력선(8)에 접속된다. 마찬가지로,  $\phi$ RESn이 하이가 되어서, 리셋 스위치(4)가 온 되어, 축적 용량(5)에 축적된 불필요한 전하가 클리어된다. 시각 t2에서는, 수평주사 클록  $\phi$ H가 로우인 채로 있다(즉, 수평주사 클록  $\phi$ H의 공급이 일시적으로 정지된다). 그 결과, 수평주사회로(24)의 동작이 일시적으로 정지되어, (n-1)번째 행의 신호의 출력도 정지한다.

- [0028] 시각 t3에서는,  $\phi$ RESn이 로우가 되어서 리셋이 종료하는 동시에,  $\phi$ TN1이 하이가 되어서, 전송 게이트(11)가 온 되고, n번째 행의 각 화소 회로에서 발생하는 노이즈 성분이 전송 용량(15)에 기억된다. 시각 t3에 있어서도, 수평주사 클록  $\phi$ H가 로우인 채로 있어, 수평주사회로(24)의 동작이 일시적으로 정지한다.

- [0029] 시각 t4에서는,  $\phi$ TN1이 로우가 되어서, 전송 게이트(11)가 오프되고, n번째 회소의 각 화소 회로에서 발생하는 노이즈 성분이 전송 용량(15)에 기억되는 것을 종료한다. 시각 t4에 있어서도, 수평주사 클록  $\phi$ H가 로우인 채로 있어, 수평주사회로(24)의 동작이 일시적으로 정지한다.

- [0030] 시각 t5에서는,  $\phi$ TXn이 하이가 되어서, n번째 행의 각 화소 회로의 전송 스위치(3)가 온 되고, 광전변환소자(2)에 축적된 신호 전하가, 축적 용량(5)에 전송된다.

- [0031] 시각 t6에서는,  $\phi$ TS1이 하이가 되어서, 전송 게이트(10)가 온 되고, 축적 용량(5)의 신호 전하가 소스 팔로우 앰프(6)에 의해 증폭되어 전압으로 변환되어서, 전송용량(14)에 기억된다. 시각 t6에 있어서도, 수평주사 클록  $\phi$ H가 로우인 채로 있어, 수평주사회로(24)의 동작이 일시적으로 정지한다.

- [0032] 시각 t7에서는,  $\phi$ TS1이 로우가 되어서, 전송 게이트(10)가 오프되어, 전송 용량(14)에의 기억을 종료한다. 시각 t7에 있어서도, 수평주사 클록  $\phi$ H가 로우인 채로 있어, 수평주사회로(24)의 동작이 일시적으로 정지한다.

- [0033] 그 후에, n번째 행의 신호들은, 시각 t9부터 개시되는 다음 수평주사기간에서, 출력 앰프(25)로부터 출력된다. 이때, 수평주사 클록  $\phi$ H는, 상술한 (n-1)번째 행의 신호 판독기간과 마찬가지로, 시각 t10, t11, t12, t14, t15에서 로우인 채로 있고, 수평주사회로(24)의 동작은 일시적으로 정지한다.

- [0034] 따라서, n번째 행의 전송 용량에의 기억과, (n-1)번째 행의 신호들의 출력 (즉, 수평주사)을 동시에 행함으로써, 활상소자로부터의 판독 시간이 단축된다. 또한, 노이즈의 원인이 되는 구동 펄스의 에지 부근에 있어서, 신호의 판독을 정지(즉, 수평주사 클록  $\phi$ H를 정지)함으로써, 노이즈가 억제되었던 신호를 출력할 수 있다.

- [0035] 본 실시 예에서는, 활상소자의 3종류의 구동 펄스의 에지에서, 수평주사 클록을 정지하고 있지만, 본 발명은 이것에 한정되지 않는다. 즉, 예를 들면, 노이즈의 원인이 될 수 있는 구동 펄스(즉, 활상소자에 인가되는 구동 펄스)의 에지에서 수평주사 클록  $\phi$ H를 로우인 채로 유지해서, 수평주사회로(24)의 동작을 일시적으로 정지시킬 수 있다.

- [0036] 또한, 본 실시 예에서는, 수평주사 클록  $\phi$ H가 로우인 기간을, 구동 펄스의 에지에 발생하는 신호 클록 기간이라고 하고 있지만, 본 발명은 이것에 한정되지 않는다. 예를 들면, 구동 펄스에 기인하는 노이즈가 복수 클록 기간에 흔입할 경우, 적어도 그 기간 동안, 수평주사 클록  $\phi$ H의 공급을 정지해도 된다.

- [0037] 또한, 본 실시 예와 같이, 수평주사 클록  $\Phi H$ 의 공급을 정지하는 기간이 있으면, 클록을 정지시킨 양만큼, 수평 주사 기간이 길어진다. 그렇지만, 그 클록을 정지시키는 기간은 매우 짧아서, 화소의 개수가 많고, 1수평주사기간이 긴 최근의 활상소자에서는, 대부분 무시할 수 있다.

- [0038] 다음에, 상기 실시 예의 활상장치 및 그 제어방법을 사용한 활상 시스템에 관하여 설명한다.

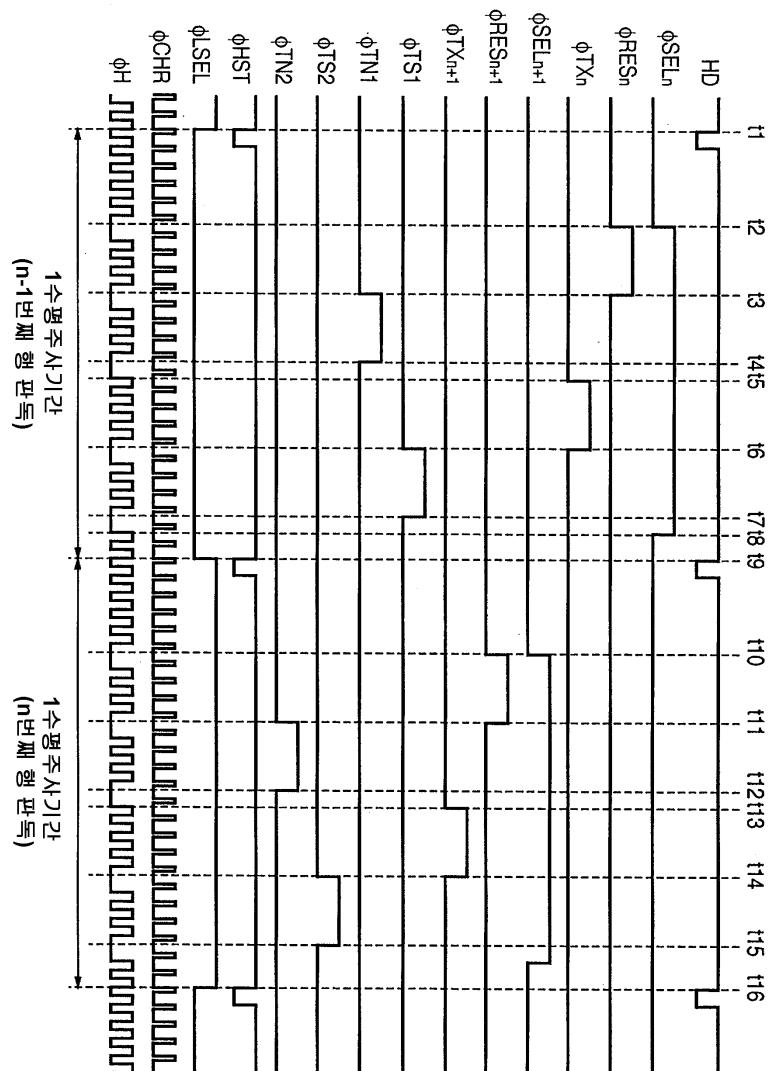

- [0039] 도 3은, 본 실시 예에 따른 활상장치로서의 디지털 스틸 카메라를 나타내는 블럭도다.

- [0040] 도 3에 있어서, 참조번호 101은 피사체의 광학상을 활상소자(105)에 결상시키는 렌즈이고, 참조번호 102는 렌즈(101)를 통과한 광량을 가변하도록 하기 위한 조리개이며, 이 조리개(102)는 조리개 제어부(113)에 의해 제어된다. 참조번호 103은 렌즈(101)에 의해 결상된 피사체 상의 빛이 활상소자(105)에 입사하는 것을 제어하는 메카니컬 셔터(mechanical shutter)이며, 이 셔터(103)는 셔터 제어부(114)에 의해 제어된다. 참조번호 104는 활상 소자(105)에 입사하는 빛의 광장 및 공간 주파수를 제한하는 광학 필터이며, 참조번호 105는 렌즈(101)에 의해 결상된 피사체 상을 화상 신호로서 캡처하는 활상소자(105)이다. 활상소자(105)에는, 도 1에 나타나 있는 바와 같이, 행 방향 및 열 방향으로 광전변환소자(2)를 각각 포함한 복수의 화소가 배치되어 있다. 참조번호 106은 활상소자(105)로부터 출력되는 화상 신호의 아날로그 처리와 아날로그-디지털 변환 처리를 행하는 아날로그 프론트 엔드(analog front-end)를 나타낸다. 아날로그 프론트 엔드(106)는, 노이즈를 제거하는 CDS 회로(107), 신호의 게인을 조정하는 앰프(108), 아날로그 신호를 디지털화하는 A/D 변환기(109)로 구성된다. 참조번호 110은 아날로그 프론트 엔드(106)로부터 출력된 디지털 화상 데이터에 대하여 각종의 보정을 행하거나 디지털 화상 데이터를 압축하거나 하는 디지털 신호 처리부다. 참조번호 115는 활상소자(105), 아날로그 프론트 엔드(106), 및 디지털 신호 처리부(110)에, 각종 타이밍 신호들을 출력하는 타이밍 발생부다. 참조번호 111은 각종 프로세스를 행하여 디지털 스틸 카메라 전체를 제어하는 시스템 제어 CPU이고, 참조번호 112는 화상 데이터를 일시적으로 기억하기 위한 화상 메모리다. 참조번호 116은 활영된 화상을 표시하기 위한 표시 인터페이스(표시 I/F)이고, 참조번호 117은 액정 디스플레이 등의 표시부다. 참조번호 118은 기록 매체에/로부터 기록/판독을 행하기 위한 기록 인터페이스부(기록 I/F)다. 참조번호 119는 화상 데이터의 기록/판독을 행하기 위한 반도체 메모리 등의 착탈 가능한 기록매체이고, 참조번호 120은 외부 컴퓨터(121) 등과 통신하기 위한 외부 인터페이스부(외부 I/F)다. 또한, 활상소자(105)는, 본 실시 예에 따른 활상소자이며, 또한 본 실시 예에 따른 구동 타이밍에서 구동된다.

- [0041] 다음에, 도 3에 나타낸 것과 같이 구성된 활영시의 활상 시스템의 동작에 관하여 설명한다.

- [0042] (도면에 나타내지 않은) 전원 스위치가 온 되면, 메인 전원이 온 된다. 다음에, 컨트롤계의 전원이 온 되고, 한 층 더, 아날로그 프론트 엔드(106) 등의 활상계 회로의 전원이 온 된다.

- [0043] 그리고, 노광을 제어하기 위해서, 시스템 제어 CPU(111)는, 조리개 제어부(113)를 거쳐서 조리개(102)를 개방하고, 또 셔터 제어부(114)를 거쳐서 메카니컬 셔터(103)를 개방한다. 활상소자(105)로부터 출력된 신호는 A/D 변환기에 의해 디지털 화상 데이터로 변환된 후, 디지털 신호 처리부(110)에 입력된다. 그 데이터에 의거하여 노출의 연산을 시스템 제어 CPU(111)에서 행한다.

- [0044] 이 측광을 행한 결과에 의거해, 밝기를 판단하고, 그 판단결과에 따라 시스템 제어 CPU(111)는 조리개(102)를 제어한다.

- [0045] 다음에, 활상소자(105)로부터 출력된 신호로부터 고주파성분을 추출하고, 피사체까지의 거리를 시스템 제어 CPU(111)가 산출한다. 그 후에, 렌즈(101)를 구동하고, 렌즈를 포커스했는지 아닌지를 판단한다. 렌즈를 포커스하지 않는다고 판단했을 때, 다시 한 번 렌즈(101)를 구동한다. 이와 같이, 초점조정처리를 행한다.

- [0046] 그리고, 포커스를 확인한 후에는, 활상소자(105)의 전자 셔터 기능을 이용하여, 본 노광의 개시 및 노광의 종료를 행한다. 또한, 본 노광의 개시와 종료를 메카니컬 셔터(103)의 개폐로 실시해도 된다는 점에 유념한다. 그 후에, 각 행마다 화상 신호를 순차 출력한다. 활상소자(105)로부터 출력된 화상 신호에 대해서는, 아날로그 프론트 엔드(106)에 의해 상관 2중 샘플링 등의 노이즈 제거, 증폭, A/D 변환이 행해진다. 그리고, 디지털화된 화상 신호가, 디지털 신호 처리부(110)를 거쳐서 시스템 제어 CPU(111)에 의해 화상 메모리(112)에 기록된다. 그 후에, 화상 메모리(112)에 기억된 화상 데이터는, 시스템 제어 CPU(111)의 제어에 의해, 기록 인터페이스부(118)를 거쳐서 착탈 가능한 반도체 메모리 등인 기록 매체(119)에 기록된다. 또한, 활상된 화상 데이터는, 표시 인터페이스부(116)를 거쳐서 액정 디스플레이 등의 표시부(117)에 표시된다. 또는, 화상 데이터는 외부 인터페이스부(120)를 거쳐서 컴퓨터(121) 등에 직접 입력되고, 그 후에 화상을 가공해도 된다.

- [0047] 다음에, 본 실시 예에 따른 활상장치 및 그 제어방법을 도 3에 나타내는 활상 시스템에 적용했을 때의 동작에 관해서, 도 4를 참조하여 설명한다.

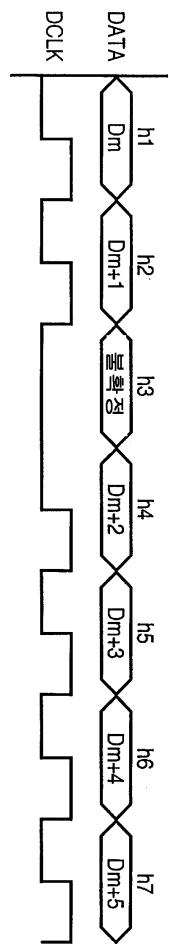

- [0048] 도 4는, 디지털 화상 데이터 DATA와 클록 펄스 DCLK과의 관계를 나타내는 타이밍도다. 디지털 화상 데이터 DATA는, 아날로그 프론트 엔드(106)로부터 출력되어, 디지털 신호 처리부(110)에 입력되는 신호다. 클록 펄스 DCLK은, 디지털 화상 데이터 DATA에 동기하여, 디지털 화상 데이터 DATA를 디지털 신호 처리부(110)에 입력하기 위한 타이밍을 규정하는 동기신호다. 또한, 클록 펄스 DCLK는, 도 3의 타이밍 발생부(115)에 의해 공급된다는 점에 유념한다.

- [0049] 도 4에 있어서, h3의 타이밍에서 출력되는 디지털 화상 데이터 DATA는, 전술한 바와 같이 수평주사 클록  $\phi_H$ 의 공급이 정지했을 때의 신호에 해당하고, 실제로, 화상 신호로서는 불필요한 신호이며, 그 출력값은 일정하지 않다. 이때, 클록펄스 DCLK을 로우인 채로 유지해서, 그 공급을 정지시킴으로써, 디지털 신호 처리부(110)에서 불필요한 신호를 수취하는 일이 없어, 화상 메모리(112)의 공간을 절약할 수 있다. 또한, 불필요한 신호를 나중에 삭제하는 등의 여분의 처리를 더 이상 행할 필요도 없다.

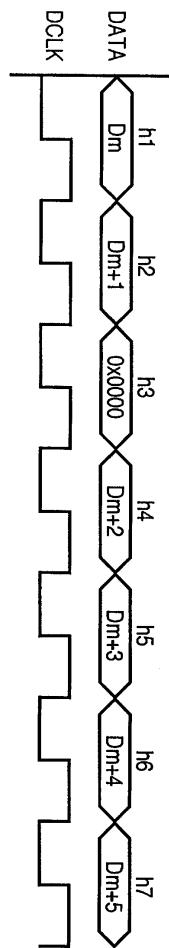

- [0050] 도 5는, 디지털 화상 데이터 DATA와 클록 펄스 DCLK과의 관계를 나타내는 타이밍 도다.

- [0051] 도 5에 있어서, h3의 타이밍에서 출력되는 디지털 화상 데이터 DATA는, 전술한 바와 같이, 수평주사 클록  $\phi_H$ 의 공급이 정지했을 때의 신호에 해당하고, 실제로, 화상 신호로서는 불필요한 신호다. 여기에서, 도 5에 나타내는 방법에서는, 아날로그 프론트 엔드(106)에 있어서, 그 디지털 화상 데이터 값을 미리 정해진 규정 값, 예를 들면 16진수의 0000(0x0000)로 고정한다. 여기에서는, 디지털 신호 처리부(110)는, 상기의 규정 값(예를 들면 0x0000)이 입력되었을 경우, 디지털 화상 데이터 값을 수취하지 않도록 구성되어 있다. 그 때문에, 디지털 신호 처리부(110)에서 불필요한 신호를 수취하는 일이 없어, 화상 메모리의 공간을 절약할 수 있다. 또한, 이 불필요한 신호를 나중에 삭제하는 등의 여분의 처리를 더 이상 행할 필요도 없다. 또한, 수평주사 클록  $\phi_H$ 의 공급을 정지시켰을 때의 출력 신호에 해당하는 디지털 화상 데이터의 값을 0x0000으로서 설명했지만, 다른 값을 사용해도 된다는 점에 유념해야 한다.

- [0052] 또한, 본 실시 예에 따른 활상 시스템에서는, 타이밍 발생부(115)가 독립적으로 구성되어 있지만, 활상소자(105)의 반도체 기판 위에 타이밍 발생부(115)를 형성하여, 활상소자(105)와 이 타이밍 발생부(115)를 일체화해도 된다. 마찬가지로, 타이밍 발생부(115)를, 아날로그 프론트 엔드(106) 또는 디지털 신호 처리부(110)와 일체화해도 된다.

- [0053] 본 발명은, 예시적인 실시 예를 참조하면서 설명되었지만, 본 발명은 이들 예시적인 실시 예에 한정되는 것이 아니다. 이하의 특허청구범위는 본 발명의 범주를 벗어나지 않고 다양한 변경 및 변형이 가능하다.

- 도면의 간단한 설명**

- [0054] 도 1은 본 발명의 바람직한 실시 예에 따른 활상소자의 구성을 도시한 도면이다.

- [0055] 도 2는 본 발명의 바람직한 실시 예에 따른 활상소자의 구동 타이밍을 도시한 도면이다.

- [0056] 도 3은 본 발명의 실시 예에 따른 활상 시스템을 디지털 스틸 카메라에 적용했을 경우를 나타내는 블럭도다.

- [0057] 도 4는 디지털 화상 데이터 DATA와 클록 펄스 DCLK과의 관계를 나타내는 타이밍도다.

- [0058] 도 5는 디지털 화상 데이터 DATA와 클록 펄스 DCLK과의 관계를 나타내는 또 다른 타이밍도다.

- [0059] 도 6은 종래의 활상소자의 구동 타이밍을 도시한 도면이다.

## 도면

## 도면1

수직주사회로

도면2

도면3

도면4

도면5

도면6

## 【심사관 직권보정사항】

## 【직권보정 1】

【보정항목】 청구범위

【보정세부항목】 청구항 제2항

## 【변경전】

A/D변환부, 디지털 신호 처리기

## 【변경후】

A/D변환기, 디지털 신호 처리부