등록특허 10-2447508

**(19) 대한민국특허청(KR)**

**(12) 등록특허공보(B1)**

**(45) 공고일자** 2022년09월27일

**(11) 등록번호** 10-2447508

**(24) 등록일자** 2022년09월21일

- (51) 국제특허분류(Int. Cl.)

*HO4N 19/423* (2014.01) *HO4N 19/105* (2014.01)

*HO4N 19/122* (2014.01) *HO4N 19/159* (2014.01)

*HO4N 19/176* (2014.01) *HO4N 19/44* (2014.01)

*HO4N 19/51* (2014.01) *HO4N 19/593* (2014.01)

*HO4N 19/82* (2014.01) *HO4N 19/96* (2014.01)

- (52) CPC특허분류

*HO4N 19/423* (2015.01)

*HO4N 19/105* (2015.01)

- (21) 출원번호 10-2021-7020284

- (22) 출원일자(국제) 2020년01월13일

심사청구일자 2021년06월29일

- (85) 번역문제출일자 2021년06월29일

- (65) 공개번호 10-2021-0089785

- (43) 공개일자 2021년07월16일

- (86) 국제출원번호 PCT/US2020/013355

- (87) 국제공개번호 WO 2020/146882

국제공개일자 2020년07월16일

- (30) 우선권주장

62/791,862 2019년01월13일 미국(US)

16/502,822 2019년07월03일 미국(US)

## (56) 선행기술조사문헌

Xiaozhong Xu et al, CE8-related: CPR mode with local search range optimization, MPEG 124th, m44321 version 1 (2018.09.25.) 1부.\*

Xiaozhong Xu et al, CE8: CPR reference memory reuse without increasing memory requirement(CE8.1.2a and CE8.1.2d), JVET of ITU-T and ISO/IEC, JVET-M0407 version 2 (2019.01.10.) 1부.\*

\*는 심사관에 의하여 인용된 문헌

전체 청구항 수 : 총 20 항

심사관 : 황수진

(54) 발명의 명칭 **인트라 빅처 블록 보상을 위한 참조 샘플 메모리 재사용 방법 및 장치****(57) 요약**

본 방법은 현재 블록에 대한 참조 블록이 현재 블록의 CTU와 상이한 코딩 트리 유닛(CTU)에 위치하는지를 결정하는 단계를 포함한다. 참조 블록이 상이한 CTU에 위치하는 경우, 본 방법은 현재 블록의 CTU 및 메모리가 동일한 크기를 갖는지를 결정하는 단계를 포함한다. 현재 블록의 CTU 및 참조 샘플 메모리가 동일한 크기를 갖는다면,

(뒷면에 계속)

**대 표 도**

본 방법은 (i) 상이한 CTU 내의 제2 영역과 병치되는 현재 블록의 CTU 내의 제1 영역을 결정하는 단계; (ii) 제1 영역의 디코딩 상태에 기초하여, 참조 블록에 대한 메모리의 메모리 위치가 이용가능한지를 결정하는 단계; 및 (iii) 참조 블록에 대한 메모리 위치가 이용가능한 경우, 메모리 위치로부터, 하나 이상의 샘플을 검색하여 현재 블록을 디코딩하는 단계를 포함한다.

(52) CPC특허분류

*H04N 19/122* (2015.01)

*H04N 19/159* (2015.01)

*H04N 19/176* (2015.01)

*H04N 19/45* (2015.01)

*H04N 19/51* (2015.01)

*H04N 19/593* (2015.01)

*H04N 19/82* (2015.01)

*H04N 19/96* (2015.01)

---

## 명세서

### 청구범위

#### 청구항 1

디코더에 대한 비디오 디코딩 방법으로서,

코딩된 비디오 비트스트림을 수신하는 단계;

현재 블록에 대한 참조 블록이 상기 현재 블록의 CTU와 상이한 코딩 트리 유닛(CTU)에 위치하는지를 결정하는 단계- 상기 참조 블록과 현재 블록은 상기 코딩된 비디오 비트스트림의 일부인 띵처에 위치함 -;

상기 참조 블록이 상기 상이한 CTU에 위치한다는 결정에 응답하여:

(i) 상기 상이한 CTU 내의 제2 영역과 병치되는 상기 현재 블록의 상기 CTU 내의 제1 영역을 결정하는 단계- 상기 제1 영역 및 상기 제2 영역은 상기 현재 블록의 상기 CTU 및 상기 참조 블록의 상기 상이한 CTU에서 동일한 위치를 가짐 -;

(ii) 상기 제1 영역의 디코딩 상태에 기초하여, 상기 참조 블록에 대한 참조 샘플 메모리의 메모리 위치가 이용가능한지를 결정하는 단계;

(iii) 상기 참조 블록에 대한 상기 메모리 위치가 이용가능하다는 결정에 응답하여, 상기 참조 블록에 대응하는 상기 메모리 위치로부터, 하나 이상의 샘플을 검색하여 상기 현재 블록을 디코딩하는 단계를 포함하며,

상기 방법은,

상기 현재 블록의 CTU의 크기가 상기 참조 샘플 메모리의 크기보다 작을지를 결정하는 단계;

상기 현재 블록의 CTU의 크기가 상기 참조 샘플 메모리의 크기보다 작다는 결정에 응답하여, 상기 참조 블록의 상이한 CTU와 상기 현재 블록의 CTU 사이의 거리가 상기 참조 샘플 메모리의 크기와 상기 현재 블록의 CTU의 크기 사이의 비를 이용하여 정의된 임계값 이하인지를 결정하는 단계: 및

상기 거리가 상기 임계값 이하라는 결정에 응답하여, 상기 참조 블록에 대응하는 상기 메모리 위치로부터, 하나 이상의 샘플을 검색하여 상기 현재 블록을 디코딩하는 단계를 추가로 포함하는, 방법.

#### 청구항 2

제1항에 있어서,

상기 제1 영역은 상기 현재 블록이고, 상기 제2 영역은 상기 참조 블록인 방법.

#### 청구항 3

제1항에 있어서,

상기 제1 영역과 상기 제2 영역은 각각  $2^M \times 2^N$ 인 크기를 갖는 방법.

#### 청구항 4

제3항에 있어서,

$M=6$ 이고  $N=6$ 인 방법.

#### 청구항 5

제1항에 있어서,

상기 제1 영역의 디코딩 상태가 상기 제1 영역이 적어도 부분적으로 디코딩되는 적어도 하나의 블록을 포함하지 않는다는 것을 나타낸다는 결정에 응답하여 상기 참조 블록에 대응하는 상기 메모리 위치는 이용가능한 것으로

결정되는 방법.

### 청구항 6

제1항에 있어서,

상기 임계값은 ((참조 샘플 메모리 크기/CTU 크기)-1)\*(CTU 폭)와 같이 정의되는, 방법.

### 청구항 7

제1항에 있어서,

상기 거리가 임계값보다 크다는 결정에 응답하여,

(i) 상기 상이한 CTU 내의 제2 영역과 병치되는 상기 현재 블록의 상기 CTU 내의 제1 영역을 결정하는 단계- 상기 제1 영역은 상기 참조 블록의 상기 상이한 CTU 내의 상기 제2 영역의 위치 좌표들과 동일한 상기 현재 블록의 상기 CTU 내의 위치 좌표들을 가짐 -;

(ii) 상기 제1 영역의 디코딩 상태에 기초하여, 상기 참조 블록에 대한 상기 참조 샘플 메모리의 메모리 위치가 이용가능한지를 결정하는 단계; 및

(iii) 상기 참조 블록에 대한 상기 메모리 위치가 이용가능하다는 결정에 응답하여, 상기 참조 블록에 대응하는 상기 메모리 위치로부터, 하나 이상의 샘플을 검색하여 상기 현재 블록을 디코딩하는 단계를 추가로 포함하는 방법.

### 청구항 8

비디오 디코딩을 위한 비디오 디코딩 장치로서,

처리 회로를 포함하고, 상기 처리 회로는:

코딩된 비디오 비트스트림을 수신하고,

현재 블록에 대한 참조 블록이 상기 현재 블록의 CTU와 상이한 코딩 트리 유닛(CTU)에 위치하는지를 결정하고- 상기 참조 블록과 현재 블록은 상기 코딩된 비디오 비트스트림의 일부인 블록에 위치함 -,

상기 참조 블록이 상기 상이한 CTU에 위치한다는 결정에 응답하여:

(i) 상기 상이한 CTU 내의 제2 영역과 병치되는 상기 현재 블록의 상기 CTU 내의 제1 영역을 결정하고- 상기 제1 영역 및 상기 제2 영역은 상기 현재 블록의 상기 CTU 및 상기 참조 블록의 상기 상이한 CTU에서 동일한 위치를 가짐 -,

(ii) 상기 제1 영역의 디코딩 상태에 기초하여, 상기 참조 블록에 대한 참조 샘플 메모리의 메모리 위치가 이용가능한지를 결정하고,

(iii) 상기 참조 블록에 대한 상기 메모리 위치가 이용가능하다는 결정에 응답하여, 상기 참조 블록에 대응하는 상기 메모리 위치로부터, 하나 이상의 샘플을 검색하여 상기 현재 블록을 디코딩하도록 구성되며,

상기 처리 회로는:

상기 현재 블록의 CTU의 크기가 상기 참조 샘플 메모리의 크기보다 작을지를 결정하고,

상기 현재 블록의 CTU의 크기가 상기 참조 샘플 메모리의 크기보다 작다는 결정에 응답하여, 상기 참조 블록의 상이한 CTU와 상기 현재 블록의 CTU 사이의 거리가 상기 참조 샘플 메모리의 크기와 상기 현재 블록의 CTU의 크기 사이의 비를 이용하여 정의된 임계값 이하인지를 결정하고,

상기 거리가 상기 임계값 이하라는 결정에 응답하여, 상기 참조 블록에 대응하는 상기 메모리 위치로부터, 하나 이상의 샘플을 검색하여 상기 현재 블록을 디코딩하도록 추가로 구성되는, 비디오 디코딩 장치.

### 청구항 9

제8항에 있어서,

상기 제1 영역은 상기 현재 블록이고, 상기 제2 영역은 상기 참조 블록인 비디오 디코딩 장치.

**청구항 10**

제8항에 있어서,

상기 제1 영역과 상기 제2 영역은 각각  $2^M \times 2^N$ 인 크기를 갖는 비디오 디코딩 장치.

**청구항 11**

제10항에 있어서,

$M=6$ 이고  $N=6$ 인 비디오 디코딩 장치.

**청구항 12**

제8항에 있어서,

상기 제1 영역의 디코딩 상태가 상기 제1 영역이 적어도 부분적으로 디코딩되는 적어도 하나의 블록을 포함하지 않는다는 것을 나타낸다는 결정에 응답하여 상기 참조 블록에 대응하는 상기 메모리 위치는 이용가능한 것으로 결정되는 비디오 디코딩 장치.

**청구항 13**

제8항에 있어서,

상기 임계값은 ((참조 샘플 메모리 크기/CTU 크기)-1)\*(CTU 폭)와 같이 정의되는, 비디오 디코딩 장치.

**청구항 14**

제8항에 있어서,

상기 거리가 임계값보다 크다는 결정에 응답하여,

(i) 상기 상이한 CTU 내의 제2 영역과 병치되는 상기 현재 블록의 상기 CTU 내의 제1 영역을 결정하고-

상기 제1 영역은 상기 참조 블록의 상기 상이한 CTU 내의 상기 제2 영역의 위치 좌표들과 동일한 상기 현재 블록의 상기 CTU 내의 위치 좌표들을 가짐 - ,

(ii) 상기 제1 영역의 디코딩 상태에 기초하여, 상기 참조 블록에 대한 상기 참조 샘플 메모리의 메모리 위치가 이용가능한지를 결정하고,

(iii) 상기 참조 블록에 대한 상기 메모리 위치가 이용가능하다는 결정에 응답하여, 상기 참조 블록에 대응하는 상기 메모리 위치로부터, 하나 이상의 샘플을 검색하여 상기 현재 블록을 디코딩하는 것을 더 포함하는 비디오 디코딩 장치.

**청구항 15**

비디오 디코더 내의 프로세서에 의해 실행될 때, 상기 프로세서로 하여금 방법을 실행하게 하는 명령어들이 저장된 비일시적 컴퓨터 판독가능 매체로서,

상기 방법은:

코딩된 비디오 비트스트림을 수신하는 단계;

현재 블록에 대한 참조 블록이 상기 현재 블록의 CTU와 상이한 코딩 트리 유닛(CTU)에 위치하는지를 결정하는 단계- 상기 참조 블록과 현재 블록은 상기 코딩된 비디오 비트스트림의 일부인 픽처에 위치함 -;

상기 참조 블록이 상기 상이한 CTU에 위치한다는 결정에 응답하여:

(i) 상기 상이한 CTU 내의 제2 영역과 병치되는 상기 현재 블록의 상기 CTU 내의 제1 영역을 결정하는 단계- 상기 제1 영역 및 상기 제2 영역은 상기 현재 블록의 상기 CTU 및 상기 참조 블록의 상기 상이한 CTU에서 동일한 위치를 가짐 -;

(ii) 상기 제1 영역의 디코딩 상태에 기초하여, 상기 참조 블록에 대한 참조 샘플 메모리의 메모리 위치가 이용가능한지를 결정하는 단계;

(iii) 상기 참조 블록에 대한 상기 메모리 위치가 이용가능하다는 결정에 응답하여, 상기 참조 블록에 대응하는 상기 메모리 위치로부터, 하나 이상의 샘플을 검색하여 상기 현재 블록을 디코딩하는 단계를 포함하며,

상기 방법은,

상기 현재 블록의 CTU의 크기가 상기 참조 샘플 메모리의 크기보다 작은지를 결정하는 단계;

상기 현재 블록의 CTU의 크기가 상기 참조 샘플 메모리의 크기보다 작다는 결정에 응답하여, 상기 참조 블록의 상이한 CTU와 상기 현재 블록의 CTU 사이의 거리가 상기 참조 샘플 메모리의 크기와 상기 현재 블록의 CTU의 크기 사이의 비를 이용하여 정의된 임계값 이하인지를 결정하는 단계: 및

상기 거리가 상기 임계값 이하라는 결정에 응답하여, 상기 참조 블록에 대응하는 상기 메모리 위치로부터, 하나 이상의 샘플을 검색하여 상기 현재 블록을 디코딩하는 단계를 추가로 포함하는, 비일시적 컴퓨터 판독가능 매체.

#### 청구항 16

제15항에 있어서,

상기 제1 영역은 상기 현재 블록이고, 상기 제2 영역은 상기 참조 블록인 비일시적 컴퓨터 판독가능 매체.

#### 청구항 17

제15항에 있어서,

상기 제1 영역과 상기 제2 영역은 각각  $2^M \times 2^N$ 인 크기를 갖는 비일시적 컴퓨터 판독가능 매체.

#### 청구항 18

제17항에 있어서,

$M=6$ 이고  $N=6$ 인 비일시적 컴퓨터 판독가능 매체.

#### 청구항 19

제15항에 있어서,

상기 제1 영역의 디코딩 상태가 상기 제1 영역이 적어도 부분적으로 디코딩되는 적어도 하나의 블록을 포함하지 않는다는 것을 나타낸다는 결정에 응답하여 상기 참조 블록에 대응하는 상기 메모리 위치는 이용가능한 것으로 결정되는 비일시적 컴퓨터 판독가능 매체.

#### 청구항 20

제15항에 있어서,

상기 임계값은 ((참조 샘플 메모리 크기/CTU 크기)-1)\*(CTU 폭)와 같이 정의되는, 비일시적 컴퓨터 판독가능 매체.

### 발명의 설명

#### 기술 분야

[0001] 본 출원은 2019년 1월 13일자로 출원된 미국 가출원 제62/791,862호, "REFERENCE SAMPLE MEMORY REUSE FOR INTRA PICTURE BLOCK COMPENSATION"에 대한 우선권의 이익을 주장하는, 2019년 7월 3일자로 출원된 미국 특허 출원 제16/502,822호, "METHOD AND APPARATUS FOR REFERENCE SAMPLE MEMORY REUSE FOR INTRA PICTURE BLOCK COMPENSATION"의 우선권의 이익을 주장한다. 앞의 출원들의 전체 개시내용들은 그 전체가 참조로서 포함된다.

[0002] 본 개시내용은 일반적으로 비디오 코딩에 관련된 실시예들을 설명한다.

#### 배경 기술

- [0003] 본 명세서에 제공된 배경 설명은 본 개시내용의 맥락을 일반적으로 제시하기 위한 것이다. 본 배경기술 부분에 설명되어 있는 현재 등록된 발명자들의 연구 및 출원 시점에 종래 기술로서 달리 간주되지 않을 수 있는 설명의 양태는 명시적으로도 암시적으로도 본 개시내용에 대한 종래 기술로 인정되지 않는다.

- [0004] 비디오 코딩 및 디코딩은 모션 보상을 동반한 인터-픽처 예측(inter-picture prediction)을 사용하여 수행될 수 있다. 압축되지 않은 디지털 비디오는 일련의 픽처들을 포함할 수 있고, 각각의 픽처는, 예를 들어, 1920x1080 루미넌스 샘플들 및 연관된 크로미넌스 샘플들의 공간 차원을 갖는다. 이 일련의 픽처들은, 예를 들어, 초당 60 픽처 또는 60Hz의, 고정된 또는 가변 픽처 레이트(비공식적으로 프레임 레이트로도 알려져 있음)를 가질 수 있다. 압축되지 않은 비디오는 상당한 비트레이트 요구들을 갖는다. 예를 들어, 샘플당 8 비트에서의 1080p60 4:2:0 비디오(60Hz 프레임 레이트의 1920x1080 루미넌스 샘플 해상도)는 1.5 Gbit/s에 근접한 대역폭을 요구한다. 1 시간 분량의 이러한 비디오는 600 기가바이트를 초과하는 저장 공간을 필요로 한다.

- [0005] 비디오 코딩 및 디코딩의 한 가지 목적은, 압축을 통한, 입력 비디오 신호에서의 중복성의 감소일 수 있다. 압축은 앞서 설명한 대역폭 또는 저장 공간 요건들을, 일부 경우들에서는, 2 자릿수 이상 감소시키는 데 도움이 될 수 있다. 무손실 및 손실 압축 양자 모두뿐만 아니라 이들의 조합이 이용될 수 있다. 무손실 압축은 압축된 원본 신호로부터 원본 신호의 정확한 사본이 재구성될 수 있는 기법들을 지칭한다. 손실 압축을 사용할 때, 재구성된 신호는 원본 신호와 동일하지 않을 수 있지만, 원본 신호와 재구성된 신호 사이의 왜곡은 재구성된 신호가 의도된 응용에 유용할 정도로 충분히 작다. 비디오의 경우, 손실 압축이 널리 이용된다. 용인되는 왜곡의 양은 응용에 의존하며; 예를 들어, 특정 소비자 스트리밍 응용들의 사용자들은 텔레비전 배포 응용들의 사용자들보다 더 높은 왜곡을 용인할 수 있다. 달성가능한 압축비는 더 높은 허용가능한/용인가능한 왜곡이 더 높은 압축비를 산출할 수 있다는 사실을 반영할 수 있다.

- [0006] 모션 보상은 손실 압축 기법일 수 있고, 이전에 재구성된 픽처 또는 그의 일부(참조 픽처)로부터의 샘플 데이터의 블록이, 모션 벡터(이후 MV)에 의해 표시된 방향으로 공간적으로 시프트된 이후에, 새롭게 재구성된 픽처 또는 픽처 부분의 예측에 사용되는 기법들과 관련될 수 있다. 일부 경우들에서, 참조 픽처는 현재 재구성 중인 픽처와 동일할 수 있다. MV들은 2개의 차원 X 및 Y, 또는 3개의 차원을 가질 수 있고, 제3 차원은 사용중인 참조 픽처의 표시이다(후자는, 간접적으로, 시간 차원일 수 있다).

- [0007] 일부 비디오 압축 기법들에서, 샘플 데이터의 특정 영역에 적용가능한 MV는 다른 MV들로부터, 예를 들어 재구성 중인 영역에 공간적으로 인접한 샘플 데이터의 다른 영역과 관련되고 디코딩 순서로 그 MV에 선행하는 것들로부터 예측될 수 있다. 그렇게 함으로써 MV를 코딩하기 위해 요구되는 데이터의 양을 실질적으로 감소시킬 수 있고, 그에 의해 중복성을 제거하고 압축을 증가시킨다. MV 예측은, 예를 들어, 카메라로부터 유도된 입력 비디오 신호(자연 비디오라고 알려짐)를 코딩할 때, 단일 MV가 적용가능한 영역보다 더 큰 영역들이 유사한 방향으로 움직이는 통계적 가능성이 있고, 따라서, 일부 경우들에서 이웃 영역의 MV들로부터 유도된 유사한 모션 벡터를 사용하여 예측될 수 있기 때문에 효과적으로 작동할 수 있다. 그 결과, 주어진 영역에 대해 발견되는 MV가 주위의 MV들로부터 예측된 MV와 유사하거나 동일하게 되고, 이는 결국, 엔트로피 코딩 이후에, MV를 직접 코딩하는 경우에 사용되는 것보다 더 적은 수의 비트들로, 표현될 수 있다. 일부 경우에, MV 예측은 원본 신호(즉, 샘플 스트림)로부터 유도된 신호(즉, MV들)의 무손실 압축의 예일 수 있다. 다른 경우들에서, MV 예측 자체는, 예를 들어, 몇몇 주위의 MV들로부터 예측자를 계산할 때의 반올림 오류들 때문에, 손실성일 수 있다.

- [0008] 다양한 MV 예측 메커니즘들이 H.265/HEVC(ITU-T Rec. H.265, "High Efficiency Video Coding", December 2016)에 설명되어 있다. H.265가 제안하는 많은 MV 예측 메커니즘들 중에서, 여기서는 이후 "공간 병합"이라고 지칭되는 기법이 본 명세서에서 설명된다.

- [0009] 현재 블록이 인트라 블록 사본을 사용하여 디코딩될 때, 메모리는 현재 블록을 디코딩하기 위한 샘플들을 검색하기 위해 참조된다. 메모리의 크기가 제한되기 때문에, 메모리가 최근에 디코딩된 블록들로부터의 샘플들로 업데이트될 때 메모리의 일부분이 덮어쓰기된다. 인트라 블록 복사를 수행하기 위해 메모리를 효율적으로 이용하는 새로운 방법들이 필요하다.

## 발명의 내용

### 해결하려는 과제

## 과제의 해결 수단

[0010]

본 개시내용의 예시적인 실시예에 따르면, 디코더에 대한 비디오 디코딩 방법은 코딩된 비디오 비트스트림을 수신하는 단계를 포함한다. 본 방법은 현재 블록에 대한 참조 블록이 현재 블록의 CTU와 상이한 코딩 트리 유닛(CTU)에 위치하는지를 결정하는 단계를 추가로 포함하고, 참조 블록과 현재 블록은 코딩된 비디오 비트스트림에 포함된 동일한 픽처에 위치한다. 본 방법은 참조 블록이 상이한 CTU에 위치한다는 결정에 응답하여, 현재 블록의 CTU와 참조 샘플 메모리가 동일한 크기를 갖는지를 결정하는 단계를 추가로 포함한다. 본 방법은 현재 블록의 CTU 및 참조 샘플 메모리가 동일한 크기를 갖는다는 결정에 응답하여: (i) 상이한 CTU 내의 제2 영역과 병치되는 현재 블록의 CTU 내의 제1 영역을 결정하는 단계- 제1 영역은 참조 블록의 상이한 CTU 내의 제2 영역의 위치 좌표들과 동일한 현재 블록의 CTU 내의 위치 좌표들을 가짐 -; (ii) 제1 영역의 디코딩 상태에 기초하여, 참조 블록에 대한 참조 샘플 메모리의 메모리 위치가 이용가능한지를 결정하는 단계; 및 (iii) 참조 블록에 대한 메모리 위치가 이용가능하다는 결정에 응답하여, 참조 블록에 대응하는 메모리 위치로부터, 하나 이상의 샘플을 검색하여 현재 블록을 디코딩하는 단계를 추가로 포함한다.

[0011]

본 개시내용의 예시적인 실시예에 따르면, 비디오 디코딩을 위한 비디오 디코더는 처리 회로를 포함한다. 처리 회로는 코딩된 비디오 비트스트림을 수신하도록 구성된다. 처리 회로는 현재 블록에 대한 참조 블록이 현재 블록의 CTU와 상이한 코딩 트리 유닛(CTU)에 위치하는지를 결정하도록 추가로 구성되고, 참조 블록과 현재 블록은 코딩된 비디오 비트스트림에 포함된 동일한 픽처에 위치한다. 처리 회로는 참조 블록이 상이한 CTU에 위치한다는 결정에 응답하여, 현재 블록의 CTU와 참조 샘플 메모리가 동일한 크기를 갖는지를 결정하도록 추가로 구성된다. 처리 회로는 현재 블록의 CTU와 참조 샘플 메모리가 동일한 크기를 갖는다는 결정에 응답하여: (i) 상이한 CTU 내의 제2 영역과 병치되는 현재 블록의 CTU 내의 제1 영역을 결정하고- 제1 영역은 참조 블록의 상이한 CTU 내의 제2 영역의 위치 좌표들과 동일한 현재 블록의 CTU 내의 위치 좌표들을 가짐 -, (ii) 제1 영역의 디코딩 상태에 기초하여, 참조 블록에 대한 참조 샘플 메모리의 메모리 위치가 이용가능한지를 결정하고, (iii) 참조 블록에 대한 메모리 위치가 이용가능하다는 결정에 응답하여, 참조 블록에 대응하는 메모리 위치로부터, 하나 이상의 샘플을 검색하여 현재 블록을 디코딩하도록 추가로 구성된다.

[0012]

본 개시내용의 예시적인 실시예에 따르면, 비디오 디코더 내의 프로세서에 의해 실행될 때 비디오 디코더로 하여금 방법을 실행하게 하는 명령어들이 저장된 비일시적 컴퓨터 관독가능 매체가 제공된다. 본 방법은 코딩된 비디오 비트스트림을 수신하는 단계를 포함한다. 본 방법은 현재 블록에 대한 참조 블록이 현재 블록의 CTU와 상이한 코딩 트리 유닛(CTU)에 위치하는지를 결정하는 단계를 추가로 포함하고, 참조 블록과 현재 블록은 코딩된 비디오 비트스트림에 포함된 동일한 픽처에 위치한다. 본 방법은 참조 블록이 상이한 CTU에 위치한다는 결정에 응답하여, 현재 블록의 CTU와 참조 샘플 메모리가 동일한 크기를 갖는지를 결정하는 단계를 추가로 포함한다. 본 방법은 현재 블록의 CTU 및 참조 샘플 메모리가 동일한 크기를 갖는다는 결정에 응답하여: (i) 상이한 CTU 내의 제2 영역과 병치되는 현재 블록의 CTU 내의 제1 영역을 결정하는 단계- 제1 영역은 참조 블록의 상이한 CTU 내의 제2 영역의 위치 좌표들과 동일한 현재 블록의 CTU 내의 위치 좌표들을 가짐 -; (ii) 제1 영역의 디코딩 상태에 기초하여, 참조 블록에 대한 참조 샘플 메모리의 메모리 위치가 이용가능한지를 결정하는 단계; 및 (iii) 참조 블록에 대한 메모리 위치가 이용가능하다는 결정에 응답하여, 참조 블록에 대응하는 메모리 위치로부터, 하나 이상의 샘플을 검색하여 현재 블록을 디코딩하는 단계를 추가로 포함한다.

## 도면의 간단한 설명

[0013]

개시된 주제의 추가의 특징들, 본질 및 다양한 이점들이 다음 상세한 설명 및 첨부 도면들로부터 더 명백할 것이다.

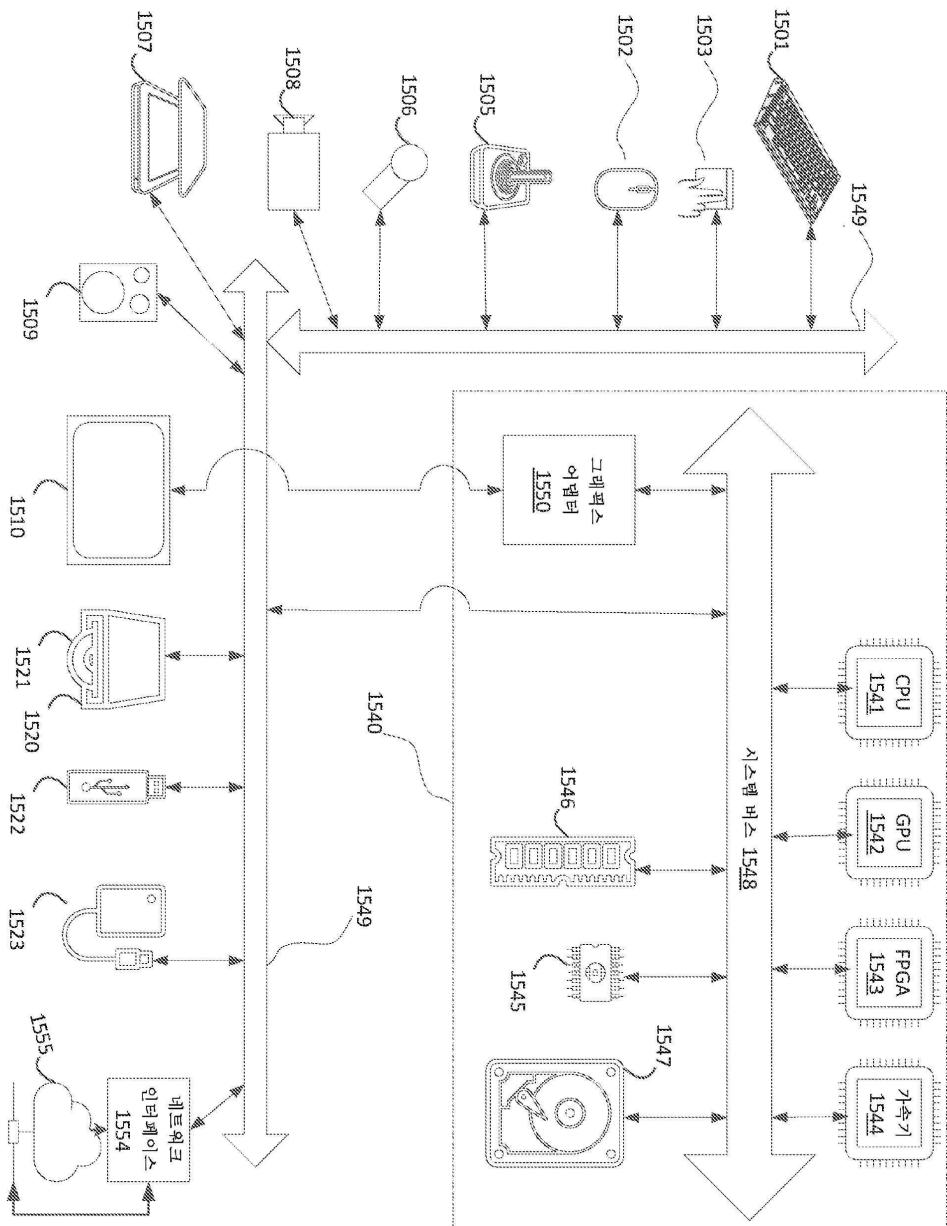

도 1은 일 실시예에 따른 통신 시스템(100)의 단순화된 블록도의 개략적 예시이다.

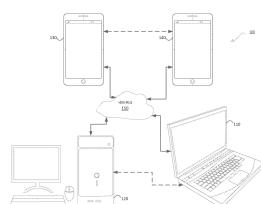

도 2는 일 실시예에 따른 통신 시스템(200)의 단순화된 블록도의 개략적 예시이다.

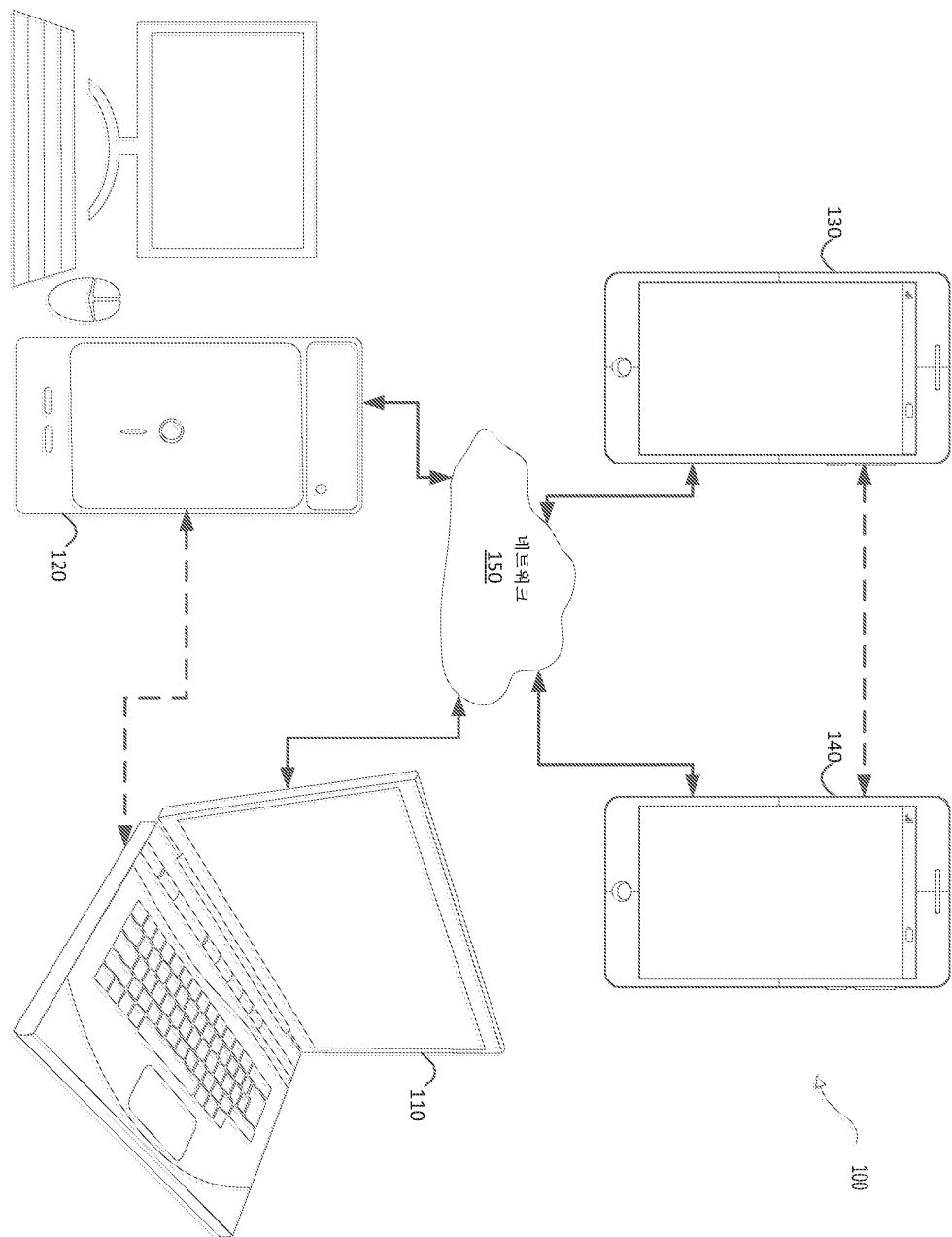

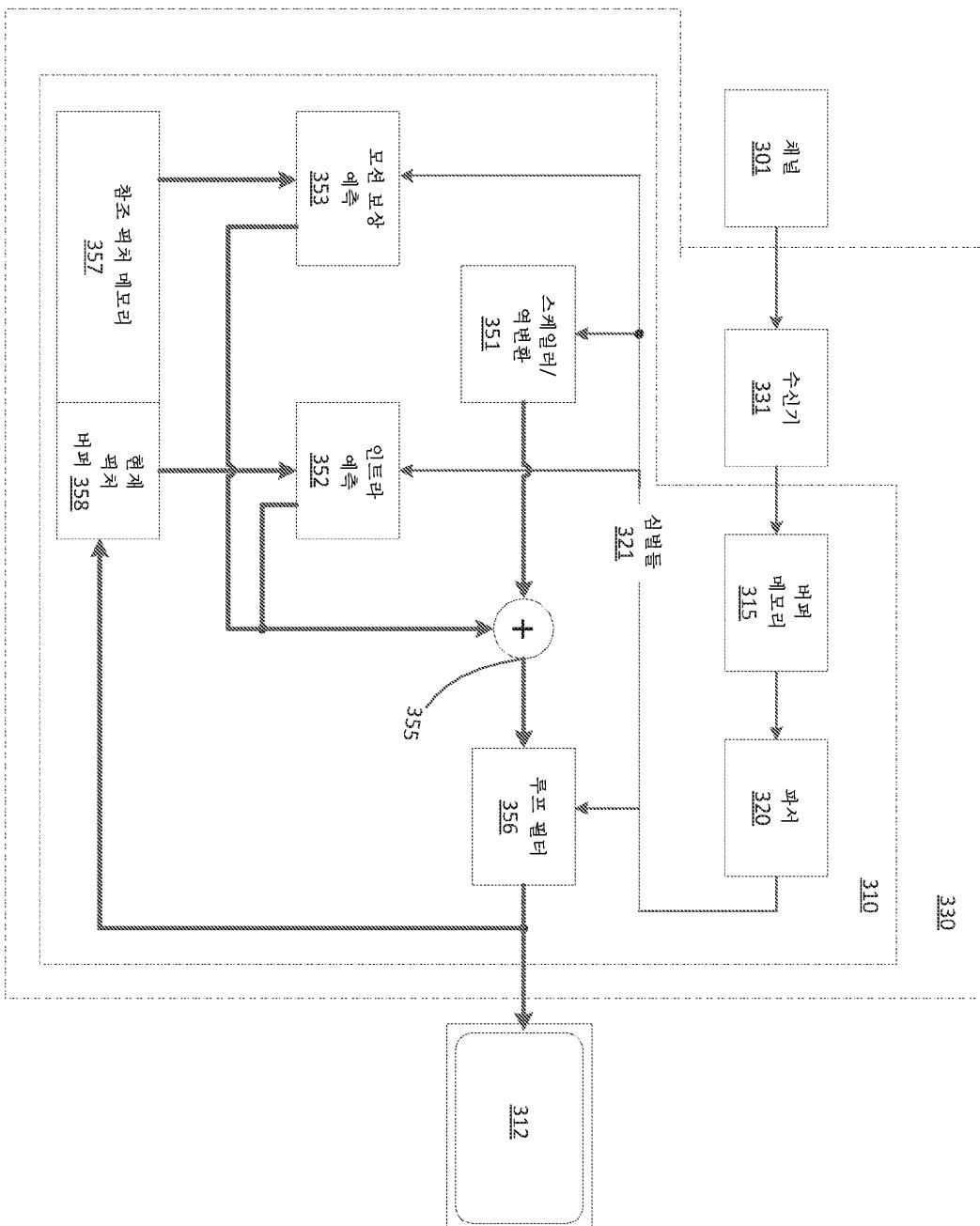

도 3은 일 실시예에 따른 디코더의 단순화된 블록도의 개략적 예시이다.

도 4는 일 실시예에 따른 인코더의 단순화된 블록도의 개략적 예시이다.

도 5는 다른 실시예에 따른 인코더의 블록도를 예시한다.

도 6은 다른 실시예에 따른 디코더의 블록도를 예시한다.

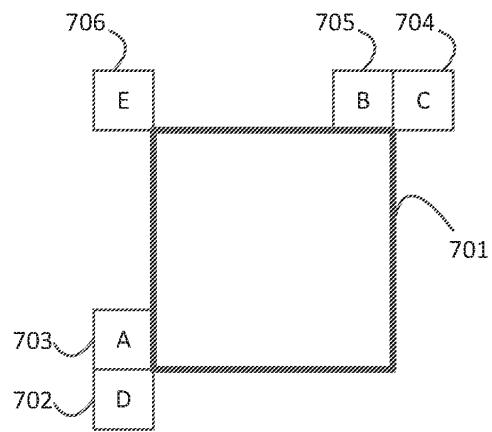

도 7은 일 예에서 현재 블록 및 그 주위의 공간 병합 후보들의 개략적 예시이다.

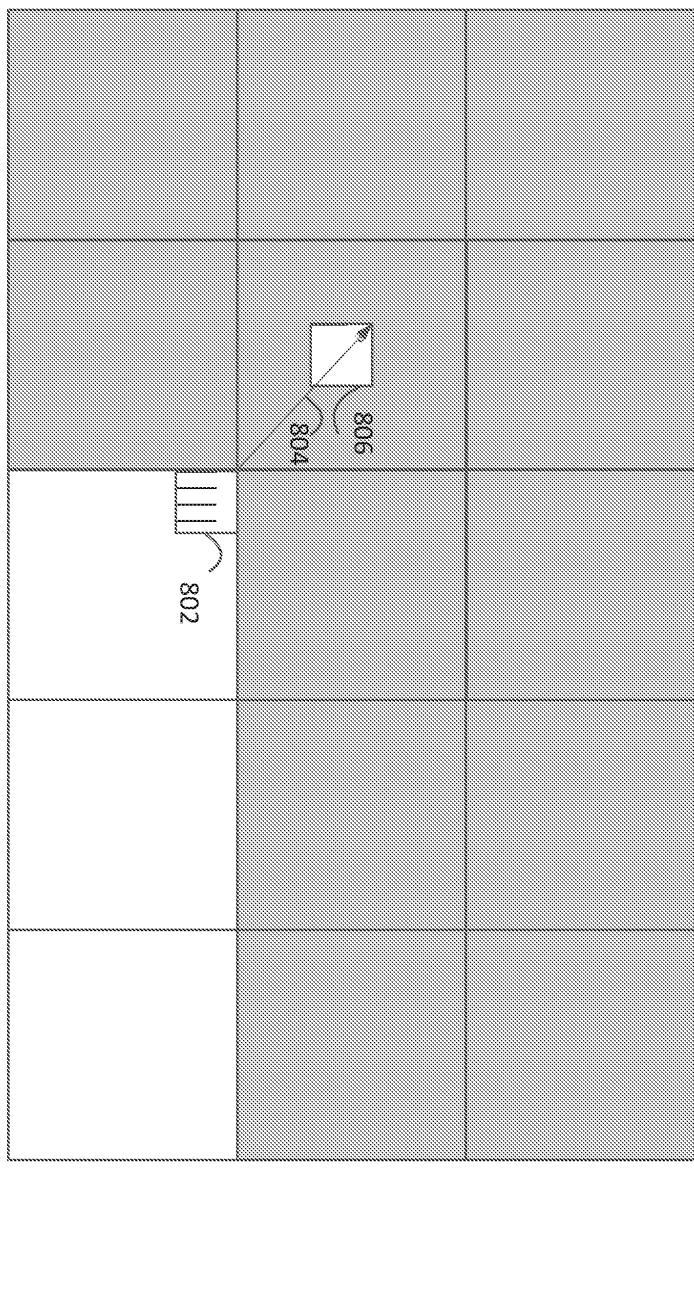

도 8은 인트라 픽처 블록 보상의 개략적 예시이다.

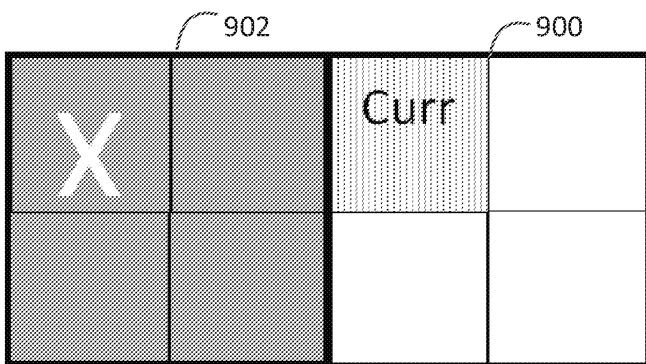

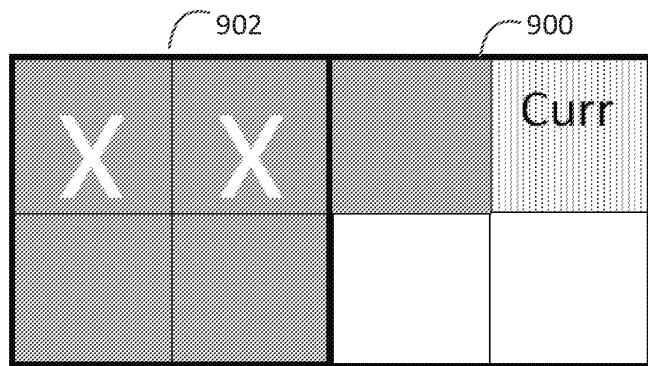

도 9a 내지 도 9d는 하나의 코딩 트리 유닛(CTU) 크기 검색 범위를 갖는 인트라 픽처 블록 보상의 개략적 예시이다.

도 10a 내지 도 10d는 참조 샘플 메모리의 개략적 예시이다.

도 11은 제1 CTU 내의 참조 블록들 및 제2 CTU 내의 대응하는 병치된 블록들의 개략적 예시이다.

도 12는 제1 CTU 내의 참조 블록들 및 제1 CTU와 제2 CTU 사이에 제3 CTU를 갖는 제2 CTU 내의 대응하는 병치된 블록들의 개략적 예시이다.

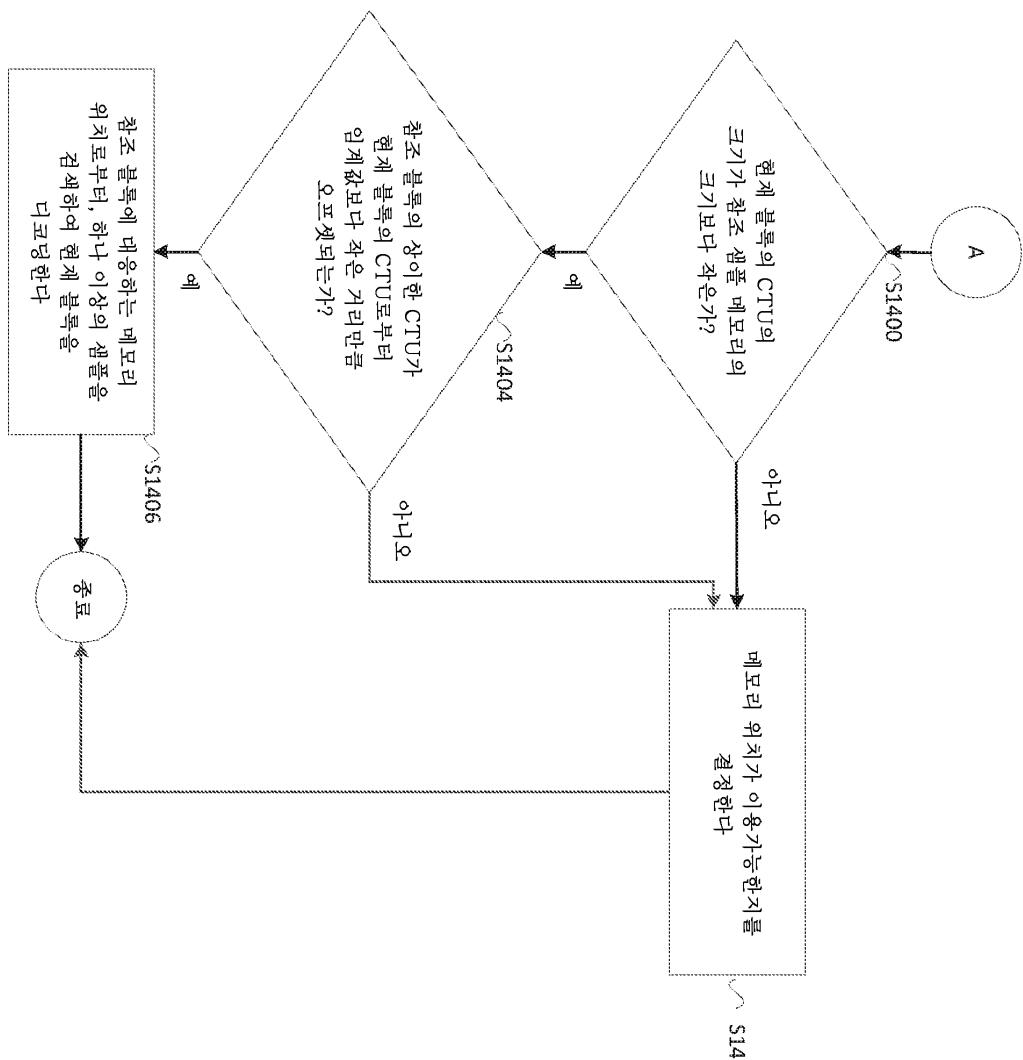

도 13 및 도 14는 인코더에 의해 수행되는 프로세스의 실시예를 예시한다.

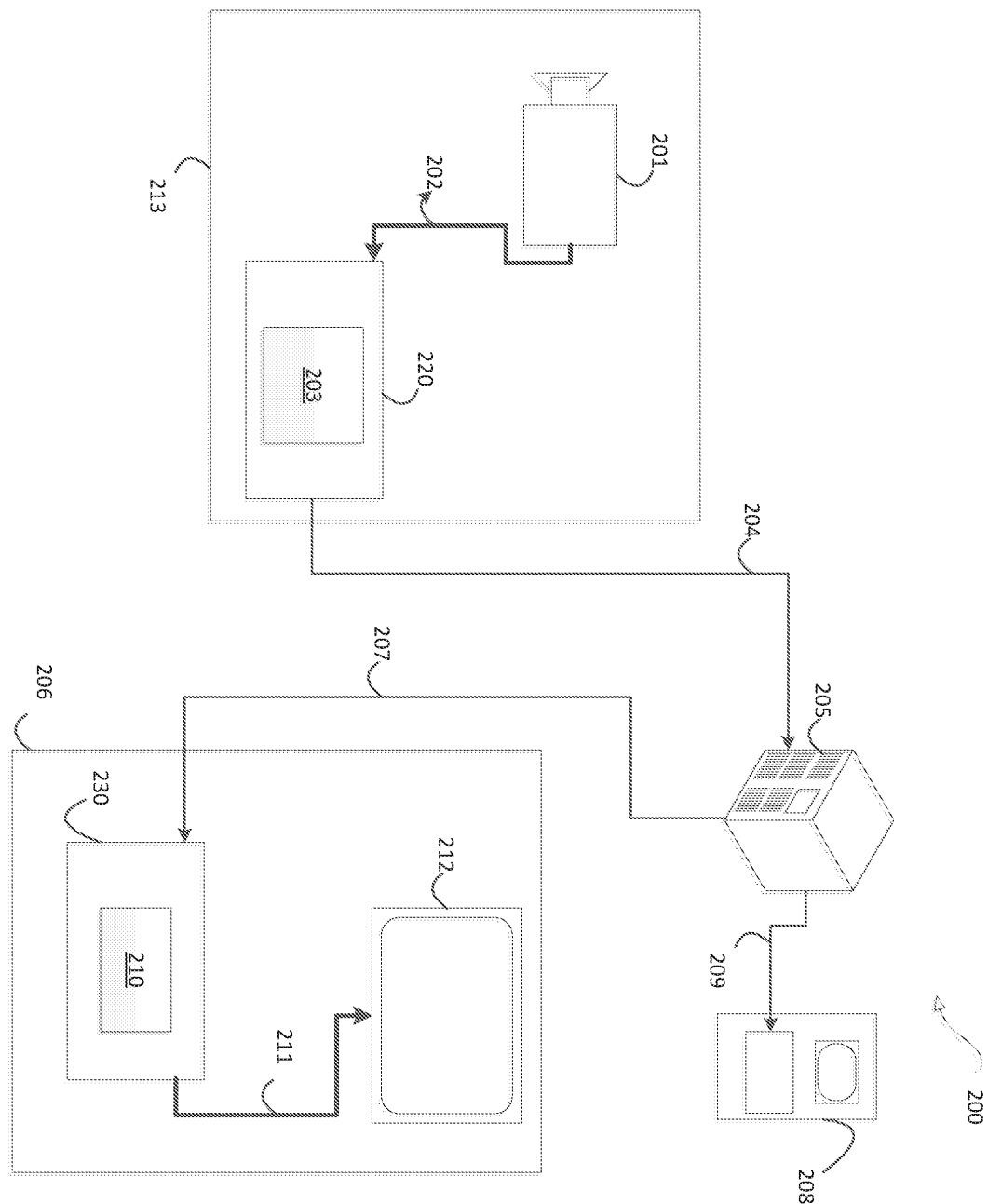

도 15는 일 실시예에 따른 컴퓨터 시스템의 개략적 예시이다.

### 발명을 실시하기 위한 구체적인 내용

[0014] 도 1은 본 개시내용의 일 실시예에 따른 통신 시스템(100)의 단순화된 블록도를 예시한다. 통신 시스템(100)은, 예를 들어, 네트워크(150)를 통해, 서로 통신할 수 있는 복수의 단말 디바이스를 포함한다. 예를 들어, 통신 시스템(100)은 네트워크(150)를 통해 상호접속된 제1 쌍의 단말 디바이스들(110 및 120)을 포함한다. 도 1의 예에서, 제1 쌍의 단말 디바이스들(110 및 120)은 데이터의 단방향 송신을 수행한다. 예를 들어, 단말 디바이스(110)는 네트워크(150)를 통해 다른 단말 디바이스(120)로의 송신을 위해 비디오 데이터(예를 들어, 단말 디바이스(110)에 의해 캡처되는 비디오 픽처들의 스트림)를 코딩할 수 있다. 인코딩된 비디오 데이터는 하나 이상의 코딩된 비디오 비트스트림의 형태로 송신될 수 있다. 단말 디바이스(120)는 네트워크(150)로부터 코딩된 비디오 데이터를 수신하고, 코딩된 비디오 데이터를 디코딩하여 비디오 픽처들을 복구하고 복구된 비디오 데이터에 따라 비디오 픽처들을 디스플레이할 수 있다. 단방향 데이터 송신은 미디어 서빙 응용들 등에서 일반적일 수 있다.

[0015] 다른 예에서, 통신 시스템(100)은, 예를 들어, 영상 회의 동안 발생할 수 있는 코딩된 비디오 데이터의 양방향 송신을 수행하는 제2 쌍의 단말 디바이스들(130 및 140)을 포함한다. 데이터의 양방향 송신을 위해, 일 예에서, 단말 디바이스들(130 및 140) 중의 각각의 단말 디바이스는 네트워크(150)를 통해 단말 디바이스들(130 및 140) 중의 다른 단말 디바이스로의 송신을 위해 비디오 데이터(예를 들어, 단말 디바이스에 의해 캡처되는 비디오 픽처들의 스트림)를 코딩할 수 있다. 단말 디바이스들(130 및 140) 중의 각각의 단말 디바이스는 또한 단말 디바이스들(130 및 140) 중의 다른 단말 디바이스에 의해 송신된 코딩된 비디오 데이터를 수신할 수 있고, 코딩된 비디오 데이터를 디코딩하여 비디오 픽처들을 복구할 수 있고, 복구된 비디오 데이터에 따라 액세스 가능한 디스플레이 디바이스에서 비디오 픽처들을 디스플레이할 수 있다.

[0016] 도 1의 예에서, 단말 디바이스들(110, 120, 130 및 140)은 서버들, 개인용 컴퓨터들 및 스마트폰들로서 예시될 수 있지만, 본 개시내용의 원리들은 이에 제한되지 않는다. 본 개시내용의 실시예들은 랩톱 컴퓨터들, 태블릿 컴퓨터들, 미디어 플레이어들 및/또는 전용 영상 회의 장비에서 응용된다. 네트워크(150)는 예를 들어, 와이어라인(유선) 및/또는 무선 통신 네트워크들을 비롯하여, 단말 디바이스들(110, 120, 130 및 140) 사이에 코딩된 비디오 데이터를 전달하는 임의의 수의 네트워크들을 나타낸다. 통신 네트워크(150)는 회선 교환 및/또는 패킷 교환 채널들에서 데이터를 교환할 수 있다. 대표적인 네트워크들은 통신 네트워크들, 로컬 영역 네트워크들, 광역 네트워크들 및/또는 인터넷을 포함한다. 본 논의의 목적을 위해, 네트워크(150)의 아키텍처 및 토플로지는 아래에서 본 명세서에서 설명되지 않는 한 본 개시내용의 동작에 중요하지 않을 수 있다.

[0017] 도 2는, 개시된 주제를 위한 응용에 대한 예로서, 스트리밍 환경에서의 비디오 인코더 및 비디오 디코더의 배치를 예시한다. 개시된 주제는, 예를 들어, 영상 회의, 디지털 TV, CD, DVD, 메모리 스틱 등을 포함하는 디지털 미디어 상의 압축된 비디오의 저장 등을 포함하여, 다른 비디오 가능 응용들에 동등하게 적용가능할 수 있다.

[0018] 스트리밍 시스템은, 예를 들어, 압축되지 않은 비디오 픽처들의 스트림(202)을 생성하는 비디오 소스(201), 예를 들어, 디지털 카메라를 포함할 수 있는 캡처 서브시스템(213)을 포함할 수 있다. 일 예에서, 비디오 픽처들의 스트림(202)은 디지털 카메라에 의해 촬영되는 샘플들을 포함한다. 인코딩된 비디오 데이터(204)(또는 코딩된 비디오 비트스트림)와 비교할 때 많은 데이터 볼륨을 강조하기 위해 굵은 라인으로 묘사된 비디오 픽처들의 스트림(202)은 비디오 소스(201)에 결합된 비디오 인코더(203)를 포함하는 전자 디바이스(220)에 의해 처리될 수 있다. 비디오 인코더(203)는 아래에서 더 상세히 설명되는 바와 같이 개시된 주제의 양태들을 가능하게 하

거나 구현하기 위해 하드웨어, 소프트웨어, 또는 이들의 조합을 포함할 수 있다. 비디오 픽처들의 스트림(202)과 비교할 때 적은 데이터 볼륨을 강조하기 위해 얇은 라인으로서 묘사된 인코딩된 비디오 데이터(204)(또는 인코딩된 비디오 비트스트림(204))는 장래의 사용을 위해 스트리밍 서버(205) 상에 저장될 수 있다. 도 2의 클라이언트 서브시스템들(206 및 208)과 같은 하나 이상의 스트리밍 클라이언트 서브시스템들은 스트리밍 서버(205)에 액세스하여 인코딩된 비디오 데이터(204)의 사본들(207 및 209)을 검색할 수 있다. 클라이언트 서브시스템(206)은, 예를 들어, 전자 디바이스(230) 내에 비디오 디코더(210)를 포함할 수 있다. 비디오 디코더(210)는 인코딩된 비디오 데이터의 착신 사본(207)을 디코딩하고 디스플레이(212)(예를 들어, 디스플레이 스크린) 또는 다른 렌더링 디바이스(묘사되지 않음) 상에 렌더링될 수 있는 비디오 픽처들의 배출 스트림(211)을 생성한다. 일부 스트리밍 시스템들에서, 인코딩된 비디오 데이터(204, 207, 및 209)(예를 들어, 비디오 비트스트림들)는 특정 비디오 코딩/압축 표준들에 따라 인코딩될 수 있다. 해당 표준들의 예들은 ITU-T 권고안(Recommendation) H.265를 포함한다. 일 예에서, 개발 중인 비디오 코딩 표준은 VVC(Versatile Video Coding)로서 비공식적으로 알려져 있다. 개시된 주제는 VVC의 맥락에서 사용될 수 있다.

[0019] 전자 디바이스들(220 및 230)은 다른 컴포넌트들(도시되지 않음)을 포함할 수 있다는 점에 유의한다. 예를 들어, 전자 디바이스(220)는 비디오 디코더(도시되지 않음)도 포함할 수 있고 전자 디바이스(230)는 비디오 인코더(도시되지 않음)도 포함할 수 있다.

[0020] 도 3은 본 개시내용의 일 실시예에 따른 비디오 디코더(310)의 블록도를 도시한다. 비디오 디코더(310)는 전자 디바이스(330)에 포함될 수 있다. 전자 디바이스(330)는 수신기(331)(예를 들어, 수신 회로)를 포함할 수 있다. 비디오 디코더(310)는 도 2의 예에서의 비디오 디코더(210) 대신에 사용될 수 있다.

[0021] 수신기(331)는 비디오 디코더(310)에 의해 디코딩될 하나 이상의 코딩된 비디오 시퀀스를 수신할 수 있으며; 동일한 또는 다른 실시예에서, 한 번에 하나의 코딩된 비디오 시퀀스를 수신하고, 여기서, 각각의 코딩된 비디오 시퀀스의 디코딩은 다른 코딩된 비디오 시퀀스들과 독립적이다. 코딩된 비디오 시퀀스는, 인코딩된 비디오 데이터를 저장하는 저장 디바이스에 대한 하드웨어/소프트웨어 링크일 수 있는, 채널(301)로부터 수신될 수 있다. 수신기(331)는 인코딩된 비디오 데이터를 다른 데이터, 예를 들어, 코딩된 오디오 데이터 및/또는 보조 데이터 스트림들과 함께 수신할 수 있고, 이들은 그 각각의 사용 엔티티들(도시되지 않음)에 포워딩될 수 있다. 수신기(331)는 코딩된 비디오 시퀀스를 다른 데이터로부터 분리할 수 있다. 네트워크 지터를 방지하기 위해, 수신기(331)와 엔트로피 디코더/파서(320)(이후 "파서(320)") 사이에 버퍼 메모리(315)가 결합될 수 있다. 특정 응용들에서, 버퍼 메모리(315)는 비디오 디코더(310)의 일부이다. 다른 응용들에서, 이는 비디오 디코더(310)(묘사되지 않음) 외부에 있을 수 있다. 또 다른 응용들에서, 예를 들어 네트워크 지터를 방지하기 위해, 비디오 디코더(310) 외부의 버퍼 메모리(도시되지 않음), 그리고 추가로, 예를 들어 재생 타이밍을 핸들링하기 위해, 비디오 디코더(310) 내부의 다른 버퍼 메모리(315)가 존재할 수 있다. 수신기(331)가 충분한 대역폭 및 제어가능성을 갖는 저장/포워드 디바이스로부터, 또는 동기식 네트워크(isynchronous network)로부터 데이터를 수신하고 있을 때, 버퍼 메모리(315)는 필요하지 않을 수 있거나, 작을 수 있다. 인터넷과 같은 베스트 에포트 패킷 네트워크들 상에서의 사용을 위해, 버퍼 메모리(315)가 요구될 수 있고, 비교적 클 수 있으며, 유리하게는 적응적 크기일 수 있고, 비디오 디코더(310) 외부의 운영 체제 또는 유사한 요소들(도시되지 않음)에서 적어도 부분적으로 구현될 수 있다.

[0022] 비디오 디코더(310)는 코딩된 비디오 시퀀스로부터 심벌들(321)을 재구성하기 위해 파서(320)를 포함할 수 있다. 해당 심벌들의 카테고리들은 비디오 디코더(310)의 동작을 관리하기 위해 사용되는 정보, 및 잠재적으로, 도 3에 도시된 바와 같이, 전자 디바이스(330)의 일체 부분(integral part)은 아니지만 전자 디바이스(330)에 결합될 수 있는 렌더링 디바이스(312)(예를 들어, 디스플레이 스크린)와 같은 렌더링 디바이스를 제어하기 위한 정보를 포함한다. 렌더링 디바이스(들)에 대한 제어 정보는 SEI(Supplemental Enhancement Information) 메시지 또는 VUI(Video Usability Information) 파라미터 세트 프래그먼트들(도시되지 않음)의 형태일 수 있다. 파서(320)는 수신되는 코딩된 비디오 시퀀스를 파싱/엔트로피 디코딩할 수 있다. 코딩된 비디오 시퀀스의 코딩은 비디오 코딩 기술 또는 표준에 따를 수 있고, 가변 길이 코딩, 허프만 코딩, 맥락 민감성(context sensitivity)을 갖거나 갖지 않는 산술 코딩 등을 포함하는 다양한 원리들을 따를 수 있다. 파서(320)는, 코딩된 비디오 시퀀스로부터, 그룹에 대응하는 적어도 하나의 파라미터에 기초하여, 비디오 디코더 내의 픽셀들의 서브그룹들 중 적어도 하나에 대한 서브그룹 파라미터들의 세트를 추출할 수 있다. 서브그룹들은 픽처 그룹(Group of Pictures, GOP)들, 픽처들, 타일들, 슬라이스들, 매크로블록들, 코딩 유닛(Coding Unit, CU)들, 블록들, 변환 유닛(Transform Unit, TU)들, 예측 유닛(Prediction Unit, PU)들 등을 포함할 수 있다. 파서(320)는 또한 코딩된 비디오 시퀀스로부터 변환 계수, 양자화기 파라미터 값, 모션 벡터 등과 같은 정보를

추출할 수 있다.

[0023] 파서(320)는 버퍼 메모리(315)로부터 수신된 비디오 시퀀스에 대해 엔트로피 디코딩/파싱 동작을 수행하여, 심벌들(321)을 생성할 수 있다.

[0024] 심벌들(321)의 재구성은(인터 및 인트라 픽처, 인터 및 인트라 블록과 같은) 코딩된 비디오 픽처 또는 그의 부분들의 탑입, 및 다른 인자들에 따라 다수의 상이한 유닛들을 수반할 수 있다. 어느 유닛들이 수반되는지, 그리고 그 방식은 파서(320)에 의해 코딩된 비디오 시퀀스로부터 파싱된 서브그룹 제어 정보에 의해 제어될 수 있다. 파서(320)와 아래의 다수의 유닛 사이의 이러한 서브그룹 제어 정보의 흐름은 명확성을 위해 묘사되어 있지 않다.

[0025] 이미 언급된 기능 블록들 이외에, 비디오 디코더(310)는 아래에 설명되는 바와 같이 개념적으로 다수의 기능 유닛으로 세분될 수 있다. 상업적 제약 하에서 동작하는 실제 구현에서, 이들 유닛 중 다수는 서로 밀접하게 상호작용하고, 적어도 부분적으로 서로 통합될 수 있다. 그러나, 개시된 주제를 설명하기 위해서는 아래의 기능 유닛들로의 개념적 세분이 적합하다.

[0026] 제1 유닛은 스케일러/역변환 유닛(351)이다. 스케일러/역변환 유닛(351)은, 파서(320)로부터의 심벌(들)(321)로서, 제어 정보뿐만 아니라 양자화된 변환 계수를 수신하고, 제어 정보는 어느 변환을 사용할지, 블록 크기, 양자화 인자, 양자화 스케일링 행렬들 등을 포함한다. 스케일러/역변환 유닛(351)은 집계기(aggregator)(355)에 입력될 수 있는 샘플 값들을 포함하는 블록들을 출력할 수 있다.

[0027] 일부 경우들에서, 스케일러/역변환(351)의 출력 샘플들은 인트라 코딩된 블록; 즉, 이전에 재구성된 픽처들로부터의 예측 정보를 사용하는 것이 아니고, 현재 픽처의 이전에 재구성된 부분들로부터의 예측 정보를 사용할 수 있는 블록에 관련될 수 있다. 이러한 예측 정보는 인트라 픽처 예측 유닛(352)에 의해 제공될 수 있다. 일부 경우들에서, 인트라 픽처 예측 유닛(352)은 현재 픽처 버퍼(358)로부터 폐치된 주위의 이미 재구성된 정보를 사용하여, 재구성 중인 블록의 동일한 크기 및 형상의 블록을 생성한다. 현재 픽처 버퍼(358)는, 예를 들어, 부분적으로 재구성된 현재 픽처 및/또는 완전히 재구성된 현재 픽처를 버퍼링한다. 집계기(355)는, 일부 경우들에서, 샘플당 기준으로, 인트라 예측 유닛(352)이 생성한 예측 정보를 스케일러/역변환 유닛(351)에 의해 제공된 출력 샘플 정보에 추가한다.

[0028] 다른 경우들에서, 스케일러/역변환 유닛(351)의 출력 샘플들은 인터 코딩되고 잠재적으로 모션 보상된 블록에 관련될 수 있다. 이 경우에, 모션 보상 예측 유닛(353)은 참조 픽처 메모리(357)에 액세스하여 예측에 사용되는 샘플을 폐치할 수 있다. 블록에 관련된 심벌들(321)에 따라 폐치된 샘플들을 모션 보상한 이후에, 이들 샘플은 집계기(355)에 의해 스케일러/역변환 유닛(351)의 출력(이 경우 잔차 샘플들 또는 잔차 신호라고 불림)에 추가되어 출력 샘플 정보를 생성할 수 있다. 모션 보상 예측 유닛(353)이 그로부터 예측 샘플들을 폐치하는 참조 픽처 메모리(357) 내의 어드레스들은, 예를 들어 X, Y, 및 참조 픽처 커포넌트들을 가질 수 있는 심벌들(321)의 형태로 모션 보상 예측 유닛(353)에 이용가능한 모션 벡터들에 의해 제어될 수 있다. 모션 보상은 또한 서브샘플 정확한 모션 벡터들이 사용중일 때 참조 픽처 메모리(357)로부터 폐치된 샘플 값들의 보간, 모션 벡터 예측 메커니즘 등을 포함할 수 있다.

[0029] 집계기(355)의 출력 샘플들에 대해 루프 필터 유닛(356) 내의 다양한 루프 필터링 기법들이 적용될 수 있다. 비디오 압축 기술들은, 파서(320)로부터의 심벌들(321)로서 루프 필터 유닛(356)에 이용가능하게 되고 코딩된 비디오 시퀀스(코딩된 비디오 비트스트림이라고도 지칭됨)에 포함된 파라미터들에 의해 제어되지만, 코딩된 픽처 또는 코딩된 비디오 시퀀스의 이전(디코딩 순서로) 부분들의 디코딩 동안 획득된 메타-정보에 응답할 뿐만 아니라, 이전에 재구성된 및 루프-필터링된 샘플 값들에 응답할 수도 있는 인-루프 필터(in-loop filter) 기술들을 포함할 수 있다.

[0030] 루프 필터 유닛(356)의 출력은 렌더링 디바이스(312)에 출력될 뿐만 아니라 미래의 인터-픽처 예측에서 사용하기 위해 참조 픽처 메모리(357)에 저장될 수도 있는 샘플 스트림일 수 있다.

[0031] 특정 코딩된 픽처들은, 완전히 재구성되면, 미래 예측을 위한 참조 픽처들로서 사용될 수 있다. 예를 들어, 현재 픽처에 대응하는 코딩된 픽처가 완전히 재구성되고 코딩된 픽처가 참조 픽처로서 식별되면(예를 들어, 파서(320)에 의해), 현재 픽처 버퍼(358)는 참조 픽처 메모리(357)의 일부가 될 수 있고, 다음 코딩된 픽처의 재구성에 착수하기 전에 새로운 현재 픽처 버퍼가 재할당될 수 있다.

[0032] 비디오 디코더(310)는 ITU-T Rec. H.265와 같은 표준에서의 미리 결정된 비디오 압축 기술에 따라 디코딩 동작들을 수행할 수 있다. 코딩된 비디오 시퀀스가 비디오 압축 기술 또는 표준의 신박스, 또는 비디오 압축 기술

또는 표준에서 문서화된 프로파일들 양자 모두를 고수한다는 점에서, 코딩된 비디오 시퀀스는 사용중인 비디오 압축 기술 또는 표준에 의해 지정된 선택스를 준수할 수 있다. 구체적으로, 프로파일은 비디오 압축 기술 또는 표준에서 이용가능한 모든 도구들로부터 해당 프로파일 하에서 사용하기 위해 이용가능한 전용 도구들로서 특정 도구들을 선택할 수 있다. 또한 준수를 위해, 코딩된 비디오 시퀀스의 복잡도가 비디오 압축 기술 또는 표준의 레벨에 의해 정의된 경계 내에 있는 것이 필요할 수 있다. 일부 경우들에서, 레벨들은 최대 픽처 크기, 최대 프레임 레이트, 최대 재구성 샘플 레이트(예를 들어, 초당 메가샘플로 측정됨), 최대 참조 픽처 크기 등을 제한한다. 레벨들에 의해 설정된 한계들은, 일부 경우들에서, HRD(Hypothetical Reference Decoder) 사양들 및 코딩된 비디오 시퀀스에서 시그널링된 HRD 베퍼 관리를 위한 메타데이터를 통해 추가로 제한될 수 있다.

[0033] 일 실시예에서, 수신기(331)는 인코딩된 비디오와 함께 추가적인(중복) 데이터를 수신할 수 있다. 이 추가적인 데이터는 코딩된 비디오 시퀀스(들)의 일부로서 포함될 수 있다. 이 추가적인 데이터는 데이터를 적절히 디코딩하고/하거나 원본 비디오 데이터를 더 정확하게 재구성하기 위해 비디오 디코더(310)에 의해 사용될 수 있다. 추가적인 데이터는 예를 들어, 시간, 공간, 또는 신호 잡음 비(SNR) 향상 층들, 중복 슬라이스들, 중복 픽처들, 순방향 오류 정정 코드들 등의 형태일 수 있다.

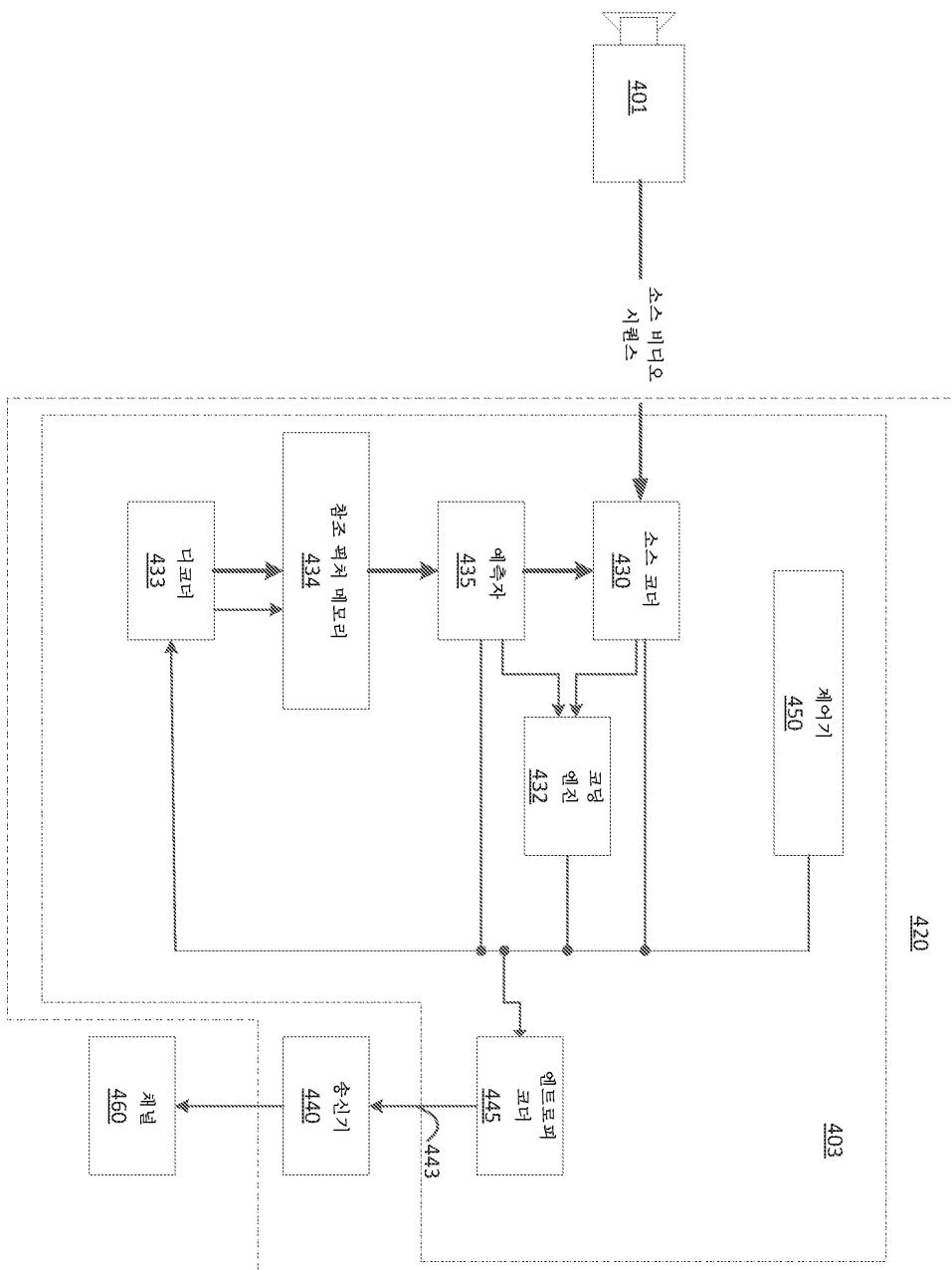

[0034] 도 4는 본 개시내용 콘텐츠의 일 실시예에 따른 비디오 인코더(403)의 블록도를 도시한다. 비디오 인코더(403)는 전자 디바이스(420)에 포함된다. 전자 디바이스(420)는 송신기(440)(예를 들어, 송신 회로)를 포함한다. 비디오 인코더(403)는 도 2의 예에서의 비디오 인코더(203) 대신에 사용될 수 있다.

[0035] 비디오 인코더(403)는 비디오 인코더(403)에 의해 코딩될 비디오 이미지(들)를 캡처할 수 있는 비디오 소스(401)(도 4의 예에서는 전자 디바이스(420)의 일부가 아님)로부터 비디오 샘플들을 수신할 수 있다. 다른 예에서, 비디오 소스(401)는 전자 디바이스(420)의 일부이다.

[0036] 비디오 소스(401)는, 임의의 적절한 비트 심도(예를 들어: 8 비트, 10 비트, 12 비트, ...), 임의의 색공간(예를 들어, BT.601 Y CrCB, RGB, ...), 및 임의의 적절한 샘플링 구조(예를 들어, Y CrCb 4:2:0, Y CrCb 4:4:4) 일 수 있는 디지털 비디오 샘플 스트림의 형태로 비디오 인코더(403)에 의해 코딩될 소스 비디오 시퀀스를 제공할 수 있다. 미디어 서빙 시스템에서, 비디오 소스(401)는 이전에 준비된 비디오를 저장하는 저장 디바이스일 수 있다. 영상 회의 시스템에서, 비디오 소스(401)는 비디오 시퀀스로서 로컬 이미지 정보를 캡처하는 카메라일 수 있다. 비디오 데이터는 순차적으로 볼 때 모션을 부여하는 복수의 개별 픽처로서 제공될 수 있다. 픽처들 자체는 픽셀들의 공간 어레이로서 조직될 수 있고, 여기서 각각의 픽셀은 사용 중인 샘플링 구조, 색 공간 등에 따라 하나 이상의 샘플을 포함할 수 있다. 본 기술분야의 통상의 기술자는 픽셀들과 샘플들 사이의 관계를 쉽게 이해할 수 있다. 아래의 설명은 샘플들에 초점을 둔다.

[0037] 일 실시예에 따르면, 비디오 인코더(403)는 소스 비디오 시퀀스의 픽처들을 실시간으로 또는 응용에 의해 요구되는 임의의 다른 시간 제약들 하에서 코딩된 비디오 시퀀스(443)로 코딩 및 압축할 수 있다. 적절한 코딩 속도를 집행하는 것이 제어기(450)의 하나의 기능이다. 일부 실시예들에서, 제어기(450)는 아래에 설명되는 바와 같이 다른 기능 유닛들을 제어하고 다른 기능 유닛들에 기능적으로 결합된다. 결합은 명확성을 위해 묘사되어 있지 않다. 제어기(450)에 의해 설정된 파라미터들은 레이트 제어 관련 파라미터들(픽처 스킁, 양자화기, 레이트-왜곡 최적화 기법들의 람다 값들, ...), 픽처 크기, 픽처 그룹(GOP) 레이아웃, 최대 모션 벡터 검색 범위 등을 포함할 수 있다. 제어기(450)는 특정 시스템 설계에 대해 최적화된 비디오 인코더(403)에 관련된 다른 적절한 기능들을 갖도록 구성될 수 있다.

[0038] 일부 실시예들에서, 비디오 인코더(403)는 코딩 루프에서 동작하도록 구성된다. 과도하게 단순화된 설명으로서, 일 예에서, 코딩 루프는 소스 코더(430)(예를 들어, 코딩될 입력 픽처, 및 참조 픽처(들)에 기초하여 심벌 스트림과 같은 심벌들을 생성하는 것을 담당함), 및 비디오 인코더(403)에 임베드된 (로컬) 디코더(433)를 포함할 수 있다. 디코더(433)는 (원격) 디코더가 또한 생성하는 것과 유사한 방식으로 샘플 데이터를 생성하기 위해 심벌들을 재구성한다(심벌들과 코딩된 비디오 비트스트림 사이의 임의의 압축이 개시된 주제에서 고려되는 비디오 압축 기술들에서 무손실이기 때문임). 재구성된 샘플 스트림(샘플 데이터)은 참조 픽처 메모리(434)에 입력된다. 심벌 스트림의 디코딩이 디코더 위치(로컬 또는 원격)와는 독립적으로 비트-동일(bit-exact) 결과들을 야기하기 때문에, 참조 픽처 메모리(434) 내의 콘텐츠도 또한 로컬 인코더와 원격 인코더 사이에서 비트-동일 상태이다. 즉, 인코더의 예측 부분은 디코딩 동안 예측을 사용할 때 디코더가 "알고 있는" 것과 정확히 동일한 샘플 값들을 참조 픽처 샘플로서 "알게" 된다. 참조 픽처 동기성의 이 기본적인 원리(그리고 결과적인 드리프트, 예를 들어, 채널 오류들 때문에 동기성이 유지될 수 없는 경우)는 일부 관련 기술들에서도 사용된다.

[0039] "로컬" 디코더(433)의 동작은 도 3과 관련하여 위에서 이미 상세히 설명된 비디오 디코더(310)와 같은 "원격"

디코더와 동일할 수 있다. 그러나, 또한 도 3을 잠시 참조하면, 심벌들이 이용가능하고 엔트로피 코더(445) 및 파서(320)에 의한 코딩된 비디오 시퀀스로의 심벌들의 인코딩/디코딩이 무손실일 수 있기 때문에, 베피 메모리(315) 및 파서(320)를 포함하는, 비디오 디코더(310)의 엔트로피 디코딩 부분들은 완전히 로컬 디코더(433)에서 구현되지 않을 수 있다.

[0040] 이 시점에서 이루어질 수 있는 관찰은, 디코더에 존재하는 파싱/엔트로피 디코딩을 제외한 임의의 디코더 기술이 또한 필연적으로, 대응하는 인코더에서, 실질적으로 동일한 기능 형태로 존재할 필요가 있다는 점이다. 이러한 이유로, 개시된 주제는 디코더 동작에 초점을 둔다. 인코더 기술들은 포괄적으로 설명된 디코더 기술들의 역이기 때문에 그것들에 대한 설명은 축약될 수 있다. 특정 영역들에서만 더 상세한 설명이 요구되고 아래에 제공된다.

[0041] 동작 동안, 일부 예들에서, 소스 코더(430)는, "참조 픽처"로 지정된 비디오 시퀀스로부터의 하나 이상의 이전에 코딩된 픽처를 참조하여 예측적으로 입력 픽처를 코딩하는, 모션 보상된 예측 코딩을 수행할 수 있다. 이러한 방식으로, 코딩 엔진(432)은 입력 픽처의 픽셀 블록들과 입력 픽처에 대한 예측 참조(들)로서 선택될 수 있는 참조 픽처(들)의 픽셀 블록들 사이의 차이들을 코딩한다.

[0042] 로컬 비디오 디코더(433)는, 소스 코더(430)에 의해 생성된 심벌들에 기초하여, 참조 픽처들로서 지정될 수 있는 픽처들의 코딩된 비디오 데이터를 디코딩할 수 있다. 코딩 엔진(432)의 동작들은 유리하게는 손실 프로세스들일 수 있다. 코딩된 비디오 데이터가 비디오 디코더(도 4에 도시되지 않음)에서 디코딩될 수 있는 경우, 재구성된 비디오 시퀀스는 전형적으로 일부 오류들을 갖는 소스 비디오 시퀀스의 복제본일 수 있다. 로컬 비디오 디코더(433)는 참조 픽처들에 대해 비디오 디코더에 의해 수행될 수 있는 디코딩 프로세스들을 복제하고 재구성된 참조 픽처들이 참조 픽처 캐시(434)에 저장되게 할 수 있다. 이러한 방식으로, 비디오 인코더(403)는 (송신 오류들이 없이) 원단(far-end) 비디오 디코더에 의해 획득될 재구성된 참조 픽처로서 공통 콘텐츠를 갖는 재구성된 참조 픽처들의 사본들을 로컬에 저장할 수 있다.

[0043] 예측자(435)는 코딩 엔진(432)에 대한 예측 검색들을 수행할 수 있다. 즉, 코딩될 새로운 픽처에 대해, 예측자(435)는 새로운 픽처들에 대한 적절한 예측 참조로서 역할할 수 있는 참조 픽처 모션 벡터들, 블록 형상들 등과 같은 특정 메타데이터 또는 샘플 데이터(후보 참조 픽셀 블록들로서)에 대해 참조 픽처 메모리(434)를 검색할 수 있다. 예측자(435)는 적절한 예측 참조들을 찾기 위해 샘플 블록-바이-픽셀 블록(sample block-by-pixel block) 기준으로 동작할 수 있다. 일부 경우들에서, 예측자(435)에 의해 획득된 검색 결과들에 의해 결정된 바와 같이, 입력 픽처는 참조 픽처 메모리(434)에 저장된 다수의 참조 픽처로부터 인출된 예측 참조들을 가질 수 있다.

[0044] 제어기(450)는, 예를 들어, 비디오 데이터를 인코딩하기 위해 사용되는 파라미터들 및 서브그룹 파라미터들의 설정을 포함하여, 소스 코더(430)의 코딩 동작을 관리할 수 있다.

[0045] 앞서 설명한 모든 기능 유닛들의 출력은 엔트로피 코더(445)에서 엔트로피 코딩을 겪을 수 있다. 엔트로피 코더(445)는 다양한 기능 유닛들에 의해 생성된 심벌들을, 허프만 코딩, 가변 길이 코딩, 산술 코딩 등과 같은 기술들에 따라 심벌들을 무손실 압축함으로써, 코딩된 비디오 시퀀스로 변환한다.

[0046] 송신기(440)는 인코딩된 비디오 데이터를 저장할 저장 디바이스에 대한 하드웨어/소프트웨어 링크일 수 있는 통신 채널(460)을 통한 송신을 준비하기 위해 엔트로피 코더(445)에 의해 생성된 코딩된 비디오 시퀀스(들)를 베피링할 수 있다. 송신기(440)는 비디오 코더(403)로부터의 코딩된 비디오 데이터를 송신될 다른 데이터, 예를 들어, 코딩된 오디오 데이터 및/또는 보조 데이터 스트림(소스들이 도시되지 않음)과 병합할 수 있다.

[0047] 제어기(450)는 비디오 인코더(403)의 동작을 관리할 수 있다. 코딩 동안, 제어기(450)는 특정 코딩된 픽처 타입을 각각의 코딩된 픽처에 할당할 수 있으며, 이는 각각의 픽처에 적용될 수 있는 코딩 기법들에 영향을 미칠 수 있다. 예를 들어, 픽처들은 종종 다음 픽처 타입들 중 하나로서 할당될 수 있다:

[0048] 인트라 픽처(I 픽처)는 예측의 소스로서 시퀀스 내의 임의의 다른 픽처를 사용하지 않고 코딩되고 디코딩될 수 있는 것일 수 있다. 일부 비디오 코덱들은, 예를 들어, "IDR(Independent Decoder Refresh)" 픽처들을 포함하는, 상이한 타입의 인트라 픽처들을 허용한다. 본 기술분야의 통상의 기술자는 I 픽처들의 해당 변형들 및 그 각각의 응용들 및 특징들을 인지하고 있다.

[0049] 예측 픽처(P 픽처)는 각각의 블록의 샘플 값들을 예측하기 위해 최대 하나의 모션 벡터 및 참조 인덱스를 사용하여 인트라 예측 또는 인터 예측을 사용하여 코딩되고 디코딩될 수 있는 것일 수 있다.

- [0050] 양방향 예측 픽처(B 픽처)는 각각의 블록의 샘플 값들을 예측하기 위해 최대 2개의 모션 벡터 및 참조 인덱스를 사용하여 인트라 예측 또는 인터 예측을 사용하여 코딩되고 디코딩될 수 있는 것일 수 있다. 유사하게, 다중-예측 픽처들은 단일 블록의 재구성을 위해 2개보다 많은 참조 픽처 및 연관된 메타데이터를 사용할 수 있다.

- [0051] 소스 픽처들은 일반적으로 복수의 샘플 블록(예를 들어, 각각 4x4, 8x8, 4x8, 또는 16x16 샘플들의 블록들)으로 공간적으로 세분되고 블록-바이-블록(block-by-block) 기준으로 코딩될 수 있다. 블록들은 블록들의 각각의 픽처들에 적용되는 코딩 할당에 의해 결정된 다른 (이미 코딩된) 블록들을 참조하여 예측적으로 코딩될 수 있다. 예를 들어, I 픽처들의 블록들은 비예측적으로 코딩될 수 있거나 동일한 픽처의 이미 코딩된 블록들을 참조하여 예측적으로 코딩될 수 있다(공간 예측 또는 인트라 예측). P 픽처의 픽셀 블록들은, 하나의 이전에 코딩된 참조 픽처를 참조하여 공간 예측을 통해 또는 시간 예측을 통해, 예측적으로 코딩될 수 있다. B 픽처들의 블록들은, 하나 또는 2개의 이전에 코딩된 참조 픽처를 참조하여 공간 예측을 통해 또는 시간 예측을 통해, 예측적으로 코딩될 수 있다.

- [0052] 비디오 인코더(403)는 ITU-T Rec. H.265와 같은 표준에서의 미리 결정된 비디오 코딩 기술에 따라 코딩 동작들을 수행할 수 있다. 그 동작에서, 비디오 인코더(403)는, 입력 비디오 시퀀스에서 시간 및 공간 중복성을 활용하는 예측 코딩 동작을 비롯한, 다양한 압축 동작을 수행할 수 있다. 따라서, 코딩된 비디오 데이터는 사용중인 비디오 코딩 기술 또는 표준에 의해 지정된 신택스를 준수할 수 있다.

- [0053] 일 실시예에서, 송신기(440)는 인코딩된 비디오와 함께 추가적인 데이터를 송신할 수 있다. 소스 코더(430)는 코딩된 비디오 시퀀스의 일부로서 이러한 데이터를 포함할 수 있다. 추가적인 데이터는 시간/공간/SNR 향상 계층들, 중복 픽처들 및 슬라이스들과 같은 다른 형태의 중복 데이터, SEI 메시지들, VUI 파라미터 세트 프래그먼트들 등을 포함할 수 있다.

- [0054] 비디오는 시간 시퀀스의 복수의 소스 픽처들(비디오 픽처들)로서 캡처될 수 있다. 인트라-픽처 예측(종종 인트라 예측으로 축약됨)은 주어진 픽처에서 공간 상관을 사용하고, 인터-픽처 예측은 픽처들 사이의 (시간 또는 다른) 상관을 사용한다. 일 예에서, 현재 픽처라고 지칭되는, 인코딩/디코딩 중인 특정 픽처가 블록들로 분할된다. 현재 픽처 내의 블록이 비디오 내의 이전에 코딩되고 여전히 베퍼링되어 있는 참조 픽처 내의 참조 블록과 유사할 때, 현재 픽처 내의 블록은 모션 벡터라고 지칭되는 벡터에 의해 코딩될 수 있다. 모션 벡터는 참조 픽처 내의 참조 블록을 가리키고, 다수의 참조 픽처가 사용중인 경우, 참조 픽처를 식별하는 제3 차원을 가질 수 있다.

- [0055] 일부 실시예들에서, 인터-픽처 예측에서 양방향 예측(bi-prediction) 기법이 사용될 수 있다. 양방향 예측 기법에 따르면, 양자 모두 비디오 내의 현재 픽처에 디코딩 순서가 앞서는(그러나, 디스플레이 순서에서, 과거 및 미래에 각각 있을 수 있는) 제1 참조 픽처 및 제2 참조 픽처와 같은 2개의 참조 픽처가 사용된다. 현재 픽처 내의 블록은 제1 참조 픽처 내의 제1 참조 블록을 가리키는 제1 모션 벡터 및 제2 참조 픽처 내의 제2 참조 블록을 가리키는 제2 모션 벡터에 의해 코딩될 수 있다. 블록은 제1 참조 블록과 제2 참조 블록의 조합에 의해 예측될 수 있다.

- [0056] 또한, 코딩 효율을 개선시키기 위해 인터-픽처 예측에서 병합 모드 기법이 사용될 수 있다.

- [0057] 본 개시내용의 일부 실시예들에 따르면, 인터-픽처 예측들 및 인트라-픽처 예측들과 같은 예측들이 블록들의 단위로 수행된다. 예를 들어, HEVC 표준에 따르면, 비디오 픽처들의 시퀀스 내의 픽처는 압축을 위해 코딩 트리 유닛들(CTU)로 분할되고, 픽처 내의 CTU들은 64x64 픽셀들, 32x32 픽셀들, 또는 16x16 픽셀들과 같은 동일한 크기를 갖는다. 일반적으로, CTU는 3개의 코딩 트리 블록(CTB)을 포함하는데, 이는 하나의 루마 CTB 및 2개의 크로마 CTB이다. 각각의 CTU는 하나 또는 다수의 코딩 유닛(CU)들로 재귀적으로 쿼드트리 분할될 수 있다. 예를 들어, 64x64 픽셀들의 CTU는 64x64 픽셀들의 하나의 CU, 또는 32x32 픽셀들의 4개의 CU, 또는 16x16 픽셀들의 16개의 CU로 분할될 수 있다. 일 예에서, 각각의 CU는, 인터 예측 타입 또는 인트라 예측 타입과 같은, CU에 대한 예측 타입을 결정하기 위해 분석된다. CU는 시간 및/또는 공간 예측성에 따라 하나 이상의 예측 유닛(PU)으로 분할된다. 일반적으로, 각각의 PU는 루마 예측 블록(PB), 및 2개의 크로마 PB를 포함한다. 일 실시예에서, 코딩(인코딩/디코딩)에서의 예측 동작은 예측 블록의 단위로 수행된다. 예측 블록의 예로서 루마 예측 블록을 사용하여, 예측 블록은, 8x8 픽셀들, 16x16 픽셀들, 8x16 픽셀들, 16x8 픽셀들 등과 같은, 픽셀들에 대한 값들(예를 들어, 루마 값들)의 행렬을 포함한다.

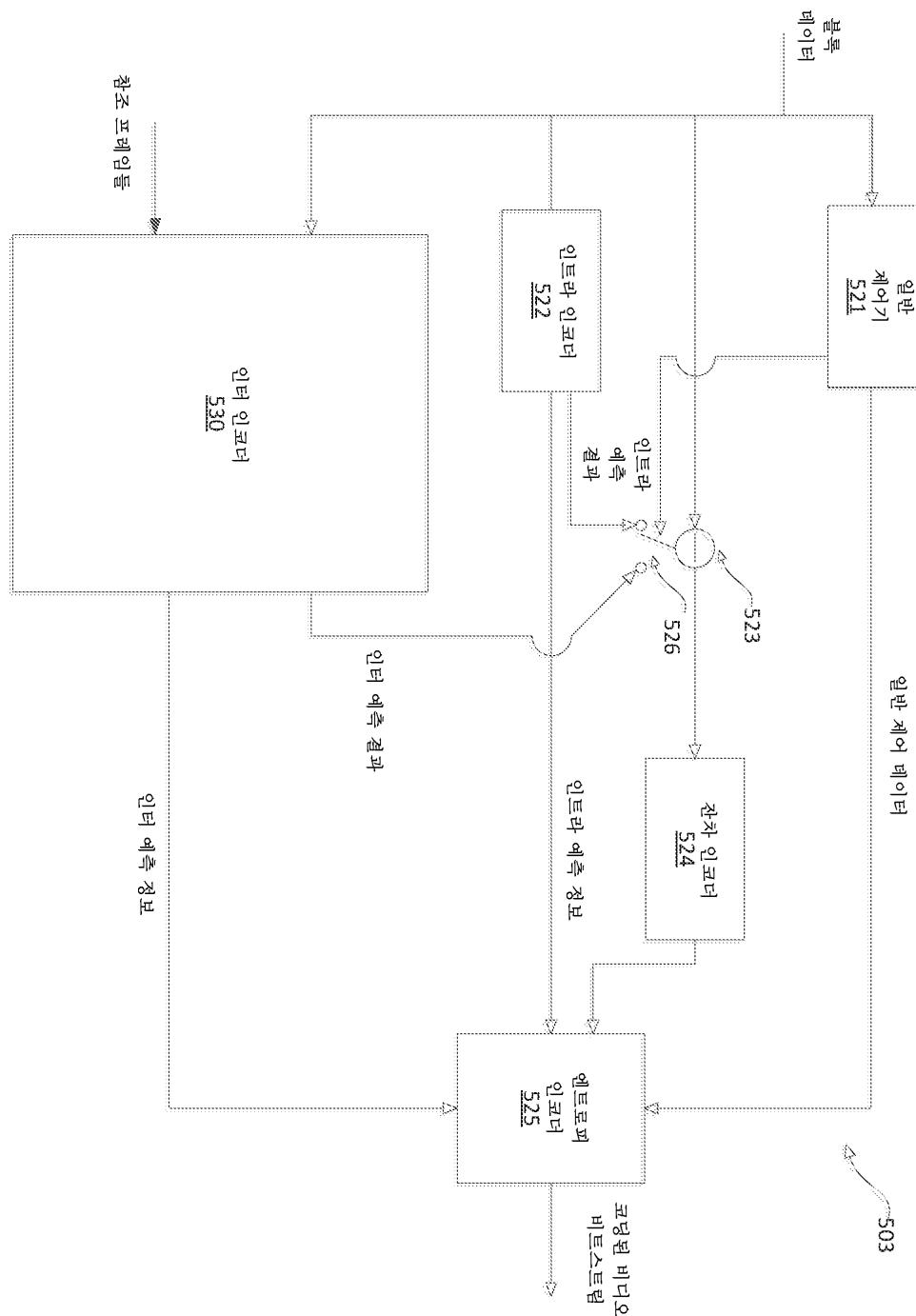

- [0058] 도 5는 본 개시내용의 다른 실시예에 따른 비디오 인코더(503)의 도면을 도시한다. 비디오 인코더(503)는 비디오 픽처들의 시퀀스에서 현재 비디오 픽처 내의 샘플 값들의 처리 블록(예를 들어, 예측 블록)을 수신하고, 처

리 블록을 코딩된 비디오 시퀀스의 일부인 코딩된 픽처 내에 인코딩하도록 구성된다. 일 예에서, 비디오 인코더(503)는 도 2의 예에서의 비디오 인코더(203) 대신에 사용된다.

[0059] HEVC 예에서, 비디오 인코더(503)는 8x8 샘플들 등의 예측 블록과 같은 처리 블록에 대한 샘플 값들의 행렬 등을 수신한다. 비디오 인코더(503)는 처리 블록이, 예를 들어, 레이트-왜곡 최적화를 사용하여 인트라 모드, 인터 모드, 또는 양방향 예측 모드 중 어느 것을 사용하여 최선으로 코딩되는지 여부를 결정한다. 처리 블록이 인트라 모드로 코딩되어야 할 때, 비디오 인코더(503)는 인트라 예측 기법을 사용하여 처리 블록을 코딩된 픽처 내에 인코딩할 수 있고; 그리고, 처리 블록이 인터 모드 또는 양방향 예측 모드로 코딩될 때, 비디오 인코더(503)는 인터 예측 또는 양방향 예측 기법을 각각 사용하여 처리 블록을 코딩된 픽처 내에 인코딩할 수 있다. 특정 비디오 코딩 기술들에서, 병합 모드는 예측자들 외부의 코딩된 모션 벡터 성분의 이점 없이 하나 이상의 모션 벡터 예측자들로부터 모션 벡터가 유도되는 인터 픽처 예측 서브모드일 수 있다. 특정 다른 비디오 코딩 기술들에서, 대상 블록에 적용가능한 모션 벡터 성분이 존재할 수 있다. 일 예에서, 비디오 인코더(503)는 처리 블록들의 모드를 결정하기 위한 모드 결정 모듈(도시되지 않음)과 같은 다른 컴포넌트들을 포함한다.

[0060] 도 5의 예에서, 비디오 인코더(503)는 도 5에 도시된 바와 같이 함께 결합된 인터 인코더(530), 인트라 인코더(522), 잔차 계산기(523), 스위치(526), 잔차 인코더(524), 일반 제어기(521), 및 엔트로피 인코더(525)를 포함한다.

[0061] 인터 인코더(530)는 현재 블록(예를 들어, 처리 블록)의 샘플들을 수신하고, 블록을 참조 픽처들 내의 하나 이상의 참조 블록(예를 들어, 이전 픽처들 및 나중 픽처들 내의 블록들)과 비교하고, 인터 예측 정보(예를 들어, 인터 인코딩 기법에 따른 중복 정보의 설명, 모션 벡터들, 병합 모드 정보)를 생성하고, 임의의 적절한 기법을 사용하여 인터 예측 정보에 기초하여 인터 예측 결과들(예를 들어, 예측된 블록)을 계산하도록 구성된다. 일부 예들에서, 참조 픽처들은 인코딩된 비디오 정보에 기초하여 디코딩되는 디코딩된 참조 픽처들이다.

[0062] 인트라 인코더(522)는 현재 블록(예를 들어, 처리 블록)의 샘플들을 수신하고, 일부 경우들에서 블록을 동일한 픽처 내의 이미 코딩된 블록들과 비교하고, 변환 이후 양자화된 계수들을 생성하고, 일부 경우들에서 또한 인트라 예측 정보(예를 들어, 하나 이상의 인트라 인코딩 기법에 따른 인트라 예측 방향 정보)를 수신하도록 구성된다. 일 예에서, 인트라 인코더(522)는 또한 동일한 픽처 내의 참조 블록들 및 인트라 예측 정보에 기초하여 인트라 예측 결과들(예를 들어, 예측 블록)을 계산한다.

[0063] 일반 제어기(521)는 일반 제어 데이터를 결정하고 일반 제어 데이터에 기초하여 비디오 인코더(503)의 다른 컴포넌트들을 제어하도록 구성된다. 일 예에서, 일반 제어기(521)는 블록의 모드를 결정하고, 모드에 기초하여 스위치(526)에 제어 신호를 제공한다. 예를 들어, 모드가 인트라 모드일 때, 일반 제어기(521)는 잔차 계산기(523)에 의한 사용을 위해 인트라 모드 결과를 선택하도록 스위치(526)를 제어하고, 인트라 예측 정보를 선택하고 인트라 예측 정보를 비트스트림에 포함시키도록 엔트로피 인코더(525)를 제어하며; 그리고, 모드가 인터 모드일 때, 일반 제어기(521)는 잔차 계산기(523)에 의한 사용을 위해 인터 예측 결과를 선택하도록 스위치(526)를 제어하고, 인터 예측 정보를 선택하고 인터 예측 정보를 비트스트림에 포함시키도록 엔트로피 인코더(525)를 제어한다.

[0064] 잔차 계산기(523)는 수신된 블록과 인트라 인코더(522) 또는 인터 인코더(530)로부터 선택된 예측 결과들 사이의 차이(잔차 데이터)를 계산하도록 구성된다. 잔차 인코더(524)는 잔차 데이터에 기초하여 동작하여 잔차 데이터를 인코딩하여 변환 계수들을 생성하도록 구성된다. 일 예에서, 잔차 인코더(524)는 잔차 데이터를 공간 도메인으로부터 주파수 도메인으로 변환하고, 변환 계수들을 생성하도록 구성된다. 그 후 변환 계수들에 대해 양자화 처리를 수행하여 양자화된 변환 계수들을 획득한다. 다양한 실시예에서, 비디오 인코더(503)는 또한 잔차 디코더(528)를 포함한다. 잔차 디코더(528)는 역변환을 수행하고, 디코딩된 잔차 데이터를 생성하도록 구성된다. 디코딩된 잔차 데이터는 인트라 인코더(522) 및 인터 인코더(530)에 의해 적절하게 사용될 수 있다. 예를 들어, 인터 인코더(530)는 디코딩된 잔차 데이터 및 인터 예측 정보에 기초하여 디코딩된 블록들을 생성할 수 있고, 인트라 인코더(522)는 디코딩된 잔차 데이터 및 인트라 예측 정보에 기초하여 디코딩된 블록들을 생성할 수 있다. 디코딩된 블록들은 디코딩된 픽처들을 생성하기 위해 적절하게 처리되고 디코딩된 픽처들은 메모리 회로(도시되지 않음)에 버퍼링되고 일부 예들에서 참조 픽처들로서 사용될 수 있다.

[0065] 엔트로피 인코더(525)는 인코딩된 블록을 포함하도록 비트스트림을 포맷하도록 구성된다. 엔트로피 인코더(525)는 HEVC 표준과 같은 적절한 표준에 따라 다양한 정보를 포함하도록 구성된다. 일 예에서, 엔트로피 인코더(525)는 일반 제어 데이터, 선택된 예측 정보(예를 들어, 인트라 예측 정보 또는 인터 예측 정보), 잔차 정보, 및 다른 적절한 정보를 비트스트림 내에 포함시키도록 구성된다. 개시된 주제에 따르면, 인터 모드 또는

양방향 예측 모드 중 어느 하나의 병합 서브모드에서 블록을 코딩할 때, 잔차 정보가 존재하지 않는다는 점에 유의한다.

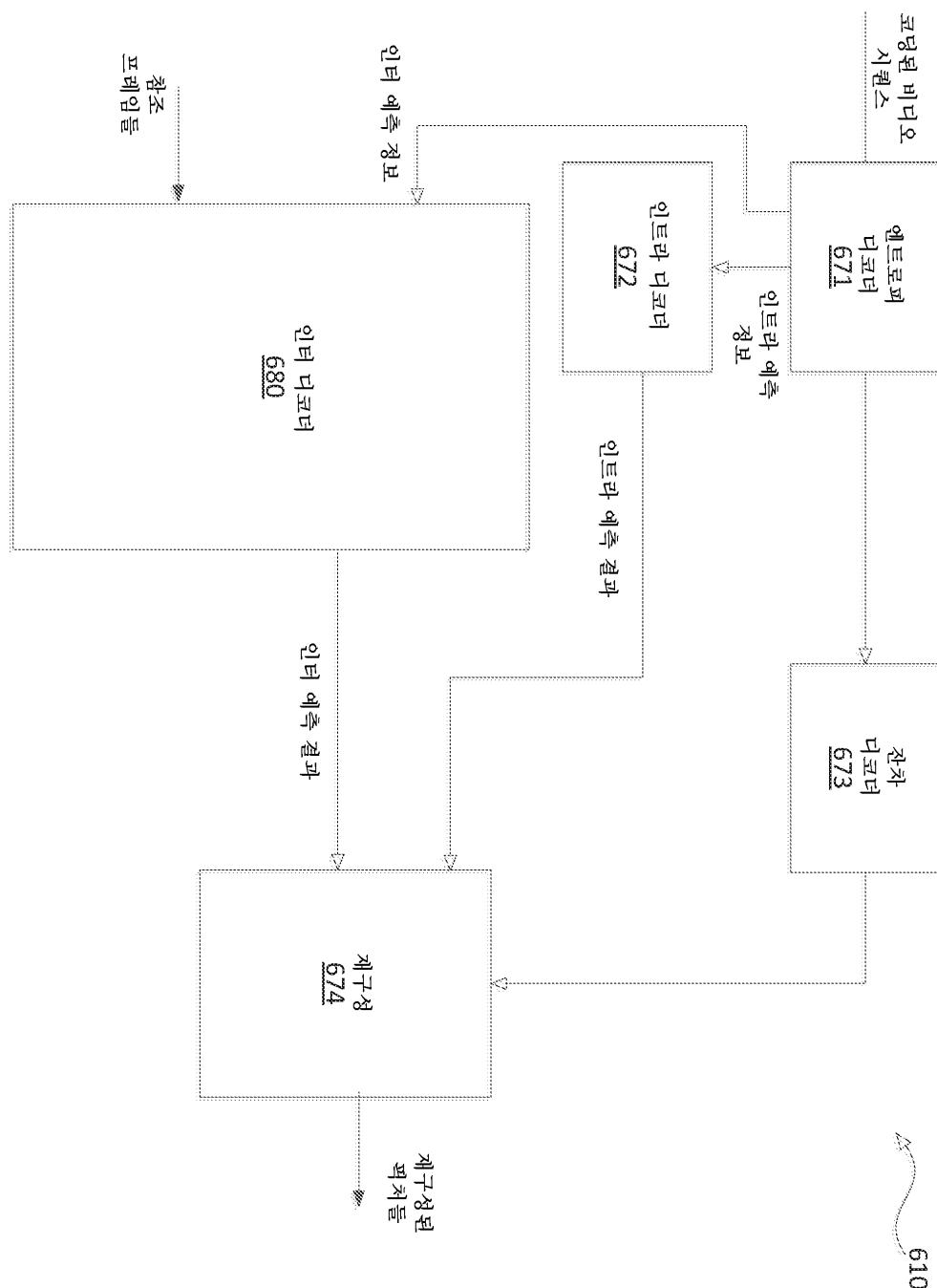

[0066] 도 6은 본 개시내용의 다른 실시예에 따른 비디오 디코더(610)의 도면을 도시한다. 비디오 디코더(610)는 코딩된 비디오 시퀀스의 일부인 코딩된 픽처들을 수신하고, 코딩된 픽처들을 디코딩하여 재구성된 픽처들을 생성하도록 구성된다. 일 예에서, 비디오 디코더(610)는 도 2의 예에서의 비디오 디코더(210) 대신에 사용된다.

[0067] 도 6의 예에서, 비디오 디코더(610)는 도 6에 도시된 바와 같이 함께 결합된 엔트로피 디코더(671), 인터 디코더(680), 잔차 디코더(673), 재구성 모듈(674), 및 인트라 디코더(672)를 포함한다.

[0068] 엔트로피 디코더(671)는, 코딩된 픽처로부터, 코딩된 픽처를 구성하는 신택스 요소들을 나타내는 특정 심벌들을 재구성하도록 구성될 수 있다. 이러한 심벌들은, 예를 들어, 블록이 코딩되는 모드(예컨대, 예를 들어, 인트라 모드, 인터 모드, 양방향 예측 모드, 후자의 둘은 병합 서브모드 또는 다른 서브모드에서임), 인트라 디코더(672) 또는 인터 디코더(680) 각각에 의한 예측을 위해 사용되는 특정 샘플 또는 메타데이터를 식별할 수 있는 예측 정보(예컨대, 예를 들어, 인트라 예측 정보 또는 인터 예측 정보), 예를 들어, 양자화된 변환 계수들의 형태로 된 잔차 정보 등을 포함할 수 있다. 일 예에서, 예측 모드가 인터 또는 양방향 예측 모드일 때, 인터 예측 정보가 인터 디코더(680)에 제공되고; 그리고 예측 타입이 인트라 예측 타입일 때, 인트라 예측 정보가 인트라 디코더(672)에 제공된다. 잔차 정보에 대해 역양자화가 수행될 수 있고 잔차 디코더(673)에 제공된다.

[0069] 인터 디코더(680)는 인터 예측 정보를 수신하고, 인터 예측 정보에 기초하여 인터 예측 결과들을 생성하도록 구성된다.

[0070] 인트라 디코더(672)는 인트라 예측 정보를 수신하고, 인트라 예측 정보에 기초하여 예측 결과들을 생성하도록 구성된다.

[0071] 잔차 디코더(673)는 역양자화를 수행하여 탈양자화된 변환 계수들을 추출하고, 탈양자화된 변환 계수들을 처리하여 잔차를 주파수 도메인으로부터 공간 도메인으로 변환하도록 구성된다. 잔차 디코더(673)는 또한 (양자화기 파라미터(QP)를 포함하도록) 특정 제어 정보를 요구할 수 있고, 그 정보는 엔트로피 디코더(671)에 의해 제공될 수 있다(이는 단지 저용량 제어 정보일 수 있으므로 데이터 경로가 도시되지 않음).

[0072] 재구성 모듈(674)은, 공간 도메인에서, 잔차 디코더(673)에 의해 출력된 잔차와 예측 결과들(경우에 따라 인터 또는 인트라 예측 모듈에 의해 출력된 것)을 조합하여 재구성된 블록을 형성하도록 구성하고, 재구성된 블록은 재구성된 픽처의 일부일 수 있고, 재구성된 픽처는 결국 재구성된 비디오의 일부일 수 있다. 시각적 품질을 개선하기 위해 디블로킹 동작 등과 같은 다른 적절한 동작들이 수행될 수 있다는 점에 유의한다.

[0073] 비디오 인코더들(203, 403, 및 503), 및 비디오 디코더들(210, 310, 및 610)은 임의의 적합한 기법을 사용하여 구현될 수 있다는 점에 유의한다. 일 실시예에서, 비디오 인코더들(203, 403, 및 503), 및 비디오 디코더들(210, 310, 및 610)은 하나 이상의 집적 회로를 사용하여 구현될 수 있다. 다른 실시예에서, 비디오 인코더들(203, 403, 및 503), 및 비디오 디코더들(210, 310, 및 610)은 소프트웨어 명령어들을 실행하는 하나 이상의 프로세서를 사용하여 구현될 수 있다.

[0074] 병합 후보들은 현재 블록의 공간적 또는 시간적 이웃 블록들로부터 모션 정보를 체크함으로써 형성될 수 있다. 도 7을 참조하면, 현재 블록(701)은 공간적으로 시프트된 동일한 크기의 이전 블록으로부터 예측가능한 것으로 모션 검색 프로세스 동안 인코더/디코더에 의해 발견된 샘플들을 포함한다. 일부 실시예들에서, 모션 벡터를 직접 코딩하는 대신에, 모션 벡터는 D, A, C, B, 및 E(각각 702 내지 706)로 표시되는 5개의 주변 샘플들 중 어느 하나와 연관된 모션 벡터를 사용하여, 하나 이상의 참조 픽처와 연관된 메타데이터로부터, 예를 들어, 가장 최근의(디코딩 순서로) 참조 픽처로부터 도출될 수 있다. 블록들 A, B, C, D, 및 E는 공간 병합 후보들이라고 지칭될 수 있다. 이러한 후보들은 병합 후보 리스트로 순차적으로 체크될 수 있다. 중복된 후보들이 리스트로부터 제거되도록 하기 위해 프루닝 동작이 수행될 수 있다.

[0075] 상이한 픽처로부터의 블록 기반 보상은 모션 보상이라고 지칭될 수 있다. 블록 보상은 또한 동일한 픽처 내의 이전에 재구성된 영역으로부터 행해질 수 있으며, 이는 인트라 픽처 블록 보상, 인트라 블록 사본(intra block copy)(IBC) 또는 현재 픽처 참조(current picture referencing)(CPR)라고 지칭될 수 있다. 예를 들어, 현재 블록과 참조 블록 사이의 오프셋을 나타내는 변위 벡터는 블록 벡터라고 지칭된다. 일부 실시예에 따르면, 블록 벡터는 이미 재구성되고 참조에 이용가능한 참조 블록을 가리킨다. 또한, 병렬 처리를 고려하여, 타일/슬라이스 경계 또는 파면 래더 형상 경계(wavefront ladder-shaped boundary)를 넘은 기준 영역은 또한 블록 벡터

에 의해 참조되지 않도록 배제될 수 있다. 이를 제약으로 인해, 블록 벡터는 모션 보상에서의 모션 벡터와 상이할 수 있고, 여기서 모션 벡터는 임의의  $x$  또는  $y$  방향에서 양수 또는 음수)일 수 있다.

[0076] 블록 벡터의 코딩은 명시적이거나 암시적일 수 있다. 인터 코딩에서 AMVP(Advanced Motion Vector Prediction) 모드라고 때때로 지칭되는 명시적 모드에서, 블록 벡터와 그의 예측자 사이의 차이가 시그널링된다. 암시적 모드에서, 블록 벡터는 병합 모드에서의 모션 벡터와 유사한 방식으로 블록 벡터의 예측자로부터 복구된다. 일부 실시예들에서, 블록 벡터의 해상도는 정수 위치들로 제한된다. 다른 실시예들에서, 블록 벡터의 해상도는 분수 위치들을 가리키도록 허용될 수 있다.

[0077] 블록 레벨에서의 인트라 블록 사본의 사용은 IBC 플래그라고 지칭되는 블록 레벨 플래그를 사용하여 시그널링될 수 있다. 일부 실시예에서, IBC 플래그는 현재 블록이 병합 모드에서 코딩되지 않을 때 시그널링된다. IBC 플래그는 또한 현재 디코딩된 픽처를 참조 픽처로서 처리함으로써 수행되는 참조 인덱스 접근법에 의해 시그널링될 수 있다. HEVC 스크린 콘텐츠 코딩(Screen Content Coding(SCC))에서, 이러한 참조 픽처는 리스트의 최종 위치에 배치된다. 이 특수 참조 픽처는 또한 DPB 내의 다른 시간 참조 픽처들과 함께 관리될 수 있다. IBC는 또한 플립된 IBC(예를 들어, 참조 블록은 현재 블록을 예측하기 위해 사용되기 전에 수평으로 또는 수직으로 플립됨) 또는 라인 기반 IBC(예를 들어,  $M \times N$  코딩 블록 내부의 각각의 보상 유닛은  $M \times 1$  또는  $1 \times N$  라인임)과 같은 변형들을 포함할 수 있다.

[0078] 도 8은 인트라 픽처 블록 보상(예를 들어, 인트라 블록 사본 모드)의 실시예를 예시한다. 도 8에서, 현재 픽처(800)는 이미 코딩/디코딩된 블록 영역들의 세트(즉, 회색 정사각형)와 아직 코딩/디코딩되지 않은 블록 영역들의 세트(즉, 백색 정사각형)를 포함한다. 아직 코딩/디코딩되지 않은 블록 영역들 중 하나의 블록(802)은 이전에 코딩/디코딩된 다른 블록(806)을 가리키는 블록 벡터(804)와 연관될 수 있다. 따라서, 블록(806)과 연관된 임의의 모션 정보가 블록(802)의 코딩/디코딩에 사용될 수 있다.

[0079] 일부 실시예들에서, CPR 모드의 검색 범위는 현재 CTU 내에 있도록 제한된다. CPR 모드에 대한 참조 샘플들을 저장하는 유효 메모리 요건은 샘플들의 1개의 CTU 크기이다. 재구성된 샘플들을 현재  $64 \times 64$  영역에 저장하기 위해 기준의 참조 샘플 메모리를 고려하면,  $64 \times 64$  크기의 참조 샘플 메모리가 3개 더 요구된다. 본 개시내용의 실시예들은 기준 픽셀들을 저장하기 위한 총 메모리 요건이 변경되지 않은 채로 유지되는 동안(1개의 CTU 크기, 총 4개의  $64 \times 64$  참조 샘플 메모리) CPR 모드의 유효 검색 범위를 좌측 CTU의 일부 부분으로 확장한다.

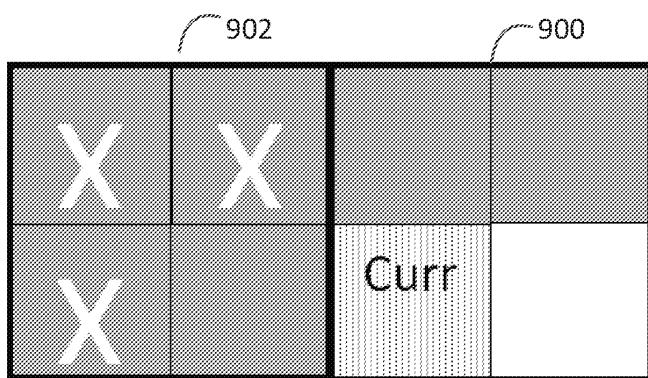

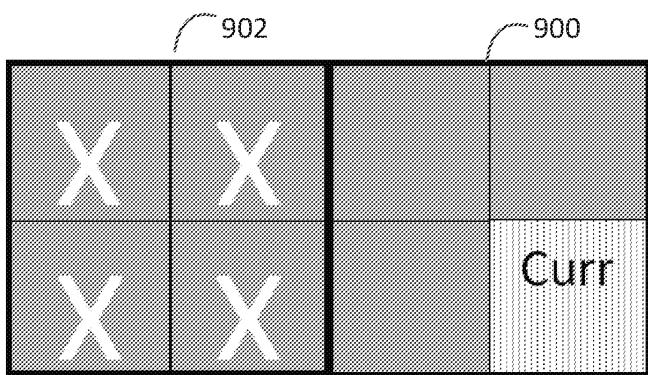

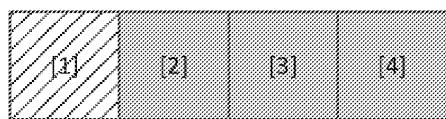

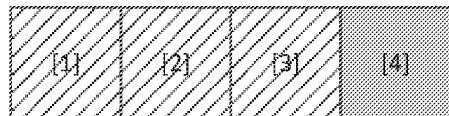

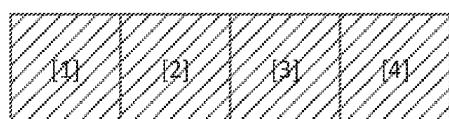

[0080] 도 9a 내지 도 9d는 각각 4개의 영역을 갖는 예시적인 CTU들(900 및 902)을 예시한다. CTU(902)는 CTU(900)의 좌측에 있고, CTU(902)의 4개의 영역 각각은 이전에 디코딩되었다. 도 10a 내지 도 10d는 하나의 CTU의 크기에 대응하는 엔트리 [1]-[4]를 갖는 참조 샘플 메모리의 일 실시예를 예시한다. 참조 샘플 메모리는 미래의 IBC 참조를 위해 이전에 디코딩된 CTU들의 참조 샘플들을 저장할 수 있다. 예를 들어, CTU(902)가 디코딩될 때, 참조 샘플 메모리 엔트리들 [1]-[4]는 CTU(902)의 4개의 영역으로부터의 샘플들로 채워지고, 엔트리 [1]은 좌측 상부 영역에 대응하고, 엔트리 [2]는 우측 상부 영역에 대응하고, 엔트리 [3]은 좌측 하부 영역에 대응하고, 엔트리 [4]는 우측 하부 영역에 대응한다. 참조 샘플 메모리의 엔트리가 채워지면, 그 엔트리는 미래의 IBC 참조에 이용가능한 샘플들을 포함한다.

[0081] 도 9a에서, CTU(900)의 좌측 상부 영역은 디코딩되고 있는 현재 영역이다. CTU(900)의 좌측 상부 영역이 디코딩될 때, 참조 샘플 메모리의 엔트리 [1]은 도 10a에 예시된 바와 같이, 이 영역으로부터 샘플들로 덮어쓰기된다(예를 들어, 덮어쓰기된 메모리 위치(들)는 대각선 크로스-해칭된다). 도 9b에서, CTU(900)의 우측 상부 영역은 디코딩되고 있는 다음 현재 영역이다. CTU(900)의 우측 상부 영역이 디코딩될 때, 참조 샘플 메모리의 엔트리 [2]는 도 10b에 예시된 바와 같이, 이 영역으로부터 샘플들로 덮어쓰기된다. 도 9c에서, CTU(900)의 좌측 하부 영역은 디코딩되고 있는 다음 현재 영역이다. CTU(900)의 좌측 하부 영역이 디코딩될 때, 참조 샘플 메모리의 엔트리 [3]은 도 10c에 예시된 바와 같이, 이 영역으로부터 샘플들로 덮어쓰기된다. 도 9d에서, CTU(900)의 우측 하부 영역은 디코딩되고 있는 다음 현재 영역이다. CTU(900)의 우측 하부 영역이 디코딩될 때, 참조 샘플 메모리의 엔트리 [4]은 도 10d에 예시된 바와 같이, 이 영역으로부터 샘플들로 덮어쓰기된다.

[0082] 본 개시내용의 실시예들은 참조 샘플 메모리의 크기가 제한될 때와 같이, 특정 참조 영역 제약들 하에서 IBC 성능을 향상시킨다. 일부 실시예들에서, 참조 샘플 메모리의 크기는  $128 \times 128$  루마 샘플들(플러스 대응하는 크로마 샘플들)로 제한된다. 일부 예에서, 참조 샘플들의 하나의 CTU 크기는 지정된 메모리 크기라고 간주된다. 추가적인 예들은 CTU 크기에 대한  $64 \times 64$  루마 샘플들(플러스 대응하는 크로마 샘플들) 및 메모리 크기에 대한  $128 \times 128$  루마 샘플(플러스 대응하는 크로마 샘플들) 등과 같은 상이한 메모리 크기/CTU 크기 조합들을 포함한다.

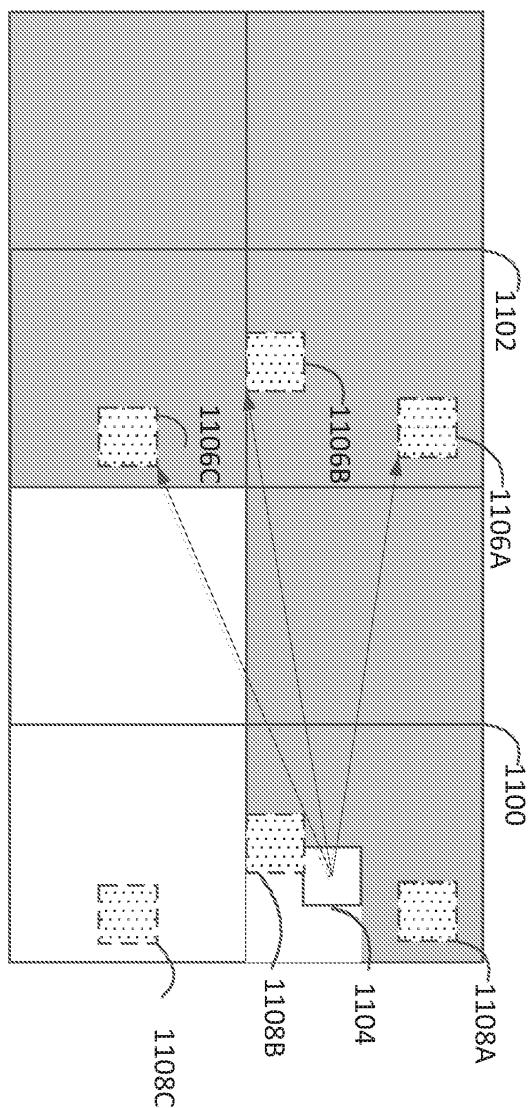

[0083] 도 11은 예시적인 CTU들(1100 및 1102)을 예시한다. 도 11에 예시된 바와 같이, CTU(1102)는 CTU(1100)의 좌측에 있고, 4개의 이전에 디코딩된 영역을 포함한다. CTU(1100)는 디코딩되고 있는 현재 CTU이고, 좌측 상부 영역은 이미 디코딩되어 있다. CTU(1100)의 우측 상부 영역은 디코딩되고 있는 현재 영역이고, 블록(1104)은 디코딩되고 있는 우측 상부 영역의 현재 블록이다. 블록(1104)은 3개의 참조 블록들(1106A-1106C)을 가질 수 있다. 도 11에 도시된 바와 같이, 참조 블록들(1106A-1106C) 각각은 CTU(1100)의 좌측에 있는 CTU(1102)에 위치한다. 블록들(1106A-1106C) 각각 각각은 CTU(1100)에서 각각 병치된 블록들(1108A-1108C)을 갖는다.

[0084] 일부 실시예들에 따르면, 병치된 블록은 이전에 코딩된 CTU 내의 하나의 블록 및 현재 CTU 내의 다른 블록과 동일한 크기를 갖는 블록들의 쌍을 지칭한다. 예를 들어, 메모리 버퍼 크기가 하나의 CTU인 경우, 이전 CTU는 현재 CTU의 좌측에 오프셋된 하나의 CTU 폭 루마 샘플을 갖는 CTU를 의미한다. 또한, 이러한 2개의 블록은 각각 그들 자신의 CTU의 좌측 상단 코너에 대해 동일한 위치 오프셋 값들을 갖는다. 이와 관련하여, 한 쌍의 병치된 블록은 꾹처의 좌측 상단 코너에 대해 동일한 y 좌표를 갖지만 서로에 대해 x 좌표에서의 CTU 폭 차이를 갖는 (즉, 2개의 병치된 블록은 각각의 CTU에서 동일한 위치 좌표들을 가짐) 2개의 블록이다. 예를 들어, 도 11에서, 참조 블록(1106A) 및 그의 병치된 블록(1108A)은 각각 CTU(1102 및 1100)에서 동일한 x, y 좌표를 갖는다. 유사하게, 참조 블록(1106B) 및 그의 병치된 블록(1108B)은 각각 CTU(1102 및 1100)에서 동일한 x, y 좌표를 갖는다. 게다가, 참조 블록(1106C) 및 그의 병치된 블록(1108C)은 각각 CTU(1102 및 1100)에서 동일한 x, y 좌표를 갖는다.

[0085] 도 11에서, 참조 샘플 메모리의 크기는 하나의 CTU라고 가정한다. 따라서, 현재 CTU 내의 대응하는 병치된 블록(1108C)이 아직 디코딩되지 않았기 때문에 참조 블록(1106C)이 참조 샘플 메모리에서 발견될 수 있고, 이는 병치된 블록(1108C)이 백색 영역에 위치하는 것에 의해 입증된다. 따라서, 참조 블록(1106C)에 대응하는 참조 샘플 메모리 내의 위치는 여전히 좌측 CTU로부터의 참조 샘플들을 저장한다.

[0086] 참조 블록(1106C)과 대조적으로, 참조 블록(1106A)은 CTU(1100) 내의 대응하는 병치된 블록(1108A)이 재구성(즉, 디코딩)되었기 때문에 사용될 수 없는데, 이는 병치된 블록(1108A)이 회색 영역에 위치하는 것에 의해 입증된다. 따라서, 참조 블록(1106A)에 대한 참조 샘플 메모리 내의 위치는 CTU(1100)로부터의 참조 샘플들로 업데이트되었고, 따라서 더 이상 이용가능하지 않다. 유사하게, CTU(1100) 내의 대응하는 병치된 블록(1108B)의 일부가 재구성되었기 때문에 참조 블록(1106B)은 디코딩에 사용될 유효 참조 블록이 아니고, 따라서 참조 블록(1106B)에 대응하는 참조 샘플 메모리 내의 위치는 CTU(1100) 내의 데이터로 업데이트되었다.

[0087] 일부 실시예들에 따르면, 현재 CTU 내의 참조 블록의 대응하는 병치된 블록이 아직 재구성되지 않은 경우, 이전에 디코딩된 CTU 내의 참조 블록은 IBC 참조를 위해 사용될 수 있다. 일부 실시예들에서, 현재 CTU 내의 참조 블록의 좌측 상단 코너 샘플의 병치된 샘플이 체크된다. 현재 CTU 내의 병치된 샘플이 아직 재구성되지 않은 경우, 그 참조 블록의 나머지는 IBC 참조를 위해 이용가능하다. 일부 실시예들에서, 메모리 크기가 1개의 CTU이면, 이전에 디코딩된 CTU를 참조하는 것은 현재 CTU의 바로 좌측에 있는 CTU를 참조하는 것을 의미한다.

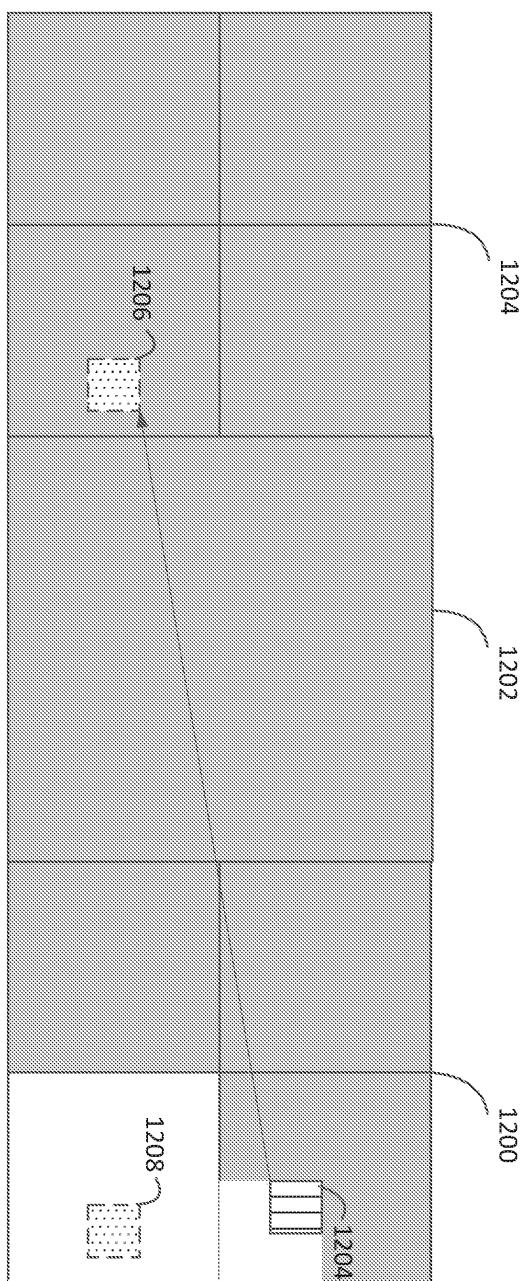

[0088] 메모리 크기가 CTU보다 큰 경우(예를 들어, 참조 샘플 메모리의 2개의 CTU 크기가 허용되는 경우), 이전에 코딩된 CTU는 도 12에 도시된 바와 같이 현재 CTU의 좌측 CTU의 좌측에 있는 CTU를 참조한다. 예를 들어, 도 12에서, CTU(1200)는 디코딩되고 있는 현재 CTU이고, CTU들(1202 및 1204)은 CTU(1200)의 좌측에 있는 2개의 이전에 디코딩된 CTU이다. 블록(1204)은 디코딩되고 있는 현재 블록이고, 참조 블록(1206)은 현재 블록(1204)에 대한 참조 블록이다. 또한, 블록(1208)은 블록(1206)과 병치되어 있다. 그러나, 이 예에서, 블록들(1206 및 1208) 사이의 x 좌표 오프셋은 CTU 폭의 2배이다.

[0089] 일부 실시예들에 따르면, 다음의 조건들은 참이다:

[0090] <수학식 1>

$$( yCb + ( \text{mvL0}[ 1 ] \gg 4 ) ) \gg \text{CtbLog2SizeY} = yCb \gg \text{CtbLog2SizeY}$$

[0092] <수학식 2>

$$( yCb + ( \text{mvL0}[ 1 ] \gg 4 ) + \text{cbHeight} - 1 ) \gg \text{CtbLog2SizeY} = yCb \gg \text{CtbLog2SizeY}$$

[0094] <수학식 3>

$$( xCb + ( \text{mvL0}[ 0 ] \gg 4 ) ) \gg \text{CtbLog2SizeY} \geq ( xCb \gg \text{CtbLog2SizeY} ) - 1$$

[0096] <수학식 4>

[0097]  $(xCb + (mvL0[0] \gg 4) + cbWidth - 1) \gg CtbLog2SizeY \geq (xCb \gg CtbLog2SizeY) - 1$

[0098] 수학식 1-4는 참조 블록을 찾기 위해 사용될 수 있다. 수학식 1 및 2는 참조 블록의 상단 및 하단이 동일한 CTU 행 내부에 있어야 한다는 것을 의미한다. 수학식 3 및 4는 참조 블록의 좌측 및 우측이 현재 또는 좌측 CTU에 있어야 한다는 것을 의미한다. 위의 수학식들에서, xCb 및 yCb는 각각 현재 블록의 x 및 y 좌표이다. 변수들 cbHeight 및 cbWidth는 각각 현재 블록의 높이 및 폭이다. 변수 CtbLog2sizeY는 log2 도메인에서의 CTU 크기를 지칭한다. 예를 들어, CtbLog2sizeY = 7은 CTU 크기가 128x128임을 의미한다. 변수 mvL0[0] 및 mvL0[1]은 각각 블록 벡터 mvL0의 x 및 y 성분을 지칭한다.

[0099] 일부 실시예들에 따르면, 현재 블록의 참조 블록이 현재 블록의 현재 CTU와 상이한 CTU에 있다고 결정될 때, 참조 샘플 메모리는 참조 블록에 대응하는 샘플들이 이용가능한지를 결정하기 위해 체크된다. 일부 실시예들에서, 참조 블록이 현재 CTU와 상이한 CTU에 있는지를 결정하는 것은 다음과 같이 결정된다:

[0100] <수학식 5>

[0101]  $(xCb + (mvL0[0] \gg 4)) \gg CtbLog2SizeY = (xCb \gg CtbLog2SizeY) - 1$

[0102] 현재 블록의 참조 블록이 현재 블록의 CTU와 상이한 CTU에 있을 때, 참조 블록에 대한 샘플들이 참조 메모리에서 이용가능한지를 결정하는 것은, 일부 실시예들에 따르면, 다음을 입력들로서 사용하여 결정된다:

[0103] (i) 현재 블록의 x 및 y 좌표(xCb, yCb); 및

[0104] (ii) 이웃 루마 위치( $(xCb + (mvL0[0] \gg 4) + (1 \ll CtbLog2SizeY), yCb + (mvL0[1] \gg 4))$ ).

[0105] 출력이 거짓이면, 참조 블록에 대한 샘플들이 이용가능한 것으로 결정된다. 예를 들어, 현재 위치(xCb, yCb)에 있는 현재 블록에 대해, 입력들 (i) 및 (ii)는 이웃 블록(xNx, yNb)이 현재 블록에 이용가능한지를 결정하는데 사용된다. 이용가능하다는 것은 블록이 이미 디코딩되었고, (예를 들어, 동일한 타일 내에서) 인트라 예측을 위해 사용될 수 있다는 것을 의미한다.

[0106] 일부 실시예들에 따르면, 현재 블록의 참조 블록이 현재 블록의 CTU와 상이한 CTU에 있을 때, 참조 블록에 대한 샘플들이 참조 샘플 메모리에서 이용가능한지를 결정하기 위해  $2^M \times 2^N$  영역이 체크된다. M 및 N은 양의 정수일 수 있다. 참조 메모리에서  $2^M \times 2^N$  영역이 이용가능한지를 결정하는 것은, 일부 실시예들에 따르면, 다음을 입력들로서 사용하여 결정된다:

[0107] (i) 현재 블록의 x 및 y 좌표(xCb, yCb); 및

[0108] (ii) 이웃 루마 위치( $((xCb + (mvL0[0] \gg 4) + (1 \ll CtbLog2SizeY)) \gg (CtbLog2SizeY - 1)) \ll (CtbLog2SizeY - 1), ((yCb + (mvL0[1] \gg 4)) \gg (CtbLog2SizeY - 1)) \ll (CtbLog2SizeY - 1)$ ).

[0109] 출력이 거짓인 경우, 참조 블록에 대한 샘플들이 이용가능한 것으로 결정된다(예를 들어, 이웃 블록이 인트라 블록 사본 사용을 위해 이용가능함). 예를 들어, M 및 N이 8과 동일하면, 현재 CTU 내의 64x64 영역의 임의의 샘플(현재 샘플이라고 지칭됨)이 재구성되었다면, 현재 샘플의 병치된 샘플이 위치하는 참조 샘플 메모리 내의 대응하는 64x64 영역은 IBC 참조에 이용가능하지 않을 것이다. 이와 같이, 참조 샘플 메모리는 64x64 기준으로 업데이트될 수 있다.

[0110] 일부 실시예들에서, 꾹쳐 내의 CTU들은 폭 또는 높이의 차이가 2배가 되거나 절반으로 줄어드는 가변 크기들을 갖는다. CTU 크기가 절반으로 감소될 때, 이전에 1개의 CTU를 저장했던 참조 샘플 메모리는 이제 4개의 CTU를 저장한다. 따라서, 도 12에 도시된 바와 같이, 현재 CTU의 좌측에 있는 2개의 CTU 대신에, 현재 CTU의 좌측에 4개의 CTU가 있을 것이다. 이러한 시나리오들에서, 가장 좌측의 CTU를 제외하고, 기준 데이터의 4개의 CTU 또는 기준 데이터의 2개의 CTU는, 현재 CTU의 좌측에 있는 다른 CTU들 내의 모든 다른 이전에 코딩된 샘플들이 위의 실시예들에서 조건 체크들을 사용하지 않고 완전히 사용가능하다. 가장 좌측의 CTU의 경우, 위의 실시예들에서의 조건 체크들은 참조 샘플들의 가용성에 대해 유사하지만, x 좌표 오프셋의 조정은 가장 좌측의 CTU에 대해 2개의 CTU가 존재할 때 2\*CTU 폭이고, 가장 좌측의 CTU에 대해 4개의 CTU가 존재할 때 4\*CTU 폭이다.

[0111] 도 13 및 도 14는 재구성 중인 블록에 대한 예측 블록을 생성하기 위해, 인트라 모드에서 코딩된 블록의 재구성에 사용되는 프로세스의 일 실시예를 예시한다. 다양한 실시예들에서, 프로세스는, 단말 디바이스들(110, 120, 130 및 140) 내의 처리 회로, 비디오 인코더(203)의 기능들을 수행하는 처리 회로, 비디오 디코더(210)의 기능들을 수행하는 처리 회로, 비디오 디코더(310)의 기능들을 수행하는 처리 회로, 인트라 예측 모듈(352)의 기능

들을 수행하는 처리 회로, 비디오 인코더(403)의 기능들을 수행하는 처리 회로, 예측기(435)의 기능들을 수행하는 처리 회로, 인트라 인코더(522)의 기능들을 수행하는 처리 회로, 인트라 디코더(672)의 기능들을 수행하는 처리 회로 등과 같은 처리 회로에 의해 실행된다. 일부 실시예들에서, 프로세스는 소프트웨어 명령어들로 구현되고, 따라서 처리 회로가 소프트웨어 명령어들을 실행할 때, 처리 회로는 프로세스를 수행한다.

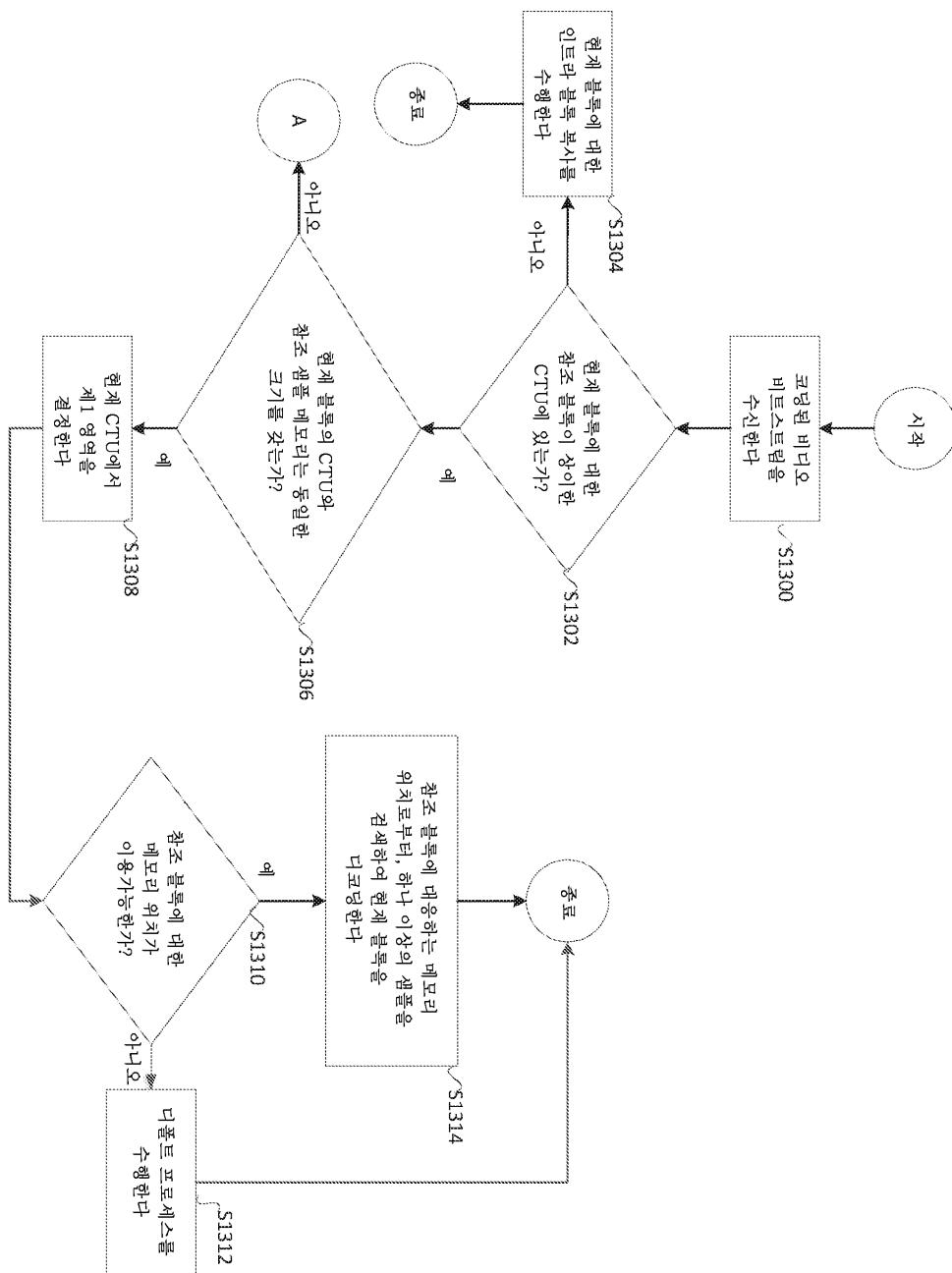

[0112] 프로세스는 일반적으로 코딩된 비디오 비트스트림이 수신되는 단계 S1300에서 시작할 수 있다. 프로세스는 단계 S1302로 진행하고, 여기서 현재 블록에 대한 참조 블록이 현재 블록에 대한 현재 CTU와 상이한 CTU에 있는지가 결정된다. 참조 블록이 상이한 CTU에 있지 않다고 결정되면, 프로세스는 단계 S1304로 진행하고, 여기서 참조 블록을 사용하여 현재 블록에 대해 IBC가 수행된다.

[0113] 참조 블록이 상이한 CTU에 있다고 결정되면, 프로세스는 단계 S1302로부터 단계 S1306으로 진행하고, 여기서 현재 블록의 CTU 및 참조 샘플 메모리가 동일한 크기를 갖는지가 결정된다. 현재 블록의 CTU 및 참조 샘플 메모리의 크기가 동일하지 않으면, 프로세스는 프로세스 A로 진행하며, 이는 아래에 더 상세히 설명된다. 현재 블록의 CTU 및 참조 샘플 메모리의 크기가 동일하면, 프로세스는 단계 S1308로 진행하고, 여기서 현재 CTU에 대해 제1 영역이 결정된다. 일 예로서, 제1 영역은 참조 블록과 병치되는 블록, 또는  $2^M \times 2^N$ 일 수 있고, 여기서 M 및 N은 양의 정수이다.

[0114] 프로세스는 단계 S1310으로 진행하고, 여기서 참조 블록에 대한 메모리 위치가 이용가능한지가 결정된다. 예를 들어, 현재 CTU에 위치된 제1 영역은 상이한 CTU 내의 제2 영역과 병치될 수 있고, 여기서 제2 영역은 참조 블록을 포함한다. 제1 영역이 적어도 부분적으로 재구성되었다면, 참조 샘플 메모리 내의 참조 블록에 대한 메모리 위치가 이용가능하지 않다고 결정된다. 참조 블록에 대한 참조 샘플 메모리 내의 메모리 위치가 이용가능하지 않다고 결정되면, 프로세스는 단계 S1312로 진행하고, 여기서 다른 참조 블록을 선택하는 것과 같은 디폴트 프로세스가 수행된다. 다른 방법에서, 참조 블록에 대한 참조 샘플 메모리 내의 메모리 위치가 이용가능하지 않다고 결정되면, 디폴트 프로세스는  $1 << (\text{bit\_depth}-1)$ 와 같은 현재 블록에 대한 참조 블록을 형성하기 위해 미리 정의된 값을 넣는 것일 수 있고, 여기서 bit\_depth는 샘플당 사용되는 비트들의 깊이이다. 참조 블록에 대한 참조 샘플 메모리 내의 메모리 위치가 이용가능하다면, 프로세스는 단계 S1310으로부터 단계 S1314로 진행하고, 여기서 현재 블록을 디코딩하기 위해 참조 블록에 대응하는 메모리 위치로부터 하나 이상의 샘플이 검색된다.

[0115] 프로세스 A는 일반적으로 현재 블록의 CTU의 크기가 참조 샘플 메모리의 크기보다 작을지가 결정되는 단계 S1400에서 시작할 수 있다. 현재 블록의 CTU의 크기가 참조 샘플 메모리의 크기보다 작지 않은 경우, 프로세스는 단계 S1402로 진행하여 참조 샘플 메모리 내의 참조 블록에 대응하는 메모리 위치가 이용가능한지를 결정한다. 예를 들어, 단계들 S1308 내지 S1312는 전술한 바와 같이 단계 S1402에서 반복될 수 있다.

[0116] 단계 S1400에서, 현재 블록의 CTU의 크기가 참조 샘플 메모리의 크기보다 작다고 결정되면, 프로세스는 단계 S1404로 진행하고, 여기서 참조 블록이 위치하는 상이한 CTU와 현재 블록이 위치하는 현재 CTU 사이의 거리가 임계값 미만인지가 결정된다. 일 예로서, 참조 블록과 현재 블록 사이의 거리는 이러한 블록들의 X 좌표들 사이의 차이에 기초하여 결정될 수 있다. 일 예로서, 임계값은 다음과 같이 정의될 수 있다:

[0117]  $((\text{참조 샘플 메모리 크기}/\text{CTU 크기})-1) * (\text{CTU 폭})$ .

[0118] 참조 블록의 상이한 CTU와 현재 블록의 CTU 사이의 거리가 임계값보다 작으면, 프로세스는 단계 S1406으로 진행하여, 참조 블록에 대응하는 메모리 위치로부터, 하나 이상의 샘플을 검색하여 현재 블록을 디코딩한다. 이와 관련하여, 상이한 CTU의 참조 블록과 현재 블록 사이의 거리가 임계값보다 작을 때, 도 13의 단계들 S1308 내지 S1312에서 설명된 메모리 체크는 수행되지 않는다. 상이한 CTU의 참조 블록과 현재 블록 사이의 거리가 임계값 이상이면, 프로세스는 단계 S1404로부터 단계 S1402로 복귀한다. 도 14에 도시된 프로세스는 단계 S1402 또는 S1404 후에 종료된다.

[0119] 도 14의 시나리오들은 참조 샘플 메모리의 크기가 현재 CTU의 크기보다 2배 큰 도 12에 도시된다. 참조 블록이 CTU(1202)에 위치하는 경우, CTU(1202)와 현재 CTU 사이의 거리는 임계값보다 작을 것이다. 따라서, 이 시나리오에서, 참조 블록에 대응하는 참조 샘플 메모리 내의 메모리 위치가 이용가능할 것이고, 따라서 참조 샘플 메모리의 메모리 체크를 수행하는 것은 필요하지 않다. 참조 블록이 CTU(1204)에 위치하는 경우, CTU(1204)와 현재 CTU 사이의 거리는 임계값 이상일 것이다. 따라서, 이 시나리오에서, 도 13의 단계들 S1308 내지 S1312에서 설명된 메모리 체크는 메모리 위치가 이용가능한지를 결정하기 위해 수행된다.

[0120] 위에서 설명된 기법들은 컴퓨터 판독가능 명령어들을 사용하여 컴퓨터 소프트웨어로서 구현되고 하나 이상의 컴

퓨터 판독가능 매체에 물리적으로 저장될 수 있다. 예를 들어, 도 15는 개시된 주제의 특정 실시예들을 구현하기에 적합한 컴퓨터 시스템(1500)을 도시한다.

[0121] 컴퓨터 소프트웨어는, 하나 이상의 컴퓨터 중앙 처리 유닛(CPU)들, 그래픽 처리 유닛(GPU)들 등에 의해, 직접, 또는 해석, 마이크로-코드 실행 등을 통해 실행될 수 있는 명령어들을 포함하는 코드를 생성하기 위해 어셈블리, 컴파일, 링킹, 또는 유사한 메커니즘들이 수행될 수 있는 임의의 적절한 머신 코드 또는 컴퓨터 언어를 사용하여 코딩될 수 있다.

[0122] 명령어들은, 예를 들어, 개인용 컴퓨터, 태블릿 컴퓨터, 서버, 스마트폰, 게이밍 디바이스, 사물 인터넷 디바이스 등을 포함하여, 다양한 타입의 컴퓨터들 또는 그것의 컴포넌트들 상에서 실행될 수 있다.

[0123] 컴퓨터 시스템(1500)에 대한 도 15에 도시된 컴포넌트들은 사실상 예시적인 것이고, 본 개시내용의 실시예들을 구현하는 컴퓨터 소프트웨어의 사용 또는 기능성의 범위에 대한 임의의 제한을 암시하는 것을 의도하지 않는다. 컴포넌트들의 구성이 컴퓨터 시스템(1500)의 예시적인 실시예에서 예시된 컴포넌트들 중 임의의 하나 또는 이들의 조합과 관련하여 임의의 종속성 또는 요건을 갖는 것으로 해석되어서도 안 된다.

[0124] 컴퓨터 시스템(1500)은 특정 휴면 인터페이스 입력 디바이스들을 포함할 수 있다. 이러한 휴면 인터페이스 입력 디바이스는, 예를 들어, 촉각 입력(예컨대: 키스트로크, 스와이프, 데이터 글러브 움직임), 오디오 입력(예컨대: 음성, 손뼉), 시각적 입력(예컨대: 제스처), 후각 입력(도시되지 않음)을 통한 하나 이상의 인간 사용자에 의한 입력에 응답할 수 있다. 휴면 인터페이스 디바이스들은 또한 오디오(예컨대: 음성, 음악, 주변 사운드), 이미지들(예컨대: 스캐닝된 이미지들, 정지 이미지 카메라로부터 획득된 사진 이미지들), 비디오(예컨대, 2차원 비디오, 입체적 비디오를 포함하는 3차원 비디오)와 같은, 인간에 의한 의식적인 입력과 반드시 직접적으로 관련되지는 않는 특정 미디어를 캡처하기 위해 사용될 수 있다.

[0125] 입력 휴면 인터페이스 디바이스들은 다음 중 하나 이상(각각 하나만이 묘사됨)을 포함할 수 있다: 키보드(1501), 마우스(1502), 트랙패드(1503), 터치 스크린(1510), 데이터-글러브(도시되지 않음), 조이스틱(1505), 마이크로폰(1506), 스캐너(1507), 카메라(1508).

[0126] 컴퓨터 시스템(1500)은 특정 휴면 인터페이스 출력 디바이스들을 또한 포함할 수 있다. 이러한 휴면 인터페이스 출력 디바이스들은, 예를 들어, 촉각 출력, 사운드, 광, 및 냄새/맛을 통해 하나 이상의 인간 사용자의 감각들을 자극하는 것일 수 있다. 이러한 휴면 인터페이스 출력 디바이스들은 촉각 출력 디바이스들(예를 들어 터치-스크린(1510), 데이터-글러브(도시되지 않음), 또는 조이스틱(1505)에 의한 촉각 피드백, 그러나, 입력 디바이스들로서 역할하지 않는 촉각 피드백 디바이스들도 있을 수 있음), 오디오 출력 디바이스들(예컨대: 스피커들(1509), 헤드폰들(도시되지 않음)), 시각적 출력 디바이스들(예컨대, 각각 터치-스크린 입력 능력을 구비하거나 구비하지 않고 각각 촉각 피드백 능력을 구비하거나 구비하지 않는 CRT 스크린들, LCD 스크린들, 플라즈마 스크린들, OLED 스크린들을 포함하는 스크린들(1510)- 이들 중 일부는 스테레오그래픽 출력과 같은 수단을 통해 2차원 시각적 출력 또는 3차원을 초과한 출력을 출력할 수 있을 수 있음 -; 가상 현실 안경(도시되지 않음), 홀로그램 디스플레이들 및 스모크 텅크들(도시되지 않음)), 및 프린터들(도시되지 않음)을 포함할 수 있다.

[0127] 컴퓨터 시스템(1500)은 인간 액세스 가능한 저장 디바이스들 및 그 연관된 매체들, 예컨대 CD/DVD 등의 매체(1521)를 갖는 CD/DVD ROM/RW(1520)를 포함하는 광학 매체, 썬-드라이브(1522), 이동식 하드 드라이브 또는 솔리드 스테이트 드라이브(1523), 테이프 및 플로피 디스크(도시되지 않음)와 같은 래거시 자기 매체, 보안 동글들(도시되지 않음)과 같은 특수화된 ROM/ASIC/PLD 기반 디바이스들 등을 또한 포함할 수 있다.

[0128] 본 기술분야의 통상의 기술자들은 또한, 현재 개시된 주제와 관련하여 사용되는 용어 "컴퓨터 판독가능 매체"가 송신 매체, 반송파들, 또는 다른 일시적 신호들을 포함하지 않는다는 것을 이해해야 한다.

[0129] 컴퓨터 시스템(1500)은 또한 하나 이상의 통신 네트워크에 대한 인터페이스를 포함할 수 있다. 네트워크들은 예를 들어 무선, 유선, 광학일 수 있다. 네트워크들은 추가로 로컬, 광역, 대도시, 차량 및 산업, 실시간, 지연-허용(delay-tolerant) 등일 수 있다. 네트워크들의 예들은 로컬 영역 네트워크들, 예컨대 이더넷, 무선 LAN들, GSM, 3G, 4G, 5G, LTE 등을 포함하는 셀룰러 네트워크들, 케이블 TV, 위성 TV 및 지상파 방송 TV를 포함하는 TV 유선 또는 무선 광역 디지털 네트워크들, CANBus를 포함하는 차량 및 산업 등을 포함한다. 특정 네트워크들은 일반적으로 (예를 들어, 컴퓨터 시스템(1500)의 USB 포트들과 같은) 특정 범용 데이터 포트들 또는 주변 버스들(1549)에 부착되는 외부 네트워크 인터페이스 어댑터들을 요구하고; 다른 것들은 일반적으로 아래에 설명되는 바와 같은 시스템 버스(예를 들어, PC 컴퓨터 시스템으로의 이더넷 인터페이스 또는 스마트폰 컴퓨터 시스템으로의 셀룰러 네트워크 인터페이스)로의 부착에 의해 컴퓨터 시스템(1500)의 코어에 통합된다. 이들 네트워

크들 중 임의의 것을 사용하여, 컴퓨터 시스템(1500)은 다른 엔티티들과 통신할 수 있다. 이러한 통신은 단방 향성 수신 전용(예를 들어, 브로드캐스트 TV), 단방향성 전송 전용(예를 들어, CANbus 대 특정 CANbus 디바이스들), 또는 예를 들어 로컬 또는 광역 디지털 네트워크들을 사용하는 다른 컴퓨터 시스템들과의 양방향성일 수 있다. 전술한 바와 같은 네트워크들 및 네트워크 인터페이스들 각각에 대해 특정 프로토콜들 및 프로토콜 스택들이 사용될 수 있다.

[0130] 앞서 설명한 휴면 인터페이스 디바이스들, 인간-액세스 가능한 저장 디바이스들, 및 네트워크 인터페이스들은 컴퓨터 시스템(1500)의 코어(1540)에 부착될 수 있다.

[0131] 코어(1540)는 하나 이상의 중앙 처리 유닛(CPU)(1541), 그래픽 처리 유닛(GPU)(1542), 필드 프로그램 가능 게이트 영역(FPGA)(1543)의 형태로 특수화된 프로그램 가능 처리 유닛들, 특정 태스크들에 대한 하드웨어 가속기들(1544) 등을 포함할 수 있다. 이들 디바이스는, 판독 전용 메모리(ROM)(1545), 랜덤 액세스 메모리(1546), 내부 비-사용자 액세스 가능 하드 드라이브들, SSD들 등과 같은 내부 대용량 저장소(1547)와 함께, 시스템 버스(1548)를 통해 연결될 수 있다. 일부 컴퓨터 시스템들에서, 시스템 버스(1548)는 추가적인 CPU들, GPU들 등에 의한 확장을 가능하게 하기 위해 하나 이상의 물리적 플러그의 형태로 액세스 가능할 수 있다. 주변 디바이스들은 코어의 시스템 버스(1548)에 직접, 또는 주변 버스(1549)를 통해 부착될 수 있다. 주변 버스를 위한 아키텍처들은 PCI, USB 등을 포함한다.

[0132] CPU들(1541), GPU들(1542), FPGA들(1543), 및 가속기들(1544)은, 조합하여, 전술한 컴퓨터 코드를 구성할 수 있는 특정 명령어들을 실행할 수 있다. 그 컴퓨터 코드는 ROM(1545) 또는 RAM(1546)에 저장될 수 있다. 과도적인 데이터가 또한 RAM(1546)에 저장될 수 있는 반면, 영구 데이터는, 예를 들어, 내부 대용량 저장소(1547)에 저장될 수 있다. 메모리 디바이스들 중 임의의 것에 대한 고속 저장 및 검색은 하나 이상의 CPU(1541), GPU(1542), 대용량 저장소(1547), ROM(1545), RAM(1546) 등과 밀접하게 연관될 수 있는 캐시 메모리의 사용을 통해 가능하게 될 수 있다.

[0133] 컴퓨터 판독가능 매체는 다양한 컴퓨터 구현 동작들을 수행하기 위한 컴퓨터 코드를 그 위에 가질 수 있다. 매체 및 컴퓨터 코드는 본 개시내용의 목적을 위해 특별히 설계되고 구성된 것들일 수 있거나, 또는 이들이 컴퓨터 소프트웨어 기술 분야의 기술자들에게 잘 알려져 있고 이용가능한 종류의 것일 수 있다.

[0134] 제한이 아니라 예로서, 아키텍처를 갖는 컴퓨터 시스템(1500), 및 구체적으로 코어(1540)는 프로세서(들)(CPU들, GPU들, FPGA, 가속기들 등을 포함함)가 하나 이상의 유형의(tangible) 컴퓨터 판독가능 매체에 구현된 소프트웨어를 실행하는 결과로서 기능성을 제공할 수 있다. 이러한 컴퓨터 판독가능 매체는 위에 소개된 바와 같은 사용자-액세스 가능한 대용량 저장소뿐만 아니라, 코어-내부 대용량 저장소(1547) 또는 ROM(1545)과 같은 비일시적 본질의 것인 코어(1540)의 특정 저장소와 연관된 매체일 수 있다. 본 개시내용의 다양한 실시예들을 구현하는 소프트웨어가 그러한 디바이스들에 저장되고 코어(1540)에 의해 실행될 수 있다. 컴퓨터 판독가능 매체는 특정 필요에 따라 하나 이상의 메모리 디바이스 또는 칩을 포함할 수 있다. 소프트웨어는 코어(1540) 및 구체적으로 그 내부의 프로세서들(CPU, GPU, FPGA 등을 포함함)로 하여금, RAM(1546)에 저장된 데이터 구조들을 정의하는 것 및 소프트웨어에 의해 정의된 프로세스들에 따라 이러한 데이터 구조들을 수정하는 것을 포함하여, 본 명세서에 설명된 특정 프로세스들 또는 특정 프로세스들의 특정 부분들을 실행하게 할 수 있다. 그에 부가하여 또는 대안으로서, 컴퓨터 시스템은 본 명세서에 설명된 특정 프로세스들 또는 특정 프로세스들의 특정 부분들을 실행하기 위해 소프트웨어 대신에 또는 그와 함께 동작할 수 있는, 회로에 하드웨어링되거나 다른 방식으로 구현된 로직(예를 들어: 가속기(1544))의 결과로서 기능성을 제공할 수 있다. 소프트웨어에 대한 참조는, 적절한 경우, 로직을 포함할 수 있고, 그 반대도 가능하다. 컴퓨터 판독가능 매체에 대한 참조는, 적절한 경우, 실행을 위한 소프트웨어를 저장하는 회로(예컨대 집적 회로(IC)), 또는 실행을 위한 로직을 구현하는 회로, 또는 양자 모두를 포함할 수 있다. 본 개시내용은 하드웨어 및 소프트웨어의 임의의 적절한 조합을 포함한다.

[0135] 부록 A: 두문자어들

[0136] JEM: joint exploration model

[0137] VVC: versatile video coding

[0138] BMS: benchmark set

[0139] MV: Motion Vector

- [0140] HEVC: High Efficiency Video Coding

- [0141] SEI: Supplementary Enhancement Information

- [0142] VUI: Video Usability Information

- [0143] GOPs: Groups of Pictures

- [0144] TUs: Transform Units,

- [0145] PUs: Prediction Units

- [0146] CTUs: Coding Tree Units

- [0147] CTBs: Coding Tree Blocks

- [0148] PBs: Prediction Blocks

- [0149] HRD: Hypothetical Reference Decoder

- [0150] SNR: Signal Noise Ratio

- [0151] CPUs: Central Processing Units

- [0152] GPUs: Graphics Processing Units

- [0153] CRT: Cathode Ray Tube

- [0154] LCD: Liquid-Crystal Display

- [0155] OLED: Organic Light-Emitting Diode

- [0156] CD: Compact Disc

- [0157] DVD: Digital Video Disc

- [0158] ROM: Read-Only Memory

- [0159] RAM: Random Access Memory

- [0160] ASIC: Application-Specific Integrated Circuit

- [0161] PLD: Programmable Logic Device

- [0162] LAN: Local Area Network

- [0163] GSM: Global System for Mobile communications

- [0164] LTE: Long-Term Evolution

- [0165] CANBus: Controller Area Network Bus

- [0166] USB: Universal Serial Bus

- [0167] PCI: Peripheral Component Interconnect

- [0168] FPGA: Field Programmable Gate Areas

- [0169] SSD: solid-state drive

- [0170] IC: Integrated Circuit

- [0171] CU: Coding Unit

- [0172] 본 개시내용이 여러 예시적인 실시예들을 설명하였지만, 본 개시내용의 범위 내에 속하는 변경들, 치환들, 및 다양한 대체 균등물들이 존재한다. 따라서, 본 기술분야의 통상의 기술자들은, 비록 본 명세서에 명시적으로 예시되거나 설명되지는 않았지만, 본 개시내용의 원리들을 구현하고 따라서 그것의 개념 및 범위 내에 있는, 다수의 시스템들 및 방법들을 안출할 수 있을 것이라는 점이 인정될 것이다.

- [0173] (1) 디코더에 대한 비디오 디코딩 방법으로서, 본 방법은 코딩된 비디오 비트스트림을 수신하는 단계; 현재 블

록에 대한 참조 블록이 현재 블록의 CTU와 상이한 코딩 트리 유닛(CTU)에 위치하는지를 결정하는 단계- 참조 블록과 현재 블록은 코딩된 비디오 비트스트림에 포함된 동일한 픽처에 위치함 -; 참조 블록이 상이한 CTU에 위치한다는 결정에 응답하여, 현재 블록의 CTU 및 참조 샘플 메모리가 동일한 크기를 갖는지를 결정하는 단계; 현재 블록의 CTU 및 참조 샘플 메모리가 동일한 크기를 갖는다는 결정에 응답하여: (i) 상이한 CTU 내의 제2 영역과 병치되는 현재 블록의 CTU 내의 제1 영역을 결정하는 단계- 제1 영역은 참조 블록의 상이한 CTU 내의 제2 영역의 위치 좌표들과 동일한 현재 블록의 CTU 내의 위치 좌표들을 가짐 -; (ii) 제1 영역의 디코딩 상태에 기초하여, 참조 블록에 대한 참조 샘플 메모리의 메모리 위치가 이용가능한지를 결정하는 단계; 및 (iii) 참조 블록에 대한 메모리 위치가 이용가능하다는 결정에 응답하여, 참조 블록에 대응하는 메모리 위치로부터, 하나 이상의 샘플을 검색하여 현재 블록을 디코딩하는 단계를 포함한다.

[0174] (2) 특징 (1)에 있어서, 제1 영역은 현재 블록이고, 제2 영역은 참조 블록이다.

[0175] (3) 특징 (1) 또는 특징 (2)에 있어서, 제1 영역과 제2 영역은 각각  $2^M \times 2^N$ 인 크기를 갖는다.

[0176] (4) 특징 (3)에 있어서,  $M=6$ 이고  $N=6$ 이다.

[0177] (5) 특징 (1) 내지 특징 (4) 중 어느 한 특징에 있어서, 제1 영역의 디코딩 상태가 제1 영역이 적어도 부분적으로 디코딩되는 적어도 하나의 블록을 포함하지 않는다는 것을 나타낸다는 결정에 응답하여 참조 블록에 대응하는 메모리 위치는 이용가능한 것으로 결정된다.

[0178] (6) 특징 (1) 내지 특징 (5) 중 어느 한 특징에 있어서, 참조 샘플 메모리 및 현재 블록의 CTU의 크기가 동일하지 않다는 결정에 응답하여, 현재 블록의 CTU의 크기가 참조 샘플 메모리의 크기보다 작을지를 결정하는 단계; 현재 블록의 CTU의 크기가 참조 샘플 메모리의 크기보다 작다는 결정에 응답하여, 참조 블록의 상이한 CTU와 현재 블록의 CTU 사이의 거리가 ((참조 샘플 메모리 크기/CTU 크기)-1)\*(CTU 폭)과 같이 정의된 임계값보다 작을지를 결정하는 단계; 및 거리가 임계값보다 작다는 결정에 응답하여, 참조 블록에 대응하는 메모리 위치로부터, 하나 이상의 샘플을 검색하여 현재 블록을 디코딩하는 단계를 추가로 포함한다.

[0179] (7) 특징 (6)에 있어서, 거리가 임계값 이상이라는 결정에 응답하여, (i) 상이한 CTU 내의 제2 영역과 병치되는 현재 블록의 CTU 내의 제1 영역을 결정하는 단계- 제1 영역은 참조 블록의 상이한 CTU 내의 제2 영역의 위치 좌표들과 동일한 현재 블록의 CTU 내의 위치 좌표들을 가짐 -; (ii) 제1 영역의 디코딩 상태에 기초하여, 참조 블록에 대한 참조 샘플 메모리의 메모리 위치가 이용가능한지를 결정하는 단계; 및 (iii) 참조 블록에 대한 메모리 위치가 이용가능하다는 결정에 응답하여, 참조 블록에 대응하는 메모리 위치로부터, 하나 이상의 샘플을 검색하여 현재 블록을 디코딩하는 단계를 추가로 포함한다.

[0180] (8) 비디오 디코딩을 위한 비디오 디코더로서, 처리 회로를 포함하고, 이 처리 회로는: 코딩된 비디오 비트스트림을 수신하고, 현재 블록에 대한 참조 블록이 현재 블록의 CTU와 상이한 코딩 트리 유닛(CTU)에 위치하는지를 결정하고- 참조 블록과 현재 블록은 코딩된 비디오 비트스트림에 포함된 동일한 픽처에 위치함 -, 참조 블록이 상이한 CTU에 위치한다는 결정에 응답하여, 현재 블록의 CTU와 참조 샘플 메모리가 동일한 크기를 갖는지를 결정하고; 현재 블록의 CTU와 참조 샘플 메모리가 동일한 크기를 갖는다는 결정에 응답하여: (i) 상이한 CTU 내의 제2 영역과 병치되는 현재 블록의 CTU 내의 제1 영역을 결정하고- 제1 영역은 참조 블록의 상이한 CTU 내의 제2 영역의 위치 좌표들과 동일한 현재 블록의 CTU 내의 위치 좌표들을 가짐 -, (ii) 제1 영역의 디코딩 상태에 기초하여, 참조 블록에 대한 참조 샘플 메모리의 메모리 위치가 이용가능한지를 결정하고, (iii) 참조 블록에 대한 메모리 위치가 이용가능하다는 결정에 응답하여, 참조 블록에 대응하는 메모리 위치로부터, 하나 이상의 샘플을 검색하여 현재 블록을 디코딩하도록 구성된다.

[0181] (9) 특징 (8)에 있어서, 제1 영역은 현재 블록이고, 제2 영역은 참조 블록이다.

[0182] (10) 특징 (8) 또는 특징 (9)에 있어서, 제1 영역과 제2 영역은 각각  $2^M \times 2^N$ 인 크기를 갖는다.

[0183] (11) 특징 (10)에 있어서,  $M=6$ 이고  $N=6$ 이다.

[0184] (12) 특징 (8) 내지 특징 (11) 중 어느 한 특징에 있어서, 제1 영역의 디코딩 상태가 제1 영역이 적어도 부분적으로 디코딩되는 적어도 하나의 블록을 포함하지 않는다는 것을 나타낸다는 결정에 응답하여 참조 블록에 대응하는 메모리 위치는 이용가능한 것으로 결정된다.

[0185] (13) 특징 (8) 내지 특징 (12) 중 어느 한 특징에 있어서, 처리 회로는 참조 샘플 메모리 및 현재 블록의 CTU의 크기가 동일하지 않다는 결정에 응답하여, 현재 블록의 CTU의 크기가 참조 샘플 메모리의 크기보다 작을지를 결정하는 단계를 포함한다.

정하고, 현재 블록의 CTU의 크기가 참조 샘플 메모리의 크기보다 작다는 결정에 응답하여, 참조 블록의 상이한 CTU와 현재 블록의 CTU 사이의 거리가 ((참조 샘플 메모리 크기/CTU 크기)-1)\*(CTU 폭)과 같이 정의된 임계값보다 작은지를 결정하고, 거리가 임계값보다 작다는 결정에 응답하여, 참조 블록에 대응하는 메모리 위치로부터, 하나 이상의 샘플을 검색하여 현재 블록을 디코딩하도록 추가로 구성된다.

[0186] (14) 특징 (13)에 있어서, 처리 회로는 거리가 임계값 이상이라는 결정에 응답하여, (i) 상이한 CTU 내의 제2 영역과 병치되는 현재 블록의 CTU 내의 제1 영역을 결정하고- 제1 영역은 참조 블록의 상이한 CTU 내의 제2 영역의 위치 좌표들과 동일한 현재 블록의 CTU 내의 위치 좌표들을 가짐 -, (ii) 제1 영역의 디코딩 상태에 기초하여, 참조 블록에 대한 참조 샘플 메모리의 메모리 위치가 이용가능한지를 결정하고, (iii) 참조 블록에 대한 메모리 위치가 이용가능하다는 결정에 응답하여, 참조 블록에 대응하는 메모리 위치로부터, 하나 이상의 샘플을 검색하여 현재 블록을 디코딩하도록 추가로 구성된다.

[0187] (15) 비디오 디코더 내의 프로세서에 의해 실행될 때, 프로세서로 하여금 방법을 실행하게 하는 명령어들이 저장된 비일시적 컴퓨터 판독가능 매체로서, 이 방법은 코딩된 비디오 비트스트림을 수신하는 단계; 현재 블록에 대한 참조 블록이 현재 블록의 CTU와 상이한 코딩 트리 유닛(CTU)에 위치하는지를 결정하는 단계- 참조 블록과 현재 블록은 코딩된 비디오 비트스트림에 포함된 동일한 픽처에 위치함 -; 참조 블록이 상이한 CTU에 위치한다는 결정에 응답하여, 현재 블록의 CTU 및 참조 샘플 메모리가 동일한 크기를 갖는지를 결정하는 단계; 현재 블록의 CTU 및 참조 샘플 메모리가 동일한 크기를 갖는다는 결정에 응답하여: (i) 상이한 CTU 내의 제2 영역과 병치되는 현재 블록의 CTU 내의 제1 영역을 결정하는 단계- 제1 영역은 참조 블록의 상이한 CTU 내의 제2 영역의 위치 좌표들과 동일한 현재 블록의 CTU 내의 위치 좌표들을 가짐 -; (ii) 제1 영역의 디코딩 상태에 기초하여, 참조 블록에 대한 참조 샘플 메모리의 메모리 위치가 이용가능한지를 결정하는 단계; 및 (iii) 참조 블록에 대한 메모리 위치가 이용가능하다는 결정에 응답하여, 참조 블록에 대응하는 메모리 위치로부터, 하나 이상의 샘플을 검색하여 현재 블록을 디코딩하는 단계를 포함한다.

[0188] (16) 특징 (15)에 있어서, 제1 영역은 현재 블록이고, 제2 영역은 참조 블록이다.

[0189] (17) 특징 (15) 또는 특징 (16)에 있어서, 제1 영역과 제2 영역은 각각  $2^M \times 2^N$ 인 크기를 갖는다.

[0190] (18) 특징 (15) 내지 특징 (17) 중 어느 한 특징에 있어서, 제1 영역의 디코딩 상태가 제1 영역이 적어도 부분적으로 디코딩되는 적어도 하나의 블록을 포함하지 않는다는 것을 나타낸다는 결정에 응답하여 참조 블록에 대응하는 메모리 위치는 이용가능한 것으로 결정된다.

[0191] (19) 특징 (15) 내지 특징 (18) 중 어느 한 특징에 있어서, 방법은 참조 샘플 메모리 및 현재 블록의 CTU의 크기가 동일하지 않다는 결정에 응답하여, 현재 블록의 CTU의 크기가 참조 샘플 메모리의 크기보다 작은지를 결정하는 단계; 현재 블록의 CTU의 크기가 참조 샘플 메모리의 크기보다 작다는 결정에 응답하여, 참조 블록의 상이한 CTU와 현재 블록의 CTU 사이의 거리가 ((참조 샘플 메모리 크기/CTU 크기)-1)\*(CTU 폭)과 같이 정의된 임계값보다 작은지를 결정하는 단계; 및 거리가 임계값보다 작다는 결정에 응답하여, 참조 블록에 대응하는 메모리 위치로부터, 하나 이상의 샘플을 검색하여 현재 블록을 디코딩하는 단계를 추가로 포함한다.

[0192] (20) 특징 (19)에 있어서, 본 방법은 거리가 임계값 이상이라는 결정에 응답하여, (i) 상이한 CTU 내의 제2 영역과 병치되는 현재 블록의 CTU 내의 제1 영역을 결정하는 단계- 제1 영역은 참조 블록의 상이한 CTU 내의 제2 영역의 위치 좌표들과 동일한 현재 블록의 CTU 내의 위치 좌표들을 가짐 -; (ii) 제1 영역의 디코딩 상태에 기초하여, 참조 블록에 대한 참조 샘플 메모리의 메모리 위치가 이용가능한지를 결정하는 단계; 및 (iii) 참조 블록에 대한 메모리 위치가 이용가능하다는 결정에 응답하여, 참조 블록에 대응하는 메모리 위치로부터, 하나 이상의 샘플을 검색하여 현재 블록을 디코딩하는 단계를 추가로 포함한다.

도면

도면1

도면2

도면3

도면4

도면5

도면6

도면7

도면8

도면9a

도면9b

도면9c

도면9d

도면10a

도면 10b

도면 10c

도면 10d

도면11

도면12

도면13

도면14

### 도면15