(19) RÉPUBLIQUE FRANÇAISE

INSTITUT NATIONAL

DE LA PROPRIÉTÉ INDUSTRIELLE

PARIS

(11) N° de publication :

(à n'utiliser que pour les

commandes de reproduction)

2 641 100

(21) N° d'enregistrement national :

90 02311

(51) Int Cl<sup>5</sup> : G 06 F 15/66.

(12)

## DEMANDE DE BREVET D'INVENTION

A1

(22) Date de dépôt : 23 février 1990.

(71) Demandeur(s) : Société dite : *SONY CORPORATION*. —

JP.

(30) Priorité : JP, 13 novembre 1985, n° 254528/85 et 19

novembre 1985, n° 259539/85.

(72) Inventeur(s) : Atsushi Hasebe, Atsushi Kikuchi, Ryohei

Kato et Norikazu Ito, *Sony Corporation*.

(43) Date de la mise à disposition du public de la

demande : BOPI « Brevets » n° 26 du 29 juin 1990.

(73) Titulaire(s) :

(60) Références à d'autres documents nationaux appa-

rentés :

Division demandée le 23 février 1990 bénéficiant de la date de

dépôt du 13 novembre 1986 de la demande initiale n° 86

15761 (art. 14 de la loi du 2 janvier 1968 modifiée).

(74) Mandataire(s) : Cabinet Beau de Loménie.

(54) Installation de traitement de données, notamment d'images et circuits générateurs d'adresse et de traitement

arithmétique.

(57) L'invention concerne les installations de traitement de

données. Elle se rapporte plus précisément à une installation

de traitement d'images destinée à assurer un traitement par

utilisation de données de pixels entourant un pixel déterminé,

une pluralité de processeurs P1, P2,... P20 étant prévue pour

effectuer le traitement, et chaque donnée de pixel étant appli-

quée simultanément aux processeurs qui ont besoin de cette

donnée parmi la dite pluralité de processeurs.

FR 2 641 100 - A1

D

La présente invention concerne une installation de traitement de données.

On a déjà proposé une installation de traitement de données, par exemple une installation de traitement d'images 5 vidéo (Journal of the Institute of Electronics and Communication Engineers of Japan, 85/4, vol. J 68-D, n° 4).

On a proposé, comme exemple d'une telle installation, un système de traitement d'images qui comporte un processeur de données d'images et un processeur de traitement 10 d'une adresse des données d'images (document JP-A-58-215813).

La réalisation d'une installation de traitement d'images à grande vitesse nécessite une grande vitesse pour les opérations arithmétiques, la configuration des opérations étant propre au traitement d'images; en outre, l'accès à une 15 grande quantité de données arrangées suivant une structure bidimensionnelle et le transfert de ces données doivent être réalisés à grande vitesse.

On a déjà proposé une installation travaillant en parallèle et une installation travaillant avec recouvrement 20 pour l'obtention d'opérations à grande vitesse.

Dans un système travaillant en parallèle, de nombreux processeurs élémentaires travaillent en parallèle afin qu'ils assurent un traitement à grande vitesse.

Bien que ce système permette un fonctionnement à 25 très grande vitesse, le logiciel commandant le traitement est soumis à une forte charge, si bien que le fait que les possibilités potentielles des circuits ne puissent pas être suffisamment utilisées pose un problème.

D'autre part, le système travaillant avec recouvrement 30 met en oeuvre une structure matérielle simple et une commande simple du traitement, si bien que l'opération à grande vitesse peut être réalisée d'une manière relativement facile. Cependant, comme la vitesse de traitement est pratiquement proportionnelle à la vitesse de commutation des transistors, 35 le fonctionnement à très grande vitesse est limité. Le traitement est limité par la structure de recouvrement et pose un problème car la souplesse d'utilisation du système est

réduite. La vitesse du transfert des données dans un système travaillant en parallèle est déterminée par le procédé de combinaison des processeurs élémentaires et de la mémoire. Le procédé de combinaison peut être du type à mémoire partagée 5 ou du type en réseau. Comme le traitement des images nécessite la gestion d'une grande quantité de données, le procédé de combinaison du type à mémoire partagée est adopté dans de nombreux systèmes. Dans le système à recouvrement, le traitement et le transfert sont mélangés si bien que la vitesse 10 de chaque étage de traitement à recouvrement doit être augmentée.

Le système de traitement d'images à grande vitesse permet divers traitements d'images et le contenu du traitement comprend non seulement un simple traitement linéaire, 15 mais aussi un traitement non linéaire, par exemple un traitement avec branchement conditionnel; en conséquence, il faut un système souple.

Cependant, un tel système ne suffit pas pour la combinaison organique de plusieurs processeurs destinés à 20 assurer un traitement à grande vitesse et des calculs élaborés.

La présente invention a donc pour objet une installation de traitement de données dans laquelle plusieurs processeurs sont combinés organiquement afin qu'ils assurent un traitement à grande vitesse et des calculs élaborés.

25 D'autres caractéristiques et avantages de l'invention seront mieux compris à la lecture de la description qui va suivre, faite en référence aux dessins annexés sur lesquels:

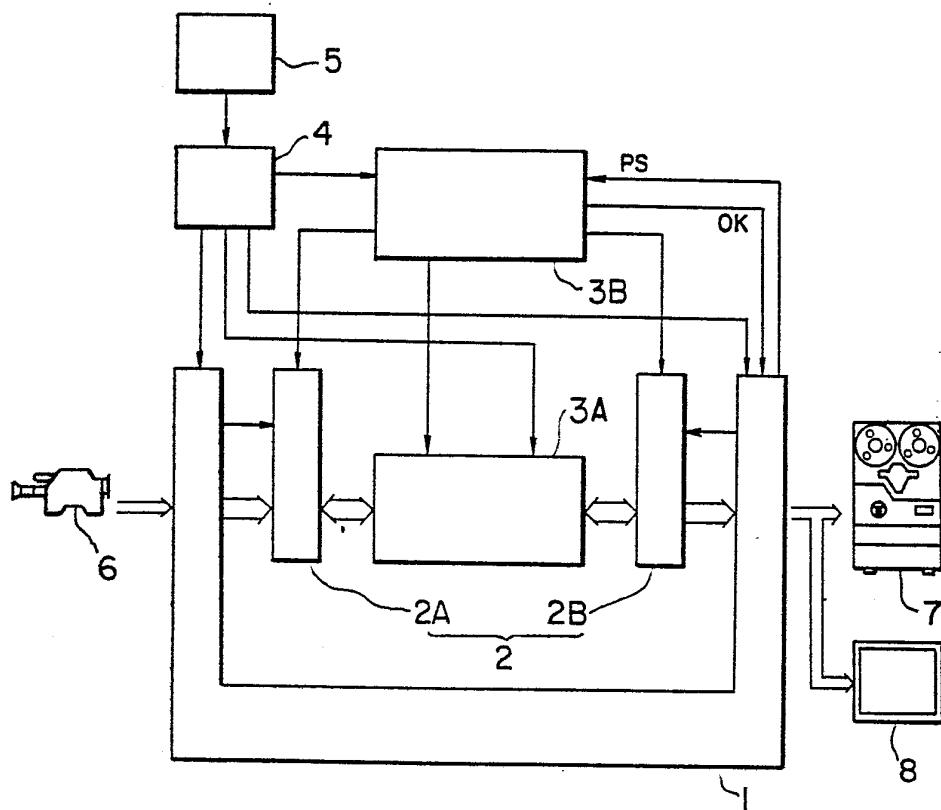

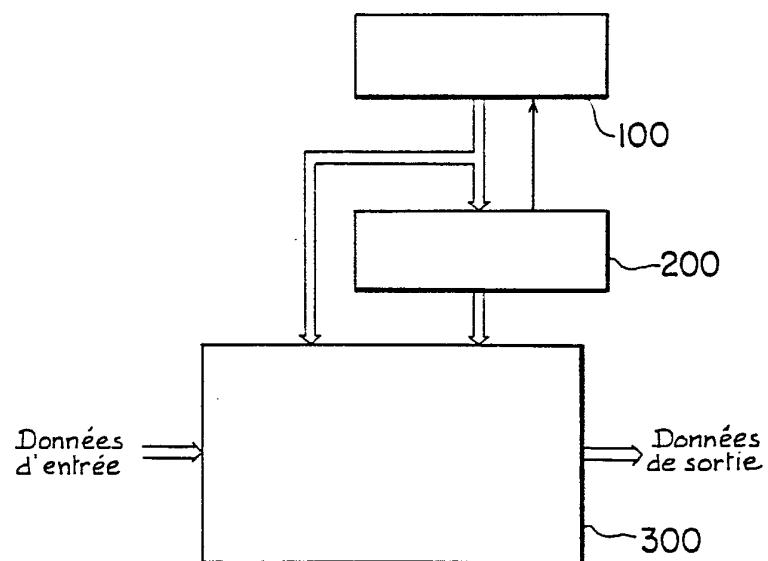

la figure 1 est un diagramme synoptique représentant l'ensemble de la configuration d'une installation de traitement d'images à laquelle s'applique un mode de réalisation 30 d'installation de traitement de données selon l'invention ;

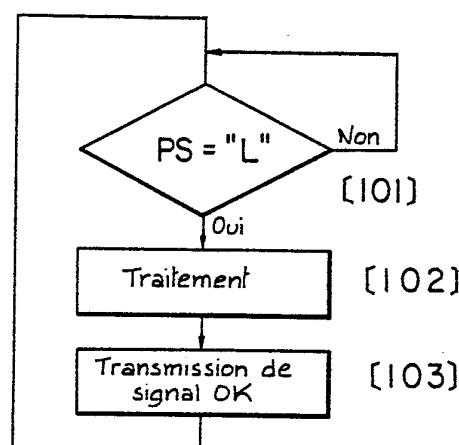

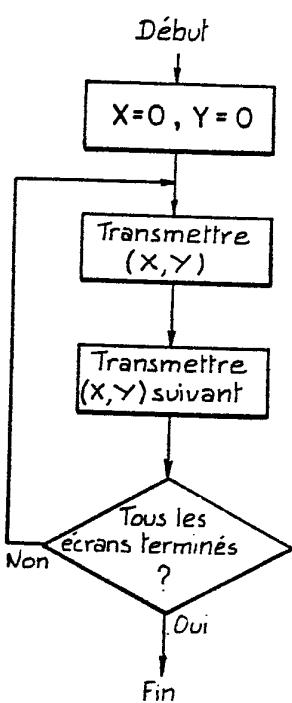

la figure 2 est un ordinogramme du fonctionnement de circuits de l'installation de traitement de la figure 1 ;

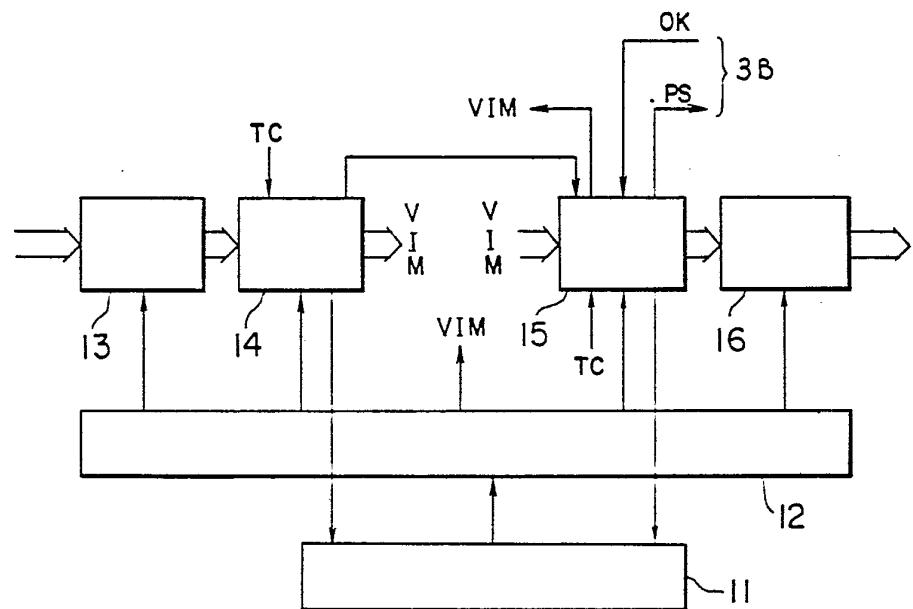

la figure 3 est un diagramme synoptique d'un exemple de section d'entrée-sortie de l'installation de la figure 1;

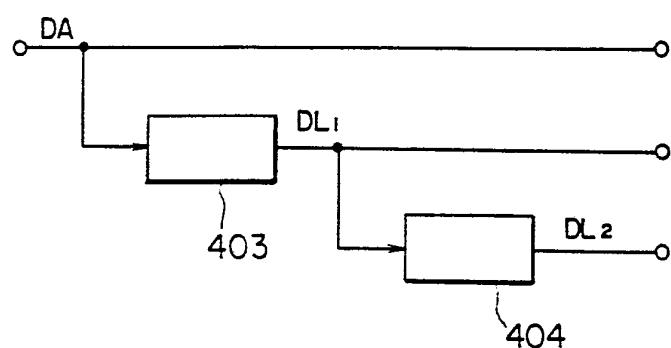

les figures 4 et 5 sont un diagramme synoptique et un diagramme des temps respectivement d'une partie du circuit de la section d'entrée-sortie de la figure 3 ;

la figure 6 est un diagramme synoptique d'un mode de réalisation des circuits de l'installation de traitement de données de la figure 1 ;

5 la figure 7 est un diagramme synoptique d'un mode de réalisation d'une partie importante des circuits de la figure 6 ;

la figure 8 est un diagramme synoptique d'un mode de réalisation des circuits de l'installation de traitement de données de la figure 1 ;

10 la figure 9 est un diagramme synoptique d'un mode de réalisation de section arithmétique principale représenté sur la figure 8 ;

15 la figure 10 est un diagramme synoptique d'un mode de réalisation de section de commande et d'une section arithmétique auxiliaire de la figure 8 ;

la figure 11 est un schéma d'un mode de réalisation de circuit générateur de signaux de mode de la figure 10 ;

20 la figure 12 est un diagramme synoptique d'un mode de réalisation de circuits générateurs d'adresse de l'installation de traitement de données de la figure 1 ;

la figure 13 est un schéma illustrant la mise en oeuvre du circuit de la figure 12 ;

25 la figure 14 est un diagramme synoptique illustrant un mode de réalisation des circuits de l'installation de traitement de données de la figure 1 ;

la figure 15 est un diagramme synoptique d'un mode de réalisation d'une section d'un circuit générateur de la figure 14 ;

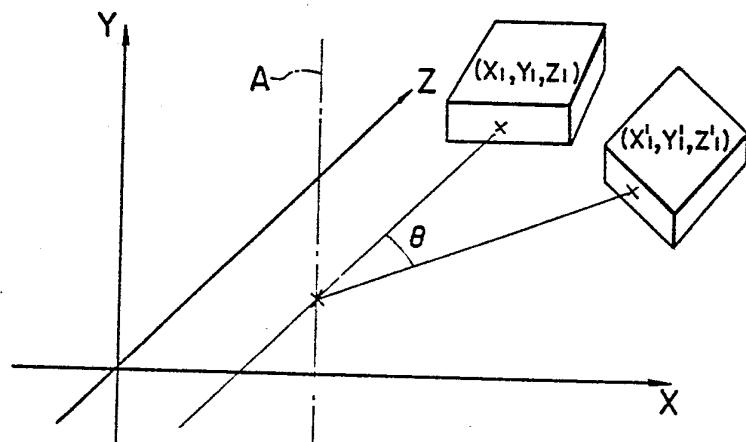

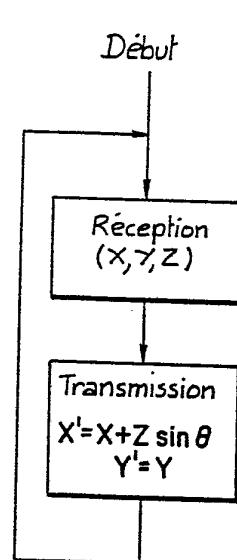

30 la figure 16 est un diagramme synoptique d'un mode de réalisation de configuration utilisé dans le cas où l'installation de traitement de données de la figure 1 est appliquée au calcul d'une adresse tridimensionnelle ;

la figure 17 est un schéma illustrant un exemple de traitement tridimensionnel ;

35 les figures 18A, 18B et 18C sont des ordinogrammes illustrant le traitement tridimensionnel dans la configuration de la figure 16 ;

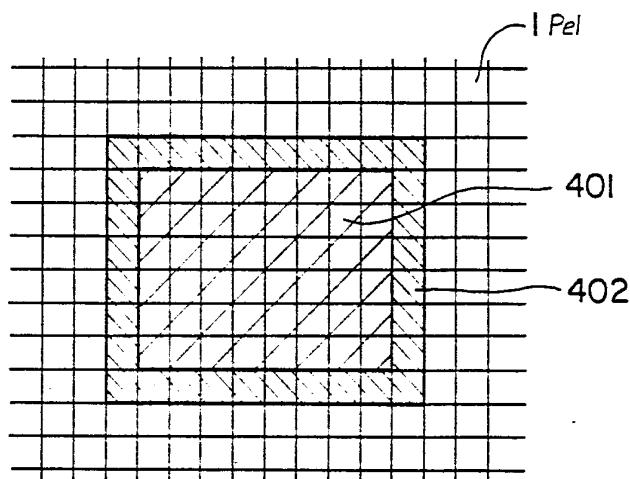

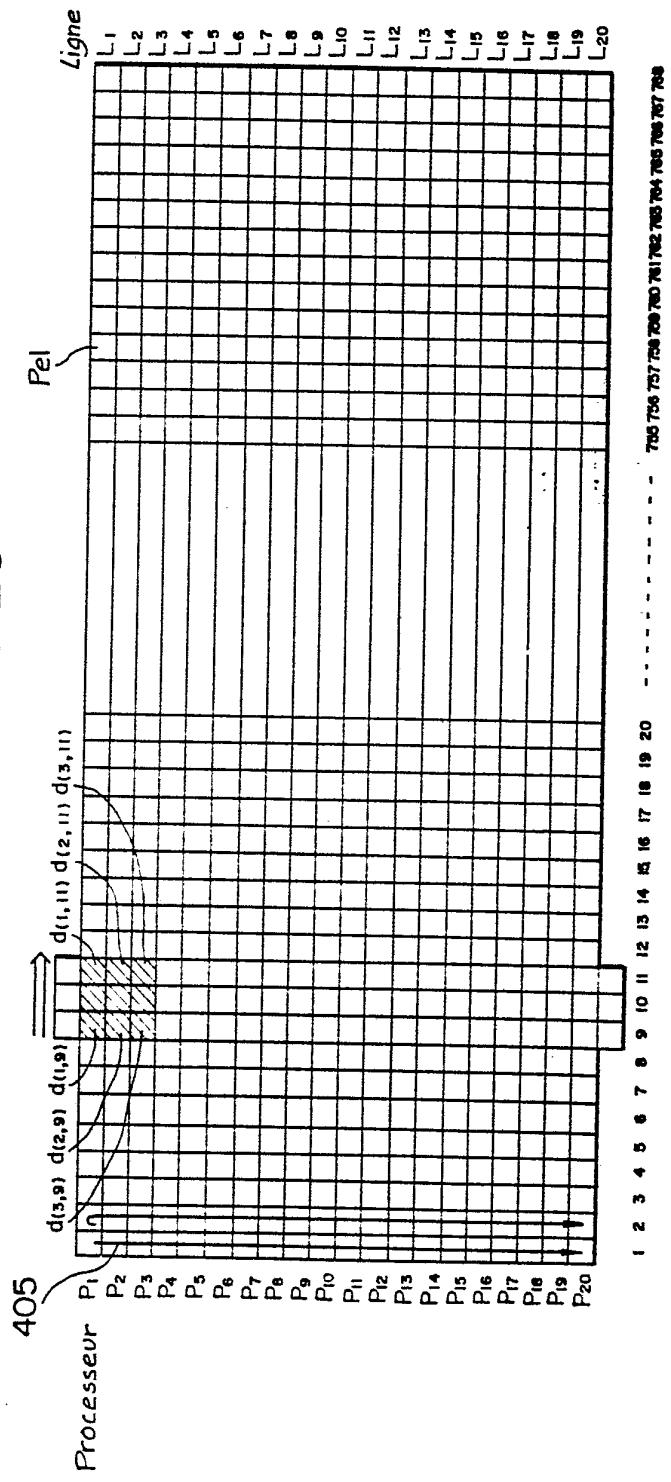

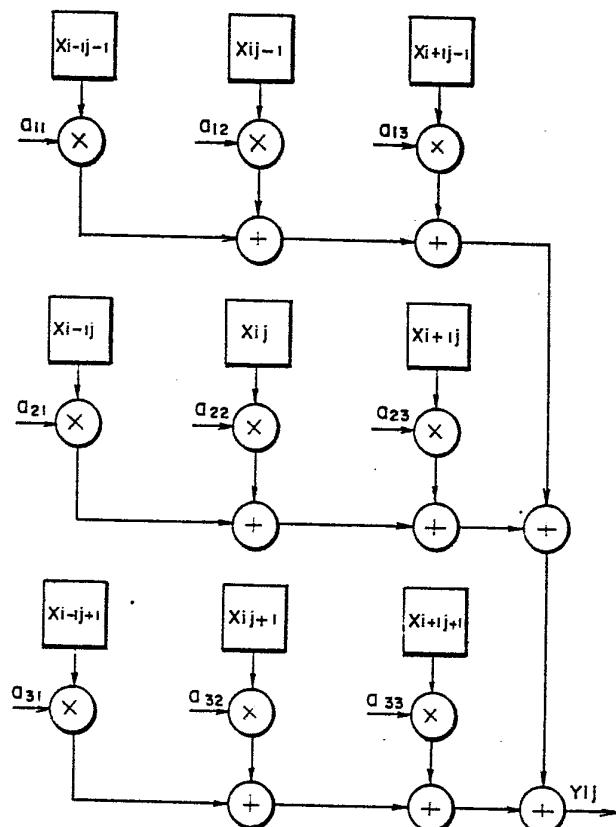

les figures 19 et 20 sont des schémas illustrant un traitement d'extraction de profils constituant un exemple dans lequel un traitement de voisinage est réalisé dans l'installation de traitement d'images de la figure 1 ;

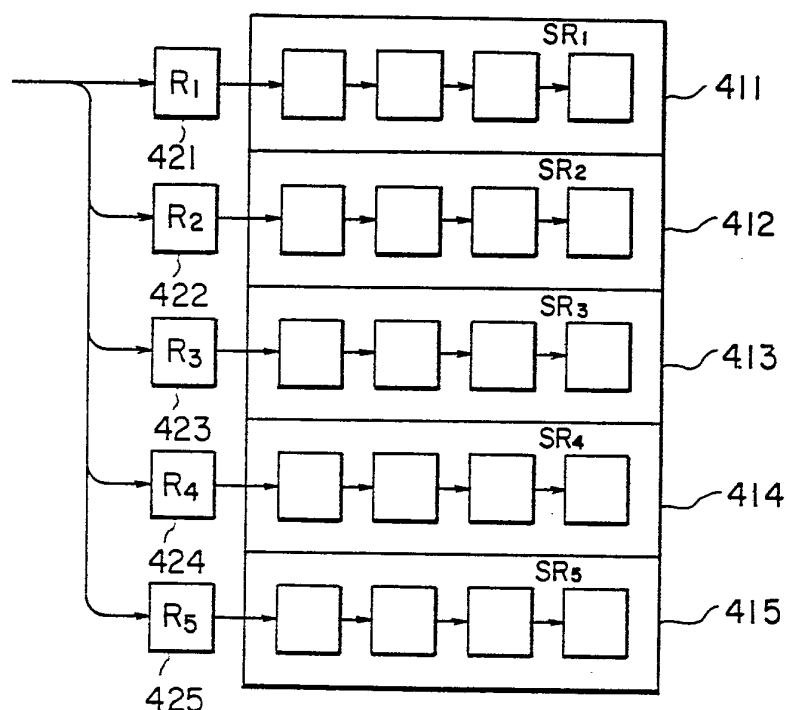

5 la figure 21 est un diagramme synoptique d'un mode de réalisation de circuit d'entrée de chaque processeur destiné à l'exécution du traitement de voisinage représenté sur les figures 19 et 20 ;

les figures 22 et 23 sont des schémas illustrant 10 un exemple de procédé destiné à assurer un traitement d'images dans l'installation de traitement d'images de la figure 1 ;

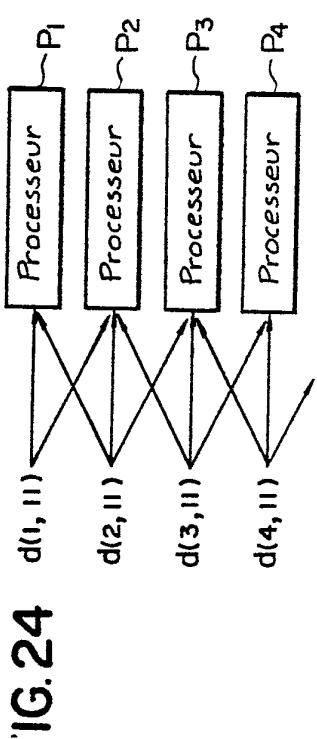

la figure 24 est un schéma illustrant un exemple de parties principales d'une installation destinée à assurer 15 le traitement d'images comme décrit en référence aux figures 22 et 23 ;

la figure 25 est un diagramme synoptique d'un exemple de registre d'entrée placé dans chaque processeur de l'installation destiné à assurer le traitement d'images 20 des figures 22 et 23 ;

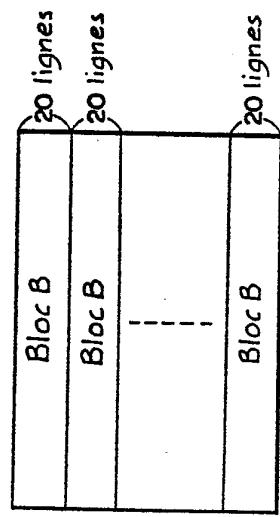

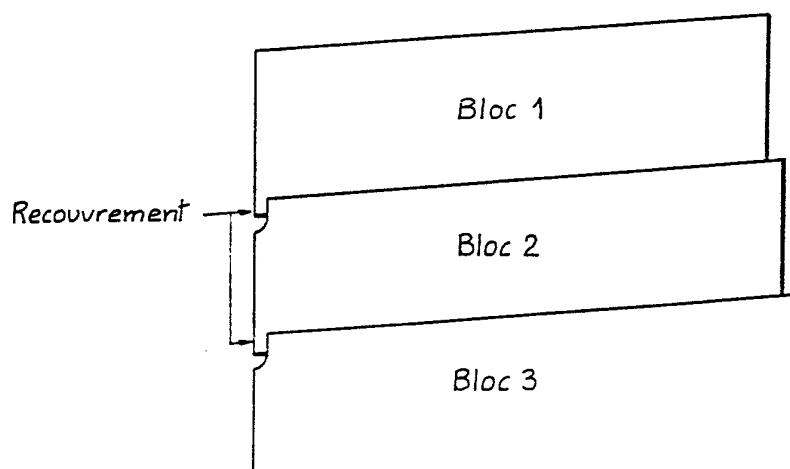

la figure 26 est un schéma représentant un procédé de division dans le cas où un traitement par division est réalisé sur un écran au cours du traitement d'image des figures 22 et 23 ;

25 la figure 27 est un diagramme synoptique illustrant la configuration de l'installation de traitement de données de la figure 1 au point de vue conceptuel ; et

la figure 28 est un tableau illustrant le contenu de la mémoire dans la configuration de la figure 27.

30 On se réfère maintenant aux dessins annexés pour la description d'un mode de réalisation de l'invention dans le cas d'une installation de traitement d'images vidéo.

L'exemple d'installation de traitement d'images vidéo de la figure 1 a pour rôle le traitement de données 35 à grande vitesse et comporte une section 1 d'entrée-sortie, une section 2 de mémoire comprenant une mémoire d'image d'entrée 2A et une mémoire d'image de sortie 2B, une section

3 de traitement de données comprenant un processeur 3A invariant en position destiné à calculer essentiellement une valeur de pel (élément d'image) et un processeur 3B variant en position destiné à assurer la commande de la circulation des données, par exemple la commande d'adressage, et à effectuer la synchronisation, et un processeur 4 jouant le rôle de l'organe de commande de l'ensemble de l'installation et destiné à commander l'exécution du traitement, sa terminaison et l'échange des programmes. Un ordinateur hôte 5 est connecté au processeur 4 et est destiné à commander l'ensemble de l'installation de traitement d'images vidéo.

La section d'entrée-sortie 1 a une configuration telle que, par exemple, un signal vidéo provenant d'une caméra vidéo 6 ou d'un magnétoscope, subit une conversion analogique-numérique afin qu'elle forme des données numériques d'image qui sont alors écrites dans la mémoire d'image d'entrée 2A ; en outre, des données traitées d'image sont lues dans la mémoire d'image de sortie 2B et sont remises sous forme d'un signal vidéo analogique par conversion numérique-analogique, ce signal étant d'abord enregistré par exemple dans un magnétoscope 7 ou étant transmis à un récepteur 8 d'image tel qu'un moniteur, si bien qu'une image vidéo peut être contrôlée.

En outre, des signaux, différents des signaux numériques et destinés à commander depuis l'extérieur la mémoire 2, par exemple un signal d'horloge, un signal de mode dominant, un signal d'adresse et un signal de commande d'écriture, sont transmis par la section d'entrée-sortie 1.

Dans ce cas, les signaux qui peuvent être transmis 30 dans la section 1 ou extraits de celle-ci sont des signaux du système NTSC ou du système R/G/B. Le système de codage des signaux est spécifié par le processeur de commande 4. En outre, un "pel" est un élément de données comprenant huit bits par exemple et représentant un élément d'image.

Une opération de lecture ou d'écriture dans la mémoire d'image 2 est réalisée dans un groupe d'une image, c'est-à-dire par une unité de trame ou d'image. A cet effet,

les mémoires 2A d'entrée et 2B de sortie comportent chacune plusieurs nappes de mémoire ayant chacune une capacité d'une trame ou image des données. Par exemple, douze nappes de mémoire d'image 768 x 512 octets sont utilisées. Dans 5 ce cas, l'utilisation de ces douze nappes de mémoire d'image n'est pas fixée, c'est-à-dire que les douze nappes peuvent être affectées arbitrairement comme mémoire d'image d'entrée 2A ou de sortie 2B en fonction de la nature du traitement ou de l'image voulue comme résultat du traitement. En outre, 10 les nappes de mémoire sont destinées à être utilisées par paires et, lorsqu'une nappe d'une paire est à l'état d'écriture, l'autre nappe peut être utilisée pour une opération de lecture, si bien que la section d'entrée-sortie 1 peut assurer un traitement parallèle comprenant un traitement 15 externe réalisé par l'intermédiaire de la mémoire 2 et un traitement interne réalisé par l'intermédiaire de la mémoire 2 à l'aide des processeurs 3A et 3B.

Dans ce cas, le signal de mode dominant destiné à déterminer si les nappes de la mémoire d'image 2 sont 20 commandées par la section d'entrée-sortie 1 ou par le processeur 3B est créé à partir de la section d'entrée-sortie 1 et est transmis à la mémoire d'image 2.

En outre, l'adresse des données numériques à traiter, le signal de commande d'écriture, le signal de mode 25 de lecture et le signal de sélection de données destiné à la commande interne de la mémoire 2 sont transmis par le processeur 3B à la mémoire 2, et les données conservées à l'adresse sont alors transférées au processeur 3A afin qu'elles y soient traitées.

30 De plus, les données traitées dans le processeur 3A sont transmises à la mémoire d'image 2, et une adresse et d'autres informations sont alors transmises par le processeur 3B à la mémoire 2. En conséquence, les données numériques ainsi traitées sont écrites dans la mémoire 2.

35 En outre, une adresse et d'autres informations sont aussi transmises par la mémoire 2 à la section d'entrée-sortie 1 et provoquent la transmission à la section d'entrée-

sortie 1 des données numériques lues en conséquence, et les données numériques sont transformées ensuite en un signal vidéo analogique prédéterminé par conversion numérique-analogique et par un autre traitement afin que le 5 signal parvienne à une borne de sortie.

La section 3 de traitement de données comporte un processeur et lit les données d'image conservées dans la mémoire d'entrée 2A en fonction du programme du processeur et exécute divers types de traitements de données, 10 et les données traitées sont alors écrites dans la mémoire d'image de sortie 2B.

La section 3 de traitement de données est subdivisée en un processeur invariant en position 3A et un processeur invariant en position 3B ; en conséquence, par rapport 15 à une section classique de traitement de données qui nécessite un temps de traitement égal au total des temps de traitement de ces sous-sections, la section 3 de traitement de données ne nécessite que le plus grand des temps de traitement étant donné la disponibilité de ces sous-sections. 20 En conséquence, dans cet exemple, le traitement peut être réalisé à grande vitesse et permet l'exécution du traitement des données vidéo presque en temps réel.

Le processeur de la section 3 de traitement de données comporte une nappe de processeurs ou plusieurs 25 nappes de processeurs, et le microprogramme contenu dans la mémoire de microprogramme peut être modifié lorsque les possibilités de traitement doivent être étendues.

Le microprogramme est transmis temporairement par l'ordinateur hôte 5 au processeur de commande 4 afin qu'il 30 soit conservé dans la mémoire à accès direct qui y est contenue et ultérieurement, par exemple à la suite d'une demande de changement de programme provenant de l'utilisateur (réglant le commutateur convenable à l'état de fermeture), le microprogramme est transmis du processeur 4 de 35 commande à chaque processeur, avec changement du microprogramme de cette manière.

Les processeurs 3A et 3B ont tous les deux une

même architecture et sont constitués de processeurs indépendants comprenant chacun une section de commande, une section arithmétique, une section de mémoire et une voie d'entrée-sortie. Ces systèmes ont des structures ayant 5 une configuration à multiprocesseur comprenant plusieurs processeurs élémentaires dans lesquels un traitement à grande vitesse est réalisé essentiellement suivant un schéma de traitement en parallèle.

Le processeur 3A comporte par exemple 60 nappes 10 de processeurs invariant en position et plusieurs nappes de sous-processeurs si bien que le traitement des données d'image provenant de la mémoire 2 est réalisé ou les données d'image sont créées dans le processeur 3A.

Le processeur 3B variant en position comporte par 15 exemple 30 nappes de processeurs destinées à commander la circulation des données internes d'image par rapport à la mémoire 2, par exemple afin que les données d'image obtenues à partir de la mémoire 2 puissent être affectées et récupérées dans le processeur 3A.

20 Ainsi, le processeur 3B crée des données d'adresse et un signal de commande transmis à la mémoire 2 et les transmet à celle-ci, et le processeur 3B crée le signal de commande d'entrée-sortie du processeur 3A et d'autres signaux de commande et les transmet au processeur 3A.

25 Le traitement des données d'image concerne non seulement le cas dans lequel les données d'une image de la mémoire d'image d'entrée 2A sont traitées et les données sont écrites dans la mémoire d'image de sortie 2B, mais aussi le cas dans lequel les données conservées dans plusieurs images de plusieurs nappes de mémoire sont traitées. 30

En outre, le nombre de bits à traiter dans les processeurs 3A et 3B est égal à 16 dans la spécification normalisée et, lors du traitement arithmétique réalisé pendant le traitement des données d'image, la vitesse de 35 traitement peut être portée à une valeur dans laquelle le traitement peut être réalisé dans une trame, c'est-à-dire que le traitement en temps réel peut être réalisé

pour des données d'image d'une image. Il existe naturellement un traitement qui nécessite un temps de traitement supérieur à celui d'une image.

Dans ce cas, le traitement des données d'image 5 par les processeurs 3A et 3B est réalisé en synchronisme avec l'image. En conséquence, le processeur 3B reçoit de la section 1 d'entrée-sortie un signal de synchronisation de début de traitement PS synchronisé sur l'image. Le signal PS est normalement à un niveau élevé et il est mis 10 à un faible niveau lorsque la synchronisation du début de traitement est détecté. D'autre part, le processeur 3B transmet à la section 1 d'entrée-sortie un signal OK indiquant qu'un traitement a été terminé. Ce signal OK est transmis par le processeur principal parmi les processeurs 15 faisant partie du processeur 3B lorsque le traitement est terminé, le processeur commandant la synchronisation de l'installation de traitement.

Ainsi, dans une étape 101 de l'ordinogramme de la figure 2, relatif à un exemple de dispositif de transmission d'un signal OK par le processeur, le processeur principal du processeur 3B détecte par logiciel le fait que le signal de synchronisation de début de traitement PS transmis par la section d'entrée-sortie 1 est mis à un faible niveau. Lors de la détection de cette condition 25 selon laquelle le signal PS est mis à un faible niveau, le processeur commence à fonctionner et transmet un signal de synchronisation TS à l'aide d'un programme transmis aux autres processeurs, y compris le processeur 3A, et il transmet alors une adresse à la mémoire d'image 2, lit 30 des données d'image dans cette mémoire 2, et effectue un traitement dans le processeur 3A (pas 102). Lorsque le traitement est terminé, le signal OK est transmis et le traitement est terminé (pas 103) afin que le signal suivant de synchronisation de début de traitement PS (pas 101) soit attendu.

Le signal PS est créé par la section d'entrée-sortie 1 de la manière suivante.

La section d'entrée-sortie 1 a la configuration représentée sur la figure 3, dans un exemple.

Ainsi, le circuit 11 destiné à créer un signal d'horloge transmet un tel signal qui est verrouillé par 5 exemple sur la phase de la sous-porteuse du signal vidéo d'entrée.

Le circuit 12 d'interface effectue une division du signal d'horloge provenant du circuit 11 et introduit un retard dans certains des signaux résultants, et les 10 signaux obtenus sont alors transmis aux sections convenables de la section d'entrée-sortie 1, de la mémoire d'entrée 2A et de la mémoire de sortie 2B.

Dans le convertisseur analogique-numérique 13, 15 le signal vidéo d'entrée est transformé à l'aide d'un signal d'horloge d'échantillonnage (par exemple à 14,32 MHz) provenant du circuit d'interface 12, en données numériques d'images dans lesquelles 8 bits sont créés pour chaque échantillonnage.

Le circuit d'entrée 14 reçoit des données numériques 20 d'image provenant du convertisseur analogique-numérique 13 et les données sont transférées à la mémoire d'entrée 2A afin qu'elles y soient écrites.

Dans ce cas, un signal spécifiant le système de codage des signaux (système NTSC ou R/G/B) est transmis 25 par le processeur 4 de commande au circuit 14 d'entrée. Dans le cas du signal NTSC, deux nappes de la mémoire d'images (ou plus de deux nappes) sont affectées comme mémoire d'image d'entrée et les données sont écrites en alternance dans la mémoire. D'autre part, dans le cas du système 30 de codage R/G/B, 6 nappes de mémoire, parmi les douze, sont affectées comme mémoire d'image d'entrée et les données sont écrites en alternance dans les deux nappes de mémoire d'images pour chaque couleur primaire. Les données sont lues dans la mémoire d'images dans laquelle l'opération 35 d'écriture n'est pas exécutée.

Comme décrit précédemment, les données d'image conservées dans la mémoire sont séparées de la section

d'entrée-sortie 1 et la circulation des données est alors commandée par le processeur 3B.

Dans ce cas, ce circuit d'entrée 14 transmet à la mémoire d'image d'entrée 2A uniquement le signal effectif d'image dont le signal de synchronisation et la partie formant le signal de salve ont été retirés et le signal obtenu est écrit dans les éléments de trame en fonction du signal d'horloge transmis par le circuit 12 d'interface.

En outre, dans le circuit 14 d'entrée, la phase du signal de salve du signal vidéo et la phase du signal d'horloge sont comparées et le signal de sortie de comparaison est transmis sous forme d'un signal de réglage de phase au circuit 11 générateur d'horloge. Le signal d'horloge du circuit 11 est soumis à une opération de verrouillage de phase par rapport à la sous-porteuse du signal vidéo.

En outre, dans le circuit 14 d'entrée, un signal d'extraction du signal de salve, un signal valide-invalide indiquant si le signal de synchronisation et la partie de signal de salve sont comprises ou non dans le signal de trame, un signal FL de début d'image indiquant la première ligne de chaque image, un signal indiquant la suppression verticale de chaque trame, et un signal vidéo d'identification sont créés avec un signal indiquant le début de la ligne, et y sont utilisés ; en outre, ces signaux sont transmis au circuit 15 de sortie décrit dans la suite pour y être traités.

Le circuit 15 de sortie reçoit les données vidéo traitées lues dans la mémoire de sortie 2B, image par image.

Dans les données ainsi lues, le signal de synchronisation ne comprend pas le signal de salve ; en conséquence, le circuit 15 de sortie comporte une mémoire passive destinée à créer un signal de synchronisation, un signal de salve et un signal de suppression verticale. Dans le système de codage NTSC, les données provenant de la mémoire d'image de sortie de B sont transmises au convertisseur numérique-analogique avec le signal de synchronisation, le signal de trame et le signal de suppression verticale (après

réarrangement le cas échéant).

En outre, dans le cas des signaux représentant les trois couleurs primaires, un signal externe de synchronisation est aussi nécessaire, et ce signal de synchronisation 5 est aussi régénéré par ce circuit de sortie 15 et est transmis au circuit tel que le moniteur.

En outre, le circuit 15 de sortie crée un signal de commande de la mémoire d'image 2. Plus précisément, un signal de mode dominant destiné à indiquer si la mémoire 10 d'image 2 est en mode de commande par la section d'entrée-sortie 1 ou par le processeur 3B est créé et est transmis à la mémoire 2. Parmi les nappes de mémoire d'image de la mémoire 2, seule une mémoire à laquelle des données d'entrée sont transmises ou à partir de laquelle des données de sortie 15 sont lues, selon le signal de mode dominant, est placée sous la commande de la section d'entrée-sortie 1. La synchronisation de la commutation du signal de mode dominant est déterminée en fonction du signal OK.

Le circuit 15 de sortie crée en outre un signal 20 d'adresse de la mémoire d'image 2 et un signal de validation d'écriture destiné à commander une opération de lecture-écriture, et les signaux sont transmis à la mémoire sous la commande de la section d'entrée-sortie 1 associée à la mémoire d'image 2. La mémoire commandée par le processeur 25 3A reçoit l'adresse et les autres signaux de commande du processeur 3B.

De plus, le circuit 15 de sortie crée un signal 30 PS de synchronisation de début de traitement à partir du signal FL de début d'image indiquant la première ligne de chaque image provenant du circuit 14 d'entrée et le signal de fin de traitement OK provenant du processeur 3B.

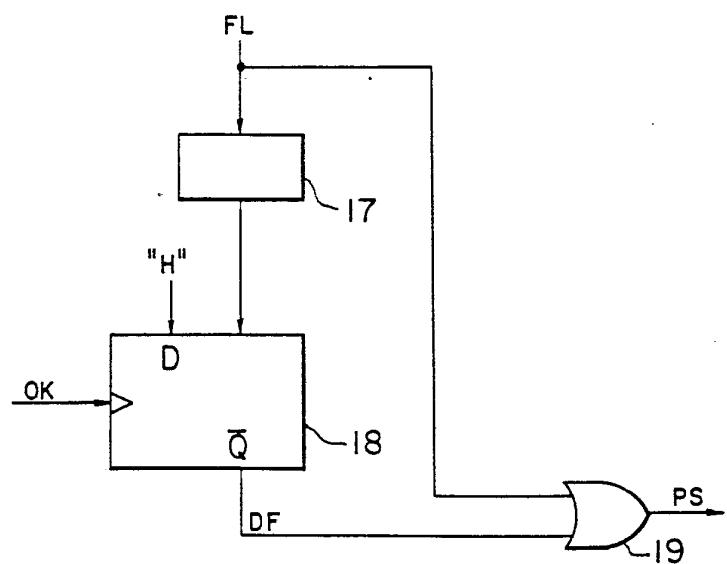

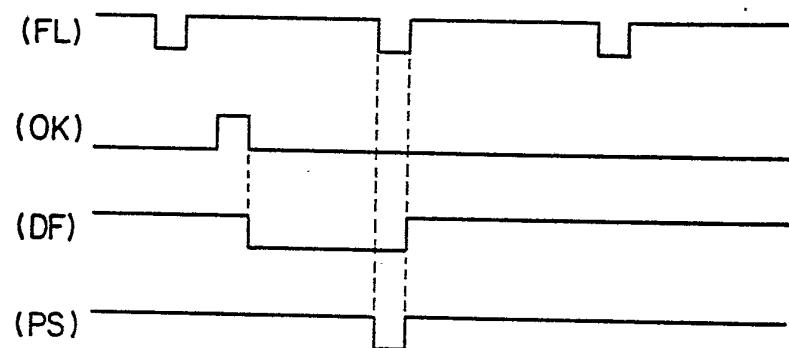

Ainsi, dans un exemple de dispositif générateur du signal PS tel que représenté sur la figure 4, le signal FL de début d'image est à un faible niveau pour une période 35 d'un signal d'horloge au point initial de chaque image (figure 5A). Le signal FL de début d'image est retardé d'une période d'horloge dans le circuit 17 à retard et est alors

transmis à la borne d'effacement du basculeur D 18. D'autre part, à la fin du traitement, la borne d'horloge du basculeur 18 reçoit un signal OK provenant du processeur 3B afin qu'il soit mis à un niveau élevé pendant une période 5 d'horloge (figure 5B).

En outre, l'entrée D du basculeur 18 est toujours à un niveau élevé.

En conséquence, jusqu'à réception du signal OK, ce basculeur 18 est vidé par le signal FL de début d'image 10 et en conséquence son signal DP de la sortie  $\bar{Q}$  (figure 5C) reste à un niveau élevé.

Lorsque le signal OK est reçu, le signal de sortie DF de ce basculeur 18 est mis à un faible niveau.

Le signal DF de sortie est transmis à la porte 15 OU 19. Cette dernière reçoit à son tour un signal FL de début d'image. Le signal de sortie de la porte OU 19 constitue le signal PS (figure 5D), et lorsque le signal FL de début d'image est reçu alors que le signal DF de sortie est à un faible niveau, le signal PS de sortie est mis 20 à un faible niveau pendant une période au cours de laquelle le signal FL est à un faible niveau. Ce n'est que lorsque le signal OK est obtenu que le signal PS de synchronisation de début de traitement, synchronisé sur l'image, peut être atteint.

25 Lors de l'exécution d'un traitement en temps réel, le signal OK est obtenu à chaque fin d'image dans tous les cas et en conséquence le signal PS devient identique au signal FL de début d'image.

D'autre part, lorsque le temps de traitement est 30 supérieur à celui d'une image, le signal PS diffère de la période d'image et peut être obtenu d'abord uniquement dans l'image suivant un signal de sortie OK.

Dans le cas de cet exemple, les trois modes suivants peuvent être sélectionnés pour le traitement des données 35 d'image.

1) Un traitement est réalisé une fois pour N images. Le traitement en temps réel est exécuté pour N = 1.

2) L'image suivant le moment auquel le traitement précédent est terminé est automatiquement décalé afin qu'elle soit traitée.

5 3) L'image suivant le moment indiqué par l'utilisateur, par exemple à l'aide d'un bouton poussoir, est décalée pour être traitée.

10 Bien que, dans le cas décrit précédemment, la totalité du traitement des données soit réalisée automatiquement sans qu'il nécessite l'intervention humaine, l'image suivant le moment auquel le traitement précédent est terminé, est décalée automatiquement afin qu'elle soit traitée, il est aussi possible que l'utilisateur puisse traiter les données 15 voulues d'image par mise à disposition d'un commutateur manuel à cet effet ; lorsque l'utilisateur spécifie une image à traiter, le signal PS doit être transmis pour l'image spécifiée, c'est-à-dire que le signal PS n'est obtenu qu'au début de l'image spécifiée.

20 Selon l'invention, comme le signal de synchronisation de début de traitement est créé après réception d'un signal indiquant la fin de traitement de données, provenant de la section de traitement de données, il n'existe pas d'incohérence telle que le signal de début du traitement suivant est créé avant la fin du traitement précédent.

25 De plus, la synchronisation du début de traitement n'a pas à être déterminée avec une marge de temps de traitement et en conséquence un traitement efficace des données peut être réalisé.

Le traitement des données d'image est réalisé comme décrit précédemment.

30 Dans la section 3 de traitement de données, un processeur d'image assurant un traitement par ordinateur est utilisé. Dans ce cas, le procédé de traitement des données d'image à grande vitesse met en oeuvre la caractéristique des données d'image qui sont disposées régulièrement suivant un arrangement bidimensionnel comprenant l'arrangement de plusieurs processeurs élémentaires ayant tous la même configuration et le fonctionnement simultané

des processeurs.

Dans une installation dans laquelle plusieurs sous-systèmes travaillent en coordination les uns avec les autres afin qu'ils exécutent un traitement, la synchronisation 5 doit être commandée convenablement afin qu'elle indique le début de traitement et la dérivation du traitement de chaque processeur.

Dans ce cas, en plus du cas dans lequel les processeurs peuvent être commandés avec une synchronisation donnant exactement le même fonctionnement, il existe des cas 10 dans lesquels il faut une synchronisation différente, c'est-à-dire que chaque processeur doit être lancé avec une légère différence de temps. Il est courant d'utiliser, pour le réglage de la synchronisation, une commande indépendante 15 de synchronisation assurant la transmission indépendante d'un signal de synchronisation d'opérations à chaque sous-système à la place de la commande de la synchronisation par un système de commande de synchronisation.

Cependant, dans le cas où chaque sous-système est 20 commandé indépendamment, il faut un même nombre de lignes de commande de synchronisation et de sous-systèmes, si bien qu'une difficulté apparaît étant donné que la taille du système 100 de commande de synchronisation devient importante.

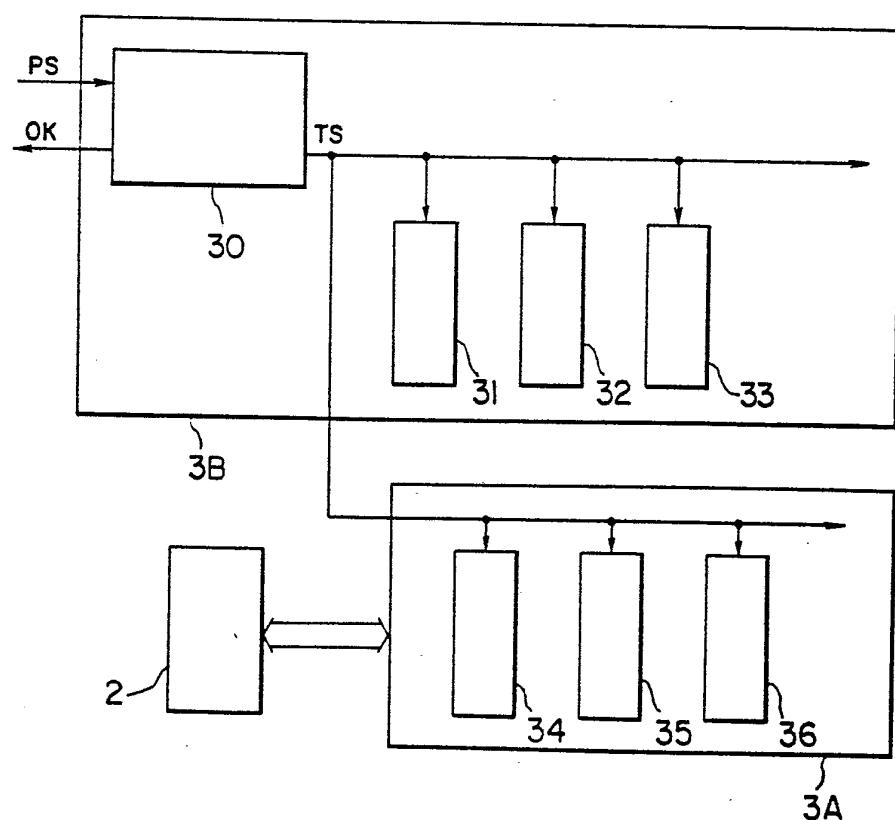

25 Selon la présente invention et comme représenté sur la figure 6, cette difficulté est supprimée par partage du signal de synchronisation entre les divers sous-systèmes.

Dans la configuration de la figure 4 qui représente 30 la section de commande de synchronisation, un processeur 30 de commande de synchronisation est disposé comme processeur principal dans le processeur 3B décrit précédemment. Le processeur 30 reçoit le signal de début de traitement PS provenant de la section d'entrée-sortie 1. Cette section 35 1 reçoit à son tour le signal de fin de traitement OK du processeur 30.

Lors de la détection du fait que le signal PS de synchronisation de début de traitement est mis à un faible

niveau, le processeur 30 transmet, comme signal TS de synchronisation, un signal sous forme d'une série dans le temps, ayant une largeur de 1 bit, aux autres processeurs 31, 32, 33, etc. du processeur 3B ; en outre, le signal de synchronisation TS est aussi transmis aux processeurs 34, 35, 36, etc. du processeur 3A. Dans ce cas, les soixante nappes de processeurs du processeur 3A sont commandées par groupes comprenant chacun 10 nappes de processeurs.

Les processeurs 31, 32, 33, .... et 34, 35, 36,... comportent chacun un décodeur du signal de synchronisation TS.

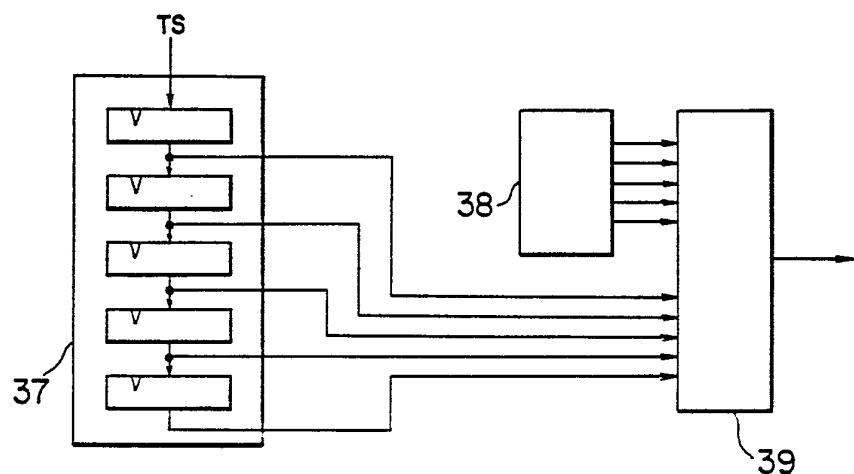

Dans un exemple de décodeur représenté sur la figure 7, le décodeur comporte un registre 37 à décalage, un circuit 38 de détermination d'un dessin de bits, et un comparateur 39.

Le registre à décalage 37 reçoit séquentiellement le signal TS de synchronisation provenant du processeur 30 de commande. Dans ce cas, l'horloge de décalage du registre 37 est synchronisée sur l'horloge de synchronisation de transmission du signal TS de synchronisation ou est un signal d'horloge dont la fréquence est supérieure à celle de l'horloge de synchronisation de transmission.

Le signal de synchronisation TS est transmis bit par bit à la suite du signal d'horloge de synchronisation de transmission afin que le signal soit décalé dans le registre 37 d'une manière telle que, par exemple, un dessin de cinq bits est décalé successivement, bit par bit.

Un dessin particulier de bit propre à chaque processeur est réglé dans l'ensemble 38 de détermination de dessin de bits correspondant.

Le comparateur 39 compare le dessin à cinq bits du signal TS de synchronisation mémorisé dans le registre 37 au dessin à cinq bits du circuit 38 de détermination. Lorsque les dessins correspondent, le signal TP de synchronisation du processeur auquel correspond le réglage du décodeur est transmis par le comparateur 39.

On suppose maintenant que, par exemple, un dessin

de bits  $|1001|$  est contenu dans le circuit 38 de détermination, et le comparateur crée un signal TP de synchronisation d'opération au moment où le dessin de bits du registre 37 qui change à chaque signal d'horloge de transmission, 5 devient égal à  $|1001|$ .

En conséquence, lorsqu'un dessin de bits qui doit être déterminé dans le circuit 38 de chaque décodeur des processeurs 31, 32, 33,... et 34, 35, 36,... est affecté à chaque processeur, le signal TP de synchronisation d'opération 10 est créé respectivement avec la synchronisation correspondante.

Dans ce cas, le processeur 30 de commande de synchronisation économise le dessin de bits de l'ensemble 15 38 de détermination de chaque décodeur des processeurs et exécute un traitement arithmétique, par exemple afin qu'il détermine la séquence de transmission  $|0111|$  du signal TS de synchronisation de manière qu'un signal voulu de synchronisation d'opérations soit transmis à chaque processeur, et le signal TS de synchronisation est transmis aux 20 processeurs si bien que la commande de synchronisation de chaque processeur est alors réalisée.

Dans ce cas, le dessin de bits qui doit être déterminé par le circuit 38 peut comprendre des données dont le nombre de bits est égal ou supérieur au nombre de bits 25 du registre 37 à décalage ; en outre, le nombre de bits peut varier pour chaque registre.

Par exemple, dans le cas où le traitement doit commencer lorsque  $|101|$  ou  $|1001|$  sont détectés par les processeurs 31 et 34 respectivement, lorsqu'un signal 30 sous forme d'une série au cours du temps  $|1|...|11011|...|10011|...$  est transmis comme signal de synchronisation, les processeurs 30 et 34 peuvent être commandés avec la synchronisation précédant  $|101|$  et avec la synchronisation suivante  $|1001|$  respectivement.

35 En outre, dans le cas où le traitement doit être commencé lors de la détection de  $|10|$  et  $|100|$  pour les processeurs 32 et 33 respectivement, lorsqu'un signal série

|1|...|11011|... est transmis comme signal de synchronisation, les processeurs 33 peuvent être commandés avec la synchronisation précédente retardée d'un cycle d'horloge de transmission par rapport au processeur 32.

5 Par ailleurs, en l'absence de disposition du décodeur comme représenté sur la figure 5, chaque processeur peut réaliser un traitement par logiciel afin qu'il détecte le dessin de bits et donne ainsi la synchronisation de l'opération.

10 En outre, à part le dessin de bits décrit précédemment, |1| peut être transmis ailleurs que pendant la transmission du signal de synchronisation TS et |0| peut être transmis pendant la transmission du signal de synchronisation TS si bien que chaque processeur compte la fréquence des 15 |1| afin qu'il détermine la synchronisation de l'opération. Dans ce cas, la fréquence peut être modifiée pour chaque processeur afin que la synchronisation particulière de l'opération de chaque processeur soit déterminée.

Comme décrit précédemment, le signal de synchronisation TS peut avoir une largeur différente d'un bit, c'est-20 à-dire que la largeur peut être égale à plusieurs bits; cependant, dans ce cas, le signal à bits parallèles comprenant plusieurs bits doit être utilisé comme signal de synchronisation et plusieurs lignes de transmission sont donc 25 nécessaires. Dans le cas d'un signal ayant une largeur de 1 bit, seule une ligne de transmission est nécessaire.

Comme décrit précédemment, selon l'invention, le signal de synchronisation est partagé par plusieurs sous-systèmes et le traitement par décodage du signal de synchronisation dans chaque sous-système, c'est-à-dire l'algorithme 30 de détection de la synchronisation de l'opération de chaque sous-système, est modifié si bien que la synchronisation respective de traitement peut être transmise aux divers sous-systèmes à l'aide de circuits de faibles dimensions.

35 Les processeurs constituant les processeurs 3A et 3B comportent chacun une section de commande ayant un microprogramme mémorisé et destiné à transmettre une micro-

- instruction, et une section arithmétique destinée à l'exécution d'une opération arithmétique en fonction de la microinstruction. Les données numériques d'entrée sont transmises à la section arithmétique. Une partie de l'information de la section arithmétique est transmise à la section de commande afin qu'elle reflète l'information arithmétique vis-à-vis du programme et le résultat de l'opération arithmétique est obtenu sous forme de données numériques de sortie de la section arithmétique.

- 10 La section arithmétique du processeur comporte un circuit multiplicateur, un circuit d'addition-soustraction, et une mémoire de facteur destinée à conserver des facteurs ou coefficients nécessaires à l'opération arithmétique, par exemple pour  $\sin \theta$  et  $\cos \theta$ .

15 Dans le processeur décrit précédemment, en plus du calcul de valeur de signaux destiné à calculer la valeur des données de sortie à partir des données d'entrée, divers types de valeurs sont associés à des calculs autres que le calcul de la valeur des signaux, par exemple d'une adresse destinée à déterminer un facteur qui doit être lu dans la mémoire de facteur et d'un nombre d'une boucle DO qui doit être déterminé en fonction du contenu du traitement.

20 Cependant, dans le cas où le calcul des divers types de valeurs autres que celles qui sont reliées au calcul de la valeur des signaux, est aussi réalisé à l'aide de la section arithmétique qui donne un calcul de la valeur des signaux, le temps de calcul est nécessaire en particulier et réduit la vitesse de traitement des données.

25 La figure 8 est un diagramme synoptique qui représente la configuration globale d'un exemple de processeur destiné à un traitement numérique utilisé dans le processeur de données selon la présente invention. Dans cet exemple, la microinstruction provenant de la section 100 de commande est transmise à la section arithmétique principale 300 et à la section arithmétique auxiliaire 200.

30 La section arithmétique principale 300 reçoit des données d'entrée qui sont alors soumises à un calcul de

20

la valeur du signal, et des données de sortie sont alors créées et transmises.

La section arithmétique auxiliaire 200 crée les 5 adresses de la mémoire de facteurs et de la mémoire de données disposées dans la section arithmétique principale 300 comme décrit dans la suite et exécute un calcul destiné à donner la valeur de répétition de la boucle DO et les adresses et la valeur de répétition de la boucle DO sont transmises à la section arithmétique principale 300 et à 10 la section 100 de commande, respectivement.

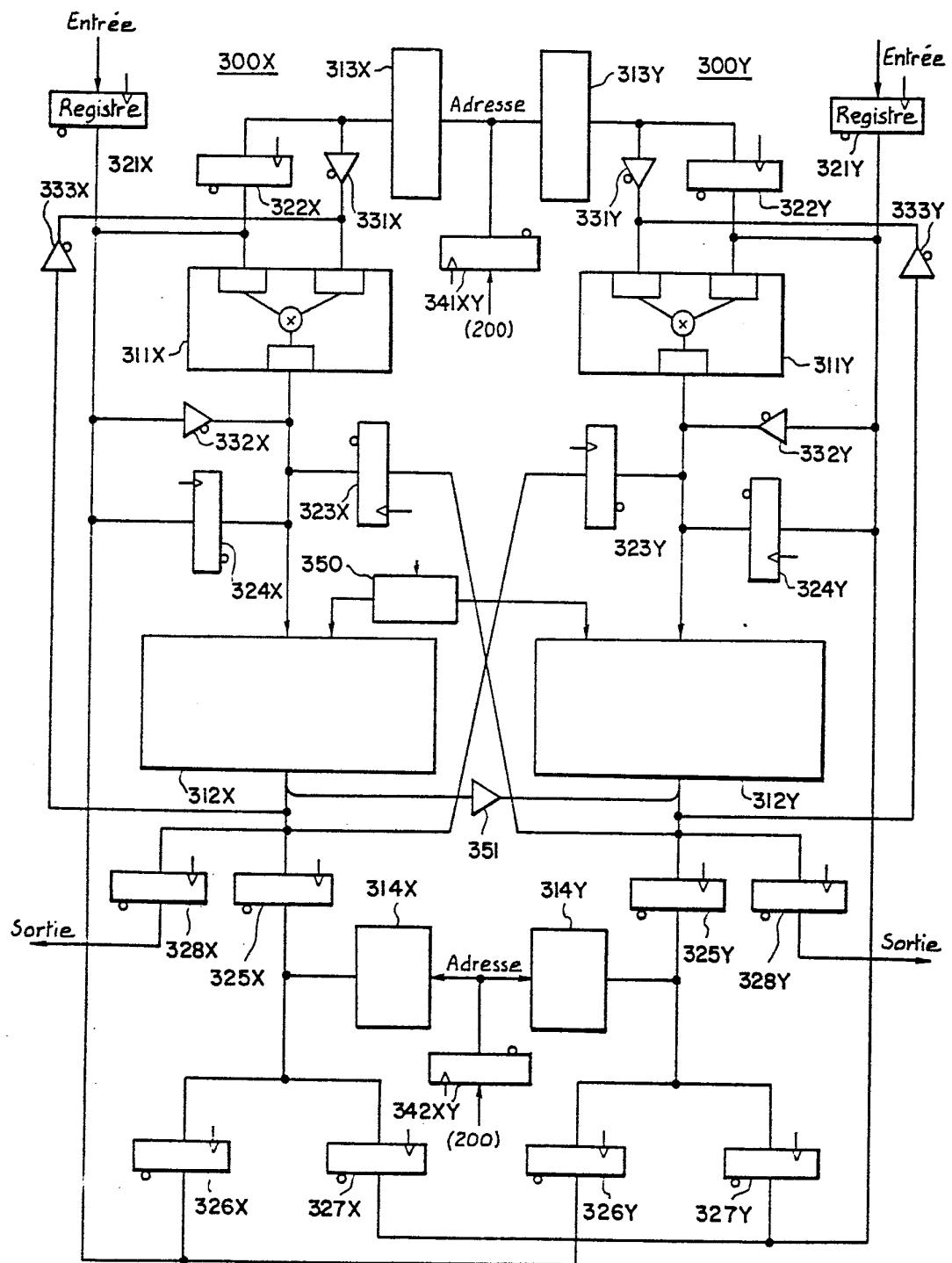

La figure 9 est un diagramme synoptique représentant 15 un exemple de section arithmétique principale 300 dans lequel deux systèmes d'unités de traitement de données correspondant chacune à une opération sur 8 bits sont disposés afin qu'elles assurent un traitement d'emploi universel, si bien qu'une opération sur des données à 16 bits est permise par le système dans son ensemble.

Ainsi, les unités arithmétiques 300X et 300Y ont 20 toutes deux exactement la même configuration si bien que les mêmes références numériques sont attribuées aux parties correspondantes, avec un suffixe X ou Y respectivement.

La première unité arithmétique 300X comporte un circuit moltiplicateur 311X, un circuit d'addition-soustraction 312X, une mémoire 313X de facteurs, une mémoire 314X 25 de données, plusieurs registres 321X-328X et des circuits tampons à trois états 331X-338X.

La section 100 de commande transmet des micro-instructions afin que les sorties des registres 321X, 328X 30 qui doivent être validées soient déterminées, afin que les données qui doivent être décalées soient déterminées, et afin que la commande éventuelle du circuit moltiplicateur 311 soit déterminée.

Les circuits tampons à trois états 331X-338X sont aussi commandés par les microinstructions.

35 Dans la première unité arithmétique 301X, les données d'entrée sont transmises au registre 321X et le registre 328X transmet des données de sortie. La mémoire

313X de facteurs contient les données de facteurs ou de coefficients telles que  $\cos \theta$  et  $\sin \theta$ . Lorsqu'un signal d'adresses est transmis par la section arithmétique auxiliaire 200 par l'intermédiaire du registre 341XY à la mémoire de facteurs 313X, un facteur nécessaire au calcul d'une valeur d'un signal est lu convenablement à cet emplacement.

La mémoire de données 314X est utilisée pour la mémorisation des données de sortie créées lorsqu'elles sont nécessaires. Lorsqu'un signal d'adresse est transmis par la section arithmétique auxiliaire 200 par l'intermédiaire du registre 342XY vers la mémoire 314X de données, les données y sont lues de la manière convenable.

La seconde unité arithmétique 300Y a une configuration analogue dans laquelle les données d'entrée sont transmises au registre 321Y et le registre 328Y transmet les données de sortie. Une adresse provenant de la section arithmétique auxiliaire 200 est transmise par l'intermédiaire du registre 314XY à la mémoire 313Y de facteurs alors qu'une adresse provenant de la section arithmétique auxiliaire 200 est transmise par l'intermédiaire du registre 342XY à la mémoire de données 314Y.

Dans ce cas, la première unité arithmétique 300X et la seconde unité arithmétique 300Y sont réalisées de manière qu'elles traitent des données à 16 bits, c'est-à-dire que 32 bits de données peuvent être traités globalement dans le système. Celui-ci a une configuration permettant le traitement d'emploi universel de manière que le traitement puisse être réalisé dans l'une ou l'autre des première et seconde unités arithmétiques 300X et 300Y ; en outre, les signaux de sortie des circuits d'addition-soustraction 312X et 312Y sont transmis aux registres 323Y et 323X respectivement alors que les signaux de sortie des registres 327X et 327Y sont transmis au registre 324 et au circuit multiplicateur 311, et au registre 324X et au circuit multiplicateur 311X respectivement, si bien que l'information peut être communiquée entre les sections arithmétiques 300X et 300Y.

De plus, les circuits ou unités d'addition-sous-

traction 312X et 312Y sont liées l'une à l'autre par une section 350 de liaison. Lorsqu'un signal prédéterminé de sélection est transmis à la section de liaison 350, l'opération peut être échangée entre deux modes, selon que les 5 circuits respectifs d'addition-soustraction 312X et 312Y travaillent chacun comme un circuit d'addition-soustraction à 16 bits avec une précision simple, ou selon que deux circuits d'addition-soustraction 312X et 312Y travaillent comme un tout sous forme d'un circuit d'addition-soustraction à 32 bits donnant une précision double.

Dans cet exemple, les circuits d'addition-soustraction 312X et 312Y sont constitués chacun sous forme d'un circuit d'addition-soustraction à 16 bits comprenant par exemple quatre microprocesseurs Am2901 de AMD, sous 15 forme d'un ensemble. Le circuit d'addition-soustraction comprend par exemple une mémoire à accès direct capable de mémoriser 16 articles de données à 16 bits. Les articles de données à 16 bits sont disposés afin qu'ils soient décalés dans la direction des colonnes suivant des relations 20 numériques, par exemple d'un facteur 1/2, d'un facteur 2, etc.

Dans un système de traitement parallèle mettant en oeuvre la configuration précitée à multiprocesseur, le processeur 4 de commande assure une commande globale 25 dans trois modes décrits dans la suite, permettant ainsi l'exécution du traitement, la terminaison du traitement et le transfert de programme (échange) sans défaut de continuité.

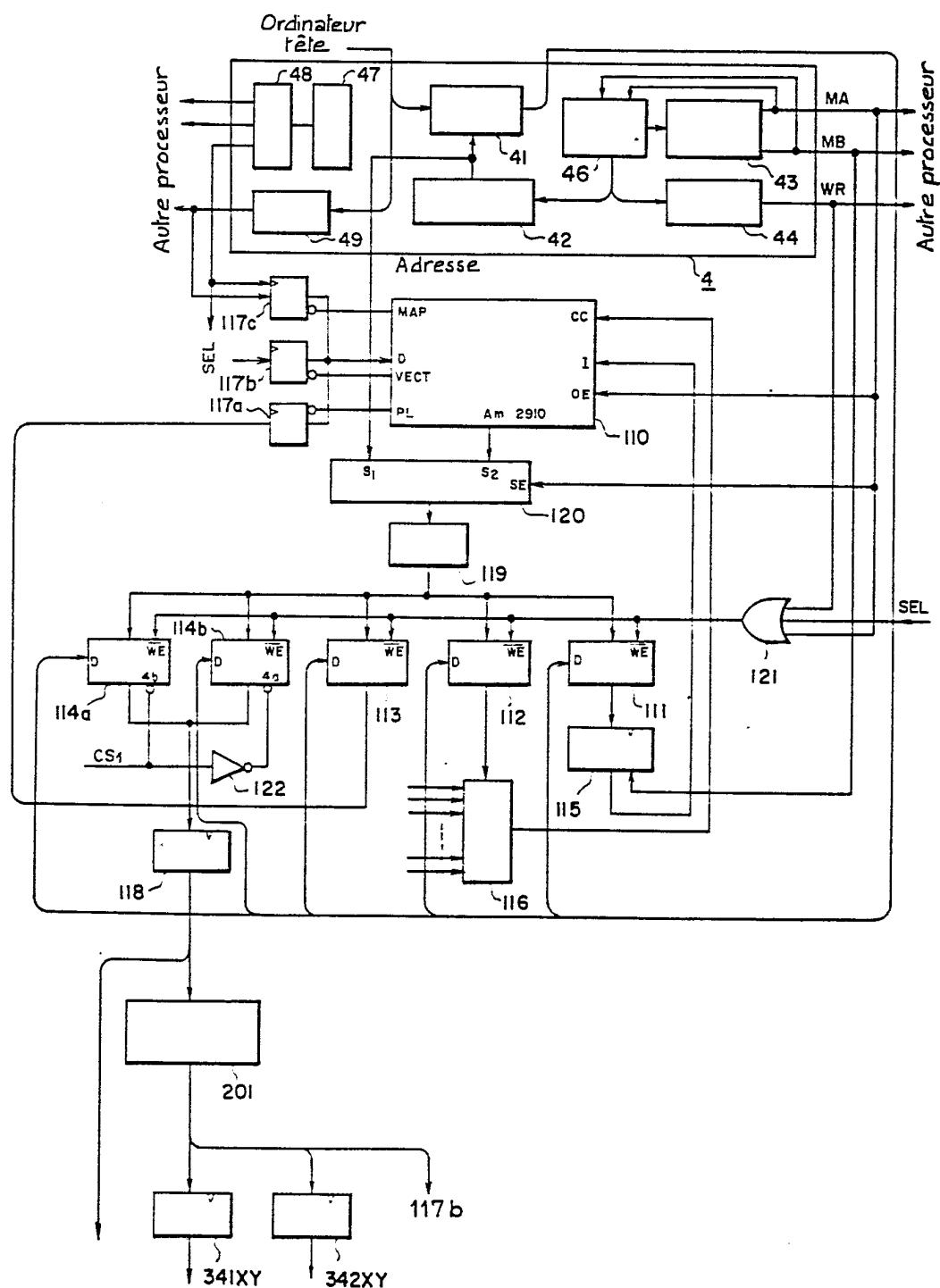

La figure 10 représente les relations de connexion 30 du processeur de commande et de la section de commande 100 de l'un des divers processeurs des processeurs 3A et 3B. Cette configuration s'applique à tous les processeurs effectuant l'échange de programme.

Ainsi, sur ce schéma, les constituants autres que 35 le processeur de commande 4 constituent un exemple de configuration de la section de commande du processeur.

L'organe 101 de commande à microprogramme crée

des adresses de la mémoire de microprogrammes 111-114a et 114b, constituées à partir de la mémoire à accès direct.

5 A partir de la mémoire 111 de microprogrammes, quatre bits d'instruction par exemple sont obtenus afin qu'ils assurent la sélection de l'une de plusieurs instructions de l'organe 110 de commande à microprogramme et les bits d'instruction sont transmis par l'intermédiaire d'un registre 115 à une borne I d'instruction de l'organe 110 de commande.

10 Dans ce cas, l'organe de commande possède 16 types d'instructions.

15 De plus, le sélecteur 116 reçoit plusieurs articles d'informations à 1 bit, et l'un de ces articles est choisi en fonction d'une information lue dans la mémoire 112 de microprogramme. L'information à 1 bit provenant du sélecteur 116 est transmise sous forme d'un code de conditions à la borne CC de l'organe 110 de commande de programme et elle est alors combinée aux bits d'instruction de manière qu'elle soit utilisée comme information pour la sélection 20 de l'adresse suivante sous forme de données qui progressent, d'une adresse à transmettre à la borne d'entrée directe D ou d'une autre adresse.

25 Une information, par exemple une adresse de destination d'une instruction "GOTO" ou une information sur la valeur de répétition d'une boucle DO est obtenue dans la mémoire 113 de microprogramme et est alors conservée dans un registre 117a.

30 Une information relative à la microinstruction est extraite de la mémoire de microprogramme 114a et 114b. Cette information est transmise par l'intermédiaire du registre 118 à la section arithmétique de ce processeur et la totalité ou une partie de la microinstruction est transmise à l'unité logique d'addition-soustraction 201 constituante une section arithmétique auxiliaire 200.

35 L'organe 110 de commande à microprogramme est réalisé de manière qu'il permette la transmission de l'un des trois signaux de validation PL, VECT et MAP suivant

le bit d'instruction. En conséquence, l'un des registrés 117a-117c est mis à un état valide de fonctionnement par le bit d'instruction et l'adresse conservée dans le registre est utilisée comme signal direct d'entrée. Dans la plupart 5 des instructions, le signal PL est validé, c'est-à-dire que le signal VECT ou le signal MAP ne peut être transmis que pour une instruction particulière. En outre, le fait que l'entrée directe doit être sélectionnée dans l'état du bit d'instruction est déterminé en fonction du code 10 d'état provenant du sélecteur 116.

Après sélection d'une microinstruction, l'unité arithmétique d'addition-soustraction 201 obtient par le calcul des signaux d'adresses de la mémoire de facteurs 313X et 313Y et de la mémoire de données 314X et 314Y de 15 la section arithmétique principale 300, et transmet les signaux obtenus d'adresses aux registres 341XY et 342XY afin qu'ils y soient mémorisés.

Dans l'unité arithmétique d'addition-soustraction 201, une information telle que la valeur de répétition 20 d'une boucle DO est obtenue par le calcul et est transmise par exemple au registre 117b qui la conserve.

Les opérations réalisées dans la section arithmétique auxiliaire 200 sont relativement plus simples que le calcul de la valeur du signal dans la section arithmétique 25 principale 300. En conséquence, dans l'exemple décrit précédemment, la section arithmétique auxiliaire 200 peut avoir une faible dimension sous forme d'un circuit matériel, de même que l'unité arithmétique d'addition-soustraction 201.

30 Comme décrit précédemment, lorsque l'unité arithmétique auxiliaire 200 est présente, par exemple dans le cas où un premier calcul du total des opérations entre les coefficients  $KA(a_1), KA(a_2), \dots, KA(a_n)$  aux adresses  $a_1, a_2, a_n$  de la mémoire de facteurs 313X et les données 35  $TA(a_1), TA(a_2), \dots, TA(a_n)$  aux adresses respectives  $a_1, a_2, \dots, a_n$  de la mémoire de données 314X, c'est-à-dire

KA ( $a_1$ ) \* TA ( $a_1$ ) + KA ( $a_2$ ) \* TA ( $a_2$ ) + ... + KA ( $a_n$ ) \* TA ( $a_n$ ) et un calcul du total des opérations entre les coefficients KB ( $a_1$ ), KB ( $a_2$ ), ... KB ( $a_n$ ) aux adresses  $a_1$ ,  $a_2$ , ...  $a_n$  de la mémoire de facteur 313Y et les données TB ( $a_1$ ), TB ( $a_2$ ), ... TB ( $a_n$ ) aux adresses respectives  $a_1$ ,  $a_2$ , ...  $a_n$  de la mémoire de données, c'est-à-dire

KB ( $a_1$ ) \* TB ( $a_1$ ) + KB ( $a_2$ ) \* TB ( $a_2$ ) + ... KB ( $a_n$ ) \* TB ( $a_n$ ) sont réalisés en même temps, le traitement peut être réalisé en  $n$  étapes ou en un peu plus de  $n$  étapes, par rapport aux  $2n$  étapes nécessaires avec la technique connue, si bien que la vitesse de traitement peut être accrue.

Selon la présente invention, comme la section arithmétique auxiliaire est destinée à calculer des valeurs telles que l'adresse de la mémoire de facteurs dans la section arithmétique principale exécutant le calcul de la valeur du signal, les opérations telles que le calcul de la valeur d'adresse réalisé habituellement dans la section arithmétique principale sont retirées des tâches de celle-ci si bien que la section arithmétique principale n'assure que le calcul de la valeur des signaux et la vitesse d'exécution du traitement est ainsi accrue.

En outre, comme les opérations effectuées dans la section arithmétique auxiliaire ne nécessitent pas des circuits de grandes dimensions dans la plupart des cas nécessaires au calcul de la valeur des signaux dans la section arithmétique principale des circuits de petites dimensions seulement sont ajoutés à la section arithmétique auxiliaire, de manière avantageuse.

Lorsqu'un traitement par adaptation est exécuté en fonction de l'information provenant de la section arithmétique et d'autres processeurs, le sélecteur 116 reçoit, comme informations d'entrée, l'information provenant de la section arithmétique et l'information provenant d'un autre processeur et, suivant l'information, une instruction telle qu'un saut conditionnel, est exécutée.

Cependant, dans le cas du système de programmation utilisé pour le traitement par adaptation décrit précédem-

ment, un traitement par adaptation même très réduit, par exemple le calcul d'une valeur absolue, a une influence sur l'écoulement des adresses du programme étant donné le saut conditionnel ou analogue.

5 En outre, lorsque plusieurs courants de données circulent pour le traitement arithmétique respectif dans un processeur, un programme créé par utilisation d'un tel code de condition ne peut pas s'adapter au traitement des données associées aux courants respectifs de données, et 10 ceci constitue un inconvénient.

Dans l'exemple considéré, les unités de mémoire 114a et 114b sont disposées comme mémoires de microprogrammes destinées à transmettre des microinstructions dans le premier système de données. Les sorties des mémoires 15 114a et 114b sont connectées mutuellement (par câblage OU) et sont reliées par le registre 118 au premier système de données.

L'information provenant du premier système de données est transmise comme signal de sélection de circuits 20 paillettes  $CS_1$  à la mémoire 114a et est transmis par un circuit 122 d'inversion à la mémoire 114b.

Dans un exemple, le contenu de la mémoire de microprogramme 114a et 114b, dans le cas où un calcul  $C = A + |B|$  est exécuté, est le suivant.

25 Adresse Contenu de la mémoire 114a Contenu de la mémoire 114b

|   |                              |                              |

|---|------------------------------|------------------------------|

| 0 | transmettre données A à UAL. | transmettre données A à UAL. |

| 1 | vérifier signe de B          | vérifier signe de B          |

| 2 | $C = A + B$                  | $C = A - B$                  |

30 Ainsi, bien que le contenu des adresses 0 et 1 de la mémoire 114a, 114b soient les mêmes, les contenus de l'adresse 2 varient avec le signe des données B. Comme le signal des données numériques est positif lorsque le bit le plus significatif est un 0 et le signal est négatif 35 lorsque ce bit est un 1, le bit le plus significatif des données B est transmis comme signal de sélection de paillettes  $CS_1$ . En conséquence, lorsque le bit le plus signi-

ficatif est un 0 indiquant le signe positif, la mémoire 114a est choisie et une opération  $C = A + B$  est réalisée dans la section arithmétique alors que lorsque le bit le plus significatif est un 1 indiquant le signe négatif, 5 la mémoire 114b est choisie et une opération  $C = A - B$  est exécutée dans la section arithmétique.

Comme décrit précédemment, sans changement de la circulation des adresses, c'est-à-dire de la circulation dans le programme lui-même, un traitement par adaptation 10 tel qu'un calcul d'une valeur absolue peut être réalisé.

Ainsi, le traitement par adaptation peut être réalisé facilement pour chaque système de données pourvu que, d'après un signal du système de données, une mémoire de programme associée à des instructions de commande du 15 système de données puisse être sélectionnée.

Lorsque la capacité d'adressage de la mémoire de programme est supérieure à la longueur du programme, il est possible d'utiliser deux mémoires telles que les mémoires 114a et 114b de l'exemple précédent. Ces unités de mémoire 20 ne sont pas sélectionnées par une opération de sélection de paillettes, c'est-à-dire que deux types de contenus de programme sont écrits dans un dispositif à mémoire, permettant la sélection de l'un de ces deux types de programme par transmission de l'information provenant du système de données au bit le plus significatif de l'adresse. 25

Selon la présente invention, comme plusieurs contenus de programme sont préparés et comme l'un des programmes est sélectionné suivant l'information provenant du système de données, le traitement par adaptation associé à l'information provenant du système de données peut être simplement obtenu sans changement de la circulation dans le programme. 30 En outre, lorsque l'instruction à 4 bits provenant du registre 115 est |0000|, une instruction de saut à zéro est supposée et l'organe 110 de commande à microprogramme 35 est mis dans un état tel qu'il transmet une adresse 0 dans tous les cas quel que soit le code de condition.

D'autre part, le processeur de commande 4 comporte

une mémoire à accès direct 41 destinée à conserver les programmes à transmettre à la mémoire de microprogramme 111-114a et 114b et un générateur 42 des adresses nécessaires.

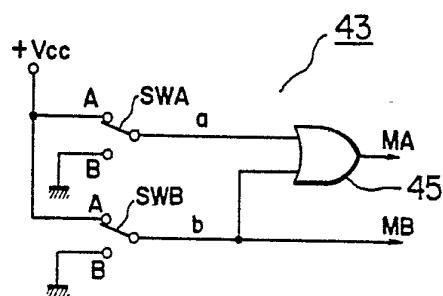

5 En outre, le dispositif générateur de signaux de mode 43, destiné à permettre trois modes comprenant le mode d'exécution, le mode de réarmement (arrêt) et le mode d'échange de programme, est disposé de manière qu'il crée des signaux de mode à 1 bit MA et MB ; en outre, le dispositif 44 générateur de signaux d'écriture est destiné à créer un signal d'écriture de programme destiné à la mémoire de microprogramme 111-114a et 114b, en mode d'échange de programme.

15 Le générateur de signal de mode 43 a par exemple la configuration représentée sur la figure 11.

Ainsi, des commutateurs SWA et SWB doivent être commutés par l'opérateur. Chaque commutateur a une entrée A recevant une tension continue positive et une autre borne B à la masse. Un signal a qui doit être obtenu à l'aide 20 du commutateur SWA est transmis à une borne d'entrée d'une porte OU 45. Un signal b obtenu à partir du commutateur SWB est transmis comme signal de mode MB et parvient à l'autre borne d'entrée de la porte OU 45 qui transmet à son tour un signal de mode MA.

25 Dans ce cas, le mode est établi de la manière suivante, en fonction des signaux de mode à un bit MA et MB.

Tableau I

MA = 0 MB = 0 mode d'échange de programme

MA = 1 MB = 0 mode de réarmement (arrêt)

30 MA = 1 MB = 1 mode d'exécution

Ainsi, lorsque le commutateur SWB est réglé sur la borne A, le mode d'exécution est sélectionné quel que soit l'état du commutateur SWA. Lorsque le commutateur SWA est réglé sur la borne A et le commutateur SWB sur 35 la borne B, le mode de réarmement est sélectionné. Lorsque le commutateur SWB est relié à la borne B et le commutateur SWA à la borne B, le mode d'échange de programme est sélec-

tionné.

5 Comme l'indique le tableau I qui précède, lorsque le signal MB est égal à zéro, l'exécution du programme est interrompue et lorsque le signal MB est égal à 1, le programme devient exécutable. En conséquence, ce signal de mode MB est appelé signal de réarmement (arrêt).

D'autre part, lorsque le signal MA est égal à 0, l'échange de programme est possible. Ce signal de mode MA est donc appelé signal d'échange.

10 Ces deux signaux de mode MA et MB sont utilisés pour l'établissement des modes respectifs de la manière suivante.

15 Le sélecteur 120 sélectionne des adresses destinées à la mémoire de microprogrammes 111-114a et 114b à partir des adresses provenant de l'organe 110 de commande et du processeur 4 de commande. Le signal MA est transmis comme signal de sélection à cet effet. Lorsque le signal MA est égal à 1, l'adresse provenant de l'organe 110 de commande est sélectionnée et lorsque ce signal MA est égal à 0, 20 l'adresse provenant du processeur 4 est sélectionnée.

En outre, le circuit porte 121 transmet le signal d'écriture WR en fonction du signal MA. Lorsque le signal MA est à 0, la porte est ouverte et le signal WR est transmis à chaque borne WE de validation d'écriture de la mémoire 25 111-114a et 114b de microprogramme.

Lorsqu'un zéro est transmis au signal WE de la mémoire 111-114a et 114b de microprogramme, celle-ci est mise à l'état de validation d'écriture.

30 En outre, le signal MB est transmis à la borne de remise à zéro du registre 115 et lorsque ce signal MB est égal à 0, le registre 115 est remis à 0.

Dans le processeur de commande 4, les états des signaux de mode MA et MB sont contrôlés par la section 46 de commande de chargement afin que le traitement réalisé 35 dans le processeur 4 soit commandé en fonction du mode.

En mode d'exécution du programme, le signal MA est égal à 1 si bien qu'une adresse provenant de l'organe

110 de commande est obtenue à partir du sélecteur 120, et ce signal d'adresse est retardé d'un signal d'horloge par l'intermédiaire du registre 119 et le signal résultant est transmis à la mémoire de microprogramme 111-114a et 114b.

5 En outre, le signal de sortie de la porte OU 121 est à 1 dans tous les cas lorsque le signal MA est à 1, et la mémoire 111-114a et 114b n'est donc pas à l'état de validation d'écriture.

10 En outre, comme le signal de mode MB est égal à 1, le registre 115 n'est pas remis à 0 et les données lues dans la mémoire 111 subissent un retard d'une impulsion d'horloge dans le registre 115 et sont transmises à la borne d'instruction de l'organe 110 de commande à microprogramme si bien qu'un programme est exécuté.

15 Dans ce cas, la microinstruction lue dans la mémoire 114 est retardée d'une impulsion d'horloge dans le registre 118 et est transmise à la section arithmétique.

20 En mode d'exécution, les registres de traitement par recouvrement sont destinés à être disposés de la manière suivante. Un registre 119 est placé entre l'organe 110 de commande et la mémoire de microprogrammes 111-114a et 114b, les registres 115 et 117a sont placés entre les côtés de sortie de la mémoire de microprogrammes 111-114a et 114b et l'organe 110 de commande, et un registre (non représenté) est relié à l'entrée du sélecteur 116. Cette disposition permet une réduction du cycle d'horloge.

25 Ainsi, dans le système de traitement d'images de cet exemple, le procédé de traitement en parallèle à l'aide de la configuration du type multiprocesseur est adopté essentiellement mais le procédé de traitement avec recouvrement partiel tel que décrit précédemment est aussi utilisé en partie afin qu'un traitement à grande vitesse soit assuré.

30 En mode de transfert de programme, le signal de mode MB est égal à 0 et en conséquence le registre 115 est remis à zéro et |0000| est transmis à la borne d'instruction de l'organe 110 de commande ; en conséquence, l'adresse transmise par cet organe 110 est maintenue à 0 ou la sortie

d'adresse est fermée. Plus précisément, les adresses du programme destiné à tous les processeurs associés aux processeurs 3A et 3B sont à 0 et l'état d'arrêt de programme est établi.

5 D'autre part, comme le signal de mode MA est aussi à 0, le sélecteur 120 est mis dans l'état permettant la sélection de l'adresse provenant du générateur d'adresses 42 du processeur 4 de commande.

10 Ainsi, en mode de transfert de programme, la mémoire de microprogramme de tous les processeurs est sous la commande du processeur 4 de commande.

15 En outre, dans ce cas, le signal MA peut être transmis à la borne OE de validation de sortie de l'organe 110 de commande si bien que le circuit tampon de sortie de l'organe 110 de commande est mis hors circuit.

20 En outre, en fonction du programme commandant le transfert de programme exécuté par le processeur 4 de commande en mode de transfert de programme, une instruction provenant de la section 46 de commande de chargement provoque la transmission par le générateur 42 d'adresse d'une adresse à la mémoire à accès direct 41, et les données de programme à transmettre à la mémoire 111-114a et 114b de microprogrammes sont lues dans la mémoire à accès direct 41. Simultanément, le signal d'écriture WR provenant du générateur 44 de signaux d'écriture est mis à 0 et le signal de mode MA est 0 ; en conséquence, le signal de sortie de la porte OU 121 est aussi à 0 si bien que la mémoire de microprogramme 111-114a et 114b est mise à l'état de validation d'écriture.

25 30 En conséquence, les données de programme provenant de la mémoire à accès direct 41 sont écrites successivement dans la mémoire de microprogramme 111-114a et 114b en fonction de l'adresse provenant du générateur 42 si bien que le transfert de programme est assuré.

35 Dans cet exemple, le transfert de programme est réalisé séquentiellement pour chaque processeur.

Ainsi, le processeur de commande 4 comporte la

mémoire passive 47 dans laquelle le signal de sélection de processeur est mémorisé. Lorsqu'un programme est transféré à partir de la mémoire passive 47, le signal de sélection de processeur est lu en fonction de l'instruction 5 provenant de la section 46 de commande de chargement. Le signal de sélection de processeur est décodé dans le décodeur 48 et seul le signal de sélection SEL du processeur à sélectionner est mis à 0, les autres signaux étant mis à 1. Le signal SEL continue à être transmis à la porte 10 OU 121 et seule la mémoire de microprogramme 111-114a et 114b du processeur pour lequel le signal de sélection SEL est à 0 est mise à l'état de validation d'écriture si bien qu'une opération de réécriture de programme est réalisée. Lorsqu'une opération d'écriture est terminée dans une mémoire 15 de microprogramme d'un processeur, le signal de processeur a destiné à un autre processeur est extrait de la mémoire passive 47 et le signal de sélection SEL du processeur est mis à 0 ; de même, le transfert du programme vers ce processeur est réalisé. Lorsque les programmes de tous 20 les processeurs doivent être changés, l'opération décrite précédemment est répétée un nombre de fois aussi grand que le nombre de processeurs.

Dans ce cas, lorsque plusieurs programmes doivent être transmis à chaque processeur ou lorsque plusieurs 25 programmes différents doivent être transmis à chaque processeur, ces programmes sont écrits comme un tout dans chaque processeur. Dans chaque processeur, le programme qui doit être exécuté ensuite est spécifié par transmission d'une adresse de début d'exécution à chaque processeur.

30 L'adresse de début d'exécution est extraite de la mémoire à accès direct 49 et est transmise au registre 117c de chaque processeur. Le signal de sélection SEL est transmis comme signal de verrouillage du registre 117c et, au moment où le signal de sélection passe de 0 à 1, 35 l'adresse de début d'exécution est verrouillée.

Le registre 117c est validé par le signal MAP provenant de l'organe 110 de commande et les données verrouil-

lées sont transmises à la borne d'entrée directe D. En mode d'exécution décrit précédemment, lorsqu'un programme commence, l'adresse provenant de ce registre 117c est transmise à l'organe 110 de commande qui crée à son tour les adresses à partir de l'adresse transmise.

De cette manière, un programme et l'adresse de début d'exécution de ce programme sont transmis successivement à un processeur.

10 L'adresse de début d'exécution pour chaque processeur, conservée dans la mémoire à accès direct 49, est transmise préalablement par l'ordinateur hôte 5.

15 Comme décrit précédemment, en mode de transfert de programme, l'organe 110 de commande à microprogramme continue à transmettre l'adresse 0 ou est à l'état d'arrêt.

En mode de réarmement (arrêt), comme les signaux de mode MA et MB sont égaux à 1 et 0 respectivement, une adresse provenant de l'organe 110 de commande est sélectionnée par le sélecteur 120 de chaque processeur et le registre 115 est remis à 0 par le signal MB ; en conséquence, l'organe 20 110 de commande continue à transmettre l'adresse 0 et l'exécution du programme est interrompue dans tous les processeurs.

25 Comme le signal MA est égal à 1, la mémoire de microprogramme 111-114a et 114b ne reçoit pas de signal d'écriture pour une valeur égale à 0.

En mode de remise à 0, parmi plusieurs programmes écrits préalablement dans la mémoire de microprogramme de chaque processeur, une adresse de début d'un programme à exécuter est réaffectée. Ainsi, comme dans l'opération de transfert de programme, les signaux de sélection de processeurs sont transmis séquentiellement par la mémoire passive 47 et l'adresse de début d'exécution est transmise séquentiellement par la mémoire passive 49 à chaque processeur, et l'adresse de début d'exécution est verrouillée successivement dans le registre 117c de chaque processeur en fonction du signal SEL.

En conséquence, lorsque le mode d'exécution est ensuite établi, chaque processeur exécute le programme à

partir de l'adresse réaffectée de début d'exécution. Plus précisément, en l'absence de transfert du nouveau programme, un autre programme peut être exécuté dans chaque processeur.

Les trois modes décrits précédemment sont commandés 5 par un programme du processeur incorporé dans le processeur de commande 4.

Dans la configuration de la figure 1, la section 3 de traitement de données lit en vue du traitement les articles nécessaires à partir des données d'image conservées 10 dans la mémoire d'image 2 et écrit les données traitées à nouveau dans la mémoire d'image 2. En conséquence, pour un groupe de données d'image, tel qu'une trame ou une image de données, en plus du cas dans lequel tous les articles de données sont lus pour l'exécution du travail lui-même, 15 il peut arriver que seules les données nécessaires d'image soient lues dans plusieurs trames, dans plusieurs trames obtenues à partir d'une mémoire d'image, ou sous forme de données appartenant à plusieurs images, et les données obtenues sont soumises au traitement afin qu'une trame ou 20 une image de données soit créée et soit alors écrite dans une mémoire de trame ou d'image. Dans ce cas, la commande des données à l'intérieur de la mémoire d'image 2 est réalisée essentiellement par la section génératrice d'adresse de la mémoire d'image 2. Un processeur est utilisé comme 25 section génératrice d'adresses, et le processeur assure la création des adresses destinées à divers types de traitement, par le calcul.

Dans un système de traitement (par exemple un système de traitement d'image) dans lequel le but du traitement 30 est la mémorisation temporaire, dans une mémoire, avant traitement et dans lequel l'adresse de la mémoire doit être créée comme décrit précédemment, ces opérations sont réalisées habituellement à l'aide d'un processeur. Dans ce cas, la caractéristique nécessaire pour la création d'adresses 35 varie avec le type de traitement. Plus précisément, les adresses nécessaires au traitement sont classées essentiellement en deux types de la manière suivante.

1) Une adresse qui doit être extraite régulièrement à grande vitesse,

2) une adresse qui doit être créée régulièrement et extraite avec une grande quantité de calcul.

5 Cependant, dans le cas où seul l'un de ces types d'adresse est utilisé dans un processeur générateur d'adresses, la réalisation d'un système de traitement convenant au traitement qui nécessite les deux types d'adresses présente des difficultés.

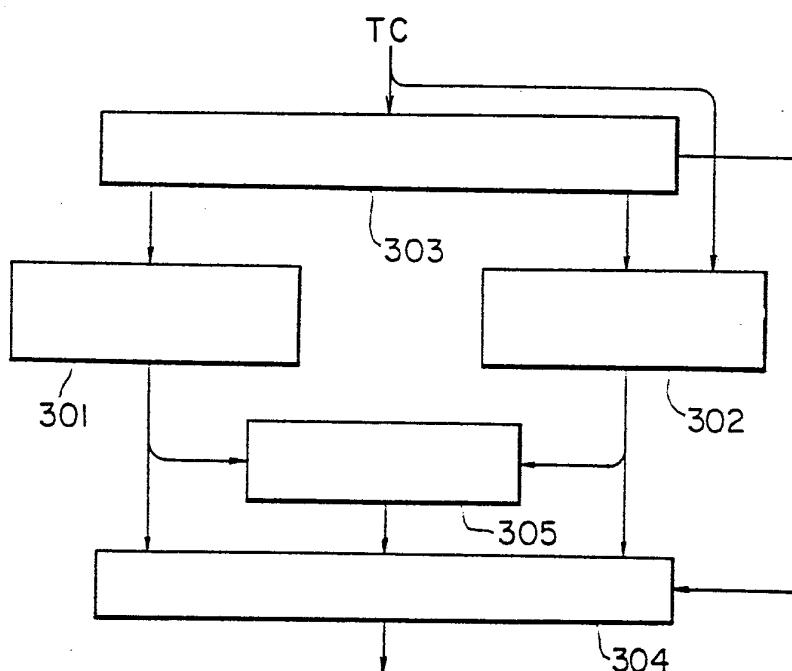

10 Dans ce cas, la section génératrice d'adresses du processeur 3B comporte un premier processeur 301 destiné à créer par le calcul une adresse simple et un second processeur 302 destiné à créer par le calcul une adresse compliquée comme représenté sur la figure 12.

15 Ainsi, sur la figure 12, le premier processeur 301 crée une adresse simple et régulière alors que le second processeur 302 peut exécuter une opération complexe afin qu'il crée une adresse compliquée. En outre, la référence 303 désigne un processeur de commande de création d'adresses destiné à commander le premier et le second processeur 301 et 302.

20 La référence 304 désigne un sélecteur parmi trois données d'adresses comprenant les données d'adresses du premier et du second processeur 301 et 302 et des données 25 composées d'adresses obtenues par exécution d'un calcul dans le circuit arithmétique 305 sur les données d'adresses provenant du premier et du second processeur, avec formation de données d'adresses en fonction d'un signal de sélection provenant du processeur 303 de commande de création d'adresses.

30 Le premier processeur 301 crée une adresse destinée à spécifier par exemple une zone rectangulaire sur un écran et peut être réalisé à l'aide de compteurs utiles à cet effet. Dans ce cas, les adresses du rectangle peuvent être créées dans les directions horizontale et verticale.

35 Le second processeur 302 est par exemple un processeur d'emploi universel qui fonctionne sous la commande d'un microprogramme et, en plus de l'opération linéaire,

ce processeur peut réaliser une opération non linéaire et une opération par adaptation et le programme est transmis par le processeur de commande 4.

Le processeur 303 de commande de création d'adresses 5 transmet des signaux de commande tels qu'un signal de début et des paramètres au premier processeur 301. Le second processeur 302 reçoit des signaux de commande tels qu'un signal de début de programme, alors que les paramètres et les autres informations sont transmis par le processeur 10 de commande 4.

En outre, le microprogramme est transmis par le processeur de commande 4 au processeur 303 de commande de création d'adresses.

Dans le processeur 303 de commande de création 15 d'adresses, la somme des adresses provenant du premier et du second processeur 301 et 302 est calculée, à titre d'exemple.

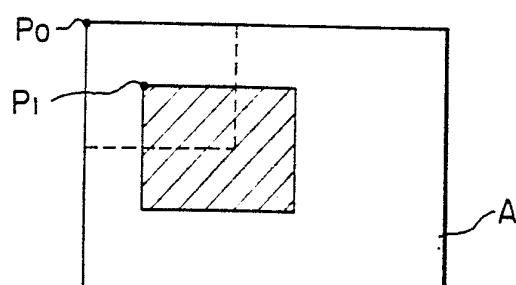

Ainsi, dans le cas où des adresses sont créées 20 afin qu'elles correspondent à une zone rectangulaire dans une partie indiquée par la région hachurée sur l'écran A de la figure 13, le second processeur 302 obtient par le calcul la position  $P$  du coin supérieur gauche de la zone rectangulaire et les données d'adresses de la position sont transmises par le second processeur 302 afin qu'elles 25 parviennent au circuit arithmétique 305.

D'autre part, le processeur 303 de commande de création d'adresse transmet au premier processeur 301 un paramètre indiquant la taille de la zone rectangulaire. Le premier processeur 301 crée alors les adresses de rectangle 30 allant du point  $P_0$  du coin supérieur gauche de l'écran A à la partie entourée par le trait interrompu. Lorsque la somme des adresses de rectangle et de l'adresse  $P_1$  du point initial est calculée, les adresses sont obtenues pour la zone voulue indiquée par les hachures sur la figure 35 13. Le sélecteur 304 sélectionne une adresse à partir du circuit arithmétique 305 en fonction du signal de sélection provenant du processeur de commande 303.

Lorsque la création d'adresses pour la zone indiquée par les hachures sur la figure 13 doit être réalisée par un processeur, un calcul nécessaire à l'obtention du point  $P_1$  et un calcul nécessaire à la création régulière des 5 adresses de la partie rectangulaire sont nécessaires et la vitesse de traitement est réduite ; cependant, comme dans cet exemple, le second processeur 302 continue à transmettre l'adresse du point  $P_1$  et le premier processeur 301 transmet régulièrement une adresse à grande vitesse si 10 bien qu'une addition est réalisée dans le circuit arithmétique 305 et permet la création d'une adresse régulière à grande vitesse à partir de l'adresse calculée par le second processeur 302.

En plus des adresses d'un rectangle, le premier 15 processeur peut créer des données régulières quelconques, par exemple une adresse ayant un ordre inversé de bits nécessaire à la mise en oeuvre d'une transformation rapide de Fourier est créée par le premier processeur 301. Dans le cas où le sélecteur 304 choisit l'une des adresses provenant du premier et du second processeur 301 et 304 l'un 20 des procédés suivants peut être adopté, d'abord un procédé dans lequel la sélection est réalisée en fonction de la vitesse de création d'adresses, et ensuite un second procédé dans lequel la sélection est réalisée en fonction de la 25 vitesse de traitement dans le processeur 3A qui exécute le traitement arithmétique des données des éléments d'images ou pels, et enfin un troisième procédé dans lequel la sélection est réalisée en fonction du temps total de traitement nécessaire à la création de l'adresse et au traitement 30 dans le processeur 3A. Dans tous les cas, lorsqu'un traitement à grande vitesse est très important, le sélecteur 304 est réalisé de manière qu'il reçoive une adresse à grande vitesse. En outre, un cas peut se présenter lorsque 35 le système sélectionne une adresse ayant la moindre probabilité d'erreur, même lorsque la vitesse de traitement est faible.

Selon l'invention, comme plusieurs adresses sont

soumises à une sélection et sont transmises comme adresses suivant l'utilisation et le but du traitement, les adresses adaptées au traitement peuvent être créées efficacement.

En outre, selon l'invention, plusieurs processeurs 5 sont disposés afin qu'ils créent plusieurs adresses et, en plus de la sélection des adresses créées à l'aide d'un sélecteur, les adresses ainsi créées sont calculées convenablement par un autre circuit arithmétique et sont combinées afin qu'elles donnent une autre adresse ; en conséquence, 10 la capacité de traitement est accrue dans le système de traitement.

Dans ce système, lorsque la création d'adresses est associée à un simple changement, par exemple un changement linéaire, il suffit que la configuration comprenne 15 une section arithmétique simple et une section de commande; cependant, lorsque le processeur 3A doit assurer la création d'une adresse compliquée, une configuration simple du processeur 3B ne remplit pas suffisamment cette condition.

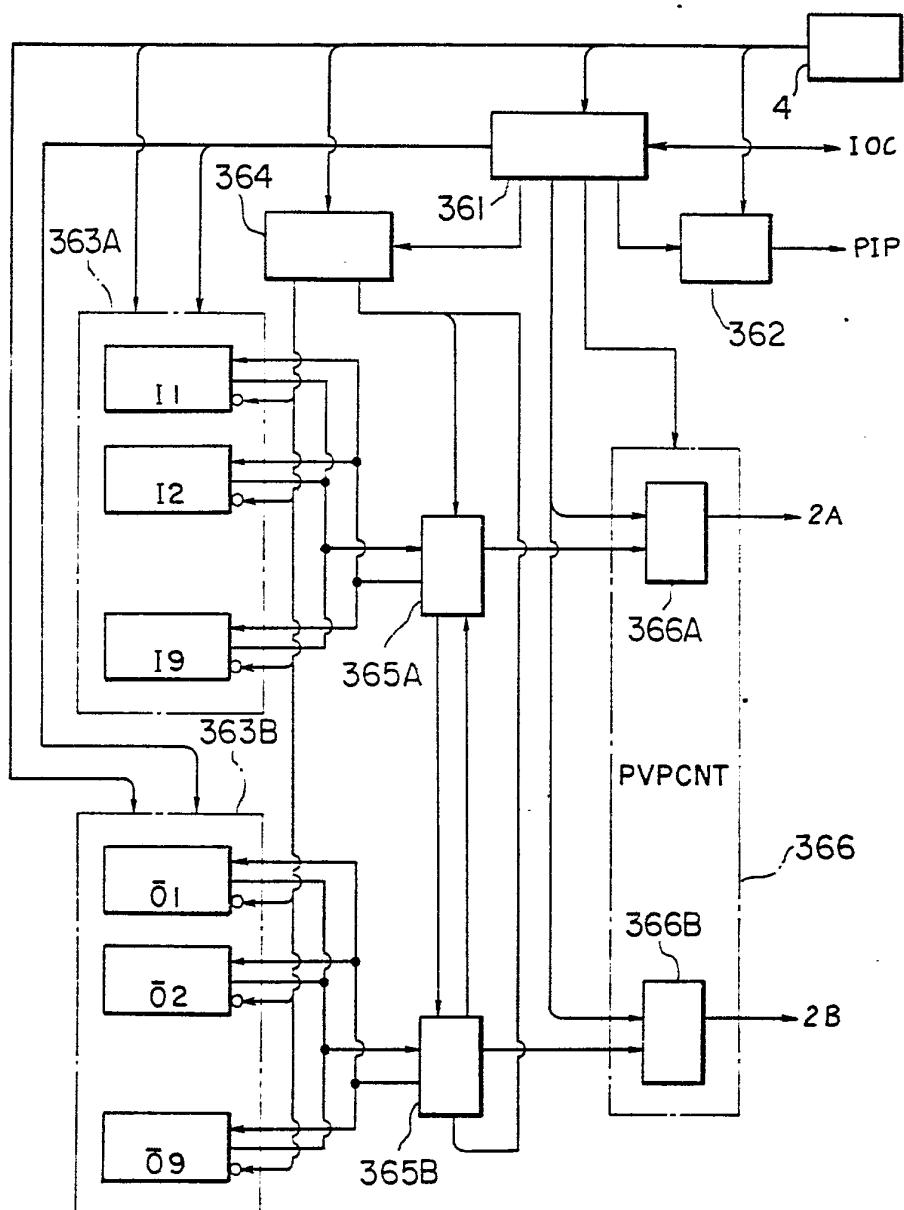

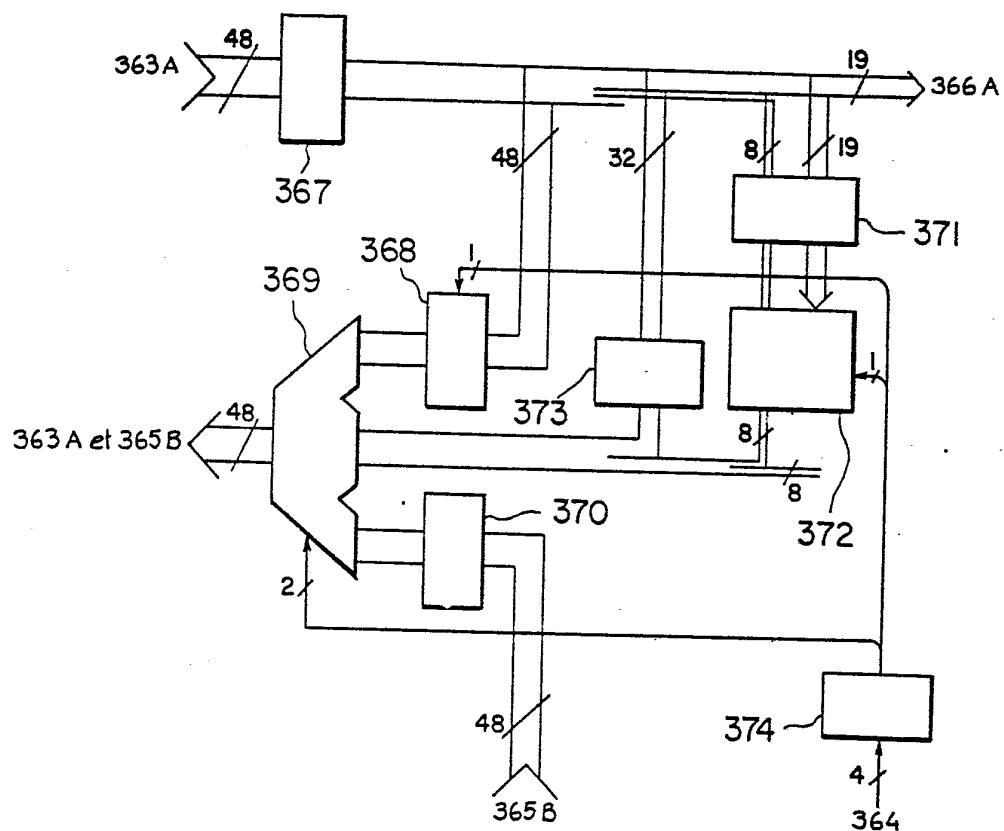

Selon la présente invention, cette difficulté est 20 supprimée par association au processeur 3B d'une section 361 de traitement préalable constituant une première section de traitement, et une information telle qu'un signal de début d'image est transmise entre le processeur préalable 361 et la section d'entrée-sortie 1.

Dans le processeur préalable 361, une adresse simple 25 telle qu'une adresse d'une zone rectangulaire, est créée d'après un microprogramme, et des signaux, tels qu'un signal de commande et un signal de synchronisation destinés à l'autre section de traitement, sont aussi créés et permettent 30 la commande de l'ensemble du fonctionnement du processeur 3B. Les adresses de la zone rectangulaire peuvent être créées dans les directions longitudinale et verticale et avec une séquence inversée de bits.

Le signal de commande provenant du processeur préalable 361 parvient à un circuit 362 constituant la seconde 35 section de traitement. Dans ce circuit 362 de traitement, un signal de commande d'entrée-sortie destiné au processeur

3A est créé en fonction du signal de commande provenant du processeur préalable 361 qui dépend du microprogramme, et il est transmis au processeur 3A.

En outre, le signal de commande provenant du processeur préalable 361 est transmis à des circuits 363A et 363V constituant les troisièmes sections de traitement. Deux systèmes de circuits 363A et 363B sont utilisés pour les mémoires d'image 2A et 2B ; en outre, ces circuits comprennent 9 circuits I1-I9 et 01-09 respectivement comme sections à processeur qui sont équivalentes de la section à processeur du processeur 2A. Dans les sections à processeur, des adresses présentant un changement non linéaire ou un changement par adaptation sont créées en fonction des microprogrammes respectifs.