(19) 日本国特許庁(JP)

## (12) 公開特許公報(A)

(11) 特許出願公開番号

特開2009-200165

(P2009-200165A)

(43) 公開日 平成21年9月3日(2009.9.3)

| (51) Int.Cl.          | F 1        | テーマコード (参考) |

|-----------------------|------------|-------------|

| HO1L 21/822 (2006.01) | HO1L 27/04 | A 5FO38     |

| HO1L 27/04 (2006.01)  | HO1L 21/82 | D 5FO64     |

| HO1L 21/82 (2006.01)  |            |             |

審査請求 未請求 請求項の数 5 O L (全 8 頁)

|           |                            |          |                                             |

|-----------|----------------------------|----------|---------------------------------------------|

| (21) 出願番号 | 特願2008-39049 (P2008-39049) | (71) 出願人 | 500174247<br>エルピーダメモリ株式会社<br>東京都中央区八重洲2-2-1 |

| (22) 出願日  | 平成20年2月20日 (2008.2.20)     | (74) 代理人 | 100123788<br>弁理士 宮崎 昭夫                      |

|           |                            | (74) 代理人 | 100106138<br>弁理士 石橋 政幸                      |

|           |                            | (74) 代理人 | 100127454<br>弁理士 緒方 雅昭                      |

|           |                            | (72) 発明者 | 卯野 裕之<br>東京都中央区八重洲2-2-1 エルピーダメモリ株式会社内       |

|           |                            | (72) 発明者 | 小林 靖明<br>東京都中央区八重洲2-2-1 エルピーダメモリ株式会社内       |

|           |                            |          | 最終頁に続く                                      |

(54) 【発明の名称】半導体装置

## (57) 【要約】

【課題】Pchトランジスタ列とNchトランジスタ列とが向かい合って配置された半導体集積回路において、両トランジスタ列間にウェルコン拡散層及びサブコン拡散層が配置された装置の集積度を高めても、CMPによる平坦化を行う際に歩留まりに悪影響のないパターンにレイアウトを最適化した半導体装置を提供する。

【解決手段】Pchトランジスタ拡散層パターン11及びNchトランジスタ拡散層パターン12との間にウェルコン拡散層パターン13及びサブコン拡散層パターン14がドット状に、Pchトランジスタ列及びNchトランジスタ列の周辺にCMP用のダミーパターン15が配置された半導体装置であって、ウェルコン、サブコン拡散層パターンがライン状に配されるときデータ率が75%を超え、ドット状とすることでデータ率を25~75%の範囲とする。

【選択図】図1

**【特許請求の範囲】****【請求項 1】**

Pchトランジスタ列及びNchトランジスタ列とが向かい合って配置され、両トランジスタ列間にウェルコンタクト拡散層及びサブコンタクト拡散層が、Pchトランジスタ列及びNchトランジスタ列の周辺にCMP用のダミーパターンが配置された半導体装置において、前記ウェルコンタクト拡散層及びサブコンタクト拡散層の少なくとも一方がドット状に形成されていることを特徴とする半導体装置。

**【請求項 2】**

前記ウェルコンタクト拡散層及びサブコンタクト拡散層がライン状に配されているときのデータ率が75%を超えるものであり、ドット状に形成してデータ率を25%～75%にしていることを特徴とする請求項1に記載の半導体装置。 10

**【請求項 3】**

前記ウェルコンタクト拡散層及びサブコンタクト拡散層の両方がドット状に形成されていることを特徴とする請求項1又は2に記載の半導体装置。

**【請求項 4】**

前記ウェルコンタクト拡散層及びサブコンタクト拡散層のドット形状が前記ダミーパターンと同サイズであることを特徴とする請求項1乃至3のいずれか1項に記載の半導体装置。

**【請求項 5】**

前記ウェルコンタクト拡散層及びサブコンタクト拡散層のドット形状がセルサイズに影響しない側に延伸した長方形形状を有することを特徴とする請求項1乃至3のいずれか1項に記載の半導体装置。 20

**【発明の詳細な説明】****【技術分野】****【0001】**

本発明は半導体装置に関し、特にパターンが密に配置される半導体装置において、CMP (Chemical Mechanical Polish) によって平坦化を行う際に歩留まりに悪影響のないパターンにレイアウトを最適化した半導体装置に関する。 30

**【背景技術】****【0002】**

STI (Shallow Trench Isolation) により素子分離をしている半導体装置では、CMPによってウェハ研磨を行い、表面を平坦化させることが一般的である。このCMPを行う際に研磨対象となる工程のパターン疎密状態に差があると、表面の平坦性を保つことが困難となる。

**【0003】**

すなわちパターンが疎である箇所は、表面部が研磨されすぎるためにくぼみ(ディッシング)が生じ、パターンが密である箇所は表面部を平坦化しきれないことがあり、いずれも半導体装置製造時の歩留まりに悪影響を及ぼす。CMPで表面を平坦化させるためには、これらのパターンのデータ率が25～75%の範囲であれば問題は起きないといわれており、この範囲内に収める設計手法が求められている。 40

**【0004】**

ここで、パターンが疎である箇所には回路セルとは電気的に関係のない、フローティングまたは電源電位に接続したダミーパターンを配置して所定のデータ率範囲とすることで、表面部の平坦化を行うことが可能である。一方、パターンが密である場合においては回路セルに必要な要素を間引くことができないため、パターン同士の間隔を離したり、パターンを分割したりしてデータ率を下げる対策を施す必要があるが、チップサイズの増加に繋がるため平坦化対策は難しい。

**【0005】**

ところで、特許文献1には、Pchトランジスタ列とNchトランジスタ列とが向かい合って配置されたマスタスライス型半導体集積回路において、Pchトランジスタ列とN

c h トランジスタ列との間で、N ウェル上にN型拡散領域（ウェルコン拡散層）が形成され、ウェルコン拡散層とN c h トランジスタ列との間にP型拡散領域（サブコン拡散層）が形成された構成が示されている。特許文献2にも同様の構造が示されている。このように、従来は、ウェルコン拡散層、サブコン拡散層は、P c h とN c h 領域の間にライン状に配置され、P c h トランジスタ、N c h トランジスタのラッチアップ対策が取られていた。

#### 【0006】

レイアウト設計では基本論理の回路セルを多数作成し、そのセルの組み合わせによってブロックの設計を行う。この際、設計の効率を上げるためにセルの高さを一定とし、セルの幅はあるピッチの倍数にすることで、縦および横方向に複数のセルを並べる形でブロックを形成する。10

#### 【0007】

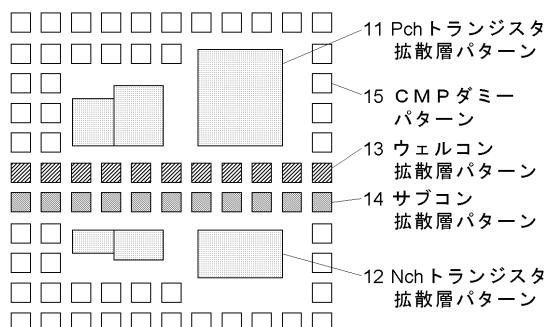

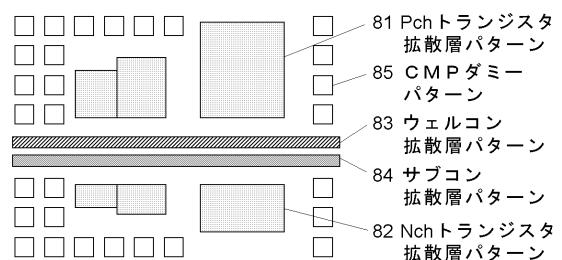

例えば、図2に示すように、トランジスタの回路セルを用いた半導体装置において、回路セルは複数のトランジスタ拡散層パターン（P c h トランジスタ拡散層パターン21、N c h トランジスタ拡散層パターン22）と、電源電位変動やラッチアップを抑制するためのウェルコン拡散層（ウェルコン拡散層パターン23）およびサブコン拡散層（サブコン拡散層パターン24）と、C M Pばらつきを抑制する目的でドット形状のC M Pダミー拡散パターン（C M Pダミーパターン25）が設けられている。

#### 【0008】

このため、素子の微細化が進むと、ウェルコン拡散層およびサブコン拡散層のパターンが密になり、C M P時に周囲よりも層間絶縁膜の研磨が十分ではなくなって、基盤面の厚さばらつきの原因となる場合がある。20

#### 【0009】

このうちトランジスタは実際の回路動作に、ウェルコン拡散層とサブコン拡散層は電源電位変動やラッチアップを抑制するために、いずれも欠かせない要素である。

【特許文献1】特開平6-29500号公報

【特許文献2】特開2006-253393号公報

#### 【発明の開示】

#### 【発明が解決しようとする課題】

#### 【0010】

このようにウェルコン拡散層及びサブコン拡散層が配置された半導体集積回路では、集積度の向上に限界があったのが実情である。30

#### 【0011】

そこで、本発明の目的は、P c h トランジスタ列とN c h トランジスタ列とが向かい合って配置された半導体集積回路において、両トランジスタ列間にウェルコン拡散層及びサブコン拡散層が配置された装置の集積度を高めても、C M Pによる平坦化を行う際に歩留まりに悪影響のないパターンにレイアウトを最適化した半導体装置を提供することにある。

#### 【課題を解決するための手段】

#### 【0012】

本発明者は、上記課題を解決するために銳意検討した結果、従来、ライン状に配されていたウェルコン拡散層及びサブコン拡散層をドット状に分割することで、データ率をC M Pに最適な範囲に低減できることを見出した。又、このようにウェルコン拡散層とサブコン拡散層をドット形状にしても、それぞれに電源電位を供給することで電源電位変動やラッチアップを抑制するという従来の目的を果たすことができるを見出した。40

#### 【0013】

すなわち、本発明の半導体装置は、P c h トランジスタ列及びN c h トランジスタ列とが向かい合って配置され、両トランジスタ列間にウェルコンタクト拡散層及びサブコンタクト拡散層が、P c h トランジスタ列及びN c h トランジスタ列の周辺にC M P用のダミーパターンが配置された半導体装置において、前記ウェルコンタクト拡散層及びサブコン

タクト拡散層の少なくとも一方がドット状に形成されていることを特徴とする半導体装置に関する。

【0014】

特に、上記ウェルコンタクト拡散層及びサブコンタクト拡散層がライン状に配されているときのデータ率が75%を超えるものであり、ドット状に形成してデータ率を25%~75%にしていることを特徴とする。

【0015】

形成されるドット状のパターンは正方形パターンや長方形パターンなど様々な形状を選択し得る。

【発明の効果】

【0016】

本発明の半導体装置は、電源電位変動やラッチアップを抑制するためのウェルコン拡散層とサブコン拡散層をドット形状で配置することによって、フィールドのデータ率をCMOSに問題ない範囲(25~75%)に近づけることができる。この結果、基盤面を平坦に保つことのできる回路セルを提供することが可能である。これは半導体製造時の歩留まり向上に繋がる。

【発明を実施するための最良の形態】

【0017】

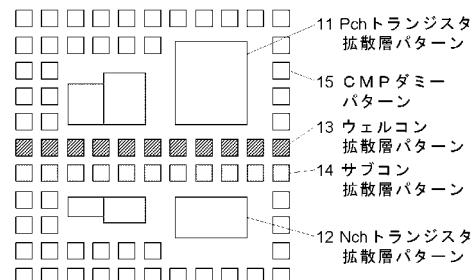

図1は、本発明の一実施形態になる集積回路装置のパターンを説明する図である。これは、先に示した図2におけるウェルコン拡散層パターン23とサブコン拡散層パターン24を、ドット状のウェルコン拡散層パターン13とサブコン拡散層パターン14に変更したものであり、Pchトランジスタ拡散層パターン11、Nchトランジスタ拡散層パターン12、CMOSダミーパターン15は、図2に示す21, 22, 25と同等である。

【0018】

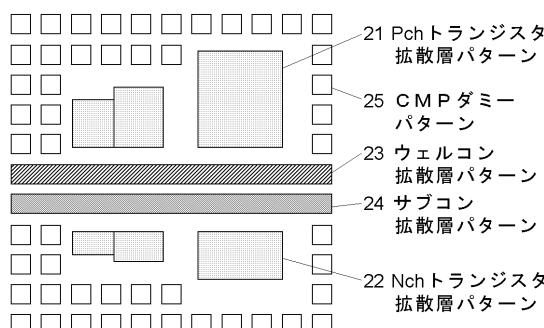

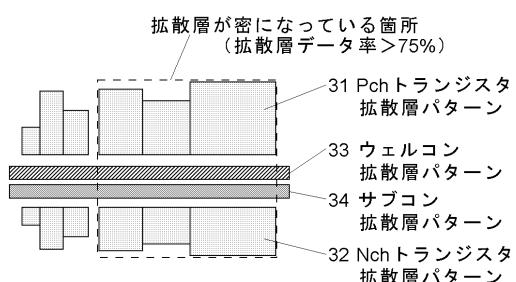

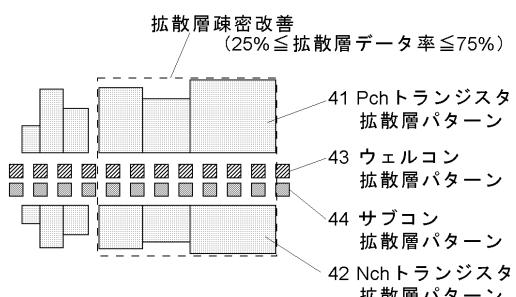

さらに、本発明について図3及び図4を参照して説明する。図3は拡散層密度が高く、CMOS時に問題となるパターンのある回路セルであり、図4は本発明適用における問題回避例である。

【0019】

回路セルはセルサイズ縮小のため同ノードの拡散層を共有させことが多い。トランジスタサイズの大きいバッファーなどを有している箇所、つまり図3における拡散層が密になっている箇所では、CMOSで基盤面を平坦化しきることが難しい。この場合、対策としてトランジスタ拡散層パターン(Pchトランジスタ拡散層パターン31、Nchトランジスタ拡散層パターン32)とウェルコン拡散層パターン33、サブコン拡散層パターン34とのスペースを広げたり、共有しているトランジスタの拡散層を分割する必要がある。

【0020】

ここで、図4のようにPN境界部のウェルコン拡散層パターン43とサブコン拡散層パターン44をドット形状にすることで上記の対策を行わずともフィールドのデータ率をCMOSに問題ない範囲(25~75%)に収めることができる。また、ウェルコン拡散層とサブコン拡散層をドット形状にしても、それぞれに電源電位を供給することで電源電位変動やラッチアップを抑制するという従来の目的を果たすことができる。

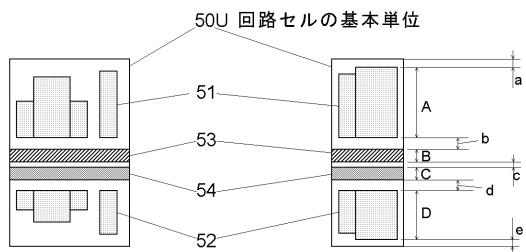

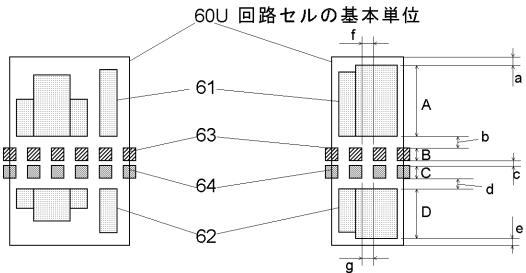

【0021】

本発明の効果について、図5及び図6を参照して具体的に説明する。図5のような回路セルに本発明を適用した場合、図6の形状になる。図6ではウェルコン拡散層パターン63およびサブコン拡散層パターン64の中心をセル幅のピッチ上に配置することで図中における回路セルの基本単位60でセルを上下左右に並べてブロックを構築できる。

【0022】

図5と図6において、(A)はPchトランジスタサイズ、(B)はウェルコン拡散層幅、(C)はサブコン拡散層幅、(D)はNchトランジスタサイズ、(a)はPchトランジスタとセル境界との間隔、(b)はPchトランジスタとウェルコン拡散層との間

隔、(c)はウェルコン拡散層とサブコン拡散層との間隔、(d)はNchトランジスタとサブコン拡散層との間隔、(e)はNchトランジスタとセル境界との間隔、(f)はウェルコン拡散層間隔、(g)はサブコン拡散層間隔である。前述したようにブロック作成時は左右にセルを配置するため、(B)、(C)および(c)は一定値となる。よってこの回路セルにおいて拡散層が最も密になるのは(A)と(D)が最大で、(a)、(b)、(d)、(e)が最小になるときである。

#### 【0023】

ここで、(A)の最大値が6μm、(B)が1μm、(C)が1μm、(D)の最大値が4μm、(a)の最小値が0.5μm、(b)の最小値が1μm、(c)が0.5μm、(d)の最小値が1μm、(e)の最小値が0.5μm、セル高さ15.5μm、また図6の(f)および(g)が1μmの回路セルを例にすると、図5では拡散層が最も密であるときのデータ率は12/15.5=77.4%となり、CMP時の高さばらつきの原因となる。これに対し、図6の場合は、拡散層が最も密であるときのデータ率でも11/15.5=71.0%となり、CMP時に悪影響の出ないデータ率になっている。

10

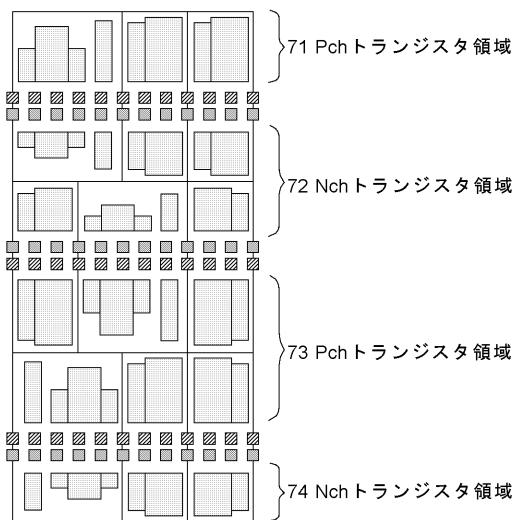

#### 【0024】

図6の回路セルパターンを使用して図7のようなブロックを形成することができ、集積回路装置全体に亘って、CMPにより平坦化が可能となる。

#### 【0025】

(他の実施形態)

前述の実施形態では、ウェルコン拡散層およびサブコン拡散層のパターン形状をCMPダミーのパターン形状と同様に正方形パターンとし、ほぼ同様の大きさとしているが、ウェルコン拡散層パターンとサブコン拡散層パターンとCMPダミーパターンの形状やサイズは任意に変更することも可能である。

20

#### 【0026】

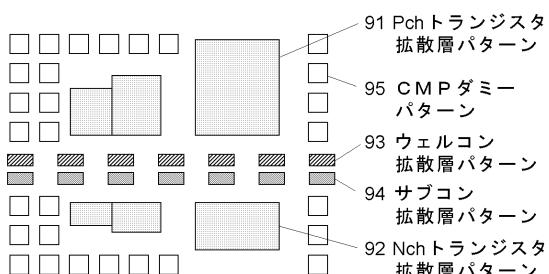

CMPダミーはパターン倒れや飛び防止のため、レイアウトにおける最小基準よりも大きめの形状で生成する場合が多く、図8のようにウェルコン拡散層パターン83、サブコン拡散層パターン84の幅がCMPダミーパターンのサイズよりも小さい回路セルの場合、前述の実施形態と同様に正方形パターンにしてしまうと、ドット数が増加し、各ドットへの電源電位供給を設けなければならない。逆に幅方向を拡張してCMPダミーパターンと同サイズのドットにすると、縦方向のセルサイズが増加することとなる。

30

#### 【0027】

この対策として、図9のようにウェルコン拡散層パターン93及びサブコン拡散層パターン94のセルサイズに影響を受ける側(幅)は図8に示す各パターン83,84と同じとし、影響のない側に延伸させることでドット数の増加を抑え、かつセルサイズを増加させることなく基盤面の平坦化を行うことが可能となる。

#### 【0028】

以上の説明では、ウェルコン拡散層パターン及びサブコン拡散層パターンの両方をドット形状にしている例を説明したが、データ率をCMPに問題ない範囲(25~75%)にできるのであれば、いずれか一方をドット状に形成するようにしても良い。

40

#### 【図面の簡単な説明】

#### 【0029】

【図1】本発明の一実施形態になるウェルコン拡散層およびサブコン拡散層パターンを有する回路セルパターンを示す図である。

【図2】従来例になるウェルコン拡散層およびサブコン拡散層形状を有する回路セルパターンを示す図である。

【図3】従来例になるウェルコン拡散層およびサブコン拡散層形状を有する回路セルのパターン密集部を示す図である。

【図4】本発明によりデータ率の改良されたウェルコン拡散層およびサブコン拡散層形状を有する回路セルのパターン密集部を示す図である。

【図5】本発明の効果を説明するための従来例パターン密度を例示する図である。

50

【図6】本発明の効果を説明するための本発明の一実施形態になるパターン密度を例示する図である。

【図7】図6の回路セルパターンを使用した半導体集積回路のプロック図である。

【図8】本発明の別の実施形態を説明するための従来例パターンを示す図である。

【図9】本発明の別実施形態になるウェルコン拡散層およびサブコン拡散層パターンを有する回路セルパターンを説明する図である。

【符号の説明】

【0 0 3 0】

1 1、4 1、6 1、9 1 Pchトランジスタ拡散層パターン

1 2、4 2、6 2、9 2 Nchトランジスタ拡散層パターン

1 3、4 3、6 3、9 3 ウェルコン拡散層パターン

1 4、4 4、6 4、9 4 サブコン拡散層パターン

1 5、9 5 CMPダミーパターン

6 0 U 回路セルの基本単位

7 1、7 3 Pchトランジスタ領域

7 2、7 4 Nchトランジスタ領域

10

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

---

フロントページの続き

F ターム(参考) 5F038 CA01 CA07 CA18 EZ20

5F064 AA04 CC12 DD05 DD07 DD10 DD31 GG10