República Federativa do Brasil

Ministério do Desenvolvimento, Indústria

e do Comércio Exterior

Instituto Nacional da Propriedade Industrial.

**(21) PI9715316-8 A2**

(62) Data de Depósito do Pedido Original:

PI9715316 - 02/06/1997

(22) Data de Depósito: 02/06/1997

**(43) Data da Publicação: 23/03/2010**

**(RPI 2046)**

\* B R P I 9 7 1 5 3 1 6 A 2 \*

**(51) Int.Cl.:**

H04N 5/60 (2010.01)

H04N 7/08 (2010.01)

H04N 7/084 (2010.01)

H04N 7/087 (2010.01)

Notificação de Depósito de Pedido Dividido:

RPI 2046 de 23/03/2010

**(54) Título: CODIFICADOR BTSC**

(30) Prioridade Unionista: 07/06/1996 US 08/661.412

(73) Titular(es): That Corporation

(72) Inventor(es): Christopher M. Hanna

(74) Procurador(es): Nellie Anne Daniel Shores

(86) Pedido Internacional: PCT US9709493 de 02/06/1997

(87) Publicação Internacional: WO 97/47102 de 11/12/1997

**(57) Resumo:** Trata-se de um codificador BTSC (200) que inclui um filtro de banda alta digital esquerdo (212) para receber um sinal de áudio digital do canal esquerdo (L) e gerar um sinal digital esquerdo filtrado; um filtro de banda alta digital direito (214) para receber um sinal de áudio digital do canal direito (R) e gerar um sinal digital direito filtrado; uma matriz inclui um adicionador (216) para somar os sinais digitais filtrados esquerdo e direito e gerar um sinal de soma digital (L+R) e incluindo um subtraído (218) para subtrair um dos sinais filtrados digitais esquerdo e direito do outro dos sinais digitais filtrados esquerdo e direito e gerar um sinal de diferença digital (L-R); um processador do canal de diferença (230) para processar de forma digital o sinal de diferença digital (L-R); e um processador do canal de soma (220) para processar de forma digital o sinal de soma digital (L+R).

"Dividido do PI 9714304-9 depositado em 02/06/1997"

Campo da Invenção

A presente invenção relaciona-se em geral com codificadores de áudio estereofônicos utilizados para a transmissão de televisão. Mais particularmente, a invenção relaciona-se com um codificador digital para gerar os sinais de áudio utilizados na transmissão de sinais de televisão estereofônicos nos Estados Unidos e em outros países.

Fundamento da Invenção

No ano de 1980, a Comissão de Comunicações Federal dos Estados Unidos (FCC) adotou novas regulamentações cobrindo a parte de áudio dos sinais de televisão que permitiam que os programas de televisão de serem transmitidos e recebidos com áudio de duplo canal, como por exemplo o som estereofônico. Nessas regulamentações, a FCC reconheceu e deu proteção especial a um método de transmissão de canais de áudio adicional endossado pela Associação de Indústrias Eletrônicas e pela Associação Nacional de Transmissoras e pelo chamado sistema de Comitê de Sistemas de Televisão (BTSC). Este padrão bem conhecido é algumas vezes referido como Som de Televisão de Múltiplos Canais (MTS) e é descrito no documento da FCC intitulado MULTICHANNEL TELEVISION SOUND TRANSMISSION AND AUDIO PROCESSING REQUIREMENTS FOR THE BTSC SYSTEM (Boletim OET Nº 60, Revisão A, Fevereiro de 1986), bem como no documento publicado pela Associação de Indústrias Eletrônicas intitulado MULTICHANNEL TELEVISION SOUND BTSC SYSTEM RECOMMENDED PRACTICES (Boletim da Sistemas de Televisão EIA Nº 5, de julho de 1985). Os sinais de televisão gerados de acordo com o padrão BTSC são referidos daqui para frente como "sinais BTSC".

Os sinais de televisão monofônicos originais transportados em um único canal de áudio. Devido a configuração do sinal de televisão monofônico e a necessidade de se manter a compatibilidade com os aparelhos de televisão existente, a informação estereofônica foi necessariamente localizada em uma região de freqüência mais elevada do sinal BTSC fazendo o canal estereofônico muito mais ruidoso do que o canal de áudio monofônico. Isto resultou em um piso de perturbação inherentemente mais elevado para o sinal estéreo do que para o sinal monofônico. O padrão BTSC superou este problema por definir um sistema de codificação que proporcionou um processamento adicional do sinal para o sinal de áudio estereofônico. Antes da transmissão de um sinal BTSC por uma estação de televisão, a parte de áudio de um programa de televisão é codificada da maneira prescrita pelo padrão BTSC e durante a recepção de um sinal BTSC um receptor (por exemplo, um aparelho de televisão) então decodifica a parte de áudio de uma maneira complementar. Esta codificação e decodificação complementar assegura que a taxa de sinal para ruído de todo o sinal de áudio estéreo seja mantida em níveis aceitáveis.

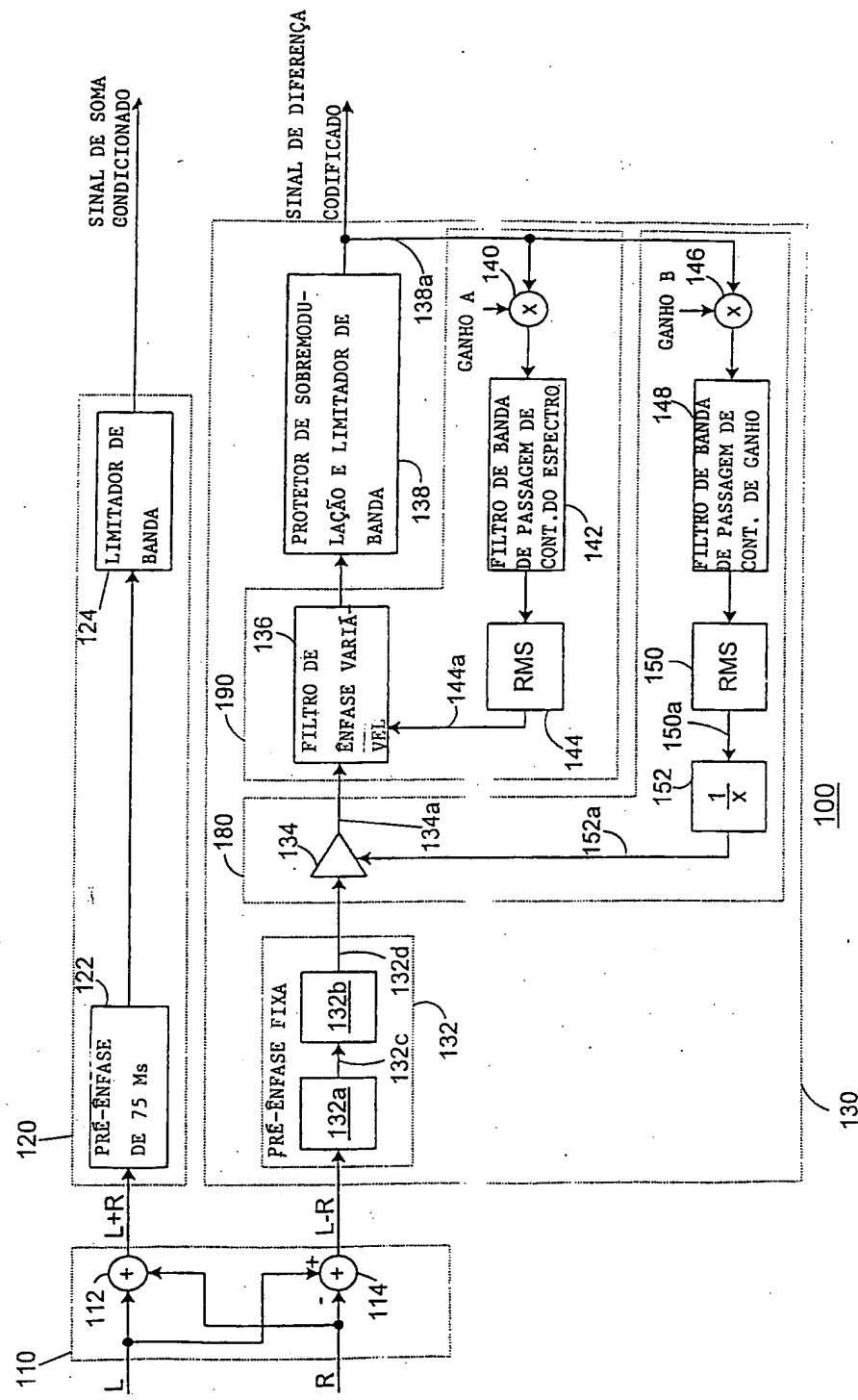

A Figura 1 é um diagrama de blocos de um sistema de codificação BTSC da técnica anterior, ou mais simplesmente, um codificador BTSC 100, como definido pelo padrão BTSC. O codificador 100 recebe sinais de entrada do canal esquerdo e direito (indicados na Figura 1 como "L" e "R", respectivamente) e gera a partir dos mesmos um sinal de soma condicionado e um sinal de diferença codificado. Deve ser apreciado que enquanto o sistema da técnica anterior e este da presente invenção são descritos como úteis para a codificação dos sinais de áudio esquerdo e direito de um sinal estereofônico que é de forma subsequente transmitido como um sinal de televisão, o sistema BTSC também proporciona um dispositivo para codificar um sinal de áudio separado, como por exemplo, a informação de áudio em uma linguagem diferente, que é separado e selecionado pelo receptor final. Adicionalmente, os componentes de redução de ruído do sistema de codificação BTSC podem ser utilizados para outros propósitos além da transmissão de televisão, tal como para aperfeiçoar as gravações de áudio.

O sistema 100 inclui uma seção de entrada 110, uma seção de processamento do canal de soma 120 e uma seção de processamento de canal de diferença 130. A seção de entrada 110n recebe os sinais de entrada de áudio dos canais esquerdo e direito e gera a partir dos mesmos um sinal de soma (indicado na Figura 1 como "L + R") e um sinal de diferença (indicado na Figura 1 como "L - R"). É bem conhecido que para os sinais estereofônicos, o sinal de soma L + R pode ser utilizado por ele próprio para proporcionar a reprodução do áudio monofônico e é este sinal que é decodificado pelos aparelhos de televisão de áudio monofônico existentes para reproduzir o som. Em aparelhos estereofônicos, os sinais de soma e de diferença podem ser adicionados e subtraídos um do outro para recuperar os dois sinais estereofônicos originais (L) e (R). A seção de entrada 110 inclui dois adicionadores de sinal 112, 114. O adicionador 112 soma os sinais de entrada de áudio do canal esquerdo e direito para gerar o sinal de soma e o adicionador 114 subtrai o sinal de entrada de áudio do canal direito do sinal de entrada de áudio do canal esquerdo para gerar o sinal de diferença. Como descrito acima, o sinal de soma L + R é transmitido através de um meio de transmissão com o mesmo sinal para a razão de ruído como alcançado com os sinais monofônicos anteriores. Entretanto, o sinal de diferença L-R é transmitido através de um canal muito ruidoso, particularmente na parte de freqüência mais elevada do espectro relevante de modo que o sinal de diferença decodificado possui uma taxa de sinal para ruído mais pobre por causa do meio ruidoso e da faixa dinâmica reduzida do meio. A faixa dinâmica é definida como a faixa de sinais entre o nível do piso de perturbação e o nível máximo onde ocorre a saturação do áudio. No canal de sinal de diferença a faixa dinâmica diminui em freqüências mais elevadas. Por consequência, o sinal de diferença está sujeito a processamento adicional ao do sinal de soma de modo que a faixa dinâmica pode ser substancialmente preservada.

Mais particularmente, a seção de processamento do canal de soma 120 recebe o sinal de soma e gera a partir do mesmo o sinal de soma condicionado. A seção 120 inclui um filtro de pré-ênfase 122 e um limitador de banda 124. O sinal de soma é aplicado para a entrada do filtro 122 que gera a partir do mesmo um sinal de saída que é aplicado para a 5 entrada do limitador de banda 124. O sinal de saída gerado pelo último é então o sinal de soma condicionado.

A seção de processamento de canal de diferença 130 recebe o sinal de diferença e gera a partir do mesmo o sinal de diferença codificado. A seção 130 inclui um filtro de pré-ênfase fixo 132 (apresentado implementado como uma cascata de dois filtros 132a e 132b), 10 um amplificador de ganho variável 134, de preferência na forma de um amplificador controlado por voltagem, um filtro de pré-ênfase/de-ênfase variável (referido daqui para frente como um “filtro de ênfase variável”) 136, um protetor de sobre-modulação e limitador de banda 138, um amplificador de ganho fixo 140, um filtro de banda baixa 142, um detector de nível RMS 144, um amplificador de ganho fixo 146, um filtro de banda de passagem 148, 15 um detector de nível RMS 150 e um gerador recíproco 152.

O sinal de diferença é aplicado a entrada do filtro de pré-ênfase fixo 132 que gera a partir do mesmo um sinal de saída que é aplicado via a linha 132d a um terminal de entrada do amplificador 134. Um sinal de saída gerado pelo gerador recíproco 152 é aplicado via a linha 152 a um terminal de controle de ganho do amplificador 134. O amplificador 134 gera 20 um sinal de saída por amplificar o sinal na linha 132d utilizando um ganho que é proporcional ao valor do sinal na linha 152a. O sinal de saída gerado pelo amplificador 134 é aplicado, via a linha 134a, para um terminal de entrada do filtro de ênfase variável 136 e um sinal de saída gerado pelo detector RMS 144 é aplicado via a linha 144a a um terminal de controle do filtro 136. O filtro de ênfase variável 136 gera um sinal de saída por pré-ênfatizar 25 ou de-ênfatizar as parte de freqüência elevada do sinal na linha 134a sob o controle do sinal na linha 144a. O sinal de saída gerado pelo filtro 136 é aplicado a entrada do protetor de sobre-modulação e do limitador de banda 138 que gera a partir do mesmo o sinal de diferença codificado.

O sinal de diferença codificado é aplicado via o caminho de realimentação 138a 30 para as entradas dos amplificadores de ganho fixo 140, 146, que amplificam o sinal de diferença codificado por Ganho A e Ganho B, respectivamente. O sinal amplificado gerado pelo amplificador 140 é aplicado a uma entrada do filtro de banda baixa 142 que gera a partir do mesmo um sinal de saída que é aplicado a entra do detector de nível RMS 144. O último gera um sinal de saída como uma função do valor RMS do nível do sinal de entrada 35 recebido a partir do filtro 142. O sinal amplificado gerado pelo amplificador 146 é aplicado a entrada do filtro de banda de passagem 148 que gera a partir do mesmo um sinal de saída que é aplicado a entrada do detector de nível RMS 150. O último gera um sinal de saída

como uma função do valor RMS do nível do sinal de entrada recebido a partir do filtro 148. O sinal de saída do detector 150 é aplicado via a linha 150a para o gerador recíproco 152 que gera um sinal na linha 152 que é representativo do recíproco do valor do sinal na linha 150a. Como afirmado acima, os sinais de saída gerados pelo detector de nível RMS 144 e pelo gerador recíproco 152 são aplicados ao filtro 136 e ao amplificador 134, respectivamente.

Como apresentado na Figura 1, a seção de processamento do canal de diferença 130 é consideravelmente mais complexa do que a seção de processamento do canal de soma 120. O processamento adicional proporcionado pela seção de processamento do canal de diferença 130, em combinação com o processamento complementar proporcionado por um decodificador (não apresentado) recebendo um sinal BTSC, mantém a taxa de sinal para ruído do canal de diferença em níveis aceitáveis mesmo na presença do piso de ruído mais elevado associado com a transmissão e a recepção do canal de diferença. A seção de processamento do canal de diferença 130 essencialmente gera o sinal de diferença codificado por dinamicamente comprimir, ou reduzir a faixa dinâmica do sinal de diferença, de modo que o sinal codificado pode ser transmitido através do caminho de transmissão de faixa dinâmica limitado associado com um sinal BTSC e de modo que um decodificador recebendo o sinal codificado possa recuperar toda a faixa dinâmica no sinal de diferença original por expandir o sinal de diferença comprimido de um modo complementar. A seção de processamento do canal de diferença 130 é uma forma particular do sistema de peso de sinal adaptativo descrito na Patente dos Estados Unidos Nº 4.539.526, que é conhecido como sendo vantajoso para transmitir um sinal possuindo uma faixa dinâmica relativamente grande através de um caminho de transmissão possuindo uma faixa dinâmica relativamente estreita dependente da freqüência.

Resumidamente, a seção de processamento do canal de diferença pode ser pensada como incluindo uma unidade de compressão de banda larga 180 e uma unidade de compressão de espectro 190. A unidade de compressão de banda larga 180 inclui o amplificador de ganho variável 134 de preferência na forma de um amplificador controlado por voltagem e os componentes do caminho de realimentação para gerar o sinal de controle para o amplificador 134 e compreendendo o amplificador 146, o filtro de banda de passagem 148, o detector de nível RMS 150 e o gerador recíproco 152. O filtro de banda de passagem 148 possui uma banda de passagem relativamente larga, ponderada em direção a freqüências de áudio inferiores, de modo que durante a operação, o sinal de saída gerado pelo filtro 148 e aplicado ao detector de nível RMS 150 é substancialmente representativo do sinal de diferença codificado. Portanto, o detector de nível RMS 150 gera um sinal de saída na linha 15a representativo de uma média ponderada do nível de energia do sinal de diferença codificado e o gerador recíproco 152 gera um sinal na linha 152a representativo do recíproco desta média ponderada. O sinal na linha 152a controla o ganho do amplificador

134 e desde que este ganho é inversamente proporcional a média ponderada (isto é, ponderada com respeito as freqüência de áudio inferiores) do nível de energia do sinal de diferença codificado, a unidade de compressão de banda larga 180 "comprime", ou reduz a faixa dinâmica do sinal na linha 132a por amplificar os sinais possuindo amplitudes relativamente baixas e sinais de atenuação possuindo amplitudes relativamente grandes.

5 A unidade de compressão de espectro 190 inclui o filtro de ênfase variável 136 e os componentes do caminho de realimentação gerando um sinal de controle para o filtro 136 e ,compreendendo o amplificador 140, o filtro de banda baixa 142 e o detector de nível RMS 144. Ao contrário do filtro 148, o filtro de banda baixa 142 possui uma banda de passagem

10 relativamente estreita que é ponderada com respeito as freqüências de áudio mais elevadas. Como é bem conhecido, o meio de transmissão associado com a parte de diferença do sistema de transmissão BTSC possui uma faixa dinâmica dependente da freqüência e a banda de passagem do filtro 142 é escolhida para corresponder a parte do espectro deste caminho de transmissão possuindo a faixa dinâmica mais estreita (isto é, a 15 parte de freqüência mais elevada). Durante a operação, o sinal de saída gerado pelo filtro 142 e aplicado ao detector de nível RMS 144 contém primariamente as partes de alta freqüência do sinal de diferença codificado. Portanto, o detector de nível RMS 144 gera um sinal de saída na linha 144a representativo do nível de energia nas partes de alta freqüência do sinal de diferença codificado. Então, este sinal controla a pré-ênfase/de-ênfase aplicada

20 pelo filtro de ênfase variável 1136 de modo que no efeito, a unidade de compressão de espectro 190 dinamicamente comprime as parte de alta freqüência do sinal na linha 134a por uma quantidade determinada pelo nível de energia nas partes de alta freqüência do sinal de diferença codificado como determinado pelo filtro 142. Então, o uso da unidade de compressão de espectro 190 proporciona uma compressão de sinal adicional com respeito

25 as partes de alta freqüência do sinal de diferença, o que combina com a compressão de banda larga proporcionada pelo amplificador de ganho variável 134 para efetivamente causar que uma compressão total aconteça em altas freqüências em relação a compressão das freqüências inferiores. Isto é feito porque o sinal de diferença tende a ser mais ruidoso na parte de freqüência mais elevada do espectro. Quando o sinal de diferença codificado é

30 decodificado com um expensor de banda larga e um expensor de espectro em um decodificador (não apresentado), respectivamente de uma maneira complementar para a unidade de compressão de banda larga 180 e para a unidade de compressão de espectro 190 do codificador, a taxa de sinal para ruído do sinal L-R aplicado a seção de processamento de canal de diferença 130 será substancialmente preservada.

35 O padrão BTSC rigorosamente define a operação desejada do filtro de pré-ênfase de 75  $\mu$ s 122, do filtro de pré-ênfase fixo 132, do filtro de ênfase variável 136 e dos filtros de banda de passagem 142, 148, em termos de filtros analógicos idealizados. Especificamente,

o padrão BTSC proporciona uma função de transferência para cada um destes componentes e as funções de transferência são descritas em termos de representações matemáticas dos filtros analógicos idealizados. O padrão BTSC também define os parâmetros de ganho, Ganho A e Ganho B, dos amplificadores 140 e 146, respectivamente 5 e também define a operação do amplificador 134, dos detectores de nível RMS 144, 150 e do gerador recíproco 152. O padrão BTSC também proporciona normas sugeridas para a operação do protetor de sobre-modulação e do limitador de banda 138 e do limitador de banda 124. Especificamente, o limitador de banda 1324 e a parte do limitador de banda do protetor de sobre-modulação e do limitador de banda 138 são descritas como filtros de baixa 10 passagem com freqüências de interrupção de 15 kHz e a parte de proteção de sobre-modulação do protetor de sobre-modulação e limitador de banda 138 é descrita como um dispositivo de limite que limita a amplitude do sinal de diferença codificado para 100% da modulação completa onde a modulação completa é o nível de desvio permitível máximo para modular o subportador de áudio em um sinal de televisão.

15        Desde que o codificador 100 é definido em termos de descrições matemáticas dos filtros idealizados, ele pode ser pensado como um codificador idealizado ou teórico e aqueles com conhecimento na técnica irão apreciar que é virtualmente impossível construir uma realização física de um codificador BTSC que combine exatamente a performance do codificador teórico 100. Portanto, é esperado que a performance de todos os codificadores 20 BTSC se desvie alguma coisa do ideal teórico e o padrão BTSC define os limites máximos nas quantidades aceitáveis de desvio. Por exemplo, o padrão BTSC afirma que um codificador BTSC deve proporcionar pelo menos 30 dB de separação de 100 Hz até 8.000 Hz onde a separação é uma medida de quanto um sinal aplicado para somente uma das entradas dos canais esquerdo e direito aparece erroneamente nas outras saídas dos canais 25 esquerdo e direito.

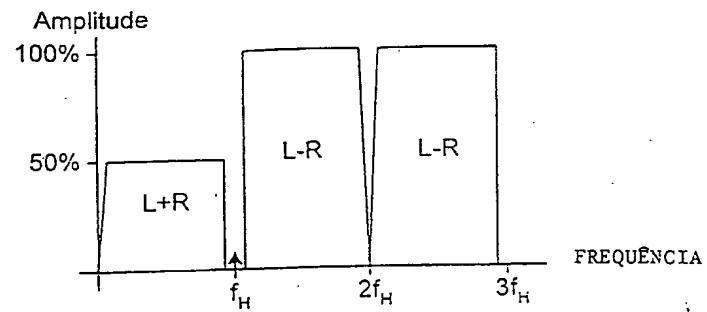

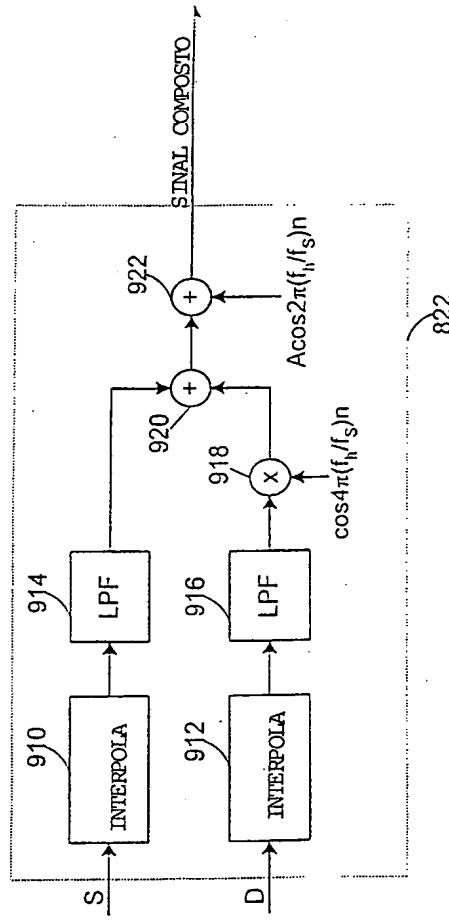

O padrão BTSC também define um sinal de banda base estereofônico composto (referido daqui para frente como o "sinal composto") que é utilizado para gerar a parte de áudio de um sinal BTSC. O sinal composto é gerado utilizando-se o sinal de soma condicionado, o sinal de diferença codificado e um sinal de tom, normalmente referido como 30 o "tom piloto" ou simplesmente como "piloto", que é uma onda seno em uma freqüência  $f_H$  onde  $f_H$  é igual a 15.734 Hz. A presença do piloto em um sinal de televisão recebido indica para o receptor que o sinal de televisão é um sinal BTSC ao invés de um sinal monofônico ou não BTSC. O sinal composto é gerado por se multiplicar o sinal de diferença codificado por uma forma de onda que oscila em duas vezes a freqüência do piloto de acordo com uma 35 função cosseno  $\cos(4\pi f_H t)$ , onde  $t$  é o tempo, para gerar um sinal portador suprimido de banda lateral dupla de amplitude modulada e por então adicionar para este sinal o sinal de soma condicionado e o tom piloto.

A Figura 2 é um gráfico do espectro do sinal composto. Na Figura 2 a banda de espectro de interesse contendo o conteúdo do sinal de soma condicionado (ou o "sinal de canal de soma") é indicada como "L + R", as duas bandas laterais do espectro contendo o conteúdo do sinal de diferença codificado de freqüência deslocada (ou o "sinal de canal de diferença") estão cada uma indicadas como "L-R", e o tom piloto é indicado pela seta na freqüência  $f_H$ . Como apresentado na Figura 2, no sinal composto, o sinal de diferença codificado é utilizado em 100% da modulação completa, o sinal de soma condicionado é utilizado em 50% da modulação completa e o tom piloto é utilizado em 10% da modulação completa.

A televisão estereofônica tem sido amplamente bem sucedida e os codificadores existente têm executado de forma admirável, entretanto, virtualmente cada codificador BTSC atualmente em uso foi construído utilizando a tecnologia de circuitamento analógico. Estes codificadores BTSC analógicos e particularmente as seções de processamento de canal de diferença analógicas, devido a sua aumentada complexidade têm sido relativamente difíceis e dispendiosas para construir. Devido a variabilidade dos componentes analógicos, uma seleção de componente complexa e uma calibragem extensiva tem sido requerido para produzir seções de processamento de canal de diferença analógicas aceitáveis. Adicionalmente, a tendência dos componentes analógicos de derivarem, durante o tempo para longe dos seus pontos de operação calibrados tem também tornado difícil produzir uma seção de processamento de canal de diferença que de forma consistente e repetida execute dentro de uma dada tolerância. Uma seção de processamento de canal de diferença digital, se puder ser construída, não iria sofrer destes problemas de seleção de componente, de calibragem e de derivação de performance e poderia potencialmente proporcionar uma performance aumentada.

Adicionalmente, a natureza analógica dos codificadores BTSC existentes os têm feito inconvenientes para uso com o equipamento digital recentemente desenvolvido ficando cada vez mais popular. Por exemplo, os programas de televisão agora podem ser armazenados utilizando um meio de armazenamento digital tal como um disco rígido ou uma fita digital, ao invés do que o meio de armazenamento analógico tradicional e no futuro um uso crescente será feito do meio de armazenamento digital. A geração de um sinal BTSC a partir de um programa armazenamento de forma digital atualmente requer que se converta os sinais de áudio digitais para sinais analógicos e então aplicar os sinais analógicos para o codificador BTSC analógico. Um codificador BTSC digital, se puder ser construído, poderia aceitar os sinais de áudio digitais diretamente e poderia portanto ser mais facilmente integrado com outro equipamento digital.

Ao mesmo tempo que um codificador BTSC digital poderia potencialmente oferecer várias vantagens, não existe um modo simples de construir um codificador utilizando a

tecnologia digital que seja funcionalmente equivalente ao codificador 100 idealizado definido pelo padrão BTSC. Um problema é que o padrão BTSC define todos os componentes críticos do codificador 100 idealizado em termos de funções de transferência de filtro analógico. Como é bem conhecido, ao mesmo tempo que é em geral possível projetar um filtro digital de modo que a resposta de magnitude ou de fase do filtro digital combine com a de um filtro analógico, é extremamente difícil combinar ambas as respostas de amplitude e de fase sem requer grandes quantidades de capacidade de processamento para dados de processamento de taxas de amostras muito altas ou sem aumentar de forma significante a complexidade do filtro digital. Sem aumentar ou a freqüência da amostra ou a ordem do filtro, a resposta de amplitude de um filtro digital pode normalmente feita para combinar de forma mais próxima do que um filtro analógico com o custo de aumentar a disparidade entre as respostas de fase dos dois filtros e vice e versa. Entretanto, desde que pequenos erros ou na amplitude ou na fase diminuem a quantidade de separação proporcionada pelos codificadores BTSC, seria essencial para um codificador BTSC digital combinar de forma próxima ambas as respostas de amplitude e de fase de um codificador idealizado do tipo apresentado como 100 na Figura 1.

Para um codificador BTSC digital proporcionar uma performance aceitável, é crítico preservar as características dos filtros analógicos de um codificador 100 idealizado. Várias técnicas existem para projetar um filtro digital para combinar a performance de um filtro analógico; entretanto, em geral, nenhuma destas técnicas produz um filtro digital (da mesma natureza do filtro analógico) possuindo respostas de amplitude e de fase que combinem de forma exata com as respostas correspondentes do filtro analógico. O codificador ideal 100 é definido em termos de funções de transferência analógicas especificadas no campo de freqüência, ou no plano s e para projetar um codificador BTSC digital, estas funções de transferência devem ser transformadas para o plano z. Tal transformação deve ser executada como um mapeamento de vários para um a partir do plano s para o plano z, que tenta preservar as características do campo de tempo. Entretanto, em tal transformação, as respostas do campo de freqüência estão sujeitas a um sinal falso resultante da digitalização de uma amostra de áudio analógica e podem ser alteradas de forma significante. Alternativamente, a transformação pode ser executada como um mapeamento de "um para um" a partir do plano s para o plano z, o que comprime todo o plano s no círculo unitário do plano z. Entretanto, tal compressão sofre da "deformação de freqüência" familiar entre as freqüências analógicas e digitais. A pré-deformação pode ser empregada para compensar este efeito de deformação de freqüência, entretanto, a pré-deformação não elimina completamente os desvios da resposta de freqüência desejada. Estes problemas teriam que ser superados para produzir um codificador BTSC digital que execute corretamente e que não seja indevidamente complexo ou dispendioso.

Portanto, existe uma necessidade de superar estas dificuldades e desenvolver um codificador BTSC digital.

Objetivos da Invenção

É um objetivo da presente invenção substancialmente reduzir ou superar os 5 problemas da técnica anterior identificados acima.

O outro objetivo da presente invenção é proporcionar um sistema de ponderação digital adaptativo.

Ainda outro objetivo da presente invenção é proporcionar um sistema de ponderação digital adaptativo para codificar um sinal de informação elétrico de uma largura 10 de banda predeterminada de modo que o sinal de informação possa ser gravado ou transmitido através de um canal dependente da freqüência dinamicamente limitado possuindo uma parte dinamicamente limitada mais estreita em uma primeira região de espectro do que em pelo menos uma outra região de espectro da largura de banda predeterminada.

15 E outro objetivo da presente invenção é proporcionar um codificador BTSC digital.

Ainda outro objetivo da presente invenção é proporcionar um codificador BTSC digital que impeça a pulsação, um problema que pode surgir com níveis de sinal de entrada substancialmente zero.

20 E ainda outro objetivo da presente invenção é proporcionar um codificador BTSC digital que utilize uma freqüência de amostra que seja um múltiplo de uma freqüência de sinal de tom piloto de 15.734 Hz de modo a impedir a interferência entre a informação de sinal do sinal codificado com o sinal de tom piloto.

Ainda outro objetivo da invenção é proporcionar um codificador BTSC digital para gerar um sinal de soma condicionado e um sinal de diferença codificado que incluem 25 substancialmente nenhuma energia de sinal na freqüência do tom piloto de 15.734 Hz.

Ainda outro objetivo da presente invenção é proporcionar um codificador BTSC digital incluindo uma seção de processamento de canal de soma para gerar o sinal de soma condicionado e uma seção de processamento de diferença para gerar o sinal de diferença codificado, a seção de processamento do canal de soma incluindo dispositivos para 30 introduzir erros de fase compensatórios no sinal de soma condicionado para compensar quaisquer erros de fase introduzidos no sinal de diferença codificado pela seção de processamento de canal de diferença.

E outro objetivo da presente invenção é proporcionar um codificador BTSC digital incluindo uma unidade de ênfase variável digital, a unidade incluindo um filtro de ênfase 35 variável digital caracterizado por uma função de transferência de coeficiente variável e a unidade adicionalmente incluindo um dispositivo para selecionar os coeficientes da função de transferência de coeficiente variável como uma função da energia do sinal do sinal de

diferença codificado.

Ainda outro objetivo da presente invenção é proporcionar um codificador BTSC digital incluindo um modulador composto para gerar um sinal modulado composto a partir do sinal de soma condicionado e do sinal de diferença codificado.

5 Ainda outro objetivo da presente invenção é proporcionar um codificador BTSC digital que possa ser implementado em um único circuito integrado.

#### Sumário da Invenção

Estes e outros objetivos são proporcionados por um codificador BTSC aperfeiçoado que inclui uma seção de entrada, uma seção de processamento de canal de soma e uma 10 seção de processamento de canal de diferença, todas as quais são implementadas utilizando-se a tecnologia digital. Em um aspecto, a seção de entrada inclui os filtros de banda alta para impedir o codificador BTSC de exibir "pulsação". Em outro aspecto, o codificador BTSC utiliza uma freqüência de amostra que é igual a um múltiplo inteiro da freqüência piloto.

15 Em ainda outro aspecto, a seção de processamento de canal de soma gera um sinal de soma condicionado e a seção de processamento de canal de diferença gera um sinal de diferença codificado e a seção de processamento de canal de soma inclui componentes para introduzir um erro de fase no sinal de soma condicionado para compensar por quaisquer erros de fase introduzidos no sinal de diferença codificado pela 20 seção de processamento de canal de diferença.

De acordo com ainda outro aspecto, a invenção proporciona um sistema de ponderação digital adaptativo para codificar um sinal de informação elétrico de uma largura de banda predeterminada de modo que o sinal de informação pode ser gravado ou transmitido através de um canal dependente de freqüência dinamicamente limitado 25 possuindo uma parte dinamicamente limitada mais estreita em uma primeira região de espectro em pelo menos uma outra região de espectro da largura de banda predeterminada.

Ainda outros objetivos e vantagens da presente invenção se tornarão prontamente 30 aparentes para aqueles com conhecimento na técnica a partir da seguinte descrição detalhada onde várias modalidades são apresentadas e descritas, simplesmente a título de ilustração do melhor modo da invenção. Como será percebido, a invenção é capaz de outras 35 modalidades diferentes e seus vários detalhes são capazes de modificação em vários aspectos, todos sem sair da invenção. Por consequência, os desenhos e descrições são para serem considerados como ilustrativos por natureza e não em um senso restritivo ou de limite, com o escopo do pedido sendo indicado nas reivindicações.

#### 35 Breve Descrição dos Desenhos

Para um entendimento mais completo da natureza e dos objetivos da presente invenção, deve ser feita referência a seguinte descrição detalhada feita em conexão com os

desenhos acompanhantes nos quais os mesmos números de referência são utilizados para indicar as mesmas partes ou similares onde:

A Figura 1 apresenta um diagrama de blocos de um codificador BTSC idealizado da técnica anterior;

5 A Figura 2 apresenta um gráfico do espectro do sinal composto gerado de acordo com os padrões BTSC;

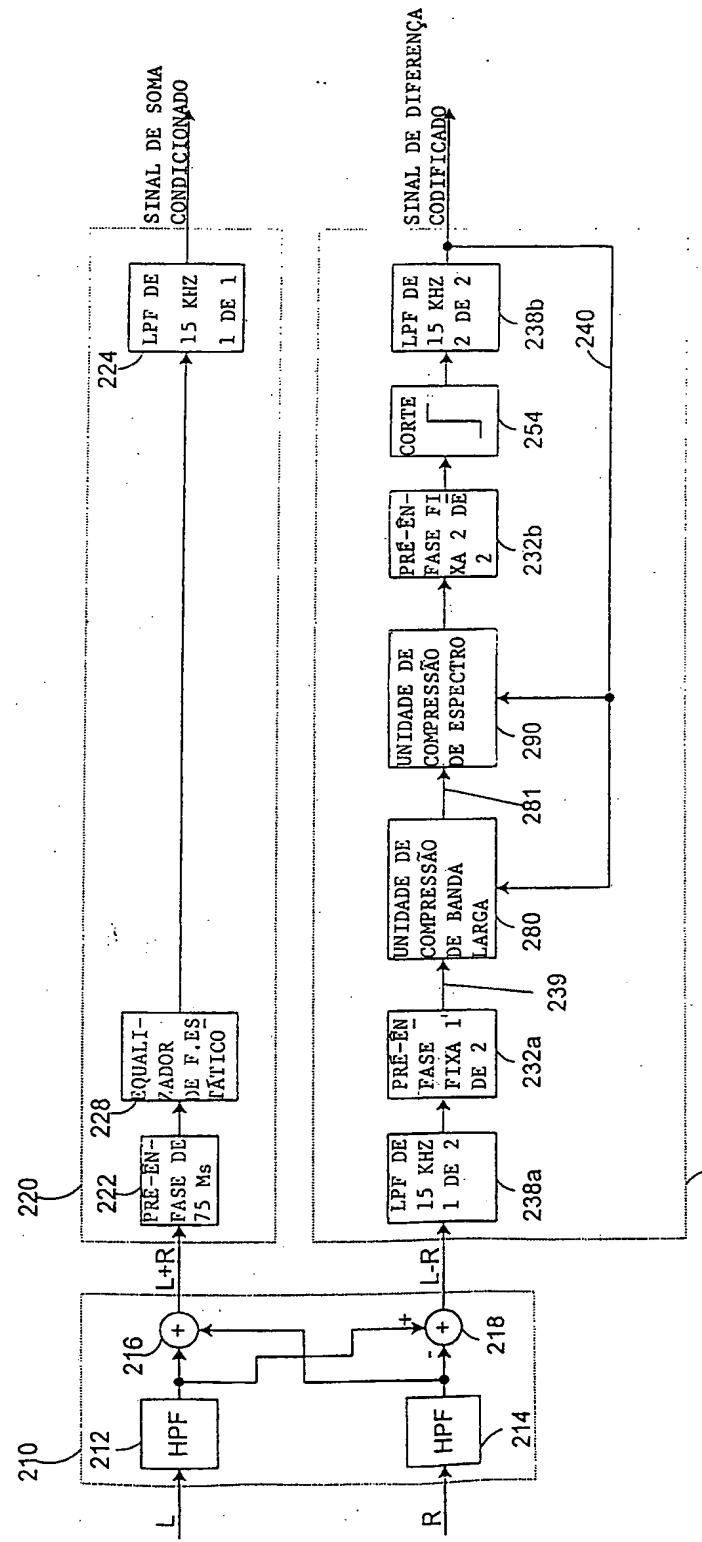

A Figura 3 apresenta um diagrama de blocos de uma modalidade de um codificador BTSC digital construído de acordo com a invenção;

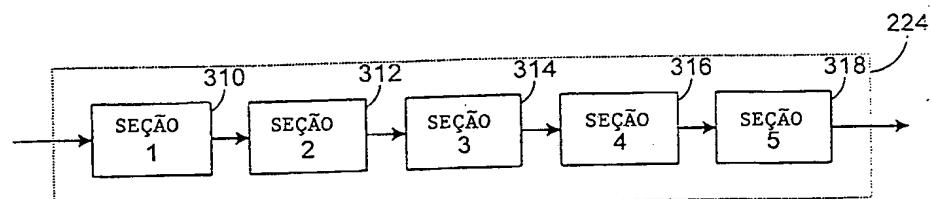

10 As Figuras 4A até 4C apresentam diagramas de blocos de filtros de banda baixa utilizados no codificador BTSC digital apresentado na Figura 3;

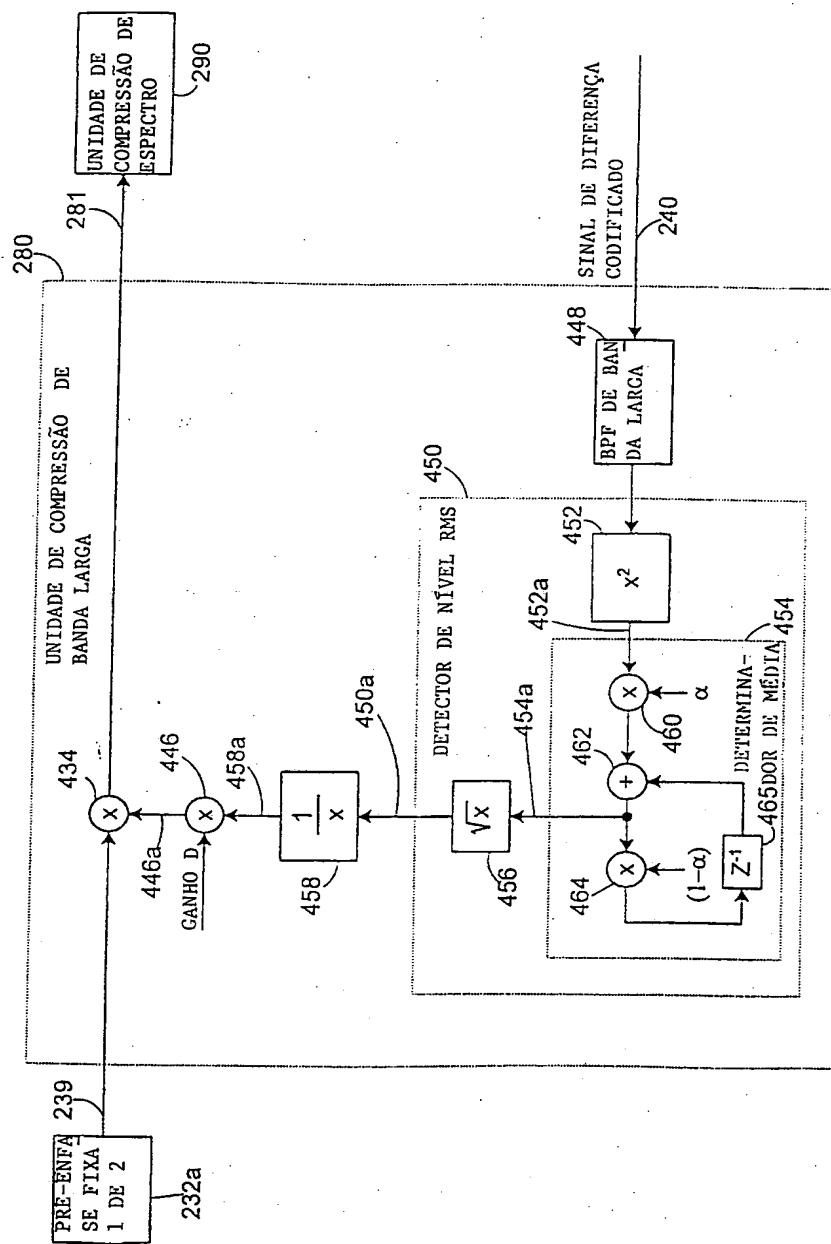

A Figura 5 apresenta um diagrama de blocos detalhado da unidade de compressão de banda larga utilizado no codificador BTSC digital apresentado na Figura 3;

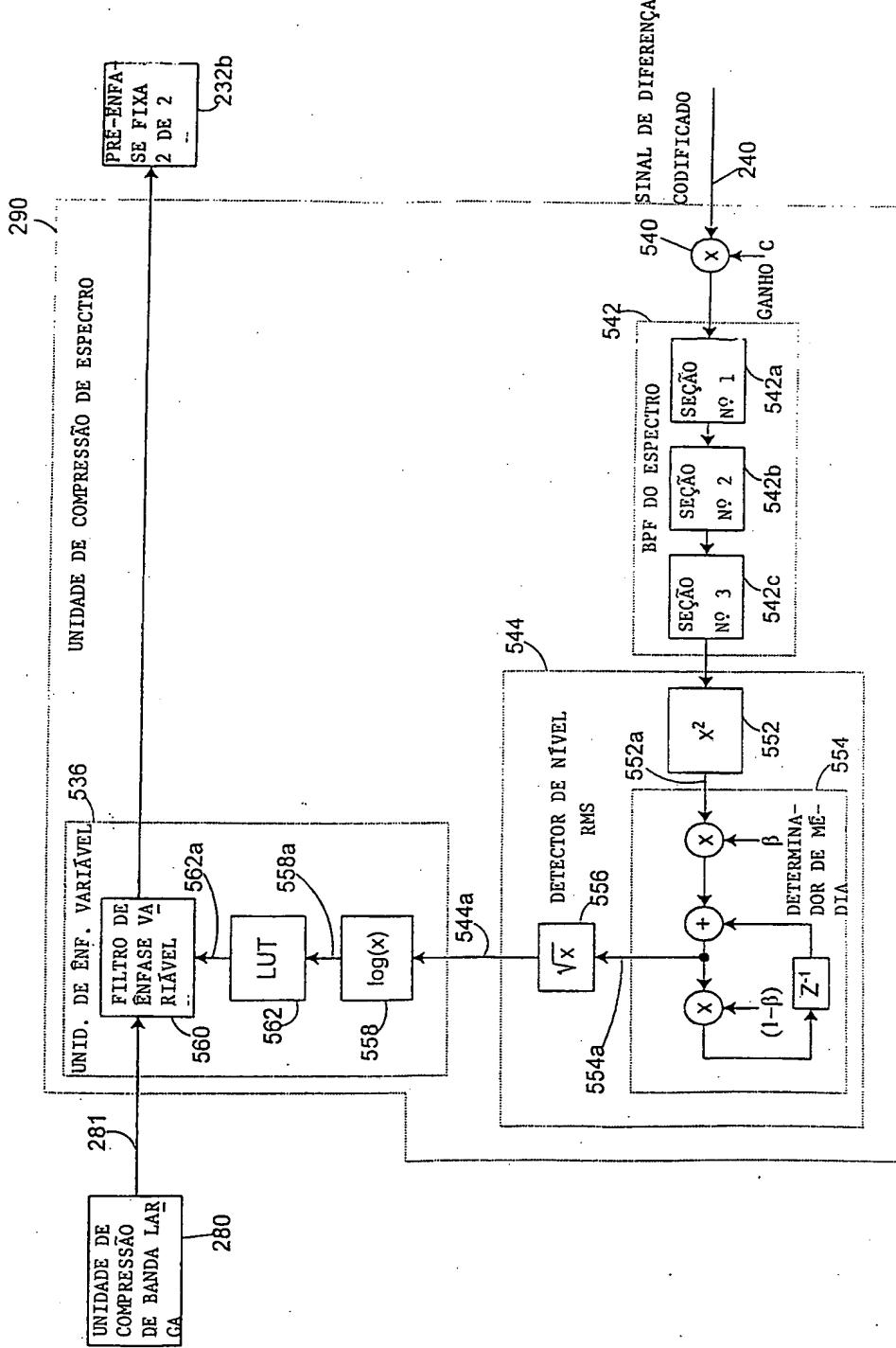

A Figura 6 apresenta um diagrama de blocos da unidade de compressão de espectro utilizada no codificador BTSC digital apresentado na Figura 3;

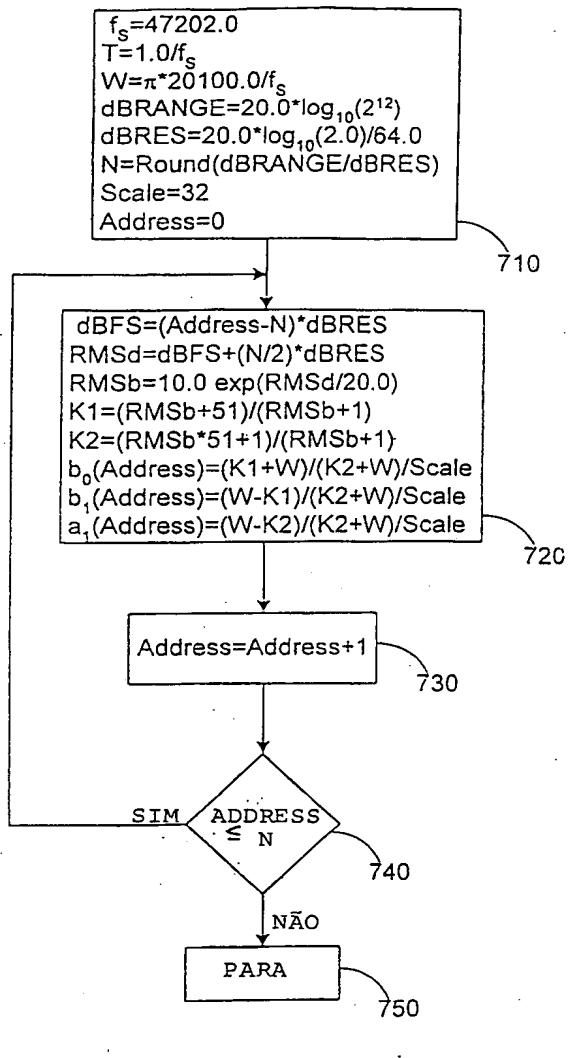

15 A Figura 7 apresenta um fluxograma utilizado na unidade de compressão de espectro apresentada na Figura 6;

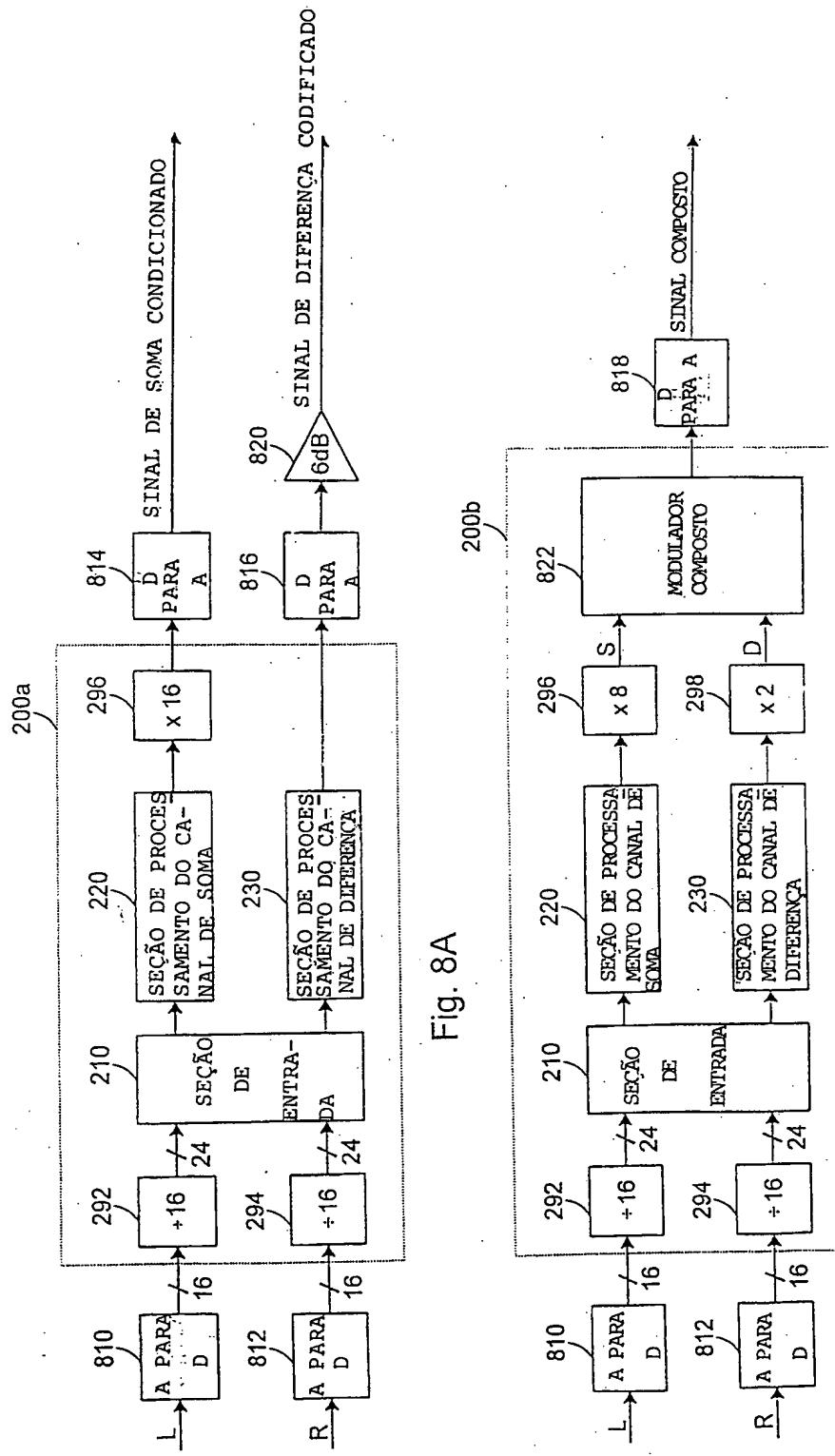

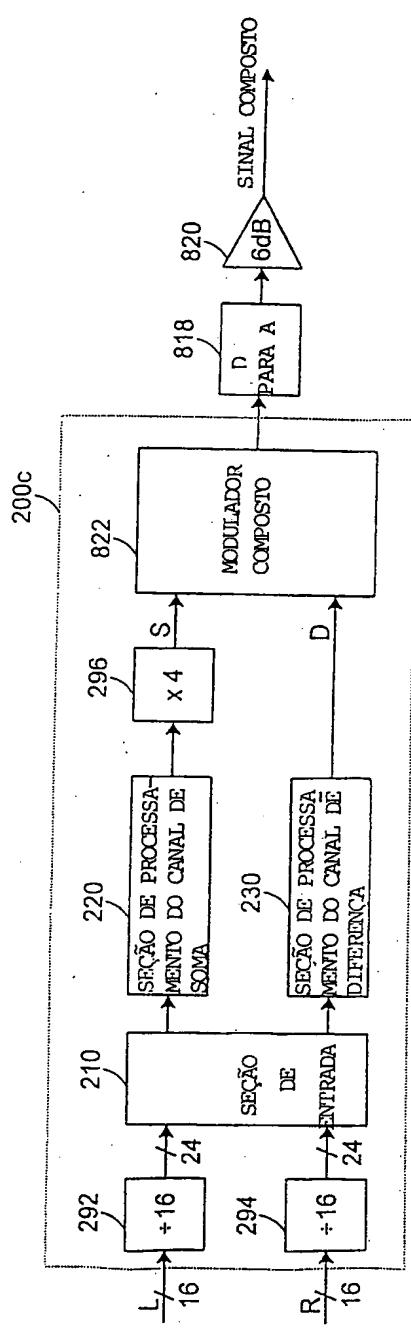

As Figuras 8A até 8D apresentam diagramas de blocos que ilustram o escalonamento do sinal que pode ser utilizado para preservar a resolução e diminuir a chance de saturação nas implementações de ponto fixo dos codificadores BTSC digitais construídos de acordo com a invenção;

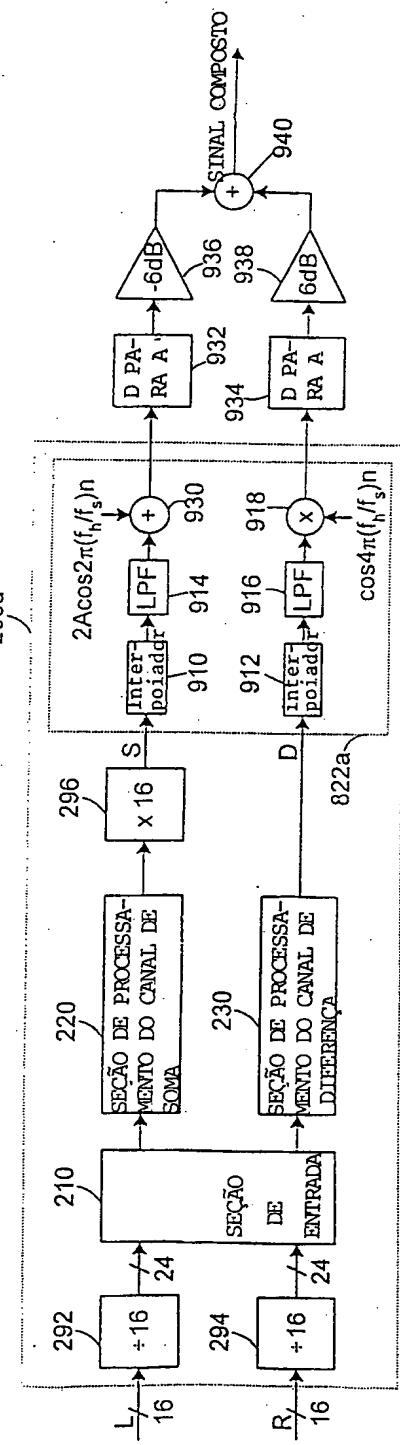

20 A Figura 9 apresenta um diagrama de blocos detalhado do modulador composto apresentado nas Figuras 8B e 8C; e

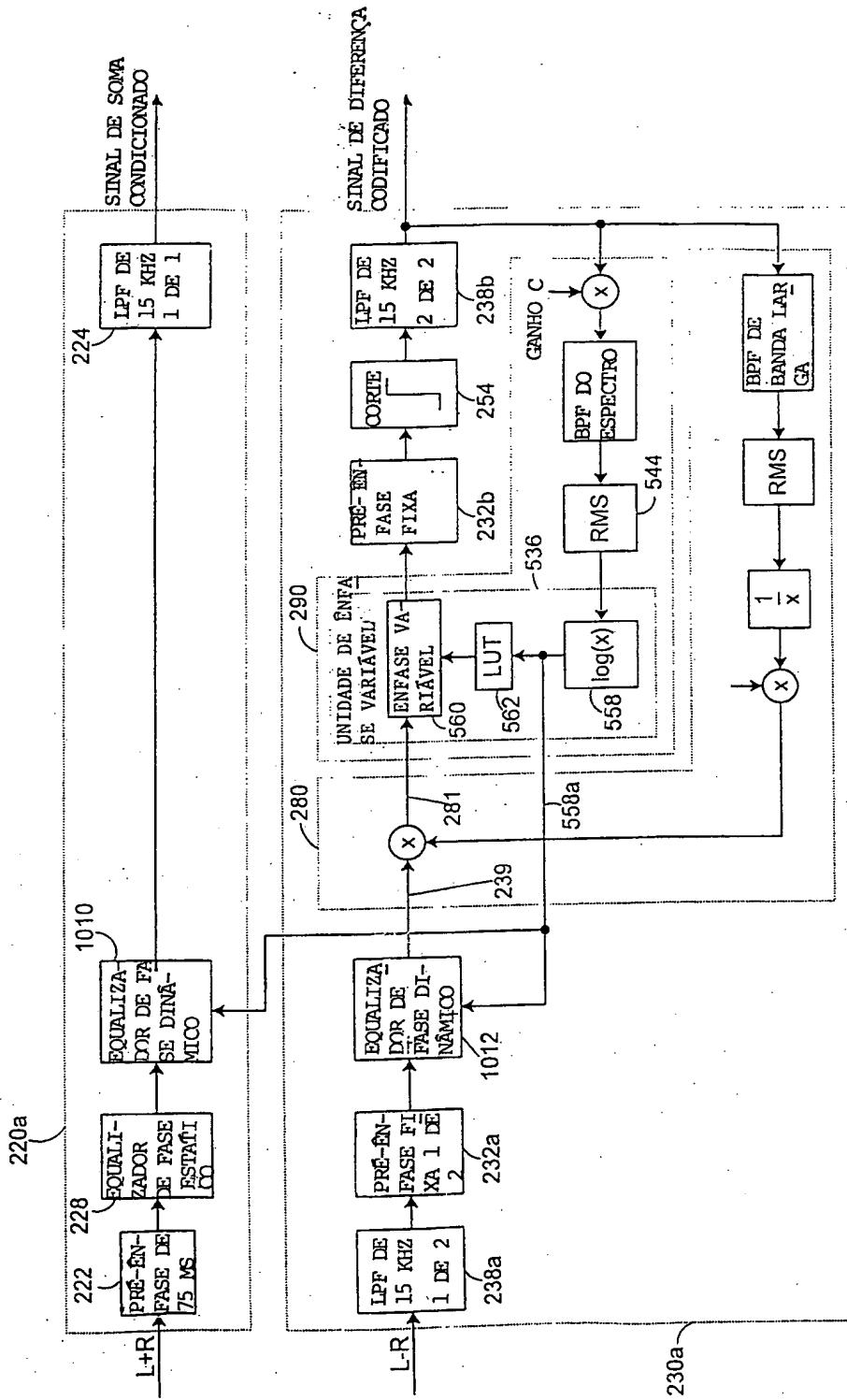

A Figura 10 apresenta um diagrama de blocos de uma modalidade preferida das seções de processamento de canal de soma e de diferença que podem ser utilizada nos 25 codificadores BTSC digitais construídos de acordo com a invenção.

#### Descrição Detalhada dos Desenhos

A Figura 3 é um diagrama de blocos de uma modalidade de um codificador BTSC digital 200 construído de acordo com a invenção. O codificador digital 200 é construído para proporcionar uma performance que é funcionalmente equivalente a performance do codificador idealizado 100 (apresentado na Figura 1). Como com o codificador idealizado 100, o codificador digital 200 recebe os sinais de entrada de áudio dos canais esquerdo e direito e gera a partir dos mesmos o sinal de soma condicionado e o sinal de diferença codificado, entretanto, no codificador digital 200, estes sinais de entrada e de saída são sinais mostrados de forma digital ao invés de sinais analógicos contínuos.

35 A escolha da freqüência de amostragem  $f_s$  para os sinais de entrada de áudio do canal esquerdo e direito afeta de forma significante o projeto do codificador digital 200. Na modalidades preferidas, a freqüência de amostragem  $f_s$  é escolhida para ser um múltiplo

inteiro da freqüência piloto  $f_H$  de modo que  $f_S = Nf_H$  onde N é um inteiro e nas modalidades mais preferidas, N é selecionado para ser maior ou igual a três. É importante para o codificador 200 assegurar que os sinais de soma condicionado e de diferença codificado não contenham energia suficiente na freqüência piloto  $f_H$  para interferir com o tom piloto que

5 está incluído no sinal composto. Como será discutido em maiores detalhes abaixo, é portanto desejável para pelo menos alguns dos filtros no codificador digital 200 proporcionar um grau excepcionalmente grande de atenuação na freqüência piloto  $f_H$  e esta escolha da freqüência de amostragem  $f_S$  simplifica o projeto de tais filtros.

O codificador digital 200 inclui uma seção de entrada 210, uma seção de processamento de canal de soma 220 e uma seção de processamento de canal de diferença 230. Ao invés de simplesmente implementar a seção de processamento de canal de diferença 230 utilizando a tecnologia digital, todas as três seções 210, 220 e 230 são implementadas utilizando-se totalmente a tecnologia digital. Vários dos componentes individuais no codificador digital 200 respectivamente correspondem aos componentes individuais no codificador idealizado 100. Em geral, os componentes do codificador digital 200 foram selecionados de modo que suas respostas de amplitude combinam de forma próxima com as resposta de amplitude respectivas dos seus componentes correspondentes no codificador 100. Isto freqüentemente resulta em existir uma diferença relativamente grande entre as respostas de fase dos componentes correspondentes. De acordo com um aspecto da presente invenção, são providos no codificador digital 200 dispositivos para compensar ou nulificar estas diferenças de fase ou erros de fase. Como os com conhecimento na técnica irão apreciar, relativamente pequenos erros de fase na seção de processamento de canal de diferença 230 podem ser compensados por se introduzir erros de fase similares na seção de processamento de canal de soma 220 e a implementação da seção de processamento de canal de soma utilizando a tecnologia digital simplifica a introdução de tais erros de fase de compensação desejados.

A seção de entrada 210 do codificador 200 inclui dois filtros de banda alta 212, 214 e dois adicionadores de sinal 216, 218. O sinal de entrada de áudio digital do canal esquerdo L é aplicado para a entrada do filtro de banda alta 212, o último gerando a partir do mesmo um sinal de saída que é aplicado para os terminais de entrada positivos dos adicionadores 216, 218. O sinal de entrada de áudio do canal direito R é aplicado para a entrada do filtro de banda alta 214 que gera a partir do mesmo um sinal de saída que é aplicado a um terminal de entrada positivo do adicionador 216 e para um terminal de entrada negativo do adicionador 218. O adicionador 216 gera um sinal de soma (indicado na Figura 3 como "L + R") por somar os sinais de saída gerados pelos filtros 212 e 214. O adicionador 218 gera um sinal de diferença (indicado na Figura 3 como "L-R") por subtrair o sinal de saída gerado pelo filtro 214 do sinal de saída gerado pelo filtro 212. A seção de

entrada 210 é portanto similar a seção de entrada 110 (apresentada na Figura 1), entretanto, a seção 210 adicionalmente inclui os dois filtros de banda alta 212, 214 e gera os sinais de soma e de diferença digitais.

Os filtros de banda alta 212, 214 de preferência possuem substancialmente 5 respostas idênticas e de preferência removem os componentes D.C. dos sinais de entrada de áudio do canal esquerdo e direito. Como será discutido em maiores detalhes abaixo, esta remoção D.C. impede o codificador 200 de exibir um comportamento referido como “Pulsação”. Desde que o conteúdo da informação de áudio dos sinais de entrada de áudio 10 do canal esquerdo e direito de interesse é considerado para estar dentro de uma banda de freqüência entre 50 Hz e 15.000 Hz, a remoção dos componentes D.C. não interfere com a transmissão do conteúdo da informação dos sinais de áudio. Os filtros 212, 214, portanto, de preferência possuem uma freqüência de interrupção abaixo de 50 Hz e mais de preferência possuem uma freqüência de interrupção abaixo de 10 Hz de modo que eles não irão 15 remover qualquer informação de áudio contida nos sinais de entrada de áudio. Os filtros 212, 214 também de preferência possuem uma resposta de magnitude plana em sua banda de passagem. Em uma modalidade preferida, os filtros 212, 214 são implementados como filtros de resposta de impulso infinito de primeira ordem (IIR), cada um possuindo uma função de transferência  $H(z)$  dada pela fórmula apresentada na seguinte equação (1).

$$H(z) = \frac{1-z^{-1}}{1+a_1z^{-1}}$$

Referindo-se novamente a Figura 3, a seção de processamento de canal de soma 20 220 recebe o sinal de soma e gera a partir do mesmo o sinal de soma condicionado. Em particular, o sinal de soma é aplicado a um filtro de pré-ênfase de  $75 \mu s$  222. O filtro 222 por sua vez gera um sinal de saída que é aplicado a um filtro de equalização de fase estático 228. O filtro 228 gera um sinal de saída que é aplicado a um filtro de banda baixa 224 da seção 220 que por sua vez gera o sinal de soma condicionado.

O filtro de pré-ênfase de  $75 \mu s$  222 proporciona o processamento de sinal que é 25 parcialmente análogo ao do filtro 122 (apresentado na Figura 1) do codificador idealizado 100. A resposta de amplitude do filtro 222 é de preferência selecionada para combinar de forma próxima com a do filtro 122. Como será discutido adicionalmente abaixo, de preferência são proporcionados dispositivos na seção de processamento de canal de diferença 230 para compensação de quaisquer diferenças nas respostas de fase dos filtros 30 222 e 122. Em uma modalidade preferida, o filtro 222 é implementado como um filtro IIR de primeira ordem possuindo uma função de transferência  $H(z)$  que é descrita pela fórmula

apresentada na seguinte Equação (2).

$$H(z) = \frac{b_0 + b_1 z^{-1}}{1 + a_1 z^{-1}}$$

(2)

O filtro de equalização de fase estático 228 executa o processamento que não é diretamente análogo a qualquer dos componentes no codificador idealizado 100 (apresentado na Figura 1). Como será discutido em maiores detalhes abaixo, o filtro de equalização de fase estático 228 é utilizado para introduzir erros de fase que compensam os erros de fase introduzidos pela seção de processamento de diferença 230. Resumidamente, o filtro de equalização de fase estático 228 é de preferência um filtro de "passa tudo" possuindo uma resposta de amplitude relativamente plana e uma resposta de fase selecionada. Em uma modalidade preferida, o filtro 228 é implementado como um filtro IIR de primeira ordem possuindo uma função de transferência  $H(z)$  que é descrita pela fórmula apresentada na seguinte Equação (3).

$$H(z) = \frac{a_0 + z^{-1}}{1 + a_0 z^{-1}}$$

(3)

O filtro de banda baixa 224 proporciona um processamento que é análogo ao limitador de banda 124 (apresentado na Figura 1) do codificador 100. O filtro de banda baixa 224 de preferência proporciona uma resposta de amplitude plana em uma banda de passagem de zero até 15 kHz e uma interrupção relativamente abrupta acima de 15 kHz. O filtro 224 também de preferência proporciona um grau excepcionalmente grande de atenuação na freqüência  $f_H$  do tom piloto (isto é, 15.734 Hz). Por proporcionar este grau excepcionalmente grande de atenuação, o filtro 224 assegura que o sinal de soma condicionado não inclui energia suficiente na freqüência piloto  $f_H$  para interferir com o tom piloto utilizado no sinal composto. Como discutido acima, a seleção da freqüência de amostra  $f_S$  para ser igual a um múltiplo inteiro da freqüência piloto  $f_H$  simplifica o projeto de um filtro que proporciona um grau excepcionalmente grande de atenuação da freqüência piloto e portanto simplifica o projeto do filtro 224. O filtro 224 de preferência possui um nulo na freqüência piloto  $f_H$  e de preferência proporciona pelo menos 70 dB de atenuação para todas as freqüências a partir da freqüência piloto  $f_H$  até a metade da taxa de amostra.

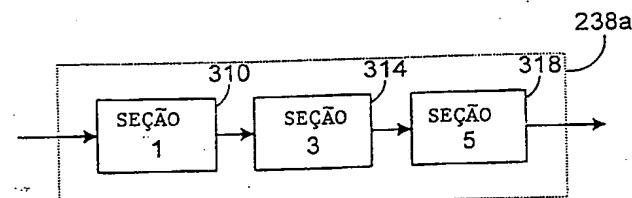

A Figura 4a é um diagrama de blocos ilustrando uma modalidade preferida do filtro de banda baixa 224. Como apresentado na Figura 4A, o filtro 224 pode ser implementado

por se fazer cascata de cinco seções de filtro 310, 312, 314, 316 e 318. Em uma modalidade preferida, todas as cinco seções de filtro 310, 312, 314, 316 e 318 são cada uma implementadas como um filtro IIR de segunda ordem possuindo as funções de transferência  $H(z)$  que são descritas pela fórmula apresentada na seguinte Equação (4).

$$H(z) = \frac{b_0 + b_1 z^{-1} + b_2 z^{-2}}{1 + a_1 z^{-1} + a_2 z^{-2}}$$

5 De modo que na modalidade apresentada na Fig. 4A, o filtro 224 é um filtro IIR de décima ordem.

Referindo-se novamente a Figura 3, a seção de processamento de canal de diferença 230 recebe o sinal de diferença e gera a partir do mesmo o sinal de diferença codificado. O sinal de diferença é aplicado a um filtro de banda baixa 238a que gera a partir 10 do mesmo um sinal de saída que é aplicado a um filtro de pré-ênfase fixo 232a. O último gera um sinal de saída que é aplicado via a linha 239 a um terminal de entrada da unidade de compressão de banda larga 280 e o sinal de diferença codificado é aplicado via a linha de realimentação 240 a um terminal detector da unidade de compressão de banda larga 280. O último gera um sinal de saída que é aplicado via a linha 281 a um terminal de 15 entrada de uma unidade de compressão de espectro 290 e o sinal de diferença codificado é também aplicado via a linha de realimentação 240 a um terminal detector da unidade 290. A última gera um sinal de saída que é aplicado a um filtro de pré-ênfase fixo 232b que por sua vez gera um sinal de saída que é aplicado a um cortador 254. O cortador 254 gera um sinal de saída que é aplicado a um filtro de banda baixa 238b que por sua vez gera o sinal de 20 diferença codificado.

Os filtros de banda baixa 238a, 238b, juntos formam um filtro de banda baixa 238 que executa o processamento que é parcialmente análogo a parte do limitador de banda do protetor de sobre-modulação e limitador de banda 138 (apresentado na Figura 1) do codificador idealizado 100. De preferência, o filtro 238 é implementado de modo que ele seja 25 substancialmente idêntico ao filtro de banda baixa 224, que é utilizado na seção de processamento de canal de soma 220. Quaisquer erros de fase introduzidos no sinal de diferença codificado pelo filtro 238 são compensados pelos erros de fase de balanceamento que são introduzidos no sinal de soma condicionado pelo filtro 224. O filtro 238 é de preferência dividido em duas seções 238a, 238b como apresentado por razões que serão 30 discutidas em maiores detalhes abaixo e o filtro 238a de preferência possui um nulo na freqüência piloto  $f_H$ .

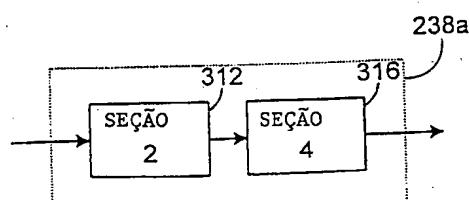

As Figuras 4B e 4C são diagramas de blocos ilustrando uma modalidade preferida

dos respectivos filtros 238a e 238b. Como apresentado na Figura 4B, o filtro 238a pode ser implementado por se fazer cascata de três seções de filtro 310, 314 e 318 que são idênticas as três seções de filtro utilizadas no filtro 224 (apresentado na Figura 4A) e como apresentado na Figura 4C, o filtro 238b pode ser implementado por se fazer cascata de 5 duas seções de filtro 312 e 314 que são idênticas as duas seções restantes utilizadas no filtro 224.

Os filtros de pré-ênfase fixos 232a e 232b (apresentados na Figura 3) juntos formam um filtro de pré-ênfase fixo 232 que executa o processamento que é parcialmente análogo ao do filtro 132 (apresentado na Figura 1) do codificador idealizado 100. A resposta 10 de amplitude do filtro 232 é de preferência selecionada para combina de forma próxima com a resposta de amplitude do filtro 132. Em uma modalidade, as respostas de fase dos filtros 232 e 132 são de forma significante diferentes e como será discutido em maiores detalhes abaixo, os erros de fase resultantes são compensados pelos filtros 222 e 228 na seção de processamento de canal de soma 220. O filtro 232 é de preferência dividido em duas seções 15 232a e 232b, como apresentado, por razões que serão discutidas abaixo. Em uma modalidade preferida, cada um dos filtros 232a e 232b são implementados como filtros IIR de primeira ordem possuindo as funções de transferência  $H(z)$  que são descritas pela fórmula apresentada na Equação (2). De modo que nesta modalidade, o filtro 232 é um filtro IIR de segunda ordem.

20 Em uma modalidade preferida, a diferença entre as respostas de fase dos filtros 232b e 132a combinam de forma próxima com a diferença entre as respostas de fase dos filtros 222 e 122. Portanto, o erro de fase introduzido no sinal de diferença codificado pelo filtro de pré-ênfase fixo 232b é balanceado pelo erro de fase introduzido no sinal de soma condicionado pelo filtro de pré-ênfase de  $75\mu s$  222. Adicionalmente, nesta modalidade, a 25 resposta de fase do filtro de equalização de fase estático 228 é selecionada para combinar de forma próxima com a diferença entre as respostas de fase do filtro de pré-ênfase fixo 232a e do filtro 132b, de modo que qualquer erro de fase introduzido no sinal de diferença codificado pelo filtro 232a é balanceado por um erro de fase compensatório no sinal de soma condicionado que é introduzido pelo filtro de equalização de fase estático 228.

30 O cortador 254 executa o processamento que é parcialmente análogo ao da parte de proteção de sobre-modulação do protetor de sobre-modulação e limitador de banda 138 (apresentado na Figura 1) utilizado no codificador idealizado 100. Resumidamente, o cortador 254 é implementado como um dispositivo de limite, entretanto, a operação do cortador 254 será discutida em maiores detalhes abaixo.

35 A unidade de compressão de banda larga 280 e a unidade de compressão de espectro 290 executam as funções de processamento que são parcialmente análogas a estas das unidades 180 e 190, respectivamente, do codificador idealizado 100 (apresentado

na Figura 1) Resumidamente, a unidade de compressão de banda larga 280 dinamicamente comprime o sinal na linha 239 em função do nível de energia total no sinal de diferença codificado e a unidade de compressão de espectro 290 adicionalmente comprime as parte de alta freqüência dos sinais na linha 281 em função da energia de alta freqüência no sinal de diferença codificado.

A Figura 5 apresenta um diagrama de blocos de uma modalidade preferida de uma unidade de compressão de banda larga digital 280. A unidade 280 inclui um multiplicador de sinal digital 434, um multiplicador de sinal digital 446, um filtro de banda de passagem digital de banda larga 448, um detector de nível RMS digital 450 e um gerador recíproco digital 458. Estes componentes executam funções de processamento parcialmente análogas a aquelas executadas pelo amplificador 134, pelo amplificador 146, pelo filtro de banda baixa 148, pelo detector de nível RMS 150 e pelo gerador recíproco 152, respectivamente, do codificador idealizado 100 (apresentado na Figura 1). O sinal de diferença codificado é aplicado via o caminho de realimentação 240 a uma entrada do filtro de banda de passagem digital de banda larga 448 que gera a partir do mesmo um sinal de saída que aplicado ao detector de nível RMS 450. O último gera um sinal de saída que é representativo do valor RMS do sinal de saída gerado pelo filtro 448 e aplica este sinal de saída, via alinha 450a, ao gerador recíproco 458. O gerador recíproco 458 então gera um sinal de saída representativo do recíproco do sinal na linha 450a e aplica este sinal de saída, via a linha 458, ao multiplicador 446. O multiplicador de sinal digital 446 multiplica o sinal na linha 458a pelo valor do parâmetro de ganho, Ganho D, e por meio disso gera um sinal de saída que é representativo de D vezes o recíproco do valor RMS e que é aplicado via a linha 446a a um terminal de entrada do multiplicador 434. O sinal de saída gerado pelo filtro de pré-ênfase fixo 232a é aplicado via a linha 239 a outro terminal de entrada do multiplicador 434. O multiplicador 434 multiplica o sinal na linha 239 pelo sinal na linha 446a e por meio disso gera a saída da unidade de compressão de banda larga 280 que é aplicada via a linha 281 a entrada da unidade de compressão de espectro 290.

O filtro de banda de passagem digital de banda larga 448 é projetado para possuir uma resposta de amplitude que é de forma próxima combina com a resposta de amplitude do filtro de banda de passagem 148 (apresentado na Figura 1). Uma escolha preferida é selecionar o filtro 448 de modo que a diferença quadrada media entre a resposta de amplitude e esta do filtro 148 seja minimizada. Em uma modalidade, a resposta de fase dos filtros 448 e 148 são substancialmente diferentes, mas desde que o sinal de saída do detector de nível RMS 450 é substancialmente insencitivo a fase se seu sinal de entrada, estas diferenças de fase podem ser ignoradas. Em uma modalidade preferida, o filtro de banda de passagem de banda larga 448 é implementado como um filtro IIR de segunda ordem possuindo uma função de transferência  $H(z)$  que é descrita pela fórmula apresentada

na Equação 4.

O detector de nível RMS 450 é projetado para aproximar a performance do detector 150 que é utilizado no codificador idealizado 100 (apresentado na Figura 1). O detector 450 inclui um dispositivo de enquadramento de sinal 452, um dispositivo de determinação de 5 média do sinal 454 e um dispositivo de raiz quadrada 456. O dispositivo de enquadramento 452 enquadra o sinal gerado pelo filtro de banda de passagem 448 e aplica este sinal enquadrado via a linha 452a a um dispositivo de determinação de média 454. O último calcula uma média ponderada de tempo do sinal na linha 452a e aplica a média via a linha 10 454a um dispositivo de raiz quadrada 456. O dispositivo de raiz quadrada 456 calcula a raiz quadrada do sinal na linha 454a e por meio disso gera um sinal na linha 450a representativo do valor RMS do sinal de saída gerado pelo filtro de banda de passagem digital de banda larga 448.

O dispositivo de determinação de média 454 inclui um multiplicador de sinal digital 460, um adicionador de sinal digital 462, um multiplicador de sinal digital 464 e um registro de atraso 465. O sinal de saída gerado pelo dispositivo de enquadramento 452 é aplicado via a linha 452a a uma entrada do multiplicador 460 que gera um sinal de saída por escalarizar o sinal na linha 452a por uma constante  $\alpha$ . O sinal de saída escalarizado gerado pelo multiplicador 460 é aplicado a uma entrada do adicionador 462 e um sinal de saída gerado pelo registro de atraso 465 é aplicado a outra entrada do adicionador 462. O 20 adicionador 462 gera um sinal de saída por somar os sinais presentes nas suas duas entradas e este sinal somado é o sinal de saída do dispositivo de determinação de média 454 e é aplicado ao dispositivo de raiz quadrada 456 via a linha 454a. O sinal somado é também aplicado a uma entrada do multiplicador 464 que gera um sinal de saída por escalarizar o sinal somado pela constante  $(1-\alpha)$ . O sinal de saída gerado pelo multiplicador 464 é aplicado 25 a entrada do registro de atraso 465. Aqueles com conhecimento na técnica irão apreciar que o determinador de média 454 é um filtro recursivo e que implementa uma função de determinação de média digital que é descrita pela fórmula recursiva apresentada na seguinte Equação (5).

$$y(n) = \alpha x(n) + (1-\alpha)y(n-1) \quad (5)$$

30 na qual  $y(n)$  representa a amostra digital corrente da saída de sinal do determinador de média 454 na linha 454a,  $y(n-1)$  representa a amostra digital anterior da saída de sinal do determinador de média 454 na linha 454a, e  $x(n)$  representa a amostra digital corrente da saída de sinal do dispositivo de enquadramento 452 na linha 452a. Aqueles com conhecimento na técnica irão apreciar que o determinador de média 454 proporciona uma 35 aproximação digital da função de determinação de média analógica definida no padrão BTSC e implementada pelo detector de nível RMS 150 (apresentado na Figura 1) do codificador idealizado 100. A constante  $\alpha$  é de preferência escolhida de modo que a

constante de tempo do detector de nível RMS 450 de aproxime de forma próxima da constante de tempo correspondente especificada no padrão BTSC para o detector de nível RMS 150.

O dispositivo de raiz quadrada digital 456 e o gerador recíproco digital 458 são apresentados na Figura 5 como dois componentes separados, entretanto, aqueles com conhecimento na técnica irão apreciar que estes dois componentes podem ser implementados utilizando-se um único dispositivo que gera um sinal de saída representativo do recíproco da raiz quadrada do seu sinal de entrada. Tal dispositivo pode ser implementado, por exemplo, como uma tabela de consulta em memória (LUT), ou alternativamente pode ser implementado utilizando-se componentes de processamento que calculam uma aproximação de polinômio da série Taylor da função de raiz quadrada inversa.

A Figura 6 apresenta um diagrama de blocos de uma modalidade preferida da unidade de compressão de espectro 290. A unidade 290 inclui uma unidade de pré-ênfase/de-ênfase variável (daqui para frente referida como a "unidade de ênfase variável") 536, um multiplicador de sinal 540, um filtro de banda de passagem de espectro 542 e um detector de nível RMS 544 e estes componentes proporcionam um processamento que é parcialmente análogo a este do filtro de ênfase variável 136, do amplificador 140, do filtro de banda de passagem 142 e do detector de nível RMS 144, respectivamente, do codificador idealizado 100 (apresentado na Figura 1). O sinal de diferença codificado é aplicado via a linha de realimentação 240 a uma entrada do multiplicador de sinal 540 que gera um sinal de saída por multiplicar o sinal de diferença codificado pelo valor do parâmetro de ganho fixo do Ganho C. O sinal de saída amplificado gerado pelo multiplicador de sinal 540 é aplicado ao filtro de banda de passagem de espectro 542 que gera um sinal de saída que é aplicado ao detector de nível RMS 544. O último gera um sinal de saída que é aplicado via a linha 544a a um terminal de controle da unidade de ênfase variável 536 e o sinal de saída gerado pela unidade compressora de banda larga 280 é aplicado via a linha 281 a um terminal de entrada da unidade 536. A última dinamicamente varia a resposta de freqüência aplicada ao sinal na linha 281 de acordo com uma função do sinal na linha 544a, o último sinal sendo uma função da energia do sinal do sinal de diferença codificado dentro da banda de freqüência passada pelo filtro de banda de passagem de espectro 542. O sinal de saída da unidade 290, que é gerado pela unidade 536 e é aplicado a entrada do filtro de pré-ênfase fixo 232b, é portanto dinamicamente comprimido em uma grande quantidade nas partes de alta freqüência do sinal do que no restante do espectro de interesse.

O filtro de banda de passagem 542 é projetado para possuir uma resposta de amplitude que combina de forma próxima com a resposta de amplitude do filtro de banda de passagem 142 (apresentando na Figura 1) do codificador idealizado 100. Como com o filtro

448 (apresentado na Figura 5), uma escolha preferida é selecionar o filtro 542 de modo que a diferença entre sua resposta de amplitude RMS e a do filtro 142 seja minimizada. Em uma modalidade, a resposta de fase dos filtros 542 e 142 são substancialmente diferentes, mas desde que a saída RMS do detector de nível RMS 544 é substancialmente insensitivo a fase da entrada para o detector, estas diferenças de fase podem ser ignoradas. Em uma modalidade preferida, o filtro de banda de passagem de espectro 542 é implementado como uma cascata de três seções de filtro IIR de segunda ordem 542a, 542b, 542c (como apresentado na Figura 6) cada um possuindo uma função de transferência  $H(z)$  que é descrita pela fórmula apresentada na Equação (4). O detector de nível RMS 544 é projetado para aproximar a performance do detector 144 que é utilizado no codificador idealizado 100 (apresentado na Figura 1). O detector 544 inclui um dispositivo de enquadramento de sinal 552, um dispositivo de determinação de média do sinal 544 e um dispositivo de raiz quadrada 556. O dispositivo de enquadramento 552 enquadra o sinal gerado pelo filtro de banda de passagem de espectro 542 e aplica este sinal enquadrado via a linha 552a para o dispositivo de determinação de média 554. O último funciona de forma similar ao dispositivo de determinação de média 454 (apresentado na Figura 5) que é utilizado na unidade de compressão de banda larga 280. apesar de o dispositivo 554 de preferência utilizar uma constante  $\beta$  diferente da constante  $\alpha$ . O comportamento do dispositivo de determinação de média 554 é obviamente também descrito pela Equação (5) quando  $\beta$  é substituído por  $\alpha$ . A constante  $\beta$  é de preferência selecionada para o dispositivo 554 de modo que a constante de tempo do detector de nível RMS 544 se aproxima de forma próxima da constante de tempo correspondente especificada pelo padrão BTSC para o detector de nível RMS 144 (apresentado na Figura 1). O dispositivo de determinação de média 554 calcula uma média ponderada de tempo do sinal na linha 552a e aplica a média ao dispositivo de raiz quadrada 556 via a linha 554a. O dispositivo de raiz quadrada 556 calcula a raiz quadrada do sinal na linha 554a e por meio disso gera um sinal na linha 544a em função do valor RMS do sinal de saída gerado pelo filtro de banda de passagem de espectro 542.

O sinal na linha 544 é aplicado ao terminal de controle da unidade de ênfase variável 536. A unidade de ênfase variável 536 executa um processamento que é parcialmente análogo ao do filtro 136 (apresentado na Figura 1) do codificador idealizado 100. Como definido pelo padrão BTSC, o filtro 136 possui respostas de amplitude e de fase que variam em função do sinal de saída gerado pelo detector de nível RMS 144. Um modo preferido de implementar a unidade 536 de modo que ela tenha respostas variáveis similares é utilizar um filtro digital possuindo coeficientes variáveis que determinam sua função de transferência e selecionar o valor dos coeficientes durante qualquer período de amostra dado, ou grupo de períodos de amostra, baseado no valor do sinal na linha 544a.

A Figura 6 apresenta uma modalidade da unidade de ênfase variável 536 que inclui

um gerador de logaritmo 558, um filtro de ênfase variável 560 e uma tabela de consulta LUT 562. O sinal de saída gerado pelo detector de nível RMS 544 é aplicado via alinha 544a ao gerador de logaritmo 558. O último gera um sinal na linha 558a que é representativo do logaritmo do sinal na linha 544a e aplica este sinal a LUT 562. A LUT 562 gera um sinal de saída selecionado a partir da LUT e representativo dos coeficientes do filtro para serem utilizados pelo filtro de ênfase variável 560. Portanto, os coeficiente gerados pela LUT 562 são aplicados via alinha 562a a um terminal de seleção de coeficiente do filtro de ênfase variável 560. O sinal de saída gerado pela unidade de compressão de banda larga 280 é aplicado a um terminal de entrada do filtro de ênfase variável 560 via a linha 281. O filtro de ênfase variável 560 gera o sinal de saída da unidade de compressão de espectro 290 que é aplicado a entrada do filtro de pré-ênfase fixo 232b.

O filtro de ênfase variável 560 é projetado para possuir uma resposta de amplitude variável que combina de forma próxima com a resposta de amplitude variável do filtro 136 (apresentado na Figura 1) do codificador idealizado 100. O filtro de ênfase variável 560 proporciona uma resposta variável similar por utilizar uma função de transferência de coeficiente variável (isto é, os coeficientes da função de transferência  $H(z)$  do filtro 560 são variáveis) e por permitir a LUT 562 selecionar o valor dos coeficientes durante intervalos baseado no período de amostra. Como será descrito em maiores detalhes abaixo, a LUT 562 armazena os valores dos coeficientes do filtro utilizados pelo filtro 560 e durante cada período de amostra, ou durante qualquer grupo selecionado de períodos de amostra, a LUT 562 seleciona um grupo de coeficientes do filtro em função do sinal de saída gerado pelo gerador logaritmo 558, na linha 558a. Em uma modalidade preferida, o filtro de ênfase variável 560 é implementado como um filtro IIR de primeira ordem possuindo uma função de transferência  $H(z)$  que é descrita pela fórmula apresentada na seguinte Equação (6).

$$H(z) = \frac{b_0 + b_1 z^{-1}}{1 + a_1 z^{-1}}$$

na qual os coeficiente do filtro  $b_0$ ,  $b_1$  e  $a_1$  são variáveis que são selecionadas pela LUT 562. Os métodos para selecionar os valores para os coeficientes do filtro utilizados pelo filtro 560 bem como por outros filtros do codificador 200 serão discutidos abaixo.

Na Figura 6, são apresentados o gerador de logaritmo 558 e o dispositivo de raiz quadrada 556, por conveniência, como dois componentes separados. Entretanto, aqueles com conhecimento na técnica irão apreciar que estes dois componentes podem ser implementados utilizando-se um único dispositivo, tal como uma LUT, ou alternativamente utilizando componentes de processamento que calculam uma aproximação de polinômio de

série Taylor do logaritmo do sinal na linha 554a e por então dividir este valor por dois. De forma similar, em implementações alternativas, as funções executadas pelo gerador de logaritmo 558, pelo dispositivo de raiz quadrada 556 e pela LUT podem ser incorporadas em um único dispositivo.

5        Como declarado acima, os filtros de banda alta 212, 214 (apresentados na Figura 3) são úteis em bloquear os componentes DC de modo a impedir o codificador 200 de exibir um comportamento conhecido como “pulsação”. No contexto de um codificador estereofônico, a pulsação se refere ao comportamento de oscilatório de baixa freqüência do codificador causado quando não existe sinal presente nas entradas de áudio de canal esquerdo e direito. O comportamento desejado de um sistema estereofônico quando não existe sinal presente nas entradas de áudio é permanecer silencioso; entretanto, um codificador conectado através de um decodificador com os alto-falantes e exibindo pulsação causa que os alto-falantes emitam um som audível, referido como um “pulso”, com um período um tanto regular que é parcialmente dependente da constante de tempo do detector de nível RMS no compressor de banda larga. Mais particularmente, no codificador 200, quando somente sinais de nível muito baixo estão presentes nas entradas de áudio e quando existe um componente D.C., ou um ramal, presente no sinal na linha 239, a unidade de compressão de banda larga 280 tende a comportar-se de um modo instável que causa a pulsação.

20      Considere o caso onde somente um sinal de áudio de baixo nível está presente na linha 239. Em tal caso, a saída do detector de nível RMS 450 na linha 450a torna-se muito pequena, o que por sua vez causa que o ganho do multiplicador 434 torne-se muito grande. Se tal sinal de áudio de baixo nível na linha 239 for constante em sua amplitude, a unidade de compressão de banda larga 280 alcança uma condição de estado estável após algum tempo (determinado pela constante de tempo  $\alpha$  aplicada ao multiplicador 460), porque o sinal de diferença codificado é realimentado na linha 240 para a unidade de compressão de banda larga 280. Pelo motivo da realimentação ser disposta para ser negativa, quando o sinal de áudio na linha 239 aumenta na sua amplitude, o sinal na linha 450a aumenta, o que por sua vez faz com que o ganho do multiplicador 434 diminuir. Quando o sinal de áudio na linha 239 diminui na sua amplitude, o sinal na linha 450a diminui, o que por sua vez faz com que o ganho do multiplicador 434 aumentar.

30      Entretanto, deve existir um sinal dc significante presente na linha 239 em adição ao sinal de áudio de baixo nível, o sinal é bloqueado a partir do processo de realimentação pela ação do filtro de banda de passagem de banda larga 448, que possui resposta zero para os 35 sinais dc. Em particular, qualquer dc presente no sinal de diferença codificado na linha 240 é bloqueado pelo filtro 448 e não é percebido pelo detector de nível RMS 450. Qualquer sinal dc presente na linha 239 será amplificado pelo multiplicador 434 com qualquer sinal de

áudio presente na linha 239, mas o fator de amplificação ou ganho será determinado somente pela amplitude do sinal de áudio percebida pelo detector de nível RMS 450 após a filtragem pelo filtro 448.

Como declarado acima, toda vez que a amplitude do sinal de áudio na linha 239 varia, o ganho do multiplicador 434 varia de forma inversa. Durante tais variações no ganho, qualquer dc presente na linha 239 irá também estar sujeito a amplificação variável, em verdade modulando o sinal dc, para por meio disso produzir um sinal ac. Deste modo, tais sinais dc podem ser modulados de modo a se criar sinais de banda de áudio significantes que não estarão sujeitos a serem rejeitados pelo filtro 448 e são portanto percebidos pelo detector 450. Quando o sinal de áudio na linha 239 é pequeno se comparado com o dc na linha 239, pequenas variações no nível do sinal de áudio, que causam alterações no ganho do amplificador 434, podem causar uma grande alteração no nível (que eleva-se a um sinal ac) na linha 281 através deste processo de modulação. O sinal ac produzido tende a aumentar o sinal total que passa através do filtro 448, independente de se a variação do sinal de áudio que deu origem ao sinal ac foi um aumento ou uma diminuição no nível do sinal. Em particular, caso o nível do sinal de áudio na linha 239 diminua, o processo de realimentação negativa normalmente aumenta o ganho do multiplicador 434. Entretanto, se um sinal dc suficiente estiver presente na linha 239, uma diminuição no sinal de áudio na linha 239 pode causar um aumento no sinal percebido pelo detector 450, forçando ao ganho do multiplicador 434 diminuir. Deste modo, o processo de realimentação negativa é revertido e a realimentação se torna positiva.

Tal realimentação positiva irá somente persistir durante o tempo em que o sinal dc modulado na linha 281 é grande o suficiente se comparado com qualquer sinal de áudio presente na linha 281, quando ponderado pela resposta de todos os filtros e o sinal se modifica entre a linha 281 e a saída do filtro 448. Uma vez que o ganho do multiplicador 434 diminui suficientemente de modo que o sinal dc modulado na linha 281 não proporcione por mais tempo uma entrada significante para o detector 450, a realimentação reverte-se para seu sentido negativo normal. De acordo com a constante de tempo do detector 450, o sistema irá readquirir um nível de ganho apropriado baseado no nível do sinal de áudio na linha 239. Mas, se um dc suficiente permanecer no sinal na linha 239, o ciclo irá repetir por si próprio uma vez que o ganho do multiplicador 434 aumente de forma suficiente. Durante cada período de realimentação positiva, é produzida uma alteração abrupta no nível dc da linha 281. Esta alteração é audível e soa alguma coisa similar ao "pulso" de um relógio. Desde que as alterações dc irão ocorrer com alguma regularidade, baseado na constante de tempo do detector 450, o fenômeno é freqüentemente referido como "pulsação".

Um método para impedir a pulsação é remover qualquer componente dc presente no sinal de entrada para o codificador 200. Isto é realizado pelos filtros de banda alta 212 e

214. Adicionalmente, os filtros de banda alta 212 e 214 ajudam a maximizar a faixa dinâmica do codificador 200 por remover os componentes dc que de outro modo pode utilizar a faixa dinâmica acima do valor. Como declarado acima e como apresentado na Figura 3, o filtro de banda baixa 238 é de preferência implementado como dois filtros 238a e 238b. O filtro de divisão 238 deste modo proporciona várias vantagens. Se o filtro 238a fosse eliminado, e todo o filtro 238 fosse localizado após o cortador 254 (isto é, na localização do filtro 238b), então, quaisquer componentes acima de 15 kHz nos sinais de entrada de áudio podem causar instabilidade na unidade de compressão de banda larga 280 similar ao comportamento de pulsação descrito acima. Isto ocorre porque quaisquer componentes do sinal acima de 15 kHz na linha 239 serão amplificados pelo multiplicador 434 (apresentado na Figura 5) e porque tais componentes não irão ser percebidos pelo detector de nível RMS desde que tais componentes são filtrados pelo filtro de banda baixa seguindo ao cortador 254 (apresentado na Figura 3). Desde que o detector 450 aumenta o ganho do multiplicador 434 quando ele percebe a ausência de um sinal, o ganho do multiplicador 434 pode tornar-se relativamente grande quando o sinal na linha 239 consistir de uma informação de sinal de áudio pequena (abaixo de 15 kHz), mas para informação de alta freqüência significante (acima de 15 kHz), o multiplicador 434 então amplifica a informação de alta freqüência, que pode gerar sinais grandes que são prováveis de serem cortadas pelos componentes na seção de processamento 230. Este corte pode produzir harmônicos que podem ser conhecidos como freqüências baixas que serão percebidas pelo detector de nível RMS 450 causando que o sistema pulse como descrito anteriormente. Alternativamente, se o filtro 238b fosse eliminado e todo o filtro 238 fosse localizado antes do filtro de pré-ênfase fixo 232a (isto é, na localização do filtro 238a), então, os artefatos de alta freqüência gerados pelo cortador 254 poderiam ser incluídos no sinal de diferença codificado -e poderia interferir com o tom piloto no sinal composto. Portanto, o filtro dividido 238 como apresentado proporciona uma disposição ótima por meio da qual o filtro 238 impede a pulsação na unidade de compressão 280 e o filtro 238b filtra os artefatos de alta freqüência que podem ser gerados pelo cortador 254.

O filtro de pré-ênfase fixo 232 é também, de preferência dividido em dois filtros 232a, 232b como apresentado na Figura 3. O filtro 232 tipicamente requer um ganho relativamente grande nas freqüências altas, como é especificado no padrão BTSC e utilizando somente uma única seção para implementar o filtro 232 se aumenta a probabilidade do filtro 232 causar o corte. É vantajoso aplicar algum do ganho do filtro 232 no lado de entrada da unidade de compressão de banda larga 280 (com o filtro 232a) e aplicar algum ganho do filtro 232 no lado de saída da unidade de compressão de banda larga 280 (com o filtro 232b). Desde que a unidade 280 normalmente comprime seu sinal de entrada, a distribuição do ganho do filtro 232 ao redor da compressão proporcionada pela unidade 280 diminui a

probabilidade de que o ganho do filtro 232 cause uma condição de transbordo.

Para minimizar o tamanho, consumo de força e custo, o codificador 200 é de preferência implementado utilizando-se um único chip de processamento de sinal digital. O codificador 200 foi implementado com sucesso utilizando um dos chips de processamento de sinal digital Motorola DSP 56002 (esta implementação deve ser referida daqui para frente como a "Modalidade DSP"). O Motorola DSP 56002 é um chip de vinte e quatro bits de ponto fixo, entretanto, outros tipos de chips de processamento, tal como chips de ponto flutuante, ou chips de ponto fixo possuindo outros comprimentos de palavra, poderiam obviamente ser utilizados. A Modalidade DSP do codificador 200 utiliza uma freqüência de amostragem  $f_s$  que é igual a três vezes a freqüência piloto  $f_H$  (isto é,  $f_s = 47202$  Hz). A Tabela 1 seguinte lista todos os coeficientes do filtro utilizados na Modalidade DSP do codificador 200 exceto aqueles utilizados no filtro de ênfase variável 560.

TABELA 1

|  |                                                          |     |                                                                  |

|--|----------------------------------------------------------|-----|------------------------------------------------------------------|

|  | Filtro de Banda Baixa<br>(Seção nº 1) 310<br>(Equação 4) | 312 | Filtro de Banda Baixa (Seção nº 2)<br>(Equação 4)                |

|  | $b_0=0,18783270$                                         |     | $b_0=0,44892888$                                                 |

|  | $b_1=0,36310206$                                         |     | $b_1=0,70268024$                                                 |

|  | $b_2=0,18783270$                                         |     | $b_2=0,44892888$                                                 |

|  | $a_1=0,388832539$                                        |     | $a_1=0,12638618$                                                 |

|  | $a_2=0,12709286$                                         |     | $a_2=0,47415181$                                                 |

|  | Filtro de Banda Baixa<br>(Seção nº 3) 314<br>(Equação 4) | 316 | Filtro de Banda Baixa (Seção nº 4)<br>(Equação 4)                |

|  | $b_0=0,70674027$                                         |     | $b_0=0,85733126$                                                 |

|  | $b_1=0,87637648$                                         |     | $b_1=0,01505047$                                                 |

|  | $b_2=0,70674027$                                         |     | $b_2=0,85733126$                                                 |

|  | $a_1=0,53702472$                                         |     | $a_1=0,74320197$                                                 |

|  | $a_2=0,75298490$                                         |     | $a_2=0,89832289$                                                 |

|  | Filtro de Banda baixa<br>(Seção nº 5) 318<br>(Equação 4) |     | Filtro de Banda de Passagem de<br>Banda Larga 448<br>(Equação 4) |

|  | $b_0=0,92737972$                                         |     | $b_0=0,02854672$                                                 |

|  | $b_1=0,92729649$                                         |     | $b_1=0,18789051$                                                 |

|  | $b_2=0,92737972$                                         |     | $b_2=0,21643723$                                                 |

|  | $a_1=0,82951974$                                         |     | $a_1=1,75073141$                                                 |

|                                                                                           |                                                                               |

|-------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------|

| $a_2=0,97259237$                                                                          | $a_2=0,75188028$                                                              |

| Filtro de Pré-ênfase Fixo<br>238a                                                         | Filtro de Pré-ênfase fixo 238b                                                |

| $b_0=9,50682180$                                                                          | $b_0=4,357528$                                                                |

| $b_1=-9,00385663$                                                                         | $b_1=-3,24843271$                                                             |

| $a_1=-0,497064357$                                                                        | $a_1=0,10881833$                                                              |

| Filtro de banda de Passagem<br>de Espectro<br>(Seção nº1) 542 <sup>a</sup><br>(Equação 4) | Filtro de Banda de Passagem de<br>espectro<br>(Seção nº2) 542b<br>(Equação 4) |

| $b_0=0,646517841$                                                                         | $b_0=0,850281278$                                                             |

| $b_1=0,649137616$                                                                         | $b_1=-0,850247036$                                                            |

| $b_2=0,0$                                                                                 | $b_2=0,0$                                                                     |

| $a_1=0,557821757$                                                                         | $a_1=-0,602159890$                                                            |