# (19) United States

# (12) Patent Application Publication (10) Pub. No.: US 2008/0266965 A1 Takeuchi et al.

## (54) NONVOLATILE SEMICONDUCTOR MEMORY HAVING PLURAL DATA STORAGE PORTIONS FOR A BIT LINE CONNECTED

(75) Inventors:

Ken Takeuchi, Tokyo (JP); Tomoharu Tanaka, Yokohama-shi (JP); Noboru Shibata, Yokohama-shi (JP)

Correspondence Address:

TO MEMORY CELLS

**BANNER & WITCOFF, LTD.** ATTORNEYS FOR CLIENT NO. 000449, 001701 1100 13th STREET, N.W., SUITE 1200 **WASHINGTON, DC 20005-4051 (US)**

Kabushiki Kaisha Toshiba, Tokyo Assignee:

(JP)

(21) Appl. No.: 12/163,676

(22) Filed: Jun. 27, 2008

#### Related U.S. Application Data

Continuation of application No. 11/511,488, filed on Aug. 29, 2006, now Pat. No. 7,394,695, which is a

(43) **Pub. Date:**

Oct. 30, 2008

division of application No. 10/073,999, filed on Feb. 14, 2002, now Pat. No. 7,177,196, which is a division of application No. 09/667,610, filed on Sep. 22, 2000, now Pat. No. 6,373,746.

#### (30)Foreign Application Priority Data

| Sep. 28, 1999 | (JP) | <br>11-275327 |

|---------------|------|---------------|

| Dec. 3, 1999  | (JP) | <br>11-345299 |

#### **Publication Classification**

(51) Int. Cl.

(2006.01)

G11C 16/04 (52)

(57)**ABSTRACT**

Data having three values or more is stored in a memory cell in a nonvolatile manner. A data circuit has a plurality of storage circuits. One of the plurality of storage circuits is a latch circuit. Another one of the plurality of storage circuits is a capacitor. The latch circuit and the capacitor function to temporarily store program/read data having two bits or more. Data held by the capacitor is refreshed using the latch circuit if data variation due to leakage causes a program. As a result, the data circuit does not become large in size even if multilevel data is used.

FIG. 1 PRIOR ART

FIG. 2 PRIOR ART

FIG. 3 PRIOR ART

FIG. 4 PRIOR ART

FIG. 5 PRIOR ART

FIG. 7 PRIOR ART

FIG.8

FIG. 10

FIG. 11

RMAINI: i-TH WORD LINE DRIVER RADDi: i-TH ROW ADDRESS DECODER

RDECADS: : WORD LINE DRIVER SELECTING SIGNAL

i=1.2.3.4. • •

FIG. 13

FIG. 16

FIG. 17

FIG. 19

FIG. 20

### PROGRAM OF EVEN PAGE DATA

FIG. 21

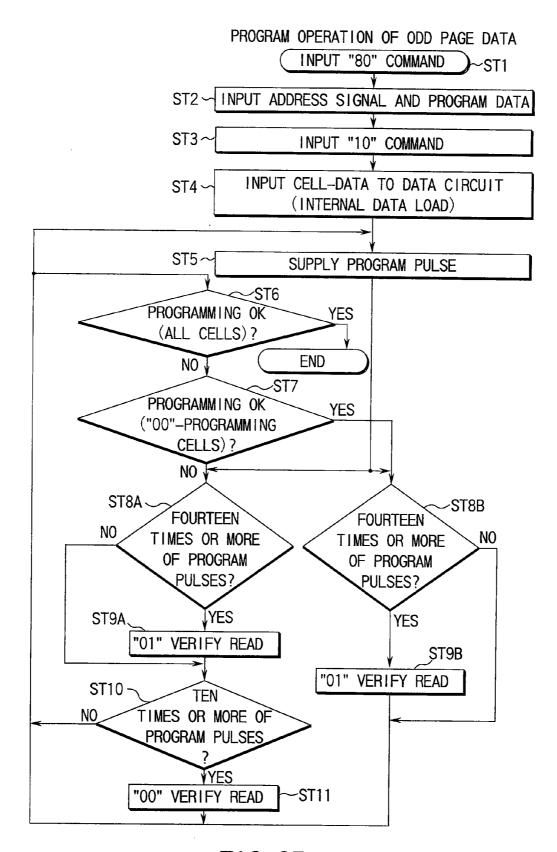

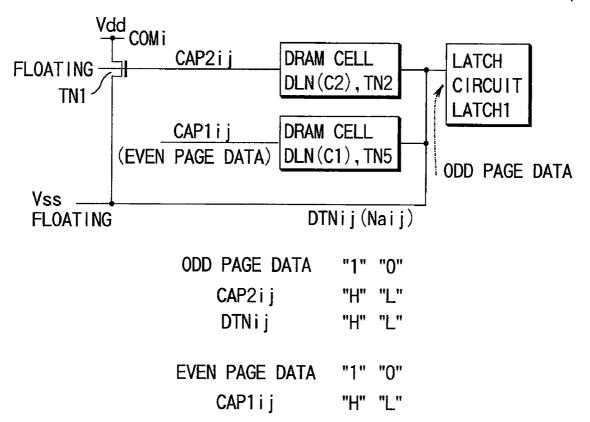

### PROGRAM OF ODD PAGE DATA

FIG. 22

FIG. 23

FIG. 24

# READ OF EVEN PAGE DATA

FIG. 25

FIG. 26

## READ OF ODD PAGE DATA

FIG. 27

# PROGRAM OPERATION OF EVEN PAGE DATA

FIG. 28

PROGRAM WHEN LSB, WLs NEIGHBORING SELECTED WL SET Vss

PROGRAM COMPLETION DETECTION IS OPERATED TOO

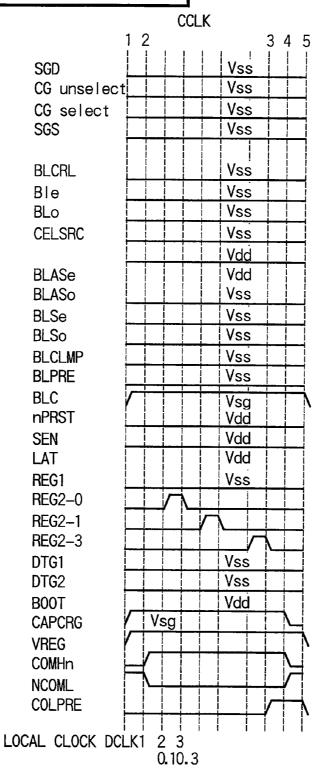

IN PERIOD CCLK1~10

FIG. 29

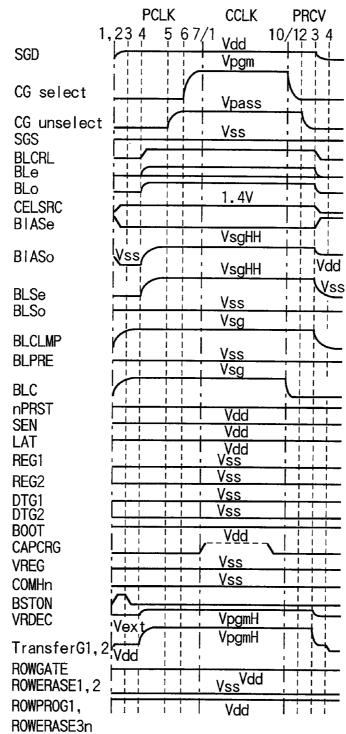

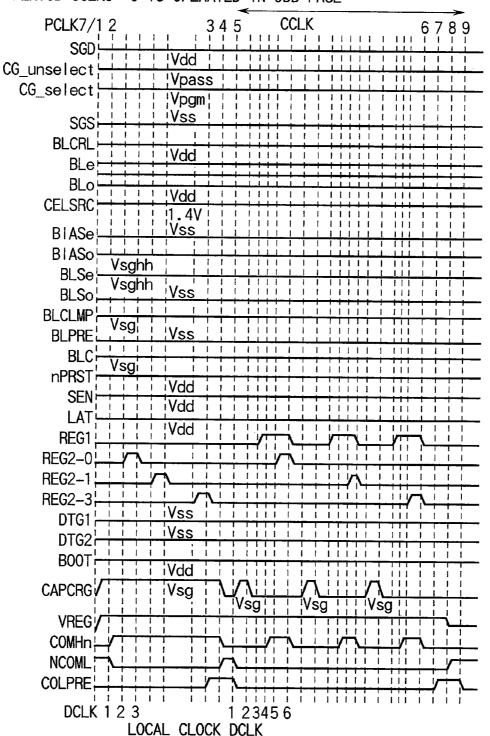

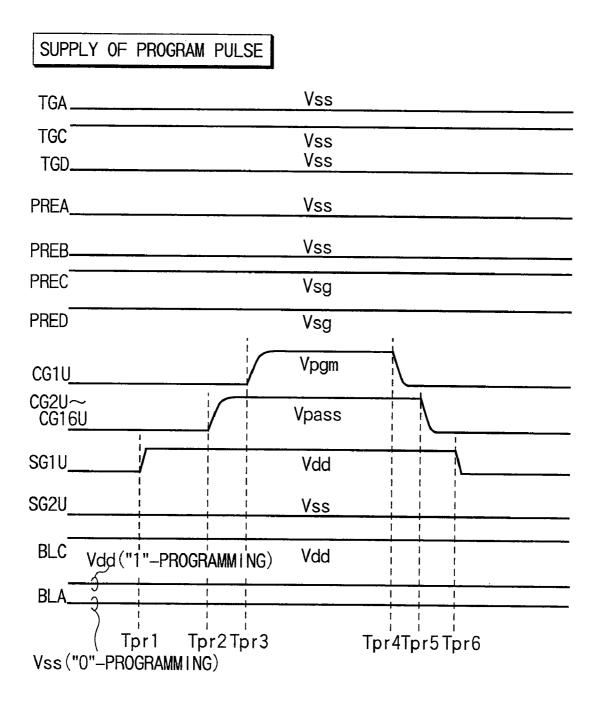

# PROGRAM OF EVEN PAGE DATA (SUPPLY PROGRAM PULSE)

FIG. 30

FIG. 31

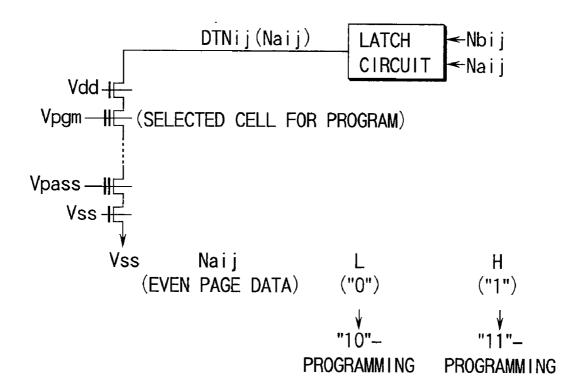

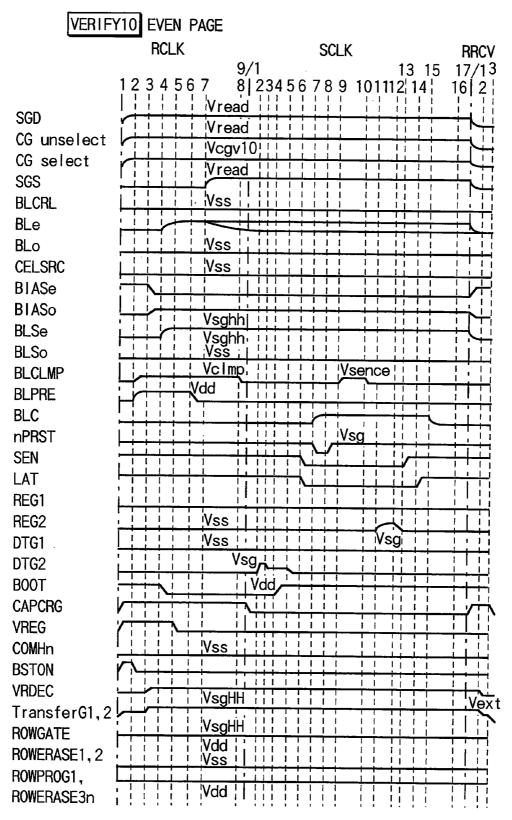

# PROGRAM OF EVEN PAGE DATA ("10" VERIFY READ)

FIG. 32

# PROGRAM COMPLETION DETECTION

PERIOD CCLK5~9 IS OMITTED IN EVEN PAGE(NOTES:CCLK5=CCLK9)

PERIOD CCLK5~9 IS OPERATED IN ODD PAGE

FIG. 33

# PROGRAM OF EVEN PAGE DATA (PROGRAM COMPLETION DETECTION)

FIG. 34

FIG. 35

FIG. 36

FIG. 37

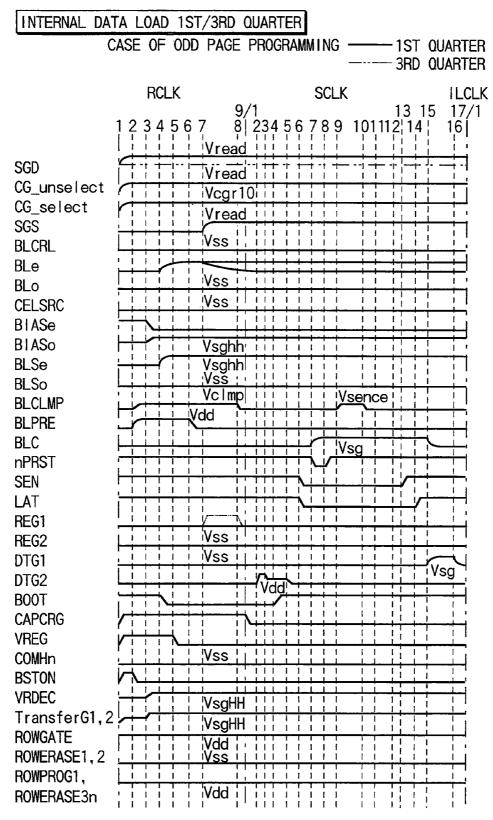

# PROGRAM OF ODD PAGE DATA (INTERNAL DATA LOAD 1ST QUARTER)

FIG. 38

# PROGRAM OF ODD PAGE DATA (INTERNAL DATA LOAD 2ND QUARTER)

FIG. 39

## PROGRAM OF ODD PAGE DATA (INTERNAL DATA LOAD 3RD QUARTER)

FIG. 40

# PROGRAM OF ODD PAGE DATA (INTERNAL DATA LOAD 4TH QUARTER)

FIG. 41

FIG. 42

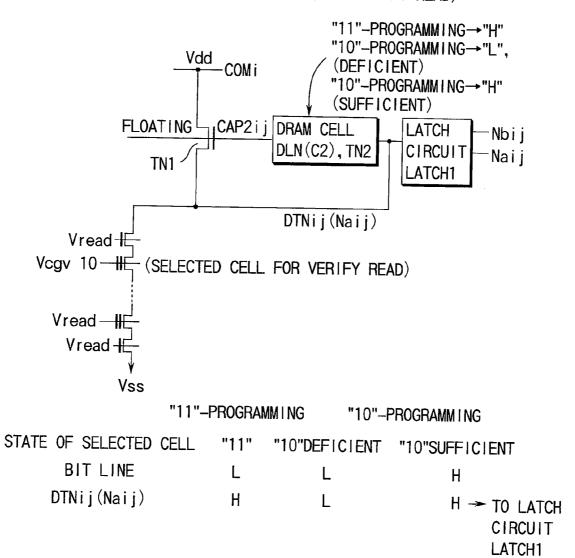

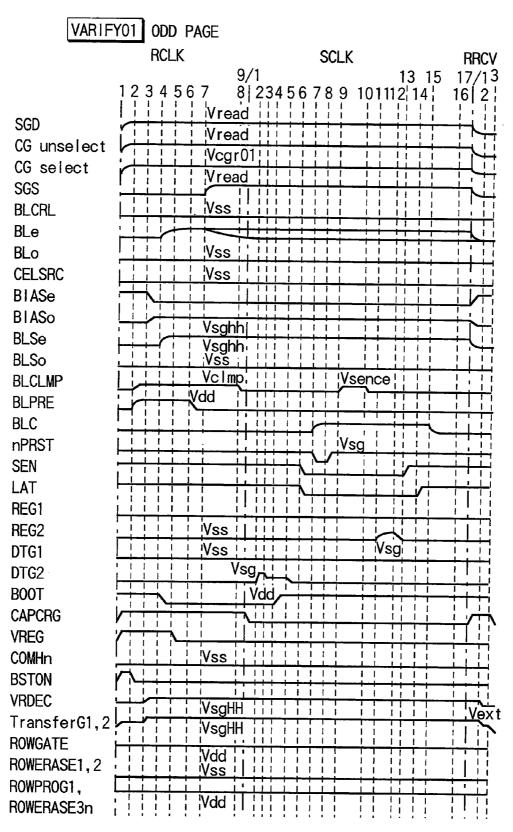

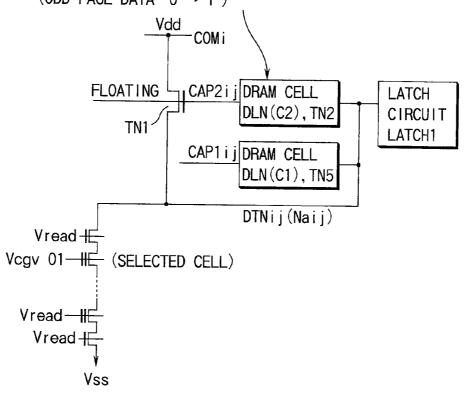

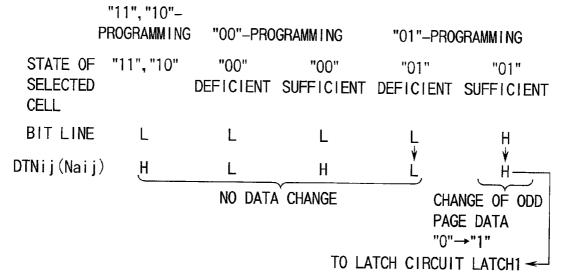

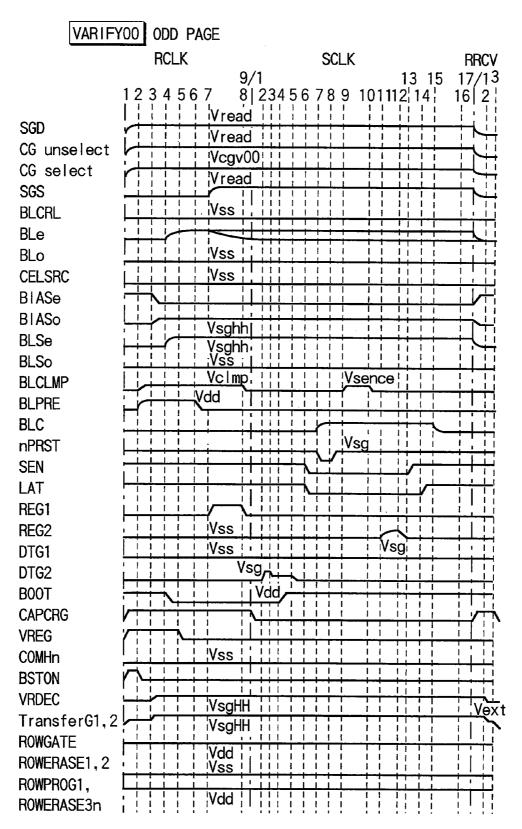

# PROGRAM OF ODD PAGE DATA ("01" VERIFY READ)

- "11", "10"-PROGRAMMING--"H"(ODD PAGE DATA "1")

- "00", "01"-PROGRAMMING (DEFICIENT) → "L"(ODD PAGE DATA "0")

- "01"-PROGRAMMING (SUFFICIENT)-→"H"(ODD PAGE DATA "0"-→"1")

- \* "00"-PROGRAMMING (SUFFICIENT) →"10"-PROGRAMMING (ODD PAGE DATA "0"-→"1")

FIG. 43

FIG. 44

FIG. 46

## ERASE VERIFY READ

VERIFY OF EVEN COLUMN→ALL DETECTION→DETECTION OF FAIL CELL NUMBER(Y-SCAN)→VERIFY OF ODD COLUMN→ALL DETECTION →DETECTION OF FAIL CELL NUMBER(Y-SCAN)

## ERASE COMPLETION DETECTION

FIG. 48

FIG. 49

REFRESH

FIG. 50

FIG. 52

FIG. 53

FIG. 54

FIG. 55

FIG. 56

FIG. 58

FIG. 59

F 16. 6

FIG. 62

FIG. 63

FIG. 64

FIG. 65

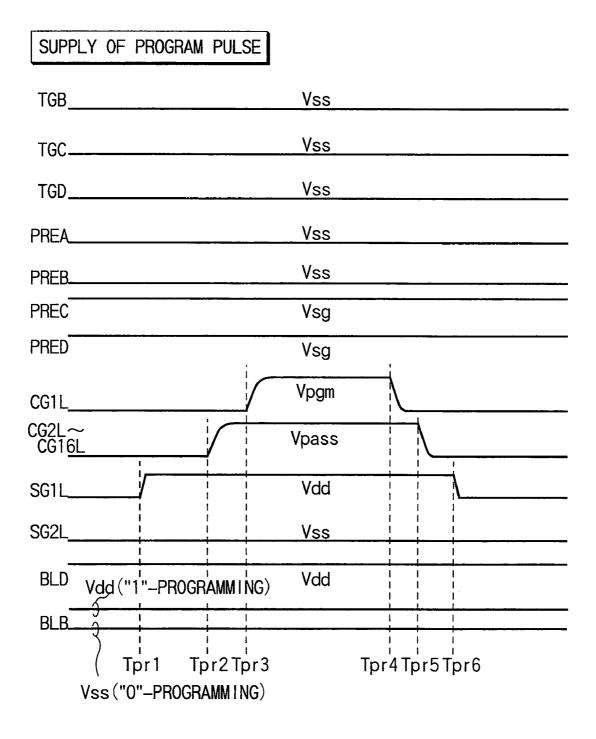

# SUPPLY OF PROGRAM PULSE

FIG. 66

FIG. 67

FIG. 68

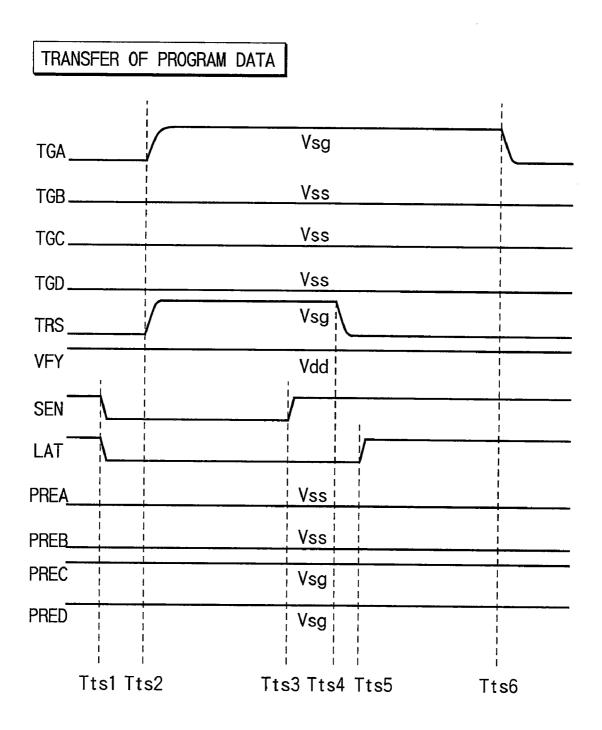

# TRANSFER OF PROGRAM DATA

FIG. 69

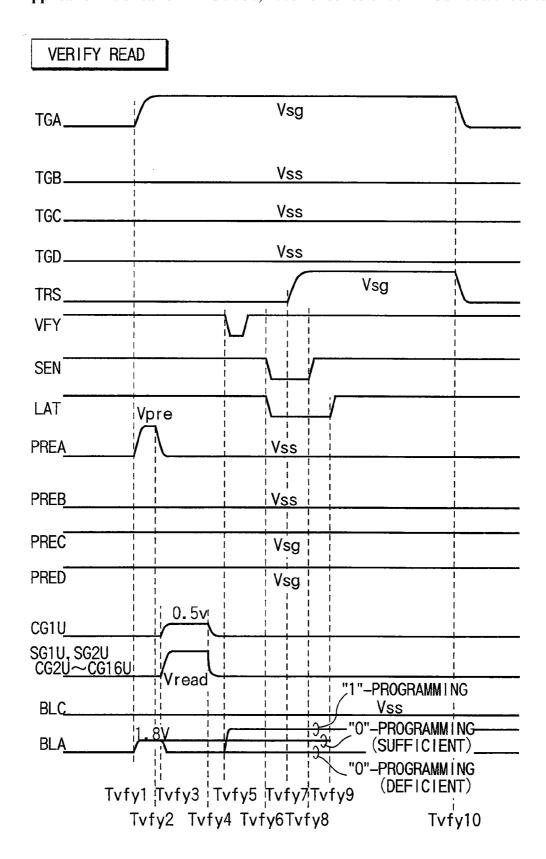

FIG. 70

FIG. 71

FIG. 72

FIG. 73

FIG. 74

|         | STEP1-1  | STEP1-2   | STEP1-3   | STEP1-4 | STEP1-5   | STEP1-2 STEP1-3 STEP1-4 STEP1-5 STEP1-6 STEP1-7 | STEP1-7                                        |

|---------|----------|-----------|-----------|---------|-----------|-------------------------------------------------|------------------------------------------------|

| TrNA1   | NO       | OFF       | 0FF       | NO      | 0FF       | OFF                                             | 0FF                                            |

| TrNA2   | 0FF      | NO        | HO0       | 0FF     | NO        | NO                                              | OFF                                            |

| TrNA3   | 0FF      | 0FF       | NO        | OFF     | 0FF       | OFF                                             | 0FF                                            |

| TrNB1   | 0FF→0N   | 0FF       | 0FF       | 0FF→0N  | 0FF       | 0FF                                             | NO                                             |

| TrNB2   | OFF.     | 0FF→0N    | 0FF       | OFF     | 0FF→0N    | NO                                              | 0FF                                            |

| TrNB3   | 0FF      | OFF       | 0FF→0N    | OFF     | OFF       | 0FF                                             | 0FF                                            |

| CellA1  | DATA LOA | NO BETE   | NT I ON   | REFRESH | PR(       | JGRAMMING-                                      | AD DATA TRANSFER PROGRAMMINGFROM BLB1 TO DL    |

| Cell A2 |          | DATA LOAI | DBETE     | NTIONF  | ÆFRESHF   | PROGRAMMIN                                      | DATA LOAD DATA REFRESHPROGRAMMING BETENTION    |

| CellA3  |          |           | DATA LOAE | )DATA   | YT I ONPF | ROGRAMM I NG                                    | DATA LOAD DATA RETENTION PROGRAMMING RETENTION |

DL : DATA LATCH (LATCH CIRCUIT IN DATA CIRCUIT)

# FIG. 75

|        |          | STEP1-8           | STEP1-9                       | STEP1-10       | STEP1-11                                | STEP1-12 |

|--------|----------|-------------------|-------------------------------|----------------|-----------------------------------------|----------|

| TrNA1  |          | ON                | 0FF                           | 0FF            | 0FF                                     | 0FF      |

| TrNA2  |          | OFF               | 0FF                           | ON             | 0FF                                     | 0FF      |

| TrNA3  |          | 0FF               | 0FF                           | 0FF            | 0FF                                     | ON \     |

| TrNB1  |          | OFF→ON            | 0FF                           | 0FF            | OFF                                     | 0FF      |

| TrNB2  |          | 0FF               | ON                            | 0FF→0N         | 0FF                                     | 0FF      |

| TrNB3  |          | 0FF               | 0FF                           | 0FF            | ON                                      | OFF→ON   |

| CellA1 |          | VERIFY            |                               | DATA RE        | TENTION                                 |          |

| CellA2 | DA<br>RE | ATA<br>ETENTION - | DATA<br>TRANSFER<br>FROM BLB2 | <b>V</b> ERIFY | DATA<br>RETEN                           |          |

| CellA3 |          | DATA<br>RETENTION | TO DL                         |                | DATA<br>TRANSFER-<br>FROM BLB3<br>TO DL | - VERIFY |

DL: DATA LATCH (LATCH CIRCUIT IN DATA CIRCUIT)

FIG. 76

|        |          | STEP1-13            | STEP1-14                                 | STEP1-15            | STEP1-16                               | STEP1-17     | 7  |

|--------|----------|---------------------|------------------------------------------|---------------------|----------------------------------------|--------------|----|

| TrNA1  |          | OFF                 | ON                                       | 0FF                 | 0FF                                    | 0FF          |    |

| TrNA2  |          | OFF                 | 0FF                                      | 0FF                 | ON                                     | ON           |    |

| TrNA3  |          | OFF                 | 0FF                                      | OFF                 | 0FF                                    | OFF          |    |

| TrNB1  |          | ON                  | 0FF                                      | 0FF                 | OFF                                    | OFF          | I  |

| TrNB2  |          | 0FF                 | 0FF                                      | ON                  | OFF                                    | ON           |    |

| TrNB3  |          |                     | 0FF                                      | OFF                 | 0FF                                    | 0FF          | \  |

| CellA1 | T<br>  E | RANSFER<br>ROM RLR1 | DATA<br>TRANSFER<br>FROM DL<br>TO BLA1 D | DATA<br>RETEI       |                                        | PROGRAMMIN   | NG |

| CellA2 |          | DATA<br>RETENTIO    | T<br>N F                                 | RANSFER<br>ROM BLB2 | DATA<br>TRANSFER<br>FROM DL<br>TO BLA2 | PROGRAMMIN   | VG |

| CellA3 |          |                     |                                          |                     |                                        | PROGRAMM I N | IG |

DL : DATA LATCH (LATCH CIRCUIT IN DATA CIRCUIT)

FIG. 77

### NONVOLATILE SEMICONDUCTOR MEMORY HAVING PLURAL DATA STORAGE PORTIONS FOR A BIT LINE CONNECTED TO MEMORY CELLS

# CROSS-REFERENCE TO RELATED APPLICATIONS

[0001] The present application is a continuation of pending U.S. patent Ser. No. 11/511,488, filed Aug. 29, 2008, which is a divisional of U.S. patent application Ser. No. 10/073,999 filed Feb. 14, 2002 (U.S. Pat. No. 7,177,196), which is a divisional of U.S. patent application Ser. No. 09/677,610, filed Sep. 22, 2000 (U.S. Pat. No. 6,373,746), entitled "Nonvolatile Semiconductor Memory Having Plural Data Storage Portions For A Bit Line Connected To Memory Cells," which are based on and claim the benefit of priority from the prior Japanese Patent Applications No. 11-275327, filed Sep. 28, 1999; and No. 11-345299, filed Dec. 3, 1999, the entire contents of which are incorporated herein by reference.

### BACKGROUND OF THE INVENTION

[0002] The present invention relates to a nonvolatile semiconductor memory and particularly relates to a nonvolatile semiconductor memory used as a multi-level NAND cell type EEPROM, e.g., a four-level NAND cell type EEPROM.

[0003] There is known, as one of nonvolatile semiconductor memories, an NAND cell type EEPROM. This EEPROM has a memory cell array consisting of a plurality of NAND cell units. Each of the NAND cell units consists of a plurality of memory cells connected in series and two select transistors connected to both ends of the memory cells, respectively. The NAND cell unit is connected between a bit line and a source line

[0004] Each memory cell consists of an n channel MOS transistor having a so-called stack gate structure in which a control gate electrode is stacked on a floating gate electrode. Each select transistor consists of an n channel MOS transistor having a structure in which an upper electrode is stacked on a lower electrode as in the case of the memory cell. It is the lower electrode, for example, that actually functions as the gate electrode of the select transistor.

[0005] One source region or one drain region is common to adjacent two transistors among a plurality of transistors (memory cells and select transistors) in an NAND cell unit.

[0006] Now, the concrete structure of an NAND cell type EEPROM will be described.

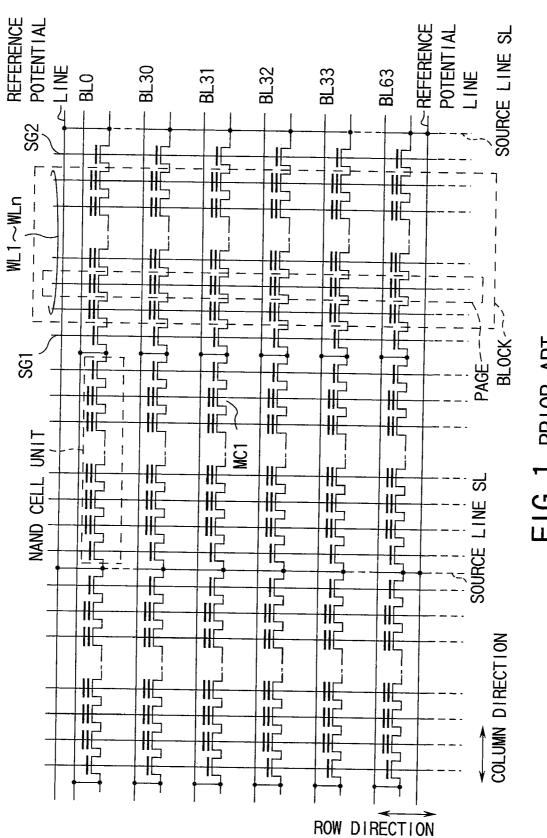

$\cite{[0007]}$  FIG. 1 shows part of a memory cell array of the NAND cell type EEPROM.

[0008] Each NAND cell unit consists of a plurality of (4, 8, 16 or the like) memory cells connected in series and two select transistors connected to both ends of the memory cells, respectively. The NAND cell unit is connected between bit lines BLi and source lines SL. Each of the source lines is connected to reference potential lines each formed of a conductive member such as polysilicon at preset positions.

[0009] The source lines SL extend in row direction, whereas the bit lines BLi and the reference potential lines extend in column direction. Contact portions on which the source line SL and the reference potential line contact are provided at intervals at which each source line SL intersects, for example, 64 bit lines, i.e., four bit lines BL0, . . . BL63.

The reference potential lines is connected to so-called peripheral circuits provided on the peripheral section of the memory cell array.

[0010] Word lines (control gate lines) WL1, and WLn extend in the row direction and the select gate lines SG1 and SG2 extend in the row direction, as well. The collection of the memory cells connected to one word line (control gate line) WLi is called one page. Further, the collection of the memory cells connected to the word lines WL1, and WLn put between the two select gate lines SG1 and SG2 is called one NAND block or simply one block.

[0011] One page consist of, for example, 256-byte (256×8) memory cells. The memory cells in one page are programmed almost simultaneously. In addition, if one page consists of 256-byte memory cells and one NAND cell unit consists of eight memory cells, one block consists of 2048-byte (2048×8) memory cells. The memory cells in one page are erased almost simultaneously.

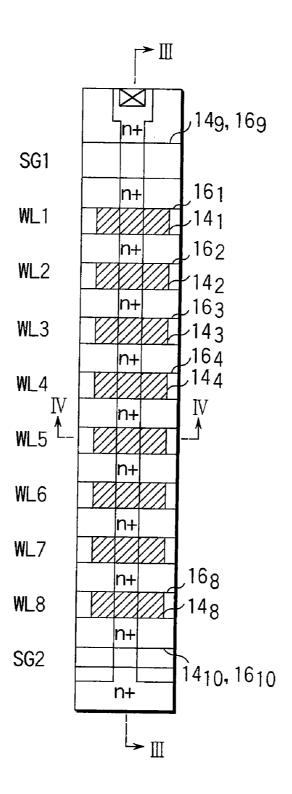

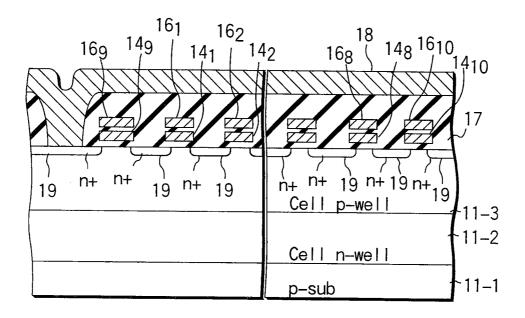

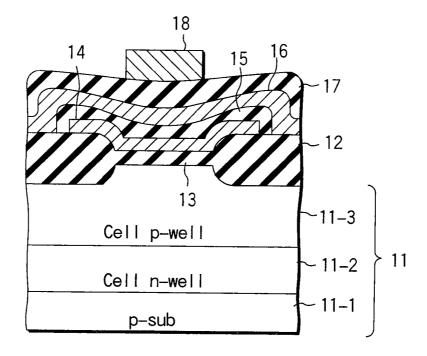

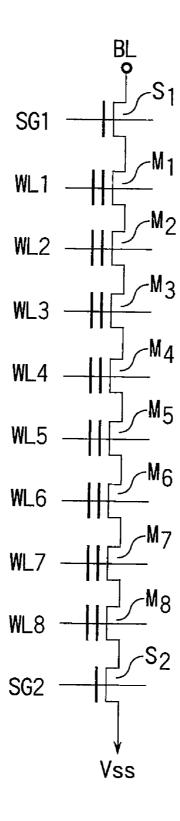

[0012] FIG. 2 is a plan view of one NAND cell unit in the memory cell array. FIG. 3 is a cross-sectional view of the NAND cell taken along line III-III of FIG. 2. FIG. 4 is a cross-sectional view thereof taken along line IV-IV of FIG. 2. FIG. 5 shows an equivalent circuit of the devices of FIGS. 2 to

[0013] In a p substrate (p-sub) 11-1, a so-called double-well region, consisting of an n well region (Cell n-well) 11-2 and p well region (Cell p-well) 11-3, is formed. The memory cells and select transistors are formed in the p well region 11-3.

[0014] The memory cells and select transistors are arranged in an element region within the p well region 11-3. The element region is surrounded by an element separation oxide film (element separation region) 12 formed on the p well region 11-3.

[0015] In this example, one NAND cell unit consists of eight memory cells M1 to M8 connected in series and two select transistors S1 and S2 connected to the both ends of the memory cells, respectively.

[0016] Each memory cell consists of a silicon oxide film (gate insulating film) 13 formed on the p well region (Cell p-well) 11-3, a floating gate electrode 14 ( $14_1$ ,  $14_2$ ...  $14_8$ ) on the silicon oxide film 13, a silicon oxide film (inter-polysilicon insulating film) 15 on the floating gate electrode 14 ( $14_1$ ,  $14_2$ ...  $14_8$ ), a control gate electrode 16 ( $16_1$ ,  $16_2$ ...  $16_8$ ) on the silicon oxide film 15 and a source-drain region 19 in the p well region (Cell p-well) 11-3.

[0017] Each select transistor consists of a silicon oxide film (gate insulating film) formed on the p well region 11-3, a gate electrode 14 (14 $_9$ , 14 $_{10}$ ) and 16 (16 $_9$ , 16 $_{10}$ ) on the silicon oxide film, and a source-drain region 19 in the p well region 11-3.

[0018] The structure of the select transistor is similar to that of the memory cell for the following reason. By simultaneously forming the memory cells and the select transistors through the same process, the number of process steps is intended to be reduced to thereby reduce production cost.

[0019] One source region (n<sup>+</sup> diffused layer) 19 or one drain region (n<sup>+</sup> diffused layer) 19 is common to adjacent two transistors among the plural transistors (memory cells and select transistors) in the NAND cell unit.

[0020] The memory cells and the select transistors are covered with a silicon oxide film (CVD oxide film) 17 formed by the CVD method. A bit line 18 connected to one end of the NAND cell unit ( $n^+$  diffused layer 19) is arranged on the CVD oxide film 17.

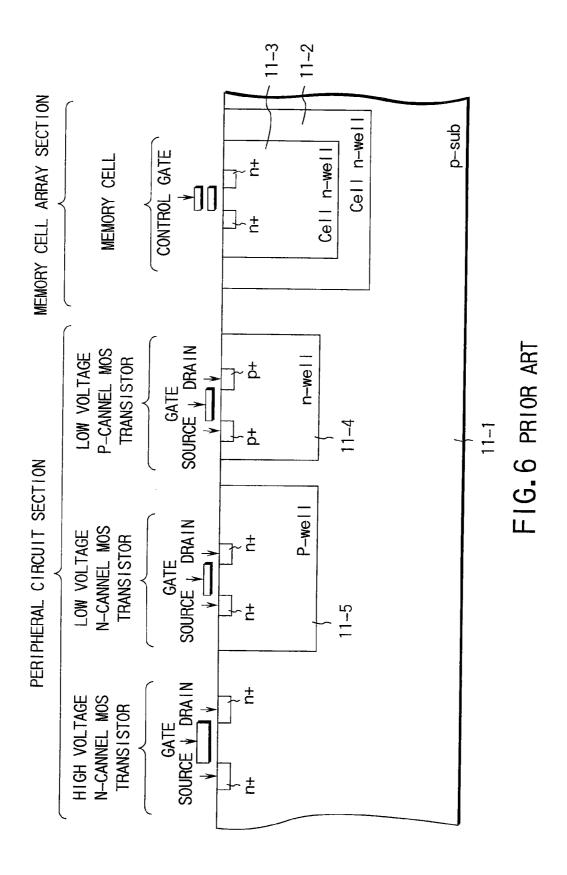

[0021] FIG. 6 shows the well structure of the NAND cell type EEPROM.

[0022] In the p substrate (p-sub) 11-1, a so-called double-well region, consisting of the n well region (Cell n-well) 11-2 and the p well region (Cell p-well) 11-3, an n well region (n-well) 11-4 and a p well region (p-well) 11-5.

[0023] The double-well region is formed on a memory cell array section, and the n well region 11-4 and the p well region 11-5 are formed on a peripheral circuit section.

[0024] The memory cells are formed in the p well region 11-3. The n well region 11-2 and the p well region 11-3 are set to have the same potential.

[0025] A high voltage n channel MOS transistor applied with a higher voltage than a power supply potential is formed on the p substrate (p-sub) 11-1. A low voltage p channel MOS transistor applied with the power supply voltage is formed on the n well region (n-well) 11-4 and a low voltage n channel MOS transistor applied with the power supply voltage is formed on the p well region (p-well) 11-5.

[0026] Next, the basic operation of the NAND cell type EEPROM will be described.

[0027] First, to facilitate the description, the following preconditions are specified. Two level data "0" and "1" are stored in a memory cell; a state in which the threshold voltage of the memory cell is low (e.g., the threshold voltage is negative) is a "0" state; and a state in which the threshold voltage of the memory cell is high (e.g., the threshold voltage is positive) is a "1" state.

[0028] In an ordinary two-level NAND cell type EEPROM, a state in which the threshold voltage of the memory cell is low is set at a "1" state and that in which the threshold voltage is high is set at a "0" state. However, as will be described later, the present invention is mainly intended for a multi-level (e.g., four-level) NAND type EEPROM. Considering this, it is assumed that a state in which the threshold voltage of the memory cell is low is a "0" state and that in which the threshold voltage of the memory cell is high is a "1" state.

[0029] As for the memory cell, it is assumed that the "0" state is an erase state and the "1" state is a program state. "Programming" involves "0"-programming and "1"-programming. The "0"-programming means maintaining the erase state ("0" state) and the "1"-programming means changing the "0" state to the "1" state.

[0030] Program Operation

[0031] In program operation, the potential of a bit line is set according to program data on a selected memory cell connected to the bit line. For example, if the program data is "1" ("1"-programming), the potential of the bit line is set at a ground potential (0V) Vss. If the program data is "0" ("01"-programming), the potential of the bit line is set at a power supply potential Vcc.

[0032] The potential of a select gate line SG1 at a bit line side (drain side) in a selected block, i.e., in an NAND cell unit including the selected memory cell is set at the power supply potential Vcc. The potential of a select gate line SG2 at a source line side in the selected block, i.e., in the NAND cell unit including the selected memory cell is set at the ground potential (0V) vss.

[0033] The potentials of select gate lines SG1 and SG2 in the unselected block, i.e., in the NAND cell unit not including the selected memory cell are all set at the ground potential (0V) Vss

[0034] In case of "1"-programming, the ground potential (0V) Vss is transmitted to the channel of the selected memory

cell in the selected block. In case of "0"-programming, the channel potential of the selected memory cell in the selected block is Vcc-Vthsg (where Vthsg is the threshold voltage of the select transistor S1). Thereafter, the channel of the selected memory cell in the selected block turns into a floating state while maintaining the potential Vcc-Vthsg so as to cut off the select transistor S1 at the bit line side (drain side) in the selected block.

[0035] If the selected memory cell is not the closest to the bit line and the threshold voltage of a memory cell positioned at the bit line side with respect to the selected memory cell (or, at least one memory cell among a plurality of memory cells which exist at the bit line side with respect to the selected memory cell) is a positive voltage Vthcell, then the channel of the selected memory cell turns into a floating state while maintaining the potential Vcc-Vthcell.

[0036]  $\,$  Then, a program potential Vpp (e.g., about 20V) is applied to a selected word line in the selected block, i.e., to the control gate electrode of the selected memory cell. An intermediate potential Vpass (e.g., about 10V) is applied to unselected word lines in the selected block, i.e., the control gate electrodes of unselected memory cells.

[0037] At this moment, the channel potential of the selected memory cell to which "1"-programming is conducted, is the ground potential (0V) Vss. Due to this, a high voltage necessary for the "1"-programming is applied between the floating gate electrode and the channel (Cell p-well) of the memory cell and electrons move from the channel to the floating gate electrode by F-N tunnel effect. As a result, the threshold voltage of the selected memory cell rises (e.g., moves from a negative value to a positive value).

[0038] On the other hand, the channel potential of the selected memory cell to which "0"-programming is conducted, is Vcc-Vthsg or Vcc-Vthcell and the channel is in a floating state. Due to this, if either Vpp or Vpass is applied to the word line, the channel potential rises by the capacitive coupling between the control gate electrode and the channel. As a result, a high voltage necessary for "1"-programming is not applied between the floating gate electrode and the channel (Cell p-well) and the threshold voltage of the selected memory cell is kept in a present status (the memory cell is kept in an erase state).

[0039] Erase Operation

[0040] Data erase is carried out in block units and data on memory cells in a selected block are erased almost simultaneously.

[0041] Concrete erase operation will be described below.

[0042] First, the potentials of all word lines (control gate electrodes) in a selected block are set at 0V and the potentials of all word lines (control gate electrodes) of unselected blocks and all select gate lines in all blocks are set at an initial potential Va and then set in a floating state.

[0043] Thereafter, a high voltage Vpp (e.g., about 20V) is applied to the p well region (Cell p-well) and the n well region (Cell n-well) for erase operation.

[0044] At this moment, as for the memory cells in the selected block, since the potentials of the word lines (control gate electrodes) are 0V and those of the well regions are VppE, a sufficiently high voltage is applied between the control gate electrodes and the well regions for erase operation.

[0045] Accordingly, in the memory cells in the selected block, electrons in the floating gate electrodes move to the

well regions and the threshold voltages of the memory cells decrease (e.g., the threshold voltages become negative) by the F-N tunnel effect.

[0046] On the other hand, the potentials of all word lines in the unselected blocks rise from the initial potential Va to VppE or a potential close to VppE by the capacitive coupling between the word lines and the well regions. Likewise, the potentials of all select gate lines in all blocks rise from the initial potential Va to VppE or a potential close to VppE by the capacitive coupling between the select gate lines and the well regions.

[0047] Accordingly, in the memory cells in the unselected blocks, a high voltage sufficient for data erase is not applied between the control gate electrodes and the well regions. That is, since electrons within the floating gate electrodes do not move, the threshold voltages of the memory cells have no change (the present state is maintained).

[0048] Read Operation

[0049] Data read is carried out by changing the potentials of bit lines according to memory cell data and by detecting the potential change.

[0050] First, a bit line (or part of bit lines if all bit lines or a bit line shield read method or the like is adopted) to which a memory cell which data is to be read is connected, is precharged, the potential of the bit line is set at a precharge potential, e.g., the power supply potential Vcc and the bit line is then turned into a floating state.

[0051] Thereafter, the potential of the selected word line, i.e., the potential of the control gate electrode of the selected memory cell is set at 0V, those of unselected word lines (or the control gates of unselected memory cells) and of the select gate lines are set at the power supply potential Vcc (e.g., about 3V), and those of the source lines are set at 0V.

[0052] At this time, if selected memory cell data is "1" (the threshold voltage Vth of the memory cell satisfies Vth>0), the selected memory cell is turned off and the potential of the bit line to which this memory cell is connected is, therefore, kept a precharge potential. (e.g., the power supply potential Vcc).

[0053] On the other hand, if the selected memory cell data is "0" (the threshold potential Vth of the memory cell satisfies Vth<0), the selected memory cell is turned on. As a result, the charges of the bit line to which the selected memory cell is connected are discharged and the potential of the bit line decreases from the precharge potential by  $\Delta V$ .

[0054] In this way, the potential of the bit line changes according to the memory cell data. Thus, if this change is detected by a sense amplifier circuit, the memory cell data can be read.

[0055] Meanwhile, so-called multi-level NAND cell type EEPROMs have been developed and put to practical use with a view of increasing one-chip memory capacity and reducing cost per bit.

[0056] In case of the above-stated NAND cell type EEPROM, binary (one-bit) data ("0", "1") can be stored in a memory cell. An n-level NAND cell type EEPROM, where n is a natural number of not lower than 3 is, by contrast, characterized in that n-level data can be stored in a memory cell.

[0057] In case of an four-level NAND cell type EEPROM, for example, four-level (2-bit) data ("00", "01", "10", "11") can be stored in a memory cell.

[0058] The prior art multi-level NAND cell type EEPROM is described in, for example, Reference 1 (Japanese Patent Application No. 8-98627).

[0059] Normally, in the n-level NAND cell type EEPROM, a plurality of latch circuits are provided per bit line connected to a selected memory cell. Namely, if n-level data are programmed into or read from a selected memory cell, the plural latch circuits function to temporarily store the n-level data.

[0060] As described in Reference 1, for example, in the four-level NAND cell type EEPROM, two latch circuits corresponding to one bit line connected to a selected memory cell are provided so as to temporarily store four-level (two-bit) data during program or read operation.

[0061] However, as shown, for example, in FIG. 7, each latch circuit consists of SRAM (static RAM) cells. Further, the latch circuit consisting of the SRAM cells is large in area. In addition, if the quantity of data stored in one memory cell increases (the value of n is higher), the number of latch circuits provided per bit line connected to the selected memory cell increases, as well.

**[0062]** In case of the four  $(=2^2)$ -level NAND cell type EEPROM, for example, two latch-circuits are provided per bit line connected to a selected memory cell. In an eight  $(=2^3)$ -level NAND cell type EEPROM, three latch circuits are provided per bit line connected to a selected memory cell.

[0063] Accordingly, if data stored in the memory cell are multi-level (n-level) data and the number of n increases, the number of latch circuits (SRAM cells) on a memory chip increases and the area of the chip disadvantageously increases.

## BRIEF SUMMARY OF THE INVENTION

[0064] The present invention has been made to solve the above-stated disadvantages. It is, therefore, an object of the present invention to provide a data circuit (a storage circuit temporarily storing multi-level data during program/read operations) which can prevent a chip area from extremely increasing even if data stored in a memory cell is multi-level data

[0065] A nonvolatile semiconductor memory according to the present invention comprises a memory cell section including at least one memory cell; a bit line connected to the memory cell section; and a data circuit connected to the bit line, the data circuit storing program/read data having two bits or more, wherein the data circuit includes the first capacitor storing the first data and the first latch circuit storing the second data.

[0066] Additional objects and advantages of the invention will be set forth in the description which follows, and in part will be obvious from the description, or may be learned by practice of the invention. The objects and advantages of the invention may be realized and obtained by means of the instrumentalities and combinations particularly pointed out hereinafter.

## BRIEF DESCRIPTION OF THE SEVERAL VIEWS OF THE DRAWING

[0067] The accompanying drawings, which are incorporated in and constitute a part of the specification, illustrate presently preferred embodiments of the invention, and together with the general description given above and the detailed description of the preferred embodiments given below, serve to explain the principles of the invention.

[0068] FIG. 1 is a circuit diagram showing the memory cell array of an NAND cell type EEPROM;

[0069] FIG. 2 is a plan view showing the device structure of an NAND cell unit;

[0070] FIG. 3 is a cross-sectional view taken along line III-III of FIG. 2;

[0071] FIG. 4 is a cross-sectional view taken along line IV-IV of FIG. 2;

[0072] FIG. 5 shows an equivalent circuit of the NAND cell unit shown in FIG. 2;

[0073] FIG. 6 shows the well structure of the NAND cell type EEPROM;

[0074] FIG. 7 shows a conventional data circuit;

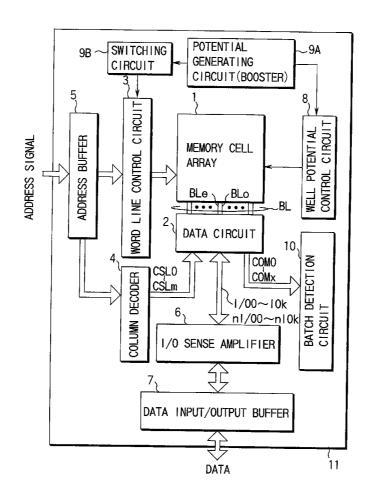

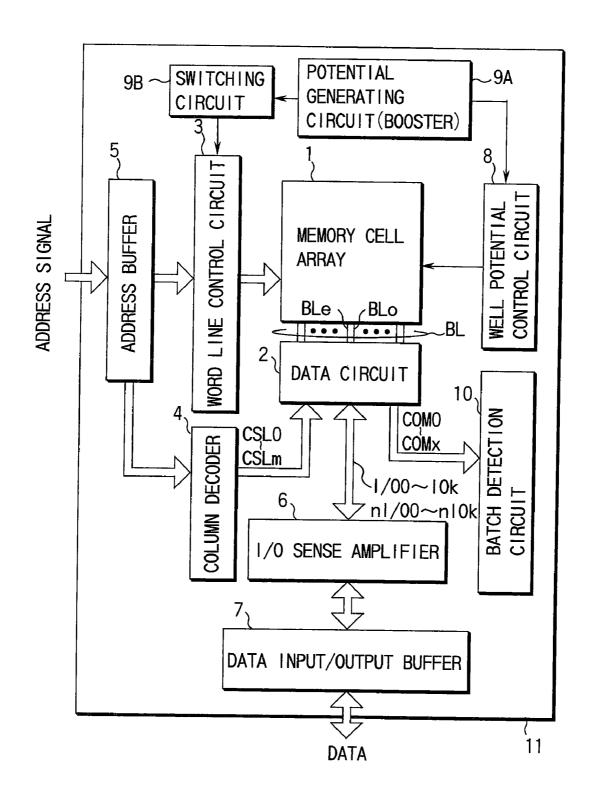

[0075] FIG. 8 shows the outline of a multi-level NAND cell type EEPROM according to the present invention;

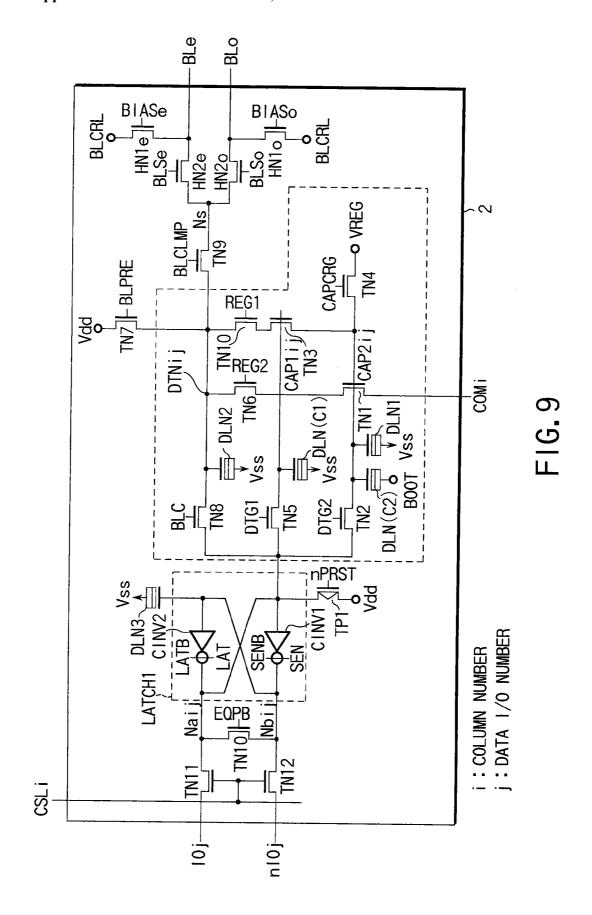

[0076] FIG. 9 shows a data circuit in the memory shown in FIG. 8:

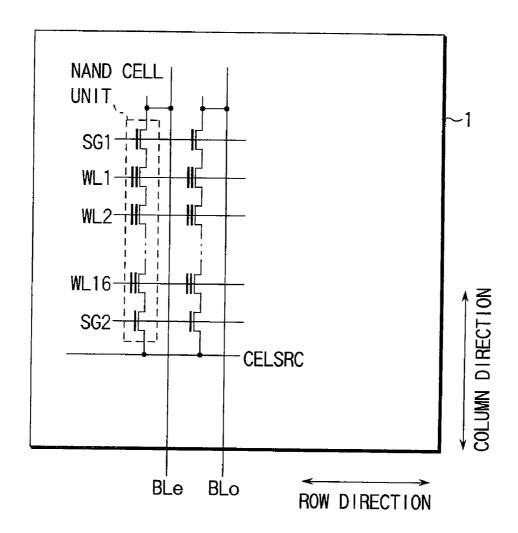

[0077] FIG. 10 shows a memory cell array in the memory shown in FIG. 8;

[0078] FIG. 11 shows a part of a column decoder in the memory shown in FIG. 8;

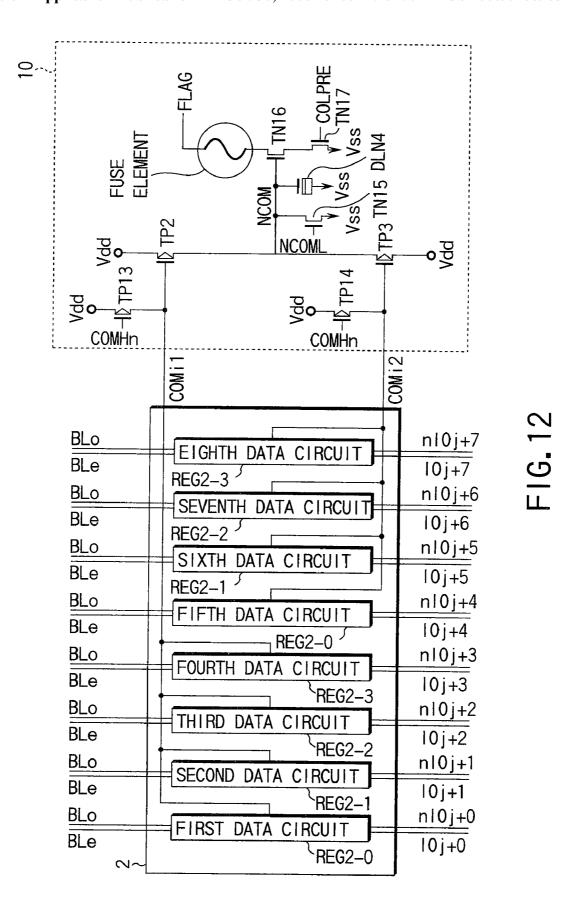

[0079] FIG. 12 shows a batch detection circuit in the memory shown in FIG. 8;

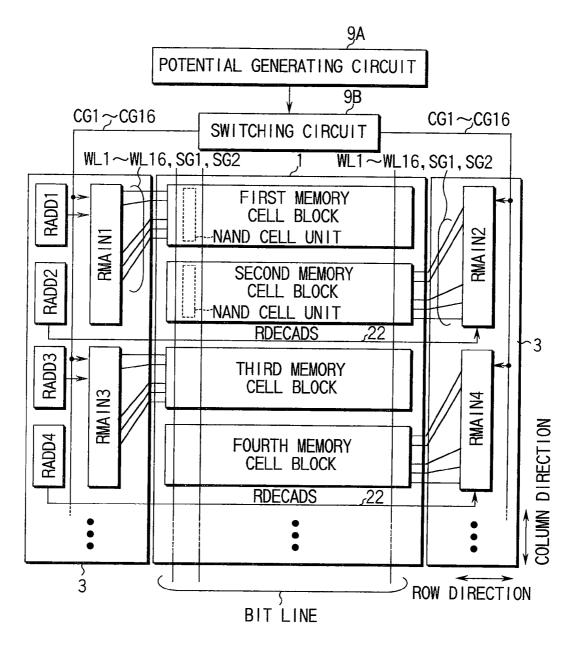

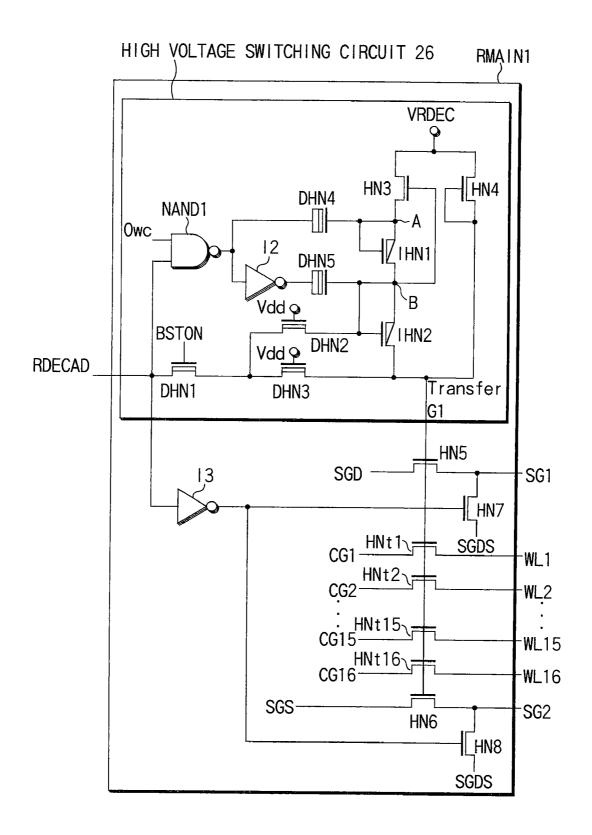

[0080] FIG. 13 shows a word line control circuit in the memory shown in FIG. 8;

[0081] FIG. 14 shows a device structure in the first memory cell block shown in FIG. 13;

[0082] FIG. 15 shows a device structure in the second memory cell block shown in FIG. 13;

[0083] FIG. 16 shows a row address decoder RADD1 shown in FIG. 13;

[0084] FIG. 17 shows a word line driver RMAIN1 shown in FIG. 13;

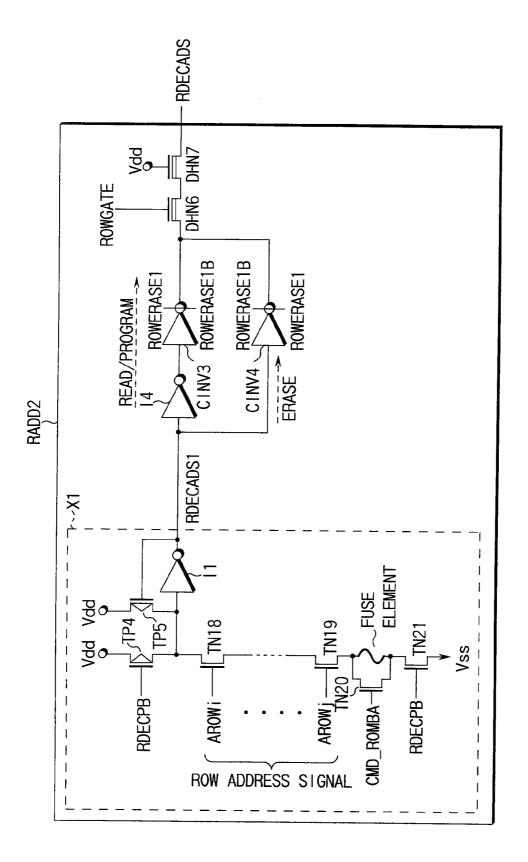

[0085] FIG. 18 shows a row address decoder RADD2 shown in FIG. 13;

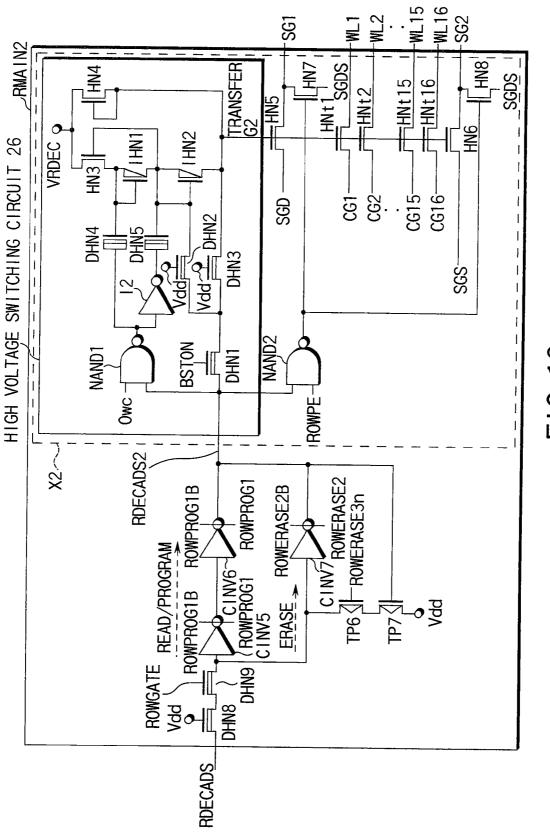

[0086] FIG. 19 shows a word line driver RMAIN2 shown in FIG. 13;

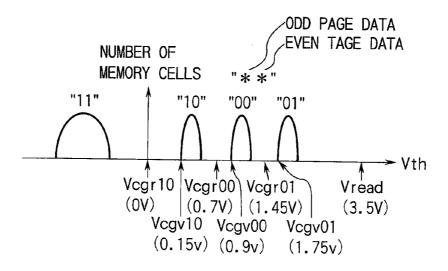

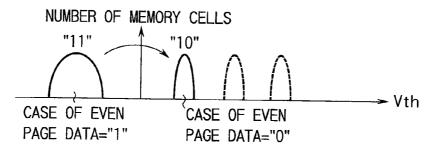

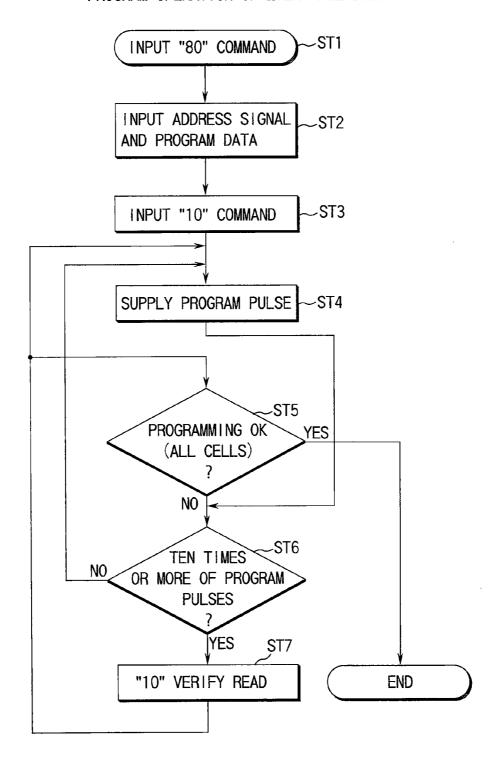

[0087] FIG. 20 shows the relationship between four-level data and the threshold voltages of memory cells;

[0088] FIG. 21 shows the threshold voltage distribution of memory cells after programming even page data;

[0089] FIG. 22 shows the threshold voltage distribution of memory cells after programming odd page data;

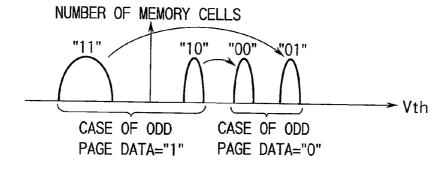

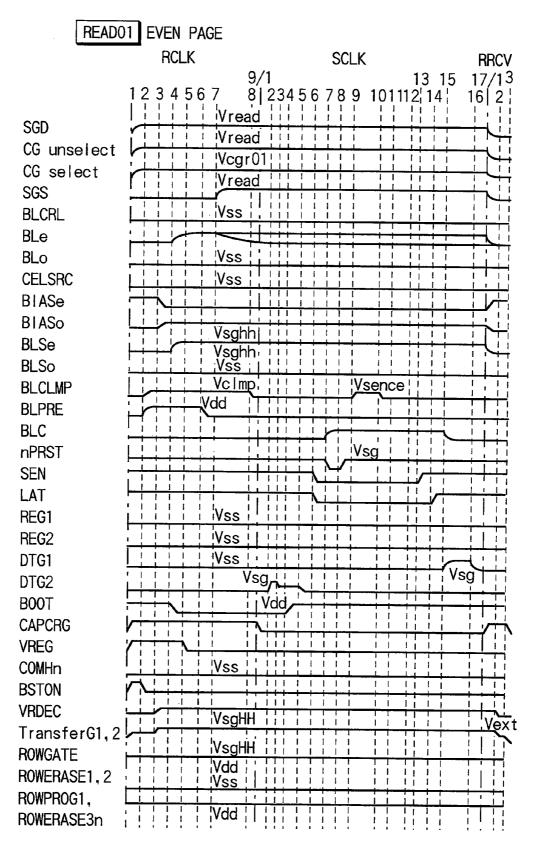

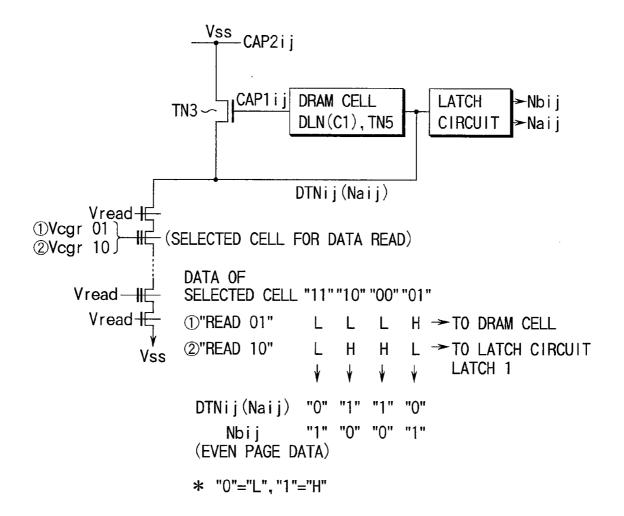

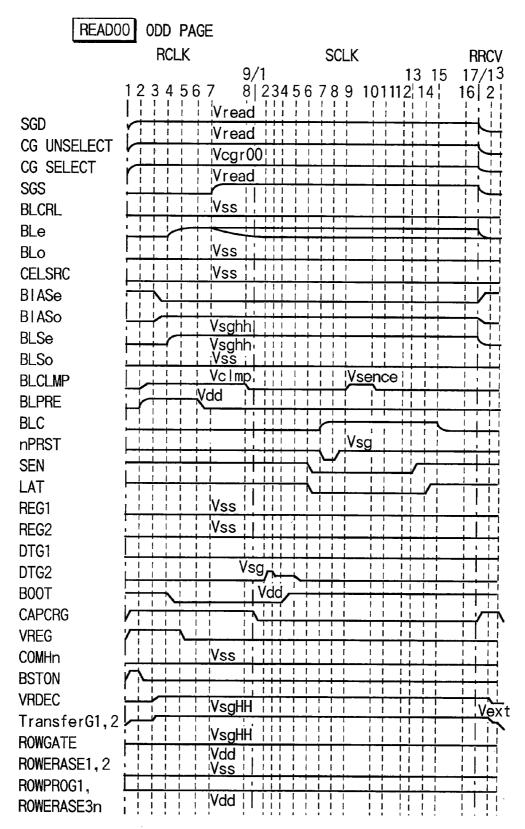

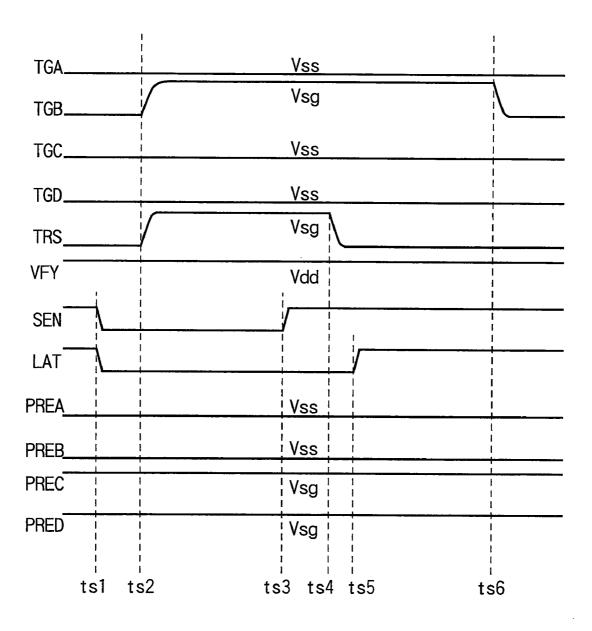

[0090] FIG. 23 is a waveform view showing operation timing relating to the read of even page data;

[0091] FIG. 24 is a waveform view showing operation timing relating to the read of even page data;

[0092] FIG. 25 shows the outline of read operation to even page data; [0093] FIG. 26 is a waveform view showing operation tim-

ing relating to the read of odd page data;

[0094] FIG. 27 shows the outline of read operation to odd page data;

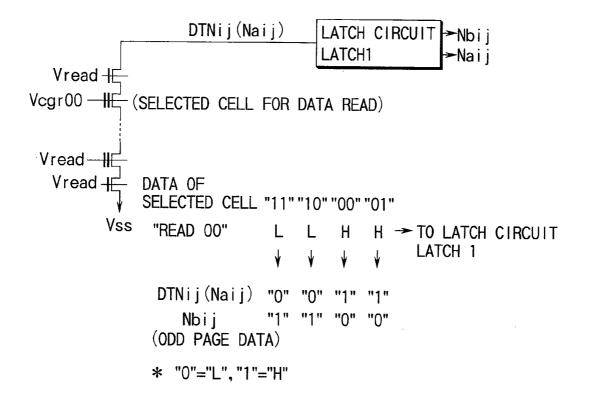

[0095] FIG. 28 is a flow chart showing even page data program operation;

[0096] FIG. 29 is a waveform view showing operation timing relating to the supply of a program pulse during program operation;

[0097] FIG. 30 shows the outline of the supply of a program pulse during the program operation;

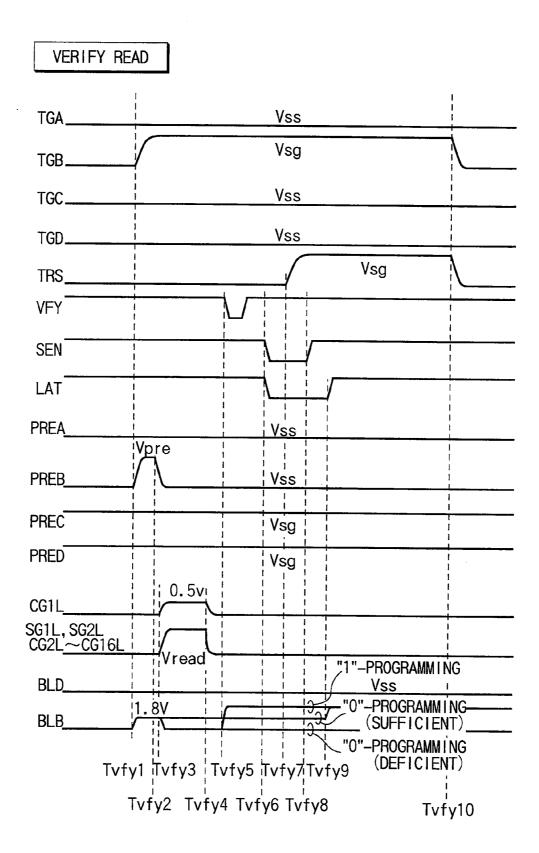

[0098] FIG. 31 is a waveform view showing operation timing relating to "10" verify read during the program operation; [0099] FIG. 32 shows the outline of "10" verify read during the program operation;

[0100] FIG. 33 is a waveform view showing operation timing relating to "Program completion detection" during the program operation;

[0101] FIG. 34 shows the outline of "Program completion detection" during the program operation;

[0102] FIG. 35 is a flow chart showing odd page data program operation;

[0103] FIG. 36 is a waveform view showing operation timing relating to "Internal Data Load 1st/3rd Quarters" during the program operation:

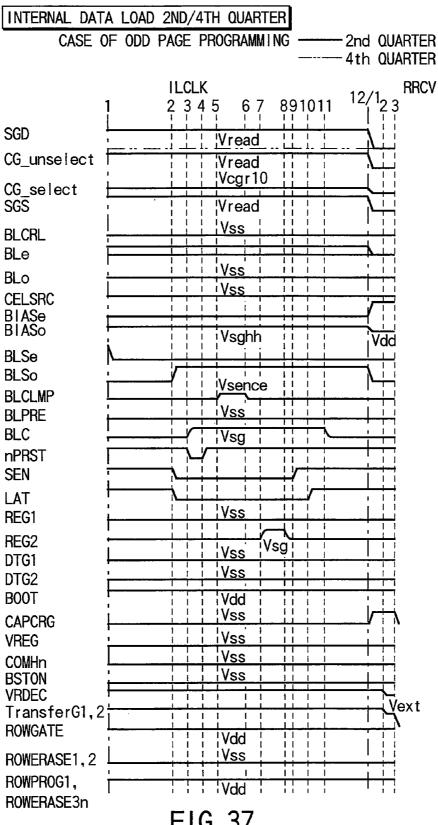

[0104] FIG. 37 is a waveform view showing operation timing relating to "Internal Data Load 2nd/4th Quarters" during the program operation;

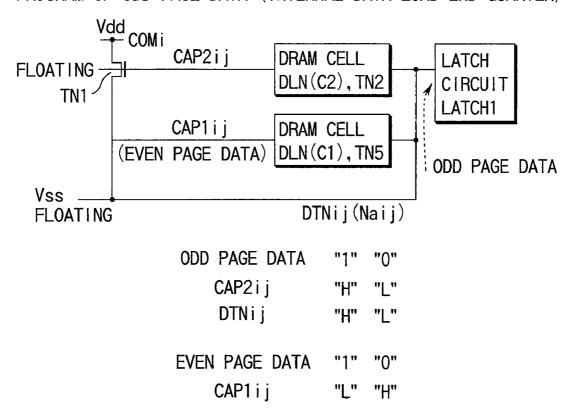

[0105] FIG. 38 shows the outline of "Internal Data Load 1st Quarter" during the program operation;

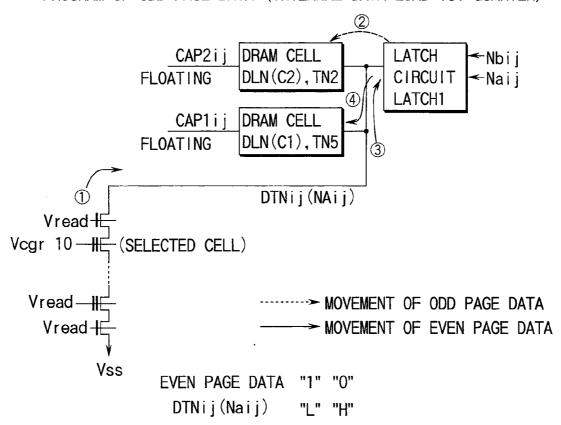

[0106] FIG. 39 shows the outline of "Internal Data Load 2nd Quarter" during the program operation;

[0107] FIG. 40 shows the outline of "Internal Data Load 3rd Quarter" during the program operation;

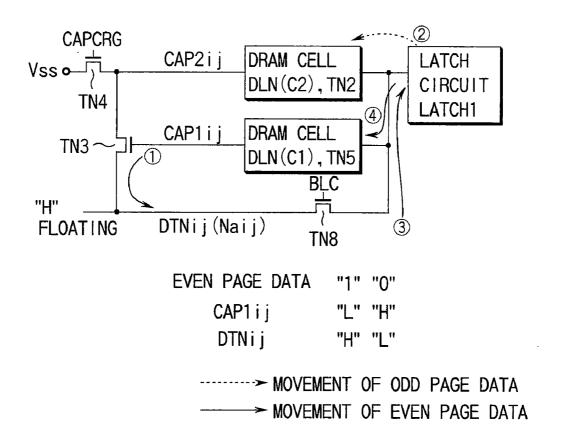

[0108] FIG. 41 shows the outline of "Internal Data Load 4th Quarter" during the program operation;

[0109] FIG. 42 is a waveform view showing operation timing relating to "01" verify read during the program operation; [0110] FIG. 43 shows the outline of "01" verify read during the program operation;

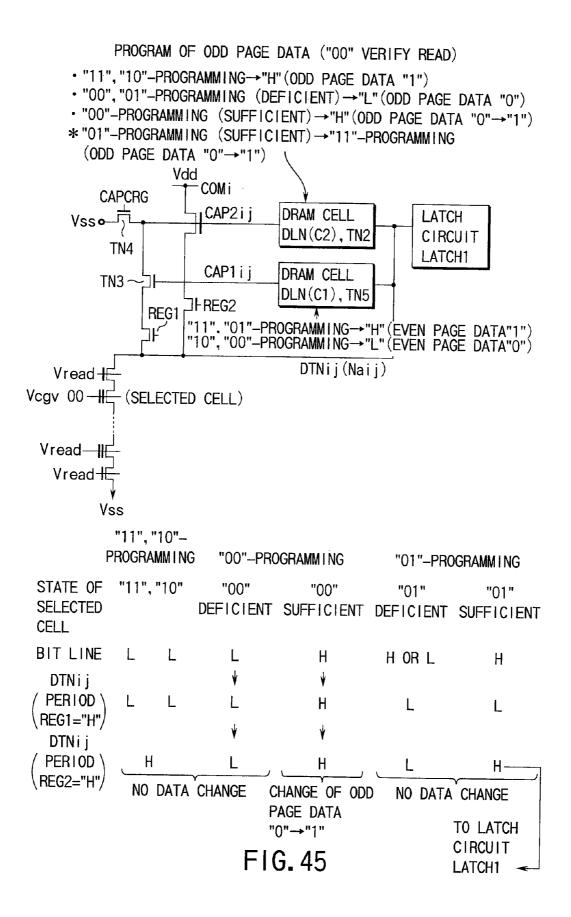

[0111] FIG. 44 is a waveform view showing operation timing relating to "00" verify read during the program operation; [0112] FIG. 45 shows the outline of "00" verify read during the program operation;

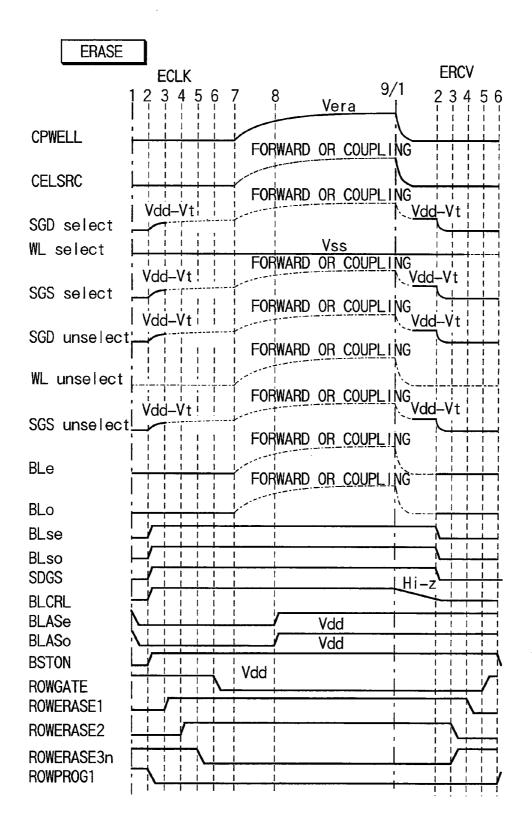

[0113] FIG. 46 is a waveform view showing operation timing relating to the supply of an erase pulse during erase operation;

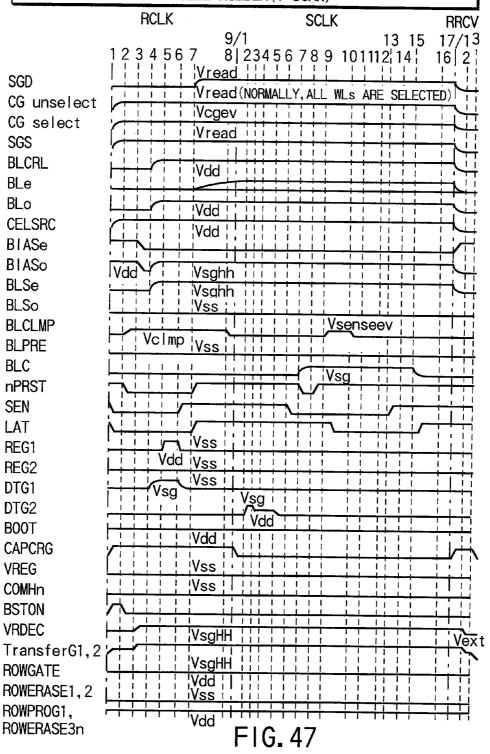

[0114] FIG. 47 is a waveform view showing operation timing relating to erase verify read during the erase operation;

[0115] FIG. 48 is a waveform view showing operation timing relating to "Erase completion detection" during the erase operation;

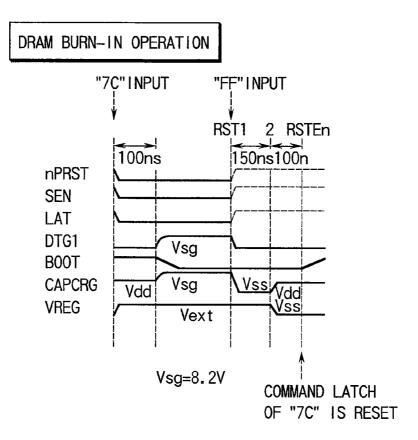

[0116] FIG. 49 is a waveform view showing operation timing relating to "DRAM Burn-in";

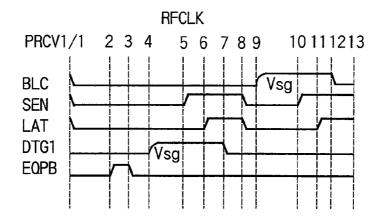

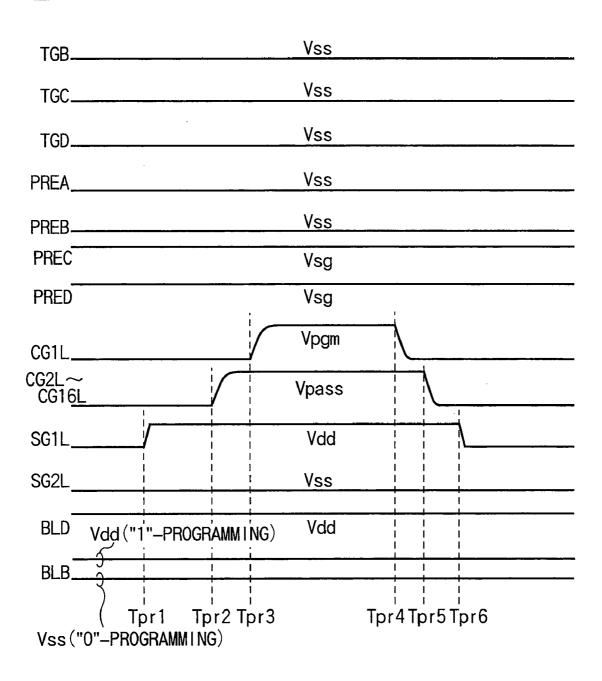

[0117] FIG. 50 is a waveform view showing operation timing relating to the refresh of a DRAM cell;

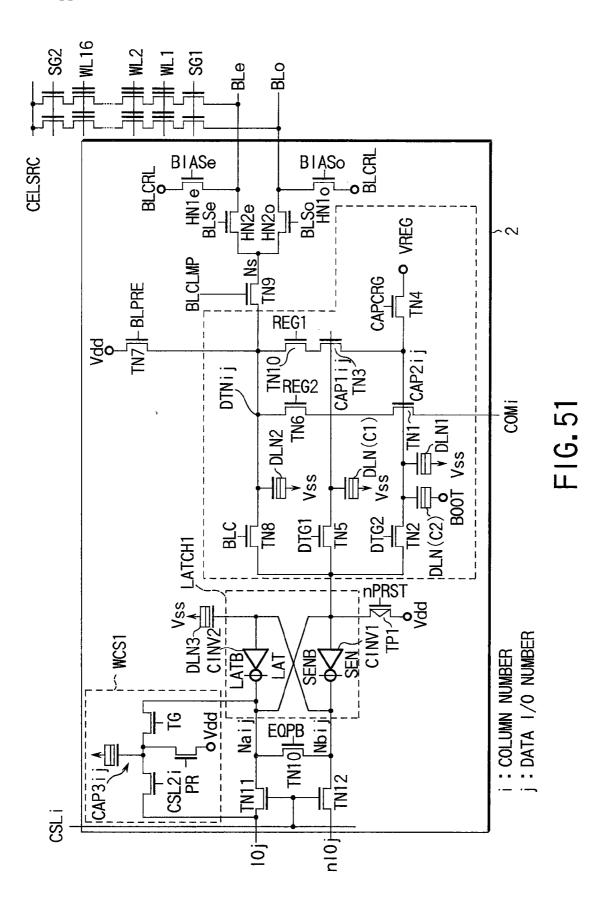

[0118] FIG. 51 shows a modification of the data circuit shown in FIG. 9;

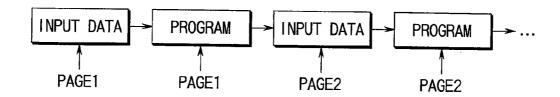

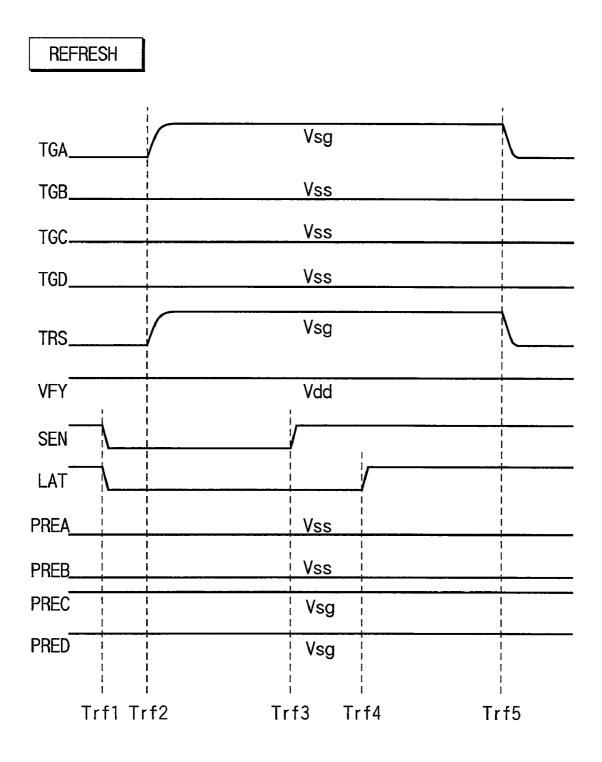

[0119] FIG. 52 shows an ordinary program sequence for a plurality of pages;

[0120] FIG. 53 is a program sequence for a plurality of pages if the data circuit shown in FIG. 51 is used;

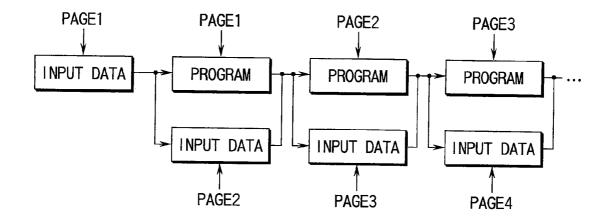

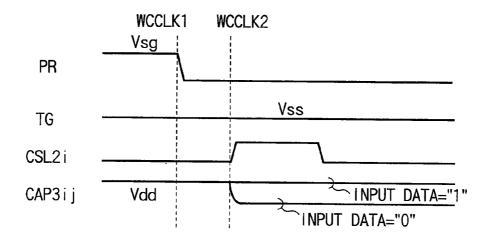

[0121] FIG. 54 is a waveform view showing operation timing for data input into a write cache in the data circuit shown in FIG. 51;

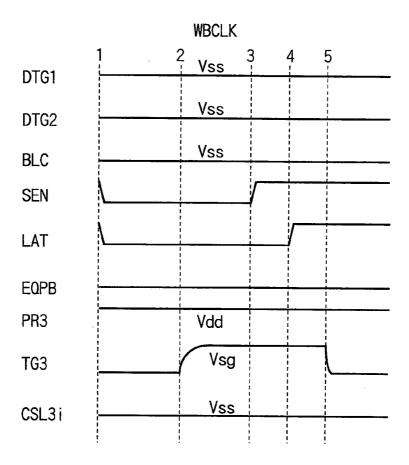

[0122] FIG. 55 is a waveform view showing operation timing for data transfer from the write cache to the latch circuit shown in FIG. 51;

[0123] FIG. 56 is a waveform view showing operation timing relating to the refresh of data in the write cache in the data circuit shown in FIG. 51;

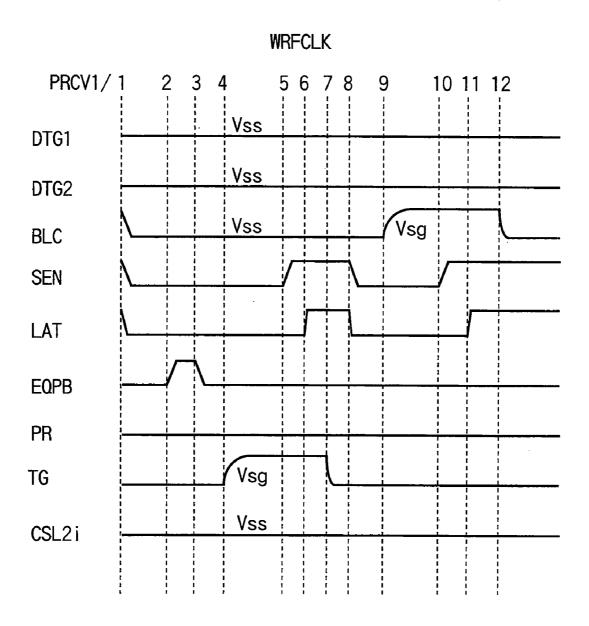

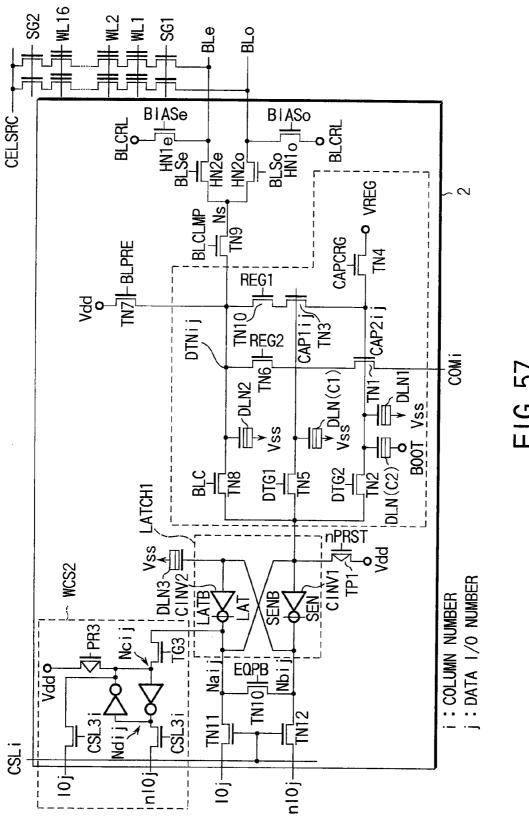

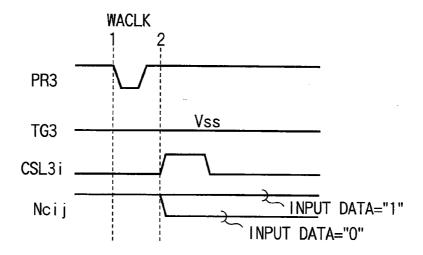

[0124] FIG. 57 shows a modification of the data circuit shown in FIG. 9;

[0125] FIG. 58 is a waveform view showing operation timing for data input into a write cache in the data circuit shown in FIG. 57;

[0126] FIG. 59 is a waveform view showing operation timing for data transfer from the write cache to the latch circuit shown in FIG. 57;

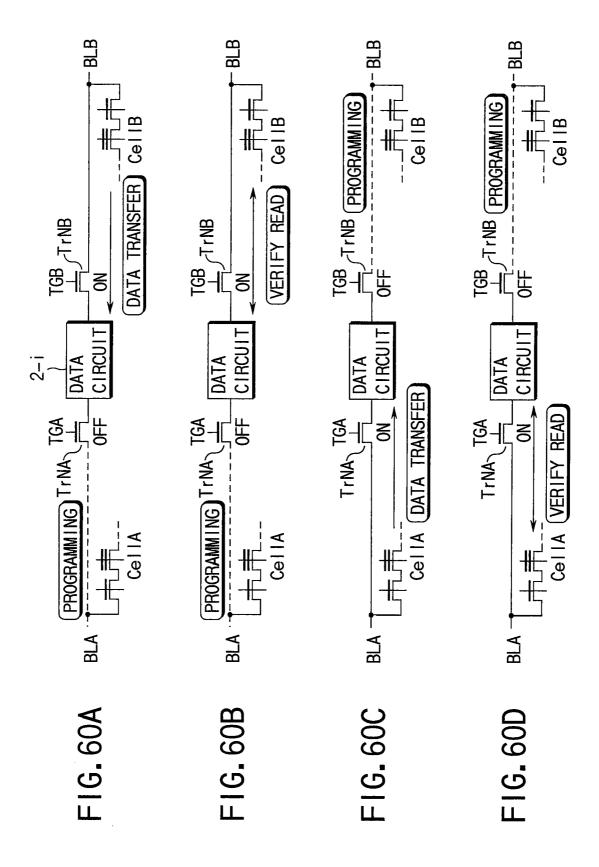

[0127] FIGS. 60A to 60D show the gist of the present invention (Concrete Example 1) relating to program speed;

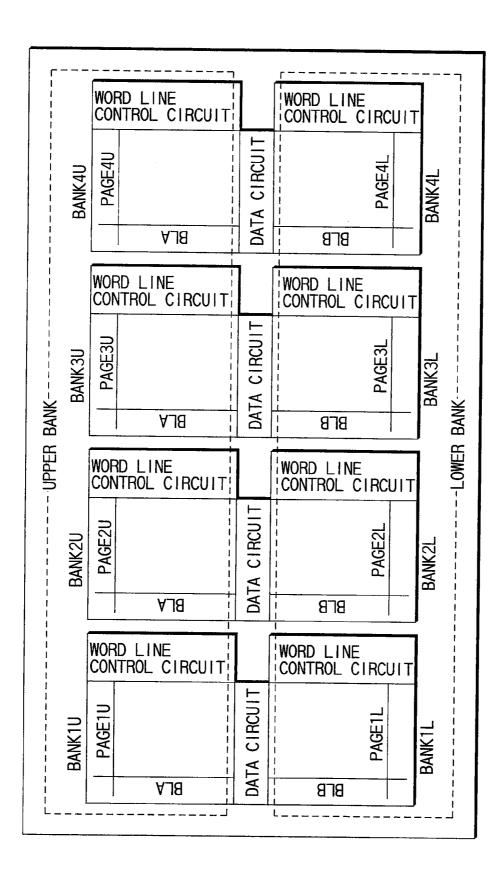

[0128] FIG. 61 shows the chip layout of a two-level NAND cell type EEPROM according to the present invention;

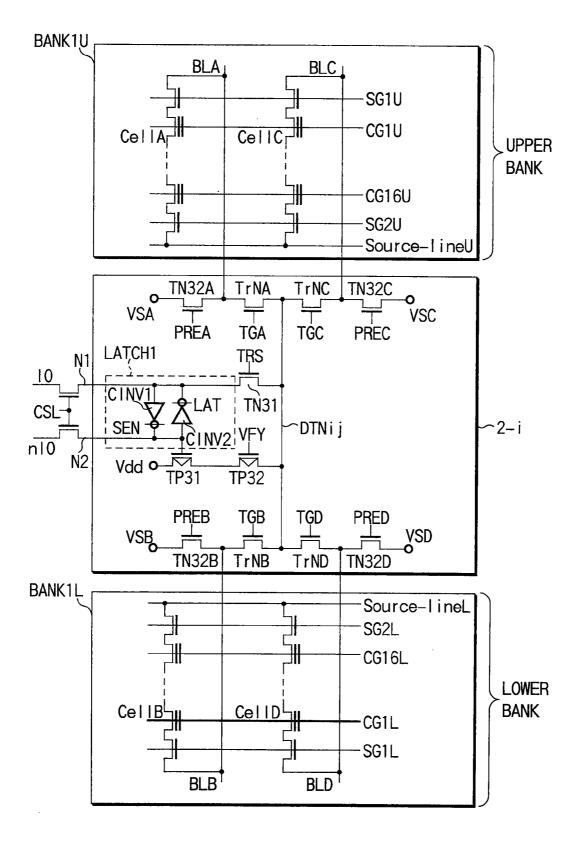

[0129] FIG. 62 shows one example of a data circuit in the memory shown in FIG. 61;

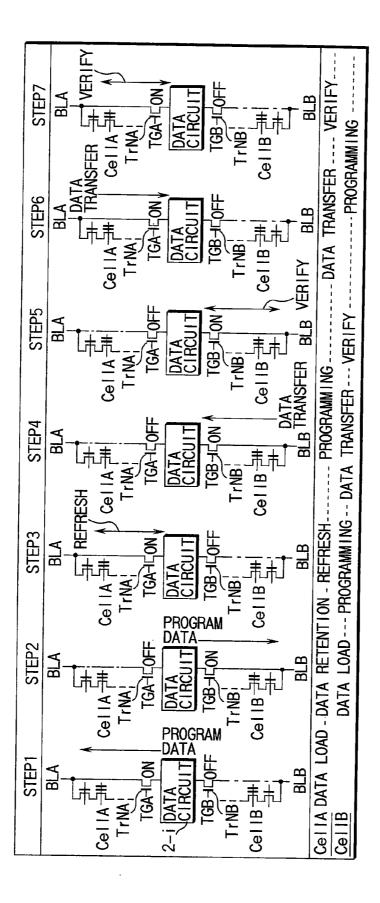

[0130] FIG. 63 shows the detail of the operation of the present invention relating to Data Load;

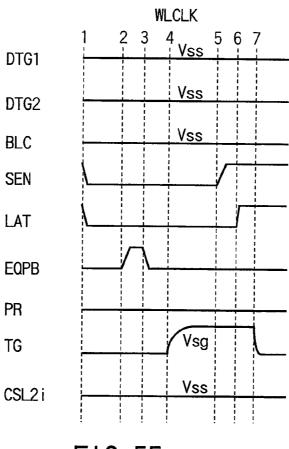

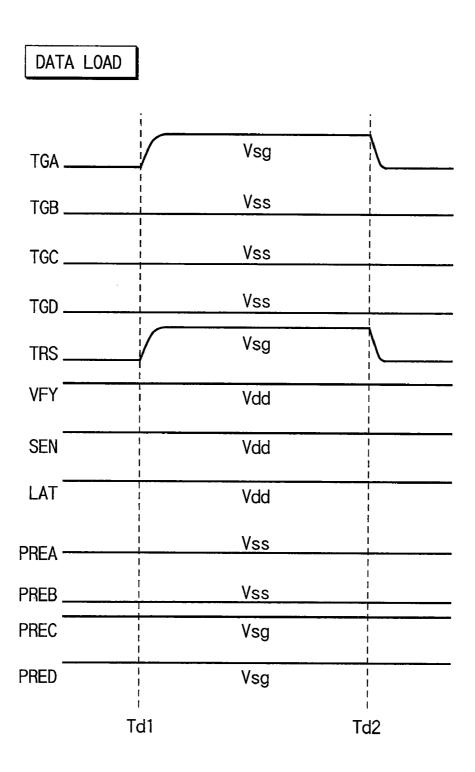

[0131] FIG. 64 is a waveform view showing operation timing relating to Data Load;

[0132] FIG. 65 is a waveform view showing operation timing relating to Data Load;

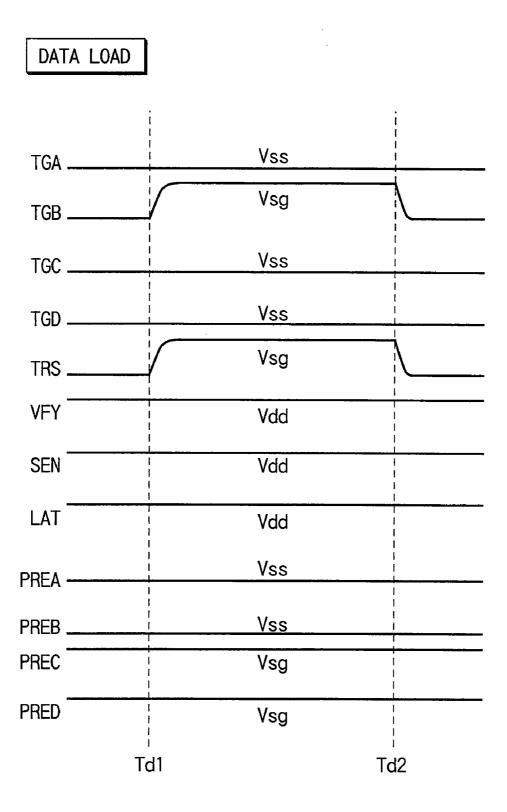

[0133] FIG. 66 is a waveform view showing operation timing relating to the supply of a program pulse;

[0134] FIG. 67 is a waveform view showing operation timing relating to refresh;

[0135] FIG. 68 is a waveform view showing operation timing relating to the supply of a program pulse;

[0136] FIG. 69 is a waveform view showing operation timing relating to program data transfer;

[0137] FIG. 70 is a waveform view showing operation timing relating to verify read;

[0138] FIG. 71 is a waveform view showing operation timing relating to the supply of a program pulse;

[0139] FIG. 72 is a waveform view showing operation timing relating to program data transfer;

[0140] FIG. 73 is a waveform view showing operation timing relating to verify read;

[0141] FIG. 74 shows the gist of the present invention (Concrete Example 2) relating to program speed;

[0142] FIG. 75 shows the detail of the operation of the present invention relating to program speed;

[0143] FIG. 76 shows the detail of the operation of the present invention relating to program speed;

[0144] FIG. 77 shows the detail of the operation of the present invention relating to program speed; and

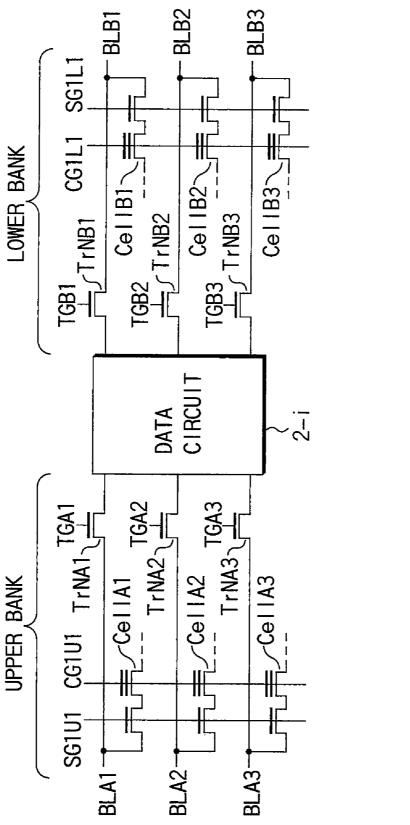

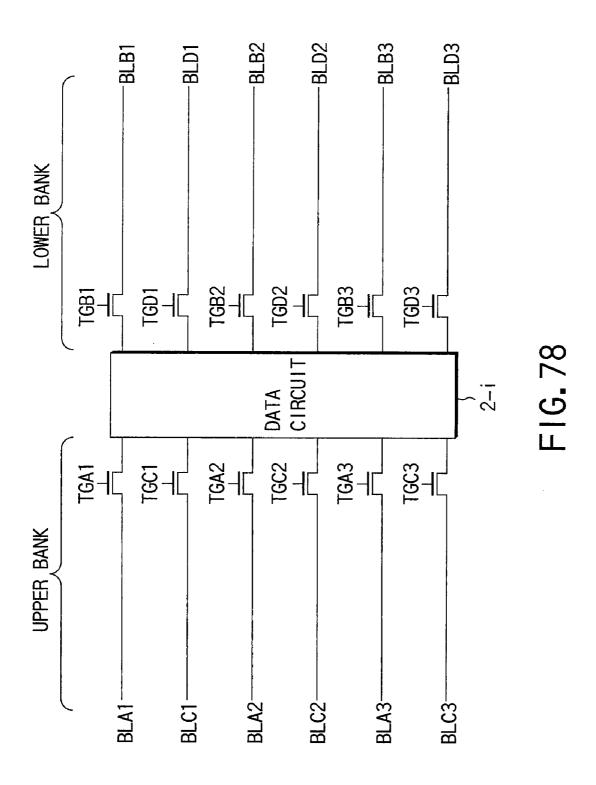

[0145] FIG. 78 shows a modification of the present invention (Concrete Example 2) relating to program speed.

## DETAILED DESCRIPTION OF THE INVENTION

[0146] A nonvolatile semiconductor memory of the present invention will be described below in detail with reference to the accompanying drawings.

[0147] [Preconditions]

[0148] First, to facilitate understanding the description to be given below, preconditions will be specified as follows. It is noted that these preconditions are intended to facilitate understanding the description only and that the present invention is realized on conditions other than these preconditions.

**[0149]** The present invention is directed to a nonvolatile semiconductor memory for storing n-level data, where n is a natural number of not lower than 3. In the following embodiments, a four-level NAND cell type EEPROM will be described to represent such nonvolatile semiconductor memories.

[0150] It is assumed that four-level data, "00", "01", "10" and "11", are stored in a memory cell. It is also assumed that a state in which the threshold voltage of the memory cell is the lowest (e.g., a threshold voltage is negative) is data "11" (or a "0" state), a state in which the threshold voltage of the memory cell is the second lowest (e.g., the threshold voltage is positive) is data "10" (or a "1" state), a state in which the threshold voltage of the memory cell is the third lowest (e.g., the threshold voltage is positive) is data "00" (or a "2" state),

and a state in which the threshold voltage of the memory cell is the highest (e.g., the threshold voltage is positive) is data "01" (or a "3" state).

[0151] In addition, since it is assumed that four-level data are stored in a memory cell, odd page data program/read operations and even page data program/read operations are required. Here, among data "\*\*", it is assumed that the left "\*" is odd page data and the right "\*" is even page data.

[0152] Further, as for the state of a memory cell, it is assumed that a state in which data "11" is stored is an erase state, and states in which data "10", "00", and "01" are stored are program states.

[0153] [Outline]

[0154] FIG. 8 is a block diagram showing the important parts of a four-level NAND cell type EEPROM according to the present invention.

[0155] Reference symbol 1 denotes a memory cell array. The memory cell array 1 has a plurality of memory cells connected in series and two select transistors connected to both ends of the memory cells, respectively. The concrete structure of the memory cell is shown in FIGS. 61 to 63.

[0156] The structure and equivalent circuit of the memory cell array 1 are almost the same as those of a two-level NAND cell type EEPROM except that each memory cell stores four-level data in the four-level NAND cell type EEPROM.

[0157] A data circuit 2 includes a plurality of storage circuits. The data circuit 2 will be described in detail later. The function of the data circuit will be described herein briefly.

[0158] The data circuit 2 includes storage circuits temporarily storing two-bit (four-level) read data during read operation. To be specific, two storage circuits per bit line connected to a selected memory cell are provided.

[0159] One of the two storage circuits temporarily stores odd page data. The other storage circuit temporarily stores even page data. The odd/even page data stored in these two storage circuits are programmed into the memory cell during program operation and outputted from a memory chip 11 during read operation.

[0160] A word line control circuit 3 includes a low address decoder and a word line driver. The word line control circuit 3 controls the potential of each word line in the memory cell array 1 based on an operation mode (a program mode, an erase mode, a read mode or the like) and a row address signal. The word line control circuit 3 will be described later in detail.

[0161] A column decoder 4 selects a column of the memory cell array 1 based on a column address signal.

[0162] During program operation, input data is inputted into storage circuits in the data circuit which storage circuits belong to the selected column, through a data input/output buffer 7 and an I/O sense amplifier 6. During read operation, output data from the storage circuits in the data circuit which storage circuits belong to the selected column is outputted externally of the memory chip 11 through the I/O sense amplifier 6 and the data input/output buffer 7.

[0163] The row address signal is inputted into the word line control circuit 3 through an address buffer 5. The column address signal is inputted into the column decoder 4 through the address buffer 5.

[0164] A well potential control circuit 8 controls the potential of a cell well region (e.g., a double-well region consisting of an n well and a p well) in which memory cells are arranged based on an operation mode (a program mode, an erase mode, a read mode or the like).

[0165] A potential generating circuit (booster) 9A generates, for example, a program potential Vpp (e.g., about 20V) and a transfer potential Vpass (e.g., about 10V) during the program operation. These potentials Vpp and Vpass are allotted to a plurality of word lines in, for example, a selected block by a switching circuit 9B.

**[0166]** The potential generating circuit **9**A also generates, for example, an erase potential VppE (e.g., about 20V) during the erase operation and applies the potential VppE to the cell well region (both the n well and the p well) in which the memory cells are arranged.

[0167] A batch detection circuit 10 verifies whether or not predetermined data has been correctly programmed into a memory cell during the program operation, and also verifies whether or not the memory cell data has been successfully erased during the erase operation.

[0168] The first feature of the present invention lies in the data circuit 2. Namely, as will be described in detail, at least one of a plurality of storage circuits arranged in the data circuit and used to temporarily store multi-level data (n-level data), is constituted by a DRAM cell (capacitor). If two storage circuits are used to temporarily store four-level data in, for example, the four-level NAND type EEPROM, one of the storage circuits is an SRAM cell (latch circuit) and the other is a DRAM cell.

[0169] As is well known, the area of the DRAM (dynamic RAM) cell is smaller than the area of the SRAM (static RAM) cell. Due to this, in consideration of the n-level NAND cell type EEPROM, where n is a natural number of not lower than 3, if part of the plural storage circuits is constituted by a DRAM cell, it is possible to decrease the area of the data circuit 2 compared with a case of constituting all storage circuits only out of SRAM cells as shown in a conventional semiconductor memory.

[0170] The second feature of the present invention lies in the word line control circuit 3. Namely, as will be described later in detail, the word line control circuit 3 consists of a row address decoder and a word line driver. The word line control circuit 2 adopts a layout in which the row address decoder is arranged only at one side of the memory cell array 1 and the word line drivers are arranged at both sides of the memory cell array 1, respectively.

[0171] In this case, a signal line for connecting the row address decoder at one side of the memory cell array 1 to the word line driver at the other side thereof, is arranged on the memory cell array 1. The present invention improves the word line control circuit 3 so as to minimize the adverse effect of this signal line on the operations of memory cells.

[0172] The third feature of the present invention lies in the read operation. Namely, according to the present invention, the relationship between four-level data and the threshold voltages of memory cells is set as shown in, for example, FIG. 20 (which detail will be described later).

[0173] In that case, even page data is read by two read operations ("READ01" and "READ00") and odd page data is read by one read operation ("READ00"). That is, a total of three read operations allow reading the four-level data, thereby making it possible to shorten read time (or accelerate data read).

[0174] The fourth feature of the present invention lies in the program operation (particularly, verification operation). Namely, according to the present invention, the relationship

between four-level data and the threshold voltages of memory cells is set as shown in, for example, FIG. 20 (which detail will be described later).

[0175] In that case, during the program operation of even page data, "11" and "10" are programmed into memory cells. Then, during the program operation of odd page data, when odd page data is "0", the "11" state is changed to the "01" state and the "10" state is changed to the "00" state. Here, the change amount of the threshold voltages in case of changing the "11" state to the "01" state is larger than the change amount of threshold voltages in case of changing the "10" state to the "00" state.

[0176] It is quite natural, therefore, that the "00"-programming is completed earlier than the "01"-programming. Thus, after completing the "00"-programming, "00" verify-read may be omitted and only "01" verify-read may be carried out. By doing so, it is possible to shorten program time (accelerate programming) for four-level data programming.

[0177] The fifth feature of the present invention lies in the fact that refresh operation is carried out to the DRAM cell (capacitor) provided instead of a latch circuit in the data circuit 2 during, for example, the program operation. Namely, according to the present invention, as shown in the first feature stated above, at least one of a plurality of storage circuits used to temporarily store multi-level data (n-level data) is changed to a DRAM cell (capacitor).

[0178] In this case, the area of the data circuit can be advantageously reduced. However, the charges of the capacitor gradually decrease due to leakage thereof. If the change of data due to leakage causes a disadvantage, refresh operation is required. In other words, during the program operation, a refresh sequence for the DRAM cell in the data circuit 2 needs to be added to an ordinary program sequence.

[0179] The sixth feature of the present invention lies in the fact that a write cache is provided in the data circuit. In this case, if a program operation is executed over a plurality of pages, for example, it is possible to execute the program operation (the supply of a program pulse) and to input program data in parallel. This can dispense with data load time for loading data on page 2 and the following pages, thereby making it possible to accelerate the program operation.

[0180] The seventh feature of the present invention lies in the fact that refresh operation is carried out to a DRAM cell if the write cache provided in the data circuit consists of the DRAM cell (capacitor) and the change of data due to leakage causes a disadvantage.

[0181] The four-level NAND cell type EEPROM according to the present invention as well as the first to second features stated above will be described hereinafter in detail.

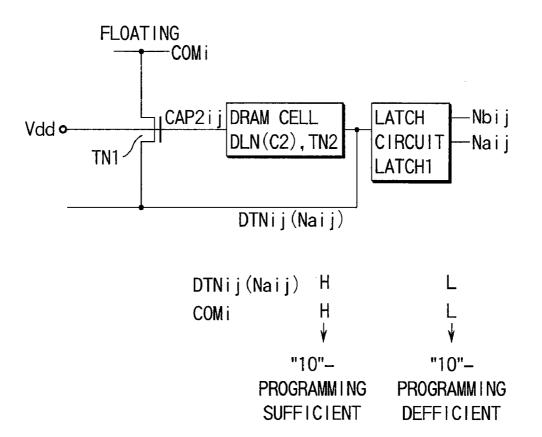

[0182] [Data Circuit] . . . First Feature

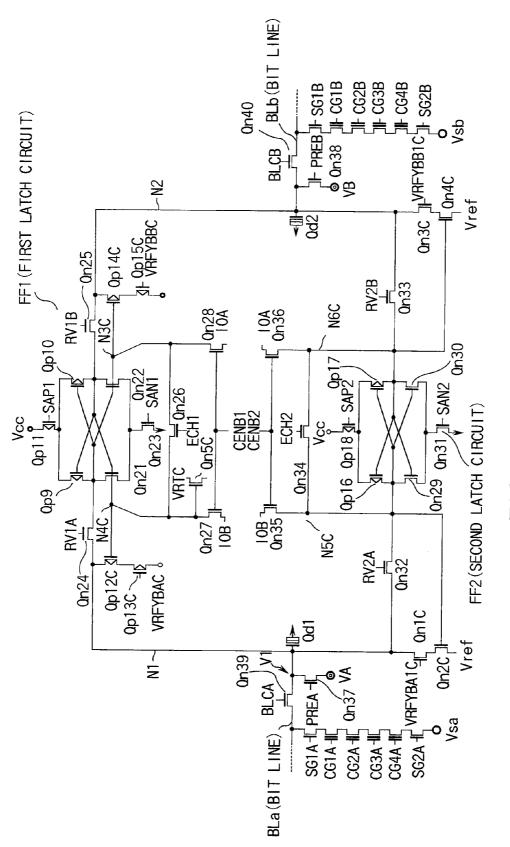

[0183] FIG. 9 shows one example of the data circuit 2 shown in FIG. 8. FIG. 10 shows part of the memory cell array 1 shown in FIG. 9.

[0184] This example shows the data circuit for one column. Actually, one data circuit is provided, for example, for each of a plurality of columns of the memory cell array 1. That is, the data circuit 2 shown in FIG. 8 consists of a plurality of data circuits corresponding to the plural columns of the memory cell array 1.

**[0185]** Further, in this embodiment, two bit lines BLe and BLo are arranged in one column and one data circuit is connected to these two bit lines BLe and BLo. The reasons the two bit lines BLe and BLo are connected to one data circuit are to attain the following objects: (1) to prevent the genera-

tion of noise due to the capacitive coupling between adjacent bit lines during the read operation (to adopt a shield bit line read method); and (2) to intend to reduce the number of data circuits and to thereby decrease the chip area.

[0186] Additionally, in this embodiment, it is assumed that four-level data (two-bit data) are stored in one memory cell. Due to this, two storage circuits are provided in one data circuit so as to temporarily store the four-level data during the program/read operations.

[0187] Reference symbol LATCH1 denotes one of the two storage circuits, i.e., a latch circuit. The latch circuit LATCH1 consists of a flip-flop circuit (SRAM cell) consisting of clocked inverters CINV1 and CINV2. The latch circuit LATCH1 is controlled by control signals SEN, SENB, LAT and LATB.

[0188] It is noted that signal "\*\*\*B" indicates the inversion signal of a signal "\*\*\*". That is, the level of the signal "\*\*\*B" and that of the signal "\*\*\*" are opposite in phase (when one level is "H", the other is "L"). This definition applies to the following description.

[0189] Reference symbol DLN(C1) denotes a capacitor which is the other storage circuit of the two storage circuits. This capacitor CLN(C1) consists of a low voltage depletion N channel MOS transistor (MOS capacitor) applied with a voltage not higher than the power supply voltage Vcc. In this embodiment, an N channel MOS transistor TN5 functions as a gate and data is latched by a node CAP1ij. That is, the latch circuit consists of a DRAM cell consisting of the capacitor DLN(C1) and the MOS transistor TN5.

[0190] In FIG. 9, an MOS transistor to which symbol "HN\*\* (\* is number, symbol or the like) is added is a high voltage enhancement N channel MOS transistors having a threshold voltage of, for embodiment, about 0.6V. A higher voltage than the power supply voltage Vcc is applied to the MOS transistor. This MOS transistor is turned off when gate potential is 0V.

[0191] Also, an MOS transistor to which symbol "DLN\*\*" is added is a low voltage depletion N channel MOS transistor having a threshold voltage of, for example, about -1V and applied with a voltage not higher than the power supply voltage Vcc. In this embodiment, this transistor is used as an MOS capacitor.

[0192] Further, an MOS transistor to which symbol "TN\*\*" is added is a low voltage enhancement N channel MOS transistor having a threshold voltage of, for example, about 0.6V and applied with a voltage not higher than the power supply voltage Vcc. This transistor is turned off when gate potential is 0V.

[0193] In case of the MOS transistors  $\mathrm{HN1}e$ ,  $\mathrm{HN1}o$ ,  $\mathrm{HN2}e$  and  $\mathrm{HN2}o$ , one of the two bit lines BLe and BLo is used as a bit line to which data is read and the other is used as a shield bit line.

[0194] That is, the potential of BLCRL is set at the ground potential Vss. Further, when the level of BIASo is "H" and that of BIASe is "L", data is read to the bit line BLe and the bit line BLo becomes a shield bit line to prevent noise generated when reading the data to the bit line BLe. On the other hand, when the level of BIASe is "H" and that of BIASo is "L", data is read to the bit line BLo and the bit line BLe becomes a shield bit line to prevent noise generated when reading the data to the bit line BLo.

[0195] An MOS transistor TN7 is a bit line precharge MOS transistor to preset one bit line, to which data is read, of the

two bit lines BLe and BLo at, for example, the power supply potential Vcc. The MOS transistor TN7 is controlled by a control signal BLPRE.

[0196] An MOS transistor TN9 is a clamping MOS transistor for controlling electrical connection/disconnection between the bit lines BLe and BLo and the data circuit (important parts thereof). The MOS transistor TN9 functions to precharge the bit lines BLe and BLo during, for example, the read operation and then keep the bit lines BLe and BLo in a floating state until the data read to the bit line BLe or BLo is sensed. The MOS transistor TN9 is controlled by a control signal BLCLMP.

[0197] The MOS transistors TN1,...,TN6,TN8 and TN10 are provided to control odd/even page data during the program/read operations (or verification operation), and to detect whether or not the program/erase operations have been successfully completed for all the selected memory cells after verify-read (Program/Erase Completion detection) during the program/erase operations.

[0198] It is noted that an output signal COMi is used during the Program/Erase completion detection.

[0199] An MOS transistor TP1 is a preset transistor for presetting the potential of a sense node DTNij at Vdd. The MOS transistor TP1 is controlled by a control signal nPRST.

[0200] The MOS transistor TN10 is an equalizer circuit equalizing the potentials of the two output nodes Naij and Nbij of the latch circuit LATCH1. The MOS transistor TN10 is controlled by a control signal EQPB.

[0201] MOS transistors TN11 and TN12 function as column switches for determining electrical connection/disconnection between the nodes Naij, Nbij and input/output lines IOj and nIOj, respectively. When the level of a column select signal CSLi is "H", the MOS transistors TN11 and TN12 are turned on and the output nodes Naij and Nbij of the latch circuit are electrically connected to the input/output lines IOj and nIOj, respectively.

[0202] The column select signal CSLi is outputted from the column decoder 4 shown in FIG. 8. A column decoder is constituted by an NAND circuit as shown in FIG. 11. That is to say, for example, VAK1, CBK2, and CCH3 are all "H", the column select signal CSLi becomes "L".

[0203] In FIG. 9, reference symbol Vdd (e.g., about 2.3V) denotes a lower internal power supply potential than an external power supply potential Vcc. The internal power supply potential vdd is generated from the external power supply potential Vcc. Alternatively, the external power supply potential Vcc instead of the internal power supply potential Vdd may be applied to the data circuit.

[0204] [Batch Detection Circuit]

[0205] FIG. 12 shows important parts of the batch detection circuit 10 shown in FIG. 8.

[0206] The batch detection circuit 10 functions to detect whether or not program/erase operations have been successfully completed for all selected memory cells after verify-read (Program/Erase completion detection).

[0207] Each data circuit has a constitution as shown in FIG. 9. REG2-k (k=0, 1, 2, 3) is REG2 (see FIG. 9) in the (k+1)-th and (k+5)-th data circuits.

[0208] Output nodes COMi of the first to fourth data circuits are mutually connected and the connection node COMi1 thereof is also connected to the gate of a P channel MOS transistor TP2. Likewise, output nodes COMi of the fifth to

eighth data circuits are mutually connected and the connection node COMi2 thereof is also connected to the gate of a P channel NOS transistor TP3.

[0209] P channel MOS transistors TP13 and TP14 function to set the potentials of nodes COMi1 and COMi2 at the internal power supply potential Vdd and then turn the nodes COMi1 and COMi2 into a floating state during the Program/ Erase completion detection. The MOS transistors TN13 and TN14 are controlled by a control signal COMHn.

[0210] An N channel MOS transistor TN15 functions to set the potential of a node NCOM at the ground potential Vss and then turn the node NCOM into a floating state. The MOS transistor TN15 is controlled by a control signal NCOML.

[0211] During the Program/Erase completion detection, the potential level of the output signal COMi (see FIG. 9) from the data circuit corresponding to the memory cell for which the program/erase operations have not been sufficiently completed, decreases from "H" to "L". Accordingly, the level of the node NCOM is changed from "L" into "H" and the level of a node FLAG becomes "L".

[0212] On the other hand, if the program/erase operations have been sufficiently completed for all the memory cells, the potential levels of output signals COMi (see FIG. 9) from all data circuits remain "H". Accordingly, the level of the node NCOM remains "L" and the level of the node FLAG becomes "H".

[0213] As can be seen from the above, by detecting the potential level of the node FLAG, it is possible to detect whether or not the program/erase operations have been successfully completed for all the selected memory cells. The operation of the Program/Erase completion detection will be described later in detail.

[0214] In this embodiment, the eight data circuits are grouped into one unit and the voltage level of the node FLAG is detected for eight columns of memory cells corresponding to these eight data circuits, thereby detecting whether or not the program/erase operations have been sufficiently completed.

[0215] The reason for grouping the eight data circuits into one unit is to replace memory cells of a redundancy circuit in units of eight columns corresponding to these eight data circuits. That is, when a fuse element (enclosed by a broken line) is cut off, the memory cells connected to these eight data circuits always turn into an unselected state and auxiliary memory cells in a redundancy region are selected.

**[0216]** Accordingly, if the memory cells of the redundancy circuit are replaced in units of n columns corresponding to n data circuits (where n is a natural number), the n data circuits are grouped into one unit.

[0217] It is noted that the node FLAG is a common node to all columns. If the number of columns is, for example, 2048 and eight data circuits (columns) are set as a redundancy replacement unit, then 256 circuits shown in FIG. 12 exist on a chip. These 256 circuits are connected to the common node FLAG.

[0218] [Word Line Control Circuit] . . . Second Feature

[0219] FIG. 13 shows a concrete example of the word line control circuit shown in FIG. 8.

[0220] The memory cell array 1 consists of a plurality of memory cell blocks arranged in column direction. Each of the memory cell blocks has a plurality of NAND cell units arranged in row direction. The concrete example of the memory cell array and the NAND cell units is shown in FIGS. 61 to 63.

[0221] In this embodiment, one row address decoder and one word line driver are provided per memory cell block.

[0222] For example, word lines WL1, WL16 and select gate lines SG1 and SG2 in the first memory cell block are connected to the first word line driver RMAIN1.

[0223] The first word line driver RMAIN1 receives the output signal (decoding result) of the first row address decoder RADD1 for determining whether to select/unselect the first memory cell block.

[0224] In this way, the word lines WL1,...WL16 and the select gate lines SG1 and SG2 in the i-th memory cell block (where i=1, 2,...) are connected to the i-th word line driver RMAIN1. The word line driver RMAIN1 receives the output signal (decoding result) of the i-th row address decoder RADDi for determining whether to select/unselect the i-th memory cell block.

[0225] In this embodiment, the word line drivers are arranged at both sides of the memory cell array 1 (two end portions thereof in row direction).

[0226] To be specific, the word line drivers RMAIN1, RMAIN3, . . . corresponding to the odd-numbered memory cell array blocks are arranged at one side (left side) of the two end portions of the memory cell array 1 in row direction, whereas the word line drivers RMAIN2, RMAIN4, . . . corresponding to the even-numbered memory cell array blocks are arranged at the other side (right side) of the two end portions of the memory cell array 1 in row direction.

[0227] Such arrangement of the word line drivers RMAIN1 on both ends of the memory cell array 1 facilitates designing the word line drivers RMAINi (or increases the degree of freedom in layout). That is to say, in this embodiment, one word line driver can secure a layout space for two memory cell blocks in column direction.

[0228] Furthermore, the word lines WL1, ... WL16 and the select gate lines SG1 and SG2 in one memory cell block are always driven from one side (or the other side) of the memory cell array 1 by the word line driver corresponding to this memory cell block. This can, therefore, prevent drive signal supply timing for the memory cells and the select transistors in a predetermined NAND cell unit in the selected block from shifting.

**[0229]** On the other hand, the row address decoders RADDi (where  $i=1,2,\ldots$ ) are arranged only at one side of the two end portions of the memory cell array 1 in row direction. This means that it suffices to arrange signal lines (address buses) for applying row address signals to the row address decoders RADDi only at one side of the memory cell array 1. The area of the address buses can be, therefore, reduced, resulting in a contribution to the reduction of the chip area.

[0230] Namely, if providing that the row address decoders RADDi are arranged on the two end portions of the memory cell array 1 in row direction as in the case of the word line drivers RAMINi, it is necessary to arrange address buses on the two end portions of the memory cell array 1 in row direction. This is not advantageous for the reduction of the area of the memory cell array 1.

[0231] In this embodiment, as a result of arranging the row address decoders RADDi only on one of the two end portions (at one side of) the memory cell array 1 in row direction, signal lines 22 are arranged on the memory cell array 1. The signal lines 22 are used to apply the output signals (decoding results) of the row address decoders RADD2, RADD4, . . .

corresponding to the even-numbered memory cell array blocks to the word line drivers RMAIN2, RMAIN4, . . . , respectively.

[0232] During normal operation, a signal RDECADS is transmitted through this signal line 22. Accordingly, it is necessary to prevent the potential of the signal lines 22 from adversely affecting the memory cell operation. The present invention provides novel row address decoders RADDi and word line drivers RMAINi which can prevent the potential of the signal lines 22 from adversely affecting the memory cell operation, which will be described later in detail.

[0233] The potential generating circuit 9A has a booster (charge-pumping circuit) and generates a program potential Vpp and a transfer potential Vpass used in the program operation. The potential generating circuit 9A is connected to a switching circuit 9B. The switching circuit 9B functions to allot potentials including the program potential Vpp, the transfer potential Vpass, the internal power supply potential Vdd and the ground potential Vss to signal lines CG1, CG16 corresponding to the word lines WL1, . . . WL16.

[0234] The signal lines CG1,...CG16 are connected to the word line drivers RMAINi. Namely, the signal lines CG1, CG16 are connected to the word lines WL1,...WL16, respectively by way of potential transfer transistors HNt1, HNt2,...HNt16 (to be described later) in the word line drivers RMAINi.

[0235] [Device Structure] . . . Regarding Signal Lines 22 shown in FIG. 13

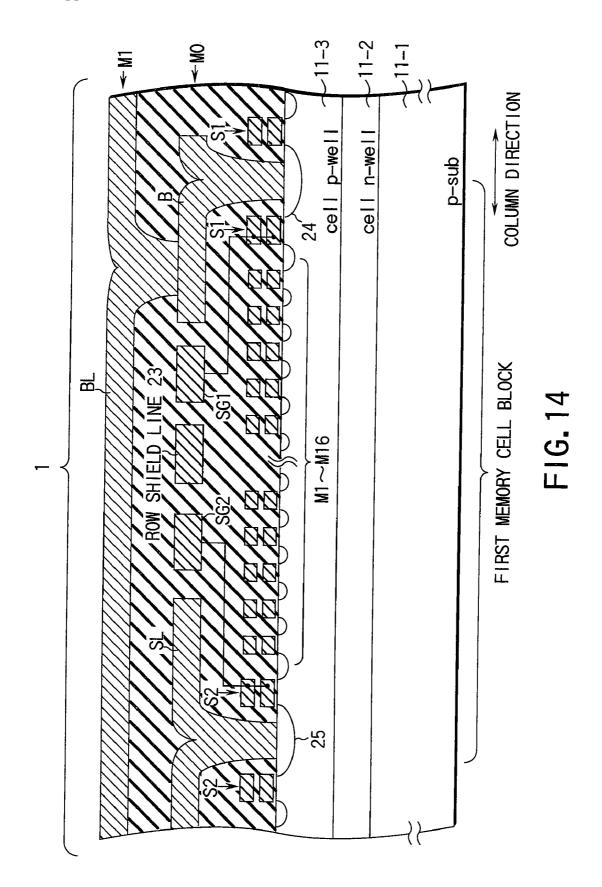

[0236] FIG. 14 is a cross-sectional view of an odd-numbered memory cell block of FIG. 13 in column direction.

[0237] In case of odd-numbered memory cell blocks, the row address decoders RADD1, RADD3, and the word line drivers RMAIN1, RMAIN3,... are arranged at one side of the memory cell array 1. Due to this, signal lines connecting the row address decoders RADD1, RADD3, with the word line drivers RAMIN1, RAMIN3, are not arranged on the memory cell array 1.

[0238] The concrete structure of the memory cell block will be described hereinafter.

[0239] A double-well region consisting of an n well region 11-2 and a p well region 11-3, is formed in a p silicon substrate 11-1. For example, 16 memory cells M1, . . . M16 connected in series are formed on the p well region 11-3. Each memory cell consists of an N channel MOS transistor and has a stack gate structure consisting of a floating gate electrode and a control gate electrode.

[0240] Select transistors S1 and S2 are connected to the two end portions of the serially-connected memory cells M1,... M16, respectively. Each of the select transistors S1 and S2 consists of an N channel MOS transistor. The diffused layer (drain) 24 of the bit line-side select transistor S1 is connected to a metal wiring B in the first wiring layer M0. The diffused layer (source) 25 of the source line-side select transistor S2 is connected to a source line SL in the first wiring layer M0.

[0241] The gate electrode (select gate line (polysilicon)) of the select transistor S1 is connected to the metal wiring SG1 in the first wiring layer M0 to decrease the wiring resistance of the select gate line. Contact portions between the select gate line (polysilicon) and the metal wiring SG1 are provided at positions, for example, at which the select gate line intersect 528 bit lines, respectively.

[0242] Likewise, the gate electrode (select gate line (polysilicon)) of the select transistor S2 is connected to the a metal wiring SG2 in the first wiring layer M0. Contact portions

between the select gate line (polysilicon) and the metal wiring SG2 are provided at positions, for example, at which the select gate line intersect 528 bit lines, respectively.

[0243] The bit lines BL is arranged in the second wiring layer M1 provided on the first wiring layer M0. The bit line BL extends in column direction and is connected to the diffused layer (drain) 24 of the select transistor S1 through the metal wiring B in the first wiring layer M0.

[0244] The respective signal lines in the first and second wiring layers M0 and M1 are made or, for example, aluminum, copper or an alloy thereof.

[0245] A row shield line 23 is arranged above the memory cells  $M1, \ldots M16$  and between the metal wirings SG1 and SG2.

[0246] The row shield line 23 is arranged so as to prevent the generation of so-called coupling noise during the program/read operations and to sufficiently increase the potentials of unselected word lines during the erase operation. The potential of the row shield line 23 is normally set at the same as that of the double-well region (cell well) 11-2 and 11-3.

[0247] During the program/read operations, the cell well potential is normally set at the ground potential Vss. At this moment, therefore, the potential of the row shield line 23 is fixed to the ground potential Vss, as well. In that case, since the coupling capacity between the bit line BL and the word line WL is almost eliminated, it is possible to prevent coupling noise from occurring to the data transmitted through the bit line.

[0248] Further, during the program/read operations, the potentials of the select gate lines (metal wirings) SG1 and SG2 in unselected blocks are set at the ground potential Vss. Due to this, the select gate lines (metal wirings) SG1 and SG2 also function as shield lines during the program/read operations.

[0249] In this way, by setting the potentials of the row shield line 23 and the select gate lines (metal wirings) SG1 and SG2 in the unselected blocks at the ground potential Vss, respectively, it is possible to reduce the capacitive coupling between the bit line BL and the word line WL and to prevent coupling noise from being applied to the data transmitted through the bit line.

[0250] Meanwhile, during the erase operation, the potential of the row shield line 23 is set at an erase potential Vera (e.g., about 20V). This is because the potentials of the word lines WL in unselected blocks are to be sufficiently increased during the erase operation.

[0251] Namely, during the erase operation, the word lines (control gate lines) WL of unselected blocks are in a floating state. When the erase potential (e.g., about 20V) is applied to the double-well region (cell well) 11-2, 11-3, the potentials of the word lines WL in the unselected blocks are increased by capacitive coupling.

[0252] Therefore, if the potential of the row shield line 23 is set at the erase potential Vera during the erase operation, the potential of the word line WL is not influenced by the potential of the row shield line 23 when the potential of the cell wells 11-2 and 11-3 rises from the ground potential Vss to the erase potential Vera. Thus, it is possible to sufficiently increase the potentials of the word lines WL in the unselected blocks to the same level as that of the erase potential Vera.

[0253] Further, the potentials of the word lines WL in the unselected blocks rise sufficiently to the same level as that of the erase potential Vera. Due to this, a high electric field is not

applied to the tunnel oxide film between the floating gate electrode and the cell wells and erroneous data erase can be, therefore, prevented.

[0254] At this moment, providing that the potential of the row shield line 23 is the ground potential Vss or the power supply potential Vcc, the potential of the word line WL is influenced by the potential of the row shield line 23 (Vss or Vcc) and does not rise to the same level as that of the erase potential Vera. Accordingly, a high electric field may possibly be applied to the tunnel oxide films of the unselected memory cells to thereby cause erroneous data erase.

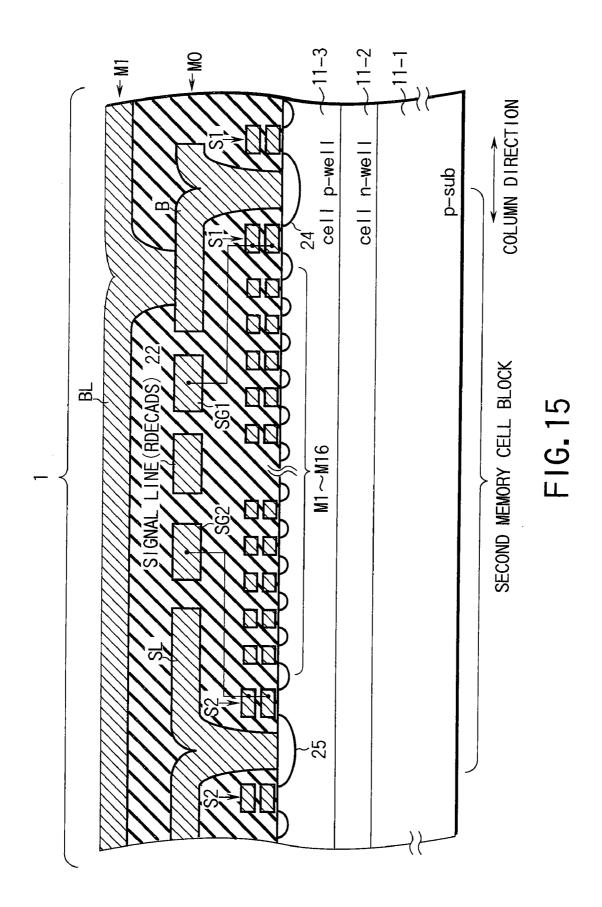

[0255] FIG. 15 is a cross-sectional view of an even-numbered memory cell block of FIG. 13 in column direction.

[0256] In case of even-numbered memory cell blocks, the row address decoders RADD2, RADD4, . . . are arranged on one end of the memory cell array 1 in row direction. The word line drivers RMAIN2, RMAIN4, . . . are arranged on the other end of the memory cell array 1 in row direction. Accordingly, signal lines 22 connecting the row address decoders RADD2, RADD4, . . . with the word line drivers RMAIN2, RMAIN4, . . . , respectively, are arranged on the memory cell array 1.

[0257] The concrete structure of the memory cell block in FIG. 15 will be described hereinafter.

[0258] A double-well region consisting of an n well region 11-2 and a p well region 11-3, is formed in a p silicon substrate 11-1. For example, 16 memory cells M1, . . . M16 connected in series are formed on the p well region 11-3. Each memory cell consists of an N channel MOS transistor and has a stack gate structure consisting of a floating gate electrode and a control gate electrode.

[0259] Select transistors S1 and S2 are connected to the two end portions of the serially connected memory cells M1,... M16, respectively. Each of the select transistors S1 and S2 consists of an N channel MOS transistor. For example, the diffused layer (drain) 24 of the bit line-side select transistor S1 is connected to a metal wiring B in the first wiring layer M0. The diffused layer (source) 25 of the source line-side select transistor S2 is connected to a source line SL in the first wiring layer M0.

[0260] The gate electrode (select gate line (polysilicon)) of the select transistor S1 is connected to the metal wiring SG1 in the first wiring layer M0 to decrease the wiring resistance of the select gate line. Contact portions between the select gate line (polysilicon) and the metal wiring SG1 are provided at positions, for example, at which the select gate line intersect 528 bit lines, respectively.

[0261] Likewise, the gate electrode (select gate line (polysilicon)) of the select transistor S2 is connected to the metal wiring SG2 in the first wiring layer M0 to decrease the wiring resistance of the select gate line. Contact portions between the select gate line (polysilicon) and the metal wiring SG2 are provided at positions, for example, at which the select gate line intersect the 528 bit lines, respectively.

[0262] The bit lines BL is arranged in the second wiring layer M1 provided on the first wiring layer M0. The bit line BL extends in column direction and is connected to the diffused layer (drain) 24 of the select transistor S1 through the metal wiring B in the first wiring layer M0.

[0263] The respective signal lines in the first and second wiring layers M0 and M1 are made of, for example, aluminum, copper or an alloy thereof.

[0264] A signal line 22 is arranged above the memory cells M1, ... M16 and between the metal wirings SG1 and SG2.

[0265] The device of the even-numbered memory cell block is characterized in that the signal line 22 is provided instead of the row shield line 23 (see FIG. 14) of the odd-numbered memory cell block.

[0266] As described with reference to FIG. 13, the signal line 22 functions to transmit the output signal RDECAD of the row address decoder to the word line driver.

[0267] Accordingly, the potential of the signal line 22 cannot be set at the same as that of the row shield line 23.

[0268] The present invention proposes a word line control circuit capable of setting the potential of the signal line 22 at an appropriate value according to an operation mode, preventing so-called coupling noise during the program/read operations and sufficiently increasing the potentials of unselected word lines during the erase operation without hampering the functions of the above-stated signal line 22.

[0269] Now, an embodiment of the word line control circuit of the present invention will be described. Then, description will be given to how the potential level of the signal line 22 varies in each operation mode if this circuit is used.

[0270] [Example of Word Line Control Circuit]

[0271] First, symbols added in the drawings are defined as follows.

[0272] An MOS transistor to which symbol "HN\* (where \* is a number, symbol or the like)" is added is a high voltage enhancement N channel transistor having a threshold voltage of, for example, about 0.6V and is applied with a higher voltage than the power supply voltage Vcc. This transistor is turned off when gate potential is 0V.

[0273] An MOS transistor to which symbol "1HN\*\* (where \* is a number, symbol or the like)" is added is a high voltage enhancement N channel MOS transistor having a threshold voltage of, for example, about 0.1V and is applied with a higher voltage than the power supply voltage Vcc.

[0274] An MOS transistor to which symbol \* "DHN\*\*" is added is a high voltage depletion N channel MOS transistor having a threshold voltage of, for example, about –1V. If the potentials of the gate and drain of the transistor are set at the power supply potential Vcc, the potential of the drain Vcc is transferred to the source thereof. In addition, if the potential of the gate is set at 0V while the potentials of the source and drain are Vcc, this transistor is turned off.

[0275] An MOS transistor to which symbol "TN\*\*" is added is a low voltage enhancement N channel MOS transistor having a threshold voltage of, for example, about 0.6V and is applied with a voltage of not higher than the power supply voltage Vcc. An MOS transistor to which symbol "TP\*\*" is added is a low voltage enhancement P channel MOS transistor having a threshold voltage of, for example, about 0.6V.

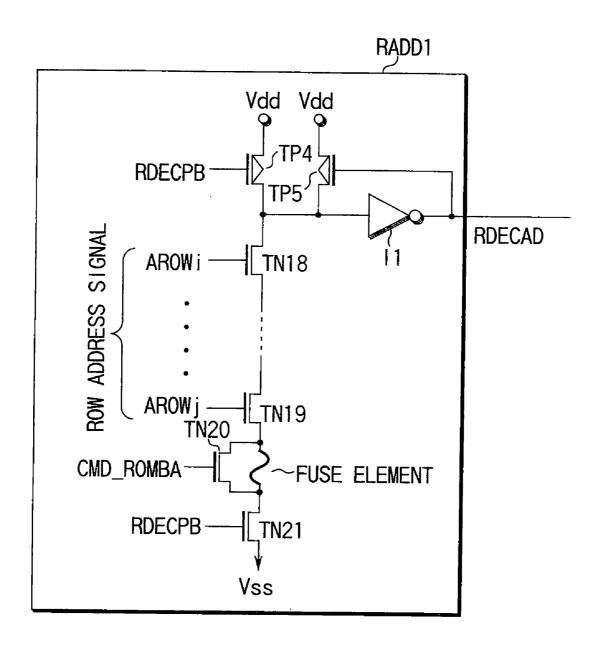

[0276] FIG. 16 shows the important parts of the row address decoder provided to correspond to the odd-numbered memory cell block.

[0277] To be exact, this row address decoder RADD1 functions as a block decoder. Namely, when the first memory block is selected, for example, the levels of all row address signals AROWi, . . . AROWj become "H" and the level of an output signal RDECAD becomes "H". The operation of the row address decoder RADD1 will be described later in detail. [0278] FIG. 17 shows the important parts of the word line driver provided to correspond to the odd-numbered memory cell block.

[0279] The main constituent elements of the word line driver RMAIN1 are a high voltage switching circuit 26 and transfer MOS transistors HN5, HN6, HNt1, HNt16.

[0280] The high voltage switching circuit 26 comprises the first booster unit consisting of an MOS capacitor DHN4 and an MOS transistor 1HN1, and the second booster unit consisting of an MOS capacitor DHN5 and an MOS transistor IHN2.

[0281] The gate of the MOS transistor HN3 is connected to a connection node B connecting the MOS transistors IHN1 and IHN2. In this case, the potentials of nodes A, B and transferG1 gradually increase synchronously with a clock signal Owc while the potential levels of the gate and the source of the MOS are maintained to be opposite in phase. Thus, boosting efficiency improves.