**(19) 대한민국특허청(KR)**

**(12) 등록특허공보(B1)**

(51) Int. Cl.

G06F 12/02 (2006.01)

(45) 공고일자

2007년06월04일

(11) 등록번호

10-0724816

(24) 등록일자

2007년05월28일

|             |                   |             |                 |

|-------------|-------------------|-------------|-----------------|

| (21) 출원번호   | 10-2001-7005435   | (65) 공개번호   | 10-2001-0085983 |

| (22) 출원일자   | 2001년04월30일       | (43) 공개일자   | 2001년09월07일     |

| 심사청구일자      | 2004년10월28일       |             |                 |

| 번역문 제출일자    | 2001년04월30일       |             |                 |

| (86) 국제출원번호 | PCT/CA1999/001054 | (87) 국제공개번호 | WO 2000/26784   |

| 국제출원일자      | 1999년10월29일       | 국제공개일자      | 2000년05월11일     |

(81) 지정국

국내특허 : 알바니아, 아르메니아, 오스트리아, 오스트레일리아, 아제르바이잔, 보스니아 헤르체고비나, 바베이도스, 불가리아, 브라질, 벨라루스, 캐나다, 스위스, 중국, 쿠바, 체코, 독일, 덴마크, 에스토니아, 스페인, 핀란드, 영국, 그鲁지야, 가나, 감비아, 크로아티아, 헝가리, 인도네시아, 이스라엘, 인도, 아이슬랜드, 일본, 케냐, 키르키즈스탄, 북한, 대한민국, 카자흐스탄, 세인트루시아, 스리랑카, 리베이라, 레소토, 리투아니아, 룩셈부르크, 라트비아, 몰도바, 마다가스카르, 마케도니아공화국, 몽고, 말라위, 멕시코, 노르웨이, 뉴질랜드, 폴란드, 포르투칼, 루마니아, 러시아, 수단, 스웨덴, 싱가포르, 슬로베니아, 슬로바키아, 시에라리온, 타지키스탄, 투르크맨, 터키, 트리니다드토바고, 우크라이나, 우간다, 미국, 우즈베키스탄, 베트남, 세르비아 앤 몬테네그로, 남아프리카, 짐바브웨,

AP ARIPO특허 : 가나, 감비아, 케냐, 레소토, 말라위, 수단, 시에라리온, 스와질랜드, 탄자니아, 우간다, 짐바브웨,

EA 유라시아특허 : 아르메니아, 아제르바이잔, 벨라루스, 키르키즈스탄, 카자흐스탄, 몰도바, 러시아, 타지키스탄, 투르크맨,

EP 유럽특허 : 오스트리아, 벨기에, 스위스, 사이프러스, 독일, 덴마크, 스페인, 핀란드, 프랑스, 영국, 그리스, 아일랜드, 이탈리아, 룩셈부르크, 모나코, 네덜란드, 포르투칼, 스웨덴,

OA OAPI특허 : 부르키나파소, 베닌, 중앙아프리카, 콩고, 코트디브와르, 카메룬, 가봉, 기니, 기니 비사우, 말리, 모리타니, 니제르, 세네갈, 차드, 토고,

(30) 우선권주장

09/182,495

1998년10월30일

미국(US)

(73) 특허권자

모사이드 테크놀로지스 인코포레이티드

캐나다 온타리오주 케이2케이 2엑스1 카나타 하이네스 로드 11

마쓰시타 덴키 산교 가부시끼 가이샤

일본 오사카후 가도마시 오아자 가도마 1006

(72) 발명자

웨이, 광성

미국, 펜실베니아 19020, 벤사렘, 네셔널 브리드라이브 1451

기쿠카와, 히로히토

일본, 오사카 573-001, 타쿠치야마 히라카타시, 2-12-3-410

마, 신사

캐나다, 온타리오 K2H6Y3, 네핀, 나나이모드라이브 34

(74) 대리인 청운특허법인

(56) 선행기술조사문현

US05572470 KR1019960008788

심사관 : 김기천

전체 청구항 수 : 총 18 항

#### (54) 신호경로 지연을 감소시키는 컬럼 여분 회로

#### (57) 요약

본 발명은 로우 및 컬럼에 배열되는 메모리 소자를 갖는 동시성 DRAM에 관한 것으로, 메모리 소자에 적용된 메모리 어드레스를 디코딩함으로써 억세스될 수 있는 메모리 소자, 디코드된 컬럼 어드레스에 응답하여 적절한 메모리 소자를 활성화하는 노멀 컬럼 드라이버; 메모리 뱅크 전체에 분포되고 뱅크 내의 다수의 블록 내에 고장난 컬럼을 대치하기 위해 유연하게 선택할 수 있는 여분의 컬럼 드라이버; 및 여분의 컬럼을 선택적으로 활성화하고 결함있는 노멀 컬럼의 활성화를 방지하는 스위치 수단을 포함하며, 컬럼 여분 방법 및 장치는 노멀 및 여분의 컬럼 경로 사이의 시간 차이를 최소화하고, 고장난 컬럼 어드레스를 수리하는데 끊어짐이 필요한 퓨즈의 수를 최소화한다.

#### 대표도

도 4

#### 특허청구의 범위

#### 청구항 1.

- a) 로우들 및 컬럼들로 이루어져 있고, 각각의 컬럼 및 로우에 컬럼 및 로우 어드레스 신호를 인가함으로써 액세스할 수 있는 메모리 소자들;

- b) 노멀 클록 인에이블 신호(YSG B)가 수신되면 노멀 컬럼 디코더에 의하여 디코드되는 디코드된 메모리 어드레스 신호(DEC)에 응답하여 적어도 하나의 연결된 노멀 컬럼을 인에이블하기 위한 노멀 컬럼 드라이버들;

- c) 결함있는 노멀 컬럼을 표시하는 여분의 디코더의 출력 신호와 여분 클록 인에이블 신호(RYSG B)에 응답하여 적어도 하나의 연결된 여분 컬럼을 선택적으로 인에이블 하기 위한 여분 컬럼 드라이버; 및

- d) 클록 신호(YSG)를 상기 노멀 컬럼 드라이버에 대한 상기 노멀 클록 인에이블 신호(YSG B) 또는 상기 여분의 컬럼 드라이버에 대한 상기 여분의 클록 인에이블 신호(RYSG B) 중 어느 하나로 스위칭함으로써, 상기 여분 컬럼 드라이버 및 상기 노멀 컬럼 드라이버 중 하나를 선택적으로 인에이블하게 하고, 결함있는 메모리 어드레스에 연결된 여분 컬럼에 데이터를 송수신하기 위하여 상기 여분 디코더의 출력 신호의 레벨에 응답하는 스위치; 를 구비하는 다수의 블록을 포함하고,

상기 블록들이 블록 선택 신호(BSEL)에 의하여 선택적으로 활성화되는 것을 특징으로 하는 반도체 메모리 소자.

#### 청구항 2.

제 1 항에 있어서,

상기 여분의 디코더는 프로그램된 결합있는 메모리 어드레스 PY 및 블록 선택 신호 BSEL에 응답하여 결합있는 노멀 컬럼을 표시하는 신호를 더 제공하며, 상기 여분 컬럼이 상기 다수의 블록 중 어느 하나에 있는 결합있는 컬럼을 대치할 수 있는 것을 특징으로 하는 반도체 메모리 소자.

### 청구항 3.

제 2 항에 있어서,

상기 여분의 디코더는 한 쌍의 어드레스-비교 회로를 포함하는 것을 특징으로 하는 반도체 메모리 소자.

### 청구항 4.

제 3 항에 있어서,

상기 여분의 디코더는 각각 컬럼 어드레스를 가지고 프로그램될 수 있는 적어도 두 개의 어드레스-비교 회로를 포함하고, 로우 어드레스 신호에 응답하여 상기 적어도 두 개의 어드레스-비교 회로 중 하나에 의하여 제공되는 결합있는 노멀 컬럼을 표시하는 신호를 선택적으로 출력하는 것을 특징으로 하는 반도체 메모리 소자.

### 청구항 5.

제 1 항에 있어서,

상기 여분의 디코더는 데이터 경로 제어 신호(DBSW\_CTL)를 더 발생시키고,

다수의 메모리 어레이 블록내에 어떠한 여분의 컬럼 드라이브도 인에이블 되어 않는 경우, 상기 데이터 경로 제어 신호(DBSW\_CTL)는 블록 선택 신호에 의하여 선택된 메모리 블록내에서 활성화하며,

상기 다수의 메모리 블록내에 적어도 하나의 여분의 컬럼 디코더가 인에이블되는 경우, 블록 선택 신호와 상관없이, 상기 데이터 경로 제어 신호(DBSW\_CTL)는 여분의 컬럼 드라이버가 인에이블된 메모리 어레이 블록내에서 활성화하는 것을 특징으로 하는 반도체 메모리 소자.

### 청구항 6.

- a) 컬럼 클럭 신호에 응답하여 노멀 컬럼 디코더에 의하여 선택적으로 인에이블되는 다수의 노멀 컬럼;

- b) 컬럼 클럭 신호에 응답하여 여분의 컬럼 디코더에 의하여 선택적으로 인에이블되는 여분의 메모리 컬럼; 및

- c) 상기 여분의 컬럼 디코더로부터 출력에 응답하여 컬럼 클록 신호를 노멀 드라이버 또는 여분의 드라이버에 스위칭하는 로컬 신호 분배 회로를 포함하여 이루어진 반도체 메모리 소자.

### 청구항 7.

제 6 항에 있어서,

상기 여분의 컬럼 디코더는 어드레스 비교 디코더인 것을 특징으로 하는 반도체 메모리 소자.

### 청구항 8.

- a) 로우 및 컬럼으로 이루어지고, 연결된 컬럼 및 로우에 컬럼 및 로우 어드레스 신호를 각각 인가함으로써 액세스할 수 있는 메모리 소자들;

- b) 각각의 입력에서 수신되는 노멀 컬럼을 인에이블하기 위한 디코드된 메모리 어드레스 신호에 응답하여 연결된 상기 노멀 컬럼들을 인에이블 하는 노멀 컬럼 드라이버들;

- c) 각각 컬럼 어드레스를 가지고 프로그램될 수 있는 적어도 두 개의 어드레스-비교 회로를 포함하며, 로우 어드레스 신호에 응답하여 상기 적어도 두 개의 어드레스-비교 회로 중 하나에 의하여 제공되는 결합있는 노멀 컬럼을 표시하는 신호를 선택적으로 출력하며, 여분의 컬럼에 액세스하기 위한 여분의 컬럼 디코더;

- d) 결합있는 노멀 컬럼을 표시하는 신호에 응답하여, 적어도 하나의 연결된 여분의 컬럼을 인에이블하는 여분의 컬럼 드라이버; 및

- e) 상기 여분의 컬럼 드라이버를 선택적으로 인에이블하고 상기 결합있는 컬럼과 연결되어 있는 노멀 컬럼 드라이버를 디스에이블하기 위하여 결합있는 노멀 컬럼을 표시하는 신호에 응답하며, 상기 노멀 및 여분의 컬럼 메모리 어드레스 신호 경로간의 타이밍이 동일한 스위치 수단;을 포함하는 것을 특징으로 하는 반도체 메모리 소자.

### 청구항 9.

- a) 로우 및 컬럼으로 이루어지고, 연결된 컬럼 및 로우에 컬럼 및 로우 어드레스 신호를 각각 인가함으로써 액세스할 수 있는 메모리 소자들;

- b) 각각의 입력에서 수신되는 노멀 컬럼을 인에이블하기 위한 디코드된 메모리 어드레스 신호에 응답하는 연결된 노멀 컬럼들을 인에이블하는 노멀 컬럼 드라이버들;

- c) 다수의 메모리 어레이 블록 중의 어느곳에 위치한 적어도 하나의 여분의 컬럼을 인에이블하게 하는 각각의 입력에서 수신되는 디코드된 메모리 어드레스 신호에 응답하여 연결된 여분 컬럼들을 인에이블하는 여분의 컬럼 드라이버들;

- d) 다수의 메모리 어레이 블록내에 어떠한 여분의 컬럼 드라이브도 인에이블되지 않는 경우, 블록 선택 신호에 의하여 선택된 메모리 블록내에서 활성화하고, 상기 다수의 메모리 블록내에 적어도 하나의 여분의 컬럼 디코더가 인에이블되는 경우, 블록 선택 신호와 상관없이, 여분의 컬럼 드라이버가 인에이블된 메모리 어레이 블록내에서 활성화하는 데이터 경로 제어 신호를 발생시키는 수단; 및

- e) 결합있는 노멀 컬럼을 표시하는 신호에 응답하여 선택적으로 결합있는 컬럼과 연결된 상기 여분의 컬럼 드라이버를 인에이블하거나 결합있는 컬럼과 연결된 상기 노멀 컬럼 드라이버를 디스에이블하며, 상기 노멀 및 여분의 컬럼 메모리 어드레스 신호 경로간의 타이밍이 동일한 스위치 수단;을 포함하는 것을 특징으로 하는 반도체 메모리 소자.

### 청구항 10.

- a) 각각이 다수의 로우, 및 다수의 노멀 컬럼과 적어도 하나의 여분의 컬럼을 포함하는 다수의 컬럼으로 이루어진 메모리 소자들을 구비한 다수의 메모리 블록;

- b) 각각의 노멀 컬럼과 결합되어 있고, 디코드된 노멀 메모리 어드레스 신호에 응답하여 결합된 노멀 컬럼에 액세스를 가능하게 하는 노멀 컬럼 드라이버;

- c) 각각의 여분의 컬럼과 결합되어 있고, 여분의 컬럼 메모리 어드레스 신호에 응답하여 결합된 여분의 컬럼에 액세스를 가능하게 하는 여분의 컬럼 드라이버; 및

d) 적어도 하나의 컬럼 메모리 어드레스 신호 및 부분 선택 신호에 응답하여 여분의 컬럼 메모리 어드레스 신호를 발생시키는 여분의 컬럼 디코더;를 포함하는 것을 특징으로 하는 반도체 메모리 소자.

### 청구항 11.

제 10 항에 있어서,

제 1 메모리 블록내에 상기 여분의 컬럼 드라이버는 또한 상기 제 1 메모리 블록내에 있는 결합있는 노멀 컬럼을 표시하는 디코드된 메모리 어드레스 신호에 응답하는 것을 특징으로 하는 반도체 메모리 소자.

### 청구항 12.

제 10 항에 있어서,

상기 다수의 메모리 블록은 각각 상부 및 하부를 포함하고,

각각의 여분의 컬럼 드라이버는 결합된 여분의 컬럼의 상기 상부 및 하부에 각각 액세스가 가능하도록 구성된 것을 특징으로 하는 반도체 메모리 소자.

### 청구항 13.

제 12 항에 있어서,

제 1 부분 선택 신호가 제 1 노멀 컬럼 어드레스의 상부에 결합을 표시하고,

제 2 부분 선택 신호가 제 2 노멀 컬럼 어드레스의 하부에 결합을 표시하는 것을 특징으로 하는 반도체 메모리 소자.

### 청구항 14.

제 12 항에 있어서,

제 1 컬럼 어드레스의 제 1 결합이 제 1 여분의 컬럼의 제 1 부분으로 대치되고,

제 2 컬럼 어드레스의 제 2 결합이 상기 제 1 여분의 컬럼의 제 2 부분으로 대치되는 것을 특징으로 하는 반도체 메모리 소자.

### 청구항 15.

제 12 항에 있어서,

제 1 메모리 블록에서 제 1 노멀 컬럼 어드레스의 상부에 제 1 결합이 제 1 여분의 컬럼의 상부로 대치되고,

상기 제 1 메모리 블록에서 제 2 컬럼 어드레스의 하부에 제 2 결합이 상기 제 1 여분의 컬럼의 하부로 대치되며,

상기 제 1 여분의 컬럼은 상기 제 1 메모리 블록내에 위치되는 것을 특징으로 하는 반도체 메모리 소자.

## 청구항 16.

제 12 항에 있어서,

제 1 메모리 블록에서 제 1 노멀 컬럼 어드레스의 상부에 제 1 결함이 제 1 여분의 컬럼의 상부로 대치되고,

상기 제 1 메모리 블록에서 제 2 컬럼 어드레스의 하부에 제 2 결함이 상기 제 1 여분의 컬럼의 하부로 대치되며,

상기 제 1 여분의 컬럼은 제 2 메모리 블록내에 위치되는 것을 특징으로 하는 반도체 메모리 소자.

## 청구항 17.

제 10 항에 있어서,

각각의 메모리 블록에 대하여,

상기 디코드된 메모리 어드레스 신호는 노멀 어드레스 디코더에 의해 제공되고,

결함있는 노멀 컬럼을 표시하는 디코드된 메모리 어드레스 신호는 여분의 어드레스 디코더에 의해 제공되는 것을 특징으로 하는 반도체 메모리 소자.

## 청구항 18.

제 10 항에 있어서,

각각의 여분의 컬럼에 있으며, 데이터 경로 제어 신호에 응답하여, 인에이블된 여분의 컬럼으로부터 공통의 데이터 버스까지 데이터를 통과시키는 데이터 통과 게이트를 포함하는 것을 특징으로 하는 반도체 메모리 소자.

### 명세서

#### 기술분야

본 발명은 반도체 메모리에 관한 것으로, 특히, 결함이 있는 컬럼(column)을 여분의 컬럼으로 대치하여 유연하고 효율적인 회로를 갖는 반도체 메모리에 관한 것이다.

#### 배경기술

반도체 다이나믹 랜덤 액세스 메모리(dynamic random access memories, DRAMs)는 통상적으로 워드라인(wordlines) 및 워드라인과 교차하는 컬럼으로 형성된다. 로우라인(rowline) 및 컬럼(column)의 각 교차점 근처의 커패시터는 저장되는 데이터를 나타내기 위하여 전하를 저장한다. 커패시터는 로우라인 상에 적절한 전압을 갖는 전하를 충전 또는 방전하기 위하여 액세스 트랜지스터에 의해 컬럼에 결합된다. 로우라인 및 컬럼은 로우(또는 X) 디코더 및 컬럼(또는 Y) 디코더 수단에 의해 특수한 커패시터에 독취 또는 기록하기 위하여 선택된다.

컬럼 또는 소자와 관련하여 물리적 결함이 생기는 경우가 이따금 있다. 이러한 이유 때문에, RAMs는 보통 여분의 메모리 소자 및 컬럼 회로를 공급하는 여분의 컬럼을 포함한다. 결함있는 컬럼이 위치한 메모리에 억세스하기 위한 여분의 메모리 및 여분의 디코더는 귀중한 반도체 칩을 사용하고 메모리의 영역 효율을 감소시킨다.

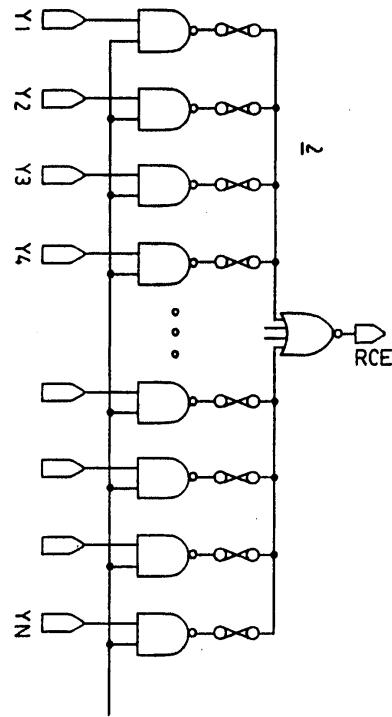

동기식 다이나믹 랜덤 액세스 메모리(synchronous dynamic random access memories, SDRAMs)에 컬럼 여분 구조를 제공하기 위해 여러 가지 기술이 실행되어 왔다. 그들 중에는 어드레스 비교(address compare) 방식, 어드레스 탐지(address detector) 방식, 시프터(shifter) 방식, 어드레스 또는 데이터 스티어링(steering) 방식 및 이들의 결합이 있다. 예를 들면, 이들 기술 중 첫 번째에서, Y 어드레스 비교기를 사용하고, 미리 디코드된 Y 어드레스 신호(PY1:N)는 도 1에

도시된 바와 같이 여분의 컬럼 인에이블 신호(redundant column enable signals, RCE)를 발생시키기 위해 퓨즈(fuses)를 통과한다. 고유 커패시턴스 및 저항을 갖는 여분의 비교기(2)와 결합된 퓨즈는 Y 여분의 경로에 여분의 지연(delay)을 부가시킨다.

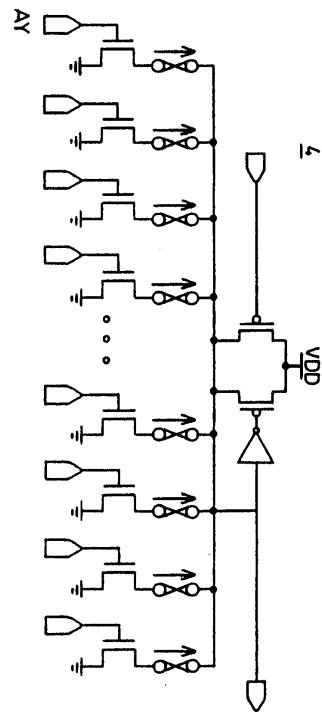

두 번째 기술은 Y 어드레스 탐지기(4)를 포함하며, 도 2에 도시된 바와 같이, Y 어드레스 신호(AY(N-1:0))는 퓨즈를 통하여 미리 방전된 노드에 연결되는 NMOS 게이트를 제어하고, 그 각각은 여분의 컬럼 인에이블 신호를 발생시킬 수 있다. Y 어드레스가 퓨즈 프로그래밍 패턴에 일치할 때, 전류 Y 어드레스에 대응하는 컬럼이 여분 컬럼으로 변화되는 것을 표시하기 위하여 컬럼 인에이블 신호(COL\_RED\_EN)는 높게 유지된다. 이러한 여분의 탐지 회로 때문에, 노멀(normal) 및 여분의 컬럼 경로 사이의 시간은 보통 서로 상이하다. 부가적인 논리회로가 시간차이를 조정하기 위해 필요하다. 즉, 여분 경로의 지연에 대해 보상하기 위해 노멀 어드레스 신호 경로에 시간 지연 회로가 사용되어야 한다.

또 다른 기술인 시프트 대치 Y 디코더는 Y 디코더 내의 퓨즈를 사용하나 신호 경로에 연결되지 않는다. 일반적으로, 두 개의 Y 선택 라인이 하나의 퓨즈 그룹을 공유한다. 컬럼을 대치하기 위하여, 컬럼은 Y 디코더 내의 퓨즈를 끊음으로써 디스에이블된다. 결합있는 블록에 대해 Y 드라이버 액세스를 근처의 드라이버로 시프트함으로써 대치가 완성된다. 이러한 시스템의 이점은 퓨즈가 컬럼 어드레스 경로에 연결되지 않기 때문에 노멀 및 여분의 경로 사이에 시간 차이가 존재하지 않는다는 점이다. 더욱이, 블록 대치가 가능하다(고장난 컬럼은 각 블록에서 각 블록의 서로 다른 디코딩으로 수리될 수 있다). 이러한 시스템의 단점은 두 개의 인접한 Y 선택 라인을 동시에 대치하여야 되며, 이 방법은 다른 방법보다 덜 유연하다. 더욱이, 한 방향의 시프트가 컬럼에 요구된다.

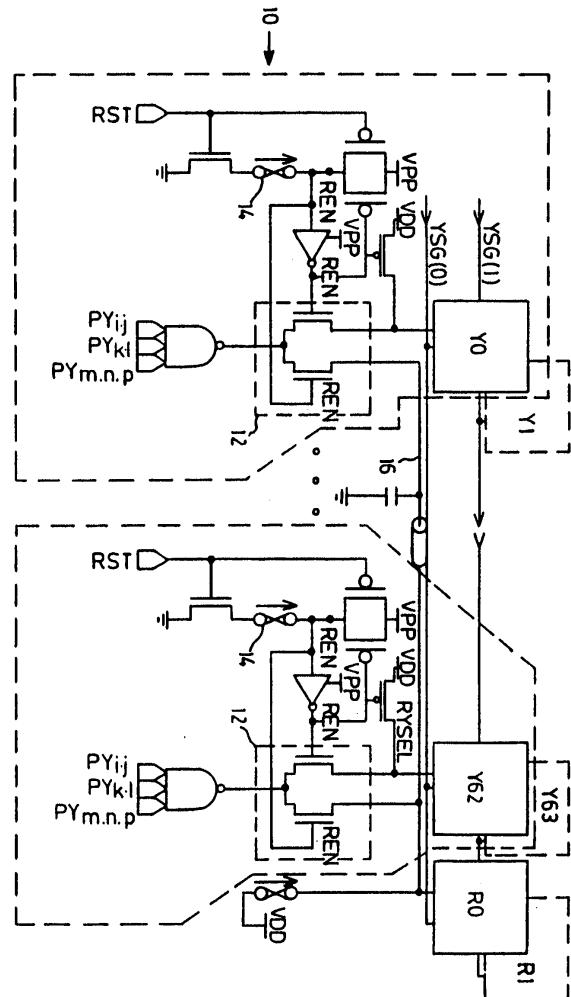

도 3에서, 여분의 회로(10)은 챙 등에 의해 MOSAID Technologies Inc.로 양도된 미국특허출원 제08/904,153호에 개시된 발명의 실시예에 따른 어드레스 스티어링 방식을 사용하여 실행된다. 이러한 접근방식에서, 각 Y 디코더는 컬럼 선택 신호를 퓨즈 회로(14)에 프로그램되어 있는 정보에 따라 노멀 또는 여분의 경로 아래로 향하게 하는 NMOS 멀티플렉서(12)로 구성된다. 멀티플렉서에 있는 NMOS 트랜지스터는 이들을 턴온하기에 충분하도록 VDD보다 큰 전압을 필요로 하기 때문에, NMOS 트랜지스터는 적절한 경로를 선택하기 위해 온-칩 상승 전압 공급(on-chip boosted voltage supply) VPP에 접속되어 사용된다. 여분의 선택 라인 RYSEL(16)은 길고 상당한 RC 지연을 나타낸다. 이러한 실행에서, 두 개의 여분의 컬럼 드라이버는 64 노멀 컬럼에 의해 접근될 수 있으나, 여분의 드라이버는 그 블록 내에 있는 결합있는 컬럼만을 대치하는데 전용되고 4분원 내의 다른 블록 내에 있는 결합있는 컬럼을 대치하는데에는 사용될 수 없다. 이러한 유연성의 부족은 64M SDRAM의 밀도에서 256M SDRAM의 밀도로 이동하는 것을 어렵게 한다. 더욱이, RYSEL 라인(16)의 길이는 256M 세대 SDRAM의 설계를 늦어지도록 한다.

그러므로, 노멀 및 여분의 컬럼 경로 사이의 시간 차이를 감소시키고 퓨즈의 수를 감소시키며, 결합있는 컬럼을 수리하는데 더욱 유연성이 있고 큰 메모리의 속도 요구에 적응할 수 있는 여분의 방식이 필요하다는 것을 알 수 있다.

## 발명의 상세한 설명

본 발명의 목적은 노멀 어드레스 경로 및 여분의 컬럼 어드레스 경로 사이의 시간 차이를 최소화하고 결합있는 컬럼을 수리하는데 있어서 절단되도록 요구되는 퓨즈의 수를 최소화하는 여분의 컬럼 방법 및 장치를 제공하는데 있다.

본 발명에 따라

- (a) 컬럼 클럭 신호에 응답하며, 노멀 컬럼 디코더들에 의해 선택적으로 인에이블되는 다수의 노멀 메모리 컬럼;

- (b) 컬럼 클럭 신호에 응답하며, 여분의 컬럼 디코더들에 의해 선택적으로 인에이블되는 여분의 메모리 컬럼들; 및

- (c) 여분의 컬럼 디코더로부터의 출력에 응답하여 노멀 드라이버 또는 여분의 드라이버에 대응하는 컬럼 클럭 신호를 스위칭하는 로컬 신호 분배 회로

를 포함하는 반도체 메모리 장치가 제공된다.

## 실시예

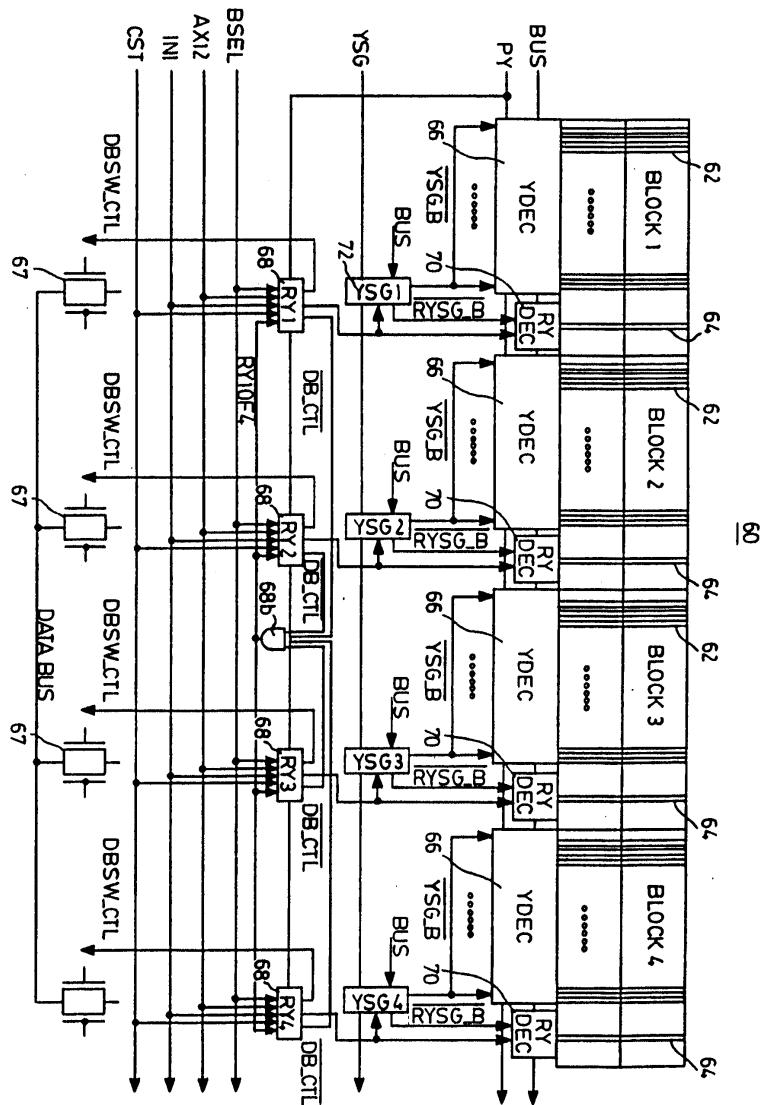

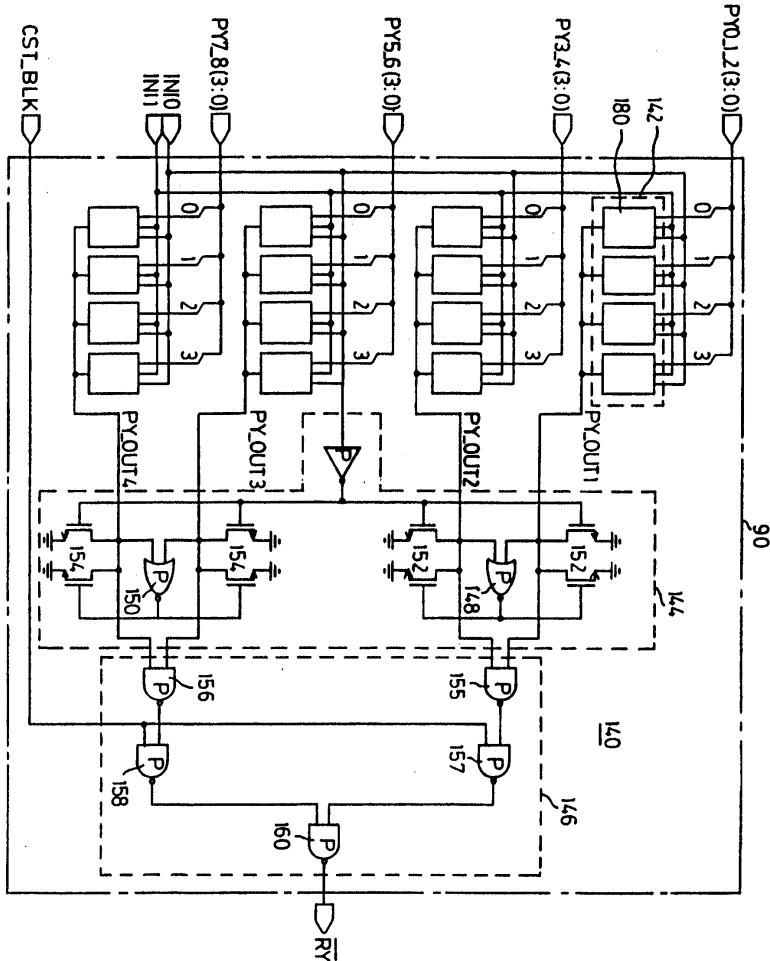

하기의 상세한 설명에서, 하기의 도면에서 유사한 참조번호는 유사한 소자를 언급한다. 도 4를 참조하면, 본 발명의 일반적인 실시예에 따른 여분의 컬럼 구조를 실행시키는 SDRAM의 일부의 구조는 참조번호 60으로 표시되어 있다. 더욱 상세

하계는 도시된 여분의 컬럼 구조는 뱅크 당  $16 \times 32$  블록, 즉, 로우라인 16 블록과 컬럼 32 블록을 가진 4 개의 뱅크로 분리된 메모리 칩에 있는 256M(Mbit) SDRAM이다. 각 뱅크는 16개의 컬럼 블록을 갖는 각 1/2 뱅크가 있는 로우 디코더에 의해 컬럼 방향에 있는 두개의 1/2 뱅크 내로 물리적으로 분리된다. 각 블록은 64개의 노멀 컬럼(62)와 하나의 여분 컬럼을 포함한다. 부품(60)은 블록 1, 블록 2, 블록 3 및 블록 4로 열거된 블록을 가지며, 이러한 구조는 1/2 뱅크에 대해 4번 반복되고 전체 뱅크에 대해 8번 반복된다. 각 블록에 결합된 여분의 컬럼(64)은 그 우측에 있다. 각 블록은 코어 Y 디코더 드라이버 회로 YDEC(66)(코어 회로란 메모리 어레이에 물리적으로 및 기능적으로 결합된 회로를 말하며, 컬럼과 Y는 교환되어 사용된다) 및 단일 코어 여분 디코더 RY(68)과 드라이버 RYDEC(70)을 갖는다. 코어 Y 디코더(66)은 칩에 대한 전체 Y 디코딩의 제2단계이다. 코어 Y 디코더(66)는 Y 프리디코더(predecoder)(도시되지 않음) 출력 PY로부터 그 입력을 받고 컬럼 디코딩을 완성한다. 컬럼 디코딩의 제1단계는, 글로벌 컬럼 어드레스 신호 ACL[0:8](도시되지 않음)으로부터 다음의 프리디코드된 Y 어드레스를 발생시키는 Y 프리디코터에 의해 수행된다: PY0\_1\_2(7:0), PY3\_4(3:0), PY5\_6(3:0), PY7\_8(3:0). 이러한 모든 어드레스는 일반적으로 프리디코드된 어드레스 신호를 코어 Y 디코더(60) 및 코어 Y 여분 회로(70)으로 전달하는 버스 PY로서 도 4에 도시되어 있다. SDRAM 분야에서 모두 잘 알려져 있는 Y 어드레스 래치(latch), 버스트 제어(burst control), 인터리브 제어(interleave control), 연속적인 버스트(sequential burst), 인터리브 버스트(interleave burst) 및 Y 어드레스 프리페치(prefetch)와 같은 논리 함수는 모두 Y 프리디코더 회로 내에서 실행된다.

상술한 바와 같이, 각 블록은 각 블록의 측면에 위치한 하나의 Y 여분 컬럼(64) 및 디코더 RY(68)을 갖는다. Y 여분 디코더 및 그 대응 블록 코어 Y 디코더는 동일한 블록 선택 신호(BSEL)를 공유한다. 그 결과, 블록 선택 신호 BSEL를 변화시킴으로써, 하나의 블록 내에 있는 여분의 컬럼은 뱅크 내의 인접한 4개의 블록에 있는 결합있는 노멀 컬럼을 대체하는데 사용될 수 있으며, 하기에 상세히 설명될 것이다. 코어 Y 디코더(66) 및 여분의 컬럼(64)는 통상적인 Y 선택 클럭 신호 YSG에 의해 클러된다. 4개의 관련되는 여분의 Y 디코더, 코어 Y 디코더에 대한 그들의 관계 및 코어 I/Os의 전체구조는 도 4에 도시되어 있다.

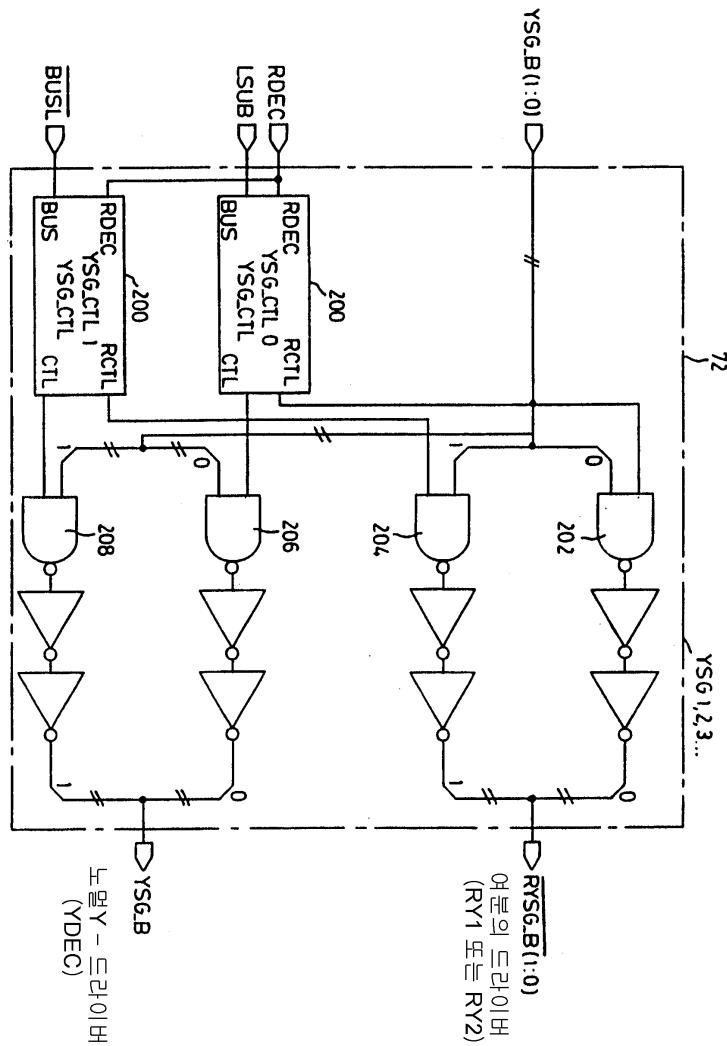

본 실시예에서, YSG 신호는 국소적으로 분배된다. 뱅크의 중심에 있는 YSG 신호 드라이버는 전체 뱅크를 통하여 YSG 신호를 통과한다. YSG1, YSG2, YSG3 등으로 표시되고, 도 10에 상세하게 도시되어 있는 로컬 YSG 신호 분배 회로가 각 블록에 제공된다. 각 로컬 YSG 신호 분포 회로(72)는 노멀 코어 Y 디코더 또는 여분의 Y 디코더로부터의 출력 RDEC에 응답하는 대응 Y 디코더(68)에 YSG 신호를 스위칭하고 구동한다. YSG 신호 분포 회로 YSG1, YSG2, YSG3 등은 도 10에 도시된 바와 같이 2 클럭 사이클에 대한 그 대응하는 여분의 Y 디코더 출력 RDEC를 래치하기 위해 BUSL 및  $\overline{BUSL}$  신호에 의해 클러된다. 만일, 래치된 논리값이 높으면, YSG 신호는 여분 컬럼(64)를 구동하도록 여분의 Y 디코더에 스위치된다. 만일, 래치된 논리값이 낮으면, YSG 신호는 노말 컬럼을 구동하도록 코어 Y 디코더에 스위치된다.

일반적으로, 인접한 홀수 또는 짝수의 블록 내의 4개의 여분 디코더는 모두 4개의 블록에 의해 공유되어 상기 4개의 블록 내의 잘못된 컬럼을 대치하기 위해 사용될 수 있다. 여분의 Y 디코더의  $\overline{DB\_CTL}$  출력은 4개의 입력 AND 게이트(68b)에 연결된다. 이 게이트로부터의 출력  $\overline{RY10F4}$ 는 네개의 여분 디코더에 의해 공유된다. 그러므로, 여분의 Y 디코더는 작동되고 있을 때, 그 출력 신호  $\overline{DB\_CTL}$ 은 낮게 설정되며, 그러므로  $\overline{RY10F4}$ 는 여분의 Y 디코더가 사용되는 것을 코어-I/O 회로(코어 데이터 경로 회로)에게 전달하기 위해 낮게 설정된다.

위치하는 블록내에서 노멀 컬럼이 선택될 때, BSEL 신호는 높게 된다. 대응하는 코어-I/O가 인에이블되도록 할 필요가 있으며 코어-I/O 제어 신호 DBSW\_CTL은 높게 된다. 만일, 선택된 노멀 컬럼이 불량하다면, 전류 블록의 내부 또는 외부의 여분의 Y 디코더에 의해 대치될 수 있다. 이것이 실패한 경우 BSEL은 아직 높다 해도 이 결합의 경우에, DBSW\_CTL이 높게 되거나 낮게 되는 것은 결합이 치환되는 위치에 의존한다. DBSW\_CTL 신호는 선택된 컬럼을 데이터 버스에 결합하기 위해 적절한 데이터 버스 패스 게이트(67)를 스위칭한다.  $\overline{RY10F4}$ , BSEL 및  $\overline{DB\_CTL}$ 은 모두 도 6에 도시된 여분의 디코더에 입력되어 출력 DBSW\_CTL을 결정하는데 사용되며, 코어 I/O 스위치를 제어한다. 코어-I/O 스위치의 작동 규칙은 하기 표에 기재되어 있다.

[표 1]

| 입력       |      | 출력        |

|----------|------|-----------|

| $RY10F4$ | BSEL | $DB\_CTL$ |

|   |   |   |   |

|---|---|---|---|

| 0 | 0 | 0 | 1 |

|   |   | 1 | 0 |

| 0 | 1 | 0 | 1 |

|   |   | 1 | 0 |

| 1 | 0 | 1 | 0 |

|   |   | 1 | 1 |

여기에는 256M SDRAM 실시예가 설명되어 있고, 모든 제어신호 및 데이터 버스의 두 가지 버전(version)이 있으며, 그 하나는 B0로 표시되고 다른 하나는 B1으로 표시된다. B0 신호가 활동하는 동안 B1 신호는 미리 충전되고, B1 신호가 활동하는 동안 B0 신호는 미리 충전된다. 그러므로, 보다 고속작동을 위한 예충전(precharge) 시간을 숨기게 된다. 이러한

이중 데이터 버스 구조는 MOSAID Technologies에 양도된 미국특허 제5,416,743호에 개시되어 있다. BUSL 및  $\overline{BUSL}$  신호는 BO 및 B1 신호 사이에서 토클(toggling)을 제어한다.

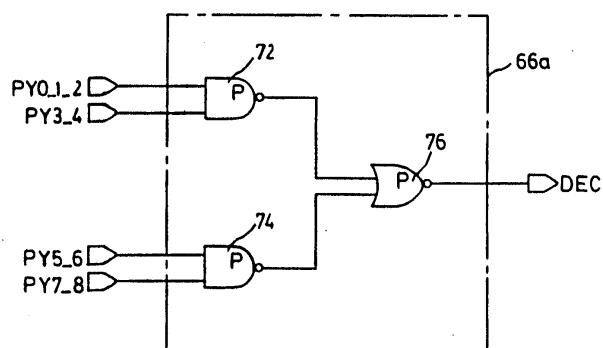

도 5a 및 5b에, 코어 Y 디코더(66a) 및 Y 드라이버(66b)의 개략도가 도시되어 있다. 조합된 회로는 도 4의 블록(66)에 개략적으로 도시되어 있다. 코어 Y 디코더(66a)는 Y 프리디코더 출력 PY0\_1\_2, PY3\_4, PY5\_6 및 PY7\_8를 수신하기 위해 한 쌍의 NAND 게이트(72 및 74)를 포함한다. NAND 게이트(72 및 74)로부터 나온 출력은 디코드된 출력 신호 DEC를 제공하기 위해 NOR 게이트 내에서 조합된다. 디코더 회로(66a)는 4개의 입력 AND 게이트와 등가이다. 코어 Y 디코더 DEC로부터 나온 출력은 도 5a에 도시된 바와 같이 컬럼 드라이버 회로(66b)에 결합된다.

노멀 또는 여분의 컬럼 드라이버(66b)는 신호 BUSL 및  $\overline{BUSL}$ 에 연결된 출력 신호 DEC에 의해 제어되는 각 CMOS 패스 게이트(82 및 84)에서 Y 클럭 인에이블 신호  $\overline{YSG\_B0}$  및  $\overline{YSG\_B1}$ 을 수신한다. 클럭 신호  $\overline{YSG\_B0}$  및  $\overline{YSG\_B1}$ 는 적당한 시간에 CMOS 게이트를 통하여 인버터(86)에 이르고, 이 인버터(86)은 BUSL 및  $\overline{BUSL}$ 의 상태에 의존하는 신호 Y\_B0 또는 Y\_B1이 있는 대응 컬럼을 구동시킨다. 그러므로, 디코드된 신호 DEC는 패스 게이트(82 및 84)를 제어한다.

도 4에 도시된 전체 코어 Y 디코더 YDEC(66)는 도 5a 및 5b에 도시된 두 성분으로 이루어질 수 있다. 예를 들면, 만일 Y 어드레스가 9개의 비트(bit)를 갖는다면, 512개의 서로 다른 디코딩 출력을 갖게 된다. 짹수의 비트와 홀수의 비트는 각각 네개의 짹수 블록과 네개의 홀수 블록을 구동하도록 분리될 수 있다. 그 배열은 1/2 뱅크에 대해 완전한 코어 폭의 디코더를 실현시키기 위해 2회 또는 전체 뱅크에 대해 4회 반복할 것이다.

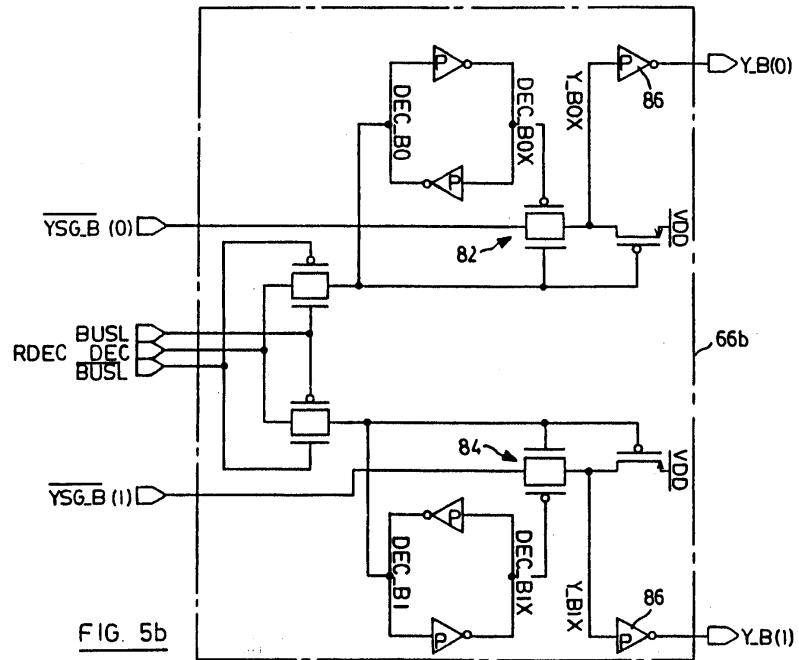

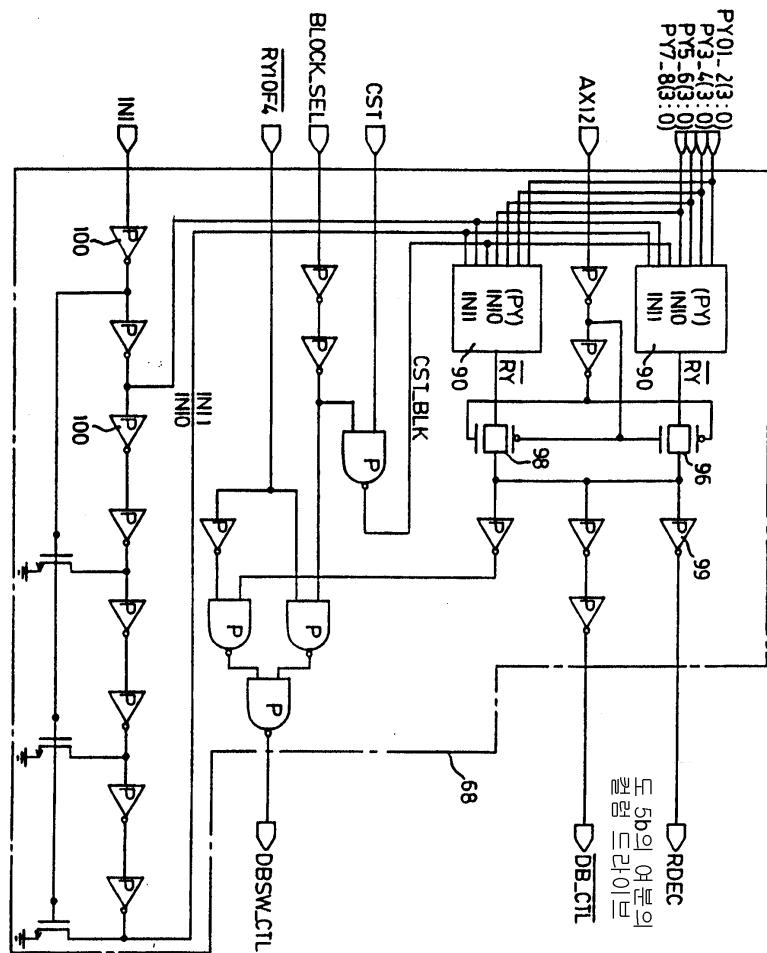

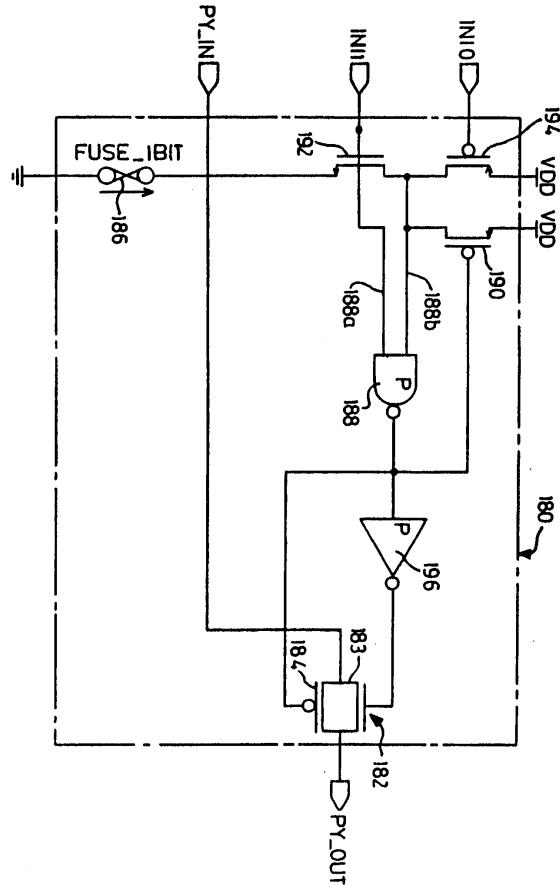

다시 도 6을 참조하면, 도 4의 여분 디코더 RY(68)의 상세도가 도시되어 있다. 여분의 Y 디코더 RY1, RY2, ..., RYN은 여분 컬럼에 액세스가 요구되는지 아닌지를 판정한다. 이러한 여분의 Y 디코더는 이러한 결정을 하기 위해 어드레스 비교 구조를 이용한다. 반복해서 말하면, 각 메모리 블록은 각 블록의 측면에 위치된 하나의 여분의 컬럼을 갖는다. 여분 디코더 RY 및 그 대응 코어 Y 디코더 YDEC은 동일한 블록 선택 신호(BSEL)를 공유한다. 도 6에 도시된 여분 디코더 RY는 프리디코더된 어드레스 PY0\_1\_2, PY3\_4, PY5\_6 및 PY7\_8를 수신하는 한 쌍의 어드레스 비교회로(90)를 포함한다. 각 어드레스 비교회로(90)는 단일 어드레스로 프로그램될 수 있으며, 따라서 여분의 Y 디코더는 두 개의 여분의 어드레스에 프로그램될 수 있다. 어드레스 비교회로(92 및 94)의 상세한 설명은 도 8을 참조하여 설명될 것이다.

노멀 컬럼은 블록 내의 상부 또는 하부에 분리되어 어드레스될 수 있기 때문에, 로우 어드레스 신호 AX12는 상부 또는 하부의 컬럼부 선택을 수행하도록 여분의 Y 디코더에 제공된다. 로우 어드레스 신호 AX12는 어드레스 비교회로(92 및 94)로부터의 각 출력을 수신하는 한 쌍의 CMOS 패스 게이트(96 및 98)의 입력을 제어하기 위해 결합된다. 그러므로, 하나의 여분의 컬럼은 두 개의 서로 다른 어드레스에 노멀 컬럼의 상부 1/2 및 하부 1/2를 대치하는데 또는 그 역으로 사용될 수 있다.  $\overline{RY}$  신호는 RDEC 신호를 구동시키도록 인버터(99)에 결합되고, 도 5b에 도시된 컬럼 드라이버(66b) 및 도 4에 도시된 YSG 신호 분배 회로를 교대로 구동시킨다.

또한 회로는 INI1 및 INIO 발생 회로를 포함한다. 일반적으로 회로는 주 INI 신호 라인으로부터 분기되는 직렬로 접속되는 인버터(100)의 연결을 가지며, INIO 및 INI1 신호는 연결로부터 텝으로 취해진다.

도 7을 참조하면, 도 6의 어드레스 비교 회로(90)이 상세하게 도시되어 있다. 프리디코더(도 4)는 다음의 프리디코드된 출력의 4개의 그룹을 갖는다: PY0\_1\_2, PY3\_4, PY5\_6 및 PY7\_8, 어드레스 비교 회로는 프로그램 가능한 퓨즈 회로(142)의 4개의 그룹을 포함한다. 퓨즈 회로(142)의 각 그룹은 도 8에 도시된 결합 퓨즈 상태 평가 회로(180)를 가진 네개의 퓨즈를 포함한다. 그룹 내의 성분 퓨즈 평가 회로의 각각에 대한 입력은 각 그룹 내의 프리디코드된 컬럼 어드레스 신호, 즉, PY0\_1\_2, PY3\_4, PY5\_6 및 PY7\_8로부터 유도된다. 그룹(142) 내의 각 퓨즈로부터의 출력 PY\_OUT는 각 신호 PY\_OUT1, PY\_OUT2, PY\_OUT3 및 PY\_OUT4를 제공하기 위해 조합된다. 이러한 신호는 어드레스 조합기(combiner) 회로(146) 내에서 조합되기 전에 초기화(initialization) 회로(144)를 통하여 통과된다. 어드레스 조합기 회로는 필수적으로 도 6에 도시된 여분의 선택 신호  $\overline{RY}$ 를 출력하는 4개의 입력 NAND 게이트이다. 이러한 회로의 각 부분이 하기에서 상세히 설명될 것이다.

회로(90)의 작동은 다음과 같다. 만일, 컬럼에 결합이 없고 여분이 필요없으며, 퓨즈 회로가 끊어지지 않으면, PY\_OUT 라인은 회로의 초기화부(144) 때문에 모두 로직 로우에 초기화될 것이다. 이것은 결합있는 어드레스의 퓨즈가 모든 비결합 컬럼의 퓨즈가 끊어지지 않고 손상되지 않은 채로 남아 있는 종래 기술의 어드레스 비교 설비에 대조된다. 그러한 접근 방식은 여분 프로그래밍 처리를 상당히 복잡하게 한다. 초기화 회로(144)는 연결된 각각이 그 입력에서 각 PY\_OUT 신호를 수신하기 위한 한 쌍의 NOR 게이트(148 및 150)로 구성된다. 각 NOR 게이트 입력은 각 NMOS 트랜지스터(152 및 154)에 결합된다. 이러한 트랜지스터의 게이트는 그들 각각의 NOR 게이트 출력에 연결된다. 그러므로, 로직 로우의 PY\_OUT는 NOR 게이트(148, 150)에 입력되고, 피드백 트랜지스터를 통한 피드백 연결이 입력을 로직 로우로 래치하는 동안에 NOR 게이트의 출력은 로직 하이가 된다. 라인 PY\_OUT 상의 동일한 로직 로우 신호는 NAND 게이트(155 및 156)으로 공급되고 그 출력에서 로직 하이를 발생시킨다. 신호 CST-BLK는 정상적으로 높은 블록 여분 테스트 신호이고, 따라서 NAND 게이트(157 및 158)을 인에이블 시킨다. 로직 하이에서 NAND 게이트(155 및 156)로부터 나온 출력이 로직 하이이고 CST-BLK 신호가 로직 하이라면, NAND 게이트(157 및 158)로부터의 양 출력이 로직 로우이며, 사용되지 않는

여분을 나타내는 NAND 게이트(160)의 외부로 로직 하이를 교대로 발생시킨다. 즉,  $\overline{RY}$ 는 로직 하이에 있다.

만일, 테스트하는 동안 잘못된 위치가 검출되면, 적절한 프리디코더 컬럼 어드레스는 전술한 퓨즈 회로 그룹의 각각으로 프로그램된다. 어드레스 비교 회로 출력이 초기화 장치에 우선하기 때문에(이 처리는 또한 상세하게 후술한다), 프로그래밍 신호 라인 PY\_OUT1, PY\_OUT2, PY\_OUT3 및 PY\_OUT4는 프리티코드된 신호를 수신하고 전부 로직 하이로 설정된다. 이 공정은 하기에서 더욱 상세히 설명될 것이다. 따라서, 두 개의 로직 하이 입력이 NAND 게이트(155 및 156)에 적용되기 때문에, 각각은 로직 로우 출력을 제공하고, 이 로우 출력이 NAND 게이트(157 및 158)에 있는 노멀 하이 CST\_Blk 신호에 조합될 때 두 개의 로직 하이 입력 신호를 NAND 게이트에 제공하며, 여분의 사용을 나타내는 활성 로우 출력 신호

$\overline{RY}$ 를 교대로 제공한다. 본 발명의 일실시예에서, 첫째로 만일 결합있는 어드레스가 검출되지 않을 때 퓨즈는 끊어질 필요가 없고, 반면에 도 1에 도시되어 있는 어드레스 비교 방식의 종래기술에서는 모든 퓨즈가 끊어지게 된다는 점이 중요하다. 둘째로 만일 결합있는 어드레스가 검출된다면 결합있는 어드레스를 프로그램하기 위해, 본 발명의 실시예에서 종래의 어드레스 비교 구조에서 12개의 퓨즈에 비하여 단지 4 개의 퓨즈 만이 끊어지게 된다. 이러한 차이점은 여분 프로그래밍 가능한 단순화를 나타낸다.

도 8을 참조하면, 도 7의 퓨즈 상태 평가 회로(180)의 상세도가 도시되어 있다. 상술한 바와 같이, 회로(180)는 각각 NMOS 및 PMOS 트랜지스터(183 및 184)에 의해 형성된 CMOS 패스 게이트(182)에 교대로 연결된 PY\_IN 터미널 상에 프리디코드된 어드레스 신호의 하나를 수신한다. CMOS 패스 게이트(182)의 출력은 신호 PY\_OUT이다. 패스 게이트(183 및 184)는 퓨즈 소자(186)에 의해 제어된다. 패스 게이트(182)의 초기 조건은 NAND 게이트(188)에 의해 설정되고 신호 INI0 및 INI1로부터 수신된 입력에 의해 결정되는 초기 조건을 교대로 갖는다. INI0 및 INI1 신호는 도 6에 도시되는 바와 같이 INI1에 선행하는 INI0를 가진 또 다른 약간 지연된 버전이다.

피드백 PMOS 트랜지스터(190)은 NAND 게이트(188)의 추력에 연결되는 게이트를 갖고 그 드레인은 NAND 게이트(188)의 입력(188b)의 하나에 연결되며 하프 래치를 형성한다. 피드백 트랜지스터(190)는 프로그램된 여분 어드레스를 래치하기 위해 사용된다. INI1 신호는 NAND 게이트(188)의 다른 입력(188a) 및 그 다른 단부가 그라운드에 연결된 퓨즈(186)의 일단부에 연결된 소스를 갖는 NMOS 트랜지스터(192)의 게이트에 직접 적용된다. NMOS 트랜지스터(192)의 드레인 터미널은  $V_{DD}$  공급기에 연결된 소스를 교대로 갖는 PMOS 트랜지스터(194)의 드레인 터미널에 연결된다. INI0 신호

는 PMOS 트랜지스터(194)의 게이트에 적용된다. PMOS 트랜지스터(194)와 NMOS 트랜지스터(192) 사이의 공통 드레인 연결은 NAND 게이트(188)의 제1 입력(188b)에 연결된다. NAND 게이트(188)로부터의 출력은 인버터(196)을 경유하여 접속되고 패스 게이트 트랜지스터(183)의 하나를 구동한다.

퓨즈 상태는 하기와 같이 평가된다. 신호 INI0 및 INI1은 POWER\_OK 신호로부터 발생되고 INI1은 INI0으로부터 지연된다. 초기에, INI0 및 INI1의 양자는 로우이고, CMOS 전송 게이트는 개방되어 있으며, 프리디코드된 신호는 통과할 수 없다. 일반적인 작동에서, 만일, 퓨즈가 끊어지지 않았다면, 일단 INI0 및 INI1 양자는 하이가 되고, CMOS 전송 게이트는 개방 상태를 유지한다. 반면에, 만일 퓨즈가 끊어졌다면 CMOS 전송 게이트는 폐쇄되고 프리디코드된 신호 PY\_IN은 여분의 프리디코드된 어드레스 신호 PY\_OUT로서 통과된다.

도 6을 참조하여 상술한 바와 같이, 신호 INI0 및 INI1의 변화 사이에 지연이 있다. INI0로부터 INI1의 지연은 퓨즈가 손상되지 않을 때 공급 전압 V<sub>DD</sub>로부터 퓨즈(186)를 통하여 그라운드에 흐르는 DC 전류가 없다는 것을 보증한다. 전술한 바와 같이, 피드백 트랜지스터(190)는 패스 게이트(182)에 대하여 퓨즈 회로의 여분의 상태를 래치하는데 사용된다. 통상적으로, 종래의 회로에서 이러한 PMOS 장치(190)는 하프 래치의 용이한 리셋트가 가능하도록 상당히 길다. 그러나, 긴 채널 트랜지스터는 더욱 많은 전력을 소비하는 경향이 있고 짧은 채널에 비하여 많은 영역을 차지한다. 지연된 초기화 신호 INI0 및 INI1의 역할은 또한 피드백 트랜지스터(190)의 크기를 보통 크기로 감소시키는 것이다. 이러한 실행은 퓨즈 평가를 하는 동안 전류 소모를 감소시킨다. 더욱이, INI0 및 INI1 신호의 지연된 활동은 다음과 같은 회피된 레이스(race) 조건을 피한다: 만일 INI0 및 INI1이 로우로부터 하이로 변화하는 동안 하나이고 동일 신호라면, 양 장치(194 및 192)가 도통된다. 장치(194)는 퓨즈 저항에 기인하여 장치(192)를 통하여 풀-다운(pull-down) 보다 빠르게 풀-업(pull-up)할 수 있기 때문에, 노드(188b)로 하이를 유지하려는 경향이 있고, 일단 INI1이 하이에 충분히 있게 되면, NAND 게이트(188)로 입력되는 양 입력은 하이가 되고, 그 출력 로우를 풀링(pulling)하고 트랜지스터(190)를 턴온시킨다. 그러나, 트랜지스터(190)가 턴온되어 있는 동안, 트랜지스터(192) 또한 턴온되어 VDD로부터 그라운드로 가는 경로를 생성하고 퓨즈는 끊어지지 않은 것으로 가정한다. 그러므로, 194, 192 및 190의 턴온 사이에 레이스가 있다. 반대로, INI0 및 INI1의 변화를 엇갈리게 함으로써, INI0은 먼저 로우로부터 하이로 가고 그 후 지연되며, 또한 INI1은 로우로부터 하이로 가고, 후속되는 작동은 상기 레이스 조건을 피한다. INI0가 초기에 로우임에도 불구하고, 장치(194)는 전력이 상승되어 온 상태에 있게 된다. INI0가 로우에서 하이로 가기 때문에, 장치(194)는 턴오프되고, 노드(188b)는 일시적으로 하이에 떠 있는 상태에 남게된다. INI1은 아직 로우에 있다는 사실 때문에, 188의 출력은 아직 하이에 있고 장치(190)은 오프 상태에 있다. INI1가 로우로부터 하이로 변화를 시작할 때(실제적인 작동에서 순간적인 사각형과 형태의 변화를 하는 로직 변화는 될 수 없기 때문에, 항상 약간 지연되어 점점 램프형 변화가 될 것이다), 트랜지스터(192)는 턴온을 시작하고 노드(188b)는 장치(194)와 마찰이 없기 때문에 용이하게 방전된다. 그 결과, INI1(노드 188a)가 로우로부터 하이로 갈 때, 노드(188b)는 떠 있는 하이로부터 로우로 가며, 따라서, 퓨즈가 끊어지지 않는 한 NAND 게이트(188)의 출력은 하이로 남게되고, 트랜지스터(190)은 턴온되지 않을 것이며, 패스 게이트(182)는 오프 상태가 될 것이다. 그 결과, PY\_IN 신호는 패스 게이트를 통하여 패스되지 않을 것이고, PY\_OUT 터미널 신호는 상술한 바와 같은 초기화된 상태로에 남을 것이다.

만일, 퓨즈가 끊어진다면, NAND 게이트(188)의 입력(188b)는 로직 로우 레벨로 풀링되지 않는다. 그 결과, NAND 게이트(188)의 양 입력(188a 및 188b)는 로직 하이에 있고, 그 결과 NAND 게이트로부터 로직 로우 출력이 된다. 이러한 로직 로우 출력은 트랜지스터(190)의 턴온을 통하여 래치되고 CMOS 패스 게이트(182)를 기능하게 한다. 그 결과, 여분의 작동(퓨즈가 끊어진)에 대하여, 패스 게이트(182)는 신호 PY\_IN이 신호 PY\_OUT를 통하여 통과하는 것을 가능하게 하고, 도 7에 도시된 대응 예충전 라인 상에 예충전 값을 무효로 한다. 단지 고장난 어드레스의 퓨즈만이 끊어질 필요가 있으며 비결함 어드레스의 퓨즈는 끊어질 필요가 없다는 것은 중요하다.

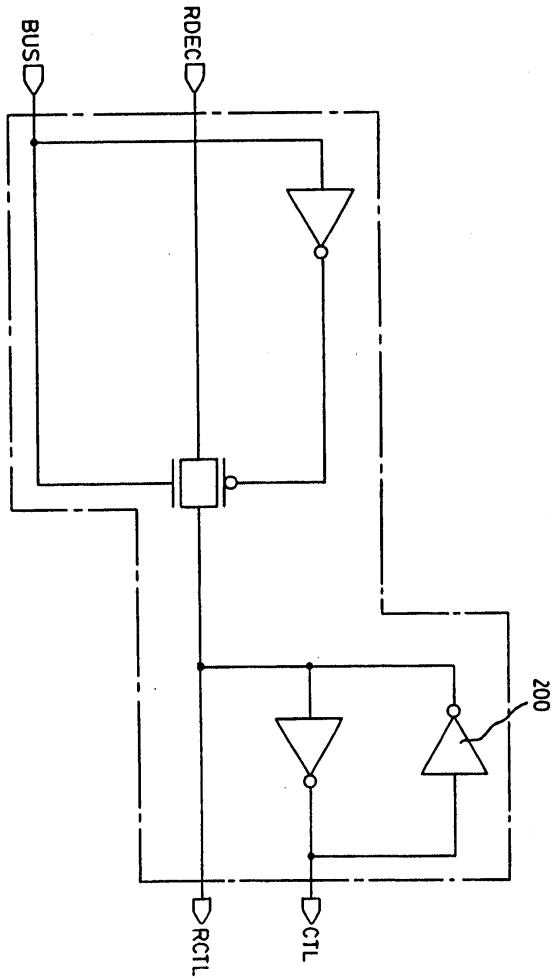

도 9를 참조하면, YSG 스위칭 회로(72)(도 4)가 상세히 도시되어 있다. 스위칭 회로는 입력 RDEC 신호를 래치하고 지연하기 위해 결합된 한 쌍의 YSG 래치(200)를 포함한다. YSG 신호는 이중 데이터 버스 구조에 기인하여 두 개의 클럭 사이클 동안 유지된다. 출력  $\overline{\text{RYSG}_B}(1:0)$  및  $\overline{\text{YSG}_B}(1:0)$ 은 여분의 드라이버(70) 및 노멀 Y 드라이버에 각각 결합된다. 래치(200)로부터의 RCTL(여분의 디코더 제어) 출력은 각 게이트(202 및 204)의 입력에 결합되고, CTL(디코더 제어) 출력은 제2의 한 쌍의 NAND 게이트(206 및 208)의 입력에 결합된다. NAND 게이트(202, 204 및 206, 208)의 양 세트는 그들의 다른 입력의 하나에서 YSG 신호를 수신한다. 도 10을 참조하면, YSG 래치(200)는 보완하는 극성을 갖는 출력 RCTL 및 CTL을 갖는다. 그러므로, NAND 게이트(202, 204 및 206, 208)는 RYSG\_B 또는 YSG\_B에 YSG 신호를 스위칭하는 역할을 한다.

본 발명은 그 특수한 실시예와 관련되어 설명되었지만, 첨부된 청구범위의 사상 및 범주를 벗어나지 않고 본 발명이 속하는 기술분야의 당업자에 의해 특수한 사용 다양한 변형 등이 가능할 것이다. 예를 들면, 노멀 Y 드라이버의 그룹에 결합된

여분의 Y 드라이버의 수는 변화될 수 있다. 더욱이, 컬럼 여분 시스템은 DRAMs, SDRAMs, SGRAMs 등과 같은 모든 유형의 RAMs에 적용될 수 있다. 또한, 이와 유사하게, 회로에 대한 잘 알려져 있는 변경을 함으로써, 여기에 기술되어 있는 여분 시스템은 로우 여분을 수행하는데 적용될 수 있다.

본 명세서에 사용된 용어 및 표현은 그 설명을 용이하게 하기 위한 것이며 그것에 한정되지 아니하고, 그러한 용어 및 표현으로 기술된 특징과 균등한 것을 배제하기 위한 의도가 아니며, 본 발명의 청구범위의 범위 내에서 다양한 변형이 가능하다는 것을 알 수 있을 것이다.

## 도면의 간단한 설명

하기의 도면과 상세한 설명을 참조하여 본 발명은 더욱 잘 이해될 것이다.

도 1은 종래기술에 따른 여분의 프로그래밍 회로.

도 2는 종래기술에 따른 또 다른 여분의 프로그래밍 회로.

도 3은 종래기술에 따른 여분의 어드레스 스티어링 구조의 개략도.

도 4는 본 발명의 일실시예에 따른 여분의 컬럼 구조를 갖는 반도체 메모리의 일부의 배치를 나타낸 평면도.

도 5a는 본 발명의 일실시예에 따른 노멀 컬럼 디코더의 개략도.

도 5b는 본 발명의 일실시예에 따른 컬럼 드라이버의 개략도.

도 6은 본 발명의 일실시예에 따른 여분의 컬럼 디코더의 개략도.

도 7은 본 발명의 일실시예에 따른 어드레스 비교 회로의 개략도.

도 8은 본 발명의 일실시예에 따른 퓨즈 평가 회로의 개략도.

도 9는 본 발명의 일실시예에 따른 컬럼 클럭 분배 회로의 개략도.

도 10은 본 발명의 일실시예에 따른 여분의 디코더 래치의 개략도.

## 도면

도면1

도면2

도면3

도면4

도면5a

## 도면5b

도면6

도면7

도면8

도면9

도면10