(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第6027905号

(P6027905)

(45) 発行日 平成28年11月16日(2016.11.16)

(24) 登録日 平成28年10月21日(2016.10.21)

|               |           |              |       |

|---------------|-----------|--------------|-------|

| (51) Int.Cl.  | F 1       |              |       |

| HO 1 L 25/065 | (2006.01) | HO 1 L 25/08 | Z     |

| HO 1 L 25/07  | (2006.01) | HO 1 L 21/92 | 602 E |

| HO 1 L 25/18  | (2006.01) | HO 1 Q 1/38  |       |

| HO 1 L 21/60  | (2006.01) |              |       |

| HO 1 Q 1/38   | (2006.01) |              |       |

請求項の数 9 (全 19 頁)

|           |                               |

|-----------|-------------------------------|

| (21) 出願番号 | 特願2013-16676 (P2013-16676)    |

| (22) 出願日  | 平成25年1月31日 (2013.1.31)        |

| (65) 公開番号 | 特開2014-150102 (P2014-150102A) |

| (43) 公開日  | 平成26年8月21日 (2014.8.21)        |

| 審査請求日     | 平成27年11月30日 (2015.11.30)      |

|           |                                           |

|-----------|-------------------------------------------|

| (73) 特許権者 | 000190688<br>新光電気工業株式会社<br>長野県長野市小島田町80番地 |

| (74) 代理人  | 100068755<br>弁理士 恩田 博宣                    |

| (74) 代理人  | 100105957<br>弁理士 恩田 誠                     |

| (72) 発明者  | 窪田 和之<br>長野県長野市小島田町80番地 新光電気<br>工業 株式会社 内 |

| (72) 発明者  | 藤井 朋治<br>長野県長野市小島田町80番地 新光電気<br>工業 株式会社 内 |

審査官 秋山 直人

最終頁に続く

(54) 【発明の名称】半導体装置

## (57) 【特許請求の範囲】

## 【請求項 1】

第1基板と、

前記第1基板に接合された第2基板と、

前記第1基板と前記第2基板との間に設けられ、前記第1基板と前記第2基板とを電気的に接続するはんだボールと、

前記第1基板及び前記第2基板の少なくとも一方に配置された電子部品と、

前記第1基板の第1面に接して前記第1基板の第1面上に形成された第1配線部と、

前記第1基板の第1面と該第1面と反対側の第2面との間を貫通し、前記第1配線部及び前記はんだボールと電気的に接続された第1貫通電極と、

前記第2基板の第1面に接して前記第2基板の第1面上に形成された第2配線部と、

前記第2基板の第1面と該第1面と反対側の第2面との間を貫通し、前記第2配線部及び前記はんだボールと電気的に接続された第2貫通電極と、

前記第1基板の第2面に接して前記第1基板の第2面上に形成され、前記第1貫通電極と接続されるとともに前記はんだボールと接続された第1配線パターンと、

前記第2基板の第2面に接して前記第2基板の第2面上に形成され、前記第2貫通電極と接続されるとともに前記はんだボールと接続された第2配線パターンと、を有し、

前記はんだボールと前記第1配線部と前記第1貫通電極と前記第2配線部と前記第2貫通電極と前記第1配線パターンと前記第2配線パターンとの全てが前記電子部品と電気的に接続されたアンテナとして機能することを特徴とする半導体装置。

10

20

## 【請求項 2】

第 1 基板と、

前記第 1 基板に接合された第 2 基板と、

前記第 1 基板と前記第 2 基板との間に設けられ、前記第 1 基板と前記第 2 基板とを電気的に接続するはんだボールと、

前記第 1 基板及び前記第 2 基板の少なくとも一方に配置された電子部品と、

前記第 1 基板の第 1 面に接して前記第 1 基板の第 1 面上に形成された第 1 配線部と、

前記第 1 基板の第 1 面と該第 1 面と反対側の第 2 面との間を貫通し、前記第 1 配線部及び前記はんだボールと電気的に接続された第 1 貫通電極と、

前記第 1 基板の第 2 面に接して前記第 1 基板の第 2 面上に形成され、前記第 1 貫通電極と接続されるとともに前記はんだボールと接続された第 1 配線パターンと、

前記第 1 基板の第 2 面に対向する前記第 2 基板の第 2 面に接して前記第 2 基板の第 2 面上に形成され、前記はんだボールと電気的に接続された第 2 配線パターンと、を有し、

前記はんだボールと前記第 1 配線部と前記第 1 貫通電極と前記第 1 配線パターンと前記第 2 配線パターンとの全てが前記電子部品と電気的に接続されたアンテナとして機能することを特徴とする半導体装置。

## 【請求項 3】

第 1 基板と、

前記第 1 基板に接合された第 2 基板と、

前記第 1 基板と前記第 2 基板との間に設けられ、前記第 1 基板と前記第 2 基板とを電気的に接続するはんだボールと、

前記第 1 基板及び前記第 2 基板の少なくとも一方に配置された電子部品と、

前記第 1 基板の第 1 面とは反対側の面であって、前記第 2 基板に対向する前記第 1 基板の第 2 面に接して前記第 1 基板の第 2 面上に形成され、前記はんだボールと電気的に接続された第 1 配線パターンと、

前記第 1 基板の第 2 面に対向する前記第 2 基板の第 2 面に接して前記第 2 基板の第 2 面上に形成され、前記はんだボールと電気的に接続された第 2 配線パターンと、を有し、

前記はんだボールと前記第 1 配線パターンと前記第 2 配線パターンとの全てが前記電子部品と電気的に接続されたアンテナとして機能することを特徴とする半導体装置。

## 【請求項 4】

前記はんだボールを複数有し、前記第 1 配線部を複数有し、前記第 1 貫通電極を複数有し、前記第 2 配線部を複数有し、前記第 2 貫通電極を複数有し、前記第 1 配線パターンを複数有し、前記第 2 配線パターンを複数有し、

複数の前記はんだボールと複数の前記第 1 配線部と複数の前記第 1 貫通電極と複数の前記第 2 配線部と複数の前記第 2 貫通電極と複数の前記第 1 配線パターンと複数の前記第 2 配線パターンとの全てが前記アンテナとして機能し、

隣接した一対の前記はんだボールは、前記複数の第 1 配線部のうち、前記隣接する一対のはんだボールに対応する一対の前記第 1 貫通電極に接続された 1 つの前記第 1 配線部を介して接続され、

異なる隣接した一対の前記はんだボールは、前記複数の第 2 配線部のうち、前記異なる隣接した一対のはんだボールに対応する一対の前記第 2 貫通電極に接続された 1 つの前記第 2 配線部を介して接続されていることを特徴とする請求項 1 に記載の半導体装置。

## 【請求項 5】

前記はんだボールを複数有し、前記第 1 配線部を複数有し、前記第 1 貫通電極を複数有し、前記第 2 配線パターンを複数有し、

複数の前記はんだボールと複数の前記第 1 配線部と複数の前記第 1 貫通電極と複数の前記第 2 配線パターンとの全てが前記アンテナとして機能し、

隣接した一対の前記はんだボールは、前記複数の第 1 配線部のうち、前記隣接する一対のはんだボールに対応する一対の前記第 1 貫通電極に接続された 1 つの前記第 1 配線部を介して接続され、

10

20

30

40

50

異なる隣接した一対の前記はんだボールは、前記複数の第2配線パターンのうち、前記異なる隣接した一対のはんだボールに直接接続された1つの前記第2配線パターンを介して接続されていることを特徴とする請求項2に記載の半導体装置。

**【請求項6】**

前記はんだボールを複数有し、前記第1配線パターンを複数有し、前記第2配線パターンを複数有し、

複数の前記はんだボールと複数の前記第1配線パターンと複数の前記第2配線パターンとの全てが前記アンテナとして機能し、

隣接した一対の前記はんだボールは、前記複数の第1配線パターンのうち、前記隣接した一対のはんだボールに直接接続された1つの前記第1配線パターンを介して接続され、

10

異なる隣接した一対の前記はんだボールは、前記複数の第2配線パターンのうち、前記異なる隣接した一対のはんだボールに直接接続された1つの前記第2配線パターンを介して接続されていることを特徴とする請求項3に記載の半導体装置。

**【請求項7】**

前記はんだボールは、コアボールと、前記コアボールの周囲を被覆するはんだとを有するコア付きはんだボールであることを特徴とする請求項1～6のいずれか一項に記載の半導体装置。

**【請求項8】**

前記はんだボールの少なくとも一部は、前記電子部品と同じ高さにあることを特徴とする請求項1～7のいずれか一項に記載の半導体装置。

20

**【請求項9】**

前記電子部品は、前記第1基板の第2面と前記第2基板の第2面との間に配置されていることを特徴とする請求項1～8のいずれか一項に記載の半導体装置。

**【発明の詳細な説明】**

**【技術分野】**

**【0001】**

本発明は、半導体装置に関するものである。

**【背景技術】**

**【0002】**

従来、能動素子や受動素子などの電子部品が実装されてなる半導体装置には様々な構造のものがある。近年、例えば、高周波(RF)通信部や制御部、水晶振動子などを含む無線通信モジュールを有する半導体装置は様々な分野で多用されるようになってきている。このような半導体装置は、アンテナを用いて無線通信を行うため、高周波通信部等と電気的に接続されるアンテナを有している(例えば、特許文献1参照)。

30

**【0003】**

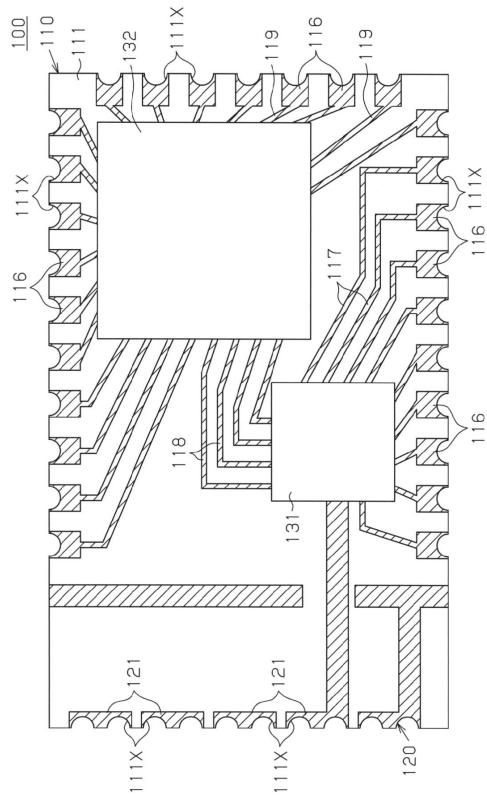

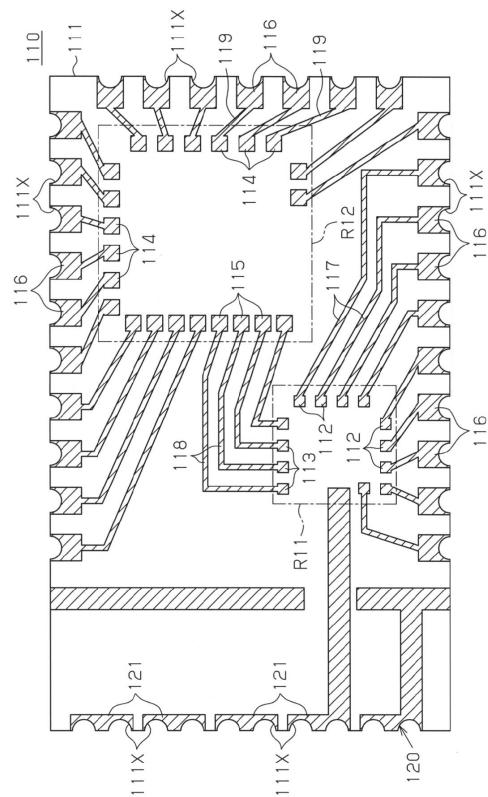

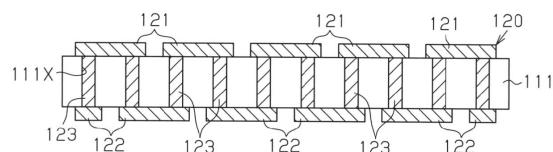

図12は、従来のアンテナ120を有する半導体装置100の平面図を示している。

図12に示すように、従来の半導体装置100は、配線基板110と、その配線基板110に実装されたRFICチップ131及び制御用ICチップ132とを有している。

**【0004】**

図13は、従来の配線基板110の平面図を示している。図13において、R11はRFICチップ131が実装される領域(以下、「RFIC実装領域R11」とする)、R12は制御用ICチップ132が実装される領域(以下、「制御用IC実装領域R12」とする)をそれぞれ示している。

40

**【0005】**

図13に示すように、配線基板110は、基板本体111と、接続パッド112～115と、端面電極116と、配線117～119と、アンテナ120とを有している。基板本体111の側面には、複数の切り欠き部111Xが形成されている。切り欠き部111Xは、半円筒形状とされており、基板本体111の上面から下面に亘るように形成されている。

**【0006】**

50

接続パッド 112, 113 は、RFIC 実装領域 R11 に対応する基板本体 111 の上面に形成され、RFIC チップ 131 と電気的に接続される。接続パッド 112 は、配線 117 を介して、端面電極 116 と電気的に接続されている。また、接続パッド 113 は、配線 118 を介して、接続パッド 115 と電気的に接続されている。

【0007】

接続パッド 114, 115 は、制御用 IC 実装領域 R12 に対応する基板本体 111 の上面に形成され、制御用 IC チップ 132 と電気的に接続される。接続パッド 114 は、配線 119 を介して、端面電極 116 と電気的に接続されている。

【0008】

アンテナ 120 は、図 14 に示すように、基板本体 111 の上面に形成された配線部 121 と、基板本体 111 の下面に形成された配線部 122 と、上記切り欠き部 111X に形成された接続部 123 を有している。これら配線部 121, 122 及び接続部 123 は互いに電気的に接続されている。そして、アンテナ 120 は、図 12 に示した RFIC チップ 131 と電気的に接続されている。

【0009】

このようにアンテナ 120 の一部（つまり、接続部 123）を基板本体 111 の側面に設けることにより、基板本体 111 の上面のみにアンテナを形成する場合に比べて、基板本体 111 の上面におけるアンテナ 120 の占有面積を小さくすることができる。

【先行技術文献】

【特許文献】

【0010】

【特許文献 1】特開 2007-324231 号公報

【発明の概要】

【発明が解決しようとする課題】

【0011】

ところが、上記配線基板 110 では、アンテナ 120 の配線長が基板本体 111 の厚さに依存することになる。このため、基板本体 111 が薄くなると、接続部 123 によってアンテナ 120 の配線長を十分に確保することができなくなり、長い配線長が必要な低周波アンテナの設計が困難となる。この場合に低周波アンテナを設計するためには、基板本体 111 の上下面に形成される配線部 121, 122 を長く形成する必要があり、配線部 121, 122 の占有面積が大きくなってしまう。このため、基板本体 111 が薄くなつた場合には、基板本体 111 の面方向のサイズを縮小することが難しく、配線基板 110 の小型化を図ることが困難になるという問題があった。さらに、配線基板 110 の小型化を図ることが困難であるため、配線基板 110 を備えた半導体装置 100 の小型化を図ることが困難になるという問題があった。

【課題を解決するための手段】

【0012】

本発明の一観点によれば、第 1 基板と、前記第 1 基板に接合された第 2 基板と、前記第 1 基板と前記第 2 基板との間に設けられ、前記第 1 基板と前記第 2 基板とを電気的に接続するはんだボールと、前記第 1 基板及び前記第 2 基板の少なくとも一方に配置された電子部品と、前記第 1 基板の第 1 面に接して前記第 1 基板の第 1 面上に形成された第 1 配線部と、前記第 1 基板の第 1 面と該第 1 面と反対側の第 2 面との間を貫通し、前記第 1 配線部及び前記はんだボールと電気的に接続された第 1 貫通電極と、前記第 2 基板の第 1 面に接して前記第 2 基板の第 1 面上に形成された第 2 配線部と、前記第 2 基板の第 1 面と該第 1 面と反対側の第 2 面との間を貫通し、前記第 2 配線部及び前記はんだボールと電気的に接続された第 2 貫通電極と、前記第 1 基板の第 2 面に接して前記第 1 基板の第 2 面上に形成され、前記第 1 貫通電極と接続されるとともに前記はんだボールと接続された第 1 配線パターンと、前記第 2 基板の第 2 面に接して前記第 2 基板の第 2 面上に形成され、前記第 2 貫通電極と接続されるとともに前記はんだボールと接続された第 2 配線パターンと、を有し、前記はんだボールと前記第 1 配線部と前記第 1 貫通電極と前記第 2 配線部と前記第 2

10

20

30

40

50

貫通電極と前記第1配線パターンと前記第2配線パターンとの全てが前記電子部品と電気的に接続されたアンテナとして機能する。

【発明の効果】

【0013】

本発明の一観点によれば、小型化を図ることができるという効果を奏する。

【図面の簡単な説明】

【0014】

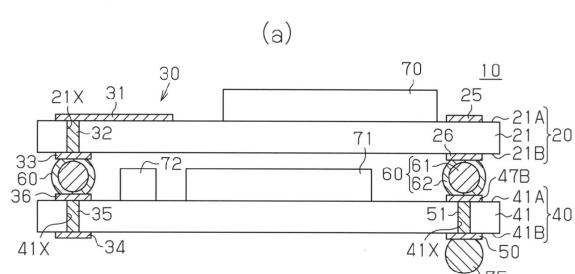

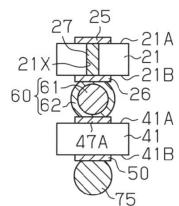

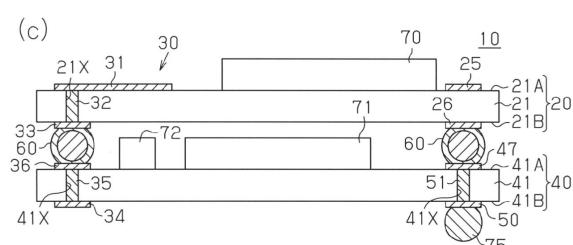

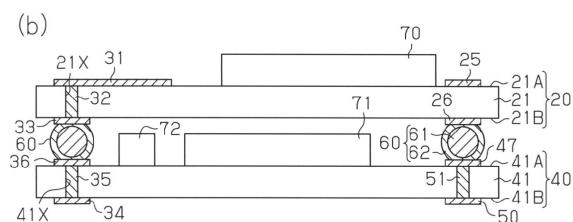

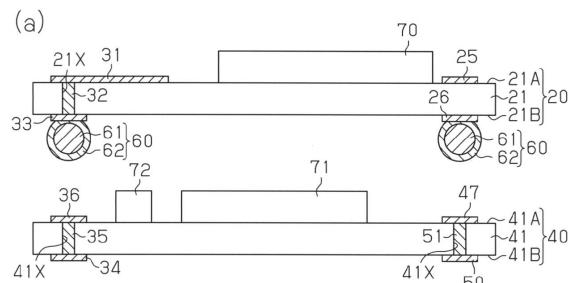

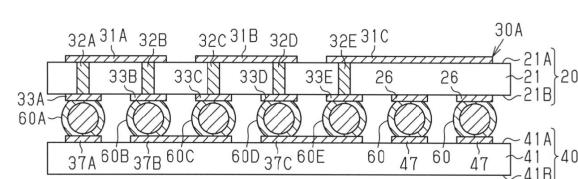

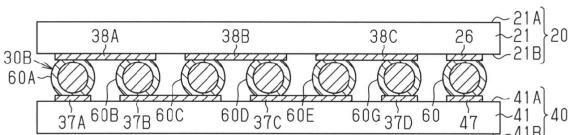

【図1】(a)は、一実施形態の半導体装置を示す概略断面図(図2及び図3における1a-1a概略断面図)、(b)は、一実施形態の半導体装置を示す概略断面図(図2及び図3における1b-1b概略断面図)。

10

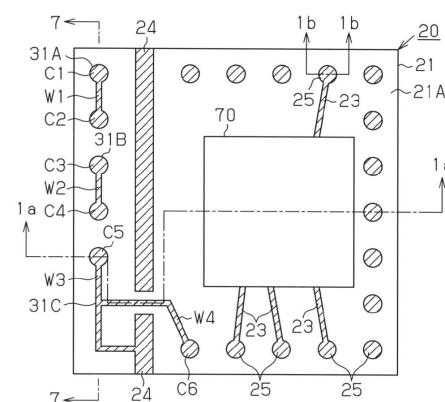

【図2】一実施形態の半導体装置の一部を示す概略平面図。

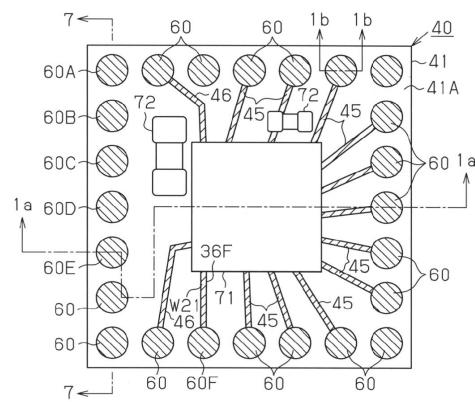

【図3】一実施形態の半導体装置の一部を示す概略平面図。

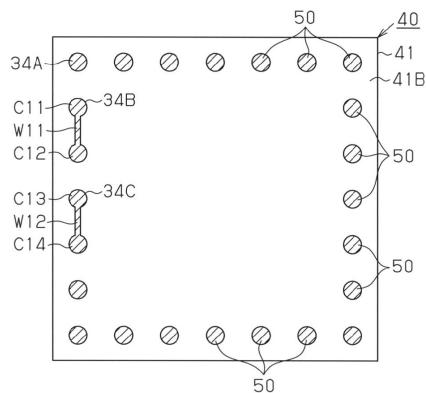

【図4】一実施形態の第1基板を示す概略平面図。

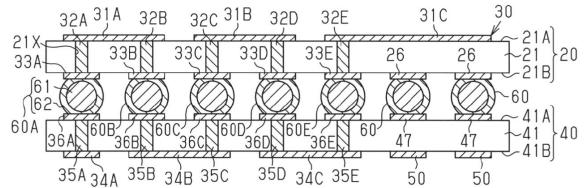

【図5】一実施形態の第2基板を示す概略平面図。

【図6】一実施形態の第2基板を示す概略平面図。

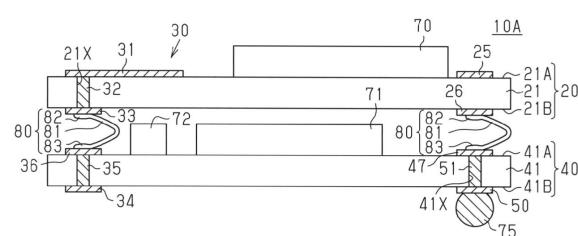

【図7】一実施形態のアンテナを示す概略断面図(図2及び図3における7-7概略断面図)。

【図8】(a)～(c)は、一実施形態の半導体装置の製造方法を示す概略断面図。

【図9】変形例の半導体装置を示す概略断面図。

【図10】変形例の半導体装置を示す概略断面図。

20

【図11】変形例の半導体装置を示す概略断面図。

【図12】従来の半導体装置を示す概略平面図。

【図13】従来の配線基板を示す概略平面図。

【図14】従来のアンテナを示す概略断面図。

【発明を実施するための形態】

【0015】

以下、一実施形態を添付図面を参照して説明する。

なお、添付図面は、特徴を分かりやすくするために便宜上特徴となる部分を拡大して示している場合があり、各構成要素の寸法比率などが実際と同じであるとは限らない。また、断面図では、各部材の断面構造を分かりやすくするために、一部の部材のハッチングを省略している。

30

【0016】

まず、半導体装置10の構造について説明する。なお、本実施形態では、アンテナ30として逆F型アンテナを2つの配線基板(第1基板20及び第2基板40)に設けた場合を例に挙げて説明する。

【0017】

図1に示すように、半導体装置10は、第1基板20と、第2基板40と、第1基板20と第2基板40とを電気的に接続するコア付きはんだボール60とを有している。第1基板20及び第2基板40には、コア付きはんだボール60を含むアンテナ30が形成されている。

40

【0018】

図1及び図2に示すように、第1基板20の上面には能動素子である半導体チップ70が実装されている。半導体チップ70としては、例えばCPU(Central Processing Unit)チップ等の制御用ICチップを用いることができる。以下の説明では、半導体チップ70を制御用ICチップ70とも称する。

【0019】

図1及び図3に示すように、第2基板40の上面には能動素子である半導体チップ71と受動素子72とが実装されている。半導体チップ71としては、例えばRFIC(Radio Frequency Integrated Circuit)チップを用いることができる。以下の説明では、半導体チップ71をRFICチップ71とも称する。受動素子72としては、例えばチップキ

50

ヤパシタ、チップインダクタやチップ抵抗を用いることができる。なお、受動素子 72 に接続される配線については図示を省略している。また、図 1 に示すように、第 2 基板 40 の下面には、外部接続端子 75 が形成されている。外部接続端子 75 は、マザーボード等の実装基板と電気的に接続するための端子である。外部接続端子 75 としては、例えばはんだボールを用いることができる。

#### 【0020】

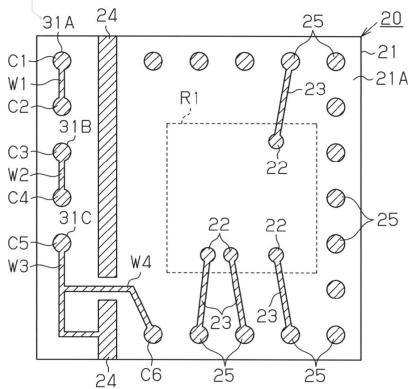

次に、図 1 及び図 4 を参照して第 1 基板 20 の構造について説明する。なお、図 4 は、図 1 に示した第 1 基板 20 の上面側を平面視した図である。図 4 において、R 1 は制御用 I C チップ 70 が実装される領域（以下、「制御用 I C 実装領域 R 1」と称する）を示している。

10

#### 【0021】

第 1 基板 20 は、第 1 基板本体 21 と、第 1 基板本体 21 の上面 21A に形成された接続パッド 22、配線 23、グランド配線 24 及び接続部 25 と、第 1 基板本体 21 の下面 21B に形成された接続パッド 26 と、上記アンテナ 30 を有している。第 1 基板本体 21 としては、その第 1 基板本体 21 の上面 21A 及び下面 21B にそれぞれ形成された接続部 25 及び接続パッド 26 が基板内部を通じて相互に電気的に接続された構造を有していれば十分である。このため、第 1 基板本体 21 の内部には配線層が形成されていてもよく、配線層が形成されていなくてもよい。なお、第 1 基板本体 21 の内部に配線層が形成される場合には、複数の配線層が層間絶縁層を介して積層され、各配線層と各絶縁層に形成されたビアとによって上記接続部 25 と接続パッド 26 とが電気的に接続されている。第 1 基板本体 21 としては、例えばコア基板を有するコア付きビルトアップ基板やコア基板を有さないコアレス基板等を用いることができる。このような第 1 基板本体 21 の厚さは、例えば 0.2 ~ 1.0 mm 程度とすることができます。

20

#### 【0022】

接続パッド 22 は、制御用 I C 実装領域 R 1 に対応する第 1 基板本体 21 の上面 21A に設けられている。接続パッド 22 は、制御用 I C チップ 70 と電気的に接続されるパッドである。接続パッド 22 は、配線 23 を介して、接続部 25 と電気的に接続されている。これら接続パッド 22、配線 23 及び接続部 25 は一体に形成されている。接続パッド 22 及び接続部 25 は例えば平面視略円形状に形成され、配線 23 は例えば平面視略帯状に形成されている。接続パッド 22、配線 23 及び接続部 25 の材料としては、例えば銅や銅合金を用いることができる。

30

#### 【0023】

グランド配線 24 は、第 1 基板本体 21 の上面 21A において、図中の上下方向に伸びるように平面視略帯状に形成されている。グランド配線 24 は、アンテナ 30 と電気的に接続されている。なお、グランド配線 24 は、グランド電位とされている。グランド配線 24 の材料としては、例えば銅や銅合金を用いることができる。

#### 【0024】

接続部 25 は、第 1 基板本体 21 の上面 21A の周縁部に形成されている。図 1 に示すように、接続部 25 は、第 1 基板本体 21 を厚さ方向に貫通する貫通電極 27 と電気的に接続されている。貫通電極 27 は、第 1 基板本体 21 の上面 21A と下面 21B との間を貫通する貫通孔 21X 内に形成されている。この貫通電極 27 は、貫通孔 21X 内を充填している。また、貫通電極 27 は、その上端部が上記接続部 25 と接続され、下端部が接続パッド 26 と接続されている。これにより、貫通電極 27 を通じて接続部 25 と接続パッド 26 とが電気的に接続される。この接続パッド 26 は、コア付きはんだボール 60 に接合され、そのコア付きはんだボール 60 を通じて第 2 基板 40 の接続パッド 47B と電気的に接続されるパッドである。なお、図示は省略するが、接続パッド 26 は、例えば平面視略円形状に形成されている。

40

#### 【0025】

貫通電極 27 及び接続パッド 26 の材料としては、例えば銅や銅合金を用いることができる。なお、本例では、貫通孔 21X 内を銅などの導電材料で充填する貫通電極 27 を形

50

成するようにしたが、例えば貫通孔 21X 内にめっきスルーホールピアである貫通電極を形成するようにしてもよい。

【0026】

なお、上述した配線 23、グランド配線 24 及び接続部 25 は、実際にはソルダレジスト層で被覆されているが、各部材の断面構造を分かりやすくするために、上記ソルダレジスト層の図示は省略している。

【0027】

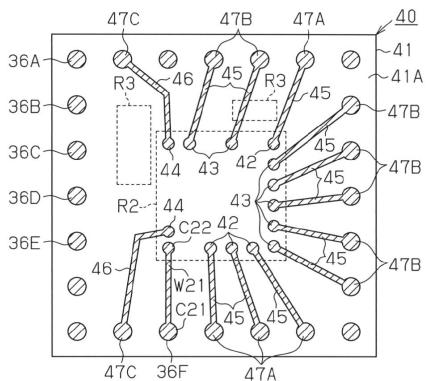

次に、図 5 及び図 6 を参照して第 2 基板 40 の構造について説明する。なお、図 5 は、図 1 に示した第 2 基板 40 の上面側を平面視した図であり、図 6 は、図 1 に示した第 2 基板 40 の下面側を平面視した図である。図 5 において、R2 は RFI C チップ 71 が実装される領域（以下、「RFI C 実装領域 R2」と称する）を示し、R3 は受動素子 72 が実装される領域（以下、「受動素子実装領域 R3」と称する）を示している。

【0028】

第 2 基板 40 は、第 2 基板本体 41 と、第 2 基板本体 41 の上面 41A に形成された接続パッド 42, 43, 44、配線 45、グランド配線 46 及び接続パッド 47A, 47B, 47C と、第 2 基板本体 41 の下面 41B に形成された接続パッド 50 と、上記アンテナ 30 とを有している。第 2 基板本体 41 としては、その第 2 基板本体 41 の上面 41A 及び下面 41B にそれぞれ形成された接続パッド 47A ~ 47C のうち少なくとも接続パッド 47B と接続パッド 50 とが基板内部を通じて相互に電気的に接続された構造を有していれば十分である。このため、第 2 基板本体 41 の内部には配線層が形成されていてもよく、配線層が形成されていなくてもよい。なお、第 2 基板本体 41 の内部に配線層が形成される場合には、複数の配線層が層間絶縁層を介して積層され、各配線層と各絶縁層に形成されたビアとによって上記接続パッド 47B と接続パッド 50 とが電気的に接続されている。第 2 基板本体 41 としては、例えばコア基板を有するコア付きビルドアップ基板やコア基板を有さないコアレス基板等を用いることができる。このような第 2 基板本体 41 の厚さは、例えば 0.2 ~ 1.0 mm 程度とすることができます。

【0029】

接続パッド 42, 43, 44 は、RFI C 実装領域 R2 に対応する第 2 基板本体 41 の上面 41A に設けられている。接続パッド 42 ~ 44 は、RFI C チップ 71 と電気的に接続されるパッドである。これら接続パッド 42 ~ 44 は、例えば平面視略円形状に形成されている。

【0030】

また、接続パッド 47A, 47B, 47C（以下、総称する場合は「接続パッド 47」という。）は、第 2 基板本体 41 の上面 41A の周縁部に形成されている。接続パッド 47A ~ 47C は、コア付きはんだボール 60 と接合されるパッドである。これら接続パッド 47A ~ 47C は、例えば平面視略円形状に形成されている。なお、接続パッド 42 ~ 44, 47A ~ 47C 及び配線 45 の材料としては、例えば銅や銅合金を用いることができる。

【0031】

接続パッド 42 は、配線 45 を介して、接続パッド 47A と電気的に接続されている。接続パッド 47A は、コア付きはんだボール 60 を通じて図 1 に示した第 1 基板 20 の接続パッド 26 と電気的に接続されている。このため、接続パッド 42 は、配線 45、接続パッド 47A、コア付きはんだボール 60、接続パッド 26、貫通電極 27、接続部 25 及び配線 23 を介して、接続パッド 22 と電気的に接続されている。これにより、RFI C 実装領域 R2 に実装される RFI C チップ 71 は、接続パッド 42、配線 45、接続パッド 47A、コア付きはんだボール 60、接続パッド 26、貫通電極 27、接続部 25、配線 23 及び接続パッド 22 を介して、制御用 IC 実装領域 R1 に実装される制御用 IC チップ 70 と電気的に接続される。

【0032】

接続パッド 43 は、配線 45 を介して、接続パッド 47B と電気的に接続されている。

10

20

30

40

50

図1に示すように、接続パッド47Bは、第2基板本体41を厚さ方向に貫通する貫通電極51と電気的に接続されている。貫通電極51は、第2基板本体41の上面41Aと下面41Bとの間を貫通する貫通孔41X内に形成されている。この貫通電極51は、貫通孔41X内を充填している。また、貫通電極51は、その上端部が上記接続パッド47Bと接続され、下端部が接続パッド50と接続されている。これにより、貫通電極51を通じて接続パッド47Bと接続パッド50とが電気的に接続されている。また、接続パッド50は、外部接続端子75と電気的に接続されるパッドである。図6に示すように、接続パッド50は、第2基板本体41の下面41Bの周縁部に形成されている。

#### 【0033】

貫通電極51及び接続パッド50の材料としては、例えば銅や銅合金を用いることができる。なお、本例では、貫通孔41X内を銅などの導電材料で充填する貫通電極51を形成するようにしたが、例えば貫通孔41X内にめっきスルーホールビアである貫通電極を形成するようにしてもよい。

#### 【0034】

接続パッド44は、グランド配線46を介して、接続パッド47Cと電気的に接続されている。この接続パッド47Cは、コア付きはんだボール60、接続パッド26(図1(a)参照)及び貫通電極27(図1(b)参照)を介して、第1基板20のグランド配線24(図4参照)と電気的に接続されている。このため、接続パッド44は、グランド配線46、接続パッド47C、コア付きはんだボール60、接続パッド26、貫通電極27、グランド配線24と電気的に接続されている。これにより、RFIC実装領域R2に実装されるRFICチップ71は、接続パッド44、グランド配線46、接続パッド47C、コア付きはんだボール60、接続パッド26、貫通電極27を介して上記グランド配線24と電気的に接続される。なお、グランド配線46は、グランド電位とされている。グランド配線46の材料としては、例えば銅や銅合金を用いることができる。

#### 【0035】

図3及び図5に示すように、各接続パッド47A～47C上には、コア付きはんだボール60が接合されている。各コア付きはんだボール60は、上記第1基板20の接続パッド26(図1(a)参照)にも接合されている。すなわち、各コア付きはんだボール60は、第1基板20と第2基板40との間に介在して設けられ、その一端が接続パッド26に接合され、他端が接続パッド47A～47Cに接合されている。コア付きはんだボール60は、第1基板20と第2基板40とを接続(接合)する接続端子として機能するとともに、第1基板20と第2基板40との間の距離(離間距離)を規定値に保持するスペーサとしても機能する。このコア付きはんだボール60の高さは、RFICチップ71の厚さ及び受動素子72の厚さよりも高く設定されている。また、コア付きはんだボール60の高さは、第1基板本体21及び第2基板本体41の厚さよりも高く設定されている。例えば、コア付きはんだボール60の高さは0.8～1.2mm程度とすることができます。

#### 【0036】

コア付きはんだボール60は、球形状の銅コアボール61の周囲をはんだ62で覆った構造を有し、はんだ62が接合材として機能し銅コアボール61がスペーサとして機能する。すなわち、コア付きはんだボール60は、はんだ62によって上記接続パッド26と接合されるとともに、はんだ62によって上記接続パッド47A～47Cと接合されている。

#### 【0037】

コア付きはんだボール60は、アンテナ30の一部として含まれるコア付きはんだボール60A, 60B, 60C, 60D, 60E, 60Fを有している。

なお、上述した配線45及びグランド配線46は、実際にはソルダレジスト層で被覆されているが、各部材の断面構造を分かりやすくするために、上記ソルダレジスト層の図示は省略している。

#### 【0038】

次に、図2～図7を参照して、アンテナ30の構造について説明する。本例のアンテナ

10

20

30

40

50

30は、逆F型アンテナである。このアンテナ30は、第1基板20及び第2基板40にそれぞれ形成されたグランド配線24, 46と電源線(図示略)とに電気的に接続されている。

【0039】

アンテナ30は、第1配線部31A～31Cと、第1貫通電極32A～32Eと、第1配線パターン33A～33Eと、第2配線部34A～34Cと、第2貫通電極35A～35Eと、第2配線パターン36A～36Fと、コア付きはんだボール60A～60Fとを有している。

【0040】

第1配線部31A～31C(以下、総称する場合は「第1配線部31」という。)は、第1基板本体21の上面21Aに形成されている。第1貫通電極32A～32E(以下、総称する場合は「第1貫通電極32」という。)は、上記貫通電極27と同様に、第1基板本体21を厚さ方向に貫通する貫通孔21X内に形成されている。第1配線パターン33A～33E(以下、総称する場合は「第1配線パターン33」という。)は、第1基板本体21の下面21Bに形成されている。なお、本例の第1配線パターン33は、図示は省略するが、例えば平面視略円形状に形成されている。

10

【0041】

第2配線部34A～34C(以下、総称する場合は「第2配線部34」という。)は、第2基板本体41の下面41Bに形成されている。第2貫通電極35A～35E(以下、総称する場合は「第2貫通電極35」という。)は、上記貫通電極51と同様に、第2基板本体41を厚さ方向に貫通する貫通孔41X内に形成されている。第2配線パターン36A～36F(以下、総称する場合は「第2配線パターン36」という。)は、第2基板本体41の上面41Aに形成されている。なお、本例の第2配線パターン36は、例えば平面視略円形状に形成されている。コア付きはんだボール60A～60Fは、第1基板20と第2基板40との間に設けられている。なお、第1配線部31、第1貫通電極32、第1配線パターン33、第2配線部34、第2貫通電極35及び第2配線パターン36の材料としては、例えば銅や銅合金を用いることができる。

20

【0042】

第1配線部31Aは、2つの第1貫通電極32A, 32Bに接続されている。この第1配線部31Aは、図4に示すように、第1貫通電極32A, 32Bとそれぞれ接続される接続部C1, C2と、それら接続部C1, C2を接続する配線部W1とを有している。これら接続部C1, C2及び配線部W1は一体に形成されている。接続部C1, C2は例えば平面視略円形状に形成され、配線部W1は例えば平面視略帯状に形成されている。

30

【0043】

図7に示すように、上記第1貫通電極32Aは、第1配線パターン33Aを介して、コア付きはんだボール60Aと電気的に接続されている。そして、コア付きはんだボール60Aは、第2配線パターン36A及び第2貫通電極35Aを介して、第2配線部34Aと接合されている。このため、第1配線部31Aは、第1貫通電極32A、第1配線パターン33A、コア付きはんだボール60A、第2配線パターン36A及び第2貫通電極35Aを介して、第2配線部34Aと電気的に接続されている。なお、図6に示すように、第2配線部34Aは例えば平面視略円形状に形成されている。

40

【0044】

一方、図7に示すように、第1貫通電極32Bは、第1配線パターン33Bを介して、コア付きはんだボール60Bと電気的に接続されている。このコア付きはんだボール60Bは、第2配線パターン36B及び第2貫通電極35Bを介して、第2配線部34Bと電気的に接続されている。このため、第1配線部31Aは、第1貫通電極32B、第1配線パターン33B、コア付きはんだボール60B、第2配線パターン36B及び第2貫通電極35Bを介して、第2配線部34Bと電気的に接続されている。

【0045】

第2配線部34Bは、2つの第2貫通電極35B, 35Cに接続されている。この第2

50

配線部 34B は、図 6 に示すように、第 2 貫通電極 35B, 35C とそれぞれ接続される接続部 C11, C12 と、それら接続部 C11, C12 を接続する配線部 W11 を有している。これら接続部 C11, C12 及び配線部 W11 は一体に形成されている。接続部 C11, C12 は例えば平面視略円形状に形成され、配線部 W11 は例えば平面視略帯状に形成されている。図 7 に示すように、上記第 2 貫通電極 35C は、第 2 配線パターン 36C、コア付きはんだボール 60C、第 1 配線パターン 33C 及び第 1 貫通電極 32C を介して、第 1 配線部 31B と電気的に接続されている。このため、第 2 配線部 34B は、第 2 貫通電極 35C、第 2 配線パターン 36C、コア付きはんだボール 60C、第 1 配線パターン 33C 及び第 1 貫通電極 32C を介して、第 1 配線部 31B と電気的に接続されている。

10

#### 【 0046 】

第 1 配線部 31B は、2 つの第 1 貫通電極 32C, 32D と接続されている。この第 1 配線部 31B は、図 4 に示すように、第 1 貫通電極 32C, 32D とそれぞれ接続される接続部 C3, C4 と、それら接続部 C3, C4 を接続する配線部 W2 を有している。これら接続部 C3, C4 及び配線部 W2 は一体に形成されている。接続部 C3, C4 は例えば平面視略円形状に形成され、配線部 W2 は例えば平面視略帯状に形成されている。図 7 に示すように、第 1 貫通電極 32D は、第 1 配線パターン 33D、コア付きはんだボール 60D、第 2 配線パターン 36D 及び第 2 貫通電極 35D を介して、第 2 配線部 34C と電気的に接続されている。このため、第 1 配線部 31B は、第 1 貫通電極 32D、第 1 配線パターン 33D、コア付きはんだボール 60D、第 2 配線パターン 36D 及び第 2 貫通電極 35D を介して、第 2 配線部 34C と電気的に接続されている。

20

#### 【 0047 】

第 2 配線部 34C は、2 つの第 2 貫通電極 35D, 35E に接続されている。この第 2 配線部 34C は、図 6 に示すように、第 2 貫通電極 35D, 35E とそれぞれ接続される接続部 C13, C14 と、それら接続部 C13, C14 を接続する配線部 W12 を有している。これら接続部 C13, C14 及び配線部 W12 は一体に形成されている。接続部 C13, C14 は例えば平面視略円形状に形成され、配線部 W12 は例えば平面視略帯状に形成されている。図 7 に示すように、上記第 2 貫通電極 35E は、第 2 配線パターン 36E、コア付きはんだボール 60E、第 1 配線パターン 33E 及び第 1 貫通電極 32E を介して、第 1 配線部 31C と電気的に接続されている。このため、第 2 配線部 34C は、第 2 貫通電極 35E、第 2 配線パターン 36E、コア付きはんだボール 60E、第 1 配線パターン 33E 及び第 1 貫通電極 32E を介して、第 1 配線部 31C と電気的に接続されている。

30

#### 【 0048 】

第 1 配線部 31C は、図 4 に示すように、上記第 1 貫通電極 32E と接続される接続部 C5 と、配線部 W3, W4 と、接続部 C6 とを有している。これら接続部 C5, C6 及び配線部 W3, W4 は一体に形成されている。接続部 C5, C6 は例えば平面視略円形状に形成され、配線部 W3, W4 は例えば平面視略 L 字状に形成されている。

#### 【 0049 】

上記配線部 W3 は、接続部 C5 とグランド配線 24 とを電気的に接続している。これにより、アンテナ 30 全体がグランド配線 24 に接続されている。また、配線部 W4 は、配線部 W3 と接続部 C6 とを電気的に接続している。これにより、接続部 C5 は、配線部 W3, W4 を介して、接続部 C6 と電気的に接続されている。接続部 C6 は、図示しない第 1 貫通電極 32 及び第 1 配線パターン 33 を介して、図 3 に示したコア付きはんだボール 60F と電気的に接続されている。このコア付きはんだボール 60F は、図 5 に示した第 2 配線パターン 36F の接続部 C21 と電気的に接続されている。

40

#### 【 0050 】

第 2 配線パターン 36F は、上記接続部 C21 と、RFIC 実装領域 R2 内に形成された接続部 C22 と、それら接続部 C21, C22 を接続する配線部 W21 とを有している。これら接続部 C21, C22 及び配線部 W21 は一体に形成されている。接続部 C21

50

, C 2 2 は例えば平面視略円形状に形成され、配線部 W 2 1 は例えば平面視略帯状に形成されている。接続部 C 2 1 は、R F I C 実装領域 R 2 に実装される R F I C チップ 7 1 と電気的に接続される。これにより、アンテナ 3 0 全体が R F I C チップ 7 1 と電気的に接続されることになる。

#### 【 0 0 5 1 】

なお、上述した第 1 配線部 3 1 A ~ 3 1 C 、第 2 配線部 3 4 A ~ 3 4 C 及び第 2 配線パターン 3 6 F の配線部 W 2 1 は、実際にはソルダレジスト層で被覆されているが、各部材の断面構造を分かりやすくするために、上記ソルダレジスト層の図示は省略している。また、図 7 に示した接続パッド 2 6 , 4 7 及びコア付きはんだボール 6 0 は、例えば制御用 I C チップ 7 0 と R F I C チップ 7 1 との間で信号を取り取りする信号配線との接続に使用したり、ダミーパッド及びダミー接続端子として使用したりする。ダミーパッド及びダミー接続端子として使用する目的は、第 1 基板 2 0 と第 2 基板 4 0 との間の接合強度を向上させ、第 1 基板 2 0 及び第 2 基板 4 0 を相互に平行に接合させることである。また、図 7 に示した接続パッド 5 0 は、例えば R F I C チップ 7 1 等と実装基板との間で信号を取り取りする信号配線との接続に使用したり、ダミーパッドとして使用したりする。ダミーパッドとして使用される場合には、例えば、半導体装置 1 0 と実装基板との間の接合強度を向上させ、半導体装置 1 0 及び実装基板を相互に平行に接合させるために、ダミーパッド（接続パッド 5 0 ）上に外部接続端子 7 5 が形成される。

#### 【 0 0 5 2 】

次に、上記半導体装置 1 0 の作用について説明する。

アンテナ 3 0 の一部に、第 1 基板 2 0 と第 2 基板 4 0 とを接合するとともに第 1 基板 2 0 と第 2 基板 4 0 とを電気的に接続する接続端子であるコア付きはんだボール 6 0 を利用するようにした。これにより、コア付きはんだボール 6 0 の高さ（つまり、第 1 基板 2 0 と第 2 基板 4 0 との間の高さ）をアンテナ 3 0 の配線長として利用することができるため、アンテナ 3 0 の配線長を容易に長く確保することができる。ここで、コア付きはんだボール 6 0 の高さは、第 1 基板本体 2 1 及び第 2 基板本体 4 1 の厚さよりも高く形成されている。このため、従来のように基板本体 1 1 1 の厚さ方向の長さを利用してアンテナ 1 2 0 を形成する場合に比べて、アンテナ 3 0 の配線長を長く形成することができる。したがって、長い配線長が必要な低周波アンテナを設計する場合であっても、第 1 配線部 3 1 及び第 1 配線パターン 3 3 や、第 2 配線部 3 4 及び第 2 配線パターン 3 6 の占有面積が増大することを抑制することができる。換言すると、第 1 配線部 3 1 等の占有面積を小さくした場合であっても、第 1 基板本体 2 1 及び第 2 基板本体 4 1 等の積層方向の長さを利用することで、アンテナ 3 0 の配線長を所望の長さ（例えば、低周波数に対応した長さ）に設定することができる。これにより、第 1 基板 2 0 及び第 2 基板 4 0 の面方向のサイズを小さくすることができるため、第 1 基板 2 0 及び第 2 基板 4 0 を小型化することができ、ひいては半導体装置 1 0 を小型化することができる。

#### 【 0 0 5 3 】

次に、半導体装置 1 0 の製造方法について説明する。

まず、図 8 ( a ) に示すように、第 1 基板 2 0 及び第 2 基板 4 0 を準備する。これら第 1 基板 2 0 及び第 2 基板 4 0 は、公知の製造方法により製造することができるため、ここでは図 8 ( a ) を参照しながら簡単に説明する。

#### 【 0 0 5 4 】

第 1 基板 2 0 は、例えば、銅張積層板 (Copper Clad Laminated : C C L) に貫通孔 2 1 X を形成し、電解めっきやペースト充填等の方法により貫通孔 2 1 X 内に第 1 貫通電極 3 2 等を形成した後、サブトラクティブ法により第 1 配線部 3 1 及び第 1 配線パターン 3 3 等を形成することによって製造される。同様に、第 2 基板 4 0 は、例えば、銅張積層板に貫通孔 4 1 X を形成し、電解めっきやペースト充填等の方法により貫通孔 4 1 X 内に第 2 貫通電極 3 5 等を形成した後、サブトラクティブ法により第 2 配線部 3 4 及び第 2 配線パターン 3 6 等を形成することによって製造される。その後、第 1 基板 2 0 の第 1 基板本体 2 1 の上面 2 1 A に制御用 I C チップ 7 0 を実装（例えば、フリップチップ実装やワ

10

20

30

40

50

ヤボンディング実装)する。また、第2基板40の第2基板本体41の上面41AにRFICチップ71及び受動素子72を実装(例えば、フリップチップ実装やはんだ実装)する。

#### 【0055】

また、図8(a)に示した工程では、第1基板本体21の下面21Bに形成された第1配線パターン33上及び接続パッド26上に、コア付きはんだボール60を搭載(接合)する。例えば第1配線パターン33上及び接続パッド26上に、適宜フラックスを塗布した後、コア付きはんだボール60を搭載し、230～260程度の温度でリフローして固定する。その後、表面を洗浄してフラックスを除去する。

#### 【0056】

そして、RFICチップ71及び受動素子72が実装された第2基板40の上方に、制御用ICチップ70が実装されコア付きはんだボール60が搭載された第1基板20を配置する。具体的には、図8(a)に示すように、第1基板本体21の下面21Bと、第2基板本体41の上面41Aとを対向させて、コア付きはんだボール60と接続パッド47及び第2配線パターン36とが対向するように位置決めされる。

#### 【0057】

続いて、図8(b)に示す工程では、接続パッド47上及び第2配線パターン36上に、コア付きはんだボール60を接合する。具体的には、まず、接続パッド47及び第2配線パターン36上に適宜フラックスを塗布する。その後、第1基板20を、コア付きはんだボール60を間に挟んだ状態で第2基板40の上に配置し、それら重ね合わされた第1基板20及び第2基板40をリフロー炉で230～260程度の温度で加熱する。これにより、コア付きはんだボール60のはんだ62が溶融し、コア付きはんだボール60が接続パッド47及び第2配線パターン36に接合される。これにより、第1配線部31、第1貫通電極32、第1配線パターン33、コア付きはんだボール60、第2配線パターン36、第2貫通電極35及び第2配線部34が互いに電気的に接続され、アンテナ30が形成されることになる。なお、本工程では、第1基板20を第2基板40に対して押圧しながらリフローが行われるが、コア付きはんだボール60の銅コアボール61がスペーサとして機能し、第1基板20と第2基板40との間の間隔は所定の距離に維持される。

#### 【0058】

そして、図8(c)に示す工程では、接続パッド50上に外部接続端子75を形成する。例えば接続パッド50上に、適宜フラックスを塗布した後、外部接続端子75(ここでは、はんだボール)を搭載し、240～260程度の温度でリフローして固定する。その後、表面を洗浄してフラックスを除去する。以上の製造工程により、本実施形態の半導体装置10が製造される。

#### 【0059】

以上説明した本実施形態によれば、以下の効果を奏することができる。

(1)アンテナ30の一部に、第1基板20と第2基板40とを接合するとともに第1基板20と第2基板40とを電気的に接続する接続端子であるコア付きはんだボール60を利用するようにした。これにより、コア付きはんだボール60の高さ(つまり、第1基板20と第2基板40との間の高さ)をアンテナ30の配線長として利用することができるため、アンテナ30の配線長を容易に長く確保することができる。その結果、第1基板20及び第2基板40の面方向のサイズを小さくすることができるため、第1基板20及び第2基板40を小型化することができ、ひいては半導体装置10を小型化することができる。

#### 【0060】

このようにコア付きはんだボール60の高さをアンテナ30の配線長として利用することにより、第1基板20及び第2基板40の面方向のサイズを大型化させることなく、アンテナ30の配線長を長くして、アンテナ30の特性を向上させることができる。

#### 【0061】

(2)さらに、上記コア付きはんだボール60に加えて、第1基板本体21に形成され

10

20

30

40

50

た第1貫通電極32と、第2基板本体41に形成された第2貫通電極35とをアンテナ30の一部に利用するようにした。これにより、コア付きはんだボール60の高さに加えて、第1基板本体21及び第2基板本体41の厚さをアンテナ30の配線長として利用することができるため、アンテナ30の配線長をより容易に長く確保することができる。その結果、第1基板20及び第2基板40の面方向のサイズをより小さくすることができるため、第1基板20及び第2基板40を容易に小型化することができ、ひいては半導体装置10を容易に小型化することができる。

#### 【0062】

##### (他の実施形態)

なお、上記実施形態は、これを適宜変更した以下の態様にて実施することもできる。

10

・上記実施形態では、第1基板20と第2基板40とを接続する接続端子としてコア付きはんだボール60を用いるようにした。これに限らず、コア付きはんだボール60の代わりに、スプリング性を有した接続端子(スプリング接続端子)や、柱状の接続端子である金属ポスト等を上記接続端子として用いるようにしてもよい。この場合には、スプリング接続端子や金属ポスト等がアンテナ30の一部として利用される。これにより、上記実施形態と同様の効果を奏すことができる。

#### 【0063】

図9は、第1基板20と第2基板40とを接続する接続端子としてスプリング接続端子80を用いた半導体装置10Aを示している。

図9に示すように、スプリング接続端子80は、第1基板20と第2基板40との間に介在して設けられている。スプリング接続端子80は、その一端が接続パッド26及び第1配線パターン33に接合され、他端が接続パッド47及び第2配線パターン36に接合されている。スプリング接続端子80は、スプリング部81と、接合部82, 83とを有している。これらスプリング部81及び接合部82, 83は一体的に形成されている。スプリング接続端子80は、適当な弾性(ばね性、曲げ性)を有した金属材料からなり、均一な厚さを有した金属薄板をスタンピング等により打ち抜き加工し、曲げ加工を施すことで作製することができる。上記金属薄板の材料としては、例えばベリリウム銅(Cu - Be)、りん青銅(Cu - Sn)、コルソン材(Cu - Ni - Si - Mg、Cu - Ni - Si、Cu - Ni - Co - Si - Cr等)などの銅をベースとした合金を用いることができる。

20

接合部82は、第1基板本体21の下面21Bに形成された接続パッド26及び第1配線パターン33に接合されている。例えば、接合部82は、接続パッド26及び第1配線パターン33にはんだ接合されている。この接合部82は、スプリング部81の上端に繋がり、そのスプリング部81よりも幅が広く、且つ平坦な形状に形成されている。

#### 【0064】

接合部83は、第2基板本体41の上面41Aに形成された接続パッド47及び第2配線パターン36に接合されている。例えば、接合部83は、接続パッド47及び第2配線パターン36にはんだ接合されている。この接合部83は、スプリング部81の下端に繋がり、そのスプリング部81よりも幅が広く、且つ平坦な形状に形成されている。

30

#### 【0065】

スプリング部81は、接合部82と接合部83との間に配置されている。スプリング部81は、外側に(つまり、接合部82, 83に対し遠ざかる方向に)湾曲するように形成されている。例えば、スプリング部81は、側面視したときにC字状や逆C字状に形成されている。この形状により、スプリング部81は、高さ方向(第1基板20及び第2基板40の積層方向)に弾性変形することができる。スプリング部81のばね定数は、例えば0.6~0.8N/mm程度とすることができます。

40

#### 【0066】

このような半導体装置10Aでは、アンテナ30の一部にスプリング接続端子80が利用されている。すなわち、アンテナ30は、第1配線部31、第1貫通電極32、第1配

50

線パターン33、第2配線部34、第2貫通電極35、第2配線パターン36及びスプリング接続端子80を有している。そして、スプリング接続端子80によって、第1基板20に形成された第1配線部31、第1貫通電極32及び第1配線パターン33と、第2基板40に形成された第2配線部34、第2貫通電極35及び第2配線パターン36とが電気的に接続されている。

【0068】

このようにアンテナ30の一部にスプリング接続端子80を利用してすることで、そのスプリング接続端子80が有する湾曲形状をアンテナ30の配線長として利用することができるため、アンテナ30の配線長を容易に長く確保することができる。

【0069】

・上記変形例では、スプリング接続端子80の両端部を接続パッド26, 47、第1配線パターン33及び第2配線パターン36に接合するようにした。これに限らず、スプリング接続端子80の一方の端部（例えば、接合部83）のみを接続パッド47及び第2配線パターン36に接合し、他方の端部（例えば、接合部82）に対して接続パッド26及び第1配線パターン33を押圧することにより、第1基板20と第2基板40とを電気的に接続するようにしてもよい。

【0070】

・上記実施形態では、コア付きはんだボール60の導電性コアボールとして銅コアボール61を用いるようにした。これに限らず、銅コアボール61の代わりに、例えば金やニッケル等の銅以外の金属により形成した導電性コアボールを用いるようにしてもよいし、樹脂により形成した樹脂コアボールを用いるようにしてもよい。あるいは、コア付きはんだボール60の代わりに、導電性コアボールや樹脂コアボールを省略した、はんだボールを用いるようにしてもよい。

【0071】

・上記実施形態及び上記各変形例におけるアンテナ30の構造は特に限定されない。例えば、図10に示すように、上記実施形態のアンテナ30から第2貫通電極35及び第2配線部34を省略した構造を有するアンテナ30Aに変更してもよい。このアンテナ30Aは、第1配線部31A～31Cと、第1貫通電極32A～32Eと、第1配線パターン33A～33Eと、第2配線パターン37A～37Cと、コア付きはんだボール60A～60Fと、図3に示した第2配線パターン36Fとを有している。そして、第1基板20に形成された第1配線部31A～31C、第1貫通電極32A～32E及び第1配線パターン33A～33Eが、コア付きはんだボール60を介して、第2基板本体41の上面41Aに形成された第2配線パターン37A～37C, 36Fと電気的に接続されている。このようなアンテナ30Aを有する半導体装置であっても、上記実施形態と同様の効果を奏することができる。

【0072】

・また、上記アンテナ30Aから第1配線パターン33A～33Eを省略した構造のアンテナに変更してもよい。この場合には、例えば第1貫通電極32A～32Eの下端面にコア付きはんだボール60A～60Eをそれぞれ接合する。

【0073】

・また、上記変形例とは反対に、上記実施形態のアンテナ30から第1配線部31及び第1貫通電極32を省略した構造を有するアンテナに変更してもよい。あるいは、上記実施形態のアンテナ30から第1配線部31、第1貫通電極32及び第2配線パターン36を省略した構造を有するアンテナに変更してもよい。この場合には、例えば第2貫通電極35A～35Eの上端面にコア付きはんだボール60A～60Eをそれぞれ接合する。

【0074】

・また、図11に示すように、上記アンテナ30から第1配線部31A～31C、第1貫通電極32A～32E、第2貫通電極35及び第2配線部34を省略した構造を有するアンテナ30Bに変更してもよい。このアンテナ30Bは、第1配線パターン38A～38Cと、第2配線パターン37A～37Dと、コア付きはんだボール60A～60E, 6

10

20

30

40

50

0 Gとを有している。このようなアンテナ30Bでは、第1配線パターン38A～38Cが、コア付きはんだボール60A～60E, 60Gを介して、第2配線パターン37A～37Dと電気的に接続されている。そして、例えば第2配線パターン37DがRFIC実装領域R2まで延在され、そのRFIC実装領域R2に実装されるRFICチップ71と電気的に接続される。なお、アンテナ30Bは、図示は省略するが、グランド配線と電源線とに電気的に接続されている。このようなアンテナ30Bを有する半導体装置であっても、上記実施形態の(1)の効果と同様の効果を奏することができる。

【0075】

・上記実施形態及び上記各変形例における第1貫通電極32を第1基板本体21の側面(又は、第1基板本体21の側面に形成された切り欠き部)に形成するようにしてよい。

10

【0076】

・上記実施形態及び上記各変形例における第2貫通電極35を第2基板本体41の側面(又は、第2基板本体41の側面に形成された切り欠き部)に形成するようにしてよい。

【0077】

・上記実施形態における第1基板20と第2基板40との間を樹脂材で封止するようにしてよい。すなわち、第1基板20と第2基板40との間の空間に樹脂材を充填するようにしてよい。上記樹脂材としては、例えばエポキシ系樹脂やポリイミド系樹脂などの絶縁性樹脂を用いることができる。また、樹脂材としては、例えばエポキシ系樹脂にシリカ(SiO<sub>2</sub>)等のフィラーを混入した樹脂材を用いることができる。また、上記樹脂材としては、例えばトランスファーモールド法、コンプレッションモールド法やインジェクションモールド法などにより形成されたモールド樹脂を用いることができる。

20

【0078】

・上記実施形態及び上記各変形例では、逆F型アンテナであるアンテナ30を有する半導体装置に具体化したが、逆F型アンテナ以外のアンテナ(例えば、逆L型アンテナ)を有する半導体装置に具体化してもよい。

【符号の説明】

【0079】

10, 10A 半導体装置

30

20 第1基板

21 第1基板本体

21A 上面(第1面)

21B 下面(第2面)

40 第2基板

41 第2基板本体

41A 上面(第2面)

41B 下面(第1面)

30, 30A, 30B アンテナ

31, 31A～31C 第1配線部

40

32, 32A～32E 第1貫通電極

33, 33A～33E 第1配線パターン

34, 34A～34C 第2配線部

35, 35A～35E 第2貫通電極

36, 36A～36F 第2配線パターン

37A～37D 第2配線パターン

38A～38C 第1配線パターン

60, 60A～60G コア付きはんだボール(接続端子)

70 半導体チップ(電子部品)

71 半導体チップ(電子部品)

50

7 2 受動素子 (電子部品)

8 0 スプリング接続端子 (接続端子)

【 四 1 】

(b)

【 図 2 】

【 図 3 】

【 図 4 】

【 四 5 】

【 8 】

【図6】

【図7】

【図9】

【図10】

【 义 1 1 】

【図12】

【図13】

【図14】

---

フロントページの続き

(56)参考文献 特開2007-324231(JP, A)

特開2009-158742(JP, A)

特開2011-40703(JP, A)

特開2006-237276(JP, A)

特開2007-227897(JP, A)

米国特許出願公開第2010/0026601(US, A1)

(58)調査した分野(Int.Cl., DB名)

H 01 L 25 / 065

H 01 L 21 / 60

H 01 L 25 / 07

H 01 L 25 / 18

H 01 Q 1 / 38