(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第5201853号

(P5201853)

(45) 発行日 平成25年6月5日(2013.6.5)

(24) 登録日 平成25年2月22日(2013.2.22)

(51) Int.Cl.

F 1

|                   |                  |            |      |

|-------------------|------------------|------------|------|

| <b>H01L 27/10</b> | <b>(2006.01)</b> | H01L 27/10 | 431  |

| <b>H01L 51/05</b> | <b>(2006.01)</b> | H01L 29/28 | 100A |

| <b>H01L 45/00</b> | <b>(2006.01)</b> | H01L 45/00 | Z    |

| <b>H01L 49/00</b> | <b>(2006.01)</b> | H01L 49/00 | Z    |

| <b>H01L 27/28</b> | <b>(2006.01)</b> | H01L 27/10 | 449  |

請求項の数 4 (全 42 頁) 最終頁に続く

(21) 出願番号 特願2007-54466 (P2007-54466)

(22) 出願日 平成19年3月5日 (2007.3.5)

(65) 公開番号 特開2007-273967 (P2007-273967A)

(43) 公開日 平成19年10月18日 (2007.10.18)

審査請求日 平成22年2月24日 (2010.2.24)

(31) 優先権主張番号 特願2006-66527 (P2006-66527)

(32) 優先日 平成18年3月10日 (2006.3.10)

(33) 優先権主張国 日本国 (JP)

(73) 特許権者 000153878

株式会社半導体エネルギー研究所

神奈川県厚木市長谷398番地

(74) 代理人 100103159

弁理士 加茂 裕邦

(72) 発明者 湯川 幹央

神奈川県厚木市長谷398番地 株式会社

半導体エネルギー研究所内

(72) 発明者 杉澤 希

神奈川県厚木市長谷398番地 株式会社

半導体エネルギー研究所内

審査官 外山 毅

最終頁に続く

(54) 【発明の名称】半導体装置

## (57) 【特許請求の範囲】

## 【請求項 1】

複数の記憶素子と、絶縁層と、を有し、前記複数の記憶素子はそれぞれ、第1の導電層と、半導体層と、有機化合物を含む層と、第2の導電層と、を有し、前記半導体層及び前記有機化合物を含む層は、前記第1の導電層と前記第2の導電層の間に設けられ、前記半導体層は、前記第1の導電層または前記第2の導電層に接して設けられ、前記絶縁層は、前記第1の導電層の端部と重なる領域を有し、前記第1の導電層は、前記絶縁層の下方に設けられ、

10

前記有機化合物を含む層と、前記第2の電極層とは、前記絶縁層の上方に設けられ、前記複数の記憶素子における前記有機化合物を含む層は、前記絶縁層の上方において分離していることを特徴とする半導体装置。

## 【請求項 2】

請求項1において、前記絶縁層の側面は、前記第1の導電層の表面に対して10度以上60度未満の傾斜角度を有することを特徴とする半導体装置。

## 【請求項 3】

請求項1または請求項2において、前記電気的作用を加えることによって、前記第1の導電層と前記第2の導電層とを短絡

20

させることを特徴とする半導体装置。

**【請求項 4】**

請求項1または請求項2において、

前記電気的作用を加えることによって、前記有機化合物を含む層を物理的または電気的に変化させることを特徴とする半導体装置。

**【発明の詳細な説明】**

**【技術分野】**

**【0001】**

本発明は、記憶素子及び当該記憶素子を有する半導体装置に関する。 10

**【背景技術】**

**【0002】**

近年、絶縁表面上に複数の回路が集積され、様々な機能を有する半導体装置の開発が進められている。また、アンテナを設けることにより、無線によるデータの送受信が可能な半導体装置の開発が進められている。このような半導体装置は、無線チップ（I D タグ、I C タグ、I C チップ、R F (Radio Frequency) タグ、無線タグ、電子タグ、R F I D (Radio Frequency Identification) ともよばれる）とよばれ、既に一部の市場で導入されている。

**【0003】**

現在実用化されているこれらの半導体装置の多くは、シリコン等の半導体基板を用いた回路（I C (Integrated Circuit) チップとも呼ばれる）とアンテナとを有する。そして、当該 I C チップは記憶回路（メモリとも呼ぶ）や制御回路等から構成されている。特に多くのデータを記憶可能な記憶回路を備えることによって、より高機能で付加価値が高い半導体装置の提供が可能となる。また、これらの半導体装置を低コストで作製することが要求されており、近年、制御回路や記憶回路等に有機化合物を用いた有機薄膜トランジスタ（以下、「有機TFT」ともいう。）や有機メモリ等の開発が盛んに行われている（例えば特許文献 1 参照）。 20

**【特許文献 1】特開 2002 - 26277 号公報**

**【発明の開示】**

**【発明が解決しようとする課題】**

**【0004】**

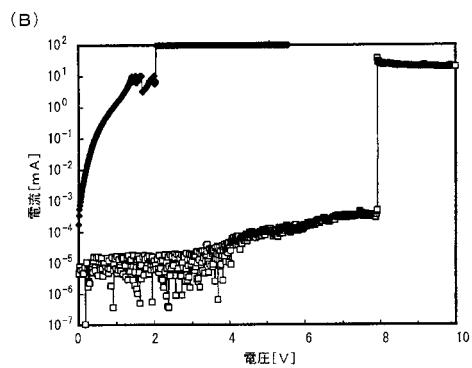

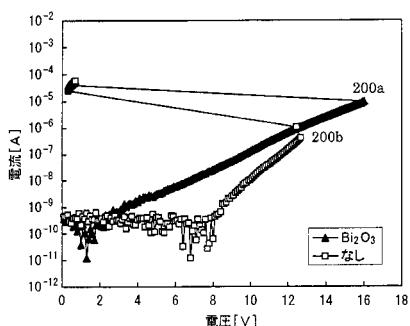

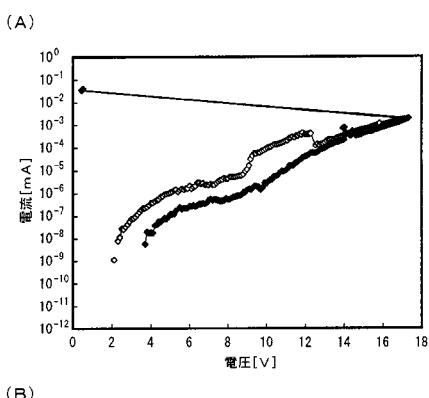

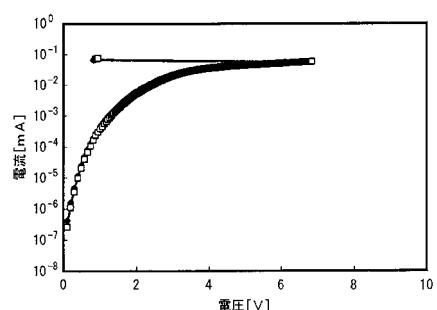

有機メモリの記憶部分としてはたらく記憶素子は、一対の電極間に有機化合物層を設けることで形成される。実際に作製し動作させると、異常な挙動を示したり、同一構成の記憶素子であっても素子毎に書き込み挙動（電流 - 電圧特性等）にばらつきが生じことがある。例えば、第 1 の導電層と、有機化合物層と、第 2 の導電層とを順に積層した記憶素子の電流 - 電圧特性を図 1 に示す。なお、第 1 の導電層には膜厚 100 nm のチタンを、有機化合物層には膜厚 8 nm の 4 , 4' - ビス [ N - ( 1 - ナフチル ) - N - フェニルアミノ ] ピフェニル（略称：N P B）を、第 2 の導電層には膜厚 200 nm のアルミニウムを用いた。図 1 ( A ) では 20 μm × 20 μm (以下、20 μm 角と表記する) の記憶素子における電流 - 電圧特性を、( B ) では 10 μm × 10 μm (10 μm 角) の記憶素子における電流 - 電圧特性を示した。それぞれサンプル数 n は 2 とし、印加方法は連続的に印加電圧を変化させるスイープ方式とした。なお、ここでは電流値の測定限界を 100 mA に設定している。 40

**【0005】**

図 1 ( A ) に示した記憶素子においては、電圧が約 7 V 付近で電流値が急増している。電極間が完全にショートしていると電流値は設定値である 100 mA となるはずであるが、電圧 7 V 以上における電流値は 100 mA 以下となっている。すなわち、完全な書き込みが達成されていないと言える。一方、図 1 ( B ) に示した記憶素子においては、2 つのサンプルの測定結果が大きく異なっている。一つは電圧約 2 V で電流値が大きく変化し、電流値は測定限界である設定値 100 mA に達している。すなわち、約 2 V で電極間がシ 50

ヨートしている。しかし、他方の記憶素子では約 8 V で電流値が大きく変化し、電流値は設定値である 100 mA に達していない。このため、これらの素子を記憶素子として利用するには信頼性が乏しいものになる。

#### 【 0 0 0 6 】

また、記憶素子を記憶装置等に利用する場合、複数の記憶素子を搭載する場合が多い。このような場合、記憶素子が素子毎にばらつくと、書き込み動作を行う際に最も高い書き込み電圧を要する記憶素子の電圧に合わせる必要があり、消費電力が高くなる。そのうえ、素子毎に挙動が異なると、信頼性の高い記憶装置を得られない。

#### 【 0 0 0 7 】

上記問題を鑑み、本発明は、記憶素子毎の挙動のばらつきを低減することを目的とする。また、性能及び信頼性に優れた記憶装置及びその記憶装置を備えた半導体装置を得ることを課題とする。10

#### 【課題を解決するための手段】

#### 【 0 0 0 8 】

本発明の一は、第 1 の導電層と、半導体層と、有機化合物層と、第 2 の導電層とを有し、半導体層及び有機化合物層は第 1 の導電層及び第 2 の導電層に挟持され、半導体層は第 1 の導電層もしくは第 2 の導電層に接して形成されることを特徴とする記憶素子である。

#### 【 0 0 0 9 】

また、本発明の一は、第 1 の導電層と、第 1 の半導体層と、有機化合物層と、第 2 の半導体層と、第 2 の導電層とを有し、第 1 の半導体層、第 2 の半導体層及び有機化合物層は第 1 の導電層及び第 2 の導電層に挟持され、第 1 の半導体層及び第 2 の半導体層は、それぞれ第 1 の導電層及び第 2 の導電層に接して形成されていることを特徴とする記憶素子である。20

#### 【 0 0 1 0 】

上記構成において、半導体層は、連続層に限らず非連続層であっても良く、例えば縞状、網目状としても良い。また、半導体層は、凹凸を有していても良い。

#### 【 0 0 1 1 】

また、本発明の一は、第 1 の導電層と、粒子と、有機化合物層と、第 2 の導電層とを有し、粒子及び有機化合物層は第 1 の導電層及び第 2 の導電層に挟持され、粒子は第 1 の導電層に接し、なおかつ半導体から形成されることを特徴とする記憶素子である。30

#### 【 0 0 1 2 】

また、本発明の一は、第 1 の導電層と、粒子と、有機化合物層と、第 2 の導電層とを有し、粒子及び有機化合物層は第 1 の導電層及び第 2 の導電層に挟持され、粒子は第 1 の導電層もしくは第 2 の導電層のいずれか一方に接し、なおかつ半導体から形成されることを特徴とする記憶素子である。

#### 【 0 0 1 3 】

また、上記記憶素子の第 1 の導電層又は第 2 の導電層にはダイオードが接続されていても良い。

#### 【 0 0 1 4 】

また、上記記憶素子において、有機化合物層は絶縁物を有していても良い。40

#### 【 0 0 1 5 】

本発明の記憶素子の有機化合物層は、電子輸送材料又はホール輸送材料を用いて形成される。また、電圧の印加により電気的特性を変化させ、データの書き込みを行う。電気的特性には例えば抵抗値があり、書き込んだ際には対となる第 1 の導電層及び第 2 の導電層の一部が接続、つまり短絡（以下、「ショート」ともいう。）することにより抵抗値に変化が生じる。

#### 【 0 0 1 6 】

また、本発明の一は上記記憶素子がマトリックス状に複数配置されていることを特徴とする半導体装置である。また、その複数の記憶素子の各々は、薄膜トランジスタに接続されていても良い。50

**【0017】**

上記半導体装置は、記憶素子と回路を介して電気的に接続された、アンテナとして機能する第3の導電層を有していても良い。

**【0018】**

書き込み電圧は、第1の導電層と第2の導電層との間に電圧を印加することにより記憶素子の電気的特性を変化させる電圧であれば特に限定されない。この記憶素子の電気的特性を大幅に変化させるために要する印加電圧の最小値を、本明細書においては書き込み電圧と表記することとする。このように電圧の印加による記憶素子の電気的特性の変化を利用してデータの書き込みを行う。また、読み取り電圧とは、書き込み動作による初期状態からの電気的特性の変化を読み取る際に用いる印加電圧であり、記憶素子の電気的特性を変化させない程度の電圧であれば特に限定されない。10

**【0019】**

また、本明細書において、第1の導電層及び第2の導電層を電極と記載することもある。。

**【発明の効果】****【0020】**

本発明により、記憶素子毎の挙動のばらつきを低減することができ、性能及び信頼性に優れた記憶装置及びその記憶装置を備えた半導体装置を得ることができる。

**【発明を実施するための最良の形態】****【0021】**

本発明の実施の形態について、図面を用いて以下に説明する。ただし、本発明は以下の説明に限定されず、本発明の趣旨及びその範囲から逸脱することなくその形態及び詳細を様々に変更し得ることは当業者であれば容易に理解される。したがって、本発明は以下に示す実施の形態の記載内容に限定して解釈されるものではない。なお、以下に説明する本発明の構成において、同じものを指す符号は異なる図面間で共通して用いる場合がある。20

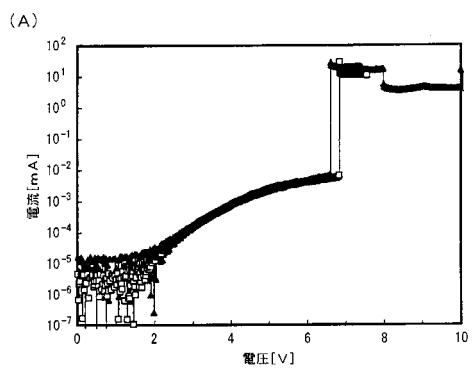

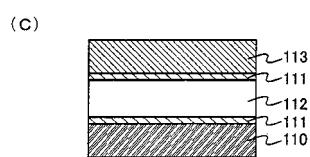

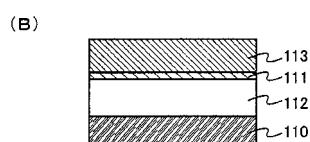

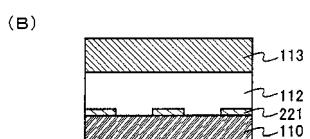

**【0022】****(実施の形態1)**

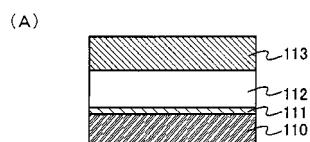

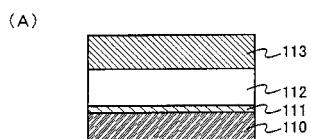

本発明の記憶素子の一構成例を図2を用いて説明する。図2(A)に示す記憶素子は、第1の導電層110と、半導体層111と、有機化合物層112と、第2の導電層113とを有する。半導体層111及び有機化合物層112は第1の導電層110と第2の導電層113に挟持された構成であり、半導体層111は、第1の導電層110上に接して形成されている。30

**【0023】**

第1の導電層110と第2の導電層113には、単層または積層構造からなる導電性の高い金属、合金、化合物等を用いることができる。

**【0024】**

例えば、インジウム錫酸化物(以下、ITOと表記する)、珪素を含有したインジウム錫酸化物、ITOに2~20 [wt%] の酸化亜鉛(ZnO)を混合したターゲットを用いて形成されるインジウム亜鉛酸化物(略称:IZO)等が挙げられる。また、チタン(Ti)、金(Au)、白金(Pt)、ニッケル(Ni)、タンゲステン(W)、クロム(Cr)、モリブデン(Mo)、鉄(Fe)、コバルト(Co)、銅(Cu)、パラジウム(Pd)、または金属材料の窒化物(例えば、窒化チタン(TiN)、窒化タンゲステン(WN)、窒化モリブデン(MoN))の他、元素周期表の1族または2族に属する金属、即ちリチウム(Li)やセシウム(Cs)等のアルカリ金属、マグネシウム(Mg)、カルシウム(Ca)、ストロンチウム(Sr)等のアルカリ土類金属、及びこれらのいずれかを含む合金(たとえば、Mg:Ag、Al:Li)等が挙げられる。また、ユーロピウム(Er)、イッテルビウム(Yb)等の希土類金属およびこれらを含む合金等を用いてもよい。40

**【0025】**

なお、第1の導電層110は、蒸着法、スパッタ法、CVD法、印刷法、電界メッキ法

50

、無電界メッキ法等を用いて形成される。

**【0026】**

第2の導電層113は、蒸着法、スパッタ法、CVD法、印刷法または液滴吐出法を用いて形成することができる。なお、液滴吐出法とは、所定の組成物を含む液滴を細孔から吐出してパターンを形成する方法である。

**【0027】**

有機化合物層112は、外部からの電圧の印加により、結晶状態、導電性や形状が変化する有機化合物で形成する。有機化合物層112は、単層で設けてもよいし、異なる有機化合物で形成された層を積層させて複数層としても良い。

**【0028】**

なお、有機化合物層112は、外部からの電圧印加により記憶素子の電気抵抗が変化する膜厚で形成する。有機化合物層112の代表的な膜厚は、5nmから100nm、好ましくは10nmから60nmである。

**【0029】**

半導体層111には、酸化モリブデン、酸化スズ、酸化ビスマス、シリコン、酸化バナジウム、酸化ニッケル、酸化亜鉛、シリコンゲルマニウム、ヒ化ガリウム、窒化ガリウム、酸化インジウム、リン化インジウム、窒化インジウム、硫化カドミウム、テルル化カドミウム、チタン酸ストロンチウムなどの無機半導体を用いることができる。

**【0030】**

なお、半導体層111の膜厚は、0.1nm以上であれば特に限定されず、例えば10nm以下の薄い膜厚でも良いし、それ以上であっても良い。なお、後者の場合においては、半導体層を設けた場合における効果の他、プロセス中に混入したゴミや導電層表面の微少な凹凸によって生じる記憶素子のショートを防ぐことができる。

**【0031】**

半導体層111は、蒸着法、電子ビーム蒸着法、スパッタリング法、CVD法等を用いて形成することができる。また、他の形成方法として、スピンドル法、ゾル・ゲル法、印刷法または液滴吐出法等を用いても良いし、上記方法とこれらを組み合わせてもよい。

**【0032】**

有機化合物層112は、正孔輸送性もしくは電子輸送性を有する有機化合物を用いて形成することができる。

**【0033】**

なお、正孔輸送性を有する有機化合物としては、2,7-ジ( N -カルバゾリル) -スピロ - 9 , 9' - ビフルオレン(略称:SFDCz)、4,4' - ビス[ N -( 1 - ナフチル ) - N - フェニルアミノ ] ビフェニル(略称:NPB)や4,4' - ビス[ N -( 3 - メチルフェニル ) - N - フェニル - アミノ ] - ビフェニル(略称:TPD)や4,4' , 4' ' - トリス( N , N - デフェニル - アミノ ) - トリフェニルアミン(略称:TDA-TA)、4,4' , 4' ' - トリス[ N -( 3 - メチルフェニル ) - N - フェニル - アミノ ] - トリフェニルアミン(略称:MTDATA)や4,4' - ビス( N -( 4 - ( N , N - デ - m - トリルアミノ ) フェニル ) - N - フェニルアミノ ) ビフェニル(略称:DNTPD)などの芳香族アミン系(即ち、ベンゼン環 - 窒素の結合を有する)の化合物やフタロシアニン(略称:H<sub>2</sub>Pc)、銅フタロシアニン(略称:CuPc)、バナジルフタロシアニン(略称:VOPc)のようなフタロシアニン化合物等が挙げられる。ここに述べた物質は、主に10<sup>-6</sup>cm<sup>2</sup>/Vs以上10<sup>-2</sup>cm<sup>2</sup>/Vs以下の正孔移動度を有する物質である。

**【0034】**

電子輸送性の高い有機化合物としては、トリス(8-キノリノラト)アルミニウム(略称:Alq)、トリス(4-メチル-8-キノリノラト)アルミニウム(略称:Almq<sub>3</sub>)、ビス(10-ヒドロキシベンゾ[h]-キノリナト)ベリリウム(略称:BeBq<sub>2</sub>)、ビス(2-メチル-8-キノリノラト)-4-フェニルフェノラト-アルミニウム(略称:BA1q)等キノリン骨格またはベンゾキノリン骨格を有する金属錯体等からなる

10

20

30

40

50

材料を用いることができる。また、この他、ビス[2-(2-ヒドロキシフェニル)ベンゾオキサゾラト]亜鉛(略称: Zn(BOX)<sub>2</sub>)、ビス[2-(2-ヒドロキシフェニル)ベンゾチアゾラト]亜鉛(略称: Zn(BTZ)<sub>2</sub>)などのオキサゾール系、チアゾール系配位子を有する金属錯体などの材料も用いることができる。さらに、金属錯体以外にも、2-(4-ビフェニリル)-5-(4-tert-ブチルフェニル)-1,3,4-オキサジアゾール(略称: PBD)、1,3-ビス[5-(p-tert-ブチルフェニル)-1,3,4-オキサジアゾール-2-イル]ベンゼン(略称: OXD-7)、3-(4-tert-ブチルフェニル)-4-フェニル-5-(4-ビフェニリル)-1,2,4-トリアゾール(略称: p-EtTAZ)、バソフェナントロリン(略称: BPhen)、バソキュプロイン(略称: BCp)等が挙げられる。ここに述べた物質は、主に $10^{-6}\text{ cm}^2/\text{Vs}$ 以上 $10^{-2}\text{ cm}^2/\text{Vs}$ 以下の電子移動度を有する物質である。

10

#### 【0035】

なお、上記範囲外の移動度を有する物質であっても良く、例えば2,3-ビス(4-ジフェニルアミノフェニル)キノキサリン(略称: TP AQn)等を用いて形成してもよい。

#### 【0036】

有機化合物層112は、蒸着法、電子ビーム蒸着法、スパッタリング法、CVD法等を用いて形成することができる。また、他の形成方法として、スピンドロート法、ゾル・ゲル法、印刷法または液滴吐出法等を用いててもよいし、上記方法とこれらを組み合わせてもよい。

20

#### 【0037】

また、有機化合物層112は、正孔輸送性もしくは電子輸送性を有する有機化合物に絶縁物が混合されていても良い。なお、絶縁物は、均一に分散されている必要はない。絶縁物を混合することにより、有機化合物層112のモルフォロジーを向上することができる。よって、部分的な膜の結晶化等を抑制することができるため、さらに記憶素子毎の挙動のばらつきを抑制することができる。

#### 【0038】

なお、絶縁物としては絶縁性を有する無機化合物または有機化合物を用いることができる。例えば無機化合物としては、酸化リチウム(Li<sub>2</sub>O)、酸化ナトリウム(Na<sub>2</sub>O)、酸化カリウム(K<sub>2</sub>O)、酸化ルビジウム(Rb<sub>2</sub>O)、酸化ベリリウム(BeO)、酸化マグネシウム(MgO)、酸化カルシウム(CaO)、酸化ストロンチウム(SrO)、酸化バリウム(BaO)等の酸化物、フッ化リチウム(LiF)、フッ化ナトリウム(NaF)、フッ化カリウム(KF)、フッ化ルビジウム(RbF)、フッ化ベリリウム(BeF<sub>2</sub>)、フッ化マグネシウム(MgF<sub>2</sub>)、フッ化カルシウム(CaF<sub>2</sub>)、フッ化ストロンチウム(SrF<sub>2</sub>)、フッ化バリウム(BaF<sub>2</sub>)等のフッ化物や、その他絶縁性を有する窒化物、塩化物、臭化物、ヨウ化物、炭酸塩、硫酸塩若しくは硝酸塩等が挙げられる。また、絶縁性を有する有機化合物としては、ポリイミド、アクリル、ポリアミド、ベンゼンシクロブテン、ポリエステル、ノボラック樹脂、メラミン樹脂、フェノール樹脂、エポキシ樹脂、珪素樹脂、フラン樹脂、ジアリルフタレート樹脂等を用いることができる。また、ケイ素と酸素との結合で主鎖骨格構造が構成される、いわゆるシロキサン系の材料を用いてもよい。

30

40

#### 【0039】

なお、このような混合層は、各々の材料を同時に成膜することにより形成することができ、たとえば抵抗加熱による共蒸着法、電子ビーム蒸着同士による共蒸着法、抵抗加熱蒸着と電子ビーム蒸着による共蒸着法、抵抗加熱蒸着とスパッタリング法による成膜、電子ビーム蒸着とスパッタリング法による成膜など、同種もしくは異種の方法を組み合わせて形成することができる。また、他の形成方法として、スピンドロート法、ゾル・ゲル法、印刷法または液滴吐出法等を用いててもよいし、これらも上記方法と組み合わせてもよい。

50

た、同時に形成するのではなく、有機化合物層を形成した後に、イオン注入法やドーピング法などによって絶縁物を導入し、有機化合物と絶縁物との混合層を形成してもよい。

#### 【0040】

上記のような構成を有する記憶素子は、第1の導電層に接して半導体層を設けることにより前記導電層表面の局所的な電界の集中を抑制することができる。よって、有機化合物層内において電流の流れる領域を増加させることができるために、過電流による導電層等の破壊や記憶素子の絶縁状態化を抑制することができる。

#### 【0041】

以上のことから、記憶素子の異常な挙動を抑制し、さらには記憶素子毎の挙動のばらつきを低減することが可能となる。

10

#### 【0042】

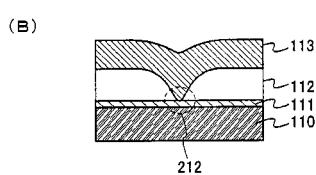

次に、記憶素子の動作機構について図3を用いて説明する。まず、電圧を印加する前の記憶素子を図3(A)に示す。第1の導電層110と第2の導電層113との間に電圧を印加すると、第1の導電層110から半導体層111にキャリアが注入され、ある印加電圧に達した時、有機化合物層112が変形する。これにより、第1の導電層110と第2の導電層113とが短絡し、その結果記憶素子がショートする(図3(B)の212参照)。このようにして、電圧印加前後での記憶素子の導電性が変化する。

#### 【0043】

このように、電圧を印加することによる記憶素子の導電性の変化を利用してデータの書き込みを行う。

20

#### 【0044】

また、記憶素子の構成は図2(A)に限らず、図2(B)のように半導体層111は第2の導電層113に接して設けられていても良い。また、図2(C)に示すように、半導体層111を第1の導電層110及び第2の導電層113に接するように2層設けても良い。

#### 【0045】

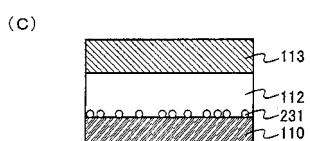

また、半導体層111の形状は、図2で示したように第1の導電層110の表面形状と同様の形状である必要はなく、図4(A)に示すように第1の導電層110に依存しない凹凸を有する半導体層211であっても良い。

30

#### 【0046】

また、半導体層111の形状は、連続層である必要はなく、図4(B)に示す半導体層221のように縞状の非連続層とすることもできる。なお、半導体層221の縞方向は、特に限定されない。たとえ、非連続層であっても導電層表面の局所的な電界の集中を抑制することができるため、上記と同様の効果を得ることができる。

#### 【0047】

また、図4(C)に示すように半導体層111を粒子231の形状で設けてもよい。このときの粒子231の粒径は特に限定されない。

#### 【0048】

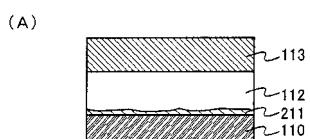

さらに、半導体層111の形状は図5に示す形状であっても良い。なお、図5は上面図であり、半導体層は半導体層311、321、331である。

40

#### 【0049】

図5(A)に示すように、半導体層311は、少なくとも第1の導電層110の一部分を覆う島状の非連続層とすることができます。ここでは、複数の非連続層である半導体層311が不規則に第1の導電層110の表面上に分散されている。

#### 【0050】

また、図5(B)に示すように、第1の導電層110上に設けられた半導体層321は、第1の導電層110のいずれかの一辺に対し所定の角度(-90度以上かつ90度未満)を有する縞状の非連続層とすることができます。

#### 【0051】

50

また、図5(C)に示すように、第1の導電層110上に設けられた半導体層331を、網状とすることもできる。

#### 【0052】

なお、半導体層は一層である必要はなく、積層構造としても良い。また、その積層された半導体層の各々は上述した形状とすることができる。

#### 【0053】

なお、本発明の記憶素子に印加する電圧は、第2の導電層113に比べ第1の導電層110により高い電圧をかけてもよいし、第1の導電層110に比べ第2の導電層113により高い電圧をかけてもよい。

#### 【0054】

以上のような構成とすることで、記憶素子における導電層等の破壊や絶縁状態化などの異常な挙動を抑制することができる。よって、記憶素子毎の挙動のばらつきを低減することが可能となる。

#### 【0055】

したがって、読み取り電圧のとり得る幅も広がり、記憶素子における設計の自由度が向上する。また、本発明の記憶素子は、書き込みを一度行った記憶素子に対しデータを消去することは不可能なため、書き換えによる偽造を防止することができる。さらに、本発明の記憶素子は一対の導電層間に半導体層及び有機化合物層が挟まれた単純な構造であるため、性能及び信頼性に優れた記憶素子を安価に作製することが可能となる。

#### 【0056】

##### (実施の形態2)

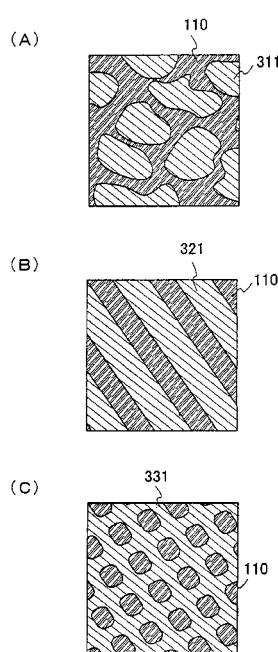

本実施形態では、本発明の記憶素子を有する半導体装置、代表的には記憶装置について図面を用いて説明する。なお、記憶装置の構成がパッシブマトリクス型の場合に関して示す。

#### 【0057】

本実施形態で示す半導体装置の一構成例を図6(A)に示す。半導体装置400は、記憶素子401がマトリクス状に設けられたメモリセルアレイ411、デコーダ412、413、セレクタ414、読み出し/書き込み回路415を有する。なお、ここで示す半導体装置400の構成はあくまで一例であり、センスアンプ、出力回路、バッファ等の他の回路を有していてもよい。

#### 【0058】

なお、デコーダ412、413、セレクタ414、読み出し/書き込み回路415、インターフェース等は、記憶素子と同様に基板上に形成しても良いし、ICチップとして外付けしても良い。

#### 【0059】

記憶素子401は、ピット線B×(1×m)に接続される第1の導電層と、ワード線W<sub>y</sub>(1 y n)に接続される第2の導電層と、第1の導電層に接する半導体層と、半導体層上の有機化合物層とを有する。

#### 【0060】

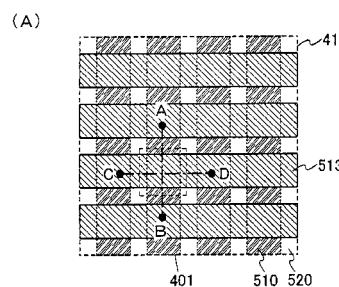

メモリセルアレイ411の上面図と断面図の一例に関して図7に示す。なお、図7(A)はメモリセルアレイ411の一部の上面図を示している。

#### 【0061】

メモリセルアレイ411には、記憶素子401がマトリクス状に設けられている。記憶素子401は、基板上に、第1の方向(A-B)に延びた第1の導電層510と、第1の導電層510を覆う半導体層及び有機化合物層520と、第1の方向と垂直な第2の方向(C-D)に延びた第2の導電層513とを有する。なお、前記半導体層は、実施の形態1で示した半導体層111と同様の物質を用いることができる。また、図7(A)では、保護膜として機能する第2の導電層513を覆うように設けられた絶縁層が省略されている。

#### 【0062】

10

20

30

40

50

なお、本実施形態における第1の導電層510は、実施の形態1における第1の導電層110に相当し、半導体層及び有機化合物層520のそれぞれは半導体層111及び有機化合物層112に相当する。また、第2の導電層513は実施の形態1における第2の導電層113に相当する。実施の形態1と同様のものに関しては共通の符号を用いて示し、同一部分又は同様な機能を有する部分の詳細な説明は省略する。

#### 【0063】

図7(A)におけるC-D間の断面構造の例を図7(B)に示す。記憶素子401が設けられた基板521には、ガラス基板や可撓性基板の他、石英基板、シリコン基板、金属基板、ステンレス基板、繊維質な材料からなる紙等を用いることができる。可撓性基板とは、折り曲げができる(フレキシブル)基板のことであり、例えば、ポリカーボネート、ポリアリレート、ポリエーテルスルファン等からなるプラスチック基板等が挙げられる。また、フィルム(ポリプロピレン、ポリエチレン、ビニル、ポリフッ化ビニル、塩化ビニルなどからなる)を用いることもできる。

10

#### 【0064】

また、絶縁性を有する基板上に薄膜トランジスタ(TFT)を設けてその上に記憶素子401を設けてもよいし、上記基板の代わりにSi等の半導体基板やSOI基板を用いて基板上に電界効果トランジスタ(FET)を形成しその上に記憶素子401を設けてもよい。また、記憶素子401と薄膜トランジスタまたは電界効果トランジスタを貼り合わせることによって設けてもよい。この場合、記憶素子部と薄膜トランジスタまたは電界効果トランジスタは別工程で作製し、その後、導電性フィルムや異方性導電接着剤等を用いて貼り合わせることによって設けることができる。

20

#### 【0065】

図7(B)では、まず基板521上に第1の導電層110を、蒸着法、スパッタ法、CVD法、印刷法、電界メッキ法、無電界メッキ法、印刷法等を用いて形成する。次に、第1の導電層110上に半導体層111および有機化合物層112を、蒸着法、電子ビーム蒸着法、スパッタリング法、CVD法等を用いて形成する。また、他の形成方法として、スピンドル法、ゾル・ゲル法、印刷法または液滴吐出法等を用いてもよいし、上記方法これらを組み合わせてもよい。さらに、有機化合物層112上に第2の導電層113を、蒸着法、スパッタ法、CVD法、印刷法または液滴吐出法を用いて形成する。そして、第2の導電層113を覆うように保護膜として機能する絶縁層522を設ける。

30

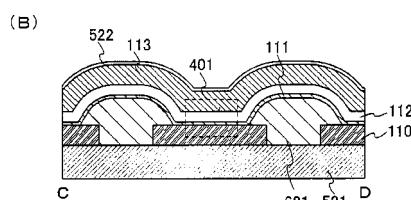

#### 【0066】

図8(A)に示すように、記憶素子401において第1の導電層110と基板521の間に整流性を有する素子を設けてもよい。整流性を有する素子とは、ショットキー・バリア型、PIN型、PN型のダイオードの他、ダイオード接続されているトランジスタ等があげられる。ここでは、第3の導電層612及び半導体層613で構成されるダイオード611を第1の導電層110の下に接して設ける。なお、各記憶素子に対応するダイオード611は、層間絶縁膜614により分離されている。また、整流性を有する素子は第2の導電層113を介して有機化合物層112と反対側に設けてもよい。

#### 【0067】

また、隣接する記憶素子間への電界の影響が懸念される場合は、各記憶素子に設けられた有機化合物層を分離するため、各記憶素子に設けられた有機化合物層の間に隔壁(絶縁層)を設けてもよい。つまり、各記憶素子ごとに有機化合物層を選択的に設けた構成としてもよい。

40

#### 【0068】

また、図8(B)に示すように、各記憶素子401の第1の導電層110の間に隔壁(絶縁層)621を設けてもよい。これにより、隣接する記憶素子間への電界の影響を防止するだけではなく、第1の導電層110を覆って半導体層111及び有機化合物層112を設ける際に第1の導電層110の段差により生じるこれら有機化合物層の段切れを防止することができる。なお、隔壁(絶縁層)621の断面において、隔壁(絶縁層)621の側面は、第1の導電層110の表面に対して10度以上60度未満、好ましくは25度

50

以上45度以下の傾斜角度を有することが好ましい。さらには、湾曲していることが好ましい。このように隔壁(絶縁層)621を設けた後、第1の導電層110および隔壁(絶縁層)621を覆うように半導体層111、有機化合物層112及び第2の導電層113を形成する。また、第1の導電層110上に半導体層111を形成した後、隔壁(絶縁層)621を形成してもよい。

#### 【0069】

次に、記憶素子へのデータの書き込み動作について説明する。ここでは、電気的作用、代表的には電圧の印加によりデータの書き込みを行う場合について図6を用いて説明する。なお、書き込みは記憶素子の電気的特性を変化させることで行うが、記憶素子の初期状態(電気的作用を加えていない状態)をデータ「0」、電気的特性を変化させた状態をデータ「1」とする。

#### 【0070】

記憶素子401にデータ「1」を書き込む場合、まず、デコーダ412、413およびセレクタ414によって記憶素子401を選択する。具体的には、デコーダ413によって、記憶素子401に接続されるワード線W3に所定の電位V2を印加する。また、デコーダ412とセレクタ414によって、記憶素子401に接続されるビット線B3を読み出し/書き込み回路415に接続する。そして、読み出し/書き込み回路415からビット線B3へ書き込み電位V1を出力する。こうして、当該記憶素子401を構成する第1の導電層と第2の導電層の間に電圧Vw = V1 - V2を印加する。電圧Vwを適切に選ぶことで、当該導電層間に設けられた有機化合物を含む層を物理的にもしくは電気的に変化させ、データ「1」の書き込みを行う。具体的には、読み出し動作電圧において、データ「1」の状態の第1の導電層と第2の導電層の間の電気抵抗が、データ「0」の状態と比べて、大幅に小さくなるように変化させるとよく、例えば第1の導電層と第2の導電層を短絡(ショート)させれば良い。なお、(V1、V2) = (0V、5~15V)、あるいは(3~5V、-12~-2V)の範囲から適宜選べば良い。電圧Vwは5V以上かつ15V以下、あるいは-15V以上かつ-5V以下とすればよい。

#### 【0071】

なお、非選択のワード線および非選択のビット線には、接続される記憶素子にデータ「1」が書き込まれないよう制御する。例えば、非選択のワード線および非選択のビット線を浮遊状態とすればよい。記憶素子に、ダイオード特性などの選択性を確保できる特性を付与する必要がある。また、非選択のワード線には、第2の導電層と同程度の電位を印加するとよい。

#### 【0072】

一方、記憶素子401にデータ「0」を書き込む場合は、記憶素子401には電気的作用を加えなければよい。回路動作上は、例えば、「1」を書き込む場合と同様に、デコーダ412、413およびセレクタ414によって記憶素子401を選択するが、読み出し/書き込み回路415からビット線B3への出力電位を、選択されたワード線W3の電位あるいは非選択ワード線の電位と同程度とし、記憶素子401を構成する第1の導電層と第2の導電層の間に、記憶素子401の電気的特性を変化させない程度の電圧(例えば-5以上5V以下)を印加すればよい。

#### 【0073】

続いて、記憶素子からデータの読み出しを行う際の動作について図6(B)を用いて説明する。データの読み出しは、記憶素子を構成する第1の導電層と第2の導電層の間の電気的特性が、データ「0」を有する記憶素子とデータ「1」を有する記憶素子とで異なることを利用して行う。例えば、データ「0」を有する記憶素子を構成する第1の導電層と第2の導電層の間の実効的な電気抵抗(以下、単に記憶素子の電気抵抗と呼ぶ)が、読み出し電圧においてR0、データ「1」を有する記憶素子の電気抵抗を、読み出し電圧においてR1とし、電気抵抗の差を利用して読み出す方法を説明する。なお、R1 << R0とする。読み出し/書き込み回路415は、読み出し部分の構成として、例えば図6(B)に示す抵抗素子450と差動増幅器451を有する回路を用いることができる。抵抗素子

10

20

30

40

50

450は抵抗値R<sub>r</sub>を有し、R<sub>1</sub> < R<sub>r</sub> < R<sub>0</sub>であるとする。また、抵抗素子450の代わりに図6(C)に示すように、トランジスタ452を用いても良いし、差動増幅器451の代わりにクロックトインバータ453を用いることも可能である。クロックトインバータ453には、読み出しを行うときにH<sub>igh</sub>(以下、H<sub>i</sub>)、行わないときにL<sub>ow</sub>(以下、L<sub>o</sub>)となる、信号又はその反転信号が入力される。もちろん、回路構成は図6(B)及び(C)に限定されない。

#### 【0074】

記憶素子402からデータの読み出しを行う場合、まず、デコーダ412、413およびセレクタ414によって記憶素子402を選択する。具体的には、デコーダ413によって、記憶素子402に接続されるワード線W<sub>y</sub>に所定の電位V<sub>y</sub>を印加する。また、デコーダ412とセレクタ414によって記憶素子402に接続されるビット線B<sub>x</sub>を、読み出し/書き込み回路415の端子Pに接続する。その結果、端子Pの電位V<sub>p</sub>は、V<sub>y</sub>とV<sub>0</sub>が抵抗素子450(抵抗値R<sub>r</sub>)と記憶素子402(抵抗値R<sub>0</sub>もしくはR<sub>1</sub>)による抵抗分割によって決定される値となる。従って、記憶素子402がデータ「0」を有する場合の端子Pの電位V<sub>p0</sub>は、 $V_{p0} = V_y + (V_0 - V_y) \times R_0 / (R_0 + R_r)$ となる。また、記憶素子402がデータ「1」を有する場合の端子Pの電位V<sub>p1</sub>には、 $V_{p1} = V_y + (V_0 - V_y) \times R_1 / (R_1 + R_r)$ となる。その結果、図6(B)では、V<sub>ref</sub>をV<sub>p0</sub>とV<sub>p1</sub>の間となるように選択することで、図6(C)ではクロックトインバータ453の変化点をV<sub>p0</sub>とV<sub>p1</sub>の間となるように選択することで、出力電位V<sub>out</sub>がデータ「0」/「1」に応じて、L<sub>o</sub>/H<sub>i</sub>(もしくはH<sub>i</sub>/L<sub>o</sub>)が出力され、読み出しを行うことができる。

10

20

#### 【0075】

例えば、差動増幅器451をV<sub>dd</sub>=3Vで動作させ、V<sub>y</sub>=0V、V<sub>0</sub>=3V、V<sub>ref</sub>=1.5Vとする。仮に、R<sub>0</sub>/R<sub>r</sub>=R<sub>r</sub>/R<sub>1</sub>=9とすると、記憶素子のデータが「0」の場合、V<sub>p0</sub>=2.7VとなりV<sub>out</sub>はH<sub>i</sub>が出力され、記憶素子のデータが「1」の場合、V<sub>p1</sub>=0.3VとなりV<sub>out</sub>はL<sub>o</sub>が出力される。こうして、記憶素子の読み出しを行うことができる。

#### 【0076】

上記の方法によると、有機化合物を含む層の電気抵抗の状態は、抵抗値の相違と抵抗分割を利用して、電圧値で読み取っている。勿論、読み出し方法は、この方法に限定されない。例えば、電気抵抗の差を利用する以外に、電流値の差を利用して読み出しても構わない。また、記憶素子の電気的特性がデータ「0」と「1」とでしきい値電圧が異なるダイオード特性を有する場合には、しきい値電圧の差を利用して読み出しても構わない。

30

#### 【0077】

また、絶縁性を有する基板上に薄膜トランジスタ(TFT)を設けてその上に記憶素子又は記憶素子アレイを設けてもよいし、絶縁性を有する基板の代わりにSi等の半導体基板やSOI基板を用いて基板上に電界効果トランジスタ(FET)を形成しその上に記憶素子又は記憶素子アレイを設けてもよい。

#### 【0078】

本実施形態で示した半導体装置は、本発明の記憶素子を有することにより導電層等の破壊や記憶素子の絶縁状態化などの異常な挙動を抑制することができる。よって、記憶素子毎の挙動のばらつきを低減することが可能となる。したがって、読み取り電圧のとり得る幅も広がり、半導体装置における設計の自由度が向上する。

40

#### 【0079】

また、半導体装置へのデータの書き込みは一度だけではなく、追加(追記)が可能である。一方、書き込みを一度行った記憶素子に対しデータを消去することは不可能なため、書き換えによる偽造を防止することができる。さらに、本発明の記憶素子は一対の導電層間に半導体層及び有機化合物層が挟まれた単純な構造であるため、性能及び信頼性に優れた半導体装置を低コストで作製することが可能となる。

#### 【0080】

なお、本実施形態は、他の実施の形態及び実施例とも自由に組み合わせることができる。

#### 【0081】

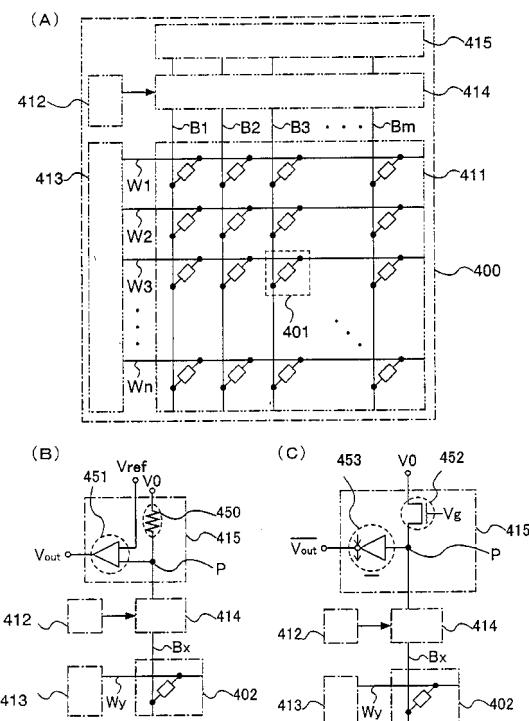

##### (実施の形態3)

本実施形態では、本発明の記憶素子を有する半導体装置について図9を用いて説明する。なお、具体的にはアクティブマトリクス型の記憶装置について説明する。

#### 【0082】

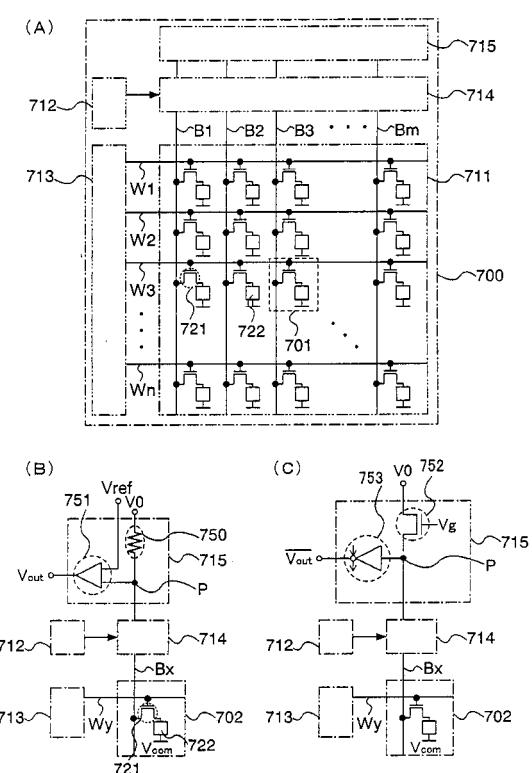

本実施形態で示す半導体装置の一構成例を図9(A)に示す。半導体装置700は、メモリセル701がマトリクス状に設けられたメモリセルアレイ711、デコーダ712、713、セレクタ714、読み出し／書き込み回路715を有する。なお、ここで示す半導体装置700の構成はあくまで一例であり、センスアンプ、出力回路、バッファ等の他の回路を有していてもよい。

10

#### 【0083】

なお、デコーダ712、713、セレクタ714、読み出し／書き込み回路715、インターフェース等は、記憶素子と同様に基板上に形成しても良いし、ICチップとして外付けしても良い。

#### 【0084】

メモリセル701は、ピット線 $B \times (1 \times m)$ に接続される第1の配線と、ワード線 $W_y (1 \times n)$ に接続される第2の配線と、薄膜トランジスタ721と、記憶素子722とを有する。記憶素子722は、一対の導電層の間に、半導体層及び有機化合物層が挟持された構造を有する。

20

#### 【0085】

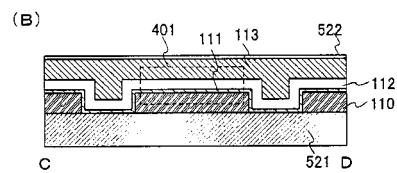

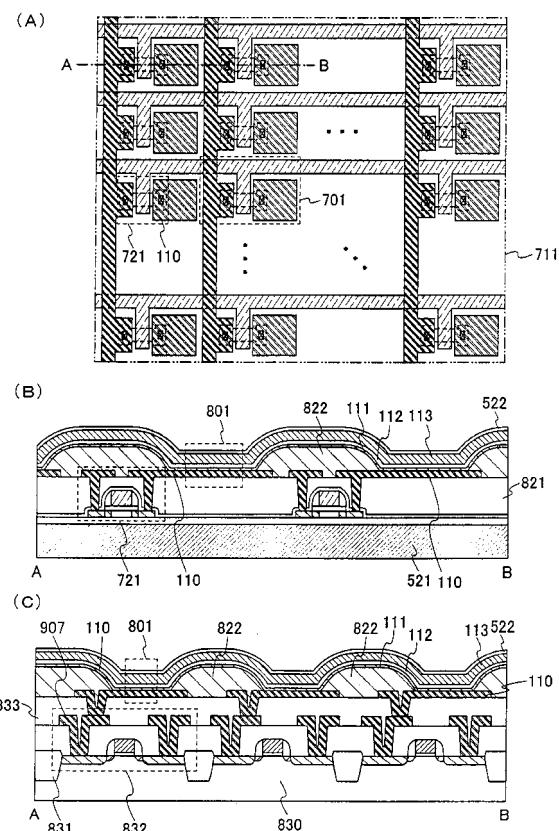

次に、上記構成を有するメモリセルアレイ711の上面図と断面図の一例に関して図10を用いて説明する。なお、図10(A)はメモリセルアレイ711の一部の上面図を示している。

#### 【0086】

メモリセルアレイ711は、複数のメモリセル701がマトリクス状に設けられている。又、メモリセル701は、絶縁表面を有する基板上にスイッチング素子として機能する薄膜トランジスタ721および当該薄膜トランジスタ721に接続された記憶素子が設かれている。

30

#### 【0087】

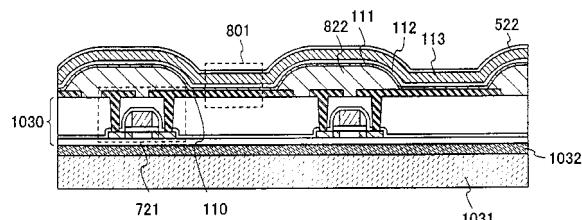

図10(A)におけるA-B間の断面構造の例を図10(B)に示す。なお、図10(A)では、第1の導電層110上に設けられている隔壁(絶縁層)822、半導体層111、有機化合物層112、第2の導電層113、絶縁層522が省略されている。

#### 【0088】

メモリセル701は、薄膜トランジスタ721と、記憶素子801と、絶縁層821と、第1の導電層110の一部を覆う隔壁(絶縁層)822とを有する。なお、記憶素子801を覆って保護膜として機能する絶縁層522が設けられている。絶縁表面を有する基板521上に形成された薄膜トランジスタ721に接続された記憶素子801は、絶縁層821上に形成された第1の導電層110と、半導体層111と、有機化合物層112と、第2の導電層113とを有する。なお、半導体層111は、実施の形態1で示した半導体層と同様の物質を用いることができる。また、薄膜トランジスタ721は、スイッチとして機能するものであれば特に限定されず、薄膜トランジスタである必要は特にならない。

40

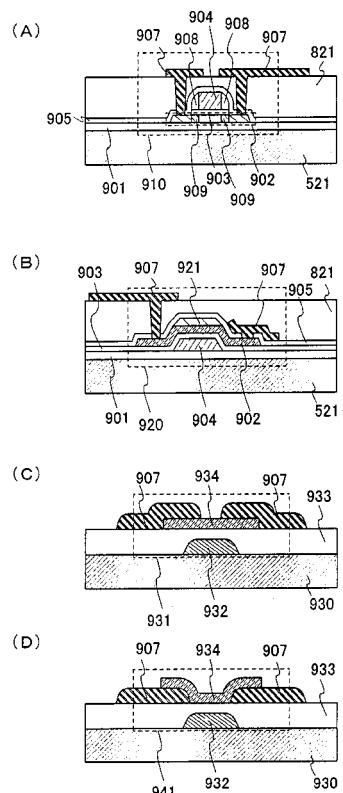

#### 【0089】

薄膜トランジスタ721の一態様について、図11を用いて説明する。図11(A)はトップゲート型の薄膜トランジスタを適用する一例を示している。基板521上に下地膜として絶縁層901が設けられ、絶縁層901上に薄膜トランジスタ910が設けられている。薄膜トランジスタ910は、絶縁層901上に半導体層902及びゲート絶縁層として機能することができる絶縁層903が形成され、さらに絶縁層903の上には半導体層902に対応してゲート電極904が形成されている。なお、薄膜トランジスタ910

50

上には保護層として機能する絶縁層 905 及び層間絶縁層として機能する絶縁層 821 が設けられている。また、半導体層のソース領域及びドレイン領域それぞれに接続する配線 907 が形成される。

#### 【0090】

絶縁層 901 には、酸化珪素膜、窒化珪素膜または酸化窒化珪素膜等の絶縁膜を用い、これら絶縁膜を単層又は 2 以上の複数層で形成する。なお、絶縁層 901 は、スパッタ法、CVD 法等を用いて形成すればよい。

#### 【0091】

半導体層 902 は、アモルファスシリコン等の非晶質半導体、セミアモルファス半導体、微結晶半導体等の非結晶性の半導体膜の他、ポリシリコン等の結晶性半導体膜を用いても良い。

10

#### 【0092】

特に、非晶質若しくは微結晶質の半導体を、レーザ光の照射により結晶化させた結晶性半導体、加熱処理により結晶化させた結晶性半導体、加熱処理とレーザ光の照射を組み合わせて結晶化させた結晶性半導体を適用することが好ましい。加熱処理においては、シリコン半導体の結晶化を助長する作用のあるニッケルなどの金属元素を用いた結晶化法を適用することができる。

#### 【0093】

レーザ光を照射して結晶化する場合には、連続発振レーザ光の照射若しくは繰り返し周波数が 10 MHz 以上であって、パルス幅が 1 ナノ秒以下、好ましくは 1 乃至 100 ピコ秒である高繰り返し周波数超短パルス光を照射することによって、結晶性半導体が溶融した溶融帯を、当該レーザ光の照射方向に連続的に移動させながら結晶化を行うことができる。このような結晶化法により、大粒径であって、結晶粒界が一方向に延びる結晶性半導体を得ることができる。キャリアのドリフト方向を、この結晶粒界が延びる方向に合わせることで、トランジスタにおける電界効果移動度を高めることができる。例えば、 $400 \text{ cm}^2 / \text{V} \cdot \text{sec}$  以上を実現することができる。

20

#### 【0094】

上記結晶化工程を、ガラス基板の耐熱温度（約 600）以下の結晶化プロセスを用いる場合、大面積ガラス基板を用いることが可能である。このため、基板あたり大量の半導体装置を作製することができる。低コスト化が可能である。

30

#### 【0095】

また、加熱温度にたえうる基板を用いて、ガラス基板の耐熱温度以上の加熱により結晶化工程を行い、半導体層 902 を形成してもよい。代表的には、絶縁性基板に石英基板を用い、非晶質若しくは微結晶質の半導体を 700 度以上で加熱して半導体層 902 を形成する。この結果、結晶性の高い半導体を形成することができる。この場合、応答速度や移動度などの特性が良好で、高速な動作が可能な薄膜トランジスタを提供することができる。

#### 【0096】

ゲート電極 904 は金属又は一導電型の不純物を添加した多結晶半導体で形成することができる。金属を用いる場合は、タンゲステン (W)、モリブデン (Mo)、チタン (Ti)、タンタル (Ta)、アルミニウム (Al) などを用いることができる。また、金属を窒化させた金属窒化物を用いることができる。或いは、当該金属窒化物からなる第 1 層と金属から成る第 2 層とを積層させた構造としても良い。積層構造とする場合には、第 1 層の端部が第 2 層の端部より外側に突き出した所謂ハット形状としても良い。このとき第 1 層を金属窒化物とすることで、バリアメタルとすることができます。すなわち、第 2 層の金属が、絶縁層 903 やその下層の半導体層 902 に拡散することを防ぐことができる。

40

#### 【0097】

なお、ゲート電極 904 の側面には、サイドウォール（側壁スペーサ）908 を形成しても良い。サイドウォールは、CVD 法により絶縁層を形成し、該絶縁層を RIE (Reactive ion etching : 反応性イオンエッチング) 法により異方性エッチングすることで形成

50

できる。

**【0098】**

半導体層902、絶縁層903、ゲート電極904などを組み合わせて構成されるトランジスタは、シングルドレイン構造、LDD（低濃度ドレイン）構造、ゲートオーバーラップドレイン構造など各種構造を適用することができる。なお、図11(A)では、サイドウォールが重畠する半導体層において、低濃度不純物領域909が形成されるLDD構造の薄膜トランジスタを示している。また、シングルゲート構造、等価的には同電位のゲート電圧が印加されるトランジスタが直列に接続された形となるマルチゲート構造、半導体層を上下にゲート電極で挟むデュアルゲート構造を適用することも可能である。

**【0099】**

絶縁層821は、酸化珪素及び酸化窒化珪素などの無機絶縁材料、又はアクリル樹脂及びポリイミド樹脂などの有機絶縁材料で形成する。スピン塗布やロールコーティングなど塗布法を用いる場合には、有機溶媒中に溶かされた絶縁膜材料を塗布した後、熱処理により酸化珪素で形成される絶縁層を用いることもできる。例えば、シロキサン結合を含む塗布膜を形成しておいて、200～400度での熱処理により形成可能な絶縁層を用いることができる。絶縁層821を、塗布法で形成する絶縁層やリフローにより平坦化した絶縁層を形成することで、その層上に形成する配線の断線を防止することができる。また、多層配線を形成する際にも有効に利用することができる。

**【0100】**

絶縁層821の上に形成される配線907は、ゲート電極904と同じ層で形成される配線と交差して設けることが可能であり、多層配線構造を形成している。絶縁層821と同様に機能を有する絶縁層を複数積層して、その層上に配線を形成することで多層配線構造を形成することができる。配線907はチタン(Ti)とアルミニウム(Al)の積層構造、モリブデン(Mo)とアルミニウム(Al)との積層構造など、アルミニウム(Al)のような低抵抗材料と、チタン(Ti)やモリブデン(Mo)などの高融点金属材料を用いたバリアメタルとの組み合わせで形成することが好ましい。

**【0101】**

図11(B)は、ボトムゲート型の薄膜トランジスタを適用する一例を示している。絶縁性基板521上に絶縁層901が形成され、その上に薄膜トランジスタ920が設けられている。薄膜トランジスタ920には、ゲート電極904、ゲート絶縁層として機能する絶縁層903及び半導体層902が設けられ、さらにその上にはチャネル保護層921、保護層として機能する絶縁層905及び層間絶縁層として機能する絶縁層821が設けられている。さらにその上層には、保護層として機能する絶縁層を形成しても良い。半導体層のソース領域及びドレイン領域それぞれに接続された配線907は、絶縁層905の層上若しくは絶縁層821の層上に形成することができる。なお、ボトムゲート型の薄膜トランジスタの場合は、絶縁層901が形成されなくともよい。

**【0102】**

また、基板521が可撓性を有する基板である場合、耐熱温度がガラス基板等の非可撓性基板と比較して低い。このため、薄膜トランジスタの半導体層に、有機半導体を用いて形成することが好ましい。

**【0103】**

ここで、有機半導体を用いる薄膜トランジスタの構造について、図11(C)、(D)を参照して説明する。図11(C)は、スタガ型の有機半導体トランジスタを適用する一例を示している。可撓性を有する基板930上に有機半導体トランジスタ931が設けられている。有機半導体トランジスタ931は、ゲート電極932、ゲート絶縁膜として機能する絶縁層933、ゲート電極932及び絶縁層933が重畠する場所に設けられた半導体層934とを有し、半導体層934には配線907が接続されている。なお、半導体層は、ゲート絶縁膜として機能する絶縁層933と配線907に接する。

**【0104】**

ゲート電極932は、ゲート電極904と同様の材料及び手法により、形成することが

10

20

30

40

50

できる。また、液滴吐出法を用い、乾燥・焼成してゲート電極 932 を形成することができる。また、可撓性を有する基板上に、微粒子を含むペーストを印刷法により印刷し、乾燥・焼成してゲート電極 932 を形成することができる。微粒子の代表例としては、金、銅、金と銀の合金、金と銅の合金、銀と銅の合金、金と銀と銅の合金のいずれかを主成分とする微粒子でもよい。また、インジウム錫酸化物 (ITO) などの導電性酸化物を主成分とする微粒子でもよい。

#### 【0105】

ゲート絶縁膜として機能する絶縁層 933 は、絶縁層 903 と同様の材料及び手法により形成することができる。但し、有機溶媒中に溶解する絶縁膜材料を塗布した後、熱処理により絶縁層を形成する場合、熱処理温度が可撓性を有する基板の耐熱温度より低い温度で行う。

10

#### 【0106】

有機半導体トランジスタの半導体層 934 の材料としては、多環芳香族化合物、共役二重結合系化合物、フタロシアニン、電界移動型錯体等が挙げられる。例えばアントラセン、テトラセン、ペンタセン、6T(ヘキサチオフェン)、TCNQ(テトラシアノキノジメタン)、PTCDA(ペリレンカルボン酸無水化物)、NTCDA(ナフタレンカルボン酸無水化物)などを用いることができる。また、有機半導体トランジスタの半導体層 934 の材料としては、有機高分子化合物等の 共役系高分子、カーボンナノチューブ、ポリビニルピリジン、フタロシアニン金属錯体等が挙げられる。特に骨格が共役二重結合から構成される 共役系高分子である、ポリアセチレン、ポリアニリン、ポリピロール、ポリチエニレン、ポリチオフェン誘導体、ポリ(3アルキルチオフェン)、ポリパラフェニレン誘導体又はポリパラフェニレンビニレン誘導体を用いると好ましい。

20

#### 【0107】

また、有機半導体トランジスタの半導体層の形成方法としては、基板に膜厚の均一な膜が形成できる方法を用いればよい。厚さは 1 nm 以上 1000 nm 以下、好ましくは 10 nm 以上 100 nm 以下が望ましい。具体的な方法としては、蒸着法、塗布法、スピニング法、バーコート法、溶液キャスト法、ディップ法、スクリーン印刷法、ロールコーティング法又は液滴吐出法を用いることができる。

#### 【0108】

図 11(D) は、コプレナー型の有機半導体トランジスタを適用する一例を示している。可撓性を有する基板 930 上に有機半導体トランジスタ 941 が設けられている。有機半導体トランジスタ 941 は、ゲート電極 932、ゲート絶縁膜として機能する絶縁層 933、ゲート電極 932 及び絶縁層 933 が重畠する場所に設けられた半導体層 934 とを有し、半導体層 934 には配線 907 が接続されている。また、半導体層 934 に接続された配線 907 は、ゲート絶縁膜として機能する絶縁層及び半導体層に接する。

30

#### 【0109】

さらには、薄膜トランジスタや有機半導体トランジスタはスイッチング素子として機能し得るものであれば、どのような構成で設けてもよい。

#### 【0110】

また、単結晶基板や SOI 基板を用いてトランジスタを形成し、その上に記憶素子を設けてもよい。SOI 基板はウェハの貼り合わせによる方法や酸素イオンを Si 基板内に打ち込むことにより内部に絶縁層 831 を形成する SIMOX と呼ばれる方法を用いて形成すればよい(図 10(C) 参照)。

40

#### 【0111】

例えば、基板に単結晶半導体を用いた場合、図 10(C) に示すように単結晶半導体基板 830 を用いて設けられた電界効果トランジスタ 832 に記憶素子 801 が接続されている。また、電界効果トランジスタ 832 の配線を覆うように絶縁層 833 を設け、当該絶縁層 833 上に記憶素子 801 を設けている。

#### 【0112】

このような単結晶半導体で形成されるトランジスタは、応答速度や移動度などの特性が

50

良好なために、高速な動作が可能なトランジスタを提供することができる。また、トランジスタは、その特性のバラツキが少ないために、高い信頼性を実現した半導体装置を提供することができる。

#### 【0113】

なお、記憶素子801は、絶縁層833上に形成される第1の導電層110と、半導体層111と、有機化合物層112と、第2の導電層113とを有し、半導体層111及び有機化合物層112は第1の導電層110と第2の導電層113に挟持された構成である。なお、半導体層111は、第1の導電層110上に接して形成される。

#### 【0114】

このように、絶縁層833を設けて記憶素子801を形成することによって第1の導電層110を自由に配置することができる。つまり、図10(A)、(B)の構成では、トランジスタに接続された配線を避けた領域に記憶素子を設ける必要があったが、絶縁層833を設けることによって、例えば、図10(C)のようにトランジスタ832の上方に記憶素子801を形成することが可能となる。その結果、記憶回路をより高集積化することが可能となる。

#### 【0115】

なお、図10(B)、(C)に示す構成において、半導体層111及び有機化合物層112は基板全面に設けた例を示しているが、各メモリセルのみにこれらの有機化合物層を設けてもよい。この場合、液滴吐出法等を用いて有機化合物を吐出し焼成して選択的に有機化合物層を設けることにより材料の利用効率を向上させることが可能となる。

#### 【0116】

また、基板上に剥離層を設け、剥離層上にトランジスタを有する層1030及び記憶素子801を形成した後、トランジスタを有する層1030及び記憶素子801を剥離層を用いて基板から剥離し、図12に示すように接着層1032を用いてトランジスタを有する層1030及び記憶素子801を前記基板と異なる基板1031と貼り合わせても良い。剥離方法としては、(1)耐熱性の高い基板とトランジスタを有する層の間に剥離層として金属酸化物層を設け、当該金属酸化物層を結晶化により脆弱化して、当該トランジスタを有する層を剥離する方法、(2)耐熱性の高い基板とトランジスタを有する層の間に剥離層として水素を含む非晶質珪素膜を設け、レーザ光の照射またはエッティングにより当該非晶質珪素膜を除去することで、当該トランジスタを有する層を剥離する方法、(3)トランジスタを有する層が形成された耐熱性の高い基板を機械的に削除する、又は溶液やNF<sub>3</sub>、BrF<sub>3</sub>、ClF<sub>3</sub>等のフッ化ハロゲンガスによるエッティングで除去する方法、(4)耐熱性の高い基板とトランジスタを有する層の間に剥離層として金属層及び金属酸化物層を設け、当該金属酸化物層を結晶化により脆弱化し、金属層の一部を溶液やNF<sub>3</sub>、BrF<sub>3</sub>、ClF<sub>3</sub>等のフッ化ハロゲンガスによりエッティングで除去した後、脆弱化された金属酸化物層において物理的に剥離する方法等を用いればよい。

#### 【0117】

また、基板1031としては、実施の形態2で示した基板521で示した可撓性基板、フィルム、繊維質な材料からなる紙等を用いることで、記憶装置の小型、薄型、軽量化を図ることが可能である。

#### 【0118】

次に、記憶装置、即ち半導体装置700へのデータの書き込み動作について図9(A)を用いて説明する。実施の形態2と同様、ここでは電気的作用、代表的には電圧印加によりデータの書き込みを行うときの動作について説明する。なお、書き込みはメモリセルの電気的特性を変化させることで行うが、メモリセルの初期状態(電気的作用を加えていない状態)をデータ「0」、電気的特性を変化させた状態をデータ「1」とする。

#### 【0119】

x行かつy列目のメモリセル701にデータを書き込む場合について説明する。メモリセル701にデータ「1」を書き込む場合、まず、デコーダ712、713およびセレクタ714によってメモリセル701を選択する。具体的には、デコーダ713によって、

10

20

30

40

50

メモリセル 701 に接続されるワード線 Wy に所定の電位 V22 を印加する。また、デコーダ 712 とセレクタ 714 によって、メモリセル 701 に接続されるビット線 Bx を読み出し / 書き込み回路 715 に接続する。そして、読み出し / 書き込み回路 715 からビット線 Bx へ書き込み電位 V21 を出力する。

#### 【0120】

こうして、メモリセルを構成する薄膜トランジスタ 721 をオン状態とし、記憶素子 722 に、共通電極及びビット線を電気的に接続し、おおむね  $Vw = Vcom - V21$  の電圧を印加する。 $Vcom$  とは、記憶素子 722 における共通電極、即ち第2の導電層の電位である。電圧  $Vw$  を適切に選ぶことで、第1の電極層と第2の導電層との間に設けられた有機化合物を含む層を物理的もしくは電気的变化させ、データ「1」の書き込みを行う。

具体的には、読み出し動作電圧において、データ「1」の状態の第1の導電層と第2の導電層の間の電気抵抗が、データ「0」の状態と比して、大幅に小さくなるように変化するとよく、単に短絡（ショート）させてもよい。なお、電位は、（V21、V22、Vcom）=（5～15V、5～15V、0V）、あるいは（-12～0V、-12～0V、3～5V）の範囲から適宜選べば良い。電圧  $Vw$  は 5V 以上かつ 15V 以下、あるいは -15V 以上かつ -5V 以下とすればよい。

10

#### 【0121】

なお、非選択のワード線および非選択のビット線には、接続されるメモリセルにデータ「1」が書き込まれないよう制御する。具体的には、非選択のワード線には接続されるメモリセルのトランジスタをオフ状態とする電位を印加したり、 $Vcom$  と同程度の電位を印加するとよい。

20

#### 【0122】

一方、メモリセル 701 にデータ「0」を書き込む場合は、メモリセル 701 には電気的作用を加えなければよい。回路動作上は、例えば、「1」を書き込む場合と同様に、デコーダ 712、713 およびセレクタ 714 によってメモリセル 701 を選択するが、読み出し / 書き込み回路 715 からビット線 Bx への出力電位を  $Vcom$  と同程度とするか、メモリセルの薄膜トランジスタ 721 をオフ状態とする電位とする。その結果、記憶素子 722 には、小さい電圧（例えば -5～5V）が印加されるか、電圧が印加されないため、電気的特性が変化せず、データ「0」書き込みが実現される。

#### 【0123】

30

次に、電気的作用により、データの読み出しを行う際の動作について図 9 (B) を用いて説明する。データの読み出しは、記憶素子 722 の電気的特性が、データ「0」を有するメモリセルとデータ「1」を有するメモリセルとで異なることを利用して行う。例えば、データ「0」を有するメモリセルを構成する記憶素子の電気抵抗が読み出し電圧において  $R0$ 、データ「1」を有するメモリセルを構成する記憶素子の電気抵抗が読み出し電圧において  $R1$  とし、電気抵抗の差を利用して読み出す方法を説明する。なお、 $R1 < R0$  とする。読み出し / 書き込み回路 715 は、読み出し部分の構成として、例えば図 9 (B) に示す抵抗素子 750 と差動增幅器 751 を用いた回路を考えることができる。抵抗素子は抵抗値  $Rr$  を有し、 $R1 < Rr < R0$  であるとする。抵抗素子 750 の代わりに、図 9 (C) に示すようにトランジスタ 752 を用いても良いし、差動增幅器 751 の代わりにクロックトインバータ 753 を用いることも可能である。もちろん、回路構成は図 9 (B) 及び (C) に限定されない。

40

#### 【0124】

$x$  行  $y$  列目メモリセル 702 からデータの読み出しを行う場合、まず、デコーダ 712、713 およびセレクタ 714 によってメモリセル 702 を選択する。具体的には、デコーダ 713 によって、メモリセル 702 に接続されるワード線 Wy に所定の電位 V24 を印加し、薄膜トランジスタ 721 をオン状態にする。また、デコーダ 712 とセレクタ 714 によって、メモリセル 702 に接続されるビット線 Bx を読み出し / 書き込み回路 715 の端子 P に接続する。その結果、端子 P の電位  $Vp$  は、 $Vcom$  と  $V0$  が抵抗素子 750（抵抗値  $Rr$ ）と記憶素子 722（抵抗値  $R0$  もしくは  $R1$ ）による抵抗分割によつ

50

て決定される値となる。従って、メモリセル702がデータ「0」を有する場合の端子Pの電位V<sub>p0</sub>には、 $V_{p0} = V_{com} + (V_0 - V_{com}) \times R_0 / (R_0 + R_r)$ となる。また、メモリセル702がデータ「1」を有する場合の端子Pの電位V<sub>p1</sub>には、 $V_{p1} = V_{com} + (V_0 - V_{com}) \times R_1 / (R_1 + R_r)$ となる。その結果、図9(B)では、V<sub>ref</sub>をV<sub>p0</sub>とV<sub>p1</sub>の間となるように選択することで、図9(C)では、クロックトインバータの変化点をV<sub>p0</sub>とV<sub>p1</sub>の間となるように選択することで、出力電位V<sub>out</sub>がデータ「0」/「1」に応じて、L<sub>o</sub>/H<sub>i</sub>(もしくはH<sub>i</sub>/L<sub>o</sub>)が出力され、読み出しを行うことができる。

#### 【0125】

例えれば、差動増幅器751をV<sub>dd</sub>=3Vで動作させ、V<sub>com</sub>=0V、V<sub>0</sub>=3V、V<sub>ref</sub>=1.5Vとする。仮に、R<sub>0</sub>/R<sub>r</sub>=R<sub>r</sub>/R<sub>1</sub>=9とし、薄膜トランジスタ721のオン抵抗を無視できるとすると、メモリセルのデータが「0」の場合、V<sub>p0</sub>=2.7VとなりV<sub>out</sub>はH<sub>i</sub>が出力され、メモリセルのデータが「1」の場合、V<sub>p1</sub>=0.3VとなりV<sub>out</sub>はL<sub>o</sub>が出力される。こうして、メモリセルの読み出しを行うことができる。

#### 【0126】

上記の方法によると、記憶素子722の抵抗値の相違と抵抗分割を利用して、電圧値で読み取っている。もちろん、読み出し方法は、この方法に限定されない。例えれば、電気抵抗の差を利用する以外に、電流値の差を利用して読み出しても構わない。また、メモリセルの電気的特性が、データ「0」と「1」とで、しきい値電圧が異なるダイオード特性を有する場合には、しきい値電圧の差を利用して読み出しても構わない。

#### 【0127】

また、絶縁性を有する基板上に薄膜トランジスタ(TFT)を設けてその上に記憶素子又は記憶素子アレイを設けてもよいし、絶縁性を有する基板の代わりにSi等の半導体基板やSOI基板を用いて基板上に電界効果トランジスタ(FET)を形成しその上に記憶素子又は記憶素子アレイを設けてもよい。

#### 【0128】

本実施形態で示した半導体装置は、本発明の記憶素子を有することにより導電層等の破壊や記憶素子の絶縁状態化などの異常な挙動を抑制することができる。よって、記憶素子毎の挙動のばらつきを低減することが可能となる。したがって、読み取り電圧のとり得る幅も広がり、半導体装置における設計の自由度が向上する。

#### 【0129】

また、半導体装置へのデータの書き込みは一度だけではなく、追加(追記)が可能である。一方、書き込みを一度行った記憶素子に対しデータを消去することは不可能なため、書き換えによる偽造を防止することができる。さらに、本発明の記憶素子は一対の導電層間に半導体層及び有機化合物層が挟まれた単純な構造であるため、性能及び信頼性に優れた半導体装置を低コストで作製することが可能となる。

#### 【0130】

なお、本実施形態は、他の実施の形態及び実施例とも自由に組み合わせができる。

#### 【0131】

##### (実施の形態4)

本実施の形態では、上記実施の形態で示す記憶装置を有する半導体装置の一構成例について図面を用いて説明する。

#### 【0132】

本実施の形態で示す半導体装置は、非接触でデータの読み出しと書き込みが可能であることを特徴としており、データの伝送形式は、一対のコイルを対向に配置して相互誘導によって交信を行う電磁結合方式、誘導電磁界によって交信する電磁誘導方式、電波を利用して交信する電波方式の3つに大別されるが、いずれの方式を用いてもよい。また、データの伝送に用いるアンテナは2通りの設け方があり、1つはトランジスタおよび記憶素子

10

20

30

40

50

が設けられた基板上にアンテナを設ける場合、もう1つはトランジスタおよび記憶素子が設けられた基板に端子部を設け、当該端子部に別の基板に設けられたアンテナを接続して設ける場合がある。

#### 【0133】

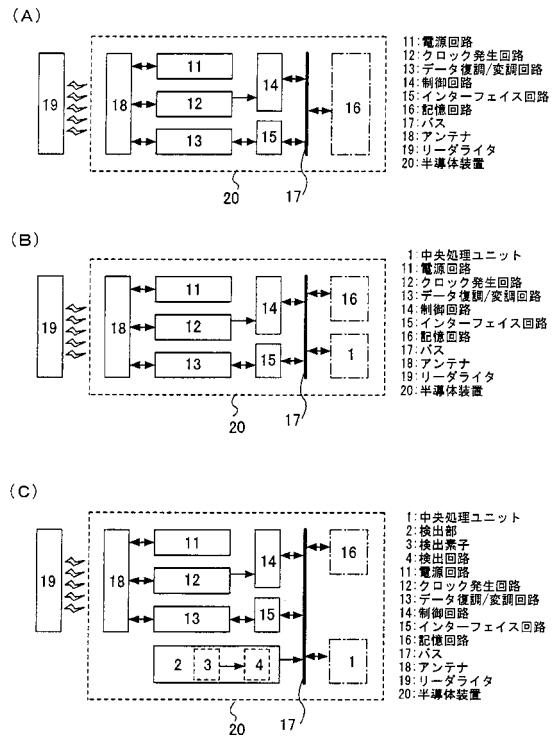

本実施形態で示す半導体装置の構成について、図13を参照して説明する。図13(A)に示すように、本発明の半導体装置20は、非接触でデータを交信する機能を有し、電源回路11、クロック発生回路12、データ復調/変調回路13、他の回路を制御する制御回路14、インターフェイス回路15、記憶回路16、バス17、アンテナ18を有する。

#### 【0134】

また、図13(B)に示すように、本発明の半導体装置20は、非接触でデータを交信する機能を有し、電源回路11、クロック発生回路12、データ復調/変調回路13、他の回路を制御する制御回路14、インターフェイス回路15、記憶回路16、バス17、アンテナ18の他、中央処理ユニット1を有しても良い。

10

#### 【0135】

また、図13(C)に示すように、本発明の半導体装置20は、非接触でデータを交信する機能を有し、電源回路11、クロック発生回路12、データ復調/変調回路13、他の回路を制御する制御回路14、インターフェイス回路15、記憶回路16、バス17、アンテナ18、中央処理ユニット1の他、検出素子3、検出回路4からなる検出部2を有しても良い。

20

#### 【0136】

電源回路11は、アンテナ18から入力された交流信号を基に、半導体装置20の内部の各回路に供給する各種電源を生成する回路である。クロック発生回路12は、アンテナ18から入力された交流信号を基に、半導体装置20の内部の各回路に供給する各種クロック信号を生成する回路である。データ復調/変調回路13は、リーダライタ19と交信するデータを復調/変調する機能を有する。制御回路14は、記憶回路16を制御する機能を有する。アンテナ18は、電磁界或いは電波の送受信を行う機能を有する。リーダライタ19は、半導体装置との交信、制御及びそのデータに関する処理を制御する。なお、半導体装置は上記構成に制約されず、例えば、電源電圧のリミッタ回路や暗号処理専用ハードウェアといった他の要素を追加した構成であってもよい。

30

#### 【0137】

記憶回路16は、実施の形態1に示す記憶素子から選択される1つ又は複数の記憶素子を有する。本発明の記憶素子を有することにより導電層等の破壊や記憶素子の絶縁状態化などの異常な挙動を抑制することができる。よって、記憶素子毎の挙動のばらつきを低減することが可能となる。したがって、読み取り電圧のとり得る幅も広がり、半導体装置における設計の自由度が向上する。

#### 【0138】

また、記憶素子へのデータの書き込みの機会は一度だけではなく、データの追加(追記)が可能である。一方、書き込みを一度行った記憶素子に対しデータを消去することは不可能なため、書き換えによる偽造を防止することができる。

40

#### 【0139】

また、検出部2は、温度、圧力、流量、光、磁気、音波、加速度、湿度、気体成分、液体成分、その他の特性を物理的又は化学的手段により検出することができる。なお、検出部2は、物理量または化学量を検出する検出素子3と当該検出素子3で検出された物理量または化学量を電気信号等の適切な信号に変換する検出回路4とを有している。検出素子3としては、抵抗素子、容量結合素子、誘導結合素子、光起電力素子、光電変換素子、熱起電力素子、トランジスタ、サーミスタ、ダイオード等で形成することができる。なお、検出部2は複数設けてもよく、この場合、複数の物理量または化学量を同時に検出することが可能である。

#### 【0140】

50

また、ここでいう物理量とは、温度、圧力、流量、光、磁気、音波、加速度、湿度等を指し、化学量とは、ガス等の気体成分やイオン等の液体成分等の化学物質等を指す。化学量としては、他にも、血液、汗、尿等に含まれる特定の生体物質（例えば、血液中に含まれる血糖値等）等の有機化合物も含まれる。特に、化学量を検出しようとする場合には、必然的にある特定の物質を選択的に検出することになるため、あらかじめ検出素子3に検出したい物質と選択的に反応する物質を設けておく。例えば、生体物質の検出を行う場合には、検出素子3に検出させたい生体物質と選択的に反応する酵素、抗体分子または微生物細胞等を高分子等に固定化して設けておくことが好ましい。

#### 【0141】

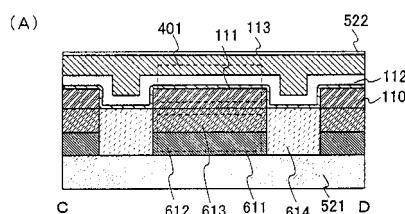

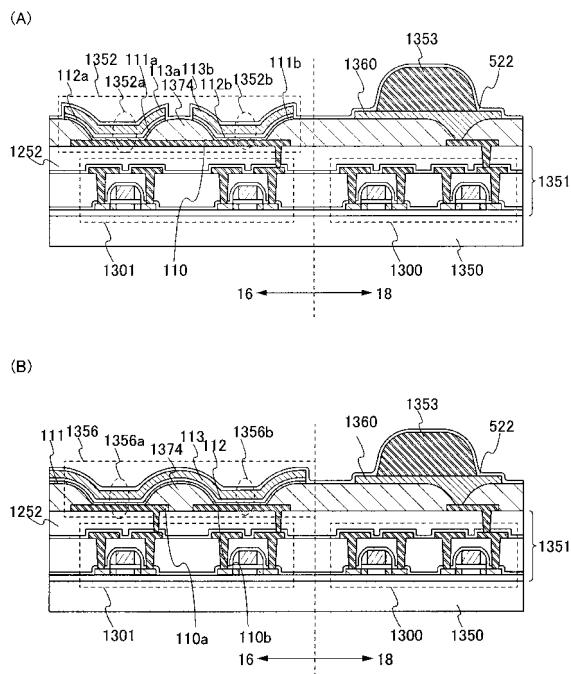

次に、複数の素子および記憶素子が設けられた基板上にアンテナを設けた半導体装置における、記憶回路16とアンテナ18が形成された断面図の一部を図14に示す。10

#### 【0142】

図14(A)はパッシブマトリクス型で構成される記憶回路を有する半導体装置を示している。半導体装置は、基板1350上にトランジスタ1300、1301を有する層1351と、トランジスタを有する層1351の上方に形成される記憶素子部1352及びアンテナとして機能する導電層1353とを有する。

#### 【0143】

なお、ここではトランジスタを有する層1351の上方に記憶素子部1352及びアンテナとして機能する導電層1353を有する場合を示しているが、この構成に限られず記憶素子部1352またはアンテナとして機能する導電層1353を、トランジスタを有する層1351の下方や同一の層に有してもよい。20

#### 【0144】

記憶素子部1352は複数の記憶素子1352a、1352bを有する。また、記憶素子1352aは、絶縁層1252上に形成される第1の導電層110と、隔壁(絶縁層)1374及び第1の導電層110の一部を覆う半導体層111aと、さらに半導体層111aを覆う有機化合物層112aと第2の導電層113aとを有する。また、記憶素子1352bは、第1の導電層110と、隔壁(絶縁層)1374及び第1の導電層110の一部を覆う半導体層111bと、さらに半導体層111bを覆う有機化合物層112bと第2の導電層113bとを有する。

#### 【0145】

また、第2の導電層113a、113b及びアンテナとして機能する導電層1353を覆って保護膜として機能する絶縁層522が形成されている。記憶素子部1352における第1の導電層110は、トランジスタ1301の配線に接続されており、記憶素子部1352は上記実施の形態で示した記憶素子と同様の材料または作製方法を用いて形成することができる。

#### 【0146】

なお、アンテナとして機能する導電層1353は第2の導電層113a、113bと同一の層で形成された導電層1360上に設けられている。なお、第2の導電層113a、113bと同一の層でアンテナとして機能する導電層を形成してもよい。アンテナとして機能する導電層1353はトランジスタ1300の配線に接続する。40

#### 【0147】

アンテナとして機能する導電層1353は、CVD法、スパッタ法、スクリーン印刷やグラビア印刷等の印刷法、液滴吐出法、ディスペンサ法、メッキ法等を用いて、導電性材料により形成する。導電性材料は、アルミニウム(A1)、チタン(Ti)、銀(Ag)、銅(Cu)、金(Au)、白金(Pt)ニッケル(Ni)、パラジウム(Pd)、タンタル(Ta)、モリブデン(Mo)から選択された元素、又はこれらの元素を主成分とする合金材料若しくは化合物材料で、単層構造又は積層構造で形成する。

#### 【0148】

例えば、スクリーン印刷法を用いてアンテナとして機能する導電層を形成する場合には、粒径が数nmから数十μmの導電体粒子を有機樹脂に溶解または分散させた導電性のペ50

ーストを選択的に印刷することによって設けることができる。導電体粒子としては、銀( A g )、金( A u )、銅( C u )、ニッケル( N i )、白金( P t )、パラジウム( P d )、タンタル( T a )、モリブデン( M o )およびチタン( T i )等のいずれか一つ以上の金属粒子やハロゲン化銀の微粒子、または分散性ナノ粒子を用いることができる。また、導電性ペーストに含まれる有機樹脂は、金属粒子のバインダー、溶媒、分散剤および被覆材として機能する有機樹脂から選ばれた一つまたは複数を用いることができる。代表的には、エポキシ樹脂、珪素樹脂等の有機樹脂が挙げられる。また、導電層の形成にあたり、導電性のペーストを押し出した後に焼成することが好ましい。例えば、導電性のペーストの材料として、銀を主成分とする微粒子( 例えは粒径 1 nm 以上 1 0 0 nm 以下 ) を用いる場合、150 ~ 300 の温度範囲で焼成することにより硬化させて導電層を得ることができる。また、はんだや鉛フリーのはんだを主成分とする微粒子を用いてもよく、この場合は粒径 20 μm 以下の微粒子を用いることが好ましい。はんだや鉛フリーはんだは、低コストであるといった利点を有している。また、上述した材料以外にも、セラミックやフェライト等をアンテナに適用してもよい。10

#### 【 0 1 4 9 】

トランジスタを有する層 1 3 5 1 に含まれるトランジスタ 1 3 0 0 、 1 3 0 1 は、実施の形態 3 で示したトランジスタ等を適宜選択し、用いることができる。

#### 【 0 1 5 0 】

また、基板上に剥離層を設け、前記剥離層上にトランジスタを有する層 1 3 5 1 、記憶素子部 1 3 5 2 、及びアンテナとして機能する導電層 1 3 5 3 を形成し、実施の形態 3 に示す剥離方法を適宜用いてトランジスタを有する層 1 3 5 1 、記憶素子部 1 3 5 2 及びアンテナとして機能する導電層 1 3 5 3 を剥離し、基板上に接着層を用いて貼り付けてもよい。基板としては、実施の形態 2 の基板 5 2 1 で示した可撓性基板、フィルム、繊維質な材料からなる紙等を用いることで、記憶装置の小型、薄型、軽量化を図ることが可能である。20

#### 【 0 1 5 1 】

図 1 4 ( B ) にアクティブマトリクス型の記憶回路を有する半導体装置の一例を示す。なお、図 1 4 ( B ) については、図 1 4 ( A ) と異なる部分に関して説明する。

#### 【 0 1 5 2 】

図 1 4 ( B ) に示す半導体装置は、基板 1 3 5 0 上にトランジスタ 1 3 0 0 、 1 3 0 1 を有する層 1 3 5 1 と、トランジスタを有する層 1 3 5 1 の上方に記憶素子部 1 3 5 6 及びアンテナとして機能する導電層 1 3 5 3 とを有する。なお、ここではトランジスタを有する層 1 3 5 1 の上方に記憶素子部 1 3 5 6 及びアンテナとして機能する導電層 1 3 5 3 を有する場合を示しているが、この構成に限られずトランジスタ 1 3 0 1 を有する層 1 3 5 1 の上方や下方に有してもよいし、記憶素子部 1 3 5 6 やアンテナ機能する導電層 1 3 5 3 を、トランジスタを有する層 1 3 5 1 の下方や同一の層に有しても可能である。30

#### 【 0 1 5 3 】

記憶素子部 1 3 5 6 は、記憶素子 1 3 5 6 a 、 1 3 5 6 b で構成される。記憶素子 1 3 5 6 a は、絶縁層 1 2 5 2 上に形成される第 1 の導電層 1 1 0 a と、第 1 の導電層 1 1 0 a 及び隔壁( 絶縁層 ) 1 3 7 4 を覆う半導体層 1 1 1 と、半導体層 1 1 1 を覆う有機化合物層 1 1 2 と第 2 の導電層 1 1 3 とを有する。記憶素子 1 3 5 6 b は、絶縁層 1 2 5 2 上に形成される第 1 の導電層 1 1 0 b と、半導体層 1 1 1 と、有機化合物層 1 1 2 と、第 2 の導電層 1 1 3 とを有する。また、記憶素子を構成する第 1 の導電層の各々にはトランジスタの配線が接続されている。すなわち、記憶素子はそれぞれ一つのトランジスタに接続されている。40

#### 【 0 1 5 4 】

また、基板上に剥離層を設け、前記剥離層上にトランジスタを有する層 1 3 5 1 、記憶素子部 1 3 5 6 及びアンテナとして機能する導電層 1 3 5 3 を形成し、実施の形態 3 に示す剥離方法を適宜用いてトランジスタを有する層 1 3 5 1 、記憶素子部 1 3 5 6 及びアンテナとして機能する導電層 1 3 5 3 を剥離し、基板上に接着層を用いて貼り付けてもよい50

。

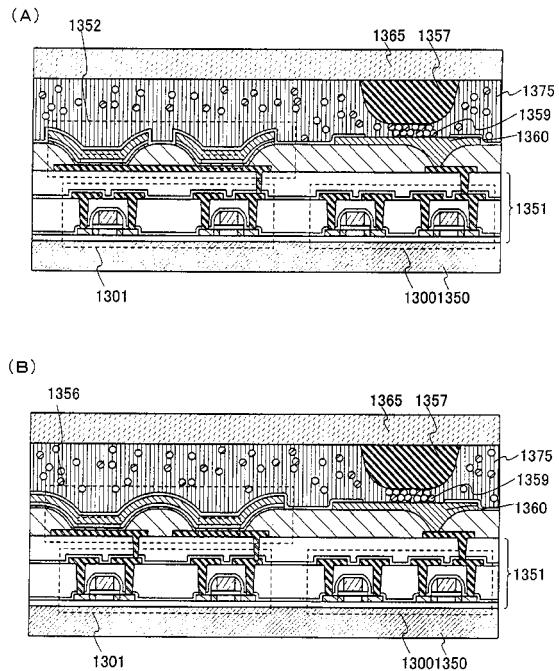

**【 0 1 5 5 】**

次に、トランジスタを有する層、アンテナに接続される端子部及び記憶素子を有する第1の基板と、当該端子部に接続されるアンテナが形成された第2の基板とを有する半導体装置の一構成例に関して図15を用いて説明する。なお、図15に関し図14と異なる部分に関して説明を行う。

**【 0 1 5 6 】**

図15(A)はパッシブマトリクス型の記憶装置を有する半導体装置を示している。半導体装置は、基板1350上に形成されたトランジスタ1300、1301を有する層1351と、トランジスタを有する層1351の上方に形成される記憶素子部1352と、アンテナに接続する端子部と、アンテナとして機能する導電層1357が形成された基板1365とを有し、導電層1357と接続端子となる導電層1360とは樹脂1375中に含まれる導電性粒子1359により接続されている。なお、トランジスタを有する層1351と記憶素子部1352等を有する基板1350と、アンテナとして機能する導電層1357が設けられた基板1365とは、接着性を有する樹脂1375により貼り合わされている。

10

**【 0 1 5 7 】**

また、銀ペースト、銅ペースト、カーボンペースト等の導電性接着剤や半田接合を行う方法を用いてアンテナとして機能する導電層1357と接続端子となる導電層1360とを接続してもよい。ここではトランジスタを有する層1351の上方に記憶素子部1352を設けた場合を示しているが、この構成に限られず記憶素子部1352を、トランジスタを有する層1351の下方や同一の層に有してもよい。

20

**【 0 1 5 8 】**

図15(B)はアクティブマトリクス型の記憶装置が設けられた半導体装置を示している。半導体装置は、基板1350上に形成されたトランジスタ1300、1301を含むトランジスタを有する層1351と、トランジスタを有する層1351の上方に形成される記憶素子部1356と、トランジスタに接続する端子部と、アンテナとして機能する導電層1357が形成された基板1365とを有し、導電層1357と接続端子となる導電層1360とは樹脂1375中に含まれる導電性粒子1359により接続されている。なお、トランジスタを有する層1351と記憶素子部1356等を有する基板と、アンテナとして機能する導電層1357が設けられた基板1365とは、接着性を有する樹脂1375により貼り合わされている。

30

**【 0 1 5 9 】**

また、銀ペースト、銅ペースト、カーボンペースト等の導電性接着剤や半田接合を行う方法を用いてトランジスタを有する層1351と記憶素子部1356等を有する基板1350と、アンテナとして機能する導電層1357が設けられた基板1365とを貼り合わせてもよい。ここではトランジスタを有する層1351の上方に記憶素子部1352を設けた場合を示しているが、この構成に限られず記憶素子部1356を、トランジスタを有する層1351の下方や同一の層に有してもよい。

40

**【 0 1 6 0 】**

また、基板上に剥離層を形成し、前記剥離層上にトランジスタを有する層1351、記憶素子部1352もしくは記憶素子部1356を形成し、実施の形態3に示す剥離方法を適宜用いてトランジスタを有する層1351及び記憶素子部1352、1356を剥離し、基板上に接着層を用いて貼り付けてもよい。

**【 0 1 6 1 】**

さらには、記憶素子部1352、1356を、アンテナとして機能する導電層1357が設けられた基板1365に設けてもよい。すなわち、トランジスタを有する層が形成される第1の基板と、記憶素子部及びアンテナとして機能する導電層が形成される第2の基板とを、導電性粒子を含む樹脂により貼り合わせてもよい。また、図14(A)及び(B)に示す半導体装置と同様に、トランジスタに接続するセンサを設けてもよい。

50

## 【0162】

本実施形態で示した半導体装置は、本発明の記憶素子を有することにより導電層等の破壊や記憶素子の絶縁状態化などの異常な挙動を抑制することができる。よって、記憶素子毎の挙動のばらつきを低減することが可能となる。したがって、読み取り電圧のとり得る幅も広がり、半導体装置における設計の自由度が向上する。

## 【0163】

また、半導体装置へのデータの書き込みは一度だけではなく、追加（追記）が可能である。一方、書き込みを一度行った記憶素子に対しデータを消去することは不可能なため、書き換えによる偽造を防止することができる。また、非接触でデータの読み出しと書き込みが可能である。さらに、本発明の記憶素子は一対の導電層間に半導体層及び有機化合物層が挟まれた単純な構造であるため、性能及び信頼性に優れた半導体装置を低成本で作製することが可能となる。

10

## 【0164】

なお、本実施形態は、他の実施の形態及び実施例とも自由に組み合わせることができる。

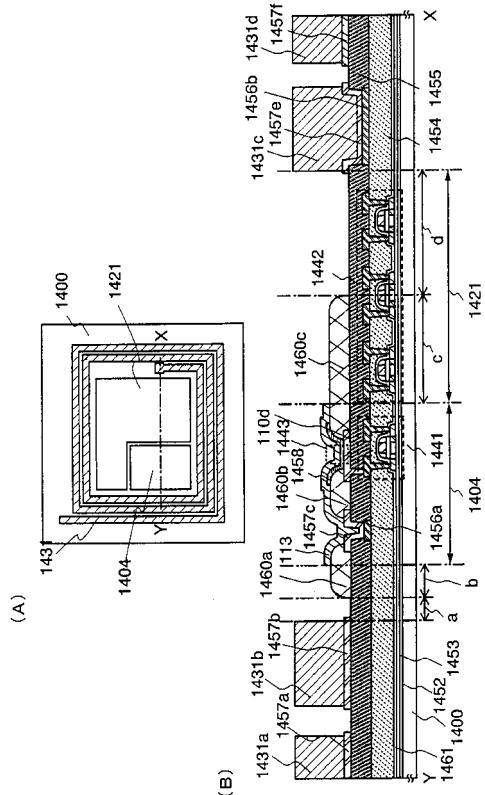

## 【0165】

## (実施の形態5)

本実施の形態では、本発明の記憶素子を有する半導体装置の一例について図面を用いて説明する。本実施の形態の半導体装置の上面図を図16(A)に、図16(A)における線X-Yの断面図を図16(B)に示す。

20

## 【0166】

図16(A)に示すように、基板1400上に記憶素子を有する記憶素子部1404、回路部1421、アンテナ1431が形成されている。図16(A)及び(B)は、作成工程途中であり、作製条件に耐えうる基板1400上に記憶素子部、回路部、及びアンテナを形成した状態である。材料及び作製工程は上記実施の形態と同様に適宜選択し、作製すればよい。

## 【0167】

基板1400上に剥離層1452、絶縁層1453を介して記憶素子部1404にはトランジスタ1441、回路部1421にはトランジスタ1442が設けられている。トランジスタ1441及びトランジスタ1442上には絶縁層1461、絶縁層1454、絶縁層1455が形成されており、絶縁層1455上には記憶素子1443が形成されている。記憶素子1443は、絶縁層1455上に設けられた第1の導電層110dと、半導体層と有機化合物層とを有する層1458と、第2の導電層113とを有し、半導体層と有機化合物層とを有する層1458は第1の導電層110dと第2の導電層113に挟持されており、前記半導体層は、第1の導電層110d上に接して形成される。なお、図16では省略されているが、隔壁として機能する絶縁層1460bにより多数設けられた記憶素子1443は個々に隔てられている。

30

## 【0168】

第1の導電層110dはトランジスタ1441の配線層と接続されている。一方、第2の導電層113は、配線層1456aに積層された導電層1457cと接続されている。また、絶縁層1455上には導電層と図16(A)で示すアンテナ1431が積層して設けられている。図16(B)において、前記導電層は、導電層1457a、導電層1457b、導電層1457e、導電層1457fであり、導電層1457aとアンテナ1431a、導電層1457bとアンテナ1431b、及び導電層1457fとアンテナ1431dとがそれぞれ積層された構成となっている。なお、導電層1457eとアンテナ1431cについては、絶縁層1455に形成された配線層1456bに達する開口部において形成されており、導電層1457eと配線層1456bとが接続されている。このようにして、アンテナと記憶素子部1404及び回路部1421とを電気的に接続されている。また、アンテナ1431a、アンテナ1431b、アンテナ1431c、及び1431d下にそれぞれ形成されている導電層1457a、導電層1457b、導電層1457e

40

50

、導電層 1457f は、絶縁層 1455 とアンテナとの密着性を向上させる効果も有する。本実施の形態では、絶縁層 1455 にポリイミド膜、導電層 1457a、導電層 1457b、導電層 1457e、及び導電層 1457f にチタン膜、アンテナ 1431a、アンテナ 1431b、アンテナ 1431c、及び 1431d にアルミニウム膜をそれぞれ用いている。

#### 【0169】

なお、第 1 の導電層 110d とトランジスタ 1441、導電層 1457c と配線層 1456a 及び導電層 1457e と配線層 1456b とがそれ接続するために絶縁層 1455 に開口（コンタクトホールとも言う）を形成している。開口を大きくし、導電層同士の接触面積を増加した方がより低抵抗となるため、本実施の形態では、第 1 の導電層 110d とトランジスタ 1441 とが接続する開口が一番小さく、その次が導電層 1457c と配線層 1456a とが接続する開口、導電層 1457e と配線層 1456b とが接続する開口が一番大きいというように順に開口を大きく設定している。本実施の形態では、第 1 の導電層 110d とトランジスタ 1441 とが接続する開口を  $5 \mu\text{m} \times 5 \mu\text{m}$ 、導電層 1457c と配線層 1456a とが接続する開口を  $50 \mu\text{m} \times 50 \mu\text{m}$ 、導電層 1457e と配線層 1456b とが接続する開口を  $500 \mu\text{m} \times 500 \mu\text{m}$  としている。10

#### 【0170】

本実施の形態では、絶縁層 1460a からアンテナ 1431b までの距離 a を  $500 \mu\text{m}$  以上、第 2 の導電層 1113 の端部から絶縁層 1460a の端部までの距離 b を  $250 \mu\text{m}$  以上、第 2 の導電層 1113 の端部から絶縁層 1460c の端部までの距離 c を  $500 \mu\text{m}$  以上、絶縁層 1460c の端部からアンテナ 1431c までの距離 d を  $250 \mu\text{m}$  以上としている。なお、回路部 1421 は部分的に絶縁層 1460c が形成されており、トランジスタ 1442 も絶縁層 1460c に覆われていない領域と覆われている領域がある。20

#### 【0171】

以上のような半導体装置を用いることで、外部入力部から電源電圧や信号を記憶素子部 1404 に直接入力することで、記憶素子部 1404 にデータ（情報に相当する）を書き込む、もしくは記憶素子部 1404 からデータを読み出すことが可能となる。

#### 【0172】

また、アンテナは、記憶素子部に対して、重なって設けてもよいし、重ならずに周囲に設ける構造でもよい。また重なる場合も全面が重なってもよいし、一部が重なっている構造でもよい。例えば、アンテナ部と記憶素子部が重なる構成であると、アンテナが交信する際に信号に載っているノイズや電磁誘導により発生する起電力の変動等の影響による、半導体装置の動作不良を減らすことが可能である。30

#### 【0173】

また、上述した非接触データの入出力が可能である半導体装置における信号の伝送方式は、電磁結合方式、電磁誘導方式またはマイクロ波方式等を用いることができる。伝送方式は、用途を考慮して適宜選択すればよく、伝送方式に伴って最適なアンテナを設ければよい。

#### 【0174】

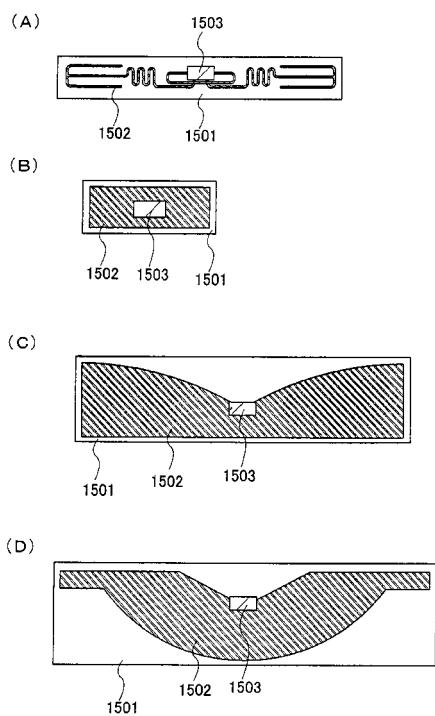

図 17(A) 乃至 (D) に、基板 1501 上に形成されたアンテナとして機能する導電層 1502 及び記憶素子 1503 を有するチップ状の半導体装置の例を示す。なお、記憶素子の他、半導体装置には集積回路等を搭載していても良い。40

#### 【0175】

半導体装置における信号の伝送方式として、マイクロ波方式（例えば、UHF 帯（ $860 \sim 960 \text{MHz}$  帯）、 $2.45 \text{GHz}$  帯等）を適用する場合には、信号の伝送に用いる電磁波の波長を考慮してアンテナとして機能する導電層の長さ等の形状を適宜設定すればよく、例えば、アンテナとして機能する導電層を線状（例えば、ダイポールアンテナ（図 17(A) 参照））、平坦な形状（例えば、パッチアンテナ（図 17(B) 参照））またはリボン型の形状（図 17(C) 及び (D) 参照）等に形成することができる。また、アンテナとして機能する導電層の形状は線状に限られず、電磁波の波長を考慮して曲線状や50

蛇行形状またはこれらを組み合わせた形状で設けてよい。

【0176】

また、半導体装置における信号の伝送方式として、電磁結合方式または電磁誘導方式（例えば13.56MHz帯）を適用する場合には、磁界密度の変化による電磁誘導を利用するために、アンテナとして機能する導電層を輪状（例えば、ループアンテナ）、らせん状（例えば、スパイラルアンテナ）に形成することが好ましい。

【0177】

また、電磁結合方式または電磁誘導方式を適用する場合であって、アンテナを備えた半導体装置を金属に接して設ける場合には、当該半導体装置と金属との間に透磁率を備えた磁性材料を設けることが好ましい。アンテナを備えた半導体装置を金属に接して設ける場合には、磁界の変化に伴い金属に渦電流が流れ、当該渦電流により発生する反磁界によって、磁界の変化が弱められて通信距離が低下する。そのため、半導体装置と金属との間に透磁率を備えた材料を設けることにより金属の渦電流を抑制し通信距離の低下を抑制することができる。なお、磁性材料としては、高い透磁率を有し高周波損失の少ないフェライトや金属薄膜を用いることができる。

10

【0178】

また、アンテナを設ける場合には、1枚の基板上にトランジスタ等の半導体素子とアンテナとして機能する導電層を直接作り込んで設けてよいし、半導体素子とアンテナとして機能する導電層を別々の基板上に設けた後に、電気的に接続するように貼り合わせることによって設けてよい。

20

【0179】

以上のように本実施形態で示した半導体装置は、本発明の記憶素子を有することにより導電層等の破壊や記憶素子の絶縁状態などの異常な挙動を抑制することができる。よって、記憶素子毎の挙動のばらつきを低減することが可能となる。したがって、読み取り電圧のとり得る幅も広がり、半導体装置における設計の自由度が向上する。

【0180】

また、半導体装置へのデータの書き込みは一度だけではなく、追加（追記）が可能である。一方、書き込みを一度行った記憶素子に対しデータを消去することは不可能なため、書き換えによる偽造を防止することができる。また、非接触でデータの読み出しと書き込みが可能である。さらに、本発明の記憶素子は一対の導電層間に半導体層及び有機化合物層が挟まれた単純な構造であるため、性能及び信頼性に優れた半導体装置を低成本で作製することができる。

30

【0181】

なお、本実施形態は、他の実施の形態及び実施例とも自由に組み合わせることができる。

【実施例1】

【0182】

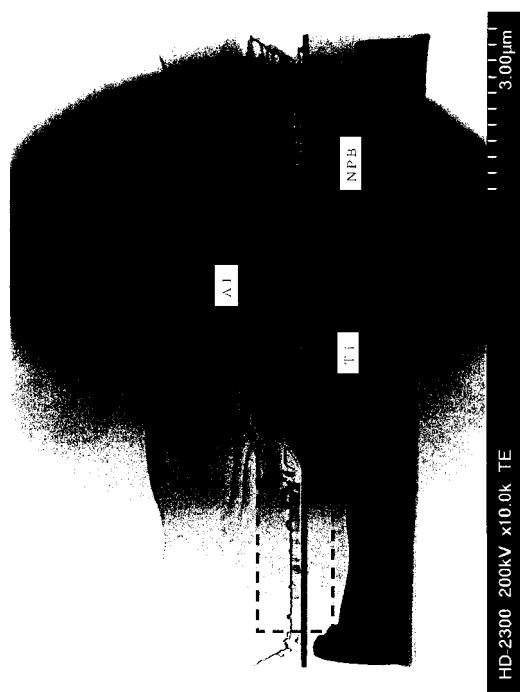

記憶素子毎の挙動のばらつきの原因を追及すべく、発明者らは以下のことを行った。チタン100nm、NPB10nm、アルミニウム200nmの積層体より構成される記憶素子に書き込み電圧を印加した後のTEM写真を図18に示す。

40

【0183】

図18より、アルミニウムが断線していることがわかる。さらに、チタンの変形が観察された。融点が高く、かつ硬い金属と一般的に認識されているチタンにまで影響を及ぼす場合があることが窺える。その他、記憶素子以外の部分にも空洞ができたりと影響を及ぼす場合もある。

【0184】

このため、記憶素子毎の挙動のばらつきは、電極等の破壊による電極の短絡もしくは電極等の断線によって素子が絶縁状態となつたためだと考えられる。

【0185】

また、記憶素子毎の挙動のばらつきについて書き込み電圧の違いより検討した。なお、

50

用いた記憶素子のサイズは  $2 \mu m$  角、 $3 \mu m$  角、 $5 \mu m$  角、 $10 \mu m$  角であり、チタン  $100 nm$ 、N P B  $10 nm$ 、アルミニウム  $200 nm$  の積層体より構成される上記と同様の記憶素子とした。

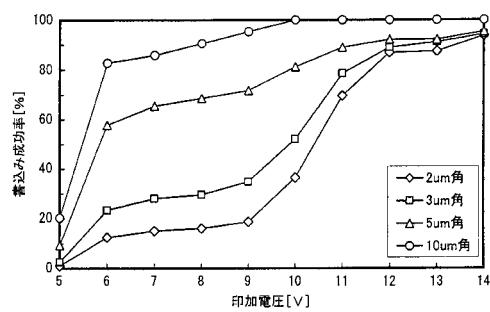

#### 【0186】

$2 \mu m$  角、 $3 \mu m$  角、 $5 \mu m$  角、 $10 \mu m$  角の記憶素子それぞれにおける印加電圧に対する書き込み成功率を図19に示す。なお、素子サイズが  $2 \mu m$  角及び  $3 \mu m$  角の記憶素子のサンプル数  $n$  はそれぞれ  $192$  であり、 $5 \mu m$  角及び  $10 \mu m$  角の記憶素子のサンプル数  $n$  はそれぞれ  $64$  とした。また、各電圧の印加時間は  $10 m$  秒とした。

#### 【0187】

図19より、素子サイズが減少するにつれて各印加電圧に対する書き込み成功率が低減し、さらに記憶素子の書き込み電圧に広がりを有することがわかった。よって、素子サイズの減少に伴い書き込み電圧のばらつきが顕著になることから、記憶素子における電極等の破壊及び絶縁状態化は導電層表面の微少な凹凸による局所的な電界の集中によって生じる過電流によるものだと考えられる。10

#### 【0188】

導電層表面の局所的な電界の集中を抑制することが可能な構成について測定結果と共に以下に示す。

#### 【0189】

本実施例では、第1の導電層に接して半導体層を有する記憶素子を作製し、本発明の一構成例である記憶素子の電流 - 電圧特性について説明する。なお、記憶素子は、基板上に第1の導電層と、半導体層と、有機化合物層と、第2の導電層とを順に積層した素子であり、その作製方法は図2(A)を用いて説明する。また、電流 - 電圧特性は、記憶素子は  $500 k$  の抵抗と直列に接続し、連続的に印加電圧を変化させるスイープ方式により測定した。20

#### 【0190】

まず、基板上に、スパッタリング法を用いてチタンを成膜し、第1の導電層  $110$  とした。なお、膜厚は  $100 nm$  とした。

#### 【0191】

次に、第1の導電層  $110$  が形成された基板を、真空蒸着装置内に設けられた基板ホルダーに、第1の導電層  $110$  が形成された面を下方となるように固定した。そして、第1の導電層  $110$  上に、抵抗加熱による蒸着法を用いて膜厚  $1 nm$  の半導体層  $111$  を形成した。30

#### 【0192】

次に、半導体層  $111$  上に、S F D C z を抵抗加熱による蒸着法を用いて  $10 nm$  となるよう成膜し、有機化合物層  $112$  を形成した。

#### 【0193】

さらに、有機化合物層  $112$  上に、アルミニウムを抵抗加熱による蒸着法を用いて膜厚が  $200 nm$  となるよう第2の導電層  $113$  を形成した。

#### 【0194】

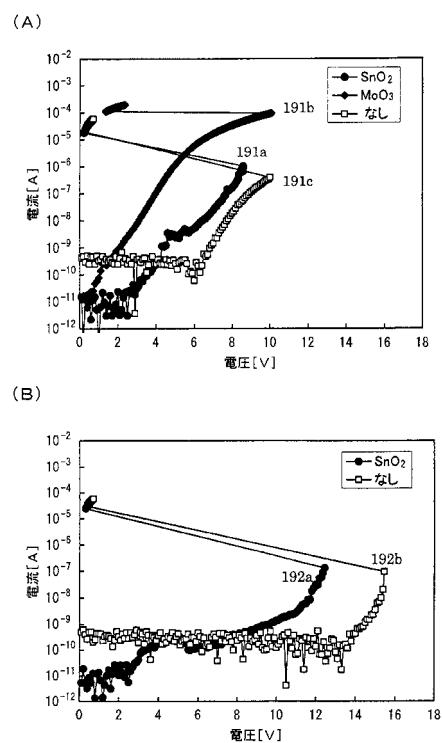

以上のようにして得られた記憶素子の電流 - 電圧特性を図20に示す。図20(A)に半導体層  $111$  に酸化スズ ( $S n O_x$ ) もしくは酸化モリブデン ( $M o O_x$ ) を用いた記憶素子における電流 - 電圧特性を示す。なお、素子サイズは  $10 \mu m$  角とし、半導体層に酸化スズを用いた記憶素子を  $191a$ 、酸化モリブデンを用いた記憶素子を  $191b$  とした。また、比較例として半導体層  $111$  を有さない記憶素子  $191c$  についての結果も併せて記載した。なお、比較例は半導体層  $111$  を有さないこと以外は、本実施例の記憶素子と同様の物質かつ手法を用いて作製した。40

#### 【0195】

図20(A)より、記憶素子  $191c$  に比べ第1の導電層に接して半導体層を有する記憶素子  $191a$  及び記憶素子  $191b$  の方が電流を流しやすいことがわかった。これは、第1の導電層に接して半導体層を設けることにより、該導電層表面の局所的な電界の集中50

が抑制されたと考えられる。

#### 【0196】

また、半導体層111に膜厚1nmの酸化スズを用いた、素子サイズ2μm角の記憶素子192aの電流-電圧特性を図20(B)に示す。なお、その他の構成については上記記憶素子と同様である。また、比較例として半導体層111を有さない、2μm角の記憶素子192bも併せて記載した。図20(B)より、第1の導電層に接して半導体層を有する記憶素子192aは、半導体層を有さない記憶素子192bより電流を流しやすいことがわかった。よって、素子サイズにかかわらず、第1の導電層と有機化合物層の間に半導体層を設けることにより該導電層表面の局所的な電界の集中を抑制できることがわかった。10

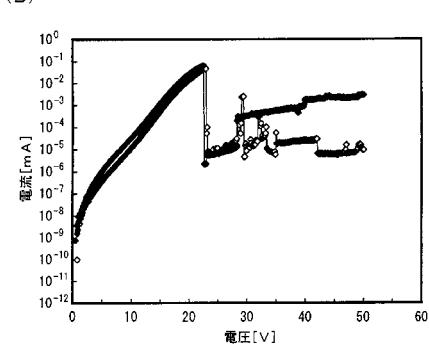

#### 【0197】

さらに、上記とは異なる半導体層111及び素子サイズの記憶素子を用いて電流-電圧特性を観察した。半導体層111に膜厚1nmの酸化ビスマス( $\text{BiO}_x$ )を用いた、素子サイズは5μm角の記憶素子200aにおける電流-電圧特性を図21に示す。なお、比較例として半導体層111を有さない記憶素子200bについての結果も併せて記載した。図21より、上記と同様、半導体層を有する記憶素子200aは、半導体層を有さない記憶素子200bより電流を流しやすいことがわかった。よって、半導体層の物質及び記憶素子のサイズにかかわらず第1の導電層に接して半導体層を設けることにより、該導電層表面の局所的な電界の集中が抑制され、有機化合物層内において電流の流れる領域が増加することがわかった。20

#### 【0198】

以上のことより、記憶素子の導電層に接して半導体層を設けることにより該導電層表面の局所的な電界の集中を抑制し、有機化合物層内において電流の流れる領域を増加させることができるため、過電流による導電層等の破壊や記憶素子の絶縁状態化を抑制することができる。20

#### 【0199】

したがって、記憶素子の異常な挙動を抑制し、さらには記憶素子毎の挙動のばらつきを低減することができる。

#### 【実施例2】

#### 【0200】

本実施例では、第1の導電層に接して半導体層を有する実施例1とは異なる記憶素子を作製し、本発明の一構成例である記憶素子の電流-電圧特性について説明する。なお、本実施例では、半導体層に膜厚0.1nmの酸化モリブデン( $\text{MoO}_x$ )を用いた以外は、実施例1と同様の物質かつ手法を用いて作製した。30

#### 【0201】

本実施例の記憶素子は、基板上に第1の導電層と、半導体層と、有機化合物層と、第2の導電層とを順に積層した素子であり、第1の導電層には膜厚100nmのチタンを、半導体層には膜厚0.1nmの酸化モリブデンを、有機化合物層には膜厚10nmのSFD CZを、第2の導電層には膜厚200nmのアルミニウムを用いた。なお、素子サイズは10μ角とした。40

#### 【0202】

また、比較例として半導体層を有さない記憶素子も作製した。なお、半導体層を有さないこと以外は、本実施例の記憶素子と同様の物質かつ手法を用いた。

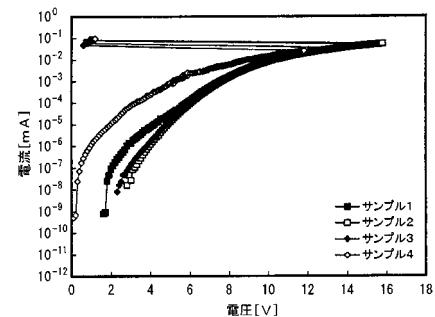

#### 【0203】

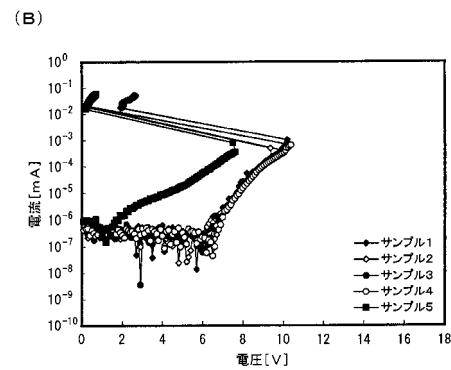

以上のように作製した半導体層を有する記憶素子の電流-電圧特性を図22(A)に、半導体層を有さない記憶素子の電流-電圧特性を図22(B)示す。なお、それぞれサンプル数nは5とし、電流-電圧特性は記憶素子を500kの抵抗と直列に接続し、ステップ方式により測定した。まず、図22(B)より、半導体層を有さない記憶素子においては、書き込み電圧に大きな差が生じ、素子毎に挙動のばらつきが観察された。また、書き込み後においても抵抗値の高い素子が存在し、異常な挙動を示した。50

**【0204】**

一方、図22(A)より半導体層を有する記憶素子では素子毎の挙動のバラツキは抑制されていることが分かる。また、図22(A)及び(B)より、半導体層を有することにより電流を流しやすいことがわかった。よって、導電層に接して半導体層を設けることにより該導電層表面の局所的な電界の集中が抑制され、有機化合物層内に流れる電流量が増加することがわかった。したがって、有機化合物層内において電流の流れる領域を増加させることにより過電流による導電層等の破壊や記憶素子の絶縁状態化を抑制し、素子毎の挙動のばらつきを低減することができた。

**【0205】**

以上のことから、たとえ0.1nmという極薄い膜厚でも半導体層を設けることにより導電層表面の局所的な電界の集中を抑制し、有機化合物層内において電流の流れる領域を増加させることができるために、過電流による導電層等の破壊や記憶素子の絶縁状態化を抑制することが可能となる。したがって、記憶素子の異常な挙動を抑制し、さらには記憶素子毎の挙動のばらつきを低減することができる。10

**【実施例3】****【0206】**

本実施例では、有機化合物層に実施例1及び2とは異なる物質を用いた記憶素子について説明する。

**【0207】**

本実施例の記憶素子は、基板上に第1の導電層と、半導体層と、有機化合物層と、第2の導電層とを順に積層した素子であり、第1の導電層に膜厚100nmのチタンを、半導体層に膜厚1.0nmの酸化スズを、有機化合物層に膜厚30nmのNPBを、第2の導電層に膜厚200nmのアルミニウムを用いた。なお、素子サイズは10μ角である。20

**【0208】**

また、比較例として半導体層を有さない記憶素子も作製した。なお、半導体層を有さないこと以外は、本実施例の記憶素子と同様の物質かつ手法を用いた。

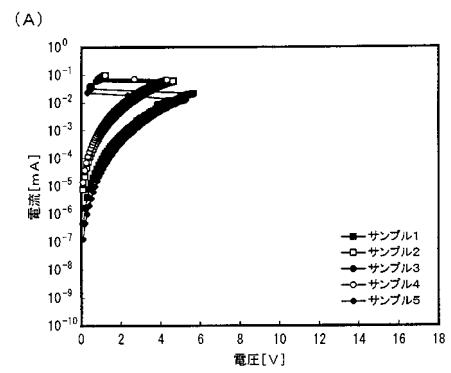

**【0209】**

以上のように作製した半導体層を有する記憶素子の電流-電圧特性を図23(A)に、半導体層を有さない記憶素子の電流-電圧特性を図23(B)示す。なお、サンプル数nは2とし、電流-電圧特性は記憶素子は500kの抵抗と直列に接続し、スイープ方式により測定した。図23(B)より、半導体層を有さない記憶素子では、電圧を印加し続けてもショートは起こらず、電圧を23Vまで印加したところで急に電流量が減少した。これは、素子が絶縁状態化したためだと考えられる。このように、有機化合物層に用いられる物質によっては実施例1や実施例2で示したような挙動がばらつく現象の他に、NPBのように記憶素子が絶縁状態になることも起こりえる。いずれにせよ、記憶素子として使用することは困難である。30

**【0210】**

一方、図23(A)より半導体層を有する記憶素子は、絶縁状態化することもなく、ある電圧に達した時点でショートさせることができた。また、素子毎の挙動のばらつきが観察されなかった。よって、第1の導電層に接して半導体層を有することにより該導電層表面上の局所的な電界の集中を抑制することができた。したがって、有機化合物層内において電流の流れる領域を増加させることができるため、過電流による導電層等の破壊や記憶素子の絶縁状態化を抑制することができる。40

**【0211】**

以上のことから、記憶素子の異常な挙動を抑制し、さらには記憶素子毎の挙動のばらつきを低減することができる。

**【0212】**

また、上記とは異なる有機化合物層を用いて電流-電圧特性を観察した。なお、有機化合物層には膜厚30nmのAlqを用い、半導体層には膜厚1.0nmの酸化モリブデンを用いた。なお、上記の記憶素子と同様の物質かつ手法を用い、素子サイズにおいても150

$0 \mu m$  角である。

【0213】

得られた記憶素子の電流 - 電圧特性を図24に示す。なお、サンプル数nは4とし、スイープ方式とした。図24より、記憶素子は絶縁状態となることなく、さらに挙動のばらつきも観察されなかった。

【0214】

以上のことから、異なる有機化合物層を用いても導電層に接して半導体層を有することにより局所的な電界の集中を抑制することができた。よって、有機化合物層内において電流の流れる領域を増加させることができるために、過電流による導電層等の破壊や記憶素子の絶縁状態化を抑制することが可能となる。したがって、記憶素子に半導体層を設けることにより、記憶素子の異常な挙動を抑制し、さらには記憶素子毎の挙動のばらつきを低減することができる。10

【実施例4】

【0215】

本実施例では、記憶素子毎の書き込み電圧について調べた。まず、本実施例で用いるために作製した記憶素子は、基板上に第1の導電層と、半導体層と、有機化合物層と、第2の導電層とを順に積層した素子であり、第1の導電層に膜厚 $100 nm$ のチタンを、半導体層に膜厚 $1.0 nm$ の酸化スズを、有機化合物層に膜厚 $10 nm$ のSFD<sub>CZ</sub>を、第2の導電層に膜厚 $200 nm$ のアルミニウムを用いた。なお、素子サイズは $10 \mu m$ 角とし、比較例とし、半導体層を有さない記憶素子についても作製した。作製方法は、半導体層を有さないこと以外は本実施例の記憶素子と同様の物質かつ手法を用いた。20

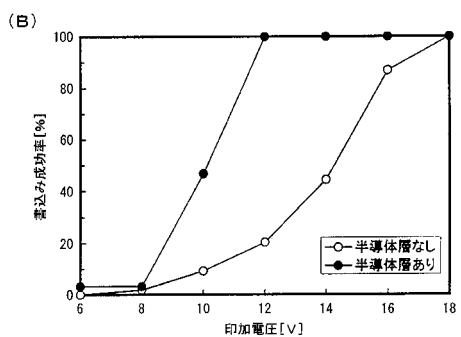

【0216】

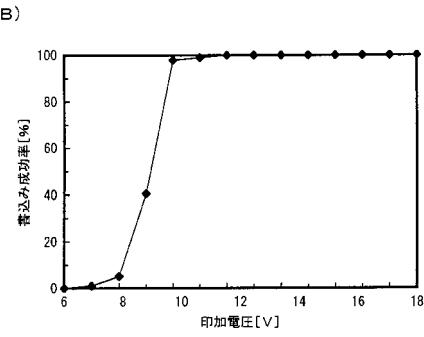

上記のように作製した各記憶素子における印加電圧に対する書き込み成功率を図25(A)に示す。また、素子サイズが $5 \mu m$ 角の記憶素子も同様のよう作製し、各記憶素子における印加電圧に対する書き込み成功率を図25(B)に示す。なお、各電圧の印加時間は $10 m$ 秒とした。 $10 \mu m$ 角の記憶素子において半導体層を有する記憶素子のサンプル数nは23、半導体層を有さない記憶素子のサンプル数nは27とし、 $5 \mu m$ 角の記憶素子においては半導体層を有する記憶素子のサンプル数nは62、半導体層を有さない記憶素子のサンプル数nは54とした。

【0217】

図25(A)及び(B)より、いずれの場合においても、印加電圧に対する半導体層を有する記憶素子における書き込み成功率は、半導体層を有さない記憶素子に比べ鋭い立ち上がりを示した。よって、半導体層を有する記憶素子では素子毎の挙動のばらつきが低減されることがわかった。30

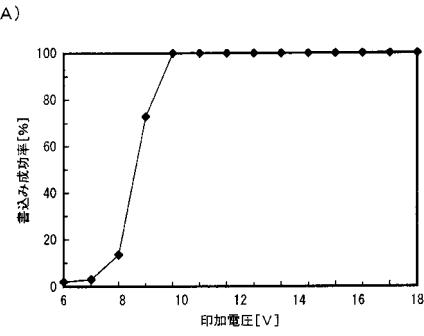

【0218】

このような記憶素子の各々に対しさらにTFTを接続した半導体装置を作製し、上記と同様各印加電圧に対する書き込み成功率を調べた。 $10 \mu m$ 角の記憶素子における測定結果を図26(A)に、 $5 \mu m$ 角の記憶素子における測定結果を図26(B)に示す。なお、記憶素子の構成はTFTが接続されている以外は上記のものと同様であり、記憶素子に電圧を印加する時間は $10 m$ 秒とした。40

【0219】

図26(A)及び(B)より、いずれの素子サイズにおいても書き込み電圧に対する書き込み成功率は鋭い立ち上がりを示し、挙動のばらつきが少ないことがわかった。したがって、読み取り電圧のとり得る幅も広くなり、記憶素子を有する半導体装置の設計における自由度を向上させることが可能となる。

【実施例5】

【0220】

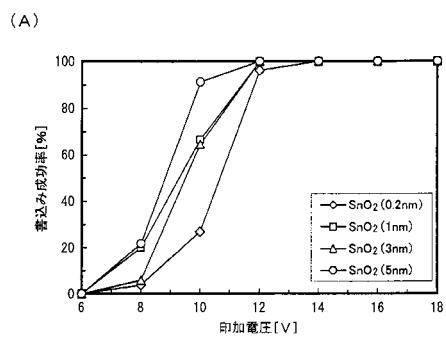

本実施例では、記憶素子毎の書き込み電圧について調べた。本実施例で用いるために作製した記憶素子は、基板上に第1の導電層と、半導体層と、有機化合物層と、第2の導電層とを順に積層した素子であり、半導体層の膜厚が異なる4種を用いた。なお、第1の導

10

20

30

40

50

電層には膜厚 100 nm のチタンを、半導体層には膜厚の異なる酸化スズを、有機化合物層には膜厚 10 nm の SFD CZ を、第 2 の導電層には膜厚 200 nm のアルミニウムを用いた。素子サイズは 10 μm 角とし、半導体層の膜厚は 0.2 nm、1 nm、3 nm または 5 nm とした。

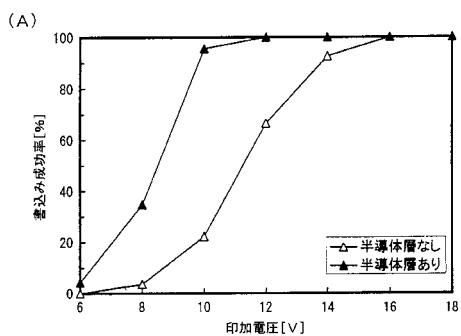

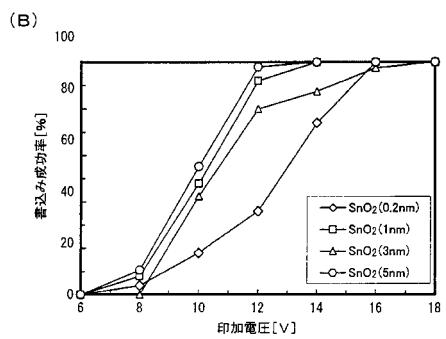

#### 【0221】

上記のように作製した各記憶素子における印加電圧に対する書き込み成功率を図 27 (A) に示す。半導体層の膜厚が 0.2 nm の記憶素子のサンプル数 n は 26、半導体層の膜厚が 1 nm の記憶素子のサンプル数 n は 15、半導体層の膜厚が 3 nm の記憶素子のサンプル数 n は 17、半導体層の膜厚が 5 nm の記憶素子のサンプル数 n は 23 とした。また、素子サイズが 5 μm 角の記憶素子も同様のように作製し、得られた各記憶素子における印加電圧に対する書き込み成功率を図 27 (B) に示す。素子サイズが 5 μm 角においては、半導体層の膜厚が 0.2 nm の記憶素子のサンプル数 n は 50、半導体層の膜厚が 1 nm の記憶素子のサンプル数 n は 25、半導体層の膜厚が 3 nm の記憶素子のサンプル数 n は 40、半導体層の膜厚が 5 nm の記憶素子のサンプル数 n は 47 とした。なお、各電圧の印加時間は 10 m 秒とした。

#### 【0222】

図 27 (A) 及び (B) より、いずれの素子サイズ及び半導体層の膜厚であっても印加電圧に対する書き込み成功率は鋭い立ち上がりを示し、挙動のばらつきが少ないとわかった。また、半導体層の膜厚を厚くしても書き込み電圧に大きな差はみられなかった。

#### 【0223】

以上のことより、本発明の記憶素子が有する半導体層は素子毎の挙動のばらつきを低減し、またその膜厚は書き込み電圧に大きな影響を与えないことがわかった。

#### 【実施例 6】

#### 【0224】

本実施例では、有機化合物層に実施例 1 乃至 5 とは異なる記憶素子について説明する。記憶素子は、基板上に第 1 の導電層と、半導体層と、絶縁物を有する有機化合物層と、第 2 の導電層とを順に積層した素子であり、その作製方法は図 2 (A) を用いて説明する。なお、素子サイズは 10 μm 角とした。

#### 【0225】

まず、基板上に、スパッタリング法を用いてチタンを成膜し、第 1 の導電層 110 とした。なお、膜厚は 100 nm とした。

#### 【0226】

次に、第 1 の導電層 110 が形成された基板を、真空蒸着装置内に設けられた基板ホルダーに、第 1 の導電層 110 が形成された面を下方となるように固定した。そして、第 1 の導電層 110 上に、半導体層 111 を抵抗加熱による蒸着法を用いて膜厚 1 nm の酸化スズを成膜した。

#### 【0227】

次に、半導体層 111 上に、NPB 及びフッ化カルシウムを抵抗加熱による共蒸着法を用いて 20 nm となるように成膜し、有機化合物層 112 を形成した。なお、有機化合物層における NPB とフッ化カルシウムとの体積比は 1 : 1 とした。

#### 【0228】

さらに、有機化合物層 112 上に、アルミニウムを抵抗加熱による蒸着法を用いて膜厚が 200 nm となるよう第 2 の導電層 113 を形成した。

#### 【0229】

以上のようにして得られた記憶素子の電流 - 電圧特性を図 28 に示す。なお、サンプル数 n は 2 とし、電流 - 電圧特性は記憶素子は 500 k Ω の抵抗と直列に接続し、スイープ方式により測定した。図 28 より電流 - 電圧特性にばらつきがほぼ存在しないことがわかる。よって、絶縁物を有する有機化合物層を用いても、半導体層を設けることにより記憶素子毎の挙動のばらつきを低減することができる。

#### 【実施例 7】

10

20

40

50

## 【0230】

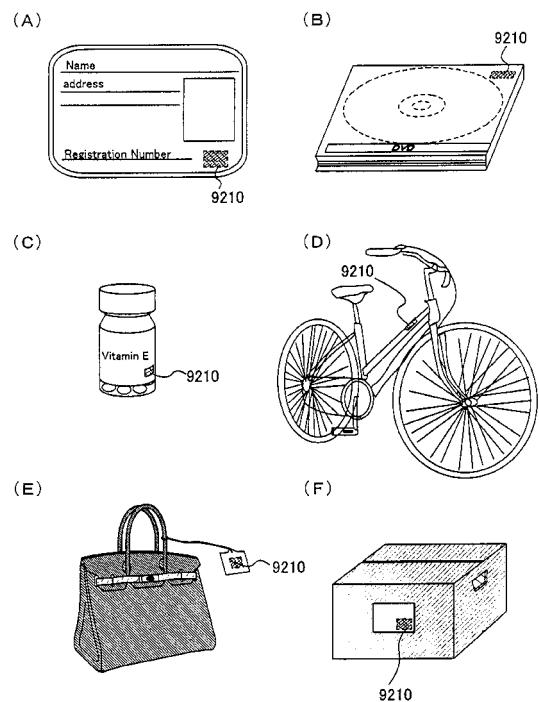

本発明により無線チップとして機能する半導体装置を形成することができる。無線チップの用途は広範にわたるが、例えば、紙幣、硬貨、有価証券類、無記名債券類、証書類(運転免許証や住民票等、図29(A)参照)、包装用容器類(包装紙やボトル等、図29(C)参照)、記録媒体(DVDソフトやビデオテープ等、図29(B)参照)、乗物類(自転車等、図29(D)参照)、身の回り品(鞄や眼鏡等)、食品類、植物類、動物類、人体、衣類、生活用品類、電子機器等の商品や荷物の荷札(図29(E)、図29(F)参照)等の物品に設けて使用することができる。電子機器とは、液晶表示装置、EL表示装置、テレビジョン装置(単にテレビ、テレビ受像機、テレビジョン受像機とも呼ぶ)及び携帯電話等を指す。

10

## 【0231】

本発明の半導体装置9210は、本発明の記憶素子を有し、プリント基板に実装したり、表面に貼ったり、埋め込んだりすることにより、物品に固定される。例えば、本なら紙に埋め込んだり、有機樹脂からなるパッケージなら当該有機樹脂に埋め込んだりして各物品に固定される。本発明の半導体装置9210は、小型、薄型、軽量を実現するため、物品に固定した後も、その物品自体のデザイン性を損なうことがない。また、紙幣、硬貨、有価証券類、無記名債券類、証書類等に本発明の半導体装置9210を設けることにより、認証機能を設けることができ、この認証機能を活用すれば、偽造を防止することができる。また、包装用容器類、記録媒体、身の回り品、食品類、衣類、生活用品類、電子機器等に本発明の半導体装置を設けることにより、検品システム等のシステムの効率化を図ることができる。

20

## 【0232】

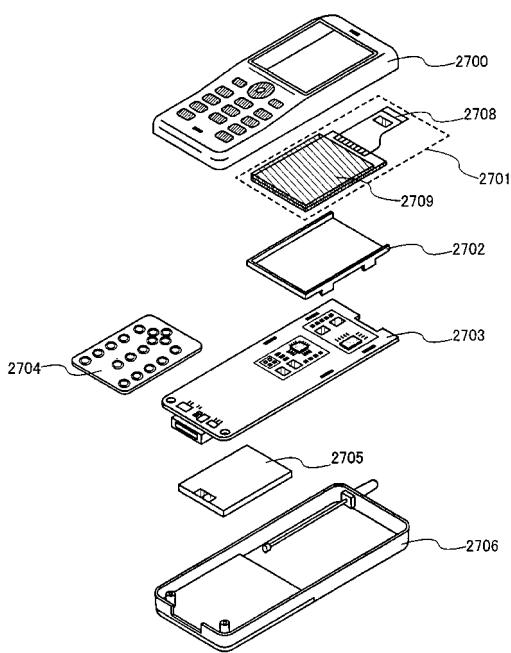

次に、本発明の半導体装置を実装した電子機器の一態様について図30を用いて説明する。ここで例示する電子機器は携帯電話機であり、筐体2700、2706、パネル2701、ハウジング2702、プリント配線基板2703、操作ボタン2704、バッテリ2705を有する。パネル2701はハウジング2702に脱着自在に組み込まれ、ハウジング2702はプリント配線基板2703に嵌着される。ハウジング2702はパネル2701が組み込まれる電子機器に合わせて、形状や寸法が適宜変更される。プリント配線基板2703には、パッケージングされた複数の半導体装置が実装されており、このうちの1つとして、本発明の記憶素子を有する半導体装置を用いることができる。プリント配線基板2703に実装される複数の半導体装置は、コントローラ、中央処理ユニット(CPU、Central Processing Unit)、メモリ、電源回路、音声処理回路、送受信回路等のいずれかの機能を有する。

30

## 【0233】

パネル2701は、接続フィルム2708を介して、プリント配線基板2703と接続される。上記のパネル2701、ハウジング2702、プリント配線基板2703は、操作ボタン2704やバッテリ2705と共に、筐体2700、2706の内部に収納される。パネル2701が含む画素領域2709は、筐体2700に設けられた開口窓から視認できるように配置されている。

40

## 【0234】

上記の通り、本発明の半導体装置は、小型、薄型、軽量であることを特徴としており、上記特徴により、電子機器の筐体2700、2706内部の限られた空間を有効に利用することができる。なお、筐体2700、2706は、携帯電話機の外観形状を一例として示したものであり、本実施例に係る電子機器は、その機能や用途に応じて様々な態様に変容しうる。

## 【0235】

なお、本発明の記憶素子は、第1の導電層と、半導体層と、有機化合物層と、第2の導電層とを有し、半導体層及び有機化合物層は第1の導電層と第2の導電層に挟持され、前記半導体層は、前記第1の導電層上に接して形成される。このような記憶素子を有することにより導電層等の破壊や記憶素子の絶縁状態などの異常な挙動を抑制することができ

50

る。よって、記憶素子毎の挙動のばらつきを低減することが可能となる。したがって、読み取り電圧のとり得る幅も広がり、半導体装置における設計の自由度が向上する。

#### 【0236】

また、半導体装置へのデータの書き込みは一度だけではなく、追加（追記）が可能である。一方、書き込みを一度行った記憶素子に対しデータを消去することは不可能なため、書き換えによる偽造を防止することができる。さらに、本発明の記憶素子は一対の導電層間に半導体層及び有機化合物層が挟まれた単純な構造であるため、性能及び信頼性に優れた記憶装置及びその記憶装置を備えた半導体装置を低成本で作製することが可能となる。

#### 【0237】

10

なお、本実施例は、実施の形態及び他の実施例とも自由に組み合わせることができる。

#### 【図面の簡単な説明】

#### 【0238】

【図1】記憶素子の電流 - 電圧特性を示す図。

【図2】本発明の記憶素子の一構成例について説明する図。

【図3】本発明の記憶素子の動作機構について説明する図。

【図4】本発明の記憶素子の一構成例について説明する図。

【図5】本発明の記憶素子の一構成例について説明する図。

【図6】本発明の半導体装置の一構成例について説明する図。

【図7】本発明の半導体装置が有するメモリセルについて説明する図。

20

【図8】本発明の記憶素子の一構成例について説明する図。

【図9】本発明の半導体装置の一構成例について説明する図。

【図10】本発明の半導体装置が有するメモリセルについて説明する図。

【図11】薄膜トランジスタの一態様について説明する図。

【図12】本発明の半導体装置の一構成例について説明する図。

【図13】本発明の半導体装置の一構成例について説明する図。

【図14】本発明の半導体装置の断面の一部を説明する図。

【図15】本発明の半導体装置の断面の一部を説明する図。

【図16】本発明の半導体装置について説明する図。

【図17】本発明のチップ状の半導体装置について説明する図。

30

【図18】記憶素子に書き込み電圧を印加した後のTEM写真。

【図19】素子サイズの異なる記憶素子における印加電圧に対する書き込み成功率を示す図。

【図20】本発明の記憶素子の電流 - 電圧特性を示す図。

【図21】本発明の記憶素子の電流 - 電圧特性を示す図。

【図22】本発明の記憶素子の電流 - 電圧特性を示す図。

【図23】本発明の記憶素子の電流 - 電圧特性を示す図。

【図24】本発明の記憶素子の電流 - 電圧特性を示す図。

【図25】本発明の記憶素子の印加電圧に対する書き込み成功率を示す図。

【図26】本発明の記憶素子の印加電圧に対する書き込み成功率を示す図。

40

【図27】本発明の記憶素子の印加電圧に対する書き込み成功率を示す図。

【図28】本発明の記憶素子の電流 - 電圧特性を示す図。

【図29】本発明の半導体装置を搭載した物品について説明する図。

【図30】本発明の半導体装置を搭載した携帯電話について説明する図。

#### 【符号の説明】

#### 【0239】

110 導電層

111 半導体層

112 有機化合物層

113 導電層

50

|       |               |    |

|-------|---------------|----|

| 2 1 1 | 半導体層          |    |

| 2 2 1 | 半導体層          |    |

| 2 3 1 | 粒子            |    |

| 3 1 1 | 半導体層          |    |

| 3 2 1 | 半導体層          |    |

| 3 3 1 | 半導体層          |    |

| 4 0 0 | 半導体装置         |    |

| 4 0 1 | 記憶素子          |    |

| 4 0 2 | 記憶素子          |    |

| 4 1 1 | メモリセルアレイ      | 10 |

| 4 1 2 | デコーダ          |    |

| 4 1 3 | デコーダ          |    |

| 4 1 4 | セレクタ          |    |

| 4 1 5 | 読み出し / 書き込み回路 |    |

| 4 5 0 | 抵抗素子          |    |

| 4 5 1 | 差動増幅器         |    |

| 4 5 2 | トランジスタ        |    |

| 4 5 3 | クロックトインバータ    |    |

| 5 0 1 | 導電層           |    |

| 5 1 0 | 導電層           | 20 |

| 5 1 3 | 導電層           |    |

| 5 2 0 | 有機化合物層        |    |

| 5 2 1 | 基板            |    |

| 5 2 2 | 絶縁層           |    |

| 6 1 1 | ダイオード         |    |

| 6 1 2 | 導電層           |    |

| 6 1 3 | 半導体層          |    |

| 6 1 4 | 層間絶縁膜         |    |

| 6 2 1 | 隔壁            |    |

|       |               | 30 |

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【図16】

【図17】

【図18】

【図19】

【図20】

【図21】

【図22】

【図23】

【図24】

【図25】

【図26】

【図27】

【図28】

【図29】

【図30】

---

フロントページの続き

| (51)Int.Cl.             | F I                  |

|-------------------------|----------------------|

| H 01 L 29/786 (2006.01) | H 01 L 27/10 4 6 1   |

| H 01 L 21/822 (2006.01) | H 01 L 29/78 6 1 3 B |

| H 01 L 27/04 (2006.01)  | H 01 L 27/04 L       |

| G 06 K 19/07 (2006.01)  | G 06 K 19/00 H       |

| G 06 K 19/077 (2006.01) | G 06 K 19/00 K       |

(56)参考文献 特開2003-007977(JP,A)

特表2004-513513(JP,A)

特開2005-183619(JP,A)

特開2005-317955(JP,A)

特開2004-047791(JP,A)

特開2006-186363(JP,A)

## (58)調査した分野(Int.Cl., DB名)

|        |             |

|--------|-------------|

| H 01 L | 2 7 / 1 0   |

| G 06 K | 1 9 / 0 7   |

| G 06 K | 1 9 / 0 7 7 |

| H 01 L | 2 1 / 8 2 2 |

| H 01 L | 2 7 / 0 4   |

| H 01 L | 2 7 / 2 8   |

| H 01 L | 2 9 / 7 8 6 |

| H 01 L | 4 5 / 0 0   |

| H 01 L | 4 9 / 0 0   |

| H 01 L | 5 1 / 0 5   |