(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第4145984号

(P4145984)

(45) 発行日 平成20年9月3日(2008.9.3)

(24) 登録日 平成20年6月27日(2008.6.27)

(51) Int.Cl.

F 1

|               |           |              |      |

|---------------|-----------|--------------|------|

| G 11 C 11/413 | (2006.01) | G 11 C 11/34 | J    |

| G 11 C 7/00   | (2006.01) | G 11 C 7/00  | 312Z |

| G 11 C 11/409 | (2006.01) | G 11 C 11/34 | 354A |

| G 11 C 11/407 | (2006.01) | G 11 C 11/34 | 362S |

請求項の数 7 (全 14 頁)

|           |                       |

|-----------|-----------------------|

| (21) 出願番号 | 特願平10-67314           |

| (22) 出願日  | 平成10年3月17日(1998.3.17) |

| (65) 公開番号 | 特開平11-265581          |

| (43) 公開日  | 平成11年9月28日(1999.9.28) |

| 審査請求日     | 平成17年3月17日(2005.3.17) |

|           |                                       |

|-----------|---------------------------------------|

| (73) 特許権者 | 000003078<br>株式会社東芝<br>東京都港区芝浦一丁目1番1号 |

| (74) 代理人  | 100058479<br>弁理士 鈴江 武彦                |

| (74) 代理人  | 100084618<br>弁理士 村松 貞男                |

| (74) 代理人  | 100092196<br>弁理士 橋本 良郎                |

| (74) 代理人  | 100091351<br>弁理士 河野 哲                 |

| (74) 代理人  | 100088683<br>弁理士 中村 誠                 |

| (74) 代理人  | 100070437<br>弁理士 河井 将次                |

最終頁に続く

(54) 【発明の名称】半導体記憶装置

## (57) 【特許請求の範囲】

## 【請求項 1】

データを記憶するメモリセルと、

マスタラッチ回路のみを有する第1のデータ記憶手段と、

マスタラッチ回路とスレーブラッチ回路を有する第2のデータ記憶手段と、

前記メモリセルと前記第1のデータ記憶手段及び第2のデータ記憶手段との接続関係を

設定された条件に従って選択することにより、前記メモリセルから同時に読み出した2つの

データのうち、先に出力することが必要とされるデータを前記第1のデータ記憶手段に出力し、

この第1のデータ記憶手段からのデータ出力の後に出力することが必要とされる

データを第2のデータ記憶手段に出力するデータバス制御手段と、

前記第1のデータ記憶手段及び第2のデータ記憶手段に記憶されたデータを順次出力する

マルチプレクサ手段とを具備し、

前記第2のデータ記憶手段が有する前記マスタラッチ回路と前記スレーブラッチ回路を

形成するトランジスタのチャネル幅は、前記第1のデータ記憶手段が有する前記マスタラ

ッチ回路を形成するトランジスタのチャネル幅に比べて小さく、

前記第2のデータ記憶手段は、前記第1のデータ記憶手段の電流駆動力よりも小さい電

流駆動力を有することを特徴とする半導体記憶装置。

## 【請求項 2】

データを記憶するメモリセルと、

動作タイミングを制御するクロック信号のサイクルの始まりに入力されたデータを前記

10

20

サイクルの前半の期間中、記憶するマスタラッチ回路を有する第1のデータ記憶手段と、前記クロック信号のサイクルの始まりに入力された前記データを前記サイクルの全期間中、記憶するマスタラッチ回路及びスレーブラッチ回路を有する第2のデータ記憶手段と、

前記メモリセルから同時に読み出した2つのデータのうち、先に出力することが必要とされるデータを前記第1のデータ記憶手段に出力し、この第1のデータ記憶手段からのデータ出力の後に出力することが必要とされるデータを第2のデータ記憶手段に出力するデータバス制御手段と。

前記クロック信号の一サイクルのうち、前半の期間では前記第1のデータ記憶手段に記憶されたデータを選択して出力し、後半の期間では前記第2のデータ記憶手段に記憶されたデータを選択して出力するマルチプレクサ手段とを具備し、

前記第2のデータ記憶手段が有する前記マスタラッチ回路と前記スレーブラッチ回路を形成するトランジスタのチャネル幅は、前記第1のデータ記憶手段が有する前記マスタラッチ回路を形成するトランジスタのチャネル幅に比べて小さく、

前記第2のデータ記憶手段は、前記第1のデータ記憶手段の電流駆動力よりも小さい電流駆動力を有することを特徴とする半導体記憶装置。

#### 【請求項3】

前記第1のデータ記憶手段と前記マルチプレクサ手段との間に設けられた第1のバッファ手段と、

前記第2のデータ記憶手段と前記マルチプレクサ手段との間に設けられた第2のバッファ手段をさらに具備し、

前記第1のバッファ手段の最終段の回路サイズと前記第2のバッファ手段の最終段の回路サイズとが等しく設定されることを特徴とする請求項1または2に記載の半導体記憶装置。

#### 【請求項4】

前記第2のバッファ手段は、直列接続された多段のバッファを有していることを特徴とする請求項3に記載の半導体記憶装置。

#### 【請求項5】

前記マルチプレクサ手段は、読み出しの動作タイミングを制御するクロック信号の一サイクルのうち、前半の期間では前記第1のデータ記憶手段に記憶されたデータを選択して出力し、後半の期間では前記第2のデータ記憶手段に記憶されたデータを選択して出力することを特徴とする請求項1または2に記載の半導体記憶装置。

#### 【請求項6】

外部よりメモリセルを選択するための第1のアドレス信号を受け取り、前記第1のアドレス信号を一時的に記憶するアドレスレジスタと、

外部より前記第1のアドレス信号を受け取り、定められた規則に従って前記第1のアドレス信号に基づいてメモリセルを選択するための第2のアドレス信号を自己生成するバーストカウンタと、

前記アドレスレジスタから出力される前記第1のアドレス信号と前記バーストカウンタにより生成される前記第2のアドレス信号の各々の信号に基づいて選択された2つのメモリセルのデータを読み出し、前記データバス制御手段に出力するセンスアンプをさらに具備することを特徴とする請求項1乃至5のいずれか1つに記載の半導体記憶装置。

#### 【請求項7】

前記半導体記憶装置の周辺部に分散して配置され、前記マルチプレクサ手段からの出力信号を外部に出力する外部出力端子と、

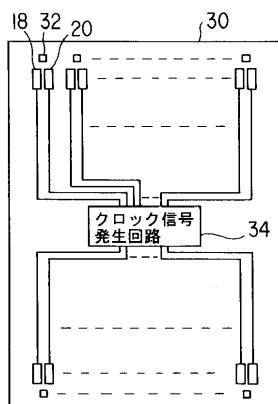

前記半導体記憶装置の中央部に配置され、前記第1のデータ記憶手段及び第2のデータ記憶手段の動作タイミングを制御するクロック信号を発生するクロック信号発生回路をさらに具備し、

前記第1のデータ記憶手段及び第2のデータ記憶手段は前記外部出力端子の近傍に配置されていることを特徴とする請求項1乃至6のいずれか1つに記載の半導体記憶装置。

10

20

30

40

50

**【発明の詳細な説明】****【0001】****【発明の属する技術分野】**

本発明は、ダブルデータレート(Double Data Rate)仕様の同期型の半導体記憶装置に関し、特にダブルデータレート仕様の半導体記憶装置に備えられた出力制御回路に関するものである。

**【0002】****【従来の技術】**

従来、同期型の半導体記憶装置の場合、データの出力タイミングがクロック信号で制御されるために、半導体記憶装置の出力制御回路には出力レジスタが設けられている。 10

**【0003】**

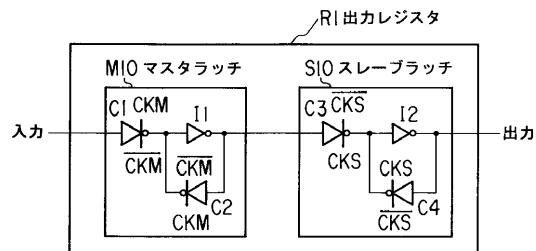

図6に従来の出力レジスタの構成を示し、図7にこの出力レジスタの動作を説明するためのタイミングチャートを示す。図6に示すように、一般的な出力レジスタR1は、マスタラッチM10とスレーブラッチS10を有している。マスタラッチM10はクロックドインバータC1、C2とインバータI1からなり、これらクロックドインバータC1、C2にはクロック信号CKMとこの反転信号/CKMが入力されている。スレーブラッチS10はクロックドインバータC3、C4とインバータI2からなり、これらクロックドインバータC3、C4にはクロック信号CKSとこの反転信号/CKSが入力されている。

**【0004】**

前記マスタラッチM10とスレーブラッチS10は、入力データをそのまま出力に転送するスルー状態と、入力を切り離してデータを保持(ラッチ)するラッチ状態の2通りの状態をとる。マスタラッチM10とスレーブラッチS10の状態は、それぞれに入力されるクロック信号で制御されるが、お互い逆の状態(一方がラッチ状態のとき、他方はスルー状態)になるようにクロック信号CKMとCKSは逆相で入力される。 20

**【0005】**

より正確に言えば、図7(d)、(e)に示すように、クロック信号CKMが“H”でクロック信号CKSが“L”となり、マスタラッチM10がラッチ状態でスレーブラッチS10がスルー状態から、逆の状態に遷移するときは、クロック信号CKSが“H”となりスレーブラッチS10がラッチ状態に遷移するタイミング(図7中のtB)よりも、クロック信号CKMが“L”となりマスタラッチM10がスルー状態に遷移するタイミング(図7中のtC)をわずかに遅れるように、それぞれのクロック信号CKM、CKSの変化のタイミングを制御する。 30

**【0006】**

こうすることにより、クロック信号CKMのサイクルの始まりであるtAの時点で、マスタラッチM10が取り込み保持していた出力レジスタへの入力データ(ア)を、tBからはスレーブラッチS10で保持する。マスタラッチM10は、tC以降に入力データをスルーとして、次のサイクルのtAで再びデータ(イ)をラッチする準備に入る。これにより、出力レジスタの出力となるスレーブラッチS10の出力は、各サイクルの始まりにおいて出力レジスタに入力されていたデータをそのサイクルの間保持することができる。 40

**【0007】**

また、前記出力レジスタの出力は、通常、信号負荷の大きい外部出力用の出力回路へデータ転送される。このため、信号遅延を抑えるために、出力レジスタは出力パッドの近傍に配置される。よって、多ビット構成の半導体記憶装置の場合には、出力レジスタは出力パッドに併せて半導体記憶装置チップ内に分散配置される。

**【0008】**

ここで、出力レジスタを制御するクロック信号はクロック信号生成回路から各出力レジスタへ出力されるため、出力レジスタがチップ内に分散配置されると、クロック信号配線の総長がのびることになる。これにより、配線自身の寄生抵抗が増加し、駆動すべき負荷容量に加えて配線自身の負荷容量も増加する。つまり、RC遅延によるクロック信号の遅延が増えることにより、性能悪化の問題が発生する。さらに、チップ内における出力レジス 50

タの位置に依存してクロック信号の R C 遅延が異なるため、これによって生ずる出力データのばらつき、いわゆるクロックスキューも問題となる。

#### 【 0 0 0 9 】

一般的に、R C 遅延に対しては、グローバルなクロック信号をさらにローカルなクロックバッファで分散駆動するなどの対策がとられ、またクロックスキューの問題に対しては、出力レジスタごとのクロック信号の R C 遅延が等価になるようにクロックの配線経路を工夫するなどの対策がとられている。しかし、いずれの問題にしても、クロック信号が駆動すべき負荷容量を最小に抑えることが重要である。

#### 【 0 0 1 0 】

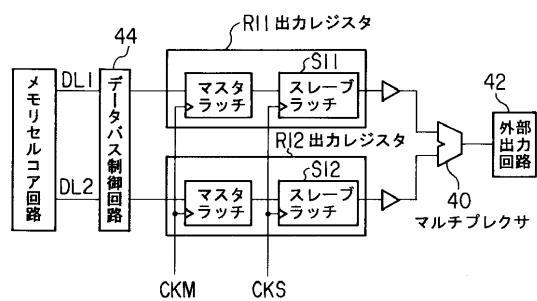

次に、前述の出力レジスタを用いた D D R 仕様の出力制御回路について説明する。図 8 は 10

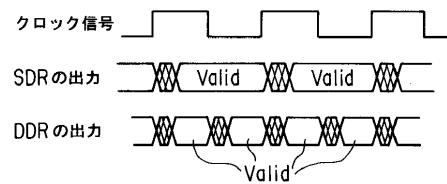

、出力レジスタを用いた D D R 仕様の出力制御回路の構成例を示す図である。通常の同期型の半導体記憶装置においては、図 9 に示すように出力制御用のクロック信号のサイクルの始まりであるアップエッジ毎にデータが入出力される方式、シングルデータレート ( S D R ; Single Data Rate ) に対し、サイクルの始まりと中間の 2 回、つまりクロックのアップエッジとダウンエッジのそれぞれにおいてシリアルにデータが入出力される方式のことをダブルデータレート ( D D R ; Double Data Rate ) という。

#### 【 0 0 1 1 】

半導体記憶装置に入力されるアドレスデータは、通常、1 つであるため、入力アドレスに対するデータと、記憶装置内部にてバーストモードで生成されるアドレスに対するデータがやりとりされる。D D R 仕様は、通常の S D R 仕様の倍のデータ転送を行おうとするものであるため、D D R 仕様における半導体記憶装置内部でのメモリセルの読み出しは、ほぼ S D R 仕様と同様の時間で行われている。つまり、入力アドレスに対するメモリセルと、半導体記憶装置内部でバーストモードで生成されるアドレスに対するメモリセルとが同時に選択されて、メモリセルに記憶されたデータが検出される。このデータが図 8 にあるように 2 本のデータ線 D L 1 、 D L 2 からパラレルに設けられた出力レジスタ R 1 1 、 R 1 2 にそれぞれ入力、保持されている。

#### 【 0 0 1 2 】

ここで、前記出力レジスタ R 1 1 、 R 1 2 の後段に設けられたマルチプレクサ 4 0 によって、サイクル前半は出力レジスタ R 1 1 側のスレーブラッチ S 1 1 のデータが外部出力回路 4 2 に出力され、サイクル後半は出力レジスタ R 1 2 側のスレーブラッチ S 1 2 のデータが外部出力回路 4 2 に出力される。そして、外部出力回路 4 2 に入力されたデータが外部に出力されるようになっている。

#### 【 0 0 1 3 】

このように、クロック信号のサイクル前後半で読み出される出力レジスタ R 1 1 側と出力レジスタ R 1 2 側のデータのアドレスの関係は、バーストモードがリニア ( Linear ) かインターリーブ ( Interleaved ) かによって異なり、さらにインターリーブの場合はスタートアドレスに応じて切り替わる。したがって、内部のメモリセルから同時に読み出された 2 つのデータを、これらのアドレスの関係に応じて出力レジスタ R 1 1 と出力レジスタ R 1 2 に選択して格納するために、出力レジスタ R 1 1 、 R 1 2 の前段にバスの接続を制御するデータバス制御回路 ( bus exchanger ) 4 4 が設けてある。このデータバス制御回路 4 4 は、メモリセルから出力レジスタまでの間で複数のデータバスの接続関係を制御することにより、メモリセルと出力レジスタとの接続関係を設定された条件に従って選択することができる回路である。なお、データバス制御回路については、特願平 9 - 2 9 5 4 3 1 号に記載されている。

#### 【 0 0 1 4 】

##### 【発明が解決しようとする課題】

図 8 に示すように、D D R 仕様の半導体記憶装置の場合、出力レジスタがパラレルに設けられるために、S D R 仕様の場合に比べて倍の数の出力レジスタが必要となる。すると、出力レジスタを制御するクロック信号 ( 図 8 中の C K M 、 C K S ) が駆動しなければならないゲート容量負荷は倍になる。つまり、D D R 仕様では、S D R 仕様の場合に存在する

10

20

30

40

50

前述したクロック信号の R C 遅延による性能悪化の問題や、クロックスキューの問題がそのまま増長されることになる。このため、S D R 仕様の倍の周波数でデータを読み出すことができなくなるという問題が発生する。

#### 【 0 0 1 5 】

そこで本発明は、前記課題に鑑みてなされたものであり、出力レジスタを制御するクロック信号のゲート容量負荷を低減することにより、クロック信号の R C 遅延による性能悪化及びクロックスキューを低減し、シングルデータレート（ S D R ）仕様の倍のデータ転送レートでデータを読み出すことができるダブルデータレート（ D D R ）仕様の半導体記憶装置を提供することを目的とする。

#### 【 0 0 1 6 】

10

#### 【課題を解決するための手段】

本発明の一実施態様の半導体記憶装置は、データを記憶するメモリセルと、マスタラッチ回路のみを有する第1のデータ記憶手段と、マスタラッチ回路とスレーブラッチ回路を有する第2のデータ記憶手段と、前記メモリセルと前記第1のデータ記憶手段及び第2のデータ記憶手段との接続関係を設定された条件に従って選択することにより、前記メモリセルから同時に読み出した2つのデータのうち、先に出力することが必要とされるデータを前記第1のデータ記憶手段に出力し、この第1のデータ記憶手段からのデータ出力の後に出力することが必要とされるデータを第2のデータ記憶手段に出力するデータバス制御手段と、前記第1のデータ記憶手段及び第2のデータ記憶手段に記憶されたデータを順次出力するマルチプレクサ手段とを具備し、前記第2のデータ記憶手段が有する前記マスタラッチ回路と前記スレーブラッチ回路を形成するトランジスタのチャネル幅は、前記第1のデータ記憶手段が有する前記マスタラッチ回路を形成するトランジスタのチャネル幅に比べて小さく、前記第2のデータ記憶手段は、前記第1のデータ記憶手段の電流駆動力よりも小さい電流駆動力を有することを特徴とする。

20

#### 【 0 0 1 7 】

本発明の他の実施態様の半導体記憶装置は、データを記憶するメモリセルと、動作タイミングを制御するクロック信号のサイクルの始まりに入力されたデータを前記サイクルの前半の期間中、記憶するマスタラッチ回路を有する第1のデータ記憶手段と、前記クロック信号のサイクルの始まりに入力された前記データを前記サイクルの全期間中、記憶するマスタラッチ回路及びスレーブラッチ回路を有する第2のデータ記憶手段と、前記メモリセルから同時に読み出した2つのデータのうち、先に出力することが必要とされるデータを前記第1のデータ記憶手段に出力し、この第1のデータ記憶手段からのデータ出力の後に出力することが必要とされるデータを第2のデータ記憶手段に出力するデータバス制御手段と、前記クロック信号の一サイクルのうち、前半の期間では前記第1のデータ記憶手段に記憶されたデータを選択して出力し、後半の期間では前記第2のデータ記憶手段に記憶されたデータを選択して出力するマルチプレクサ手段とを具備し、前記第2のデータ記憶手段が有する前記マスタラッチ回路と前記スレーブラッチ回路を形成するトランジスタのチャネル幅は、前記第1のデータ記憶手段が有する前記マスタラッチ回路を形成するトランジスタのチャネル幅に比べて小さく、前記第2のデータ記憶手段は、前記第1のデータ記憶手段の電流駆動力よりも小さい電流駆動力を有することを特徴とする。

30

#### 【 0 0 1 9 】

40

#### 【発明の実施の形態】

以下、図面を参照してこの発明の実施の形態について説明する。

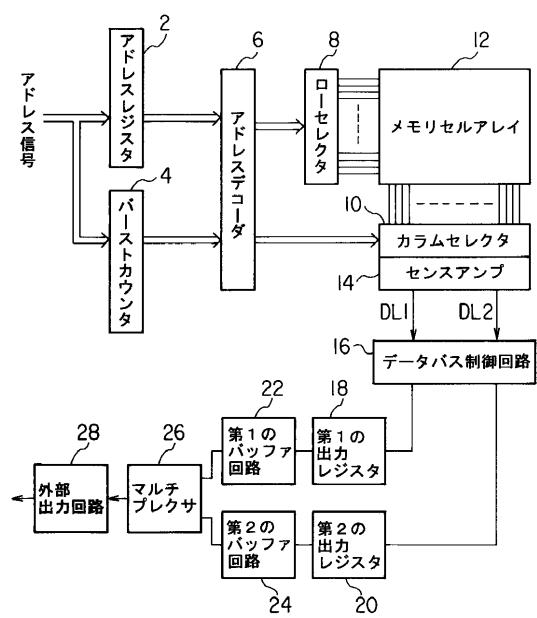

図1は、この発明の実施の形態の半導体記憶装置の構成を示すブロック図である。

#### 【 0 0 2 0 】

図1に示すように、この半導体記憶装置は、入力されたアドレス信号を記憶するアドレスレジスタ2、アドレスを自己発生するために入力されたアドレス信号から定められた規則に従ってバーストアドレス信号を生成するバーストカウンタ4、これらアドレスレジスタ2及びバーストカウンタ4から出力されるアドレス信号及びバーストアドレス信号をデコードしてローアドレス及びカラムアドレスを生成するアドレスデコーダ6、このアドレス

50

デコーダ6から出力されるロードアドレスを受け取りワード線を選択するローデコーダ8、前記アドレスデコーダ6から出力されるカラムアドレスを受け取りビット線を選択するカラムセレクタ10、これらローデコーダ8とカラムセレクタ10によって選択可能なメモリセルがマトリクス状に配置されたメモリセルアレイ12、選択されたメモリセルに記憶されたデータを読み出すセンスアンプ14、このセンスアンプ14により読み出された複数のデータを受け取り、後述する第1及び第2の出力レジスタのいずれに出力するかを選択するデータバス制御回路16、このデータバス制御回路16から出力されるデータを記憶する第1の出力レジスタ18及び第2の出力レジスタ20、第1の出力レジスタ18の出力を増幅する第1のバッファ回路22、第2の出力レジスタ20の出力を増幅する第2のバッファ回路24、これら第1のバッファ回路22及び第2のバッファ回路24の出力を受け取り、入力された複数データを1つの出力データにマルチプレクスするマルチブレクサ26、このマルチブレクサ26の出力を外部に出力するための外部出力回路28から構成される。10

#### 【0021】

以下に前述した半導体記憶装置において、センスアンプ14から外部出力回路28の間に形成された出力制御回路について詳細に説明する。

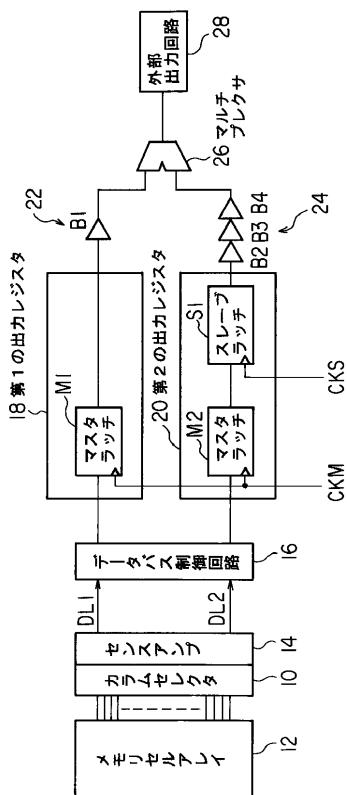

図2は、前記半導体記憶装置における出力制御回路の構成を示す図である。

#### 【0022】

データバス制御回路16は、メモリセルアレイ12を構成するメモリセルから第1、第2の出力レジスタ18、20までの間で複数のデータバスの接続関係を制御することにより、メモリセルと第1、第2の出力レジスタ18、20との接続関係を設定された条件に従って選択することができる回路である。前記データバス制御回路16は、メモリセルアレイ12中のメモリセルからセンスアンプ14によって読み出された2つの第1、第2のデータを受け取り、これらのうち先に出力することが必要とされるデータ（ここでは第1のデータ）を前記第1のデータ記憶手段に出力し、この第1のデータ記憶手段からのデータ出力の後にデータ出力が必要とされるデータ（ここでは第2のデータ）を第2の出力レジスタ20に出力する。20

#### 【0023】

第1の出力レジスタ18は、クロック信号CKMにて制御されるマスタラッチM1からなる。第2の出力レジスタ20は、クロック信号CKMにて制御されるマスタラッチM2と、クロック信号CKSにて制御されるスレーブラッチS1からなる。30

#### 【0024】

前記第2の出力レジスタ20のマスタラッチM2は、第1の出力レジスタ18のマスタラッチM1に比べて、小さいサイズのトランジスタで形成される。すなわち、マスタラッチM2を形成するトランジスタのチャネル幅は、マスタラッチM1を形成するトランジスタのチャネル幅より短くなっている。また、第2の出力レジスタ20のスレーブラッチS1は、図8に示した従来のスレーブラッチ、第1の出力レジスタ18のマスタラッチM1に比べて、小さいサイズのトランジスタで形成される。

#### 【0025】

なお、マスタラッチM2及びスレーブラッチS1を形成するトランジスタのサイズについては、これらがそれぞれのラッチ回路として機能する最小のサイズ以上であればよい。これは、第2の出力レジスタ20の後段に第2のバッファ回路24を設け、マルチブレクサ26に入力される信号の駆動力を第1の出力レジスタ18側と第2の出力レジスタ20側とでそろえているためである。40

#### 【0026】

前記マスタラッチM1とマスタラッチM2にはクロック信号CKMが入力され、これらマスタラッチM1、M2はクロック信号CKMのアップエッジ、すなわち“L”から“H”への立ち上がりでデータをラッチし、クロック信号CKMのダウンエッジ、すなわち“H”から“L”への立ち下がりでデータをスルーする。スレーブラッチS1にはクロック信号CKSが入力され、このスレーブラッチS1はクロック信号CKSのアップエッジでデ50

ータをラッチし、クロック信号CKSのダウンエッジでデータをスルーする。

**【0027】**

また、第1のバッファ回路22は、バッファB1からなり、マスタラッチM1の出力を増幅する。第2のバッファ回路24には、マルチプレクサ26に接続された最終段のバッファ回路の駆動力をA側とB側とでそろえるために、例えば図2に示すように3段のバッファB2、B3、B4を設けて、バッファB4の駆動力をバッファB1の駆動力と同じにする。マルチプレクサ26は、これらバッファB1及びバッファB4の出力を1つの出力にマルチプレクスして、外部出力回路28に出力する。

**【0028】**

すなわち、図8に示した従来例との違いは、クロック信号CKMのサイクル前半、クロックアップエッジで読み出す第1の出力レジスタ18をマスタラッチM1だけの構成とする。さらに、クロック信号CKMのサイクル後半、クロックダウンエッジで読み出す第2の出力レジスタ20はマスタラッチM2とスレーブラッチS1からなる構成とする。そして、第2の出力レジスタ20のマスタラッチM2とスレーブラッチS1を形成するトランジスタのチャネル幅を第1の出力レジスタ18のマスタラッチM1のトランジスタのチャネル幅に比べて小さくする。

10

**【0029】**

さらに、第1の出力レジスタ18の後段に設けられた第1のバッファ回路22のマルチプレクサ26への出力信号の駆動力と、第2の出力レジスタ20の後段に設けられた第2のバッファ回路24のマルチプレクサ26への出力信号の駆動力をそろえるために、ここでは第2の出力レジスタ20側に3段のバッファB2～B4を設けて最終段のバッファB4の駆動力をバッファB1の駆動力とそろえている。

20

**【0030】**

以上のように構成された半導体記憶装置の動作を図1、図2及び図3を参照して説明する。

図1に示すように、外部からアドレス信号がアドレスレジスタ2とバーストカウンタ4に入力される。アドレスレジスタ2に入力されたアドレス信号はアドレスレジスタ2に一時的に記憶された後、アドレスデコーダ6に出力される。一方、バーストカウンタ4にアドレス信号が入力されると、バーストカウンタ4は定められた規則に従ってバーストアドレス信号を生成してアドレスデコード6に出力する。

30

**【0031】**

前記アドレスデコーダ6は、アドレス信号をデコードしてローアドレス及びカラムアドレスを生成し、ローデコーダ8及びカラムセレクタ10にそれぞれ出力する。同様に、アドレスデコーダ6は、バーストアドレス信号をデコードしてローアドレス及びカラムアドレスを生成し、ローデコーダ8及びカラムセレクタ10にそれぞれ出力する。

**【0032】**

前記ローデコーダ8は、入力されたローアドレスに従ってワード線の選択を行う。カラムセレクタ10は、入力されたカラムアドレスに従ってピット線の選択を行う。なお、ここでは前記アドレス信号によって1つのメモリセルが選択され、また前記バーストアドレス信号によって他の1つのメモリセルが選択されるものとする。

40

**【0033】**

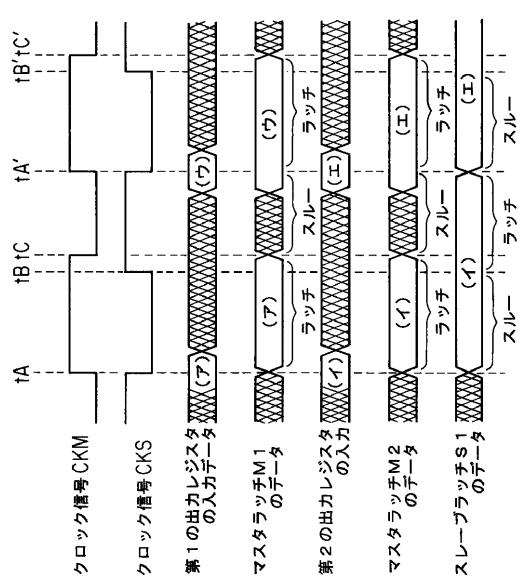

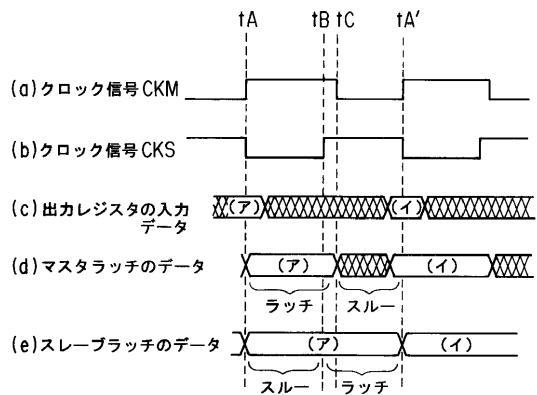

次に、図2と、図3に示す第1、第2の出力レジスタ18、20の動作を示したタイミングチャートを参照して説明する。

前記アドレス信号に基づいて選択されたワード線とピット線によってメモリセルが選択され、このメモリセルに記憶されているデータがセンスアンプ14によって読み出される。ここで、読み出される前記データをデータ(ア)とする。このデータ(ア)は、データ線DL1によりデータバス制御回路16に出力される。また、バーストアドレス信号に基づいて選択されたワード線とピット線によってメモリセルが選択され、このメモリセルに記憶されているデータがセンスアンプ14によって読み出される。ここで、読み出される前記データをデータ(イ)とする。データ(イ)は、データ線DL2によりデータバス制御

50

回路 1 6 に出力される。

**【 0 0 3 4 】**

続いて、前記データバス制御回路 1 6 では、データ(ア)とデータ(イ)のうち先に外部に出力することが必要とされるデータ(ここではデータ(ア))が第1の出力レジスタ 18 に出力され、他のデータ(ここではデータ(イ))が第2の出力レジスタ 20 に出力される。すなわち、データ(ア)とデータ(イ)のうち、クロック信号のサイクル前半に出力するデータ(ア)が第1の出力レジスタ 18 に出力され、クロック信号のサイクル後半に出力するデータ(イ)が第2の出力レジスタ 20 に出力される。

**【 0 0 3 5 】**

次に、図3に示すように、クロック信号CKMによりクロック信号のサイクル前半がマスタラッチM1、M2に入力されると、すなわちここではクロック信号CKMが“L”から“H”へ立ち上がると(図3中のtA)、マスタラッチM1にはデータ(ア)がラッチされ、マスタラッチM2にはデータ(イ)がラッチされる。マスタラッチM1にラッチされたデータ(ア)はバッファB1に出力され、このバッファB1により増幅されてマルチプレクサ26の第1端子に出力される。

**【 0 0 3 6 】**

このとき、前記クロック信号CKMが“L”から“H”へ立ち上がるのに同期して、図3に示すようにクロック信号CKSが“H”から“L”へ立ち下がると(図3中のtA)、スレーブラッチS1はスルー状態となりマスタラッチM2にラッチされているデータ(イ)をそのままバッファB2に出力する。出力されたデータ(イ)は、バッファB2～B4により増幅されてマルチプレクサ26の第2端子に出力される。

**【 0 0 3 7 】**

続いて、スレーブラッチS1に入力されているクロック信号CKSが“L”から“H”へ立ち上がると(図3中のtB)、スレーブラッチS1はスルー状態からラッチ状態へ遷移してマスタラッチM2にラッチされていたデータ(イ)をラッチする。スレーブラッチS1にラッチされたデータ(イ)はバッファB2に出力され、バッファB2～B4により増幅されてマルチプレクサ26の第2端子に出力される。

**【 0 0 3 8 】**

さらに、クロック信号CKMによりクロック信号のサイクル後半が入力されると、すなわちクロック信号CKMが“H”から“L”に立ち下がると(図3中のtC)、マスタラッチM1及びマスタラッチM2はラッチ状態からスルー状態へ遷移する。

**【 0 0 3 9 】**

次に、図3に示すように、第1の出力レジスタ18と第2の出力レジスタ20にそれぞれ入力されるデータを、データ(ウ)、データ(エ)とする。再び、クロック信号CKMによりクロック信号のサイクル前半がマスタラッチM1、M2に入力されると(図3中のtA)、マスタラッチM1にはデータ(ウ)がラッチされ、マスタラッチM2にはデータ(エ)がラッチされる。マスタラッチM1にラッチされたデータ(ウ)はバッファB1に出力され、このバッファB1により増幅されてマルチプレクサ26の第1端子に出力される。

**【 0 0 4 0 】**

このとき、前記クロック信号CKMが“L”から“H”へ立ち上がるのに同期して、図3に示すようにクロック信号CKSが“H”から“L”へ立ち下がると(図3中のtA)、スレーブラッチS1はスルー状態となりマスタラッチM2にラッチされているデータ(エ)をそのままバッファB2に出力する。出力されたデータ(エ)は、バッファB2～B4により増幅されマルチプレクサ26の第2端子に出力される。

**【 0 0 4 1 】**

続いて、スレーブラッチS1に入力されているクロック信号CKSが“L”から“H”へ立ち上がると(図3中のtB)、スレーブラッチS1はスルー状態からラッチ状態へ遷移してマスタラッチM2にラッチされていたデータ(エ)をラッチする。スレーブラッチS1にラッチされたデータ(エ)はバッファB2に出力され、バッファB2～B4により増

10

20

30

40

50

幅されてマルチプレクサ26の第2端子に出力される。

**【0042】**

さらに、クロック信号CKMによりクロック信号のサイクル後半が入力されると(図3中のtC)、マスタラッチM1及びマスタラッチM2はラッチ状態からスルー状態へ遷移する。

**【0043】**

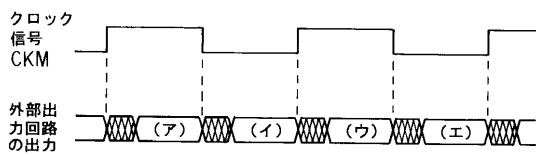

次に、前記マルチプレクサ26は、クロック信号CKMのクロック信号のサイクル前半で第1端子に入力されているデータ(ア)を取り込み、そのサイクル後半で第2端子に入力されているデータ(イ)を取り込む。さらに、次のクロック信号CKMのクロック信号のサイクル前半で第1端子に入力されているデータ(ウ)を取り込み、そのサイクル後半で第2端子に入力されているデータ(エ)を取り込む。これにより、マルチプレクサ26に取り込まれたデータは、図4に示すようにクロック信号CKMの半サイクル毎にデータが10出力される信号となって外部出回路28に出力され、この外部出回路28から外部に出力される。

**【0044】**

前述したように、クロック信号CKMのサイクル前半では第1、第2の出力レジスタ18、20内のデータはマスタラッチM1、M2で保持されており、スレーブラッチS1がデータを保持するのはクロック信号CKMのサイクル後半である。ところで、DDR仕様においては第1の出力レジスタ18からデータを読み出すのはサイクル前半のみであり、サイクル後半は第2の出力レジスタ20からデータが読み出される。

20

**【0045】**

したがって、クロック信号CKMのサイクル後半に第1の出力レジスタ18でデータを保持しておく必要はなく、この第1の出力レジスタ18にスレーブラッチが設けられてなくても動作上に支障はない。この実施の形態では、第1の出力レジスタ18のスレーブラッチを削除することにより、このスレーブラッチの動作タイミングを制御していたクロック信号が不要となる。これにより、SDR仕様からDDR仕様になり出力レジスタの個数が2倍となったにもかかわらず、スレーブラッチを制御するクロック信号CKSについてはゲート容量負荷が増加することはない。

**【0046】**

また、前記第1、第2の出力レジスタ18、20を構成するトランジスタの駆動力は、入力から出力までのデータバスについて各ゲート回路間のファンアウトを考慮して、データ転送がなるべく高速となるように決定される。外部出回路28は、半導体記憶装置以外の外部負荷を駆動する必要から大きなファンアウトとなるため、第1、第2の出力レジスタ18、20を構成するトランジスタもそれに合わせた駆動力を持たせる必要があり、さらには図2に示すように、第1、第2の出力レジスタ18、20の後ろにバッファを設けるなどして駆動力を確保している。これは、クロック信号のサイクル前半でマスタラッチがラッチ状態に、スレーブラッチがスルー状態になった瞬間に、出力レジスタに取り込まれたデータを出力段に高速に転送して出力駆動する必要があるためである。

30

**【0047】**

しかし、DDR仕様の第2の出力レジスタ20においては、事情が違い以下のようなになる。第2の出力レジスタ20へのデータ取り込みは、第1の出力レジスタ18と同様にクロック信号CKMのサイクル前半に行われ、マルチプレクサ26の入力端子まではデータが転送される。ただし、そのデータが実際にマルチプレクサ26に取り込まれるのは、クロック信号CKMのサイクル後半になりマルチプレクサ26が第2の出力レジスタ20側に切り替わる、クロック信号CKMのダウンエッジにおいてである。

40

**【0048】**

よって、第1の出力レジスタ18側と異なり、第2の出力レジスタ20に入力されたデータがマルチプレクサ26に取り込まれるまでに、約半サイクルの時間的余裕があることになる。したがって、図2に示すように、第2の出力レジスタ20からマルチプレクサ26までの間にバッファの段数を増やしても、それによる遅れが半サイクルを越えない限りは

50

動作タイミング上は問題はない。

**【0049】**

また、出力が第2の出力レジスタ20側に切り替わった際の、すなわちマルチプレクサ26のデータの取り込みが出力レジスタ20側に切り替わった際のマルチプレクサ26以降のデータ転送スピードを第1の出力レジスタ18側とそろえるためには、最終段のバッファB4の駆動力を、第1の出力レジスタ18側のバッファB1とそれえておけばよい。これにより、第2の出力レジスタ20においては外部出力回路28へのファンアウトを考えて特に駆動力を考慮する必要がなくなり、第2の出力レジスタ20を構成するトランジスタのサイズを第1の出力レジスタ18に比べて小さく絞って設定することができる。

**【0050】**

したがって、SDR仕様からDDR仕様になり、出力レジスタが倍の数必要となった場合でも、マスタラッチ側を制御するクロック信号についてのゲート容量負荷の増加を大幅に抑制することができる。また、スレーブラッチ側に関しては、第1の出力レジスタ側のスレーブラッチが削除でき、かつ第2の出力レジスタ側のトランジスタのサイズを小さくできることから、SDR仕様の場合よりもクロック信号のゲート容量負荷を低減することができる。

10

**【0051】**

また、この実施の形態の半導体記憶回路では、クロックスキューを低減するために、前記第1、第2の出力レジスタ18、20、及びクロック信号発生回路34のチップ内におけるレイアウトを次のように工夫している。

20

**【0052】**

図5は、チップ内における第1、第2の出力レジスタ18、20、及びクロック信号発生回路34のレイアウトを示す図である。

この図5に示すように、チップ30内の周辺部には出力パッド32が配設されている。出力パッド32の近傍には、前記第1の出力レジスタ18と第2の出力レジスタ20が配置される。また、チップ30の中央付近には、これら第1、第2の出力レジスタ18、20を制御するためのクロック信号CKM、CKSを発生するクロック信号発生回路34が配置される。

**【0053】**

このように、クロック信号発生回路34をチップ30の中央付近に配置し、第1、第2の出力レジスタ18、20をチップ30の周辺部に配置することにより、クロック信号発生回路34から第1、第2の出力レジスタ18、20までの配線長に大きな違いが生じないように、すなわちクロック信号の配線経路がほぼ均一になるようとする。これにより、出力レジスタごとのクロック信号のRC遅延がほぼ均一になるようにして、出力レジスタに対するクロックスキューを低減している。

30

**【0054】**

以上説明したようにこの発明の実施の形態によれば、出力レジスタを制御するクロック信号の負荷容量が低減されるために、SDR仕様からDDR仕様になり出力レジスタの数が実質的に倍必要となっても、それによるクロック信号のRC遅延の増加、クロックスキューの増大などの問題を回避することが可能となる。これにより、SDR仕様の場合に比べて、倍の周波数でデータを読み出すことができる、言い換えると実質倍のデータ転送レートが確保できる高速なDDR仕様の半導体記憶装置が実現できる。

40

**【0055】**

**【発明の効果】**

以上述べたように本発明によれば、出力レジスタを制御するクロック信号のゲート容量負荷を低減することにより、クロック信号のRC遅延による性能悪化及びクロックスキューを低減し、シングルデータレート(SDR)仕様の倍のデータ転送レートでデータを読み出すことができるダブルデータレート\_DDR)仕様の半導体記憶装置を提供することができる。

**【図面の簡単な説明】**

50

【図1】この発明の実施の形態の半導体記憶装置の構成を示すブロック図である。

【図2】この発明の実施の形態の半導体記憶装置における出力制御回路の構成を示す図である。

【図3】第1、第2の出力レジスタ18、20の動作を示すタイミングチャートである。

【図4】出力制御クロックと前記半導体記憶装置の外部出力回路から出力されるデータを示すタイミングチャートである。

【図5】前記半導体記憶装置のチップ内における第1、第2の出力レジスタ18、20及びクロック信号発生回路34のレイアウトを示す図である。

【図6】従来の出力レジスタの構成を示す図である。

【図7】従来の出力レジスタの動作を説明するためのタイミングチャートである。 10

【図8】前記出力レジスタを用いたDDR仕様の出力制御回路の構成例を示す図である。

【図9】SDR仕様及びDDR仕様の半導体記憶装置の出力を示すタイミングチャートである。

【符号の説明】

2 ... アドレスレジスタ

4 ... バーストカウンタ

6 ... アドレスデコーダ

8 ... ローデコーダ

10 ... カラムセレクタ

12 ... メモリセルアレイ

14 ... センスアンプ

16 ... データバス制御回路

18 ... 第1の出力レジスタ

20 ... 第2の出力レジスタ

22 ... 第1のバッファ回路

24 ... 第2のバッファ回路

26 ... マルチプレクサ

28 ... 外部出力回路

28 から構成される。

M1、M2 ... マスタラッチ

S1 ... スレーブラッチ

B1、B2、B3、B4 ... バッファ

30 ... チップ

32 ... 出力パッド

34 ... クロック信号発生回路

10

20

30

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

---

フロントページの続き

(72)発明者 大塚 伸朗

神奈川県川崎市幸区堀川町580番1号 株式会社東芝半導体システム技術センター内

(72)発明者 平林 修

神奈川県川崎市幸区堀川町580番1号 株式会社東芝半導体システム技術センター内

審査官 加藤 俊哉

(56)参考文献 特開平06-267279(JP,A)

特開平09-274559(JP,A)

(58)調査した分野(Int.Cl., DB名)

G11C 11/413

G11C 7/00

G11C 11/407

G11C 11/409