**(19) 대한민국특허청(KR)**

**(12) 등록특허공보(B1)**

(51) Int. Cl.

H03M 1/12 (2006.01)

(45) 공고일자

2007년03월29일

(11) 등록번호

10-0701204

(24) 등록일자

2007년03월22일

(21) 출원번호 10-2000-0014342

(22) 출원일자 2000년03월21일

심사청구일자 2005년03월21일

(65) 공개번호 10-2001-0006843

(43) 공개일자 2001년01월26일

(30) 우선권주장 09/274,202 1999년03월22일 미국(US)

(73) 특허권자

핵심 인코포레이티드

미국 캘리포니아 94043 마운틴 뷰 C-200 노스 쇼어라인 블러바드 883

(72) 발명자

데이비드 샤오 동 양

미합중국 캘리포니아 94306 마운틴 뷰 캘리포니아 애비뉴 20 20

보이드 에이 파우러

미합중국 캘리포니아 94086 선니밸리 사우즌 베이뷰 애비뉴4 번가 265

아바스 엘 가멜

미합중국 캘리포니아 94301 팔로 알토 해밀顿 애비뉴 1485

(74) 대리인

박종현

황의창

최영민

임영희

(56) 선행기술조사문현

US 5,140,591 A US 5,264,851 A

US 5,461,425 A US 5,502,440 A

\* 심사관에 의하여 인용된 문현

**심사관 : 김자영**

전체 청구항 수 : 총 48 항

**(54) 동시 아날로그-디지털 변환 및 승산 방법**

**(57) 요약**

본 발명은 비트-직렬 ADCs 및 단일 기울기 ADCs로 A/D 변환 및 승산을 동시에 제공하기 위한 방법에 관한 것이다. 비트 직렬 ADC는 각각의 비교기 및 1-비트 래치에 입력되는 램프 신호 및 BITX 신호를 사용한다. 램프가 아날로그 입력 값을 초과할 때, 비교기는 BITX의 값을 출력하기 위해 래치를 트리거 시킨다. 비트들은 연속적으로 출력된다. 램프 신호는 전압 레벨 및 전압 스텝을 가진 계단식 형태를 가진다. 본 발명에 있어서, 두 개의 계수에 의한 승산이 가능하다. 일 계수는 적당하게 디지인된 램프에 의해 결정되고, 다른 계수는 적당하게 디자인된 BITX에 의해 결정된다. 램프를 통한 승산은 1/X의

인자에 의해 전압 레벨을 변경함으로써 달성되고, 여기에서 X는 승산 계수이다(즉, 0.5의 인자에 의한 승산은 전압 레벨의 전압을 두 배 함으로써 달성된다). BITX를 통한 승산은 X의 인자에 의해 BITX의 주파수를 지연시킴으로써 달성된다. 또한, BITX를 통한 승산이 높은 정확성을 가지도록 BITX 및 램프의 디자인 방법을 설명한다. 또한, 본 발명은 설명된 승산 방법을 사용하여 광 검출기 어레이로 데이터 압축/필터링 방법을 포함한다. 본 발명이 단지 매우 간단한 하드웨어를 필요로 하기 때문에 본 발명은 다중채널 환경에서의 사용이 유용하다.

## 대표도

도 21

### 특허청구의 범위

#### 청구항 1.

비트 직렬 아날로그-디지털 변환기(Analog-to-Digital Converter; ADC)가, 램프(RAMP) 신호를 받는 비교기 반전 입력과, 입력 아날로그 신호를 받는 비교기 비 반전 입력을 갖는 비교기를 포함하고, 비(非)승산(Multiplication)을 제공하는 것으로 정의된 1-램프 신호가 존재하며, 비트 직렬 아날로그-디지털 변환기내의 X의 인자에 의해 아날로그-디지털 변환 및 입력 아날로그 신호의 승산을 동시에 실행하기 위한 방법에 있어서,

- a) M-램프 신호를 발생시키는 단계, 여기에서 상기 M-램프 신호의 전압 레벨은  $1/X$ 의 인자에 의해 상기 1-램프 신호의 전압 레벨보다 높고;

- b) 상기 M-램프 신호를 상기 비교기 반전 입력에 적용하는 단계를 포함하는 방법.

#### 청구항 2.

제 1 항에 있어서,  $0 < X < 1$ 인 방법.

#### 청구항 3.

비트 직렬 아날로그-디지털 변환기(ADC)가, 램프(RAMP) 신호를 받는 비교기 반전 입력과, 입력 아날로그 신호를 받는 비교기 비 반전 입력을 갖는 비교기를 포함하고, 비(非)승산(Multiplication)을 제공하는 것으로 정의된 1-램프 신호가 존재하며, 1-램프 신호는 일정한 크기 V의 전압 스텝을 포함하고, 1-램프는 장시간에 걸쳐 측정된 전압/시간 기울기인 T의 평균 기울기를 가지며, 비트 직렬 아날로그-디지털 변환기내의 X의 인자에 의해 아날로그-디지털 변환 및 입력 아날로그 신호의 승산을 동시에 실행하기 위한 방법에 있어서,

- a) 크기  $VN/K$  및 크기  $V(N+1)/K$ 의 전압 스텝을 포함하는 M-램프 신호를 생산하는 단계, 여기에서 상기 N은 정수이고, K도 정수이며, M-램프는 장시간에 걸쳐 측정된 전압/신호 기울기인  $T/X$ 의 평균 기울기를 가지고;

- b) 상기 M-램프 신호를 상기 비교기 반전 입력에 적용하는 단계를 포함하는 방법.

#### 청구항 4.

제 3 항에 있어서,  $0 < X < 1$ 인 방법.

#### 청구항 5.

제 3 항에 있어서,  $K=2^D$ 이고, 여기에서, D는  $1/X$ 의 소수부를 표현하기 위해 사용되는 2진 비트의 수인 방법.

### 청구항 6.

제 3 항에 있어서,  $K=1$ 인 방법.

### 청구항 7.

제 3 항에 있어서, N은  $N \leq (K/X) < N+1$ 이 되도록 선택되는 방법.

### 청구항 8.

삭제

### 청구항 9.

삭제

### 청구항 10.

삭제

### 청구항 11.

삭제

### 청구항 12.

비트 직렬 아날로그-디지털 변환기(ADC)가, BITX 신호를 받는 데이터 입력을 가진 래치(Latch)를 포함하고, 비(非)승산(Multiplication)을 제공하는 주파수  $F_o$ 를 가진 1-BITX 신호가 존재하며, 비트 직렬 아날로그-디지털 변환기내의 X의 인자에 의해 아날로그-디지털 변환 및 입력 아날로그 신호의 승산을 동시에 실행하기 위한 방법에 있어서,

- a) 주파수  $KF_o/N$  및 주파수 크기  $KF_o/(N+1)$ 의 선택적인 세그먼트(Segment)를 포함하는 M-BITX 신호를 생산하는 단계, 여기에서 N은 정수이고, K도 정수이며, 상기 선택적인 세그먼트는, M-BITX가 장시간에 걸쳐 측정된  $XF_o$ 의 평균 주파수를 갖도록 선택된 시간을 가지고;

- b) 상기 M-BITX 신호를 상기 데이터 입력에 적용하는 단계를 포함하는 방법.

### 청구항 13.

제 12 항에 있어서,  $0 < X < 1$ 인 방법.

### 청구항 14.

제 12 항에 있어서,  $K=2^D$ 이고, 여기에서, D는  $1/X$ 의 소수부를 표현하기 위해 사용되는 2진 비트의 수인 방법.

### 청구항 15.

제 12 항에 있어서,  $K=1$ 인 방법.

### 청구항 16.

제 12 항에 있어서,  $N$ 은  $N \leq (K/X) < N + 1$ 이 되도록 선택되는 방법.

### 청구항 17.

제 12 항에 있어서, 상기 M-BITX의 평균 주파수는  $1/2^n$ 의 인자 내까지  $XF_0$ 과 동일하고, 여기에서  $n$ 은 아날로그-디지털 변환을 원하는 해상도의 비트 수인 방법.

### 청구항 18.

삭제

### 청구항 19.

제 12 항에 있어서, 상기 M-BITX의 평균 주파수는  $XF_0$ 의 10% 이내인 방법.

### 청구항 20.

제 12 항에 있어서, 상기 M-BITX의 평균 주파수는  $XF_0$ 의 5% 이내인 방법.

### 청구항 21.

비 승산을 제공하는 주파수  $F_0$ 을 가진 1-BITX 신호가 존재하며, 비트 직렬 아날로그-디지털 변환기 내의 X의 인자에 의해 아날로그-디지털 변환 및 승산을 동시에 제공하기 위한 M-램프 신호 발생 방법에 있어서,

a) 관계:

$$N + \frac{A}{B} \approx \frac{K}{X}$$

에 따라  $N$ ,  $A$  및  $B$ 를 선택하는 단계, 여기에서  $N$ 은 정수이고,  $K$ 는 정수이며 격자 밀도 인자이고;

b)  $2KF_0$ 의 비율로 다음 단계 (i)-(iv)를 실행하는 단계:

i) 제 1 실행 합계에  $A$ 를 가산하는 단계, 여기에서 상기 제 1 실행 합계는  $B$ 의 최대값을 가지고;

ii) a) 상기 제 1 실행 합계가 단계 (i) 동안  $B$ 에 를오버 되지 않으면  $N$ 의 값, 및

b) 상기 제 1 실행 합계가 단계 (i) 동안  $B$ 에 를오버 되지 않으면  $N + 1$ 의 값을 가진 디지털 수를 생산하는 단계;

iii) 제 2 실행 합계에 단계 (ii)에서 생산된 상기 디지털 수를 가산하는 단계;

iv) 상기 제 2 실행 합계를 아날로그 값으로 변환하는 단계;를 포함하고,

그것에 의하여 생산된 일련의 아날로그 값들은 상기 비트 직렬 아날로그-디지털 변환기에 사용될 때 X에 의한 승산을 제공하는 상기 M-BITX 신호인 방법.

### 청구항 22.

제 21 항에 있어서,  $0 < X < 1$ 인 방법.

### 청구항 23.

제 21 항에 있어서,  $K=2^D$ 이고, 여기에서, D는  $1/X$ 의 소수부를 표현하기 위해 사용되는 2진 비트의 수인 방법.

### 청구항 24.

제 21 항에 있어서,  $K=1$ 인 방법.

### 청구항 25.

제 21 항에 있어서, 상기 N은  $N \leq (K/X) < N + 1$  되도록 선택되는 방법.

### 청구항 26.

제 24 항에 있어서, 상기  $N + (A/B)$ 은  $1/2^n$ 의 인자 내까지  $K/X$ 와 동일하고, 여기에서  $n$ 은 아날로그-디지털 변환을 원하는 해상도의 비트 수인 방법.

### 청구항 27.

삭제

### 청구항 28.

제 24 항에 있어서, 상기  $N + (A/B)$ 은  $K/X$ 의 12.5% 이내인 방법.

### 청구항 29.

삭제

### 청구항 30.

제 21 항에 있어서, 상기 N, A 및 B는

$N=K/X$ 의 정수부,

$B=2^n K$ , 및

$A=\text{Round}(B(\text{frac}(K/X)))$  되도록 선택되고,

여기에서  $n$ 은 아날로그-디지털 변환을 원하는 해상도의 비트 수인 방법.

### 청구항 31.

제 21 항에 있어서, 상기  $N$ ,  $A$  및  $B$ 는

$$B = \text{Round}(2^n X K),$$

$$N = K^2 2^n / B \text{의 정수부, 및}$$

$$A = K^2 2^n \bmod(B) \text{가 되도록 선택되고,}$$

여기에서  $n$ 은 아날로그-디지털 변환을 원하는 해상도의 비트 수인 방법.

### 청구항 32.

제 21 항에 있어서, 상기  $N$ ,  $A$  및  $B$ 는 관계:

$$B/C = N + (A/B)$$

에 따라 선택되고,

여기에서  $C$ 는 기 결정된 상수 미만의 정수이고, 상기 분수  $B/C$ 는 상기 기 결정된 상수가 주어지면  $B/C$ 가 가능한  $K/X$ 에 근접하도록 스턴-브로코트 수 트리로부터 선택되는 방법.

### 청구항 33.

제 23 항에 있어서, 상기 기 결정된 상수는  $2^n K$ 이고, 여기에서  $n$ 은 아날로그-디지털 변환을 원하는 해상도의 비트 수인 방법.

### 청구항 34.

비 승산을 제공하는 주파수  $F_0$ 을 가진 1-BITX 신호가 존재하며, 비트 직렬 아날로그-디지털 변환기 내의  $X$ 의 인자에 의해 아날로그-디지털 변환 및 승산을 동시에 제공하기 위한 M-BITX 신호 발생 방법에 있어서,

a) 관계:

$$N + \frac{A}{B} \approx \frac{K}{X}$$

에 따라  $N$ ,  $A$  및  $B$ 를 선택하는 단계, 여기에서  $N$ 은 정수이고,  $K$ 는 정수이며 격자 밀도 인자이고;

b) 실행 합계에  $A$ 를 가산하는 단계, 여기에서 상기 실행 합계는  $B$ 의 최대값을 가지고;

c) i) 상기 실행 합계가 단계 (b) 동안  $B$ 에 롤오버(roll over) 되지 않으면 주파수  $KF_0/N$ ,

ii) 상기 실행 합계가 단계 (b) 동안 B에 롤오버(roll over) 되지 않으면 주파수  $KF_0/(N+1)$ ;을 가진 방형파 신호를 생산하는 단계를 포함하고,

여기에서 단계 (b)는 단계 (c)에서 생산된 상기 방형파 신호의 모든 천이 후에 실행되고;

그것에 의하여 상기 방형파 신호는 상기 비트 직렬 아날로그-디지털 변환기에 사용될 때 X에 의한 승산을 제공하는 상기 M-BITX 신호인 방법.

### 청구항 35.

제 34 항에 있어서,  $0 < X < 1$ 인 방법.

### 청구항 36.

제 34 항에 있어서,  $K=2^D$ 이고, 여기에서 D는  $1/X$ 의 소수부를 표현하기 위해 사용되는 2진 비트의 수인 방법.

### 청구항 37.

제 34 항에 있어서,  $K=1$ 인 방법.

### 청구항 38.

제 34 항에 있어서, 상기 N은  $N \leq (K/X) < N+1$ 이 되도록 선택되는 방법.

### 청구항 39.

제 37 항에 있어서, 상기  $N+(A/B)$ 은  $1/2^n$ 의 인자 내까지  $K/X$ 와 동일하고, 여기에서 n은 아날로그-디지털 변환을 원하는 해상도의 비트 수인 방법.

### 청구항 40.

삭제

### 청구항 41.

제 37 항에 있어서, 상기  $N+(A/B)$ 은  $K/X$ 의 12.5% 이내인 방법.

### 청구항 42.

삭제

### 청구항 43.

제 34 항에 있어서, 상기 N, A 및 B는

$N=K/X$ 의 정수부,

$B=2^nK$ , 및

$A=\text{Round}(B(\text{frac}(K/X)))$ 가 되도록 선택되고,

여기에서  $n$ 은 아날로그-디지털 변환을 원하는 해상도의 비트 수인 방법.

#### 청구항 44.

제 34 항에 있어서, 상기  $N$ ,  $A$  및  $B$ 는

$B=\text{Round}(2^nXK)$ ,

$N=K^22^n/B$ 의 정수부, 및

$A=K^22^n \bmod(B)$ 가 되도록 선택되고,

여기에서  $n$ 은 아날로그-디지털 변환을 원하는 해상도의 비트 수인 방법.

#### 청구항 45.

제 34 항에 있어서, 상기  $N$ ,  $A$  및  $B$ 는 방정식:

$B/C=N+(A/B)$

에 따라 선택되고,

여기에서  $C$ 는 기 결정된 상수 미만의 정수이고, 상기 분수  $B/C$ 는 상기 기 결정된 상수가 주어지면  $B/C$ 가 가능한  $K/X$ 에 근접하도록 스턴-브로코트 수 트리로부터 선택되는 방법.

#### 청구항 46.

제 45 항에 있어서, 상기 기 결정된 상수는  $2^nK$ 이고, 여기에서  $n$ 은 아날로그-디지털 변환을 원하는 해상도의 비트 수인 방법.

#### 청구항 47.

비 승산을 제공하는 주파수  $F_0$ 을 가진 1-BITX 신호가 존재하며, 비트 직렬 아날로그-디지털 변환기 내의  $X$ 의 인자에 의해 아날로그-디지털 변환 및 승산을 동시에 제공하기 위한 M-램프 신호 발생 장치에 있어서,

a)  $KF_0$ 의 주파수에서 제 1 실행 합계에 증분  $A$ 를 가산하기 위한 제 1 누산기, 여기에서 상기 증분  $A$  및 커페시티  $B$ 는 관계:

$$N+\frac{A}{B} \approx \frac{K}{X}$$

에 따라 선택되고, 여기에서 N은 정수이고, K는 정수이며 격자 밀도 인자이고;

b) 상기 제 1 누산기와 통신하는 수 선택기, 상기 수 선택기는

i ) A가 상기 실행 합계에 가산된 후에 상기 제 1 실행 합계가 상기 커패시티 B에 롤오버 되지 않을 때의 디지털 수와 같은 N,

ii) A가 상기 실행 합계에 가산된 후에 상기 제 1 실행 합계가 상기 커패시티 B에 롤오버 되지 않을 때의 디지털 수와 같은 N+1을 출력하도록 하고;

c) KF<sub>0</sub>의 주파수에서 제 2 실행 합계에 단계 (b)에서 생산된 상기 디지털 수를 가산하기 위한 제 2 누산기;

d) 상기 제 2 실행 합계를 수신하여 상기 제 2 실행 합계를 아날로그 값으로 변환하기 위한 디지털-아날로그 변환기를 포함하는 장치.

#### 청구항 48.

제 47 항에 있어서, K=1인 장치.

#### 청구항 49.

제 47 항에 있어서, 상기 제 1 및 제 2 누산기가 2KF<sub>0</sub>의 주파수에서 가산될 수 있도록 상기 제 1 및 제 2 누산기에 주파수를 제공하기 위한 클럭을 더 포함하는 장치.

#### 청구항 50.

제 47 항에 있어서, 상기 디지털-아날로그 변환기가 2KF<sub>0</sub>의 주파수에서 상기 제 2 실행 합계의 디지털-아날로그 변환을 실행하도록 상기 디지털-아날로그 변환기에 주파수를 제공하기 위한 클럭을 더 포함하는 장치.

#### 청구항 51.

비 승산을 제공하는 주파수 F<sub>0</sub>을 가진 1-BITX 신호가 존재하며, 비트 직렬 아날로그-디지털 변환기 내의 X의 인자에 의해 아날로그-디지털 변환 및 승산을 동시에 제공하기 위한 M-BITX 신호 발생 장치에 있어서,

a) 실행 합계에 증분 A를 가산하기 위한 제 1 누산기, 여기에서 상기 증분 A 및 커패시티 B는 관계:

$$N + \frac{A}{B} \approx \frac{K}{X}$$

에 따라 선택되고, 여기에서 N은 정수이고, K는 정수이며 격자 밀도 인자이고;

b) 상기 누산기와 통신하는 방형파 주파수 발생기, 상기 주파수 발생기는

i ) A가 상기 실행 합계에 가산된 후에 상기 실행 합계가 상기 커패시티 B에 롤오버 되지 않을 때의 주파수 KF<sub>0</sub>/N,

ii) A가 상기 실행 합계에 가산된 후에 상기 실행 합계가 상기 커페시티 B에 롤오버 되지 않을 때의 주파수  $KF_0/(N+1)$ 을 발생하도록 하고;

여기에서  $F_0$ 은 비 승산을 제공하는 1-BITX 신호의 주파수이고,

c) 상기 누산기로 하여금 상기 주파수 발생기의 모든 천이 예지가 출력된 후에 상기 실행 합계에 증분 A를 가산시키는 수단을 포함하는 장치.

### 청구항 52.

제 51 항에 있어서,  $K=1$ 인 장치.

### 청구항 53.

제 51 항에 있어서, 상기 방형과 주파수 발생기는, 주파수  $KF_0$ 를 제공하는 클럭(Clock)과 N 또는  $N+1$ 을 선택할 수 있는 모듈을 갖는 주파수 분할기를 포함하고, 상기 주파수 분할기는 주파수  $KF_0$ 를 입력받고 상기 누산기의 실행 합계에 따라  $KF_0/N$  또는  $KF_0/(N+1)$ 의 출력 주파수를 발생시키는 장치.

### 청구항 54.

단일 기울기 아날로그-디지털 변환기(ADC)가, 램프 신호를 받는 비교기 반전 입력과, 입력 아날로그 신호를 받는 비교기 비 반전 입력을 갖는 비교기를 포함하고, 비 승산을 제공하는 1-SS-램프 신호가 존재하고, 1-SS-램프 신호는 S의 전압 대 시간 기울기를 가지며, 단일 기울기 아날로그-디지털 변환기 내의 X의 인자에 의해 아날로그-디지털 변환 및 입력 아날로그 신호의 승산을 동시에 실행하기 위한 방법에 있어서,

a) S/X의 평균 전압 대 시간 기울기를 가진 M-SS-램프 신호를 상기 비교기 반전 입력에 적용하는 단계를 포함하는 방법.

### 청구항 55.

제 54 항에 있어서,  $0 < X < 1$ 인 방법.

### 청구항 56.

삭제

### 청구항 57.

삭제

### 청구항 58.

단일 기울기 아날로그-디지털 변환기(ADC)가, SS-주파수 입력을 갖는 카운터(Counter)를 포함하고, 비 승산을 제공하는 1-SS-주파수 신호가 존재하고, 1-SS-주파수 신호는 주파수 Q를 가지며, 단일 기울기 아날로그-디지털 변환기 내의 X의 인자에 의해 아날로그-디지털 변환 및 입력 아날로그 신호의 승산을 동시에 실행하기 위한 방법에 있어서,

a) Q/X의 평균 주파수를 가진 M-SS-주파수 신호를 상기 카운터의 SS-주파수 입력에 적용하는 단계를 포함하는 방법.

청구항 59.

제 58 항에 있어서,  $0 < X < 1$ 인 방법.

청구항 60.

삭제

청구항 61.

삭제

청구항 62.

삭제

청구항 63.

삭제

청구항 64.

삭제

청구항 65.

삭제

청구항 66.

삭제

청구항 67.

삭제

청구항 68.

삭제

청구항 69.

삭제

청구항 70.

삭제

청구항 71.

삭제

청구항 72.

삭제

청구항 73.

삭제

청구항 74.

삭제

**청구항 75.**

삭제

**청구항 76.**

삭제

**청구항 77.**

삭제

**청구항 78.**

삭제

**청구항 79.**

삭제

**청구항 80.**

삭제

**청구항 81.**

삭제

**청구항 82.**

삭제

**청구항 83.**

삭제

**청구항 84.**

삭제

**청구항 85.**

삭제

**명세서**

## 발명의 상세한 설명

### 발명의 목적

#### 발명이 속하는 기술 및 그 분야의 종래기술

본 발명은 일반적으로 아날로그-디지털 변환 방법 및 전자 승산의 실행 방법에 관한 것이다. 보다 상세하게는, 본 발명은 승산과 함께 동시에 아날로그-디지털 변환의 실행 방법을 제공한다. 본 발명은 다수의 병렬 아날로그 신호의 데이터 압축을 다루는 것에 특히 적합하다. 게다가, 본원은 2 차원 화상 센서 배열로 분리 가능한 변형을 실행할 수 있는 아키텍처(architecture)를 가르친다.

전하 결합 소자(CCDs) 또는 포토다이오드 어레이(arrays)와 같은 화상 센서 어레이에는 보통 머신 비전(machine vision) 또는 디지털 카메라와 같은 화상 애플리케이션(imaging applications)으로 사용된다. 이러한 화상 어레이에는 전형적으로 화상 칩의 표면에 배열된 500,000에서 1,000,000 미시적(microscopic) 광 센서로 이루어진다. 각 센서는 입사 광 세기(incident light intensity)의 함수인 아날로그 값(예를 들면, 전압)을 산출한다. 화상을 저장하기 위해서는, 각 센서로부터의 아날로그 값을 디지털화 할 필요가 있다.

디지털화는 전형적으로 각 센서로부터의 아날로그 신호를 순차적으로 디지털화 하는 고속 아날로그-디지털 변환기(ADC)로 실행된다. 획득된 각 화상에 의해 생산되는 많은 양의 데이터 때문에 화상 어레이 내의 다수의 센서가 생기게 된다. 그러므로, 대부분의 화상 장치를 위해, 보다 쉽게 저장 및 전송하도록 화상을 디지털화 하여 일종의 데이터 압축 형태(scheme)를 사용한다.

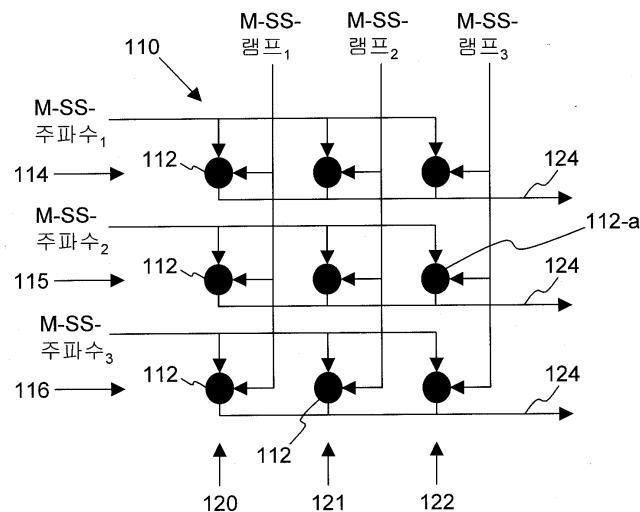

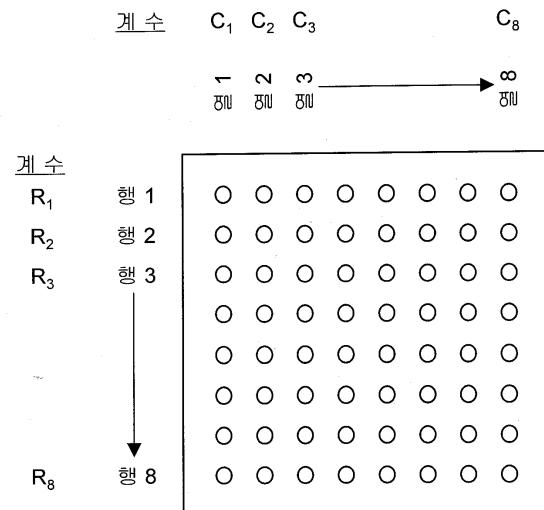

분리 가능 2-D 변형(separable 2-D transforms)은 보통 상대적으로 쉽게 이행할 수 있기 때문에(분리 가능하기 때문에) 데이터 압축을 사용한다. JPEG 및 MPEG는 분리 가능 2-D 변형을 사용하는 화상 데이터 압축 기술의 예이다. 도 1은  $8 \times 8$  픽셀 어레이를 나타내고 분리 가능 2-D 변형을 수반하는 다소의 기본 개념을 설명한다. 분리 가능 2-D 변형에 있어서, 각 행 및 각 열로부터의 디지털 값은 기산정된 디지털 계수( $R_1, R_2, \dots, R_8; C_1, C_2, \dots, C_8$ )에 승산 된다. 이런 식으로, 각 픽셀 값은 숫자  $R_i C_j$ 에 승산 되고, 여기서  $i$ 와  $j$ 는 1과 8 사이의 정수이다. 계산 및 분리 가능 2-D 변형은 신호 처리과정의 본 기술분야에 공지되어 있다. 서로 다른 많은 종류의 분리 가능 2-D 변형이 존재한다. 분리 가능 2-D 변형을 포함하는 많은 데이터 압축 기술은 다수의 디지털화 픽셀 값에 기인하여 실행되는 다수의 산술 승산을 요구한다. 도 1의  $8 \times 8$  픽셀 어레이는 전형적으로 수많은 픽셀을 가진 보다 큰 픽셀 어레이의 단지 작은 블록인 것을 유념하여야 한다.

이 승산(예를 들면, 디지털 카메라에 있어서)을 실행하기 위한 현재의 접근법은 디지털 승산을 실행하기 위해 전용 디지털 신호 처리기로 디지털 픽셀 값을 출력하는 것이다. 이것은 상대적으로 고비용의 처리 칩을 요구하고 약간의 전력을 소비하기 때문에 문제점이 있다.

디지털화 전의 아날로그 값에 의해 직접적으로 승산을 실행하는 논문에서 제안되는 다른 방식의 접근법은 가변의 스텝 크기 양자화(디지털화)로 이해된다. 이 접근법은 큰 실리콘 영역 및 전력을 요구하고 이행하기 어려운 아주 복잡한 아날로그 처리 및 아날로그 메모리를 요구하기 때문에 바람직하지 못하다. 보다 많은 정보를 위해, 1997년 2월, CA 샌프란시스코, 기술 논문의 ISSCC 요람(ISSCC Digest of Technical Papers), S. 카와히토 등에 의해 쓰여진 "아날로그 2-D 분리 코사인 변형 처리기 및 ADC/양자화를 사용하는 압축된 디지털 출력 CMOS 센서"를 참조한다.

파우리 등의 미국 특허 5,801,657은 픽셀 레벨에서의 아날로그-디지털 변환(ADC) 실행 장치 및 방법을 설명한다. 다시 말해서, 각 픽셀은 간단한 ADC를 가지고 있다. 각 ADC는 센서 어레이의 바깥쪽 구동 회로로부터 조회 신호(inquiry signal)를 수신한다. 일 구동 회로는 오직 완전한 어레이를 필요로 한다. 디지털 픽셀 값은 연속적으로 출력된다. 이 방법은 다중 채널 비트 직렬(MCBS) 아날로그-디지털 변환으로 불리어진다. 단일 채널 버전의 MCBS는 비트 직렬 ADC로 불리어진다. MCBS ADC는 화상 획득에 적절한 많은 장점을 가지고 있지만, 디지털 승산을 제공하지 않는다. 분리 가능 2-D 변형이 MCBS-디지털화 화상으로 실행될 수 있다면, 추가적인 디지털 신호 처리기가 요구된다. 이것은 화상 장치의 비용 및 전력을 증가시킨다.

그러므로, 분리 가능 디지털 신호 처리기를 요구함이 없이 일련의 디지털화 값으로 승산을 실행할 수 있게 하는 것이 바람직 할 것이다.

또한, MCBS ADCs는 많은 장점을 가지고 있으므로, MCBS 하드웨어 및 앞에 설명된 방법을 사용하여 승산을 실행하는 것이 바람직 할 것이다.

### MCBS ADC 동작의 요약

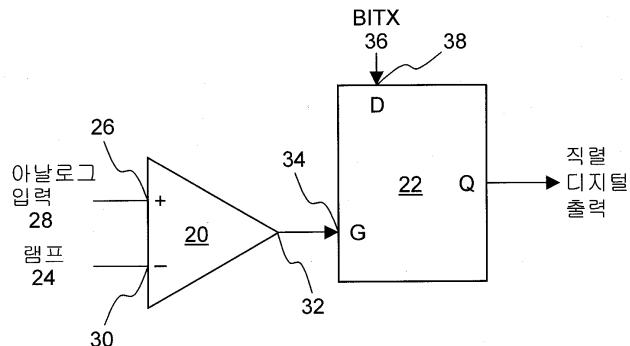

도 2는 파우리 등의 미국 특허 5,801,657에 따른 단일 채널 비트 직렬 ADC를 도시한다.

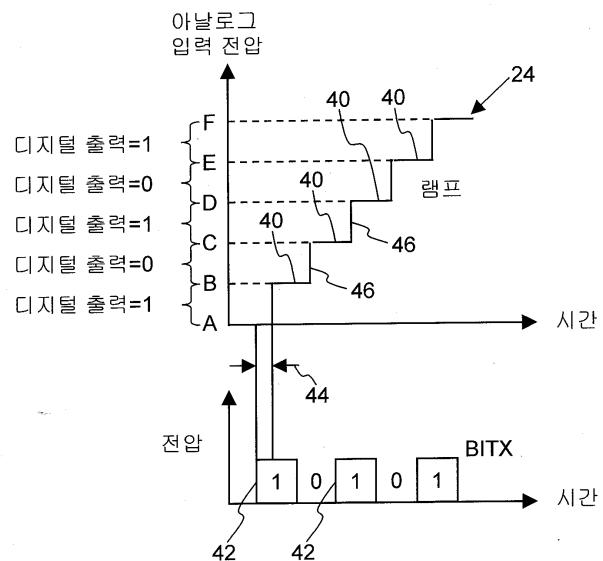

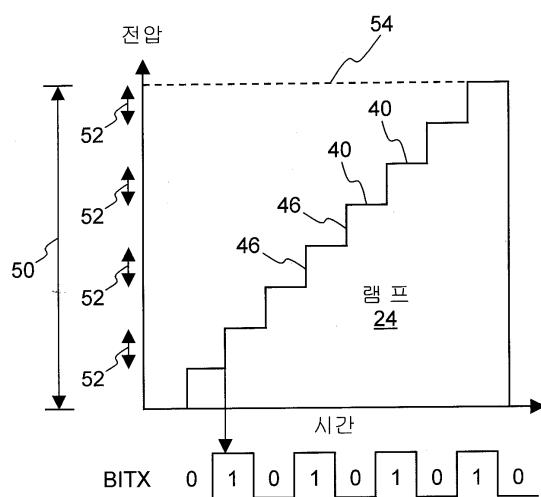

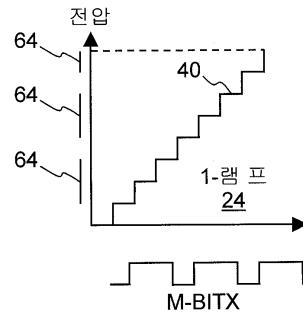

단일 채널 비트 직렬 ADC는 비교기(20)와 1-비트 래치(latch)(22)를 포함한다. 비교기의 출력(32)은 래치 게이트 입력(34)에 연결된다. 단조롭게 증가하는 계단스텝 램프 신호(24)는 비교기 반전 입력(30)에 입력되고 디지털화하기 위한 아날로그 값(전원)(28)은 비교기 비 반전 입력(26)에 입력된다. 그러므로, 램프(24)가 아날로그 전원(28)을 초과하면, 비교기의 출력(32)은 로우(low)가 된다. 비교기 출력은 래치(22)의 게이트(34)에 입력된다. BITX(36)는 래치(22)의 데이터 입력(38)에 입력된다. 그러므로, 램프 신호가 아날로그 전압(28)을 초과하면, 래치(22)는 BITX 값은 래치한다. 래치된 BITX 값은 직렬 디지털 출력에 제공된다.

도 3은 램프 및 BITX 신호 사이의 상호작용을 설명하는 도면이다. 램프(24)는 기 결정된 전압 레벨(40) 및 전압 스텝(46)을 가진 계단식 파형이다. BITX는 방형파이다. BITX는 BITX 천이(transition)(42) 및 램프 전압 스텝(46) 사이의 지연(44)을 위하여 시간을 지정한 천이(42)를 가진다. 비교기가 상태를 바꾸기 전에 지연(44)은 래치에 준비 시간을 제공한다.

원했던 디지털 값(0 또는 1)은 A-B, B-C, C-D, D-E 및 E-F와 같이 도시된 기 결정 아날로그 전압 범위와 관련되므로 램프와 BITX를 함께 설계된다. 전압 범위는 램프 신호의 전압 스텝(46)에 의해 결정된다.

도 4는 도3의 램프 및 BITX 신호에 대한 양자화 표를 나타낸다. 전압 범위와 관련된 디지털 출력은 변경된 BITX에 의해 변화된다.

비트 직렬 ADC 기술은 정밀한 비트를 다중화 시키기 위해 아날로그 값을 디지털화 하도록 사용될 수 있다. 비트는 연속적으로 출력된다. 비트는 원하는 순서로 출력될 수 있으며, 예를 들면, 최상위 비트(MSB)가 먼저 나오거나 또는 최하위 비트(LSB)가 먼저 나올 수 있다. 별개의 램프 과정은 정밀한 각 비트가 요구된다. 데이터는 각 램프 과정 사이의 래치 출력으로부터 출력된다. 램프의 전압 레벨(40)과 BITX의 패턴은 원하는 임의의 양자화 표를 출력하도록 변화될 수 있다. 예를 들면, 그레이 코드(gray code)는 적당하게 설계된 BITX 및 램프에 의해 출력된다.

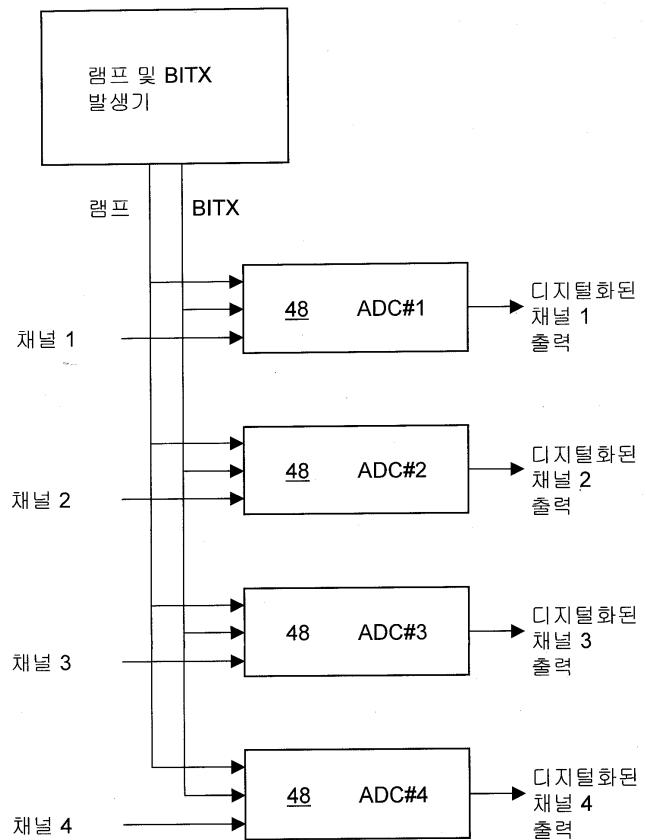

비트 직렬 ADCs의 뛰어난 장점중의 하나는 분리 가능 ADC가 다중 채널 비트 직렬(MCBS) ADC를 형성하기 위해 병렬로 동작될 수 있다는 것이다. 이것은 도 5에 도시되었다. 램프 및 BITX를 발생시키는 회로소자는 동일 램프 및 BITX를 모든 ADCs(48)에 전달한다. 각 ADC에 대한 하드웨어는 실제로 다루기 용이하므로, 많은 ADCs(예를 들면, 다수의)는 병렬로 동작할 수 있다. 이 특징은 MCBS ADC 특히 다수의 아날로그 값을 디지털화 하여야 하는 애플리케이션에 유용하다. 이 상태는 예를 들면, 화상 센서로부터의 아날로그 신호를 디지털화 하여 발생된다. 화상 센서에 있어서, 단일 ADC는 각 픽셀 또는 작은 그룹의 픽셀을 제공할 수 있다.

### 발명이 이루고자 하는 기술적 과제

따라서, 본 발명의 주요한 목적은:

- 1) 다중-채널 비트 직렬 아날로그-디지털 변환 방법 및 하드웨어를 완전히 호환할 수 있는 디지털 승산 실행방법을 제공하는 데 있다.

- 2) 기존의 MCBS 회로소자에 부가되는 추가적인 하드웨어를 요구하지 않는 디지털 승산 실행방법을 제공하는 데 있다.

- 3) 2 개의 독립적으로 조절 가능한 계수에 의해 각 디지털 값을 승산하기 위해 사용되는 디지털 승산 실행방법을 제공하는 데 있다.

- 4) 정확히 결정된 계수에 의해 승산 되도록 프로그램화되는 디지털 승산 실행방법을 제공하는 데 있다.

- 5) 화상 데이터 압축을 위한 분리 가능 2-D 변형, 컨벌루션(convolution) 및 필터링을 실행하도록 사용되는 디지털 승산 실행방법을 제공하는 데 있다.

- 6) 다수의 병렬 아날로그 신호가 계수에 의해 디지털화 및 승산 되는 임의의 상황에서 사용되는 디지털 승산 실행방법을 제공하는 데 있다.

- 7) 아날로그-디지털 변환 및 디지털 승산이 실행되는 임의의 상황에서 사용되는 디지털 승산 실행방법을 제공하는 데 있다.

또한, 본 발명은 목적은 단일 기울기 아날로그-디지털 변환기에서의 동시 아날로그-디지털 변환 및 승산 실행방법을 제공하는 데 있다.

이것과 다른 목적 및 장점들은 다음 상세한 설명 및 첨부된 도면을 읽으면 명백해 질 것이다.

상기 목적 및 장점들은 비트 직렬 ADC에 공급되는 램프 및 BITX 신호를 변경함으로써 달성된다. 램프 신호를 변경하는 것은 계수에 의한 디지털 출력의 승산의 결과로서 생길 수 있고, BITX 신호를 변경하는 것은 제 2 계수에 의한 디지털 출력의 승산의 결과로서 생길 수 있다.

M-램프 및 M-BITX는 승산을 제공하는 램프 및 BITX 신호를 나타내기 위해 사용되는 일반 용어이다.

승산을 제공하지 않는 1-램프 신호가 있다. 램프를 사용하는 X의 인수에 의한 승산은 1-램프 신호의 전압 레벨과 다른 1/X의 인수만큼의 전압 레벨을 가지는 M-램프 신호를 발생시킴으로써 이루어진다. M-램프 신호는 그리고 나서 비트 직렬 ADC의 비교기 입력에 적용된다.

비 승산을 제공하는 주파수  $F_0$ 을 가진 1-BITX 신호가 있다. BITX를 통해 승산을 제공함에 있어서, M-BITX 신호는 평균 주파수에 근접한  $XF_0$ 을 구비하여 제공된다. M-BITX 신호는 주파수  $KF_0/N$  및 주파수  $KF_0/N+1$ 의 선택적인 세그먼트 (alternating segments)를 포함하고, 여기에서 N은 양의 정수이고, K는 정수이다. M-BITX 신호는 그리고 나서 비트 직렬 ADC의 데이터 입력에 적용된다.  $K=1$ 인 경우, 램프 신호도 변경되어야 한다.

바람직하게는,  $K=2^D$ 이고, 여기에서 D는 1/X의 소수부를 나타내기 위해 사용되는 2진 비트 수이다. 바람직하게는,  $N \leq (K/X) < N+1$ 이 되도록 N을 선택한다.

또한 바람직하게는, M-BITX의 평균 주파수는  $XF_0$ 에 근접한다. 예를 들면, M-BITX의 평균 주파수는  $1/2^n$ 의 인수 내에서  $XF_0$ 과 가급적 일치시키고, 여기에서 n은 아날로그-디지털 변환에 대한 희망 해상도(resolution)의 비트 수이다. 선택적으로, M-BITX의 평균 주파수는  $XF_0$ 의 5% 또는 10% 범위 내이다.

본 발명은 또한 '격자에 대한 스냅(snap to grid)' 지표를 가진 M-램프 생성 방법을 포함한다. 상기 방법은 관계:

$$N + \frac{A}{B} \approx \frac{K}{X}$$

에 따른 N, A 및 B를 선택하기 시작한다. N 및 K는 정수이다. K는 격자 밀도 인자이다. 값 A는  $2KF_0$ 의 주파수에서 제 1 실행 합계(first running sum)에 더해진다. 제 1 실행 합계는 누산기(accumulator)로 생성된다. A가 더해진 후에 실행 합계가 값 B에 롤오버(roll over)되지 않으면 값 N을 가진 값 A 디지털 수가 생산된다. A가 더해진 후에 실행 합계가 값 B에 롤오버 되지 않으면 디지털 수는 값  $N+1$ 을 가진다. 생산되는 일련의 디지털 수는  $2KF_0$ 의 비율로 제 2 실행 합계에 더해진다. 제 2 실행 합계는 디지털-아날로그 변환기(DAC)로 전송된다. DAC의 출력은 희망 M-램프 신호이다. 바람직하게, N은  $N \leq (K/X) < N+1$ (즉, N은 가급적 K/X의 정수부)이 되도록 선택된다. 또한 바람직하게, N + A/B는 K/X 값과 아주 근접된다. 본 발명은 N, A 및 B를 선택하기 위한 알고리즘(algorithms)을 포함한다.

본 발명은 또한 격자에 대한 스냅 지표를 가진 M-BITX를 생성하기 위한 유사 방법을 포함한다. 상기 방법은 관계:

$$N + \frac{A}{B} \approx \frac{K}{X}$$

에 따른 N, A 및 B를 선택하기 시작한다. N 및 K는 정수이다. K는 격자 밀도 인자이다. 값 A는 실행 합계(running sum)에 더해진다. 실행 합계는 예를 들면, 누산기(accumulator)로 생성된다. A가 더해진 후에 실행 합계가 값 B에 롤오버 되지 않으면 주파수  $KF_0/N$ 을 가진 다음 방형파 신호가 생산된다. A가 더해진 후에 실행 합계가 값 B에 롤오버 되지 않으면 방형파 신호는 주파수  $KF_0/(N+1)$ 을 가진다. 값 A는 방형파 신호의 모든 예지 천이(edge transition) 후에 실행 합계에 더해진다. 방형파 신호는 X 인자에 의한 승산을 제공하는 희망 M-BITX 신호이다. 바람직하게, N은  $N \leq (K/X) < N+1$ (즉, N은 가급적 K/X의 정수부)이 되도록 선택된다. 또한 바람직하게, N + A/B는 K/X 값과 아주 근접된다. 본 발명은 N, A 및 B를 선택하기 위한 알고리즘을 포함한다.

본 발명은 또한 M-램프 발생 장치를 포함한다. 상기 장치는 제 1 실행 합계를 생성하기 위한 제 1 누산기를 가진다. 제 1 누산기는 커패시티 B를 가진다. 값 A는  $2KF_0$  주파수에서 제 1 실행 합계에 더해진다. 값 N, A 및 B는 관계:

$$N + \frac{A}{B} \approx \frac{K}{X}$$

에 따라 선택되고, 여기에서 N은 정수이고 K는 격자 밀도 인자이다. 상기 장치는 또한 수 선택자(number selector)를 가진다. A가 더해진 후에 실행 합계가 커페시티 B에 룰오버 되지 않으면 수 선택자는 디지털 수 N을 제공한다. A가 더해진 후에 실행 합계가 커페시티 B에 룰오버 되지 않으면 수 선택자는 디지털 수 N+1을 제공한다. 수 선택자는 2KF<sub>0</sub>주파수에서 디지털 수를 제공한다. 상기 장치는 또한 제 2 실행 합계에 디지털 수를 합산하기 위한 제 2 누산기를 가진다. 상기 장치는 제 2 실행 합계를 아날로그 값으로 변환하기 위한 디지털-아날로그 변환기(DAC)를 더 가진다. DAC에 의해 제공된 아날로그 값은 X 인자에 의해 승산을 제공하는 희망 M-램프 신호를 포함한다. 상기 장치는 누산기 및 DAC가 정확한 주파수에서 동작할 것을 보장하기 위한 클럭(clock)을 더 포함할 수 있다.

본 발명은 또한 격자에 대한 스냅 지표를 가진 M-BITX 발생 장치를 포함한다. 상기 장치는 누산기 내의 실행 합계에 값 A를 합산하기 위한 누산기를 가진다. 상기 누산기는 커페시티 B를 가진다. 값 N, A 및 B는 관계:

$$N + \frac{A}{B} \approx \frac{K}{X}$$

에 따라 선택되고, 여기에서 N은 정수이고 K는 격자 밀도 인자이다. 상기 장치는 또한 누산기와 통신하는 방형파 주파수 발생기를 가진다. A가 실행 합계에 더해진 후에 실행 합계가 커페시티 B에 룰오버 되지 않으면 주파수 발생기는 주파수 KF<sub>0</sub>/N을 발생시킨다. A가 실행 합계에 더해진 후에 실행 합계가 커페시티 B에 룰오버되지 않으면 주파수 발생기는 주파수 KF<sub>0</sub>/(N+1)을 발생시킨다. 누산기는 방형파 주파수 발생기 출력의 예지 천이 후에 실행 합계에 A를 합산하다. 주파수 발생기 출력은 X 인자에 의해 승산을 제공하는 희망 M-BITX 신호이다. 바람직하게, 방형파 주파수 발생기는 N 또는 N+1을 선택할 수 있는 모듈을 가지는 주파수 분할기(frequency divider)와 통신하는 주파수 KF<sub>0</sub>을 제공하는 클럭을 포함한다.

본 발명은 또한 화상 획득 장치 및 화상 압축/필터링 장치를 포함한다. 상기 장치는 아날로그 신호를 생산하기 위한 광 검출기의 어레이를 가진다. 광 검출기는 행 및 열로 배열된다. 상기 장치는 광 검출기와 통신하는 비트 직렬 아날로그-디지털 변환기(ADCs)를 가진다. 상기 장치는 서로 다른 계수에 의해 승산을 제공하는 다수의 서로 다른 M-램프 신호를 생성하기 위한 M-램프 발생기를 가진다. 상기 장치는 서로 다른 계수에 의해 승산을 제공하는 다수의 서로 다른 M-BITX 신호를 생성하기 위한 M-BITX 발생기를 가진다. 상기 장치는 서로 다른 M-램프 신호에 서로 다른 열을 제공하고, 서로 다른 M-BITX 신호에 서로 다른 행을 제공하기 위한 회로소자를 가진다. 회로소자는 예를 들면, 스위치 행렬(switch matrix)을 포함한다. M-램프 및 M-BITX 발생기는 서로 다른 M-램프 및 M-BITX 신호의 디자인상에 정보를 저장하는 조사표(look-up tables)를 포함할 수 있다. 또한, M-램프 및 M-BITX 발생기는 분주-N 위상 동기 루프를 포함할 수 있다. 본 발명의 행 및 열은 교환할 수 있다는 것은 자명하다. 그러므로, 서로 다른 행에 제공되는 M-램프와 서로 다른 열에 제공되는 M-BITX를 가진 장치는 충분히 청구된 발명의 범위 내이다. 또한 행 및 열은 6각형 어레이, 또는 방사 어레이 또는 픽셀로 될 수 있다는 것은 자명하다.

본 발명은 또한 단일 기울기 ADC의 X 인자에 의해 동시 A/D 변환 및 승산 실행 방법을 포함한다. 상기 방법은 1/X 인자에 의해 단일 기울기 ADC에 사용되는 단일 기울기 램프(SS-램프) 신호의 전압/시간 기울기를 변화시키는 단계를 가진다.

본 발명은 또한 단일 기울기 ADC의 X 인자에 의해 동시 A/D 변환 및 승산 실행하기 위한 제 2방법을 포함한다. 상기 방법은 X 인자에 의해 단일 기울기 ADC에 사용되는 단일 기울기 주파수(SS-주파수) 신호의 전압/시간 기울기를 변화시키는 단계를 가진다.

본 발명은 또한 동시 아날로그-디지털 변환을 실행하고, 비트 직렬 ADCs와 통신하는 화상 광 검출기 어레이의 압축/필터링 하기 위한 방법을 포함한다. 서로 다른 M-BITX 신호는 주어진 행에서의 광 검출기로부터의 디지털 값이 동일 계수에 의해 승산 되도록 서로 다른 행에 제공된다. 서로 다른 M-램프 신호는 주어진 열에서의 광 검출기로부터의 디지털 값이 동일 계수에 의해 승산 되도록 서로 다른 열에 제공된다. 그러므로, 어레이 내의 각 광 검출기로부터의 각 디지털 값은 어레이에서의 광 검출기의 위치에 의해 결정된 2개의 계수에 의해 승산 된다. 본 발명은 어레이 내의 작은 블록에 적용된다. 비트 직렬 ADCs는 광 검출기 어레이 상에 위치시킬 수 있고, 분리 가능 칩 상에 위치시킬 수 있다.

본 발명은 또한 동시 아날로그-디지털 변환을 실행하고, 단일 기울기 ADCs와 통신하는 화상 광 검출기 어레이의 압축/필터링 하기 위한 방법을 포함한다. 서로 다른 승산 SS-주파수 신호(M-SS-주파수)는 주어진 행에서의 광 검출기로부터의 디지털 값이 동일 계수에 의해 승산 되도록 서로 다른 행에 제공된다. 서로 다른 승산 SS-램프 신호(M-SS-램프)는 주어

진 열에서의 광 검출기로부터의 디지털 값이 동일 계수에 의해 승산 되도록 서로 다른 열에 제공된다. 그러므로, 어레이 내의 각 광 검출기로부터의 각 디지털 값은 어레이 내의 광 검출기의 위치에 의해 결정된 2개의 계수에 의해 승산 된다. 본 발명은 어레이 내의 작은 블록에 적용된다. 단일 기울기 ADCs는 광 검출기 어레이 상에 위치시킬 수 있고, 분리 가능 칩 상에 위치시킬 수 있다.

### 발명의 구성

본 발명은 A/D 변환과 동시에 승산을 실행하는 방법을 설명한다. 설명된 모든 실시예에 있어서, 승산 계수는 1미만인 것이 바람직하다. 이것은 디지털화 되는 아날로그 신호가 ADC의 전체 동적 범위에 위치한다고 가정하였기 때문이다. 아날로그 신호가 ADC의 전체 동적 범위에 위치하지 않으면, 1보다 큰 계수에 의해 승산이 가능해진다.

계수의 세트가 표준화되었기 때문에 1보다 큰 계수는 대부분의 데이터 압축 애플리케이션에 요구되지 않는다.

본 발명은 두 개의 독립 계수에 의해 디지털 출력을 승산하기 위한 각 비트 직렬 ADC에 대한 방법을 제공한다. 일 계수는 적절히 변경된 램프(24) 과형에 의해 결정되고, 다른 계수는 적절히 변경된 BITX(36) 과형에 의해 결정된다. 램프(24) 과형을 통한 승산은 개념적으로 간단하므로 먼저 설명한다.

### 램프를 통한 승산

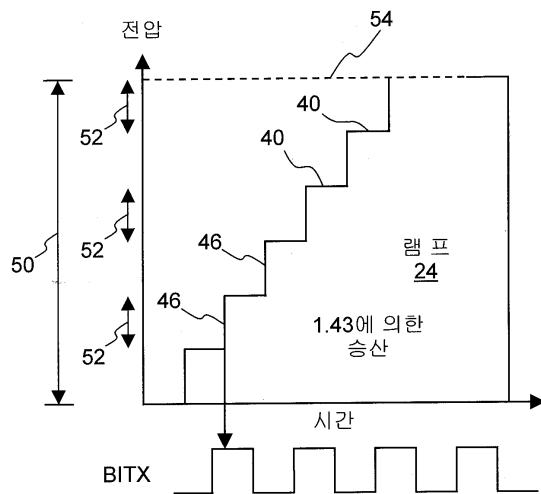

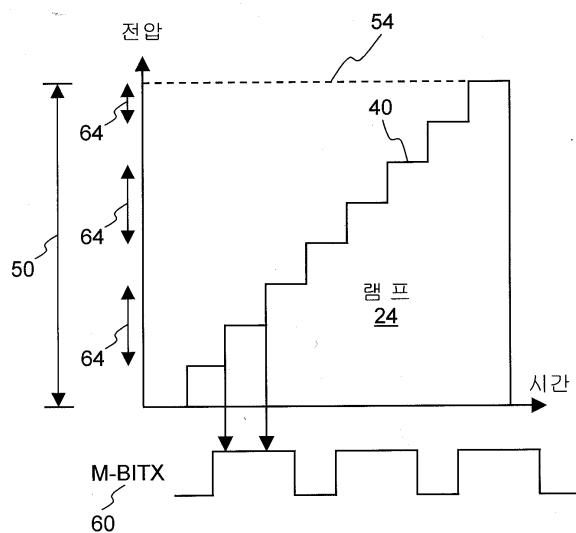

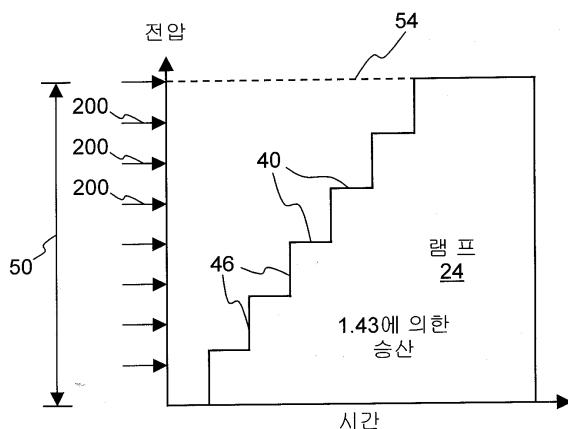

도 6은 비 승산을 제공하는(즉, 1의 인자에 의한 승산) 1-램프 신호(24)를 도시한다. 아날로그 입력의 입력 범위(50)가 또한 도시되고, 최대 아날로그 전압 레벨(50)을 규정한다. 1-램프 신호(24)는 아날로그 입력으로서 동일 입력 범위(50)를 가진다. 전압 범위(52)는 디지털 출력이 1(출력 하이)이 되는 아날로그 입력 전압을 표시한다. 전압 범위(52)는 BITX가 1일 때 발생하는 전압 스텝(46)과 일치한다. 1-램프 신호(24)는 램프 신호가 승산 없이 아날로그-디지털 변환을 제공할 때 정의된다.

램프를 통한 승산은 희망 승산 계수의 반전에 의해 1-램프의 전압 레벨(40)을 승산 함으로써 달성된다. BITX는 영향을 받지 않는다. 승산을 제공하는 램프 신호는 M-램프 신호로 불리어진다. X에 의한 승산에 관하여, 전압 레벨(40)은  $1/X$ 에 의해 승산 된다. 예를 들면, 계수 0.7에 의해 비트 직렬 ADC의 디지털 출력을 승산하기 위해, 1-램프 전압 레벨은 1.43(즉,  $1/0.7$ )에 의해 승산 된다. 도 7은 0.7에 의한 승산에 관한 0.7M-램프 신호를 생산하기 위해 1.43에 의해 승산된 1-램프 신호(24)를 도시한다. 0.7M-램프 신호는 최대 아날로그 전압(54)에서 계산과정이 종결된다. 1-램프에서 0.7M-램프로의 변화는 1의 디지털 출력에 의해 생긴 아날로그 입력에 대한 전압 범위(52)로 증가한다. 그러므로, 아날로그 입력은 동일 디지털 출력을 생성하기 위하여 균형적으로 보다 큰 전압을 가져야 한다. 그러므로, 디지털 승산(1미만의 계수에 의한)은 전압 레벨(40)의 전압을 증가함으로써 달성된다.

1보다 큰 계수에 의한 승산은 전압 레벨(40)의 전압을 감소함으로써 달성되고, 승산하지 않으면, 1-램프의 범위(50)는 아날로그 입력의 동적 범위보다 크다.

다중 비트에 대한 승산은 동일 계수에 의해 모든 1-램프 과형(MSB에서 LSB까지)의 전압 레벨(40)을 간단히 승산 함으로써 달성된다.

### BITX를 통한 승산

BITX는 승산을 제공하거나 비 승산을 제공할 수 있다. 다음 설명에 있어서, 비 승산을 제공하는 BITX 과형은 1-BITX로 일컬어지고; 승산을 제공하는 BITX 과형은 M-BITX로 일컬어진다. 1-BITX는  $F_0$ 의 주파수를 가진 방형파이다.

BITX에 의한 승산을 위해, 어떤 경우에(즉, 기준 클럭이 기준 주파수  $F_0$ 보다 빠르게 실행되고 격자 밀도 인자 K가 1보다 클 경우) 램프의 변화가 또한 요구된다. 그렇지만, 클럭이  $F_0$ 보다 빠를 때, 램프의 변화는 램프에 의한 승산을 제공하기 위해 사용되는 전압 레벨의 변화와는 관계없다. 그러므로, 본 발명은 두 개의 독립 계수에 의해 비트 직렬 ADC의 출력을 승산하기 위한 방법을 제공하며; 일 계수는 램프의 디자인에 의해 정해지고, 다른 계수는 BITX의 디자인에 의해 정해진다. 이 논점들은 보다 상세하게 아래에 설명된다.

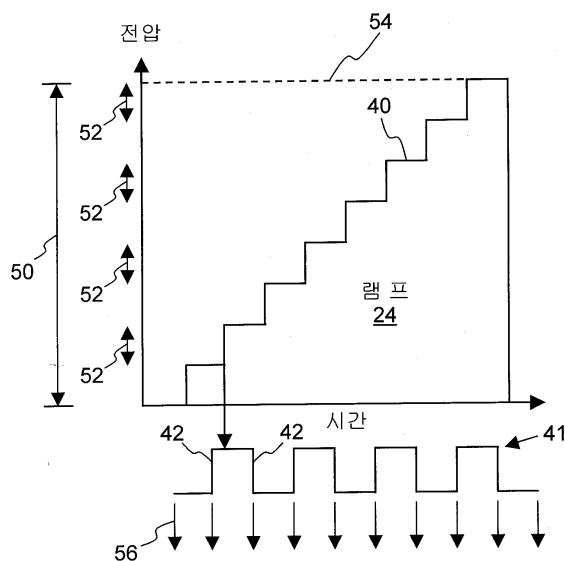

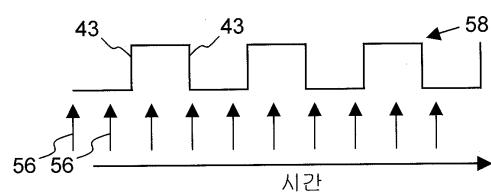

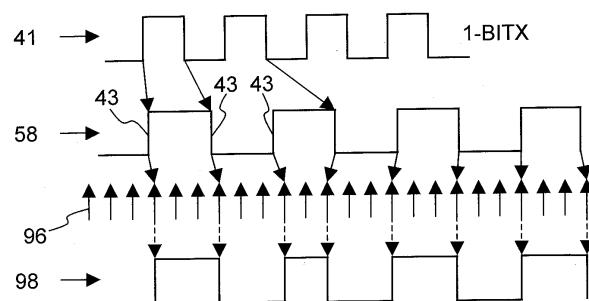

도 8은 비 승산을 제공하는 전형적인 램프 및 1-BITX(41) 파형을 도시한다. 1-BITX 신호(41)는 정기적으로 일정한 간격이 유지된 에지 천이(42)를 가진다. 램프는 각 램프 전압 스텝에 대한 일 시간 위치를 가진 일련의 시간 위치(56)를 확립한다. 1-BITX는 주파수  $F_0$ 을 가진다. 일련의 시간 위치는 주파수  $2F_0$ 을 가진다.

BITX를 사용하는 X의 인자에 의한 승산은  $XF_0$ 의 평균 주파수(긴 시간 주기에 대하여 측정될 때의 평균)를 가진 M-BITX(승산한 BITX 신호)를 생산함으로써 이루어진다. 전형적으로, X는 1미만이 되도록 표준화되므로 M-BITX는 1-BITX보다 늦은 주파수를 가진다. 그렇지만, M-BITX는  $1/X$ 가 정수가 아니면 일정한 주파수  $XF_0$ 에서 신호를 만들 수 없다. 이것은 유용한 M-BITX 신호가 시간 위치(56)와 동시에 에지 천이를 가져야 하기 때문이다. 주파수  $XF_0$ 을 가진 방형파는  $1/X$ 가 정수일 경우에만 시간 위치(56)와 동시에 에지 천이를 가질 것이다.

도 9에 도시된 주파수  $0.7F_0$ (58)의 방형파에 대해 살펴본다.  $1/0.7=1.43$ 이고 1.43은 정수가 아니므로, 천이 예지(43)는 임의의 시간 위치(56)와 동기하지 않는다.

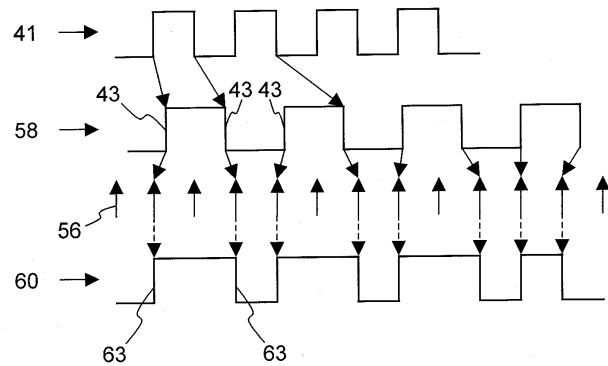

그렇지만, M-BITX 신호를 사용하는 0.7에 근접한 인자에 의한 승산은 여전히 가능하다. 도 10은 0.7에 의한 승산을 제공하는  $0.7M$ -BITX 신호(60)의 디자인을 설명한다. 주파수  $F_0$ 에서의 최초 1-BITX 신호(41)가 도시된다. 램프(24)는 시간 위치(56)를 확립한다. 일정한 주파수  $0.7F_0$ (58)의 방형파는 시간 위치(56)와 동기되는 천이 예지(43)를 가지지 않기 때문에 M-BITX 신호와 같이 사용되지 않는다. 0.7의 인자에 의해 승산을 제공하는 유용한  $0.7M$ -BITX는 '격자에 대한 스냅' 기술에 따른 가장 근접한 시간 위치(56)에 방형파(58)의 천이 예지를 위치시킴으로써 설계된다. 합성  $0.7M$ -BITX 신호(60)는 주파수  $F_0$  및 주파수  $0.5F_0$ 의 선택적인 세그먼트(alternating segments)로 이루어진다. 보다 상세하게는, 합성  $0.7M$ -BITX 신호는 시간의 40% 주파수  $F_0$ 과 시간의 60% 주파수  $0.5F_0$ 을 가진다( $0.5(0.6)+1.0(0.4)=0.7$ 이므로). '격자에 대한 스냅' 기술에 의해 생산된  $0.7M$ -BITX의 평균 주파수는  $0.7F_0$ 이다. 긴 시간 간격에 대하여 측정될 때, M-BITX의 평균 주파수(60)는  $0.7F_0$ 이다.

도 11은 도 8의 최초 램프 신호와 제휴하는  $0.7M$ -BITX(60)를 도시한다. 범위(64)는 ADC가 출력 1이 되기 위한 전압을 나타낸다. 범위(64)는 전압이 증가되고 도 7의 범위(52)와 비교하여 '보다 넓게(wider)' 된다( $0.7M$ -BITX의 평균 주파수 보다 느리기 때문에). 그러므로, 입력 아날로그 전압은 동일 디지털 출력을 생산하기 위해 높아야 한다. 그러므로 1미만의 수에 의한 승산은  $0.7M$ -BITX(60)를 사용함으로써 제공된다. 이런 특수한 경우에 있어서, 범위(64)는 반드시 0.7에 의한 승산을 정확히 하기 위한 것은 아님에 유의하여야 한다. 그렇지만, 도 11은 승산이 M-BITX의 주파수를 변화함으로써 가능하다는 것을 설명하기에 아주 도움이 된다. 아래에 설명된 본 방법의 보다 좋은 실시예는 M-BITX를 사용하여 승산의 정확성을 증가시키는 방법을 깨닫게 한다.

보다 큰 전압 스텝(46)이 램프 신호에 있으면 승산이 보다 정확해진다.

'격자에 대한 스냅'(시간 위치(56)에 의해 정의된 격자)에 대한 상기 상세한 설명은 M-BITX가 승산 계수에 어떻게 의존하는지를 이해하도록 개념적으로 도와준다. 상기 상세한 설명은 M-BITX가 실제로 생성되는 방법을 설명할 필요가 없다. M-BITX는 방형파 신호(58)에 '격자에 대한 스냅' 동작을 실행하는 이산 장치를 사용하여 생성될 필요가 없다. 그렇지만, 임의의 유용한 M-BITX 신호는 '격자에 대한 스냅' 지표를 가져야 한다. '격자에 대한 스냅' 지표를 가진 M-BITX 신호를 생산하는 임의의 방법은 본 발명의 범위 내라는 것을 유의하여야 한다.

아래에 설명된 보다 좋은 실시예는 M-BITX가 임의의 승산 계수 X를 생성하는 방법을 설명한다.

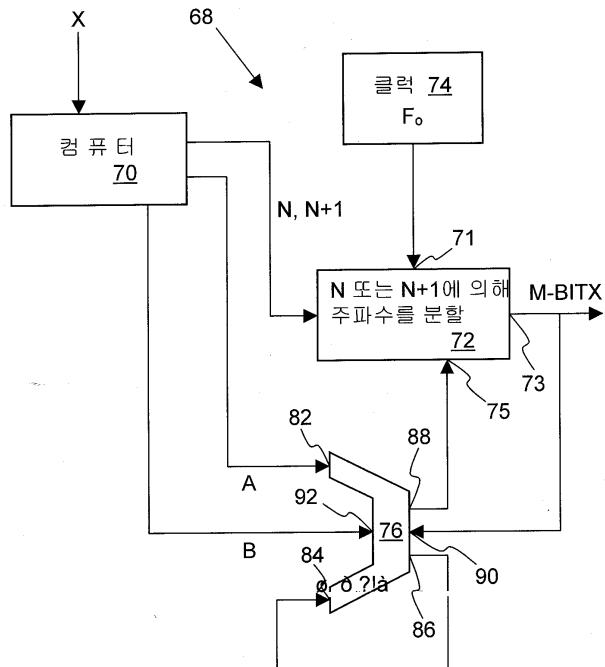

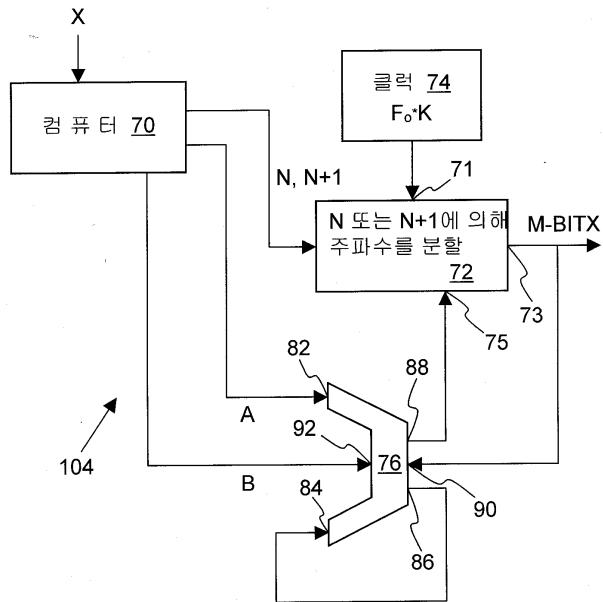

도 12는 '격자에 대한 스냅' 지표와 계수 X(상기 예에 있어서  $X=0.7$ )에 대한  $F_0X$ 의 평균 주파수, 기준 주파수  $F_0$ 을 가진 M-BITX 신호를 생성할 수 있는 회로(68)를 도시한다. M-BITX 생산 방법은 분주-N 위상 동기-루프 합성 기술과 유사하다. 분주-N PLL 합성에 관한 보다 많은 정보를 위해, 1996년 9월, 마이크로웨이브 저널, B.G 골드버그에 의한 "분주-N PLL 합성의 전개 및 완성"을 참조한다.

회로(68)는 컴퓨터(70), 주파수 분할기(72), 클럭(74) 및 누산기(76)(디지털 가산기)를 포함한다. 클럭(74)은 고정된 기준 주파수  $F_0$ 에서 방형파 신호가 발생되도록 정한다. 주파수 분할기는 입력(71), 출력(73) 및 모듈 제어(75)를 가진다. 누산기

(76)는 제 1 입력(82), 제 2 입력(84), 출력(86), 캐리 아웃(carry out)(88), 에지-감지 트리거(edge-sensitive trigger) (90) 및 커페시티 세트 입력(92)을 가진다.  $F_0$ 에서의 클럭 신호는 입력(71)에 연결된다. 캐리 아웃(88)은 모듈 제어(75)에 연결된다. 누산기의 출력(86)은 제 2 입력(84)에 연결된다.

승산 계수 X가 주어진 컴퓨터(70)는 관계:

$$N + \frac{A}{B} \approx \frac{K}{X}$$

에 기초하여 양 N, A 및 B를 결정한다.

$1/X$ 의 값에 근접한  $N + (A/B)$  값은 정확한 A/D 변환 및 승산을 제공한다. N은 정수이다.

일반적인 지침에 있어서, N은 보통  $1/X$ (예를 들면,  $1/X=3.43$ 에서  $N=3$ )의 정수부와 일치한다. 또한, A 및 B는 보통  $A/B$ 가  $(1/X)$ 의 소수부와 거의 일치하도록 선택된다. 예를 들면,  $1/X=3.43$ 이면, A 및 B는 보통  $A/B \approx 0.43$ 이 되도록 선택된다.

이하에는 주어진 계수 X의 N, A 및 B를 선택하기 위한 세 가지 유용한 알고리즘(알고리즘 1-3)을 설명한다.

N, A 및 B가 결정된 후에, 회로(68)는 다음 환경(settings)들을 가지고 형성된다:

1)값 1은 제 1 입력(82)에서 연속적으로 제공된다.

2)누산기의 커페시티는 B로 정한다.

3)주파수 분할기 모듈은 모듈 제어(75)에서의 신호에 의존하여, N 또는  $N + 1$ 이 되도록 정한다. 분할기의 모듈은 캐리 아웃(88)이 하이일 때(누산기 내의 실행 합계가 커페시티 B에 롤오버될 때)  $N + 1$ 이다.

4)누산기의 내부 상태는 0과  $B-1$  사이의 값으로 초기화된다. 바람직하게는, 누산기의 내부 상태는  $B/2$ 로 초기화된다.

이 환경들은 수동 또는 컴퓨터(70)에 의해 만들어지거나, 회로는 X가 회로(68)의 라이프(life)에 대해 일정하면 N, A 및 B의 일정한 값을 사용하여 영구적으로 정할 수 있다.

동작 중, 주파수  $F_0$ 은 주파수 분할기에 입력된다. 주파수 분할기는 출력(73)으로  $F_0/N$ 을 출력한다. 누산기는 제 1(82) 및 제 2(84) 입력에서의 디지털 수와 출력(73)에서 발생한 매시간 친이(하이에서 로우 또는 로우에서 하이)를 가산한다. 누산기 출력(86)은 제 2 입력(84)에 연결되므로, 실행 합계는 누산기(76) 내에서 발생된다. 누산기가 0의 값으로 초기화되면, 실행 합계는 연속적인 값 0, A, 2A, 3A, 4A 및 커페시티 B까지(즉, A는 주파수 분할기 출력(73)의 모든 친이와 함께 실행 합계에 가산된다)를 가진다. 누산기가  $1/2B$ 의 값으로 초기화되면, 실행 합계는 연속적인 값  $1/2B$ ,  $1/2B+A$ ,  $1/2B+2A$ ,  $1/2B+3A$  및 커페시티 B까지를 가진다. 실행 합계가 커페시티 B에 도달하면, 캐리 아웃(88)은 하이로 되고 주파수 분할기 모듈은  $N + 1$ 로 변경된다. 캐리 아웃(88)이 하이일 동안, 주파수 분할기는 주파수  $F_0/N + 1$ 을 출력한다. 그러므로, 주파수 분할기 출력은 주파수  $F_0/N$  및 주파수  $F_0/N + 1$ 의 선택적인 세그먼트를 제공한다.

선택적으로, 제 1 누산기는 모든 램프 신호가 발생된(즉, MCBS ADC에 의해 제공된 각 출력 비트에 대해) 후에 0과  $B-1$  사이의 기 결정된 값으로 리셋된다.

누산기는 실행 합계가 B를 초과할 때, 실행 합계의 값이 B를 초과하는 총계로 정해지는 것을 의미하는 B의 커페시티를 가진다. 커페시티 B는 '롤오버 된다'는 예를 들면, A=27이고 B=100에서, 실행 합계가 90의 값을 가지면, 다음 실행 합계 값은 17이다. 캐리 아웃이 하이가 되면, 실행 합계의 다음 값은  $27 + 17 = 44$ 이다. 17에서 44는 롤오버 동작을 포함하지 않으므로 캐리 아웃은 로우로 복귀한다.

주파수 분할기의 출력은 X의 인자에 의해 승산을 제공하는 희망 M-BITX 신호이다. 주파수 분할기 출력의 평균 주파수(긴 시간 간격에 의해 평균된)는  $F_0 X$ 이다. 회로에 의해 생성된 M-BITX 신호의 모든 친이는 클럭(74)에 의해 발생된 최초  $F_0$  신호의 친이와 동기된다. 그러므로, 회로에 의해 발생된 M-BITX 신호는 '격자에 대한 스냅' 지표를 가진다.

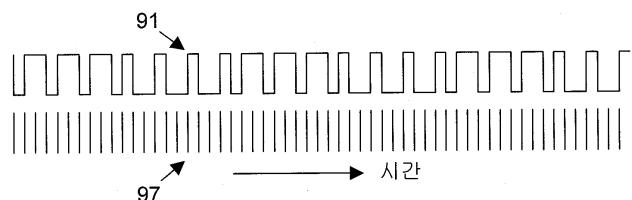

도 13은  $X=0.7$ 의 본 발명에 의해 생성된 M-BITX 신호(91)를 도시한다. 누산기는 0에서 초기화된다. 라인(97)은 주파수  $2F_0$ 의 '격자에 대한 스냅' 시간 위치를 나타낸다. 사용된 두 개의 주파수는  $F_0$  및  $1/2F_0$  ( $1 < 1.43 < 2$  이므로)이다. 주파수는 보통 모든 천이로 바꿔지므로, 서로 다른 주파수들은 '하이' 및 '로우' 상태의 서로 다른 시간으로 나타난다.

### N, A 및 B를 선택하기 위한 알고리즘 1-3

다음의 모든 알고리즘에 있어서,  $n$ 은 A/D 변환을 원하는 정밀도의 다수의 비트로 정의된다(예를 들면, 정밀도의 3비트가 A/D 변환을 원하면  $n=3$ ).

#### 알고리즘 1

이 예의 알고리즘에 있어서,

$N=1/X$ 의 정수부, 즉,  $N \leq 1/X < N+1$

$B=2^n$ , 및

$A=\text{버림}(\text{round})(B(\text{frac}(1/X)))$

여기에서 '버림(round)'은 '가장 가까운 정수로 라운드' 동작을 나타내고, 'frac'은 '소수부를 취함' 동작을 나타낸다.

#### 알고리즘 2

이 알고리즘은 전형적으로 가장 효과적이다. 아이디어는  $C$ 가 선택된 상수미만의 제약 조건을 가지고, 가능한 정확하게 분수  $B/C$ 로  $X$ 를 표현하는 것이다. 예를 들면, 제약 조건  $C < 2^n$ 이 사용된다. 그러면,  $N$ ,  $A$  및  $B$ 는  $N$ 이 정수인 제약 조건을 가진 표현:

$$\frac{B}{C} = N + \frac{A}{B}$$

으로부터 획득된다. 분수  $B/C$ 는 수 체계로서의 스텐-브로코트 트리(stern-brocot tree)를 사용하여 얻어진다. 분수  $B/C$ 를 찾기 위한 스텐-브로코트 트리를 사용하여 보다 많은 정보를 위하여, 그레이엄(Graham), 컨유드(Knuth) 및 파타쉬니크(Patashnik)에 의한 구체적인 수학(Concrete Mathematics), 페이지 118-122를 참조한다.

#### 알고리즘 3

이 알고리즘에 있어서,

$B=\text{round}(2^nX)$ , 여기에서 'round'은 '가장 가까운 정수로 라운드' 동작을 나타낸다,

$N=2^n/B$ 의 정수부 및

$A=2^n \bmod B$ , 여기에서 'mod'는 모듈 동작을 나타낸다.

알고리즘 3에 있어서,  $N$ 은  $1/X$ 의 정수부와 일치할 필요가 없다.

본 발명은 알고리즘 1-3에 한정되지 않는다.  $N + (A/B) \approx 1/X$ 가 되도록  $N$ ,  $A$  및  $B$ 를 찾기 위해 많은 기술들이 사용될 수 있다.

상기에 진술한 바와 같이, 정확한 A/D 변환을 위해,  $N+(A/B)$ 은  $1/X$ 에 근접하여야 한다. 즉, A/D 변환의 희망 비트 해상도에 의존하여 근접시키는 방법은  $n$ 에 의존한다. 최선의 결과를 위해,  $N+(A/B)$ 은  $1/X$ 의  $(1/2^n)$ 의 인자 내이어야 한다. 예를 들면,  $n=1$ (1비트 해상도 A/D 변환)에서,  $N+(A/B)$ 은  $1/X$ 의 50% 내이어야 한다.  $n=3$ 에서,  $N+(A/B)$ 은  $1/X$ 의 12.5% 내이어야 한다. 그렇지만, 이것은 일반적인 지침이고, 절대 요구조건은 아니다.

회로(68)에 의해 생산된 M-BITX 신호는 상대적으로 불명확한 디지털 출력의 승산의 결과로서 생긴다. 이 불명확의 이유는 시간 위치(56)의 '격자'가 상대적으로 조잡하고 상대적으로 전압 스텝(46)의 작은 수만 있기 때문이다. 각 전압 스텝은 1 또는 0의 출력 값과 관련되어야 한다. 램프 신호 내의 상대적으로 적은 전압 스텝(46)이면, 출력은 높은 정확성을 가질 수 없다. 그러므로, 램프 신호에 전압 스텝(46)을 더 추가하는 것은 보다 높은 승산 정확성을 가진 출력을 제공할 수 있다. 그렇지만, 보다 많은 전압 스텝 이외에 시간 위치(56)에 의해 형성된 격자가 보다 많은 시간 위치를 가진다면(즉, 단위 시간당 보다 많은 시간 위치(56)가 있으면), 출력의 정확도만 향상된다.

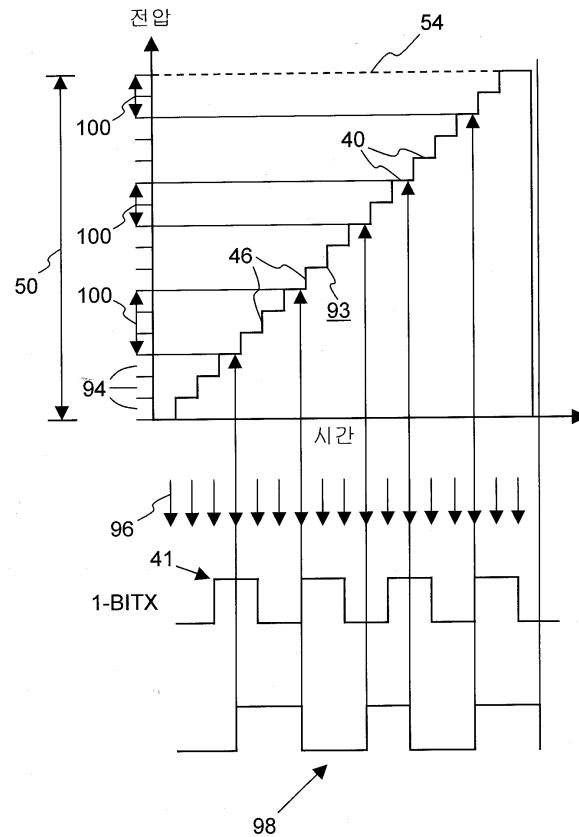

도 14는 램프(93)가 도 8 및 11의 램프 신호의 전압 스텝(46) 및 레벨(40)보다 두 배 많은 경우의 램프 신호(93) 및 1-BITX 신호를 도시한다. 램프(93)가 두 배의 보다 많은 전압 스텝(46)을 가지므로 시간 위치(96)는 시간 위치(56)보다 두 배 조밀하다. 램프의 우수한 구조는 도 6 및 8의 램프와 비교하여 두 배 많은 전압 범위(94)로 입력 범위(50)를 분할한다. 시간 위치(96)의 증가된 밀도 및 전압 범위(94)의 보다 큰 수는 보다 높은 정확성 승산을 허용한다. 비록 전압 스텝(46)의 수 및 시간 위치(96)가 두 배지만, 1-BITX(41)에 대한 주파수는 여전히  $F_0$ (도 6 및 8에 사용된 동일 주파수)임에 유의해야 한다.

도 14의 향상된 정확성 접근에 있어서, M-BITX의 발생은 시간 위치(96)가 시간 위치(56)의 두 배 많은 수이지만, 도 10의 동일 '격자에 대한 스냅' 접근에 따르도록 고려된다.

도 15는  $X=0.7$ 에 대한 예를 설명한다. 여기에서, 주파수  $F_0$ 을 가진 방형파 신호(58)가 도시된다. 가장 가까운 시간 위치(96)에 대한 천이(43)를 스냅핑(snapping)하는 것은 적당한 M-BITX 신호(98)를 제공한다. 시간 위치(96)는 보다 가깝게 위치되므로(위치(56)와 비교하여), 결과 M-BITX 신호(98)는 방형파(58)와 보다 가깝게 유사하다(M-BITX 신호(60)와 비교하여).

M-BITX 신호(98)는 램프 신호(93)와 동조된다. 1의 디지털 값을 지정하는 전압 범위(100)에 의해 램프(93)와 M-BITX 신호(98)의 사용이 기인된다. 전압 범위(100)는 도 11의 전압 범위(64)보다 0.7에 의한 승산을 보다 정확하게 표현한다.

본 애플리케이션에 있어서, 1-BITX 기준 주파수( $F_0$ )의 천이의 밀도와 비교하여 시간 위치(56,96)(램프의 전압 스텝에 의해 결정되는)의 밀도는 격자 밀도 인자  $K$ 로서 일컬어진다. 상기 예에 있어서, 격자 밀도 인자  $K$ 는 2(즉,  $K=2$ )이다. 모든 이전의 예에 있어서, 격자 밀도 인자  $K$ 는 1(즉,  $K=1$ )이다.

2의 격자 밀도 인자는 1의 격자 밀도 인자와 비교하여 정확성에서 큰 증가를 제공하지 않는다는 것을 유의하여야 한다. 도 14의 예는 단지 증가한 격자 밀도 인자가 본 발명의 방법의 정확성을 향상시키는 방법의 예를 제공하기 위한 것이다. 가장 일반적으로, 격자 밀도 인자가 커질수록 승산이 보다 정확해진다.

임의의 격자 밀도 인자  $K$  및 계수  $X$ 에 따라 M-BITX 신호를 발생할 수 있는 회로(104)를 도시한다. 모든 회로 구성요소는  $KF_0$ 의 주파수에서 실행되는 클럭(74) 이외에 도 12와 동일하다.

승산 계수  $X$  및 격자 밀도 인자  $K$ 가 주어진 컴퓨터(70)는 관계:

$$N+ \frac{A}{B} \approx \frac{K}{X}$$

에 일반적으로 기초한다.

$K/X$ 의 값에 근접한  $N+(A/B)$  값은 정확한 A/D 변환 및 승산을 제공한다.  $N$  및  $K$ 는 정수이다.

일반적인 지침에 있어서, N은 보통  $K/X$ (즉,  $K/X=3.43$ 에서  $N=3$ )의 정수부와 일치한다. 또한, A 및 B는 보통  $A/B$ 가 ( $K/X$ )의 소수부와 거의 일치하도록 선택된다. 예를 들면,  $K/X=3.43$ 이면, A 및 B는 보통  $A/B \approx 0.43$ 이 되도록 선택된다. 그렇지만, N, A 및 B에 대한 다른 옵션들은 많이 존재하며 본 발명의 범위 내이다.

이하에는 계수 X 및 격자 밀도 인자 K가 주어진 N, A 및 B를 선택하기 위한 세 가지 유용한 알고리즘(알고리즘 4-6)을 설명한다.

N, A 및 B가 결정된 후에, 회로(104)는 다음 환경(settings)들을 가지고 형성된다:

1) 값 A는 제 1 입력(82)에서 연속적으로 유지된다.

2) 누산기의 커페시티는 B로 정한다.

3) 주파수 분할기 모듈은 모듈 제어(75)에서의 신호에 의존하여, N 또는  $N+1$ 이 되도록 정한다. 분할기의 모듈은 캐리 아웃(88)이 하이일 때(누산기 내의 실행 합계가 커페시티 B에 롤오버(roll over)될 때)  $N+1$ 이다.

4) 누산기의 내부 상태는 0과  $B-1$  사이의 값으로 초기화된다. 바람직하게는, 누산기의 내부 상태는  $B/2$ 로 초기화된다.

이 환경들은 수동 또는 컴퓨터(70)에 의해 만들어지거나, 회로는 X 및 K가 회로(104)의 라이프(life)에 대해 일정하면 N, A 및 B의 일정한 값을 사용하여 영구적으로 정할 수 있다.

동작 중, 주파수  $KF_0$ 의 방형파는 주파수 분할기에 입력된다. 주파수 분할기는 출력(73)으로  $KF_0/N$ 을 출력한다. 누산기는 제 1(82) 및 제 2(84) 입력에서의 디지털 수와 출력(73)에서 발생한 매시간 천이(하이에서 로우 또는 로우에서 하이)를 가산한다. 누산기 출력(86)은 제 2 입력(84)에 연결되므로, 실행 합계는 누산기(76) 내에서 발생된다. 누산기가 0의 값으로 초기화되면, 실행 합계는 연속적인 값 0, A, 2A, 3A, 4A 및 커페시티 B까지(즉, A는 주파수 분할기 출력(73)의 모든 천이와 함께 실행 합계에 가산된다)를 가진다. 누산기가  $1/2B$ 의 값으로 초기화되면, 실행 합계는 연속적인 값  $1/2B$ ,  $1/2B+A$ ,  $1/2B+2A$ ,  $1/2B+3A$  및 커페시티 B까지를 가진다. 실행 합계가 커페시티 B에 도달하면, 캐리 아웃(88)은 하이로 되고 주파수 분할기 모듈은  $N+1$ 로 변경된다. 캐리 아웃(88)이 하이일 동안, 주파수 분할기는 주파수  $KF_0/N+1$ 을 출력한다. 그러므로, 주파수 분할기 출력(73)은 주파수  $KF_0/N$  및 주파수  $KF_0/N+1$ 의 선택적인 세그먼트를 제공한다.

격자 밀도 인자  $K > 1$ 에서, 램프 신호에서 해당하는 변화가 만들어진다. 보다 상세하게는, 램프는 전압 스텝(46)보다 K배 많이 가지고 변화된다. 이것은 최초 램프 신호(즉,  $K=1$ 에서의 램프)의 각 전압 스텝을 K 등분 전압 스텝으로 분할함으로써 달성된다.

먼저  $K=1$ 은 도 12의 예를 설명하는 것은 자명하다.

$1/X=I.F$ 를 살펴보면, 여기에서 I는  $1/X$ 의 정수부이고, F는  $1/X$ 의 소수부(즉,  $K=1$ 에서  $I=N$ 이고  $F=M$ )이다. 본 발명에 있어서, X는 2진수로 표현되고, F는 2진수로 표현된다. F를 표현하기 위해 사용되는 비트의 수는 D로 정의된다. 전형적으로, D는 대략 4-6(즉, F는 4-6 이진 숫자에 의해 표현된다)이다. 본 발명의 보다 바람직한 실시예에 있어서,  $K=2^D$ 이다. 그렇지만, K는 2제곱이 아닌 값을 포함하는 임의의 정수값을 가질 수 있다. K에 대한 값이 커질수록 아날로그-디지털 변환은 보다 정확해진다. 또한, K의 값이 커질수록 보다 빠른 클럭 속도가 요구된다.

다음의 모든 알고리즘에 있어서, n은 A/D 변환을 원하는 정밀도의 다수의 비트로 정의된다(예를 들면, 정밀도의 3비트가 A/D 변환을 원하면  $n=3$ ).

#### N, A 및 B를 선택하기 위한 알고리즘 4-6

##### 알고리즘 4

이 예의 알고리즘에 있어서,

$N=K/X$ 의 정수부, 즉,  $N \leq K/X < N+1$

$B=2^n K$ , 및

$A=\text{버림}(\text{round})(B(\text{frac}(K/X)))$

여기에서 '버림(round)'은 '가장 가까운 정수로 라운드' 동작을 나타내고, 'frac'은 '소수부를 취함' 동작을 나타낸다.

### 알고리즘 5

이 알고리즘은 전형적으로 가장 효과적이다. 아이디어는  $C$ 가 선택된 상수미만의 제약 조건을 가지고, 가능한 정확하게 분수  $B/C$ 로  $X/K$ 를 표현하는 것이다. 예를 들면, 제약 조건  $C < 2^n K$ 가 사용된다. 그러면,  $N$ ,  $A$  및  $B$ 는  $N$ 은 표현:

$$\frac{B}{C} = N + \frac{A}{B}$$

으로부터 획득된다. 분수  $B/C$ 는 수 체계로서의 스텐-브로코트 트리(stern-brocot tree)를 사용하여 얻어진다. 분수  $B/C$ 를 찾기 위한 스텐-브로코트 트리를 사용하여 보다 많은 정보를 위하여, 그레이엄(Graham), 커뮤드(Knuth) 및 파타쉬니크(Patashnik)에 의한 구체적인 수학(Concrete Mathematics), 페이지 118-122를 참조한다.

### 알고리즘 6

이 알고리즘에 있어서,

$B=\text{round}(2^n XK)$ , 여기에서 'round'는 '가장 가까운 정수로 라운드' 동작을 나타낸다,

$N=K^2 2^n / B$ 의 정수부 및

$A=K^2 2^n \text{mod}(B)$ , 여기에서 'mod'는 모듈 동작을 나타낸다.

알고리즘 6에 있어서,  $N$ 은  $K/X$ 의 정수부와 일치할 필요가 없다. 다시 말해서  $N$ 은 부등식  $N \leq K/X < N+1$ 을 준수할 필요가 없다.

알고리즘 1-3은  $K=1$ 의 특수한 경우에 대하여 알고리즘 4-6과 동일하게 보여진다.

본 발명은 알고리즘 4-6에 한정되지 않는다.  $N+(A/B) \approx K/X$ 가 되도록  $N$ ,  $A$  및  $B$ 를 찾기 위해 많은 기술들이 사용될 수 있다.

상기에 진술한 바와 같이, 정확한 A/D 변환을 위해,  $N+(A/B)$ 은  $K/X$ 에 근접하여야 한다. 즉, A/D 변환의 희망 비트 해상도에 의존하여 근접시키는 방법은  $n$ 에 의존한다. 최선의 결과를 위해,  $N+(A/B)$ 은  $K/X$ 의  $(1/2^n)$ 의 인자 내이어야 한다. 예를 들면,  $n=1$ (1비트 해상도 A/D 변환)에서,  $N+(A/B)$ 은  $K/X$ 의 50% 내이어야 한다.  $n=3$ 에서,  $N+(A/B)$ 은  $K/X$ 의 12.5% 내이어야 한다. 그렇지만, 이것은 일반적인 지침이고, 본 발명의 절대 요구조건은 아니다.

### M-램프를 발생하기 위한 보다 좋은 방법

본 발명에 있어서, 승산을 제공하기 위한 램프 신호는 디지털-아날로그 변환기(DAC)를 사용하여 발생되는 것이 바람직하다. 분명히, 임의의 DAC는 주로 디지털 입력, 그 중에서도 인자에 의해 결정되는 한정된 출력 전압 해상도를 가진다. 예를 들면, 8-비트 DAC는 256 전압만을 제공할 수 있다. 그러므로, 도 6에 사용된 램프를 발생시키기 위해 DAC가 사용되면, 전압 레벨(40)은 단지 8-비트 DAC로부터 획득될 수 있는 256 전압 중에서 하나와 일치하는 전압 값을 가질 수 있다.

도 7은 상기에 설명된 바와 같이 X=1.43에서의 0.7M-램프 신호를 도시한다. 전압 레벨(40)은 비 승산을 제공하는 기준 1-램프 신호와 비교하여 정확하게 1.43의 인자에 의해 전압이 증가된다. 그렇지만, 1.43에 의한 승산에 대한 도 7에 도시된 정확한 전압 레벨(40)은 DAC로부터 획득될 수 없다. 그러므로, M-램프 발생 DAC의 한정된 전압 해상도는 MCBS 장치에서 A/D 변환 및 승산의 해상도를 제한한다.

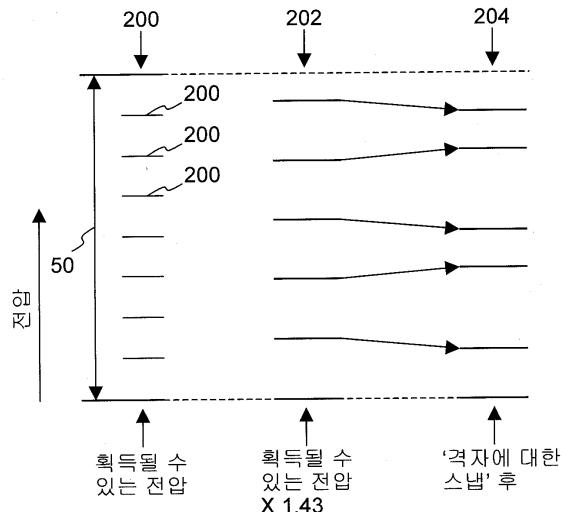

도 17은 전압 범위(50)에 대한 M-램프 신호를 발생하기 위해 설계된 3-비트 DAC로부터 획득될 수 있는 8 전압(200)을 도시한다. 획득될 수 있는 전압(200)은 일반적으로 0.7M-램프 신호를 생산하기 위해 요구되는 전압 레벨(40)과 일치하지 않는다.

그렇지만, 3-비트 DAC는 '격자에 대한 스냅' 지표를 가진 M-램프 신호를 생성함으로써 대략 0.7M-램프 신호인 M-램프 신호를 생산할 수 있다. 이 '격자에 대한 스냅' 지표는 상기에 설명된 M-BITX 신호의 '격자에 대한 스냅' 지표와 비슷하다.

도 18은 M-램프 신호의 격자에 대한 스냅 지표를 설명한다. 3-비트 DAC로부터 획득될 수 있는 전압(200)이 도시된다. 획득될 수 있는 전압(200)은 균일하게 위치되고 '격자'를 형성한다. 전압(202)은 1.43에 의해 승산된 획득할 수 있는 전압이다. 전압(202)은 0.7M-램프 신호에 존재하는 전압 레벨의 전압이다. 전압(204)은 '격자에 대한 스냅' 지표를 가진 M-램프 신호에 존재하는 전압이다. 모든 전압(204)은 3-비트 DAC로부터 획득될 수 있다. 물론, 격자에 대한 스냅 지표는 임의의 비트 해상도(예를 들면, 8-비트 또는 임의의 비트)를 가진 시스템에 유용하다.

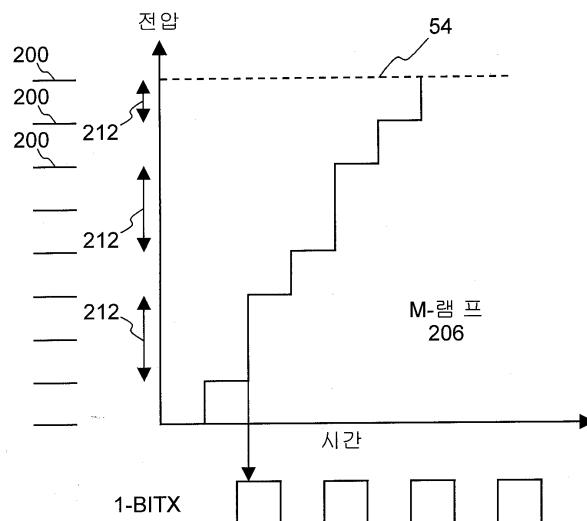

도 19는 격자에 대한 스냅 지표를 가진 M-램프 신호(206)를 도시한다. 모든 전압 레벨(200)은 획득될 수 있는 전압(200)과 일치한다. 1-BITX 신호도 또한 도시된다. 범위(212)는 MCBS ADC의 디지털 출력이 1일 때의 아날로그 입력 전압을 나타낸다. 범위(212)는 도 7에 도시된 범위(42)와 거의 일치한다.

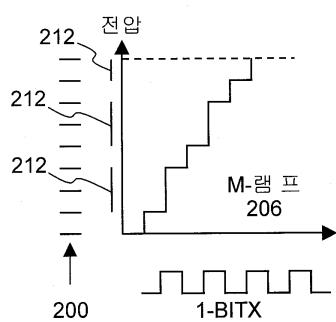

도 20a는 격자에 대한 스냅을 가진 M-램프를 이용하는 본 방법을 도시하고 도 20b는 격자에 대한 스냅을 가진 M-BITX를 이용하는 본 방법을 도시한다. M-램프에 대한 범위(212)와 M-BITX에 대한 범위(64)는 동등하다. 도 20a-b는 둘 모두 격자에 대한 스냅 지표를 가진 경우의 M-램프 및 M-BITX 사이의 아날로그를 설명한다. M-램프의 경우에 있어서, '격자'(200)는 DAC로부터 이용할 수 있는 전압에 의해 결정된다. M-BITX의 경우에 있어서, '격자'는 M-램프 전압 스텝의 시간 위치(56,96)에 의해 결정된다. M-BITX는 M-램프가 많은 전압 스텝을 가질 때(즉, 시간 위치(56,96)가 근접되게 위치된다) 정확한 승산을 제공한다. 유사하게, M-램프는 M-램프를 발생시키기 위해 사용되는 DAC가 높은 비트 해상도를 가질 때 정확한 승산을 제공한다.

격자에 대한 스냅을 가진 M-램프 신호는 전압(202) 상에 '격자에 대한 스냅' 동작을 실행하는 이산 장치를 사용하여 발생 시킬 필요가 없다. 그렇지만, M-BITX 신호는 '격자에 대한 스냅' 지표를 가지는 것이 바람직하다. '격자에 대한 스냅' 지표를 가진 M-램프 신호를 생산하기 위한 임의의 방법은 본 발명의 범위 내인 것을 유의하여야 한다. 보다 좋은 기술은 아래에 논의된다.

그렇지만, 임의의 계수 X에 대한 격자에 대한 스냅 지표를 가진 M-램프 신호의 발생 방법이 명확하지 않다.

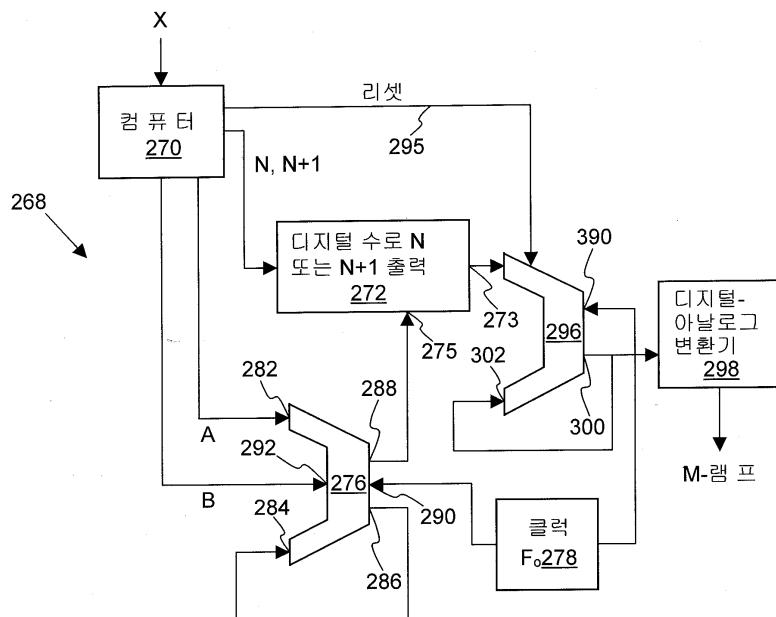

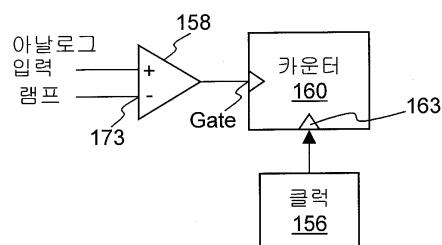

도 21은 임의의 계수 X에 대한 격자에 대한 스냅 지표를 가진 M-램프 신호를 발생시키기 위한 본 발명에 따른 회로(268)를 도시한다. 회로(268)는 도 12에 도시된 M-BITX 발생 회로(68)와 아주 유사하다.

회로(268)는 컴퓨터(270), 디지털 수 선택기(272), 제 1 누산기(276)(디지털 가산기), 제 2 누산기(296), 클럭(278) 및 디지털-아날로그 변환기(298)를 포함한다. 수 선택기는 출력(273) 및 제어(275)를 가진다. 제 1 누산기(276)는 제 1 입력(282), 제 2 입력(284), 출력(286), 캐리 아웃(288), 에지-감지 트리거(290) 및 커패시티 세트 입력(292)을 가진다. 캐리 아웃(288)은 제어(275)에 연결된다. 제 1 누산기의 출력(286)은 제 2 입력(284)에 연결된다. 컴퓨터(270)는 또한 제 2 누산기의 내부 상태를 영으로 리셋 제어(295)를 가진다.

제 2 누산기(296)는 수 선택기(272)로부터 디지털 수 (N 또는 N+1)를 수신하기 위해 연결된다. 제 2 누산기(296)의 출력(300)은 제 2 누산기가 실행 합계를 발생하도록 입력(302)에 연결된다.

제 1 누산기 트리거(290) 및 제 2 누산기 트리거(390)에 연결되는 클럭(278)은 주파수  $F_0$ 에서 방형파 신호를 제공한다. 누산기(276,296)는 클럭 신호의 모든 천이 예지(정방향 및 역방향 천이)를 가산하기 위해 트리거 된다. 그러므로, 누산기(276,296)는  $2F_0$ 의 주파수에서 가산된다. 실제로는, 전기 신호가 제 1 누산기(276)로부터 전달되기 위한 시간을 가지도록 제 2 누산기(296)의 동작을 지연시킬 필요가 있을 수 있다.

동작 중, 컴퓨터(270)는 관계:

$$N + \frac{A}{B} \approx \frac{K}{X}$$

에 기초하여 수 N, A 및 B를 결정한다.

$K/X$ 의 값에 근접한  $N + (A/B)$  값은 정확한 A/D 변환 및 승산을 제공한다. N은 정수이다. N, A 및 B의 값은 상기에 설명된 알고리즘 1-6을 사용하여 선택된다.

N, A 및 B가 결정된 후에, 회로(268)는 다음 환경(settings)들을 가지고 형성된다:

1) 값 A는 제 1 누산기 제 1 입력(282)에서 연속적으로 제공된다.

2) 제 1 누산기의 커페시티는 B로 정한다.

3) 수 선택기는 제어(275)에서의 신호에 의존하는 출력(273)에서 N 또는  $N + 1$ 을 제공하기 위해 정한다. 선택기의 출력은 캐리 아웃(288)이 하이일 때(즉, 제 1 누산기 내의 제 1 실행 합계가 커페시티 B에 롤오버될 때)  $N + 1$ 이다. 선택기(272)의 출력은 캐리 아웃(288)이 로우일 때 N이다.

4) 제 1 누산기의 내부 상태는 0과  $B - 1$  사이의 값으로 초기화된다. 바람직하게는, 제 1 누산기의 내부 상태는  $B/2$ 로 초기화된다.

5) 제 2 누산기의 커페시티는 디지털-아날로그 변환기(298)(예를 들면, 3-비트 DAC(298)에서 커페시티는 8이다)에 의해 수신할 수 있는 최대 값과 일치하도록 정하는 것이 바람직하다.

6) 제 2 누산기의 내부 상태는 영으로 초기화(즉, 리셋)된다.

이 환경들은 수동 또는 컴퓨터(70)에 의해 만들어지거나, 회로는 X가 회로(68)의 라이프(life)에 대해 일정하면 N, A 및 B의 일정한 값을 사용하여 영구적으로 정할 수 있다. 제 2 누산기(296)는 모든 M-램프 신호가 발생된 후에 영으로 리셋되어야 한다. 또한, 제 1 누산기는 모든 M-램프 신호가 발생된 후에 0과  $B - 1$  사이의 값으로 리셋되어야 한다.

동작 중, 회로(268)는 도 12의 회로(68)와 거의 동일한 방식으로 작동된다. 클럭이 발진함에 따라, 제 1 누산기(276)는 실행 합계(예를 들면, 0, A, 2A, 3A, 4A...)를 생산한다. 또한, 제 2 누산기는 실행 합계(예를 들면, 0, N, 2N, 3N, 4N...)를 생산한다. 제 2 누산기의 실행 합계는 DAC로 입력된다. DAC는 제 2 누산기 실행 합계에 비례하는 아날로그 출력 전압을 생산한다. 제 2 누산기 실행 합계는 불연속적으로 증가하므로, DAC는 계단식 파형 출력을 제공한다.

제 1 누산기 실행 합계가 커페시티 B에 도달할 때, 캐리 아웃(288)은 하이로 되고, 수 선택기(272)는 제 2 누산기(296)로  $N + 1$ 을 제공한다. 캐리 아웃이 하이일 동안, DAC 아날로그 전압 출력은  $N + 1$ 에 비례하는 스텝으로 증가한다.

캐리 아웃(288)이 로우로 복귀될 때, DAC 출력은 N에 비례하는 스텝으로 증가한다.

DAC가 K에 비례하는 비트 해상도를 가지는 것은 자명하다. 그러므로, K 값이 커질 때에, 전압 스텝은 보다 작은 크기를 가진다.

이런 식으로, DAC 출력은 두 개의 서로 다른 크기의 전압 스텝을 제공한다. 서로 다른 전압 스텝은 DAC 출력의 평균 기울기(아주 긴 시간 주기에 의해 측정된 전압/시간 기울기)가  $T/X$ (여기에서 T는 1-램프의 전압/시간 기울기이다)에 근접하

도록 생산된다. 1-램프의 전압 스텝은 크기  $V$ 를 가진 것으로 정의된다. 그러므로, M-램프의 전압 스텝은 크기  $VN/K$  및  $V(N+1)/K$ 를 가진다. 두 개의 서로 다른 전압 스텝 크기( $VN/K$  및  $V(N+1)/K$ )는 T/X의 평균 기울기를 가진 M-램프에 의한 양식으로 발생된다.

M-램프 신호가 발생된 후, 제 2 누산기는 영으로 리셋되고, 제 1 누산기는 자신의 최초 초기화 값으로 리셋된다. 그리고 나서, MCBS ADC 출력의 다음 비트를 제공하기 위해 다른 M-램프 신호가 발생된다.

격자 밀도 인자  $K \neq 1$ 이 사용된 경우, 클럭 주파수는  $KF_0$ 이다. 또한, DAC 출력의 전압 스텝은  $K$ 의 인자에 의해 분할된다. 모든 다른 구성요소 및 환경은 여전히 변하지 않는다.

### 화상 센서에 대한 애플리케이션

다음 설명에 있어서, BITX 및 램프는 승산을 제공하거나 제공하지 않는 신호를 나타낸다.

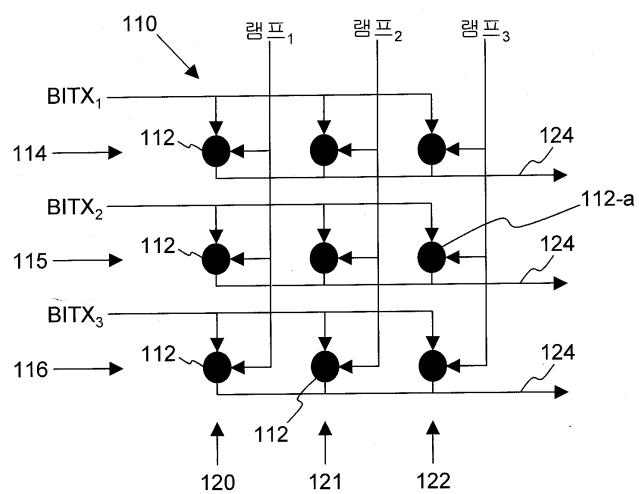

도 22는 각 픽셀에 의해 발생된 아날로그 값에 대한 동시 A/D 변환 및 승산을 제공하는 화상 센서(110)를 도시한다. 화상 센서(110)는 픽셀들(112)을 가지며, 각 픽셀은 비트 직렬 ADC를 가진다. 동작 중, BITX<sub>1</sub>, BITX<sub>2</sub> 및 BITX<sub>3</sub>은 각각의 행(114, 115, 116)의 모든 픽셀들에 입력된다. 각각의 BITX<sub>1</sub>, BITX<sub>2</sub> 및 BITX<sub>3</sub>은 서로 다른 계수 B<sub>1</sub>, B<sub>2</sub> 및 B<sub>3</sub>에 의한 승산을 제공한다. 램프<sub>1</sub>, 램프<sub>2</sub> 및 램프<sub>3</sub>은 각각의 열(120, 121, 122)의 모든 픽셀들에 입력된다. 각각의 램프<sub>1</sub>, 램프<sub>2</sub> 및 램프<sub>3</sub>은 서로 다른 계수 R<sub>1</sub>, R<sub>2</sub> 및 R<sub>3</sub>에 의한 승산을 제공한다. 예를 들면, 픽셀 112-a로부터의 아날로그 값은 B<sub>2</sub>R<sub>3</sub>의 인자에 의해 디지털화 및 승산 된다. 디지털화 및 승산된 신호는 출력(124)에서 제공된다. 승산 형태(scheme)는 공지된 MPEG 및 JPEG 표준에 따라 화상 데이터 압축을 제공한다. 보다 일반적으로, 이 승산 형태는 임의의 2-D 분리 가능 변형 기술에 따라 데이터 압축 및 필터링을 제공할 수 있다.

동작 중, BITX<sub>1</sub>, BITX<sub>2</sub> 및 BITX<sub>3</sub> 신호는 여기에 설명된 회로와 같은 서로 다른 세 가지 BITX 발생기에 의해 발생된다. 램프<sub>1</sub>, 램프<sub>2</sub> 및 램프<sub>3</sub> 신호는 서로 다른 세 가지 DACs에 의해 발생된다. 선택적으로, 단일 BITX 발생기는 BITX<sub>1</sub>, BITX<sub>2</sub> 및 BITX<sub>3</sub>을 발생하기 위해 사용되고, 출력은 각각의 서로 다른 행(114, 115, 116)에 다중화 된다. 또한, 선택적으로, 단일 램프 발생기는 램프<sub>1</sub>, 램프<sub>2</sub> 및 램프<sub>3</sub>을 발생하기 위해 사용되고, 출력은 각각의 서로 다른 열(120, 121, 122)에 다중화 된다. 게다가, 조사표 테이블들(look-up tables)은 램프 및 BITX 신호의 디자인에 디지털 정보를 저장하기 위해 사용된다. 그리고 나서, 이 정보는 검색되고 BITX 및 램프 신호로 변환된다.

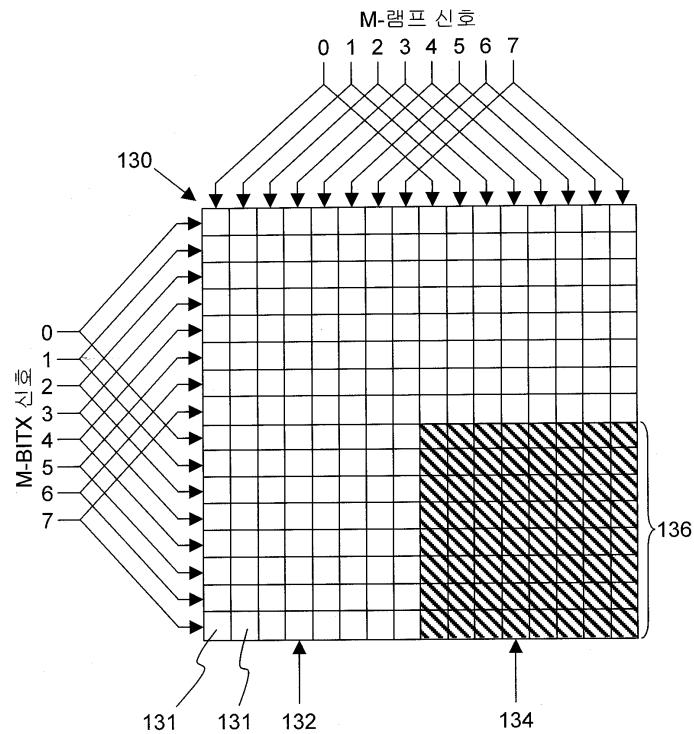

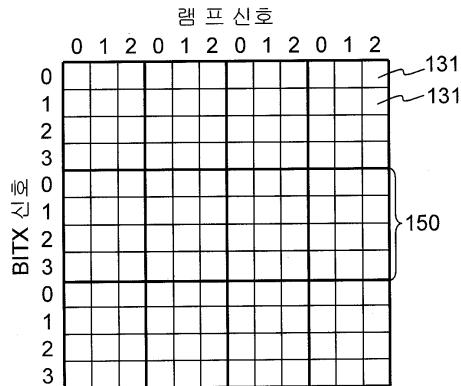

본 발명의 사용에서 중요하게 고려할 사항은 2-D 분리 가능 변형(예를 들면, DCT, JPEG, MPEG, 컨벌루션(convolution) 또는 고역/저역 통과 필터링)에 사용되는 블록 크기와 사용될 수 있는 BITX 및 램프 신호의 수를 일치시키는 것이다. 예를 들면, 8개의 서로 다른 램프와 8개의 서로 다른 BITX 신호가 이용될 수 있는 특수한 화상 장치를 살펴본다. 이 경우에, 압축/필터링은 화상 장치 내의 픽셀의 8×8 블록을 사용하여 실행된다. 도 23은 개개의 픽셀들(131)을 포함하는 16×16 픽셀 어레이(130)를 도시한다. 데이터 압축은 본 발명에 따른 4개의 8×8 블록으로 실행된다. 4개의 블록 중의 하나는 해칭(hatching)된다(136). 8×8 블록이 사용되므로, 8 램프 신호들(0-7의 라벨을 붙인)과 8 BITX 신호들(0-7의 라벨을 붙인)이 요구된다. 각 램프 신호는 두 개의 열에 제공되고, 각 BITX 신호는 두 개의 행에 제공된다. 예를 들면, 램프 신호 3은 양쪽의 열 4(132) 및 열 12(134)에 제공된다.

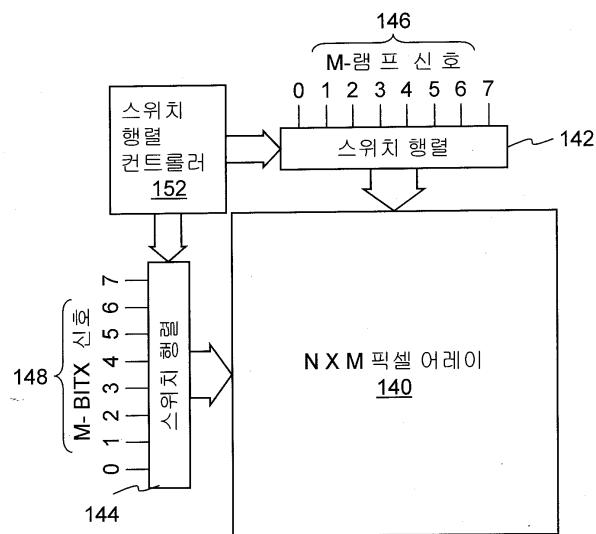

어떤 경우에는 블록 크기(예를 들면, 다른 압축/필터링 알고리즘을 사용하기 위한)를 바꾸는 것이 바람직하다. 도 24는 데이터 압축/필터링의 실행에 사용되는 블록 크기들을 변화시킬 수 있는 본 발명의 실시예를 도시한다. 장치는 광 검출기의 화상 어레이와 같은 픽셀 어레이(140)를 가진다. 데이터 압축/필터링의 실행에 있어서, 픽셀 어레이(140)는 처리하기 위한 블록으로 분할된다. 블록은 사용되는 압축/필터링 알고리즘에 의해 매우 다른 크기가 된다. 블록은 정사각형 또는 직사각형이 된다. 예로는 8×8, 2×2, 3×3, 16×16, 2×3 및 3×4 픽셀 블록이 포함된다.

도 24의 장치는 제 1 스위치 행렬(142) 및 제 2 스위치 행렬(144)을 가진다. 제 1 스위치 행렬(142)은 램프 신호 0-7(146)을 수신하고; 제 2 스위치 행렬(144)은 BITX 신호 0-7(148)을 수신한다. 제 1 스위치 행렬(142)은 램프 신호를 적당한 열로 발송한다. 제 2 스위치 행렬(144)은 BITX 신호를 적당한 행으로 발송한다. 가장 일반적으로, 제 1 스위치 행렬(142)은 임의의 열이 임의의 램프 신호(램프 신호 0-7의 임의의 하나)를 수신하도록 허용한다. 제 2 스위치 행렬(144)은

임의의 행이 임의의 BITX 신호(BITX 신호 0-7의 임의의 하나)를 수신하도록 허용한다. 행 및 열에 대한 적당한 램프 및 BITX 신호는 블록 크기 및 압축/필터링 알고리즘에 의존한다. 스위치 행렬들은 스위치 행렬 컨트롤러(152)에 의해 동적으로 제어될 수 있다.

도 25는, 예를 들면,  $12 \times 12$  픽셀 어레이가 픽셀(131)의  $3 \times 4$  블록(150)으로 처리되는 특수한 경우를 도시한다. 모든 세 번째 열은 동일 램프 신호(0,1 또는 2)를 수신하고, 모든 네 번째 행은 동일 BITX 신호(0,1,2 또는 3)를 수신한다. 램프 및 BITX 신호들은 스위치 행렬들(142,144)에 의해 적당한 행 및 열로 보내진다(이 특수한 예에 있어서, 램프 신호 3-7은 사용되지 않고 BITX 신호 4-7은 사용되지 않는다). 행 및 열은 교환할 수 있고 소자를 90도 회전함으로써 같아진다는 것은 자명하다. 용어 '행' 및 '열'은 단지 도면의 수평 및 수직 정렬을 나타내기 위해 편의를 제공하고, 픽셀들 또는 픽셀들과 관련된 비트 직렬 ADCs의 동작에 대한 임의의 근본적인 차이를 나타내지 않는다.

도 24의 예에 있어서, 8개의 서로 다른 램프 신호 및 8개의 서로 다른 BITX 신호들은 제 1 및 제 2 스위치 행렬들(142,144)에 제공된다. 그러므로, 처리되는 가장 큰 블록은  $8 \times 8$  블록이다. 보다 작은 블록 크기들은  $3 \times 4$  블록에 대해 상기에 설명한 바와 같이 램프 및 BITX 신호들의 단지 일부분을 사용함으로써 처리된다. 예를 들면,  $3 \times 3$  블록을 위해서, 3개의 서로 다른 램프 신호 및 3개의 서로 다른 BITX 신호가 요구된다. 다른 수의 램프 및 BITX 신호가 스위치 행렬들(142,144)에 제공될 수 있다는 것도 또한 자명하다.

8 램프 및 8 BITX 신호가 제공되면,  $8 \times 8$ 까지의 블록이 처리된다. 보다 작은 블록을 위해, 스위치 행렬들(142,144)을 사용하여 램프 또는 BITX 신호에 알맞게 발송할 필요가 있다. 최대 크기(본 예에 있어서  $8 \times 8$ )까지의 모든 가능한 크기의 블록을 사용하기 위해 필요한 배열 수는 램프 및 BITX 신호의 수에 의해 결정된다. 8 신호에 관하여, 각 스위치 행렬에 5 배열이 요구된다. 이것은 아래의 표에 설명된다.

| 배열 | 픽셀들의 블록 길이 |

|----|------------|

| 1  | 2,4,8      |

| 2  | 3,6        |

| 3  | 5          |

| 4  | 6          |

| 5  | 7          |

## 8 입력 신호에 대한 스위치 행렬의 다른 배열들

| 신호(램프 또는 BITX 신호)의 수 | 관련된 스위치 행렬의 배열 수 |

|----------------------|------------------|

| 9                    | 5                |

| 10                   | 5                |

| 11                   | 6                |

| 12                   | 6                |

2,4 및 8 픽셀의 블록 길이는 8이 2 및 4로 균일하게 분할되기 때문에 동일 스위치 행렬 수에 의해 조종된다. 비슷한 인수(argument)는 동일 행렬 배열이 일면(6은 3으로 균일하게 분할된다)에 3 및 6 픽셀들에 대해 사용되었기 때문이다. 요구되는 배열 수는 다음으로 가장 큰 정수('반올림(averaged up)')로 베림(round)되는  $N/2$ 와 항상 동일하고, 여기에서  $N$ 은 제공된 램프 또는 BITX 신호의 수이다. 아래의 표는 다른 램프 또는 BITX 신호 수에 대한 스위치 행렬 배열의 수를 도시한다.

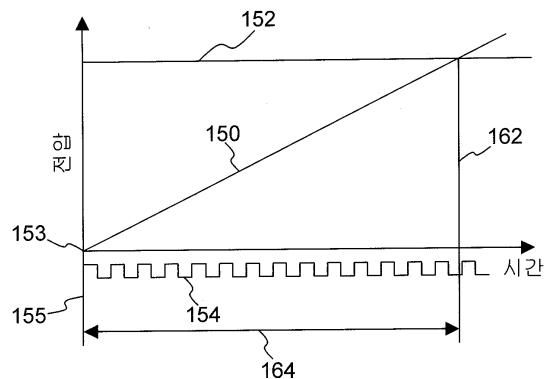

## 단일 기울기 ADC의 승산

본 발명은 단일-기울기 ADC의 동시 승산 및 A/D 변환을 제공하기 위한 방법을 포함한다. 단일 기울기 ADCs는 본 기술분야에 공지되었다. 도 26a는 동작을 설명하는 타이밍도를 도시한다. 도 26b는 단일 기울기 A/D 변환기를 도시한다. 단일 기울기 변환기에 있어서, SS-램프 파형(150)은 비교기(158)의 SS-램프 입력(173)에 입력된다. 비교기(158)는 SS-램프와 아날로그 전압(152)을 비교한다. SS-램프(150)는 정확하게 규정된 전압 대 시간 기울기를 가지고 0V(153)에서 시작된다. 클럭(156)은 정확한 주파수의 발진기 신호 SS-주파수(154)를 발생시킨다. SS-주파수(154)는 신호(154)의 주기를 계수하는 카운터(160)의 SS-주파수 입력(163)에 제공된다. 카운터는 포인트(155)에서 계수하기 시작한다. 카운터(160)

가 포인트(162)에서 즉, SS-램프(150)가 아날로그 전압(152)을 초과할 때 계수를 멈추도록 카운터를 비교기에 연결한다. 그러므로, 카운터(160)는 기간(164)을 계수한다. 기간(164)에서 카운터에 의해 계수된 주기의 수는 아날로그 전압(152)의 디지털 측정을 제공한다.

도 26b의 단일 기울기 ADC의 디지털 출력은:

$$D_{OUT} = \frac{QV_a}{S}$$

에 의해 정해진다. 여기에서  $V_a$ 는 아날로그 전압 입력이고,  $S$ 는 SS-램프의 기울기이며,  $Q$ 는 SS-주파수(154)의 주파수이다.

임의의 단일 기울기 ADC를 위해, 아날로그 전압의 정확한 표현을 가진 디지털 출력을 제공하는 1-SS-램프 및 1-SS-주파수가 존재한다. 본 상세한 설명에 있어서, 1-SS-램프는 기울기  $S$ 를 가진 것으로 정의되고, 1-SS-주파수는 주파수  $Q$ 를 가진 것으로 정의된다. 1-SS-램프 및 1-SS-주파수는 디지털 출력의 비 승산(즉, 1의 인자에 의한 승산)을 제공하기 위해 고려된다.

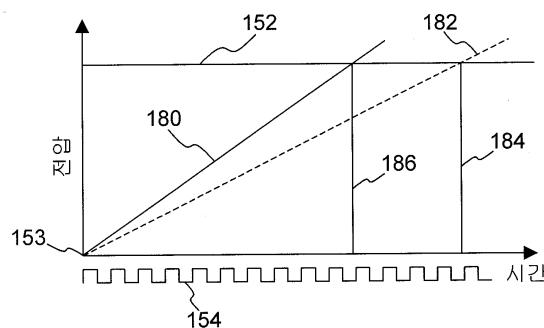

본 발명의 일 양상에 있어서, 계수  $X$ 에 의한 동시 A/D 변환 및 승산은 기울기  $S/X$ 를 가진 M-SS-램프("승산 단일 기울기 램프 신호")를 사용함으로써 제공된다. 도 27은 기울기  $S/X$ 를 가진 M-SS-램프(180)에 대한 타이밍도이고, 여기에서  $X=3/4$ 이다. 1-SS-램프(182)도 또한 도시되었다. 아날로그 입력(152)에 관하여, 카운터는 1-SS-램프가 사용되면 포인트(184)에서 정지한다. M-SS-램프는 보다 큰 기울기를 가지므로 M-SS-램프가 사용되면 카운터는 포인트(186)에서 정지한다. 그러므로 M-SS-램프는 카운터로부터의 1/4 작은 디지털 출력과  $X=3/4$ 의 인자에 의한 디지털 출력의 승산에 의해 생긴다. 물론, 승산은 기울기  $S$ 보다 작은 기울기를 가진 M-SS-램프를 사용함으로써  $X>1$ 에서 달성될 수도 있다.

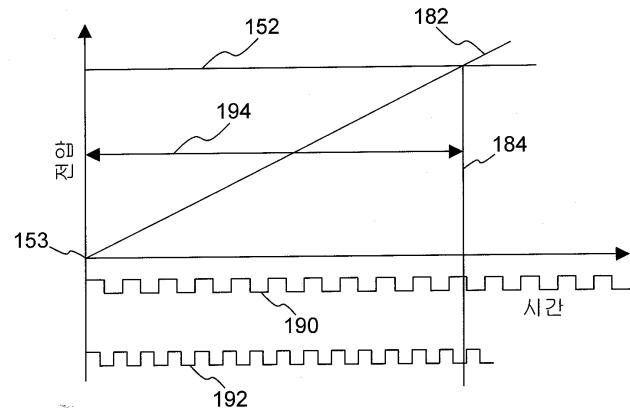

본 발명의 다른 양상에 있어서, 계수  $X$ 에 의한 동시 A/D 변환 및 승산은 주파수  $QX$ 를 가진 M-SS-주파수("승산 단일 기울기 주파수 신호")를 사용함으로써 제공된다. 도 28은 주파수  $QX$ 를 가진 M-SS-주파수(190)에 대한 타이밍도이고, 여기에서  $X=3/4$ 이다. 1-SS-주파수(192)도 또한 도시되었다. 카운터로 하여금 기간(194)을 계수하도록 허용함에 의해, 1-SS-램프(182)는 포인트(184)에서 정지한다. 아날로그 입력(152)에 관하여, 카운터는 1-SS-주파수(192)가 사용되면 기간(194) 내의 보다 많은 주기를 계수한다. 카운터는 1-SS-주파수(190)가 사용되면 기간(194) 내의 1/4 적은 주기를 계수한다. 그러므로 M-SS-주파수는 카운터로부터의 1/4 작은 디지털 출력과  $X=3/4$ 의 인자에 의한 디지털 출력의 승산에 의해 생긴다. 물론, 승산은 주파수  $Q$ 보다 큰 주파수를 가진 M-SS-주파수를 사용함으로써  $X>1$ 에서 달성될 수도 있다.

M-SS-주파수 신호는 분주-N PLL 합성 기술을 사용하여 발생된다는 것을 유념하는 것이 중요하다. M-SS-주파수의 평균 주파수가 정확하게 제어되기 때문에 분주-N PLL 합성이 바람직하다. 또한, M-SS-램프는 분주-N PLL 합성 기술을 사용하여 발생된다. 이 경우에 있어서, M-SS-램프는 실제로 다수의 스텝을 가진 계단식 스텝 파형이다. M-SS-램프의 다수의 스텝은 원활하게 변하는 램프 신호에 접근한다.

또한, M-SS-주파수 및 M-SS-램프는 전자 메모리 내의 조사표로부터 발생된다.

M-SS-주파수를 사용하는 승산 및 M-SS-램프를 사용하는 승산은 동시에 실행된다. 본 발명은 두 개의 계수: M-SS-램프에 의해 결정되는 일 계수, M-SS-주파수에 의해 결정되는 다른 계수에 의한 승산 가능성을 포함한다.

특수한 애플리케이션에 있어서, 데이터 압축/필터링은 단일 기울기 ADCs를 사용하여 광 검출기의 화상 어레이에 제공된다. 도 29는 픽셀들(112)의 3×3 어레이를 가진 그러한 장치를 도시한다. 도 29는 도 27의 BITX 및 램프 신호가 M-SS-주파수 및 M-SS-램프 신호로 대체된 것을 제외하고, 도 22와 아주 유사하다. 또한, 각 픽셀(112)은 도 22(ADCs는 미도시)와 같은 비트 직렬 ADC 대신에, 관련된 단일 기울기 ADC를 가진다. 단일 기울기 ADCs는 광 검출기와 같은 동일 칩 또는 내부 칩에 위치한다.

동작 중,  $M-SS-주파수_1$ ,  $M-SS-주파수_2$  및  $M-SS-주파수_3$ 은 각각의 행(114, 115, 116) 내의 모든 픽셀들에 각각 입력된다. 각각의  $M-SS-주파수_1$ ,  $M-SS-주파수_2$  및  $M-SS-주파수_3$ 은 서로 다른 계수  $F_1$ ,  $F_2$  및  $F_3$ 에 의한 승산을 제공한다.  $M-SS-램프_1$ ,  $M-SS-램프_2$  및  $M-SS-램프_3$ 은 각각의 열(120, 121, 122)의 모든 픽셀들에 각각 입력된다. 각각의  $M-SS-램프_1$ ,  $M-SS-램프_2$  및  $M-SS-램프_3$ 은 서로 다른 계수  $R_1$ ,  $R_2$  및  $R_3$ 에 의한 승산을 제공한다. 예를 들면, 픽셀 112-a로부터

터의 아날로그 값은  $F_2R_3$ 의 인자에 의한 디지털화 및 승산을 경험한다. 디지털화 및 승산된 신호는 출력(124)에서 제공된다. 승산 형태는 공지된 MPEG 및 JPEG 표준에 따라 화상 데이터 압축을 제공한다. 보다 일반적으로, 이 승산 형태는 임의의 2-D 분리 가능 변형 기술에 따라 데이터 압축 및 필터링을 제공할 수 있다.

스위치 행렬들은 단일 기울기 ADCs와 M-SS-램프 및 M-SS-주파수 신호와 공동으로 사용된다는 것을 또한 유의하여야 한다.

본 발명은 광 검출기 어레이에 외부적으로 아날로그-디지털 변환을 위치시킬 가능성을 포함한다. 이 경우에 있어서, 광 검출기로부터의 아날로그 신호는 분리 가능 칩 또는 아날로그-디지털 변환을 위한 구성요소에 전달된다. 비록 아날로그-디지털 변환이 광 검출기 어레이 상에 일어나지 않더라도, 본 방법은 여전히 실행된다. 보다 상세하게는, 승산은 다른 행의 광 검출기와 통신하는 아날로그-디지털 변환기에 적당한 M-BITX 신호를 제공함으로써 실행된다. 또한, 적당한 M-램프 신호가 다른 줄의 광 검출기와 통신하는 아날로그-디지털 변환기에 제공된다. 그렇지만, 광 검출기와 같은 동일 칩에 아날로그-디지털 변환을 위치시키는 것이 바람직하다는 것을 유의하여야 한다.

M-BITX 및 M-램프 발생기는 본 발명의 실행을 위해 제공될 필요가 없다는 것을 유의하는 것이 중요하다. 승산 계수의 세트가 기 결정되면, M-BITX 및 M-램프는 조사표와 같은 컴퓨터 메모리에 저장된다. 이것은 단일, 특수한 데이터 압축/필터링 기술이 사용되는 화상 장치의 경우일 수 있다. 화상 어레이로부터의 데이터로 특수한 데이터 압축을 처리하는 실행에 있어서, 단지 약간의(예를 들면, 8) M-BITX 신호 및 약간의(예를 들면, 8) M-램프 신호가 사용될 필요가 있다. 8 M-BITX 신호 및 8 M-램프 신호는 컴퓨터 메모리에 저장되고 DAC를 사용하여 재생산될 필요가 있게 된다. 그리므로, 본 발명은 도 12, 16 및 21에 도시된 바와 같은 회로를 사용하지 않고 실행된다.

본 발명이 서로 다른 기하학적인 양식으로 배열된 많은 유형의 픽셀 어레이가 사용된다는 것을 또한 유의하여야 한다. 픽셀들은 많은 도면에 도시된 바와 같은 사각형의 격자로 배열될 필요가 없다. 픽셀들은 '행' 및 '열'이 직선이 아닌 경우에 육각형 어레이로 배열된다. 또한, 픽셀들은 방사선에 따라 배열된 '행'과 방사선 양식의 중심을 둘러싼 원으로 이루어진 '열'을 가진 방사형으로 배열된다. 용어 '행' 및 '열'은 넓게 해석될 것이다. 용어 '행' 및 '열'은 교차하는 임의의 두 개의 선(곡선 또는 직선) 세트를 둘러싼다. 본 발명은 2-차원 분리 가능 변형(즉, 픽셀들의 선을 교차하는 것처럼 묘사되는 임의의 픽셀 어레이)과 호환할 수 있는 구조를 가진 임의의 픽셀 어레이가 사용된다.

비록 본 발명이 주로 화상 광 검출기를 참조하여 설명되었지만, 본 발명은 다수의 아날로그 신호를 디지털화 할 필요가 있는 임의의 상황에서 사용되고, 그 결과로서 생긴 데이터는 2-차원 분리 가능 변형에 따라 압축되고 필터링 된다. 예를 들면, 다수의 마이크로폰 또는 자계 센서로부터의 아날로그 신호는 본 발명을 사용하여 디지털화 되고 압축/필터링 된다.

M-램프, M-BITX, M-SS-램프 및 M-SS-주파수는 열-제어 및 행-제어 신호로 불리어지는 것이 더 일반화된다. 제어 신호들은 원하는 계수들에 의한 승산에 영향을 미치기 위해 센서 어레이 내의 ADCs의 동작을 제어한다. 열 및 행 제어 신호가 모두 사용되면, 어레이 내의 각 아날로그 신호는 두 개의 계수에 의해 승산 된다.

상기 실시예가 본 발명의 범위를 벗어나지 않고 많은 방법으로 변경될 수 있다는 것은 본 기술분야의 당업자에게 명백할 것이다. 따라서, 본 발명의 범위는 다음의 청구항 및 그것의 법률상 균등물에 의해 결정될 것이다.

## 발명의 효과

본 발명에 따른 동시 아날로그-디지털 변환 및 승산 방법에 의하면, 다중-채널 비트 직렬 아날로그-디지털 변환 방법 및 하드웨어를 완전히 호환할 수 있고, 기존의 MCBS 회로소자에 부가되는 추가적인 하드웨어를 요구하지 않고, 2 개의 독립적으로 조절 가능한 계수에 의해 각 디지털 값을 승산하기 위해 사용되고, 정확히 결정된 계수에 의해 승산 되도록 프로그램화되고, 화상 데이터 압축을 위한 분리 가능 2-D 변형, 컨벌루션 및 필터링을 실행하도록 사용되고, 다수의 병렬 아날로그 신호가 계수에 의해 디지털화 및 승산 되는 임의의 상황에서 사용되고, 아날로그-디지털 변환 및 디지털 승산이 실행되는 임의의 상황에서 사용될 수 있는 효과가 있다.

## 도면의 간단한 설명

도 1은 종래의  $8 \times 8$  픽셀 화상 센서.

도 2는 종래의 MCBS ADC를 사용하는 하드웨어.

도 3은 종래의 MCBS 동작 방법.

도 4는 종래의 도 3의 파형으로 동작하는 MCBS에 대한 양자화 표.

도 5는 종래의 다중 채널 MCBS ADC.

도 6은 1(즉, 비 승산) 인자에 의해 승산을 제공하는 램프 및 BITX 신호도.

도 7은 승산을 제공하는 M-램프 신호의 예시도.

도 8은 승산을 제공하지 않는 BITX 신호의 예시도.

도 9 및 10은 M-BITX의 '격자에 대한 스냅' 지표.

도 11은 도 10에 따라 구성된 M-BITX 신호를 사용한 결과도.

도 12는 '격자에 대한 스냅' 지표 및  $F_0X$ 의 평균 주파수를 가진 M-BITX 신호를 생성하기 위해 사용되는 회로도.

도 13은 서로 다른 주파수의 선택적인 세그먼트로 이루어진 M-BITX 신호의 예시도.

도 14는 격자 밀도 인자가 2인 경우에 발생되는 램프 및 M-BITX 신호도.

도 15는 격자 밀도 인자가 일보다 클 경우에 '격자에 대한 스냅' 지표의 적용 방법의 설명도.

도 16은 승산 계수 X 및 격자 밀도 인자 K가 주어질 때의 M-BITX 신호 발생 회로도.

도 17은 M-램프 신호 및 3-비트 D/A 변환기(DAC)로부터 얻을 수 있는 전압(200) 설명도.

도 18은 DAC에 의해 생산된 M-램프 신호에 적용되는 '격자에 대한 스냅' 개념도.

도 19는 격자에 대한 스냅 지표를 가진 M-램프 신호의 동작도.

도 20a 및 20b는 격자에 대한 스냅 지표를 가진 M-BITX 및 M-램프 신호의 동작도.

도 21은 격자에 대한 스냅 지표를 가진 M-램프 신호의 발생 회로도.

도 22는 본 발명에 따른 화상 센서( $3 \times 3$  픽셀 어레이를 가진). 상기 어레이에는 데이터 압축에 대한 본 발명의 방법을 사용한다.

도 23은 본 발명에 따른  $16 \times 16$  화상 픽셀 어레이. 상기 어레이에는 4개의  $8 \times 8$  픽셀 블록의 데이터를 처리한다.

도 24는 M-램프 및 M-BITX 신호를 어레이 내의 적당한 행 및 열에 발송하기 위해 스위치 행렬이 사용되는 본 발명의 실시예.

도 25는 데이터를  $3 \times 4$  픽셀 블록으로 처리하는  $12 \times 12$  화상 픽셀 어레이.

도 26a-26b는 단일 기울기 ADC의 동작도.

도 27은 ADC에 사용된 SS-램프 신호의 기울기(전압/시간)를 변화시킴으로써 단일 기울기 ADC에 승산을 실행하는 본 발명의 방법.

도 28은 ADC에 사용된 SS-주파수 신호의 주파수를 변화시킴으로써 단일 기울기 ADC에 승산을 실행하는 본 발명의 방법.

도 29는 동시 A/D 변환 및 데이터 압축을 위해 단일 기울기 ADCs를 사용하는 화상 픽셀 어레이.

도면

도면1

도면2

도면3

도면4

| 도. 3에 대한 진리표   |           |

|----------------|-----------|

| 범위 내<br>아날로그 값 | 디지털<br>출력 |

| A-B            | 1         |

| B-C            | 0         |

| C-D            | 1         |

| D-E            | 0         |

| E-F            | 1         |

## 도면5

도면6

도면7

도면8

도면9

도면10

도면11

도면12

도면13

도면14

도면15

도면16

도면17

도면18

도면19

도면20a

## 도면20b

## 도면21

## 도면22

도면23

도면24

도면25

도면26a

도면26b

도면27

도면28

도면29