(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第4065503号

(P4065503)

(45) 発行日 平成20年3月26日(2008.3.26)

(24) 登録日 平成20年1月11日(2008.1.11)

(51) Int.Cl.

H04N 1/393 (2006.01)

G06T 3/40 (2006.01)

F 1

H04N 1/393

G06T 3/40

A

請求項の数 4 (全 43 頁)

|              |                              |

|--------------|------------------------------|

| (21) 出願番号    | 特願2002-202918 (P2002-202918) |

| (22) 出願日     | 平成14年7月11日 (2002.7.11)       |

| (65) 公開番号    | 特開2004-48372 (P2004-48372A)  |

| (43) 公開日     | 平成16年2月12日 (2004.2.12)       |

| 審査請求日        | 平成17年6月30日 (2005.6.30)       |

| (31) 優先権主張番号 | 特願2001-250406 (P2001-250406) |

| (32) 優先日     | 平成13年8月21日 (2001.8.21)       |

| (33) 優先権主張国  | 日本国 (JP)                     |

| (31) 優先権主張番号 | 特願2001-250407 (P2001-250407) |

| (32) 優先日     | 平成13年8月21日 (2001.8.21)       |

| (33) 優先権主張国  | 日本国 (JP)                     |

| (31) 優先権主張番号 | 特願2002-138343 (P2002-138343) |

| (32) 優先日     | 平成14年5月14日 (2002.5.14)       |

| (33) 優先権主張国  | 日本国 (JP)                     |

|           |                                            |

|-----------|--------------------------------------------|

| (73) 特許権者 | 000001007<br>キヤノン株式会社<br>東京都大田区下丸子3丁目30番2号 |

| (74) 代理人  | 100090538<br>弁理士 西山 恵三                     |

| (74) 代理人  | 100096965<br>弁理士 内尾 裕一                     |

| (72) 発明者  | 上田 浩市<br>東京都大田区下丸子3丁目30番2号キヤ<br>ノン株式会社内    |

|           | 審査官 仲間 晃                                   |

最終頁に続く

(54) 【発明の名称】画像処理装置、画像入出力装置、変倍処理方法、及びメモリ制御方法

## (57) 【特許請求の範囲】

## 【請求項 1】

入力した画像データに変倍処理を施す画像処理装置であつて、

入力した画像データを分割処理して所定の大きさの複数のタイル画像データを生成する分割手段と、

前記分割手段により生成された複数のタイル画像データを圧縮処理して該圧縮処理されたタイル画像データを含む複数のデータパケットを生成する圧縮手段と、

前記圧縮手段により生成された複数のデータパケットを記憶する記憶手段と、

前記記憶手段に記憶された複数のデータパケットの各々に含まれるタイル画像データを読み出して伸張処理する伸張手段と、

前記伸張手段により伸張処理された複数のデータパケットに基づく複数のタイル画像データを変倍処理して前記所定の大きさの複数のタイル画像データを生成する変倍手段と、

前記記憶手段に記憶された複数のデータパケットに基づいて前記変倍処理を実行させる場合に、前記伸張手段、前記変倍手段、前記圧縮手段、前記記憶手段の順で前記複数のデータパケットを転送させるためのヘッダ情報を前記複数のデータパケットに付加する付加手段とを有し、

前記伸張手段は前記記憶手段に記憶された複数のデータパケットの各々に含まれるタイル画像データを伸張処理して、該伸張処理されたタイル画像データを含む複数のデータパケットを前記ヘッダ情報を基づいて前記変倍手段へ転送し、

前記変倍手段は前記伸張手段から転送された前記複数のデータパケットの各々に含まれ

10

20

るタイル画像データを変倍処理して、該変倍処理により生成されたタイル画像データを含む複数のデータパケットを前記ヘッダ情報に基づいて前記圧縮手段へ転送し、

前記圧縮手段は、前記変倍手段から転送された前記複数のデータパケットの各々に含まれるタイル画像データを圧縮処理して、該圧縮処理されたタイル画像データを含む複数のデータパケットを前記ヘッダ情報に基づいて前記記憶手段に転送することを特徴とする画像処理装置。

**【請求項 2】**

前記伸張手段により伸張処理された複数のデータパケットをパケット単位で画像処理して複数のタイル画像データを生成する画像処理手段を複数有し、

前記データパケットは、前記複数の画像処理手段及び前記変倍手段のいずれで処理されるべきかを示すヘッダ情報を含むことを特徴とする請求項1に記載の画像処理装置。 10

**【請求項 3】**

前記複数の画像処理手段及び前記変倍手段が接続されるバスと、

前記データパケットに含まれるヘッダ情報を基づいて、前記データパケットを前記複数の画像処理手段及び前記変倍手段のいずれかに転送するバスインターフェースとを有することを特徴とする請求項2に記載の画像処理装置。

**【請求項 4】**

変倍処理を実行する変倍部と、圧縮処理を実行する圧縮部と、伸張処理を実行する伸張部とを有する画像処理装置の変倍処理方法であって、

入力した画像データを分割処理して所定の大きさの複数のタイル画像データを生成する分割工程と、 20

前記分割工程により生成された複数のタイル画像データを前記圧縮部にて圧縮処理して該圧縮処理されたタイル画像データを含む複数のデータパケットを生成する第1圧縮工程と、

前記第1圧縮工程により生成された複数のデータパケットをメモリに書き込む第1書き込み工程と、

前記メモリに記憶された複数のデータパケットに基づいて前記変倍処理を実行させる場合に、前記伸張部、前記変倍部、前記圧縮部、前記メモリの順で前記複数のデータパケットを転送させるためのヘッダ情報を前記複数のデータパケットに付加する付加工程と、

前記メモリに書き込まれた複数のデータパケットの各々に含まれるタイル画像データを前記伸張部にて伸張処理して、該伸張処理されたタイル画像データを含む複数のデータパケットを前記ヘッダ情報を基づいて前記変倍部へ転送する伸張工程と、 30

前記伸張工程により前記伸張部から前記変倍部に転送された前記複数のデータパケットの各々に含まれるタイル画像データを前記変倍部にて変倍処理して該変倍処理により生成された前記所定の大きさのタイル画像データを含む複数のデータパケットを前記ヘッダ情報を基づいて前記圧縮部に転送する変倍工程と、

前記変倍工程により前記変倍部から前記圧縮部に転送された前記複数のデータパケットの各々に含まれるタイル画像データを圧縮処理して該圧縮処理されたタイル画像データを含む複数のデータパケットを前記ヘッダ情報を基づいて前記メモリに転送する第2圧縮工程と、 40

前記第2圧縮工程にて前記圧縮部から前記メモリに転送された前記複数のデータパケットを前記メモリに書き込む第2書き込み工程と、

を有することを特徴とする変倍処理方法。

**【発明の詳細な説明】**

**【0001】**

**【発明の属する技術分野】**

本発明は、入力した画像データに画像処理、特に変倍処理を施すための画像処理装置、画像入出力装置、変倍処理方法、及びメモリ制御方法に関する。

**【0002】**

**【従来の技術】**

画像の変倍処理は、デジタル複写機等の画像入出力装置や、パソコン用コンピュータ等の情報処理装置において、非常に重要な機能となっている。特に画像入出力装置においては、頻繁に用いられる機能であり、通常、専用の変倍回路が設けられている。

#### 【0003】

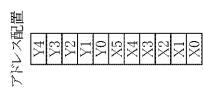

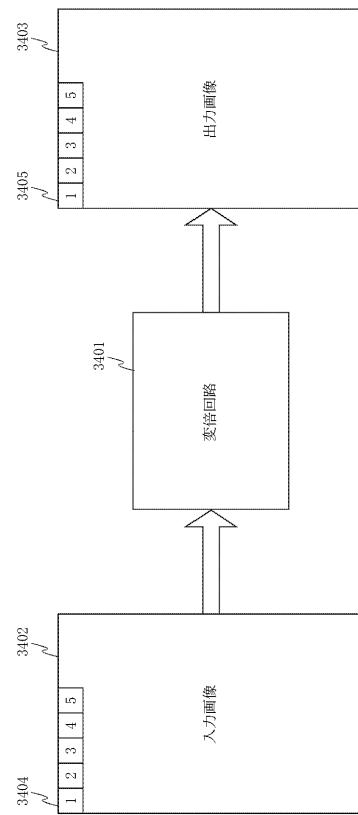

従来の変倍回路の動作概略を図34に示す。図34において、3401は変倍回路を示し、3402は変倍される原画像(入力画像)全体を、3403は変倍後の出力画像全体を示している。また、3404は変倍前、3405は変倍後の画像の各画素を示している。各画像の内部に示された各番号は変倍回路3401に入力或いは出力される順番を示す。

#### 【0004】

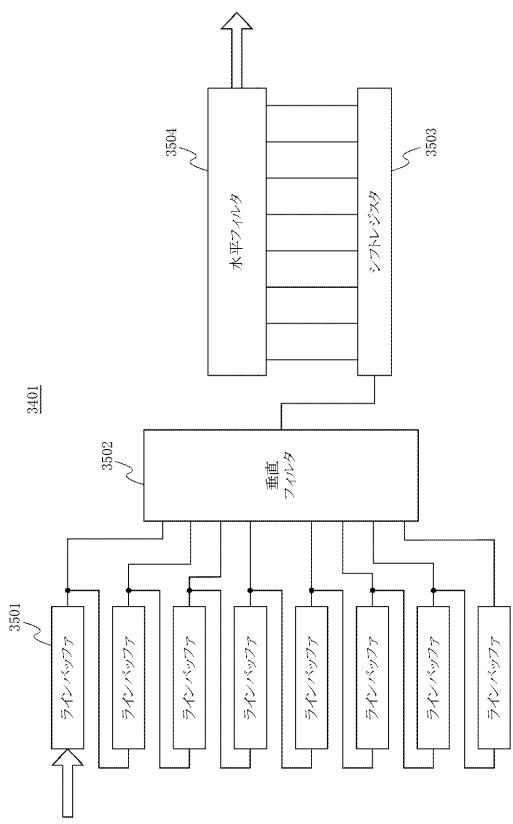

図35は、従来の変倍回路3401の詳細な構成を示すブロック図である。図35において、3501はラインバッファ、3502は垂直フィルタ、3503はシフトレジスタ、3504は水平フィルタである。水平及び垂直フィルタの詳細な構成については図36に示す。

10

#### 【0005】

図34に示す従来の変倍回路3401は、1枚の画像における画像データ(ピクセルデータ)をスキャン順に受け取って、変倍結果をスキャン順に出力する。この変倍回路3401の内部における処理について図35を用いて説明する。まず、外部から変倍回路3401に入力されたピクセルデータは、ラインバッファ3501に蓄積される。そして、垂直フィルタ3502は水平方向に一致した位置でかつ垂直方向が1ラインずつシフトさせた複数の画像データ(図35では8ライン分)のフィルタ処理を行う。垂直方向のフィルタ処理を行った後、その結果の画像データは水平方向の変倍処理を行うべくシフトレジスタ3503に入力され、垂直方向と同様に画像データ(図35では8画素)フィルタ処理が行われる。

20

#### 【0006】

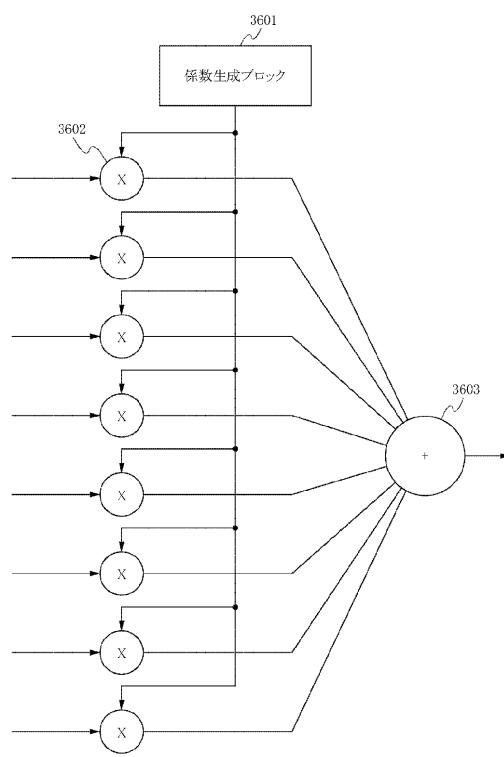

図36は、フィルタ処理回路の動作を示す図である。図36において、3601はフィルタ係数発生回路、3602は乗算回路、3603は加算回路である。ここで、フィルタ係数発生回路3601からフィルタ係数が出力され、一方で、垂直或いは水平方向に連続した画像データが、ラインバッファ3501或いはシフトレジスタ3503から入力される。そして、画像データの各々の画素と、その画素に対応するフィルタ係数との掛け算を乗算回路3602で行った後、すべての演算結果が加算回路3603で加算されて出力される。以上が従来の変倍処理の構成である。

30

#### 【0007】

ところで、特開平2002-8002号公報に開示されるように、各処理ブロックがタイル単位で画像処理を行う画像入出力装置が本出願人より提案されている。この画像入出力装置の画像処理部の構成はICチップ化に適しており、その処理ブロックの一つとして変倍回路を備えることができる。

30

#### 【0008】

##### 【発明が解決しようとする課題】

しかしながら、昨今の取り扱う画像サイズの巨大化に伴い、上記従来例のような変倍回路では、変倍処理に必要なバッファが非常に大きなものとなる。図35の回路の場合、ラインバッファは8ライン分必要なので、例えばA4、600dpiの原画像の場合、約7000画素分のバッファが必要となる。

40

#### 【0009】

そして、特に上述したタイル単位で画像データを管理する画像入出力装置に変倍回路を実装する場合、従来の変倍回路では、1つのチップ内に変倍回路を組み込もうとしても、ラインバッファも巨大なものとなるので、IC化に際しては現実的ではなかった。

#### 【0010】

また、変倍回路を含むICチップにラインバッファを持たず、管理可能なチップ外部のメモリをラインバッファの代わりとして利用する装置構成も考えられるが、この構成のみでは、外部メモリへのアクセスが集中し、変倍回路の処理速度が制限されることがある。

50

**【 0 0 1 1 】**

本発明は上述した問題点を解決するためのものであり、少ないメモリ容量でタイル単位に変倍処理を行える画像処理装置及び画像処理装置の変倍処理方法を提供することを目的とする。

**【 0 0 1 2 】**

また、外部メモリを用いた画像処理、特に変倍処理を行う際の処理速度を向上させた画像処理装置及び画像処理装置のメモリ制御方法を提供することを目的とする。

**【 0 0 1 3 】**

また、簡単な構成で変倍処理と画像データの書き込み処理を行う際のメモリ管理を容易に効率よく行える画像処理装置及び画像処理装置のメモリ制御方法を提供することを目的とする。 10

**【 0 0 1 4 】**

また、回路のクロック速度を上げることなく、変倍処理を行う際の処理速度を向上させた画像処理装置及び画像処理装置の変倍処理方法を提供することを目的とする。

**【 0 0 1 5 】**

また、外部メモリを用いた変倍処理におけるデータ管理を容易にした画像入出力装置及び画像入出力装置の変倍処理法を提供することを目的とする。

**【 0 0 1 6 】**

また、I Cチップ内の回路構成にはほとんど影響を与えることなく、様々な変倍率や画像サイズに対応した変倍処理を可能とした画像入出力装置及び画像入出力装置の変倍処理法を提供することを目的とする。 20

**【 0 0 1 7 】****【課題を解決するための手段】**

上記目的を達成するために、本発明の画像処理装置は、入力した画像データに変倍処理を施す画像処理装置であって、入力した画像データを分割処理して所定の大きさの複数のタイル画像データを生成する分割手段と、前記分割手段により生成された複数のタイル画像データを圧縮処理して該圧縮処理されたタイル画像データを含む複数のデータパケットを生成する圧縮手段と、前記圧縮手段により生成された複数のデータパケットを記憶する記憶手段と、前記記憶手段に記憶された複数のデータパケットの各々に含まれるタイル画像データを読み出して伸張処理する伸張手段と、前記伸張手段により伸張処理された複数のデータパケットに基づく複数のタイル画像データを変倍処理して前記所定の大きさの複数のタイル画像データを生成する変倍手段と、前記記憶手段に記憶された複数のデータパケットに基づいて前記変倍処理を実行させる場合に、前記伸張手段、前記変倍手段、前記圧縮手段、前記記憶手段の順で前記複数のデータパケットを転送させるためのヘッダ情報を前記複数のデータパケットに付加する付加手段とを有し、前記伸張手段は前記記憶手段に記憶された複数のデータパケットの各々に含まれるタイル画像データを伸張処理して、該伸張処理されたタイル画像データを含む複数のデータパケットを前記ヘッダ情報に基づいて前記変倍手段へ転送し、前記変倍手段は前記伸張手段から転送された前記複数のデータパケットの各々に含まれるタイル画像データを変倍処理して、該変倍処理により生成されたタイル画像データを含む複数のデータパケットを前記ヘッダ情報に基づいて前記圧縮手段へ転送し、前記圧縮手段は、前記変倍手段から転送された前記複数のデータパケットの各々に含まれるタイル画像データを圧縮処理して、該圧縮処理されたタイル画像データを含む複数のデータパケットを前記ヘッダ情報に基づいて前記記憶手段に転送することを特徴とする。 30

**【 0 0 2 3 】**

また、本発明の変倍処理方法は、変倍処理を実行する変倍部と、圧縮処理を実行する圧縮部と、伸張処理を実行する伸張部とを有する画像処理装置の変倍処理方法であって、入力した画像データを分割処理して所定の大きさの複数のタイル画像データを生成する分割工程と、前記分割工程により生成された複数のタイル画像データを前記圧縮部にて圧縮処理して該圧縮処理されたタイル画像データを含む複数のデータパケットを生成する第1圧 40

縮工程と、前記第1圧縮工程により生成された複数のデータパケットをメモリに書き込む第1書込工程と、前記メモリに記憶された複数のデータパケットに基づいて前記変倍処理を実行させる場合に、前記伸張部、前記変倍部、前記圧縮部、前記メモリの順で前記複数のデータパケットを転送させるためのヘッダ情報を前記複数のデータパケットに付加する付加工程と、前記メモリに書き込まれた複数のデータパケットの各々に含まれるタイル画像データを前記伸張部にて伸張処理して、該伸張処理されたタイル画像データを含む複数のデータパケットを前記ヘッダ情報に基づいて前記変倍部へ転送する伸張工程と、前記伸張工程により前記伸張部から前記変倍部に転送された前記複数のデータパケットの各々に含まれるタイル画像データを前記変倍部にて変倍処理して該変倍処理により生成された前記所定の大きさのタイル画像データを含む複数のデータパケットを前記ヘッダ情報に基づいて前記圧縮部に転送する変倍工程と、前記変倍工程により前記変倍部から前記圧縮部に転送された前記複数のデータパケットの各々に含まれるタイル画像データを圧縮処理して該圧縮処理されたタイル画像データを含む複数のデータパケットを前記ヘッダ情報に基づいて前記メモリに転送する第2圧縮工程と、前記第2圧縮工程にて前記圧縮部から前記メモリに転送された前記複数のデータパケットを前記メモリに書き込む第2書込工程と、を有することを特徴とする。

10

#### 【0025】

また、本発明の変倍処理方法は、入力した画像データに変倍処理を施す画像処理装置のメモリ制御方法であって、入力した画像データを分割処理してメモリに複数のタイル画像データを書き込む書込工程と、前記メモリに書き込まれたタイル画像データを読み出す読出工程と、

20

前記読出工程において読み出されたタイル画像データを変倍処理する変倍工程と、指定された垂直方向の変倍率が  $n$  ( $n < 1$ ) である場合、前記メモリにおいて管理すべき垂直方向のタイル画像データの数を少なくとも  $(1/n) + 2$  個とし、前記読出工程及び前記書込工程における前記メモリへのアクセスに関する排他制御を行う排他制御工程とを有することを特徴とする。

#### 【0029】

##### 【発明の実施の形態】

以下、図面を参照しながら本発明に係る実施の形態を詳細に説明する。

#### 【0030】

##### (第1の実施形態)

まず、1枚の画像を複数のタイルに分割し、タイル単位で画像データを授受し管理する画像入出力装置の構成及び動作について説明する。この画像入出力装置は、一般にデジタル複写機と呼ばれるものであり、本発明に係る変倍処理を実行することができる。

#### 【0031】

##### [画像入出力装置の構成]

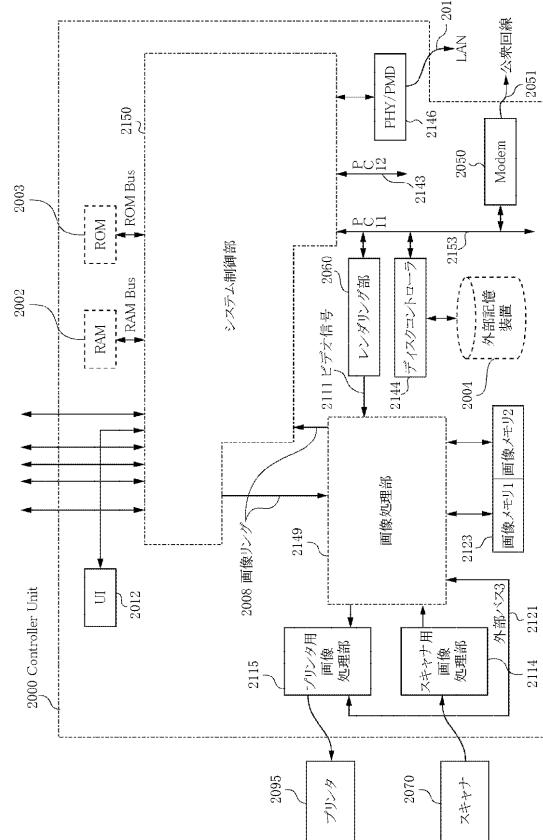

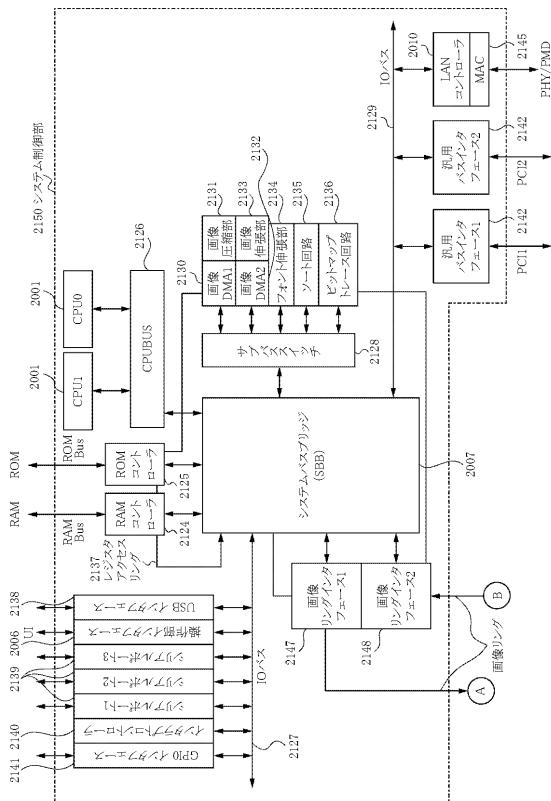

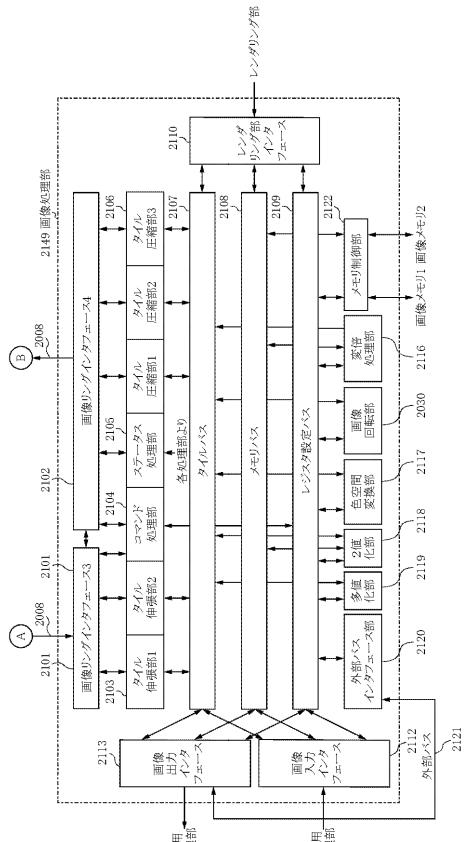

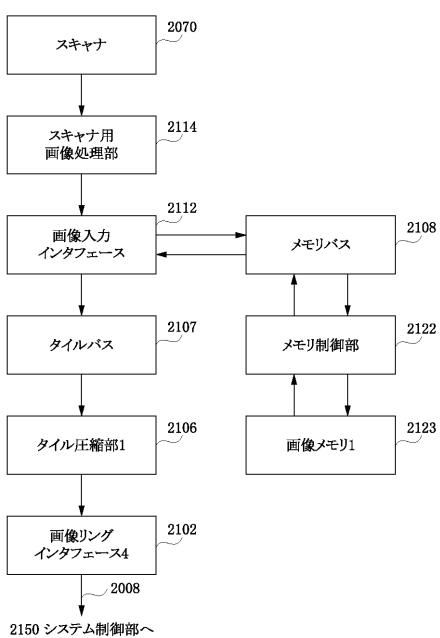

図1は、本発明を適用可能な画像入出力装置（デジタル複写機）の構成を説明するブロック図である。図2は、図1に示すシステム制御部の構成を説明する詳細ブロック図であり、図3は、図1に示す画像処理部の構成を説明する詳細ブロック図である。

#### 【0032】

図1～図3において、Controller Unit 2000は画像入力デバイスであるスキャナ2070や画像出力デバイスであるプリンタ2095と接続し、一方ではLAN2011や公衆回線（WAN）2051と接続することで、画像情報やデバイス情報の入出力、PDLデータのイメージ展開を行う為のコントローラである。

40

#### 【0033】

図2において、CPU2001はシステム全体を制御するプロセッサである。本実施形態では2つのCPUを用いた例を示す。これら二つのCPUは、共通のCPUバス2126に接続され、さらに、システムバスブリッジ2007に接続される。

#### 【0034】

システムバスブリッジ2007は、バススイッチであり、CPUバス2126、RAMコ

50

ントローラ 2124、ROMコントローラ 2125、I/Oバス 2127、サブバススイッチ 2128、I/Oバス 2129、画像リングインターフェース(1) 2147、画像リングインターフェース(2) 2148が接続される。

#### 【0035】

サブバススイッチ 2128は、第二のバススイッチであり、画像DMA(1) 2130、画像DMA(2) 2132、フォント伸張部 2134、ソート回路 2135、ビットマップトレース部 2136が接続され、これらのDMAから出力されるメモリアクセス要求を調停し、システムバスブリッジへの接続を行う。

#### 【0036】

図1において、RAM 2002は、CPU 2001が動作するためのシステムワークメモリであり、画像データを一時記憶するための画像メモリでもある。RAM 2002は、図2のRAMコントローラ 2124により制御され、本実施形態では、ダイレクトRDRAMを採用する例を示す。10

#### 【0037】

ROM 2003はブートROMであり、システムのブートプログラムが格納されている。ROM 2003は、図2のROMコントローラ 2125により制御される。

#### 【0038】

図2において、画像DMA(1) 2130は、画像圧縮部 2131に接続し、レジスタアクセスリング 2137を介して設定された情報に基づき、画像圧縮部 2131を制御し、RAM 2002上にある非圧縮データの読み出し、圧縮、圧縮後データの書き戻しを行う20。本実施形態では、JPEGを圧縮アルゴリズムに採用した例を示す。

#### 【0039】

画像DMA(2) 2132は、画像伸長部 2133に接続し、レジスタアクセスリング 2137を介して設定された情報に基づき、画像伸長部 2133を制御し、RAM 2002上にある圧縮データの読み出し、伸長、伸長後データの書き戻しを行う。本実施形態では、JPEGを伸長アルゴリズムに採用した例を示す。

#### 【0040】

フォント伸長部 2134は、LANインターフェース 2010等を介し外部より転送されるPDLデータに含まれるフォントコードに基づき、ROM 2003もしくは、RAM 2002内に格納された、圧縮フォントデータの伸長を行う。本実施形態では、FBEアルゴリズムを採用した例を示す。30

#### 【0041】

ソート回路 2135は、PDLデータを展開する段階で生成されるディスプレイリストのオブジェクトの順番を並び替える回路である。ビットマップトレース回路 2136は、ビットマップデータより、エッジ情報を抽出する回路である。

#### 【0042】

I/Oバス 2127は、内部I/Oバスの一種であり、標準バスであるUSBバスのコントローラ、USBインターフェース 2138、汎用シリアルポート 2139、インタラプトコントローラ 2140、GPIOインターフェース 2141が接続される。I/Oバス 2127には、バスアービタ(図示せず)が含まれる。40

#### 【0043】

操作部 I/F 2006は、図1の操作部(U/I) 2012のインターフェース部で、操作部 2012に表示する画像データを操作部 2012に対して出力する。また、操作部 2012から本システム使用者が入力した情報を、CPU 2001に伝える役割をする。

#### 【0044】

I/Oバス 2129は内部I/Oバスの一種であり、汎用バスインターフェース(1, 2) 2142と、LANコントローラ 2010が接続される。I/Oバス 2129にはバスアービタ(図示せず)が含まれる。

#### 【0045】

汎用バスインターフェース(1, 2) 2142は、2つの同一のバスインターフェースから成50

り、標準I/Oバスをサポートするバスブリッジである。本実施形態では、PCIバス2143, 2153を採用した例を示す。

**【0046】**

図1において、2004はハードディスクドライブ(HDD)で、システムソフトウェア、画像データを格納する。HDD2004は、ディスクコントローラ2144を介して一方のPCIバス2153に接続される。

**【0047】**

図2のLANコントローラ2010は、MAC回路2145、PHY/PMD回路2146を介しLAN2011に接続し、情報の入出力を行う。Modem2050は公衆回線2051に接続し、情報の入出力を行う。

10

**【0048】**

図2において、画像リングインターフェース(1)2147及び画像リングインターフェース(2)2148は、システムバスブリッジ2007と画像データを高速で転送する画像リング2008を接続し、タイル化後に圧縮されたデータをRAM2002とタイル画像処理部2149間で転送するDMAコントローラである。

**【0049】**

画像リング2008は、一対の単方向接続経路の組み合わせにより構成される。図3に示すように、画像リング2008は、タイル画像処理部2149内で、画像リングインターフェース(3)2101及び画像リングインターフェース(4)2102を介し、タイル伸長部(1, 2)2103、コマンド処理部2104、ステータス処理部2105、タイル圧縮部(1 - 3)2106に接続される。本実施形態では、タイル伸長部2103を2組、タイル圧縮部2106を3組実装する例を示す。

20

**【0050】**

タイル伸長部(1, 2)2103は、画像リングインターフェース(3)2101への接続に加え、タイルバス2107に接続され、画像リングより入力された圧縮後の画像データを伸長し、タイルバス2107へ転送するバスブリッジである。本実施形態では、JPEG及びパックビット方式による伸長アルゴリズムを採用した例を示す。

**【0051】**

タイル圧縮部(1 - 3)2106は、画像リングインターフェース(4)2102への接続に加え、タイルバス2107に接続され、タイルバス2107より入力された圧縮前の画像データを圧縮し、画像リング2008へ転送するバスブリッジである。本実施形態では、タイル伸長部と同じ様にJPEG及びパックビット方式による圧縮アルゴリズムを採用した例を示す。

30

**【0052】**

コマンド処理部2104は、画像リングインターフェースへの接続に加え、レジスタ設定バス2109に接続され、画像リングを介して入力したCPU2001より発行されたレジスタ設定要求を、レジスタ設定バス2109に接続される該当ブロックへ書き込む。また、CPU2001より発行されたレジスタ読み出し要求に基づき、レジスタ設定バスを介して該当レジスタより情報を読み出し、画像リングインターフェース2102に転送する。

**【0053】**

40

ステータス処理部2105は、各画像処理部の情報を監視し、CPU2001に対してインタラプトを発行するためのインタラプトパケットを生成し、画像リングインターフェース2102に出力する。タイルバス2107には上記ブロックに加え、以下の機能ブロックが接続される。

**【0054】**

レンダリング部インターフェース2110、画像入力インターフェース2112、画像出力インターフェース2113、多値化部2119、2値化部2118、色空間変換部2117、画像回転部2030、変倍処理部2116、レンダリング部インターフェース2110。

**【0055】**

レンダリング部インターフェース2110は、後述するレンダリング部2060により生

50

成されたビットマップイメージを入力するインタフェースとして機能をする。レンダリング部 2060 とレンダリング部インターフェース 2110 は、一般的なビデオ信号 2111 にて接続される。レンダリング部インターフェース 2110 は、タイルバス 2107 に加え、メモリバス 2108、レジスタ設定バス 2109 へ接続される。そして、レンダリング部インターフェース 2110 は、レジスタ設定バス 2109 を介して設定された所定の方法により、入力されたラスタ画像をタイル画像へ構造変換するとともにクロックの同期化を行い、タイルバス 2107 に対しタイル画像の出力をを行う。

#### 【0056】

画像入力インターフェース 2112 は、後述するスキャナ用画像処理部 2114 により補正画像処理されたラスタイメージデータを入力する。そして、画像入力インターフェース 2112 は、レジスタ設定バス 2109 を介して設定された所定の方法により、入力したラスタイメージデータをタイル画像へ構造変換するとともにクロックの同期化を行い、タイルバス 2107 に対しタイル画像の出力をを行う。10

#### 【0057】

画像出力インターフェース 2113 は、タイルバスからのタイル画像データ（データパケット）を入力し、入力したタイル画像データをラスタ画像へ構造変換するとともにクロックレートの変更を行い、ラスタ画像をプリンタ用画像処理部 2115 へ出力する。

#### 【0058】

画像回転部 2030 は画像データの回転を行う。変倍処理（解像度変換）部 2116 は画像の変倍処理（解像度の変更）を行う。変倍部 2116 は、本実施形態における主要部であり、その詳細については後述する。色空間変換部 2117 はカラー及びグレースケール画像の色空間の変換を行う。2 値化部 2118 は、多値（カラー、グレースケール）画像を2 値化する。多値化部 2119 は2 値画像を多値データへ変換する。20

#### 【0059】

外部バスインターフェース部 2120 は、画像リングインターフェース（1）2147、（3）2101、コマンド処理部 2104、レジスタ設定バス 2109 を介し、CPU 2001 により発行された、書き込み、読み出し要求を外部バス 2121 に変換出力するバスブリッジである。外部バス 2121 は本実施形態では、プリンタ用画像処理部 2115、スキャナ用画像処理部 2114 に接続されている。

#### 【0060】

メモリ制御部 2122 は、メモリバス 2108 に接続され、各画像処理部の要求に従い、あらかじめ設定されたアドレス分割により、画像メモリ（1，2）2123 に対して、画像データの書き込み、読み出し、必要に応じてリフレッシュ等の動作を行う。本実施形態では、画像メモリに SDRAM を用いた例を示す。30

#### 【0061】

図1において、スキャナ用画像処理部 2114 は、画像入力デバイスであるスキャナ 2070 によりスキャンされた画像データを補正画像処理する。

#### 【0062】

プリンタ用画像処理部 2115 では、プリンタ出力のための補正画像処理を行い、結果をプリンタ 2095 へ出力する。レンダリング部 2060 は PDL コードもしくは、中間ディスプレイリストをビットマップイメージに展開する。40

#### 【0063】

[画像入出力装置のユニット構成]

図1の画像入出力装置の Controller Unit 2000 は、1つのコントローラボードに構成されている。そして、システム制御部 2150、及び画像処理部 2149 は、このボード上にそれぞれ I C チップとして実装されている。この2つの I C チップ間のデータ転送は、画像リングを介して、後述の各パケットにより行なわれる。

#### 【0064】

また、画像メモリ（1，2）2123 は、画像処理部 2149 の外部メモリとして、同じくコントローラボード上に独立して設けられている。本実施形態において、このメモリは50

、ボード上のメモリスロットに対して着脱可能なカードの形態を有しており、必要に応じて異なる容量の別のメモリに差し替えることもできる。なお、画像メモリ 2123 は、カードの形態に限らず、コントローラボードに直接埋め込まれる I C チップの形態を有していてもよい。

#### 【0065】

##### [ネットワークシステムの構成]

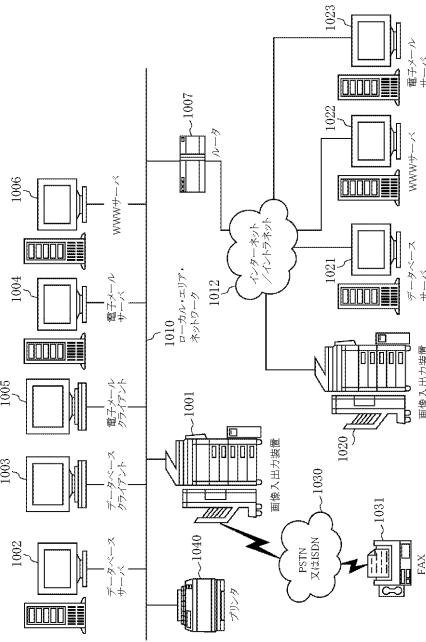

図4は、図1の画像入出力装置（デジタル複写機）を含むネットワークシステム全体の構成を説明する図である。

#### 【0066】

図4において、1001は図1の画像入出力装置であり、スキャナとプリンタから構成され、スキャナから読み込んだ画像をローカルエリアネットワーク（以下 LAN）1010に流したり、LANから受信した画像をプリンタによりプリントアウトできる。また、スキャナから読み込んだ画像を図示しない FAX 送信手段により、PSTN または ISDN 1030 に送信したり、PSTN または ISDN から受信した画像をプリンタによりプリントアウトできる。1002は、データベースサーバで、画像入出力装置1001により読み込んだ2値画像及び多値画像をデータベースとして管理する。

10

#### 【0067】

1003は前記データベースサーバ1002のデータベースクライアントで、データベースサーバ1002に保存されている画像データを閲覧／検索等できる。

20

#### 【0068】

1004は電子メールサーバで、画像入出力装置1001により読み取った画像を電子メールの添付として受け取ることができる。1005は、電子メールクライアントで、電子メールサーバ1004の受け取ったメールを受信し閲覧したり、電子メールを送信したりすることが可能である。

30

#### 【0069】

1006はHTML文書をLANに提供するWWWサーバで、画像入出力装置1001によりWWWサーバで提供されるHTML文書をプリントアウトできる。

#### 【0070】

1007はルータで、LAN1010をインターネット／イントラネット1012と連結する。インターネット／イントラネットに、前述したデータベースサーバ1002、WWWサーバ1006、電子メールサーバ1004、画像入出力装置1001と同様の装置が、それぞれ1020、1021、1022、1023として連結している。

30

#### 【0071】

一方、画像入出力装置1001は、PSTN または ISDN 1030 を介して、FAX 装置1031と送受信可能になっている。

#### 【0072】

また、LAN上にプリンタ1040も連結されており、画像入出力装置1001により読み取った画像をプリントアウト可能なように構成されている。

#### 【0073】

40

##### [パケット構成]

次に、本実施形態における画像データ処理に用いられるパケットのフォーマットについて説明する。本実施形態における Controller Unit 2000 は、画像データ、CPU2001によるコマンド、及び各画像処理部（2116, 2117, 2118, 2119, 2030）より発行される割り込み情報を、パケット化された形式で転送する。パケットデータには、以下の種類がある。

#### 【0074】

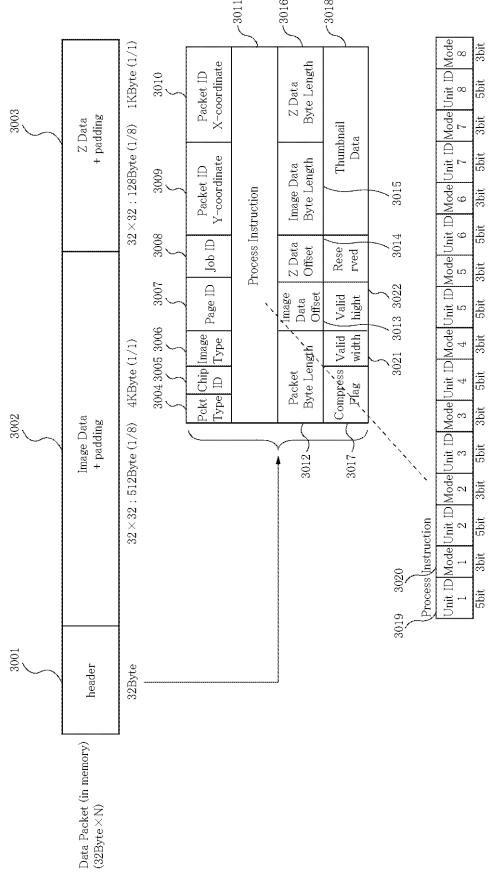

##### (1) データパケット（図5）

図5に示すデータパケットは所定画素数（本実施形態では 32 pixel × 32 pixel とする）で分割したタイル単位の画像データ3002と、後述する制御情報を格納するヘッダ情報3001と画像付加情報等3003とから構成される。

50

**【0075】**

以下、ヘッダ情報3001内に含まれる情報について説明を行う。

**【0076】**

PacketType3004はパケット・タイプを識別する。このPacketType3004にはリピートフラグが含まれており、画像データ3002が1つ前に送信したデータパケットの画像データと同一の場合、リピートフラグがセットされる。

**【0077】**

ChipID3005はパケットの送信先のChipを示す。ImageType3006は画像データのタイプを示す。PageID3007は画像データのページ番号を示す。

JobID3008はソフトウェアで画像処理を管理するためのジョブIDを格納する。

PacketIDY3009及びPacketIDX3010は、パケットに含まれる(又は指定される)画像データが、画像全体においてどの位置におけるタイルに相当するかを示す。ここでタイル位置はY方向(PacketIDY3009)とX方向(PacketIDX3010)を組み合わせ、YnXnで表される。

10

**【0078】**

データパケットは画像データが圧縮されている場合と非圧縮の場合とがある。本実施形態では、圧縮アルゴリズムとして、多値カラー(多値グレースケールを含む)の場合はJPEGを、2値の場合はパックビットを採用した例を示した。圧縮されている場合と非圧縮の場合との区別は、後述するCompressFlag3017で示される。

20

**【0079】**

ProcessInstruction3011は5ビットのUnitID3019と3ビットのMode3020との組である処理Unit1-8から構成され、各処理Unitは左(下位)から順番に処理される。処理されたUnitID及びModeは廃棄され、次に処理されるUnitID及びModeが左端に位置するように、ProcessInstruction全体が左に8ビットシフトされる。ProcessInstruction3011にはUnitID3019とMode3020との組が最大8組格納される。UnitID3019は各画像データ処理部を指定し、Mode3020は各画像データ処理部での動作モードを指定する。これにより、1つの画像データパケットに含まれる(又は指定される)画像データに対して、最大でのべ8つの画像データ処理部による連続処理を指定することが可能である。

30

**【0080】**

PacketByteLength3012はパケットのトータルバイト数を示す。ImageDataByteLength3015は画像データのバイト数を示す。ZDataByteLength3016は画像付加情報のバイト数を示す。ImageDataOffset3013、ZDataOffset3014はそれぞれ、画像データ及び画像付加情報の、パケットの先頭からのオフセットを示す。

**【0081】**

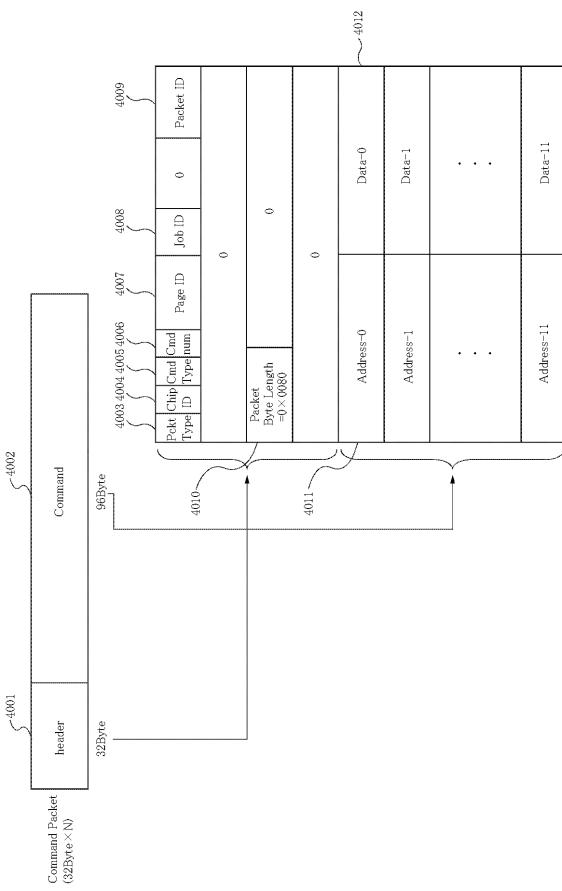

## (2) コマンドパケット(図6)

図6に示すコマンドパケットはレジスタ設定バス2109へのアクセスを行うためのものである。このパケットを用いることにより、CPU2001より画像メモリ(1,2)2123へのアクセスも可能である。また、コマンドパケットは、ヘッダ4001及びコマンド(パケットデータ部)4002から構成される。

40

**【0082】**

このヘッダ4001におけるChipID4004には、コマンドパケットの送信先となる画像処理部2149を表すIDが格納される。

**【0083】**

PageID4007及びJobID4008はそれぞれ、ソフトウェアで管理するためのPageID及びJobIDを格納する。PacketID4009は1次元で表され、DataPacketのX-coordinateのみを使用する。PacketByteLength4010は128Byte固定である。

50

**【0084】**

一方、パケットデータ部4002には、アドレス4011とデータ4012の組を1つのコマンドとして最大12個のコマンドを格納することが可能である。ライトカリードかのコマンドのタイプはCmdType4005で示され、コマンドの数はCmdnum4006で示される。

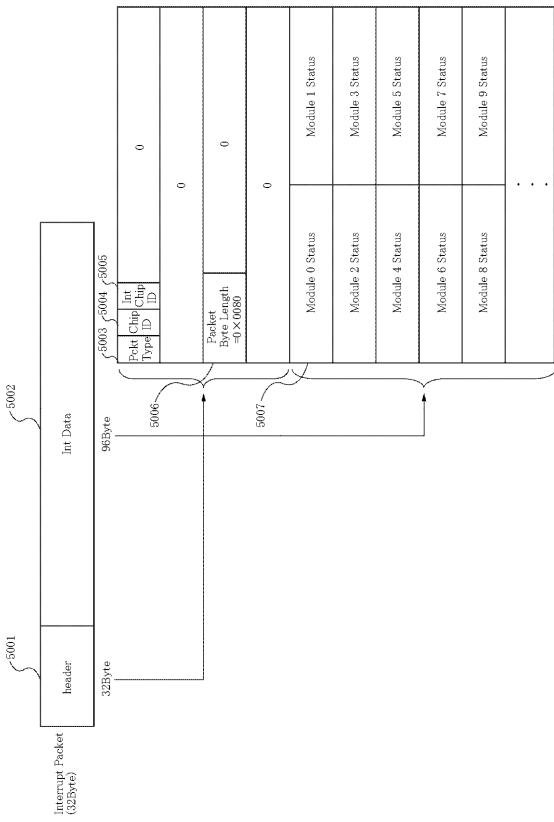

**【0085】****(3) インタラプトパケット(図7)**

図7に示すインタラプトパケットはヘッダ5001及びインタラプトデータ(パケットデータ部)5002からなり、画像処理部2149からCPU2001への割り込みを通知するため用いられる。

10

**【0086】**

ステータス処理部2105はインタラプトパケットを送信すると、次に送信の許可がされるまではインタラプトパケットを送信してはならない。PacketByteLengthh5006は128Byte固定である。

**【0087】**

パケットデータ部5002には、画像処理部2149の各々の内部モジュールのステータス情報5007が格納されている。ステータス処理部2105は画像処理部2149内のモジュールのステータス情報を集め、一括してシステム制御部2150に送ることができる。

20

**【0088】**

ChipID5004には、インタラプトパケットの送信先となるシステム制御部2150を表すIDが格納される。また、IntChipID5005にはインタラプトパケットの送信元となる画像処理部2149を表すIDが格納される。

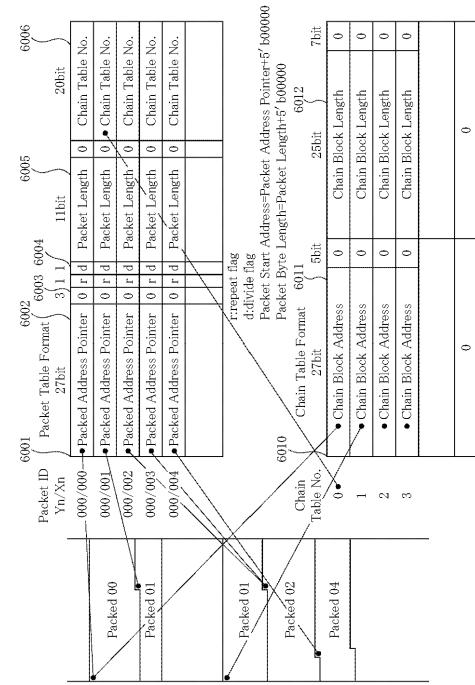

**【0089】****[パケットテーブルの構成]**

上述した各パケットは、図8に示すようなパケットテーブル6001によって管理される。このパケットテーブル6001は画像データと対で使用され、画像データが図1に示すRAM2002に展開されている場合は、RAM2002上で管理される。また、画像データが外部記憶装置2004に格納される場合には、このパケットテーブル6001も同時に外部記憶装置2004に格納される。外部記憶装置2004に格納された画像データが再びRAM2002に展開される場合、同時にこのパケットテーブル6001もRAM2002に読み出され、画像データが展開されるアドレス情報に応じてアドレス情報の書き換えが行われる。

30

**【0090】**

パケットテーブル6001の値(ポインタ及び長さ)に0を5bit付加すると、パケットの先頭Address(PacketStartAddress)6002、パケットのバイト長(PacketByteLength)6005となる。即ち、

$$\begin{aligned} \text{Packet Address Pointer } (27\text{bit}) + 5b00000 \\ = \text{Packet先頭Address} \\ \text{Packet Length } (11\text{bit}) + 5b00000 = \text{Packet Byte Length} \end{aligned}$$

40

となる。

**【0091】**

尚、パケットテーブル6001とチェーンテーブル(ChainTable)6010とは分割されないものとする。

**【0092】**

パケットテーブル6001は、常に走査方向に並んでおり、Yn/Xn=000/000, 000/001, 000/002, ...という順に並んでいる。このパケットテーブル6001のエントリは一意に1つのタイルを示す。また、Yn/Xmaxの次のエントリはYn+1/X0となる。

50

**【0093】**

ここで、パケットがひとつ前のパケットとまったく同じデータである場合は、そのパケットはメモリ上に格納されず、パケットテーブル6001のエントリに1つ前のエントリと同じPacket Address Pointer、Packet Lengthを格納する。

**【0094】**

つまり、1つのパケットデータを2つのテーブルエントリが指すようなかたちになる。この場合、2つ目のテーブルエントリのRepeat Flag 6003がセットされる。

**【0095】**

また、パケットがチェーンDMAにより複数に分断された場合、DivideFlag 6004をセットし、そのパケットの先頭部分が入っているチェーンブロックのチェーンテーブル番号6006をセットする。

**【0096】**

チェーンテーブル6010のエントリはChain Block Address 6011とChain Block Length 6012とから構成され、チェーンテーブルの最後のエントリにはChain Block Address 6011、Chain Block Length 6012共に0を格納しておく。

**【0097】****[データパケットによる画像入力処理]**

次に、スキャナ2070で読み取った画像データをタイル画像に分割し、タイル画像からデータパケットを生成し、RAM2002に格納する画像入力処理について説明する。

20

**【0098】**

図9は、画像入力処理に関するプロック間のデータの経路と処理手順を示す図である。以下では、図1-3に示したプロック図に加えて、この図9を参照しながら説明する。

**【0099】**

まず、スキャナ2070において画像の読み取りが行われると、読み取られた画像データはラスタデータとして順次スキャナ用画像処理部2114に転送される。スキャナ用画像処理部2114はラスタデータの順に必要な画像処理を行い、処理された画像データを画像入力インターフェース2112に転送する。画像入力インターフェース2112はラスタデータの順に転送されてくる画像データを、メモリバス2108を介してメモリ制御部2122に転送する。

30

**【0100】**

メモリ制御部2122は画像メモリ(1)2123にラスタの形式で展開していく。この画像メモリ(1)2123は最小容量としてラスタデータ32ライン分で構成されている。32ライン分の画像データが画像メモリ(1)2123に展開されると、画像入力インターフェース2112は32pixels×32ラインのタイル画像の単位で読み出しを開始する。このタイル画像の読み出しがメモリ制御部2122、メモリバス2108を介して行われる。

**【0101】**

画像入力インターフェース2112は、生成されたタイル画像3002にヘッダ3001とZデータ3003を附加して、図3に示すフォーマットのデータパケットを生成する。ここで、Process instruction 3001には、RAM2002に画像データを格納するための経路情報が記載される。

40

**【0102】**

次に、画像入力インターフェース2112は、タイルバス2107に対してタイル圧縮部(1)2106への接続を要求する。その後、画像入力インターフェース2112は、タイルバス2107によってタイル圧縮部(1)2106に接続されると、データパケットをタイル圧縮部(1)2106に転送する。

**【0103】**

タイル圧縮部(1)2106はデータパケットのタイル画像3002をJPEG圧縮し、

50

J P E G圧縮されたデータパケットを画像リングインタフェース(4)2102に転送する。そして、画像リングインタフェース2102(4)は画像リング2008を介して、システム制御部2150にデータパケットを転送する。システム制御部2150では、転送されてきたデータパケットをR A M 2 0 0 2に格納する。

#### 【0104】

このようにして、スキャナ2070で読み取った画像データからデータパケットが生成され、データ圧縮された後に、システム制御部2150のR A M 2 0 0 2に格納される。

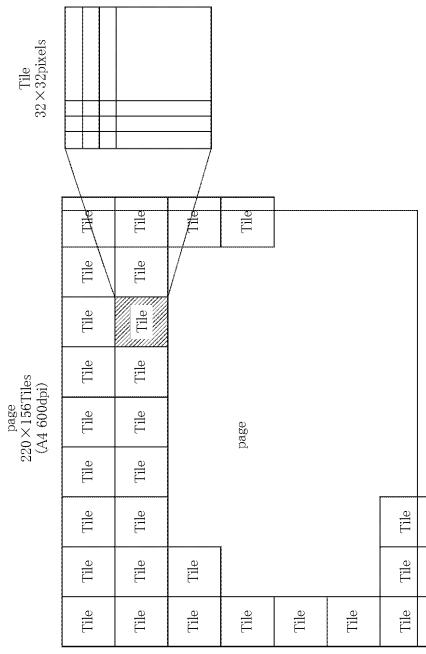

#### 【0105】

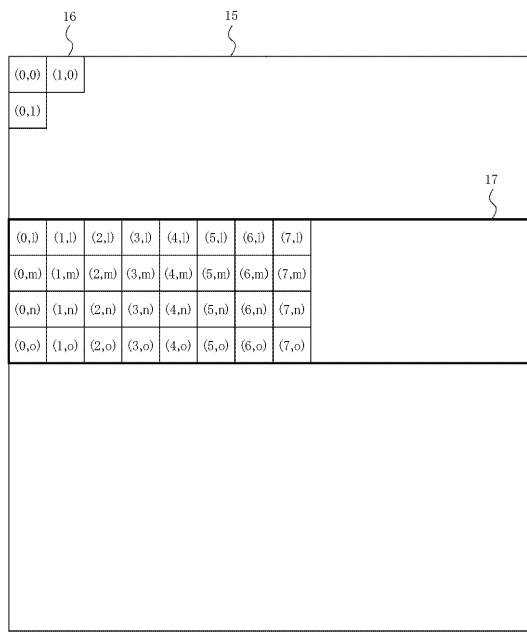

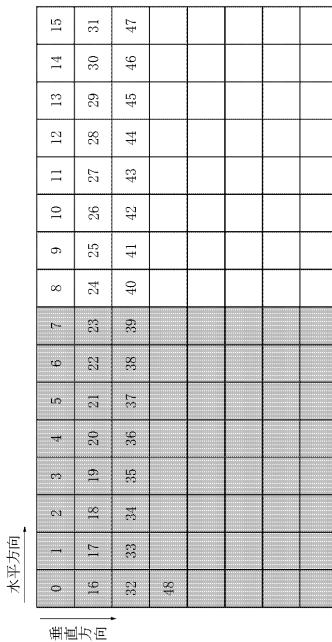

スキャナ2070で読み取った原稿画像のタイル画像への分割例を図10に示す。図10に示すように、1ページの原稿が複数のタイルに分割され、タイル毎にタイル画像データが生成される。ここで、A4サイズ( $210 \times 297\text{ mm}$ )の原稿をスキャナ2070で $600 \times 600\text{ dpi}$ の解像度で読み取ったとする。このとき、画像の画素数は、1インチが $25.4\text{ mm}$ であるとすると、縦4961画素×横7016画素となる。そして、 $32 \times 32$ 画素のタイルで分割したとすると、A4サイズの原稿から34320個のタイル画像データが生成される。

#### 【0106】

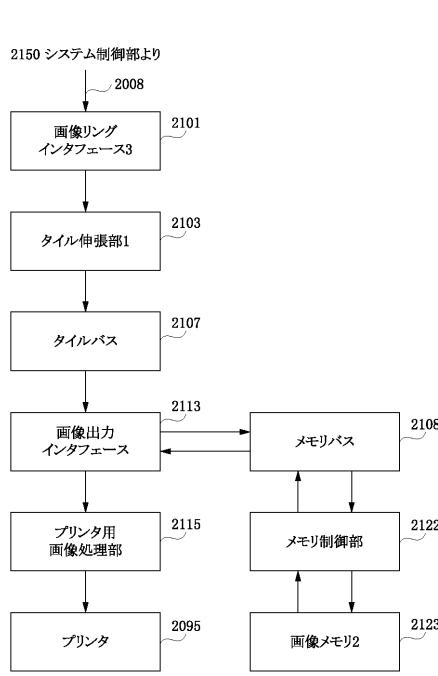

##### [データパケットによる画像出力処理]

続いて、システム制御部2150のR A M 2 0 0 2に格納されているデータパケットをもとにプリンタ2095でプリントする画像出力処理について説明する。

#### 【0107】

図11は、画像出力処理に関連するブロック間のデータの経路と処理手順を示している。以下の説明では、図1-3のブロック図に加え、この図11を適宜参照されたい。

#### 【0108】

まず、システム制御部2150から出力されたデータパケットは、画像リング2008を介して、画像リングインタフェース(3)2101に入力される。なお、ここでP r o c e s s I n s t r u c t i o n 3 0 1 1には、R A M 2 0 0 2の画像データをプリンタ2095で出力するための経路情報が記載されている。

#### 【0109】

画像リングインタフェース2101(3)は、タイル伸張部(1)2103を選択して、画像タイルデータを転送する。このタイル伸張部(1)2103の選択は前記したパケットフォーマットのP r o c e s s I n s t r u c t i o n 3 0 1 1に従って行われる。

#### 【0110】

タイル伸張部(1)2103はデータパケットのタイル画像をJ P E G伸張して、非圧縮の画像データに変換する。次にタイル伸張部(1)2103はタイルバス2107に対して、画像出力インタフェース2113への接続要求を行う。その後、タイル伸張部(1)2103は、タイルバス2107によって画像出力インタフェース2113に接続されると、データパケットを画像出力インタフェース2113に転送する。

#### 【0111】

データパケットを受け取った画像出力インタフェース2113は、メモリバス2108を介して、データパケットのタイル画像をメモリ制御部2122に転送する。メモリ制御部2122は、転送されてくるタイル画像を画像メモリ(2)2123に展開する。この展開はタイル単位で行うが、画像メモリ(2)2123の内部にはラスタデータの形式で行っていく。

#### 【0112】

このラスタデータがプリンタ2095で出力する32ライン分のラスタデータとして全て展開されると、画像出力インタフェース2113はラスタ順のデータ読み出しを開始する。このラスタデータの読み出しはメモリ制御部2122、メモリバス2108を介して行われる。ラスタ順にデータを読み出した画像出力インタフェース2113は、このデータをプリンタ用画像処理部2115に転送する。そして、ラスタデータを受け取ったプリンタ2095はラスタデータに基づいてプリントする。

10

20

30

40

50

**【0113】****[画像入出力装置の複合処理]**

本実施形態では、上述した画像入力処理と画像出力処理を組み合わせることによって、スキャナ2070とプリンタ2095を用いた複写処理を行うことができる。

**【0114】**

また、上記画像入力処理を実行後、RAM2002のデータパケットを外部記憶装置2004に格納することで、画像のファイリング処理を行うことができる。

**【0115】**

また、RAM2002のデータパケットを所定のフォーマットに変換してLANや公衆回線へ出力することにより、メール添付送信等、所定のプロトコルに従う画像送信処理やファクシミリ送信処理を行うことが可能である。10

**【0116】**

また、上記画像出力処理において、外部装置からの受信データに基づきレンダリング処理を行うレンダリング部2060からタイル画像を入力することにより、プリント処理を行うことができる。

**【0117】**

また、RAM2002のデータパケットを画像処理部2149において処理した後、再びRAM2002に格納するといった画像処理も可能であり、必要に応じて、この処理経路をとる画像処理と上記各処理と組み合わせて実行することもできる。

**【0118】**

以上、本実施形態の画像入出力装置で実行できる主な処理を述べたが、データパケットで画像処理を行う構成により、画像処理部2149内の各処理ブロックはタイル単位で確保される。したがって、画像処理部2149には、複数の処理に関する画像データを混在させることができる。すなわち、本実施形態の画像入出力装置は、複数の画像データに関する画像処理を並行に実行することができるものである。20

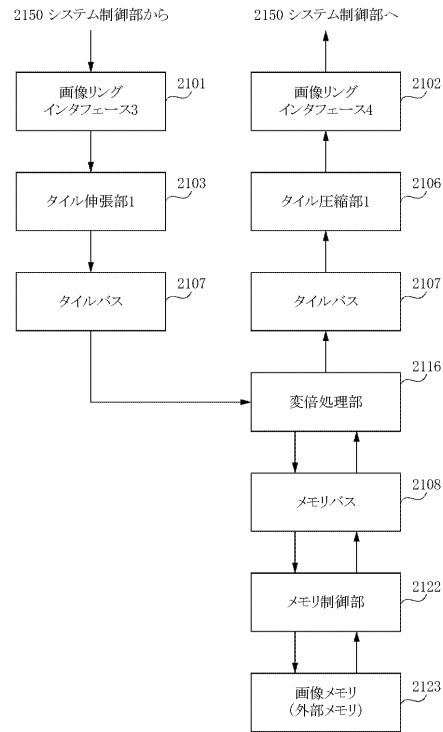

**【0119】****[データパケットによる変倍処理]**

次に、本実施形態におけるデータパケットによる変倍処理について詳細に説明する。

**【0120】**

以下では、RAM2002に格納されたデータパケット（タイル画像）を変倍処理部2116において150%伸張し、再びRAM2002に格納する、という処理を例にとって説明する。30

**【0121】**

図12は、データパケットの変倍処理に関するプロック間のデータの経路と処理手順を示す図である。以下では、図1-3に示したプロック図に加えて、この図12を参照しながら説明する。

**【0122】**

まず、システム制御部2150はRAM2002からデータパケットを読み出し、読み出したデータパケットを画像リングインターフェース(3)2147を介して、画像処理部2149に送出する。ここで、生成されたデータパケットのProcess Instruction 3011には、タイル伸張部(1)2103 变倍処理部2116で150%伸張 タイル圧縮部(1)2016で圧縮 RAM2002に格納、という処理を指定するためのデータが格納されている。具体的には、Unit ID 1にタイル伸張部2103のIDが格納され、Unit ID 2に变倍処理部2116のIDが格納され、Unit ID 3にタイル圧縮部(1)2016が格納され、Unit ID 4にRAM2002のIDが格納される。そして、Mode 1からMode 3には各処理部で行われる処理に対応した値が格納される。本実施形態では变倍処理部2116で行われる150%伸張はレジスタインタフェースにて指示されるためMode 2には何も格納されない。40

**【0123】**

次に、システム制御部2150から出力されたデータパケットは、画像リング2008を50

介して画像リングインタフェース(3)2101に入力される。この画像リングインタフェース(3)2101はタイル伸張部(1)2103を選択して、データパケットを転送する。ここで、タイル伸張部(1)2103の選択は、図5に示したパケットフォーマットのProcess Instruction 3011に従って行われる。

#### 【0124】

タイル伸張部(1)2103では転送されたデータパケットをJPEG伸張して、非圧縮の画像データに変換する。次に、タイル伸張部(1)2103は、タイルバス2107に対して変倍処理部2116への接続要求を行う。そして、タイル伸張部(1)2103は、タイルバス2107を介して変倍処理部2116に接続されると、データパケットを変倍処理部2116に転送する。

10

#### 【0125】

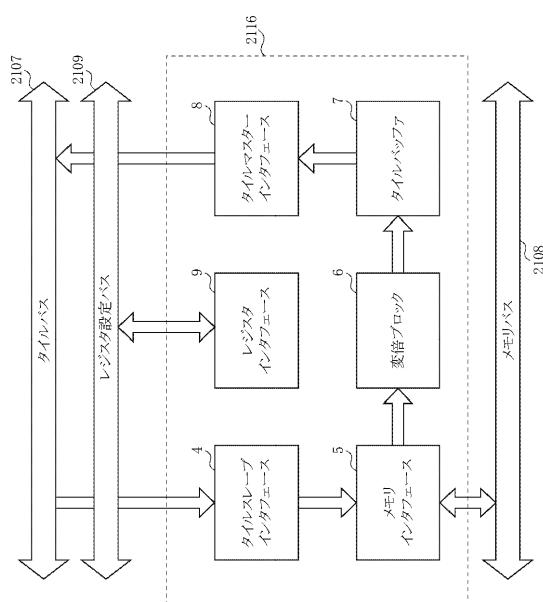

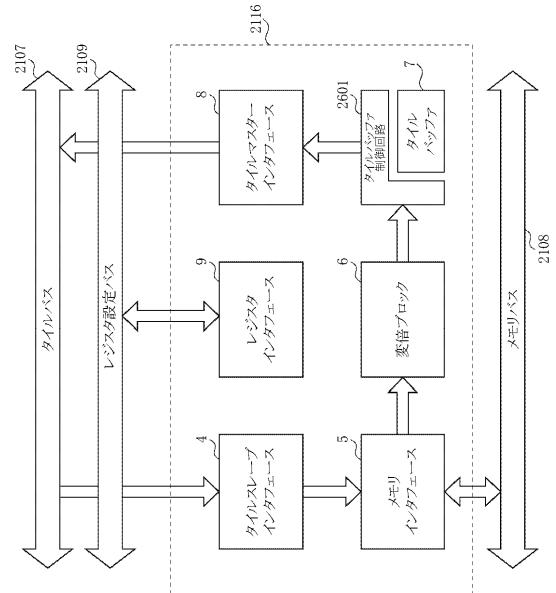

図13は、本実施形態における変倍処理部2116の構成を示す図である。変倍処理部2116は、自身が構成されるICチップの外部に設けられている画像メモリ(1,2)2123を利用して処理を実行する。以下、変倍処理部2116の内部処理を説明する際は、画像メモリ(1,2)を外部メモリ2123と呼ぶこととする。

#### 【0126】

図13において、4はタイルスレーブインタフェースであり、タイル伸張部(1)2103からタイルバス2107を介してデータパケットを受け取るためのインタフェースである。5はメモリインタフェースであり、タイルスレーブインタフェース4が受け取ったタイルデータを外部メモリ上にラスタ展開し、後述する変倍ブロックが必要とするタイルデータをラスタ展開されたメモリから読み出してくるためのインタフェースである。6は変倍ブロックであり、実際に変倍操作を行う。7はタイルバッファであり、変倍処理されたタイルデータを1タイル分蓄積する。8はタイルマスターインタフェースであり、変倍処理されたタイルデータをタイル圧縮部(1)2108にタイルバス2107経由で出力する。9は変倍ブロック6で変倍率及びフィルタの設定等を行うためのレジスタインタフェースである。

20

#### 【0127】

この変倍処理部2116においては、まずタイルスレーブインタフェース4にデータパケットが入力される。ここで、タイルスレーブインタフェース4は入力されたデータパケットのヘッダの内容を解析する。具体的には、データパケットのヘッダに含まれるPage ID 3007及びJob ID 3008を検出しデータの正当性を確認し、更に、Packet ID Y 3009及びPacket ID X 3010にてパケットの画像全体における位置を把握する。このとき、タイル伸張部2103によってProcess Instruction 3011は既に8ビットシフトされており、Unit ID 2及びMode 2はそれぞれ、Unit ID 1及びMode 1になっている。そして、メモリインタフェース5に対し位置情報とともにタイルデータを出力し、メモリインタフェース5は確保されている外部メモリ2123上にタイルデータを展開する。

30

#### 【0128】

変倍ブロック6は、メモリインタフェース5を介して入力されたタイルデータに対して150%の画像伸張を行う。この詳細な処理については後述する。

40

#### 【0129】

変倍処理されたタイルデータは順次、タイルバッファ7を介してタイルマスターインタフェース8に送られる。ここで、タイルマスターインタフェース8は、変倍ブロック6から送られてきたデータ長に関する情報に基づき、有効画素範囲情報(図3に示したデータパケットの、valid width 3021及びvalid height 3022)等をヘッダに記載する。具体的には、タイルマスターインタフェース8は、タイルデータに関して、valid width 3021及びvalid height 3022にそれぞれ、有効画素範囲情報としての値“32”及び“32”を記述する。

#### 【0130】

そして、タイルマスターインタフェース8は、各タイルデータと、それぞれのタイルデー

50

タに対応したヘッダとから新たにデータパケットを生成する。ここで、Process Instruction 3011は8ビットシフトされ、Unit ID 1にタイル圧縮部(1)2106のIDが記載され、Mode 1にはタイル圧縮部の処理を記述したMode 2の値がシフトされる。同様に、Unit ID 2以降のUnit ID及びModeも8ビットシフトが行われるが、今回の例では圧縮部での処理が最後であるため結果的には何も格納されない。

#### 【0131】

次に、タイルマスターインターフェース8は、タイルバス2107に対してシフト後のUnit ID 1に該当するタイル圧縮部(1)2106への接続を要求する。その後、タイルマスターインターフェース8は、タイルバス2107によってタイル圧縮部(1)2106に接続されると、データパケットをタイル圧縮部(1)2106に転送する。10

#### 【0132】

タイル圧縮部(1)2106ではデータパケットをJPEG圧縮し、JPEG圧縮されたデータパケットを画像リングインターフェース2102に転送する。画像リングインターフェース2102は画像リング2008を介して、システム制御部2150に転送する。そして、最後にシステム制御部2150が、転送されてきたデータパケットのタイルデータをRAM2002に格納することによって、一連の変倍処理が終了する。

#### 【0133】

##### [変倍処理の詳細]

ここで、変倍処理部2116における変倍ブロック6の変倍処理について更に詳述する。20

#### 【0134】

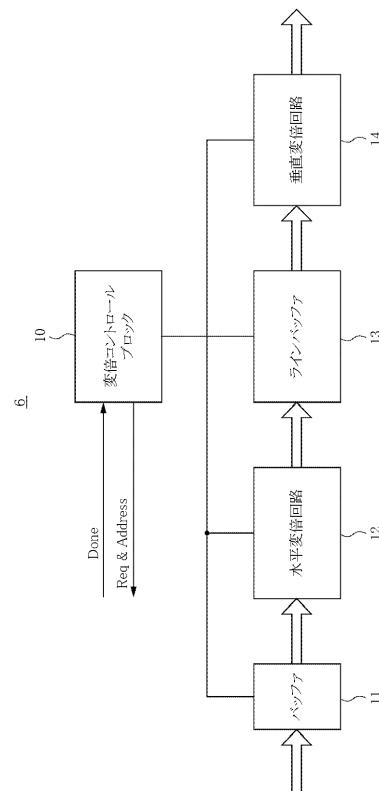

図14は、変倍ブロック6の詳細な構成を示すブロック図である。図14において、10は変倍コントロールブロックであり、変倍処理全体を制御する。11はバッファであり、メモリバス2108と変倍ブロック6間のタイルデータの幅及びスピード差を吸収する。12は水平変倍回路であり、水平方向の変倍処理を行う。13は水平方向の変倍処理結果を格納する複数のラインバッファであり、タイルの水平方向画素分の長さを持つ。14は垂直変倍回路であり、垂直方向の変倍処理を行う。

#### 【0135】

図15は、外部メモリ2123上に展開されるタイル単位のラスタデータを示す図である。図15において、15は処理される画像全体を示す。16はタイルに分割された画像を示し、タイル内の番号は原画像におけるタイルの位置をx y座標で示している。17は外部メモリ2123に実際に確保されるメモリエリアであり、垂直方向1タイル分の処理が終了する毎に、このエリア17は図の下側へ移動する。30

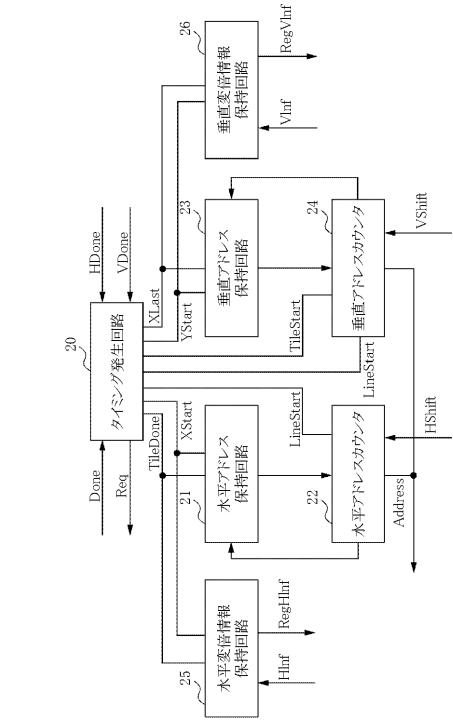

#### 【0136】

図16は、図14に示した変倍コントロールブロック10の詳細を示すブロック図である。図16において、20はタイミング発生回路、21は水平アドレス保持回路、22は水平アドレスカウンタ、23は垂直アドレス保持回路、24は垂直アドレスカウンタ、25は水平変倍情報保持回路、26は垂直変倍情報保持回路である。

#### 【0137】

まず、タイル伸張部(1)2103からタイルバス2107を介してタイルスレーブインターフェース4に入力されたタイルデータはメモリインターフェース5に転送され、メモリバス2108及びメモリ制御部2122を介して、一旦図15に示されるように1枚の画像の形に戻される。但し、外部メモリ2123は1枚の画像データ分を確保しているわけではなく、必要な垂直のメモリ確保量は変倍処理を行うのに必要とされる量、即ち、図15に示す太線で示されるエリアを展開できる程度の量が実際には確保される。更に、メモリインターフェース5は少なくとも垂直方向に1タイル分の画像データを外部メモリ2123に展開し終えた時点で変倍ブロック6にReady信号を通知する。40

#### 【0138】

一方、変倍ブロック6はメモリインターフェース5からReady信号を受けて変倍処理に必要なタイルデータのアドレスをメモリインターフェース5に通知し、外部メモリ212350

からの読み出し要求を行う。読み出し要求を受けたメモリインタフェース5はメモリバス2108を介して外部メモリ2123から該当する位置のタイルデータを読み出して変倍ブロック6へ送出する。これにより、変倍ブロック6はメモリインタフェース5より送出されたタイルデータ及びレジスタインタフェース9を介して設定された変倍率及びフィルタ係数に基づき変倍処理を実行する。そして変倍ブロック6は、変倍処理を行った結果をタイルバッファ7に蓄積し、1タイル分の変倍画像を生成し終えた段階でタイルマスターインタフェース8にDone信号を通知する。このDone信号を通知されたタイルマスターインタフェース8は、変倍結果のタイルデータをタイルバッファ7より読み出し、タイルバス2107を介して次の処理ブロック(タイル圧縮部)へ出力を行う。

## 【0139】

10

このように、図13に示すメモリインタフェース5より送出されたタイルデータは図14に詳細を示す変倍ブロック6のバッファ11でバス幅の違い及び画像の読み出し速度の違いを吸収し、水平変倍回路12で水平方向の変倍操作を行う。この変倍処理を行う回路は前述した図15に示したフィルタ回路と同じである。そして、水平方向に変倍処理された結果はラインバッファ13に格納され、垂直変倍回路14で垂直方向の変倍処理が行われた後、図13に示すタイルバッファ7に出力される。

## 【0140】

ここで、図16を参照しながら上述の変倍コントロールブロック10の詳細な構成及び動作について説明する。

## 【0141】

20

図1に示すメモリインタフェース5からDone信号を受けて、変倍コントロールブロック10のタイミング発生回路20は、バッファ11及び水平変倍回路12(図14)、図16に示す水平アドレスカウンタ22の各ブロックにLineStart信号を出力する。また、タイミング発生回路20は、ラインバッファ13及び垂直変倍回路14(図14)、図16に示す垂直アドレスカウンタ24の各ブロックにTileStart信号を出力する。さらに、タイミング発生回路20は、図16に示す水平アドレス保持回路21及び水平変倍情報保持回路25にXstart信号を出力し、垂直アドレス保持回路23及び垂直変倍情報保持回路26にYstart信号を出力して各ブロックを初期化させる。その後、メモリインタフェース5へタイルデータの読み出し要求信号Reqを出力する。また、水平アドレスカウンタ22及び垂直アドレスカウンタ24は、変倍処理を行うのに必要な読み出したいタイルデータのアドレスを示す信号Addressを出力する。

30

## 【0142】

ここで、外部メモリ2123よりタイルデータが読み出され、従来例と同様な水平方向の変倍処理がタイル単位で開始され、水平方向アドレスカウンタ22は原画像データのシフトが発生したことを示すShift信号に基づき、カウンタの値をカウントアップしていく。

## 【0143】

その後、タイル1ライン分の水平方向変倍処理が終了すると(HDone信号)、タイミング発生回路20は新たにバッファ11及び水平変倍回路12(図14)、図16に示す水平アドレスカウンタ22、垂直アドレスカウンタ24の各ブロックにLineStart信号を出力し、バッファ11及び水平変倍回路12を初期化する。これと同時に、図16に示す水平アドレスカウンタ22のカウント値を水平アドレス保持回路21にロードし、フィルタ係数生成回路には水平変倍情報保持回路に保持された値(RegHInf)をロードさせ、垂直アドレスカウンタ24の値をカウントアップさせる。そして、更新された水平及び垂直アドレスAddressと読み出し要求信号Reqとに基づき、メモリインタフェース5は次のラインの画像データを外部メモリ2123から読み出す。

40

## 【0144】

上述の操作により、図14に示すラインバッファ13に所定の変倍結果が揃うと垂直方向変倍回路14が動作を開始し、タイルのライン数分の変倍処理を終了するとタイル終了信号Vdone信号が図16に示すタイミング発生回路20に入力される。この信号に基づ

50

きタイミング発生回路 20 は水平アドレス保持回路 21 に次の水平アドレスカウンタの値を保持させる信号 T i l e D o n e を出力する。これらの処理を繰り返した後、変倍出力タイルが水平方向の最後のタイルを処理し終えたときにタイミング発生回路 20 は垂直アドレス保持回路 23 に対し、現在の垂直アドレスカウンタ 24 の値を保持させる信号 X 1 a s t を出力する。これにより、タイミング発生回路 20 は垂直アドレス保持回路 23 に現在の垂直アドレスカウンタ値を保持させる。

#### 【 0 1 4 5 】

次の出力タイルは水平方向アドレスが 0 であるので、タイミング発生回路 20 は T i l e S t a r t 信号を出力する前に水平アドレス保持回路 21 の値を初期化する信号 X s t a r t 信号を水平アドレス保持回路 21 に出力する。そして、水平アドレス保持回路 21 により保持されている水平アドレスが初期化された後、出力基準にて垂直方向に 1 タイル進んだタイルの変倍処理が実行される。ここで、ラインバッファ 13 は、変倍処理部 2116 の出力がタイル基準で実行されるため、1 タイル画像の水平方向画素数分の長さを持つ複数の（先の従来例と同様であれば 8 ライン分）ラインバッファで構成される。したがって、1 タイルの水平方向画素数がもし 32 画素であるとすれば先の従来例に比べおおよそ 200 分の 1 の量でよいことになる。

#### 【 0 1 4 6 】

以上説明したように、本実施形態によれば、必要とするラインバッファの長さはタイルの水平方向画素数分であり、垂直方向の変倍フィルタの構成を従来例と同様とすると、1 タイルの水平方向画素数を 32、処理できる最大画素の水平方向画素数を約 7000 画素とした場合、変倍処理部 2116 が必要とするラインバッファの量は従来例のおおよそ 200 分の 1 で済む。したがって、少ないラインバッファの量で従来例の変倍装置と同等な変倍処理が可能であり、変倍処理を含む複数の機能を 1 つの I C チップ内に実現するのに最適である。

#### 【 0 1 4 7 】

また、タイル画像のラスタ展開用のメモリを外部メモリとしているため、様々な変倍率やより大きな画像サイズへの対応を考えた場合にもタイルのサイズが同じであるならば I C チップ内の回路規模にはほとんど影響がなく対応が可能である。

#### 【 0 1 4 8 】

また、変倍処理部は、C P U 等から直接制御されることなく、データパケットのヘッダの座標情報に基づいて外部メモリ上の適切な領域に画像データをラスタ展開することができる、外部メモリを用いた変倍処理におけるデータの管理が容易である。

#### 【 0 1 4 9 】

##### （第 2 の実施形態）

第 1 の実施形態のような装置構成であっても、画像データがフルカラーである場合等においては、かなりの大きさの外部メモリが要求されることがある。例えば A 4 長手サイズ、600 d p i の画像では約 7000 画素となり、1 タイルの垂直方向画素数を 32 とすると、8 ピットフルカラーの画像データを 1 タイル幅でラスタ展開するには、おおよそ 1 M バイトの外部メモリが必要とされる。さらに、変倍処理として、特に垂直方向の縮小を行うためには複数のタイルが必要とされるため、ラスタ展開に必要とされるメモリ量は更に増大する。

#### 【 0 1 5 0 】

このような状況を考慮した場合、外部メモリに、レイテンシーの高い S R A M を用いるより、汎用の S D R A M を用いるほうがコスト的には好ましい。

#### 【 0 1 5 1 】

しかしながら、変倍回路においては変倍率によって変倍処理に必要な開始画素位置も必要とされる画素数も異なってくる。このため、画像メモリに S D R A M を用いた場合、必要な画素データ全てを 1 度にバースト転送することは処理上も、またバッファの量的にも問題があり、どうしてもメモリからの画素データの読み出し待ち時間により変換処理速度が上がらなくなってしまう。

10

20

30

40

50

**【0152】**

本実施形態では、変倍処理の開始時に、外部のメモリにラスタ展開された画像データの読み出しデータ量を制御することにより、例えばSDRAMのように読み出し待ち時間が生じる画像メモリを用いた場合でも、高速な変倍処理を実行可能とする。

**【0153】****[変倍処理の詳細]**

本実施形態の変倍処理部2116のブロック構成は、図13に示したものと同じである。

図17は、図13に示したメモリインタフェース5の詳細な構成を示す図である。

**【0154】**

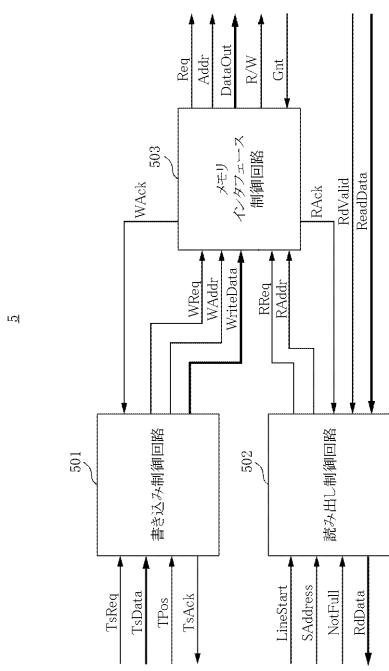

図17において、501は書き込み制御回路であり、図13に示したタイルスレーブインターフェース4からのデータを受け取り、外部メモリ2123への書き込み制御を行う。502は読み出し制御回路であり、図13に示した変倍ブロック6からの要求信号を受け取り、必要な画像データを外部メモリ2123から読み出す。503はメモリインタフェース制御回路であり、書き込み制御回路501及び読み出し制御回路502からの要求に応じて外部メモリ2123との通信を行い、データの書き込み又は読み出しを制御する。

10

**【0155】**

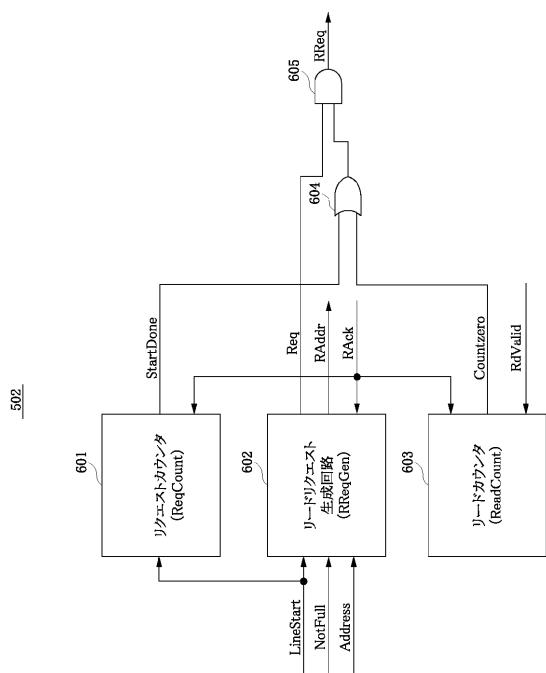

図18は、図17に示した読み出し制御回路502の詳細な構成を示す図である。図18において、601はリクエストカウンタ(ReqCount)であり、外部メモリの読み出しリクエスト数をカウントする。602はリードリクエスト生成回路(RReqGen)であり、変倍ブロック6のバッファ(FIFO)状態を示す信号(NotFull)や水平方向変倍開始パルス(LineStart)又は変倍に必要なデータの位置を示すメモリアドレス(Address)を受け取り、メモリ読み出し信号(Req)と読み出しあドレス(RAddr)を生成する。603はリードカウンタ(ReadCount)であり、読み出し要求から求められるデータ数と実際に読み出されたデータ数をカウントする。604はOR回路であり、リクエストカウンタ601から出力されるStartDone信号とリードカウンタ603から出力されるCountZero信号とを入力し、その論理和を出力する。605はAND回路であり、リードリクエスト生成回路602から出力されるReq信号とOR回路604から出力される信号とを入力し、その論理積を出力する。

20

**【0156】**

30

以上の構成を有する変倍回路の動作について図中に示す信号を参照しながら説明する。

**【0157】**

タイル伸張部(1)2103から、図13に示したタイルバス2107を経由してタイルスレーブインターフェース4に入力された画像データは、メモリインタフェース5に転送され、メモリバス2108及び外部メモリインタフェース2122を経由して、一旦図15に示した、1枚の画像の形に戻される。

**【0158】**

第1の実施形態と同様に、外部メモリ2123は1枚の画像データ分を確保しているわけではなく、必要な垂直のメモリ確保量は変倍処理を行うのに必要とされる量、即ち、図15に示した太線のエリアを展開できる程度の量が実際には確保される。更に、図1に示したメモリインタフェース5は、少なくとも垂直方向に1タイル分の画像データを外部メモリ2123に展開し終えた時点で変倍ブロック6にReady信号を通知する。

40

**【0159】**

一方、変倍ブロック6はメモリインタフェース5からのReady信号を受けて変倍処理に必要な画像データのアドレスをメモリインタフェース5に通知し、読み出し要求を行う。読み出し要求を受けたメモリインタフェース5はメモリバス2108経由で外部メモリ2123から該当する位置の画像データを読み出して変倍ブロック6へ送出する。これにより、変倍ブロック6はメモリインタフェース5より送出された画像データ及びレジスタインタフェース9を介して設定された変倍率及びフィルタ係数に基づき、変倍処理を行う。そして、その結果をタイルバッファ7に蓄積し、1タイル分の変倍画像を生成し終えた

50

段階で、タイルマスターインターフェース8にDone信号を通知する。Done信号を通知されたタイルマスターインターフェース8は、変倍結果の画像をタイルバッファ7より読み出し、タイルバス2107を介してタイル圧縮部(1)2106へ出力する。

#### 【0160】

ここで、メモリインターフェース5で授受される信号は図17に示したようになる。そして、図13に示したタイルスレーブインターフェース4より得られた画像データ(TsData)とタイルの番号(Tpos)が書き込み制御回路501で対応する外部メモリのアドレスに書き込むようにメモリインターフェース制御回路503に対して書き込みリクエスト信号(WReq)を出力する。そして、最終的に対応するメモリのアドレスへ画像データが書き込まれる。

10

#### 【0161】

一方、外部メモリ2123に書き込まれた画像データのうち、変倍ブロック6にて変倍処理に必要とされる画像データは、読み出し制御回路502において、変倍ブロック6より得られる水平方向変倍開始パルス(LineStart)と、それ以前に確定された読み出し開始アドレス(Address)と、変倍ブロック406のバッファ状態を示す信号(NotFull)とに基づき、読み出され始める。ここで、読み出し制御回路502で授受される信号は図17に示したようになる。

#### 【0162】

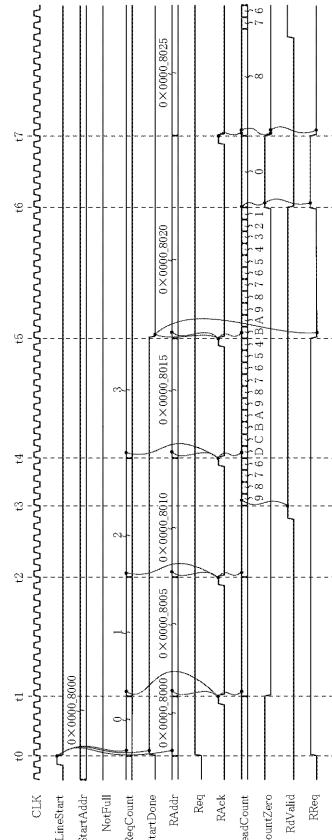

次に、この読み出し制御回路502の動作を図19に示すタイミングチャートを参照しながら説明する。まず、変倍ブロック6からの水平方向変倍開始信号(LineStart)パルスが“1”にアサートされる(t0)。この時、図18に示したリードリクエスト生成回路(RequestGen)602からの読み出しアドレス(Address)が変倍ブロック6に供給される読み出し開始アドレス(Address)としてラッチされる。そして、メモリ読み出し信号(Req)により変倍ブロック6のバッファ状態を示す信号(NotFull)のサンプリングが開始される。

20

#### 【0163】

同時に、リクエストの発行数をカウントするリクエストカウンタ(RequestCount)601の発行カウンタを“0”にリセットし、StartDone信号を“1”にセットする。StartDone信号によりAND回路605によるマスクを解除されたReq信号はRequest信号として図17に示すメモリインターフェース制御回路503に読み出し要求を通知する。これに応じて、メモリインターフェース制御回路503が外部メモリインターフェース2122と通信を行い、読み出し要求受理信号を受けると、Ack信号は“1”にセットされる。

30

#### 【0164】

このAck信号が“1”にアサートされたことを確認すると(t1)、リクエストカウンタ(RequestCount)601の発行カウンタを1増加し、リードリクエスト生成回路(RequestGen)602は読み出しアドレス(Address)の値を必要なだけインクリメントする(この例では8)。同時に、リードカウンタ(ReadCount)603が読み出し要求のビート数だけ、カウンタの値を増加させる。尚、カウンタの値が“0”になくなつたため、CountZero信号は“0”になるが、リクエストカウンタ(RequestCount)601から出力されるStartDone信号が“1”であるため、OR回路604の出力は“1”でありつづける。従つて読み出し要求信号Requestは“1”でありつづける。

40

#### 【0165】

次に、外部メモリインターフェース2122への読み出し要求を終えたメモリインターフェース405は新たな読み出し要求信号(Request)に基づき新たな読み出し要求を外部メモリインターフェース2122に発行したことをAck信号で通知する。Ack信号で読み出し要求が伝わつたことを検知すると、リクエストカウンタ(RequestCount)601、リードリクエスト生成回路(RequestGen)602からの読み出しアドレス(Address)、及びリードカウンタ(ReadCount)を上述のt1と同様にそれぞれ必

50

要な値だけ増加させる( t 2 )。尚、図 19 に示す例では、カウンタ及びアドレスの値は 16 進表記である。

#### 【 0 1 6 6 】

その後、外部メモリインターフェース 2122 より画像データの読み出し準備が整い、読み出しが開始されたことを示す信号( R d V a l i d )が“ 1 ”にアサートされると、リードカウンタ( R e a d C o u n t ) 603 はそのカウンタの値を現在値から“ 1 ”づつ減少させる( t 3 )。変倍ブロック 406 のバッファ( F I F O )にまだ余裕があり、読み出し要求( R R e q )が“ 1 ”であったため、メモリインターフェース 405 経由で外部メモリ 2123 に要求していた読み出し要求が受け付けられたことを示す R A c k 信号が帰ってくる。そして、先ほど( t 2 )と同様に、リクエストカウンタ( R e q C o u n t ) 10 、読み出しあドレス( R A d d r )が必要な値だけ増加される。

#### 【 0 1 6 7 】

但し、現時点で既にデータの読み出しが開始されているため、リードカウンタ( R e a d C o u n t ) 603 の値は、通常の増加分( この例では“ 8 ”)を増加させた値から読み出しによる減少分“ 1 ”があるため、直前の値より結果的に“ 7 ”だけ増加した値となる( t 4 )。

#### 【 0 1 6 8 】

変倍ブロック 6 のバッファ( F I F O )にまだ余裕があり、読み出し要巨 M 号( R R e q )が“ 1 ”であったため、メモリインターフェース 2122 経由で外部メモリ 2123 に要求していた読み出し要求が受け付けられたことを示す R A c k 信号が帰ってくる。そして、読み出しあドレス( R A d d r )が必要な値だけ増加され、リードカウンタ( R e a d C o u n t ) 603 も先ほどと同様に直前の値に対して“ 7 ”だけ増加する。 20

#### 【 0 1 6 9 】

一方、リクエストカウンタ( R e q C o u n t ) 601 は今回の読み出し要求の受付でバッファ( F I F O )の段数分の読み出しを終了するので現時点の値を保持し、 S t a r t D o n e 信号が“ 0 ”にデアサートされる。これにより、変倍ブロック 406 のバッファ( F I F O )状態を示す信号( N o t F u l l )の状態にかかわらずマスク用の信号 S t a r t D o n e 及び C o u n t Z e r o の両信号が共に“ 0 ”となる。従って OR 回路 604 の出力は“ 0 ”、 AND 回路 605 の出力も“ 0 ”となり、メモリインターフェース 2122 への読み出し要求信号は発生しなくなる( t 5 )。 30

#### 【 0 1 7 0 】

ここで、外部メモリ 2123 から順調に画像データの読み出しが行われ、読み出し要求分の画像データの読み出しが終了すると、リードカウンタ( R e a d C o u n t ) 603 は“ 0 ”となり、 C o u n t Z e r o 信号は“ 1 ”となる。これにより、読み出し要求信号( R R e q )のマスクが解除され、新たな読み出し要求信号がメモリインターフェースに対して発行される( t 6 )。

#### 【 0 1 7 1 】

本実施形態では変倍ブロック 406 が順調に画像データ処理を行い、結果的にバッファが一杯にならなかった場合を示している。もちろん、変倍率の設定で画像データの消費量が異なり、バッファが一杯に近い状態になり、バッファ状態を示す信号( N o t F u l l )が“ 0 ”となる場合もありうる。この場合には、もちろん読み出し要求は発生しない。 40

#### 【 0 1 7 2 】

その後、外部メモリインターフェース 2122 に読み出し要求が受け付けられ、 R A c k が帰ってくるとリードカウンタ( R e a d C o u n t ) 603 はビート数“ 8 ”だけ増加する。そして、 C o u n t Z e r o 信号は“ 0 ”となり、 R e q 信号のマスクが有効になり、読み出し要求信号( R R e q )は“ 0 ”となり、新たな読み出し要求は、( t 7 )で受け付けられた読み出し要求が完了するまで発行されない。

#### 【 0 1 7 3 】

以上説明したように、本実施形態によれば、各タイルに関して、水平方向の変倍処理開始時に水平変倍回路のバッファの量だけの画像データを変倍処理回路の処理状態によらず、 50

メモリインターフェースから転送するようにした。これにより、水平変倍回路が処理を行う際に必要な画像データがメモリインターフェースからの読み出し待ち状態となることを少な

くでき、処理速度の高速化が可能となる。

#### 【0174】

また、読み出し処理を集中させることにより外部S D R A Mのヒット率を高くすることができ、I Cチップ内の外部S D R A Mを用いる機能ブロックに対しても、ラスタ展開時の書き込みについても高速化が図れる。

#### 【0175】

更に、変倍処理のように処理の開始時点で必要とされるデータ量すべての読み出しが困難であり、逐次的に読み出さざるを得ないシステムにおけるスプリットトランザクションをサポートする読み出し制御を簡単に行える。10

#### 【0176】

以上、外部S D R A Mを用いる変倍処理部を例に説明したが、変倍処理部に限らず、他の処理ブロックにおける画像処理にも、本実施形態における発明を適用することができる。

#### 【0177】

例えば、図9の画像入力処理におけるタイル画像の生成処理の際に、画像入力インターフェース2112において、タイル単位でのラスタ展開のために画像メモリを用いている。このとき、本実施形態と同様な連続読み出しのメモリアクセス制御を行うことができ、タイル画像生成の高速化が達成できる。

#### 【0178】

##### (第3の実施形態)

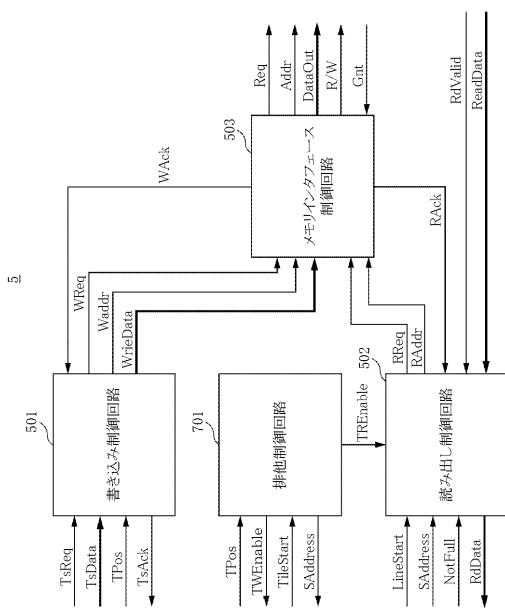

上記実施形態のように、外部メモリを用いて変倍処理を実行する場合、メモリを管理して処理の信頼性を向上させるために、外部メモリへのタイル画像の書き込み、読み出しに対する排他制御を行うことが好ましい。本実施形態では、以下説明するような排他制御の構成をとることにより、変倍率に応じたメモリ管理を、簡単な装置構成で実行できるよう<sup>20</sup>にする。

#### 【0179】

##### [変倍処理の詳細]

本実施形態の変倍処理部2116のブロック構成は、図13に示したものと同じである。

図20は、図13に示したメモリインターフェース5の一例を示す詳細ブロック図である。30

#### 【0180】

図20において、書き込み制御回路501、読み出し制御回路502、メモリインターフェース制御回路503は、第2の実施系形態で説明した同一符号の回路と同様な機能を有している。

#### 【0181】

701は排他制御回路で、書き込みを行おうとしているタイルの位置情報(タイルポジション信号T p o s)と、読み出しを行おうとしている読み出しアドレスに基づき書き込み、読み出しの許可(許可信号T R E n a b l e)を与える制御を各信号T p o s, T W E n a b l e, T i l e S t a r t, S A d d r e s sに従って行う。

#### 【0182】

図21は、図20に示した排他制御回路701の詳細回路の一例を示すブロック図である。40

#### 【0183】

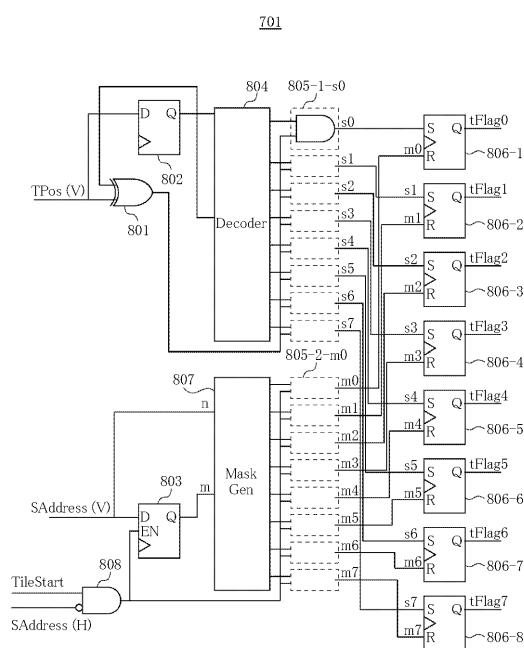

図21において、801はE x c l u s i v e O Rゲート、802はD - F l i p F l o p、803はE n a b l e付きのD - F l i p F l o p、804はデコーダ回路、805 - 1 - s 0 ~ 805 - 1 - s 7, 805 - 2 - m 0 ~ 805 - 2 - m 7はA n d回路、806 - 1 ~ 806 - 8はR S - F l i p F l o p、807はマスク生成回路(M a s k G e n)、808はアンドゲートである。

#### 【0184】

図22～図25は、図20に示した排他制御回路701によるタイル画像データ転送処理50

時のメモリ状態を説明するための図である。

**【0185】**

図22～図25において、 $tFlag0 \sim 7$ は変倍処理の進行状態に従い変化する同一垂直方向のタイル位置の変倍処理終了有無を示すフラグで、ラスタ展開される外部のメモリ上の垂直方向のタイル位置に応じたメモリ状態がRS-F1ipFlag806-1~806-8上に保持される。

**【0186】**

なお、RS-F1ipFlag806-1~806-8は、図21に示した排他制御回路701のデコード回路804の出力とマスク回路807の出力とに基づいてセット（「1」）またはリセット（「0」）される。そして、該フラグ $tFlag0 \sim 7$ の状態に従って、外部のメモリに対するデータ書き込み時におけるタイルスレーブインターフェース4によるデータの受信動作、すなわちタイルスレーブインターフェース4に対する信号TWEnableのセットまたはリセットを制御するとともに、外部のメモリからのデータ読み出し時における読み出し制御回路502に対する信号TUREnableのセットまたはリセットを制御する。

10

**【0187】**

なお、本実施形態においては、図22～図25において変倍装置で変倍可能な最小倍率は、例えば0.25（1/4）であるとし、ラスタメモリの垂直方向のタイル数は条件式より求められる最小の値（ $4 + 2 = 6$ ）であるから、これ以上、かつ最小の2のべき乗の値である「8」として説明する。

20

**【0188】**

変倍動作開始時には、図22～図25におけるフラグ $tFlag0 \sim 7$ はすべて「0」にクリアされた状態にあり、画像データはタイルバスにて図22中の左上から順に送られてくる。

**【0189】**

図22に示す例では、一番上の左から3つ目までがデータ転送が終了し、現在4つ目の図22の斜線で示されたタイル画像の転送が現在行われているとする。

**【0190】**

そして、タイル画像の転送がさらに進み、図22の一番上の列の転送が終了し、図23に示すように上から2列目の転送が開始されると、1列目の書き込み終了を示すフラグ $tFlag0$ が「1」にセットされる。同様にして列の書き込みが終了した時点で該当するフラグが順次「1」にセットされる。

30

**【0191】**

一方、変倍処理による読み出し側の制御は、例えば、1/4倍の変倍を行っている場合のメモリ状態は図24に示す通りであり、図24ではラスタ展開された画像のうち斜線で示された（ $3, 8n$ ）から（ $8, 8n+5$ ）のタイルに含まれる画像データを用い、1タイル分の変倍結果を出力しようとしている。

**【0192】**

本来、変倍率が（この例では水平垂直とも）1/4であるので、水平方向および垂直方向とも、4タイルずつ（この例では（ $4, 8n+1$ ）から（ $7, 8n+4$ ）の部分）の画像があればよいと思われるが、実際にはフィルタ処理を行う関係上周辺の画像データをも必要とするため、図24に示すような（ $3, 8n$ ）から（ $8, 8n+5$ ）のタイルに含まれる画像データが必要となる。

40

**【0193】**

この状態から水平方向に変倍処理を実行していき、水平方向の変倍処理を終え、垂直方向に変倍結果として1タイル分処理した場合のメモリの状態図およびフラグの値は図25に示す通りとなる。

**【0194】**

図25に示したように、つまり図24のメモリ状態から図25のメモリ状態に移った場合、変倍処理のために使用するタイル画像の位置は（ $0, 8n+4$ ）から（ $4, 8(n+1)$ ）

50

) + 1 ) の位置に移動する。ただし、( 0 , 8 ( n + 1 ) ) から ( 4 , 8 ( n + 1 ) + 1 ) の位置のタイル画像はメモリ上の位置は図 2 4 のタイル画像と同じであるが、新たにタイルスレーブより得られた画像データをおく必要があるため、該当するフラグ t F l a g 0 ~ 3 は図示してあるようにクリアされている。

#### 【 0 1 9 5 】

これら図 2 2 から図 2 3 および図 2 4 から図 2 5 の変化に対応し該当するフラグのセットおよびクリアを実現する回路の一例が図 2 1 に示す排他制御回路 7 0 1 である。

#### 【 0 1 9 6 】

1 垂直方向の画像データ書き込み終了時、つまり図 2 2 に示すメモリ状態から図 2 3 に示すメモリ状態への変化時には、タイルスレーブインターフェース 4 より入力されるタイルの位置を示す情報（信号 T p o s ）内の垂直方向情報（図 2 0 に示す信号 T p o s ( V ) ）が変化する。したがって、その変化のタイミングを捉え、デコーダ回路 2 4 が出力する現在書き込み中の位置信号を、ゲートし、該当する位置のフラグをセットする信号（図 2 2 および図 2 3 の例ではゲート 8 0 5 - 1 - s 0 ) を 8 0 6 の R S - F l i p F l o p 8 0 6 - 1 に出力する。該当する R S - F l i p F l o p はそのフラグをセットする。

10

#### 【 0 1 9 7 】

一方、1 垂直方向分の変倍処理が終了した場合、つまり、図 2 3 に示すメモリ状態から図 2 4 に示すメモリ状態への変化時には、メモリからの水平位置の読み出しアドレスは「 0 」である。したがって、水平読み出しアドレスが「 0 」であるときのタイル変倍開始パルス（信号 T i l e S t a r t ）でマスク生成回路 2 7 の出力を有効にしてやることでフラグをクリアする。

20

#### 【 0 1 9 8 】

また、マスク生成回路 8 0 7 は、図 2 3 に示すメモリ状態時点での変倍開始時の垂直方向データ読み出しアドレスと、図 2 4 に示すメモリ状態時点での変倍開始時の垂直方向データ読み出しアドレスから読み出しが終了した垂直方向タイル位置を判断する。そして、判断結果から、読み出し終了位置に該当するフラグをクリアするための信号を発生する。デコーダ回路 8 0 4 の出力例を表 1 に示す。

#### 【 0 1 9 9 】

#### 【 表 1 】

30

|   | 0  | 1  | 2  | 3  | 4  | 5  | 6  | 7  | n  |

|---|----|----|----|----|----|----|----|----|----|

| m | 00 | 01 | 03 | 07 | 0F | 1F | 3F | 7F |    |

|   | FE | 00 | 02 | 06 | 0E | 1E | 3E | 7E |    |

|   | FC | FD | 00 | 04 | 0C | 1C | 3C | 7C |    |

|   | F8 | F9 | FB | 00 | 08 | 18 | 38 | 78 |    |

|   | F0 | F1 | F3 | F7 | 00 | 10 | 30 | 70 |    |

|   | E0 | E1 | E3 | E7 | EF | 00 | 20 | 60 | 40 |

|   | C0 | C1 | C3 | C7 | CF | DF | 00 | 40 |    |

|   | 80 | 81 | 83 | 87 | 8F | 9F | BF | 00 |    |

40

#### 【 0 2 0 0 】

このフラグデータに基づき、書き込み時には書き込もうとするタイル位置の画像データがすでに変倍処理による読み出しが終了しているかどうかを判断する。変倍処理による読み出しが終了していれば、図 1 0 に示された信号 T W E n a b l e を「 1 」にすることで、タイルスレーブインターフェース 4 はデータの受信を行う。逆に、変倍処理による読み出し

50

が終了していない場合には、T W E n a b l e 信号を「0」にすることでタイルスレーブインターフェース4は本変倍装置に画像データを送ろうとしているタイルマスタインターフェース8を該当する位置の書き込みフラグが「0」になるまで待たせる。

#### 【0201】

一方、読み出し時には、読み出そうとしているアドレスのフラグがセットされている場合には、図20に示した排他制御回路701から読み出し制御回路502に出力されるT R E n a b l e 信号を「1」とし、図20の読み出し制御回路502はメモリインターフェース制御回路12に対しメモリ読み出し要求信号R R e q およびR A d d r 信号を出力する。

#### 【0202】

逆に、フラグがセットされていない場合には、T R E n a b l e 信号を「0」とすることで、読み出し制御回路502はメモリインターフェース制御回路503への読み出し要求信号の出力を制限する。

#### 【0203】

上記実施形態では、書き込みのための制御信号T W E n a b l e をタイルスレーブインターフェースに出力し、タイルデータの転送を制限したが、この信号を書き込み制御回路501へ出力し、書き込み要求信号を制限しても結果は同じである。

#### 【0204】

本実施形態によれば、タイル画像をラスタ変換するためのメモリの書き込み、読み出しの排他制御を垂直方向のタイル単位で行い、しかも、管理すべき垂直方向のタイル数を変倍処理部が処理可能な最小倍率をn(<1)とした場合、管理すべき垂直方向のタイル数を(1/n)+2以上、かつ2のべき乗に制限することでメモリ管理を簡単に実現した。

#### 【0205】

また、変倍処理部の特殊事情による読み出し済みメモリの解放に関しても垂直方向の出力タイルの変化時点に行うことで全体の構成を簡単に実現することが可能となった。

#### 【0206】

なお、管理すべき垂直方向のタイル数は、2のべき乗に限定するものではない。すなわち、上記実施形態の構成において、垂直方向のタイル数を6、または7個としても、同様にメモリ管理を簡単にすることができます。

#### 【0207】

##### (第4の実施形態)

上記各実施形態で説明した装置をI Cチップ化する場合、ある程度高速な変倍処理を実行することができるが、今後、さらなる変倍処理の高速化が要求されることが予想される。

#### 【0208】

回路全体のクロック速度を上げることにより、この要求を満たす回路を構成することができるが、I C化に際する制約を与えことになる。また、外部メモリの要求スピードもクロック速度の高速化に伴い高速化されるため、使用されるメモリーチップのコストを上げる要因ともなる。

#### 【0209】

本実施形態では、変倍処理回路に多少の回路を追加する代わりに、従来と同様なクロックスピードで従来よりも高速に変倍処理を行えるようにする。

#### 【0210】

##### [変倍処理の詳細]

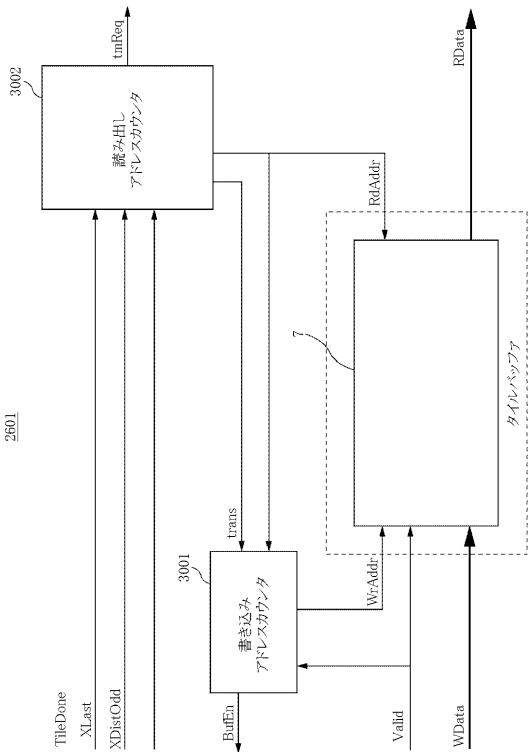

本実施形態における変倍処理部2116のブロック図を図26に示す。第1-3の実施系形態と異なるのは、タイルバッファ7を制御するためのタイルバッファ制御回路2601を設けた点である。

#### 【0211】

本実施形態における変倍ブロック6の詳細な構成は、図14に示したものと同じであり、変倍コントロールブロック10の詳細な構成も、図16に示したものと同じである。

#### 【0212】

10

20

30

40

50

ただし、変倍処理部 2116 は、上記各実施形態とは異なり、2 タイル単位で変倍処理を実行する。以下、変倍処理部 2116 の全体動作を説明する。

#### 【0213】

まず、タイル伸張部(1)2103 から図26 に示すタイルバス2107 を介してタイルスレーブインターフェース4 に入力されたタイルデータはメモリインターフェース5 に転送され、メモリバス2108 及びメモリ制御部2122 を介して、一旦図11 に示されるように1枚の画像の形に戻される。但し、外部の画像メモリ2123 は1枚の画像データ分を確保しているわけではなく、必要な垂直のメモリ確保量は変倍処理を行うのに必要とされる量、即ち、上記実施形態と同様に、図15 に示す太線で示されるエリアを展開できる程度の量が実際には確保される。更に、図26 に示すメモリインターフェース5 は少なくとも垂直方向に1タイル分の画像データを画像メモリ2123 に展開し終えた時点で変倍ブロック6 にReady 信号を通知する。10

#### 【0214】

一方、変倍ブロック6 はメモリインターフェース5 からReady 信号を受けて変倍処理に必要なタイルデータのアドレスをメモリインターフェース5 に通知する。これを受けて、メモリインターフェース5 は画像メモリ2123 からの読み出し要求を行う。読み出し要求を受けたメモリインターフェース5 はメモリバス2108 を介して画像メモリ2123 から該当する位置のタイルデータを読み出して変倍ブロック6 へ送出する。これにより、変倍ブロック6 はメモリインターフェース5 より送出されたタイルデータ及びレジスタインタフェース9 を介して設定された変倍率及びフィルタ係数に基づき、変倍処理を行った結果をタイルバッファ7 に蓄積し、2タイル分の変倍画像を生成し終えた段階でタイルマスターインターフェース8 にDone 信号を通知する。このDone 信号を通知されたタイルマスターインターフェース8 は、変倍結果のタイルデータをタイルバッファ7 よりタイル単位で読み出し、タイルバス2107 を介してタイル圧縮部(1)2106 へ出力を行う。20

#### 【0215】

ここで、図16 を参照しながら上述の変倍コントロールブロック10 の詳細な構成及び動作について説明する。

#### 【0216】

図26 に示すメモリインターフェース5 からDone 信号を受けて、変倍コントロールブロック10 のタイミング発生回路20 は、バッファ11 及び水平変倍回路12 (図14) 、図16 に示す水平アドレスカウンタ22 の各ブロックにLineStart 信号を出力する。また、タイミング発生回路20 は、ラインバッファ13 及び垂直変倍回路14 (図14) 、図16 に示す垂直アドレスカウンタ24 の各ブロックにTileStart 信号を出力する。さらに、タイミング発生回路20 は、図16 に示す水平アドレス保持回路21 及び水平変倍情報保持回路25 にXstart 信号を出力し、垂直アドレス保持回路23 及び垂直変倍情報保持回路26 にYstart 信号を出力して各ブロックを初期化させる。その後、メモリインターフェース5 へタイルデータの読み出し要求信号Req を出力する。また、水平アドレスカウンタ22 及び垂直アドレスカウンタ24 は、変倍処理を行うのに必要な読み出したいタイルデータのアドレスを示す信号Address を出力する。30

#### 【0217】

ここで、外部メモリ2123 よりタイルデータが読み出され、水平方向の変倍処理が開始され、水平方向アドレスカウンタ22 は元画像データのシフトが発生したことを示すShift 信号に基づき、カウンタの値をカウントアップしていく。

#### 【0218】

その後、タイル1 ライン分の2倍の画素数分の水平方向変倍処理が終了すると(HDone 信号)、タイミング発生回路20 は新たにバッファ11 及び水平変倍回路12 (図14) 、図16 に示す水平アドレスカウンタ22 、垂直アドレスカウンタ24 の各ブロックにLineStart 信号を出力し、バッファ11 及び水平変倍回路12 を初期化する。これと同時に、図16 に示す水平アドレスカウンタ22 のカウント値を水平アドレス保持回路21 にロードし、フィルタ係数生成回路には水平変倍情報保持回路に保持された値(R40

`e g H I n f`) をロードさせ、垂直アドレスカウンタ 24 の値をカウントアップさせる。そして、更新された水平及び垂直アドレス Address และ `R e q` とに基づき、メモリインタフェース 5 は次のラインの画像データを外部メモリ 2123 から読み出す。

#### 【0219】

上述の操作により、図 14 に示すラインバッファ 13 に所定の変倍結果が揃うと垂直方向変倍回路 14 が動作を開始し、垂直方向に変倍処理を実施した結果画像データをタイルバッファ制御回路 2601 に出力する。垂直方向変倍回路 14 においてタイルのライン数分の変倍処理を終了するとタイル終了信号 `V d o n e` 信号が図 16 に示すタイミング発生回路 20 に入力される。この信号に基づきタイミング発生回路 20 は水平アドレス保持回路 21 に次の水平アドレスカウンタの値を保持させる信号 `T i l e D o n e` を出力する。これらの処理を繰り返した後、変倍出力タイルが水平方向の最後のタイルを処理し終えたときにタイミング発生回路 20 は垂直アドレス保持回路 23 に対し、現在の垂直アドレスカウンタ 24 の値を保持させる信号 `X l a s t` を出力し、垂直アドレス保持回路 23 に現在の垂直アドレスカウンタ値を保持させる。

#### 【0220】

一方、タイルバッファ制御回路 2601 は垂直方向変倍回路 14 にて垂直方向の変倍をも実施された変倍結果画像データを数え、タイルバッファの該当する位置へと書き込みを行う。また、タイルマスターインターフェース回路の読み出し要求アドレスに従い該当するタイル画像データを読み出し、出力する。このとき、読み出すべきタイル画像データが水平方向に連続した 2 つのタイル画像のうち初めのものであるか後のものであるかを判断し、読み出しアドレスを該当するアドレスに変換してタイルバッファから読み出しを行う。

#### 【0221】

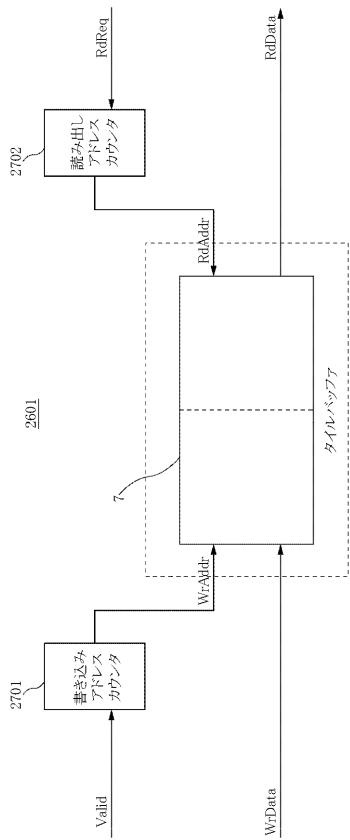

タイルバッファ制御回路 2601 の一例を図 27 に示す。図 27 において、2701 は変倍ブロック 6 より変倍結果画像と同時に outputされる `V a l i d` 信号をカウントする書き込みアドレスカウンタ、2702 はタイルマスターインターフェースより読み出し要求を受け読み出し画素数をカウントする読み出しアドレスカウンタである。

#### 【0222】

本実施形態の変倍処理の特徴を明確に説明するため、タイルの大きさを水平方向 8 画素、垂直方向 8 ラインであるとする。この場合のタイルバッファ 7 におけるアドレスの一例を図 28 に示す。図 28 にてハッチがかかっている部分が最初のタイル部分を示す。

#### 【0223】

タイルバッファ 7 への書き込み時は、書き込みアドレスは図 28 に示した番号順に出力され、タイルバッファ上の図示される位置に格納される。一方、読み出し時にはタイル単位で出力する必要があるため、読み出しアドレスを 0 1 ... 7 16 17 ... として読み出し、図にてハッチがかかった部分を読み出した後、今度は 8 9 ... 15 24 ... と読み出しを行う。そのため、読み出しアドレスは読み出しアドレスカウンタの出力アドレス信号の位置を入れ替えた信号をタイルバッファ 7 に与えることで実現できる。

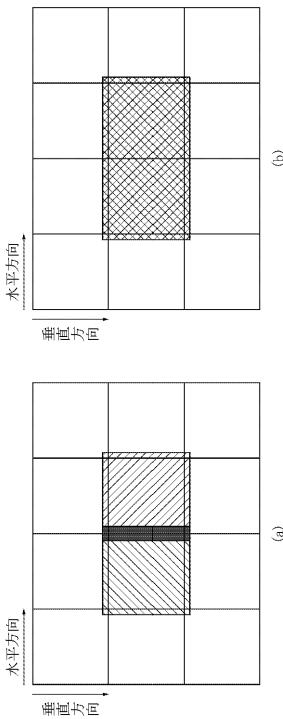

#### 【0224】

次に、本実施形態の構成を用いて変倍処理を行った場合のタイル 1 ラインあたりの処理時間を概算する。まず、タイル単位で処理を行う場合と、水平方向に 2 タイル連続して処理を行う場合との処理領域の違いを図 29 に示す。図 29 は簡単のため変倍率を 1 (つまり 100%) とした時の処理に必要な原画像データと、出力のタイルを示すものである。図 29 (a) はタイル単位で処理を行う場合を図示し、ハッチがけを行った部分が外部メモリから読み出す必要がある画像データである。図に示すように、タイル単位で処理を行うため中央の濃い色でハッチがけされた部分は実際には外部メモリから 2 回、( 最初のタイルの最後と次のタイルの最初 ) 読み出される必要がある。

#### 【0225】

2 タイル連続して出力を行う本実施形態の処理結果を図 29 (b) に図示する。図 29 (b) では、水平方向に連続した 2 タイルを一度に処理するため、図 29 (a) で示したよ

10

20

30

40

50

うな外部メモリ 2123 から 2 度読み出さなければならない領域が発生していない。もちろん、2 タイル連続したタイルを生成した後には、同じように 2 度読みする領域が発生するが、その発生頻度は図 29(a) に図示した場合の半分である。

#### 【0226】

次に、倍率 1 の場合のラインあたりの処理に要するクロックサイクルの概算を行う。処理を開始し、メモリインタフェースから画像データが出力されるまでの遅延は外部メモリを用いる以上避けることができず、読み出し要求を出してから、実際にメモリからデータが読み出されるまでのサイクル数は水平変倍回路が動作できない不要なサイクルとなる。このサイクル数を TA とする。

#### 【0227】

また、メモリからの読み出しは、高速アクセスを行う必要上、バースト読み出しを行う必要があり、読み出し開始位置と、実際に変倍処理に必要な画素位置とが一致するとは限らないため、ここでも不要なサイクルが発生し、その値を TB とする。

#### 【0228】

変倍演算開始時のオーバーヘッドおよび、パイプライン処理終了処理に要するサイクル数を TC とする。

#### 【0229】

以上の条件にて実際の水平方向処理サイクル数を計算する、ただし、上記 TA、TB、TC には各々 10、7、5 を代表値として用いるとすると、1 タイル相当画素数の水平変倍に要する処理サイクルは

$$TA + TB + 32 + TC = 54$$

一方、連続した 2 タイル分の水平方向変倍を一括処理する場合には

$$TA + TB + 64 + TC = 86$$

これを 1 タイル分に換算するとその半分になるので  $86 / 2 = 43$

となり、平均して約 20% の処理サイクルの短縮つまり、高速化が可能となる。

#### 【0230】

以上説明したように、本実施形態では、2 つのタイルを処理するので、クロック速度の高速化等を行わなくても、高速な変倍処理が可能となる。なお、一括して処理するタイルの数は 2 つに限るものではなく、3 つや 4 つを一括して処理するようにしてもよい。

#### 【0231】

##### (第 5 の実施形態)

上記第 4 の実施形態では、複数タイルを一括して変倍処理するため、水平方向の端部の処理時には、本来必要としないデータまでも変倍ブロックから出力されてしまうことがある。

#### 【0232】

本実施形態では、複数タイル単位で変倍処理する場合においても、有効なタイルのみを出力するように変倍処理部を制御する。

#### 【0233】

##### [変倍処理の詳細]

本実施形態における変倍処理部 2116 のブロック構成は、第 4 の実施形態で説明した図 26 のものと同様である。ただし、タイルバッファ制御回路 2601 の構成が、第 4 の実施形態と異なっている。以下、タイルバッファ制御回路 2601 の詳細について説明する。

#### 【0234】

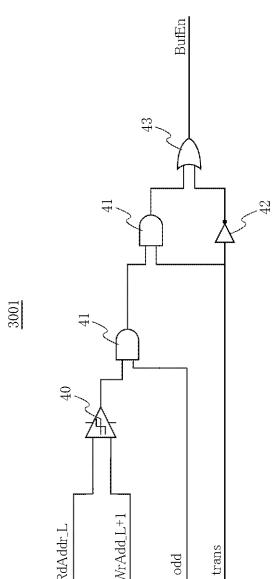

本実施形態のタイルバッファ制御回路のブロック図を、図 30 に示す。図 30 において、3001 は変倍ブロック 6 より変倍結果画像と同時に outputされる Vaid 信号をカウントする書き込みアドレスカウンタ、3002 はタイルマスティンタフェースより読み出し要求を受けて読み出し画素数をカウントする読み出しあドレスカウンタである。

#### 【0235】

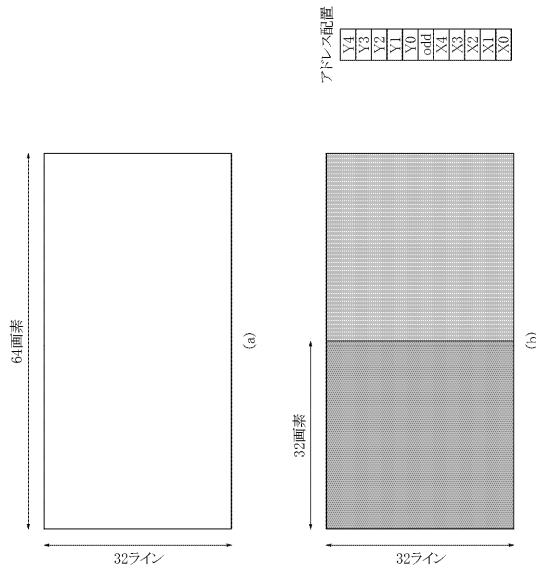

図 31 はタイルバッファのアドレス配置を説明するための図である。いま、図 31(a)

10

20

30

40

50

に示されるように、タイルバッファが水平方向に 2 タイル分領域を確保して用いられるとすると、書き込み時のアドレスは図中に示されるようなアドレス配置となり、下位 6 ビットは水平方向の画素カウンタで占められ、上位 5 ビットはライン方向のカウンタで占められる。

**【 0 2 3 6 】**

一方、図 3 1 ( b ) に示されるように、タイルバッファに格納されたタイルデータの読み出し時のアドレスは、タイル単位で読み出す必要上、水平方向に偶数番目のタイルか奇数番目のタイルかを示すビットがはさまれ、それより下位側の 5 ビットはタイル内の水平方向画素アドレスを、上位側 5 ビットは垂直方向のラインアドレスで占められる。

**【 0 2 3 7 】**

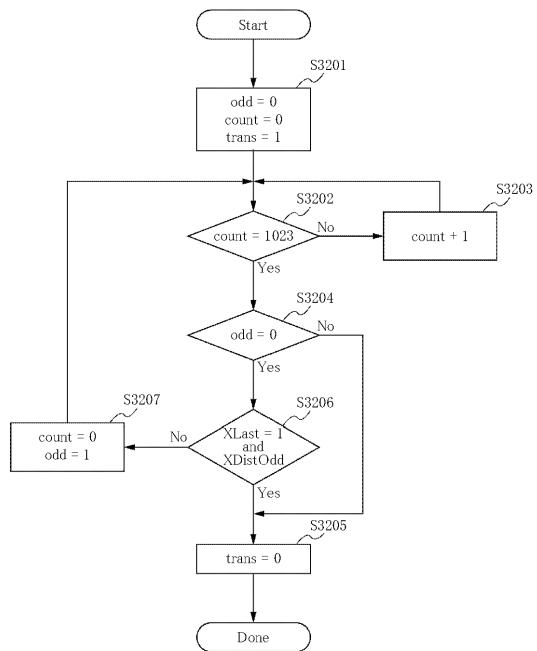

この読み出し時のアドレスを正しく生成するために、読み出しアドレスカウンタは図 3 2 にて示されるようなフローに従いアドレスを生成する。

**【 0 2 3 8 】**

図 3 2 のフローチャートの処理は、変倍処理部 2 1 1 6 に内蔵される C P U ( 図示せず ) により制御されるものであり、処理に必要なパラメータ等は、ヘッダ情報を解析するタイルスレーブインターフェース 4 やレジスタインターフェース 9 から取得することができる。

**【 0 2 3 9 】**

まず、変倍ブロック 6 から 2 タイル分の変倍処理が終了したことを示す信号が入力されるとタイルバッファ読み出し中であることを示す信号 t r a n s を 1 にセットする。また、アドレスカウンタを 0 にリセットし、かつ、タイルの番号を示す信号 o d d を 0 にリセットする ( S 3 2 0 1 )。

**【 0 2 4 0 】**

そして、タイルバッファより 1 画素ずつデータを読み出し、1 タイル分のデータが読み出されるまでカウンタをカウントアップする ( S 3 2 0 2 : N o , 及び S 3 2 0 3 )。

**【 0 2 4 1 】**

1 タイル分の変倍出力をタイルバッファより読み出し終えたら ( S 3 2 0 2 : Y e s ) 、現在出力しているタイルバッファの内容が 2 タイル目であるかどうかを判断する ( S 3 2 0 4 )。

**【 0 2 4 2 】**

2 タイル目であるならば ( S 3 2 0 4 : N o ) 、タイルバッファの読み出し終了動作を示す信号 t r a n s を 0 にリセットする ( S 3 2 0 5 )。逆に、読み出したタイルバッファの内容が 1 タイル目であった場合には ( S 3 2 0 4 : Y e s ) 、水平方向の最後の変倍結果であるかどうかの信号 X 1 a s t と、期待される出力タイル数が奇数であるかどうかを示す信号 X d i s t O d d を確認する ( S 3 2 0 6 )。

**【 0 2 4 3 】**

ここで、水平方向の最終出力であり、かつ、期待される出力タイル数が奇数の場合 ( S 3 2 0 6 : Y e s ) には、読み出しアドレスのカウントを中止し、 t r a n s 信号を 0 にリセットする ( S 3 2 0 5 )。それ以外の場合 ( S 3 2 0 6 : N o ) には o d d を 1 にセットし、カウンタを 0 にリセットした後 ( S 3 2 0 7 ) 、ステップ S 3 2 0 2 に戻り、上記のカウントアップ動作を再度実行する。

**【 0 2 4 4 】**

このように、書き込みアドレスカウンタ 3 0 0 1 は、タイルバッファ 7 への書き込み制御を行うため、 V a l i d 信号が 1 のときにカウントアップ動作を行うカウンタで構成される。また、書き込みアドレスカウンタ 3 0 0 1 は、タイルバッファ 7 への書き込み許可信号 B u f E n を出力するために、図 3 3 に示されるような回路にて構成される。

**【 0 2 4 5 】**

図 3 3 の回路は、 B u f E n が 1 である場合にはタイルバッファ 7 への該当するラインへの書き込みデータ出力を変倍ブロック 6 に対し許可し、 0 である場合には変倍ブロック 6 のタイルバッファ 7 への該当するラインへの書き込みデータ出力処理を停止させることで、タイルバッファ 7 への書き込みを制御する。

10

20

30

40

50

**【0246】**

図33の回路は、タイルマスターインターフェース8が動作していない場合には、タイルバッファ7への書き込みを許可する。

**【0247】**

また、タイルマスターインターフェース8が動作中で、タイルマスターインターフェース8が最初のタイルを出力中の場合には、タイルバッファ7への書き込みを禁止する。

**【0248】**

また、タイルマスターインターフェース8が動作中で、タイルマスターインターフェース8が2番目のタイルを出力中の場合には、読み出し中のタイルのラインアドレスR d A d d r\_Lと書き込もうとしているラインアドレスから計算される値W r A d d \_L + 1の大きさを比較し、R d A d d r\_L > W r A d d \_L + 1である場合のみ書き込みを許可する。ここで、書き込みアドレスに対し + 1が行われるのは、書き込み制御をライン単位で行わせることにより回路を簡単化するためである。10

**【0249】**

以上説明したように、複数のタイルを一括して変倍処理する場合においても、有効な画像データのみを出力させるようにすることができる。

**【0250】****(他の実施形態)**

上記各実施形態の画像入出力装置は、複数の画像データに関する画像処理を並行に実行できるように構成されている。この画像入出力装置において、変倍処理を実行中、回転処理部等、他の画像処理部が画像メモリを同時に使用したとしても、本発明の適用により、互いの処理に関する画像メモリの競合を少なくすることができます。特に、画像入力インターフェースからの画像入力処理との並行処理を実行する際には、画像処理部において非常に大きな容量の画像データが同時に処理されることになる。しかし、この場合においても、画像メモリは各処理に関してタイル単位で確保されるので、円滑に並行処理を実行することができる。20

**【0251】**

上記各実施形態では、デジタル複写機等の画像入出力装置を例に、本発明を説明してきたが、これに限るものではなく、本発明は複数の機器（例えば、ホストコンピュータ、インターフェース機器、リーダ、プリンタなど）から構成されるシステムに適用しても、一つの機器からなる装置（例えば、複写機、ファクシミリ装置など）等、様々な画像入出力装置に適用してもよい。30

**【0252】**

また、本発明は、画像入出力装置に限らず、パーソナルコンピュータ等情報処理装置にも、適用可能である。この場合、例えば、上記画像入出力装置の変倍処理に係る部分をオプションカード上に構成し、そのオプションカードを情報処理装置の汎用バスに接続して用いる装置構成が考えられる。

**【0253】**

また、情報処理装置のCPUとメインメモリを上記変倍回路とし、画像処理専用の他のメモリを外部メモリとする装置構成をとるようとしても、本発明の処理は実行可能である。この場合、CPUが上記実施形態で説明した変倍処理のプログラムを実行することにより、メインメモリの記憶領域を節約することができる。このとき用いられる変倍処理のためのプログラムは、予め装置の記憶媒体等に格納されることになる。40

**【0254】**

すなわち、本発明の目的は前述した実施形態の機能を実現するソフトウェアのプログラムコードを記録した記憶媒体を、システム或いは装置に供給し、そのシステム或いは装置のコンピュータ（CPU若しくはMPU）が記憶媒体に格納されたプログラムコードを読み出し実行することによっても、達成されることは言うまでもない。

**【0255】**

この場合、記憶媒体から読み出されたプログラムコード自体が前述した実施形態の機能を実50

現することになり、そのプログラムコードを記憶した記憶媒体は本発明を構成することになる。

**【0256】**

プログラムコードを供給するための記憶媒体としては、例えばフロッピー（R）ディスク、ハードディスク、光ディスク、光磁気ディスク、CD-ROM、CD-R、磁気テープ、不揮発性のメモリカード、ROMなどを用いることができる。

**【0257】**

また、コンピュータが読出したプログラムコードを実行することにより、前述した実施形態の機能が実現されるだけでなく、そのプログラムコードの指示に基づき、コンピュータ上で稼働しているOS（オペレーティングシステム）などが実際の処理の一部又は全部を行い、その処理によって前述した実施形態の機能が実現される場合も含まれることは言うまでもない。10

**【0258】**

更に、記憶媒体から読出されたプログラムコードが、コンピュータに挿入された機能拡張ボードやコンピュータに接続された機能拡張ユニットに備わるメモリに書込まれた後、そのプログラムコードの指示に基づき、その機能拡張ボードや機能拡張ユニットに備わるCPUなどが実際の処理の一部又は全部を行い、その処理によって前述した実施形態の機能が実現される場合も含まれることは言うまでもない。

**【0259】**

同様に、本発明は、前述した実施形態の機能を実現するソフトウェアのプログラムコードを蓄積した外部装置（例えばアプリケーションサーバー等）から、ネットワークを介してダウンロードすることにより、システムあるいは装置の記憶装置に供給し、そのシステムあるいは装置のコンピュータ（またはCPUやMPU）がこの外部装置に格納されたプログラムコードを読み出し実行することによっても、完成されることは言うまでもない。20

**【0260】**

**【発明の効果】**

以上説明してきたように、本発明によれば、少ないメモリ容量でタイル単位に変倍処理を行うことができるという効果がある。

**【0261】**

また、外部メモリを用いた画像処理、特に変倍処理を行う際の処理速度を向上させることができるという効果がある。30

**【0262】**

また、簡単な構成で変倍処理と画像データの書き込み処理を行う際のメモリ管理を容易に効率よく行えるという効果がある。

**【0263】**

また、回路のクロック速度を上げることなく、変倍処理を行う際の処理速度を向上させることができるという効果がある。

**【0264】**

また、外部メモリを用いた変倍処理におけるデータ管理を容易にすることができますといいう効果がある。40

**【0265】**

また、ICチップ内の回路構成にはほとんど影響を与えることなく、様々な変倍率や画像サイズに対応した変倍処理が可能となるという効果がある。

**【図面の簡単な説明】**

**【図1】**本発明を適用可能な画像入出力装置（デジタル複写機）の構成を説明するブロック図である。

**【図2】**システム制御部の構成を説明する詳細ブロック図である。

**【図3】**画像処理部の構成を説明する詳細ブロック図である。

**【図4】**図1の画像入出力装置を含むネットワークシステム全体の構成を説明する図である。50

- 【図 5】図 1 の画像入出力装置で用いられるデータパケットを説明するための図である。

- 【図 6】図 1 の画像入出力装置で用いられるコマンドパケットを説明するための図である。

- 【図 7】図 1 の画像入出力装置で用いられるインタラプトパケットを説明するための図である。

- 【図 8】各パケットを管理するパケットテーブルを説明するための図である。

- 【図 9】画像入力処理に関するプロック間のデータの経路と処理手順を示す図である。

- 【図 10】スキャナ 2070 で読み取った原稿画像のタイル画像への分割例を示す図である。

- 【図 11】画像出力処理に関するプロック間のデータの経路と処理手順を示す図である 10

- 【図 12】データパケットの変倍処理に関するプロック間のデータの経路と処理手順を示す図である。

- 【図 13】第 1 - 3 の実施形態における変倍処理部の構成を示す図である。

- 【図 14】変倍プロック 6 の詳細な構成を示すプロック図である。

- 【図 15】外部メモリ上に展開されるタイル単位のラスタデータを示す図である。

- 【図 16】図 14 に示した変倍コントロールプロックの詳細を示すプロック図である。

- 【図 17】第 2 の実施形態におけるメモリインターフェース 5 の詳細な構成を示す図である 20

- 【図 18】図 17 に示した読み出し制御回路の詳細な構成を示す図である。

- 【図 19】読み出し制御回路の動作を説明するためのタイミングチャートである。

- 【図 20】図 13 に示したメモリインターフェースの一例を示す詳細プロック図である。

- 【図 21】図 20 に示した排他制御回路の詳細回路の一例を示すプロック図である。

- 【図 22】図 20 に示した排他制御回路によるタイル画像データ転送処理時のメモリ状態を説明するための図である。

- 【図 23】図 20 に示した排他制御回路によるタイル画像データ転送処理時のメモリ状態を説明するための図である。 30

- 【図 24】図 20 に示した排他制御回路によるタイル画像データ転送処理時のメモリ状態を説明するための図である。

- 【図 25】図 20 に示した排他制御回路によるタイル画像データ転送処理時のメモリ状態を説明するための図である。

- 【図 26】第 4、第 5 の実施形態における変倍処理部のプロック構成を示す図である。

- 【図 27】第 4 の実施形態におけるタイルバッファ制御回路を示すプロック図である。

- 【図 28】タイルバッファ 7 におけるアドレスの一例を示す図である。

- 【図 29】タイル単位で処理を行う場合と、水平方向に 2 タイル連続して処理を行う場合との処理領域の違いを示す図である。

- 【図 30】第 5 の実施形態におけるタイルバッファ制御回路を示すプロック図である。

- 【図 31】タイルバッファのアドレス配置を説明するための図である。

- 【図 32】読み出しあドレスカウンタが従うアドレス生成のためのフローである。

- 【図 33】書き込みアドレスカウンタの回路構成を示す図である 40

- 【図 34】従来の変倍回路の動作概略を示す図である。

- 【図 35】従来の変倍回路の詳細な構成を示すプロック図である。

- 【図 36】フィルタ処理回路の動作を示す図である。

- 【符号の説明】

- 4 タイルスレーブインターフェース

- 5 メモリインターフェース

- 6 変倍プロック

- 7 タイルバッファ

- 8 タイルマスターインターフェース

- 9 レジスタインターフェース 50

2 1 1 6 变倍处理部

2 1 2 3 画像(外部)メモリ

【 四 1 】

【 义 2 】

【 四 3 】

【 四 4 】

【 义 5 】

【 义 6 】

〔四七〕

【 図 8 】

【 四 9 】

【 図 1 0 】

ページ中のタイル数:  $220 \times 156 = 34,320$  個

【図 1 1】

【 図 1 2 】

【习题 1 3】

( 四 1 4 )

【図 1 5】

【図 1 6】

【図 1 7】

【図 1 8】

【図19】

【図20】

【図21】

【図22】

|            |          |          |          |          |          |          |          |          |          |

|------------|----------|----------|----------|----------|----------|----------|----------|----------|----------|

| tFlag0=0 → | (0,8n)   | (1,8n)   | (2,8n)   | (3,8n)   | (4,8n)   | (5,8n)   | (6,8n)   | (7,8n)   | (8,8n)   |

| tFlag1=0 → | (0,8n+1) | (1,8n+1) | (2,8n+1) | (3,8n+1) | (4,8n+1) | (5,8n+1) | (6,8n+1) | (7,8n+1) | (8,8n+1) |

| tFlag2=0 → | (0,8n+2) | (1,8n+2) | (2,8n+2) | (3,8n+2) | (4,8n+2) | (5,8n+2) | (6,8n+2) | (7,8n+2) | (8,8n+2) |

| tFlag3=0 → | (0,8n+3) | (1,8n+3) | (2,8n+3) | (3,8n+3) | (4,8n+3) | (5,8n+3) | (6,8n+3) | (7,8n+3) | (8,8n+3) |

| tFlag4=0 → | (0,8n+4) | (1,8n+4) | (2,8n+4) | (3,8n+4) | (4,8n+4) | (5,8n+4) | (6,8n+4) | (7,8n+4) | (8,8n+4) |

| tFlag5=0 → | (0,8n+5) | (1,8n+5) | (2,8n+5) | (3,8n+5) | (4,8n+5) | (5,8n+5) | (6,8n+5) | (7,8n+5) | (8,8n+5) |

| tFlag6=0 → | (0,8n+6) | (1,8n+6) | (2,8n+6) | (3,8n+6) | (4,8n+6) | (5,8n+6) | (6,8n+6) | (7,8n+6) | (8,8n+6) |

| tFlag7=0 → | (0,8n+7) | (1,8n+7) | (2,8n+7) | (3,8n+7) | (4,8n+7) | (5,8n+7) | (6,8n+7) | (7,8n+7) | (8,8n+7) |

【図23】

|            |          |          |          |          |          |          |          |          |          |

|------------|----------|----------|----------|----------|----------|----------|----------|----------|----------|

| tFlag0=1 → | (0,8n)   | (1,8n)   | (2,8n)   | (3,8n)   | (4,8n)   | (5,8n)   | (6,8n)   | (7,8n)   | (8,8n)   |

| tFlag1=0 → | (0,8n+1) | (1,8n+1) | (2,8n+1) | (3,8n+1) | (4,8n+1) | (5,8n+1) | (6,8n+1) | (7,8n+1) | (8,8n+1) |

| tFlag2=0 → | (0,8n+2) | (1,8n+2) | (2,8n+2) | (3,8n+2) | (4,8n+2) | (5,8n+2) | (6,8n+2) | (7,8n+2) | (8,8n+2) |

| tFlag3=0 → | (0,8n+3) | (1,8n+3) | (2,8n+3) | (3,8n+3) | (4,8n+3) | (5,8n+3) | (6,8n+3) | (7,8n+3) | (8,8n+3) |

| tFlag4=0 → | (0,8n+4) | (1,8n+4) | (2,8n+4) | (3,8n+4) | (4,8n+4) | (5,8n+4) | (6,8n+4) | (7,8n+4) | (8,8n+4) |

| tFlag5=0 → | (0,8n+5) | (1,8n+5) | (2,8n+5) | (3,8n+5) | (4,8n+5) | (5,8n+5) | (6,8n+5) | (7,8n+5) | (8,8n+5) |

| tFlag6=0 → | (0,8n+6) | (1,8n+6) | (2,8n+6) | (3,8n+6) | (4,8n+6) | (5,8n+6) | (6,8n+6) | (7,8n+6) | (8,8n+6) |

| tFlag7=0 → | (0,8n+7) | (1,8n+7) | (2,8n+7) | (3,8n+7) | (4,8n+7) | (5,8n+7) | (6,8n+7) | (7,8n+7) | (8,8n+7) |

【図24】

|            |          |          |          |          |          |          |          |          |          |

|------------|----------|----------|----------|----------|----------|----------|----------|----------|----------|

| tFlag0=1 → | (0,8n)   | (1,8n)   | (2,8n)   | (3,8n)   | (4,8n)   | (5,8n)   | (6,8n)   | (7,8n)   | (8,8n)   |

| tFlag1=1 → | (0,8n+1) | (1,8n+1) | (2,8n+1) | (3,8n+1) | (4,8n+1) | (5,8n+1) | (6,8n+1) | (7,8n+1) | (8,8n+1) |

| tFlag2=1 → | (0,8n+2) | (1,8n+2) | (2,8n+2) | (3,8n+2) | (4,8n+2) | (5,8n+2) | (6,8n+2) | (7,8n+2) | (8,8n+2) |

| tFlag3=1 → | (0,8n+3) | (1,8n+3) | (2,8n+3) | (3,8n+3) | (4,8n+3) | (5,8n+3) | (6,8n+3) | (7,8n+3) | (8,8n+3) |

| tFlag4=1 → | (0,8n+4) | (1,8n+4) | (2,8n+4) | (3,8n+4) | (4,8n+4) | (5,8n+4) | (6,8n+4) | (7,8n+4) | (8,8n+4) |

| tFlag5=1 → | (0,8n+5) | (1,8n+5) | (2,8n+5) | (3,8n+5) | (4,8n+5) | (5,8n+5) | (6,8n+5) | (7,8n+5) | (8,8n+5) |

| tFlag6=1 → | (0,8n+6) | (1,8n+6) | (2,8n+6) | (3,8n+6) | (4,8n+6) | (5,8n+6) | (6,8n+6) | (7,8n+6) | (8,8n+6) |

| tFlag7=1 → | (0,8n+7) | (1,8n+7) | (2,8n+7) | (3,8n+7) | (4,8n+7) | (5,8n+7) | (6,8n+7) | (7,8n+7) | (8,8n+7) |

【図25】

|            |              |              |              |              |              |              |              |              |              |

|------------|--------------|--------------|--------------|--------------|--------------|--------------|--------------|--------------|--------------|

| tFlag0=0 → | (0,8(n+1))   | (1,8(n+1))   | (2,8(n+1))   | (3,8(n+1))   | (4,8(n+1))   | (5,8(n+1))   | (6,8(n+1))   | (7,8(n+1))   | (8,8(n+1))   |

| tFlag1=0 → | (0,8(n+1)+1) | (1,8(n+1)+1) | (2,8(n+1)+1) | (3,8(n+1)+1) | (4,8(n+1)+1) | (5,8(n+1)+1) | (6,8(n+1)+1) | (7,8(n+1)+1) | (8,8(n+1)+1) |

| tFlag2=0 → | (0,8n+2)     | (1,8n+2)     | (2,8n+2)     | (3,8n+2)     | (4,8n+2)     | (5,8n+2)     | (6,8n+2)     | (7,8n+2)     | (8,8n+2)     |

| tFlag3=0 → | (0,8n+3)     | (1,8n+3)     | (2,8n+3)     | (3,8n+3)     | (4,8n+3)     | (5,8n+3)     | (6,8n+3)     | (7,8n+3)     | (8,8n+3)     |

| tFlag4=1 → | (0,8n+4)     | (1,8n+4)     | (2,8n+4)     | (3,8n+4)     | (4,8n+4)     | (5,8n+4)     | (6,8n+4)     | (7,8n+4)     | (8,8n+4)     |

| tFlag5=1 → | (0,8n+5)     | (1,8n+5)     | (2,8n+5)     | (3,8n+5)     | (4,8n+5)     | (5,8n+5)     | (6,8n+5)     | (7,8n+5)     | (8,8n+5)     |

| tFlag6=1 → | (0,8n+6)     | (1,8n+6)     | (2,8n+6)     | (3,8n+6)     | (4,8n+6)     | (5,8n+6)     | (6,8n+6)     | (7,8n+6)     | (8,8n+6)     |

| tFlag7=1 → | (0,8n+7)     | (1,8n+7)     | (2,8n+7)     | (3,8n+7)     | (4,8n+7)     | (5,8n+7)     | (6,8n+7)     | (7,8n+7)     | (8,8n+7)     |

【図26】

【図27】

【図28】

【図29】

【図30】

【図31】

【図32】

【図33】

【図34】

【図35】

【図36】

---

フロントページの続き

(56)参考文献 特開2000-149002(JP,A)

特開平10-304184(JP,A)

国際公開第96/031974(WO,A1)

(58)調査した分野(Int.Cl., DB名)

H04N 1/393

G06T 3/40