(19) 日本国特許庁(JP)

## (12) 特 許 公 報(B2)

(11) 特許番号

特許第4514022号

(P4514022)

(45) 発行日 平成22年7月28日(2010.7.28)

(24) 登録日 平成22年5月21日(2010.5.21)

(51) Int.Cl.

F 1

|                     |                  |                   |             |

|---------------------|------------------|-------------------|-------------|

| <b>H01L 21/8238</b> | <b>(2006.01)</b> | <b>H01L 27/08</b> | <b>321E</b> |

| <b>H01L 27/092</b>  | <b>(2006.01)</b> | <b>H01L 29/78</b> | <b>301L</b> |

| <b>H01L 21/336</b>  | <b>(2006.01)</b> | <b>H01L 29/78</b> | <b>301G</b> |

| <b>H01L 29/78</b>   | <b>(2006.01)</b> |                   |             |

請求項の数 11 (全 10 頁)

|               |                               |

|---------------|-------------------------------|

| (21) 出願番号     | 特願2003-555591 (P2003-555591)  |

| (86) (22) 出願日 | 平成14年12月19日 (2002.12.19)      |

| (65) 公表番号     | 特表2005-514772 (P2005-514772A) |

| (43) 公表日      | 平成17年5月19日 (2005.5.19)        |

| (86) 國際出願番号   | PCT/US2002/041330             |

| (87) 國際公開番号   | W02003/054969                 |

| (87) 國際公開日    | 平成15年7月3日 (2003.7.3)          |

| 審査請求日         | 平成17年12月19日 (2005.12.19)      |

| (31) 優先権主張番号  | 10/022,847                    |

| (32) 優先日      | 平成13年12月20日 (2001.12.20)      |

| (33) 優先権主張国   | 米国(US)                        |

|           |                                                                                                                                                                                                |

|-----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| (73) 特許権者 | 591016172<br>アバンスト・マイクロ・ディバイシズ・<br>インコーポレイテッド<br>ADVANCED MICRO DEVICES INCORPORATED<br>アメリカ合衆国、94088-3453<br>カリフォルニア州、サンノイベイル、ビィ・<br>オウ・ボックス・3453、ワン・エイ・<br>エム・ディ・ブレイス、メイル・ストップ<br>・68 (番地なし) |

| (74) 代理人  | 100108833<br>弁理士 早川 裕司                                                                                                                                                                         |

| (74) 代理人  | 100132207<br>弁理士 太田 昌孝                                                                                                                                                                         |

最終頁に続く

(54) 【発明の名称】電気的にプログラムされたソース／ドレイン直列抵抗を有するMOSトランジスタ

## (57) 【特許請求の範囲】

## 【請求項 1】

半導体デバイスであって、

トランジスタが形成された半導体基板を有し、前記トランジスタは、前記基板上に形成された互いに対向するサイドウォールを備えたゲート電極を含むものであり、

前記基板上に形成されたソース／ドレイン領域及び前記ソース／ドレイン領域よりも薄く形成されるソース／ドレイン伸長領域を含む活性領域を有し、

ゲート電極対向サイドウォールに沿って形成されるとともに当該ゲート電極対向サイドウォールに接している絶縁サイドウォールスペーサを有し、

前記サイドウォールスペーサに埋め込まれ、前記ソース／ドレイン伸長領域を覆うように形成される導電層を有し、前記導電層は、前記ゲート電極及び前記活性領域から電気的に絶縁されているものであり、

前記埋め込まれた導電層は、金属及び金属シリサイドのうちから選択された導電材料を含み、バイアスされることで前記ソース／ドレイン伸長領域に電荷を蓄積する、

半導体デバイス。

## 【請求項 2】

前記活性領域は、ソース及びドレイン領域を含む、

請求項1記載の半導体デバイス。

## 【請求項 3】

前記ゲート電極と前記活性領域間に挿入されたゲート絶縁層を更に含む、

10

20

請求項 1 記載の半導体デバイス。

**【請求項 4】**

前記サイドウォールスペーサは、窒化シリコンを含む、

請求項 1 記載の半導体デバイス。

**【請求項 5】**

前記埋め込まれた導電層の膜厚は、50 ~ 300 である、

請求項 1 記載の半導体デバイス。

**【請求項 6】**

前記サイドウォールスペーサの幅は、300 ~ 2000 である、

請求項 1 記載の半導体デバイス。

10

**【請求項 7】**

前記埋め込まれた導電層の幅は、100 ~ 1800 である、

請求項 1 記載の半導体デバイス。

**【請求項 8】**

前記導電層は、ゲート電極側壁から、50 ~ 500 離間されている、

請求項 1 記載の半導体デバイス。

**【請求項 9】**

前記埋め込まれた導電層には、バイアスがかけられる、

請求項 1 記載の半導体デバイス。

**【請求項 10】**

20

半導体デバイスであって、

トランジスタが形成された半導体基板を有し、前記トランジスタは、前記基板上に形成された互いに対向するサイドウォールを備えたゲート電極を含むものであり、

前記基板上に形成されたソース / ドレイン領域及び前記ソース / ドレイン領域よりも薄く形成されるソース / ドレイン伸長領域を含む活性領域を有し、

ゲート電極対向サイドウォールに沿って形成されるとともに当該ゲート電極対向サイドウォールに接している絶縁サイドウォールスペーサを有し、

前記サイドウォールスペーサに埋め込まれ、前記ソース / ドレイン伸長領域を覆うように形成される導電層を有し、前記導電層は、前記ゲート電極及び前記活性領域から電気的に絶縁されているものであり、

30

前記埋め込まれた導電層は、導電性ポリシリコンを含み、バイアスされることで前記ソース / ドレイン伸長領域に電荷を蓄積する、

半導体デバイス。

**【請求項 11】**

半導体デバイスであって、

トランジスタ (32) が形成された半導体基板を有し、前記トランジスタは、N M O S トランジスタ及びP M O S トランジスタを含み、

前記トランジスタ (32) は、前記基板 (10) 上に形成された互いに対向するサイドウォール (20) を備えたゲート電極 (18) を含み、

前記基板 (10) 上に形成されたソース / ドレイン領域 (28) 及び前記ソース / ドレイン領域 (28) よりも薄く形成されるソース / ドレイン伸長領域 (30) を含む活性領域 (14) を有し、

40

前記ゲート電極対向サイドウォール (20) に沿って形成されるとともに当該ゲート電極対向サイドウォール (20) に接している絶縁サイドウォールスペーサ (27) を有し、

前記サイドウォールスペーサ (27) に埋め込まれ、前記ソース / ドレイン伸長領域 (30) を覆うように形成される導電層 (24) を有し、前記導電層 (24) は、前記ゲート電極 (18) 及び前記活性領域 (14) から電気的に絶縁されているものであり、

前記N M O S トランジスタ及び前記P M O S トランジスタの前記導電層 (24) にバイアスをかけることにより、前記活性領域 (14) のソース / ドレイン伸長領域 (30) に

50

電荷を蓄積することで、ソース／ドレイン伸長領域（30）の抵抗値を低くすることが可能に構成されている、

半導体デバイス。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、金属酸化膜半導体（MOS：metal oxide semiconductor）トランジスタ分野、より具体的には、電気的にプログラムしたソース／ドレイン直列抵抗（source/drain series resistance）を有するMOSトランジスタに関する。

【背景技術】

10

【0002】

半導体業界において、進行中の研究の重要な目的は、半導体デバイスの性能を向上させることである。例えば金属酸化膜半導体電界効果トランジスタ（MOSFET）のようなブレーナトランジスタは、特に高密度の集積回路の使用に適している。MOSトランジスタには一般的に2種類の様式があり、p型ウェハにn型ソース／ドレインが構成されているNチャンネルMOS（NMOS）と、p型ソース／ドレイン領域が構成されているPチャンネルMOS（PMOS）である。NMOSトランジスタは、トランジスタチャンネルを通じて電子を誘導し、一方、PMOSトランジスタは、トランジスタチャンネルを通じて正孔（ホール）を誘導する。一般的に、ソース／ドレイン領域は、n型ソース／ドレイン領域を形成するためにリン又はヒ素でドープされ、一方、p型ソース／ドレイン領域を形成するために、ボロンドーピングが用いられる。

20

【0003】

相補型金属酸化膜半導体（CMOS）デバイスは、同じ基板上にN及びPチャンネルMOSトランジスタを有する。高性能半導体デバイスを製造するためにCMOSデバイスの速度を改善することが要請されている。ソース／ドレイン領域の電気抵抗を削減することは、トランジスタの速度を上げる。CMOSトランジスタを形成するために従来の方法を用いて、効果的な方法で高速トランジスタを製造することが要請されている。

【0004】

30

この中で使用される半導体デバイスという用語は、特定的に開示された実施形態に制限されない。この中で使用される半導体デバイスは、フリップチップ、フリップチップ／パッケージアッセンブリ、トランジスタ、キャパシタ、マイクロプロセッサ、ランダムアクセスメモリ等を含む幅広い多様な電子デバイスを含む。一般的に、半導体デバイスは、半導体を含むあらゆる電気デバイスを示す。

【発明の開示】

【発明が解決しようとする課題】

【0005】

高速度MOSFETを形成するための半導体デバイス技術が要請されている。この技術において、従来のトランジスタ材料から形成されている高速度CMOSを形成するための技術が要請されている。この技術において、削減したソース／ドレイン領域直列抵抗を有するCMOSデバイスを形成するための技術が要請されている。

40

【課題を解決するための手段】

【0006】

こうした要請、又は他の要請は、トランジスタを備えた半導体基板を有する半導体デバイスを形成する本発明の実施形態によって、実現される。このトランジスタは、基板上に互いに対向して形成されたサイドウォールを含むゲート電極を有する。基板上には活性領域が形成される。ゲート電極対向サイドウォールに沿って、かつこれらのゲート電極対向サイドウォールと接触して、絶縁体サイドウォールスペーサが形成される。導電層は、サイドウォールスペーサ内に埋め込まれている。この埋め込まれた導電層は、電気的にゲート電極と活性領域から絶縁している。

【0007】

50

上述した要請は、本発明において、トランジスタを備えた半導体基板を形成する過程を有する半導体デバイスを形成する実施形態によって解決される。このトランジスタは、基板上に形成された対向サイドウォールを有するゲート電極と、基板内に形成された活性領域を含む。第1絶縁層は、ゲート電極と活性領域を覆うように形成され、導電層は、この第1導電層を覆うようにデポジットされる。前述の導電層部分は、ゲート電極と活性領域を覆う第1絶縁層部分を露光するために除去される。第2絶縁層は、導電層と第1絶縁層を覆うように形成される。第1絶縁層と第2絶縁層部分は、ゲート電極拮抗サイドウォールに沿って形成され、接し、中に導電層が埋め込まれているサイドウォールスペーサを形成するために、除去される。

## 【0008】

10

本発明は、例えばCMOSデバイスのような改善した高速トランジスタを提供することを目的としたものである。本発明は、電気的にプログラムされて、ソース／ドレイン領域直列抵抗が減少されたトランジスタを提供するものである。

## 【0009】

本発明の上述した又は他の特性、様相、及び利点は、添付する図面を参照しながら、以下の詳細な説明において明らかになるであろう。

## 【発明を実施するための最良の形態】

## 【0010】

本発明は、改善された高速半導体デバイスの製造を可能にする。本発明は、ソース／ドレイン領域直列抵抗が減少されたMOSトランジスタの製造を可能にする。これらの利点の少なくとも一部は、MOSトランジスタゲートのサイドウォールスペーサ内に電気的に絶縁した導電層を埋め込むことによって達成される。

20

## 【0011】

トランジスタゲートサイドウォールスペースペーサに埋め込まれた絶縁された導電層は、フロート状態とすることもでき、また、バイアス電源に設けられたコンタクトを介してバイアス状態とすることが可能である。埋め込まれた導電層は、埋め込まれた導電層の下方にある浅くドープされたソース／ドレイン領域内に電荷を蓄積するために使用される。この埋め込まれた導電層によって、ソース／ドレイン領域の直列／抵抗のプログラムが可能となる。この際、この埋め込まれた導電層がフロート状態である場合はトランジスタゲートによって上述のプログラム（設定）がなされる。また、埋め込まれた導電層がバイアス状態である場合、バイアス電位によって上述のプログラムがなされる。

30

## 【0012】

本発明は、添付する図面を説明しながら、半導体デバイスの形成に関連して記載される。しかしながら、これは、本発明の請求項範囲の例示のみのためであって、図面に説明された特定的なデバイスの形成に限定されない。

## 【0013】

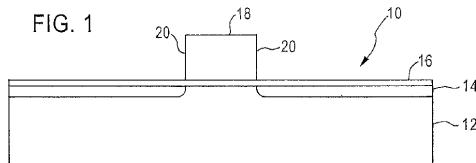

図1に示すように、例えばシリコンウェハのような、活性領域（14）が形成したベース層（12）を含む半導体基板（10）が用意される。ゲート絶縁層（16）は、活性領域（14）を覆うように形成される。一般的に、ゲート絶縁層（16）は、半導体基板の熱酸化、又は例えば化学気相成長法（CVD）のようなデポジション技術によって形成された、約100から約1000までの膜厚を有する酸化層である。半導体基板（10）は、さらに、ゲート絶縁層（16）に形成された互いに対向するサイドウォール（20）を有するゲート電極（18）を含む。このゲート電極（18）は、一般的に約100から約5000までの膜厚を有するポリシリコン層を含む。本発明の若干の実施形態において、ゲート電極（18）は、約100から約100までの膜厚を有する。

40

## 【0014】

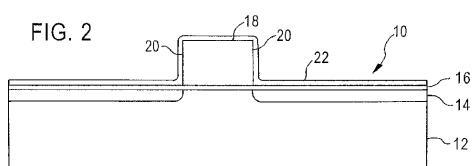

図2に示すように、第1絶縁層（22）は、ゲート電極（18）を覆うように形成される。ある実施形態においては、この第1絶縁層（22）は、約50から約300までの膜厚を有する窒化シリコン層である。これに代えて、第1絶縁層（22）は、ゲート電極（18）、活性領域（14）、又は他の適切な絶縁層の熱酸化によって形成された酸化

50

層としてもよい。

**【0015】**

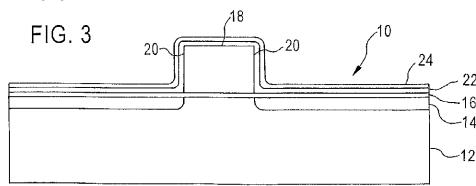

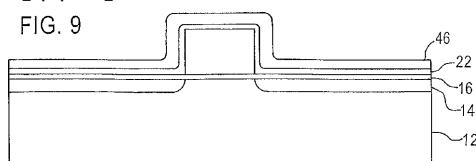

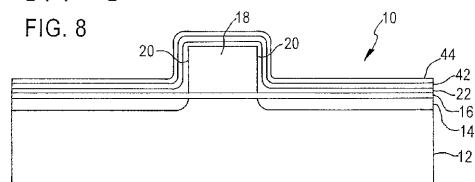

図3に示すように、約50から約300までの膜厚を有する導電層(24)は、第1絶縁層(22)を覆うように形成される。この導電層(24)は、例えば、ポリシリコン、金属、又は金属ケイ化物(metal silicide)である。ポリシリコン層は、一般にはCVD技術によってデポジションされる。例えばアルミニウム、チタン、タングステン、ニッケル、及びコバルトのような金属層は、CVD又はスパッタリングのような従来の金属デポジション技術によって、デポジットされる。これに代えて、本発明のある実施形態においては、図8に示すように、導電層は、ポリシリコン層をデポジットし、その後にチタン、タングステン、ニッケル、又はコバルトのような金属層(44)をデポジットすることによって形成される金属シリサイドである。図9に示すように、金属ケイ化物の生成は半導体基板(10)を、金属シリサイド層(46)が形成されるように、ポリシリコン層(42)が金属層(44)と反応するに十分な温度まで熱することによって行われる。

10

**【0016】**

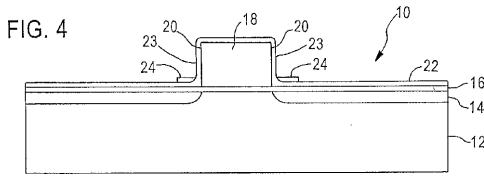

導電層24は、導電層24の一部を除去して、ゲート電極(18)を覆う第1絶縁層と、活性領域(14)を覆う部分と、が露出されるようにパターンが選択的に形成され、また、図4に示されるように、導電層(24)における、互いに対向するゲート電極サイドウォール(20)に隣接した部分が残るようにパターン形成がなされる。

導電層(24)における残された部分の幅は、約100から約1800である。導電層(24)は、例えば等方性エッチング、異方性エッチング、又は等方性エッチングと異方性エッチングの組み合わせのような、従来のマスキングとエッチング技術によってパターン形成がされる。使用されるエッチング技術と特定のエッチング液は、導電層材料の特定的な種類の除去のために適切である、周知の技術とエッチング液から選択される。

20

**【0017】**

本発明のある実施形態においては、導電層(24)は、選択的マスキングと異方性エッチングによりパターン形成がなされ、その後、パターンされた導電層(24)が得られるように第2マスキングとその後の等方性エッチングがなされる。図4に示すように、パターンした導電層(24)を形成するために、その後の等方性エッチでは、異方性エッチングの後で第1絶縁層(22)のサイドウォール部分(23)に沿って残る導電層部分(24)を除去する。実施形態によっては、第2マスキングとその後の等方性エッチを実行しない場合もある。

30

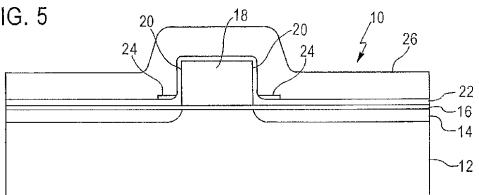

**【0018】**

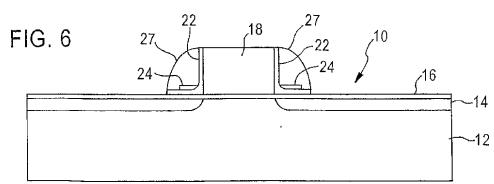

選択的に導電層(24)を除去した後で、図5に表すように、残され導電層(24)と第1絶縁層(22)とを覆うように第2絶縁層(26)がデポジットされる。第2絶縁層は、一般的に約300から約2000までの膜厚を有するCVD窒化シリコン層である。第2絶縁層(26)は、その後、図6に示すように、埋め込まれた導電層(24)を有するサイドウォールスペーサ(27)を形成するように、例えばプラズマエッチングのような従来の異方性エッチングを用いて、異方性エッチされる。実施形態によっては、酸化ゲート絶縁層(16)を用いると、窒化シリコン層(22, 26)をエッチングしてサイドウォールスペーサ(27)を形成するためのエッチストップとして有用である。

40

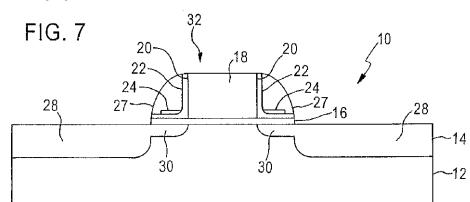

**【0019】**

ソース/ドレインを深くイオン注入している間、サイドウォールスペーサ(27)は、浅くドープしたソース/ドレイン伸長領域(30)をマスクする。活性領域(14)を露出させるためのソース/ドレインへ深いイオン注入は、ゲート絶縁層(16)をエッチングする前又は後のどちらで行ってもよい。ゲート絶縁層(16)は、異方性エッチング又は等方性エッチングのどちらかによって、エッチされる。実施形態によっては、酸化シリコンを有するゲート絶縁層(16)は、例えばバッファード酸化物エッチ(buffered oxide etch)又はフッ化水素酸のような、シリコン酸化物に対して選択性を有するエッチング液を用いてエッチされる。

**【0020】**

図7に示すように、本発明に従って形成されたMOSトランジスタの活性領域(14)は、ソース／ドレイン領域(28)と浅くドープされたソース／ドレイン伸長領域(30)とを有する。埋め込まれた導電層(24)は、ソース／ドレイン伸長領域(30)を覆うように配置され、ゲート電極(18)と活性領域(14)から電気的に絶縁されている。

#### 【0021】

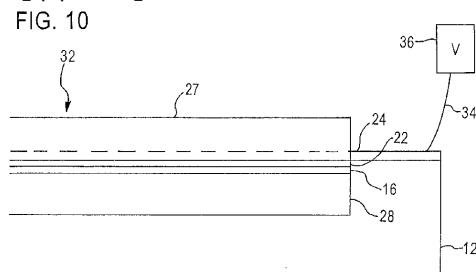

埋め込まれた導電層(24)は、図7に示すように電気的にフロート状態としても、あるいは、図10に示すようにバイアスされてもよい。例えば、埋め込まれた導電層をポテンシオスタット(potentiostat)のような電源に接続することによって、導電層(24)をバイアスすることが可能である。トランジスタ(32)の断面図(図10)に示すように、電源(36)からは、埋め込まれた導電層(24)に対してリード線を介してバイアスがかけられる。実施形態においては、NMOSトランジスタの埋め込まれた導電層(24)は、負電位方向にバイアスがかけられ、PMOSトランジスタの埋め込まれた導電層は、正電位方向にバイアスがかけられることになる。

10

#### 【0022】

CMOSデバイスは、本発明に従って同じ基板にNMOSトランジスタとPMOSトランジスタを形成することによって得られる。NMOSとPMOSの埋め込まれた導電層(24)に対してのそれぞれ異なるバイアスに加えて、本発明に係るCMOSデバイスでは、フローティング状態の埋め込まれた導電層(24)を有するNMOSトランジスタとPMOSトランジスタを含むことができる。

20

#### 【0023】

本発明のトランジスタは、高速デバイスを形成するようMOSトランジスタのソース／ドレイン領域直列抵抗をプログラムする能力を用意する。本発明のある実施形態によると、トランジスタ(32)のソース／ドレイン領域(28)の電気的抵抗は、埋め込まれた導電層(24)へのバイアスを調節することによって、あるいは、埋め込まれた導電層(24)に使用された材料の種類を選択することによって、所望の電気的直列抵抗が得られるように「プログラム」可能、つまり「設定」することが可能である。所望のソース／ドレイン領域直列抵抗の選択に影響する因子としては、チャンネル寸法、ドーパントの濃度、要求されるトランジスタ速度、及びCMOSデバイスのバランスをとることが挙げられる。NMOSトランジスタ内の電子の移動度は、通常、PMOSトランジスタ内の正孔(ホール)の移動度より高いため、CMOSデバイスは、概してバランスが取れていない。埋め込まれた導電層(24)を使用することで、NMOSトランジスタとPMOSトランジスタの活性領域(14)の直列抵抗が個別にプログラム可能になり、よりバランスの取れたCMOSを実現可能となる。

30

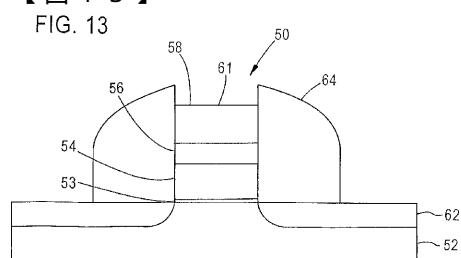

#### 【0024】

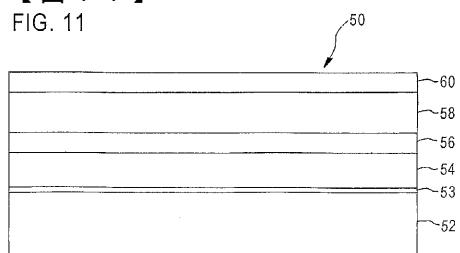

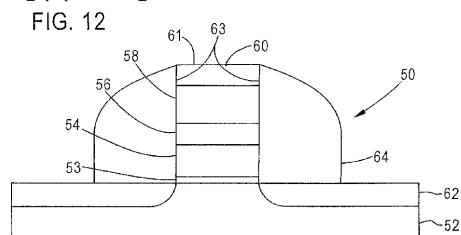

他の形態において、矩形状のサイドウォールスペーサを有する半導体デバイスが半導体基板に形成される。例えばシリコンウェハのような半導体基板(52)を有してこの半導体基板(52)を覆うように形成されたゲート絶縁層(53)を備えた半導体デバイス(50)が用意される。図11に示すように、ゲート絶縁層(53)を覆うようにポリシリコン層(54)が形成され、ポリシリコン層(54)を覆うように第1窒化シリコン層が形成される。第1窒化シリコン層(56)を覆うように酸化シリコン層(58)が形成され、第2窒化シリコン層(60)は、反射防止膜(BARC)として、酸化シリコン層(58)を覆うように形成される。

40

#### 【0025】

ゲート絶縁層(53)、ポリシリコン層(54)、第1窒化シリコン層(56)、酸化シリコン層(58)、及び窒化シリコン層(60)が形成された半導体デバイス(50)は、互いに対向するサイドウォール(63)を備えた積層構造(61)を形成するためにパターンされる。その後、浅くドープされたソース／ドレイン伸長領域(62)を形成するために半導体デバイス(50)がイオン注入にさらされる。ソース／ドレイン伸長領域(62)を形成した後、積層構造(61)と半導体基板は、絶縁材料の層で覆われ、図1

50

2に示すように、この絶縁材料は、積層構造の互いに対向するサイドウォール(63)に沿って、サイドウォールスペーサ(64)が形成されるように異方性エッチが行われる。

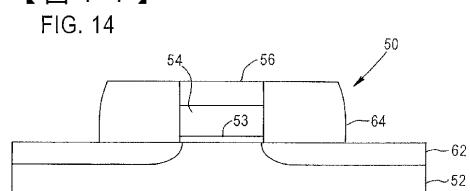

#### 【0026】

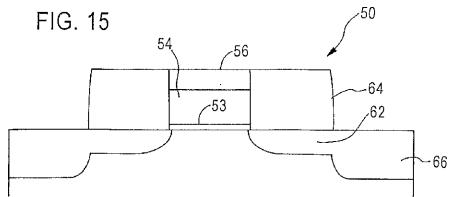

第2窒化シリコン層(60)は、図13に示すように積層構造(61)から除去される。積層構造(61)とサイドウォールスペーサ(64)の高さを削減するために半導体デバイス(50)は、化学機械研磨(CMP)が行われ、図14に示す矩形形状のサイドウォールスペーサ(64)が形成される。第1窒化シリコン層(56)は、CMPの間、ポリッシュのストップ(polish stop)として機能する。次に、図15に示すように、半導体デバイス(50)のソース/ドレイン領域(66)を形成するために、半導体デバイス(50)は深いイオン注入にさらされる。

10

#### 【0027】

本発明の開示において明示された実施形態は、説明目的に示されたに過ぎない。これらは、請求項の範囲を制限するために解釈されてはならない。当業者にとって、明らかなように本開示は、ここに特定的に明示されたものに限定されるのではなく、幅広い多様な実施形態を含む。

#### 【図面の簡単な説明】

#### 【0028】

【図1】ソース/ドレイン領域直列抵抗が小さいMOSトランジスタ構造を示す概略図。

【図2】ソース/ドレイン領域直列抵抗が小さいMOSトランジスタ構造を示す概略図。

【図3】ソース/ドレイン領域直列抵抗が小さいMOSトランジスタ構造を示す概略図。

20

【図4】ソース/ドレイン領域直列抵抗が小さいMOSトランジスタ構造を示す概略図。

【図5】ソース/ドレイン領域直列抵抗が小さいMOSトランジスタ構造を示す概略図。

【図6】ソース/ドレイン領域直列抵抗が小さいMOSトランジスタ構造を示す概略図。

【図7】ソース/ドレイン領域直列抵抗が小さいMOSトランジスタ構造を示す概略図。

【図8】金属シリサイド導電層の構造の説明図。

【図9】金属シリサイド導電層の構造の説明図。

【図10】バイアスがかけられた埋め込まれた導電層の説明図。

【図11】矩形状のサイドウォールスペーサを有するトランジスタ構造を示す概略図。

【図12】矩形状のサイドウォールスペーサを有するトランジスタ構造を示す概略図。

【図13】矩形状のサイドウォールスペーサを有するトランジスタ構造を示す概略図。

30

【図14】矩形状のサイドウォールスペーサを有するトランジスタ構造を示す概略図。

【図15】矩形状のサイドウォールスペーサを有するトランジスタ構造を示す概略図。

【図 1】

【図 2】

【図 3】

【図 4】

【図 9】

【図 10】

【図 11】

【図 5】

【図 6】

【図 7】

【図 8】

【図 12】

【図 13】

【図 14】

【図 15】

FIG. 15

---

フロントページの続き

(74)代理人 100162156

弁理士 村雨 圭介

(74)代理人 100099324

弁理士 鈴木 正剛

(74)代理人 100111615

弁理士 佐野 良太

(74)代理人 100108604

弁理士 村松 義人

(72)発明者 ジェイムズ エフ. ピュラー

アメリカ合衆国、テキサス州 78759、オースティン、インディカ コウブ 6908

(72)発明者 キ シャン

アメリカ合衆国、カリフォルニア州 95129、サン ノゼ、テムズ ドライブ 1119

(72)発明者 デリック ジェイ. リスタートーズ

アメリカ合衆国、テキサス州 78738、ビー ケイブズ、オーバーランド パス 13710

審査官 粟野 正明

(56)参考文献 特開昭63-025967(JP,A)

特開平10-144918(JP,A)

(58)調査した分野(Int.Cl., DB名)

H01L 21/8238

H01L 21/336

H01L 27/092

H01L 29/78

H01L 29/788

H01L 29/792

H01L 27/115

H01L 21/8247